(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-78379

(P2012-78379A)

(43) 公開日 平成24年4月19日(2012.4.19)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/30 | Z 5C080     |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 641D 5C380  |

|                             | G09G 3/20 | 642P        |

|                             | G09G 3/20 | 611H        |

審査請求 未請求 請求項の数 11 O L (全 16 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2010-220553 (P2010-220553) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地  |

| (22) 出願日  | 平成22年9月30日 (2010.9.30)       | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号     |

|           |                              | (74) 代理人 | 110000154<br>特許業務法人はるか国際特許事務所                  |

|           |                              | (72) 発明者 | 秋元 肇<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内      |

|           |                              | (72) 発明者 | 河野 亨<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】

【課題】従来技術における有機EL表示装置においては、駆動トランジスタの特性の検出を高精度かつ高速度で行うことができない。

【解決手段】表示装置であって、発光素子と、階調値に応じた電流を前記発光素子に供給する駆動トランジスタと、をそれぞれ有する複数の画素と、前記各駆動トランジスタの特性を検出する検出手段と、前記各発光素子の発光後に、前記各駆動トランジスタのゲート・ソース間に第1の電圧信号を供給する手段と、前記第1の電圧信号が供給された後、前記各駆動トランジスタのゲート・ソース間に、前記第1の電圧信号とは異なる第2の電圧信号を供給する手段とを有し、前記検出手段は、前記第2の電圧信号を供給する期間に、前記各駆動トランジスタの特性を検出し、前記第1の電圧信号は、前記第2の電圧信号に比べ、前記駆動トランジスタのソース・ドレイン間により多くの電流を供給可能な電圧を有する電圧信号である。

【選択図】図3

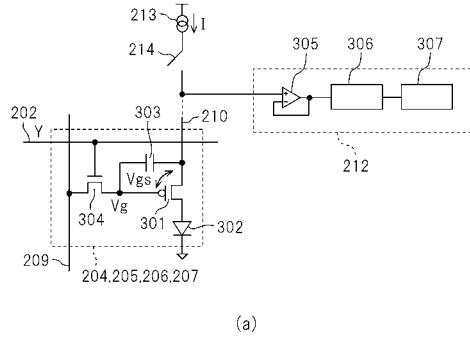

(a)

(b)

**【特許請求の範囲】****【請求項 1】**

発光素子と、階調値に応じた電流を前記発光素子に供給する駆動トランジスタと、をそれぞれ有する複数の画素と、前記各駆動トランジスタの特性を検出する検出手段と、前記各発光素子の発光後に、前記各駆動トランジスタのゲート・ソース間に第1の電圧信号を供給する手段と、前記第1の電圧信号が供給された後、前記各駆動トランジスタのゲート・ソース間に、前記第1の電圧信号とは異なる第2の電圧信号を供給する手段とを有し、前記検出手段は、前記第2の電圧信号を供給する期間に、前記各駆動トランジスタの特性を検出し、

前記第1の電圧信号は、前記第2の電圧信号に比べ、前記駆動トランジスタのソース・ドレイン間により多くの電流を供給可能な電圧を有する電圧信号であることを特徴とする表示装置。 10

**【請求項 2】**

前記第2の電圧信号を供給する期間は、前記第1の電圧信号を供給する期間よりも長いことを特徴とする請求項1記載の表示装置。

**【請求項 3】**

前記表示装置は、更に、前記検出手段の検出結果に基づいて、前記各複数の画素へ供給するデータ信号を補正する補正手段を有することを特徴とする請求項1又は2記載の表示装置。 20

**【請求項 4】**

前記検出手段は、前記各駆動トランジスタのソースへ定電流を供給する電流源を有し、前記検出手段は、前記各駆動トランジスタのソース電位を検出することを特徴とする請求項1乃至3のいずれかに記載の表示装置。

**【請求項 5】**

前記検出手段は、前記各駆動トランジスタのソースへ定電圧を供給する電圧源を有し、前記検出手段は、前記各発光素子の一端における電位を検出することを特徴とする請求項1乃至3のいずれかに記載の表示装置。

**【請求項 6】**

前記発光素子は、有機発光ダイオードであることを特徴とする請求項1乃至5のいずれかに記載の表示装置。 30

**【請求項 7】**

前記駆動トランジスタは、TFTであることを特徴とする請求項1乃至5のいずれかに記載の表示装置。

**【請求項 8】**

前記TFTは、多結晶Si半導体デバイスであることを特徴とする請求項7に記載の表示装置。

**【請求項 9】**

前記TFTは、微結晶Si半導体デバイスであることを特徴とする請求項7に記載の表示装置。

**【請求項 10】**

前記TFTは、アモルファス半導体デバイスであることを特徴とする請求項7に記載の表示装置。 40

**【請求項 11】**

前記TFTは、酸化物半導体デバイスであることを特徴とする請求項7に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示素子に関し、特には、自発光素子を有する表示装置に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

近年、有機発光ダイオード (Organic Light Emitting Diode) に代表される有機 E L (Organic Electro-luminescent) 素子と呼ばれる自発光体を用いた表示装置 (以下、「有機 E L 表示装置」という。) が実用化段階にある。この有機 E L 表示装置は、従来の液晶表示装置と比較して、自発光体を用いているため、視認性、応答速度の点で優れているだけでなく、バックライトのような補助照明装置を要しないため、更なる薄型化が可能となっている。

**【0003】**

このような有機 E L 表示装置は、マトリクス状に多数の画素を配置した表示パネルを有する。そして、各画素は、有機 E L 素子と当該有機 E L 素子を駆動する駆動トランジスタを含む。当該駆動トランジスタは、一般に薄膜トランジスタ (Thin Film-Transistor) で構成されることから、製造上の問題等により、当該各駆動トランジスタの閾値電圧にバラツキが生じる。よって、各画素の発光特性にバラツキが生じ、結果として、表示パネルの表示が不均一になるという問題がある。

10

**【0004】**

そこで、次のような従来技術における有機 E L 表示装置が知られている。当該有機 E L 表示装置においては、各画素に流れる電流を検出し、当該検出した電流値に基づいて補正用オフセットを算出する。そして、画像データに当該補正用オフセットを付加することにより、画面の表示の不均一の発生を防止する (下記特許文献 1、2 参照)。あるいは、駆動トランジスタのソースに定電流源を接続してその電圧を計測することにより閾値電圧のバラツキを検出する方法も提案されている (下記特許文献 3 参照)。

20

**【先行技術文献】****【特許文献】****【0005】**

【特許文献 1】特開 2004 - 264793 号公報

【特許文献 2】特開 2005 - 284172 号公報

【特許文献 3】特開 2010 - 170079 号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

30

しかしながら、上記従来技術における有機 E L 表示装置においては、駆動トランジスタの特性の検出精度を高くすると、検出時間が長くなってしまうという課題がある。

**【0007】**

具体的には、駆動トランジスタにおけるヒステリシスの影響を考慮すると、駆動トランジスタの特性が安定した状態になるまでの待機時間として、数 msec の待機時間が必要となる。ここで、充分な待機時間を確保しない場合には、当該ヒステリシスの影響を受けるため、検出精度が大幅に低下するという問題がある。一方、電圧レンジを考慮した場合、最大でも 1 画素あたり  $\mu$  A オーダー程度の電流しか流すことができず、検出速度が制限され、結果として、十分な待機時間を確保できないという問題がある。

40

**【0008】**

そこで、本発明は、各画素に含まれる駆動トランジスタの特性を高精度かつ高速度で検出することができる表示装置を提供することを目的とする。

**【課題を解決するための手段】****【0009】**

本発明の表示装置は、発光素子と、階調値に応じた電流を前記発光素子に供給する駆動トランジスタと、をそれぞれ有する複数の画素と、前記各駆動トランジスタの特性を検出する検出手段と、前記各発光素子の発光後に、前記各駆動トランジスタのゲート・ソース間に第 1 の電圧信号を供給する手段と、前記第 1 の電圧信号が供給された後、前記各駆動トランジスタのゲート・ソース間に、前記第 1 の電圧信号とは異なる第 2 の電圧信号を供給する手段とを有し、前記検出手段は、前記第 2 の電圧信号を供給する期間に、前記各駆

50

動トランジスタの特性を検出し、前記第1の電圧信号は、前記第2の電圧信号に比べ、前記駆動トランジスタのソース・ドレイン間により多くの電流を供給可能な電圧を有する電圧信号であることを特徴とする。

【0010】

本発明の表示装置において、前記第2の電圧信号を供給する期間は、前記第1の電圧信号を供給する期間よりも長いことを特徴としてもよい。

【0011】

本発明の表示装置において、前記表示装置は、更に、前記検出手段の検出結果に基づいて、前記各複数の画素へ供給するデータ信号を補正する補正手段を有することを特徴としてもよい。

10

【0012】

本発明の表示装置において、前記検出手段は、前記各駆動トランジスタのソースへ定電流を供給する電流源を有し、前記検出手段は、前記各駆動トランジスタのソース電位を検出することを特徴としてもよい。

【0013】

本発明の表示装置において、前記検出手段は、前記各駆動トランジスタのソースへ定電圧を供給する電圧源を有し、前記検出手段は、前記各発光素子の一端における電位を検出することを特徴としてもよい。

20

【0014】

本発明の表示装置において、前記発光素子は、有機発光ダイオードであることを特徴としてもよい。

【0015】

本発明の表示装置において、前記駆動トランジスタは、TFTであることを特徴としてもよい。

【0016】

本発明の表示装置において、前記TFTは、多結晶Si半導体デバイスであることを特徴としてもよい。

30

【0017】

本発明の表示装置において、前記TFTは、微結晶Si半導体デバイスであることを特徴としてもよい。

【0018】

本発明の表示装置において、前記TFTは、アモルファス半導体デバイスであることを特徴としてもよい。

【0019】

本発明の表示装置において、前記TFTは、酸化物半導体デバイスであることを特徴としてもよい。

40

【発明の効果】

【0020】

各画素に含まれる駆動トランジスタの特性を高精度かつ高速度で検出することができる表示装置を提供することができる。

【図面の簡単な説明】

【0021】

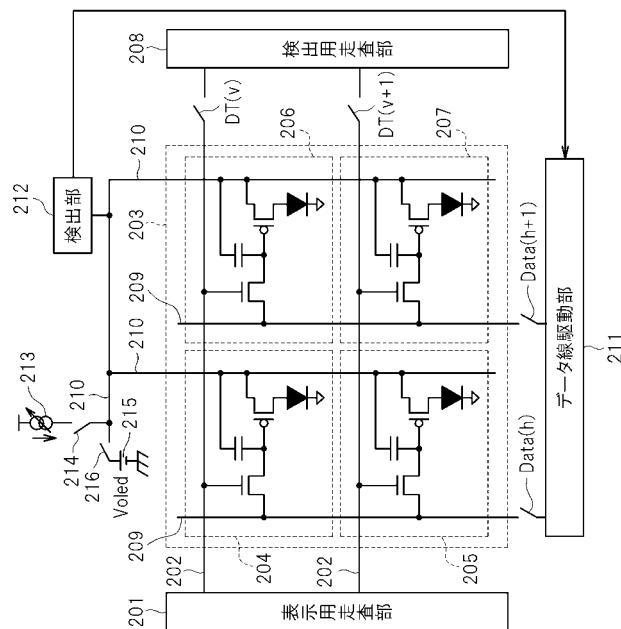

【図1】本発明の実施の形態における表示装置を示す図である。

【図2】図1に示した表示装置の構成を説明するための図である。

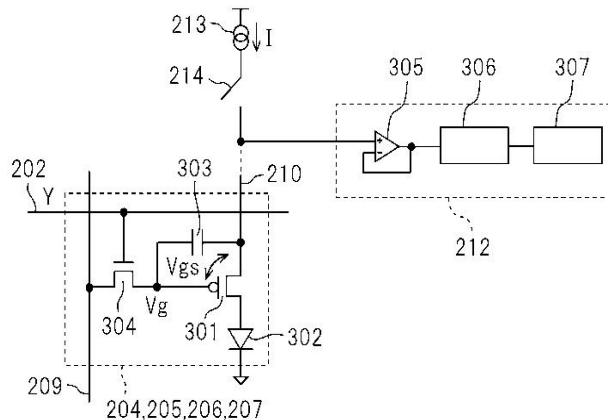

【図3】図1に示した表示装置の構成を説明するための図である。

【図4】図1に示したデータ線駆動部の構成を説明するための図である。

【図5】駆動トランジスタの特性の検出動作の概要について説明するための図である。

【図6】画素に含まれる駆動トランジスタのヒステリシス特性について説明するための図である。

【図7】画素に含まれる駆動トランジスタのヒステリシス特性について説明するための図

50

である。

【図 8】画素に含まれる駆動トランジスタのヒステリシス特性について説明するための図である。

【図 9】表示装置全体としての検出動作の際に制御される信号のタイミングチャートについて説明するための図である。

【図 10】本実施の形態における表示装置の実装についての例を説明するための図である。

【図 11】本実施の形態における表示装置の実装についての例を説明するための図である。

【図 12】本発明の変形例における各画素及び検出部を説明するための図である。

【図 13】変形例における駆動トランジスタの特性の検出動作の概要について説明するための図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面については、同一又は同等の要素には同一の符号を付し、重複する説明は省略する。

【0023】

図1は、本発明の実施の形態に係る表示装置を示す図である。図1に示すように、表示装置100は、表示パネルを有するTFT (Thin Film Transistor) 基板200を挟むように固定する上フレーム110及び下フレーム120と、表示する情報を生成する回路素子を備える回路基板140と、その回路基板140において生成されたRGBの情報をTFT基板200に伝えるフレキシブル基板130と、により構成される。

【0024】

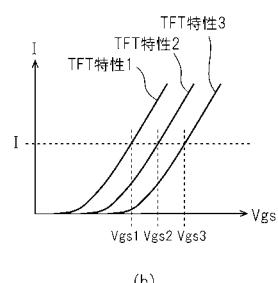

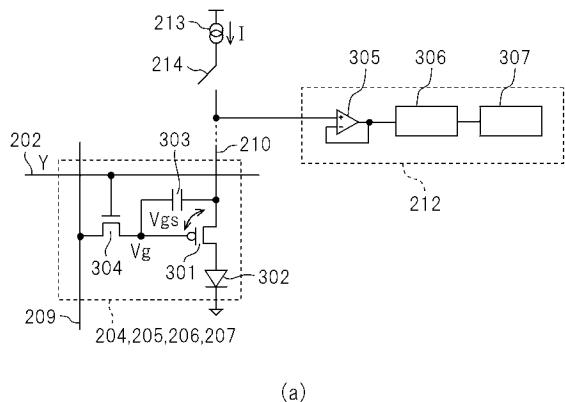

図2及び図3は、図1に示した表示装置の構成を説明するための図である。図2に示すように、表示装置100は、表示用走査部201、表示領域203、検出用走査部208、データ線駆動部211等を有する。なお、図2においては、説明の簡略化のため、DT(v)、Dt(v+1)、及び、Data(h)、Data(h+1)で表したスイッチを、それぞれ検出用走査部208及びデータ線駆動部211の外部に示しているが、実際には検出用走査部208及びデータ線駆動部211の内部に形成される。

【0025】

また、表示用走査部201、検出用走査部208、データ線駆動部211は、各々別々のLSI等で形成してもよいし、1つのLSI等で形成してもよい。また、表示用走査部201、検出用走査部208、データ線駆動部211等は、例えば、TFT基板200上に形成される。

【0026】

表示用走査部201は、走査線202を介して、表示領域203へ表示用走査信号を出力することにより、表示動作時にデータ信号を書き込む画素204、205、206、207や発光させる画素204、205、206、207を選択する。

【0027】

なお、走査線202は、図2に示すように、マトリクス状に配置された各画素204、205、206、207の行方向に、検出線210及びデータ線209は、マトリクス状に配置された各画素204、205、206、207の列方向に、配置される。

【0028】

検出用走査部208は、走査線202を介して、表示領域203へ検査用走査信号を出力することにより、検出動作時にトラップ電圧及びデトラップ電圧を付加する画素204、205、206、207を選択する。

【0029】

ここで、トラップ電圧とは、実際に駆動トランジスタ301の特性を検出する期間であるデトラップ期間において、駆動トランジスタ301のヒステリシスにおける変動を十分に抑制するために、駆動トランジスタ301のゲートに印加する電圧に相当する。また、

10

20

30

40

50

デトラップ電圧とは、上記デトラップ期間において、駆動トランジスタ 301 のゲートに印加する電圧に相当する。なお、当該トランジスタ、デトラップ電圧等については、後に詳述する。

#### 【0030】

また、上記表示動作とは、各画素 204、205、206、207 の表示に関する動作をいい、具体的には、各画素 204、205、206、207 へのデータ信号の書き込み動作や、各画素 204、205、206、207 の発光についての動作等に相当する。検出動作とは、各画素 204、205、206、207 に含まれる各駆動トランジスタ 301 の特性の検出に関する動作をいうが、具体的には後述する。なお、当該検出動作は、例えば、上記表示動作の発光期間と書き込み動作の間に行われてもよいし、または、表示装置 100 が、例えば、携帯電話等である場合には、携帯電話の折りたたみ時等、画面の表示を行う必要がない時間に行われてもよい。

10

#### 【0031】

表示領域 203 は、マトリクス状に配置された複数の画素 204、205、206、207 を有する。また、各画素 204、205、206、207 は、駆動トランジスタ 301、有機 EL 素子 302、容量 303、セレクトスイッチ 304 を有する。なお、図 2 においては、図面の簡略化のため、4 の画素 204、205、206、207 のみを示しているが、必要に応じてその他の数が用いられることはいうまでもない。

20

#### 【0032】

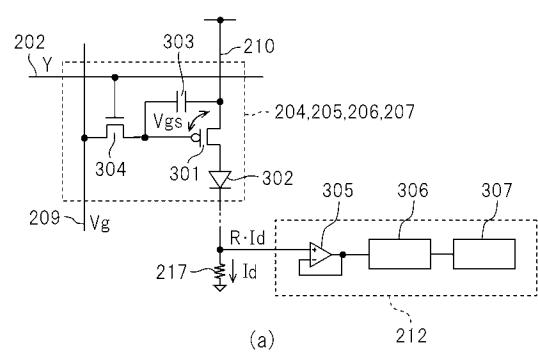

図 3 (a) に示すように、駆動トランジスタ 301 は、ソースが、容量 303 の一端に接続され、ドレインが有機 EL 素子 302 のアノードに接続され、ゲートがセレクトスイッチ 304 のドレインに接続される。

20

#### 【0033】

有機 EL 素子 302 は、アノードが上述のように接続され、カソードは、接地される。

#### 【0034】

セレクトスイッチ 304 は、ゲートが走査線 202 に接続され、ソースがデータ線 209 に接続され、ドレインが、容量 303 の他端に接続される。

30

#### 【0035】

容量 303 は、一端が駆動トランジスタ 301 のソースに接続され、他端が駆動トランジスタ 301 のゲート及びセレクトスイッチ 304 のドレインに接続される。

#### 【0036】

電流源 213 は、駆動トランジスタ 301 のソースにスイッチ 214 を介して、接続され、検出期間に各検出線 210 に定電流 I を出力する。また、電圧源 215 は、スイッチ 216 を介して、駆動トランジスタ 301 のソースに接続され、表示動作時に駆動トランジスタ 301 を駆動する電源 Voleed を供給する。また、スイッチ 214 は、駆動トランジスタ 301 の特性を検出する検出動作時にオンし、スイッチ 216 は、表示装置 100 の表示動作時にオンする。

40

#### 【0037】

また、表示動作時には、表示用走査部 201 からの信号に応じてセレクトスイッチ 304 がオンし、容量 303 に、後述するデータ線駆動部 211 からのデータ信号に対応した信号が書き込まれる。そして、駆動トランジスタ 301 が、当該書き込まれた信号に応じて有機 EL 素子 302 を発光させることにより、表示領域 203 は、画像を表示する。なお、当該表示装置 100 の表示動作は周知であるため、詳細な説明については省略する。

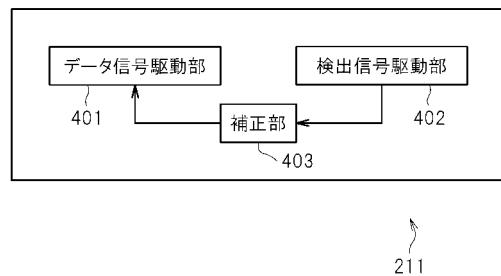

#### 【0038】

データ線駆動部 211 は、図 4 に示すようにデータ信号駆動部 401、検出信号駆動部 402、補正部 403 を有する。データ信号駆動部 401 は、表示装置 100 の表示動作時に、データ線 209 を介して、表示する画素 204、205、206、207 の階調値に対応するデータ信号を各画素 204、205、206、207 に出力する。

#### 【0039】

検出信号駆動部 402 は、当該表示装置 100 の検出動作時に、データ線 209 を介し

50

てトラップ電圧及びデトラップ電圧を各画素 204、205、206、207 の駆動トランジスタ 301 のゲートに出力する。

【0040】

補正部 403 は、検出部 212 からの各駆動トランジスタ 301 のソース電圧、及び、検出期間における検出信号駆動部 402 からの対応する各駆動トランジスタ 301 のゲートに与えられるデトラップ電圧から、各駆動トランジスタ 301 の閾値電圧  $V_{th}$  を求める。

【0041】

具体的には、後述するデトラップ期間に、セレクトスイッチ 304 がオンすると、データ線 209 から駆動トランジスタ 301 のゲート端子にゲート電圧 ( $V_g$ ) が与えられる。検出部 212 は、当該状態において、駆動トランジスタ 301 のソース端子の電圧を検出する。

10

【0042】

ここで、データ線 209 に与える電圧  $V_g$  から駆動トランジスタ 301 の閾値電圧  $V_{th}$  の絶対値を引いた値であるオーバードライブ電圧より、駆動トランジスタ 301 のソース・ドレイン間電圧  $V_{ds}$  が充分に大きい条件では、駆動トランジスタ 301 は、飽和領域を保つ。したがって、検出電圧 (ソース電圧) とデータ線 209 に与える電圧 (ゲート電圧  $V_g$ ) から、電流源 213 から定電流  $I$  を駆動トランジスタ 301 に流した時の駆動トランジスタ 301 のゲート・ソース間電圧  $V_{gs}$  を検出することができる。このゲート・ソース間電圧  $V_{gs}$  は、駆動トランジスタ 301 の持つ閾値電圧  $V_{th}$  のバラツキに対応する。よって、当該ゲート・ソース間電圧  $V_{gs}$  から、駆動トランジスタ 301 の持つ閾値電圧  $V_{th}$  を求めることができる。

20

【0043】

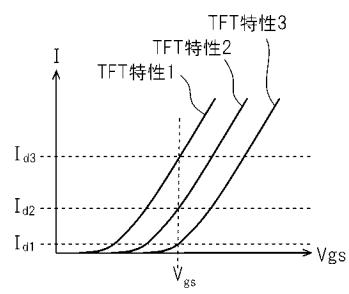

例えば、図 3 (b) に示したように、各画素 204、205、206、207 に含まれる駆動トランジスタ 301 のトランジスタ特性は、TFT 特性 1 乃至 3 のいずれかとなる。そして、当該 TFT 特性 1 乃至 3 のそれぞれに対応するゲート・ソース間電圧  $V_{gs1}$  乃至  $V_{gs3}$  を検出することにより、各駆動トランジスタ 301 の閾値電圧  $V_{th}$  を求めることができる。なお、図 3 の例においては、当該ゲート電圧  $V_g$  がデトラップ電圧に相当するが、詳細には後述する。

30

【0044】

上記のように、補正部 403 は、検出部 212 からの各駆動トランジスタ 301 のソース電圧、及び、検出信号駆動部 402 から対応する各駆動トランジスタ 301 のゲートに与えられるゲート電圧  $V_g$  に基づいて、各駆動トランジスタ 301 の閾値電圧を求める。そして、当該各駆動トランジスタ 301 の閾値電圧  $V_{th}$  のバラツキに基づき、各画素 204、205、206、207 の輝度のバラツキが少なくなるようにデータ信号を補正する補正信号を算出し、データ信号駆動部 401 に出力する。

40

【0045】

なお、データ信号駆動部 401 は、当該補正信号に基づき、データ信号を各画素 204、205、206、207 に出力することはいうまでもない。また、具体的な補正信号の算出等については、例えば、上記特許文献 1 及び 2 等に記載された方法等を用いればよい。

40

【0046】

検出部 212 は、検出線 210 を介して、各駆動トランジスタ 301 のソースに接続され、検出期間に、電流源 213 からの定電流を駆動トランジスタ 301 に流した際の駆動トランジスタ 301 のソース電圧を検出する。

【0047】

具体的には、検出部 212 は、図 3 (a) に示すように、例えば、バッファ回路 305、ローパスフィルタ 306、A/D 変換器 307 を有する。

【0048】

バッファ回路 305 は、電流源 213 とローパスフィルタ 306 との間に配置される。

50

具体的には、例えば、バッファ回路 305 は O P アンプから形成される。そして、O P アンプの非反転入力端子は、駆動トランジスタ 301 のソースに接続され、O P アンプの反転入力端子は O P アンプの出力端子に接続される。

【0049】

ローパスフィルタ 306 は、入力側がバッファ回路 305 の出力端子に接続され、出力側は、A / D 変換器 307 に接続される。

【0050】

A / D 変換器 307 は、駆動トランジスタ 301 のソース電圧をデジタルデータに変換し、当該データを補正部 403 に出力する。

【0051】

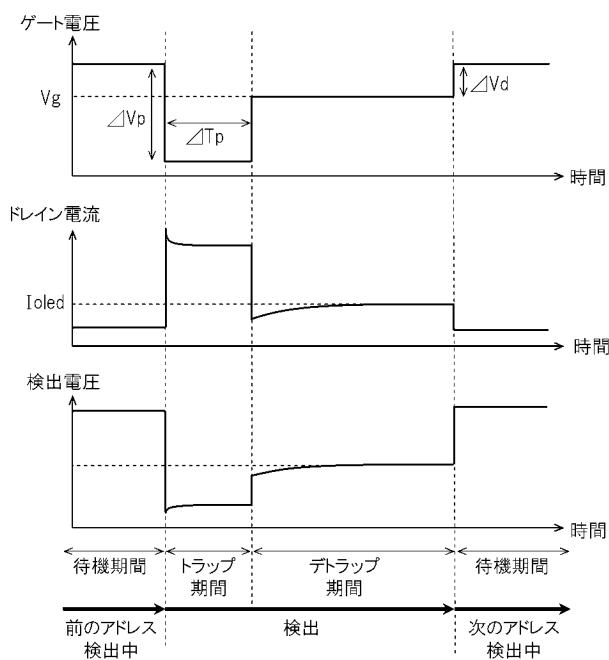

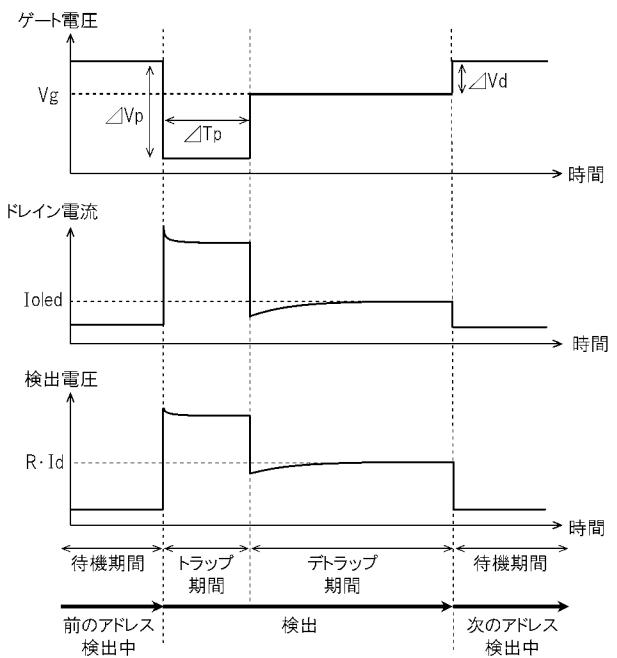

次に、図 5 を用いて、各画素 204、205、206、207 の閾値電圧  $V_{th}$  の検出についての動作の概要について説明する。

【0052】

まず、待機期間においては、駆動トランジスタ 301 はオフである。1 つの画素の検出期間中、後述するようにその他の全ての画素がオフされる。

【0053】

次のトラップ期間においては、駆動トランジスタ 301 のゲートにトラップ電圧が入力される。なお、図 5 においては、当該トラップ電圧は、 $V_p$  に相当し、トラップ期間は  $T_p$  に対応する。

【0054】

次のデトラップ期間においては、駆動トランジスタ 301 のゲートにデトラップ電圧が入力され、このとき、検出部 212 は、駆動トランジスタ 301 のソース電圧を検出する。なお、図 5 においては、当該デトラップ電圧は、 $V_d$  に相当する。

【0055】

上記のように、トラップ期間にはトラップ電圧を印加し、デトラップ期間における各駆動トランジスタ 301 のヒステリシスによる変動を抑制する。この点につき、下記により具体的に説明する。

【0056】

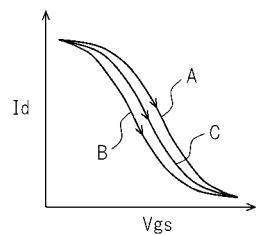

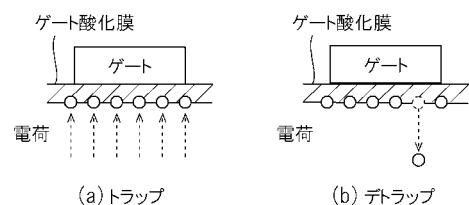

図 6、図 7、及び図 8 は、画素 204、205、206、207 内の各駆動トランジスタ 301 のヒステリシス特性について説明するための図である。

【0057】

駆動トランジスタ 301 のゲート電圧とドレイン電流の関係が図 6 に示すようなヒステリシス特性を有する場合がある。なお、図 6 において、縦軸は、駆動トランジスタ 301 のドレイン電流を表し、横軸は、駆動トランジスタ 301 のゲート・ソース間電圧を表す。

【0058】

このヒステリシス特性は、図 7 に示すような駆動トランジスタ 301 のゲート酸化膜にトラップされるキャリア（主に正電荷）の数によって生じる。

【0059】

具体的には、駆動トランジスタ 301 のゲート酸化膜には、図 7 (a) に示すように、ゲートにキャリアをトラップする状態と、一方、図 7 (b) に示すような、ゲートにキャリアをデトラップする状態がある。そして、ゲートにキャリアがトラップされた状態では駆動トランジスタ 301 の閾値電圧がエンハンスされ、デトラップされた状態ではディップリートされる。また、ゲートにキャリアをトラップする時間に比べて、デトラップする時間の方が充分に大きい。

【0060】

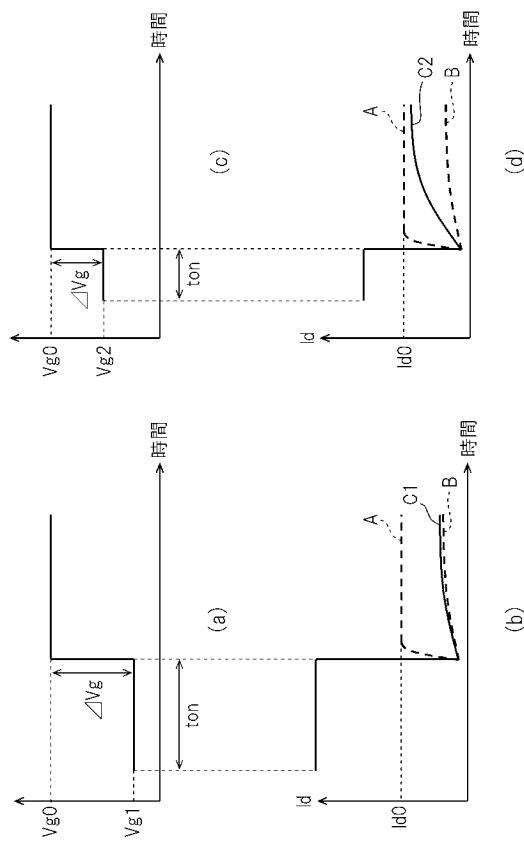

また、図 8 (a) に示すように、所定の電位差を所定期間駆動トランジスタ 301 のゲート・ソース間に印加する場合、当該電位差  $V_g$  が大きい程、また当該期間  $t_{on}$  が長い程、図 8 (b) に示すように、当該電位差印加後の駆動トランジスタ 301 の特性は時間を経ても変化しにくい。

10

20

30

40

50

## 【0061】

具体的には、例えば、図8(a)に示すように、図8(c)に示した場合と比べて、長い時間、大きな電位差を与える場合、図8(b)に示すように、当該電位差印加後の駆動トランジスタ301のゲート電圧・ドレイン電流の関係は、図8(d)に示した場合に比べ、時間が経過しても変化が少ない。いいかえれば、図8(a)に示した場合は、時間が経過しても、図8(b)のBで示した状態に近い特性C1を保つのに対し、図8(d)に示した場合は、図8(d)に示した特性C2のように、図8(b)に示した場合と比べ速く図8(d)のAで示した特性に近づく。

## 【0062】

なお、図6に示した場合において、駆動トランジスタ301にゲートに印加される電位差の大きさ及び時間に応じて、駆動トランジスタ301のドレイン電流と経過時間についての特性は、図6に示したAからBの状態までばらつくものとして説明した。また、図6及び図8に示した特性A及びBは、それぞれ対応し、特性CはC1またはC2に対応する。

10

## 【0063】

したがって、上記のように  $V_g$  及び当該  $V_g$  を与える期間を適切に調整することにより、図6及び図8に示した駆動トランジスタ301の特性Bから特性Aに回復する時定数を大きくし、実際に検出動作を行うデトラップ期間に各駆動トランジスタ301の特性を特性Bに近い特性に揃えてから、検出することができる。

20

## 【0064】

つまり、トラップ電圧及びトラップ期間とはそれぞれ、上記のように  $V_g$  の印加後のデトラップ期間に、駆動トランジスタ301の特性変動を十分に抑制することができる  $V_g$  及び  $V_g$  を与える期間  $t_{on}$  に相当する。また、デトラップ期間とは、当該トラップ電圧を印加するトラップ期間の後、実際に検出動作を行う期間に相当する。言い換れば、トラップ電圧とは、駆動トランジスタ301の特性変動を、デトラップ期間において十分に抑制するために、駆動トランジスタ301のゲート・ソース間に印加する電圧であって、駆動トランジスタ301のゲートに印加する電圧に相当する。つまり、図8の例を用いて説明すれば、図8(b)において特性Bに近接した特性(例えば図8(b)のC1)を有するように、トラップ期間に駆動トランジスタ301のゲートに印加する電圧に相当する。

30

## 【0065】

具体的には、 $V_p$  は0.5V以上、10V以下の値が望ましいが、特に表示装置100に実装される電圧発生回路の負担を最小限に留めつつ最大限の効果を得るために、1V以上5V以下であることがより望ましく、最適値は3V前後である。また、トラップ期間  $T_p$  は、0.1μ秒以上の値が望ましいが、特に多画素化に伴う高速駆動に支障なく最大限の効果を得るために、1μ秒以上1m秒以下であることがより望ましく、最適値は10μ秒前後である。このように、トラップ期間  $t_{on}$  よりデトラップ期間を長い状態とすることで、検出動作をより安定に行うことができる。

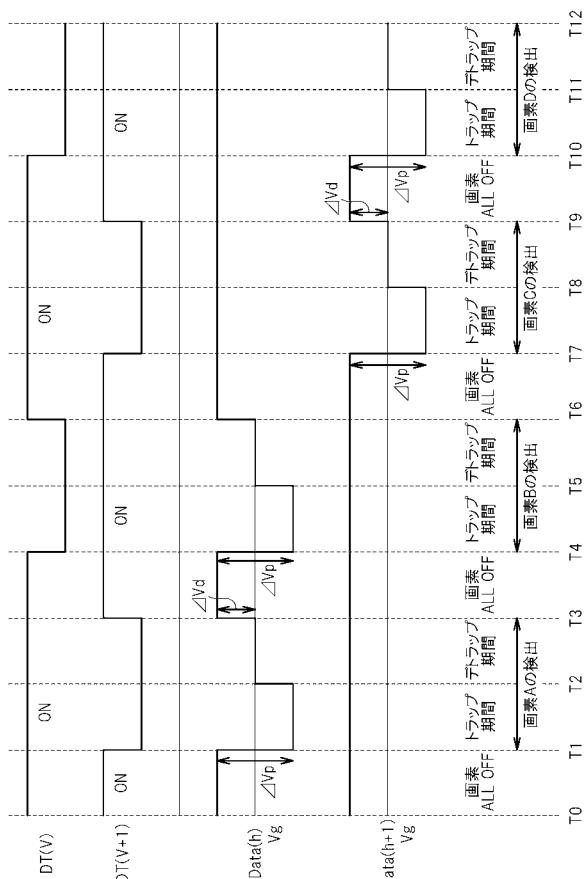

## 【0066】

次に、図9を用いて、本実施の形態における表示装置100全体としての検出動作の際に制御される信号のタイミングチャートについて説明する。なお、図2及び図3に示したように、本実施の形態においては、セレクトスイッチ304は、nMOSであることからゲート電圧が高電圧の時にオンし、駆動トランジスタ301はpMOSであることから、ゲート電圧が低電圧の時にオンすることはいうまでもない。

40

## 【0067】

時刻  $T_0$ においては、 $D_T(v)$ 、 $D_t(v+1)$ をオンし、 $Data(h)$ 及び $Data(h+1)$ をハイ電圧とする。これにより、各画素204乃至207に含まれるセレクトスイッチ304がオンするとともに、駆動トランジスタ301のゲート電圧を、ハイ電圧とする。これにより、全ての画素204乃至207の駆動トランジスタ301は、オフする。

50

## 【0068】

時刻  $T_1$  においては、 $D_T(v)$  をオンの状態に保ち、 $D_t(v+1)$  をオフする。また、 $Data(h)$  を上記トラップ電圧とする。これにより、画素 204 の駆動トランジスタ 301 のゲート端子にトラップ電圧を印加する。なお、図 9 においては、当該時刻  $T_1$  から次の時刻  $T_2$  までの期間がトラップ期間に相当する。また、 $V_p$  がトラップ電圧に相当する。

## 【0069】

時刻  $T_2$  においては、 $Data(h)$  を上記デトラップ電圧とする。よって、画素 204 の駆動トランジスタ 301 のゲート端子にデトラップ電圧が印加される。このとき、上述のように、画素 204 の駆動トランジスタ 301 のソースの電圧を検出する。なお、図 9 においては、当該時刻  $T_2$  から次の時刻  $T_3$  までの期間がデトラップ期間となる。また、 $V_d$  がデトラップ電圧に相当する。

10

## 【0070】

その他の画素 205 乃至 207 についても、上記と同様にトラップ期間及びデトラップ期間を設ける。具体的には、時刻  $T_3$  においては、 $D_T(v)$  をオンの状態に保ち、 $D_t(v+1)$  をオンする。また、 $Data(h)$  をハイ電圧とし、及び  $Data(h+1)$  をハイ電圧の状態に保つ。これにより、時刻  $T_1$  と同様に、全ての画素 204 乃至 207 の駆動トランジスタ 301 は、オフする。

## 【0071】

時刻  $T_4$  においては、 $D_T(v)$  をオフし、 $D_t(v+1)$  など  $D_T(V)$  以外のスイッチをオンの状態に保つ。また、 $Data(h)$  をトラップ電圧とする。 $Data(h)$  以外のデータ線はハイ電圧のままとする。これにより、画素 205 の駆動トランジスタ 301 のゲート端子にトラップ電圧を印加する。なお、当該時刻  $T_4$  から次の時刻  $T_5$  までの期間がトラップ期間に相当する。

20

## 【0072】

時刻  $T_5$  においては、 $Data(h)$  を、デトラップ電圧とする。このとき、画素 B の駆動トランジスタ 301 のソースの電圧を検出する。なお、当該時刻  $T_5$  から次の時刻  $T_6$  までの期間がデトラップ期間となる。

## 【0073】

時刻  $T_6$  においては、 $D_T(v)$  をオンし、 $D_t(v+1)$  をオン状態に保つ。また、 $Data(h)$  をハイ電圧とし、及び  $Data(h+1)$  をハイ電圧の状態に保つ。これにより、時刻  $T_1$  と同様に、全ての画素の駆動トランジスタ 301 はオフする。

30

## 【0074】

時刻  $T_7$  においては、 $D_T(v)$  など  $D_T(V+1)$  以外のスイッチをオン状態に保ち、 $D_t(v+1)$  をオフする。また、 $Data(h+1)$  を上記トラップ電圧とする。 $Data(h+1)$  以外のデータ線はハイ電圧のままとする。これにより、画素 206 の駆動トランジスタ 301 のゲート端子にトラップ電圧を印加する。なお、当該時刻  $T_7$  から次の時刻  $T_8$  までの期間がトラップ期間に相当する。

## 【0075】

時刻  $T_8$  においては、 $Data(h+1)$  を、上記デトラップ電圧とする。このとき、画素 206 の駆動トランジスタ 301 のソースの電圧を検出する。なお、当該時刻  $T_8$  から次の時刻  $T_9$  までの期間がデトラップ期間となる。

40

## 【0076】

時刻  $T_9$  においては、 $D_T(v)$  をオンの状態に保ち、 $D_t(v+1)$  をオンする。また、 $Data(h)$  をハイ電圧に保ち、及び  $Data(h+1)$  をハイ電圧とする。これにより、時刻  $T_1$  と同様に、全ての画素の駆動トランジスタ 301 はオフする。

## 【0077】

時刻  $T_{10}$  においては、 $D_T(v)$  をオフし、 $D_t(v+1)$  をオン状態に保つ。また、 $Data(h+1)$  を上記トラップ電圧とする。これにより、画素 207 の駆動トランジスタ 301 のゲート端子にトラップ電圧を印加する。なお、当該時刻  $T_{10}$  から次の時

50

刻 T 1 1 までの期間がトラップ期間に相当する。

【0078】

時刻 T 1 1 においては、Data (h + 1) を、上記デトラップ電圧とする。このとき、画素 207 の駆動トランジスタ 301 のソースの電圧が検出される。なお、当該時刻 T 1 1 から次の時刻 T 1 2 までの期間がデトラップ期間となる。

【0079】

時刻 T 1 2 においては、DT (v) をオンし、Dt (v + 1) をオン状態に保つ。また、Data (h) をハイ電圧の状態に保ち、Data (h + 1) をハイ電圧とする。これにより、全て画素 204 乃至 207 の駆動トランジスタ 301 はオフする。

【0080】

上記のように、図 2 に示した画素 204、205、206、207 の順に、順次、各画素 204、205、206、207 に含まれる駆動トランジスタ 301 のソース電圧を検出する。なお、図 2 及び 9 については、図面の簡略化のため、表示領域 203 が 4 の画素のみを有する場合について説明したが、その他の数の画素を有する場合にも同様に、順次各画素に含まれる駆動トランジスタのソース電圧を検出することはいうまでもない。

【0081】

なお、本実施の形態における表示装置 100 は、例えば、図 10 または図 11 に示すような、携帯電話 150 や PDA 160 等の携帯端末やテレビ 170、ビデオカメラ 180 等に実装される。その他、本実施形態における表示装置 100 は、パソコン用ディスプレイ、公告表示用ディスプレイ等の各種の情報表示用の表示装置として採用できる。また、デジタルスチルカメラ、カーナビゲーションシステム、カーオーディオ、ゲーム機器、携帯情報端末など、各種の電子機器の表示部として利用することも可能である。

【0082】

また、以上の説明においては発光素子として有機 EL 素子 302 を用いることとしたが、これに限らず、本実施の形態に係る表示装置 100 は、例えば無機 EL 素子や FED (Field-Emission Device) など、各種の発光素子を用いた表示装置 100 であってもよい。また、駆動トランジスタ 301 は、例えば多結晶 Si 半導体デバイス、微結晶 Si 半導体デバイス、アモルファス半導体デバイス、または、酸化物半導体デバイスにより形成される。

【0083】

上記のように構成することで、本実施の形態に係る表示装置 100 によれば、各画素に含まれる駆動トランジスタのヒステリシスによる影響を抑制しつつ、各駆動トランジスタの特性を検出することができる。よって、従来技術に比べ、高精度かつ高速度で各駆動トランジスタの特性を検出することができる。また、当該検出結果に応じてデータ信号を補正することで、従来技術に比べ、高画質化を図ることができる。

【0084】

なお、本発明は、上記実施の形態に限定されるものではなく、種々の変形が可能である。例えば、上記実施の形態で示した構成と実質的に同一の構成、同一の作用効果を奏する構成又は同一の目的を達成することができる構成で置き換えてよい。

【0085】

[変形例]

図 12 及び 13 は、本発明の変形例を説明するための図である。本変形例では、上記実施の形態と比較して、主に、検出部 212 の配置が異なる。その他の点は、上記実施の形態と同様であり、同様である点については説明を省略する。

【0086】

図 12 及び 13 に示すように、有機 EL 素子 302 のカソードには抵抗 217 の一端が接続され、当該抵抗 217 の他端は接地される。

【0087】

また、検出部 212 は、当該有機 EL 素子 302 の抵抗 217 の接続部分に接続される。つまり、本変形例においては、検出部 212 は、当該抵抗 217 の抵抗値 R と当該抵抗

10

20

30

40

50

217を流れる電流値  $I_d$  ( 例えは図 3 ( b ) の  $I_d 1$  乃至  $I_d 3$  ) との積を検出する。そして、補正部 403 は、当該積に基づいて、各駆動トランジスタ 301 の閾値電圧を求める。つまり、本変形例においては、電流源 213 及びそのスイッチ 214 は、不要である。なお、その他の構成及び動作については、上記実施の形態と同様であるので、説明を省略する。また、ここでは当該有機 EL 素子 302 のカソード側において検出部を設けた例を述べたが、当該有機 EL 素子の電極構成によってはアノード側となる場合もある。

【 0 0 8 8 】

上記のように構成することで、上記実施の形態と同様、本変形例による表示装置 100 によれば、各画素に含まれる駆動トランジスタのヒステリシスによる影響を抑制しつつ、各駆動トランジスタの特性を検出することができる。よって、従来技術に比べ、高精度かつ高速度で各駆動トランジスタの特性を検出することができる。また、当該検出結果に応じてデータ信号を補正することで、従来技術に比べ、高画質化を図ることができる。

【 0 0 8 9 】

なお、本発明は、上記実施の形態及び変形例に限定されるものではなく、種々の変形が可能である。例えば、上記変形例で示した構成と実質的に同一の構成、同一の作用効果を奏する構成又は同一の目的を達成することができる構成で置き換えてよい。

## 【 符号の説明 】

( 0 0 9 0 )

100 表示装置、110 上フレーム、120 下フレーム、130 フレキシブル基板、140 回路基板、200 TFT 基板、201 表示用走査部、202 走査線、203 表示領域、204、205、206、207 画素、208 検出用走査部、209 データ線、210 検出線、211 データ線駆動部、212 検出部、213 電流源、214 スイッチ、215 電圧源、301 駆動トランジスタ、302 有機EL素子、303 容量、304 セレクトスイッチ、401 データ信号駆動部、402 検出信号駆動部、403 補正部。

( 四 1 )

【 义 2 】

【図3】

〔 図 4 〕

〔 5 〕

〔 6 〕

( 义 7 )

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

(b)

【図 1 3】

## フロントページの続き

(51) Int.Cl.

| F I           | テマコード(参考) |

|---------------|-----------|

| G 0 9 G 3/20  | 6 2 1 A   |

| G 0 9 G 3/20  | 6 2 3 D   |

| G 0 9 G 3/20  | 6 4 1 P   |

| G 0 9 G 3/20  | 6 4 2 B   |

| G 0 9 G 3/20  | 6 2 4 B   |

| H 0 5 B 33/14 | A         |

(72) 発明者 倉永 順英

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

(72) 発明者 景山 寛

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

F ターム(参考) 3K107 AA01 BB01 CC31 EE03 HH04 HH05

|            |      |      |       |      |      |      |      |      |      |

|------------|------|------|-------|------|------|------|------|------|------|

| 5C080 AA06 | BB05 | DD05 | JJ02  | JJ03 | JJ04 | JJ05 | JJ06 |      |      |

| 5C380 AA01 | AB06 | AB21 | AB22  | AB23 | AB34 | AC05 | AC07 | AC09 | AC10 |

| AC11       | AC12 | AC13 | BA39  | BB04 | CA12 | CA54 | CB31 | CC02 | CC09 |

| CC26       | CC33 | CC62 | CD012 | DA02 | DA06 | DA49 | DA50 | FA02 | FA28 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2012078379A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2012-04-19 |

| 申请号            | JP2010220553                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2010-09-30 |

| [标]申请(专利权)人(译) | 株式会社日立制作所<br>佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司<br>佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 秋元肇<br>河野亨<br>倉永卓英<br>景山寛                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 秋元 肇<br>河野 亨<br>倉永 卓英<br>景山 寛                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.J G09G3/30.Z G09G3/20.641.D G09G3/20.642.P G09G3/20.611.H G09G3/20.621.A G09G3/20.623.D G09G3/20.641.P G09G3/20.642.B G09G3/20.624.B H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB21 5C380/AB22 5C380/AB23 5C380/AB34 5C380/AC05 5C380/AC07 5C380/AC09 5C380/AC10 5C380/AC11 5C380/AC12 5C380/AC13 5C380/BA39 5C380/BB04 5C380/CA12 5C380/CA54 5C380/CB31 5C380/CC02 5C380/CC09 5C380/CC26 5C380/CC33 5C380/CC62 5C380/CD012 5C380/DA02 5C380/DA06 5C380/DA49 5C380/DA50 5C380/FA02 5C380/FA28 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

解决的问题：以高精度和高速度检测常规有机EL显示装置中的驱动晶体管的特性。显示装置包括：多个像素，每个像素具有发光元件；以及驱动晶体管，其将与灰度值相对应的电流提供给发光元件；以及用于检测每个驱动晶体管的特性的检测。用于在发光元件发光之后在每个驱动晶体管的栅极和源极之间提供第一电压信号的装置，以及在提供第一电压信号之后用于每个驱动晶体管的栅极的装置。在源之间，存在用于提供与第一电压信号不同的第二电压信号的装置，即检测装置，在提供第二电压信号的期间内，每个驱动晶体管检测到该特性，并且第一电压信号是具有电压的电压信号，该电压信号与第二电压信号相比能够在驱动晶体管的源极和漏极之间提供更大的电流量。[选择图]图3

(a)