(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-12642

(P2019-12642A)

(43) 公開日 平成31年1月24日(2019.1.24)

|                               |                              |                                                                               |

|-------------------------------|------------------------------|-------------------------------------------------------------------------------|

| (51) Int.Cl.                  | F 1                          | テーマコード (参考)                                                                   |

| <b>H05B 33/26 (2006.01)</b>   | H05B 33/26                   | Z 3K107                                                                       |

| <b>H01L 27/32 (2006.01)</b>   | H01L 27/32                   |                                                                               |

| <b>H01L 51/50 (2006.01)</b>   | H05B 33/14                   | A                                                                             |

| <b>H05B 33/22 (2006.01)</b>   | H05B 33/22                   | Z                                                                             |

| <b>H05B 33/10 (2006.01)</b>   | H05B 33/10                   |                                                                               |

| 審査請求 未請求 請求項の数 6 O L (全 25 頁) |                              |                                                                               |

| (21) 出願番号                     | 特願2017-128990 (P2017-128990) | (71) 出願人 514188173<br>株式会社 J O L E D<br>東京都千代田区神田錦町三丁目23番地                    |

| (22) 出願日                      | 平成29年6月30日 (2017.6.30)       | (74) 代理人 110001900<br>特許業務法人 ナカジマ知的財産総合事務所                                    |

|                               |                              | (72) 発明者 篠川 泰治<br>東京都千代田区神田錦町三丁目23番地<br>株式会社 J O L E D 内                      |

|                               |                              | F ターム (参考) 3K107 AA01 BB01 CC33 CC36 CC45<br>DD37 DD90 EE03 FF04 GG03<br>GG05 |

(54) 【発明の名称】有機EL表示パネル及び有機EL表示パネルの製造方法

## (57) 【要約】

【課題】画素開口率の高い有機EL表示パネルを提供する。

【解決手段】有機EL表示パネルは、基板と、基板上に配された薄膜半導体層と、薄膜半導体層上に配された下部絶縁層と、下部絶縁層上に部分的に配され、基板側に凹入する凹部を有する給電用の補助電極と、下部絶縁層及び補助電極の上方に配された上部絶縁層と、上部絶縁層上に配されたEL素子と、を備える。上部絶縁層には、補助電極の凹部まで達するコンタクト孔が開設されている。EL素子は、上部絶縁層上のコンタクト孔が開設されていない部分に配された画素電極と、画素電極上に配された発光層と、発光層上及びコンタクト孔内に配された共通電極層と、を含む。コンタクト孔内において、共通電極層は、孔内壁及び補助電極表面に沿って形成されている。

【選択図】図13

## 【特許請求の範囲】

## 【請求項 1】

有機 E L 表示パネルであって、

基板と、

基板上に配された薄膜半導体層と、

前記薄膜半導体層上に配された下部絶縁層と、

前記下部絶縁層上に部分的に配され、前記基板側に凹入する凹部を有する給電用の補助電極と、

前記下部絶縁層及び前記補助電極の上方に配された上部絶縁層と、

前記上部絶縁層上に配された E L 素子と、を備え、

前記上部絶縁層には、前記補助電極の前記凹部まで達するコンタクト孔が開設され、

前記 E L 素子は、前記上部絶縁層上の前記コンタクト孔が開設されていない部分に配された画素電極と、前記画素電極上に配された発光層と、前記発光層上及び前記コンタクト孔内に配された共通電極層と、を含み、

前記コンタクト孔内において、前記共通電極層は、孔内壁及び前記補助電極表面に沿って形成されている

有機 E L 表示パネル。

## 【請求項 2】

前記 E L 素子は、さらに、前記発光層上及び前記コンタクト孔内、かつ前記共通電極層の下方に配された機能層を含み、

前記コンタクト孔内において、前記機能層は、孔内壁及び前記補助電極表面に沿って形成され、前記補助電極の前記凹部の内壁に位置する部分が欠落している又は薄層化しており、

前記共通電極層は、前記機能層の欠落により露出している前記補助電極と直接接触し、前記機能層が薄層化している部分においてそれ以外の前記機能層の部分よりも低い抵抗にて前記補助電極に電気的に接続している

請求項 1 の有機 E L 表示パネル。

## 【請求項 3】

前記補助電極を第 1 補助電極、前記コンタクト孔を第 1 コンタクト孔と定義した場合、

前記薄膜半導体層は、前記基板上に配されるゲート電極と、前記ゲート電極の上方に配されるソース電極及びドレイン電極と、前記第 1 補助電極の下方に位置する部分に配される前記ソース電極及び前記ドレイン電極と同層の第 2 補助電極と、を含み、

前記下部絶縁層には、前記第 2 補助電極まで達する第 2 コンタクト孔が開設され、

前記第 2 コンタクト孔内において、前記第 1 補助電極は、孔内壁及び前記第 2 補助電極表面に沿って形成されている

請求項 1 の有機 E L 表示パネル。

## 【請求項 4】

有機 E L 表示パネルの製造方法であって、

基板上に薄膜半導体層を形成する工程と、

前記薄膜半導体層上に下部絶縁層を形成する工程と、

前記下部絶縁層上に部分的に、前記基板側に凹入する凹部を有する給電用の補助電極を形成する工程と、

前記下部絶縁層及び前記補助電極の上方に上部絶縁層を形成する工程と、

前記上部絶縁層に、前記補助電極の前記凹部まで達するコンタクト孔を開設する工程と、

前記上部絶縁層上に E L 素子を形成する工程と、を含み、

前記 E L 素子を形成する工程は、

前記上部絶縁層上の前記コンタクト孔が開設されていない部分に画素電極を形成する工程と、

前記画素電極上に発光層を形成する工程と、

10

20

30

40

50

前記発光層上及び前記コンタクト孔内に共通電極層を形成する工程と、を含み、

前記共通電極層を形成する工程は、前記コンタクト孔内において、孔内壁及び前記補助電極表面に沿って前記共通電極層を形成する

有機EL表示パネルの製造方法。

【請求項5】

前記EL素子を形成する工程は、さらに、前記発光層の上方及び前記コンタクト孔内、かつ前記共通電極層の下方に機能層を形成する工程を含み、

前記機能層を形成する工程は、前記コンタクト孔内において、孔内壁及び前記補助電極表面に沿って、前記補助電極層の前記凹部の内壁上に位置する部分において欠落する又は薄層化するよう真空蒸着法により前記機能層を形成し、

前記共通電極層を形成する工程は、前記機能層の欠落により露出している前記補助電極と直接接触するように、前記機能層が薄層化している部分においてそれ以外の前記機能層の部分よりも低い抵抗にて前記補助電極に電気的に接続するように、前記共通電極層をスパッタリング法またはCVD (Chemical Vapor Deposition) 法により形成する

請求項4の有機EL表示パネルの製造方法。

【請求項6】

前記補助電極を第1補助電極、前記コンタクト孔を第1コンタクト孔と定義した場合、前記薄膜半導体層を形成する工程は、

前記基板上にゲート電極を形成する工程と、

前記ゲート電極の上方にソース電極及びドレイン電極を形成する工程と、

前記ソース電極及び前記ドレイン電極と同層に第2補助電極を形成する工程と、を含み、

更に、前記下部絶縁層に、前記第2補助電極まで達する第2コンタクト孔を開設する工程、を含み、

前記第1補助電極を形成する工程は、前記第2コンタクト孔内において、孔内壁及び前記第2補助電極表面に沿って、前記第1補助電極を形成する

請求項4の有機EL表示パネルの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、有機材料の電界発光現象を利用した有機EL (Electro Luminescence) 素子を用いた有機EL表示パネル及びその製造方法に関する。

【背景技術】

【0002】

近年、デジタルテレビ等の表示装置に用いられる表示パネルとして、基板上有機EL素子をマトリックス状に複数配列した有機EL表示パネルが実用化されている。

有機EL表示パネルでは、一般に各有機EL素子の発光層と、隣接する有機EL素子とは、絶縁材料からなる絶縁層で仕切られている。カラー表示用の有機EL表示パネルにおいては、有機EL素子がRGB各色に発光する副画素を形成し、隣り合うRGBの副画素が組み合わさってカラー表示における単位画素が形成されている。

【0003】

有機EL素子は、一対の電極の間に有機発光材料を含む発光層が配設された基本構造を有し、駆動時には、一対の電極間に電圧を印加し、発光層に注入されるホールと電子との再結合に伴って発光する。

トップエミッション型の有機EL素子は、基板上有画素電極、有機層(発光層を含む)及び共通電極層が順に設けられた素子構造をしている。発光層からの光は、光反射性材料からなる画素電極にて反射されるとともに、光透光性材料からなる共通電極層から上方に出射される。

【0004】

10

20

30

40

50

上記の共通電極層は、基板全面にわたって成膜するが多く、共通電極層の電気抵抗が大きい場合、給電部から遠い部分では電圧降下により電流が十分に供給されずに発光効率が低下し、これに起因して輝度ムラが発生してしまう可能性がある。

そこで、共通電極層の低抵抗化のために補助電極を設ける手法が提案されている（例えば、特許文献1）。特許文献1によると、補助電極を画素電極と同層に形成し、補助電極を、画素電極とは電気的に絶縁しつつ、共通電極層とは電気的に接続している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002-318556号公報

10

【特許文献2】特開平5-163488号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、補助電極を画素電極と同層に形成すると、基板上に占める画素電極の面積が小さくなり、画素開口率が低下してしまうという課題がある。また、有機EL表示パネルの製造工程によっては、比較的電気抵抗の高い層を補助電極と共に共通電極層との間に形成する場合があり、その場合に補助電極と共に共通電極層との間の電気抵抗が高くなるという課題がある。

【0007】

20

本開示は、上記課題を解決し、画素開口率を下げることなく、かつ、比較的電気抵抗の高い有機層を補助電極と共に共通電極層との間に形成する場合における共通電極層と補助電極との間の電気的接続における電気抵抗の低減を図ることのできる有機EL表示パネル及びこの有機EL表示パネルの製造に適した製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

30

本開示の一態様に係る有機EL表示パネルは、基板と、基板上に配された薄膜半導体層と、薄膜半導体層上に配された下部絶縁層と、下部絶縁層上に部分的に配され、基板側に凹入する凹部を有する給電用の補助電極と、下部絶縁層及び補助電極の上方に配された上部絶縁層と、上部絶縁層上に配されたEL素子と、を備える。上部絶縁層には、補助電極の凹部まで達するコンタクト孔が開設されている。EL素子は、上部絶縁層上のコンタクト孔が開設されていない部分に配された画素電極と、画素電極上に配された発光層と、発光層上及びコンタクト孔内に配された共通電極層と、を含む。コンタクト孔内において、共通電極層は、孔内壁及び補助電極表面に沿って形成されている。

【発明の効果】

【0009】

40

本開示の一態様に係る有機EL表示パネルは、画素電極と異なる層に補助電極を形成するので、画素電極の小面積化を抑制でき、その結果、画素開口率の低下を抑えることができる。また、補助電極を専用の層に形成するので補助電極の大面積化により共通電極層の低抵抗化を実現できる。さらに、補助電極の表面の凹部により、比較的電気抵抗の高い有機層を補助電極と共に共通電極層との間に形成する場合でも、有機層の成膜法と共に共通電極層の成膜法とで、ステップカバレッジの異なる成膜法を利用することで、補助電極と共に共通電極層との間の電気接続の低抵抗化を容易に実現することができる。

【図面の簡単な説明】

【0010】

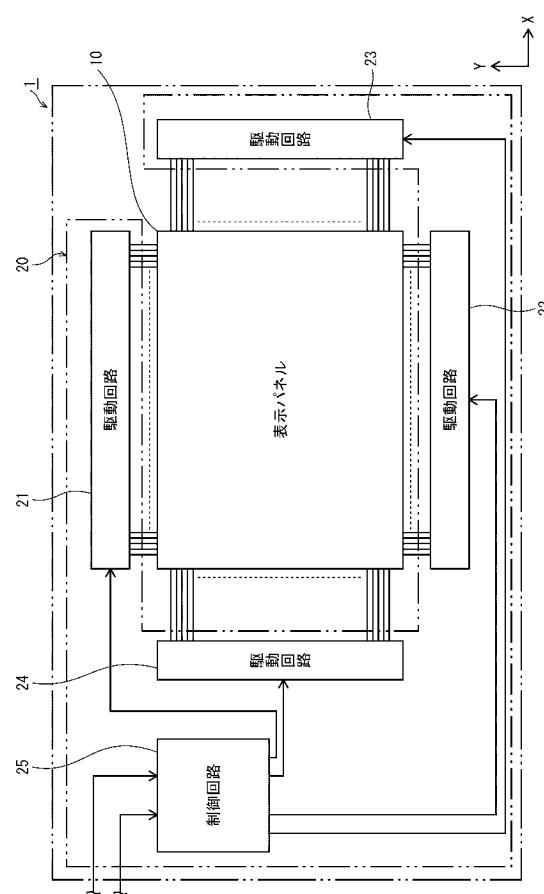

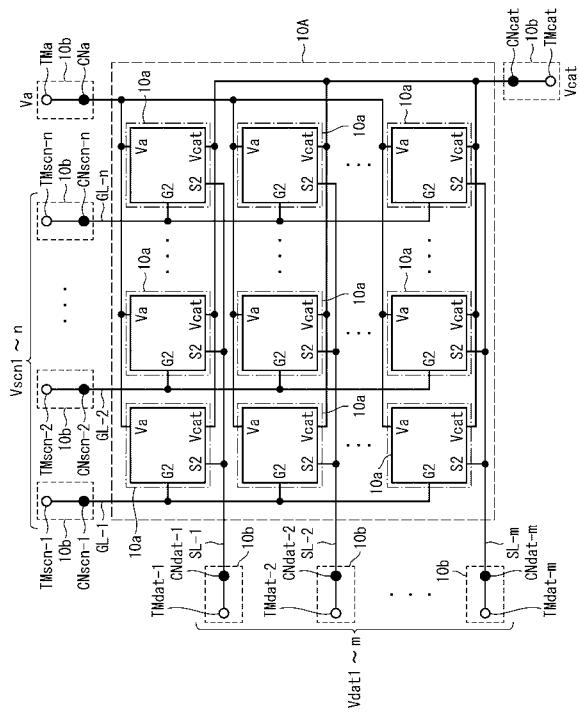

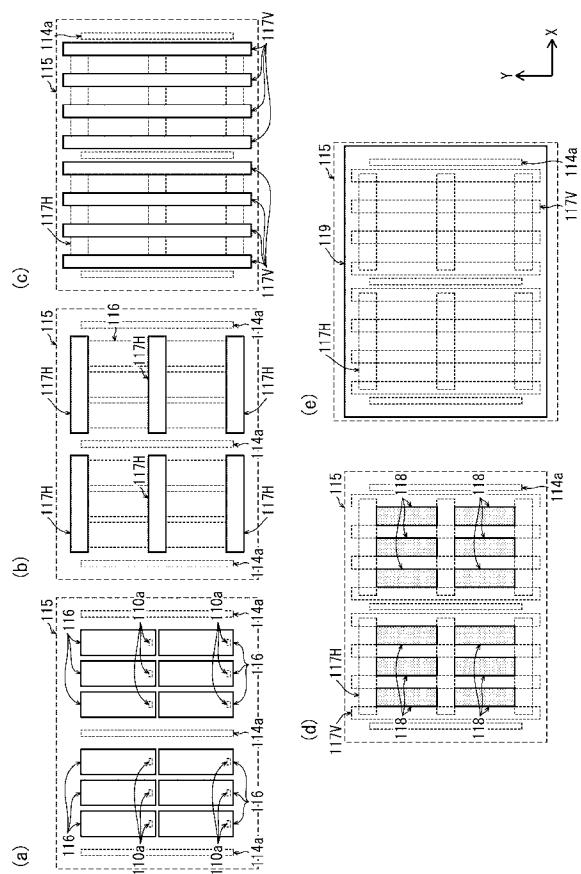

【図1】表示装置1の構成を示す模式図である。

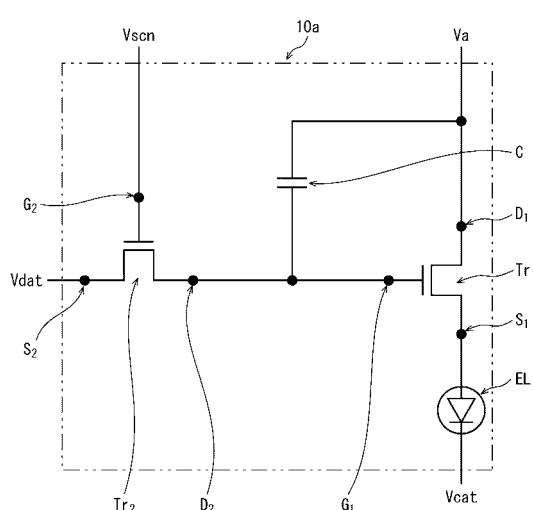

【図2】表示パネル10の各画素における10aにおける回路構成を示す模式図である。

【図3】表示パネル10の回路構成を示す模式図である。

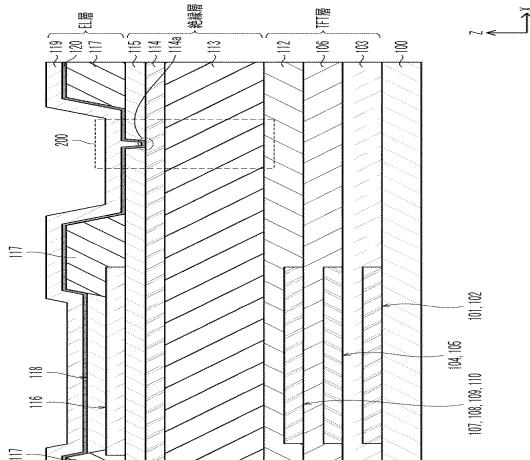

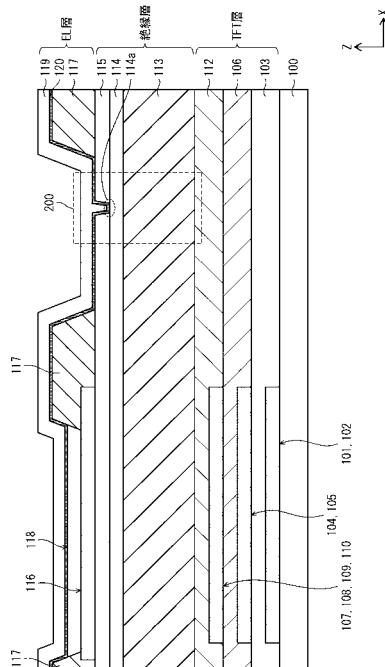

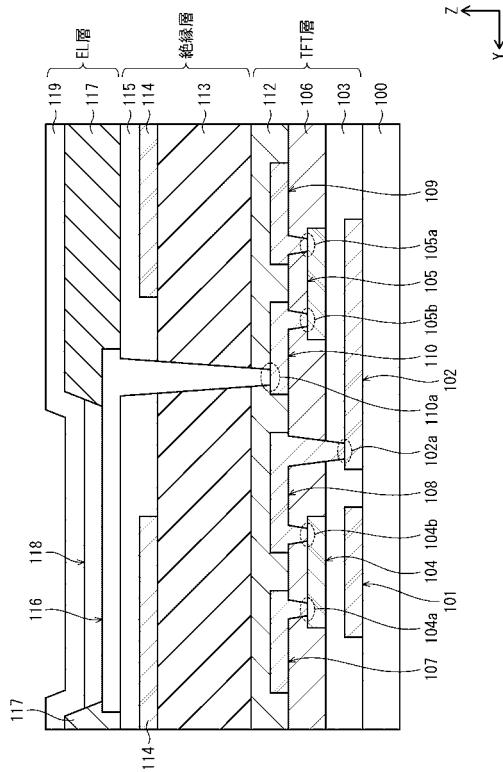

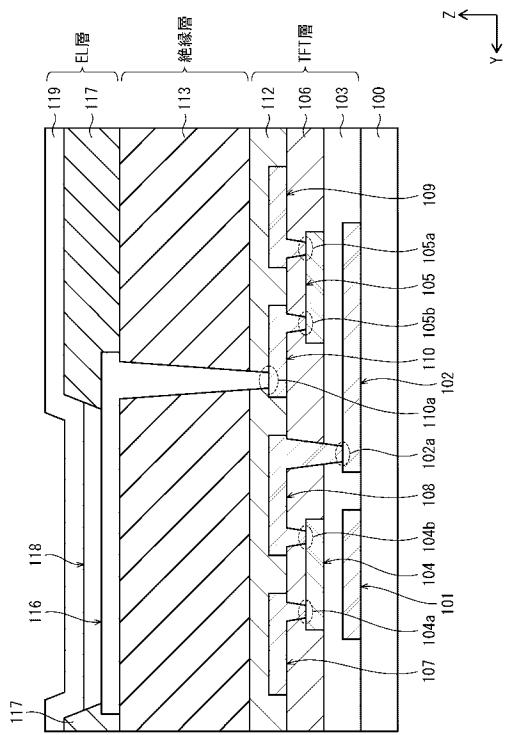

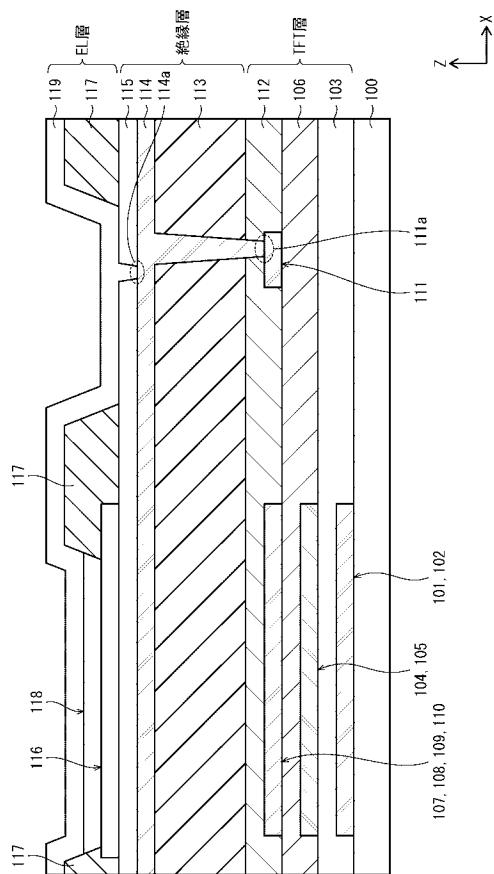

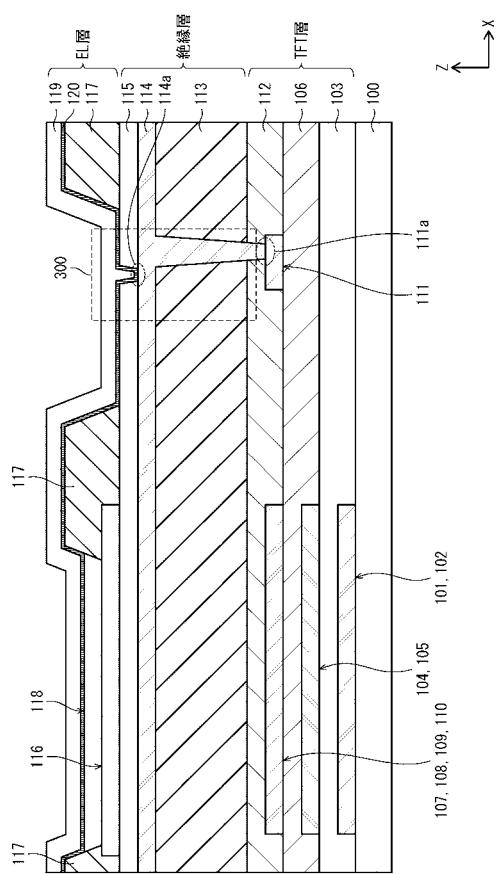

【図4】表示パネル10の断面構成を示す模式図である。

【図5】表示パネル10の断面構成を示す模式図である。

50

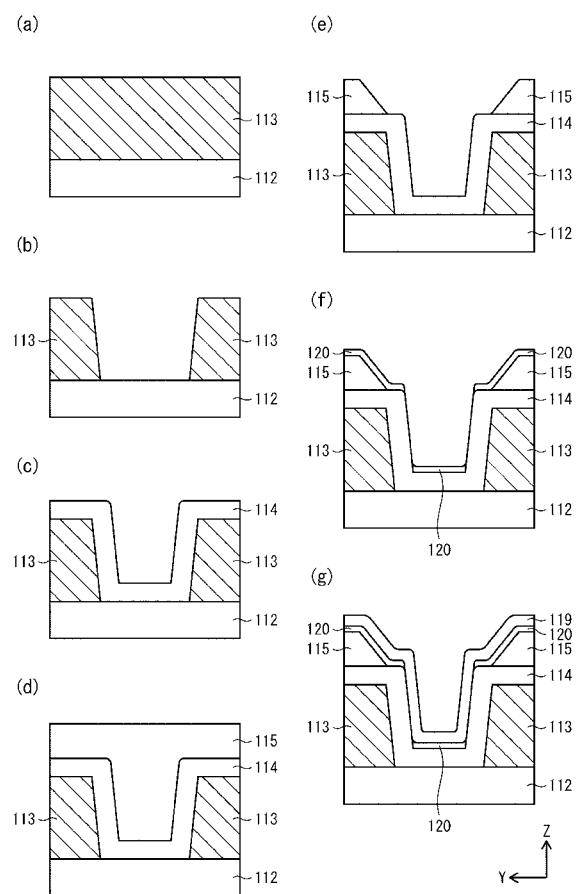

【図6】表示パネル10の製造工程を説明するための模式図である。

【図7】表示パネル10の製造工程を説明するための模式図である。

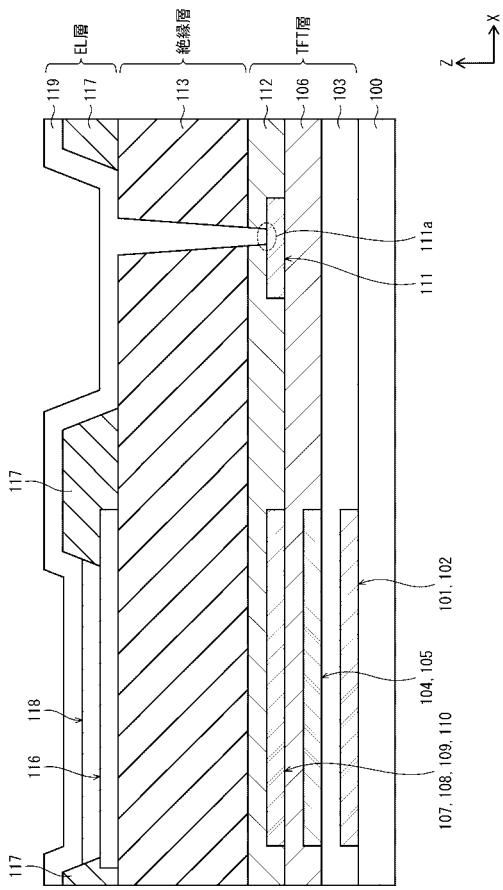

【図8】表示パネル10の断面構成を示す模式図である。

【図9】表示パネル10の断面構成を示す模式図である。

【図10】表示パネル10の製造工程を説明するための模式図である。

【図11】表示パネル10の断面構成を示す模式図である。

【図12】表示パネル10の製造工程を説明するための模式図である。

【図13】表示パネル10の断面構成を示す模式図である。

【図14】表示パネル10の断面構成を示す模式図である。

【図15】表示パネル10の製造工程を説明するための模式図である。

【図16】表示パネル10の断面構成を説明するための模式図である。

【図17】表示パネル10の断面構成を示す模式図である。

【発明を実施するための形態】

【0011】

(実施の形態1)

1.1 構成

1.1.1 表示装置1の構成

実施の形態1に係る表示装置1の構成について、図1を用いて説明する。

図1に示すように、表示装置1は、表示パネル10と、これに接続された駆動制御回路部20とを有し構成されている。

【0012】

表示パネル10は、有機材料の電界発光現象を利用した有機EL(Electro-Luminescence)パネルであって、複数の有機EL素子が、例えば、マトリクス状に配列され構成されている。駆動制御回路部20は、4つの駆動回路21～24と制御回路25とにより構成されている。

なお、表示装置1において、表示パネル10に対する駆動制御回路部20の各回路の配置形態については、図1に示した形態に限定されない。

【0013】

1.1.2 表示パネル10の各画素10aの回路構成

表示パネル10においては、複数の画素10aが行列状に配されて表示領域を構成している。各画素10aの回路構成について、図2を用いて説明する。

図2に示すように、本実施の形態に係る表示パネル10では、各画素10aが2つのトランジスタTr<sub>1</sub>、Tr<sub>2</sub>と一つのキャパシタC、及び発光部としての有機EL素子部ELとを有し構成されている。トランジスタTr<sub>1</sub>は、駆動トランジスタであり、トランジスタTr<sub>2</sub>は、スイッチングトランジスタである。

【0014】

スイッチングトランジスタTr<sub>2</sub>のゲートG<sub>2</sub>は、走査ラインVscnに接続され、ソースS<sub>2</sub>は、データラインVdatに接続されている。スイッチングトランジスタTr<sub>2</sub>のドレインD<sub>2</sub>は、駆動トランジスタTr<sub>1</sub>のゲートG<sub>1</sub>に接続されている。

駆動トランジスタTr<sub>1</sub>のドレインD<sub>1</sub>は、電源ラインV<sub>a</sub>に接続されており、ソースS<sub>1</sub>は、有機EL素子部ELの画素電極(アノード)に接続されている。有機EL素子部ELにおける共通電極層(カソード)は、接地ラインVcatに接続されている。

【0015】

なお、キャパシタCの第1端は、スイッチングトランジスタTr<sub>2</sub>のドレインD<sub>2</sub>及び駆動トランジスタTr<sub>1</sub>のゲートG<sub>1</sub>と接続され、キャパシタCの第2端は、電源ラインV<sub>a</sub>と接続されている。

1.1.3 表示パネル10の回路構成

表示パネル10の回路構成について、図3を用いて説明する。表示パネル10においては、図2に示すような回路構成を有する画素10aが、図3に示すように行列状に配されて表示領域10Aを構成している。

10

20

30

40

50

## 【0016】

行列状に配された各画素 10a のゲート G<sub>2</sub> からゲートライン G<sub>L-1~n</sub> が引き出され、表示領域 10A 外に存する接続部 10b において、配線接続部 C<sub>Nscn-1~n</sub> を介して外部接続端子 T<sub>Mscn-1~n</sub> に接続され、走査ライン V<sub>scn-1~n</sub> に接続されている。

同様に、行列状に配された各画素 10a のソース S<sub>2</sub> からソースライン S<sub>L-1~m</sub> が引き出され、接続部 10b において、配線接続部 C<sub>Ndat-1~m</sub> を介して外部接続端子 T<sub>Mdat-1~m</sub> に接続され、データライン V<sub>dat-1~m</sub> に接続されている。

## 【0017】

また、各画素の電源ライン V<sub>a</sub> は集約され、接続部 10b において、配線接続部 C<sub>Na</sub> を介して外部接続端子 T<sub>Ma</sub> に接続されている。

なお、カラー表示を行う表示装置 1 においては、隣接する複数の画素 10a ( 例えば、赤色 ( R ) と緑色 ( G ) と青色 ( B ) の発光色の 3 つの画素 10a ) をそれぞれサブ画素として、これら複数のサブ画素を組み合わせて一つの画素を構成してもよい。

## 【0018】

## 1.1.4 表示パネル 10 の断面構成

表示パネル 10 は、トップエミッション型の有機 EL 表示パネルであって、Z 軸方向下方に TFT 層が形成され、その上に平坦化層が形成され、さらにその上に EL 層が形成されている。

## ( TFT 層 )

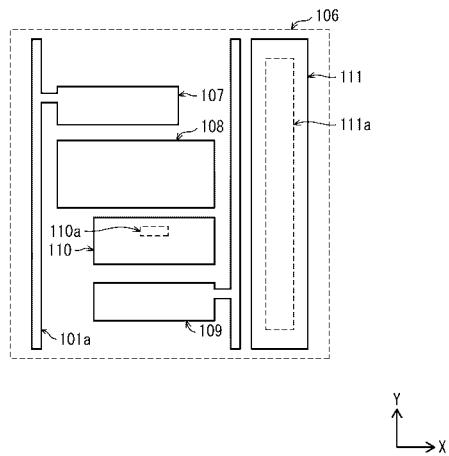

図 4 を参照して TFT 層について説明する。図 4 は、表示パネル 10 の YZ 平面の断面構成の一例を示す図である。

## 【0019】

基板 100 上には、ゲート電極 101、102 が互いに間隔を開けて形成されている。そして、ゲート電極 101、102 及び基板 100 の表面を被覆するように、ゲート絶縁層 103 が形成されている。

ゲート絶縁層 103 上には、ゲート電極 101、102 のそれぞれに対応してチャネル層 104、105 が形成されている。そして、チャネル層 104、105 及びゲート絶縁層 103 の表面を被覆するように、チャネル保護層 106 が形成されている。

## 【0020】

チャネル保護層 106 上には、ゲート電極 101 及びチャネル層 104 に対応してソース電極 107 及びドレイン電極 108 が互いに間隔を開けて形成されている。同様に、ゲート電極 102 及びチャネル層 105 に対応してソース電極 110 及びドレイン電極 109 が互いに間隔を開けて形成されている。そして、ソース電極 107、110、ドレイン電極 108、109、及びチャネル保護層 106 の表面を被覆するようにパッシベーション層 112 が形成されている。

## 【0021】

ゲート絶縁層 103 及びチャネル保護層 106 には、ゲート電極 102 のコンタクト領域 102a の上方にコンタクト孔が設けられており、このコンタクト孔の底でドレイン電極 108 がゲート電極 102 に接触している。

チャネル保護層 106 には、チャネル層 104 のコンタクト領域 104a の上方にコンタクト孔が設けられており、このコンタクト孔の底でソース電極 107 がチャネル層 104 に接触している。同様に、チャネル保護層 106 には、チャネル層 104 のコンタクト領域 104b の上方にコンタクト孔が設けられており、このコンタクト孔の底でドレイン電極 109 がチャネル層 104 に接触している。

## 【0022】

チャネル保護層 106 には、チャネル層 105 のコンタクト領域 105a の上方にコンタクト孔が設けられており、このコンタクト孔の底でドレイン電極 109 がチャネル層 105 に接触している。同様に、チャネル保護層 106 には、チャネル層 105 のコンタクト領域 105b の上方にコンタクト孔が設けられており、このコンタクト孔の底でソース

10

20

30

40

50

電極 110 がチャネル層 105 に接触している。

【0023】

また、パッシベーション層 112 には、ソース電極 110 のコンタクト領域 110a の上方にコンタクト孔が設けられており、このコンタクト孔の底で、後述する画素電極 116 がソース電極 110 に接触している。

なお、ゲート電極 101 が図 2 のゲート  $G_2$  に対応し、ソース電極 107 が図 2 のソース  $S_2$  に対応し、ドレイン電極 108 が図 2 のドレイン  $D_2$  に対応する。同様に、ゲート電極 102 が図 2 のゲート  $G_1$  に対応し、ソース電極 110 が図 2 のソース  $S_1$  に対応し、ドレイン電極 109 が図 2 のドレイン  $D_1$  に対応する。

【0024】

(平坦化層)

図 4 及び図 5 を参照して平坦化層について説明する。図 5 は、表示パネル 10 の XZ 平面の断面構成の一例を示す図である。

パッシベーション層 112 上には、下部層間絶縁層 113 が形成され、下部層間絶縁層 113 上には、補助電極 114 が形成されている。そして、補助電極 114 及び下部層間絶縁層 113 の表面を被覆するように上部層間絶縁層 115 が形成されている。

【0025】

下部層間絶縁層 113 及び上部層間絶縁層 115 には、図 4 に示すように、ソース電極 110 のコンタクト領域 110a の上方にコンタクト孔が設けられている。

上部層間絶縁層 115 には、図 5 に示すように、補助電極 114 のコンタクト領域 114a の上方にコンタクト孔が設けられており、このコンタクト孔の底で、後述する共通電極層 119 が補助電極 114 に接触している。

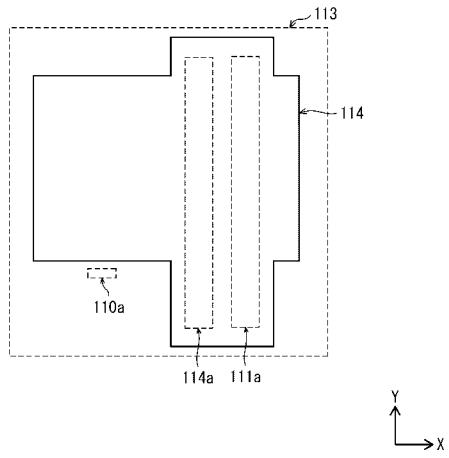

【0026】

補助電極 114 は、下部層間絶縁層 113 及び上部層間絶縁層 115 に設けられているソース電極 110 のコンタクト領域 110a の上方のコンタクト孔を避けて、X 軸方向及び Y 軸方向に延伸して設けられている。なお、補助電極 114 のコンタクト領域 114a は、X 軸方向に複数画素（例えば 3 画素）おきに、Y 軸方向に延伸して設けられている。

(EL 層)

図 4 を参照して EL 層について説明する。

【0027】

上部層間絶縁層 115 上には、補助電極 114 のコンタクト領域 114a の上方のコンタクト孔が開設されていない部分に画素 10a 単位で画素電極 116 が設けられている。画素電極 116 は、パッシベーション層 112、下部層間絶縁層 113、及び上部層間絶縁層 115 のソース電極 110 のコンタクト領域 110a の上方に開設されたコンタクト孔を通してソース電極と接続されている。

【0028】

画素電極 116 上には、画素電極 116 の端縁を被覆するようにバンク 117 が形成されている。バンク 117 の囲繞により、各画素 10a に対応する開口が形成されている。

画素電極 116 上のバンク 117 により規定された開口内には、発光層 118 が形成されている。

発光層 118、バンク 117、及び上部層間絶縁層 115 を被覆するように共通電極層 119 が形成されている。共通電極層 119 は、表示パネル全体に連続した状態で形成され、補助電極 114 のコンタクト領域 114a の上方に設けられた上部層間絶縁層 115 のコンタクト孔を通して補助電極に接続されている。

【0029】

1.2 構成材料

各部の構成材料について説明する。

(1) 基板 100

基板 100、130 としては、例えば、ガラス基板、石英基板、シリコン基板、硫化モリブデン、銅、亜鉛、アルミニウム、ステンレス、マグネシウム、鉄、ニッケル、金、銀

10

20

30

40

50

などの金属基板、ガリウム砒素基などの半導体基板、プラスチック基板等を採用することができる。

【0030】

プラスチック材料としては、熱可塑性樹脂、熱硬化性樹脂いずれの樹脂を用いてもよい。例えば、ポリエチレン、ポリプロピレン、エチレン-プロピレン共重合体、エチレン-酢酸ビニル共重合体(EVA)等のポリオレフィン、環状ポリオレフィン、変性ポリオレフィン、ポリ塩化ビニル、ポリ塩化ビニリデン、ポリスチレン、ポリアミド、ポリイミド(PI)、ポリアミドイミド、ポリカーボネート、ポリ-(4-メチルベンテン-1)、アイオノマー、アクリル系樹脂、ポリメチルメタクリレート、アクリル-スチレン共重合体(AS樹脂)、ブタジエン-スチレン共重合体、ポリオ共重合体(EVOH)、ポリエチレンテレフタレート(PET)、ポリブチレンテレフタレート、ポリエチレンナフタレート(PEN)、ブリシクロヘキサンテレフタレート(PECT)等のポリエステル、ポリエーテル、ポリエーテルケトン、ポリエーテルスルホン(PES)、ポリエーテルイミド、ポリアセタール、ポリフェニレンオキシド、変形ポリフェニレンオキシド、ポリアリレート、芳香族ポリエステル(液晶ポリマー)、ポリテトラフルオロエチレン、ポリフッ化ビニリデン、その他フッ素系樹脂、スチレン系、ポリオレフィン系、ポリ塩化ビニル系、ポリウレタン系、フッ素ゴム系、塩素化ポリエチレン系等の各種熱可塑性エラストマー、エポキシ樹脂、フェノール樹脂、ユリア樹脂、メラミン樹脂、不飽和ポリエステル、シリコーン樹脂、ポリウレタン等、またはこれらを主とする共重合体、ブレンド体、ポリマー-アロイ等が挙げられ、これらのうち1種、または2種以上を積層した積層体を用いることができる。

10

20

20

【0031】

(2) ゲート電極101, 102

ゲート電極101、102としては、例えば、モリブデン-タンゲステン合金(MoW)を採用している。ゲート電極101、102の構成については、これに限定されず、例えば、チタン(Ti)とアルミニウム(Al)との積層体(Ti/Al or Al合金)/Tiなどを採用することもできるし、次のような材料を採用することも可能である。

30

【0032】

採用することが可能な材料としては、モリブデン(Mo)、タンゲステン(W)、銅(Cu)、クロム(Cr)、アルミニウム(Al)、タンタル(Ta)、ニオブ(Nb)、銀(Ag)、金(Au)、プラチナ(Pt)、パラジウム(Pd)、インジウム(In)、ニッケル(Ni)、ネオジム(Nd)などの金属もしくはこれらの合金、または、酸化亜鉛、酸化スズ、酸化インジウム、酸化ガリウムなどの導電性金属酸化物もしくは酸化インジウムスズ(ITO)、酸化インジウム亜鉛(IZO)、酸化アルミニウム亜鉛(AZO)、酸化ガリウム亜鉛(GZO)などの導電性金属複合酸化物、または、ポリアニリン、ポリピロール、ポリチオフェン、ポリアセチレンなどの導電性高分子もしくはそれらに、塩酸、硫酸、スルホン酸などの酸、六フッ化リン、五フッ化ビ素、塩化鉄などのルイス酸、ヨウ素などのハロゲン原子、ナトリウム、カリウムなどの金属原子などのドーパントを添加したもの、もしくは、カーボンブラックや金属粒子を分散した導電性の複合材料などが挙げられる。また、金属微粒子とグラファイトのような導電性粒子を含むポリマー混合物を用いてもよい。これらは、1種または2種以上を組み合わせて用いることもできる。

40

【0033】

(3) ゲート絶縁層103

ゲート絶縁層103としては、例えば、酸化シリコン(SiO<sub>2</sub>)と窒化シリコン(SiN<sub>x</sub>)との積層体を採用している。ただし、ゲート絶縁層103の構成は、これに限定されるものではなく、ゲート絶縁層の構成材料としては、例えば、電気絶縁性を有する材料であれば、公知の有機材料や無機材料のいずれも用いることができる。

【0034】

有機材料としては、例えば、アクリル系樹脂、フェノール系樹脂、フッ素系樹脂、エポ

50

キシ系樹脂、イミド系樹脂、ノボラック系樹脂などを用い形成することができる。

また、無機材料としては、例えば、酸化ケイ素、酸化アルミニウム、酸化タンタル、酸化ジルコニウム、酸化セリウム、酸化亜鉛、酸化コバルトなどの金属酸化物、窒化ケイ素、窒化アルミニウム、窒化ジルコニウム、窒化セリウム、窒化亜鉛、窒化コバルト、窒化チタン、窒化タンタルなどの金属窒化物、チタン酸バリウムストロンチウム、ジルコニウムチタン酸鉛などの金属複合酸化物が挙げられる。これらは、1種または2種以上組み合わせて用いることができる。

#### 【0035】

さらに、表面処理剤 (ODTS OTS HMDS PTS) などでその表面を処理したものも含まれる。

##### (4) チャネル層 104、105

チャネル層 104、105 としては、例えば、アモルファス酸化インジウムガリウム亜鉛 (IGZO) からなる層を採用している。チャネル層 104、105 の構成材料は、これに限定されるものではなく、インジウム (In)、ガリウム (Ga)、亜鉛 (Zn) から選択される少なくとも一種を含む酸化物半導体を採用することができる。

また、チャネル層 104、105 の構成材料として、低温ポリシリコン (LTPS) を用いることもできる。

#### 【0036】

##### (5) チャネル保護層 106

チャネル保護層 106 としては、例えば、酸化シリコン (SiO<sub>2</sub>) からなる層を採用している。チャネル保護層 106 の構成材料は、これに限定されるものではなく、例えば、酸窒化シリコン (SiON)、窒化シリコン (SiN)、あるいは酸化アルミニウム (AlO<sub>x</sub>) を用いることができる。また、上記のような材料を用いた層を複数積層することで構成することもできる。

#### 【0037】

##### (6) ソース電極 107、110、ドレイン電極 108、109

ソース電極 107、110、ドレイン電極 108、109、としては、チタン (Ti) とアルミニウム (Al) との積層体 (Ti / Al (or Al 合金) / Ti) を採用している。また、ソース電極 107、110、ドレイン電極 108、109、としては、銅マンガン (CuMn) と銅 (Cu) とモリブデン (Mo) の積層体を用いることができる。

#### 【0038】

##### (7) パッシベーション層 112

パッシベーション層 112 としては、例えば、酸化シリコン (SiO<sub>2</sub>) からなる層を採用している。パッシベーション層の構成材料は、これに限定されるものではなく、例えば、酸窒化シリコン (SiON)、窒化シリコン (SiN)、あるいは酸化アルミニウム (AlO<sub>x</sub>) を用いることができる。また、上記のような材料を用いた層を複数積層することで構成することもできる。

#### 【0039】

##### (8) 下部層間絶縁層 113

下部層間絶縁層 113 は、例えば、ポリイミド、ポリアミド、アクリル系樹脂材料などの有機化合物を用い形成されている。下部層間絶縁層 113 の構成材料はこれに限定されるものではなく、酸化シリコン (SiO<sub>2</sub>)、酸窒化シリコン (SiON)、窒化シリコン (SiN) などの無機材料を用いて形成することもできる。

#### 【0040】

##### (9) 補助電極 114

補助電極 114 は、例えば、タンゲステンなどの金属材料から構成されている。補助電極 114 の構成材料はこれに限定されるものではなく、金属層や合金層、透明導電層の単層を採用することもできる。また、金属層、合金層、透明導電膜の中から選択される複数の膜を積層させた構造であってもよい。金属層としては、例えば、タンゲステン (W) の他に、酸化タンゲステン (WO<sub>x</sub>)、モリブデン (Mo)、銀 (Ag) またはアルミニウム

10

20

30

40

50

ム ( A 1 ) を含む金属材料から構成することができる。合金層としては、例えば、A P C (銀、パラジウム、銅の合金)、A R A (銀、ルビジウム、金の合金)、M o C r (モリブデンとクロムの合金)、N i C r (ニッケルとクロムの合金)等を用いることができる。透明導電層の構成材料としては、例えば、酸化インジウムスズ ( I T O ) や酸化インジウム亜鉛 ( I Z O ) などを用いることができる。

#### 【 0 0 4 1 】

##### ( 1 0 ) 上部層間絶縁層 1 1 5

上部層間絶縁層 1 1 5 は、例えば、ポリイミド、ポリアミド、アクリル系樹脂材料などの有機化合物を用い形成されている。下部層間絶縁層 1 1 3 の構成材料はこれに限定されるものではなく、酸化シリコン ( S i O <sub>2</sub> ) 、酸窒化シリコン ( S i O N ) 、窒化シリコン ( S i N ) などの無機材料を用いて形成することもできる。

10

#### 【 0 0 4 2 】

##### ( 1 1 ) 画素電極 1 1 6

画素電極 1 1 6 は、タングステン ( W ) とアルミニウム ( A 1 ) 又はアルミニウム合金との積層体から構成されている。トップエミッショ型の表示パネル 1 0 の場合には、その表面部が高い反射性を有することが好ましい。

なお、画素電極 1 1 6 については、上記に示した構成だけではなく、金属層や合金層、透明導電層の単層を採用することもできる。また、金属層、合金層、透明導電膜の中から選択される複数の膜を積層させた構造であってもよい。金属層としては、例えば、タングステン ( W ) 、酸化タングステン ( W O x ) 、銀 ( A g ) またはアルミニウム ( A 1 ) を含む金属材料から構成することができる。合金層としては、例えば、A P C (銀、パラジウム、銅の合金)、A R A (銀、ルビジウム、金の合金)、M o C r (モリブデンとクロムの合金)、N i C r (ニッケルとクロムの合金)等を用いることができる。透明導電層の構成材料としては、例えば、酸化インジウムスズ ( I T O ) や酸化インジウム亜鉛 ( I Z O ) などを用いることができる。例えば、画素電極 1 1 6 は、W O x / A 1 合金、I Z O / A 1 合金、I T O / A 1 合金などの積層体であってもよい。

20

#### 【 0 0 4 3 】

##### ( 1 2 ) バンク 1 1 7

バンク 1 1 7 は、樹脂等の有機材料を用い形成されており絶縁性を有する。バンク 1 1 7 の形成に用いる有機材料の例としては、アクリル系樹脂、ポリイミド系樹脂、ノボラック型フェノール樹脂等があげられる。バンク 1 1 7 は、有機溶剤耐性を有することが好ましい。さらに、バンク 1 1 7 は、製造工程中において、エッチング処理、ベーク処理など施されることがあるので、それらの処理に対して過度に変形、変質などをしないような耐性の高い材料で形成されることが好ましい。また、表面に撥水性をもたせるために、表面をフッ素処理することもできる。

30

#### 【 0 0 4 4 】

さらに、バンク 1 1 7 の構造については、図 4 に示すような一層構造だけでなく、二層以上の多層構造を採用することもできる。この場合には、層毎に上記材料を組み合わせることもできるし、層毎に無機材料と有機材料とを用いることもできる。

40

##### ( 1 3 ) 発光層 1 1 8

発光層 1 1 8 は、上述のように、ホールと電子とが注入され再結合されることにより励起状態が生成され発光する機能を有する。発光層 1 1 8 の形成に用いる材料は、湿式印刷法を用い製膜できる発光性の有機材料を用いることが必要である。

#### 【 0 0 4 5 】

具体的には、例えば、特許文献 2 に記載のオキシノイド化合物、ペリレン化合物、クマリン化合物、アザクマリン化合物、オキサゾール化合物、オキサジアゾール化合物、ペリノン化合物、ピロロピロール化合物、ナフタレン化合物、アントラセン化合物、フルオレン化合物、フルオランテン化合物、テトラセン化合物、ピレン化合物、コロネン化合物、キノロン化合物及びアザキノロン化合物、ピラゾリン誘導体及びピラゾロン誘導体、ローダミン化合物、クリセン化合物、フェナントレン化合物、シクロペンタジエン化合物、ス

50

チルベン化合物、ジフェニルキノン化合物、スチリル化合物、ブタジエン化合物、ジシアノメチレンピラン化合物、ジシアノメチレンチオピラン化合物、フルオレセイン化合物、ピリリウム化合物、チアピリリウム化合物、セレナピリリウム化合物、テルロピリリウム化合物、芳香族アルダジエン化合物、オリゴフェニレン化合物、チオキサンテン化合物、アンスラセン化合物、シアニン化合物、アクリジン化合物、8-ヒドロキシキノリン化合物の金属錯体、2-ビピリジン化合物の金属錯体、シップ塩とIII族金属との錯体、オキシン金属錯体、希土類錯体などの蛍光物質で形成されることが好ましい。透明導電層の構成材料としては、例えば、酸化インジウムスズ(ITO)や酸化インジウム亜鉛(IZO)などを用いることができる。

## 【0046】

10

## (14) 共通電極層119

共通電極層119は、例えば、酸化インジウムスズ(ITO)若しくは酸化インジウム亜鉛(IZO)などを用い形成される。本実施の形態のように、トップエミッション型の本実施の形態に係る表示パネル10の場合においては、光透過性の材料で形成されなければならない。光透過性については、透過率が80[%]以上とすることが好ましい。

## 【0047】

20

## 1.3 製造方法

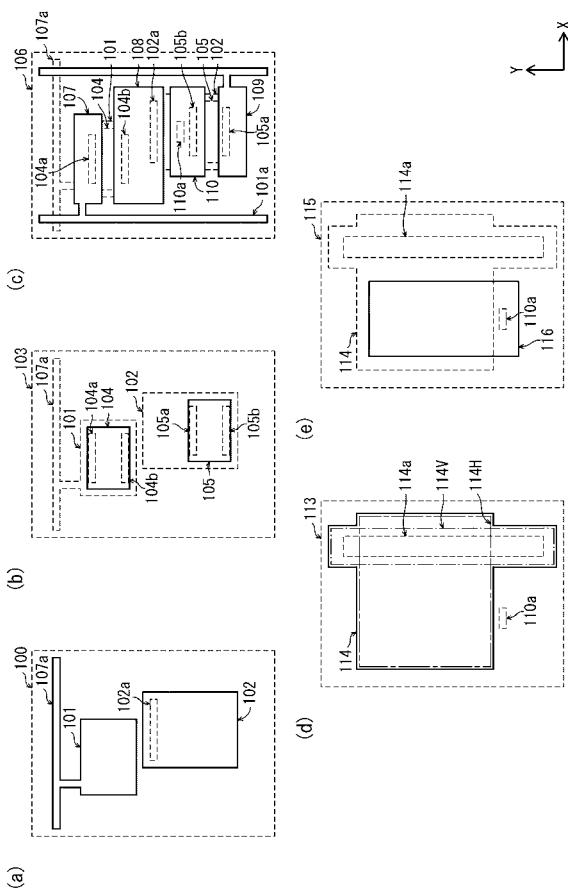

表示パネル10の製造方法について図6及び図7を参照して説明する。

## (1) ゲート電極101、102及びゲート絶縁層103の形成

基板100のZ軸方向上側の表面に、例えば、図6(a)に示すように互いに間隔をあけたゲート電極101、102を形成する。ゲート電極101、102の形成は、例えば、基板100の表面に対して、メタルスパッタリング法を用いてMoWからなる金属薄膜を形成し、その上にフォトリソグラフィー法を用いてレジストパターンを形成する。次に、ウェットエッティングを実施した後、レジストパターンを除去する。これにより、ゲート電極101、102の形成がなされる。

## 【0048】

なお、図6(a)に示す配線101aは図2におけるゲートラインGL-1~nに対応する。

ゲート電極101、102および基板100の表面を被覆するように、ゲート絶縁層103を形成する。ゲート絶縁層103形成は、プラズマCVD(Chemical Vapor Deposition)法あるいはスパッタリング法を用いてなされる。

30

## 【0049】

## (2) チャネル層104、105及びチャネル保護層106の形成

ゲート絶縁層103の表面に、例えば、図6(b)に示すように互いに間隔をあけたチャネル層104、105を形成する。チャネル層104、105の形成は、例えば、スパッタリング法を用い、酸化物半導体膜を形成し、フォトリソグラフィー法およびウェットエッティング法を用いてパターニングすることでなされる。

## 【0050】

40

チャネル層104、105およびゲート絶縁層103の表面を被覆するように、チャネル保護層106を積層形成する。チャネル保護層106の形成は、プラズマCVD法あるいはスパッタリング法を用い、SiOからなる層を積層形成し、成膜後にドライエアまたは酸素雰囲気下で、成膜温度以上の温度でアニール処理を実行することでなされる。

(3) ソース電極107、110、ドレイン電極108、109の形成、パッシベーション層112の形成

チャネル保護層106の表面に、例えば、図6(c)に示すように、ソース電極107、110およびドレイン電極108、109を形成する。

## 【0051】

50

先ず、ゲート絶縁層103及びチャネル保護層106の該当部分(ゲート電極102、チャネル層104、105のコンタクト領域102a、104a、104b、105a、105bの上方の部分)にコンタクト孔をあける。コンタクト孔の形成は、フォトリソグ

ラフィー法を用いパターン形成した後、ドライエッチング法を用いエッチングを実行することでなされる。次に、スパッタリング法を用い、例えば、Tiからなる金属薄膜と、Alからなる金属薄膜と、Tiからなる金属薄膜とを順に積層する。そして、フォトリソグラフィー法およびウェットエッチング法を用い、ソース電極107、110およびドレイン電極108、109をパターニング形成する。

#### 【0052】

なお、図6(c)に示す配線107aは図2におけるソースラインSL-1~nに対応する。また、図6(c)に示す配線109aは図2における電源ラインVaに対応する。

ソース電極107、110およびドレイン電極108、109およびチャネル保護層106を被覆するように、パッシベーション層112を形成する。パッシベーション層112の形成は、プラズマCVD法、ALD(Atomic Layer Deposition)法、あるいはスパッタリング法を用い成膜することでなされる。

#### 【0053】

(4) 下部層間絶縁層113、補助電極114、上部層間絶縁層115の形成

パッシベーション層112を被覆するように、下部層間絶縁層113を積層形成する。下部層間絶縁層113の形成は、上述の有機材料を塗布し、表面を平坦化することによりなされる。

補助電極114の形成は、スパッタリング法あるいは真空蒸着法などを用い、タンゲステン(W)からなる金属膜を成膜した後、フォトリソグラフィー法およびエッチング法を用い、パターニングすることでなされる。例えば、図6(d)に示すように、ソース電極110のコンタクト領域110aの上方に位置する部分を避けて、X軸方向に延伸する領域114HとY軸方向に延伸する領域114Vとを有するように、補助電極114をパターニングする。領域114HはX軸方向に複数画素にわたって延伸して設けられ、領域114VはY軸方向に複数画素にわたって延伸して設けられる。領域114V内には、補助電極114のコンタクト領域114aが設けられる。

#### 【0054】

下部層間絶縁層113及び補助電極114を被覆するように、上部層間絶縁層115を積層形成する。上部層間絶縁層115の形成は、上述の有機材料を塗布し、表面を平坦化することによりなされる。

#### (5) 画素電極116の形成

下部層間絶縁層113及び上部層間絶縁層115におけるソース電極110のコンタクト領域110a上にコンタクト孔を開設し、画素電極116を形成する。

#### 【0055】

コンタクト孔の形成は、フォトリソグラフィー法を用いパターン形成した後、ドライエッチング法を用いエッチングを実行することでなされる。画素電極116の形成は、スパッタリング法あるいは真空蒸着法などを用い、タンゲステン(W)からなる薄膜とアルミニウム(Al)又はアルミニウム合金からなる薄膜とを順に積層して金属膜を成膜した後、フォトリソグラフィー法およびエッチング法を用い、例えば、図6(e)に示すようにパターニングすることでなされる。配列状に複数の画素電極116をパターニング形成することにより、図7(a)に示すように上部層間絶縁層115上に複数の画素電極116が形成される。

#### 【0056】

なお、画素電極116は、コンタクト孔を通してソース電極110のコンタクト領域と接触し、ソース電極110と電気的に接続された状態となる。

また、下部層間絶縁層113及び上部層間絶縁層115におけるソース電極110のコンタクト領域110a上にコンタクト孔を開設するのと同様の手順により、上部層間絶縁層115における補助電極114のコンタクト領域114a上にコンタクト孔を開設する。

#### 【0057】

#### (6) バンク117の形成

10

20

30

40

50

画素電極 116 に対して、その縁部を覆うようにバンク 117 を形成する。バンク 117 は、各画素を規定する開口を囲繞し、その底部に画素電極 116 の表面が露出するよう 10 に設けられる。

バンク 117 の形成では、図 7 (b) に示すように行バンク 117H を形成し、その後、図 7 (c) に示すように列バンク 117V を形成する。

#### 【0058】

バンク 117 の形成は、先ず、画素電極 116 及び上部層間絶縁層 115 の上に、スピ 10 ノコート法などを用い、バンク 117 の構成材料（例えば、感光性樹脂材料）からなる膜を積層形成する。そして、樹脂膜をパターニングして行バンク 117H、列バンク 117V を順に形成することにより画素電極 116 が露出する開口を形成する。行バンク 117H、列バンク 117V のパターニングは、樹脂膜の上方にフォトマスクを利用し露光を行い、現像工程、焼成工程をすることによりなされる。

#### 【0059】

##### (7) 発光層 118 の形成

発光層 118 の形成は、インクジェット法を用い、構成材料を含むインクをバンク 117 により規定される開口内に塗布した後、焼成することによりなされる。具体的には、この工程では、開口において露出する画素電極 116 上に、インクジェット法により R、G、B いずれかの有機発光層の材料を含むインクを充填し、充填したインクを減圧下で乾燥させ、ベーク処理することによって、図 7 (d) に示すように発光層 118 を形成する。このとき、発光層 118 のインクの塗布では、先ず、液滴吐出装置を用いて発光層 118 の形成するための溶液の塗布を行う。赤色発光層、緑色発光層、青色発光層の何れかを形成するためのインクの塗布が終わると、次に、別の色のインクを塗布し、次に 3 色目のインクを塗布する工程が繰り返し行われ、3 色のインクを順次塗布する。これにより、赤色発光層、緑色発光層、青色発光層が、繰り返して並んで形成される。

#### 【0060】

##### (8) 共通電極層 119 の形成

発光層 123 を形成した後、図 7 (e) に示すように、表示パネル 10 の全面にわたって、CVD (Chemical Vapor Deposition) 法、スパッタリング法などにより、共通電極層 119 を形成する。

共通電極層 119 は、上部層間絶縁層 115 上の補助電極 114 のコンタクト領域 114a が露出するコンタクト孔の上にも形成される。共通電極層 119 は、コンタクト孔を通して補助電極 114 のコンタクト領域 114a と接触し、補助電極 114 と電気的に接続された状態となる。

#### 【0061】

##### 1.4 効果

表示パネル 10 は、画素電極 116 と異なる層に補助電極 114 を形成するので、画素電極 116 の小面積化を抑制でき、その結果、画素開口率の低下を抑えることができる。

また、補助電極 114 を専用の層に形成するので補助電極 114 の配線自由度が高い。具体的に、下部層間絶縁層 113 上に画素電極 116 とソース電極 110 とを電気的に接続するためのコンタクト孔を避けて補助電極 114 をパターニングするという制約を守れば、下部層間絶縁層 113 上に補助電極 114 を自由にパターニングすることが可能である。これにより、補助電極 114 の大面積化が容易であり、その結果、共通電極層の低抵抗化を実現できる。

#### 【0062】

##### 2 变形例

実施の形態 1 に係る表示パネル 10 を説明したが、本開示は、その本質的な特徴的構成要素を除き、上述の実施の形態に限定されるものではない。例えば、実施の形態に対して当業者が思いつく各種変形を施して得られる形態や、本発明の趣旨を逸脱しない範囲で各実施の形態における構成要素及び機能を任意に組み合わせることで実現される形態も本開示に含まれる。以下では、そのような形態の一例として、表示パネル 10 の変形例を説明

10

20

30

40

50

する。

#### 【0063】

(1) 実施の形態1において補助電極114は、平坦化層を構成する下部層間絶縁層113と上部層間絶縁層の間に形成するとしたが、補助電極の形成位置はこれに限定されるものではない。補助電極は、TFT層に形成することも可能である。

以下、変形例1に係る表示パネルとして、補助電極をTFT層に形成する表示パネルについて説明する。なお、実施の形態1と同じ構成・構成材料・製造方法については説明を省略する。

#### 【0064】

##### (1-1. 構成)

変形例1に係る表示パネルの構成について図8, 9を用いて説明する。図8は、表示パネルのYZ平面の断面構成の一例を示す図であり、図9は、表示パネルのXZ平面の断面構成の一例を示す図である。

図9に示すように、チャネル保護層106上には、ソース電極107、110及びドレイン電極108、109と間隔を開けて、補助電極111が形成されている。そして、ソース電極107、110、ドレイン電極108、109、補助電極111及びチャネル保護層106の表面を被覆するようにパッシベーション層112が形成されている。

#### 【0065】

パッシベーション層112上には、下部層間絶縁層113が形成されている。パッシベーション層112及び下部層間絶縁層113には、補助電極111のコンタクト領域111aの上方にコンタクト孔が設けられており、このコンタクト孔の底で、共通電極層119が補助電極111に接触している。

上述の実施の形態1と異なり、図8, 9に示すように、下部層間絶縁層113上には、補助電極114及び上部層間絶縁層115形成されず、画素電極116、バンク117、共通電極層119が形成されている。

#### 【0066】

なお、図示してはいないが、補助電極111は、ソース電極107、110、ドレイン電極108, 109を避けて、X軸方向及び/又はY軸方向に延伸して複数の画素に連続して設けられている。なお、補助電極111のコンタクト領域111aは、X軸方向に複数画素おきに、Y軸方向に延伸して設けられている。

##### (1-2. 構成材料)

補助電極111としては、ソース電極107、110、ドレイン電極108、109と同様の構成材料、すなわち、チタン(Ti)とアルミニウム(Al)との積層体(Ti/Al (or Al合金)/Ti)や、銅マンガン(CuMn)と銅(Cu)とモリブデン(Mo)の積層体を用いることができる。

#### 【0067】

##### (1-3. 製造方法)

変形例1に係る表示パネルの製造方法について説明する。

チャネル保護層106の表面に、補助電極111を形成する。補助電極111の形成は、スパッタリング法を用い、Tiからなる金属薄膜と、Alからなる金属薄膜と、Tiからなる金属薄膜とを順に積層する。そして、フォトリソグラフィー法およびウェットエッチング法を用い、補助電極111を図10に示すようにパターニング形成する。なお、補助電極111の形成は、ソース電極107、110、ドレイン電極108、109の形成と一緒にして行うことができる。

#### 【0068】

下部層間絶縁層113における補助電極111のコンタクト領域111a上へのコンタクト孔の開設は、実施の形態1において、上部層間絶縁層115における補助電極114のコンタクト領域114a上へのコンタクト孔の開設と同様の手順で行うことができる。

##### (1-4. 効果)

変形例1に係る表示パネル10は、画素電極116と異なる層に補助電極114を形成

10

20

30

40

50

するので、画素電極 116 の小面積化を抑制でき、その結果、画素開口率の低下を抑えることができる。

#### 【0069】

また、ソース電極 107, 110 及びドレイン電極 108, 109 と同層に同じ構成材料で補助電極 111 を形成するので、製造工程の簡素化が可能である。

(2) 変形例 1 に係る表示パネルでは、TFT 層に補助電極を形成し、平坦化層には補助電極を形成しないとしたが、TFT 層と平坦化層の両方に補助電極を形成してもよい。

以下、変形例 2 に係る表示パネルとして、TFT 層と平坦化層の両方補助電極を形成する表示パネルについて説明する。なお、実施の形態 1、変形例 1 と同じ構成・構成材料・製造方法については説明を省略する。

10

#### 【0070】

##### (2-1) 構成

変形例 2 に係る表示パネルの構成について図 11 を用いて説明する。

図 11 に示すように、変形例 1 と同様に、チャネル保護層 106 上には、ソース電極 107、110 及びドレイン電極 108、109 と間隔を開けて、補助電極 111 が形成されている。

#### 【0071】

また、実施の形態 1 と同様に、下部層間絶縁層 113 上には、補助電極 114 及び上部層間絶縁層 115 形成されている。

パッセーション層 112 及び下部層間絶縁層 113 には、補助電極 111 のコンタクト領域 111a の上方にコンタクト孔が設けられており、このコンタクト孔の底で、補助電極 114 が補助電極 111 に接触している。

20

#### 【0072】

##### (2-2) 製造方法

変形例 2 に係る表示パネルの製造方法について説明する。

変形例 1 と同様に、チャネル保護層 106 の表面に、補助電極 111 を形成し、その後、下部層間絶縁層 113 における補助電極 111 のコンタクト領域 111a 上方にコンタクト孔を開設する。

#### 【0073】

下部層間絶縁層 113 にコンタクト孔を開設した後、補助電極 114 を形成する。補助電極 114 の形成は、スパッタリング法あるいは真空蒸着法などを用い、タンゲステン (W) からなる金属膜を成膜した後、フォトリソグラフィー法およびエッチング法を用い、例えば、図 12 に示すようにパターニングすることでなされる。補助電極 111 のコンタクト領域 111a 上方の下部層間絶縁層 113 に開設されたコンタクト孔の底で補助電極 114 と補助電極 111 とが接触する。そして、補助電極 114 に設けられたコンタクト領域 114a において、共通電極層 119 と補助電極 114 とが接触する。

30

#### 【0074】

##### (2-3) 効果

変形例 2 に係る表示パネル 10 は、画素電極 116 と異なる層に補助電極 114 を形成するので、画素電極 116 の小面積化を抑制でき、その結果、画素開口率の低下を抑えることができる。

40

また、補助電極 114 を専用の層に形成するので補助電極 114 の配線自由度が高い。これにより、補助電極 114 の大面積化が容易であり、その結果、共通電極層の低抵抗化を実現できる。

#### 【0075】

また、ソース電極 107, 110 及びドレイン電極 108, 109 と同層に同じ構成材料で補助電極 111 を形成するので、製造工程の簡素化が可能である。

(3) 有機 EL 表示パネルの製造工程において、発光効率向上のために、発光層と共通電極層との間に、共通電極層から注入された電子を発光層へ輸送する機能を有する電子輸送層などの有機層を形成することが可能である。発光層を形成した後に、真空蒸着法など

50

の成膜方法を用いて、表示パネルの前面に有機層を形成すると、補助電極と共に電極層との間にも比較的電気抵抗の高い有機層が形成され、補助電極と共に電極層との間の電気抵抗が高くなるという課題がある。これに対し、マスクを用いて、補助電極と共に電極層との接触部分を避けて有機層を成膜することにより、補助電極と共に電極層との間の電気抵抗が高くなることを防ぐことができる。また、補助電極の共通電極層との接触部分の形状を工夫することにより、マスク蒸着を行わずに、補助電極と共に電極層との間の電気抵抗が高くなることを防ぐことができる。

#### 【0076】

変形例3に係る表示パネルとして、発光層と共に電極層との間に電子輸送層などの有機層を形成する場合において、マスク蒸着を行わずに、補助電極と共に電極層との間の電気抵抗が高くなることを防ぐことのできる表示パネルを説明する。なお、実施の形態1、変形例1、変形例2と同じ構成・構成材料・製造方法については説明を省略する。

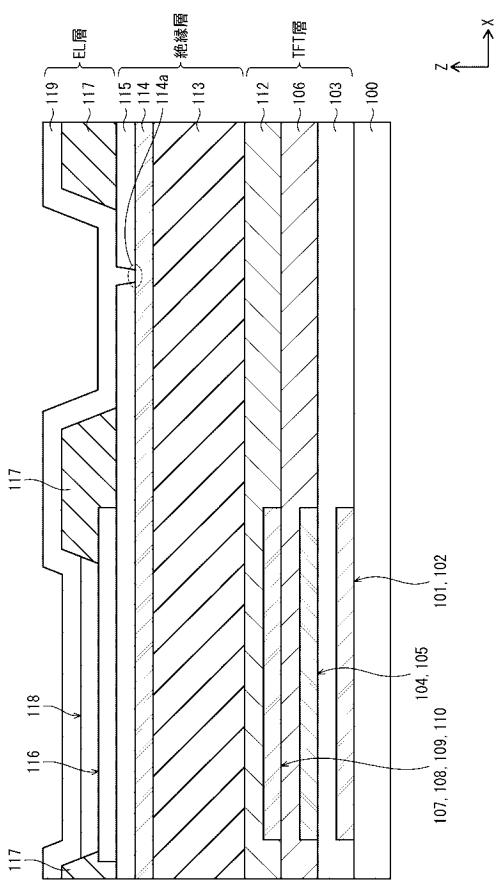

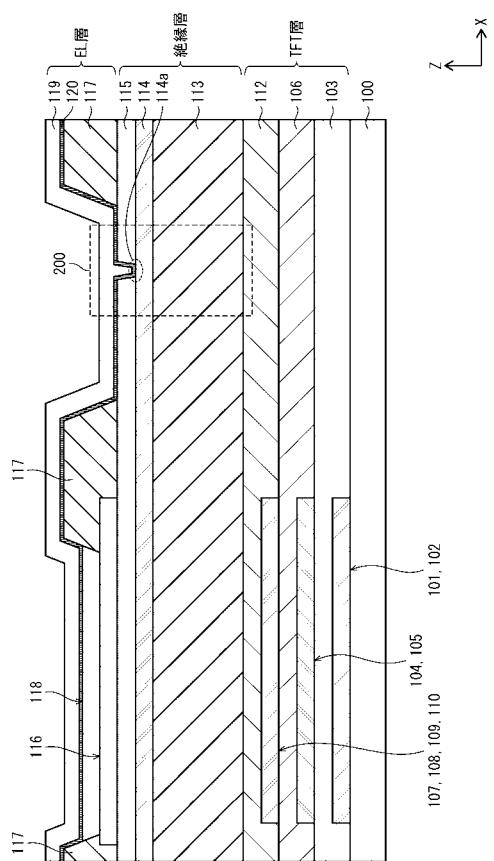

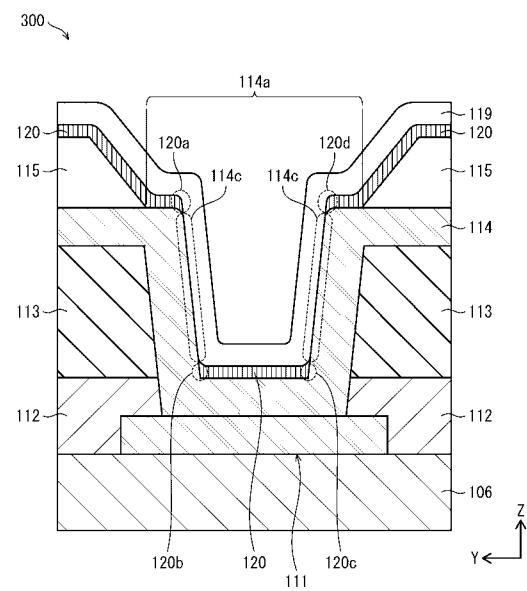

##### (3-1.構成)

変形例3に係る表示パネルの構成について図13を用いて説明する。図13は、表示パネルのXZ平面の断面構成の一例を示す図である。

#### 【0077】

変形例3に係る表示パネルにおいては、発光層118と共に電極層119との間に、電子輸送層120が形成される。電子輸送層120については、表示パネル10全体に連続した状態で形成されている。すなわち、上部層間絶縁層115に開設されたコンタクト孔の底に露出している補助電極114の上方にも電子輸送層120が形成され、さらにその上方に共通電極層119が形成されている。

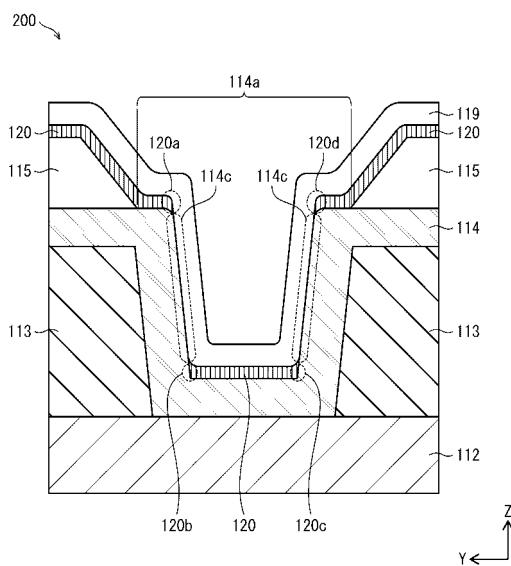

#### 【0078】

変形例3に係る表示パネルにおける補助電極114と共に電極層119との接続部分について図14を用いて説明する。図14は、実施の形態1の表示パネルにおける図13の符号200の部分に相当する、変形例3に係る表示パネルにおける補助電極114と共に電極層119との接続部分の断面の模式図である。

図14に示すように、下部層間絶縁層113の補助電極114の下方に位置する部分の一部にコンタクト孔が開設され底にパッシベーション層112が露出している。そして、このコンタクト孔に沿って、補助電極114にパッシベーション層112側（基板100側）に凹入した凹部が形成されている。

#### 【0079】

補助電極114の上方には、上部層間絶縁層115が形成されており、上部層間絶縁層115には、補助電極114の凹部を含むコンタクト領域114aが露出するコンタクト孔が開設されている。

上部層間絶縁層115及びコンタクト孔により露出している補助電極114の上方には電子輸送層120が形成されている。電子輸送層120は、補助電極114の凹部において、完全に又は部分的に欠落（図の端部120a～b間、または、端部120c～d間）しており、欠落部分において補助電極114のコンタクト面114cが露出している。

#### 【0080】

電子輸送層120の上方には、共通電極層119が形成されている。共通電極層119は、電子輸送層120の欠落部分（端部120a～b間、または端部120c～d間）において露出している補助電極114のコンタクト面114cと、直接接触するように形成されている。

##### (3-2.構成材料)

電子輸送層120は、電子輸送性が高い有機材料が用いられる。電子輸送層120に用いられる有機材料としては、例えば、オキサジアゾール誘導体（OXD）、トリアゾール誘導体（TAZ）、フェナンスロリン誘導体（BCP、Bphen）などの電子系低分子有機材料が挙げられる。また、電子輸送層120は、電子輸送性が高い有機材料に、アルカリ金属、又は、アルカリ土類金属から選択されるドープ金属がドープされて形成された層を含んでいてもよい。また、電子輸送層120は、フッ化ナトリウムで形成された層

10

20

30

40

50

を含んでいてもよい。アルカリ金属は、具体的には、Li(リチウム)、Na(ナトリウム)、K(カリウム)、Rb(ルビジウム)、Cs(セシウム)、Fr(フランシウム)である。また、アルカリ土類金属は、具体的には、Ca(カルシウム)、Sr(ストロンチウム)、Ba(バリウム)、Ra(ラジウム)である。

#### 【0081】

##### (3-3. 製造方法)

変形例3に係る表示パネルの製造方法について図15を参照して説明する。

図15は、変形例3に係る表示パネルにおける補助電極114と共通電極層119との接続部分の製造方法を説明する図である。

まず、パッシベーション層112上に、下部層間絶縁層113を形成し(図15(a))、形成した下部層間絶縁層113に、フォトリソグラフィー法を用いパターン形成した後、ドライエッティング法を用いエッティングを実行することにより、コンタクト孔を開設する(図15(b))。

#### 【0082】

下部層間絶縁層113にコンタクト孔を開設した後、スパッタリング法あるいは真空蒸着法などを用い、タンクステン(W)からなる金属膜を成膜し、フォトリソグラフィー法およびエッティング法を用い、パターニングすることにより、補助電極114を形成する(図15(c))。このとき、コンタクト孔の内壁に沿って金属膜を形成することにより補助電極114の凹部を形成する。

#### 【0083】

補助電極114を形成した後、下部層間絶縁層113及び補助電極114を被覆するように上部層間絶縁層を形成し(図15(d))、形成した上部層間絶縁層115に、フォトリソグラフィー法を用いパターン形成した後、ドライエッティング法を用いエッティングを実行することにより、コンタクト孔を開設する(図15(e))。

下部層間絶縁層113にコンタクト孔を開設した後、真空蒸着法などにより電子輸送層120を形成する(図15(f))。このとき、補助電極114の凹部のコンタクト面114cにおいて意図的に欠落(段切れ)を発生させ、その欠落部分において補助電極114の凹部のコンタクト面114cが露出するように成膜する。

#### 【0084】

電子輸送層120を形成した後、電子輸送層120を被覆するように、共通電極層119を、CVD(Chemical Vapour Deposition)法、スパッタリング法などにより形成する(図15(g))。このとき、共通電極層119は、電子輸送層120の欠落部分に回り込み、電子輸送層120の欠落部分において露出している補助電極114の凹部のコンタクト面114cに直接接触するように成膜する。

#### 【0085】

##### (3-4. 補助電極114と共通電極層119とを直接接觸させる構成)

補助電極114では、コンタクト面114cの傾斜角は60[度]以上120[度]以下であることが望ましい。60[度]未満では、電子輸送層120が断切れせず、共通電極層119との電気的接続を確保しにくくなる。一方、120[度]を超えると、共通電極層119も補助電極114の凹部の内壁で断切れてしまい、補助電極114が共通電極層119と接觸しにくくなるためである。この傾斜角は、下部層間絶縁層113に開設されるコンタクト孔の側面の傾斜角と一致するため、下部層間絶縁層113にコンタクト孔を形成する際の露光量により制御することができる。また、補助電極114の凹部の深さは、例えば、1[μm]以上から7[μm]の範囲で形成される。補助電極114の凹部の幅は、例えば2[μm]から10[μm]の範囲で形成される。

#### 【0086】

このような形状により、補助電極114の上に形成される電子輸送層120は、補助電極114の凹部において途切れ(断切れして)形成される。詳細には、電子輸送層120では、補助電極114のコンタクト面114cが露出するように、端部120a, b間(あるいは端部120c, d間)が離れて配置される。一方、共通電極層119は、この

10

20

30

40

50

電子輸送層 120 の端部 120a, b 間 (あるいは端部 120c, d 間) に回り込むよう に、補助電極 114 のコンタクト面 114c に接触して形成される。

【0087】

補助電極 114 は、下部層間絶縁層 113 のコンタクト孔の側面で段切れしないように、ステップカバレッジの優れた成膜方法 (例えば、スパッタリング法や CVD 法) により形成することが望ましい。また、ステップカバレッジの優れた成膜方法によっても補助電極 114 の膜厚が過度に薄いと、段切れが発生する可能性があるため、膜厚は、25 [nm] 以上で形成することが好ましい。

【0088】

電子輸送層 120 は、補助電極 114 の凹部において段切れしてコンタクト面 114c が露出するように、比較的ステップカバレッジの劣る成膜方法 (例えば、真空蒸着法) により形成することが望ましい。また、電子輸送層 120 の膜厚が過度に薄いと、共通電極層 119 から発光層 118 へ電子が直接移動し、発光層 118 への電子の注入を制限する機能を果たせない。従って、電子輸送層 120 の膜厚を 3 [nm] 以上に形成することが望ましい。一方、電子輸送層 120 の厚膜化は、電子輸送層 120 の透過率を低下させ、また、段切れの発生を阻害する。電子輸送層 120 を通過する光を過度に減衰させないため、かつ、補助電極 114 の凹部において意図的に段切れを発生させるため、電子輸送層 120 の膜厚を 40 [nm] 以下に形成することが好ましい。

10

【0089】

共通電極層 119 は、電子輸送層 120 の段切れ部分にまわりこんで形成されるように、ステップカバレッジの優れた成膜方法 (例えば、スパッタリング法や CVD 法) により形成することが望ましい。共通電極層 119 が過度に薄いと、段切れ発生の要因にもなるため、共通電極層 119 は膜厚を 25 [nm] 以上に形成することが望ましい。一方、共通電極層 119 の厚膜化は、共通電極層 119 の透過率を低下させるため、共通電極層 119 は膜厚を 300 [nm] 以下に形成することが望ましい。

20

【0090】

(3-5. 効果)

変形例 3 に係る表示パネルは、補助電極 114 に凹部を設けることにより、電子輸送層 120 を段切れさせ、段切れによって露出した補助電極 114 のコンタクト面 114c と共通電極層 119 とが直接接触する構成である。係る構成により、電子輸送層 120 を形成する際に、補助電極 114 を避けて形成するためにマスク蒸着を行う必要がなく、精密マスクの高精度の位置合わせに伴う生産性低下を回避することができる。

30

【0091】

なお、変形例 2 に係る表示パネルのように、TFT 層及び平坦化層に補助電極を形成する場合にも、図 16, 17 に示すように補助電極を形成することにより同様の効果を奏する。

(4) 変形例 3 に係る表示パネルにおいて、電子輸送層 120 は、補助電極 114 の凹部内においてコンタクト面 114c が露出するように欠落しているとしたが、共通電極層 119 と補助電極 114 との電気的接続における電気抵抗の低減することができれば、欠落しておらずコンタクト面 114c が完全に露出していなくてもよい。例えば、電子輸送層 120 は、補助電極 114 の凹部内においてコンタクト面 114c に接する部分が例えば、1 [nm] 以下の膜厚まで薄層化し、薄層化している部分において、それ以外の電子輸送層 120 の部分よりも低い電気抵抗で共通電極層 119 が補助電極 114 に電気的に接続されていてもよい。

40

【0092】

(5) 上述の実施の形態において、画素電極 116 と発光層 118 との間にホール注入層が形成されてもよい。

ホール注入層は、ホールの生成を補助し、発光層 118 に対して安定的にホールを注入及び輸送する機能を有する。ホール注入層は、例えば、銀 (Ag)、モリブデン (Mo)、クロム (Cr)、バナジウム (V)、タンゲステン (W)、ニッケル (Ni)、イリジ

50

ウム (Ir) などの酸化物、あるいは、PEDOT (ポリチオフェンとポリスチレンスルホン酸との混合物) などの導電性ポリマー材料からなる層である。

【0093】

(6) 以上で説明した実施の形態は、いずれも本発明の好ましい一具体例を示すものである。実施の形態で示される数値、形状、材料、構成要素、構成要素の配置位置及び接続形態、工程、工程の順序などは一例であり、本発明を限定する主旨ではない。また、実施の形態における構成要素のうち、本発明の最上位概念を示す独立請求項に記載されていない工程については、より好ましい形態を構成する任意の構成要素として説明される。

【0094】

また、上記の工程が実行される順序は、本発明を具体的に説明するために例示するためのものであり、上記以外の順序であってもよい。また、上記工程の一部が、他の工程と同時に（並列）に実行されてもよい。

また、発明の理解の容易のため、上記各実施の形態で挙げた各図の構成要素の縮尺は実際のものと異なる場合がある。また本発明は上記各実施の形態の記載によって限定されるものではなく、本発明の要旨を逸脱しない範囲において適宜変更可能である。

【0095】

また、各実施の形態及びその変形例の機能のうち少なくとも一部を組み合わせてもよい。

さらに、本実施の形態に対して当業者が思いつく範囲内の変更を施した各種変形例も本発明に含まれる。

3 補足

以下、更に、本開示の構成について説明する。

【0096】

(1) 本開示の第1態様に係る有機EL表示パネルは、基板と、基板上に配された薄膜半導体層と、薄膜半導体層上に配された下部絶縁層と、下部絶縁層上に部分的に配され、基板側に凹入する凹部を有する給電用の補助電極と、下部絶縁層及び補助電極の上方に配された上部絶縁層と、上部絶縁層上に配されたEL素子と、を備える。上部絶縁層には、補助電極の凹部まで達するコンタクト孔が開設されている。EL素子は、上部絶縁層上のコンタクト孔が開設されていない部分に配された画素電極と、画素電極上に配された発光層と、発光層上及びコンタクト孔内に配された共通電極層と、を含む。コンタクト孔において、共通電極層は、孔内壁及び補助電極表面に沿って形成されている。

【0097】

(2) 本開示の第2態様に係る有機EL表示パネルは、第1態様に係る有機EL表示パネルにおいて、EL素子は、さらに、発光層上及びコンタクト孔内、かつ共通電極層の下方に配された機能層を含む。コンタクト孔内において、機能層は、孔内壁及び補助電極表面に沿って形成され、補助電極の凹部の内壁に位置する部分が欠落している又は薄層化しており、共通電極層は、機能層の欠落により露出している補助電極と直接接触し、機能層が薄層化している部分においてそれ以外の機能層の部分よりも低い抵抗にて補助電極に電気的に接続している。

【0098】

(3) 本開示の第3態様に係る有機EL表示パネルは、第1態様に係る有機EL表示パネルにおいて、補助電極を第1補助電極、コンタクト孔を第1コンタクト孔と定義した場合、薄膜半導体層は、基板上に配されるゲート電極と、ゲート電極の上方に配されるソース電極及びドレイン電極と、ソース電極及びドレイン電極と同層に配される第2補助電極であって、第1補助電極の下方に位置する部分に配される第2補助電極と、を含む。下部絶縁層には、第2補助電極まで達する第2コンタクト孔が開設されている。第2コンタクト孔内において、第1補助電極は、孔内壁及び第2補助電極表面に沿って形成されている。

【0099】

(4) 本開示の第4態様に係る有機EL表示パネルの製造方法は、基板上に薄膜半導体

10

20

30

40

50

層を形成する工程と、薄膜半導体層上に下部絶縁層を形成する工程と、下部絶縁層上に部分的に、基板側に凹入する凹部を有する給電用の補助電極を形成する工程と、下部絶縁層及び補助電極の上方に上部絶縁層を形成する工程と、上部絶縁層に、補助電極の凹部まで達するコンタクト孔を開設する工程と、上部絶縁層上にEL素子を形成する工程と、を含む。EL素子を形成する工程は、上部絶縁層上のコンタクト孔が開設されていない部分に画素電極を形成する工程と、画素電極上に発光層を形成する工程と、発光層上及びコンタクト孔内に共通電極層を形成する工程と、を含む。共通電極層を形成する工程は、コンタクト孔内において、孔内壁及び補助電極表面に沿って共通電極層を形成する。

#### 【0100】

(5) 本開示の第5態様に係る有機EL表示パネルの製造方法は、第4態様に係る有機EL表示パネルの製造方法において、EL素子を形成する工程は、さらに、発光層の上方及びコンタクト孔内、かつ共通電極層の下方に機能層を形成する工程を含む。機能層を形成する工程は、コンタクト孔内において、孔内壁及び補助電極表面に沿って、補助電極の凹部の内壁上に位置する部分において欠落する又は薄層化するよう真空蒸着法により機能層を形成する。共通電極層を形成する工程は、機能層の欠落により露出している補助電極と直接接触するように、機能層が薄層化している部分においてそれ以外の機能層の部分よりも低い抵抗にて補助電極に電気的に接続するように、共通電極層をスパッタリング法またはCVD (Chemical Vapor Deposition) 法により形成する。

10

#### 【0101】

(6) 本開示の第6態様に係る有機EL表示パネルの製造方法は、第4態様の有機EL表示パネルの製造方法において、補助電極を第1補助電極、コンタクト孔を第1コンタクト孔と定義した場合、薄膜半導体層を形成する工程は、基板上にゲート電極を形成する工程と、ゲート電極の上方にソース電極及びドレイン電極を形成する工程と、ソース電極及びドレイン電極と同層に第2補助電極を形成する工程と、を含む。更に、有機EL表示パネルの製造方法は、更に、下部絶縁層に、第2補助電極まで達する第2コンタクト孔を開設する工程、を含む。第1補助電極を形成する工程は、第2コンタクト孔内において、孔内壁及び第2補助電極表面に沿って、第1補助電極を形成する。

20

#### 【0102】

(7) 本開示の第7態様に係る有機EL表示パネルは、基板と、基板上に配されたゲート電極と、ゲート電極の上方に配されたソース電極及びドレイン電極と、ソース電極及びドレイン電極と同層に配された給電用の補助電極と、ソース電極、ドレイン電極、及び補助電極の上方に配された絶縁層と、絶縁層の上方に配されたEL素子と、を備える。絶縁層には、補助電極まで達するコンタクト孔が開設されている。EL層は、絶縁層上のコンタクト孔が開設されていない部分に配された画素電極と、画素電極上に配された発光層と、発光層上及びコンタクト孔内に配された共通電極層と、を含む。コンタクト孔内において、共通電極層は、孔内壁及び補助電極表面に沿って形成されている。

30

#### 【0103】

(8) 本開示の第8態様に係る有機EL表示パネルは、基板と、基板上に配されたゲート電極と、ゲート電極の上方に配されたソース電極及びドレイン電極と、ソース電極及びドレイン電極と同層に配された給電用の第1補助電極と、ソース電極、ドレイン電極、及び第1補助電極の上方に配された下部絶縁層と、下部絶縁層上の第1補助電極の上方に位置する部分に配された給電用の第2補助電極と、下部絶縁層及び第2補助電極の上方に配された上部絶縁層と、上部絶縁層上に配されたEL素子と、を備える。下部絶縁層には、第1補助電極まで達する第1コンタクト孔が開設されている。第2補助電極は、第1コンタクト孔内において第1コンタクト孔の内壁及び第1補助電極の表面に沿って形成されている。上部絶縁層には、第2補助電極まで達する第2コンタクト孔が開設されている。EL素子は、上部絶縁層上の第2コンタクト孔が開設されていない部分に配された画素電極と、画素電極上に配された発光層と、発光層上及び第2コンタクト孔内に配された共通電極層と、を含む。第2コンタクト孔内において、共通電極層は、孔内壁及び第2補助電極

40

50

表面に沿って形成されている。

【産業上の利用可能性】

【0104】

本発明に係る有機EL表示パネル、及び有機EL表示装置は、テレビジョンセット、パソコン用コンピュータ、携帯電話などの装置、又はその他表示パネルを有する様々な電子機器に広く利用することができる。

【符号の説明】

【0105】

1 表示装置

10 表示パネル

100 基板

101, 102 ゲート電極

104, 105 チャネル層

107, 110 ソース電極

108, 109 ドレイン電極

111, 114 補助電極

116 画素電極

117 バンク

118 発光層

119 共通電極層

10

20

【図1】

【図2】

【 図 3 】

【 図 4 】

【 図 5 】

〔 囮 6 〕

【 図 7 】

【 図 8 】

【 図 9 】

【 図 1 0 】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

|                |                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL显示面板和制造有机EL显示面板的方法                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2019012642A</a>                                                                                            | 公开(公告)日 | 2019-01-24 |

| 申请号            | JP2017128990                                                                                                             | 申请日     | 2017-06-30 |

| [标]申请(专利权)人(译) | 日本有机雷特显示器股份有限公司                                                                                                          |         |            |

| 申请(专利权)人(译)    | 株式会社JOLED                                                                                                                |         |            |

| [标]发明人         | 篠川泰治                                                                                                                     |         |            |

| 发明人            | 篠川 泰治                                                                                                                    |         |            |

| IPC分类号         | H05B33/26 H01L27/32 H01L51/50 H05B33/22 H05B33/10                                                                        |         |            |

| FI分类号          | H05B33/26.Z H01L27/32 H05B33/14.A H05B33/22.Z H05B33/10                                                                  |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/CC36 3K107/CC45 3K107/DD37 3K107/DD90 3K107/EE03 3K107/FF04 3K107/GG03 3K107/GG05 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                |         |            |

### 摘要(译)

提供了一种具有高像素孔径比的有机EL显示面板。有机EL显示面板包括基板，设置在基板上的薄膜半导体层，设置在薄膜半导体层上的下绝缘层，部分设置在下绝缘层上的下绝缘层，上绝缘层设置在下绝缘层和辅助电极上方，EL元件设置在上绝缘层上。在上绝缘层中，形成到达辅助电极的凹入部分的接触孔。EL元件包括设置在上绝缘层的未形成接触孔的部分上的像素电极，设置在像素电极上的发光层，设置在发光层上的公共电极层和接触孔并且，包括。在接触孔中，公共电极层沿着孔的内壁和辅助电极表面形成。.The 13