(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4103500号

(P4103500)

(45) 発行日 平成20年6月18日(2008.6.18)

(24) 登録日 平成20年4月4日(2008.4.4)

|                       |                     |

|-----------------------|---------------------|

| (51) Int.CI.          | F 1                 |

| G 09 G 3/30 (2006.01) | G 09 G 3/30 J       |

| G 09 G 3/20 (2006.01) | G 09 G 3/20 6 1 2 E |

|                       | G 09 G 3/20 6 1 2 K |

|                       | G 09 G 3/20 6 2 2 D |

|                       | G 09 G 3/20 6 2 4 B |

請求項の数 8 (全 22 頁) 最終頁に続く

|           |                              |           |                                                   |

|-----------|------------------------------|-----------|---------------------------------------------------|

| (21) 出願番号 | 特願2002-245444 (P2002-245444) | (73) 特許権者 | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号        |

| (22) 出願日  | 平成14年8月26日(2002.8.26)        | (74) 代理人  | 100090033<br>弁理士 荒船 博司                            |

| (65) 公開番号 | 特開2004-85802 (P2004-85802A)  | (74) 代理人  | 100093045<br>弁理士 荒船 良男                            |

| (43) 公開日  | 平成16年3月18日(2004.3.18)        | (72) 発明者  | 山田 裕康<br>東京都八王子市石川町2951番地5 カ<br>シオ計算機株式会社 八王子研究所内 |

| 審査請求日     | 平成15年7月15日(2003.7.15)        | (72) 発明者  | 白崎 友之<br>東京都八王子市石川町2951番地5 カ<br>シオ計算機株式会社 八王子研究所内 |

|           |                              | 審査官       | 濱本 袞広                                             |

|           |                              |           | 最終頁に続く                                            |

(54) 【発明の名称】表示装置及び表示パネルの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する複数の発光素子と、複数の供給線と、

各走査線を選択するオンレベルの選択信号を、各々の前記走査線の選択期間に、各々の前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する走査ドライバと、

前記走査ドライバによって各々の前記走査線にオンレベルの選択信号が供給されている時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流すデータドライバと、

各々の前記発光素子の周辺に設けられるとともに前記発光素子と前記供給線との間に接続されたトランジスタを備え、当該信号線に流れる指定電流のレベルに従った駆動電流を当該発光素子に流すための画素回路と、

指定電流を流すための指定電流用基準電位と駆動電流を流すための駆動電流用基準電位とを前記複数の供給線について同期をとって前記複数の供給線に出力する発振回路と、

を備え、

前記発振回路は、前記選択期間に前記指定電流用基準電位を前記複数の供給線に出力するとともに、前記各選択期間の間に、前記駆動電流用基準電位を前記複数の供給線に出力することを特徴とする表示装置。

## 【請求項 2】

各々の前記画素回路は、

前記走査ドライバによって前記オンレベルの選択信号が当該走査線に供給されている最中に前記発振回路から当該供給線を介して指定電流用基準電位が入力されている時に、当該信号線に流れる指定電流を当該画素回路に流すことでその指定電流のレベルを電圧レベルに変換し、

当該走査線に選択信号が供給されていない時に当該信号線に流れる指定電流を遮断するとともに変換された電圧レベルを保持し、

前記発振回路から当該供給線を介して駆動電流用基準電位が入力された時に、保持された電圧レベルに従ったレベルの駆動電流を当該発光素子に流すように構成されていることを特徴とする請求項 1 に記載の表示装置。 10

#### 【請求項 3】

前記発光素子が有機 E L 素子であり、当該有機 E L 素子のアノードが当該画素回路に接続されていることを特徴とする請求項 1 又は 2 に記載の表示装置。

#### 【請求項 4】

各々の前記画素回路は、

ゲートが当該走査線に接続され、ソースが当該信号線に接続された第一トランジスタと、

ゲートが当該走査線に接続され、ドレインで前記発振回路から当該供給線を介して指定電流用基準電位及び駆動電流用基準電位が選択的に入力される第二トランジスタと、を更に備え、 20

前記トランジスタのゲートが前記第二トランジスタのソースに接続され、前記トランジスタのドレインが前記第二トランジスタのドレインに接続され、前記トランジスタのソースが前記第一トランジスタのドレインに接続され且つ当該有機 E L 素子のアノードに接続され、

当該走査線から前記オンレベルの選択信号が前記第一トランジスタのゲートに供給されている最中に前記発振回路が指定電流用基準電位を出力している時に、前記第一トランジスタが前記発振回路から前記トランジスタを介して当該信号線へ指定電流を流すことによって、前記トランジスタが該指定電流のレベルをゲート - ソース間の電圧レベルに変換し、

当該走査線から前記オフレベルの選択信号が前記第二トランジスタのゲートに供給されている時に、前記第二トランジスタが前記トランジスタによって変換されたゲート - ソース間の電圧レベルを保持し、 30

前記トランジスタのドレインに駆動電流用基準電位が入力されている時に、前記トランジスタが、保持された電圧レベルに従ったレベルの駆動電流を前記発振回路から当該供給線を介して前記発光素子へ流すように構成されていることを特徴とする請求項 3 に記載の表示装置。

#### 【請求項 5】

前記発振回路によって出力される指定電流用基準電位が前記有機 E L 素子のカソードの電位以下に設定されており、前記発振回路によって出力される駆動電流用基準電位が前記有機 E L 素子のカソードの電位を越えるように設定されていることを特徴とする請求項 3 又は 4 に記載の表示装置。 40

#### 【請求項 6】

前記発光素子、前記走査ドライバ、前記データドライバ及び前記画素回路は表示パネル内に形成され、前記発振回路は、外部回路に形成されることを特徴とする請求項 1 から 5 の何れか一項に記載の表示装置。

#### 【請求項 7】

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する発光素子と、

前記複数の供給線と、

各走査線を選択するオンレベルの選択信号を、各々の前記走査線の選択期間に、各々の 50

前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する走査ドライバと、

前記走査ドライバによって各々の前記走査線に前記オンレベルの選択信号が供給されている前記選択期間時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流すデータドライバと、

各々の前記発光素子の周辺に設けられるとともに前記発光素子と前記供給線との間に接続されたトランジスタを備え、指定電流のレベルに従った駆動電流を当該発光素子に流すための画素回路と、

各々の前記走査線の前記選択期間に、指定電流を流すための指定電流用基準電位を前記複数の供給線について同期をとって前記複数の供給線に出力し、各々の前記走査線の非選択期間のうちの前記各選択期間の間のオフレベルの選択信号が前記複数の走査線に供給されているときに、駆動電流を流すための駆動電流用基準電位を前記複数の供給線について同期をとって前記複数の供給線に出力する電位出力回路と、

を備えることを特徴とする表示装置。

#### 【請求項 8】

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する発光素子と、

各々の前記発光素子の周辺に設けられた画素回路と、を備える表示パネルを駆動する表示パネルの駆動方法であって、

オンレベルの選択信号を、各々の前記走査線の選択期間に、各々の前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する動作と、

各々の前記走査線にオンレベルの選択信号が供給されている前記選択期間時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流す動作と、

各々の前記走査線に選択信号が供給されている最中に少なくとも一回指定電流用基準電位を全ての前記画素回路に出力する動作と、を含み、

各々の前記画素回路によって、

オンレベルの選択信号が当該走査線に供給されている最中に、指定電流用基準電位が入力されている時に、当該信号線に流れる指定電流が当該画素回路に流れることでその指定電流のレベルが電圧レベルに変換され、

当該走査線にオフレベルの選択信号が供給されている時に当該信号線に流れる指定電流が遮断されるとともに変換された電圧レベルが保持され、

各選択期間の間にオフレベルの選択信号が前記複数の走査線に供給されている間であつて且つ駆動電流用基準電位が入力されている時に、保持された電圧レベルに従ったレベルの駆動電流が当該発光素子に流れる、ことを特徴とする表示パネルの駆動方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、駆動電流のレベルが定まるとき一義的に輝度が定まる発光素子を画素ごとに備える表示パネルを駆動する表示パネルの駆動方法、及び、前記表示パネルとデータドライバと走査ドライバとを具備し、前記データドライバ及び前記走査ドライバで前記表示パネルを駆動する表示装置に関する。

##### 【0002】

##### 【従来の技術】

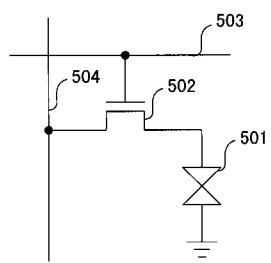

一般に、液晶ディスプレイにはアクティブマトリクス駆動方式のものと、単純マトリクス駆動方式のものがある。アクティブマトリクス駆動方式の液晶ディスプレイにおいては、単純マトリクス駆動方式の液晶ディスプレイに比較しても高輝度、高コントラスト及び高精細な画面表示が行われる。アクティブマトリクス駆動方式の液晶ディスプレイにおいては、図7に示されるように、コンデンサとしても機能する液晶素子501と、スイッチング素子として機能するトランジスタ502とが、画素ごとに設けられている。アクティブ

10

20

30

40

50

マトリクス駆動方式では、シフトレジスタである走査ドライバによって走査線 503 に信号が入力されて走査線 503 が選択されている時に、輝度を表すレベルの電圧がデータドライバによって信号線 504 に印加されると、トランジスタ 502 を介して液晶素子 501 に電圧が印加される。走査線 503 に入力された信号が終了してから次に信号が入力されるまでの間においてトランジスタ 502 がオフ状態になっても、液晶素子 501 がコンデンサとして機能するため、次の信号が走査線 503 に入力されるまでの間電圧レベルが保持される。以上のように、走査線 503 に信号が入力されている時において液晶素子 501 の光透過率が新たにリフレッシュされて、バックライトの光がリフレッシュされた光透過率で液晶素子 501 を透過することによって、液晶ディスプレイの階調表現が行われる。

10

#### 【0003】

一方、自発光素子である有機 EL (エレクトロルミネッセンス) 素子を用いた有機 EL ディスプレイは、液晶ディスプレイのようにバックライトを必要とせず、薄型化に最適であるとともに、液晶ディスプレイのような視野角の制限もないため、次世代の表示装置として実用化が大きく期待されている。

#### 【0004】

高輝度、高コントラスト、高精細といった観点から、有機 EL ディスプレイも、液晶ディスプレイと同様にアクティブマトリクス駆動方式のものが特に望まれている。しかし、有機 EL 素子においては液晶素子と比較しても容量が極めて低く、有機 EL 素子自体に電流が流れてしまうから、図 7 に示されたような画素の回路において液晶素子 501 の代わりに有機 EL 素子を設けただけでは、トランジスタ 502 がオフ状態になっても有機 EL 素子の発光を維持することは困難になる。

20

#### 【0005】

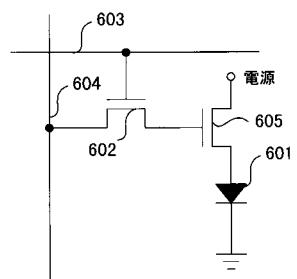

そこで、例えば図 8 に示されるように、従来のアクティブマトリクス駆動方式の有機 EL ディスプレイにおいては、有機 EL 素子 601 と、スイッチング素子として機能するトランジスタ 602 と、輝度を表す電圧レベルを保持しておくとともに電圧レベルに従ったレベルの駆動電流を有機 EL 素子 601 に流すトランジスタ 605 とが、画素ごとに設けられている。このディスプレイでは、シフトレジスタである走査ドライバによって走査線 603 に信号が入力されて走査線 603 が選択されている時に、輝度を表すレベルの電圧がデータドライバによって信号線 604 に印加されると、トランジスタ 605 のゲート電極にそのレベルの電圧が印加されることによってトランジスタ 605 のゲート電極に輝度データとして書き込まれることになる。これにより、トランジスタ 605 がオン状態になり、ゲート電極の電圧レベルに応じたレベルの駆動電流が電源からトランジスタ 605 を介して有機 EL 素子 601 に流れ、有機 EL 素子 601 が電流レベルに応じた輝度で発光する。走査線 603 の信号が終了してから次の信号が開始するまでの間では、トランジスタ 602 がオフ状態になることによってトランジスタ 605 のゲート電極の電圧レベルが保持され続け、有機 EL 素子 601 が電圧レベルに従った輝度で発光する。以上のように、信号が走査線 603 に入力されている間においてトランジスタ 605 のゲート電圧がリフレッシュされることによって有機 EL 素子 601 の発光輝度がリフレッシュされて、有機 EL ディスプレイの階調表現が行われる。

30

#### 【0006】

ところで、一般的にトランジスタは、周囲の温度変化によってチャネル抵抗が変化したり、長時間の使用によりチャネル抵抗が変化したりするために、ゲート閾値電圧が経時変化したり、ゲート閾値電圧がトランジスタごとに異なる。従って、トランジスタ 605 のゲート電極に印加する電圧のレベルを変化させることによって有機 EL 素子 601 に流れる電流のレベルを変化させること、換言すれば、トランジスタ 605 のゲート電極に印加する電圧のレベルを変化させることによって有機 EL 素子 601 の輝度を変化させることを行っても、トランジスタ 605 のゲート電圧レベルで有機 EL 素子 601 に流れる電流レベルを一義的に指定するのは困難である。つまり、複数の画素の間で同じレベルのゲート電圧をトランジスタ 605 に印加したものとしても、複数の画素の間で有機 EL 素子 60

40

50

1の発光輝度が異なってしまい、表示面内でバラツキが生じてしまう。

【0007】

そこで、有機EL素子の輝度をトランジスタのゲート電極に印加される電圧のレベルで制御するのではなく、トランジスタに流れる電流のレベルで制御する手法が研究されている。つまり、信号線にゲート電圧のレベルを指定する電圧指定方式ではなく、有機EL素子に流れる電流のレベルを直接信号線に指定する電流指定方式を有機ELディスプレイのアクティブマトリクス駆動方式に適用するというものである。

【0008】

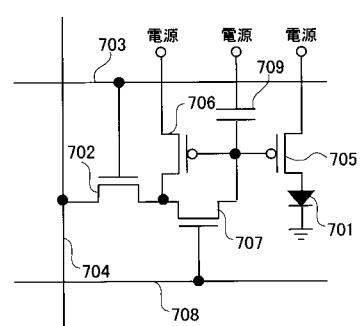

電流指定方式をアクティブマトリクス駆動方式の有機ELディスプレイに適用した場合、例えば、図9に示される有機ELディスプレイが提案されている。図9に示された有機ELディスプレイでは、有機EL素子701と、ゲート電極が第一走査線703に接続されたトランジスタ702と、ゲート電極が第二走査線708に接続されたトランジスタ707と、指定電流レベルをゲートの電圧レベルに変換する機能のNチャネルのトランジスタ706と、トランジスタ706のゲート電圧レベルを保持する機能のコンデンサ709と、変換された電圧レベルに従ったレベルの駆動電流を有機EL素子701に流す機能のPチャネルのトランジスタ705とが、画素ごとに設けられている。また、この有機ELディスプレイは、それぞれの行の走査線703を順次選択する第一走査ドライバと、それぞれの行の走査線708を順次選択する第二走査ドライバとを具備し、シフトレジスタである第二走査ドライバによってリセット信号が第二走査線708に入力され、リセット信号より遅延した選択信号がシフトレジスタである第一走査ドライバによって第一走査線703に入力される。

10

【0009】

このディスプレイでは、第二走査ドライバによってリセット信号が第二走査線708に入力されて、トランジスタ707がオン状態になり、トランジスタ706及びトランジスタ705のゲート電圧が一旦リセットされる。そして、リセット信号の終了前に第一走査ドライバによって選択信号が第一走査線703に入力されている時に、輝度を表すレベルの指定電流がデータドライバによって信号線704に流れると、トランジスタ706にも指定電流が流れる。ここで、トランジスタ706によって指定電流のレベルがゲート電圧のレベルに変換されて、変換されたゲート電圧レベルがトランジスタ705によって駆動電流のレベルに変換される。これにより、有機EL素子701に駆動電流が流れ、有機EL素子701が駆動電流のレベルに従った輝度で発光する。そして、第二走査線708に入力されているリセット信号が終了すると、トランジスタ707がオフ状態になることによって、トランジスタ705及びトランジスタ707のゲート電極が保持され、次のリセット信号が第二走査線708に入力されるまでの間、有機EL素子701が発光し続ける。

20

【0010】

【発明が解決しようとする課題】

しかしながら、図8の有機ELディスプレイでは一つの走査ドライバで駆動することができたのに対して、図9の有機ELディスプレイでは二つの走査ドライバを必要としている。そのため、図9の有機ELディスプレイにおいては、製造コストが高く、走査ドライバの実装面積も増えてしまう。また、図9の有機ELディスプレイでは、画素ごとに四つのトランジスタが設けられているため、製造コストが高くなり、歩留りの低下にも繋がる。それに対して、図8の有機ELディスプレイは、走査ドライバの実装面積、歩留り、製造コストについては図9の有機ELディスプレイより優れているが、表示画面内の複数の画素間に輝度バラツキがあるため表示品質の点で図9の有機ELディスプレイより劣っている。

30

【0011】

そこで、本発明が解決しようとする課題は、高品質な表示を行うことができるとともに、製造コストが低く、歩留りの高い表示装置及び表示パネルの駆動方法を提供することである。

【0012】

40

50

## 【課題を解決するための手段】

以上の課題を解決するために、請求項 1 に係る表示装置は、

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する複数の発光素子と、

複数の供給線と、

各走査線を選択するオンレベルの選択信号を、各々の前記走査線の選択期間に、各々の前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する走査ドライバと、

前記走査ドライバによって各々の前記走査線にオンレベルの選択信号が供給されている時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流すデータドライバと、

各々の前記発光素子の周辺に設けられるとともに前記発光素子と前記供給線との間に接続されたトランジスタを備え、当該信号線に流れる指定電流のレベルに従った駆動電流を当該発光素子に流すための画素回路と、

指定電流を流すための指定電流用基準電位と駆動電流を流すための駆動電流用基準電位とを前記複数の供給線について同期をとって前記複数の供給線に出力する発振回路と、

を備え、

前記発振回路は、前記選択期間に前記指定電流用基準電位を前記複数の供給線に出力するとともに、前記各選択期間の間に、前記駆動電流用基準電位を前記複数の供給線に出力することを特徴とする。

## 【0013】

また、請求項 2 に記載の発明は、請求項 1 に記載の表示装置において、

前記走査ドライバによってオンレベルの選択信号が当該走査線に供給されている最中に前記発振回路から当該供給線を介して指定電流用基準電位が入力されている時に、当該信号線に流れる指定電流を当該画素回路に流すことでその指定電流のレベルを電圧レベルに変換し、

当該走査線に選択信号が供給されていない時に当該信号線に流れる指定電流を遮断するとともに変換された電圧レベルを保持し、

前記発振回路から当該供給線を介して駆動電流用基準電位が入力された時に、保持された電圧レベルに従ったレベルの駆動電流を当該発光素子に流すように構成されていることを特徴とする。

## 【0014】

また、請求項 3 に記載の発明は、請求項 1 又は 2 に記載の表示装置において、前記発光素子が有機 E L 素子であり、当該有機 E L 素子のアノードが当該画素回路に接続されていることを特徴とする。

## 【0015】

また、請求項 4 に記載の発明は、請求項 3 に記載の表示装置において、

各々の前記画素回路は、

ゲートが当該走査線に接続され、ソースが当該信号線に接続された第一トランジスタと、

ゲートが当該走査線に接続され、ドレインで前記発振回路から当該供給線を介して指定電流用基準電位及び駆動電流用基準電位が選択的に入力される第二トランジスタと、を更に備え、

前記トランジスタのゲートが前記第二トランジスタのソースに接続され、前記トランジスタのドレインが前記第二トランジスタのドレインに接続され、前記トランジスタのソースが前記第一トランジスタのドレインに接続され且つ当該有機 E L 素子のアノードに接続され、

当該走査線から前記オンレベルの選択信号が前記第一トランジスタのゲートに供給されている最中に前記発振回路が指定電流用基準電位を出力している時に、前記第一トランジスタが前記発振回路から前記トランジスタを介して当該信号線へ指定電流を流すことによって、前記トランジスタが該指定電流のレベルをゲート - ソース間の電圧レベルに変換し

10

20

30

40

50

、当該走査線から前記オフレベルの選択信号が前記第二トランジスタのゲートに供給されている時に、前記第二トランジスタが前記トランジスタによって変換されたゲート・ソース間の電圧レベルを保持し、

前記トランジスタのドレインに駆動電流用基準電位が入力されている時に、前記トランジスタが、保持された電圧レベルに従ったレベルの駆動電流を前記発振回路から当該供給線を介して前記発光素子へ流すように構成されていることを特徴とする。

【0016】

また、請求項5に記載の発明は、請求項2又は3に記載の表示装置において、前記発振回路によって出力される指定電流用基準電位が前記有機EL素子のカソードの電位以下に設定されており、前記発振回路によって出力される駆動電流用基準電位が前記有機EL素子のカソードの電位を越えるように設定されていることを特徴とする。

10

【0017】

請求項6に記載の発明は、請求項1から5の何れか一項に記載の表示装置において、前記発光素子、前記走査ドライバ、前記データドライバ及び前記画素回路は表示パネル内に形成され、前記発振回路は、外部回路に形成されることを特徴とする。

【0018】

請求項7に係る表示装置は、

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する発光素子と、

20

前記複数の供給線と、

各走査線を選択するオンレベルの選択信号を、各々の前記走査線の選択期間に、各々の前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する走査ドライバと、

前記走査ドライバによって各々の前記走査線に前記オンレベルの選択信号が供給されている前記選択期間時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流すデータドライバと、

各々の前記発光素子の周辺に設けられるとともに前記発光素子と前記供給線との間に接続されたトランジスタを備え、指定電流のレベルに従った駆動電流を当該発光素子に流すための画素回路と、

30

各々の前記走査線の前記選択期間に、指定電流を流すための指定電流用基準電位を前記複数の供給線について同期をとって前記複数の供給線に出力し、各々の前記走査線の非選択期間のうちの前記各選択期間の間のオフレベルの選択信号が前記複数の走査線に供給されているときに、駆動電流を流すための駆動電流用基準電位を前記複数の供給線について同期をとって前記複数の供給線に出力する電位出力回路と、

を備えることを特徴とする。

【0019】

また、請求項8に係る表示パネルの駆動方法は、

複数の走査線と前記走査線に対して垂直な複数の信号線との各交差部に配置されているとともに、流れる駆動電流のレベルに従った輝度で発光する発光素子と、

40

各々の前記発光素子の周辺に設けられた画素回路と、を備える表示パネルを駆動する表示パネルの駆動方法であって、

オンレベルの選択信号を、各々の前記走査線の選択期間に、各々の前記走査線に順次供給するとともに、各選択期間の間にオフレベルの選択信号を前記複数の走査線に供給する動作と、

各々の前記走査線にオンレベルの選択信号が供給されている前記選択期間時に、輝度情報に従ったレベルの指定電流を各々の前記信号線に流す動作と、

各々の前記走査線に選択信号が供給されている最中に少なくとも一回指定電流用基準電位を全ての前記画素回路に出力する動作と、を含み、

各々の前記画素回路によって、

50

オンレベルの選択信号が当該走査線に供給されている最中に、指定電流用基準電位が入力されている時に、当該信号線に流れる指定電流が当該画素回路に流れることでその指定電流のレベルが電圧レベルに変換され、

当該走査線にオフレベルの選択信号が供給されている時に当該信号線に流れる指定電流が遮断されるとともに変換された電圧レベルが保持され、

各選択期間の間にオフレベルの選択信号が前記複数の走査線に供給されている間であつて且つ駆動電流用基準電位が入力されている時に、保持された電圧レベルに従ったレベルの駆動電流が当該発光素子に流れる、ことを特徴とする。

【0024】

【発明の実施の形態】

以下に、図面を用いて本発明の具体的な態様について説明する。ただし、発明の範囲を図示例に限定するものではない。

【0025】

〔第一の実施の形態〕

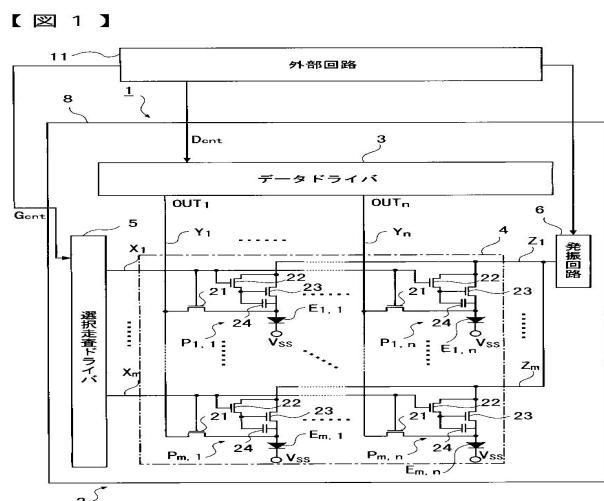

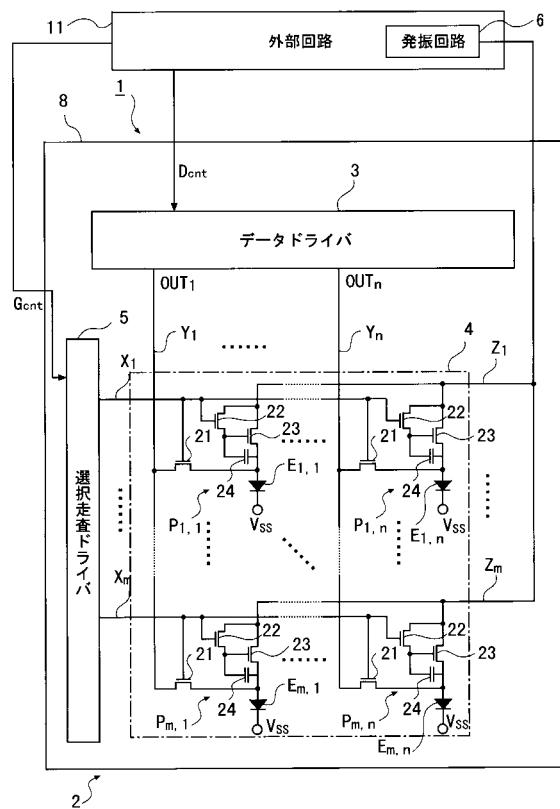

図1は、本発明の適用された有機ELディスプレイを示した図面である。図1に示されるように、有機ELディスプレイ1は、基本構成として、有機EL表示パネル2と、外部回路11からクロック信号CK1や輝度階調信号Scを含む制御信号群D\_CNTが入力されるデータドライバ3と、外部回路11からクロック信号CK2を含む制御信号群G\_CNTが入力される選択走査ドライバ5と、発振回路6と、を備える。

【0026】

有機EL表示パネル2は、画像が実質的に表示される表示部4が透明基板8に設けられた構造となっている。表示部4の周囲に選択走査ドライバ5、データドライバ6及び発振回路6が配設されている。選択走査ドライバ5及びデータドライバ6は、透明基板8上に設けられていても良いし、透明基板8の周辺に配された基板(図示略)上に設けられても良い。

【0027】

表示部4においては、(m×n)個の画素P<sub>1,1</sub>～P<sub>m,n</sub>がマトリクス状となって透明基板8上に設けられており、縦方向(列方向)にm個の画素P<sub>i,j</sub>が配列され、横方向(行方向)にn個の画素P<sub>i,j</sub>が配列されている。ここで、m, nは1以上の整数であり、iは1以上m以下の或る整数であり、jは1以上n以下の或る整数であり、縦にi番目(つまり、i行目)であって横にj番目(つまり、j列目)である画素を画素P<sub>i,j</sub>と記す。

【0028】

また、表示部4においては、m本の選択走査線X<sub>1</sub>～X<sub>m</sub>と、m本の周期信号供給線Z<sub>1</sub>～Z<sub>m</sub>と、n本の信号線Y<sub>1</sub>～Y<sub>n</sub>とが透明基板8上に形成されている。選択走査線X<sub>1</sub>～X<sub>m</sub>は、互いに平行となって横方向に延在している。周期信号供給線Z<sub>1</sub>～Z<sub>m</sub>が選択走査線X<sub>1</sub>～X<sub>m</sub>に対して交互に配列されている。信号線Y<sub>1</sub>～Y<sub>n</sub>は、互いに平行となって縦方向に延在し、選択走査線X<sub>1</sub>～X<sub>m</sub>に対して垂直に交差している。これら選択走査線X<sub>1</sub>～X<sub>m</sub>、周期信号供給線Z<sub>1</sub>～Z<sub>m</sub>及び信号線Y<sub>1</sub>～Y<sub>n</sub>は層間絶縁膜等によって互いに絶縁されている。また、選択走査線X<sub>1</sub>～X<sub>m</sub>は選択走査ドライバ5のそれぞれの出力端子に接続されており、周期信号供給線Z<sub>1</sub>～Z<sub>m</sub>は互いに導電して発振回路6の出力端子に接続されている。

【0029】

また、選択走査線X<sub>i</sub>及び周期信号供給線Z<sub>i</sub>には、横方向に配列されたn個の画素P<sub>i,1</sub>～P<sub>i,n</sub>が接続されており、信号線Y<sub>j</sub>には、縦方向に配列されたm個の画素P<sub>1,j</sub>～P<sub>m,j</sub>が接続されており、選択走査線X<sub>i</sub>と信号線Y<sub>j</sub>との交差部に画素P<sub>i,j</sub>が配されている。

【0030】

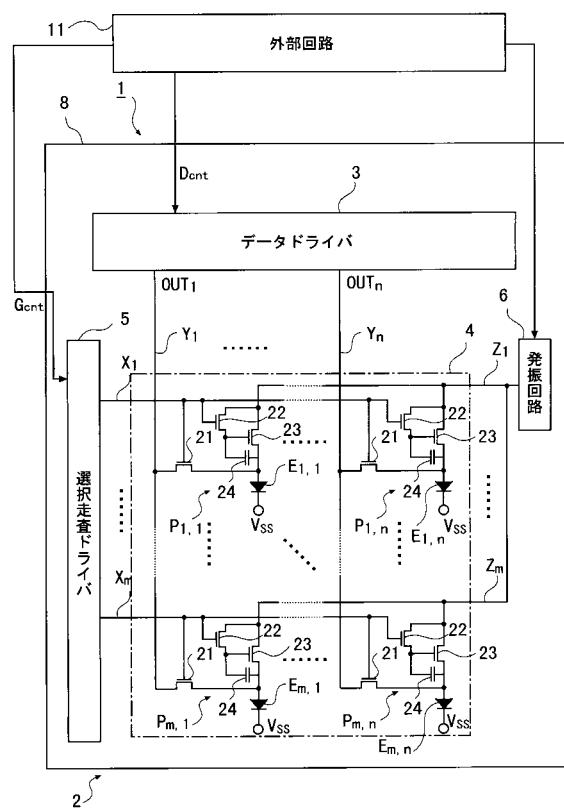

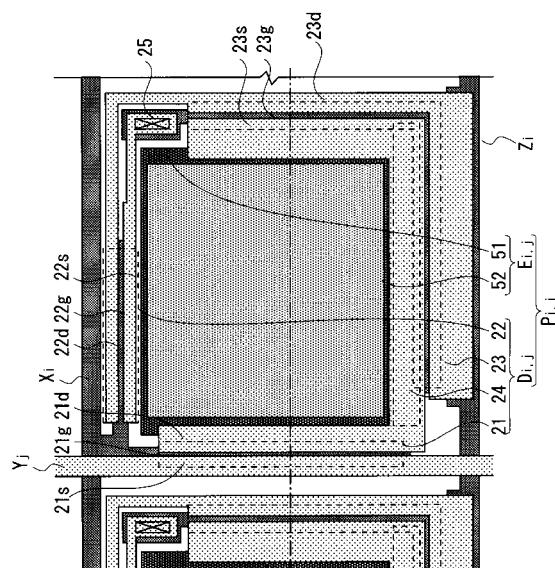

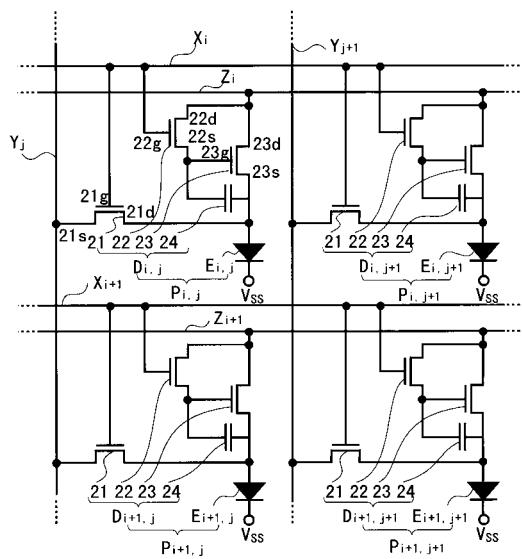

次に、図2及び図3を用いて画素P<sub>i,j</sub>について説明する。図2は画素P<sub>i,j</sub>を示した平面図であり、図3は四つの画素P<sub>i,j</sub>, P<sub>i+1,j</sub>, P<sub>i,j+1</sub>, P<sub>i+1,j+1</sub>の等価回路図である。

【0031】

画素P<sub>i,j</sub>は、駆動電流のレベルに従った輝度で発光する有機EL素子E<sub>i,j</sub>と、有機EL

10

20

30

40

50

素子  $E_{i,j}$  の周辺に設けられている画素回路  $D_{i,j}$  と、から構成されている。

【0032】

有機EL素子  $E_{i,j}$  は、透明基板 8 上にアノード 51、有機EL層 52、カソード（図示略）が順に積層した積層構造となっている。

【0033】

アノード 51 は画素  $P_{1,1} \sim P_{m,n}$  ごとにパターニングされており、信号線  $Y_1 \sim Y_n$  と選択走査線  $X_1 \sim X_m$  とによって囲繞された各囲繞領域に形成されている。

【0034】

アノード 51 は、導電性を有しているとともに、可視光に対して透過性を有している。また、アノード 51 は、比較的仕事関数の高いものであり、有機EL層 52 へ正孔を効率よく注入するものが好ましい。アノード 51 としては、例えば、錫ドープ酸化インジウム（ITO）、亜鉛ドープ酸化インジウム（IZO）、酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）又は酸化亜鉛（ZnO）を主成分としたものがある。

【0035】

各々のアノード 51 上には、有機化合物を含む有機EL層 52 が成膜されており、有機EL層 52 も画素  $P_{1,1} \sim P_{m,n}$  ごとにパターニングされている。有機EL層 52 は、例えば、アノード 51 から順に正孔輸送層、狭義の発光層、電子輸送層となる三層構造であっても良いし、アノード 51 から順に正孔輸送層、狭義の発光層となる二層構造であっても良いし、狭義の発光層からなる一層構造であっても良いし、これらの層構造において適切な層間に電子或いは正孔の注入層が介在した積層構造であっても良いし、その他の積層構造であっても良い。

【0036】

有機EL層 52 は、正孔及び電子を注入する機能、正孔及び電子を輸送する機能、正孔と電子の再結合により励起子を生成して赤色、緑色又は青色の何れかに発光する機能を有する広義の発光層である。つまり、画素  $P_{i,j}$  が赤である場合にはその画素  $P_{i,j}$  の有機EL層 52 は赤色に発光し、画素  $P_{i,j}$  が緑である場合にはその画素  $P_{i,j}$  の有機EL層 52 は緑色に発光し、画素  $P_{i,j}$  が青である場合にはその画素  $P_{i,j}$  の有機EL層 52 は青色に発光する。

【0037】

また、有機EL層 52 は、電子的に中立な有機化合物であることが望ましく、これにより正孔及び電子が有機EL層 52 でバランス良く注入され、輸送される。また、電子輸送性の物質が狭義の発光層に適宜混合されていても良いし、正孔輸送性の物質が狭義の発光層に適宜混合されても良いし、電子輸送性の物質及び正孔輸送性の物質の両方が狭義の発光層に適宜混合されていても良い。

【0038】

有機EL層 52 上にはカソードが形成されている。カソードは、全ての画素  $P_{1,1} \sim P_{m,n}$  に共通の層となる共通電極であっても良いし、画素  $P_{1,1} \sim P_{m,n}$  ごとにパターニングされていても良い。いずれにしてもカソードは、選択走査線  $X_1 \sim X_m$ 、信号線  $Y_1 \sim Y_n$  及び周期信号供給線  $Z_1 \sim Z_m$  に対して電気的に絶縁されている。カソードは、仕事関数の低い材料で形成されており、例えば、インジウム、マグネシウム、カルシウム、リチウム若しくはバリウム又はこれらの少なくとも一種を含む合金若しくは混合物等で形成されている。また、カソードは、以上の各種材料の層が積層された積層構造となっていても良いし、以上の各種材料の層に加えて金属層が堆積した積層構造となっていても良く、具体的には、以上の各種材料の層上にアルミニウム、クロム等といった高仕事関数で且つ低抵抗の金属層が被覆された積層構造となっていても良い。また、カソードは、可視光に対して遮光性を有するとともに可視光に対して高い反射性を有することで、鏡面として作用するのが望ましい。なお、アノード 51 及びカソードのうちの少なくとも一方が透明であっても良いが、片方の電極が透明であり且つ他方の電極が高反射性であることがより良い。

【0039】

以上のように積層構造となる有機EL素子  $E_{i,j}$  では、アノード 51 とカソードとの間に

順バイアス電圧（アノード 5 1 がカソードより高電位）が印加されると、正孔がアノード 5 1 から有機 E L 層 5 2 へ注入され、電子がカソードから有機 E L 層 5 2 に注入される。そして、有機 E L 層 5 2 で正孔及び電子が輸送されて、有機 E L 層 5 2 にて正孔及び電子が再結合することによって励起子が生成され、励起子が有機 E L 層 5 2 内の蛍光体を励起して、有機 E L 層 5 2 内にて光が発する。

#### 【 0 0 4 0 】

有機 E L 素子 E <sub>i, j</sub> の発光輝度は、有機 E L 素子 E <sub>i, j</sub> に流れる駆動電流のレベルに依存し、電流レベルが増大するにつれて発光輝度も増大する。つまり、有機 E L 素子 E <sub>i, j</sub> に流れる駆動電流のレベルが定まると、有機 E L 素子 E <sub>i, j</sub> の輝度が一義的に定まる。

#### 【 0 0 4 1 】

画素回路 D <sub>i, j</sub> は、データドライバ 3、選択走査ドライバ 5 及び発信回路 6 から出力された信号に基づいて有機 E L 素子 E <sub>i, j</sub> を駆動するものである。各画素回路 D <sub>i, j</sub> は、三つの薄膜トランジスタ（以下単にトランジスタと記述する。）2 1, 2 2, 2 3 と、コンデンサ 2 4 とを備える。

#### 【 0 0 4 2 】

トランジスタ 2 1, 2 2, 2 3 は、ゲート電極、ドレイン電極、ソース電極、半導体層、不純物半導体層、ゲート絶縁膜等から構成された M O S 型の電界効果トランジスタであり、特にアモルファスシリコンを半導体層（チャネル領域）とした a - S i トランジスタであるが、ポリシリコンを半導体層とした p - S i トランジスタであってもよい。また、トランジスタ 2 1, 2 2, 2 3 の構造は逆スタガ型であっても良いし、コプラナ型であっても良い。なお、ゲート電極、ドレイン電極、ソース電極、半導体層、不純物半導体層、ゲート絶縁膜等の組成はトランジスタ 2 1, 2 2, 2 3 についてそれぞれ同じであり、トランジスタ 2 1, 2 2, 2 3 は同一工程で同時に形成されるが、形状、大きさ、寸法、チャネル幅、チャネル長等はトランジスタ 2 1, 2 2, 2 3 についてそれぞれ異なる。以下では、トランジスタ 2 1, 2 2, 2 3 の何れもが、N チャネル型の a - S i 電界効果トランジスタであるとして説明する。また、以下では、トランジスタ 2 1 を第一トランジスタ 2 1 と、トランジスタ 2 2 を第二トランジスタ 2 2 と、トランジスタ 2 3 を第三トランジスタ 2 3 と記述する。

#### 【 0 0 4 3 】

第二トランジスタ 2 2 のゲート電極 2 2 g は選択走査線 X <sub>i</sub> に接続されている。第二トランジスタ 2 2 のドレイン電極 2 2 d は、第三トランジスタ 2 3 のドレイン電極 2 3 d に接続されているとともに、周期信号供給線 Z <sub>i</sub> に接続されている。第二トランジスタ 2 2 のソース電極 2 2 s は、コンタクトホール 2 5 を介して第三トランジスタ 2 3 のゲート電極 2 3 g に接続されているとともに、コンデンサ 2 4 の一方の電極に接続されている。

#### 【 0 0 4 4 】

第三トランジスタ 2 3 のソース電極 2 3 s は、コンデンサ 2 4 の他方の電極に接続されているとともに第一トランジスタ 2 1 のドレイン電極 2 1 d に接続されている。

#### 【 0 0 4 5 】

第一トランジスタ 2 1 のゲート電極 2 1 g は選択走査線 X <sub>i</sub> に接続されており、第一トランジスタ 2 1 のソース電極 2 1 s は信号線 Y <sub>j</sub> に接続されている。第三トランジスタ 2 3 のソース電極 2 3 s、コンデンサ 2 4 の他方の電極及び第一トランジスタ 2 1 のドレイン電極 2 1 d は、有機 E L 素子 E <sub>i, j</sub> のアノード 5 1 に接続されている。有機 E L 素子 E <sub>i, j</sub> のカソードの電位は、一定の基準電位 V <sub>ss</sub> に保たれており、本実施形態では、有機 E L 素子 E <sub>i, j</sub> のカソードが接地されることで基準電位 V <sub>ss</sub> が 0 [V] となっている。

#### 【 0 0 4 6 】

次に、表示部 4 の周囲に配設されたデータドライバ 3、選択走査ドライバ 5 及び発振回路 6 について説明する。

選択走査ドライバ 5 はいわゆるシフトレジスタであり、m 個のフリップフロップ回路等が直列に接続された構成であり、選択信号をそれぞれの選択走査線 X <sub>1</sub> ~ 選択走査線 X <sub>m</sub> に出力するものである。つまり、選択走査ドライバ 5 は、外部回路 1 1 から入力したクロック

10

20

30

40

50

信号  $C_K 2$  に基づいて選択走査線  $X_1$  から選択走査線  $X_m$  への順 (選択走査線  $X_m$  の次は選択走査線  $X_1$  ) にハイレベル (オンレベル) の選択信号を順次出力する (供給する) ことで、選択走査線  $X_1 \sim X_m$  を順次選択するものである。

#### 【 0 0 4 7 】

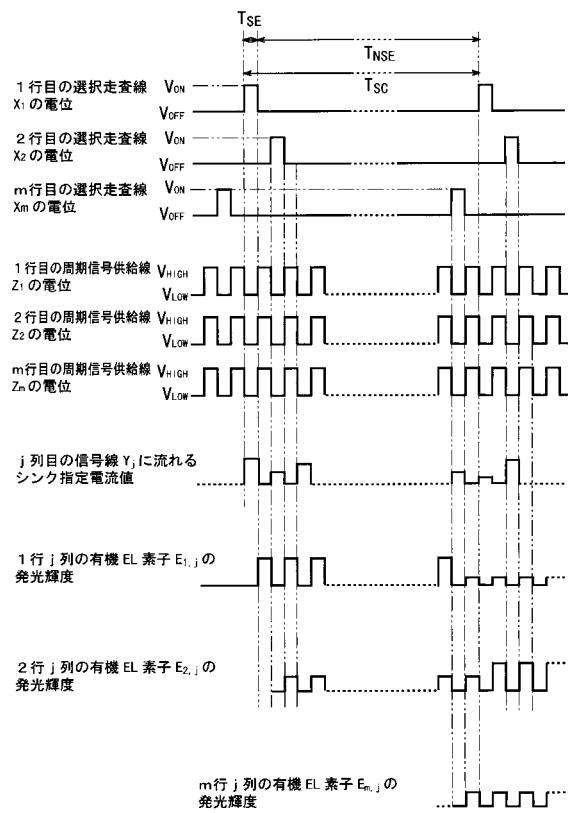

詳細には図 5 に示されるように、選択走査ドライバ 5 は、ハイレベルの選択信号としてオン電位  $V_{ON}$  (例えば基準電位  $V_{SS}$  より十分高い。) 又はローレベルの選択信号としてオフ電位  $V_{OFF}$  (例えば基準電位  $V_{SS}$  以下である。) の何れかのレベルの電位を選択走査線  $X_1 \sim X_m$  に個別に印加することによって、所定周期で各選択走査線  $X_i$  を選択する。

#### 【 0 0 4 8 】

即ち、選択走査線  $X_i$  が選択される選択期間  $T_{SE}$  では、選択走査ドライバ 5 がハイレベルの選択信号としてオン電位  $V_{ON}$  を選択走査線  $X_i$  に印加することにより、選択走査線  $X_i$  に接続されたトランジスタ 21, 22 (画素回路  $D_{i,1} \sim D_{i,n}$  全てのトランジスタ 21, 22 である。) がオン状態になる。トランジスタ 21 がオン状態になることによって信号線  $Y_j$  に流れる電流が画素回路  $D_{i,j}$  に流れ得るようになる。一方、選択期間  $T_{SE}$  以外の非選択期間  $T_{NSE}$  では、選択走査ドライバ 5 がローレベルの選択信号としてオフ電位  $V_{OFF}$  を走査線  $X_i$  に印加することにより、トランジスタ 21, 22 がオフ状態になる。トランジスタ 21 がオフ状態になることで、信号線  $Y_j$  に流れる電流は画素回路  $D_{i,j}$  に流れ得ないようになる。ここで、 $T_{SE} + T_{NSE} = T_{SC}$  で表される期間が一走査期間であり、選択走査線  $X_1 \sim X_m$  の選択期間  $T_{SE}$  は互いに重ならない。なお、図 5 において「 $T_{SE}$ 」、「 $T_{NSE}$ 」及び「 $T_{SC}$ 」が記されているが、これらは 1 行目の選択走査線  $X_1$  についてのものである。

#### 【 0 0 4 9 】

また、選択走査ドライバ 5 が選択信号としてオン電位  $V_{ON}$  を選択走査線  $X_i$  に印加してから次の選択走査線  $X_{i+1}$  にオン電位  $V_{ON}$  を印加するまでには時間的間隔がある。

#### 【 0 0 5 0 】

図 1、図 3 に示されるように、発振回路 6 は、水晶発振器等から構成され、ハイレベルとローレベルとの間で振動する周期的信号を全ての周期信号供給線  $Z_1 \sim Z_m$  に出力するものである。

#### 【 0 0 5 1 】

詳細には図 5 に示されるように、発振回路 6 から出力される周期的信号の周期 (周期的信号がハイレベルになってから次にハイレベルになるまでの周期) は、選択期間  $T_{SE}$  の二倍である。そして、発振回路 6 から出力される周期的信号がローレベルになっている期間とハイレベルになっている期間は同じである。また、発振回路 6 から出力された周期的信号がハイレベルからローレベルに下がる時に、選択走査ドライバ 5 によって選択走査線  $X_1 \sim X_m$  の何れかに出力されている選択信号が立ち上がり、発振回路 6 から出力された周期的信号がローレベルからハイレベルに立ち上がる時に、選択ドライバ 5 によって選択走査線  $X_1 \sim X_m$  の何れかに出力されている選択信号が下がる。

#### 【 0 0 5 2 】

また、発振回路 6 から出力される周期的信号がローレベルになっている時が、選択走査線  $X_1 \sim X_m$  のうちの何れか一つの選択期間  $T_{SE}$  である。つまり、周期的信号がハイレベルになっている時には、選択走査ドライバ 5 はオフ電位  $V_{OFF}$  を全ての選択走査線  $X_1 \sim X_m$  に印加して、全ての選択走査線  $X_1 \sim X_m$  にオフレベルの選択信号を出力する。一方、周期的信号がローレベルになっている時には、選択走査ドライバ 5 が選択走査線  $X_1 \sim X_m$  のうちの何れか一つの選択走査線  $X_i$  にオン電位  $V_{ON}$  を印加して、その一つの選択走査線  $X_i$  にオンレベルの選択信号を出力するとともに、選択走査線  $X_i$  を除く選択走査線  $X_1 \sim X_m$  にオフレベルの選択信号を出力する。

#### 【 0 0 5 3 】

発振回路 6 から出力される周期的信号がローレベルである時その電位 (指定電流用基準電位)  $V_{LOW}$  は、基準電位  $V_{SS}$  以下であるが、ここでは、基準電位  $V_{SS}$  と同じである。そのため、第三トランジスタ 23 がオン状態となっていても、周期的信号がローレベルである

10

20

30

40

50

時には有機EL素子E<sub>i,j</sub>にゼロ電圧又は逆バイアス電圧が印加されていることになるから有機EL素子E<sub>i,j</sub>に電流が流れない。一方、発振回路6から出力されるハイレベルの電位(駆動電流用基準電位)V<sub>HIGH</sub>が基準電位V<sub>SS</sub>より高く、第三トランジスタ23がオン状態となっていれば、有機EL素子E<sub>i,j</sub>に順バイアス電圧が印加されていることになるから周期信号供給線Z<sub>i</sub>から有機EL素子E<sub>i,j</sub>へと電流が流れる。

#### 【0054】

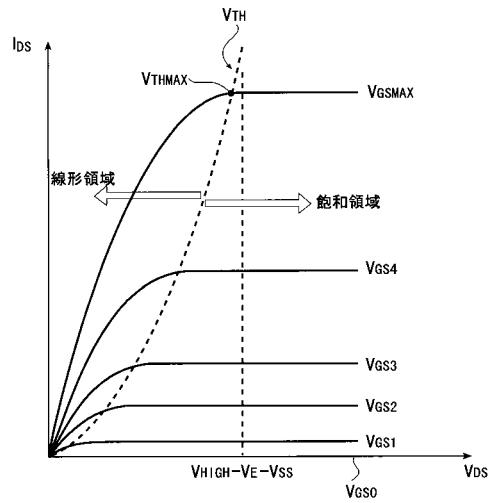

電位V<sub>HIGH</sub>について説明する。図4は、Nチャネル型の電界効果トランジスタ23の電流-電圧特性を表したグラフである。図4において、横軸はドレイン-ソース間の電圧レベルを表し、縦軸はドレイン-ソース間の電流レベルを表す。図中の線形領域(ソース-ドレイン間電圧レベルV<sub>DS</sub> < ドレイン飽和電圧レベルV<sub>TH</sub>)となっている領域:ドレイン飽和電圧レベルV<sub>TH</sub>は、ゲート-ソース間電圧レベルV<sub>GS</sub>の関数であり、ゲート-ソース間電圧レベルV<sub>GS</sub>が定まれば一義的に定まる。)では、ゲート-ソース間電圧レベルV<sub>GS</sub>が一定であると、ソース-ドレイン間電圧レベルV<sub>DS</sub>が大きくなるにつれてソース-ドレイン間電圧レベルI<sub>DS</sub>が大きくなる。更に、図中の飽和領域(ソース-ドレイン間電圧レベルV<sub>DS</sub> > ドレイン飽和電圧レベルV<sub>TH</sub>)では、ゲート-ソース間電圧レベルV<sub>GS</sub>が一定であると、ソース-ドレイン間電圧レベルV<sub>DS</sub>が大きくなつてもソース-ドレイン間電流レベルI<sub>DS</sub>はほぼ一定となる。

10

#### 【0055】

また、図4において、ゲート-ソース間電圧レベルV<sub>GS0</sub>~V<sub>GSMAX</sub>は、V<sub>GS0</sub> = 0 [V] < V<sub>GS1</sub> < V<sub>GS2</sub> < V<sub>GS3</sub> < V<sub>GS4</sub> < V<sub>GSMAX</sub>の関係となっている。つまり、図4から明らかのように、ドレイン-ソース間電圧レベルV<sub>DS</sub>が一定の場合、ゲート-ソース間電圧レベルV<sub>GS</sub>が大きくなるにつれて、線形領域、飽和領域のいずれであってもドレイン-ソース間電流レベルI<sub>DS</sub>が大きくなる。更に、ゲート-ソース間電圧レベルV<sub>GS</sub>が大きくなるにつれて、ドレイン飽和電圧レベルV<sub>TH</sub>が大きくなる。

20

#### 【0056】

以上のことから、線形領域では、ソース-ドレイン間電圧レベルV<sub>DS</sub>がわずかに変わるとソース-ドレイン間電流レベルI<sub>DS</sub>が変わってしまうが、飽和領域では、ゲート-ソース間電圧レベルV<sub>GS</sub>が定まれば、ソース-ドレイン間電圧レベルV<sub>DS</sub>に関わらずドレイン-ソース間電流レベルI<sub>DS</sub>が一義的に定まる。

#### 【0057】

30

ここで、第三トランジスタ23に最大のゲート-ソース間電圧レベルV<sub>GSMAX</sub>が印加されている時のドレイン-ソース間電流レベルI<sub>DS</sub>は、最大輝度で発光する有機EL素子E<sub>i,j</sub>のアノード51とカソードとの間に流れる電流レベルに設定されている。

また、第三トランジスタ23のゲート-ソース間電圧レベルV<sub>GS</sub>が最大レベルV<sub>GSMAX</sub>であっても、第三トランジスタ23が飽和領域を維持するように、下記に示す条件式を満たしている。

$$V_{HIGH} - V_E - V_{SS} = V_{THMAX}$$

ここで、V<sub>E</sub>は、最高輝度で発光する有機EL素子E<sub>i,j</sub>のアノード-カソード間の電圧レベルであって、有機EL素子E<sub>i,j</sub>の発光寿命期間中に有機EL素子E<sub>i,j</sub>が高抵抗化するが発光寿命期間中で予想される最大のアノード-カソード間電圧のレベルである。V<sub>THMAX</sub>は、V<sub>GSMAX</sub>時のトランジスタ23のソース-ドレイン間の飽和電圧レベルである。以上の条件式を満たすように電位V<sub>HIGH</sub>が設定されている。従って、第三トランジスタ23と直列に接続された有機EL素子E<sub>i,j</sub>の分圧により第三トランジスタ23のゲート-ソース間電圧レベルV<sub>DS</sub>が低くなつても、ソース-ドレイン間電圧レベルV<sub>DS</sub>が常に飽和状態の範囲内なので、第三トランジスタ23を流れるソース-ドレイン間電流レベルI<sub>DS</sub>はゲート-ソース間電圧レベルV<sub>G</sub>により一義的に決まることになる。

40

#### 【0058】

次に、データドライバ3について説明する。図1、図3に示されるように、データドライバ3の出力端子OUT<sub>1</sub>~OUT<sub>n</sub>には、それぞれ信号線Y<sub>1</sub>~Y<sub>n</sub>が接続されている。データドライバ3には外部回路11からクロック信号CK1や輝度階調信号S<sub>C</sub>を含む制御

50

信号群  $D_{CNT}$  が入力され、データドライバ 3 は入力したクロック信号 CK 1 のタイミングによって輝度階調信号  $S_c$  をラッチし、信号線  $Y_1 \sim Y_n$  からそれぞれの出力端子  $OUT_1 \sim OUT_n$  に輝度階調信号  $S_c$  に従って階調指定シンク電流を 流す。具体的には、選択走査線  $X_1 \sim X_m$  が選択されている各々の選択期間  $T_{SE}$  の時に、データドライバ 3 によって階調指定シンク電流が同期して信号線  $Y_1 \sim Y_n$  から全ての出力端子  $OUT_1 \sim OUT_n$  に向かって流れる。階調指定シンク電流とは、外部回路 11 からの輝度階調信号  $S_c$  にしたがった輝度で有機 EL 素子  $E_{i,1} \sim E_{i,n}$  を発光するために、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に流れる電流レベル（電流値）と等価の電流であって、信号線  $Y_1 \sim Y_n$  からそれぞれの出力端子  $OUT_1 \sim OUT_n$  に向かって流れる電流である。

## 【0059】

10

次に、データドライバ 3、選択走査ドライバ 5 及び発振回路 6 で有機 EL 表示パネル 2 を駆動する方法及び有機 EL ディスプレイ 1 の表示動作について説明する。

## 【0060】

図 5 に示されるように、選択走査ドライバ 5 が、外部回路 11 から入力したクロック信号 CK 2 に基づいて、1 行目の選択走査線  $X_1$  から  $m$  行目の選択走査線  $X_m$  への順に（但し、選択走査線  $X_m$  の次は選択走査線  $X_1$  である。）順次オン電位  $V_{ON}$  を印加してハイレベルの選択信号を出力する。これにより、選択走査線  $X_1$  から選択走査線  $X_m$  の順に走査されていく。

## 【0061】

20

選択走査ドライバ 5 が順次選択して走査しているのと同時に、発振回路 6 が、全ての周期信号供給線  $Z_1 \sim Z_m$  に周期的信号を出力するが、どの周期信号供給線  $Z_1 \sim Z_m$  に出力された周期的信号も互いに同期している。そして、どの画素回路  $D_{1,1} \sim D_{m,n}$  においても、周期的信号を第二トランジスタ 22 のソース電極 22s 及び第三トランジスタ 23 のソース電極 23s で入力する。

## 【0062】

更に、選択走査ドライバが順次走査している最中において、データドライバ 3 は、外部回路 11 から入力したクロック信号 CK 1 に基づいて輝度階調信号  $S_c$  をラッチし、ラッチした輝度階調信号  $S_c$  に基づいたレベルの階調指定シンク電流をそれぞれの選択走査線  $X_1 \sim X_m$  に選択信号が出力されるのに同期して信号線  $Y_1 \sim Y_n$  からデータドライバ 3 の出力端子  $OUT_1 \sim OUT_n$  に向かって流れさせる。

30

## 【0063】

ここで、オンレベルの選択信号が或る選択走査線  $X_i$  に出力されている時には、他の選択走査線  $X_1 \sim X_m$  ( $X_i$  を除く。) にはオフレベルの選択信号が出力されており、この期間が  $i$  行目の選択期間  $T_{SE}$  となる。従って、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  については、第一トランジスタ 21 及び第二トランジスタ 22 がオン状態であり、他の行の画素回路  $D_{1,1} \sim D_{m,n}$  (但し、画素回路  $D_{i,1} \sim D_{i,n}$  を除く。) については、第一トランジスタ 21 及び第二トランジスタ 22 がオフ状態である。

## 【0064】

40

第一トランジスタ 21 及び第二トランジスタ 22 がオンすると、ドレイン電極 23d が第二トランジスタ 22 のドレイン電極 22d に接続され且つゲート電極 23g が第二トランジスタ 22 のソース電極 22s に接続されている第三トランジスタ 23 のゲート - ソース間及びソース - ドレイン間には、データドライバ 3 からの階調指定シンク電流の引き込みにより第一トランジスタ 21 のソース - ドレイン間及び第三トランジスタ 23 のソース - ドレイン間に階調指定シンク電流が流れるような電圧が加わる。

## 【0065】

従って、 $i$  行目の選択期間  $T_{SE}$  中に  $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の第一トランジスタ 21 及び第二トランジスタ 22 がオン状態になることによって、信号線  $Y_1 \sim Y_n$  からデータドライバ 3 に引き込まれる階調指定シンク電流が、 $i$  行目のそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  に取り込まれる状態になり、つまり  $i$  行目の第三トランジスタ 23 が階調指定シンク電流を流すことができる状態になり、他の行の画素回路  $D_{1,1} \sim D_{m,n}$  (但し、画素回路

50

$D_{i,1} \sim D_{i,n}$ を除く。)には取り込まれない状態になり、つまり他の行の第三トランジスタ23が階調指定シンク電流を流すことができない状態になる。このように $i$ 行目の選択期間 $T_{SE}$ において、それぞれの画素回路 $D_{i,1} \sim D_{i,n}$ に階調指定シンク電流に応じた第三トランジスタ23のゲート-ソース間のチャージが取り込まれることによって、その前までに取り込まれた第三トランジスタ23のゲート-ソース間のチャージがリフレッシュされる。 $i$ 行目の選択期間 $T_{SE}$ 後の非選択期間 $T_{NSE}$ において、画素回路 $D_{i,1} \sim D_{i,n}$ は、それぞれの第三トランジスタ23のゲート-ソース間にチャージされた電荷に従ったレベルの駆動電流を(階調指定シンク電流と等レベルである。)それぞれの発光素子 $E_{i,1} \sim E_{i,n}$ に流すことによってそれぞれの発光素子 $E_{i,1} \sim E_{i,n}$ を発光させる。

【0066】

10

以上のように選択走査ドライバ5が1行目から $m$ 行目へと線順次に選択信号をシフトしていくことによって、データドライバ3に入力された輝度階調信号 $S_C$ に従って1行目の画素回路 $D_{1,1} \sim D_{1,n}$ から $m$ 行目の画素回路 $D_{m,1} \sim D_{m,n}$ の順に階調指定シンク電流が流れて各第三トランジスタ23のゲート-ソース間にチャージされた電荷がリフレッシュされていく。このような線順次の走査が繰り返されることで、有機EL表示パネル2の表示部4で画像表示が為される。

【0067】

ここで、 $i$ 行目の選択期間 $T_{SE}$ に画素回路 $D_{i,1} \sim D_{i,n}$ が階調指定シンク電流を取り込む動作と、取り込んだ階調指定シンク電流に基づいてそれぞれの有機EL素子 $E_{i,1} \sim E_{i,n}$ を発光させる動作について詳細に説明する。

20

【0068】

$i$ 行目の選択期間 $T_{SE}$ では、外部回路11からクロック信号CK2を含む制御信号群 $G_{CN_T}$ に応じて選択走査ドライバ5から $i$ 行目の選択走査線 $X_i$ へオン電位 $V_{ON}$ の選択信号が出力されることで、選択走査線 $X_i$ に接続された全ての画素回路 $D_{i,1} \sim D_{i,n}$ の第一トランジスタ21及び第二トランジスタ22が選択期間 $T_{SE}$ の間中オン状態となる。更に、 $i$ 行目の選択期間 $T_{SE}$ の開始時では周期的信号が電位 $V_{LOW}$ に下がり、 $i$ 行目の選択期間 $T_{SE}$ においては電位 $V_{LOW}$ が周期信号供給線 $Z_i$ に印加される。そして、第二トランジスタ22がオン状態となっているので、第三トランジスタ23のゲート電極23gにも電圧が印加され、第三トランジスタ23がオン状態となる。

【0069】

30

更に、選択された行の有機EL素子 $E_{i,1} \sim E_{i,n}$ のうち何れかの列を後述する非選択期間 $T_{NSE}$ に発光させる場合には、データドライバ3が出力端子 $OUT_1 \sim OUT_n$ のうちの発光させるべき列の電位を電位 $V_{LOW}$ より低く制御することで、画素回路 $D_{i,j}$ のうち発光すべき列で階調指定シンク電流が周期信号供給線 $Z_i$ からデータドライバ3へと流れる。

一方、選択された行の有機EL素子 $E_{i,1} \sim E_{i,n}$ のうち何れかの列を後述する非選択期間 $T_{NSE}$ に発光させない場合には、データドライバ3が出力端子 $OUT_1 \sim OUT_n$ のうちの発光させない列の電位を電位 $V_{LOW}$ と等しくなるように制御することで、画素回路 $D_{i,j}$ のうち発光すべき列で階調指定シンク電流が周期信号供給線 $Z_i$ からデータドライバ3へと流れない。そして、 $i$ 行目の選択期間 $T_{SE}$ 中にデータドライバ3はそれぞれの出力端子 $OUT_1 \sim OUT_n$ の電位を制御することでデータドライバ3へ階調指定シンク電流をそれぞれの信号線 $Y_1 \sim Y_n$ に流し(但し、発光させない列については階調指定シンク電流は流れない)、 $i$ 行目の各画素回路 $D_{i,1} \sim D_{i,n}$ では、第一トランジスタ21及び第二トランジスタ22がオン状態になることによって周期信号供給線 $Z_i$ 、第三トランジスタ23、第一トランジスタ21に対応する信号線 $Y_1 \sim Y_n$ 、データドライバ3へと階調指定シンク電流が流れようになる。このように、 $i$ 行目の選択期間 $T_{SE}$ 中には、画素回路 $D_{i,1} \sim D_{i,n}$ 、それぞれの第一トランジスタ21は、周期信号供給線 $Z_i$ からそれぞれの第三トランジスタ23を通じてそれぞれの信号線 $Y_1 \sim Y_n$ に階調指定シンク電流を流すように機能する。

【0070】

これにより、各画素回路 $D_{i,1} \sim D_{i,n}$ には、階調指定シンク電流のレベルに応じた電圧が

40

50

取り込まれる。このとき 1 列目から  $n$  列目の何れの列においても、階調指定シンク電流のレベルは、輝度階調信号  $S_C$  に従って有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に流れる電流のレベルであり、データドライバ 3 によって指定されているためこの選択期間  $T_{SE}$  中の階調指定シンク電流のレベルは一定である。

【0071】

$i$  行目の選択期間  $T_{SE}$  中に周期信号供給線  $Z_i$  第三トランジスタ 23 第一トランジスタ 21 対応する信号線  $Y_1 \sim Y_n$  データドライバ 3 へと一定レベルの階調指定シンク電流が流れることによって、 $i$  行目の選択期間  $T_{SE}$  中に周期信号供給線  $Z_i \sim$  第三トランジスタ 23 ~ 第一トランジスタ 21 ~ 対応する信号線  $Y_1 \sim Y_n \sim$  データドライバ 3 における電圧が定常状態になる。

10

【0072】

つまり、第三トランジスタ 23 に階調指定シンク電流が流れ周期信号供給線  $Z_i \sim$  第三トランジスタ 23 ~ 第一トランジスタ 21 ~ 対応する信号線  $Y_1 \sim Y_n \sim$  データドライバ 3 における電圧が定常状態になることによって、第三トランジスタ 23 に流れる階調指定シンク電流のレベルに従ったレベルの電圧が第三トランジスタ 23 のゲート電極 23g とソース電極 23s との間に印加され、第三トランジスタ 23 のゲート電極 23g とソース電極 23s との間の電圧のレベルに従った大きさの電荷がコンデンサ 24 にチャージされる。換言すれば、 $i$  行目の選択期間  $T_{SE}$  において  $i$  行目の各々の画素回路  $D_{i,1} \sim D_{i,n}$  では、第一トランジスタ 21 及び第二トランジスタ 22 が、信号線  $Y_j$  に流れる階調指定シンク電流を第三トランジスタ 23 に流すように機能し、第三トランジスタ 23 が、階調指定シンク電流レベルをゲート - ソース間電圧のレベルに変換するように機能する。

20

【0073】

以上のように、 $i$  行目の選択期間  $T_{SE}$  中において、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  のコンデンサ 24 にチャージされる電荷の大きさが前回の一走査期間  $T_{SC}$  からリフレッシュされるとともに、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 23 のドレイン - ソース間電流レベル及びソース - ゲート間電圧レベルも前回の一走査期間  $T_{SC}$  からリフレッシュされる。

30

【0074】

ここで、第三トランジスタ 23 第一トランジスタ 21 信号線  $Y_j$  までの間の任意の点での電位は、経時変化するトランジスタ 21, 22, 23 の内部抵抗等に因って変化してしまう。しかしながら、本実施形態では、第三トランジスタ 23 第一トランジスタ 21 信号線  $Y_j$  へと流れる階調指定シンク電流のレベルは、輝度階調信号  $S_C$  に従ってデータドライバ 3 が強制的に流しているため、トランジスタ 21, 22, 23 の内部抵抗が経時変化しても、第三トランジスタ 23 第一トランジスタ 21 信号線  $Y_j$  へと流れる階調指定シンク電流のレベルは所望通りとなる。

40

【0075】

また、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  のカソードは基準電位  $V_{SS}$  であり、周期信号供給線  $Z_i$  は基準電位  $V_{SS}$  と同じ又は基準電位  $V_{SS}$  より低い電位  $V_{LOW}$  であるため、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  にはされるから又は  $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に電圧が印加されないから、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には電流が流れず、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  は発光しない。

40

【0076】

続いて、 $i$  行目の選択期間  $T_{SE}$  の終了時刻 ( $i$  行目の非選択期間  $T_{NSE}$  の開始時刻) では、選択走査ドライバ 5 から選択走査線  $X_i$  に出力される選択信号が電位  $ON$  のハイレベルから電位  $OFF$  のローレベルになり、発振回路 6 から周期信号供給線  $Z_i$  に出力される周期的信号が電位  $V_{LOW}$  に下がる。つまり、この終了時刻から次の  $i$  行目の選択期間  $T_{SE}$  の開始時刻までの非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の第一トランジスタ 21 のゲート電極 21g 及び第二トランジスタ 22 のゲート電極 22g に対してオフ電位  $V_{OFF}$  が選択走査ドライバ 5 によって印加される。

【0077】

50

このため、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の第一トランジスタ 2 1 がオフ状態になり、周期信号供給線  $Z_i$  から対応する信号線  $Y_1 \sim Y_n$  へ流れる階調指定シンク電流を遮断する。更に、 $i$  行目の非選択期間  $T_{NSE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  に何れにおいても、トランジスタ 2 2 がオフ状態になつても、直前の  $i$  行目の選択期間  $T_{SE}$  においてコンデンサ 2 4 にチャージされた電荷が第二トランジスタ 2 2 によって閉じ込められる。これにより、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、第三トランジスタ 2 3 は、非選択期間  $T_{NSE}$  中オン状態を維持し続ける。つまり、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、非選択期間  $T_{NSE}$  における第三トランジスタ 2 3 のゲート - ソース間電圧レベル  $V_{GS}$  がその直前の選択期間  $T_{SE}$  における第三トランジスタ 2 3 のゲート - ソース間電圧レベル  $V_{GS}$  と等しくなるように、第二トランジスタ 2 2 が第三トランジスタ 2 3 のゲート - ソース間電圧レベル  $V_{GS}$  を保持する。

10

#### 【0078】

そして、 $i$  行目の非選択期間  $T_{NSE}$  においても、発振回路 6 は周期信号供給線  $Z_i$  に周期的信号を出力している。ここで、 $i$  行目の非選択期間  $T_{NSE}$  の最中において周期的信号が電位  $V_{HIGH}$  になっている時は、 $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  のカソードが基準電位  $V_{SS}$  である上、周期信号供給線  $Z_i$  が基準電位  $V_{SS}$  より高い電位  $V_{HIGH}$  であり、更に、直列に接続されている第三トランジスタ 2 3 のゲート - ソース間に、 $i$  行目の非選択期間  $T_{NSE}$  に階調指定シンク電流にしたがつた電圧がチャージされていれば  $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  には階調指定シンク電流に従つた順バイアス電圧が印加される。従つて、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、周期信号供給線  $Z_i$  から第三トランジスタ 2 3 を通じて  $i$  行目の有機 EL 素子  $E_{i,1} \sim E_{i,n}$  へ階調指定シンク電流に等しい駆動電流が流れて、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  が発光する。

20

#### 【0079】

つまり、非選択期間  $T_{SE}$  中の各々の画素回路  $D_{i,1} \sim D_{i,n}$  においては、第一トランジスタ 2 1 が、対応した信号線  $Y_j$  に流れる階調指定シンク電流を第三トランジスタ 2 3 に流れないように信号線  $Y_j$  と第三トランジスタ 2 3 との間を電気的に遮断するように機能し、第二トランジスタ 2 2 が、コンデンサ 2 4 の電荷を閉じ込めてることによって、選択期間  $T_{SE}$  において変換された第三トランジスタ 2 3 のゲート - ソース間電圧のレベルを保持するように機能する。そして、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の何れにおいても、非選択期間  $T_{SE}$  の最中に周期的信号が電位  $V_{HIGH}$  になっている時には、第三トランジスタ 2 3 が、保持されたゲート - ソース間電圧レベルに応じたレベルの駆動電流を有機 EL 素子  $E_{i,j}$  に流すように機能する。

30

#### 【0080】

ここで、周期的信号が  $V_{HIGH}$  になっている時に有機 EL 素子  $E_{i,1} \sim E_{i,n}$  に流れる駆動電流のレベルは、それぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 に流れる電流のレベルと同じであり、従つて、直前の  $i$  行目の選択期間  $T_{SE}$  においてそれぞれの画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 に流れる階調指定シンク電流のレベルと同じである。上述したように、 $i$  行目の選択期間  $T_{SE}$  では、 $i$  行目の画素回路  $D_{i,1} \sim D_{i,n}$  の第三トランジスタ 2 3 の電流レベルは所望通りとなるから、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  それぞれの駆動電流レベルも所望通りになる。従つて、有機 EL 素子  $E_{i,1} \sim E_{i,n}$  それぞれは所望の階調輝度で発光する。

40

#### 【0081】

以上のように本実施の形態では、非選択期間  $T_{NSE}$  の最中に周期的信号が電位  $V_{HIGH}$  になっている時に有機 EL 素子  $E_{i,j}$  に流れる駆動電流のレベルを、その直前の選択期間  $T_{SE}$  において階調指定シンク電流のレベルで表している。従つて、例えば、画素回路  $D_{1,1} \sim D_{m,n}$  の間で第三トランジスタ 2 3 の特性にバラツキがあったとしても、画素回路  $D_{1,1} \sim D_{m,n}$  の間で階調指定シンク電流レベルが同じであれば、各画素の有機 EL 素子  $E_{1,1} \sim E_{m,n}$  の間で輝度にバラツキが生じない。つまり、本実施形態では、同じ電圧レベルの輝度階調信号が画素に出力されても画素の間で輝度が異なってしまうという面内バラツキを抑えることができる。従つて、本実施形態の有機 EL ディスプレイ 1 は、高品質な画像表示

50

を行える。

【0082】

また、非選択期間  $T_{NSE}$ において周期的信号が( $m - 1$ )回  $V_{HIGH}$ になっており、有機EL素子  $E_{i,j}$ の発光デューティは約50%である(実際には発光デューティは( $m - 1$ )/2mであり、行( $m$ )が1より十分に大きければ約50%である。)。それに対して、縦にm個横にn個に有機EL素子が配列された単純マトリクス駆動方式のディスプレイならば、発光デューティは1/mである。従って、単純マトリクス駆動方式のディスプレイは高解像度になるに連れて有機EL素子の発光デューティが小さくなってしまうが、本実施形態の有機ELディスプレイ1は高解像度になっても有機EL素子  $E_{i,j}$ の発光デューティが小さくならず、高輝度、高コントラスト及び高精細な画像表示を行える。

10

【0083】

また、一行につき二つの選択走査線  $X_i$ と周期信号供給線  $Z_i$ が設けられているが、周期信号供給線  $Z_i$ に対しては走査のための信号ではなく単に周期的信号が発振回路6によって出力されている。この有機ELディスプレイ1が具備する走査のためのシフトレジスタは、選択走査ドライバ5だけである。シフトレジスタは一般的にm個のフリップフロップ回路等から構成されるが、発振回路6は水晶発振器等から構成されるため、発振回路6はシフトレジスタに比較しても実装面積が低く、構成が簡略であり、素子の数も少ない。従って、シフトレジスタがドライバとして二個設けられた従来の有機ELディスプレイに比較しても、本実施形態の有機ELディスプレイ1の製造コストが低く、歩留りが高い。

【0084】

20

また、有機EL素子  $E_{i,j}$ の周囲に設けられた画素回路  $D_{i,j}$ が三つのトランジスタ21, 22, 23とコンデンサ24から構成されるため、図9に示されるように画素ごとに四つのトランジスタ702, 705, 706, 707が設けられた有機ELディスプレイと比較しても、本実施形態の有機ELディスプレイ1は、製造コストが低くなり、製造歩留りも向上し、画素の開口率も向上する。また、トランジスタ21, 22, 23の全てが、アモルファスシリコンを半導体層としたNチャネル型電界効果トランジスタであるため、同一工程でトランジスタ21, 22, 23を形成することができ、有機EL表示ディスプレイ1の製造方法が簡略化される。

【0085】

〔第二の実施の形態〕

30

次に、第二の実施の形態の有機ELディスプレイについて説明する。

第二実施形態においても、有機ELディスプレイは、図1に示された第一実施形態の有機ELディスプレイ1と同様に、有機EL表示パネル2と、データドライバ3と、選択走査ドライバ5と、を備える。データドライバ3、表示部4、選択走査ドライバ5、画素回路  $D_{1,1} \sim D_{m,n}$ 、有機EL素子  $E_{1,1} \sim E_{m,n}$ については、第一実施形態の有機ELディスプレイ1と同様の構成をしているため、第二の実施の形態では詳細な説明を省略する。

【0086】

第二の実施の形態において、発振回路6は有機ELディスプレイ1に接続された外部回路11内に設けられている。このため、有機ELディスプレイ1の基板の画素の占有面積の割合を向上することができる。

40

なお、第二の実施の形態の有機ELディスプレイ1は第一の実施の形態と同様に図5に示すような波形チャートで動作することができる。

【0087】

なお、本発明は、上記各実施の形態に限定されることなく、本発明の趣旨を逸脱しない範囲において、種々の改良並びに設計の変更を行っても良い。

例えば、上記各実施の形態における画素回路  $D_{i,j}$ の第一トランジスタ21、第二トランジスタ22及び第三トランジスタ23は全てNチャネル型のトランジスタであったが、全てPチャネル型として有機EL素子  $E_{i,j}$ とのアノードとカソードを逆向きに接続してもよい。このとき、図5に示す波形は、上下反転するように設定すればよい。

50

## 【0088】

また、上記各実施の形態では発光素子として有機EL素子を用いているが、整流性のある他の発光素子を用いても良い。つまり、逆バイアス電圧が印加された場合には電流が流れないとともに順バイアス電圧が印加された場合には電流が流れれるような発光素子であって、流れる電流の大きさに従った輝度で発光する発光素子であっても良い。整流性のある発光素子としては、例えばLED (Light Emitting Diode) 素子が挙げられる。

## 【0089】

また、上記各実施形態においてはデータドライバ3及び選択走査ドライバ5が外部回路11から入力されるクロック信号に基づいて動作していたが、発振回路6で出力された周期的信号がクロック信号としてデータドライバ3及び選択走査ドライバ5に入力され、周期的信号に基づいてデータドライバ3及び選択走査ドライバ5が動作しても良い。

10

## 【0090】

また、上記各実施形態では、発振回路6から出力される周期的信号がロー・レベル、つまり階調指定シンク電流を流す回数は、選択期間 $T_{SE}$ 当たり一回であったが、選択期間 $T_{SE}$ 当たり二回以上であっても良い。

## 【0091】

## 【発明の効果】

本発明によれば、発光素子に駆動電流が流れることで発光素子が発光するが、駆動電流のレベルは、画素回路に保持された電圧レベルに従っており、その電圧レベルは指定電流のレベルを変換したものであるから、発光素子は指定電流のレベルに依存した輝度で発光する。つまり、発光素子は所望通りの輝度で発光するから、指定電流のレベルが画素の間で同じであれば、複数の発光素子の間で輝度のバラツキが生じず、高品質な画面表示を行うことができる。

20

## 【0092】

また、各々の走査線に選択信号を供給するのは走査ドライバだけであり、走査のための他のドライバが設けられていない。また、発振回路は、走査ドライバに比較しても素子数も少なく、簡単な構成である。従来の図9の有機ELディスプレイが二つの走査ドライバとデータドライバで駆動されていたのに対して、本発明では、表示パネルが一つの走査ドライバ、データドライバ及び発振回路で駆動されている。そのため、本発明では、図9の有機ELディスプレイと比較しても、ドライバの実装面積が小さく、歩留りも向上する。

30

## 【図面の簡単な説明】

【図1】本発明が適用された有機ELディスプレイの具体的な態様を示したブロック図。

【図2】図1の有機ELディスプレイの画素を示した平面図。

【図3】図1の有機ELディスプレイの画素の等価回路を示した図面。

【図4】Nチャネル型の第三トランジスタ23の電流-電圧特性を示した図面。

【図5】図1の有機ELディスプレイにおける信号のレベルを示したタイミングチャート。

【図6】別の有機ELディスプレイの画素を示した平面図。

【図7】従来の液晶ディスプレイの画素の等価回路を示した図面。

【図8】従来の電圧指定型の有機ELディスプレイの画素の等価回路を示した図面。

40

【図9】従来の電流指定型の有機ELディスプレイの画素の等価回路を示した図面。

## 【符号の説明】

- 1 有機ELディスプレイ (表示装置)

- 2 有機EL表示パネル (表示パネル)

- 3 データドライバ

- 5 選択走査ドライバ (走査ドライバ)

- 6 発振回路

- 11 外部回路

- 21 第一トランジスタ

- 22 第二トランジスタ

50

## 2 3 第三トランジスタ

E<sub>1,1</sub> ~ E<sub>m,n</sub> 有機EL素子(発光素子)Y<sub>1</sub> ~ Y<sub>n</sub> 信号線X<sub>1</sub> ~ X<sub>n</sub> 選択走査線(走査線)Z<sub>1</sub> ~ Z<sub>n</sub> 周期信号供給線P<sub>1,1</sub> ~ P<sub>m,n</sub> 画素D<sub>1,1</sub> ~ D<sub>m,n</sub> 画素回路

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【圖 6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 624 E

G 09 G 3/20 641 D

(56)参考文献 国際公開第01/006484 (WO, A1)

特開平10-312173 (JP, A)

特表2004-531772 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30, 3/20

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示面板的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP4103500B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2008-06-18 |

| 申请号            | JP2002245444                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2002-08-26 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 山田裕康<br>白寄友之                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 山田 裕康<br>白寄 友之                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/32 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/2011 G09G3/325 G09G3/3283 G09G2300/0408 G09G2300/0842 G09G2300/0866 G09G2310/0248 G09G2310/0251 G09G2310/0256 G09G2310/0297 G09G2310/066 H01L27/3244                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/30.J G09G3/20.612.E G09G3/20.612.K G09G3/20.622.D G09G3/20.624.B G09G3/20.624.E G09G3/20.641.D G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD03 5C080/DD22 5C080/DD27 5C080/DD28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB34 5C380/BA11 5C380/BA13 5C380/BA29 5C380/BA38 5C380/BB02 5C380/BB22 5C380/BB23 5C380/CA08 5C380/CA13 5C380/CB01 5C380/CC13 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC41 5C380/CC62 5C380/CD013 5C380/CE04 5C380/CF58 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 其他公开文献         | JP2004085802A                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

本发明的目的是提供一种显示装置和显示面板驱动方法，其能够提供高质量的显示，低制造成本和高产量。有机EL显示器1包括有机EL显示面板2。在有机EL显示面板2中，像素P<sub>i,j</sub>以矩阵排列，并且像素P被布置。i,j包括有机EL元件E<sub>b,j</sub>和像素电路D<sub>b,j</sub>。有机EL显示面板2由数据驱动器3，选择性扫描驱动器5和振荡电路6驱动。当在选择时段期间周期信号变低时，像素电路D<sub>i,j</sub>遵循在信号线Y<sub>j</sub>中流动的指定吸收电流电平的灰度。当在非选择时段期间周期信号变为高电平时，根据晶体管23的电压电平的电平的驱动电流被转移到有机EL元件E<sub>i,j</sub>让流动。[选图]图1