# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-12897 (P2004-12897A)

(43) 公開日 平成16年1月15日(2004.1.15)

| (51) Int.C1. <sup>7</sup> | F 1                          |                      |                    | テー                     | マコード  | <br>(参考)       |

|---------------------------|------------------------------|----------------------|--------------------|------------------------|-------|----------------|

| GO9G 3/30                 | GO9G                         | 3/30                 | J                  | 3 K (                  | 007   |                |

| GO9G 3/20                 | GO9G                         | 3/20 €               | 8 1 1 A            | 5 C (                  | 080   |                |

| HO5B 33/14                | GO9G                         | 3/20 €               | S 2 4 B            |                        |       |                |

|                           | GO9G                         | 3/20 €               | 641D               |                        |       |                |

|                           | HO5B                         | 33/14                | Α                  |                        |       |                |

|                           |                              | 審査部                  | 青求 有               | 請求項の数 12               | OL    | (全 26 頁)       |

| (21) 出願番号                 | 特願2002-167390 (P2002-167390) | (71) 出願人             | 000001             | .443                   |       |                |

| (22) 出願日                  | 平成14年6月7日 (2002.6.7)         | カシオ計算機株式会社           |                    |                        |       |                |

|                           |                              |                      | 東京都渋谷区本町1丁目6番2号    |                        |       |                |

|                           |                              | (74) 代理人             | 100096             |                        |       |                |

|                           |                              |                      |                    | 鹿嶋 英實                  |       |                |

|                           |                              | (72) 発明者             |                    | 裕康<br>                 |       |                |

|                           |                              |                      | 東京都八王子市石川町2951番地の5 |                        |       |                |

|                           |                              |                      | *10-               |                        | カシオ   | 計算機株式会         |

|                           |                              | (50) <b>70 FD +x</b> |                    | 子研究所内                  |       |                |

|                           |                              | (72) 発明者             | 武居                 |                        |       | 1 354 44 45 17 |

|                           |                              |                      | 宋                  | 八王子市石川町                |       |                |

|                           |                              |                      | <b>≯</b> 4 € ∓5    | 之四來能力                  | ガンオー  | 計算機株式会         |

|                           |                              | <br> F ター 1. (参      |                    | 子研究所内<br>107 AB03 AB11 | ΔR17  | AR18 DR03      |

|                           |                              | F クーム (多             | J) SKC             | GA04                   | VDI 1 | פטמת סומע      |

|                           |                              |                      |                    | 最終頁に続く                 |       |                |

(54) 【発明の名称】表示装置及び表示装置の駆動制御方法

# (57)【要約】

【課題】発光素子を電流指定方式で発光制御するディスプレイにおいて、簡易かつ安価な回路構成を有しつつ、 画像表示に伴う消費電力を抑制することができるとともに、表示パネルの発光輝度の低下を抑制することができる表示装置及び表示装置の駆動制御方法を提供する。

【解決手段】有機 E L 素子や発光ダイオード等のように、供給される電流値に応じて所定の輝度で自己発光する発光素子をマトリクス状に配列してなる表示パネルを備えたディスプレイにおいて、各表示画素ごとの発光素子に付設された画素駆動回路により、表示画素への書込電流よりも一定のオフセット電流分小さい駆動電流を発光素子に供給するように構成されている。

【選択図】 図1

## 【特許請求の範囲】

# 【請求項1】

表示パネルを構成する各表示画素に対して、表示信号に応じた第1の電流値を指定して電流を供給することにより、該各表示画素に設けられた発光素子を所定の輝度で発光させ、前記表示パネルに所望の画像情報を表示する表示装置において、

前記各表示画素は、前記発光素子の発光動作を制御する画素駆動回路を備え、

該画素駆動回路は、

前記第1の電流値を有する書込電流を前記画素駆動回路に流下させる制御を行う書込制御手段と、

前記書込制御手段に付設され、前記書込電流の流下に伴って第1の電荷を蓄積する第1の電荷蓄積手段と、

前記発光素子に前記表示信号に応じた駆動電流を供給して、前記発光素子を前記所定の輝度で発光動作させる制御を行う発光制御手段と、

前記発光制御手段に付設され、前記書込電流の流下に伴って第2の電荷を蓄積する第2の電荷蓄積手段と、

を備え、

前記発光素子に供給される前記駆動電流は、前記第1の電荷蓄積手段に蓄積された前記第 1の電荷及び前記第2の電荷蓄積手段に蓄積された前記第2の電荷に基づく電圧に対応する第2の電流値を有するように設定されていることを特徴とする表示装置。

### 【請求項2】

前記第2の電流値は、前記第1の電流値から、前記第1の電荷蓄積手段に蓄積された前記第1の電荷に基づく電圧に対応した電流値を除いた値となるように設定されていることを特徴とする請求項1記載の表示装置。

#### 【請求項3】

前記書込制御手段は、前記画素駆動回路に前記書込電流を流下させることにより、前記第 1 の電荷蓄積手段に前記第 1 の電荷を蓄積させるとともに、前記第 2 の電荷蓄積手段に前記第 2 の電荷を蓄積させ、

前記発光制御手段は、前記第1の電荷と前記第2の電荷に基づいて生成される電圧により、前記発光素子に前記駆動電流を供給することを特徴とする請求項1又は2記載の表示装置。

【請求項4】

前記第1の電荷蓄積手段の蓄積容量と、前記第2の電荷蓄積手段の蓄積容量は、同等になるように設定されていることを特徴とする請求項1乃至3のいずれかに記載の表示装置。

# 【請求項5】

前記第1の電荷蓄積手段の蓄積容量は、前記第2の電荷蓄積手段の蓄積容量に比較して、 大きくなるように設定されていることを特徴とする請求項1乃至3のいずれかに記載の表示装置。

## 【請求項6】

前記表示パネルは、

前記各表示画素を行単位で選択するための走査信号が印加される走査線と、

前記各表示画素に前記書込電流を流下するための書込信号が供給される信号線と、

前記各表示画素の前記画素駆動回路に前記書込電流を流下させるとともに、前記発光素子に前記駆動電流を流下させるための電源電圧が供給される電源線と、を備え、

発光制御手段は、電流路及び制御端子を有し、前記電流路の一端側が前記発光素子の入力端子に接続されるとともに、前記電流路の他端側が前記電源線に接続され、前記電流路の一端側と前記制御端子との間の電圧に応じた電流値を有する電流が前記電流路に流れる第1のスイッチング素子からなり、

前記第2の電荷蓄積手段は、前記第1のスイッチング素子の前記電流路及び前記制御端子間に設けられた容量素子からなり、

前記書込制御手段は、各々電流路及び制御端子を有し、前記制御端子が前記走査線に接続

20

10

30

40

され、前記走査信号に応じて、前記第1のスイッチング素子の制御端子に印加される電圧を制御する第2のスイッチング素子、及び、前記信号線に流下する電流を制御する第3のスイッチング素子からなり、

前記第1の電荷蓄積手段は、前記第2のスイッチング素子の前記電流路及び前記制御端子間に設けられた容量素子からなることを特徴とする請求項1乃至5のいずれかに記載の表示装置。

# 【請求項7】

前記第1の電荷蓄積手段は、前記第2のスイッチング素子の前記電流路及び前記制御端子間に形成された寄生容量であり、

前記第2の電荷蓄積手段は、前記第1のスイッチング素子の前記電流路及び前記制御端子間に形成された寄生容量であることを特徴とする請求項6記載の表示装置。

#### 【請求項8】

前記表示装置は、少なくとも、

前記走査線に前記走査信号を印加する走査駆動手段と、

前記信号線に前記書込電流を流下させるための電流引き込み回路を有する信号駆動手段と

前記電源線に所定の電源電圧を印加する電源駆動手段と、

を備えることを特徴とする請求項6又は7記載の表示装置。

#### 【請求項9】

前記第1のスイッチング素子、前記第2のスイッチング素子及び前記第3のスイッチング素子は、nチャネル型のアモルファスシリコン薄膜トランジスタであることを特徴とする請求項6又は7記載の表示装置。

## 【請求項10】

前記発光素子は、有機エレクトロルミネッセント素子であることを特徴とする請求項 1 乃至 9 のいずれかに記載の表示装置。

# 【請求項11】

表示パネルを構成する各表示画素を選択して、該表示画素に表示信号に応じた第1の電流値を指定して電流を供給することにより、該表示画素に設けられた発光素子を所定の輝度で発光させ、前記表示パネルに所望の画像情報を表示する表示装置の駆動制御方法において、

前記各表示画素は、

前記第1の電流値を有する書込電流を前記表示画素に流下させる制御を行う書込制御手段と、

前記書込電流の流下に伴って第1の電荷を蓄積する第1の電荷蓄積手段と、

前記発光素子に前記表示信号に応じた駆動電流を供給して、前記発光素子を前記所定の輝度で発光動作させる制御を行う発光制御手段と、

前記書込電流の流下に伴って第2の電荷を蓄積する第2の電荷蓄積手段と、

からなる画素駆動回路を備え、

前記各表示画素の選択期間中に、前記各表示画素に前記書込電流を流下させて、前記第 1 の電荷蓄積手段に第 1 の電荷を蓄積させるとともに、前記第 2 の電荷蓄積手段に第 2 の電荷を蓄積させ、

前記各表示画素の非選択期間中に、前記第1の電荷及び前記第2の電荷に基づく電圧に対応する第2の電流値を有する前記駆動電流を、前記発光素子に供給することを特徴とする表示装置の駆動制御方法。

#### 【請求項12】

前記第2の電流値は、前記第1の電流値に対して、前記第1の電荷蓄積手段に蓄積された前記第1の電荷に基づく電圧に対応した電流値分だけ小さくなるように設定されていることを特徴とする請求項11記載の表示装置の駆動制御方法。

#### 【発明の詳細な説明】

# [0001]

30

40

10

20

20

30

40

50

### 【発明の属する技術分野】

本発明は、表示装置及び表示装置の駆動制御方法に関し、特に、画像信号に応じた電流を供給することにより所定の輝度階調で発光する光学要素(発光素子)を、複数配列してなる表示パネル(画素アレイ)を備えた表示装置、及び、該表示装置の駆動制御方法に関する。

## [00002]

## 【従来の技術】

従来、有機エレクトロルミネッセンス素子(以下、「有機EL素子」と略記する)、無機エレクトロルミネッセンス素子(以下、「無機EL素子」と略記する)、あるいは、発光ダイオード(LED)等のような自己発光型の発光素子を、マトリクス状に配列した表示パネルを備えた発光素子型のディスプレイ(表示装置)が知られている。特に、アクティブマトリックス駆動方式を適用した発光素子型ディスプレイは、近年普及が著しい液晶表示装置(LCD)に比較して、表示応答速度が速く、視野角依存性もなく、また、高輝度・高コントラスト化、表示画質の高精細化、低消費電力化等が可能であるとともに、液晶表示装置の場合のように、バックライトを必要としないので一層の薄型軽量化が可能であるという極めて優位な特徴を有している。

### [00003]

ここで、上述した各種の発光素子を備えたディスプレイにおいては、発光素子を発光制御するための駆動制御機構や制御方法が種々提案されている。例えば、表示パネルを構成する各表示画素ごとに、上記発光素子に加えて、該発光素子を発光制御するための複数のスイッチング手段からなる駆動回路(以下、便宜的に、「画素駆動回路」と記す)を備えたものが知られている。

## [0004]

以下に、上述した各種の発光素子のうち、近年、実用化に向けて研究開発が盛んに行われている有機化合物を発光材料とする有機 EL素子を備えたディスプレイの表示画素に適用される回路構成について、図面を参照して説明する。

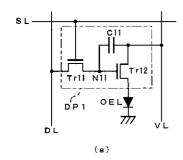

図13は、有機EL素子を備えた発光素子型ディスプレイにおける、従来技術の各表示画素の構成例を示す等価回路である。

# [0005]

従来技術における表示画素は、例えば、図13(a)に示すように、表示パネルにマトリクス状に配設された複数の走査ラインSL及びデータライン(信号ライン)DLの各交点近傍に、ゲート端子が走査ラインSLに、ソース端子及びドレイン端子がデータラインDL及び接点N11に各々接続された薄膜トランジスタ(TFT)Tr11と、ゲート端子が接点N11に、ソース端子が電源ラインVLに各々接続された薄膜トランジスタTr12とを備えた画素駆動回路DP1、及び、画素駆動回路DP1の薄膜トランジスタTr12のドレイン端子にアノード端子が接続され、カソード端子が接地電位に接続された有機EL素子OELを有して構成されている。

## [0006]

ここで、図13(a)において、C11は、薄膜トランジスタTr12のゲート・ソース間に形成される寄生容量である。すなわち、図13(a)に示した画素駆動回路DP1においては、薄膜トランジスタTr11及びTr12からなる2個のトランジスタ(スイッチング手段)をオン、オフ制御することにより、以下に示すように、有機EL素子OELを発光制御するように構成されている。

# [ 0 0 0 7 ]

このような構成を有する画素駆動回路 D P 1 において、図示を省略した走査ドライバにより、走査ライン S L にハイレベルの走査信号を印加して表示画素を選択状態に設定すると、薄膜トランジスタTr 1 1 がオン動作して、図示を省略したデータドライバによりデータライン D L に印加された、表示データ(画像信号)に応じた信号電圧(階調電圧)が薄膜トランジスタTr 1 2 のゲート端子に印加される。これにより、薄膜トランジスタTr 1 2 が上記信号電圧に応じた導通状態でオン動作し

30

50

て、電源ラインVLから薄膜トランジスタTr12を介して所定の駆動電流が流れ、有機 EL素子OELが表示データに応じた輝度階調で発光する。

### [00008]

次いで、走査ラインSLにローレベルの走査信号を印加して表示画素を非選択状態に設定すると、薄膜トランジスタTr11がオフ動作することにより、データラインDLと画素駆動回路DP1とが電気的に遮断される。これにより、薄膜トランジスタTr12のゲート端子に印加された電圧が寄生容量C11により保持されて、薄膜トランジスタTr12は、オン状態を保持することになり、電源ラインVLから薄膜トランジスタTr12を介して有機EL素子OELに所定の駆動電流が流れて、発光動作が継続される。この発光動作は、次の表示データに応じた信号電流が各表示画素に書き込まれるまで、例えば、1フレーム期間継続されるように制御される。

このような駆動制御方法は、各表示画素(薄膜トランジスタTr 1 2 )に印加する電圧を調整することにより、有機 E L 素子に流す駆動電流を制御して、所定の輝度階調で発光動作させていることから、電圧駆動方式と呼ばれている。

#### [0009]

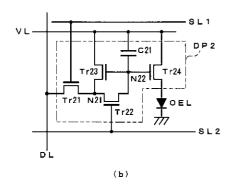

また、従来技術における表示画素の他の例としては、例えば、図13(b)に示すように、相互に並行して配設された第1及び第2の走査ラインSL1、SL2とデータラインDLとの各交点近傍に、ゲート端子が第1の走査ラインSL1に、ソース端子及びドレイン端子がデータラインDL及び接点N21に各々接続された薄膜トランジスタTr21と、ゲート端子が第2の走査ラインSL2に、ソース端子及びドレイン端子が接点N21に各々接続された薄膜トランジスタTr22と、ゲート端子が接点N22に、ソース端子が電源ラインVLに、ドレイン端子が接点N21に各々接続された薄膜トランジスタTr24とを備えた画素駆動回路DP2、及び、画素駆動回路DP2の薄膜トランジスタTr24のドレイン端子にアノード端子が接続され、カソード端子が接地電位に接続された有機EL素子OELを有して構成されている。

# [ 0 0 1 0 ]

ここで、図13(b)において、薄膜トランジスタTr21はnチャンネル型MOSトランジスタ(NMOS)により構成され、薄膜トランジスタTr22乃至Tr24はpチャンネル型MOSトランジスタ(PMOS)により構成されている。また、C21は、薄膜トランジスタTr23及びTr24のゲート・ソース間(接点N22と電源ラインVL)に形成される寄生容量である。すなわち、図13(b)に示した画素駆動回路DP2においては、薄膜トランジスタTr21乃至Tr24からなる4個のトランジスタをオン、オフ制御することにより、以下に示すように、有機EL素子OELを発光制御するように構成されている。

# [0011]

このような構成を有する画素駆動回路において、図示を省略した走査ドライバにより、走査ラインSL1にローレベル、走査ラインSL2にハイレベルの走査信号を各々印加して表示画素を選択状態に設定すると、薄膜トランジスタTr21及びTr22がオン動作して、図示を省略したデータドライバによりデータラインDLに供給された、表示データに応じた信号電流(階調電流)が薄膜トランジスタTr21及びTr22を介して接点N22に取り込まれるとともに、該信号電流レベルが薄膜トランジスタTr23により電圧レベルに変換されてゲート・ソース間に所定の電圧が生じる(書込動作)。

# [0012]

次いで、例えば、走査ラインSL2にローレベルの走査信号を印加すると、薄膜トランジスタTr22がオフ動作することにより、薄膜トランジスタTr23のゲート・ソース間に生じた電圧が寄生容量C21により保持され、次に、走査ラインSL1にハイレベルの走査信号を印加すると、薄膜トランジスタTr21がオフ動作することにより、データラインDLと画素駆動回路DP2とが電気的に遮断される。これにより、上記寄生容量C21に保持された電圧(ハイレベル)に基づいて、薄膜トランジスタTr24がオン状態と

20

30

50

なって、電源ラインVLから薄膜トランジスタTr24を介して所定の駆動電流が流れて 、有機EL素子OELが表示データに応じた輝度階調で発光する(発光動作)。

#### [0013]

ここで、薄膜トランジスタTr24を介して有機EL素子OELに供給される駆動電流は、表示データの輝度階調に基づいた電流値になるように制御され、この発光動作は、次の表示データに応じた信号電流が各表示画素に書き込まれるまで、例えば、1フレーム期間継続されるように制御される。

このような駆動制御方法は、各表示画素(薄膜トランジスタTr12)に印加する電圧を調整することにより、有機EL素子に流す駆動電流を制御して、所定の輝度階調で発光動作させていることから、電圧駆動方式と呼ばれている。

このような駆動制御方法は、各表示画素に表示データに応じて電流値を指定した電流を供給し、該電流値に応じて保持される電圧に基づいて、有機 EL素子に流す駆動電流を制御して、所定の輝度階調で発光動作させていることから、電流指定方式と呼ばれている。

# [0014]

【発明が解決しようとする課題】

しかしながら、上述したような各種の画素駆動回路を表示画素に備えた表示装置においては、以下に示すような問題を有していた。

すなわち、電圧駆動方式を採用した画素駆動回路(図13(a)参照)においては、2個の薄膜トランジスタTr11及びTr12の素子特性(チャネル抵抗等)が、周囲の温度や使用時間に依存して変化した場合には、発光素子に供給される駆動電流に影響を与えるため、長期間にわたり安定的に所望の発光特性(所定の輝度階調での表示)を実現することが困難になるという問題を有していた。

## [0015]

また、表示画質の高精細化を図るために、表示パネルを構成する各表示画素を微細化すると、画素駆動回路を構成する薄膜トランジスタTr11及びTr12の動作特性(ソース・ドレイン間電流等)のバラツキが大きくなるため、適正な階調制御が行えなくなり、各表示画素の表示特性にバラツキが生じて画質の劣化を招くという問題を有していた。

# [0016]

これに対して、図13(b)に示したような電流指定方式を適用した画素駆動回路においては、各表示画素に供給される表示データに応じた信号電流の電流レベルを、電圧レベルに変換する薄膜トランジスタTr23(電流/電圧変換用トランジスタ)及び有機EL素子OELに所定の電流値の駆動電流を供給する薄膜トランジスタTr24(発光駆動用トランジスタ)を備えて、有機EL素子OELに供給する信号電流を設定することにより、各薄膜トランジスタの動作特性のバラツキの影響を抑制することができる。

# [ 0 0 1 7 ]

また、一般に、電流指定方式の画素駆動回路においては、最下位の輝度(最低輝度)又は比較的輝度の低い表示データに基づく信号電流を各表示画素に書き込む場合、表示データを書き込む動作は、データラインを所定の電圧まで充電することに相当するので、特に、表示パネルの大型化等によりデータラインの配線長が長く設計されている場合には、信号電流の電流値が小さくなるほど(すなわち、輝度階調の低い表示データほど)、表示画素への書込時間(データラインの充電時間)が長くなるという問題を有していた。また、表示画質を高精細化するために、表示パネルに配設される走査ラインの数を増加させて、走査ラインの選択期間を短く設定した場合には、信号電流の電流値が小さくなるほど、表示画素への十分な書込動作が行われなくなるという問題を有していた

### [0018]

これに対して、図13(b)に示したような電流指定方式を適用した画素駆動回路においては、薄膜トランジスタTr23及びTr24をカレントミラー回路構成となるように接続して、データラインに供給する信号電流に対して表示画素に供給する電流を小さくする

20

30

40

50

ように構成することにより、最下位の輝度又は比較的輝度の低い表示データに基づく信号電流を各表示画素に書き込む場合であっても、データラインに比較的大きな電流値を有する信号電流を供給して、表示画素への書込時間を短縮しつつ、該信号電流に対して、カレントミラー回路により設定される所定の比例関係(電流比率)を有する小さな電流値の駆動電流を有機 E L 素子に供給して、各表示画素の適正な階調制御を行うことができるので、表示パネルにおける表示応答速度や表示画質の向上を図ることができる。

[0019]

しかしながら、図13(b)に示したような画素駆動回路においては、データラインに供給する電流は、有機EL素子に供給する電流を所定比率倍した電流となるため、最下位の輝度階調でも良好に発光動作させることができるように、有機EL素子に供給する駆動電流の電流値を設定し、かつ、表示画素への書込時間が短縮されるようにデータラインに供給する信号電流の電流はとなってした場合、すなわち、最下位の輝度階調における設定を基準とした場合、輝度の階調数及びカレントミラー回路により設定される電流比率に応じて、最上位の輝度(最高輝度)を有する表示データに対応してデータラインに供給する信号電流の電流値が過大となってしまい、表示装置の消費電力が著しく大きくなるという問題を有していた。

[0020]

例えば、有機 E L 素子に供給される駆動電流のうち、最下位の輝度階調における発光動作を行うために必要な駆動電流の電流値を I m i n として、カレントミラー回路により、その k 倍の電流比率の信号電流をデータラインに供給するように設計した場合、表示装置(表示パネル)の駆動制御上、最低限必要な電流値を I m u s t とすると、次式(11)のような関係を有している必要がある。

Imin $\times$ k Imust  $\cdots$  (11)

[0021]

ここで、例えば、表示データの輝度階調を256階調に設定した場合、最大輝度のときに有機EL素子に本来供給すべき駆動電流の電流値は、Iminx256であるのに対して、データラインに供給すべき信号電流の電流値は、カレントミラー回路により設定される電流比率kにより、Iminx256xkが必要となり、次式(12)に示すように、Iminx256x(k・1)もの余分な電流 Iを流す必要が生じる。そのため、画素駆動回路における消費電力が著しく大きくなるとともに、データラインとして、上記のような大電流の流下に耐え得る配線抵抗を備える必要もあるという問題を有していた。

$I = (Imin \times 256 \times k) - (Imin \times 256)$ =  $Imin \times 256 \times (k-1)$  · · · (12)

[0022]

また、図13(b)に示したような画素駆動回路のように、複数(図13(b)では4個)の薄膜トランジスタから構成されている場合、各表示画素の全体面積に占める有機EL素子の形成面積が相対的に小さくなるため、これに伴って発光面積も狭くなり、表示パネルの単位面積当たりの発光輝度が低下するという問題を有している。ここで、上記発光輝度をある程度高く設定するためには、有機EL素子に供給する駆動電流(すなわち、各表示画素に供給する信号電流)をより高くする必要があるため、消費電力がさらに大きくなるとともに、大電流の供給により有機EL素子の発光寿命の劣化等を招くという問題を有していた。また、一つの表示画素に形成される薄膜トランジスタの数が増加すると、素子特性のバラツキや不良箇所の発生比率が指数関数的に高くなり、製造歩留まりが著しく低下するという問題も有していた。

[ 0 0 2 3 ]

さらに、図13(b)に示したような画素駆動回路のように、PMOS及びNMOSからなる薄膜トランジスタが混在して構成されている場合、PMOSは、アモルファスシリコントランジスタでは、十分に機能するものを形成することができない。そのため、上述した画素駆動回路においては、ポリシリコントランジスタや単結晶シリコンの技術を用いなければならず、製造コストが上昇するという問題も有している。

### [0024]

そこで、本発明は、上述した種々の問題点に鑑み、発光素子を電流指定方式で発光制御するディスプレイにおいて、簡易かつ安価な回路構成を有しつつ、画像表示に伴う消費電力を抑制することができるとともに、表示パネルの発光輝度の低下を抑制することができる表示装置及び表示装置の駆動制御方法を提供することを目的とする。

#### [0025]

## 【課題を解決するための手段】

請求項1記載の表示装置は、表示パネルを構成する各表示画素に対して、表示信号に応じた第1の電流値を指定して電流を供給することにより、該各表示画素に設けられた発出の電流を供給することに所望の画像情報を表示表に設まる表示装置に対して、前記各表示がネルに所望の画像情報を表示の路を備え、前記各表示の発光動作を制御する画素駆動回路を備え、前記者と、前記者を前記画素を前記画素を前記画素を前記部の電流値を有する書込電流を前記書込電流の流下に伴って第一個で表別の電荷を蓄積する第1の電荷を著積する第1の電荷を発光動作させる制御を行う発光制御手段に付設され、前記書との電荷を蓄積する第1の電荷を著積する第1の電流の流下に伴って第2の電荷を蓄積するに設定されていることを特徴としている。

#### [0026]

請求項2記載の表示装置は、請求項1記載の表示装置において、前記第2の電流値は、前記第1の電流値から、前記第1の電荷蓄積手段に蓄積された前記第1の電荷に基づく電圧に対応した電流値を除いた値となるように設定されていることを特徴としている。 請求項3記載の表示装置は、請求項1又は2記載の表示装置において、前記書込制御手段は、前記画素駆動回路に前記書込電流を流下させることにより、前記第1の電荷蓄積手段

### [0027]

請求項4記載の表示装置は、請求項1乃至3のいずれかに記載の表示装置において、前記第1の電荷蓄積手段の蓄積容量と、前記第2の電荷蓄積手段の蓄積容量は、同等になるように設定されていることを特徴としている。

請求項5記載の表示装置は、請求項1乃至3のいずれかに記載の表示装置において、前記第1の電荷蓄積手段の蓄積容量は、前記第2の電荷蓄積手段の蓄積容量に比較して、大きくなるように設定されていることを特徴としている。

### [0028]

20

10

30

40

20

30

40

50

1の電荷蓄積手段は、前記第2のスイッチング素子の前記電流路及び前記制御端子間に設けられた容量素子からなることを特徴としている。

#### [0029]

請求項7記載の表示装置は、請求項6記載の表示装置において、前記第1の電荷蓄積手段は、前記第2のスイッチング素子の前記電流路及び前記制御端子間に形成された寄生容量であり、前記第2の電荷蓄積手段は、前記第1のスイッチング素子の前記電流路及び前記制御端子間に形成された寄生容量であることを特徴としている。

請求項8記載の表示装置は、請求項6又は7記載の表示装置において、前記表示装置は、少なくとも、前記走査線に前記走査信号を印加する走査駆動手段と、前記信号線に前記書 込電流を流下させるための電流引き込み回路を有する信号駆動手段と、前記電源線に所定 の電源電圧を印加する電源駆動手段と、を備えることを特徴としている。

#### [0030]

請求項9記載の表示装置は、請求項6又は7記載の表示装置において、前記第1のスイッチング素子、前記第2のスイッチング素子及び前記第3のスイッチング素子は、nチャネル型のアモルファスシリコン薄膜トランジスタであることを特徴としている。

請求項10記載の表示装置は、請求項1乃至9のいずれかに記載の表示装置前記発光素子は、有機エレクトロルミネッセント素子であることを特徴としている。

# [0031]

請求項12記載の表示装置の駆動制御方法は、請求項11記載の表示装置の駆動制御方法において、前記第2の電流値は、前記第1の電流値に対して、前記第1の電荷蓄積手段に蓄積された前記第1の電荷に基づく電圧に対応した電流値分だけ小さくなるように設定されていることを特徴としている。

# [0032]

すなわち、本発明に係る表示装置及びその駆動制御方法は、有機 EL素子や発光ダイオード等のように、供給される電流値に応じて所定の輝度で自己発光する発光素子をマトリクス状に配列してなる表示パネルを備えたディスプレイにおいて、各表示画素ごとの発光素子に付設された画素駆動回路により、表示画素への書込電流よりも一定のオフセット電流分小さい駆動電流を発光素子に供給するように構成されている。

#### [0033]

具体的には、発光素子に駆動電流を供給する発光制御トランジスタと、該発光制御トランジスタの動作を制御する駆動制御トランジスタと、各表示画素への表示データの書き込みを制御する書込制御トランジスタと、発光制御トランジスタのゲート・ソース間に付設されたコンデンサと、駆動制御トランジスタのゲート・ソース間に付設されたコンデンサと、を備え、書込動作時(選択期間)に駆動制御トランジスタ及び書込制御トランジスタがオン動作することにより、発光制御トランジスタがオン動作して、上記各コンデンサに蓄積された電荷にで書込制御トランジスタがオフ動作するとともに、上記各コンデンサに蓄積された電荷に

20

30

40

50

基づくゲート電圧を保持して、発光制御トランジスタを所定の導通状態でオン動作させる

### [0034]

これにより、書込電流から、駆動制御トランジスタに付設されたコンデンサに蓄積された電荷分の電流(オフセット電流)を減算した駆動電流が発光素子に供給される。このとき、表示データの輝度階調に関わらず、上記オフセット電流は一定であり、また、書込電流よりも小さく、かつ、表示データの輝度階調に対応した駆動電流が発光制御トランジスタを介して供給されるので、最下位の輝度階調を有する表示データを書き込む場合であっても、比較的大きな電流を流してデータライン及び画素駆動回路に付設されたコンデンサを充電することができ、書込動作に係る所要時間を短縮することができる。

### [0035]

また、所定の表示データに対応した輝度で発光するための駆動電流に対して、一定のオフセット電流を付加(加算)した書込電流を各表示画素に流せばよいので、従来技術に示したような、駆動電流の所定数倍の書込電流を必要とするカレントミラー方式を適用した画素駆動回路に比較して、上位の輝度を有する表示データほど、書込電流を相対的に抑制することができ、表示装置の消費電力を抑制することもできる。

# [0036]

## 【発明の実施の形態】

以下、本発明に係る表示装置及び表示装置の駆動制御方法について、実施の形態を示して 詳しく説明する。

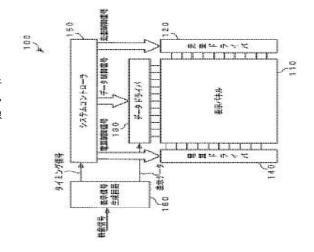

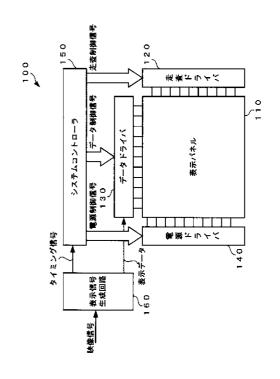

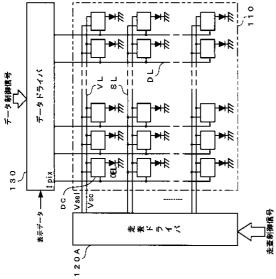

まず、本発明に係る表示装置に適用される全体構成について、図面を参照して説明する。 図1は、本発明に係る表示装置の全体構成の一例を示す概略ブロック図であり、図2は、 本実施形態に係る表示装置に適用される表示パネルの一例を示す概略構成図である。ここ で、上述した従来技術と同等の構成については、同一の符号を付して説明する。

## [0037]

図1、図2に示すように、本実施形態に係る表示装置100は、概略、相互に並行して配 設 さ れ た 複 数 の 走 査 ラ イ ン ( 走 査 線 ) S L 及 び 電 源 ラ イ ン ( 電 源 線 ) V L と 複 数 の デ ー タ ライン(信号線)DLとの各交点近傍に、後述する画素駆動回路DC及び有機EL素子( 発光素子)OELからなる複数の表示画素がマトリクス状に配列された表示パネル(画素 アレイ) 1 1 0 と、表示パネル 1 1 0 の走査ラインSLに接続され、各走査ラインSLに 所 定 の タ イ ミ ン グ で 順 次 八 イ レ ベ ル の 走 査 信 号 V s e l を 印 加 す る こ と に よ り 、 行 ご と の 表示画素群を選択状態に制御する走査ドライバ(走査駆動手段)120と、表示パネル1 10のデータラインDLに接続され、データラインDLへの表示データに応じた信号電流 (階調電流Ipi×)の供給状態を制御するデータドライバ(信号駆動手段)130と、 表示パネル110の走査ラインSLに並行して配設された電源ラインVLに接続され、各 電源ラインVLに所定のタイミングで順次ハイレベル又はローレベルの電源電圧Vscを 印加することにより、表示画素群に表示データに応じた所定の信号電流(階調電流、駆動 電流)を流下させる電源ドライバ(電源駆動手段)140と、後述する表示信号生成回路 160から供給されるタイミング信号に基づいて、少なくとも、走査ドライバ120及び デ ー タ ド ラ イ バ 1 3 0 、 電 源 ド ラ イ バ 1 4 0 の 動 作 状 態 を 制 御 す る 走 査 制 御 信 号 及 び デ ー タ制御信号、電源制御信号を生成、出力するシステムコントローラ 1 5 0 と、表示装置 1 0 0 の外部から供給される映像信号に基づいて、表示データを生成してデータドライバ 1 30に供給するとともに、該表示データを表示パネル110に画像表示するためのタイミ ング信号(システムクロック等)を生成、又は、抽出してシステムコントローラ150に 供給する表示信号生成回路160と、を備えて構成されている。

# [0038]

以下、上記各構成について具体的に説明する。

図3は、本実施形態に係る表示装置に適用されるデータドライバの要部構成を示すプロック図であり、図4は、本実施形態に係るデータドライバに適用される電圧/電流変換回路の一例を示す回路構成図である。また、図5は、本発明に係る表示装置に適用される走査

20

30

40

50

ドライバの他の例を示す概略構成図である。

# [0039]

(表示パネル)

表示パネルにマトリクス状に配列された表示画素は、図2に示すように、走査ドライバ120から走査ラインSLに印加される走査信号Vsel、及び、信号ドライバ130からデータラインDLに供給される信号電流、電源ドライバ140から電源ラインVLに印加される電源電圧Vscに基づいて、後述する表示画素への書込動作及び発光素子の発光動作を制御する画素駆動回路DCと、供給される駆動電流の電流値に応じて発光輝度が制御される有機EL素子OELと、を有して構成されている。

#### [0040]

ここで、画素駆動回路 D C は、概略、走査信号に基づいて該表示画素の選択 / 非選択状態を制御し、選択状態において表示データに応じた階調電流を取り込んで電圧レベルとして保持し、非選択状態において上記保持した電圧レベルに応じた駆動電流を流して発光素子を発光する動作を所定期間維持する機能を有している。

なお、画素駆動回路の具体回路例や回路動作については後述する。また、本発明に係る表示装置においては、画素駆動回路により発光制御される発光素子として、従来技術においても説明した有機 EL素子や発光ダイオード等を良好に適用することができる。

## [0041]

(走査ドライバ)

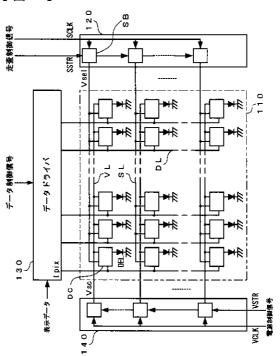

走査ドライバ120は、システムコントローラ150から供給される走査制御信号に基づいて、各走査ラインSLにハイレベルの走査信号Vselを順次印加することにより、各行ごとの表示画素を選択状態とし、データドライバ130によりデータラインDLを介して供給された表示データに基づく階調電流Ipixを表示画素に書き込むように制御する

## [0042]

走査ドライバ120は、具体的には、図2に示すように、シフトレジスタとバッファからなるシフトブロックSB1、SB2、・・・を、各走査ラインSLごとに対応して複数段備え、システムコントローラから供給される走査制御信号(走査スタート信号SSTR、走査クロック信号SCLK等)に基づいて、シフトレジスタにより表示パネル110の上方から下方に順次シフトしつつ生成されたシフト出力が、バッファを介して所定の電圧レベル(ハイレベル)を有する走査信号Vse1として各走査ラインSLに印加される。

# [ 0 0 4 3 ]

(データドライバ)

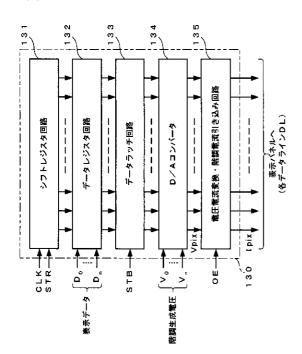

図3は、本実施形態に係る表示装置に適用されるデータドライバの要部構成を示すブロック図であり、図4は、本実施形態に係るデータドライバに適用される電圧電流変換・階調電流引き込み回路の一例を示す回路構成図である。

データドライバ130は、システムコントローラ150から供給されるデータ制御信号(出力イネーブル信号OE、データラッチ信号STB、サンプリングスタート信号STR、シフトクロック信号CLK等)に基づいて、表示信号生成回路160から供給される表示データを所定のタイミングで取り込んで保持し、所定のタイミングで該表示データに対応する階調電圧を電流成分に変換して、階調電流Ipixとして各データラインDLに供給する。

# [0044]

データドライバ130は、具体的には、図3に示すように、システムコントローラ150からデータ制御信号として供給されるシフトクロック信号CLKに基づいて、サンプリングスタート信号STRを順次シフトしつつシフト信号を出力するシフトレジスタ回路131と、該シフト信号の入力タイミングに基づいて、表示信号生成回路160から供給される1行分の表示データD。~Dn(デジタルデータ)を順次取り込むデータレジスタ回路132と、データラッチ信号STBに基づいて、データレジスタ回路132により取り込まれた1行分の表示データD。~Dnを保持するデータラッチ回路133と、図示を省略

30

40

50

した電源供給手段から供給される階調生成電圧V。~Vnに基づいて、上記保持された表示データD。~Dnを所定のアナログ信号電圧(階調電圧Vpix)に変換するD/Aコンバ・タ134と、アナログ信号電圧に変換された表示データに対応する階調電流Ipixを生成し、システムコントローラ150から供給される出力イネ・ブル信号OEに基づいて、該階調電流Ipixを表示パネル110に配設されたデータラインDLを介して供給する(本実施形態においては、階調電流Ipixとして負極性の信号電流を生成することにより、階調電流Ipixを引き込む)電圧電流変換・階調電流引き込み回路135と、を有して構成されている。

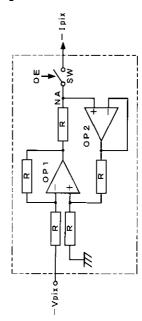

#### [0045]

ここで、電圧電流変換・階調電流引き込み回路135に適用可能であって、各データラインごとに接続される回路構成としては、例えば、図4に示すように、ハカカは、他方の入力は、Rを介して逆極性の階調電圧(・Vpix)が入力され、他方の入力端子(正入力(+))に、入力抵抗Rを介して基準電圧(接地電位)が入力されるとともに、出力端子が帰還抵抗Rを介して一方の入力端子(・)に接続されたオペアフプロア1と、オペアンプロア1の出力端子に出力抵抗Rを介して設けられた接点NAの電位が、一方の入力端子(+)に入力され、出力端子が他方の入力端子(+)に基準電圧(接地電位)を入力し、出力端子が帰還抵抗Rを介して一方の入力端子(+)に基準電圧(プロともに、出力抵抗Rを介してオペアンプロア150から供給されるオペアンプロと、接点NAに、システムコントローラ150から供給される出力イネ・ブル信号のと、接点NAに、システムコントローラ150から供給されるプロと、接点NAに、システムコントローラ150から供給されるプルに基づいてオン/オフ動作し、データラインDLへの階調電流Ipixの供給状態の本実施形態においては、生成される階調電流Ipixが負極性となるので、当該電流を引き込む)スイッチング手段SWと、を備えた構成を有している。

# [0046]

(・Vpix)に対して、・Ipix=(・Vpix)/Rからなる負極性の階調電流が生成され、出力イネーブル信号OEに基づいて、データラインDLに供給される。したがって、本実施形態に係るデータドライバ130によれば、表示データに応じた階調電圧から階調電流(負極性)に変換され、所定のタイミングでデータラインDLに供給されることにより、データラインDL側からデータドライバ130側へ引き込む方向に、表示データに対応する階調電流Ipixが流下するように制御される。

このような電圧電流変換・階調電流引き込み回路によれば、入力される負極性の階調電圧

# [ 0 0 4 7 ]

# (システムコントローラ)

システムコントローラ150は、走査ドライバ120及びデータドライバ130、電源ドライバ140の各々に対して、動作状態を制御する走査制御信号及びデータ制御信号(上述した走査シフトスタート信号SSTRや走査クロック信号SCLK、シフトスタート信号STRやシフトクロック信号CLK、ラッチ信号STB、出力イネ・ブル信号OE等)、電源制御信号(後述する電源スタート信号VSTR、電源クロック信号VCLK等)を出力することにより、各ドライバを所定のタイミングで動作させて走査信号Vse1及び階調電流Ipix、電源電圧Vscを生成、出力させ、後述する画素駆動回路における駆動制御動作(表示装置の駆動制御方法)を実行させて、所定の映像信号に基づく画像情報を表示パネル110に表示させる制御を行う。

#### [0048]

# (電源ドライバ)

電源ドライバ140は、システムコントローラ150から供給される電源制御信号に基づいて、上記走査ドライバ120により各行ごとの表示画素群が選択状態に設定されるタイミングに同期して、電源ラインVLにローレベルの電源電圧Vsc1(例えば、接地電位以下の電圧レベル)を印加することにより、電源ラインVLから表示画素(画素駆動回路)を介してデータドライバ130方向に、表示データに基づく階調電流Ipixに対応する書込電流(シンク電流)を引き込み、一方、走査ドライバ120により各行ごとの表示画素群が非選択状態に設定されるタイミングに同期して、電源ラインVLにハイレベルの

30

40

50

電源電圧Vschを印加することにより、電源ラインVLから表示画素(画素駆動回路)を介して有機EL素子OEL方向に、表示データに基づく階調電流Ipixに対応する駆動電流を流すように制御する。

### [0049]

電源ドライバ140は、図2に示すように、概略、上述した走査ドライバ120と同様に、シフトレジスタとバッファからなるシフトブロックSB1、SB2、・・・を、各電源ラインVLごとに対応して複数段備え、システムコントローラから供給される走査制御信号と同期する電源制御信号(電源スタート信号VSTR、電源クロック信号VCLK等)に基づいて、シフトレジスタにより表示パネル110の上方から下方に順次シフトしつつ生成されたシフト出力が、バッファを介して所定の電圧レベル(走査ドライバによる選択状態においてはローレベル、非選択状態においてはハイレベル)を有する電源電圧Vsc1、Vschとして各電源ラインVLに印加される。

#### [0050]

(表示信号生成回路)

表示信号生成回路160は、例えば、表示装置の外部から供給される映像信号から輝度階調信号成分を抽出し、表示パネル110の1行分ごとに表示データとしてデータドライバ130のデータレジスタ回路132に供給する。ここで、上記映像信号が、テレビ放送信号(コンポジット映像信号)のように、画像情報の表示タイミングを規定するタイミング信号成分を抽出してシステムコントローラ150に供給する機能のほか、タイミング信号成分を抽出してシステムコントローラ150に供給する機能を有するものであってもよい。この場合においては、上記システムコントローラ150は、表示信号生成回路160から供給されるタイミング信号に基づいて、走査ドライバ120やデータドライバ130、電源ドライバ140に対して供給する走査制御信号及びデータ制御信号、電源制御信号を生成する。

## [0051]

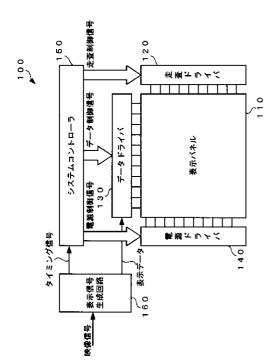

なお、本実施形態においては、表示パネル110の周辺に付設されるドライバとして、図1及び図2に示すように、走査ドライバ120、データドライバ130及び電源ドライバ140を個別に配置した構成について説明したが、本発明はこれに限定されるものではなく、上述したように、走査ドライバ120及び電源ドライバ140は、タイミングが同期する同等の制御信号(走査制御信号及び電源制御信号)に基づいて動作するので、例えば、図5に示すように、走査ドライバ120Aに、走査信号の生成、出力タイミングに同期して電源電圧Vscを供給する機能を有するように構成したものであってもよい。このような構成によれば、周辺回路の構成を簡素化することができる。

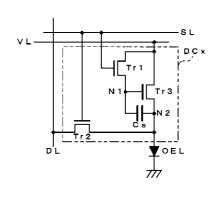

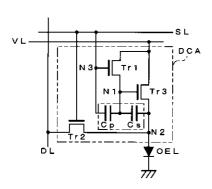

# [0052]

(表示画素:画素駆動回路)

次いで、上述した表示画素に適用される画素駆動回路の具体例について、図面を参照して説明する

まず、本実施形態に係る表示装置に適用可能な画素駆動回路の基本構成及びその動作について説明する。

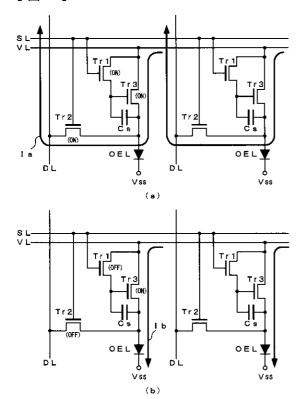

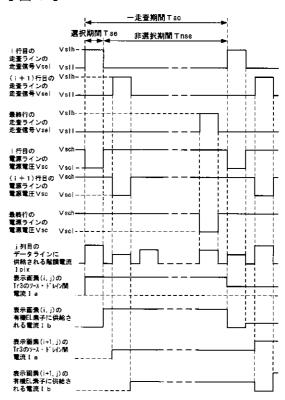

図6は、本発明に係る表示装置に適用可能な画素駆動回路の基本構成を示す回路構成図であり、図7は、本実施形態に適用可能な画素駆動回路の基本動作を示す概念図である。図8は、本実施形態に係る表示装置における画像情報の表示タイミングを示すタイミングチャ・トである。

# [0053]

基本構成に係る画素駆動回路 D C x は、例えば、図 6 に示すように、表示パネル 1 1 0 に相互に直交するように配設された走査ライン S L とデータライン D L との各交点近傍に、ゲート端子が走査ライン S L に、ソース端子が電源ライン V L に、ドレイン端子が接点 N 1 に各々接続された薄膜トランジスタ(第 2 のスイッチング素子) T r 1 と、ゲート端子が走査ライン S L に、ソース端子及びドレイン端子がデータライン D L 及び接点 N 2 に各々接続された薄膜トランジスタ(第 3 のスイッチング素子) T r 2 と、ゲート端子が接点

N1に、ソース端子及びドレイン端子が電源ラインVL及び接点N2に各々接続された薄膜トランジスタ(第1のスイッチング素子)Tr3と、接点N1及び接点N2間に接続されたコンデンサ(第2の電荷蓄積手段、容量素子)Csと、を備えた構成を有し、有機EL素子OELのアノード端子が接点N2に、カソード端子が接地電位に各々接続されている。ここで、コンデンサCsは、薄膜トランジスタTr3のゲート・ソース間に形成される寄生容量であってもよい。なお、上記薄膜トランジスタTr1及びTr2を含む回路構成は、本発明に係る発光制御手段を構成し、薄膜トランジスタTr3を含む回路構成は、本発明に係る発光制御手段を構成する。

## [0054]

このような構成を有する画素駆動回路における発光素子(有機EL素子)の発光駆動制御は、例えば、図8に示すように、一走査期間Tscを1サイクルとして、該一走査期間Tsc内に、特定の走査ラインに接続された表示画素群を選択して表示データに対応する信号電流を書き込み、信号電圧として保持する書込動作期間(又は、表示画素の選択期間)Tseと、該書込動作期間Tseに書き込み、保持された信号電圧に基づいて、上記表示データに応じた駆動電流を有機EL素子に供給して、所定の輝度階調で発光動作させる発光動作期間(又は、表示画素の非選択期間)Tnseと、を設定することにより実行される(Tsc=Tse+Tnse)。ここで、各行ごとに設定される書込動作期間Tseは、相互に時間的な重なりが生じないように設定される。

## [0055]

(書込動作期間:選択期間)

すなわち、表示画素への書込動作(選択期間Tse)においては、図8に示すように、まず、走査ドライバ120から特定の行(i行目)の走査ラインSLに対して、ハイレベルの走査信号Vsel(Vslh)が印加されるとともに、電源ドライバ140から当該行(i行目)の電源ラインVLに対して、ローレベルの電源電圧Vsclが印加される。また、このタイミングに同期して、データドライバ130により取り込まれた当該行(i行目)の表示データに対応する負極性の階調電流(‐Ipix)が各データラインDLに供給される。

#### [0056]

これにより、画素駆動回路 D C x を構成する薄膜トランジスタTr1及びTr2がオン動作して、ローレベルの電源電圧 V s c l が接点 N 1 (すなわち、薄膜トランジスタTr3 のゲート端子及びコンデンサ C s の一端)に印加されるとともに、データライン D L を介して負極性の階調電流(- I p i x )が引き込む動作が行われることにより、ローレベルの電源電圧 V s c l よりも低電位の電圧レベルが接点 N 2 (すなわち、薄膜トランジスタTr3のソース端子及びコンデンサ C s の他端)に印加される。

## [0057]

このように、接点N1及びN2間(薄膜トランジスタTr3のゲート・ソース間)に電位差が生じることにより、薄膜トランジスタTr3がオン動作して、図7(a)に示すように、電源ラインVLから薄膜トランジスタTr3、接点N2、薄膜トランジスタTr2、データラインDLを介して、データドライバ130に、階調電流Ipixに対応した書込電流Iaが流下する。

このとき、コンデンサ C s には、接点 N 1 及び N 2 間(薄膜トランジスタのTr3のゲート・ソース間)に生じた電位差に対応する電荷が蓄積され、電圧成分として保持される(充電される)。また、電源ラインVLには、接地電位以下の電圧レベルを有する電源電圧 V s c 1 が印加され、さらに、書込電流 I a がデータライン方向に流下するように制御されていることから、有機 E L 素子 O E L のアノード端子(接点 N 2 )に印加される電位はカソード端子の電位(接地電位)よりも低くなり、有機 E L 素子 O E L に逆バイアス電圧が印加されていることになるため、有機 E L 素子 O E L には駆動電流が流れず、発光動作は行われない。

#### [0058]

(発光動作期間:非選択期間)

20

30

次いで、書込動作期間(選択期間Tse)終了後の有機EL素子の発光動作(非選択期間Tse)においては、図8に示すように、走査ドライバ120から特定の行( i 行目)の走査ラインSLに対して、ローレベルの走査信号Vse1(Vs11)が印加されるとともに、電源ドライバ140から当該行( i 行目)の電源ラインVLに対して、ハイレベルの電源電圧Vschが印加される。また、このタイミングに同期して、データドライバ130による階調電流の引き込み動作が停止される。

[0059]

これにより、画素駆動回路 D C x を構成する薄膜トランジスタTr1及びTr2がオフ動作して、接点N1(すなわち、薄膜トランジスタTr3のゲート端子及びコンデンサCsの一端)への電源電圧Vscの印加が遮断されるとともに、接点N2(すなわち、薄膜トランジスタTr3のソース端子及びコンデンサCsの他端)へのデータドライバ130による階調電流の引き込み動作に起因する電圧レベルの印加が遮断されるので、コンデンサCsは、上述した書込動作において蓄積された電荷を保持する。

[0060]

このように、コンデンサ C s が書込動作時の充電電圧を保持することにより、接点 N 1 及び N 2 間 (薄膜トランジスタの T r 3 のゲート・ソース間)の電位差が保持されることになり、薄膜トランジスタ T r 3 はオン状態を維持する。また、電源ライン V L には、接地電位よりも高い電圧レベルを有する電源電圧 V s c h が印加されるので、有機 E L 素子 O E L のアノード端子(接点 N 2 )に印加される電位はカソード端子の電位(接地電位)よりも高くなる。

[0061]

したがって、図7(b)に示すように、電源ラインVLから薄膜トランジスタTr3、接点N2を介して、有機EL素子OELに順バイアス方向に所定の駆動電流Ibが流れ、有機EL素子OELが発光する。ここで、コンデンサCsにより保持される電位差(充電圧)は、薄膜トランジスタTr3において階調電流Ipixに対応した書込電流Iaを流下させる場合の電位差に相当するので、有機EL素子OELに流下する駆動電流Ibは、上記書込電流Iaと同等の電流値を有することになる。これにより、選択期間Tse後の非選択期間Tnseにおいては、選択期間Tseに書き込まれた表示データ(階調電流)に対応する電圧成分に基づいて、薄膜トランジスタTr3を介して、駆動電流が継続的に供給されることになり、有機EL素子OELは表示データに対応する輝度階調で発光する動作を継続する。

[0062]

そして、上述した一連の動作を、図8に示すように、表示パネルを構成する全ての行の表示画素群について順次繰り返し実行することにより、表示パネル1画面分の表示データが書き込まれて、所定の輝度階調で発光し、所望の画像情報が表示される。

ここで、本実施形態に係る画素駆動回路に適用される薄膜トランジスタTr1~Tr3については、特に限定するものではないが、薄膜トランジスタTr1~Tr3は全てnチャネル型トランジスタにて構成することができるため、nチャネル型アモルファスシリコンTFTを良好に適用することができる。その場合、すでに確立された製造技術を適用して、動作特性の安定した画素駆動回路を比較的安価に製造することができる。

[ 0 0 6 3 ]

また、上述したような回路構成を有する画素駆動回路によれば、表示画質の高精細化に伴って、表示データの書込動作を行う際の各表示画素(各行ごと)の選択時間が短く設定された場合であっても、表示データの輝度階調に応じた比較的大きな電流値を有する階調電流をデータドライバにより引き込むように流下させて、発光素子を発光動作させるための発光制御トランジスタのゲート・ソース間に付設されたコンデンサCs (薄膜トランジスタTr3の寄生容量)に階調電流に対応した電圧を良好に充電する(書き込む)ことができるので、表示データの書き込み速度を向上させて表示応答特性の改善を図ることができる。

[0064]

50

10

20

30

30

40

50

ところで、上述したような回路構成を有する画素駆動回路 D C x を各表示画素に適用した場合、画素駆動回路を介して発光素子に供給される駆動電流 I b は、当該表示画素の選択期間 T s e に、データドライバ 1 3 0 により設定される階調電流 I p i x に基づいて画素駆動回路 D C x に流下される書込電流 I a (より詳しくは、書込電流 I a によりコンデンサ C s に蓄積される電荷量)に依存する。

そのため、一定の選択期間Tseに比較的大きな書込電流Iaを流下させて、最高位の輝度階調に対応した電圧を良好に書き込めるように動作条件や回路特性を設定すると、コンデンサCsに蓄積される電荷量の最小値(すなわち、最下位の輝度階調に対応してコンデンサCsに充電される電圧)が比較的大きな値となってしまい、最下位又は比較的下位の輝度階調で発光素子を発光動作させる際に、発光素子に供給される駆動電流Ibの最小値が比較的大きく設定されてしまうという制約があった。ここで、最下位又は比較的下位の輝度階調で発光素子を発光動作させる場合、本来的には、輝度階調に対応したより小さな駆動電流Ibを供給すればよい。

# [0065]

そこで、本発明においては、発光素子への駆動電流の供給を制御する発光制御トランジスタ (薄膜トランジスタTr3)のゲート電圧を制御する駆動制御トランジスタ (薄膜トランジスタTr1)のゲート・ソース間に付設されるコンデンサ (寄生容量)に充電される電圧を利用して、発光素子 (有機 E L 素子 O E L )に供給される駆動電流を輝度階調に応じたより小さい電流値になるように設定して、各表示画素への階調電流の書込動作を高速化しつつ、発光動作時の消費電力を抑制するようにしたことを特徴としている。

#### [0066]

#### (具体実施例)

以下、本発明に係る表示装置に適用可能な画素駆動回路の具体実施例について、図面を参照しつつ具体的に説明する。

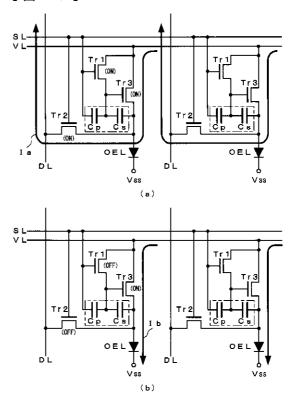

図9は、本発明に係る表示装置に適用可能な画素駆動回路の具体実施例を示す回路構成図であり、図10は、本実施例に係る画素駆動回路における駆動制御動作(表示装置の駆動制御方法)を示す概念図である。なお、ここでは、上述した画素駆動回路と同等の構成及び動作については、図6乃至図8を参照しながら簡略化して説明する。

# [0067]

図9に示すように、本発明に係る表示装置に適用可能な画素駆動回路DCAは、上述した図6に示した回路構成(薄膜トランジスタTr1、Tr2、Tr3及びコンデンサCsからなる回路)を基本として、有機EL素子OELへの駆動電流Ibの供給を制御する薄膜トランジスタTr1のゲート端子(接点N3)とソース端子(接点N1)間に接続されたコンデンサ(第1の電荷蓄積手段、容量素子)Cpを備えた構成を有している。

# [0068]

ここで、コンデンサ C p は、薄膜トランジスタTr1のゲート・ソース間に形成される寄生容量であってもよいし、それに加えてゲート・ソース間に更に、容量素子を付加するようにしてもよい。この場合、薄膜トランジスタTr1のゲート・ソース間に形成される寄生容量(コンデンサ C p )は、一般に、薄膜トランジスタの素子特性に影響を及ぼし、画素駆動回路の動作特性を劣化させるため、極力小さくなるように設計することが望ましいものであるが、本発明においては、後述するように、この寄生容量による影響(書込動作時に充電される電圧)を積極的に利用するために、容量値(蓄積容量)をある程度大きく、具体的には、寄生容量が薄膜トランジスタTr3に付設されるコンデンサ(寄生容量+付加蓄積容量)Csに対して、無視できない程度に大きい容量値(本実施例においては、同等の値;Cp Cs)となるように設計した構成を有している。

### [0069]

このような構成を有する画素駆動回路DCAにおける書込動作(選択期間Tse)は、図10(a)に示すように、走査ドライバ120によりハイレベルの走査信号Vselが走査ラインSLに印加されることにより薄膜トランジスタTr1及びTr2がオン動作する

30

40

50

。このとき、データドライバにより表示データに応じた負極性の階調電流(- Ipix)がデータラインDLに供給されるとともに、電源ドライバ140によりローレベルの電源電圧 Vsclが電源ライン VLに印加されることにより、電源ライン VLから薄膜トランジスタ Tr3、接点 N2、薄膜トランジスタ Tr2を介して、データライン DLに上記階調電流に応じた書込電流 Iaが引き込まれるように流下する。

[0070]

このとき、薄膜トランジスタTr3のゲート電圧(接点N1の電位)Vgは、薄膜トランジスタTr3のドレイン・ソース間(電流路)に書込電流Iaを流下させるために必要な電圧値になり、このゲート電圧Vgが薄膜トランジスタTr3のゲート・ソース間に設けられたコンデンサ(寄生容量+付加蓄積容量)Csに充電される。また、薄膜トランジスタTr1のゲート電圧(ハイレベルの走査信号Vse1)とソース電圧(薄膜トランジスタTr1のゲート電圧Vg)間の電位差がコンデンサ(寄生容量)Cpに電圧成分として充電される。なお、この状態では、電源ラインVLに接地電位以下の電圧レベル(ローレベル)を有するまのでは、電源ラインVLに接地電位以下の電圧レベル(ローレベル)を有するように制御されていることから、有機EL素子OELには逆バイアス電圧が印加されることになり、有機EL素子OELは発光しない。

[0071]

次いで、書込動作期間(選択期間Tse)後の有機EL素子の発光動作(非選択期間Tnse)においては、図10(b)に示すように、走査ドライバ120によりローレベルの走査信号Vse1が走査ラインSLに印加されることにより薄膜トランジスタTr1及びTr2がオフ動作する。このとき、電源ドライバ140によりハイレベルの電源電圧Vschが電源ラインVLに印加され、また、このタイミングに同期して、データドライバ130による階調電流の引き込み動作が停止される。

[0072]

一方、コンデンサ C s に充電された電圧が保持されることにより、薄膜トランジスタT r 3 はオン状態を維持し、また、電源ラインVLには、接地電位よりも高い電圧レベル(ハイレベル)を有する電源電圧Vschが印加されるので、有機EL素子OELには順方向にバイアス電圧が印加されることになり、薄膜トランジスタT r 3 により供給される駆動電流 I b に基づいて、表示データに応じた輝度階調で有機EL素子OELが発光する。このとき、有機EL素子OELに供給される駆動電流 I b は、上記書込動作において画素駆動回路(薄膜トランジスタT r 3 )を流下した書込電流 I a から、薄膜トランジスタT r 1 のゲート・ソース間に設けられたコンデンサ(寄生容量) C p に充電された電圧に対応する電流分、減少した電流値に設定される。

[ 0 0 7 3 ]

ここで、本実施例に示した画素駆動回路に適用されるコンデンサ(寄生容量) Cs、Cpの設計条件について、上述した画素駆動回路の基本構成と本実施例に係る回路構成とを比較して具体的に説明する。

上述したような画素駆動回路において、コンデンサCpを薄膜トランジスタTr1のゲート・ソース間に形成される寄生容量(以下、説明の都合上、「寄生容量Cp」と記す)とし、コンデンサCsを薄膜トランジスタTr3のゲート=・ソース間に形成される寄生容量と付加蓄積容量の和からなる容量成分(以下、説明の都合上、「寄生容量Cs」と記す)として、例えば、書込動作時にハイレベルの走査信号Vse1(Vs1h)として5Vの信号レベルが印加されるとともに、階調電流Ipixの引き込みにより書込電流Iaが画素駆動回路を流下して薄膜トランジスタTr3のソース端子(接点N2)に・15Vの信号レベルが印加されているものとする。

また、書込動作後の発光動作時にローレベルの走査信号 V s e 1 ( V s 1 1 ) として - 2 0 V の信号レベルが印加されるとともに、階調電流 I p i x の引き込みが停止されることにより書込電流 I a の流下が遮断されて、薄膜トランジスタ T r 3 のソース端子に 5 V の信号レベルが保持されているものとする。

[0074]

この場合、書込動作時に上記各寄生容量 C p 及び C s に蓄積された電荷(第 2 の電荷、第 1 の電荷)は、電荷保存の法則により、発光動作時においても保持されることから、次式 ( 1 ) に示す関係が得られる。

Cp(Vg1-Vslh)+Cs(Vg1-Vs1)

$= C p (V g 2 - V s 1 1) + C s (V g 2 - V s 2) \cdot \cdot \cdot (1)$

ここで、 V g 1 は書込動作時における接点 N 1 の電位(薄膜トランジスタTr 3 のゲート電圧)であり、 V g 2 は発光動作時における接点 N 1 の電位である。また、 V s 1 h は書込動作時におけるハイレベルの走査信号であり、 V s 1 l は発光動作時におけるローレベルの走査信号である。 V s 1 は書込動作時における接点 N 2 の電位(薄膜トランジスタTr 3 のソース電圧)であり、 V s 2 は発光動作時における接点 N 2 の電位である。

[0075]

上記式(1)により、書込動作時と発光動作時における薄膜トランジスタTr3のゲート電圧Vgの変化量 Vgは、次式(2)のように表すことができる。

Vg=(Cp× Vsel+Cs× Vs)/(Cs+Cp) ・・・(2) ここで、 Vg=Vg1-Vg2、 Vs=Vs1-Vs2、 Vsel=Vslh-V sllである。

[0076]

上記式(2)において、画素駆動回路が、上述した図6、図7に示したような基本構成に係る回路構成を有している場合、すなわち、薄膜トランジスタTr1の寄生容量Cpを極力抑制するために、薄膜トランジスタTr3の寄生容量Csに比較して十分小さい値になるように設定した場合(Cs Cp)には、次式(3)のように表すことができる。

$Vg (Cs \times Vs)/(Cs)$

= V s · · · (3)

[0077]

したがって、書込動作時と発光動作時における薄膜トランジスタTr3のゲート電圧Vgの変化量とソース電圧Vsの変化量は略同等となるので、次式(4)に示すように、薄膜トランジスタTr3のゲート・ソース間電圧Vgsも変化しないことになる。

$Vgs = Vg - Vs 0 \cdots (4)$

このことから、書込動作時に薄膜トランジスタTr3のゲート端子に書き込まれた電圧(寄生容量Csに充電された電圧)が、発光動作時においてもそのまま印加されることになり、発光動作時に有機EL素子OELに供給される駆動電流Ibは、書込動作時に画素駆動回路を流下する書込電流Iaと同等になる。

そのため、最下位の輝度階調を有する表示データを表示画素に書き込みを行う場合、微小な駆動電流 Ibと同等の書込電流 Iaを表示画素に流下することになり、書込動作に必要とする時間が長くなるという問題があった。

[0078]

一方、上記式(2)において、画素駆動回路が、上述した図9、図10に示したような本実施例に係る回路構成を有している場合、すなわち、薄膜トランジスタTr1の寄生容量 C p をある程度大きくして、薄膜トランジスタTr3の寄生容量 C s に比較して無視できない程度に大きな値になるように設定した場合(例えば、C s C p ) には、上記式(4)は次式(5)のように書き換えることができる。

V g s = V g - V s

= (Cpx Vsel+Csx Vs)/(Cs+Cp) - Vs

= (Cpx Vsel+Csx Vs-Csx Vs-Cpx Vs)/(Cs+Cp)

= ( C p x V s e l - C p x V s ) / ( C s + C p )

$= Cp / (Cs + Cp) \times (Vsel - Vs)$  · · · (5)

[0079]

ここで、上述したように、ハイレベルの走査信号 V s e l ( V s l h ) を 5 V、ローレベルの走査信号 V s e l ( V s l l )を - 2 0 Vと設定すると、走査信号 V s e l の電圧変

10

20

30

40

30

40

50

化 V s e l は、次式(6)のように算出することができ、 V s e l > 0 の関係が得られる。

Vsel=Vslh-Vsll=5-(-20)=25・・・(6)また、書込動作時における薄膜トランジスタTr3のソース電圧(接点N2の電位) Vs1を-15V、発光動作時における薄膜トランジスタTr3のソース電圧Vs2を5Vと設定すると、ソース電圧Vs電圧変化Vsは、次式(7)のように算出することができ

### [0800]

Vs < 0 の関係が得られる。

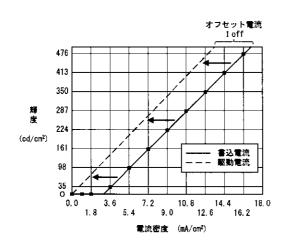

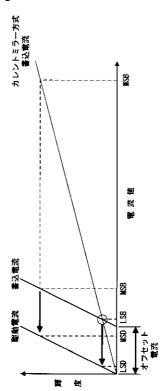

このことから、 Vgs>0の関係が得られ、これは、書込動作時に薄膜トランジスタT r3のゲート端子に書き込まれた電圧の変化に比較して、発光動作時に印加される電圧の変化が小さいことを意味し、すなわち、図11に示すように、発光動作時に有機EL素子に流下する駆動電流Ibを、書込動作時に画素駆動回路に流下する書込電流Iaよりも所定電流分(以下、便宜的に「オフセット電流」と記す)、小さくすることができることを意味する。ここで、図11は、本実施例に係る画素駆動回路における書込電流と駆動電流間の変化量を示すグラフである。

# [0081]

ここで、上述した本実施例に係る画素駆動回路(図9)と従来技術に示したカレントミラー回路構成を有する画素駆動回路(図13(b)参照)における書込動作時の書込電流について、図面を参照して比較検討する。

図 1 2 は、本実施例に係る画素駆動回路とカレントミラー回路構成を有する画素駆動回路 における書込電流の電流値の比較を示すグラフである。

図12に示すように、まず、書込動作(選択期間)において、各表示画素に表示データを書き込む際に、本実施例及びカレントミラー構成を有する画素駆動回路のいずれにおいても、表示装置の所定の表示応答特性(応答速度)を実現するために要求される、最下位の輝度階調に対応した書込電流Iaの電流値(第1の電流値)をLSBとし、その場合に発光素子に供給される駆動電流Ibの電流値をMSBとし、その場合に発光素子に供給される駆動電流Ibの電流値をMSDとする。

### [0082]

この場合、本実施例に係る画素駆動回路においては、図11に示したように、発光動作時に有機EL素子OELに供給すべき駆動電流Ibに対して、一定のオフセット電流Ioff分加算した電流値(第2の電流値)を有する書込電流Iaを、書込動作時に表示画素に流下させればよい。すなわち、図12に示すように、最下位の輝度階調を有する表示データを書き込む場合には、電流値LSB(=LSD+Ioff)を有する書込電流Iaを、データラインDLを介して電流を引き込むようにすればよい。また、表示データの輝度階調をm階調とし、最上位の輝度階調を有する表示データを書き込む場合には、電流値MSB(=MSD+Ioff=mxLSD+Ioff)を有する書込電流Iaを有する書込電流 Iaを、画素駆動回路DCAに流下するように、データドライバにより階調電流Ipixを生成して、データラインDLを介して電流を引き込むようにすればよい。

#### [0083]

このようにした場合、前述のカレントミラー構成を有する画素駆動回路においては、図12に示すように、有機EL素子に供給すべき駆動電流Ibに対するデータラインDLに印加する電流の比率はカレントミラー回路により規定される電流比率kで一定であるのに対し、本実施例の構成とした場合には、発光動作時に有機EL素子OELに供給すべき駆動電流Ibに対するデータラインDLを介して引き込む書込電流Iaの増加比率は、オフセット電流Ioffは一定であるため、下位の輝度階調時、すなわち駆動電流Ibが小さいときほど増加率が大きくなる。ここで、データラインを所定の電圧まで充電するに要する時間は流す電流値に反比例するため、表示データの書込動作時(選択期間)には、比較的

30

40

50

大きな電流値を有する書込電流を流して、特に下位の輝度階調時の書込動作に要する時間を短縮することができ、且つ、上位の輝度階調時に書込電流 I a が過大となることを抑制して、表示装置の消費電力の増加を抑制することができる。

### [0084]

このように、本実施例に係る画素駆動回路を適用した表示装置によれば、発光素子の発光動作に要する駆動電流に対して一定のオフセット電流を付加した電流値を有する比較的下位の輝度階調に対応した小さい駆動電流を発光素子に供給する場合であっても、データラインに存在する配線容量等を短短で充電して、特に低位の輝度階調表示データの書込動作に要する時間を短縮することができるので、各表示画素への階調電流の書き込み動作を実行することができるので、各表示画素への階調電流の書き込み動作を実行することができることなく、所望の輝度階調に応じた電流値で書き込み動作を実行することができる。ことができる。あるいは、表示データの書込動作に係る電流の増加を抑制して表示装置の消費電力の増加を抑制することができる。

#### [0085]

なお、上述した実施例においては、薄膜トランジスタTr1のゲート・ソース間に接続されるコンデンサ(寄生容量)Cpとして、薄膜トランジスタTr1のゲート・ソース間に接続されるコンデンサCsに比較して無視できないほど大きく設定した場合(具体的には、略同等に設定した場合)について説明したが、本発明はこれに限定されるものではなく、例えば、コンデンサCpをコンデンサCsに比較して、より大きくなるように設定(Cs Cp)したものであってもよい。

#### [0086]

すなわち、このようなコンデンサ C p の蓄積容量の設定によれば、コンデンサ C s における蓄積容量を無視することができるので、上記式(5)は、次式(8)のように書き換えることができる。

Vgs = Vg - Vs

= C p / ( C s + C p ) x ( V s e l - V s )

V s e 1 - V s · · · (8)

これにより、薄膜トランジスタTr3のゲート・ソース間電圧Vgsは、コンデンサCs 及びCpに依存しない電圧変化を示すことになる。したがって、薄膜トランジスタTr3 に形成されるコンデンサ(寄生容量)Cs等に起因する、発光制御トランジスタの経時的 な特性変動の影響を受けることなく、上記オフセット電流を電圧設計のみで簡易に設定す ることができる画素駆動回路を構成することができる。

# [0087]

また、上述した実施形態及び実施例においては、画素駆動回路として3個の薄膜トランジスタを備えた回路構成を示して説明したが、本発明はこの実施形態形態に限定されるものではなく、電流指定方式を適用した画素駆動回路を備えた表示装置であって、発光素子への駆動電流の供給を制御する発光制御トランジスタ、及び、該発光制御トランジスタのゲート電圧を制御する駆動制御トランジスタを有し、表示データに応じた書込電流を各制御トランジスタに付設されたコンデンサ(又は、寄生容量)に電圧成分として充電した後、該充電電圧に応じて、上記発光制御トランジスタをオン動作させて駆動電流を供給して、発光素子を所定の発光輝度で発光させるものであれば、他の回路構成を有するものであってもよい。

# [0088]

### 【発明の効果】

以上説明したように、本発明に係る表示装置及びその駆動制御方法によれば、有機EL素子や発光ダイオード等のように、供給される電流値に応じて所定の輝度で自己発光する発 光素子をマトリクス状に配列してなる表示パネルを備えたディスプレイにおいて、各表示 画素ごとに付設された画素駆動回路により、表示画素への書込電流よりも一定のオフセット電流分小さい駆動電流を発光素子に供給するように構成されているので、最下位の輝度階調を有する表示データを書き込む場合であっても、比較的大きな電流を流してデータライン及び画素駆動回路に付設された容量成分を充電することができ、書込動作に係る所要時間を短縮することができる。

[0089]

また、所定の表示データに対応した輝度で発光するための駆動電流に対して、一定のオフセット電流を付加(加算)した書込電流を各表示画素に流せばよいので、駆動電流の所定数倍の書込電流を必要とするカレントミラー方式を適用した画素駆動回路に比較して、書込電流を相対的に抑制することができ、表示装置の消費電力を抑制することもできる。

【図面の簡単な説明】

【図1】本発明に係る表示装置の全体構成の一例を示す概略ブロック図である。

【図2】本実施形態に係る表示装置に適用される表示パネルの一例を示す概略構成図である。

【 図 3 】 本実 施 形 態 に 係 る 表 示 装 置 に 適 用 さ れ る デ ー タ ド ラ イ バ の 要 部 構 成 を 示 す ブ ロ ッ ク 図 で あ る 。

【図4】本実施形態に係るデータドライバに適用される電圧/電流変換回路の一例を示す 回路構成図である。

【図 5 】本発明に係る表示装置に適用される走査ドライバの他の例を示す概略構成図である。

【 図 6 】 本 発 明 に 係 る 表 示 装 置 に 適 用 可 能 な 画 素 駆 動 回 路 の 基 本 構 成 を 示 す 回 路 構 成 図 で あ る 。

【図7】本実施形態に適用可能な画素駆動回路の基本動作を示す概念図である。

【図8】本実施形態に係る表示装置における画像情報の表示タイミングを示すタイミング チャ・トである。

【図9】本発明に係る表示装置に適用可能な画素駆動回路の具体実施例を示す回路構成図である。

【図 1 0 】本実施例に係る画素駆動回路における駆動制御動作(表示装置の駆動制御方法)を示す概念図である。

【図 1 1 】本実施例に係る画素駆動回路における書込電流と駆動電流間の変化量を示すグラフである。

【図12】本実施例に係る画素駆動回路とカレントミラー回路構成を有する画素駆動回路 における書込電流の電流値の比較を示すグラフである。

【図13】有機EL素子を備えた発光素子型ディスプレイにおける、従来技術の各表示画素の構成例を示す等価回路である。

【符号の説明】

D C A 画素駆動回路

SL 走査ライン

DL データライン

VL 電源ライン

Tr1~Tr3 薄膜トランジスタ

C s 、 C p コンデンサ

O E L 有機 E L 素子

1 0 0 表示装置

1 1 0 表示パネル

120 走査ドライバ

130 データドライバ

1 4 0 電源ドライバ

150 システムコントローラ

160 表示信号生成回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図8】

【図9】

【図10】

【図11】

【図12】

# 【図13】

# フロントページの続き

F ターム(参考) 5C080 AA06 BB05 CC03 DD08 DD26 EE19 EE29 FF11 FF12 JJ02 JJ03 JJ04

| 专利名称(译)        | 显示装置和显示装置的驱动控制方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | <u>JP2004012897A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2004-01-15 |  |  |  |

| 申请号            | JP2002167390                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2002-06-07 |  |  |  |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

| [标]发明人         | 山田裕康<br>武居学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |

| 发明人            | 山田 裕康<br>武居 学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| IPC分类号         | H01L51/50 G09G3/00 G09G3/20 G09G3/30 G09G3/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |  |

| CPC分类号         | G09G3/325 G09G2300/0417 G09G2300/0819 G09G2300/0847 G09G2300/0852 G09G2300/0866 G09G2310/027 G09G2320/0223 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |  |

| FI分类号          | G09G3/30.J G09G3/20.611.A G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/3241 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |  |

| F-TERM分类号      | 3K007/AB03 3K007/AB11 3K007/AB17 3K007/AB18 3K007/DB03 3K007/GA04 5C080/AA06 5C080 /BB05 5C080/CC03 5C080/DD08 5C080/DD26 5C080/EE19 5C080/EE29 5C080/FF11 5C080/FF12 5C080/JJ02 5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC14 3K107 /CC21 3K107/CC33 3K107/CC35 3K107/CC45 3K107/EE03 3K107/HH04 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AC04 5C380/BA28 5C380/BA29 5C380/BA38 5C380 /BA39 5C380/BB21 5C380/BD01 5C380/CA04 5C380/CA08 5C380/CA17 5C380/CA32 5C380/CA34 5C380/CB01 5C380/CB26 5C380/CC02 5C380/CC14 5C380/CC26 5C380/CC33 5C380/CC41 5C380 /CC52 5C380/CC62 5C380/CD012 5C380/CD013 5C380/CD014 5C380/CD023 5C380/CB19 5C380 /CF07 5C380/CF09 5C380/CF22 5C380/CF27 5C380/CF41 5C380/DA02 5C380/DA06 |         |            |  |  |  |

| 其他公开文献         | JP3972359B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |

# 摘要(译)

要解决的问题:在通过电流指定方法控制发光元件发光的显示器中,具有简单且廉价的电路构造,同时抑制显示面板的功耗并抑制显示面板的发光亮度的降低。 提供一种显示装置和用于该显示装置的驱动控制方法。 解决方案:每个显示器都设置在包括显示面板的显示器中,在该显示面板中以矩阵形式排列了发光元件,例如有机EL元件和根据提供的电流值以预定亮度自发光的发光二极管。 附接至每个像素的发光元件的像素驱动电路被配置为通过恒定的偏置电流将小于写电流的驱动电流提供给显示像素到显示元件。 [选型图]图1