(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5236156号

(P5236156)

(45) 発行日 平成25年7月17日(2013.7.17)

(24) 登録日 平成25年4月5日(2013.4.5)

(51) Int.CI.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 7 O J |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 4 1 D |

|             |              |                  | G09G | 3/20 | 6 2 4 B |

|             |              |                  | G09G | 3/20 | 6 2 1 A |

請求項の数 2 (全 11 頁) 最終頁に続く

(21) 出願番号

特願2005-364023 (P2005-364023)

(22) 出願日

平成17年12月16日 (2005.12.16)

(65) 公開番号

特開2007-4114 (P2007-4114A)

(43) 公開日

平成19年1月11日 (2007.1.11)

審査請求日

平成19年5月2日 (2007.5.2)

(31) 優先権主張番号

10-2005-0053120

(32) 優先日

平成17年6月20日 (2005.6.20)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーグ、ヨ

ウイーテロ 128

(74) 代理人 100110423

弁理士 曾我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

最終頁に続く

(54) 【発明の名称】有機発光ダイオード表示装置

(57) 【特許請求の範囲】

【請求項 1】

複数の画素を有し、前記複数の画素それぞれが電流により発光する有機発光ダイオードと、前記有機発光ダイオードを駆動する有機発光ダイオード駆動回路を備える有機発光ダイオードパネルと、

前記有機発光ダイオードパネルのゲートラインにスキャンパルスを供給するゲート駆動回路と、

前記有機発光ダイオードパネルのデータラインにデータ電圧を供給するデータ駆動回路と、

前記有機発光ダイオードパネルのリセットラインにリセットパルスを供給するリセット駆動回路と、

を備える有機発光ダイオード表示装置において、

前記有機発光ダイオード駆動回路は、

前記ゲートラインからのスキャンパルスに応答して、前記データラインからのデータ電圧を第2トランジスタに接続された第1ノードに供給する第1トランジスタと、

前記第1ノードと前記有機発光ダイオードとの間に接続され、前記第1ノード上のデータ電圧により、前記有機発光ダイオードに流れる電流を制御する前記第2トランジスタと、

前記リセットラインからのリセットパルスに応答して、前記第1ノードのデータ電圧を放電させる第3トランジスタと

10

20

を備え、

前記データ電圧は、第1低電位の基準電圧から上昇し、

前記スキャンパルス及び前記リセットパルスは、前記第1低電位の基準電圧より低い第2低電位の基準電圧から上昇し、

前記第3トランジスタは、ネガティブのストレス電圧を前記第1ノードに供給し、

前記スキャンパルス及び前記リセットパルスの第2低電位の基準電圧の調節を通じて、前記第1ノードのネガティブのバイアスストレスの大きさが調節され、

前記ネガティブのストレス電圧は、前記スキャンパルス及び前記リセットパルスの第2低電位の基準電圧と同一電圧に設定される

ことを特徴とする有機発光ダイオード表示装置。

10

#### 【請求項2】

前記リセットパルスは、前記スキャンパルスの発生時点より1/2フレーム期間だけ遅延された時点に発生することを特徴とする請求項1に記載の有機発光ダイオード表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、有機発光ダイオード表示装置に係り、特に有機発光ダイオード駆動素子の特性変化を防止できる有機発光ダイオード駆動回路を利用した有機発光ダイオード表示装置に関する。

20

##### 【背景技術】

##### 【0002】

最近、陰極線管の短所である重量及び体積を減少できる各種の平板表示装置が注目されている。このような平板表示装置としては、液晶表示装置（LCD：Liquid Crystal Display）、電界放出表示装置（FED：Field Emission Display）、プラズマディスプレイパネル（PDP：Plasma Display Panel）及び発光ダイオード（以下、“LED”という。）（LED：Light-Emitting Diode）表示装置などがある。

##### 【0003】

そのうち、LED表示装置は、電子と正孔との再結合により蛍光体を発光させるLEDを利用し、前記LEDは、蛍光体として無機化合物を使用する無機LED表示装置と、有機化合物を使用する有機LED（以下、“OLED”という（OLED：Organic Light-Emitting Diode））表示装置とに区分される。前記OLED表示装置は、低電圧駆動、自己発光、薄膜型、広い視野角、速い応答速度及び高いコントラストなどの多くの長所を有しているので、次世代の表示装置として期待されている。

30

##### 【0004】

OLEDは、通常、負極と正極との間に積層された電子注入層、電子輸送層、発光層、正孔輸送層及び正孔注入層から構成される。前記OLEDでは、正極と負極との間に所定の電圧を印加する場合、負極から発生した電子が電子注入層及び電子輸送層を通じて発光層側に移動し、正極から発生した正孔が正孔注入層及び正孔輸送層を通じて発光層側に移動する。これにより、発光層では、電子輸送層及び正孔輸送層から供給された電子と正孔との再結合により光を放出する。

40

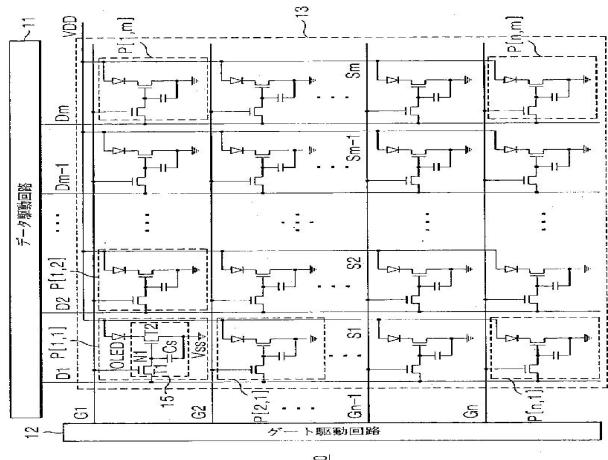

##### 【0005】

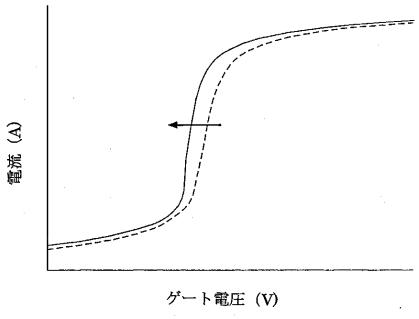

図1に示したように、前記OLEDを利用するアクティブマトリックスタイプのOLED表示装置10は、n個のゲートラインG1～Gn（ただし、nは正の整数）とm個のデータラインD1～Dm（ただし、mは正の整数）との交差により定義された領域にn×mマトリックス形態に配列されたn×m個の画素P[i,j]（ただし、P[i,j]はi行、j列に位置した画素、iはnより小さいか、または同じ正の整数、jはmより小さいか、または同じ正の整数）を含むOLEDパネル13、OLEDパネル13のゲートラインG1～Gnを駆動するゲート駆動回路12、OLEDパネル13のデータラインD1～Dmを駆動するデータ駆動回路11、及びデータラインD1～Dmと並べて配列されて、

50

高電位の電源電圧  $V_{DD}$  を各画素  $P[i, j]$  に供給する  $m$  個の電源電圧供給ライン  $S_1 \sim S_m$  を備える。

**【0006】**

ゲート駆動回路 12 は、ゲートライン  $G_1 \sim G_n$  にスキャンパルスを供給して、ゲートライン  $G_1 \sim G_n$  を順次に駆動する。

**【0007】**

データ駆動回路 11 は、外部から入力されたデジタルデータ電圧をアナログデータ電圧に変換する。そして、データ駆動回路 11 は、アナログデータ電圧をスキャンパルスが供給される度にデータライン  $D_1 \sim D_m$  に供給する。

**【0008】**

画素  $P[i, j]$  は、それぞれ第  $i$  ゲートライン  $G_i$  にスキャンパルスが供給されるとき、第  $j$  データライン  $D_j$  からのデータ電圧を供給されてそのデータ電圧に相応する光を発生させる。

**【0009】**

このために、各画素  $P[i, j]$  は、第  $j$  電源電圧供給ライン  $S_j$  に正極が接続された OLED と、OLED を駆動するために、OLED の負極に接続されると共に、第  $i$  ゲートライン  $G_i$  及び第  $j$  データライン  $D_j$  と接続され、低電位の電源電圧  $V_{SS}$  が供給される OLED 駆動回路 15 を備える。

**【0010】**

前記 OLED 駆動回路 15 は、第  $i$  ゲートライン  $G_i$  からのスキャンパルスに応答して、第  $j$  データライン  $D_j$  からのデータ電圧を第 1 ノード  $N_1$  に供給する第 1 トランジスタ  $T_1$ 、第 1 ノード  $N_1$  の電圧に応答して OLED に流れる電流量を制御する第 2 トランジスタ  $T_2$ 、及び第 1 ノード  $N_1$  上の電圧が充電されるストレージキャパシタ  $C_s$  を備える。

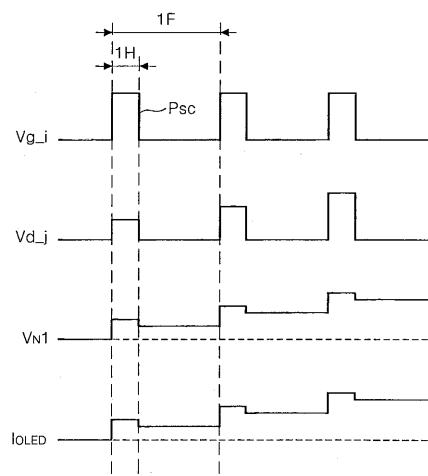

**【0011】**

この OLED 駆動回路 15 の駆動波形は、図 2 に示すようである。図 2において、“ $1F$ ”は 1 フレーム期間、“ $1H$ ”は 1 水平期間、“ $V_{g_i}$ ”は第  $i$  ゲートライン  $G_i$  から供給されるゲート電圧、“ $P_{sc}$ ”はスキャンパルス、“ $V_{d_j}$ ”は第  $j$  データライン  $D_j$  から供給されるデータ電圧、“ $P_{rs}$ ”はリセットパルス、“ $V_{N1}$ ”は第 1 ノード  $N_1$  上の電圧（以下、第 1 ノード電圧  $V_{N1}$  という。），“ $I_{OLED}$ ”は OLED を通じて流れる電流を表す。

**【0012】**

図 1 及び図 2 に示すように、第 1 トランジスタ  $T_1$  は、ゲートライン  $G_i$  を通じてスキャンパルスが供給されれば、ターンオンされてデータライン  $D_j$  から供給されたデータ電圧  $V_d$  を第 1 ノード  $N_1$  に供給する。第 1 ノード  $N_1$  に供給されたデータ電圧  $V_d$  は、ストレージキャパシタ  $C_s$  に充電されると共に第 2 トランジスタ  $T_2$  のゲート端子に供給される。このように供給されるデータ電圧  $V_d$  により第 2 トランジスタ  $T_2$  がターンオンされれば、OLED を通じて電流が流れる。このとき、OLED を通じて流れる電流は、高電位の電源電圧  $V_{DD}$  により発生し、電流量は、第 2 トランジスタ  $T_2$  に印加されるデータ電圧  $V_d$  の大きさに比例する。そして、第 1 トランジスタ  $T_1$  がターンオフされても、第 2 トランジスタ  $T_2$  は、ストレージキャパシタ  $C_s$  による第 1 ノード電圧  $V_{N1}$  によりターンオン状態を維持して、次のフレームのデータ電圧  $V_d$  が供給されるまで OLED を経由して流れる電流量を制御する。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0013】**

前記 OLED 駆動回路 15 には、次のような問題点がある。

**【0014】**

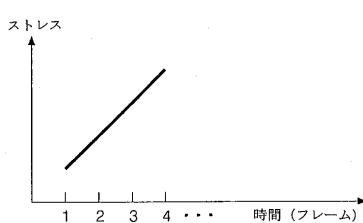

図 2 に示すように、OLED を駆動する第 2 トランジスタ  $T_2$  のゲート電極には、ポジティブ（正）のデータ電圧  $V_d$  が長時間印加される。このように長時間印加されるポジテ

10

20

30

40

50

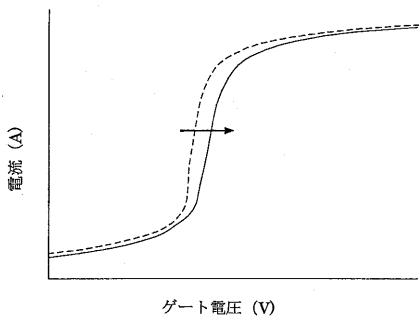

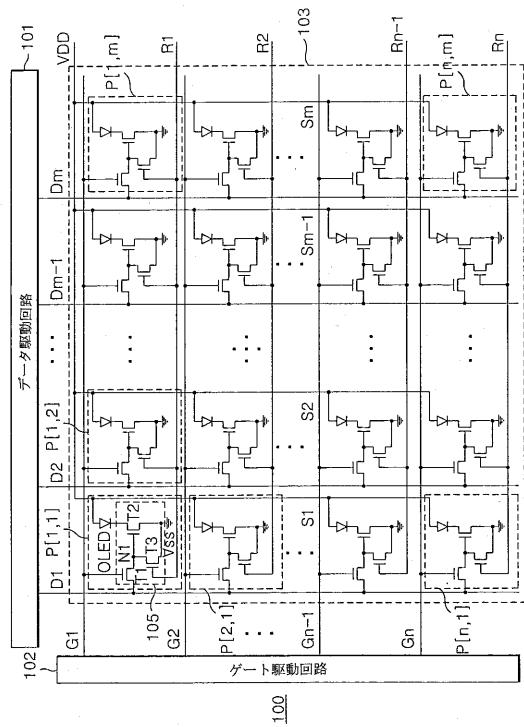

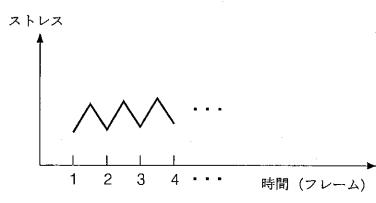

イブのデータ電圧  $V_d$  により、第 2 トランジスタ T 2 には、図 3 に示すように累積ゲートバイアスストレスが発生し、このような累積ゲートバイアスストレスにより、第 2 トランジスタ T 2 には、図 4 A に示すように劣化による特性変化が発生する。図 4 A は、ポジティブのゲートバイアスストレスによるトランジスタの特性変化を示し、図 4 B は、ネガティブ(負)のゲートバイアスストレスによるトランジスタの特性変化を示し、図 4 A 及び図 4 B で矢印は、トランジスタのしきい電圧の移動を表す。このようにゲートバイアスストレスにより発生する第 2 トランジスタ T 2 のような OLE D 駆動素子の特性変化は、OLE D に流れる電流量を変化させて OLE D 駆動回路 15 の動作の信頼性を低下させ、さらに、OLE D 表示装置の動作についての信頼性を低下させる。

## 【0015】

10

本発明は、かかる問題点を解決するためになされたものであり、OLE D 駆動素子の特性変化を防止して OLE D 駆動回路の動作の信頼性を確保し、さらに、OLE D 表示装置の動作の信頼性を確保できる OLE D 駆動回路を利用した OLE D 表示装置を提供することを目的としている。

## 【課題を解決するための手段】

## 【0016】

20

前記の目的を達成するために、本発明による OLE D 表示装置は、複数の画素を有し、前記複数の画素それぞれが電流により発光する有機発光ダイオードと、前記有機発光ダイオードを駆動する有機発光ダイオード駆動回路を備える有機発光ダイオードパネルと、前記有機発光ダイオードパネルのゲートラインにスキャンパルスを供給するゲート駆動回路と、前記有機発光ダイオードパネルのデータラインにデータ電圧を供給するデータ駆動回路と、前記有機発光ダイオードパネルのリセットラインにリセットパルスを供給するリセット駆動回路と、を備える有機発光ダイオード表示装置において、前記有機発光ダイオード駆動回路は、前記ゲートラインからのスキャンパルスに応答して、前記データラインからのデータ電圧を第 2 トランジスタに接続された第 1 ノードに供給する第 1 トランジスタと、前記第 1 のノードと前記有機発光ダイオードとの間に接続され、前記第 1 ノード上のデータ電圧により、前記有機発光ダイオードに流れる電流を制御する前記第 2 トランジスタと、前記リセットラインからのリセットパルスに応答して、前記第 1 ノードのデータ電圧を放電させる第 3 トランジスタとを備え、前記データ電圧は、第 1 低電位の基準電圧から上昇し、前記スキャンパルス及び前記リセットパルスは、前記第 1 低電位の基準電圧より低い第 2 低電位の基準電圧から上昇し、前記第 3 トランジスタは、ネガティブのストレス電圧を前記第 1 ノードに供給し、前記スキャンパルス及び前記リセットパルスの第 2 低電位の基準電圧の調節を通じて、前記第 1 ノードのネガティブのバイアスストレスの大きさが調節され、前記ネガティブのストレス電圧は、前記スキャンパルス及び前記リセットパルスの第 2 低電位の基準電圧と同一電圧に設定される。

30

## 【0017】

本発明による OLE D 表示装置は、互いに交差するデータライン及びゲートラインと、前記ゲートラインにスキャンパルスを供給するゲート駆動回路と、前記データラインにビデオデータ電圧を供給するデータ駆動回路と、電流により発光する有機発光ダイオードと、前記有機発光ダイオードを駆動する前記構成の OLE D 駆動回路とを備える。

40

## 【発明の効果】

## 【0019】

本発明による OLE D 駆動回路及び OLE D 表示装置は、リセットパルスに応答して OLE D 駆動素子の制御ノードを放電させる第 3 トランジスタを備えて、OLE D 駆動素子の劣化による特性変化を防止できるので動作の信頼性が向上する。さらに、データ電圧の低電位の基準電圧よりスキャンパルス及びリセットパルスの低電位の基準電圧を低くする駆動波形を供給して、さらに向上した OLE D 駆動回路の動作の信頼性を確保できる。

## 【発明を実施するための最良の形態】

## 【0020】

以下、図 5 ~ 図 9 B を参照して、本発明の望ましい実施の形態について説明する。

50

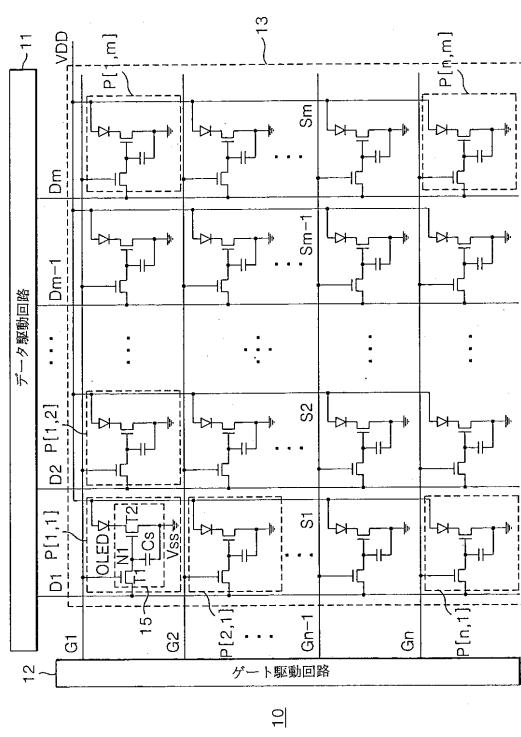

## 【0021】

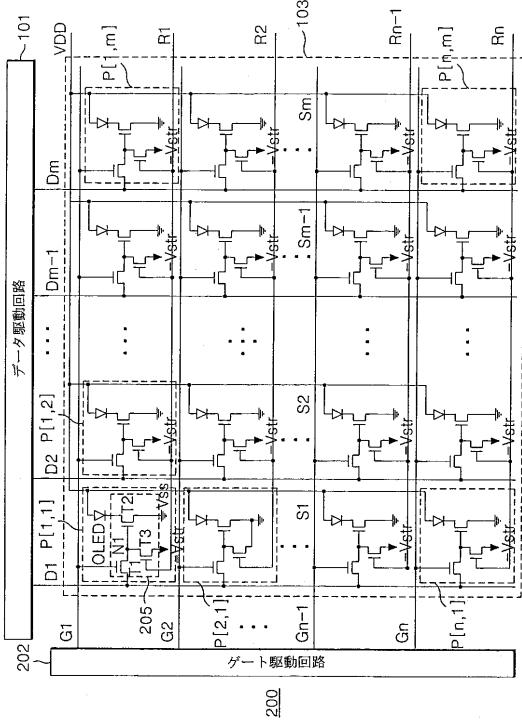

図5に示すように、本発明の実施形態によるOLED表示装置は、n個のゲートラインG<sub>1</sub>～G<sub>n</sub>（ただし、nは正の整数）とm個のデータラインD<sub>1</sub>～D<sub>m</sub>（ただし、mは正の整数）との交差により定義された領域にn×mマトリックス形態に配列されたn×m個の画素P[i,j]（ただし、P[i,j]はi行、j列に位置した画素、iはnより小さいか、または同じ正の整数、jはmより小さいか、または同じ正の整数）を含むOLEDパネル103、OLEDパネル103のゲートラインG<sub>1</sub>～G<sub>n</sub>を駆動するゲート駆動回路102、OLEDパネル103のデータラインD<sub>1</sub>～D<sub>m</sub>を駆動するデータ駆動回路101、データラインD<sub>1</sub>～D<sub>m</sub>と並べて配列されて、高電位の電源電圧VDDを各画素P[i,j]に供給するm個の電源電圧供給ラインS<sub>1</sub>～S<sub>m</sub>、及びゲートラインG<sub>1</sub>～G<sub>n</sub>と並行に配列されて、リセット信号を各画素P[i,j]に供給するリセットラインR<sub>1</sub>～R<sub>n</sub>を備える。

10

## 【0022】

ゲート駆動回路102は、ゲートラインG<sub>1</sub>～G<sub>n</sub>にスキャンパルスを供給して、ゲートラインG<sub>1</sub>～G<sub>n</sub>を順次駆動する。

## 【0023】

データ駆動回路101は、外部から入力されたデジタルデータ電圧をアナログデータ電圧に変換する。そして、データ駆動回路101は、スキャンパルスが供給される度に、アナログデータ電圧をデータラインD<sub>1</sub>～D<sub>m</sub>に供給する。

20

## 【0024】

画素P[i,j]は、それぞれ第iゲートラインG<sub>i</sub>にスキャンパルスP<sub>s</sub><sub>c</sub>が供給されるとき、第jデータラインD<sub>j</sub>からのデータ電圧V<sub>d</sub><sub>\_j</sub>が供給されて、そのデータ電圧に相応する光を発生させる。

## 【0025】

このために、各画素P[i,j]は、第j電源電圧供給ラインS<sub>j</sub>に正極が接続されたOLEDと、OLEDを駆動するために、OLEDの負極に接続されると共に、第iゲートラインG<sub>i</sub>、第jデータラインD<sub>j</sub>及び第iリセットラインR<sub>i</sub>と接続され、低電位の電源電圧V<sub>s</sub><sub>s</sub>が供給されるOLED駆動回路105とを備える。

## 【0026】

前記OLED駆動回路105は、第iゲートラインG<sub>i</sub>からのスキャンパルスに応答して、第jデータラインD<sub>j</sub>からのデータ電圧を第1ノードN<sub>1</sub>に供給する第1トランジスタT<sub>1</sub>、第1ノードN<sub>1</sub>上の電圧に応答してOLEDに流れる電流量を制御する第2トランジスタT<sub>2</sub>、及び第iリセットラインR<sub>i</sub>からのリセットパルスに応答して第1ノードN<sub>1</sub>を放電させる第3トランジスタT<sub>3</sub>を備える。トランジスタT<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>は、非晶質のシリコンタイプまたはポリシリコンタイプのトランジスタで具現される。

30

## 【0027】

このOLED駆動回路105の駆動波形は、図6に示すようである。図6において、“1F”は1フレーム期間、“1H”は1水平期間、“V<sub>g</sub><sub>\_i</sub>”は第iゲートラインG<sub>i</sub>から供給されるゲート電圧、“P<sub>s</sub><sub>c</sub>”はスキャンパルス、“V<sub>d</sub><sub>\_j</sub>”は第jデータラインD<sub>j</sub>から供給されるデータ電圧、“V<sub>r</sub><sub>\_i</sub>”は第iリセットラインR<sub>i</sub>から供給されるリセット電圧、“P<sub>r</sub><sub>s</sub>”はリセットパルス、“V<sub>N</sub><sub>1</sub>”は第1ノードN<sub>1</sub>上の電圧、“I<sub>OLED</sub>”はOLEDを通じて流れる電流を表す。

40

## 【0028】

図5及び図6に示すように、第1トランジスタT<sub>1</sub>は、第iゲートラインG<sub>i</sub>を通じてスキャンパルスP<sub>s</sub><sub>c</sub>が供給されれば、ターンオンされて第jデータラインD<sub>j</sub>から供給されたデータ電圧V<sub>d</sub>を第1ノードN<sub>1</sub>に供給する。第1ノードN<sub>1</sub>に供給されたデータ電圧V<sub>d</sub>は、第2トランジスタT<sub>2</sub>のゲート端子に供給される。このように供給されるデータ電圧V<sub>d</sub>により第2トランジスタT<sub>2</sub>がターンオンされれば、OLEDを通じて電流が流れる。このとき、OLEDを通じて流れる電流は、高電位の電源電圧VDDにより発生し、その電流量は、第2トランジスタT<sub>2</sub>のゲート電極に印加されるデータ電圧V<sub>d</sub>の

50

大きさに比例する。そして、第1トランジスタT1がターンオフされても、データ電圧Vdによる第1ノードN1上の電圧VN1は、リセットパルスPrsにより第3トランジスタT3がターンオンされて第1ノードN1が放電されるまで維持する。したがって、第2トランジスタT2も、リセットパルスPrsが供給されるまでターンオン状態を維持する。このとき、第iリセットラインRiから供給されるリセットパルスPrsは、フレーム期間ごとにスキャンパルスPscと1/2フレーム期間の時間差をおいて発生する。

#### 【0029】

リセットパルスPrsは、リセット駆動回路(図示せず)から発生する。リセット駆動回路は、ゲート駆動回路102と同様に、シフトレジスタを備えてゲート駆動回路102からのスキャンパルスに続いてリセットパルスPrsを発生させ、そのリセットパルスPrsを順次シフトさせる。10

#### 【0030】

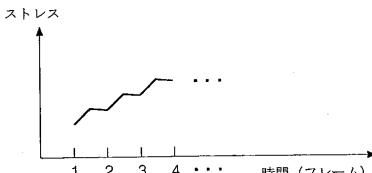

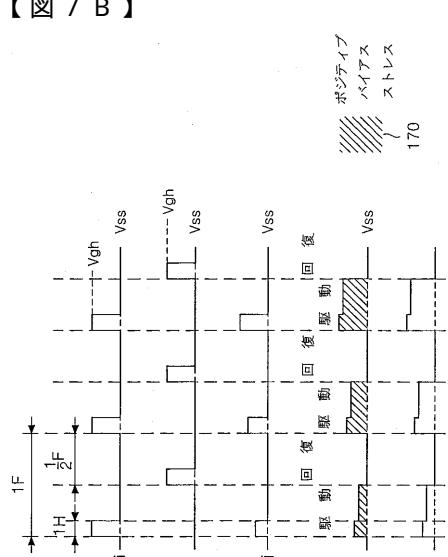

このようにスキャンパルスPscと1/2フレーム期間の時間差をおいて発生するリセットパルスPrsにより、第3トランジスタT3を利用して第1ノードN1を放電することによって、第2トランジスタT2は、1/2フレーム期間のストレス回復期間を有する。すなわち、図7Aに示すように、1/2フレーム期間のターンオン期間に第2トランジスタT2に累積されて増加するゲートバイアスストレスは、ターンオフされる1/2フレーム期間だけ減少する。

#### 【0031】

つまり、第2トランジスタT2、すなわちOLED駆動素子は、1/2フレーム期間にターンオン状態を維持した後、1/2フレーム期間にはターンオフ状態を維持する。したがって、図7Bに示すように、ターンオン状態であるときに発生したOLED駆動素子の特性変化は、ターンオフ状態であるときに回復期間に回復されるので、OLED駆動素子の劣化による特性変化を防止して、OLED駆動回路の動作についての信頼性を向上させる。20

#### 【0032】

図7Bに示すように、ポジティブのバイアスストレスは、斜線で示した領域170のように1/2フレーム期間に次第に第2トランジスタT2のゲート電極に累積される。本発明は、残りの1/2フレーム期間の回復期間に第2トランジスタT2のゲート電圧を放電させて、ストレスによる第2トランジスタT2の劣化を防止できる。30

#### 【0033】

回復区間にOLED駆動素子のゲート電極にソース及びデータ電極より相対的に低い電源を印加する場合には、ネガティブのバイアスストレス効果をさらに向上させる。すなわち、ネガティブのバイアスストレス効果をさらに向上させて、OLED駆動素子の特性回復を向上させる。一般的にゲートバイアスストレスは、印加された電圧の大きさに比例であり、これによりOLED駆動素子の低電位の基準電圧より低い第2低電位の基準電圧を利用して、ネガティブのバイアスストレス効果を強化して、全体的に駆動による特性変化による信頼性を非常に向上させる。

#### 【0034】

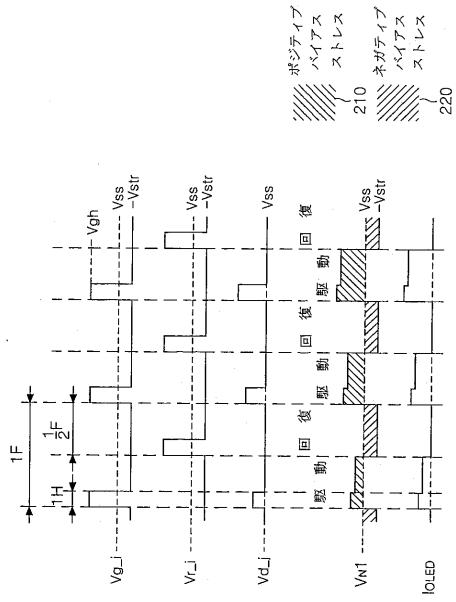

図8は、本発明の他の実施の形態によるOLED表示装置のブロック図である。40

#### 【0035】

図8に示すように、OLED表示装置200は、データ駆動回路101、ゲート駆動回路202、OLEDパネル103及びOLED駆動回路205を備える。複数のリセットラインR1～Rnは、複数のゲートラインG1～Gnと並行に設ける。リセットラインR1～Rnは、第3トランジスタT3のソース端子に接続される。ネガティブのストレス電圧-Vstrは、リセットラインR1～Rnを通じて第3トランジスタT3のソース端子に供給される。ネガティブのストレス電圧-Vstrは、低電位の基準電圧より低くてもよいものとする。ゲート駆動回路202は、ゲートハイ電圧Vghとネガティブのストレス電圧-Vstrとの間でスイングするスキャンパルスを発生させる。リセット電圧は、ネガティブのストレス電圧-Vstrから上昇するが、データ電圧は、ネガティブのスト50

レス電圧 - V<sub>s tr</sub> より高い低電位の電源電圧 V<sub>SS</sub> から上昇する。

**【0036】**

図 9 A 及び図 9 B は、図 6 の OLE D 駆動回路の駆動波形、及びそれに比べて回復効果を向上させて信頼性を強化した場合の駆動波形を示す図面である。この駆動波形は、ゲート電圧 V<sub>g\_i</sub> の波形及びリセット電圧 V<sub>r\_i</sub> の波形の低電位の基準電圧が、データ電圧 V<sub>d\_g</sub> の低電位の基準電圧より低いことを特徴とする。OLE D 駆動素子の制御ノード（第 1 ノード）に印加される累積バイアスストレスは、斜線で示した領域 210, 220 のようである。図 9 B の駆動波形により OLE D 駆動素子が駆動する場合、累積バイアスストレスを最小化して特性変化を最小化できる。また、データ電圧 V<sub>d\_g</sub> の低電位の基準電圧に比べて相対的に低い第 2 低電位の基準電圧（すなわち、ゲート電圧とリセット電圧との低電位の基準電圧）の調節を通じて、ネガティブのバイアスストレスの大きさを調節でき、それを通じて累積バイアスストレスを最小化できる。

10

**【0037】**

前述したように、本発明の実施形態による OLE D 駆動回路は、リセットパルスに応答して OLE D 駆動素子の制御ノードを放電させる第 3 トランジスタを備えて、OLE D 駆動素子の劣化による特性変化を防止できるので動作の信頼性が向上する。さらに、データ電圧の低電位の基準電圧よりリセットパルス及びリセットパルスの低電位の基準電圧を低くする駆動波形を供給して、さらに向上した OLE D 駆動回路の動作の信頼性を確保できる。

20

**【0038】**

以上説明した内容を通じて、当業者であれば、本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であるということが分かる。したがって、本発明の技術的範囲は、明細書の詳細な説明に記載された内容に限定されるものではなく、特許請求の範囲により決まらねばならない。

20

**【産業上の利用可能性】**

**【0039】**

本発明は、OLE D 表示装置関連の技術分野に適用可能である。

**【図面の簡単な説明】**

**【0040】**

【図 1】従来の OLE D 表示装置を示す図面である。

30

【図 2】図 1 の OLE D 駆動回路の駆動波形を示す図面である。

【図 3】電圧印加時間による累積ゲートバイアスストレスを示す図面である。

【図 4 A】ポジティブのゲートバイアスストレスによる素子の特性変化を示す図面である。

。

【図 4 B】ネガティブのゲートバイアスストレスによる素子の特性変化を示す図面である。

。

【図 5】本発明の実施形態による OLE D 表示装置を示す図面である。

【図 6】図 5 の OLE D 駆動回路の駆動波形を示す図面である。

【図 7 A】図 5 の OLE D 駆動回路によるゲートバイアスストレスの減少を示す図面である。

40

【図 7 B】図 7 A のポジティブのバイアスストレスをもたらす駆動波形を示す図面である。

。

【図 8】本発明の他の実施形態による OLE D 表示装置を示す図面である。

【図 9 A】図 8 の OLE D 駆動回路によるゲートバイアスストレスの減少を示す図面である。

【図 9 B】図 9 A のポジティブのバイアスストレスをもたらす駆動波形を示す図面である。

。

**【符号の説明】**

**【0041】**

100, 200 OLE D 表示装置、101, 201 データ駆動回路、102, 20

50

## 2 ゲート駆動回路。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図7A】

【図7B】

【図8】

【図9 A】

【図9 B】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 623 C

G 09 G 3/20 622 C

H 05 B 33/14 A

(72)発明者 スヨン・ユン

大韓民国、キョンギ - ド、ゴヤン - シ、ドキヤン - グ、ヘンシン・2 - ドン、ムウォン・ミヨル・

10 - ダンジ、ソグワン・アパートメント 1010 - 802

(72)発明者 ミンドゥ・チョン

大韓民国、ソウル、クワンジン - グ、ジョンコク・3 - ドン 174 - 1

審査官 小川 浩史

(56)参考文献 特開2004-102278 (JP, A)

特開2004-118132 (JP, A)

特開2002-91376 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 20 - 3 / 38

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光二极管显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP5236156B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2013-07-17 |

| 申请号            | JP2005364023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2005-12-16 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | スヨン・ユン<br>ミンドウ・チョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | スヨン・ユン<br>ミンドウ・チョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3233 G09G3/3291 G09G2300/043 G09G2300/0847 G09G2310/0254 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.J G09G3/20.670.J G09G3/20.641.D G09G3/20.624.B G09G3/20.621.A G09G3/20.623.C<br>G09G3/20.622.C H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/<br>/BB01 3K107/CC21 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 5C080/AA06 5C080/BB05<br>5C080/DD29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380<br>/AB06 5C380/AB22 5C380/AB23 5C380/BB22 5C380/BB23 5C380/BD01 5C380/BD02 5C380/BD07<br>5C380/CA04 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CB31 5C380/CC02 5C380/CC26 5C380<br>/CC33 5C380/CC38 5C380/CC62 5C380/CC63 5C380/CD012 5C380/CD073 5C380/CF07 5C380<br>/DA02 5C380/DA06 5C380/DA20 5C380/DA47 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 审查员(译)         | 小川博                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 1020050053120 2005-06-20 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2007004114A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

**摘要(译)**

要解决的问题：提供用于有机发光二极管的驱动电路，其可以防止有机发光二极管驱动元件的特性变化，使用有机发光二极管的显示装置和有机发光二极管的驱动方法显示设备。解决方案：根据本发明的有机发光二极管驱动电路包括：有机发光二极管，其利用电流发光；第一开关，其响应于扫描脉冲向第一节点提供数据电压；第二开关，通过第一节点上的数据电压控制在有机发光二极管中流动的电流，以及控制第一节点上的数据电压的应力补偿电路。

Z