(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5171807号

(P5171807)

(45) 発行日 平成25年3月27日(2013.3.27)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 2 4 B |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 4 1 D |

|             |              |                  | G09G | 3/20 | 6 1 1 H |

|             |              |                  | G09G | 3/20 | 6 4 2 A |

請求項の数 8 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2009-502428 (P2009-502428)

(86) (22) 出願日 平成19年10月1日 (2007.10.1)

(86) 国際出願番号 PCT/JP2007/069184

(87) 国際公開番号 WO2008/108024

(87) 国際公開日 平成20年9月12日 (2008.9.12)

審査請求日 平成21年5月11日 (2009.5.11)

(31) 優先権主張番号 特願2007-58021 (P2007-58021)

(32) 優先日 平成19年3月8日 (2007.3.8)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100104695

弁理士 島田 明宏

(74) 代理人 100121348

弁理士 川原 健児

(72) 発明者 岸 宣孝

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】表示装置およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電流駆動型の表示装置であって、

複数の走査線と複数のデータ線との各交差点に対応して配置された複数の画素回路と、

走査信号出力回路と、

表示信号出力回路とを備え、

前記画素回路は、それぞれ、

2本の電源配線間に設けられた電気光学素子と、

前記電気光学素子と共に前記電源配線間に直列に設けられた駆動素子と、

前記駆動素子の制御端子と前記データ線とに接続され、前記走査線に接続された制御端子を有する第1のスイッチング素子と、

前記駆動素子の制御端子と一方の導通端子との間に設けられた第2のスイッチング素子と、

前記電気光学素子および前記駆動素子と共に前記電源配線間に直列に設けられた第3のスイッチング素子と、

一端が前記駆動素子の制御端子に接続された容量とを含み、

前記表示信号出力回路は、複数のアナログバッファと、前記データ線ごとに設けられた複数の補正用容量および複数のスイッチ回路とを含み、

前記走査信号出力回路は、書き込み対象の画素回路について、閾値補正期間において、前記第1および第2のスイッチング素子を導通状態、前記第3のスイッチング素子を非導

通状態に設定することにより、前記駆動素子の閾値電圧に前記駆動素子の制御端子の電圧を近づけて当該電圧を前記データ線に出力させ、次に前記第2のスイッチング素子を非導通状態に変化させ、さらに前記第1のスイッチング素子を非導通状態、前記第3のスイッチング素子を導通状態に変化させる制御を行い、

前記スイッチ回路を用いて、前記補正用容量の一方の電極を前記データ線に接続し、他方の電極に所定の固定電圧を印加するか、前記補正用容量の一方の電極を前記アナログバッファを介して前記データ線に接続し、他方の電極に表示データに対応したデータ電圧を印加するかを切り替えることにより、前記表示信号出力回路は、前記第2のスイッチング素子が導通状態にあるときの前記データ線の電圧に基づき、前記第2のスイッチング素子が非導通状態に変化した後に、前記データ電圧に前記駆動素子の閾値電圧に対応した補正電圧を加算または減算した電圧を前記データ線に印加し、

前記閾値補正期間は、前記駆動素子の制御端子の電圧が前記駆動素子の閾値電圧に到達する前に終了することを特徴とする、表示装置。

#### 【請求項2】

前記駆動素子および前記第1～第3のスイッチング素子は薄膜トランジスタであり、

前記第1および第3のスイッチング素子のうち一方はPチャネル型、他方はNチャネル型であり、両者の制御端子は共通の配線に接続されていることを特徴とする、請求項1に記載の表示装置。

#### 【請求項3】

前記駆動素子および前記第1～第3のスイッチング素子は薄膜トランジスタであり、

前記第2および第3のスイッチング素子のうち一方はPチャネル型、他方はNチャネル型であり、両者の制御端子は共通の配線に接続されていることを特徴とする、請求項1に記載の表示装置。

#### 【請求項4】

前記駆動素子はPチャネル型のエンハンスマント型トランジスタであり、

前記走査信号出力回路によって選択された画素回路は、前記電源配線の電圧のうち高いほうから前記補正電圧の絶対値を減算した電圧を前記データ線に出力することを特徴とする、請求項1に記載の表示装置。

#### 【請求項5】

前記駆動素子はNチャネル型のエンハンスマント型トランジスタであり、

前記走査信号出力回路によって選択された画素回路は、前記電源配線の電圧のうち低いほうに前記補正電圧の絶対値を加算した電圧を前記データ線に出力することを特徴とする、請求項1に記載の表示装置。

#### 【請求項6】

前記表示信号出力回路は、前記第1のスイッチング素子の導通期間の一部において、前記データ線に所定の固定電圧を印加することを特徴とする、請求項1に記載の表示装置。

#### 【請求項7】

前記アナログバッファは、複数の前記データ線ごとに設けられていることを特徴とする、請求項1に記載の表示装置。

#### 【請求項8】

複数の走査線と複数のデータ線との各交差点に対応して配置され、それぞれが、2本の電源配線間に設けられた電気光学素子と、前記電気光学素子と共に前記電源配線間に直列に設けられた駆動素子と、前記駆動素子の制御端子と前記データ線とに接続され、前記走査線に接続された制御端子を有する第1のスイッチング素子と、前記駆動素子の制御端子と一方の導通端子との間に設けられた第2のスイッチング素子と、前記電気光学素子および前記駆動素子と共に前記電源配線間に直列に設けられた第3のスイッチング素子と、一端が前記駆動素子の制御端子に接続された容量とを含む複数の画素回路を備えた表示装置の駆動方法であって、

書き込み対象の画素回路について、閾値補正期間において、前記第1および第2のスイッチング素子を導通状態、前記第3のスイッチング素子を非導通状態に設定することによ

10

20

30

40

50

り、前記駆動素子の閾値電圧に前記駆動素子の制御端子の電圧を近づけて当該電圧を前記データ線に出力させ、次に前記第2のスイッチング素子を非導通状態に変化させ、さらに前記第1のスイッチング素子を非導通状態、前記第3のスイッチング素子を導通状態に変化させるステップと、

複数のアナログバッファと、前記データ線ごとに設けられた複数の補正用容量および複数のスイッチ回路とを含む表示信号出力回路において、前記スイッチ回路を用いて、前記補正用容量の一方の電極を前記データ線に接続し、他方の電極に所定の固定電圧を印加するか、前記補正用容量の一方の電極を前記アナログバッファを介して前記データ線に接続し、他方の電極に表示データに対応したデータ電圧を印加するかを切り替えることにより、前記第2のスイッチング素子が導通状態にあるときの前記データ線の電圧に基づき、前記第2のスイッチング素子が非導通状態に変化した後に、前記データ電圧に前記駆動素子の閾値電圧に対応した補正電圧を加算または減算した電圧を前記データ線に印加するステップとを備え、

前記閾値補正期間は、前記駆動素子の制御端子の電圧が前記駆動素子の閾値電圧に到達する前に終了することを特徴とする、表示装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、表示装置に関し、より特定的には、有機ELディスプレイやFEDなどの電流駆動素子を用いた表示装置およびその駆動方法に関する。

##### 【背景技術】

##### 【0002】

近年、薄型、軽量、高速応答可能な表示装置の需要が高まり、これに伴い、有機EL(Electro Luminescence)ディスプレイやFED(Field Emission Display)に関する研究開発が活発に行われている。

##### 【0003】

有機ELディスプレイに含まれる有機EL素子は、印加される電圧が高く、流れる電流が多いほど、高い輝度で発光する。ところが、有機EL素子の輝度と電圧の関係は、駆動時間や周辺温度などの影響を受けて容易に変動する。このため、有機ELディスプレイに電圧制御型の駆動方式を適用すると、有機EL素子の輝度のばらつきを抑えることが非常に困難になる。これに対して、有機EL素子の輝度は電流にはほぼ比例し、この比例関係は周辺温度などの外的要因の影響を受けにくい。したがって、有機ELディスプレイには電流制御型の駆動方式を適用することが好ましい。

##### 【0004】

一方、表示装置の画素回路や駆動回路は、アモルファスシリコン、低温多結晶シリコン、CG(Continuous Grain)シリコンなどで構成されたTFT(Thin Film Transistor:薄膜トランジスタ)を用いて構成される。ところが、TFTの特性(例えば、閾値電圧や移動度)には、ばらつきが生じやすい。そこで、有機ELディスプレイの画素回路にはTFTの特性のばらつきを補償する回路が設けられ、この回路の作用により有機EL素子の輝度のばらつきが抑えられる。

##### 【0005】

電流駆動型の駆動方式においてTFTの特性のばらつきを補償する方式は、駆動用TFTに流れる電流の量を電流信号で制御する電流プログラム方式と、この電流の量を電圧信号で制御する電圧プログラム方式とに大別される。電流プログラム方式を用いれば閾値電圧と移動度のばらつきを補償することができ、電圧プログラム方式を用いれば閾値電圧のばらつきのみを補償することができる。

##### 【0006】

ところが、電流プログラム方式には、第1に、非常に微少な量の電流を扱うので画素回路や駆動回路の設計が困難である、第2に、電流信号を設定する間に寄生容量の影響を受けやすいので大面積化が困難であるという問題がある。これに対して、電圧プログラム方

10

20

30

40

50

式では、寄生容量などの影響は軽微であり、回路設計も比較的容易である。また、移動度のばらつきが電流量に与える影響は、閾値電圧のばらつきが電流量に与える影響よりも小さく、移動度のばらつきは TFT 作製工程である程度抑えることができる。したがって、電圧プログラム方式を適用した表示装置でも、十分な表示品位が得ることができる。

#### 【0007】

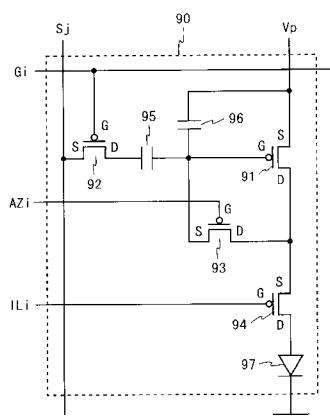

電流駆動型の駆動方式を適用した有機ELディスプレイについては、従来から、以下に示す画素回路が知られている。図11は、特許文献1に記載された画素回路の回路図である。図11に示す画素回路90は、駆動用TFT91、スイッチ用TFT92～94、コンデンサ95、96、および、有機EL素子97(OLED:Organic Light Emitting Diodeともいう)を備えている。画素回路90に含まれるTFTは、いずれもPチャネル型である。10

#### 【0008】

画素回路90では、電源配線Vp(電位はVDD)と共に陰極(GND)との間に、駆動用TFT91、スイッチ用TFT94および有機EL素子97が、この順序で直列に設けられている。駆動用TFT91のゲート端子とデータ線Sjとの間には、コンデンサ95とスイッチ用TFT92がこの順序で直列に設けられている。駆動用TFT91のゲート端子とドレイン端子との間にはスイッチ用TFT93が設けられ、駆動用TFT91のゲート端子と電源配線Vpとの間にはコンデンサ96が設けられている。スイッチ用TFT92、93、94のゲート端子は、それぞれ、走査線Gi、オートゼロ線AZiおよび照明線ILiに接続されている。20

#### 【0009】

図12は、画素回路90に対するデータ書き込み時のタイミングチャートである。時刻t0より前では、走査線Giとオートゼロ線AZiの電位はハイレベルに、照明線ILiの電位はローレベルに、データ線Sjの電位は基準電位Vstdに制御される。時刻t0において走査線Giの電位がローレベルに変化すると、スイッチ用TFT92が導通状態に変化する。次に時刻t1においてオートゼロ線AZiの電位がローレベルに変化すると、スイッチ用TFT93が導通状態に変化する。これにより、駆動用TFT91のゲート端子とドレイン端子は同電位となる。20

#### 【0010】

次に時刻t2において照明線ILiの電位がハイレベルに変化すると、スイッチ用TFT94が非導通状態に変化する。このとき、電源配線Vpから駆動用TFT91とスイッチ用TFT93を経由して駆動用TFT91のゲート端子に電流が流れ込み、駆動用TFT91のゲート端子電位は駆動用TFT91が導通状態である間は上昇する。駆動用TFT91は、ゲート-ソース間電圧が閾値電圧Vth(負の値)になる(すなわち、ゲート端子電位が(VDD + Vth)になる)と、非導通状態に変化する。したがって、駆動用TFT91のゲート端子電位は(VDD + Vth)まで上昇する。30

#### 【0011】

次に時刻t3においてオートゼロ線AZiの電位がハイレベルに変化すると、スイッチ用TFT93が非導通状態に変化する。このときコンデンサ95には、駆動用TFT91のゲート端子とデータ線Sjとの電位差(VDD + Vth - Vstd)が保持される。40

#### 【0012】

次に時刻t4においてデータ線Sjの電位が基準電位Vstdからデータ電位Vdataに変化すると、駆動用TFT91のゲート端子電位は、同じ量(Vdata - Vstd)だけ変化して(VDD + Vth + Vdata - Vstd)となる。次に時刻t5において走査線Giの電位がハイレベルに変化すると、スイッチ用TFT92が非導通状態に変化する。このときコンデンサ96には、駆動用TFT91のゲート-ソース間電圧(Vth + Vdata - Vstd)が保持される。次に時刻t6において、データ線Sjの電位がデータ電位Vdataから基準電位Vstdに変化する。

#### 【0013】

次に時刻t7において照明線ILiの電位がローレベルに変化すると、スイッチ用TFT50

T94が導通状態に変化する。これにより、電源配線Vpから駆動用TFT91とスイッチ用TFT94を経由して有機EL素子97に電流が流れ。駆動用TFT91を流れる電流の量はゲート端子電位( $V_{DD} + V_{th} + V_{data} - V_{std}$ )に応じて増減するが、閾値電圧 $V_{th}$ が異なっていても電位差( $V_{data} - V_{std}$ )が同じであれば電流量は同じである。したがって、閾値電圧 $V_{th}$ の値にかかわらず、有機EL素子97には電位 $V_{data}$ に応じた量の電流が流れ、有機EL素子97はデータ電位 $V_{data}$ に応じた輝度で発光する。

#### 【0014】

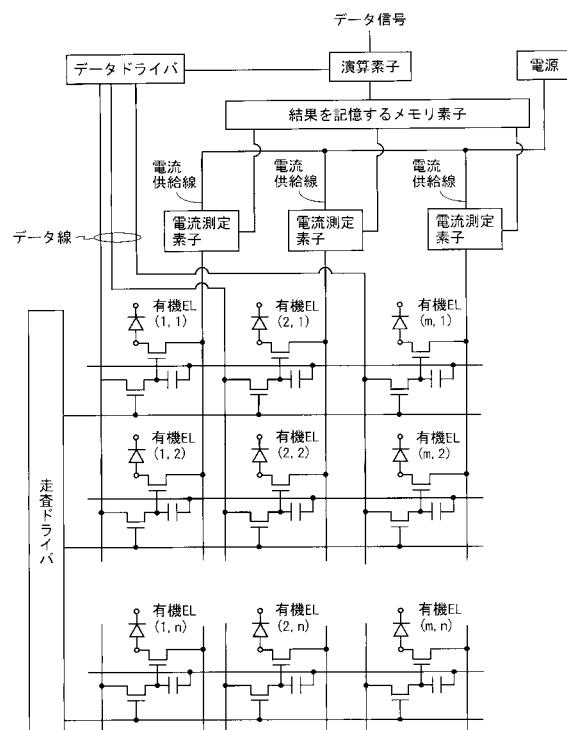

これ以外にも有機ELディスプレイについては、閾値補正回路を画素回路の外部に設ける方法や、閾値補正期間を画素回路の選択期間よりも長くする方法が知られている。例えば、特許文献2には、駆動素子の電流能力を測定して画素回路の外部に設けたメモリに記憶し、パネルに供給する電圧を記憶した電流能力に応じて変化させる方法が記載されている(図13を参照)。また、特許文献3には、閾値補正期間を選択期間よりも長くするために、カップリング容量の一端に初期電圧を与えるためのスイッチを設ける方法が記載されている。

【特許文献1】国際公開第98/48403号パンフレット

【特許文献2】日本国特開2002-278513号公報

【特許文献3】日本国特開2004-133240号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0015】

上述したように、図11に示す画素回路90を用いれば、駆動用TFT91の閾値電圧のばらつきを補償し、有機EL素子97を所望の輝度で発光させることができる。しかしながら、この画素回路(以下、従来の画素回路という)には、以下に示す問題点がある。

#### 【0016】

第1の問題点は、データ電圧の振幅を効率よく利用できることである。従来の画素回路では、容量カップリングによるデータ書き込みが行われるので、画素回路の外部からあるデータ電圧を書き込んでも、オーバードライブ電圧として実際に駆動用TFTに印加される電圧は、その $C_c / (C_c + C_s + C_{gs})$ 倍になる(ただし、 $C_c$ はコンデンサ95の容量、 $C_s$ はコンデンサ96の容量、 $C_{gs}$ は駆動用TFT91のゲート-ソース間容量)。このようにデータ電圧を効率よく利用できないので、データドライバ回路の消費電力が増大する。カップリング容量 $C_c$ を極めて大きくすれば、データ電圧の振幅を効率よく利用できるが、そうすると画素回路の面積が増大する。また、高い精度で制御できない寄生容量 $C_{gs}$ が駆動電圧に影響を及ぼすことも問題となる。

#### 【0017】

第2の問題点は、閾値補正の精度が低いことである。上述したように、実際の駆動電圧は外部から与えた電圧の $C_c / (C_c + C_s + C_{gs})$ 倍になるので、閾値補正の効果も $C_c / (C_c + C_s + C_{gs})$ 倍になる。このため、閾値電圧を完全に補正することは困難である。

#### 【0018】

第3の問題点は、画素回路の規模が大きくなることである。上述したように、寄生容量対策としてカップリング容量 $C_c$ を大きくすると、画素回路のレイアウトにおいてコンデンサ95の占める面積が大きくなる。このため、光を基板下部から取り出すボトムエミッション構成の有機ELディスプレイでは、開口率が低下する。また、回路面積の増大は製造時の歩留まり低下の要因になるので、画素回路の面積や素子数を削減する必要がある。

#### 【0019】

第4の問題点は、製造時の検査が困難になることである。従来の画素回路では、駆動用TFTのゲート端子はコンデンサを介してデータ線に接続されているので、データ線経由で駆動用TFTの電流を検査することは困難である。このため、検査で歩留まりを向上させることが困難になる。

10

20

30

40

50

## 【0020】

第5の問題点は、閾値補正期間が短い時間に制限されることである。従来の画素回路では、画素回路の選択期間内に閾値補正とデータ書き込みを行う必要がある。閾値補正には、ダイオード接続された駆動素子のゲート-ソース間電圧が閾値電圧に十分に近づくまでの時間を必要とする。ところが、高精細の表示装置では、選択期間の長さは極めて短くなる。例えば、解像度がVGAのパネルを60フレーム/sで駆動した場合、選択期間は約30μsとなる。このような短時間のうちに閾値補正とデータ書き込みを完了することは困難である。

## 【0021】

特許文献2に記載された方法によれば、上記第3の問題点を解決できるが、各駆動素子の電流能力を記憶するメモリを設けるために周辺回路のコストやレイアウト面積が増大する。また、特許文献3に記載された方法によれば、上記第5の問題を解決できるが、初期電圧を与えるスイッチを設けるために画素回路の規模がさらに大きくなる。

10

## 【0022】

それ故に、本発明は、画素回路の規模を増大させずに、データ電圧の振幅を効率よく利用し、高い精度で閾値補正を行う表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0023】

本発明の第1の局面は、電流駆動型の表示装置であって、

複数の走査線と複数のデータ線との各交差点に対応して配置された複数の画素回路と、

20

走査信号出力回路と、

表示信号出力回路とを備え、

前記画素回路は、それぞれ、

2本の電源配線間に設けられた電気光学素子と、

前記電気光学素子と共に前記電源配線間に直列に設けられた駆動素子と、

前記駆動素子の制御端子と前記データ線とに接続され、前記走査線に接続された制御端子を有する第1のスイッチング素子と、

前記駆動素子の制御端子と一方の導通端子との間に設けられた第2のスイッチング素子と、

前記電気光学素子および前記駆動素子と共に前記電源配線間に直列に設けられた第3のスイッチング素子と、

30

一端が前記駆動素子の制御端子に接続された容量とを含み、

前記表示信号出力回路は、複数のアナログバッファと、前記データ線ごとに設けられた複数の補正用容量および複数のスイッチ回路とを含み、

前記走査信号出力回路は、書き込み対象の画素回路について、閾値補正期間において、前記第1および第2のスイッチング素子を導通状態、前記第3のスイッチング素子を非導通状態に設定することにより、前記駆動素子の閾値電圧に前記駆動素子の制御端子の電圧を近づけて当該電圧を前記データ線に出力させ、次に前記第2のスイッチング素子を非導通状態に変化させ、さらに前記第1のスイッチング素子を非導通状態、前記第3のスイッチング素子を導通状態に変化させる制御を行い、

40

前記スイッチ回路を用いて、前記補正用容量の一方の電極を前記データ線に接続し、他方の電極に所定の固定電圧を印加するか、前記補正用容量の一方の電極を前記アナログバッファを介して前記データ線に接続し、他方の電極に表示データに対応したデータ電圧を印加するかを切り替えることにより、前記表示信号出力回路は、前記第2のスイッチング素子が導通状態にあるときの前記データ線の電圧に基づき、前記第2のスイッチング素子が非導通状態に変化した後に、前記データ電圧に前記駆動素子の閾値電圧に対応した補正電圧を加算または減算した電圧を前記データ線に印加し、

前記閾値補正期間は、前記駆動素子の制御端子の電圧が前記駆動素子の閾値電圧に到達する前に終了することを特徴とする。

## 【0026】

50

本発明の第2の局面は、本発明の第1の局面において、

前記駆動素子および前記第1～第3のスイッチング素子は薄膜トランジスタであり、

前記第1および第3のスイッチング素子のうち一方はPチャネル型、他方はNチャネル

型であり、両者の制御端子は共通の配線に接続されていることを特徴とする。

## 【0027】

本発明の第3の局面は、本発明の第1の局面において、

前記駆動素子および前記第1～第3のスイッチング素子は薄膜トランジスタであり、

前記第2および第3のスイッチング素子のうち一方はPチャネル型、他方はNチャネル

型であり、両者の制御端子は共通の配線に接続されていることを特徴とする。

## 【0028】

本発明の第4の局面は、本発明の第1の局面において、

前記駆動素子はPチャネル型のエンハンスマント型トランジスタであり、

前記走査信号出力回路によって選択された画素回路は、前記電源配線の電圧のうち高い

ほうから前記補正電圧の絶対値を減算した電圧を前記データ線に出力することを特徴とす

る。

## 【0029】

本発明の第5の局面は、本発明の第1の局面において、

前記駆動素子はNチャネル型のエンハンスマント型トランジスタであり、

前記走査信号出力回路によって選択された画素回路は、前記電源配線の電圧のうち低い

ほうに前記補正電圧の絶対値を加算した電圧を前記データ線に出力することを特徴とす

る。

## 【0030】

本発明の第6の局面は、本発明の第1の局面において、

前記表示信号出力回路は、前記第1のスイッチング素子の導通期間の一部において、前

記データ線に所定の固定電圧を印加することを特徴とする。

## 【0032】

本発明の第7の局面は、本発明の第1の局面において、

前記アナログバッファは、複数の前記データ線ごとに設けられていることを特徴とす

る。

## 【0033】

本発明の第8の局面は、複数の走査線と複数のデータ線との各交差点に対応して配置さ

れ、それぞれが、2本の電源配線間に設けられた電気光学素子と、前記電気光学素子と共に

前記電源配線間に直列に設けられた駆動素子と、前記駆動素子の制御端子と前記データ

線とに接続され、前記走査線に接続された制御端子を有する第1のスイッチング素子と、

前記駆動素子の制御端子と一方の導通端子との間に設けられた第2のスイッチング素子と

、前記電気光学素子および前記駆動素子と共に前記電源配線間に直列に設けられた第3の

スイッチング素子と、一端が前記駆動素子の制御端子に接続された容量とを含む複数の画

素回路を備えた表示装置の駆動方法であって、

書き込み対象の画素回路について、閾値補正期間において、前記第1および第2のスイ

ッチング素子を導通状態、前記第3のスイッチング素子を非導通状態に設定することによ

り、前記駆動素子の閾値電圧に前記駆動素子の制御端子の電圧を近づけて当該電圧を前記

データ線に出力させ、次に前記第2のスイッチング素子を非導通状態に変化させ、さらに

前記第1のスイッチング素子を非導通状態、前記第3のスイッチング素子を導通状態に変

化させるステップと、

複数のアナログバッファと、前記データ線ごとに設けられた複数の補正用容量および複

数のスイッチ回路とを含む表示信号出力回路において、前記スイッチ回路を用いて、前記

補正用容量の一方の電極を前記データ線に接続し、他方の電極に所定の固定電圧を印加す

るか、前記補正用容量の一方の電極を前記アナログバッファを介して前記データ線に接続

し、他方の電極に表示データに対応したデータ電圧を印加するかを切り替えることにより

、前記第2のスイッチング素子が導通状態にあるときの前記データ線の電圧に基づき、前

10

20

30

40

50

記第2のスイッチング素子が非導通状態に変化した後に、前記データ電圧に前記駆動素子の閾値電圧に対応した補正電圧を加算または減算した電圧を前記データ線に印加するステップとを備え、

前記閾値補正期間は、前記駆動素子の制御端子の電圧が前記駆動素子の閾値電圧に到達する前に終了することを特徴とする。

#### 【発明の効果】

##### 【0034】

本発明の第1または第8の局面によれば、選択された画素回路から駆動素子の制御端子の電圧（駆動素子の閾値電圧に近づいているが、まだ駆動素子の閾値電圧に到達していない電圧）を読み出し、読み出した電圧に基づき、データ電圧に補正電圧（駆動素子の閾値電圧に対応した電圧）を加算または減算した電圧を駆動素子の制御端子に与えることができる。したがって、駆動素子の閾値電圧を検出して閾値電圧のばらつきを補償し、電気光学素子を所望の輝度で発光させることができる。また、閾値補正回路を画素回路の外部に設け、データ線を用いて閾値電圧を検出することにより、画素回路の規模や面積を縮小することができる。また、閾値電圧を電圧信号として検出することにより、電流信号を帰還する場合とは異なり電流電圧変換素子が不要になるので、補正効果のばらつきを抑えることができる。また、カップリング容量を介さずに駆動素子の制御端子に所望の電圧を与えるので、データ電圧の振幅を有効に利用し、消費電力を低減することができる。10

##### 【0035】

また、閾値補正に使用する容量を削減し、開口率と歩留まりを向上させ、消費電力を削減することができる。20

##### 【0036】

また、画素回路の選択期間を閾値電圧を検知する期間と補正後のデータ電圧を書き込む期間とに分け、閾値電圧を読み出すための帰還線とデータを書き込むためのデータ線とを共通化することができる。

また、表示信号出力回路は、データ線の電圧に「データ電圧と固定電圧の差」を加算した電圧をデータ線に印加することができる。したがって、固定電圧を好適に決定すれば、画素回路からデータ線に出力された電圧に基づき、データ電圧に補正電圧（駆動素子の閾値電圧に対応した電圧）を加算または減算した電圧をデータ線に印加することができる。

また、この加算または減算を画素回路の外部で行うことにより、画素回路の規模を小さくすることができます。また、補正用容量とデータ線との間にアナログバッファを設けることにより、補正用容量に保持された電圧のカップリングによる減衰を抑え、高画質化を実現することができる。30

##### 【0037】

本発明の第2または第3の局面によれば、第1～第3のスイッチング素子の制御端子に接続される配線を共通化して配線数を減らし、画素の開口率をさらに高くすることができる。

##### 【0038】

本発明の第4の局面によれば、Pチャネル型の駆動素子では閾値電圧の絶対値を減算した電圧を制御端子に与えれば閾値電圧のばらつきを補償できるので、選択された画素回路から出力された電圧を用いて駆動素子の閾値電圧のばらつきを補償することができる。40

##### 【0039】

本発明の第5の局面によれば、Nチャネル型の駆動素子では閾値電圧の絶対値を加算した電圧を制御端子に与えれば閾値電圧のばらつきを補償できるので、選択された画素回路から出力された電圧を用いて駆動素子の閾値電圧のばらつきを補償することができる。

##### 【0040】

本発明の第6の局面によれば、駆動素子の制御端子に好適な固定電圧を与えることにより、駆動素子の閾値電圧に応じた電圧がデータ線に出力されるまでの時間を短縮することができる。したがって、閾値補正期間が短い場合でも、補正効果のばらつきを抑え、画質を向上させることができる。50

## 【0042】

本発明の第7の局面によれば、データ線ごとに配置するには回路規模が大きいアナログバッファを複数のデータ線ごとに配置し、高精細の表示パネルを実現することができる。

## 【図面の簡単な説明】

## 【0043】

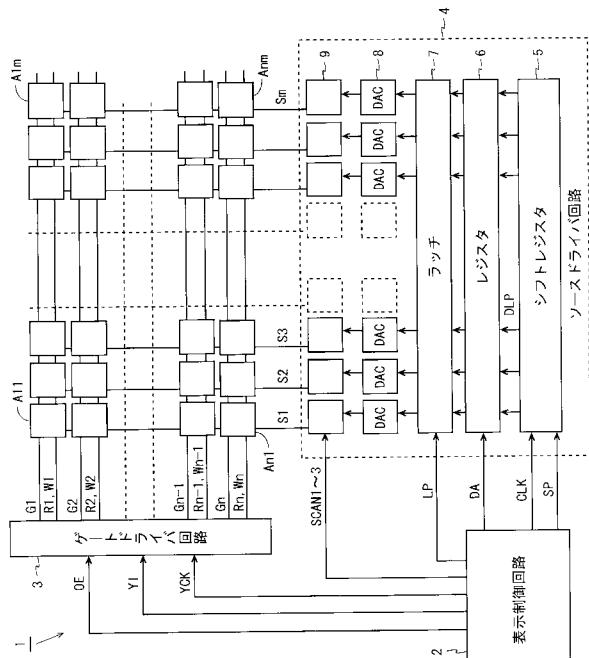

【図1】本発明の第1～第3の実施形態に係る表示装置の構成を示すブロック図である。

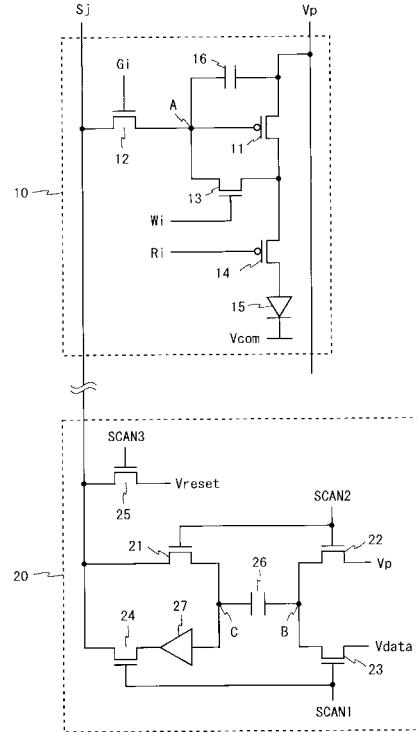

【図2】本発明の第1の実施形態に係る表示装置に含まれる画素回路と閾値補正回路の回路図である。

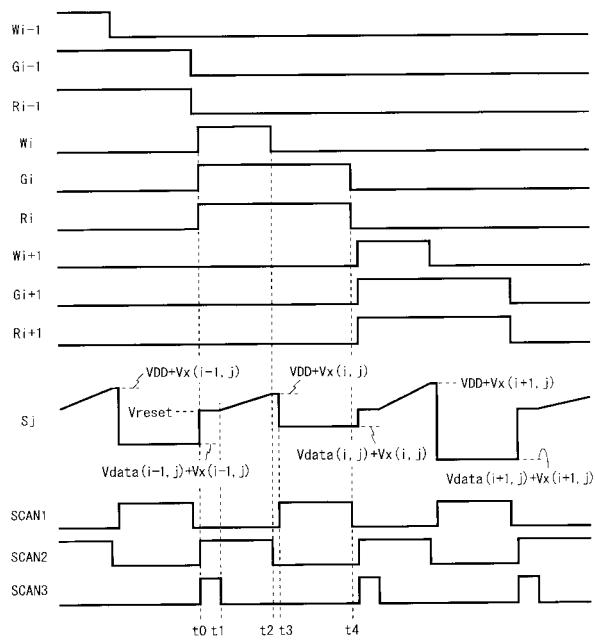

【図3】本発明の第1の実施形態に係る表示装置における画素回路に対するデータ書き込み時のタイミングチャートである。 10

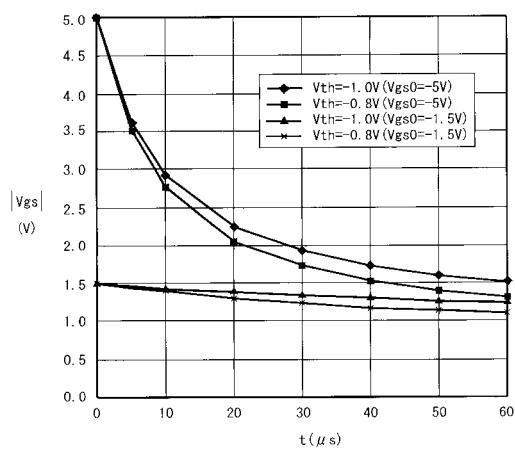

【図4】ダイオード接続されたTFTにおけるゲート・ソース間電圧の時間的变化の例を示す図である。

【図5A】オフセットキャンセル機能を有するバッファの回路図である。

【図5B】図5Aに示すバッファのタイミングチャートである。

【図5C】図5Aに示すバッファの動作を説明するための図である。

【図5D】図5Aに示すバッファの動作を説明するための図である。

【図6A】本発明の第1の実施形態の第1変形例に係る表示装置に含まれる画素回路の回路図である。

【図6B】本発明の第1の実施形態の第2変形例に係る表示装置に含まれる画素回路の回路図である。 20

【図7】本発明の第2の実施形態に係る表示装置に含まれる画素回路と閾値補正回路の回路図である。

【図8】本発明の第2の実施形態に係る表示装置における画素回路に対するデータ書き込み時のタイミングチャートである。

【図9】本発明の第3の実施形態に係る表示装置に含まれる閾値補正回路の回路図である。

【図10】本発明の第3の実施形態に係る表示装置における画素回路に対するデータ書き込み時のタイミングチャートである。

【図11】従来の表示装置に含まれる画素回路の回路図である。

【図12】図11に示す画素回路に対するデータ書き込み時のタイミングチャートである。 30

。

【図13】従来の表示装置の構成を示すブロック図である。

## 【符号の説明】

## 【0044】

1 … 表示装置

2 … 表示制御回路

3 … ゲートドライバ回路

4 … ソースドライバ回路

5 … シフトレジスタ

6 … レジスタ

7 … ラッチ

8 … D / A 変換器

9、20、50、60 … 閾値補正回路

A i j、10、17、18、40 … 画素回路

11、41 … 駆動用TFT

12～14、42～44 … スイッチ用TFT

15、45 … 有機EL素子

16、26、46 … コンデンサ

21～25、61 … スイッチ

27 … アナログバッファ

40

50

【発明を実施するための最良の形態】

【0045】

図1～図10を参照して、本発明の第1～第3の実施形態に係る表示装置について説明する。以下に示す表示装置は、電気光学素子や複数のスイッチング素子を含む画素回路を備えている。画素回路に含まれるスイッチング素子は、低温ポリシリコンTFTやCGシリコンTFTやアモルファスシリコンTFTなどで構成することができる。これらTFTの構成や作成プロセスは公知であるため、ここではその説明を省略する。また、画素回路に含まれる電気光学素子は、有機EL素子であるとする。有機EL素子の構成も公知であるので、ここではその説明を省略する。以下、第1～第3の実施形態に共通する表示装置の全体構成について説明し、その後に各実施形態に係る表示装置の画素回路と閾値補正回路について説明する。

10

【0046】

(表示装置の全体構成)

図1は、本発明の第1～第3の実施形態に係る表示装置の構成を示すブロック図である。図1に示す表示装置1は、複数の画素回路A<sub>i</sub>j( iは1以上n以下の整数、jは1以上m以下の整数)、表示制御回路2、ゲートドライバ回路3、および、ソースドライバ回路4を備えている。ゲートドライバ回路3は走査信号出力回路として機能し、ソースドライバ回路4は表示信号出力回路として機能する。

【0047】

表示装置1には、互いに平行な複数の走査線G<sub>i</sub>と、これに直交する互いに平行な複数のデータ線S<sub>j</sub>とが設けられる。画素回路A<sub>i</sub>jは、走査線G<sub>i</sub>とデータ線S<sub>j</sub>の各交差点に対応してマトリクス状に配置されている。また、走査線G<sub>i</sub>と平行に、互いに平行な複数の制御線W<sub>i</sub>、R<sub>i</sub>が配置されている。走査線G<sub>i</sub>と制御線W<sub>i</sub>、R<sub>i</sub>はゲートドライバ回路3に接続され、データ線S<sub>j</sub>はソースドライバ回路4に接続されている。さらに、画素回路A<sub>i</sub>jの配置領域には、図示しない電源配線V<sub>p</sub>と共に通陰極V<sub>com</sub>が配置されている。なお、共通陰極V<sub>com</sub>に代えて、陰極配線CA<sub>i</sub>を配置してもよい。

20

【0048】

表示制御回路2は、ゲートドライバ回路3に対してタイミング信号OE、スタートパルスYIおよびクロックYCKを出力し、ソースドライバ回路4に対してスタートパルスSP、クロックCLK、表示データDA、および、ラッチパルスLPを出力する。また、表示制御回路2は、ソースドライバ回路4の制御線SCAN1～SCAN3の電位を制御する。

30

【0049】

ゲートドライバ回路3は、シフトレジスタ回路、論理演算回路およびバッファ(いずれも図示せず)を含んでいる。シフトレジスタ回路は、クロックYCKに同期してスタートパルスYIを順次転送する。論理演算回路は、シフトレジスタ回路の各段から出力されたパルスとタイミング信号OEとの間で論理演算を行う。論理演算回路の出力は、バッファを経由して、対応する走査線G<sub>i</sub>と制御線W<sub>i</sub>、R<sub>i</sub>に与えられる。1本の走査線G<sub>i</sub>にはm個の画素回路A<sub>i</sub>jが接続されており、画素回路A<sub>i</sub>jは走査線G<sub>i</sub>を用いてm個ずつ一括して選択される。

40

【0050】

ソースドライバ回路4は、mビットのシフトレジスタ5、レジスタ6、ラッチ7、m個のD/A変換器8、および、m個の閾値補正回路9を含み、1行分の画素回路A<sub>i</sub>jにデータを同じタイミングで送信する線順次走査を行う。より詳細には、シフトレジスタ5は、継続接続されたm個のレジスタを有し、初段のレジスタに供給されたスタートパルスSPをクロックCLKに同期して転送し、各段のレジスタからタイミングパルスDLPを出力する。タイミングパルスDLPの出力タイミングに合わせて、レジスタ6には表示データDAが供給される。レジスタ6は、タイミングパルスDLPに従い、表示データDAを記憶する。レジスタ6に1行分の表示データDAが記憶されると、表示制御回路2はラッチ7に対してラッチパルスLPを出力する。ラッチ7は、ラッチパルスLPを受け取ると

50

、レジスタ6に記憶された表示データを保持する。

#### 【0051】

D/A変換器8と閾値補正回路9は、データ線S<sub>j</sub>に対応して設けられる。D/A変換器8は、ラッチ7に保持された表示データをアナログ信号電圧に変換し、対応する閾値補正回路9に出力する。閾値補正回路9は、ゲートドライバ回路3によって選択された画素回路A<sub>i</sub>jから出力された電圧（駆動用TFTの閾値電圧に応じた電圧）をデータ線S<sub>j</sub>経由で受け取り、当該電圧に基づき、D/A変換器8の出力電圧に駆動用TFTの閾値電圧に対応した補正電圧を加算または減算した電圧をデータ線S<sub>j</sub>に印加する。閾値補正回路9の作用により、画素回路A<sub>i</sub>jに含まれる駆動用TFTの閾値電圧のばらつきを補償することができる（詳細は後述）。

10

#### 【0052】

なお、ソースドライバ回路4は、線順次走査に代えて、各画素回路に1つずつ順にデータを送信する点順次走査を行ってもよい。点順次走査を行うときには、ある走査線G<sub>i</sub>が選択されている間、データ線S<sub>j</sub>の電圧はデータ線S<sub>j</sub>の容量によって保持される。点順次走査を行うソースドライバ回路の構成は公知であるので、ここでは説明を省略する。

#### 【0053】

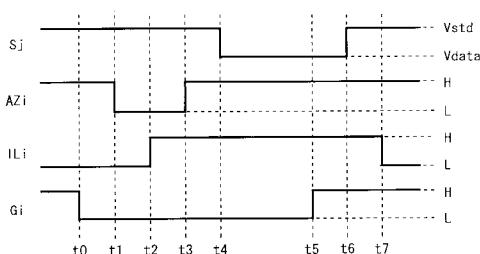

（第1の実施形態）

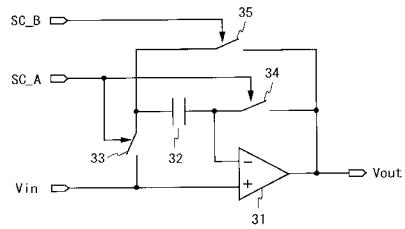

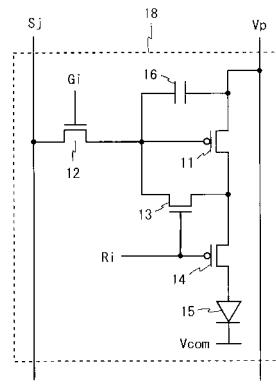

図2は、本発明の第1の実施形態に係る表示装置に含まれる画素回路と閾値補正回路の回路図である。図2に示す画素回路10と閾値補正回路20は、図1では画素回路A<sub>i</sub>jと閾値補正回路9に相当する。図2に示すように、画素回路10は、駆動用TFT11、スイッチ用TFT12～14、有機EL素子15、および、コンデンサ16を備えている。駆動用TFT11はPチャネル型のエンハンスマント型、スイッチ用TFT12、13はNチャネル型、スイッチ用TFT14はPチャネル型である。

20

#### 【0054】

画素回路10は、電源配線V<sub>p</sub>、共通陰極V<sub>com</sub>、走査線G<sub>i</sub>、制御線W<sub>i</sub>、R<sub>i</sub>、および、データ線S<sub>j</sub>に接続されている。以下、電源配線V<sub>p</sub>の電位をV<sub>DD</sub>、共通陰極V<sub>com</sub>の電位をV<sub>SS</sub>（ただし、V<sub>DD</sub> > V<sub>SS</sub>）とする。共通陰極V<sub>com</sub>は、表示装置内のすべての有機EL素子15の共通電極となる。

#### 【0055】

画素回路10では、電源配線V<sub>p</sub>と共にV<sub>com</sub>との間に、電源配線V<sub>p</sub>側から順に、駆動用TFT11、スイッチ用TFT14および有機EL素子15が直列に設けられている。駆動用TFT11のゲート端子とデータ線S<sub>j</sub>との間には、スイッチ用TFT12が設けられている。駆動用TFT11のゲート端子とドレイン端子との間にはスイッチ用TFT13が設けられ、駆動用TFT11のゲート端子と電源配線V<sub>p</sub>との間にはコンデンサ16が設けられている。スイッチ用TFT12～14のゲート端子は、それぞれ、走査線G<sub>i</sub>、制御線W<sub>i</sub>および制御線R<sub>i</sub>に接続されている。走査線G<sub>i</sub>および制御線W<sub>i</sub>、R<sub>i</sub>の電位はゲートドライバ回路3によって制御され、データ線S<sub>j</sub>の電位はソースドライバ回路4によって制御される。以下、駆動用TFT11のゲート端子が接続される節点をAという。

30

#### 【0056】

閾値補正回路20は、スイッチ21～25、コンデンサ26、および、アナログバッファ27を備え、データ線S<sub>j</sub>に接続されている。スイッチ21～25はいずれもNチャネル型のトランジスタであり、アナログバッファ27はボルテージホロワ回路（ユニティゲインアンプ）である。

40

#### 【0057】

コンデンサ26の一方の電極（図2で右側に描かれた電極）が接続される節点をB、他方の電極が接続される節点をCという。スイッチ21はデータ線S<sub>j</sub>と節点Cとの間に設けられ、スイッチ22は節点Bと電源配線V<sub>p</sub>との間に設けられている。スイッチ23の一端は節点Bに接続され、節点Cとデータ線S<sub>j</sub>との間には、節点C側から順に、アナログバッファ27とスイッチ24が直列に設けられている。スイッチ25の一端は、データ

50

線 S j に接続されている。

#### 【 0 0 5 8 】

スイッチ 2 3 の他端には D / A 変換器 8 から出力されたデータ電圧 V d a t a が与えられ、スイッチ 2 5 の他端には初期電圧 V r e s e t ( 詳細は後述 ) が与えられる。スイッチ 2 1 、 2 2 のゲート端子は制御線 S C A N 2 に接続され、スイッチ 2 3 、 2 4 のゲート端子は制御線 S C A N 1 に接続され、スイッチ 2 5 のゲート端子は制御線 S C A N 3 に接続されている。

#### 【 0 0 5 9 】

以下、駆動用 T F T 1 1 の閾値電圧を V t h ( 負の値 ) とする。後述するように、コンデンサ 2 6 は、駆動用 T F T 1 1 の閾値電圧 V t h に対応した補正電圧 V x を保持する補正用容量として機能する。また、スイッチ 2 1 ~ 2 4 は、コンデンサ 2 6 の一方の電極をデータ線 S j に接続し、他方の電極に固定電圧 V D D を印加するか、コンデンサ 2 6 の一方の電極をアナログバッファ 2 7 を介してデータ線 S j に接続し、他方の電極にデータ電圧 V d a t a を印加するかを切り替えるスイッチ回路として機能する。10

#### 【 0 0 6 0 】

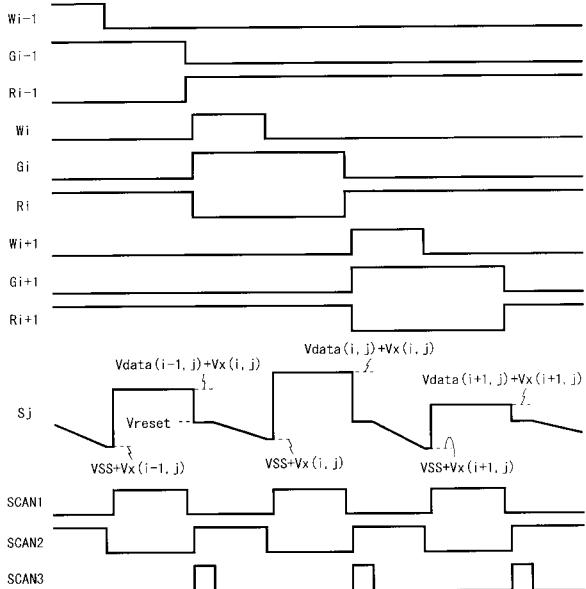

図 3 は、画素回路 1 0 に対するデータ書き込み時のタイミングチャートである。以下、図 3 を参照して、走査線 G i とデータ線 S j に接続された画素回路 1 0 にデータ電圧 V d a t a を書き込むときの動作を説明する。図 3 では、時刻 t 0 から時刻 t 4 までが画素回路 1 0 の選択期間となる。時刻 t 2 より前では、駆動用 T F T 1 1 の閾値電圧を検知する処理が行われ、時刻 t 2 より後では、補正後のデータ電圧を書き込む処理が行われる。20

#### 【 0 0 6 1 】

時刻 t 0 より前では、走査線 G i と制御線 W i 、 R i の電位はローレベルに制御されており、スイッチ用 T F T 1 2 、 1 3 は非導通状態、スイッチ用 T F T 1 4 は導通状態にある。このとき駆動用 T F T 1 1 は導通状態にあり、電源配線 V p から駆動用 T F T 1 1 とスイッチ用 T F T 1 4 を経由して有機 E L 素子 1 5 に電流が流れ、有機 E L 素子 1 5 は発光する。

#### 【 0 0 6 2 】

時刻 t 0 において走査線 G i と制御線 R i 、 W i 、 S C A N 3 の電位がハイレベルに変化すると、スイッチ用 T F T 1 2 、 1 3 およびスイッチ 2 5 は導通状態に変化し、スイッチ用 T F T 1 4 は非導通状態に変化する。これにより、データ線 S j には初期電圧 V r e s e t が印加され、データ線 S j と節点 A の電位は V r e s e t となる。時刻 t 0 以降、駆動用 T F T 1 1 を通過した電流は、スイッチ用 T F T 1 3 経由で接点 A に流れ込む。30

#### 【 0 0 6 3 】

次に時刻 t 1 において制御線 S C A N 3 の電位がローレベルに変化すると、スイッチ 2 5 は非導通状態に変化する。時刻 t 1 以降も、駆動用 T F T 1 1 を通過した電流は、スイッチ用 T F T 1 3 経由で節点 A に流れ込み、節点 A の電位 ( 駆動用 T F T 1 1 のゲート端子電位 ) は駆動用 T F T 1 1 が導通状態にある間は上昇する。このときスイッチ用 T F T 1 2 は導通状態にあるので、データ線 S j の電位は節点 A の電位に等しい。

#### 【 0 0 6 4 】

時刻 t 0 から時刻 t 2までの間、制御線 S C A N 1 の電位はローレベルに、制御線 S C A N 2 の電位はハイレベルに制御される。このため、スイッチ 2 1 、 2 2 は導通状態、スイッチ 2 3 、 2 4 は非導通状態となり、節点 B は電源配線 V p に、節点 C はデータ線 S j に接続される。したがって、このとき節点 B の電位は V D D であり、節点 C の電位は節点 A およびデータ線 S j の電位に等しい。40

#### 【 0 0 6 5 】

次に時刻 t 2 において制御線 W i 、 S C A N 2 の電位がローレベルに変化すると、スイッチ用 T F T 1 3 およびスイッチ 2 1 、 2 2 は非導通状態に変化する。時刻 t 2 における節点 A の電位を ( V D D + V x ) ( ただし、 V x は負の値で、 V x の絶対値は V t h の絶対値よりも大きい ) とする。時刻 t 2 では接点 C の電位も ( V D D + V x ) であるので、時刻 t 2 においてスイッチ 2 1 、 2 2 が非導通状態に変化すると、コンデンサ 2 6 には電50

圧  $V_x$  が保持される。

【0066】

上述したように、節点 A の電位は、駆動用 TFT11 が導通状態にある間は上昇する。したがって、十分な時間があれば、節点 A の電位は、駆動用 TFT11 のゲート - ソース間電圧が閾値電圧  $V_{th}$  (負の値) になるまで上昇し、最終的には ( $V_{DD} + V_{th}$ ) に到達する。時刻  $t_2$  における節点 A の電位 ( $V_{DD} + V_x$ ) は、( $V_{DD} + V_{th}$ ) よりも低い。また、電圧  $V_x$  は閾値電圧  $V_{th}$  に応じて変化し、電圧  $V_x$  の絶対値は閾値電圧  $V_{th}$  の絶対値が大きいほど大きい。

【0067】

次に時刻  $t_3$  において制御線 SCAN1 の電位がハイレベルに変化すると、スイッチ 23、24 は導通状態に変化する。時刻  $t_3$  以降、節点 B には D/A 変換器 8 から出力されたデータ電圧  $V_{data}$  が印加され、節点 C はアナログバッファ 27 を介してデータ線  $S_j$  に接続される。コンデンサ 26 が電圧  $V_x$  を保持している間に節点 B の電位が  $V_{DD}$  から  $V_{data}$  に変化すると、節点 C の電位も同じ量 ( $V_{data} - V_{DD}$ ) だけ変化して ( $V_{DD} + V_x$ ) + ( $V_{data} - V_{DD}$ ) = ( $V_{data} + V_x$ ) となる。

10

【0068】

このときスイッチ 24 は導通状態にあり、アナログバッファ 27 の入力電圧と出力電圧は等しいので、データ線  $S_j$  の電位は節点 C と同じく ( $V_{data} + V_x$ ) となる。また、このときスイッチ用 TFT12 も導通状態にあるので、節点 A の電位もデータ線  $S_j$  と同じく ( $V_{data} + V_x$ ) となる。

20

【0069】

次に時刻  $t_4$  において走査線  $G_i$  および制御線  $R_i$ 、SCAN1 の電位がローレベルに変化すると、スイッチ用 TFT12 およびスイッチ 23、24 は非導通状態、スイッチ用 TFT14 は導通状態に変化する。このときコンデンサ 16 には、駆動用 TFT11 のゲート - ソース間電圧 ( $V_{DD} - V_{data} - V_x$ ) が保持される。なお、制御線  $R_i$  に与えられるオン電位 (ローレベル電位) は、スイッチ用 TFT14 が線形領域で動作するよう決定される。

【0070】

時刻  $t_4$  以降、コンデンサ 16 に保持された電圧は変化しないので、節点 A の電位は ( $V_{data} + V_x$ ) のままである。したがって、時刻  $t_4$  以降、次に制御線  $R_i$  の電位がハイレベルとなるまで、電源配線  $V_p$  から駆動用 TFT11 とスイッチ用 TFT14 を経由して有機 EL 素子 15 に電流が流れ、有機 EL 素子 15 は発光する。このとき駆動用 TFT11 を流れる電流の量は節点 A の電位 ( $V_{data} + V_x$ ) に応じて増減するが、以下に示すように、閾値電圧  $V_{th}$  が異なっていても電位  $V_{data}$  が同じであれば電流量を同じにすることができる。

30

【0071】

駆動用 TFT11 を飽和領域で動作させたとき、ドレイン - ソース間を流れる電流  $I_{EL}$  は、チャネル長変調効果を無視すれば、次式 (1) で与えられる。

$$I_{EL} = -1/2 \cdot W/L \cdot C_{ox} \cdot \mu (V_g - V_{DD} - V_{th})^2 \quad \dots (1)$$

ただし、上式 (1) において、 $W/L$  は駆動用 TFT11 のアスペクト比、 $C_{ox}$  はゲート容量、 $\mu$  は移動度、 $V_g$  はゲート端子電位 (節点 A の電位) である。

40

【0072】

式 (1) に示す電流  $I_{EL}$  は、一般には、閾値電圧  $V_{th}$  に応じて変動する。本実施形態に係る表示装置では、ゲート端子電位  $V_g$  が ( $V_{data} + V_x$ ) となるので、電流  $I_{EL}$  は次式 (2) に示すようになる。

$$I_{EL} = -1/2 \cdot W/L \cdot C_{ox} \cdot \mu \{ V_{data} - V_{DD} + (V_x - V_{th}) \}^2 \quad \dots (2)$$

式 (2) において電圧  $V_x$  が閾値電圧  $V_{th}$  に一致すれば、電流  $I_{EL}$  は閾値電圧  $V_{th}$  には依存しない。また、電圧  $V_x$  が閾値電圧  $V_{th}$  に一致しなくても、両者の差が一定であれば、電流  $I_{EL}$  は閾値電圧  $V_{th}$  には依存しない。

50

## 【0073】

本実施形態に係る表示装置では、2つのTFT間で電圧 $V_x$ の差が閾値電圧 $V_{th}$ の差とほぼ同じになるように、閾値補正期間（時刻 $t_1$ から時刻 $t_2$ までの期間）の長さや初期電圧 $V_{reset}$ のレベルが決定される。このため、式(2)に含まれる電圧差( $V_x - V_{th}$ )はほぼ一定になる。したがって、閾値電圧 $V_{th}$ の値にかかわらず、有機EL素子15にはデータ電圧 $V_{data}$ に応じた量の電流が流れ、有機EL素子15はデータ電圧 $V_{data}$ に応じた輝度で発光する。本実施形態に係る表示装置では、閾値補正是画素回路10の外部に設けられた閾値補正回路20によって行われるが、閾値補正回路20には複雑な論理回路やメモリなどを設ける必要がない。

## 【0074】

ここで、初期電圧 $V_{reset}$ について説明する。図3に示す時刻 $t_0$ でスイッチ用TFT13が導通状態になると、駆動用TFT11はダイオード接続された状態になる。従来の有機ELディスプレイでは、駆動用TFTがダイオード接続されてから、駆動用TFTのゲート-ソース間電圧 $V_{gs}$ が閾値電圧 $V_{th}$ に十分に近づくまでの時間が、閾値補正期間となる。電圧 $V_{gs}$ が閾値電圧 $V_{th}$ に十分に近づけば、2つの駆動用TFT間の閾値電圧の差を検出できるからである。

## 【0075】

ところが、高精細の表示装置では、画素回路の選択期間が短く、選択期間内に電圧 $V_{gs}$ を閾値電圧 $V_{th}$ に十分に近づけられないことがある。特に、本実施形態に係る表示装置では、駆動用TFT11の閾値電圧 $V_{th}$ を検知するときに、コンデンサ26とデータ線 $S_j$ の寄生容量を充電する必要があるので、選択期間内に閾値電圧を検知する処理と補正後のデータ電圧を書き込む処理を行うためには工夫が必要である。

## 【0076】

そこで、本実施形態に係る表示装置では、補正後のデータ電圧を書き込む処理を開始する前に閾値電圧 $V_{th}$ のばらつきを検知するために、スイッチ25の作用によりデータ線 $S_j$ に固定の初期電圧 $V_{reset}$ が与えられる。これにより、駆動用TFT11の閾値電圧 $V_{th}$ に応じた電圧( $V_{DD} + V_x$ )がデータ線 $S_j$ に出力されるまでの時間を短縮することができる。したがって、閾値補正期間が短い場合でも、補正効果のばらつきを抑え、画質を向上させることができる。

## 【0077】

初期電圧 $V_{reset}$ は、閾値補正期間の長さや閾値補正に要求される精度などに基づき決定される。スイッチ用TFT13が導通状態にあり、駆動用TFT11がダイオード接続されているとき、駆動用TFT11の電流バランスに関して次式(3)が成立する。

## 【数1】

$$k(V_{gs}(t) - V_{th})^2 = -C \frac{dV_{gs}(t)}{dt} \quad \dots (3)$$

ただし、式(3)において、 $k$ は定数、 $C$ は保持容量と信号線容量の和である。

## 【0078】

この微分方程式を解くと、次式(4)が得られる。

## 【数2】

$$V_{gs}(t) = \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0} - V_{th}}} + V_{th} \quad \dots (4)$$

ただし、式(4)において、 $V_{gs0}$ は電圧 $V_{gs}$ の初期値である。

## 【0079】

閾値電圧が $V_{th}$ だけ異なる2つのTFTを考えたとき、所定時間経過後に2つのT

10

20

30

40

50

F T 間で電圧 V g s の差が V t h に近ければ、各 T F T の閾値電圧を検出できたと言える。電圧 V g s の差は、次式(5)で与えられる。

【数3】

$$\Delta V_{gs}(t) = \Delta V_{th} + \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0}-V_{th}-\Delta V_{th}}} - \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0}-V_{th}}} \quad \dots (5)$$

したがって、許容時間内に式(5)に示す V g s ( t ) が V t h に十分に近づくように電圧 V g s の初期値 V g s 0 を決定し、それに応じて初期電圧 V r e s e t を求めればよい。

10

【0080】

図4は、ダイオード接続された駆動用TFTのゲート-ソース間電圧 V g s の時間的変化の例を示す図である。図4には、閾値電圧が異なる2つのTFT ( V t h = -0.8 V と V t h = -1.0 V ) に対して、2種類の初期電圧 V g s 0 ( V g s 0 = -5 V と V g s 0 = -1.5 V ) を与えたときの結果が記載されている。

【0081】

2つのTFTに対して初期電圧 V g s 0 を与え、30 μs 経過後の電圧 V g s を比較する。V g s 0 = -5 V の場合には、30 μs 後に、2つの電圧はそれぞれの最終値 (-0.8 V と -1.0 V) から離れているが、両者の差は既に最終値 (0.2 V) にほぼ等しくなっている。これに対して、V g s 0 = -1.5 V の場合には、30 μs 後に、2つの電圧はそれぞれの最終値に接近しているが、両者の差は依然として最終値から離れている。

20

【0082】

このように、初期電圧 V g s 0 の絶対値が大きいほど、電圧 V g s の差は速く増大するので、閾値補正期間を短くすることができます。したがって、高い精度で閾値補正を行うためには、初期電圧 V g s 0 の絶対値を大きくすることが好ましい。一方、初期電圧 V g s 0 の絶対値を大きくすると、データ線 S j とコンデンサ 26 の充放電によって消費電力が増加する。したがって、プロセスによる閾値電圧のばらつきの程度や仕様を考慮して、初期電圧 V r e s e t を決定すればよい。

30

【0083】

次に、アナログバッファ 27について説明する。データ線 S j の容量がコンデンサ 26 の容量と比べて無視できる程度に小さい場合には、閾値補正回路 20 にアナログバッファ 27 を設ける必要はない。一方、数インチ以上の表示パネルでは、データ線 S j の容量は数 pF 以上になる場合が多いので、このような場合にはアナログバッファ 27 を設ける必要がある。この場合、アナログバッファ 27 としてボルテージホロワ回路（ユニティゲインアンプ）を用いれば、回路規模の増大を最小限に抑えながら駆動能力を高めることができる。

【0084】

また、アナログバッファ 27 に一般的な差動増幅器を用いた場合、差動対を形成するトランジスタの特性がばらつき、アナログバッファ 27 の特性がばらつくことがある。このようなばらつきが発生すると、表示画面には筋状のむらが現れ、表示品位が低下する。そこで、この不具合を防止するためには、アナログバッファ 27 を表示パネル上に形成せずに、表示パネル外の周辺 IC に内蔵すればよい。周辺 IC に内蔵される回路は、典型的には単結晶シリコンによるトランジスタで形成される。したがって、周辺 IC に内蔵すれば、特性のばらつきが極めて小さいアナログバッファ 27 を得ることができる。

40

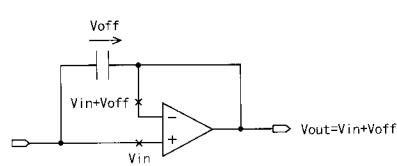

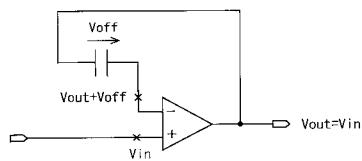

【0085】

また、上記の不具合を防止するために、アナログバッファ 27 として、オフセットキャンセル機能を有するバッファ（図 5 A ~ 図 5 D を参照）を用いてもよい。図 5 A に示すバッファでは、差動増幅器 31 の正側入力端子、負側入力端子および出力端子は、それぞれ、バッファの入力端子、コンデンサ 32 の一方の電極、および、バッファの出力端子に接

50

続されている。コンデンサ32の他方の電極とバッファの入力端子との間には、スイッチ33が設けられている。差動増幅器31の負側入力端子と出力端子との間には、スイッチ34が設けられている。コンデンサ32の他方の電極と差動増幅器31の出力端子との間には、スイッチ35が設けられている。スイッチ33、34は制御信号SC\_Aによって制御され、スイッチ35は制御信号SC\_Bによって制御される。

#### 【0086】

制御信号SC\_A、SC\_Bは、図5Bに示すように排他的にスイッチを導通状態にするレベル(ここでは、ハイレベルとする)になる。制御信号SC\_Aがハイレベルである間(図5Cを参照)、スイッチ33、34は導通状態、スイッチ35は非導通状態となる。このとき、差動増幅器31の正側入力端子と負側入力端子の間には、差動増幅器31のオフセット電圧Voffが現れる。オフセット電圧Voffは、コンデンサ32に保持される。10

#### 【0087】

制御信号SC\_Bがハイレベルである間(図5Dを参照)、スイッチ33、34は非導通状態、スイッチ35は導通状態となる。これに伴い、差動増幅器31の負側入力電圧はオフセット電圧Voffだけ変化し、差動増幅器31の出力電圧(バッファの出力電圧)も同じ量だけ変化して入力電圧Vinに等しくなる。このように、図5Aに示すバッファを用いれば、差動増幅器31のオフセット電圧をキャンセルすることができる。なお、オフセットキャンセル機能を有するバッファを表示パネル外の周辺ICに内蔵してもよい。

#### 【0088】

以下、本実施形態に係る表示装置の効果を説明する。本実施形態に係る表示装置によれば、ゲートドライバ回路3によって選択された画素回路10から駆動用TFT11の閾値電圧Vthに応じた電圧(VDD+Vx)を読み出し、データ電圧Vdataに補正電圧Vx(閾値電圧Vthに対応した電圧)を加算した電圧(Vdata+Vx)を駆動用TFT11のゲート端子に与えることができる。一般に、Pチャネル型の駆動用TFTでは、閾値電圧の絶対値を減算した電圧をゲート端子に与えれば、閾値電圧のばらつきを補償することができる。したがって、本実施形態に係る表示装置によれば、駆動用TFT11の閾値電圧を検出して閾値電圧のばらつきを補償し、有機EL素子15を所望の輝度で発光させることができる。20

#### 【0089】

また、閾値補正回路20を画素回路の外部に設け、データ線Sjを用いて閾値電圧を検出することにより、画素回路10の規模や面積を縮小することができる。また、閾値電圧を電圧信号として検出することにより、電流信号を帰還する場合とは異なり電流電圧変換素子が不要になるので、補正効果のばらつきを抑えることができる。また、閾値電圧に対応した補正電圧Vxをそのままデータ電圧Vdataに加算することにより、高い精度で閾値補正を行うことができる。また、カップリング容量を介さずに駆動用TFT11のゲート端子に所望の電圧を与えられるので、データ電圧Vdataの振幅を有効に利用し、消費電力を低減することができる。また、データ線Sjと駆動用TFT11との間に容量が設けられていないので、駆動用TFT11を容易に検査することができる。駆動用TFT11を検査するときには、電源配線Vpから駆動用TFT11のドレイン端子とゲート端子を経由してデータ線Sjに電流を流せばよい。40

#### 【0090】

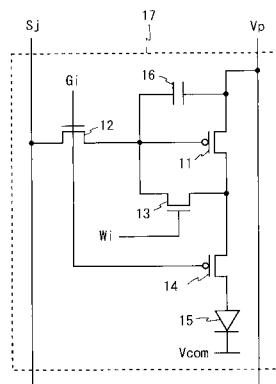

なお、本実施形態に係る表示装置は、画素回路10に代えて、図6Aや図6Bに示す画素回路を備えていてもよい。図6Aに示す画素回路17は、画素回路10に対して、スイッチ用TFT14を走査線Giに接続し、走査線Giと制御線Riを共通化する変更を施したものである。画素回路17では、スイッチ用TFT12、14は排他的に導通状態となる。また、図6Bに示す画素回路18は、画素回路10に対して、スイッチ用TFT13を制御線Riに接続し、制御線Riと制御線Wiを共通化する変更を施したものである。画素回路18では、スイッチ用TFT13、14は排他のに導通状態となる。

#### 【0091】

10

20

30

40

50

これら変形例に係る表示装置は、画素回路 10 を備えた表示装置と同様に動作し、同様の効果を奏する。これに加えて、スイッチ用 TFT 12 ~ 14 の制御端子に接続される配線を共通化して配線数を 3 本から 2 本に減らし、画素の開口率をさらに高くして、画面を明るくすることができる。

#### 【0092】

##### (第 2 の実施形態)

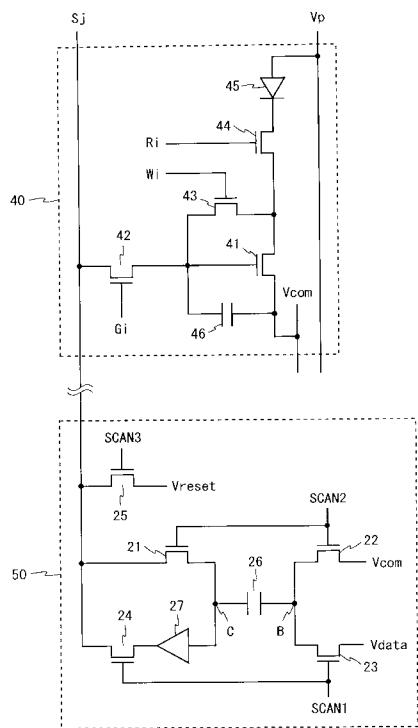

図 7 は、本発明の第 2 の実施形態に係る表示装置に含まれる画素回路と閾値補正回路の回路図である。図 7 に示す画素回路 40 と閾値補正回路 50 は、図 1 では画素回路 Aij と閾値補正回路 9 に相当する。図 7 に示すように、画素回路 40 は、駆動用 TFT 41、スイッチ用 TFT 42 ~ 44、有機 EL 素子 45、および、コンデンサ 46 を備えている。駆動用 TFT 41 は N チャネル型のエンハンスマント型、スイッチ用 TFT 42 ~ 44 は N チャネル型である。

#### 【0093】

画素回路 40 では、電源配線 Vp と共に陰極 Vcom との間に、電源配線 Vp 側から順に、有機 EL 素子 45、スイッチ用 TFT 44 および駆動用 TFT 41 が直列に設けられている。駆動用 TFT 41 のゲート端子とデータ線 Sj との間には、スイッチ用 TFT 42 が設けられている。駆動用 TFT 41 のゲート端子とドレイン端子との間にはスイッチ用 TFT 43 が設けられ、駆動用 TFT 41 のゲート端子と共に陰極 Vcom との間にはコンデンサ 46 が設けられている。スイッチ用 TFT 42 ~ 44 のゲート端子は、それぞれ、走査線 Gi および制御線 Wi、Ri に接続されている。

#### 【0094】

閾値補正回路 50 は、第 1 の実施形態に係る閾値補正回路 20 と同じ構造を有する。ただし、閾値補正回路 50 では、スイッチ 22 は、接点 B と共に陰極 Vcom の間に設けられている。それ以外の点では、閾値補正回路 50 は閾値補正回路 20 と同じである。

#### 【0095】

図 8 は、画素回路 40 に対するデータ書き込み時のタイミングチャートである。本実施形態に係る表示装置は、第 1 の実施形態に係る表示装置と同様に動作し、同様の効果を奏する。なお、一般に、N チャネル型の駆動用 TFT では、閾値電圧の絶対値を加算した電圧をゲート端子に与えれば、閾値電圧のばらつきを補償することができる。また、本実施形態についても、第 1 の実施形態と同様に、スイッチ用 TFT 42 ~ 44 の制御端子に接続される配線を共通化した変形例を構成することができる。

#### 【0096】

このように駆動用 TFT 41 とスイッチ用 TFT 42 ~ 44 をすべて N チャネル型とした画素回路 40 は、アモルファスシリコンを用いた表示パネルに適用できる。

#### 【0097】

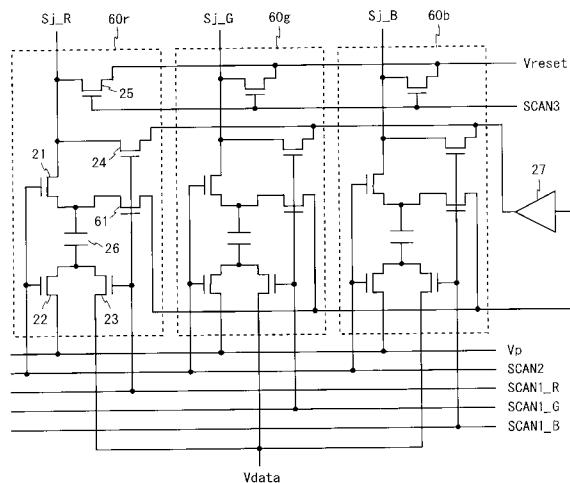

##### (第 3 の実施形態)

第 1 および第 2 の実施形態に係る表示装置では、アナログバッファ 27 はデータ線 Sj ごとに設けられている。ところが、例えば 2 インチ QVGA フルカラーパネル (RGB サブ画素を備える) では、サブ画素のピッチは約  $4.2 \mu m$  となる。駆動用 TFT の閾値電圧に応じた補正電圧  $Vx$  を保持するコンデンサ 26 はこのピッチで配置できるが、高性能のアナログバッファ 27 はこのピッチで配置できないことがある。そこで、第 3 の実施形態では、アナログバッファ 27 の数を減らした表示装置について説明する。

#### 【0098】

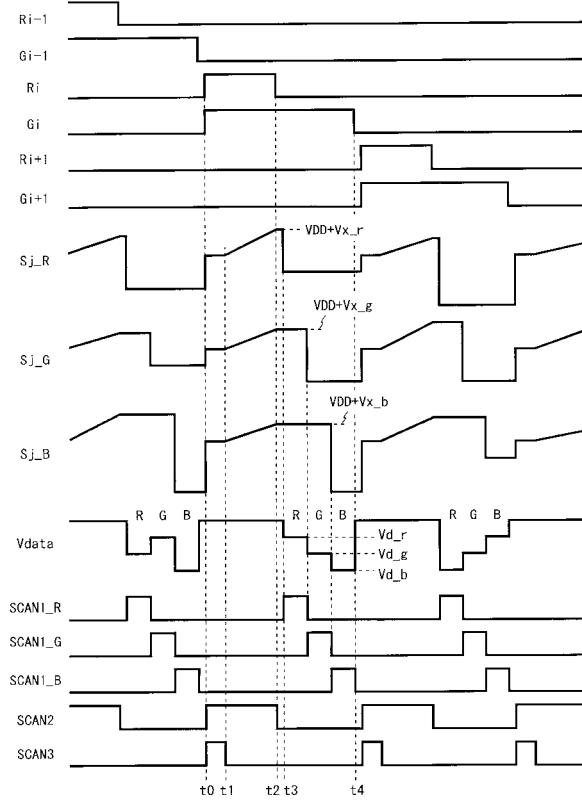

図 9 は、本発明の第 3 の実施形態に係る表示装置に含まれる閾値補正回路の回路図である。図 9 に示す閾値補正回路 60r、60g、60b は、図 1 では閾値補正回路 9 に相当する。また、図 9 に示すデータ線 Sj\_R、Sj\_G、Sj\_B は、図 1 ではデータ線 Sj に相当する。

#### 【0099】

図 9 に示すように、アナログバッファ 27 は、3 本のデータ線 Sj\_R、Sj\_G、Sj\_B に対応して設けられている。閾値補正回路 60r は、第 1 の実施形態に係る閾値補

10

20

30

40

50

正回路 20 (図 2) に、アナログバッファ 27 を共有する機能を追加したものである。具体的には、閾値補正回路 60r には、コンデンサ 26 の一方の電極 (図 9 で上側に描かれた電極) とアナログバッファ 27 の入力端子との間にスイッチ 61 が設けられている。また、スイッチ 23、24、61 のゲート端子は、制御線 SCAN1\_R に接続されている。閾値補正回路 60g、60b の構成も、これと同様である。

#### 【0100】

図 10 は、本実施形態に係る表示装置における画素回路に対するデータ書き込み時のタイミングチャートである。以下、図 10 を参照して、走査線 Gi とデータ線 Sj\_R、Sj\_G、Sj\_B に接続された 3 個の画素回路にデータを書き込むときの動作を説明する。

10 図 10 では、時刻 t0 から時刻 t4 までが 3 個の画素回路の選択期間となる。時刻 t2 より前では、3 個の画素回路の駆動用 TFT の閾値電圧を並列に検知する処理が行われ、時刻 t2 より後では、3 個の画素回路に対して順に補正後のデータ電圧を書き込む処理が行われる。なお、ここでは、表示装置は図 6B に示す画素回路 18 を備えることとしたが、画素回路の種類は任意でよい。

#### 【0101】

時刻 t0 より前では、走査線 Gi と制御線 Ri の電位はローレベルに制御されている。時刻 t0 において走査線 Gi と制御線 Ri、SCAN3 の電位がハイレベルに変化すると、データ線 Sj\_R、Sj\_G、Sj\_B の電位と、3 個の画素回路の駆動用 TFT のゲート端子電位は Vreset となる。

20

#### 【0102】

次に時刻 t1 において制御線 SCAN3 の電位がローレベルに変化すると、データ線 Sj\_R、Sj\_G、Sj\_B の電位はいずれも上昇する。時刻 t0 から時刻 t2 までの間、制御線 SCAN1\_R、SCAN1\_G、SCAN1\_B の電位はローレベルに、制御線 SCAN2 の電位はハイレベルに制御される。

30

#### 【0103】

時刻 t2 における 3 個の画素回路の駆動用 TFT のゲート端子電位を ( $VDD + Vx_r$ )、( $VDD + Vx_g$ )、( $VDD + Vx_b$ ) とする (ただし、 $Vx_r$ 、 $Vx_g$  および  $Vx_b$  は負の値)。時刻 t2 において制御線 Ri、SCAN2 の電位がローレベルに変化すると、閾値補正回路 60r、60g、60b のコンデンサ 26 には、それぞれ、電圧  $Vx_r$ 、 $Vx_g$ 、 $Vx_b$  が保持される。

30

#### 【0104】

次に時刻 t3 から時刻 t4 までの間に、制御線 SCAN1\_R、SCAN1\_G、SCAN1\_B の電位が所定時間ずつハイレベルとなり、これに同期して、D/A 変換器 8 から出力されるデータ電圧  $Vdata$  も、 $Vd_r$ 、 $Vd_g$ 、 $Vd_b$  と変化する。これにより、まず、データ線 Sj\_R に接続された画素回路の駆動用 TFT のゲート端子電位が ( $Vd_r + Vx_r$ ) となり、次に、データ線 Sj\_G に接続された画素回路の駆動用 TFT のゲート端子電位が ( $Vd_g + Vx_g$ ) となり、最後に、データ線 Sj\_B に接続された画素回路の駆動用 TFT のゲート端子電位が ( $Vd_b + Vx_b$ ) となる。

40

#### 【0105】

次に時刻 t4 において走査線 Gi の電位がローレベルに変化すると、3 個の画素回路のコンデンサには、それぞれ、電圧 ( $VDD - Vd_r - Vx_r$ )、( $VDD - Vd_g - Vx_g$ )、( $VDD - Vd_b - Vx_b$ ) が保持される。

40

#### 【0106】

時刻 t4 以降、3 個の画素回路の駆動用 TFT のゲート端子電位は、それぞれ、( $Vd_r + Vx_r$ )、( $Vd_g + Vx_g$ )、( $Vd_b + Vx_b$ ) のままである。このとき各駆動用 TFT を流れる電流の量はこれらの電位に応じて増減するが、閾値電圧が異なっていても、データ電圧が同じであれば電流量は同じになる。したがって、閾値電圧の値にかかわらず、各画素回路の有機 EL 素子にはデータ電圧  $Vdata$  に応じた量の電流が流れ、有機 EL 素子はデータ電圧  $Vdata$  に応じた輝度で発光する。

50

**【0107】**

なお、以上の説明では、3本のデータ線  $S_j_R$ 、 $S_j_G$ 、 $S_j_B$  に対応してアナログバッファを設けることとしたが、アナログバッファを  $p$  本（ $p$  は 2 以上の任意の整数）本のデータ線に対応して設けてもよい。

**【0108】**

このように本実施形態に係る表示装置によれば、データ線ごとに配置するには回路規模が大きいアナログバッファを複数のデータ線ごとに配置し、高精細の表示パネルを実現することができる。

**【0109】**

なお、以上に述べた各実施形態では、画素回路は電気光学素子として有機EL素子を含むこととしたが、有機EL素子以外の電流駆動型の電気光学素子（例えば、半導体LEDやFEDの発光部など）を含んでいてもよい。また、画素回路は、電気光学素子の駆動素子として、ガラス基板などの絶縁基板上に形成されたMOSトランジスタ（シリコンゲートMOS構造を含む）である TFT を含むこととしたが、閾値電圧を有する任意の電圧制御型の素子（すなわち、制御端子に印加された制御電圧に応じて出力電流が変化し、制御電圧が所定値以上または以下になると出力電流を遮断する素子）を含んでいてもよい。したがって、画素回路は、駆動素子として、半導体基板上に形成されるMOSトランジスタなども含む、一般的の絶縁ゲート型電界効果トランジスタを含んでいてもよい。

10

**【0110】**

また、第1の実施形態では、スイッチ用 TFT 12 が導通状態に変化するのとほぼ同じときに、スイッチ用 TFT 13 が導通状態に変化し、スイッチ用 TFT 14 が非導通状態に変化することとした。これに代えて、スイッチ用 TFT 12 が導通状態に変化するよりも前に、スイッチ用 TFT 13 が導通状態に変化し、スイッチ用 TFT 14 が非導通状態に変化してもよい。第2および第3の実施形態でも、これと同様である。

20

**【0111】**

また、本発明は上述した各実施形態に限定されるものではなく、種々の変更が可能である。異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態も、本発明の技術的範囲に含まれる。

**【産業上の利用可能性】****【0112】**

30

本発明の表示装置は、画素回路の規模を増大させずに、データ電圧の振幅を効率よく利用し、高い精度で閾値補正を行えるという効果を奏するので、各種の電子機器の表示装置として利用することができる。

【図1】

【図2】

【図3】

【図4】

【図 5 A】

【図 5 B】

【図 5 C】

【図 5 D】

【図 6 A】

【図 6 B】

【図 7】

【図 8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 2 P

H 05 B 33/14 A

(56)参考文献 特開2005-352411(JP, A)

特開2006-301250(JP, A)

特開2006-084899(JP, A)

特開2005-128521(JP, A)

特開2004-252110(JP, A)

国際公開第2005/013250(WO, A1)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30

G09G 3/20

|                |                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP5171807B2</a>                                                                       | 公开(公告)日 | 2013-03-27 |

| 申请号            | JP2009502428                                                                                      | 申请日     | 2007-10-01 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                            |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                              |         |            |

| [标]发明人         | 岸宣孝                                                                                               |         |            |

| 发明人            | 岸 宣孝                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                       |         |            |

| CPC分类号         | G09G3/3291 G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2320/0233 G09G2320/0295                     |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.641.D G09G3/20.611.H G09G3/20.642.A G09G3/20.642.P H05B33/14.A |         |            |

| 代理人(译)         | 岛田彰<br>川原贤治                                                                                       |         |            |

| 审查员(译)         | 福村 拓                                                                                              |         |            |

| 优先权            | 2007058021 2007-03-08 JP                                                                          |         |            |

| 其他公开文献         | <a href="#">JPWO2008108024A1</a>                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                         |         |            |

## 摘要(译)

在像素电路10中，TFT12和13接通，同时TFT14截止，并且取决于驱动TFT11的阈值电压V<sub>th</sub>的电压(V<sub>DD</sub> + V<sub>x</sub>)被读取到数据线S<sub>j</sub>上。此外，源极驱动器电路中的开关21和22导通，并且电压V<sub>x</sub>保持在电容器26。接着，TFT13截止，开关21至24的状态被切换，并且电压(V<sub>data</sub> + V<sub>x</sub>)被应用于数据线S<sub>j</sub>。此外，TFT14在TFT14导通时截止。在TFT14导通之后流过有机EL元件15的电流由驱动TFT11的栅极端子的电压(V<sub>data</sub> + V<sub>x</sub>)确定。因此，可以有效地利用在不增加像素电路10的比例的情况下，以高精度补偿数据电压的幅度并补偿驱动TFT11的阈值电压的变化。

$$(V_{GS}(t) - V_{th})^2 = -C \frac{dV_{GS}(t)}{dt} \quad \dots (3)$$