(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4158570号

(P4158570)

(45) 発行日 平成20年10月1日(2008.10.1)

(24) 登録日 平成20年7月25日(2008.7.25)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

G09G 3/30 K

G09G 3/30 J

G09G 3/20 6 1 1 H

G09G 3/20 6 2 3 R

G09G 3/20 6 2 4 B

請求項の数 34 (全 40 頁) 最終頁に続く

(21) 出願番号

特願2003-82368 (P2003-82368)

(22) 出願日

平成15年3月25日 (2003.3.25)

(65) 公開番号

特開2004-287345 (P2004-287345A)

(43) 公開日

平成16年10月14日 (2004.10.14)

審査請求日

平成17年1月18日 (2005.1.18)

前置審査

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 白崎 友之

東京都八王子市石川町2951番地の5

カシオ計算機株式会社 八王子研究所内

(72) 発明者 服部 励治

福岡県福岡市西区姪浜町200-1-10

9

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】表示駆動装置及び表示装置並びにその駆動制御方法

(57) 【特許請求の範囲】

【請求項 1】

行方向に延伸して配列された複数の走査線及び列方向に延伸して配列された複数の信号線の各交点に配列された複数の表示画素を有する表示パネルを表示信号に応じて駆動する表示駆動装置において、

第1のクロック信号が供給され、前記複数の走査線の各々に沿って配列された前記各表示画素を選択状態とする走査信号を出力するタイミングを設定する第1の出力信号を出力する第1のシフトレジスタ回路と、

第2のクロック信号が供給され、前記複数の信号線の各々に対応した第2の出力信号を出力する第2のシフトレジスタ回路と、

前記表示信号を前記第2のシフトレジスタ回路より供給される前記第2の出力信号に応じたタイミングで順次取り込み、取り込んだ前記表示信号を出力する表示信号保持回路と、

前記表示信号保持回路より出力される前記表示信号に基づいて、前記表示パネルに前記表示信号に応じた画像表示を行わせる制御を行う駆動制御回路と、

前記表示信号を特定の信号に設定し、前記表示信号保持回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に一括して印加した後、前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記第1のシフトレジスタ回路から出力される前

記第1の出力信号及び前記第2のシフトレジスタ回路から出力される前記第2の出力信号に基づくタイミングで、当該表示画素の発光特性に関連する特定量を順次抽出する特定量抽出手段と、

前記抽出された特定量を記憶する記憶手段と、

前記特定量に基づく補正值を用いて、前記表示画素を所望の輝度階調で発光動作させるための前記表示信号を補正する信号補正手段と、

を備えることを特徴とする表示駆動装置。

#### 【請求項2】

前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、該表示画素に流れる駆動電流に対応する電流成分の電流値を前記特定量として測定することを特徴とする請求項1記載の表示駆動装置。 10

#### 【請求項3】

前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記表示画素に流れる前記駆動電流に対応して蓄積された電圧成分に基づいて、該表示画素に流れる電流の電流値を前記特定量として測定することを特徴とする請求項2記載の表示駆動装置。

#### 【請求項4】

前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記表示画素に流れる前記駆動電流に対応して蓄積された電圧成分に基づいて、前記表示駆動装置に流れる電流の電流値を前記特定量として測定することを特徴とする請求項2記載の表示駆動装置。 20

#### 【請求項5】

前記特定量抽出手段は、前記特定量として測定された電流値をデジタル信号に変換して抽出することを特徴とする請求項2乃至4のいずれかに記載の表示駆動装置。

#### 【請求項6】

前記信号補正手段は、前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、前記補正值を設定することを特徴とする請求項2乃至5のいずれかに記載の表示駆動装置。

#### 【請求項7】

前記信号補正手段は、前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を実行することを特徴とする請求項6記載の表示駆動装置。 30

#### 【請求項8】

前記特定量抽出手段は、

前記表示画素に対して、前記特定の信号電圧を印加する書込動作時には、前記表示画素に前記駆動電流を流すための駆動電源電圧を印加し、

前記表示画素の各々から前記特定量を抽出する読出動作時には、前記表示画素への前記駆動電源電圧の印加を遮断することを特徴とする請求項2記載の表示駆動装置。

#### 【請求項9】

前記特定量抽出手段は、

少なくとも、前記書込動作時に、前記表示画素に前記駆動電源電圧を印加する書込制御スイッチと、

前記読出動作時に、前記表示画素から前記特定量を抽出する読出制御スイッチと、を備えることを特徴とする請求項8記載の表示駆動装置。 40

#### 【請求項10】

前記特定量抽出手段は、

前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、

前記読出動作時に、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする請求項8又は9記載の表示駆動装置。

#### 【請求項11】

前記特定の信号電圧は、前記表示画素を最高の輝度階調で発光動作させるための最高階調電圧に設定していることを特徴とする請求項1乃至9のいずれかに記載の表示駆動装置。

**【請求項12】**

前記特定量抽出手段は、前記複数の表示画素を選択状態に設定する走査信号に基づいて、前記読み出動作を実行することを特徴とする請求項8乃至11のいずれかに記載の表示駆動装置。

**【請求項13】**

前記特定量抽出手段は、前記複数の表示画素を所望の輝度階調で発光動作させる階調信号電圧に基づいて、前記読み出動作を実行することを特徴とする請求項8乃至11のいずれかに記載の表示駆動装置。 10

**【請求項14】**

行及び列方向に延伸して配設された複数の走査線及び信号線の各交点に、複数の表示画素が配列された表示パネルと、

第1のクロック信号が供給され、該第1のクロック信号に応じたタイミングで前記複数の走査線の各々に対応する第1の出力信号を出力する第1のシフトレジスタ回路を有し、前記第1の出力信号に応じたタイミングで前記表示パネルの各行ごとの前記表示画素を選択状態に設定する走査駆動回路と、

第2のクロック信号が供給され、前記複数の信号線の各々に対応した第2の出力信号を出力する第2のシフトレジスタ回路と、所望の画像情報を表示するための表示信号を前記第2のシフトレジスタ回路より供給される前記第2の出力信号に応じたタイミングで順次取り込み、取り込んだ前記表示信号を出力する表示信号保持回路と、前記表示信号保持回路から出力される前記表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加する信号駆動回路と、 20

前記表示画素の各々の発光特性に応じて、前記表示画素を所望の輝度階調で発光動作させるための表示信号を補正する補正制御回路と、

を備え、

前記補正制御回路は、

前記表示信号を特定の信号に設定し、前記信号駆動回路における前記表示信号保持回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、走査駆動回路より出力される前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に一括して印加した後、前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記走査駆動回路における前記第1のシフトレジスタ回路から出力される前記第1の出力信号及び前記信号駆動回路における前記第2のシフトレジスタ回路から出力される前記第2の出力信号に基づくタイミングで、当該表示画素の発光特性に関連する特定量を順次抽出する特定量抽出手段と、 30

前記抽出された特定量を記憶する記憶手段と、

前記特定量に基づく補正值を用いて、前記表示信号を補正して前記信号駆動回路に供給する信号補正手段と、 40

を有することを特徴とする表示装置。

**【請求項15】**

前記表示画素は、

前記階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、

前記駆動電流の電流値に応じた輝度階調で発光動作する電流制御型の発光素子と、

を備え、

前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に対応する電流成分の電流値を前記特定量として測定することを特徴とする請求項14記載の表示装置。 50

**【請求項 16】**

前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光駆動回路に蓄積された前記電圧成分に基づいて、前記発光素子に流れる電流の電流値を前記特定量として測定することを特徴とする請求項15記載の表示装置。

**【請求項 17】**

前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に応じた電圧成分を蓄積する蓄積手段を備え、

前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記特定量抽出手段に蓄積された前記電圧成分に基づいて、前記補正制御回路に流れる電流の電流値を前記特定量として測定することを特徴とする請求項15記載の表示装置。 10

**【請求項 18】**

前記補正制御回路は、前記特定量として測定された電流値をデジタル信号に変換して、前記記憶手段に記憶することを特徴とする請求項15乃至17のいずれかに記載の表示装置。

**【請求項 19】**

前記補正制御回路は、前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、前記補正值を設定し、前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を実行することを特徴とする請求項15乃至18のいずれかに記載の表示装置。 20

**【請求項 20】**

前記補正制御回路は、

前記表示画素に対して、前記特定の信号電圧を印加する書込動作時には、前記表示画素に前記駆動電流を流すための駆動電源電圧を印加し、

前記表示画素の各々から前記特定量を抽出する読出動作時には、前記表示画素への前記駆動電源電圧の印加を遮断することを特徴とする請求項15乃至19のいずれかに記載の表示装置。 20

**【請求項 21】**

前記補正制御回路は、

前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、 30

前記読出動作時に、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする請求項20記載の表示装置。

**【請求項 22】**

前記特定の信号電圧は、前記発光素子を最高の輝度階調で発光動作させるための最高階調電圧に設定されていることを特徴とする請求項14乃至21のいずれかに記載の表示装置。

**【請求項 23】**

前記補正制御回路は、前記走査駆動回路により前記表示画素に印加される前記走査信号に基づいて、前記読出動作を実行することを特徴とする請求項20乃至22のいずれかに記載の表示装置。 40

**【請求項 24】**

前記補正制御回路は、前記信号駆動回路により前記表示画素に印加される前記階調信号電圧に基づいて、前記読出動作を実行することを特徴とする請求項20乃至22のいずれかに記載の表示装置。

**【請求項 25】**

前記補正制御回路は、前記表示パネルを構成する基板上に、前記表示画素とともに一体的に形成されていることを特徴とする請求項14乃至24のいずれかに記載の表示装置。

**【請求項 26】**

前記補正制御回路は、前記走査駆動回路と一体的に形成されていることを特徴とする請求項23記載の表示装置。 50

**【請求項 27】**

前記補正制御回路は、前記信号駆動回路と一体的に形成されていることを特徴とする請求項24記載の表示装置。

**【請求項 28】**

前記補正制御回路は、少なくとも、

前記書込動作時に、前記表示画素に前記駆動電源電圧を印加するnチャネル型トランジスタからなる書込制御スイッチと、

前記読出動作時に、前記表示画素から前記特定量を抽出するnチャネル型トランジスタからなる読出制御スイッチと、

を備え、

10

前記発光駆動回路は、少なくとも、

前記走査駆動回路から印加される前記走査信号により、前記信号駆動回路から印加される前記階調信号電圧を取り込むnチャネル型トランジスタからなる選択スイッチと、

前記階調信号電圧に応じた電流値を有する駆動電流を流すnチャネル型トランジスタからなる発光駆動スイッチと、

を備えることを特徴とする請求項14乃至27のいずれかに記載の表示装置。

**【請求項 29】**

行及び列方向に延伸して配設された複数の走査線及び信号線の各交点に、複数の表示画素が配列された表示パネルと、所定のタイミングで前記表示パネルの各行ごとの前記表示画素に走査信号を順次印加して、選択状態に設定する走査駆動回路と、所望の画像情報を表示するための表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加する信号駆動回路と、を備え、前記信号駆動回路により前記表示画素の各々に、前記階調信号電圧を印加することにより、前記表示画素を所定の輝度階調で発光動作させて、前記表示パネルに所望の画像情報を表示する表示装置の駆動制御方法において、

20

前記走査駆動回路は、第1のクロック信号に応じたタイミングで前記複数の走査線の各々に対応する第1の出力信号を出力し、前記第1の出力信号に応じたタイミングで前記表示パネルの各行ごとの前記表示画素に走査信号を順次印加して選択状態に設定し、

前記信号駆動回路は、第2のクロック信号に応じたタイミングで前記複数の信号線の各々に対応する第2の出力信号を出力し、所望の画像情報を表示するための表示信号を前記第2の出力信号に応じたタイミングで順次取り込み、出力し、前記表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加し、

30

前記表示信号を特定の信号に設定し、前記信号駆動回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、走査駆動回路より出力される前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に対して、特定の信号電圧を一括して印加するステップと、

前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記走査駆動回路における前記第1の出力信号及び前記信号駆動回路における前記第2の出力信号に基づくタイミングで、当該表示画素に流れる駆動電流に対応する電流成分の電流値を測定するステップと、

40

前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、補正值を生成するステップと、

前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を行つて前記信号駆動回路に供給するステップと、

を含むことを特徴とする表示装置の駆動制御方法。

**【請求項 30】**

前記表示画素は、前記階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、前記駆動電流の電流値に応

50

じた輝度階調で発光動作する電流制御型の発光素子と、を備え、

前記電流成分の電流値を測定するステップは、前記発光駆動回路に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に対応する電流成分の電流値を測定することを特徴とする請求項 29 記載の表示装置の駆動制御方法。

#### 【請求項 31】

前記特定の信号電圧を印加するステップは、前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、

前記電流成分の電流値を測定するステップは、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする請求項 29 又は 30 記載の表示装置の駆動制御方法。

#### 【請求項 32】

前記特定の信号電圧は、前記発光素子を最高の輝度階調で発光動作させるための最高階調電圧に設定されていることを特徴とする請求項 29 乃至 31 のいずれかに記載の表示装置の駆動制御方法。

#### 【請求項 33】

前記電流成分の電流値を測定するステップは、前記走査駆動回路により前記表示画素に印加される前記走査信号に基づいて実行されることを特徴とする請求項 29 乃至 32 のいずれかに記載の表示装置の駆動制御方法。

#### 【請求項 34】

前記電流成分の電流値を測定するステップは、前記信号駆動回路により前記表示画素に印加される前記階調信号電圧に基づいて実行されることを特徴とする請求項 29 乃至 32 のいずれかに記載の表示装置の駆動制御方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、表示駆動装置及び表示装置並びにその駆動制御方法に関し、特に、表示データに応じた電流を供給することにより所定の輝度階調で発光する電流制御型（又は、電流駆動型）の発光素子を、複数配列してなる表示パネル（画素アレイ）に適用可能な表示駆動装置、及び、該表示駆動装置を備えた表示装置、並びに、該表示装置における駆動制御方法に関する。

##### 【0002】

##### 【従来の技術】

近年、パーソナルコンピュータや映像機器のモニタやディスプレイとして、液晶表示装置（LCD）等の陰極線管（CRT）を適用した表示装置に替わる表示デバイスの普及が著しい。特に、液晶表示装置は、旧来の表示装置に比較して、薄型軽量化、省スペース化、低消費電力化等が可能であるため、急速に普及している。また、比較的小型の液晶表示装置は、近年普及が著しい携帯電話やデジタルビデオカメラ、デジタルスチルカメラ、携帯情報端末（PDA）等の表示デバイスとしても広く適用されている。

##### 【0003】

このような液晶表示装置に続く次世代の表示デバイス（ディスプレイ）として、有機エレクトロルミネッセンス素子（以下、「有機EL素子」と略記する）や無機エレクトロルミネッセンス素子（「無機EL素子」と略記する）、あるいは、発光ダイオード（LED）等のような自己発光型の光学要素を、マトリクス状に配列した表示パネルを備えた発光素子型の表示デバイス（以下、「発光素子型ディスプレイ」と記す）の本格的な実用化が期待されている。

##### 【0004】

特に、アクティブマトリックス駆動方式を適用した発光素子型ディスプレイは、上記液晶表示装置に比較して、表示応答速度が速く、視野角依存性もなく、また、高輝度・高コントラスト化、表示画質の高精細化、低消費電力化等が可能であるとともに、液晶表示装置のようにバックライトを必要としないので、一層の薄型軽量化が可能であるという極めて優位な特徴を有している。

10

20

30

40

50

**【 0 0 0 5 】**

ここで、上述した発光素子型ディスプレイにおいては、発光素子の動作（発光状態）を制御するための駆動制御機構や制御方法が種々提案されている。例えば、特許文献1等に記載されているように、表示パネルを構成する各表示画素に、上記発光素子に加えて、該発光素子を発光駆動制御するための複数のスイッチング素子からなる駆動回路（以下、便宜的に、「発光駆動回路」と記す）を備えた構成が知られている。

**【 0 0 0 6 】**

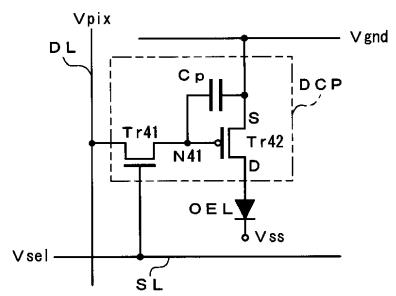

図21は、従来技術における有機EL素子を備えた発光素子型ディスプレイの各表示画素の回路構成例を示す等価回路図である。

特許文献1に記載された表示画素は、図21に示すように、表示パネル（図示を省略）にマトリクス状に配設された複数の走査ライン（走査線）SL及びデータライン（信号線）DLの各交点近傍に、ゲート端子が走査ラインSLに、ソース端子及びドレイン端子がデータラインDL及び接点N41に各々接続された薄膜トランジスタ（TFT）Tr41と、ゲート端子が接点N41に、ソース端子が接地電位Vgndに各々接続された薄膜トランジスタTr42と、を備えた発光駆動回路DCP、及び、該発光駆動回路DCPの薄膜トランジスタTr42のドレイン端子にアノード端子が接続され、カソード端子が接地電位Vgndよりも低い負電圧からなる定電源電圧Vssに接続された有機EL素子OELを有して構成されている。

**【 0 0 0 7 】**

なお、図21において、Cpは、薄膜トランジスタTr42のゲート-ソース間に形成される寄生容量（保持容量）である。また、薄膜トランジスタTr41はnチャンネル型MOSトランジスタ（NMOSトランジスタ）により構成され、薄膜トランジスタTr42はpチャンネル型MOSトランジスタ（PMOSトランジスタ）により構成されている。そして、このような構成を有する発光駆動回路DCPにおいては、以下に示すように、薄膜トランジスタTr41及びTr42からなる2個のトランジスタ（スイッチング手段）を所定のタイミングでオン、オフ制御することにより、有機EL素子OELを発光制御する。

**【 0 0 0 8 】**

すなわち、発光駆動回路DCPにおいて、まず、図示を省略したゲートドライバ（走査線駆動回路）により、走査ラインSLにハイレベルの走査信号Vselを印加して表示画素を選択状態に設定すると、薄膜トランジスタTr41がオン動作し、図示を省略したデータドライバ（データ線駆動回路）によりデータラインDLに印加された、表示データ（画像信号）に応じた階調信号電圧Vpixが薄膜トランジスタTr41を介して、薄膜トランジスタTr42のゲート端子に印加される。これにより、薄膜トランジスタTr42が上記信号電圧Vpixに応じた導通状態でオン動作して、接地電位Vgndから薄膜トランジスタTr42を介して定電源電圧Vss方向に所定の発光駆動電流が流れ、有機EL素子OELが上記表示データ（階調信号電圧Vpix）に応じた輝度階調で発光する。

**【 0 0 0 9 】**

次いで、走査ラインSLにローレベルの走査信号Vselを印加して表示画素を非選択状態に設定すると、薄膜トランジスタTr41がオフ動作することにより、データラインDLと発光駆動回路DCPとが電気的に遮断される。これにより、薄膜トランジスタTr42のゲート端子に印加されていた電圧が寄生容量Cpにより保持されて、薄膜トランジスタTr42は、オン状態を維持することになり、接地電位Vgndから薄膜トランジスタTr42を介して有機EL素子OELに発光駆動電流が流れる状態が維持され、発光動作が継続される。この発光動作は、次の表示データに応じた信号電圧Vpixが各表示画素に書き込まれるまで、例えば、1フレーム期間継続されるように制御される。

このような駆動制御方法は、各表示画素（薄膜トランジスタTr42）に印加する電圧（階調信号電圧Vpix）を調整することにより、有機EL素子OELに流す発光駆動電流の電流値を制御して、所定の輝度階調で発光動作させていることから、電圧駆動方式又は電圧印加方式と呼ばれている。

10

20

30

40

50

【0010】

【特許文献1】

特開2002-156923号公報 (第4頁、図2)

【0011】

【発明が解決しようとする課題】

しかしながら、上述したような発光駆動回路を表示画素に備えた表示装置においては、以下に示すような問題を有していた。

すなわち、図21に示したような発光駆動回路においては、2個の薄膜トランジスタTr41及びTr42の素子特性(チャネル抵抗等)や有機EL素子OELの素子特性(抵抗等)が、周囲の温度等の外的環境や使用時間に依存して変化(劣化)した場合には、有機EL素子OELに供給される発光駆動電流の電流値に影響を与えるため、長期間にわたり安定的に所望の発光特性(所定の輝度階調での表示)を実現することが困難になるという問題を有していた。10

【0012】

また、表示画質の高精細化を図るために、表示パネルを構成する各表示画素を微細化すると、発光駆動回路を構成する薄膜トランジスタTr41及びTr42の動作特性(ソース-ドレイン間電流等)のバラツキが大きくなるため、適正な階調制御が行えなくなり、各表示画素の表示特性にバラツキが生じて画質の劣化を招くという問題を有していた。

【0013】

そこで、本発明は、上述した種々の問題点に鑑み、表示画素(発光素子)を所望の輝度階調で発光動作させるディスプレイにおいて、外的環境の変化や経時劣化による各表示画素の発光特性のバラツキを抑制して、表示データに応じた適切な輝度階調で発光動作させることができる発光駆動装置を提供し、以て、画像情報を良好に表示することができる表示装置並びにその駆動制御方法を提供することを目的とする。20

【0014】

【課題を解決するための手段】

請求項1記載の表示駆動装置は、行方向に延伸して配列された複数の走査線及び列方向に延伸して配列された複数の信号線の各交点に配列された複数の表示画素を有する表示パネルを表示信号に応じて駆動する表示駆動装置において、第1のクロック信号が供給され、前記複数の走査線の各々に沿って配列された前記各表示画素を選択状態とする走査信号を出力するタイミングを設定する第1の出力信号を出力する第1のシフトレジスタ回路と、第2のクロック信号が供給され、前記複数の信号線の各々に対応した第2の出力信号を出力する第2のシフトレジスタ回路と、前記表示信号を前記第2のシフトレジスタ回路より供給される前記第2の出力信号に応じたタイミングで順次取り込み、取り込んだ前記表示信号を出力する表示信号保持回路と、前記表示信号保持回路より出力される前記表示信号に基づいて、前記表示パネルに前記表示信号に応じた画像表示を行わせる制御を行う駆動制御回路と、前記表示信号を特定の信号に設定し、前記表示信号保持回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に一括して印加した後、前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記第1のシフトレジスタ回路から出力される前記第1の出力信号及び前記第2のシフトレジスタ回路から出力される前記第2の出力信号に基づくタイミングで、当該表示画素の発光特性に関連する特定量を順次抽出する特定量抽出手段と、前記抽出された特定量を記憶する記憶手段と、前記特定量に基づく補正值を用いて、前記表示画素を所望の輝度階調で発光動作させるための前記表示信号を補正する信号補正手段と、を備えることを特徴とする。30

【0015】

請求項2記載の表示駆動装置は、請求項1記載の表示駆動装置において、前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、該表示画素に流れる駆動電流に対応する電流成分の電流値を前記特定量として測定することを特徴とする40

。

請求項 3 記載の表示駆動装置は、請求項 2 記載の表示駆動装置において、前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記表示画素に流れる前記駆動電流に対応して蓄積された電圧成分に基づいて、該表示画素に流れる電流の電流値を前記特定量として測定することを特徴とする。

#### 【 0 0 1 6 】

請求項 4 記載の表示駆動装置は、請求項 2 記載の表示駆動装置において、前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記表示画素に流れる前記駆動電流に対応して蓄積された電圧成分に基づいて、前記表示駆動装置に流れる電流の電流値を前記特定量として測定することを特徴とする。

10

請求項 5 記載の表示駆動装置は、請求項 2 乃至 4 のいずれかに記載の表示駆動装置において、前記特定量抽出手段は、前記特定量として測定された電流値をデジタル信号に変換して抽出することを特徴とする。

#### 【 0 0 1 7 】

請求項 6 記載の表示駆動装置は、請求項 2 乃至 5 のいずれかに記載の表示駆動装置において、前記信号補正手段は、前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、前記補正值を設定することを特徴とする。

請求項 7 記載の表示駆動装置は、請求項 6 記載の表示駆動装置において、前記信号補正手段は、前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を実行することを特徴とする。

20

#### 【 0 0 1 8 】

請求項 8 記載の表示駆動装置は、請求項 2 記載の表示駆動装置において、前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加する書込動作時には、前記表示画素に前記駆動電流を流すための駆動電源電圧を印加し、前記表示画素の各々から前記特定量を抽出する読出動作時には、前記表示画素への前記駆動電源電圧の印加を遮断することを特徴とする。

請求項 9 記載の表示駆動装置は、請求項 8 記載の表示駆動装置において、前記特定量抽出手段は、少なくとも、前記書込動作時に、前記表示画素に前記駆動電源電圧を印加する書込制御スイッチと、前記読出動作時に、前記表示画素から前記特定量を抽出する読出制御スイッチと、を備えることを特徴とする。

30

#### 【 0 0 2 0 】

請求項 10 記載の表示駆動装置は、請求項 8 又は 9 記載の表示駆動装置において、前記特定量抽出手段は、前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、前記読出動作時に、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする。

請求項 11 記載の表示駆動装置は、請求項 1 乃至 9 のいずれかに記載の表示駆動装置において、前記特定の信号電圧は、前記表示画素を最高の輝度階調で発光動作させるための最高階調電圧に設定されていることを特徴とする。

#### 【 0 0 2 1 】

40

請求項 12 記載の表示駆動装置は、請求項 8 乃至 11 のいずれかに記載の表示駆動装置において、前記特定量抽出手段は、前記複数の表示画素を選択状態に設定する走査信号に基づいて、前記読出動作を実行することを特徴とする。

請求項 13 記載の表示駆動装置は、請求項 8 乃至 11 のいずれかに記載の表示駆動装置において、前記特定量抽出手段は、前記複数の表示画素を所望の輝度階調で発光動作させる階調信号電圧に基づいて、前記読出動作を実行することを特徴とする。

#### 【 0 0 2 2 】

請求項 14 記載の表示装置は、行及び列方向に延伸して配設された複数の走査線及び信号線の各交点に、複数の表示画素が配列された表示パネルと、第 1 のクロック信号が供給され、該第 1 のクロック信号に応じたタイミングで前記複数の走査線の各々に対応する第

50

1の出力信号を出力する第1のシフトレジスタ回路を有し、前記第1の出力信号に応じたタイミングで前記表示パネルの各行ごとの前記表示画素を選択状態に設定する走査信号を出力する走査駆動回路と、第2のクロック信号が供給され、前記複数の信号線の各々に対応した第2の出力信号を出力する第2のシフトレジスタ回路と、所望の画像情報を表示するための表示信号を前記第2のシフトレジスタ回路より供給される前記第2の出力信号に応じたタイミングで順次取り込み、取り込んだ前記表示信号を出力する表示信号保持回路と、前記表示信号保持回路から出力される前記表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加する信号駆動回路と、前記表示画素の各々の発光特性に応じて、前記表示画素を所望の輝度階調で発光動作させるための表示信号を補正する補正制御回路と、を備え、前記補正制御回路は、前記表示信号を特定の信号に設定し、前記信号駆動回路における前記表示信号保持回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、走査駆動回路より出力される前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に一括して印加した後、前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記走査駆動回路における前記第1のシフトレジスタ回路から出力される前記第1の出力信号及び前記信号駆動回路における前記第2のシフトレジスタ回路から出力される前記第2の出力信号に基づくタイミングで、当該表示画素の発光特性に関連する特定量を順次抽出する特定量抽出手段と、前記抽出された特定量を記憶する記憶手段と、前記特定量に基づく補正值を用いて、前記表示信号を補正して前記信号駆動回路に供給する信号補正手段と、を有することを特徴とする。

#### 【0023】

請求項1\_5記載の表示装置は、請求項1\_4記載の表示装置において、前記表示画素は、前記階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、前記駆動電流の電流値に応じた輝度階調で発光動作する電流制御型の発光素子と、を備え、前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に対応する電流成分の電流値を前記特定量として測定することを特徴とする。

#### 【0024】

請求項1\_6記載の表示装置は、請求項1\_5記載の表示装置において、前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光駆動回路に蓄積された前記電圧成分に基づいて、前記発光素子に流れる電流の電流値を前記特定量として測定することを特徴とする。

請求項1\_7記載の表示装置は、請求項1\_5記載の表示装置において、前記特定量抽出手段は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に応じた電圧成分を蓄積する蓄積手段を備え、前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加した場合の、前記特定量抽出手段に蓄積された前記電圧成分に基づいて、前記補正制御回路に流れる電流の電流値を前記特定量として測定することを特徴とする。

#### 【0025】

請求項1\_8記載の表示装置は、請求項1\_5乃至1\_7のいずれかに記載の表示装置において、前記補正制御回路は、前記特定量として測定された電流値をデジタル信号に変換して、前記記憶手段に記憶することを特徴とする。

請求項1\_9記載の表示装置は、請求項1\_5乃至1\_8のいずれかに記載の表示装置において、前記補正制御回路は、前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、前記補正值を設定し、前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を実行することを特徴とする。

#### 【0026】

請求項2\_0記載の表示装置は、請求項1\_5乃至1\_9のいずれかに記載の表示装置におい

10

20

30

40

50

て、前記補正制御回路は、前記表示画素に対して、前記特定の信号電圧を印加する書込動作時には、前記表示画素に前記駆動電流を流すための駆動電源電圧を印加し、前記表示画素の各々から前記特定量を抽出する読出動作時には、前記表示画素への前記駆動電源電圧の印加を遮断することを特徴とする。

## 【0027】

請求項2\_1記載の表示装置は、請求項2\_0記載の表示装置において、前記補正制御回路は、前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、前記読出動作時に、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする。

## 【0028】

請求項2\_2記載の表示装置は、請求項1\_4乃至2\_1のいずれかに記載の表示装置において、前記特定の信号電圧は、前記発光素子を最高の輝度階調で発光動作させるための最高階調電圧に設定されていることを特徴とする。

請求項2\_3記載の表示装置は、請求項2\_0乃至2\_2のいずれかに記載の表示装置において、前記補正制御回路は、前記走査駆動回路により前記表示画素に印加される前記走査信号に基づいて、前記読出動作を実行することを特徴とする。

## 【0029】

請求項2\_4記載の表示装置は、請求項2\_0乃至2\_2のいずれかに記載の表示装置において、前記補正制御回路は、前記信号駆動回路により前記表示画素に印加される前記階調信号電圧に基づいて、前記読出動作を実行することを特徴とする。

請求項2\_5記載の表示装置は、請求項1\_4乃至2\_4のいずれかに記載の表示装置において、前記補正制御回路は、前記表示パネルを構成する基板上に、前記表示画素とともに一体的に形成されていることを特徴とする。

請求項2\_6記載の表示装置は、請求項2\_3記載の表示装置において、前記補正制御回路は、前記走査駆動回路と一体的に形成されていることを特徴とする。

請求項2\_7記載の表示装置は、請求項2\_4記載の表示装置において、前記補正制御回路は、前記信号駆動回路と一体的に形成されていることを特徴とする。

## 【0030】

請求項2\_8記載の表示装置は、請求項1\_4乃至2\_7のいずれかに記載の表示装置において、前記補正制御回路は、少なくとも、前記書込動作時に、前記表示画素に前記駆動電源電圧を印加するnチャネル型トランジスタからなる書込制御スイッチと、前記読出動作時に、前記表示画素から前記特定量を抽出するnチャネル型トランジスタからなる読出制御スイッチと、を備え、前記発光駆動回路は、少なくとも、前記走査駆動回路から印加される前記走査信号により、前記信号駆動回路から印加される前記階調信号電圧を取り込むnチャネル型トランジスタからなる選択スイッチと、前記階調信号電圧に応じた電流値を有する駆動電流を流すnチャネル型トランジスタからなる発光駆動スイッチと、を備えることを特徴とする。

## 【0031】

請求項2\_9記載の表示装置の駆動制御方法は、行及び列方向に延伸して配設された複数の走査線及び信号線の各交点に、複数の表示画素が配列された表示パネルと、所定のタイミングで前記表示パネルの各行ごとの前記表示画素に走査信号を順次印加して、選択状態に設定する走査駆動回路と、所望の画像情報を表示するための表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加する信号駆動回路と、を備え、前記信号駆動回路により前記表示画素の各々に、前記階調信号電圧を印加することにより、前記表示画素を所定の輝度階調で発光動作させて、前記表示パネルに所望の画像情報を表示する表示装置の駆動制御方法において、前記走査駆動回路は、第1のクロック信号に応じたタイミングで前記複数の走査線の各々に対応する第1の出力信号を出力し、前記第1の出力信号に応じたタイミングで前記表示パネルの各行ごとの前記表示画素に走査信号を順次印加して選択状態に設定し、前記信号駆動回路は、第2のクロック信号に応じたタイミングで前記複数の信号線の各々に対応する第2の出力信号を出力し、所望の

10

20

30

40

50

画像情報を表示するための表示信号を前記第2の出力信号に応じたタイミングで順次取り込み、出力し、前記表示信号に応じた階調信号電圧を生成し、前記選択状態に設定された行の前記表示画素に印加し、前記表示信号を特定の信号に設定し、前記信号駆動回路に取り込まれて出力される前記特定の信号に応じた特定の信号電圧を、走査駆動回路より出力される前記各走査信号により選択状態にされた、前記走査線に沿って行方向に配列された複数の前記表示画素、又は、前記信号線に沿って列方向に配列された複数の前記表示画素に対して、特定の信号電圧を一括して印加するステップと、前記特定の信号電圧が印加された前記複数の表示画素の各々から、前記走査駆動回路における前記第1の出力信号及び前記信号駆動回路における前記第2の出力信号に基づくタイミングで、当該表示画素に流れる駆動電流に対応する電流成分の電流値を測定するステップと、前記測定された電流値と、前記表示画素に前記特定の信号電圧を印加した場合の、該表示画素に流れる前記駆動電流の理想値との差分に基づいて、補正值を生成するステップと、前記表示画素の各々に対応する前記表示信号に、前記補正值を加算する補正処理を行って前記信号駆動回路に供給するステップと、を含むことを特徴とする。

#### 【0032】

請求項3\_0記載の表示装置の駆動制御方法は、請求項2\_9記載の表示装置の駆動制御方法において、前記表示画素は、前記階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、前記駆動電流の電流値に応じた輝度階調で発光動作する電流制御型の発光素子と、を備え、前記電流成分の電流値を測定するステップは、前記発光駆動回路に対して、前記特定の信号電圧を印加した場合の、前記発光素子に流れる駆動電流に対応する電流成分の電流値を測定することを特徴とする。

#### 【0035】

請求項3\_1記載の表示装置の駆動制御方法は、請求項2\_9又は3\_0記載の表示装置の駆動制御方法において、前記特定の信号電圧を印加するステップは、前記書込動作時に、前記表示パネルに配列された前記表示画素ごとに、前記特定の信号電圧を順次個別に印加し、前記電流成分の電流値を測定するステップは、前記表示画素の各々から前記特定量を個別に抽出することを特徴とする。

請求項3\_2記載の表示装置の駆動制御方法は、請求項2\_9乃至3\_1のいずれかに記載の表示装置の駆動制御方法において、前記特定の信号電圧は、前記発光素子を最高の輝度階調で発光動作させるための最高階調電圧に設定されていることを特徴とする。

#### 【0036】

請求項3\_3記載の表示装置の駆動制御方法は、請求項2\_9乃至3\_2のいずれかに記載の表示装置の駆動制御方法において、前記電流成分の電流値を測定するステップは、前記走査駆動回路により前記表示画素に印加される前記走査信号に基づいて実行されることを特徴とする。

請求項3\_4記載の表示装置の駆動制御方法は、請求項2\_9乃至3\_2のいずれかに記載の表示装置の駆動制御方法において、前記電流成分の電流値を測定するステップは、前記信号駆動回路により前記表示画素に印加される前記階調信号電圧に基づいて実行されることを特徴とする。

#### 【0037】

すなわち、本発明に係る表示駆動装置及び該表示駆動装置を備えた表示装置並びにその駆動制御方法は、表示信号（表示データ）に応じた階調信号電圧を各表示画素に印加することにより、各表示画素を構成する発光素子を所定の輝度階調で発光動作させて、所望の画像情報を表示パネルに表示する表示装置において、信号駆動回路（データドライバ）により、走査線に沿って行方向に配列された複数の表示画素、又は、前記信号線に沿って列方向に配列された複数の表示画素に特定の信号電圧（例えば、最高階調電圧）を一括して印加し、特定の信号電圧が印加された各表示画素から、発光素子の発光特性に関連する特定量として、発光素子に流れる駆動電流（書込電流）の電流値を、表示駆動装置（補正制御回路）により直接又は間接的に測定し、その電流値と、上記特定の信号電圧を印加した

10

20

30

40

50

場合の発光素子に流れる駆動電流の設定値（理想値）との差分に基づいて補正值を生成し、該補正值を用いて表示画素の各々に対応する表示信号を補正する処理を行って、信号駆動回路に供給するように構成されている。

#### 【0038】

これによれば、表示画素（発光素子）の発光特性に関連した特定量（駆動電流に対応する電流成分の電流値）に基づいて、表示信号を補正することができるので、各表示画素に発光素子の発光特性に応じた（発光特性のバラツキや劣化を補填することができる電圧値に設定された）階調信号電圧を印加することができ、発光素子に、予め設定された理想値に近似した電流値を有する発光駆動電流を流すことができ、表示信号に良好に対応した輝度階調で発光素子を発光動作させることができる。

10

#### 【0039】

ここで、表示パネルを構成する各表示画素は、階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、該駆動電流の電流値に応じた輝度階調で発光動作する電流制御型の発光素子と、を備えた構成を適用することができ、この場合、発光素子の発光特性に関連する特定量として、表示画素に対して、特定の信号電圧を印加した場合の、発光駆動回路に蓄積された電圧成分に基づいて、発光素子に流れる電流（測定電流　書込電流）の電流値を測定する手法を適用することができる。

#### 【0040】

これによれば、通常の画像表示動作において表示画素（発光駆動回路）に階調信号電圧を実際に印加した場合と同等の条件で、表示画素の発光特性に関連する特定量を抽出することができるので、発光素子の素子特性のみならず、発光駆動回路を構成するトランジスタや容量素子等の機能素子の素子特性をも含めた特定量を取得することができる。

20

#### 【0041】

また、表示駆動装置（補正制御回路）として、表示画素に対して、特定の信号電圧を印加した場合の、発光素子に流れる駆動電流に応じた電圧成分を蓄積する蓄積手段を備えた構成を適用することができ、この場合、発光素子の発光特性に関連する特定量として、表示画素に対して、特定の信号電圧を印加した場合の、当該蓄積手段に蓄積された電圧成分に基づいて、表示駆動装置（補正制御回路）に流れる電流（測定電流）の電流値を測定する手法を適用することができる。

30

#### 【0042】

これによれば、各表示画素の表示パネル上での配置位置に関わらず、表示駆動装置（補正制御回路）に流れる電流の電流値に基づいて、全ての表示画素の発光特性に関連する特定量を抽出することができるので、表示画素が微細化された場合や表示パネルが大型化された場合であっても、上記表示駆動装置（補正制御回路）に流れる電流を早期に安定化させて、迅速に特定量を取得することができる。

#### 【0043】

なお、表示画素の発光特性に関連する特定量を抽出する手法としては、表示パネルの行方向に配列された複数の表示画素ごと、又は、列方向に配列された複数の表示画素ごとに、特定の信号電圧を一括して印加し、表示画素の各々から特定量を順次個別に抽出するものであってもよいし、あるいは、任意の位置に配置された表示画素ごとに、特定の信号電圧を印加し、表示画素の各々から特定量を個別に抽出するものであってもよい。

40

#### 【0044】

また、上記表示駆動装置（補正制御回路）を、表示パネルの走査駆動回路（ゲートドライバ）側に配置した構成、もしくは、走査駆動回路と一体的に設けた構成においては、上記表示画素から特定量を抽出する動作を、走査駆動回路により表示画素に印加される走査信号を用いて実行制御するものであってもよい。また、上記表示駆動装置（補正制御回路）を、表示パネルの信号駆動回路（データドライバ）側に配置した構成、もしくは、信号駆動回路と一体的に設けた構成においては、上記表示画素から特定量を抽出する動作を、信号駆動回路により表示画素に印加される階調信号電圧を用いて実行制御するものであって

50

もよい。これによれば、表示駆動装置（補正制御回路）を動作制御するための構成を簡素化することができる。

#### 【0045】

さらに、上記表示駆動装置（補正制御回路）は、全て又は一部の構成が表示パネルを構成する基板上に、表示画素とともに一体的に薄膜形成された構成を有するものであってもよい。これによれば、既存の走査駆動回路や信号駆動回路のドライバチップ（ICチップ）をそのまま使用することができ、本発明に係る表示装置を大幅な設計変更を伴うことなく、安価に実現することができる。また、上記表示駆動装置（補正制御回路）の全て又は一部の構成を、走査駆動回路や信号駆動回路と一体的に形成し、単一のドライバチップに内蔵した構成を有するものであってもよい。これによれば、少なくとも補正制御回路と走査駆動回路又は信号駆動回路をユニット化することができ、既存の表示パネルとの接続構造やプロセスをそのまま適用することができ、製造工程の簡素化を図ることができる。10

#### 【0046】

##### 【発明の実施の形態】

以下、本発明に係る表示駆動装置及び表示装置並びにその駆動制御方法について、実施の形態を示して詳しく説明する。

##### <表示装置の第1の実施形態>

まず、本発明に係る表示駆動装置を適用可能な表示装置の概略構成について、図面を参照して説明する。

#### 【0047】

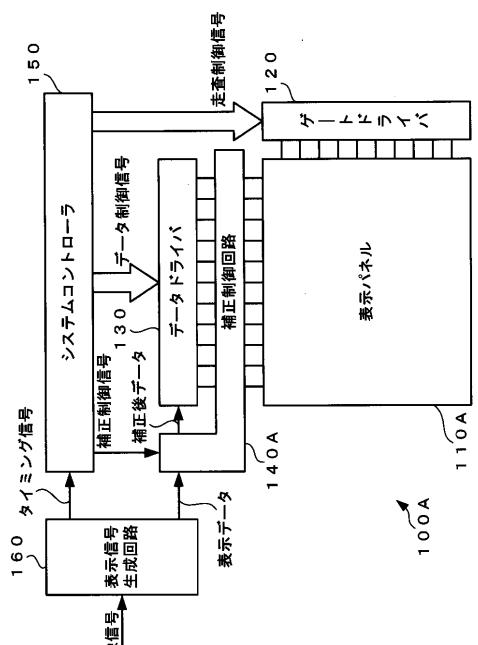

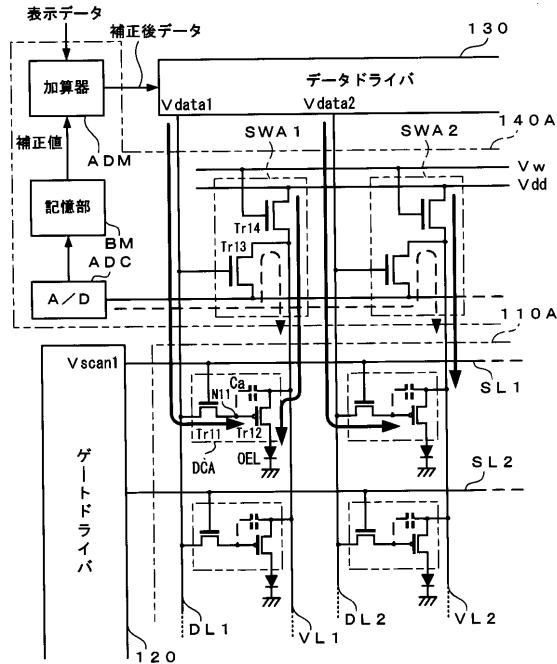

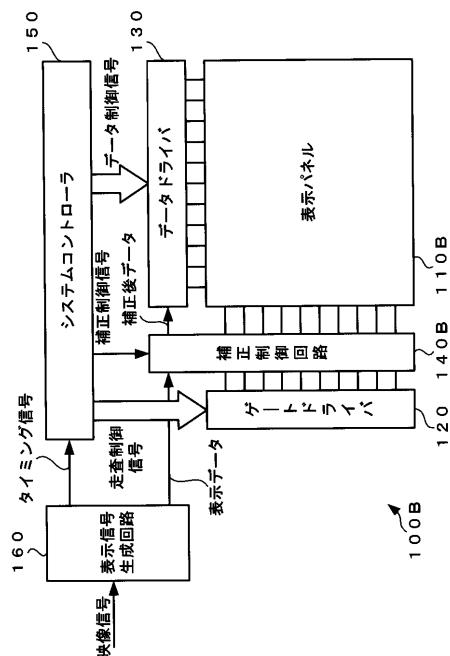

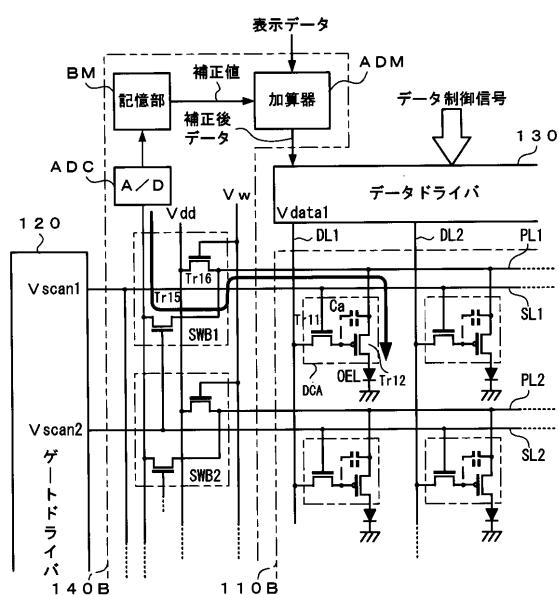

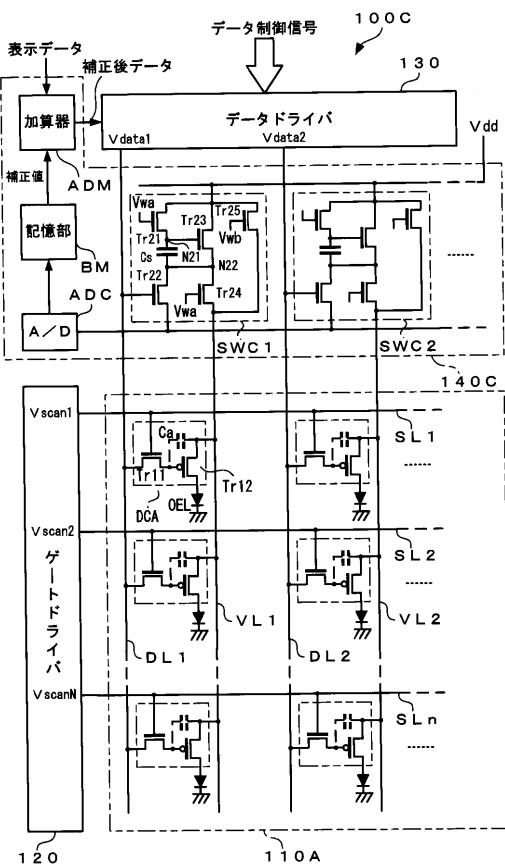

図1は、本発明に係る表示駆動装置を適用した表示装置の全体構成の第1の実施形態を示すブロック図であり、図2は、本実施形態に係る表示装置の要部構成を示す概略構成図である。20

なお、図2においては、図示の都合上、ゲートドライバを表示パネルの左側に配置して示す（図1においては、表示パネルの右側）。また、以下の説明においては、表示パネルを構成する表示画素として、有機EL素子を備えた構成を示すが、本発明に係る表示装置はこれに限るものではなく、供給される発光駆動電流（駆動電流）の電流値に応じた輝度階調で発光動作する電流制御型の発光素子であれば、有機EL素子の他に、例えば、発光ダイオード等を発光素子として良好に適用することができる。

#### 【0048】

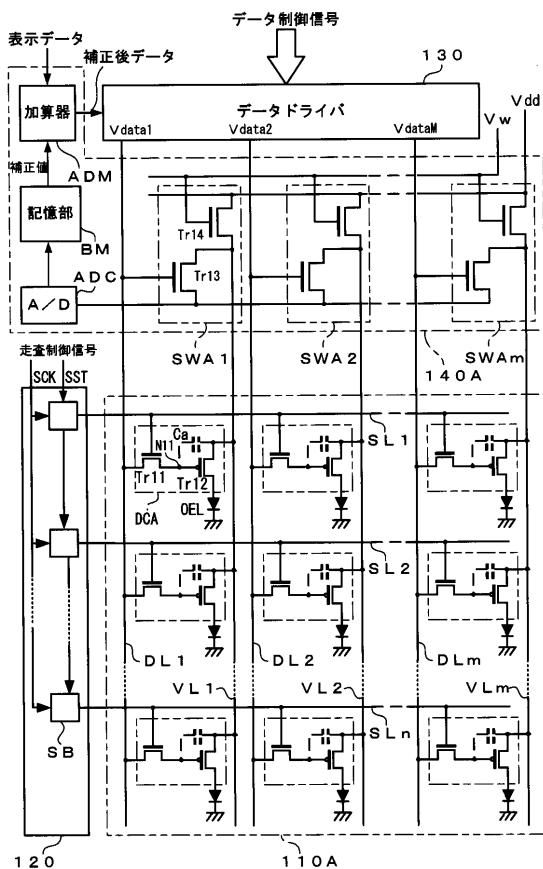

図1、図2に示すように、本実施形態に係る表示装置100Aは、概略、相互に直交するよう配設された複数の走査ライン（走査線）SL1、SL2、…SLn（以下、「走査ラインSL」とも記す）と複数のデータライン（信号線）DL1、DL2、…DLm（以下、「データラインDL」とも記す）との各交点近傍に、画素駆動回路（発光駆動回路）DCA及び有機EL素子（電流制御型の発光素子）OELを備えた複数の表示画素が配列された表示パネル110Aと、該表示パネル110Aの走査ラインSLに接続され、各走査ラインSLに所定のタイミングで順次ハイレベルの走査信号V<sub>scan1</sub>、V<sub>scan2</sub>、…V<sub>scanN</sub>（以下、「走査信号V<sub>scan</sub>」とも記す）を印加することにより、行ごとの表示画素群を選択状態に設定（走査）するゲートドライバ（走査駆動回路）120と、表示パネル110AのデータラインDLに接続され、表示データに基づいて、階調信号電圧V<sub>data1</sub>、V<sub>data2</sub>、…V<sub>datam</sub>（以下、「階調信号電圧V<sub>data</sub>」とも記す）を生成して、各データラインDLに供給するデータドライバ（信号駆動回路）130と、所定のタイミングで各表示画素に設けられた有機EL素子OELの発光特性（又は、素子特性）に関連する特定量を測定し、当該発光特性に基づいて、データドライバ130に供給される表示データを補正する補正制御回路（表示駆動装置）140Aと、後述する表示信号生成回路160から供給されるタイミング信号に基づいて、少なくとも、ゲートドライバ120及びデータドライバ130、補正制御回路140Aの動作状態を制御する走査制御信号及びデータ制御信号、補正制御信号を生成、出力するシステムコントローラ150と、表示装置100Aの外部から供給される映像信号に基づいて、デジタル信号からなる表示データを生成して、上記補正制御回路140Aを介してデータドライバ130に供給する304050

とともに、該表示データを表示パネル 110A に画像表示するためのタイミング信号（システムクロック等）を抽出、又は、生成してシステムコントローラ 150 に供給する表示信号生成回路 160 と、を備えて構成されている。

#### 【0049】

以下、上記各構成について説明する。

##### (表示パネル 110A)

本実施形態に係る表示装置に適用可能な表示パネル 110A は、例えば、図 2 に示すように、相互に直交するように配設された走査ライン SL 及びデータライン DL に加え、各データライン DL に並列に配設された電源ライン VL1、VL2、…VLm（以下、「電源ライン VL」とも記す）とを備え、走査ライン SL と、データライン DL 及び電源ライン VL の各交点に、上述した従来技術（図 21 参照）に示した発光駆動回路 DCP と同等の回路構成を有する画素駆動回路 DCA と有機 EL 素子 OEL を備えた表示画素が接続された構成を有している。10

#### 【0050】

ここで、各表示画素は、ゲート端子が走査ライン SL に、ソース端子及びドレイン端子がデータライン DL 及び接点 N11 に各々接続された薄膜トランジスタ（選択トランジスタ；選択スイッチ）Tr11 と、ゲート端子が接点 N11 に、ソース端子が電源ライン VL に各々接続された薄膜トランジスタ（発光駆動トランジスタ；発光駆動スイッチ）Tr12 と、を備えた画素駆動回路 DCA、及び、該画素駆動回路 DCP の薄膜トランジスタ Tr12 のドレイン端子にアノード端子が接続され、カソード端子が接地電位（Vgnd）に接続された有機 EL 素子 OEL を有して構成されている。なお、図 2 に示した画素駆動回路 DCA において、Ca は薄膜トランジスタ Tr12 のゲート - ソース間に形成される寄生容量である。20

#### 【0051】

このような表示画素において、所定のタイミングでゲートドライバ 120 から走査ライン SL に印加される走査信号 Vscan、及び、データドライバ 130 からデータライン DL に印加される階調信号電圧 Vdata、後述する補正制御回路 140A から電源ライン VL に印加される電源電圧（駆動電源電圧）Vdd に基づいて、各表示画素において、画素駆動回路 DCA により有機 EL 素子の発光動作及び発光時の輝度階調が制御される。詳しくは後述する。30

#### 【0052】

##### (ゲートドライバ 120)

ゲートドライバ 120 は、システムコントローラ 150 から供給される走査制御信号に基づいて、各走査ライン SL にハイレベルの走査信号 Vscan を順次印加することにより、各行ごとの表示画素群を選択状態とし、データドライバ 130 によりデータライン DL を介して印加される所定の階調信号電圧 Vdata の、画素駆動回路 DCA への書き込みを行うように制御する。

#### 【0053】

ここで、ゲートドライバ 120 は、具体的には、例えば、図 2 に示すように、シフトレジスタとバッファからなるシフトブロック SB を、各走査ライン SL に対応させて複数段備え、後述するシステムコントローラ 150 から供給される走査制御信号（走査スタート信号 SST、走査クロック信号 SCK 等）に基づいて、シフトレジスタにより表示パネル 110A の上方から下方にシフト信号を順次シフトしつつ、生成されたシフト信号を、バッファを介して所定の電圧レベル（ハイレベル）に変換して走査信号 Vscan として各走査ライン SL に出力する。40

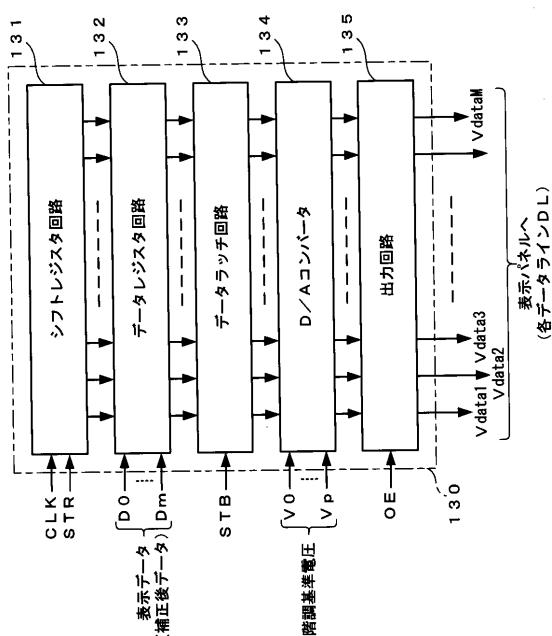

#### 【0054】

##### (データドライバ 130)

図 3 は、本実施形態に係る表示装置に適用されるデータドライバの要部構成を示すプロック図である。

データドライバ 130 は、システムコントローラ 150 から供給されるデータ制御信号（50

出力イネーブル信号 O E、データラッチ信号 S T B、サンプリングスタート信号 S T R、シフトクロック信号 C L K 等)に基づいて、表示信号生成回路 160 から出力され、補正制御回路 140 A を介して供給されるデジタル信号からなる表示データ(補正後データ)を所定のタイミングで取り込んで保持し、該表示データに対応する信号電圧(アナログ信号)を生成して、階調信号電圧 V data として各データライン D L に印加する。

#### 【0055】

ここで、データドライバ 130 は、具体的には、図 3 に示すように、システムコントローラ 150 から供給されるデータ制御信号(シフトクロック信号 C L K、サンプリングスタート信号 S T R)に基づいて、順次シフト信号を出力するシフトレジスタ回路 131 と、該シフト信号の入力タイミングに基づいて、表示信号生成回路 160 から供給される 1 行分の表示データ D 0 ~ D m を順次取り込むデータレジスタ回路 132 と、データ制御信号(データラッチ信号 S T B)に基づいて、データレジスタ回路 132 により取り込まれた 1 行分の表示データ D 0 ~ D m を一括保持するデータラッチ回路 133 と、図示を省略した電源供給手段から供給される階調基準電圧 V 0 ~ V p に基づいて、上記保持された表示データ D 0 ~ D m を所定のアナログ信号電圧に変換する D / A コンバータ 134 と、システムコントローラ 150 から供給されるデータ制御信号(出力イネーブル信号 O E)に基づくタイミングで、当該アナログ信号電圧を階調信号電圧 V data として、各データライン D L に印加する出力回路 135 と、を有して構成されている。

このようなデータドライバ 130 により、表示信号生成回路 160 から補正制御回路 140 A を介して供給される表示データ(デジタル信号)に対応した階調信号電圧(アナログ信号)が生成されて、所定のタイミングで各データライン D L に一括して、もしくは、順次出力される。

#### 【0056】

##### (補正制御回路 140 A)

補正制御回路 140 A は、例えば、図 2 に示すように、各データライン D L ごとに設けられ、後述する各表示画素(有機 E L 素子 O E L)における発光特性に関連する特定量(具体的には、特定の測定条件において有機 E L 素子 O E L を流れる測定電流の電流値)を測定する動作を行うとともに、各表示画素への高電位電圧 V dd の印加を制御する動作を行う複数のスイッチ回路部 S W A 1、S W A 2、…、S W A m(以下、「スイッチ回路部 S W A」とも記す)と、該スイッチ回路部 S W A を介して各表示画素の有機 E L 素子 O E L に流れる測定電流(電流成分)の電流値(アナログ信号)を、アナログ - デジタル変換処理してデジタル値(デジタル信号)に変換するアナログ - デジタル変換器(以下、「A / D コンバータ」と略記する) A D C と、各表示画素ごとの上記デジタル値を順次取り込んで、一時的に記憶するバッファメモリ等の記憶部(記憶手段) B M と、表示信号生成回路 160 とデータドライバ 130 との間に設けられ、表示信号生成回路 160 から供給される表示データ(デジタル信号)に対して、上記記憶部 B M に記憶された各表示画素(有機 E L 素子 O E L)ごとのデジタル値を補正值として用いて加算し、上記データドライバ 130 に補正後データとして供給する加算器(信号補正手段) A D M と、を有して構成されている。

#### 【0057】

ここで、各スイッチ回路部 S W A は、ゲート端子がデータライン D L に、ソース端子及びドレイン端子が電源ライン V L 及び A / D コンバータ A D C に各々接続された薄膜トランジスタ(読出制御トランジスタ; 読出制御スイッチ) T r 13 と、ゲート端子にシステムコントローラ 150 から出力される補正制御信号(書き制御信号 V w)が供給され、ソース端子及びドレイン端子が高電位電圧 V dd 及び電源ライン V L に各々接続された薄膜トランジスタ(書き制御トランジスタ; 書き制御スイッチ) T r 14 と、を備えた構成を有している。

すなわち、薄膜トランジスタ T r 13 及び A / D コンバータ A D C は、本発明に係る特定量抽出手段を構成している。

#### 【0058】

10

20

30

40

50

(システムコントローラ)

システムコントローラ150は、ゲートドライバ120及びデータドライバ130、補正制御回路140Aの各々に対して、動作状態を制御する走査制御信号（上述した走査スタート信号SST、走査クロック信号SCK等）及びデータ制御信号（上述した出力イネーブル信号OE、データラッチ信号STB、サンプリングスタート信号STR、シフトクロック信号CLK等）、補正制御信号（上述した書き制御信号Vw等）を出力することにより、各ドライバ及び制御回路を所定のタイミングで動作させて、表示信号生成回路160から出力される表示データを所定の補正值（デジタル値）に基づいて補正処理するとともに、走査信号V<sub>scan</sub>及び階調信号電圧V<sub>data</sub>を生成させ、各走査ラインSL及びデータラインDLに印加して各表示画素における発光動作を連続的に実行させて、所定の映像信号に基づく画像情報を表示パネル110Aに表示させる制御を行う。

10

【0059】

(表示信号生成回路)

表示信号生成回路160は、例えば、表示装置100Aの外部から供給される映像信号から輝度階調信号成分を抽出して、表示パネル110Aの1行分ごとに、該輝度階調信号成分をデジタル信号からなる表示データとして、上記補正制御回路140Aを介してデータドライバ130のデータレジスタ回路132に供給する。ここで、上記映像信号が、テレビ放送信号（コンポジット映像信号）のように、画像情報の表示タイミングを規定するタイミング信号成分を含む場合には、表示信号生成回路160は、上記輝度階調信号成分を抽出する機能のほか、タイミング信号成分を抽出してシステムコントローラ150に供給する機能を有するものであってもよい。この場合においては、上記システムコントローラ150は、表示信号生成回路160から供給されるタイミング信号に基づいて、ゲートドライバ120やデータドライバ130、補正制御回路140Aに対して供給する走査制御信号及びデータ制御信号、補正制御信号を生成する。

20

【0060】

また、表示装置100の外部から供給される映像信号がデジタル信号により形成され、また、タイミング信号が当該映像信号とは別に供給されている場合には、当該映像信号（デジタル信号）を表示データとして、補正制御回路140Aを介してデータドライバに供給するとともに、当該タイミング信号を直接システムコントローラ150に供給するようにして、表示信号生成回路160を省略するようにしてもよい。

30

【0061】

<表示装置の駆動制御方法の第1の実施形態>

次に、上述した構成を有する表示装置における駆動制御動作（駆動制御方法）について、図面を参照して具体的に説明する。

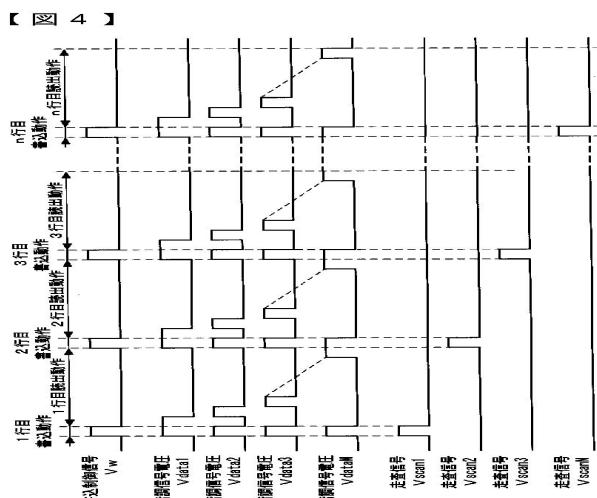

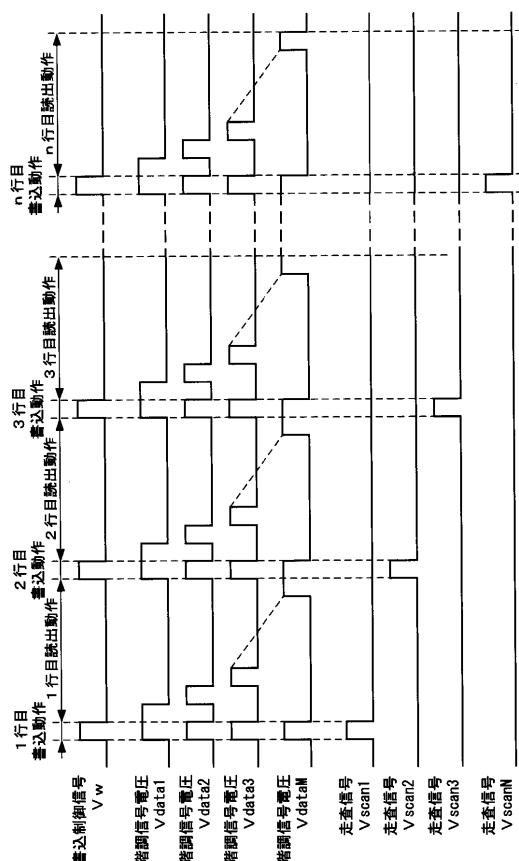

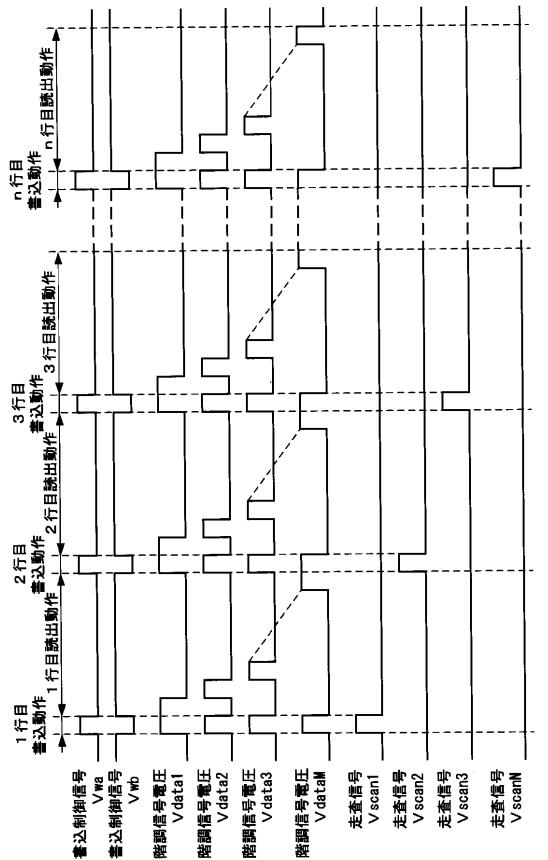

図4は、本実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。図5は、本実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書き動作）を示す動作概念図であり、図6は、本実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。

40

【0062】

本実施形態に係る表示装置における駆動制御方法は、表示装置100Aの外部から供給される映像信号に基づいて、表示パネル110Aに所望の画像情報を表示する画像表示動作と、該画像表示動作に先立つ任意のタイミングで、各表示画素（有機EL素子OEL）の発光特性に関連する特定量（測定電流の電流値）を測定する特定量測定動作と、上記画像表示動作時に、特定量測定動作により得られた特定量に基づいて、データドライバ130に供給される表示データ（デジタル信号）を補正するデータ補正動作と、を含んでいる。以下、各動作について説明する。

【0063】

(特定量測定動作)

本実施形態に係る特定量測定動作は、システムコントローラ150により特定量測定状態

50

が設定されると、例えば、表示信号生成回路 160 から、あるいは、記憶部 BM から、測定用データ RD0 として、"HHHHHHHHHHHH...HHHH"（全てハイレベル）からなるシリアルデータがデータドライバ 130 に入力される。これにより、データドライバ 130 は、システムコントローラ 150 から供給されるデータ制御信号に基づくタイミングで、図 4 に示すように、上記測定用データ RD0 に基づいて、いずれもハイレベル（最高階調電圧：MSB）からなる階調信号電圧（測定用の信号電圧）Vdata1 ~ VdataM を生成して、各データライン DL に印加する。

#### 【0064】

次いで、システムコントローラ 150 から供給される走査制御信号に基づくタイミングで、図 4、図 5 に示すように、ゲートドライバ 120 により 1 行目の走査ライン SL1 にハイレベルの走査信号 Vscan1 を印加して、走査ライン SL1 に接続された各表示画素の画素駆動回路 DCA に設けられた薄膜トランジスタ（選択トランジスタ）Tr11 をオン動作させ、当該行の表示画素群を選択状態に設定する。そして、このタイミングで、補正制御回路 140A の各スイッチ回路部 SWA に設けられた薄膜トランジスタ（書き制御トランジスタ）Tr14 のゲート端子に、システムコントローラ 150 から供給されるハイレベルの書き制御信号 Vw（補正制御信号）が印加されることにより、薄膜トランジスタ Tr14 がオン動作して、高電位電圧 Vdd が各表示画素の電源ライン VL に印加される。

#### 【0065】

これにより、図 5 中、実線矢印で示すように、各データライン DL に印加されたハイレベル（= MSB）を有する階調信号電圧 Vdata が、各表示画素（画素駆動回路 DCA）の薄膜トランジスタ Tr11 を介して、薄膜トランジスタ（発光駆動トランジスタ）Tr12 のゲート端子に印加されて、当該ゲート電圧（すなわち、階調信号電圧 Vdata）に応じた導通状態でオン動作するので、高電位電圧 Vdd と接地電位間の電位差、及び、階調信号電圧 Vdata の電圧値に応じて、高電位電圧 Vdd 側から薄膜トランジスタ Tr12 及び有機 EEL 素子 OEL を介して接地電位に電流（書き電流；駆動電流）が流れる。このとき、薄膜トランジスタ Tr12 のゲート - ソース間に生じる電位差が、ゲート - ソース間の寄生容量 Ca に電圧成分として保持される（1 行目の表示画素群への測定用信号電圧の書き動作）。

#### 【0066】

ここで、図 5 に示すように、A/D コンバータ ADC が、補正制御回路 140A を構成する薄膜トランジスタ（読み出制御トランジスタ）Tr13 の電流路の一端側に固定的に接続された回路構成を有する場合には、上記書き動作によりデータライン DL にハイレベル（= MSB）の階調信号電圧 Vdata が印加されることにより、薄膜トランジスタ Tr13 のゲート端子にも同等のゲート電圧が印加されてオン動作するため、図中、点線矢印で示すように、A/D コンバータ ADC から薄膜トランジスタ Tr13 を介して電源ライン VL に電流が流れる場合も考えられる。しかしながら、各表示画素において薄膜トランジスタ（発光駆動トランジスタ）Tr12 を介して有機 EEL 素子 OEL に流れる電流は、薄膜トランジスタ Tr12 のゲート電圧（すなわち、階調信号電圧 Vdata）に依存するので、上記書き動作において、薄膜トランジスタ Tr12 のゲート - ソース間寄生容量 Ca に保持される電圧に影響を与えることはない。

#### 【0067】

なお、本実施形態に適用した補正制御回路 140A においては、薄膜トランジスタ（読み出制御トランジスタ）Tr13 の電流路の一端側に A/D コンバータ ADC が固定的に接続された構成を示したが、上記書き動作時に、上述したような A/D コンバータ ADC から薄膜トランジスタ Tr13 を介して電源ライン VL に電流が流れる現象を完全に防止するために、A/D コンバータ ADC と各スイッチ回路部 SWA（薄膜トランジスタ Tr13）との間に、補正制御回路 140A の動作状態に応じて、双方の接続状態を切り換える切換制御手段（例えば、スイッチ等）を介在させて、上記書き動作においては、双方の接続状態を切り離す（遮断する）ようにしてもよい。

#### 【0068】

10

20

30

40

50

次いで、図4、図6に示すように、ゲートドライバ120により1行目の走査ラインSL1に印加される走査信号V<sub>scan1</sub>を、ローレベルに切り換えることにより、当該行の表示画素（画素駆動回路DCA）の薄膜トランジスタ（選択トランジスタ）Tr11をオフ動作させて、当該行の表示画素群を非選択状態に設定する。そして、このタイミングで、システムコントローラ150により各スイッチ回路部SWAの薄膜トランジスタTr14のゲート端子に印加される書き制御信号V<sub>w</sub>を、ローレベルに切り換えることにより、薄膜トランジスタTr14をオフ動作させて、各電源ラインVLへの高電位電圧V<sub>dd</sub>の印加を遮断する。

#### 【0069】

次いで、"H00000000···0000"（1番目のデータのみハイレベル）からなる測定用データ（シリアルデータ）RD1をデータドライバ130に入力する。これにより、データドライバ130は、該測定用データRD1に基づいて、1列目のデータラインDL1にのみハイレベル（=MSB）の階調信号電圧（測定用の信号電圧）V<sub>data1</sub>を印加するとともに、他の列のデータラインDL2～DLmにはローレベルの階調信号電圧を印加する。

10

#### 【0070】

これにより、図6中、実線矢印で示すように、1列目のデータラインDL1にハイレベル（=MSB）を有する階調信号電圧V<sub>data1</sub>が、補正制御回路140Aの1列目のスイッチ回路部SWA1に設けられた薄膜トランジスタ（読み出制御トランジスタ）Tr13のゲート端子に印加されてオン動作することにより、A/DコンバータADCから薄膜トランジスタTr13を介して、1列目の電源ラインVL1に測定用電圧（高電位電圧V<sub>dd</sub>）が印加される。

20

#### 【0071】

ここで、1行目の表示画素群を構成する各画素駆動回路（薄膜トランジスタTr12のゲート-ソース間寄生容量Ca）には、上記測定用信号電圧の書き動作におけるゲート-ソース間電圧が保持されているため、当該電圧により薄膜トランジスタTr12はオン状態を維持し、A/DコンバータADCにより電源ラインVL1に印加された測定用電圧（V<sub>dd</sub>）と接地電位との間に電位差、及び、薄膜トランジスタTr12のゲート-ソース間電圧に応じて、A/DコンバータADC側から、1行1列目の表示画素の薄膜トランジスタTr12及び有機EL素子OELを介して接地電位に電流（測定電流）が流れる。

30

#### 【0072】

そして、本実施形態においては、この1行1列目の表示画素（有機EL素子OEL）に流れる測定電流（アナログ信号電流）を、A/DコンバータADCによりサンプリングしてデジタル信号化し、記憶部BMに記憶する。ここで、A/DコンバータADCによりサンプリングされる測定電流は、上記測定用データRD0の書き動作により当該表示画素（画素駆動回路DCA）の薄膜トランジスタTr12のゲート-ソース間寄生容量Caに保持された電圧成分に応じた電流値を有している。これにより、特定の測定条件（すなわち、特定の階調信号電圧）を印加した場合における、1行1列目の表示画素（有機EL素子OEL）の発光特性に関連する特定量（測定電流の電流値）がデジタルデータとして記憶部BMに記憶される（1行1列目の表示画素からの測定電流の読み出動作）。

40

#### 【0073】

以下、同様に、"0H0000000···0000"（2番目のデータのみハイレベル）からなる測定用データRD2をデータドライバ130に入力して、図4に示すように、2列目のデータラインDL2にのみハイレベル（=MSB）の階調信号電圧（測定用の信号電圧）V<sub>data2</sub>を印加することにより、図6に示した場合と同様に、2列目のデータラインDL2に接続されたスイッチ回路部SWA2の薄膜トランジスタ（読み出制御トランジスタ）Tr13がオン動作して、A/DコンバータADCから2列目の電源ラインVL1に測定用電圧（V<sub>dd</sub>）が印加される。

#### 【0074】

これにより、上記測定用信号電圧の書き動作において、1行2列目の表示画素の薄膜トラ

50

ンジスタ T r 1 2 のゲート - ソース間寄生容量 C a に保持された電圧成分に応じて、A / D コンバータ A D C 側から 1 行 2 列目の表示画素に測定電流が流れる。この測定電流を A / D コンバータ A D C によりサンプリングすることにより、1 行 2 列目の表示画素（有機 E L 素子 O E L ）の発光特性に関連する特定量がデジタルデータとして記憶部 B M に記憶される。

そして、このような測定電流の読み出動作を、各列の表示画素について順次繰り返し実行することにより、1 行目の各表示画素（有機 E L 素子 O E L ）における発光特性に関する特定量が取得される。

#### 【 0 0 7 5 】

次いで、図 4 に示すように、上述した 1 行目の表示画素群に対して実行した特定量測定動作（各行の表示画素群への測定用信号電圧の書き動作、各列の表示画素からの測定電流の読み出動作）を 2 行目以降の各行についても順次繰り返し実行することにより、表示パネル 1 1 0 A を構成する全ての表示画素（有機 E L 素子 O E L ）における発光特性に関する特定量をデジタルデータとして取得することができる。10

#### 【 0 0 7 6 】

##### （画像表示動作 / データ補正動作）

次に、本実施形態における通常の画像情報の表示動作、及び、データ補正動作について説明する。

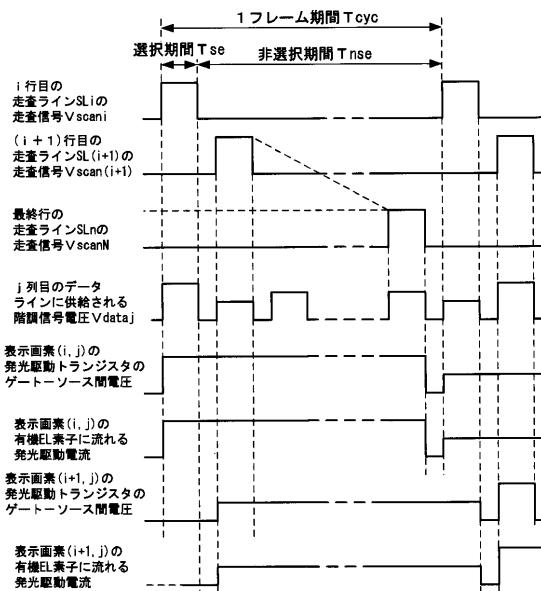

図 7 は、本実施形態に係る表示装置の駆動制御方法に適用される画像表示動作の一例を示すタイミングチャートである。ここで、上述した特定量測定動作と同等の動作については20、その説明を簡略化して説明する。

#### 【 0 0 7 7 】

本実施形態における通常の画像表示動作は、図 1、図 2 に示した表示装置において、まず、表示信号生成回路 1 6 0 から出力された 1 行分の表示データ（ $i$  行目の表示画素群に対応した表示データ； $1 \leq i \leq n$ ）は、補正制御回路 1 4 0 A の加算器 A D M を介して、データドライバ 1 3 0 に供給される。ここで、表示信号生成回路 1 6 0 から出力される表示データは、例えば、表示装置 1 0 0 A の外部から供給される映像信号に基づいて生成されるデジタル信号からなるシリアルデータであって、当該表示装置 1 0 0 A の表示パネル 1 1 0 A（各表示画素の有機 E L 素子 O E L ）の発光特性を考慮したものではない。

#### 【 0 0 7 8 】

そこで、本実施形態における画像表示動作では、上述した特定量測定動作により取得され、記憶部 B M に記憶された、各表示画素（有機 E L 素子 O E L ）の発光特性に関する特定量（特定の階調信号電圧を印加した場合の測定電流の電流値）と、上記特定量測定動作において各表示画素に階調信号電圧（測定用信号電圧）を印加した場合における書き電流の理想値（設定値）との差分を算出し、当該差分に基づいて、各表示画素（有機 E L 素子 O E L ）ごとの補正值（デジタル値）を生成して、各表示画素に対応する表示データに加算器 A D M により当該補正值を加算処理して、補正後データとしてデータドライバ 1 3 0 に供給する（データ補正動作）。これにより、後述するように、補正後データに基づいて生成された階調信号電圧が各表示画素に印加されることにより、各有機 E L 素子 O E L に30 流れる発光駆動電流の電流値を、予め設定された理想値に近似させることができる。

#### 【 0 0 7 9 】

データドライバ 1 3 0 は、加算器 A D M を介して供給された補正表示データに基づいて、各列のデータライン D L に対応する階調信号電圧 V data を生成して印加する。このとき、システムコントローラ 1 5 0 からハイレベルの書き制御信号 V w が印加されることにより、補正制御回路 1 4 0 A の各列に設けられた薄膜トランジスタ（書き制御トランジスタ）T r 1 4 がオン動作して、各列の電源ライン V L に高電位電圧 V dd が共通に印加される。

#### 【 0 0 8 0 】

次いで、図 7 に示すように、ゲートドライバ 1 2 0 により  $i$  行目の走査ライン S L  $i$  にハイレベルの走査信号 V scan $i$  を印加して、当該行の表示画素群の画素駆動回路 D C A に設けられた薄膜トランジスタ（選択トランジスタ）T r 1 1 をオン動作させることにより、4050

薄膜トランジスタ（発光駆動トランジスタ）Tr12のゲート端子に、各データラインDLに印加された階調信号電圧Vdataに基づくゲート電圧が印加されて、当該ゲート電圧に応じた導通状態でオン動作する。

#### 【0081】

これにより、高電位電圧Vdd側から電源ラインVLを介して、i行目の表示画素群（例えば、i行j列目の表示画素；1 j m）の薄膜トランジスタTr12及び有機EL素子OELに、階調信号電圧Vdatajに基づく電流値を有する発光駆動電流が流れ、有機EL素子OELが所定の発光輝度で発光動作する（選択期間Tse）。このとき、薄膜トランジスタTr12のゲート-ソース間に生じる電位差により、ゲート-ソース間寄生容量Caが充電される。10

#### 【0082】

次いで、図7に示すように、ゲートドライバ120によりi行目の走査ラインSLiにローレベルの走査信号Vscaniを印加して、当該行の表示画素群の画素駆動回路DCAに設けられた薄膜トランジスタTr11をオフ動作させることにより、薄膜トランジスタTr12のゲート端子への階調信号電圧Vdataiの印加を遮断する。このとき、上記選択期間Tseに、薄膜トランジスタTr12のゲート-ソース間に印加されていた電位差は、ゲート-ソース間寄生容量Caに電圧成分として保持されるため、薄膜トランジスタTr12は、この電圧成分によりオン状態を維持し、上記選択期間Tseと同等の発光駆動電流がi行j列目の表示画素の薄膜トランジスタTr12及び有機EL素子OELに流れ、所定の発光輝度で発光する動作を継続する（非選択期間Tnse）。20

このような画像表示動作において設定される選択期間Tse及び非選択期間Tnseは、その合計時間が、例えば、表示パネルに1画面分の画像情報を表示する動作期間である1フレーム期間Tcycになるように設定される。

#### 【0083】

以下、同様に、(i+1)行目の表示画素群についても、図7に示すように、選択期間Tseにおいて、走査ラインSL(i+1)に走査信号Vscan(i+1)が印加されることにより、補正処理された表示データ（補正後データ）に基づく階調信号電圧Vdataが各列のデータラインDLを介して、当該行の各表示画素に印加されて、有機EL素子OELが発光動作するとともに、該発光動作に伴う電圧成分が寄生容量Caに保持される。また、非選択期間Tnseにおいては、各表示画素の寄生容量Caに保持された電圧に基づいて、当該行の各表示画素（有機EL素子OEL）の発光動作が維持される。30

このような一連の画像表示動作（データ補正動作を含む）を、各行について順次繰り返し実行することにより、1画面分の画像情報を表示パネル110Aに表示される。

#### 【0084】

したがって、上述した特定量測定動作により、特定の信号電圧（測定用信号電圧）の印加に対して、各表示画素（有機EL素子）に流れる測定電流の電流値を取得し、該電流値に基づいて、各表示画素ごとの発光特性に対応した補正值を算出（すなわち、各表示画素の発光素子に流れる発光駆動電流の電流値が予め設定された理想値に近づくように補正值を設定）し、通常の画像表示動作において、データドライバに供給される表示データに上記補正值を加算して、各表示画素の発光特性に応じたデジタル値に補正するデータ補正動作を行い、階調信号電圧を生成して各表示画素に印加することができる、映像信号本来の輝度階調に良好に対応した電流値を有する発光駆動電流を発光素子に流して発光動作させることができ、各表示画素の発光素子の発光特性のバラツキや劣化が補正されて、画像情報を良好な画質で表示することができる。40

#### 【0085】

<表示装置の第2の実施形態>

次に、本発明に係る表示駆動装置を適用可能な表示装置の第2の実施形態について、図面を参照して説明する。

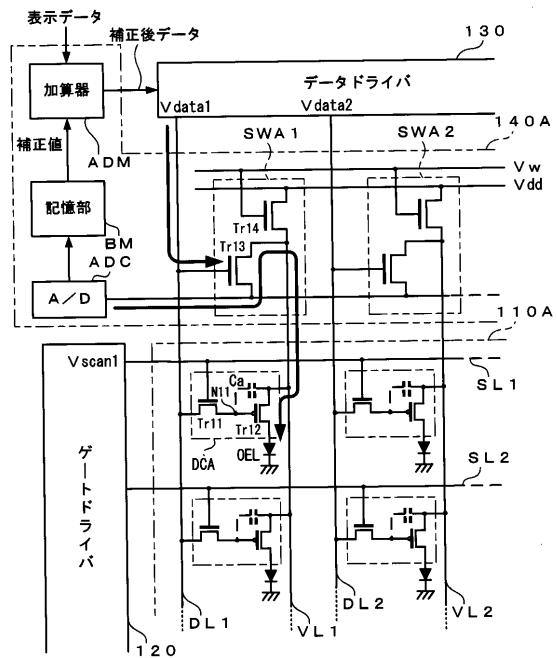

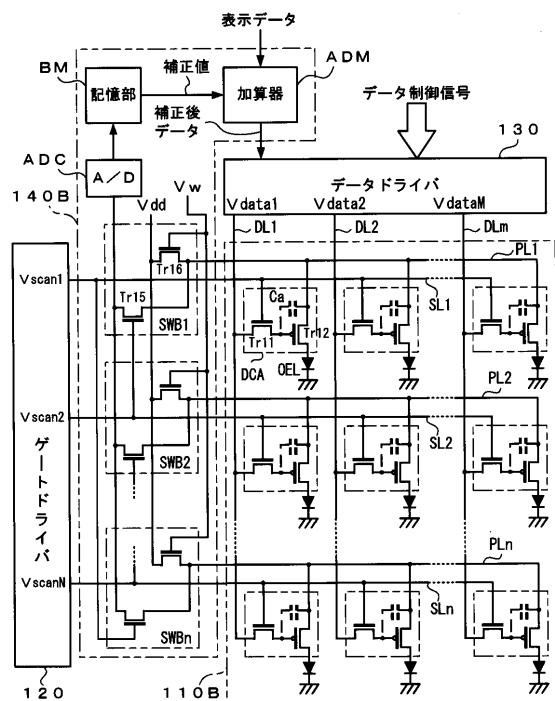

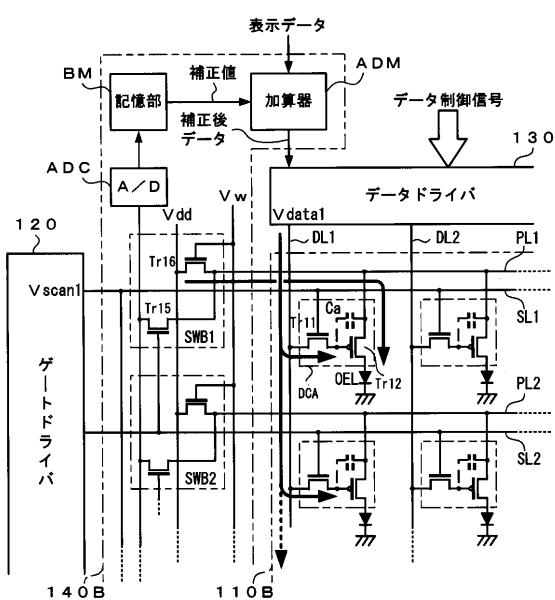

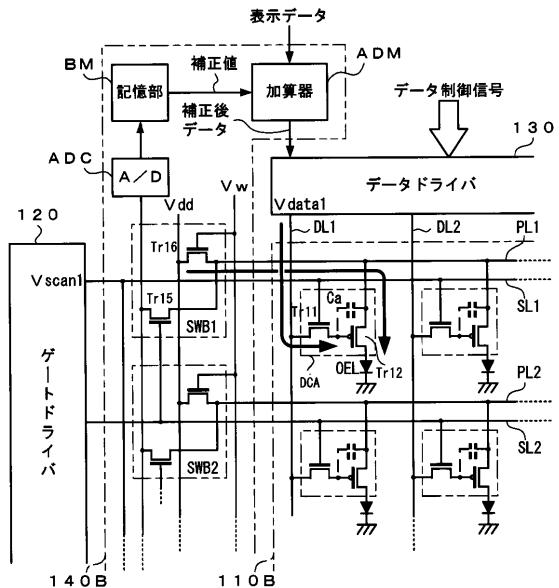

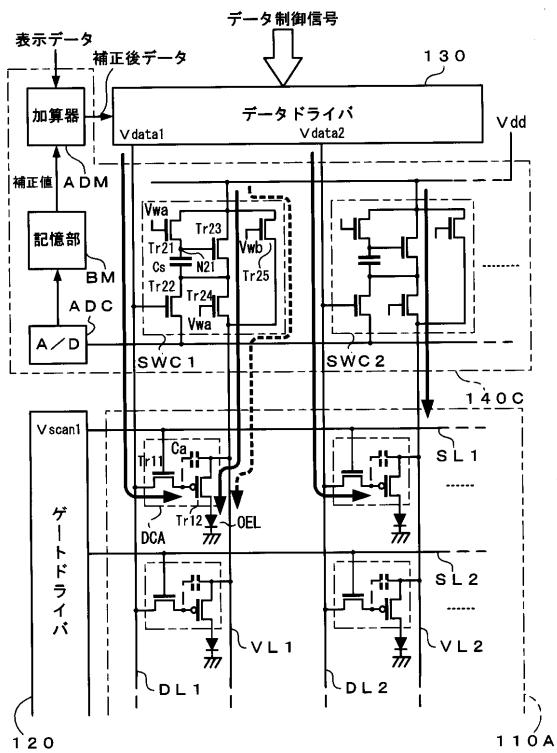

図8は、本発明に係る表示駆動装置を適用した表示装置の全体構成の第2の実施形態を示すブロック図であり、図9は、本実施形態に係る表示装置の要部構成を示す概略構成図で50

ある。なお、ここでは、上述した第1の実施形態と同等の構成については、同一の符号を付して、その説明を簡略化又は省略する。

#### 【0086】

上述した第1の実施形態においては、データドライバと表示パネルとの間に補正制御回路を設け、特定の信号電圧を各行の表示素子群に一括して印加した場合に、各発光素子（有機EL素子）に流れる測定電流（書込電流）を各列ごとに順次サンプリングしてデジタルデータとして記憶し、通常の画像表示動作において、表示データの補正処理に適用する場合について説明したが、本実施形態においては、ゲートドライバと表示パネルとの間に補正制御回路を設け、特定の信号電圧を各列の表示素子群に一括して印加した場合に、各発光素子（有機EL素子）に流れる測定電流（書込電流）を各行ごとに順次サンプリングしてデジタルデータとして記憶し、通常の画像表示動作において、表示データの補正処理に適用する構成を有している。10

#### 【0087】

すなわち、図8、図9に示すように、本実施形態に係る表示装置100Bは、概略、上述した第1の実施形態と同等の構成を有するゲートドライバ120、データドライバ130、システムコントローラ150、表示信号生成回路160に加え、相互に直交するように配設された走査ラインSL及びデータラインDL、各走査ラインSLに並列に配設された電源ラインPL1、PL2、…PLn（以下、「電源ラインPL」とも記す）とを備え、走査ラインSL及び電源ラインPLとデータラインDLとの各交点に、画素駆動回路DCA及び有機EL素子OELからなる複数の表示画素が配列された表示パネル110Bと、後述する本実施形態特有の構成を有する補正制御回路140Bと、を備えて構成されている。20

#### 【0088】

なお、本実施形態に適用されるゲートドライバ120は、第1の実施形態に示したように、システムコントローラ150から供給される走査制御信号に基づいて、走査信号V<sub>scan</sub>を各走査ラインSLに順次印加する機能に加え、後述する特定量測定動作において示すように、例えば、ハイレベルの走査信号V<sub>scan</sub>を全ての走査ラインSLに一斉に印加する機能を備えている。

#### 【0089】

##### （補正制御回路140B）

補正制御回路140Bは、例えば、図9に示すように、上述した第1の実施形態と同等の構成を有するA/DコンバータADC、記憶部BM、加算器ADMに加え、各走査ラインSLごとに設けられ、上述した第1の実施形態と同様に、各表示画素（有機EL素子OEL）における発光特性に関連する特定量を測定する動作を行うとともに、各表示画素への高電位電圧V<sub>dd</sub>の印加を制御する動作を行う複数のスイッチ回路部SWB1、SWB2、…SWBm（以下、「スイッチ回路部SWB」とも記す）と、を有して構成されている。30

#### 【0090】

ここで、各スイッチ回路部SWBは、ゲート端子が次の行の走査ラインSLに、ソース端子及びドレイン端子が電源ラインPL及びA/DコンバータADCに各々接続された薄膜トランジスタ（読み出制御トランジスタ）Tr15と、ゲート端子にシステムコントローラ150から出力される補正制御信号（書込制御信号Vw）が供給され、ソース端子及びドレイン端子が高電位電圧V<sub>dd</sub>及び電源ラインPLに各々接続された薄膜トランジスタ（書込制御トランジスタ）Tr16と、を備えた構成を有している。特に、i行目の表示画素（又は、電源ラインPL）に対応して設けられた薄膜トランジスタTr15のゲート端子は、（i+1）行目の走査ラインSL(i+1)に順次接続された構成を有し、また、最終行（n行目）の表示画素に対応して設けられた薄膜トランジスタTr15のゲート端子は、1行目の走査ラインSL1に接続された構成を有している。40

#### 【0091】

<表示装置の駆動制御方法の第2の実施形態>

50

次に、上述した構成を有する表示装置における駆動制御動作（駆動制御方法）について、図面を参照して具体的に説明する。

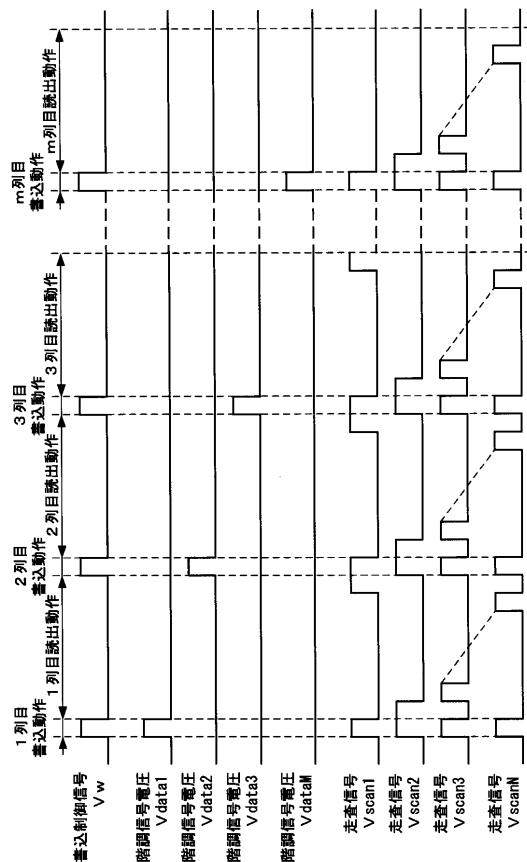

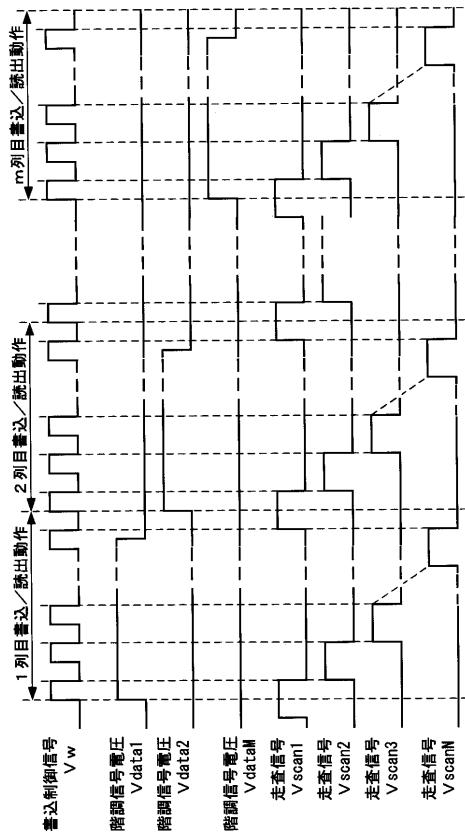

図10は、本実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。図11は、本実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書込動作）を示す動作概念図であり、図12は、本実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。

#### 【0092】

本実施形態に係る表示装置の駆動制御方法においても、上述した第1の実施形態と同様に、映像信号に基づく所望の画像情報を、表示パネル110Bに表示する画像表示動作と、各表示画素（有機EL素子OEL）の発光特性に関連する特定量を測定する特定量測定動作と、該特定量測定動作により得られた特定量に基づいて、表示データを補正するデータ補正動作と、を含んでいる。10

#### 【0093】

##### （特定量測定動作）

本実施形態に係る特定量測定動作は、システムコントローラ150により特定量測定状態が設定されると、測定用データRD0として、"H0000000...00000"（1番目のデータのみハイレベル）からなるシリアルデータがデータドライバ130に入力される。これにより、データドライバ130は、データ制御信号に基づくタイミングで、図10に示すように、上記測定用データRD0に基づいて、1列目のデータラインDL1にのみハイレベル（最高階調電圧：MSB）の階調信号電圧（測定用の信号電圧）Vdata1を印加するとともに、他の列のデータラインDL2～DLmにはローレベルの階調信号電圧を印加する。また、このタイミングで、補正制御回路140Bの各スイッチ回路部SWBに設けられた薄膜トランジスタTr16のゲート端子に、システムコントローラ150からハイレベルの書込制御信号Vwが印加されることにより、薄膜トランジスタTr16がオン動作して、高電位電圧Vddが各表示画素の電源ラインPLに印加される。20

#### 【0094】

次いで、走査制御信号に基づくタイミングで、図10、図11に示すように、ゲートドライバ120により全ての行の走査ラインSLにハイレベルの走査信号Vscan1～VscanNを印加して、各走査ラインSLに接続された各表示画素の画素駆動回路DCAに設けられた薄膜トランジスタTr11をオン動作させ、全ての表示画素を選択状態に設定する。30

#### 【0095】

これにより、図11中、実線矢印で示すように、データラインDL1に印加されたハイレベル（=MSB）を有する階調信号電圧Vdata1が、1列目の各表示画素（画素駆動回路DCA）の薄膜トランジスタTr11を介して、薄膜トランジスタTr12のゲート端子に印加されて、当該ゲート電圧（階調信号電圧Vdata1）に応じた導通状態でオン動作するので、高電位電圧Vdd側から薄膜トランジスタTr12及び有機EL素子OELを介して接地電位に電流（書込電流）が流れ。このとき、薄膜トランジスタTr12のゲート-ソース間に生じる電位差が、ゲート-ソース間の寄生容量Caに電圧成分として保持される（1列目の表示画素群への測定用信号電圧の書込動作）。40

#### 【0096】

次いで、図10、図12に示すように、ゲートドライバ120により2行目の走査ラインSL2にハイレベルの走査信号Vscan2を引き続き印加するとともに、他の行の走査ラインSL1、SL3～SLnにローレベルの走査信号Vscan1、Vscan3～VscanNを印加することにより、2行目の表示画素群のみを選択状態に設定する。また、このタイミングで、書込制御信号Vwをローレベルに切り換えることにより、各スイッチ回路部SWBの薄膜トランジスタTr16をオフ動作させて、各電源ラインPLへの高電位電圧Vddの印加を遮断する。

#### 【0097】

これにより、図12中、実線矢印で示すように、2行目の走査ラインSL2に印加された

10

20

30

40

50

ハイレベルを有する走査信号  $V_{scan2}$  が、補正制御回路 140B の 1 行目のスイッチ回路部 SWB1 の薄膜トランジスタ Tr15 のゲート端子に印加されてオン動作することにより、A/D コンバータ ADC から薄膜トランジスタ Tr15 を介して、1 行目の電源ライン PL1 に測定用電圧（高電位電圧  $V_{dd}$ ）が印加される。

#### 【0098】

ここで、1 列目の表示画素群を構成する各画素駆動回路（薄膜トランジスタ Tr12 のゲート - ソース間寄生容量 Ca）には、上記測定用信号電圧の書込動作におけるゲート - ソース間電圧が保持されているため、当該電圧により薄膜トランジスタ Tr12 はオン状態を維持し、A/D コンバータ ADC 側から、1 行 1 列目の表示画素の薄膜トランジスタ Tr12 及び有機 EL 素子 OEL を介して接地電位に電流（測定電流）が流れる。 10

#### 【0099】

そして、この 1 行 1 列目の表示画素（有機 EL 素子 OEL）に流れる測定電流（アナログ信号電流）を、A/D コンバータ ADC によりサンプリングしてデジタル信号化し、記憶部 BM に記憶する。ここで、A/D コンバータ ADC によりサンプリングされる測定電流は、上述した第 1 の実施形態と同様に、測定用データ RD0 の書込動作により当該表示画素（画素駆動回路 DCA）の薄膜トランジスタ Tr12 のゲート - ソース間寄生容量 Ca に保持された電圧成分に応じた電流値を有しているので、当該表示画素（有機 EL 素子 OEL）の発光特性に関連する特定量（測定電流の電流値）が記憶部 BM に記憶されることになる（1 行 1 列目の表示画素からの測定電流の読み出動作）。 20

#### 【0100】

以下、同様に、3 行目以降の走査ライン SLi にハイレベルの走査信号  $V_{scan_i}$  を順次印加することにより、(i-1) 行目のスイッチ回路部 SWB(i-1) の薄膜トランジスタ Tr15 が順次オン動作して、A/D コンバータ ADC から薄膜トランジスタ Tr15 を介して、(i-1) 行目の電源ライン PL(i-1) に測定用電圧（ $V_{dd}$ ）が印加され、A/D コンバータ ADC 側から、(i-1) 行目の表示画素の有機 EL 素子 OEL に電流（測定電流）が流れる。この測定電流を、A/D コンバータ ADC により順次サンプリングすることにより、1 列目の各表示画素（有機 EL 素子 OEL）における発光特性に関する特定量が記憶部 BM に記憶される。 20

#### 【0101】

そして、図 10 に示すように、上述した 1 列目の表示画素群に対して実行した特定量測定動作（各列の表示画素群への測定用信号電圧の書込動作、各行の表示画素からの測定電流の読み出動作）を 2 列目以降の各列についても順次繰り返し実行することにより、表示パネル 110B を構成する全ての表示画素（有機 EL 素子 OEL）における発光特性に関する特定量がデジタルデータとして取得される。 30

#### 【0102】

なお、本実施形態における通常の画像表示動作においても、上述した第 1 の実施形態と同等に、上記特定量測定動作により記憶部 BM に記憶された測定電流の電流値に基づいて、各表示画素（有機 EL 素子 OEL）の発光特性に対応した補正值を生成し、表示信号生成回路 160 から供給される表示データに対して、加算器 ADM により該補正值を加算する補正処理を行って、補正後データとしてデータドライバ 130 に供給するデータ補正動作が実行され、該補正後データに基づく階調信号電圧を用いて、各表示画素を適切な輝度階調で発光動作させることにより所望の画像情報が表示される。したがって、ここでは、データ補正動作を含む画像表示動作についての説明を省略する。 40

これにより、補正後データに基づいて生成された階調信号電圧が各表示画素に印加され、各有機 EL 素子 OEL に流れる発光駆動電流の電流値を、予め設定された理想値に近似させて、映像信号に良好に対応した輝度階調で発光素子を発光動作させることができる。

#### 【0103】

<表示装置の駆動制御方法の第 3 の実施形態>

次に、本発明に係る表示装置における駆動制御動作（駆動制御方法）の第 3 の実施形態について、図面を参照して具体的に説明する。ここで、本実施形態に係る表示装置は、上述

した第2の実施形態と同等の構成(図8、図9参照)を適用することができる。

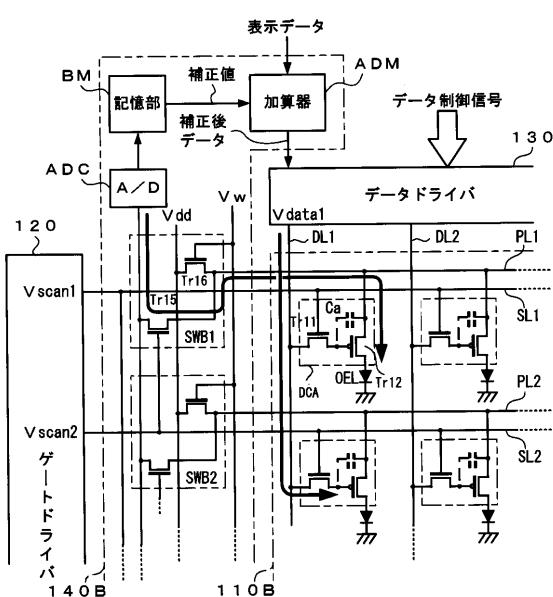

#### 【0104】

図13は、第3の実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。図14は、本実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態(書込動作)を示す動作概念図であり、図15は、本実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態(読み出動作)を示す動作概念図である。なお、上述した第1及び第2の実施形態と同等の構成及び動作については、その説明を簡略化又は省略する。また、上述した第2の実施形態に示した構成(図8、図9参照)を適宜参照して説明する。

#### 【0105】

本実施形態においては、上述した第2の実施形態と同様に、ゲートドライバと表示パネルとの間に補正制御回路を設けた構成において、特定の信号電圧を各列の表示素子群に継続的に印加した場合に、各発光素子(有機EL素子)に流れる測定電流(書込電流)を各行ごとに順次サンプリングしてデジタルデータとして記憶し、通常の画像表示動作において表示データの補正処理に適用する構成を有している。

#### 【0106】

本実施形態に係る表示装置の駆動制御方法においても、上述した第1及び第2の実施形態と同様に、通常の画像表示動作と、特定量測定動作と、データ補正動作と、を含んでいる。なお、本実施形態においても、上述した第1の実施形態と同等に、上記特定量測定動作により取得された特定量(測定電流の電流値)に基づいて、表示データを補正してデータドライバ130に供給するデータ補正動作が実行され、該補正後データに基づく階調信号電圧を用いて、各表示画素を適切な輝度階調で発光動作させることにより所望の画像情報を表示する画像表示動作が実行される。したがって、ここでは、データ補正動作を含む画像表示動作についての説明を省略する。

#### 【0107】

##### (特定量測定動作)

本実施形態に係る特定量測定動作は、図8、図9に示した表示装置100Bの構成において、システムコントローラ150により特定量測定状態が設定されると、測定用データRD0として、"H0000000...00000"からなるシリアルデータがデータドライバ130に入力され、これにより、データ制御信号に基づくタイミングで、図13に示すように、1列目のデータラインDL1にのみハイレベル(最高階調電圧:MSB)の階調信号電圧(測定用の信号電圧)Vdata1が印加されるとともに、他の列のデータラインDL2~DLmにローレベルの階調信号電圧が印加される。

#### 【0108】

また、このタイミングで、システムコントローラ150からハイレベルの書込制御信号Vwが供給されることにより、補正制御回路140Bの各スイッチ回路部SWBに設けられた薄膜トランジスタTr16がオン動作して、高電位電圧Vddが各電源ラインPLに印加される。

ここで、本実施形態においては、1列目のデータラインDL1に印加されるハイレベルの階調信号電圧Vdata1は、後述する当該列の各表示画素における測定電流のサンプリングが全て終了するまで継続的に印加される。

#### 【0109】

次いで、走査制御信号に基づくタイミングで、図13、図14に示すように、ゲートドライバ120により1行目の走査ラインSL1にハイレベルの走査信号Vscan1を印加して、該走査ラインSL1に接続された各表示画素の画素駆動回路DCAに設けられた薄膜トランジスタTr11をオン動作させ、選択状態に設定する。

#### 【0110】

これにより、図14中、実線矢印で示すように、データラインDL1に印加されたハイレベル(=MSB)の階調信号電圧Vdata1が、1行1列目の表示画素(画素駆動回路DCA)に印加されることにより、薄膜トランジスタTr12が当該階調信号電圧Vdata1に

10

20

30

40

50

応じた導通状態でオン動作するので、高電位電圧  $V_{dd}$  側から薄膜トランジスタ  $T_{r12}$  及び有機EL素子  $OEL$  に電流（書き電流）が流れる。このとき、薄膜トランジスタ  $T_{r12}$  のゲート - ソース間に生じる電位差が、ゲート - ソース間の寄生容量  $C_a$  に電圧成分として保持される（1行1列目の表示画素への測定用信号電圧の書き動作）。

#### 【0111】

次いで、図13、図15に示すように、ゲートドライバ120により2行目の走査ライン  $S_L2$  にハイレベルの走査信号  $V_{scan2}$  を印加して、補正制御回路140Bの1行目のスイッチ回路部  $SWB1$  の薄膜トランジスタ  $T_{r15}$  をオン動作させるとともに、このタイミングで、システムコントローラ150により書き制御信号  $V_w$  をローレベルに切り換えることにより、各スイッチ回路部  $SWB$  の薄膜トランジスタ  $T_{r16}$  をオフ動作させて、各電源ライン  $PL$  への高電位電圧  $V_{dd}$  の印加を遮断する。

10

#### 【0112】

これにより、図15中、実線矢印で示すように、A/DコンバータADCから薄膜トランジスタ  $T_{r15}$  を介して、1行目の電源ライン  $PL1$  に測定用電圧（高電位電圧  $V_{dd}$ ）が印加される。

ここで、1列目の表示画素群の各画素駆動回路（薄膜トランジスタ  $T_{r12}$  のゲート - ソース間寄生容量  $C_a$ ）には、上記測定用信号電圧の書き動作におけるゲート - ソース間電圧が保持されているため、薄膜トランジスタ  $T_{r12}$  はオン状態を維持し、A/DコンバータADC側から、1行1列目の表示画素の薄膜トランジスタ  $T_{r12}$  及び有機EL素子  $OEL$  に電流（測定電流）が流れる。

20

そして、この1行1列目の表示画素（有機EL素子  $OEL$ ）に流れる測定電流を、A/DコンバータADCによりサンプリングしてデジタル信号化し、記憶部BMに記憶する（1行1列目の表示画素からの測定電流の読み出動作）。

#### 【0113】

次いで、ゲートドライバ120により2行目の走査ライン  $S_L2$  へのハイレベルの走査信号  $V_{scan2}$  の印加を継続するとともに、補正制御回路140Bの各スイッチ回路部  $SWB$  にハイレベルの書き制御信号  $V_w$  を供給することにより、データライン  $DL1$  に印加されているハイレベル（=  $MSB$ ）の階調信号電圧  $V_{data1}$  が、2行1列目の表示画素（画素駆動回路  $DCA$ ）に印加されて、当該表示画素の薄膜トランジスタ  $T_{r12}$  が当該階調信号電圧  $V_{data1}$  に応じた導通状態でオン動作して、薄膜トランジスタ  $T_{r12}$  及び有機EL素子  $OEL$  に書き電流が流れる。このとき、薄膜トランジスタ  $T_{r12}$  のゲート - ソース間に生じる電位差が、ゲート - ソース間の寄生容量  $C_a$  に電圧成分として保持される（2行1列目の表示画素への測定用信号電圧の書き動作）。

30

#### 【0114】

以下、同様に、図13に示すように、3行目以降の走査ライン  $S_Li$  にハイレベルの走査信号  $V_{scani}$  を印加するとともに、補正制御回路140Bの各スイッチ回路部  $SWB$  にロー レベルの書き制御信号  $V_w$  を供給することにより、 $i$  行1列目の表示画素（画素駆動回路  $DCA$ ）の薄膜トランジスタ  $T_{r12}$  及び有機EL素子  $OEL$  に測定電流が流れ、この測定電流がA/DコンバータADCによりサンプリングされてデジタルデータとして記憶部BMに記憶される（ $i$  行1列目の表示画素からの測定電流の読み出動作）。

40

#### 【0115】

そして、図13に示すように、上述した1列目の表示画素群に対して実行した特定量測定動作（各列の表示画素への測定用信号電圧の書き動作、各行の表示画素からの測定電流の読み出動作）を2列目以降の各列についても順次繰り返し実行することにより、表示パネル110Bを構成する全ての表示画素（有機EL素子  $OEL$ ）における発光特性に関連する特定量がデジタルデータとして取得される。

これにより、補正後データに基づいて生成された階調信号電圧が各表示画素に印加され、各有機EL素子  $OEL$  に流れる発光駆動電流の電流値を、予め設定された理想値に近似させて、映像信号に良好に対応した輝度階調で発光素子を発光動作させることができる。

#### 【0116】

10

20

30

40

50

また、本実施形態に係る特定量測定動作においては、 $i$  行  $j$  列目の表示画素への測定用信号電圧の書込動作の直後に、当該表示画素からの測定電流の読出動作を実行することができる。これにより、測定用信号電圧の書込動作により各表示画素（画素駆動回路 D C A）の薄膜トランジスタ T r 1 2 に生じるゲート - ソース間の寄生容量 C a に充電された電圧成分が、測定電流の読出動作までの待機期間に電荷のリークにより低下して、上記表示画素に流れる測定電流の電流値に影響を与える（本来の電流値よりも低下する）ことを抑制して、各表示画素（有機 E L 素子）の発光特性に良好に対応したデジタルデータを取得することができる。

#### 【 0 1 1 7 】

<表示装置の第 4 の実施形態 >

10

次に、本発明に係る表示駆動装置を適用可能な表示装置の第 4 の実施形態について、図面を参照して説明する。

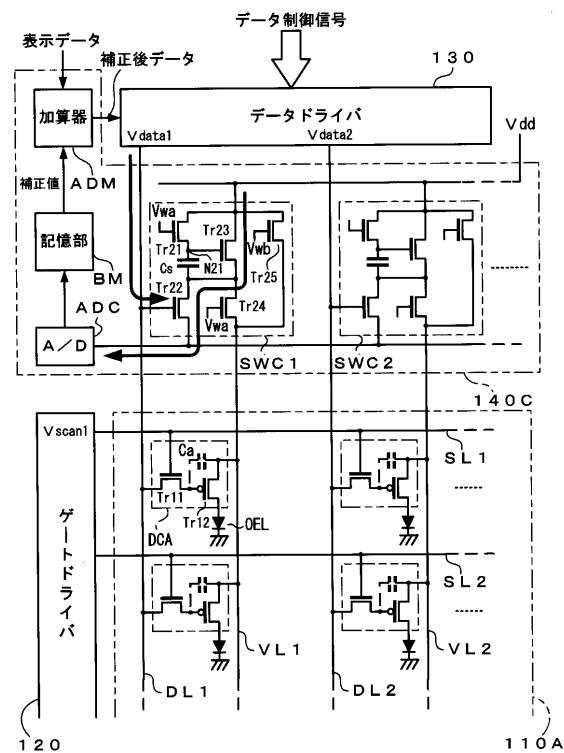

図 1 6 は、本発明に係る表示駆動装置を適用した表示装置の第 4 の実施形態を示す要部概略構成図である。なお、ここでは、上述した第 1 の実施形態（図 1、図 2 参照）と同等の構成については、同一の符号を付して、その説明を簡略化又は省略する。

#### 【 0 1 1 8 】

上述した第 1 乃至第 3 の実施形態においては、特定の信号電圧を各表示素子に印加した場合に、各発光素子（有機 E L 素子）に流れる測定電流（書込電流）を順次サンプリングしてデジタルデータとして記憶する場合について説明したが、本実施形態においては、データドライバと表示パネルとの間に設けた補正制御回路により、特定の信号電圧を各表示素子に印加した場合に、補正制御回路に流れる測定電流（書込電流；電流成分）を各表示画素行ごとに順次サンプリングしてデジタルデータとして記憶し、通常の画像表示動作において、表示データの補正処理に適用する構成を有している。

20

#### 【 0 1 1 9 】

すなわち、図 1 6 に示すように、本実施形態に係る表示装置 1 0 0 C は、概略、上述した第 1 の実施形態と同等の構成を有する表示パネル 1 1 0 A、ゲートドライバ 1 2 0、データドライバ 1 3 0、システムコントローラ（図示を省略）1 5 0、表示信号生成回路（図示を省略）1 6 0 に加え、後述する本実施形態特有の構成を有する補正制御回路 1 4 0 C と、を備えて構成されている。

#### 【 0 1 2 0 】

30

（補正制御回路 1 4 0 C ）

補正制御回路 1 4 0 C は、例えば、図 1 6 に示すように、上述した第 1 の実施形態と同等の構成を有する A / D コンバータ A D C、記憶部 B M、加算器 A D M に加え、各データライン D L ごとに設けられ、上述した第 1 の実施形態と同様に、各表示画素（有機 E L 素子 O E L ）における発光特性に関連する特定量を測定する動作を行うとともに、各表示画素への高電位電圧 V dd の印加を制御する動作を行う複数のスイッチ回路部 S W C 1、S W C 2、… S W C m（以下、「スイッチ回路部 S W C」とも記す）と、を有して構成されている。

#### 【 0 1 2 1 】

ここで、各スイッチ回路部 S W C は、ゲート端子にシステムコントローラ 1 5 0 から出力される補正制御信号（第 1 の書込制御信号 V wa）が供給され、ソース端子及びドレイン端子が高電位電圧 V dd 及び接点 N 2 1 に各々接続された薄膜トランジスタ（書込制御トランジスタ）T r 2 1 と、ゲート端子がデータライン D L に、ソース端子及びドレイン端子が A / D コンバータ A D C 及び接点 N 2 2 に各々接続された薄膜トランジスタ（読出制御トランジスタ）T r 2 2 と、接点 N 2 1 と接点 N 2 2 との間に接続されたコンデンサ（保持容量；蓄積手段）C s と、ゲート端子が接点 N 2 1 、ソース端子及びドレイン端子が高電位電圧 V dd 及び接点 N 2 2 に各々接続された薄膜トランジスタ（データ保持トランジスタ）T r 2 3 と、ゲート端子に補正制御信号（第 1 の書込制御信号 V wa）が供給され、ソース端子及びドレイン端子が接点 N 2 2 及び電源ライン V L に各々接続された薄膜トランジスタ（書込制御トランジスタ）T r 2 4 と、ゲート端子に補正制御信号（第 2 の書込制御信号

40

50

信号  $V_{wb}$  ) が供給され、ソース端子及びドレイン端子が高電位電圧  $V_{dd}$  及び電源ライン  $V_L$  に各々接続された薄膜トランジスタ ( 切換制御トランジスタ )  $T_{r25}$  と、を備えた構成を有している。

ここで、システムコントローラ 150 から出力され、薄膜トランジスタ  $T_{r21}$  、 $T_{r24}$  のゲート端子に印加される第 1 の書込制御信号  $V_{wa}$  と、薄膜トランジスタ  $T_{r25}$  のゲート端子に印加される第 2 の書込制御信号  $V_{wb}$  は、後述するように、相互に位相が逆転した信号波形を有するように設定されている。

#### 【 0122 】

< 表示装置の駆動制御方法の第 4 の実施形態 >

次に、上述した構成を有する表示装置における駆動制御動作 ( 駆動制御方法 ) について、図面を参照して具体的に説明する。 10

図 17 は、本実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。図 18 は、本実施形態に係る表示装置において実行される特定量測定動作の第 1 の動作状態 ( 書込動作 ) 、及び、通常の画像表示動作を示す動作概念図であり、図 19 は、本実施形態に係る表示装置において実行される特定量測定動作の第 2 の動作状態 ( 読出動作 ) を示す動作概念図である。

本実施形態に係る表示装置の駆動制御方法においても、上述した各実施形態と同様に、通常の画像表示動作と、特定量測定動作と、データ補正動作と、を含んでいる。以下、各動作について説明する。 20

#### 【 0123 】

( 特定量測定動作 )

本実施形態に係る特定量測定動作は、システムコントローラ 150 により特定量測定状態が設定されると、測定用データ  $RDO$  として、" HHHHHHHHHHHH...H HHHH " ( 全てハイレベル ) からなるシリアルデータがデータドライバ 130 に入力され、これにより、データ制御信号に基づくタイミングで、図 17 に示すように、いずれもハイレベル ( 最高階調電圧 : MSB ) からなる階調信号電圧 ( 測定用の信号電圧 )  $V_{data1} \sim V_{dataM}$  が各データライン  $DL$  に印加される。 20

#### 【 0124 】

また、このタイミングで、補正制御回路 140C の各スイッチ回路部  $SWC$  に設けられた薄膜トランジスタ  $T_{r21}$  、 $T_{r24}$  のゲート端子に、システムコントローラ 150 からハイレベルの書込制御信号  $V_{wa}$  が印加されとともに、薄膜トランジスタ  $T_{r25}$  のゲート端子に、ローレベルの書込制御信号  $V_{wb}$  が印加されることにより、薄膜トランジスタ  $T_{r21}$  、 $T_{r24}$  がオン動作するとともに、薄膜トランジスタ  $T_{r25}$  がオフ動作する。これにより、スイッチ回路部  $SWC$  の接点  $N21$  ( 薄膜トランジスタ  $T_{r23}$  のゲート端子 ) に高電位電圧  $V_{dd}$  に基づくハイレベルが印加されて、薄膜トランジスタ  $T_{r23}$  がオン動作するため、薄膜トランジスタ  $T_{r23}$  、 $T_{r24}$  を介して、各表示画素の電源ライン  $V_L$  に高電位電圧  $V_{dd}$  が印加される。 30

#### 【 0125 】

次いで、走査制御信号に基づくタイミングで、図 17 、図 18 に示すように、ゲートドライバ 120 により 1 行目の走査ライン  $SL1$  にハイレベルの走査信号  $V_{scan1}$  を印加して、走査ライン  $SL1$  に接続された各表示画素の画素駆動回路  $DCA$  に設けられた薄膜トランジスタ  $T_{r11}$  をオン動作させ、選択状態に設定する。 40

#### 【 0126 】

これにより、図 18 中、実線矢印で示すように、データライン  $DL1$  に印加されたハイレベル ( = MSB ) の階調信号電圧  $V_{data1}$  が、1 行 1 列目の表示画素 ( 画素駆動回路  $DCA$  ) に印加されることにより、薄膜トランジスタ  $T_{r12}$  が当該階調信号電圧  $V_{data1}$  に応じた導通状態でオン動作するので、高電位電圧  $V_{dd}$  側から薄膜トランジスタ  $T_{r12}$  及び有機 E L 素子 OEL に電流 ( 書込電流 ) が流れる。このとき、薄膜トランジスタ  $T_{r12}$  のゲート - ソース間に生じる電位差が、ゲート - ソース間の寄生容量  $C_a$  に電圧成分として保持される ( 1 行 1 列目の表示画素への測定用信号電圧の書込動作 ) 。 50

## 【0127】

これにより、図18中、実線矢印で示すように、各データラインD Lに印加されたハイレベル(=MSB)の階調信号電圧V dataが、1行目の各表示画素(画素駆動回路D C A)に印加されて、薄膜トランジスタT r 1 2が当該階調信号電圧V dataに応じた導通状態でオン動作するので、電源ラインV L(高電位電圧V dd)側から薄膜トランジスタT r 1 2及び有機EL素子O E Lに電流(書込電流)が流れる。このとき、薄膜トランジスタT r 1 2のゲート-ソース間に生じる電位差が、ゲート-ソース間の寄生容量C aに電圧成分として保持されるとともに、補正制御回路140Cの各スイッチ回路S W Cに設けられた薄膜トランジスタT r 2 3がオン動作することにより、薄膜トランジスタT r 2 3のゲート-ソース間に生じる電位差が、ゲート-ソース間に接続された保持容量C sに電圧成分として保持される(1行目の表示画素への測定用信号電圧の書込動作)。

## 【0128】

次いで、図17、図19に示すように、ゲートドライバ120により1行目の走査ラインS L 1に印加される走査信号V scan1を、ローレベルに切り換えることにより、当該行の表示画素群を非選択状態に設定する。また、このタイミングで、システムコントローラ150により各スイッチ回路部S W Cに印加される書込制御信号V waをローレベルに、また、書込制御信号V wbをハイレベルに切り換えることにより、薄膜トランジスタT r 2 1、T r 2 4をオフ動作させるとともに、薄膜トランジスタT r 2 5をオン動作させて、各電源ラインV Lへの高電位電圧V ddの印加を遮断する。

## 【0129】

次いで、"H 0 0 0 0 0 0 0 · · · 0 0 0 0"(1番目のデータのみハイレベル)からなる測定用データ(シリアルデータ)R D 1をデータドライバ130に入力することにより、1列目のデータラインD L 1にのみハイレベル(=MSB)の階調信号電圧(測定用の信号電圧)V data1を印加するとともに、他の列のデータラインD L 2 ~ D L mにはローレベルの階調信号電圧を印加する。

これにより、図19中、実線矢印で示すように、1列目のデータラインD L 1に印加されたハイレベルを有する階調信号電圧V data1が、補正制御回路140Cの1列目のスイッチ回路部S W C 1の薄膜トランジスタT r 2 2のゲート端子に印加されてオン動作する。

## 【0130】

ここで、1列目のスイッチ回路部S W Cに設けられた薄膜トランジスタT r 2 3のゲート-ソース間の保持容量C sには、上記測定用信号電圧の書込動作において、1行1列目の表示画素に書込電流を流す際に薄膜トランジスタT r 2 3のゲート-ソース間に生じた電位差が電圧成分として保持されているため、当該電圧により薄膜トランジスタT r 2 3はオン状態を維持する。これにより、高電位電圧V ddから薄膜トランジスタT r 2 3、接点N 2 2、薄膜トランジスタT r 2 2を介して、A / DコンバータA D Cに電流(測定電流)が流れる。

## 【0131】

そして、このA / DコンバータA D Cに流れ込む測定電流を、サンプリングしてデジタル信号化し、記憶部B Mに記憶する。ここで、A / DコンバータA D Cによりサンプリングされる測定電流は、測定用データR D 0の書込動作により1行1列目の表示画素(画素駆動回路D C A)の薄膜トランジスタT r 1 2のゲート-ソース間寄生容量C aに保持された電圧成分に対応した電流値を有しているので、当該表示画素(有機EL素子O E L)の発光特性に関連する特定量(測定電流の電流値)が記憶部B Mに記憶されることになる(1行1列目の表示画素からの測定電流の読出動作)。

## 【0132】

以下、同様に、2列目以降のデータラインD L jにハイレベル(=MSB)の階調信号電圧(測定用の信号電圧)V data2を印加することにより、図19に示した場合と同様に、j列目のデータラインD L jに接続されたスイッチ回路部S W C jの薄膜トランジスタT r 2 2がオン動作して、高電位電圧V ddから薄膜トランジスタT r 2 3、T r 2 2を介して、A / DコンバータA D Cに測定電流が流れ込むので、A / DコンバータA D Cにより

10

20

30

40

50

この測定電流を順次サンプリングすることにより、1行目の各表示画素（有機EL素子OEL）における発光特性に関する特定量が記憶部BMに順次記憶される。

#### 【0133】

そして、図17に示すように、上述した1行目の表示画素群に対して実行した特定量測定動作（各行の表示画素群への測定用信号電圧の書込動作、各列の表示画素からの測定電流の読出動作）を2行目以降の各行についても順次繰り返し実行することにより、表示パネル110Aを構成する全ての表示画素（有機EL素子OEL）における発光特性に関連する特定量がデジタルデータとして取得される。

#### 【0134】

（画像表示動作／データ補正動作）

10

本実施形態における通常の画像表示動作は、図16に示した表示装置において、まず、表示信号生成回路160から出力された1行分の表示データが、補正制御回路140Cによりデータ補正処理されて、補正後データとしてデータドライバ130に供給される。ここで、補正制御回路140Cにより実行されるデータ補正処理（データ補正動作）は、上述した第1の実施形態と同様に、特定量測定動作により記憶部BMに記憶された測定電流の電流値に基づいて、各表示画素（有機EL素子OEL）の発光特性に対応した補正值を生成し、表示信号生成回路160から供給される表示データに対して、加算器ADMにより該補正值を加算する補正処理を行って、補正後データとしてデータドライバ130に供給する。

#### 【0135】

20

これにより、データドライバ130は、補正表示データに基づいて、各列のデータラインDLに対応する階調信号電圧Vdataを生成して印加する。このとき、システムコントローラ150からローレベルの書込制御信号Vwa及びハイレベルの書込制御信号Vwbが補正制御回路140Cに印加されることにより、補正制御回路140Cの各列に設けられたスイッチ回路部SWCの薄膜トランジスタTr21、Tr24がオフ動作するとともに、薄膜トランジスタTr25がオン動作して、薄膜トランジスタTr25を介して各列の電源ラインVLに高電位電圧Vddが印加される。

#### 【0136】

次いで、ゲートドライバ120により1行目の走査ラインSLiにハイレベルの走査信号Vscaniを印加して、当該行の表示画素群を選択状態に設定することにより、画素駆動回路DCAの薄膜トランジスタTr12が階調信号電圧Vdataに応じた導通状態でオン動作して、電源ラインVLから薄膜トランジスタTr12及び有機EL素子OELに発光駆動電流が流れ、有機EL素子OELが所定の発光輝度で発光動作する。

30

#### 【0137】

このように、特定量測定動作により取得された各表示画素（有機EL素子OEL）の発光特性に関連した特定量に基づいて、表示データをデータ補正し、該補正後データに基づく階調信号電圧を各表示画素に印加することにより、有機EL素子OELに流れる発光駆動電流の電流値を、予め設定された理想値に近似させることができ、映像信号に良好に対応した輝度階調で発光素子を発光動作させることができる。

#### 【0138】

40

なお、上述した各実施形態においては、特定量測定動作の実行タイミングについて、通常の画像表示動作に先立って実行する場合について説明したが、本発明はこれに限定されるものではなく、例えば、表示装置の起動時（起動直後）や、表示動作終了時、あるいは、表示待機時等、定期又は不定期の任意のタイミングで実行するものであってもよい。

また、上述した特定量測定動作においては、各表示画素に印加する測定用の信号電圧として、最高階調電圧（=MSB）のみを適用した場合について説明したが、本発明はこれに限定されるものではなく、例えば、他の階調信号電圧や、複数の異なる階調信号電圧に対して発光素子に流れる測定電流の電流値を測定して、当該電流値に基づいて、データ補正動作を実行するものであってもよい。

#### 【0139】

50

さらに、上述した特定量測定動作を実行している期間（書込動作、読出動作）においては、一時的に、各表示画素の有機EL素子OELに書込電流や測定電流が流れるため、所定の輝度階調で順次点灯する動作が表示装置の使用者に視認されるが、これにより、特定量測定動作が正常に実行されていることを認識させることもできる。

#### 【0140】

加えて、上述した各実施形態においては、表示パネルと、データドライバ又はゲートドライバと、補正制御回路との関係について特に説明しなかったが、本発明においては、例えば、表示パネルを構成する基板上に、少なくとも、表示画素（画素駆動回路及び発光素子）と補正制御回路の全て又は一部の構成を一体的に薄膜形成された構成を有するものであってもよい。これによれば、既存のデータドライバやゲートドライバ等のドライバチップ（ドライバ用のICチップ）をそのまま使用することができ、本発明に係る表示装置を大幅な設計変更を伴うことなく、安価に実現することができる。さらには、データドライバ又はゲートドライバを上記基板上に補正制御回路とともに一体的に形成した構成を適用するものであってもよく、これによれば、表示装置の装置規模を大幅に小型化することができる。

10

#### 【0141】

また、本発明においては、上記補正制御回路の全て又は一部の構成を、データドライバ又はゲートドライバと一体的に形成し、単一のドライバチップに内蔵した構成を有するものであってもよい。これによれば、少なくとも補正制御回路及びドライバをユニット化することができ、既存の表示パネルとの接続構造やプロセスをそのまま適用することができ、製造工程の簡素化を図ることができる。

20

#### 【0142】

ところで、上述した各実施形態においては、表示画素を構成する画素駆動回路DCAとして、従来技術に示した構成と同様に、nチャネル型の薄膜トランジスタ（選択トランジスタ）Tr11と、pチャネル型の薄膜トランジスタ（発光駆動トランジスタ）Tr12と、を備えた回路構成を適用した場合について説明した。このような回路構成によれば、pチャネル型とnチャネル型のトランジスタが混在した回路構成となるので、ポリシリコンプロセスを適用して、良好な動作特性を有する薄膜トランジスタを製造することができ、表示画素の発光特性のバラツキや劣化を抑制した画素駆動回路を実現することができる。

#### 【0143】

30

ここで、本発明に適用可能な画素駆動回路は、上述したようなpチャネル型とnチャネル型の薄膜トランジスタが混在した回路構成に限定されるものではなく、單一チャネル型の薄膜トランジスタからなる回路構成を適用することもできる。以下、本発明に適用可能な画素駆動回路の他の例について説明する。

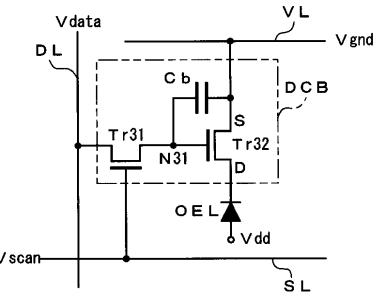

図20は、本発明に係る表示装置の表示画素に適用可能な画素駆動回路（発光駆動回路）の他の例を示す等価回路図である。

#### 【0144】

図20に示すように、本発明に係る表示装置に適用可能な画素駆動回路DCBは、ゲート端子が走査ラインSLに、ソース端子及びドレイン端子がデータラインDL及び接点N31に各々接続されたnチャネル型の薄膜トランジスタTr31と、ゲート端子が接点N31に、ソース端子が接地電位Vgndに各々接続された薄膜トランジスタTr32と、を備えた構成を有している。また、該画素駆動回路DCBにより発光状態が制御される有機EL素子OEL（発光素子）は、カソード端子が画素駆動回路DCBの薄膜トランジスタTr32のドレイン端子に、アノード端子が接地電位Vgndよりも高い高電圧からなる定電源電圧Vddに接続された構成を有している。なお、図20において、Cbは、薄膜トランジスタTr32のゲート-ソース間に形成される寄生容量である。

40

#### 【0145】

このような画素駆動回路を備えた表示パネルによれば、画素駆動回路DCBを構成する薄膜トランジスタが、nチャネル型の薄膜トランジスタのみからなる回路構成を有しているので、ポリシリコンや単結晶シリコンを用いた製造プロセスに比較して、製造プロセスが

50

既に確立され、簡易かつ安価なアモルファスシリコンプロセスを適用して、良好な動作特性を実現することができる。

なお、上述した各実施形態においては、画素駆動回路として、2個の薄膜トランジスタを備えた回路構成のみを示したが、本発明はこれに限定されるものではなく、薄膜トランジスタを3個以上設けたものであってもよいことはいうまでもない。

#### 【0146】

##### 【発明の効果】

以上説明したように、本発明に係る表示駆動装置及び該表示駆動装置を備えた表示装置並びにその駆動制御方法によれば、表示データに応じた階調信号電圧を各表示画素に印加することにより、各表示画素を所定の輝度階調で発光動作させて、所望の画像情報を表示する表示装置において、走査線に沿って行方向に配列された複数の表示画素、又は、前記信号線に沿って列方向に配列された複数の表示画素に特定の信号電圧（例えば、最高階調電圧）を一括して印加し、特定の信号電圧が印加された各表示画素から、発光素子の発光特性に関連する特定量として、発光素子に流れる駆動電流の電流値を、補正制御回路により直接又は間接的に測定し、その電流値と該駆動電流の設定値（理想値）との差分に基づいて補正值を生成し、該補正值を用いて表示画素の各々に対応する表示信号を補正する処理を行うように構成されているので、各表示画素に発光素子の発光特性に応じた（発光特性のバラツキや劣化を補填することができる電圧値に設定された）階調信号電圧を印加することができ、発光素子に、予め設定された理想値に近似した電流値を有する発光駆動電流を流して、表示信号に良好に対応した輝度階調で発光素子を発光動作させることができる。10

#### 【0147】

また、表示パネルを構成する各表示画素として、階調信号電圧に応じた電流値を有する駆動電流を流すとともに、該階調信号電圧に応じた電圧成分を蓄積する発光駆動回路と、該駆動電流の電流値に応じた輝度階調で発光動作する電流制御型の発光素子と、を備えた構成を適用した場合、発光素子の発光特性に関連する特定量として、表示画素に対して、特定の信号電圧を印加した場合の、発光駆動回路に蓄積された電圧成分に基づいて、発光素子に流れる電流（測定電流　書込電流）の電流値を測定する手法を適用することができる。したがって、通常の画像表示動作において表示画素（発光駆動回路）に階調信号電圧を実際に印加した場合と同等の条件で、表示画素の発光特性に関連する特定量を抽出することができる。発光素子の素子特性のみならず、発光駆動回路を構成するトランジスタや容量素子等の機能素子の素子特性をも含めた特定量を取得することができる。20

#### 【0148】

また、補正制御回路として、表示画素に対して、特定の信号電圧を印加した場合の、発光素子に流れる駆動電流に応じた電圧成分を蓄積する蓄積手段を備えた構成を適用した場合、発光素子の発光特性に関連する特定量として、表示画素に対して、特定の信号電圧を印加した場合の、当該蓄積手段に蓄積された電圧成分に基づいて、補正制御回路に流れる電流（測定電流）の電流値を測定する手法を適用することができる。したがって、各表示画素の表示パネル上の配置位置に関わらず、補正制御回路に流れる電流の電流値に基づいて、全ての表示画素の発光特性に関連する特定量を抽出することができるので、表示画素が微細化された場合や表示パネルが大型化された場合であっても、上記補正制御回路に流れる電流を早期に安定化させて、迅速に特定量を取得することができる。30

##### 【図面の簡単な説明】

【図1】本発明に係る表示駆動装置を適用した表示装置の全体構成の第1の実施形態を示すブロック図である。

【図2】第1の実施形態に係る表示装置の要部構成を示す概略構成図である。

【図3】第1の実施形態に係る表示装置に適用されるデータドライバの要部構成を示すブロック図である。

【図4】第1の実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。40

50

50

50

【図5】第1の実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書込動作）を示す動作概念図である。

【図6】第1の実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。

【図7】第1の実施形態に係る表示装置の駆動制御方法に適用される画像表示動作の一例を示すタイミングチャートである。

【図8】本発明に係る表示駆動装置を適用した表示装置の全体構成の第2の実施形態を示すブロック図である。

【図9】第2の実施形態に係る表示装置の要部構成を示す概略構成図である。

【図10】第2の実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。 10

【図11】第2の実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書込動作）を示す動作概念図である。

【図12】第2の実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。

【図13】第3の実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。

【図14】第3の実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書込動作）を示す動作概念図である。

【図15】第3の実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。 20

【図16】本発明に係る表示駆動装置を適用した表示装置の第4の実施形態を示す要部概略構成図である。

【図17】第4の実施形態に係る表示装置の駆動制御方法に適用される特定量測定動作の一例を示すタイミングチャートである。

【図18】第4の実施形態に係る表示装置において実行される特定量測定動作の第1の動作状態（書込動作）、及び、通常の画像表示動作を示す動作概念図である。

【図19】第4の実施形態に係る表示装置において実行される特定量測定動作の第2の動作状態（読み出動作）を示す動作概念図である。

【図20】本発明に係る表示装置の表示画素に適用可能な画素駆動回路（発光駆動回路）の他の例を示す等価回路図である。 30

【図21】従来技術における有機EL素子を備えた発光素子型ディスプレイの各表示画素の回路構成例を示す等価回路図である。

#### 【符号の説明】

|                     |             |

|---------------------|-------------|

| 1 0 0 A ~ 1 0 0 C   | 表示装置        |

| 1 1 0 A、 1 1 0 B    | 表示パネル       |

| 1 2 0               | ゲートドライバ     |

| 1 3 0               | データドライバ     |

| 1 4 0 A ~ 1 4 0 C   | 補正制御回路      |

| 1 5 0               | システムコントローラ  |

| D C A、 D C B        | 画素駆動回路      |

| O E L               | 有機EL素子      |

| S W A、 S W B、 S W C | スイッチ回路部     |

| A D C               | A / D コンバータ |

| B M                 | 記憶部         |

| A D M               | 加算器         |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 D

G 09 G 3/20 6 4 1 P

G 09 G 3/20 6 4 2 A

G 09 G 3/20 6 7 0 J

H 05 B 33/14 A

(56)参考文献 国際公開第98/040871(WO, A1)

特開平10-254410(JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30

G09G 3/20

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示驱动装置和显示装置及其驱动控制方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP4158570B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2008-10-01 |

| 申请号            | JP2003082368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2003-03-25 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 白寄友之<br>服部励治                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 白寄 友之<br>服部 励治                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.611.H G09G3/20.623.R G09G3/20.624.B G09G3/20.641.D G09G3/20.641.P G09G3/20.642.A G09G3/20.670.J H05B33/14.A G09G3/20.642.P G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/EE59 3K107/HH02 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD29 5C080/EE29 5C080/FF01 5C080/FF11 5C080/GG09 5C080/GG12 5C080/JJ02 5C080/JJ04 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB46 5C380/AC04 5C380/BA10 5C380/BA11 5C380/BA28 5C380/BA36 5C380/BB04 5C380/BD04 5C380/CA04 5C380/CA05 5C380/CA08 5C380/CA09 5C380/CA12 5C380/CA17 5C380/CA22 5C380/CA26 5C380/CA33 5C380/CB01 5C380/CB14 5C380/CB29 5C380/CB33 5C380/CC02 5C380/CC09 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC62 5C380/CC72 5C380/CD012 5C380/CE05 5C380/CE17 5C380/CE19 5C380/CF01 5C380/CF07 5C380/CF09 5C380/CF18 5C380/CF22 5C380/CF48 5C380/CF49 5C380/DA02 5C380/DA06 5C380/DA32 5C380/DA33 5C380/DA39 5C380/FA03 5C380/FA21 5C380/FA28 |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | <a href="#">JP2004287345A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

#### 摘要(译)

要解决的问题：通过抑制由于外部环境和长期变化引起的显示像素的发光特性的散射，提供具有与显示数据对应的适当亮度等级的发光操作的发光驱动装置，并提供能够出色地显示图像信息的显示装置及其驱动控制方法。

**SOLUTION：**显示装置具有显示面板110A，其中配备有有机EL元件OEL的多个显示像素以矩阵形式排列；栅极驱动器120，其将逐行扫描信号Vsel施加到扫描线SL；数据驱动器130，将对应于显示数据的灰度信号电压Vdata提供给数据线DL；校正控制电路140A，测量各个显示像素的有机EL元件OEL的发光特性，以校正显示数据；系统控制器150输出用于控制栅极驱动器120和数据驱动器130的操作的各种控制信号，以及校正控制电路140A。