(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4007336号

(P4007336)

(45) 発行日 平成19年11月14日(2007.11.14)

(24) 登録日 平成19年9月7日(2007.9.7)

(51) Int.CI.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b>  | <b>K</b>    |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>624B</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>642P</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>670J</b> |

|             |              |                  | <b>H05B</b> | <b>33/14</b> | <b>A</b>    |

請求項の数 12 (全 19 頁)

(21) 出願番号

特願2004-116778 (P2004-116778)

(22) 出願日

平成16年4月12日 (2004.4.12)

(65) 公開番号

特開2005-300897 (P2005-300897A)

(43) 公開日

平成17年10月27日 (2005.10.27)

審査請求日

平成17年2月1日 (2005.2.1)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 野澤 俊之

長野県諏訪市大和3丁目3番5号セイコーエプソン株式会社内

審査官 樋口 信宏

最終頁に続く

(54) 【発明の名称】画素回路の駆動方法、画素回路、電気光学装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

画素回路において、

所定の経路を介して供給された駆動電流に応じて発光する発光素子と、

前記発光素子より放出された光を受光し、当該受光した光に応じた光電流を出力する光電変換素子と、

前記光電変換素子より出力された前記光電流の積分値を電荷として蓄積する第1のキャパシタと、

前記第1のキャパシタに蓄積された電荷に応じて設定される第1の電圧が、データ線を介して供給されたデータに応じて設定される第2の電圧に達したタイミングで、出力電圧のレベルを切り替えるコンパレータと、

前記コンパレータからの出力電圧に応じて導通制御され、前記第1の電圧が前記第2の電圧に達していない場合には、前記発光素子を発光させるとともに、前記第1の電圧が前記第2の電圧に達した場合には、前記発光素子の発光を停止させる第1のスイッチング素子と

を有することを特徴とする画素回路。

## 【請求項 2】

前記第1のスイッチング素子は、前記発光素子に駆動電流を供給する経路中に設けられており、前記第1の電圧が前記第2の電圧に達していない場合には、前記駆動電流の経路を形成するとともに、前記第1の電圧が前記第2の電圧に達した場合には、前記駆動電流

の経路を遮断することを特徴とする請求項 1 に記載された画素回路。

【請求項 3】

前記データ線を介して供給されたデータを保持する第 2 のキャパシタと、

前記第 2 のキャパシタに自己のゲートが接続されており、前記第 2 のキャパシタに保持されているデータに応じて、前記駆動電流を生成する駆動トランジスタとをさらに有することを特徴とする請求項 1 に記載された画素回路。

【請求項 4】

前記第 1 のスイッチング素子は、前記第 2 のキャパシタと並列に設けられており、前記第 1 の電圧が前記第 2 の電圧に達していない場合には、前記第 2 のキャパシタの一対の電極を電気的に分離するとともに、前記第 1 の電圧が前記第 2 の電圧に達した場合には、前記第 2 のキャパシタの一対の電極を電気的に接続することを特徴とする請求項 3 に記載された画素回路。10

【請求項 5】

前記光電変換素子および前記第 1 のキャパシタが共通接続されたノードと、所定のリセット電圧が供給される電圧端子との間に設けられ、前記リセット電圧によって、前記第 1 のキャパシタに蓄積された電荷をリセットする第 2 のスイッチング素子をさらに有することを特徴とする請求項 1 から 4 のいずれかに記載された画素回路。

【請求項 6】

前記光電変換素子および前記第 1 のキャパシタが共通接続されたノードと、前記コンパレータの入力ノードとの間に設けられたソースフォロワ回路をさらに有することを特徴とする請求項 1 から 4 のいずれかに記載された画素回路。20

【請求項 7】

電気光学装置において、

複数の走査線と、

複数のデータ線と、

前記複数の走査線と、前記複数のデータ線との交差に対応して設けられた複数の画素回路と、

前記複数の走査線を順次選択する走査線駆動回路と、

前記走査線駆動回路と協働して、前記複数のデータ線にデータ電圧を出力するデータ線駆動回路とを有し、30

前記画素回路は、請求項 1 から 6 のいずれかに記載された画素回路であることを特徴とする電気光学装置。

【請求項 8】

請求項 7 に記載された電気光学装置を実装したことを特徴とする電子機器。

【請求項 9】

画素回路の駆動方法において、

所定の経路を介して駆動電流を発光素子に供給することにより、前記発光素子を発光させる第 1 のステップと、

前記発光素子より放出された光を受光し、当該受光した光に応じた光電流を光電変換素子より出力する第 2 のステップと、40

前記光電変換素子より出力された前記光電流の積分値を電荷として第 1 のキャパシタに蓄積する第 3 のステップと、

前記第 1 のキャパシタに蓄積された電荷に応じて設定される第 1 の電圧が、データ線を介して供給されたデータに応じて設定される第 2 の電圧に達したタイミングで、コンパレータからの出力電圧のレベルを切り替える第 4 のステップと、

前記コンパレータからの出力電圧に応じて第 1 のスイッチング素子を導通制御し、前記第 1 の電圧が前記第 2 の電圧に達していない場合には、前記発光素子を発光させるとともに、前記第 1 の電圧が前記第 2 の電圧に達した場合には、前記発光素子の発光を停止させる第 5 のステップと

を有することを特徴とする画素回路の駆動方法。50

**【請求項 10】**

前記第1のスイッチング素子は、前記発光素子に駆動電流を供給する経路中に設けられており、

前記第5のステップは、

前記第1の電圧が前記第2の電圧に達していない場合には、前記第1のスイッチング素子をオンさせて、駆動電流の経路を形成するステップと、

前記第1の電圧が前記第2の電圧に達した場合には、前記第1のスイッチング素子をオフさせて、前記駆動電流の経路を遮断するステップとを含むことを特徴とする請求項9に記載された画素回路の駆動方法。

**【請求項 11】**

10

前記第1のステップは、

前記データ線を介して供給されたデータを第2のキャパシタに書き込むステップと、

前記第2のキャパシタに保持されているデータに応じて、駆動電流を変調するステップと、

前記変調された駆動電流を所定の経路を介して前記発光素子に供給することにより、前記発光素子を発光させるステップとを含むことを特徴とする請求項9に記載された画素回路の駆動方法。

**【請求項 12】**

前記第1のスイッチング素子は、前記第2のキャパシタと並列に設けられており、

前記第5のステップは、

20

前記第1の電圧が前記第2の電圧に達していない場合には、前記第1のスイッチング素子をオフさせて、前記第2のキャパシタの一対の電極を電気的に分離するステップと、

前記第1の電圧が前記第2の電圧に達した場合には、前記第1のスイッチング素子をオンさせて、前記第2のキャパシタの一対の電極を電気的に接続するステップとを含むことを特徴とする請求項11に記載された画素回路の駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画素回路の駆動方法、画素回路、電気光学装置および電子機器に係り、特に、光電変換素子を内蔵した光フィードバック型の画素回路に関する。

30

**【背景技術】****【0002】**

近年、有機EL( Electronic Luminescence )素子を用いたフラットパネルディスプレイ(FPD)が注目されている。有機EL素子は、自己を流れる駆動電流によって駆動する電流駆動型素子の一つであり、その電流レベルに応じた輝度で自ら発光する。有機ELディスプレイでは、有機EL素子の特性(特に、電流-輝度特性)のばらつきが表示の均一性に悪影響を及ぼす。また、有機EL素子は、液晶等の他材料を用いた素子と比較して、経時劣化の度合いが大きいことが知られている。そのため、有機ELディスプレイでは、表示していた画像に対応して、個体間の劣化度合いが異なってしまい、画面の焼き付きなどが生じ易い。

40

**【0003】**

このような問題を解決すべく、特許文献1には、光電変換素子を内蔵した光フィードバック型の画素回路が開示されている。この画素回路は、発光素子に駆動電流を供給する駆動トランジスタと、この駆動トランジスタにゲート電圧を印加するキャパシタと、このキャパシタに並列接続され、発光素子から放出された光を受光する光電変換素子とを有する。光電変換素子は、受光した光の強度に応じた光電流を発生する。キャパシタにデータとして保持されている蓄積電荷は、光電流に応じて放電される。発光効率の高い高輝度の発光素子については、光電流が大きくなるので、発光が比較的急速に減衰していく。これに対して、発光効率の低い低輝度の発光素子については、光電流が小さくなるので、発光が比較的緩慢に減衰していく。その結果、発光素子の特性が個体間でばらついていても、

50

フレーム全体における輝度の積分値がほぼ同一になるので、発光素子の特性ばらつきが補償される。

【特許文献 1】特表 2003 - 509728 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来技術では、表示の均一性を有効に確保することが困難である。なぜなら、駆動トランジスタの特性ばらつきの影響を受け易いからである。駆動トランジスタの閾値電圧  $V_{th}$  には、個体間のばらつきが存在する。そのため、同一階調であっても、駆動トランジスタ毎にオフするタイミングが異なり、発光素子の発光が停止するタイミングも異なってしまう。その結果、同一階調でも輝度のばらつきが生じて、表示の均一性が低下する。このような均一性の低下は、特に低階調領域において顕著になる。低階調領域では、受光素子の S/N がリーク等の影響で低下するので、フィードバックによる制御性が悪化してしまうからである。従来技術では、キャパシタの放電に伴い、発光素子の輝度が経時的に減少していくので、必然的に受光素子の S/N が悪い領域を使わなければならない。

【0005】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、光電変換素子を内蔵した光フィードバック型の画素回路において、発光素子の特性ばらつきや経時劣化等に依存することなく、表示の均一性を有効に確保することである。

【課題を解決するための手段】

【0006】

かかる課題を解決するために、第 1 の発明は、所定の経路を介して供給された駆動電流に応じて発光する発光素子と、発光素子より放出された光を受光し、受光した光に応じた光電流を出力する光電変換素子と、光電変換素子より出力された光電流の積分値を電荷として蓄積する第 1 のキャパシタと、第 1 のキャパシタに蓄積された電荷に応じて設定される第 1 の電圧が、データ線を介して供給されたデータに応じて設定される第 2 の電圧に達したタイミングで、出力電圧のレベルを切り替えるコンパレータと、コンパレータからの出力電圧に応じて導通制御され、第 1 の電圧が第 2 の電圧に達していない場合には、発光素子を発光させるとともに、第 1 の電圧が第 2 の電圧に達した場合には、発光素子の発光を停止させる第 1 のスイッチング素子とを有する画素回路を提供する。

【0007】

第 1 の発明において、第 1 のスイッチング素子は、発光素子に駆動電流を供給する経路中に設けられており、第 1 の電圧が第 2 の電圧に達していない場合には、駆動電流の経路を形成するとともに、第 1 の電圧が第 2 の電圧に達した場合には、駆動電流の経路を遮断することが好ましい。

【0008】

第 1 の発明において、データ線を介して供給されたデータを保持する第 2 のキャパシタと、第 2 のキャパシタに自己のゲートが接続されており、第 2 のキャパシタに保持されているデータに応じて、駆動電流を生成する駆動トランジスタとをさらに設けてよい。この場合、第 1 のスイッチング素子は、第 2 のキャパシタと並列に設けられており、第 1 の電圧が第 2 の電圧に達していない場合には、第 2 のキャパシタの一対の電極を電気的に分離するとともに、第 1 の電圧が第 2 の電圧に達した場合には、第 2 のキャパシタの一対の電極を電気的に接続することが好ましい。

【0009】

第 1 の発明において、光電変換素子および第 1 のキャパシタが共通接続されたノードと、所定のリセット電圧が供給される電圧端子との間に設けられ、リセット電圧によって、第 1 のキャパシタに蓄積された電荷をリセットする第 2 のスイッチング素子をさらに設けてよい。

【0010】

10

20

30

40

50

第1の発明において、光電変換素子および第1のキャパシタが共通接続されたノードと、コンパレータの入力ノードとの間に設けられたソースフォロワ回路をさらに設けてよい。

#### 【0011】

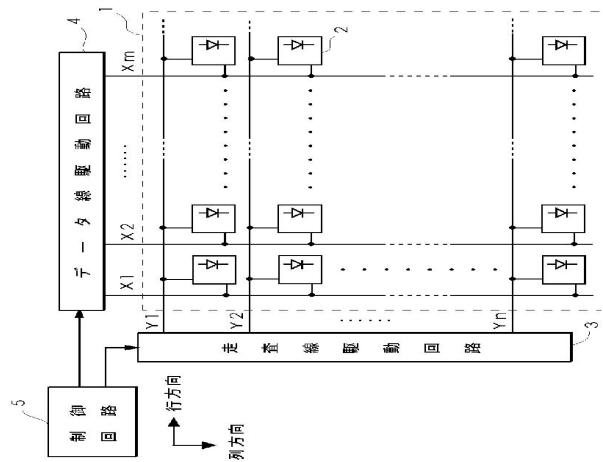

第2の発明は、複数の走査線と、複数のデータ線と、複数の走査線および複数のデータ線の交差に対応して設けられた複数の画素回路と、複数の走査線を順次選択する走査線駆動回路と、走査線駆動回路と協働して、複数のデータ線にデータ電圧を出力するデータ線駆動回路とを有する電気光学装置を提供する。ここで、画素回路は、上述した第1の発明にかかる画素回路である。

#### 【0012】

第3の発明は、上述した第2の発明にかかる電気光学装置を実装した電子機器を提供する。

#### 【0013】

第4の発明は、所定の経路を介して駆動電流を発光素子に供給することにより、発光素子を発光させる第1のステップと、発光素子より放出された光を受光し、受光した光に応じた光電流を光電変換素子より出力する第2のステップと、光電変換素子より出力された光電流の積分値を電荷として第1のキャパシタに蓄積する第3のステップと、第1のキャパシタに蓄積された電荷に応じて設定される第1の電圧が、データ線を介して供給されたデータに応じて設定される第2の電圧に達したタイミングで、コンパレータからの出力電圧のレベルを切り替える第4のステップと、コンパレータからの出力電圧に応じて第1のスイッチング素子を導通制御し、第1の電圧が第2の電圧に達していない場合には、発光素子を発光させるとともに、第1の電圧が第2の電圧に達した場合には、発光素子の発光を停止させる第5のステップとを有する画素回路の駆動方法を提供する。

#### 【0014】

第4の発明において、第1のスイッチング素子は、発光素子に駆動電流を供給する経路中に設けられていることが好ましい。この場合、第5のステップは、第1の電圧が第2の電圧に達していない場合には、第1のスイッチング素子をオンさせて、駆動電流の経路を形成するステップと、第1の電圧が第2の電圧に達した場合には、第1のスイッチング素子をオフさせて、駆動電流の経路を遮断するステップとを含むことが望ましい。

#### 【0015】

第4の発明において、第1のステップは、データ線を介して供給されたデータを第2のキャパシタに書き込むステップと、第2のキャパシタに保持されているデータに応じて、駆動電流を変調するステップと、記変調された駆動電流を所定の経路を介して発光素子に供給することにより、発光素子を発光させるステップとを含むことが好ましい。

#### 【発明の効果】

#### 【0016】

本発明では、光電変換素子より出力された光電流の積分値を第1のキャパシタの電荷として蓄積し、この電荷に応じて設定される第1の電圧が第2の電圧に達したタイミングで、発光素子の発光を停止させる。これにより、発光素子から放出される光の総量をプログラムできるので、発光素子の特性ばらつきや経時劣化等に依存することなく、表示の均一性を有效地に確保することができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

##### (第1の実施形態)

図1は、本実施形態にかかる電気光学装置のブロック構成図である。表示部1は、例えばTFT(Thin Film Transistor)によって発光素子を駆動するアクティブマトリクス型の表示パネルである。この表示部1には、mドット×nライン分の画素群がマトリクス状(二次元平面的)に並んでいる。表示部1には、それぞれが水平方向に延在している走査線群Y1~Ynと、それぞれが垂直方向に延在しているデータ線群X1~Xmとが設けられており、これらの交差に対応して画素2(画素回路)が配置されている。なお、後述する各

10

20

30

40

50

画素回路との関係で、同図に示した1本の走査線Yが複数の走査線のセットを示すことがある。

#### 【0018】

制御回路5は、図示しない上位装置からの外部信号をベースに各種の内部信号を生成し、これらに基づいて、走査線駆動回路3とデータ線駆動回路4とを同期制御する。この同期制御の下、これらの駆動回路3, 4は互いに協働して、表示部1の表示制御を行う。走査線駆動回路3は、シフトレジスタ、出力回路等を主体に構成されており、走査線Y<sub>1</sub>~Y<sub>n</sub>に走査信号を出力する。走査信号は、高電位レベル（以下「Hレベル」という）または低電位レベル（以下「Lレベル」という）の2値的な信号レベルをとり、データの書き込み対象となる画素行に対応する走査線YはHレベル、これ以外の走査線YはLレベルにそれぞれ設定される。10 走査線駆動回路3は、1画像の表示期間に相当する1フレーム（1F）毎に、所定の選択順序で（一般的には最上から最下に向かって）、それぞれの走査線Yを順番に選択する線順次走査を行う。一方、データ線駆動回路4は、シフトレジスタ、ラインラッチ回路、出力回路等を主体に構成されている。データ線駆動回路4は、1本の走査線Yを選択する期間に相当する1水平走査期間（1H）において、今回データを書き込む画素行に対するデータ電圧V<sub>data</sub>の一斉出力と、次の1Hで書き込みを行う画素行に関するデータの点順次的なラッチとを同時に行う。ある1Hにおいて、データ線Xの本数に相当するm個のデータが順次ラッチされる。そして、次に1Hにおいて、ラッチされたm個のデータは、電圧D A Cにおいてデータ電圧V<sub>data</sub>に変換された上で、対応するデータ線X<sub>1</sub>~X<sub>m</sub>に一斉に出力される。20

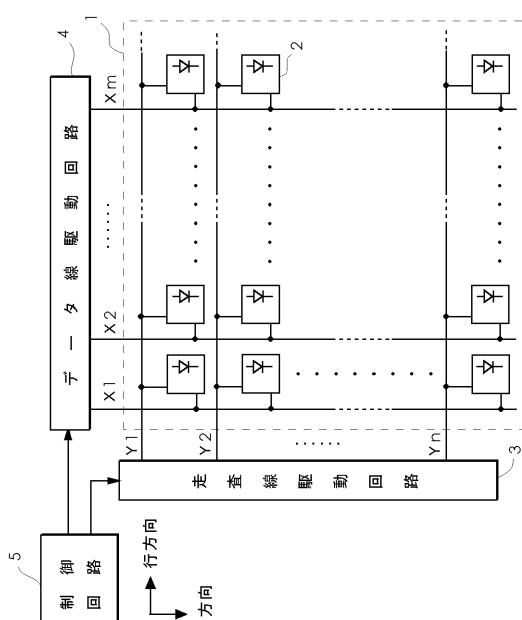

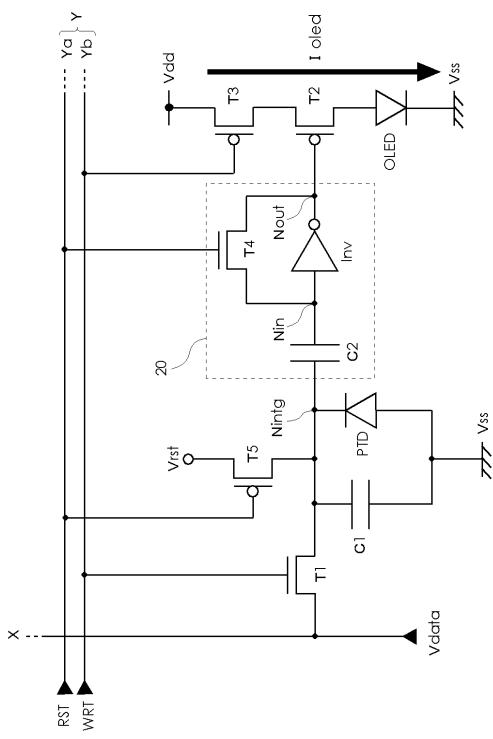

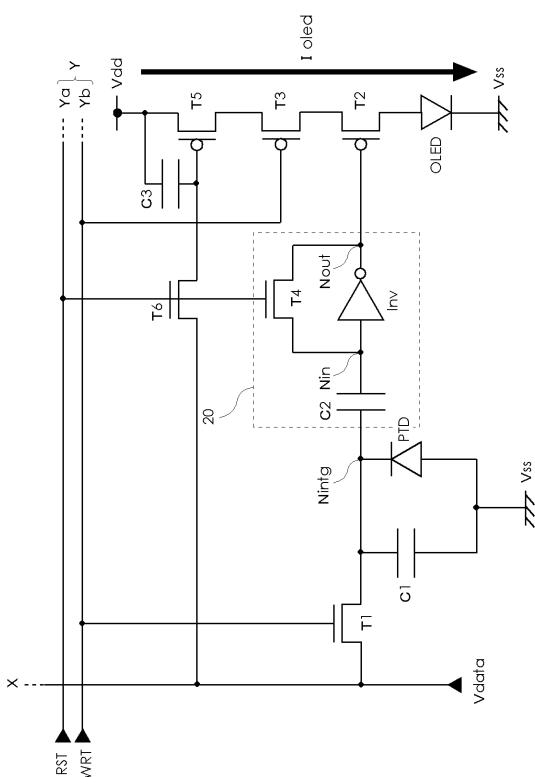

#### 【0019】

図2は、本実施形態にかかる光フィードバック型の画素回路図である。図1に示した1本の走査線Yは、図示した2本の走査線Y<sub>a</sub>, Y<sub>b</sub>のセットに相当する。この画素回路は、発光素子である有機EL素子OLEDと、5個のトランジスタT<sub>1</sub>~T<sub>5</sub>と、2個のキャパシタC<sub>1</sub>, C<sub>2</sub>と、インバータINVと、光電変換素子PTDとで構成されている。ダイオードとして表記された有機EL素子OLEDは、自己を流れる電流に応じて輝度が設定される典型的な電流駆動型の発光素子である。また、本実施形態では、光電変換素子PTDとして、入射光強度に比例した光電流を出力するフォトダイオードを用いている。フォトダイオードの構成としては、PN、PIN、ショットキー、有機フォトダイオード（有機EL素子でも可）、TFTを用いたフォトダイオード、アモルファスシリコン、ポリシリコン等のバリエーションが考えられる。また、同図の構成例では、トランジスタT<sub>2</sub>, T<sub>3</sub>をpチャネル型とし、その他をnチャネル型としているが、これは一例に過ぎず、別の組み合わせでチャネル型を設定してもよい。なお、本明細書では、ソース、ドレインおよびゲートを備える三端子型素子であるトランジスタに関して、ソースまたはドレインの一方を「一方の端子」と呼び、他方を「他方の端子」と呼ぶ。30

#### 【0020】

スイッチング素子であるトランジスタT<sub>1</sub>のゲートは、一方の走査信号であるライト信号W R Tが供給される第2の走査線Y<sub>b</sub>に接続されている。このトランジスタT<sub>1</sub>の一方の端子は、データ電圧V<sub>data</sub>（および後述するリセット電圧V<sub>rst</sub>）が供給されるデータ線Xに接続されており、その他方の端子は、積分ノードN<sub>intg</sub>に接続されている。この積分ノードN<sub>intg</sub>には、キャパシタC<sub>1</sub>の一方の電極と、フォトダイオードPTDのカソード（陰極）とが共通接続されているとともに、コンパレータ20の一部を構成するキャパシタC<sub>2</sub>の一方の電極も接続されている。キャパシタC<sub>1</sub>の他方の電極は、このキャパシタC<sub>1</sub>に並列接続されたフォトダイオードPTDのアノード（陽極）と共に、電源電圧V<sub>dd</sub>よりも低い基準電圧V<sub>ss</sub>が常時供給されるV<sub>ss</sub>端子に接続されている。40

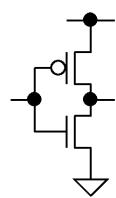

#### 【0021】

本実施形態では、コンパレータ20として、キャパシタC<sub>2</sub>、インバータINVおよびトランジスタT<sub>4</sub>で構成されたチョッパ型コンパレータを用いている。インバータINVの入力ノードN<sub>in</sub>は、キャパシタC<sub>2</sub>の他方の電極と、スイッチング素子であるトランジスタT<sub>4</sub>の一方の端子に共通接続されている。トランジスタT<sub>4</sub>のゲートは、他方の走査信号である50

リセット信号 R S T が供給される第 1 の走査線 Y a に接続され、その他方の端子は、インバータ INV の出力ノード N out に接続されている。トランジスタ T 4 は、リセット信号 R S T による導通制御によって、インバータの入力ノード N in とその出力ノード N out とを短絡（ショート）する。なお、インバータ INV は、p チャネル型のトランジスタと n チャネル型のトランジスタとを組み合わせた CMOS 構成、能動負荷のついた nMOS 構成、あるいは、抵抗付の MOS 構成のいずれであってもよい。図 1-2 に CMOS 構成のインバータの回路図を示す。

#### 【0022】

インバータ INV の出力ノード N out は、スイッチング素子であるトランジスタ T 2 のゲートに接続されている。このトランジスタ T 2 の一方の端子は、有機 EL 素子 OLED のアノードに接続されている。この有機 EL 素子 OLED のカソードは、V ss 端子に接続されている。また、トランジスタ T 2 の他方の端子は、トランジスタ T 3 の一方の端子に接続されている。このトランジスタ T 3 の他方の端子は、電源電圧 V dd が常時供給される V dd 端子に接続されているとともに、そのゲートは、第 2 の走査線 Y b に接続されている。

#### 【0023】

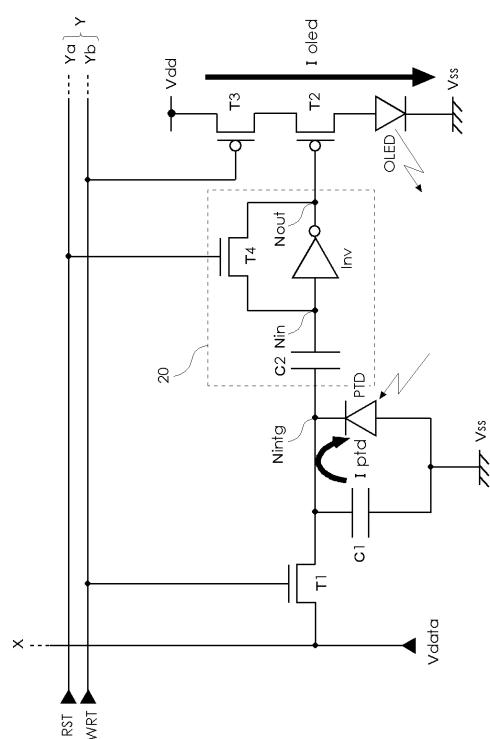

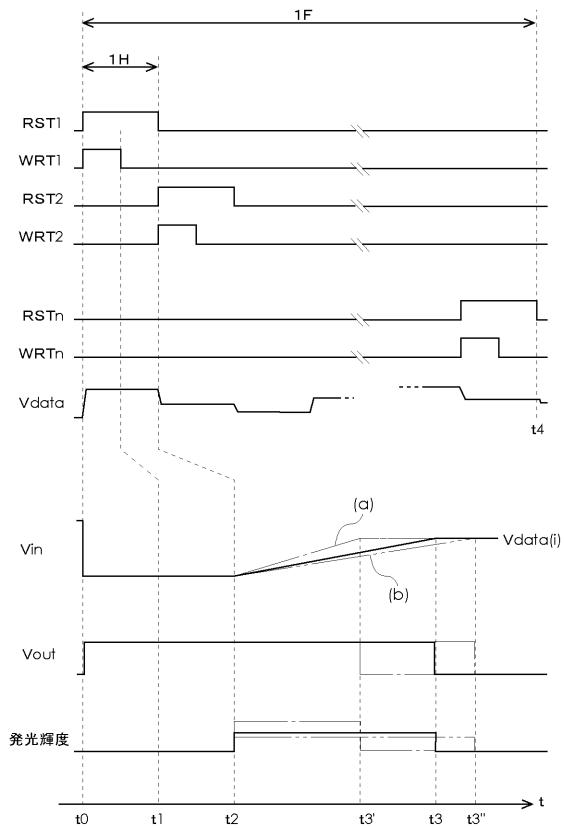

図 3 は、図 2 に示した画素回路の動作タイミングチャートである。上述した 1F に相当する期間 t 0 ~ t 4 における一連の動作プロセスは、期間 t 0 ~ t 1 のデータ書き込みプロセスと、期間 t 1 ~ t 2 のリセットプロセスと、期間 t 2 ~ t 4 の駆動プロセスとに大別される。

#### 【0024】

まず、画素回路の動作プロセスの説明に先立ち、表示部 1 の全体的な表示プロセスについて概略的に説明する。走査線駆動回路 3 は、まず最初の 1H に相当する期間 t 0 ~ t 2 で、走査線群 Y 1 ~ Y n のうち、最上の画素行に対応する走査線 Y 1 (= Y a, Y b) を選択する。これにより、この走査線 Y 1 に関して、一方の走査信号であるライト信号 W R T 1 は、1H 全体（すなわち期間 t 0 ~ t 2）に亘って H レベルに設定される。これに対して、他方の走査信号であるリセット信号 R S T 1 は、1H 前半のデータ書き込み期間 t 0 ~ t 1 において H レベルに設定され、その後半のリセット期間 t 1 ~ t 2 において L レベルに設定される。データ線駆動回路 4 は、走査線駆動回路 3 による走査線 Y 1 の選択と同期して、最上の画素行に関する m 個のデータ電圧 V data(i) (i = 1) をデータ線 X 1 ~ X m に一斉に出力する。ただし、データ電圧 V data(i) は、データ書き込み期間 t 0 ~ t 1 においてのみ出力され、後半のリセット期間 t 1 ~ t 2 では所定のリセット電圧 V rst が出力される。画素 2 の表示階調は、リセット電圧 V rst とデータ電圧 V data(i) との間の電位差 | V rst - V data(i) | によって一義的に特定され、この電位差が大きくなるほど輝度が高くなる。

#### 【0025】

次の 1H において、走査線駆動回路 3 は、2 番目の走査線 Y 2 を選択する。これにより、この走査線 Y 2 に関して、ライト信号 W R T 2 は、1H 全体において H レベルに設定され、リセット信号 R S T 2 は、1H 前半のみにおいて H レベルに設定される。データ線駆動回路 4 は、走査線 Y 2 の選択と同期して、2 番目の画素行に関する m 個のデータ電圧 V data(i) (i = 2) をデータ線 X 1 ~ X m に一斉に出力する。以下、最下の走査線 Y n に至るまで、走査線 Y 3, Y 4, ..., Y n が 1H 毎に順番に選択され、これに対応した画素行に関するデータ電圧 V data(i) (i = 3, 4, ..., n) が繰り返し出力される。

#### 【0026】

つぎに、画素回路の動作プロセスについて、走査信号 R S T 1, W R T 1 によって選択される画素回路を例に説明する。まず、データ書き込み期間 t 0 ~ t 1 では、キャパシタ C 2 に対するデータの書き込みと、コンパレータ 20 のリセットとが行われる。具体的には、リセット信号 R S T 1 が H レベルになって、コンパレータ 20 内のトランジスタ T 4 がオンする。これにより、インバータ INV の入出力ノード N in, N out が短絡して、その入出力電圧 V in, V out が共にインバータ INV の反転閾値 V th (-1/2V dd) に設定される。また、ライト信号 W R T 1 が H レベルになって、トランジスタ T 1 がオンする。この期間 t 0 ~ t 1 においてデータ線 X に供給されたデータ電圧 V data(i) は、オンしたトランジスタ T 1 を介して、キャパシタ C 1, C 2 が接続された積分ノード N intg に供給される。これにより、キャパ

10

20

30

40

50

シタ C1には、積分ノード Nintg ( $V_{intg} = V_{data(i)}$ ) と  $V_{ss}$  端子との間の電位差  $|V_{data(i)} - V_{ss}|$  に相当する電荷が蓄積される。ただし、このキャパシタ C1の蓄積電荷は、次のリセットプロセスによってリセットされる。また、キャパシタ C2には、ノード NI ntg ( $V_{intg} = V_{data(i)}$ ) と入力ノード Nin ( $V_{in} = V_{th}$ ) との間の電位差  $|V_{th} - V_{da ta(i)}|$  に相当する電荷が蓄積される（データ書き込み）。

#### 【0027】

なお、データ書込期間  $t_0 \sim t_1$  および次のリセット期間  $t_1 \sim t_2$  では、ライト信号 WRT1 によって導通制御される p チャネル型のトランジスタ T3 がオフしている。したがって、これら一連の期間  $t_0 \sim t_2$  では、コンパレータ 20 からの出力電圧のレベルに関わりなく、駆動電流  $I_{oled}$  の経路が形成されないので、有機 EL 素子 OLED は発光しない。 10

#### 【0028】

続くりリセット期間  $t_1 \sim t_2$  では、リセット電圧  $V_{rst}$  によって、キャパシタ C1 に蓄積されている電荷がリセットされる。具体的には、リセット信号 RST1 が H レベルから L レベルになって、コンパレータ 20 内のトランジスタ T4 がオフする。これにより、短絡していた入出力ノード Nin, Nout が電気的に分離されて、それぞれがフローティング状態になる。また、この期間  $t_1 \sim t_2$  では、ライト信号 WRT1 が H レベルでトランジスタ T1 がオンしている状態において、データ線 X の電圧が、データ電圧  $V_{data(i)}$  からリセット電圧  $V_{rst}$  へと変化する。このリセット電圧  $V_{rst}$  は、表示すべき階調に依存しない一定の電圧である。これにより、積分ノード Nintg の電圧  $V_{intg}$ （以下、「積分電圧  $V_{intg}$ 」という）は、データ線 X の電圧変化に伴い、データ電圧  $V_{data(i)}$  からリセット電圧  $V_{rst}$  へと変化する。キャパシタ C1 には、積分ノード Nintg ( $V_{intg} = V_{rst}$ ) と  $V_{ss}$  端子との間の電位差  $|V_{rst} - V_{ss}|$  に相当する電荷が蓄積される。すなわち、キャパシタ C1 の蓄積電荷は、先のプロセスで設定された電位差  $|V_{data(i)} - V_{ss}|$  相当から、データ電圧  $V_{data(i)}$  に依存しない電位差  $|V_{rst} - V_{ss}|$  相当にリセットされる（リセット状態）。 20

#### 【0029】

また、インバータ INV の入力ノード Nin は、キャパシタ C2 を介して積分ノード Nintg と容量結合している。したがって、積分電圧  $V_{intg}$  が  $|V_{rst} - V_{data(i)}|$  変化すると、インバータ INV の入力電圧  $V_{in}$  も  $k |V_{rst} - V_{data(i)}|$  だけ変化して、 $V_{in} = V_{th} + k (V_{rst} - V_{data(i)})$  になる。キャパシタ C2 には、積分ノード Nintg ( $V_{intg} = V_{rst}$ ) と入力ノード Nin ( $V_{in} = V_{th} + k (V_{rst} - V_{data(i)})$ ) との間の電位差に相当する電荷が蓄積される。ここで、係数  $k$  は、キャパシタ C1, C2 の容量比によって一義的に特定される定数である。キャパシタ C2 の保持データは、キャパシタ C1 とは異なり、データ電圧  $V_{data(i)}$  に依存する（ $V_{th}, V_{rst}, k$  は定数）。 30

#### 【0030】

リセット期間  $t_1 \sim t_2$  では、インバータ INV の入力電圧  $V_{in}$  が反転閾値  $V_{th}$  を越えるので、その出力電圧  $V_{out}$  は L レベル（=  $V_{ss}$ ）になる。したがって、駆動電流  $I_{oled}$  の経路中に設けられたトランジスタ T2 がオンする。しかしながら、この期間  $t_1 \sim t_2$  では、トランジスタ T2 の上段に位置するトランジスタ T3 がオフのままである。したがって、駆動電流  $I_{oled}$  の経路が遮断され、有機 EL 素子 OLED は発光しない。 40

#### 【0031】

そして、駆動期間  $t_2 \sim t_4$  では、発光素子である有機 EL 素子 OLED の発光が許容される。この期間  $t_2 \sim t_4$  では、ライト信号 WRT1 が L レベルになって、トランジスタ T1 がオフするとともに、トランジスタ T3 がオンする。これにより、 $V_{dd}$  端子からトランジスタ T3, T2 および有機 EL 素子 OLED を経て  $V_{ss}$  端子に向かう経路で、駆動電流  $I_{oled}$  が流れれる。この駆動電流  $I_{oled}$  は、トランジスタ T3 のチャネル電流に相当し、その電流レベルは自己のゲート電圧、すなわち、ライト信号 WRT の L レベルに依存した一定値となる。これにより、有機 EL 素子 OLED は、タイミング  $t_2$  において、駆動電流  $I_{oled}$ （一定値）に応じた一定の輝度で発光し始める。 50

#### 【0032】

有機 EL 素子 OLED の発光は、有機 EL 素子 OLED から放出された光の時間的積分値（その

時間平均が人間によって知覚される輝度に相当する)が、ある設定値に達するタイミング  $t_3$  で終了する。すなわち、表示すべき階調の設定は、外乱要素を考慮しなければ一定輝度で発光する有機EL素子OLEDの発光時間を制御することによって行われる。タイミング  $t_2$  で有機EL素子OLEDが発光し始めると、同一の画素回路内のフォトダイオードPTDは、有機EL素子OLEDより放出された光を受光する。このフォトダイオードPTDは、受光した光を電流に変換し、光の強度に応じたレベルの光電流  $I_{ptd}$  を出力する。これにより、上述したリセット状態のキャパシタC1より、光電流  $I_{ptd}$  の積分値に相当する電荷がディスチャージ(放電)される。光電流  $I_{ptd}$  の積分値は、積分電圧  $V_{intg}$  の変化となって表れ、積分電圧  $V_{intg}$  が  $V_{rst}$  から  $V_{data(i)}$  に向かって経時的に変化していく。そして、この変化に伴い、積分ノード  $N_{intg}$  と容量結合した入力ノード  $N_{in}$  の入力電圧  $V_{in}$  も、 $V_{th} + k(V_{rst} - V_{data(i)})$  から  $V_{th}$  に向かって経時的に変化していく。積分電圧  $V_{intg}$  が  $V_{data(i)}$  に達するまで、換言すれば、入力電圧  $V_{in}$  が  $V_{th}$  に達するまでの期間  $t_2 \sim t_3$  では、インバータINVの出力電圧  $V_{out}$  がLレベルで、トランジスタT2がオンのままである。したがって、この期間  $t_2 \sim t_3$  では、駆動電流  $I_{oled}$  の経路が形成され続けるので、有機EL素子OLEDの発光が継続する。光電流  $I_{ptd}$  によるキャパシタC1のディスチャージが更に進み、入力電圧  $V_{in}$  が  $V_{th}$  に達するタイミング、すなわち、積分電圧  $V_{intg}$  が  $V_{data(i)}$  に達するタイミング  $t_3$  で、インバータINVの出力電圧  $V_{out}$  がLレベルからHレベルに切り替わる。これによって、トランジスタT2がオンからオフへと切り替わり、駆動電流  $I_{oled}$  の経路が遮断されて、有機EL素子OLEDの発光が停止する。

## 【0033】

低階調時には、データ電圧  $V_{data(i)}$  が低く設定される。この場合には、電位差  $|V_{rst} - V_{data(i)}|$  が小さくなり、光電流  $I_{ptd}$  の時間積分によって変化する入力電圧  $V_{in}$  が比較的早く  $V_{th}$  に達する。したがって、出力電圧  $V_{out}$  がLレベルからHレベルに切り替わるタイミングも短くなっている。有機EL素子OLEDが短い時間で発光する。これに対して、高階調時には、データ電圧  $V_{data(i)}$  が高く設定される。この場合には、電位差  $|V_{rst} - V_{data(i)}|$  が大きくなっている。入力電圧  $V_{in}$  が比較的遅く  $V_{th}$  に達する。したがって、出力電圧  $V_{out}$  がLレベルからHレベルに切り替わるタイミングも長くなっている。有機EL素子OLEDが長い時間で発光する。

## 【0034】

同一階調を表示する場合であっても、有機EL素子OLEDの特性や劣化の度合い等に起因して、個体間で発光輝度が違ってくる。本実施形態では、光フィードバックにて発光期間を調整することで、このような発光輝度の違いを吸収する。例えば、有機EL素子OLEDの劣化が進んでおらず発光輝度が高い場合には、フォトダイオードPTDによって出力される光電流  $I_{ptd}$  が大きくなる。この場合、図3の一点鎖線(a)で示すように、積分電圧  $V_{intg}$  の変化量が大きく、 $V_{intg} = V_{data(i)} (V_{in} = V_{th})$  に到達するタイミング  $t_{3'}$  がタイミング  $t_3$  よりも早くなるので、有機EL素子OLEDの発光時間が短くなる。これに対して、有機EL素子OLEDの劣化が進んで発光輝度が低い場合には、フォトダイオードPTDによって出力される光電流  $I_{ptd}$  が小さくなる。この場合、図3の二点鎖線(b)で示すように、積分電圧  $V_{intg}$  の変化量が小さく、 $V_{intg} = V_{data(i)} (V_{in} = V_{th})$  に到達するタイミング  $t_{3''}$  がタイミング  $t_3$  よりも遅くなるので、有機EL素子OLEDの発光時間が長くなる。発光輝度の時間積分は、有機EL素子OLEDの輝度(劣化状況)に関わりなく一定である。したがって、図3の実線で示したタイミング  $t_3$  で発光が停止するケース、同図の一点鎖線(a)で示したタイミング  $t_{3'}$  で発光が停止するケース、或いは、同図の二点鎖線(b)で示したタイミング  $t_{3''}$  で発光が停止するケースのいずれであっても、視覚的には同一階調として表示されることになる。なお、発光輝度の時間積分は、データ書き込期間  $t_0 \sim t_1$  で入力したデータ電圧  $V_{data(i)}$  に依存している。

## 【0035】

以上のように、本実施形態では、フォトダイオードPTDに並列接続されたキャパシタC1によって、フォトダイオードPTDから出力される光電流  $I_{ptd}$  を積分する。コンパレータ20は、この積分値が出現する積分電圧  $V_{intg}$  が、データ線Xを通じて設定されたデータ電

10

20

30

40

50

圧  $V_{data}(i)$  になったことを、  $V_{in} = V_{th}$  を以て検出し、 そのタイミング  $t_3$  で出力信号  $V_{out}$  のレベルを切り替える。トランジスタ  $T_2$  は、 コンパレータ  $20$  からの出力電圧  $V_{out}$  を受けて、 タイミング  $t_3$  で駆動電流  $I_{oled}$  の経路を遮断する。このような構成によれば、 従来技術と比較して、 表示の均一性を有効に確保することが可能になる。本実施形態では、 有機 EL 素子 OLED の特性や劣化度合い等が個体間でばらついても、 1 フレームにおける輝度の時間積分値（人によって知覚される階調）が等しくなる。したがって、 有機 EL 素子 OLED の特性ばらつき等が表示の均一性に与える悪影響を有効に低減できる。また、 本実施形態によれば、 有機 EL 素子 OLED の輝度の時間積分を書き込んだデータ値から直接制御できるため、 駆動トランジスタの特性ばらつきの影響を受け難くすることが可能になる。さらに、 本実施形態によれば、 フォトダイオード PTD を S / N の悪い領域で使用しなくて済むという利点がある。この点に関して、 従来技術では、 発光輝度を経時に減衰させており、 かつ、 低階調表示時には、 有機 EL 素子 OLED を低輝度で発光させている。そのため、 フォトダイオード PTD の受光量が不足し、 S / N の悪い領域を必然的に使わざるを得なかつた。これに対して、 本実施形態では、 表示すべき階調に関わりなく発光輝度は一定であり、 かつ、 低階調表示時であっても発光輝度を必ずしも低くする必要はない。そのため、 S / N の良い領域でフォトダイオード PTD を使用した、 光フィードバック型の画素回路が実現可能になる。

## 【 0036 】

なお、 データ書込期間  $t_0 \sim t_1$  およびリセット期間  $t_1 \sim t_2$  が、 1 フレーム（ 1 F ）に対して充分短く、 これらの期間に有機 EL 素子 OLED が発光しても表示に差し支えなければ、 トランジスタ  $T_3$  を省いてもよい。

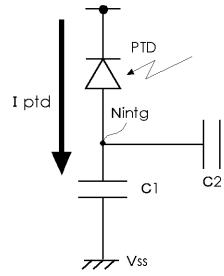

## 【 0037 】

また、 本実施形態では、 フォトダイオード PTD をキャパシタ  $C_1$  に並列接続し、 キャパシタ  $C_1$  を最初に高い電圧（絶対値）にリセットした後に、 フォトダイオード PTD の光電流  $I_{ptd}$  でディスチャージする例について説明した。しかしながら、 本発明は、 これに限定されるものではなく、 図 4 に示すように、 フォトダイオード PTD をキャパシタ  $C_1$  に直列接続してもよい。この場合、 キャパシタ  $C_1$  を最初に低い電圧（絶対値）にリセットした後に、 光電流  $I_{ptd}$  でチャージ（充電）する。なお、 以上の点については、 本明細書で列挙している各実施形態においても同様に適用することが可能である。

## 【 0038 】

## （第 2 の実施形態）

図 5 は、 第 2 の実施形態にかかる光フィードバック型の画素回路図である。この画素回路の特徴は、 積分ノード  $N_{intg}$  と、 リセット電圧  $V_{rst}$  が常時供給されるリセット端子  $V_{rst}$  との間に、 リセット信号  $RST$  によって導通制御される p チャネル型のトランジスタ  $T_5$  を追加した点にある。なお、 それ以外の構成については、 図 2 のそれと同様であるので、 同一の符号を付してここでの説明を省略する。また、 この画素回路の動作については、 図 3 に示したタイミングチャートと基本的に同様である。

## 【 0039 】

データ書込期間  $t_0 \sim t_1$  では、 リセット信号  $RST$  が H レベルなので、 p チャネル型のトランジスタ  $T_5$  はオフしている。したがって、 第 1 の実施形態と同様のプロセスで、 データ書き込みと、 コンパレータ  $20$  のリセットとが行われる。続くりセット期間  $t_1 \sim t_2$  では、 リセット信号  $RST$  が H レベルから L レベルに立ち下がって、 トランジスタ  $T_5$  がオンする。この期間  $t_1 \sim t_2$  では、 トランジスタ  $T_1$  がオフし、 データ線  $X$  と積分ノード  $N_{intg}$  とが電気的に分離されている。これにより、 リセット端子  $V_{rst}$  からトランジスタ  $T_5$  を介して、 リセット電圧  $V_{rst}$  が積分ノード  $N_{intg}$  に供給される。その結果、 この積分ノード  $N_{intg}$  に接続されたキャパシタ  $C_1$  がリセット状態に設定される。

## 【 0040 】

本実施形態では、 キャパシタ  $C_1$  のリセット電圧  $V_{rst}$  をデータ線  $X$  とは別系統で供給している。これにより、 第 1 の実施形態と同様の効果を有するほか、 データ線駆動系の動作設計に関するフレキシビリティの向上を図ることができる。なお、 本実施形態にかかる特徴

10

20

30

40

50

点は、本明細書で列挙している各実施形態においても同様に適用することが可能である。

#### 【0041】

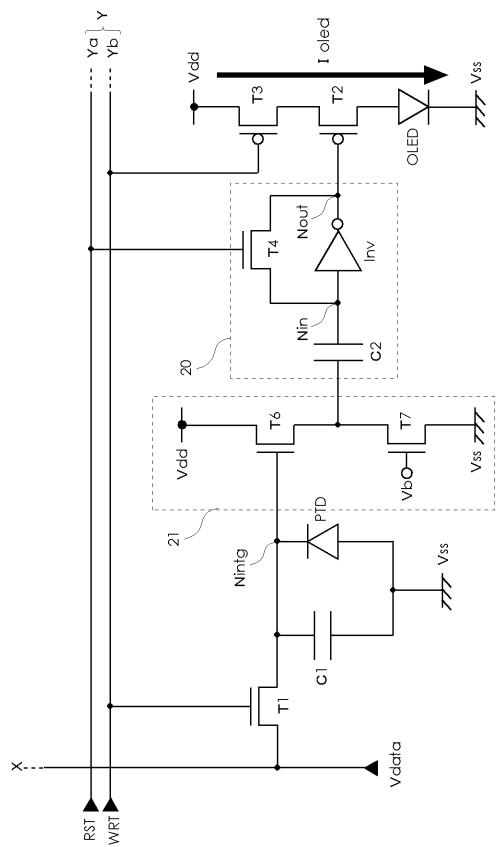

##### (第3の実施形態)

図6は、第3の実施形態にかかる光フィードバック型の画素回路図である。この画素回路の特徴は、図2の構成をベースとし、積分ノードNintgとコンパレータ20との間にソースフォロワ回路21を追加した点にある。このソースフォロワ回路21は、直列接続されたnチャネル型の2つのトランジスタT6, T7で構成されている。トランジスタT6のゲートは、積分ノードNintgに接続されており、その一方の端子は、Vdd端子に接続されている。また、トランジスタT6の他方の端子は、コンパレータ20の一部を構成するキャパシタC1の一方の電極と、トランジスタT7の一方の端子とに共通接続されている。このトランジスタT7のゲートには、所定のバイアス電圧Vbが印加されるとともに、その他方の端子は、Vss端子に接続されている。なお、それ以外の構成については、図2のそれと同様であるから、同一の符号を付してここでの説明を省略する。10

#### 【0042】

本実施形態によれば、第1の実施形態と同様の効果を有するほか、ソースフォロワ回路21を追加することで、画素回路の動作の安定性を向上させることができる。なお、本実施形態にかかる特徴点は、本明細書で列挙している各実施形態においても同様に適用することが可能である。

#### 【0043】

##### (第4の実施形態)

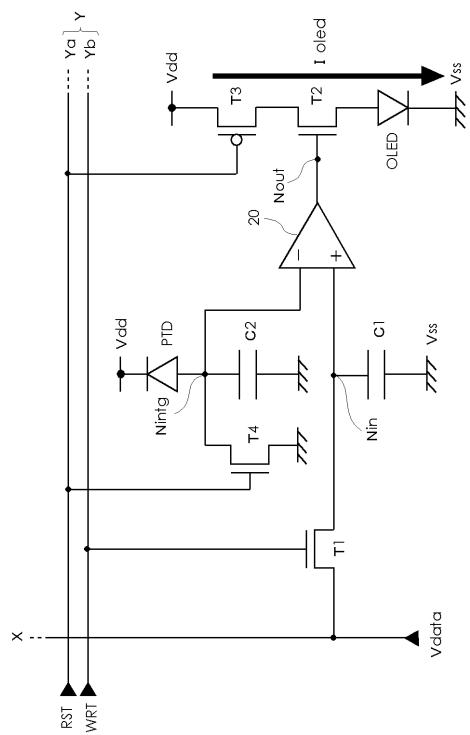

20

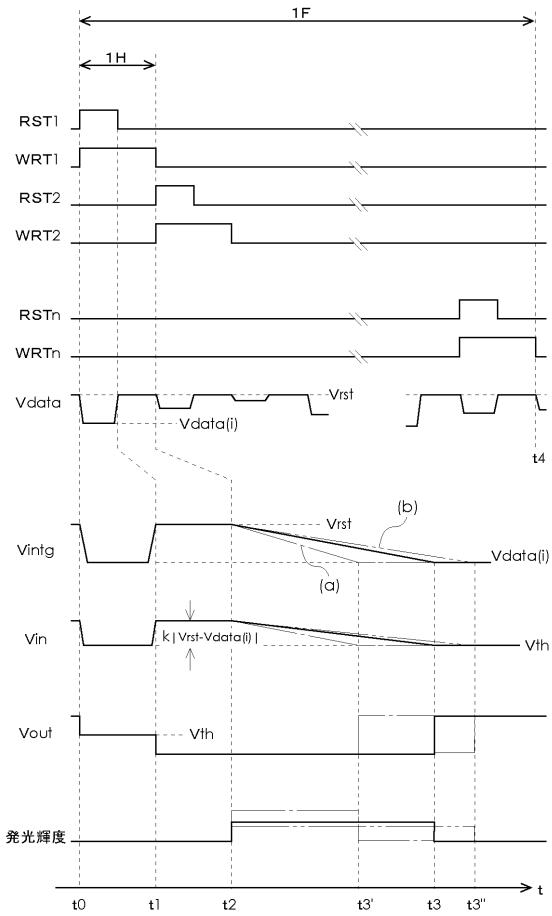

図7は、第4の実施形態にかかる光フィードバック型の画素回路図である。図1に示した1本の走査線Yは、図示した2本の走査線Ya, Ybのセットに相当する。この画素回路は、発光素子としての有機EL素子OLEDと、4個のトランジスタT1~T4と、2個のキャパシタC1, C2と、一般的なオペアンプで構成された2入力のコンパレータ20と、光電変換素子としてのフォトダイオードPTDとで構成されている。なお、同図の構成例では、トランジスタT3のみをpチャネル型とし、その他をnチャネル型としているが、これは一例に過ぎず、別の組み合わせでチャネル型を設定してもよい。

#### 【0044】

コンパレータ20の非反転入力端(+端子)は、入力ノードNinに接続されており、この入力ノードNinには、スイッチング素子であるトランジスタT1の一方の端子と、キャパシタC1の一方の電極とが共通接続されている。トランジスタT1のゲートは、ライト信号WRTが供給される第2の走査線Ybに接続されており、その一方の端子は、データ電圧Vdataが供給されるデータ線Xに接続されている。キャパシタC1の他方の電極は、Vss端子に接続されている。また、コンパレータ20の反転入力端(-端子)は、積分ノードNintgに接続されており、この積分ノードNintgには、キャパシタC2の一方の電極と、フォトダイオードPTDのアノードと、スイッチング素子であるトランジスタT4の一方の端子とが共通接続されている。フォトダイオードPTDのカソードはVdd端子に、キャパシタC2の他方の電極はVss端子にそれぞれ接続されている。トランジスタT4のゲートは、リセット信号RSTが供給される第1の走査線Yaに接続されており、その他方の端子は、Vss端子に接続されている。30

#### 【0045】

コンパレータ20の出力ノードNoutは、スイッチング素子であるトランジスタT2のゲートに接続されている。このトランジスタT2の一方の端子は、有機EL素子OLEDのアノードに接続されており、その他方の端子は、スイッチング素子であるトランジスタT3の一方の端子に接続されている。有機EL素子OLEDのカソードは、Vss端子に接続されている。また、トランジスタT3の他方の端子は、Vdd端子に接続されており、そのゲートは、第1の走査線Yaに接続されている。40

#### 【0046】

図8は、図7に示した画素回路の動作タイミングチャートである。1Fに相当する期間t0~t4は、ライト信号WRT1によって規定されるデータ書き込み期間t0~t1と、ライト

50

信号W R T 1およびリセット信号R S T 1によって規定されるリセット期間 $t_1 \sim t_2$ と、それに続く駆動期間 $t_2 \sim t_4$ とに大別される。

#### 【0047】

まず、データ書き込み期間 $t_0 \sim t_1$ では、キャパシタC1のデータ書き込みが行われる。具体的には、ライト信号W R T 1がHレベルになって、トランジスタT1がオンする。これにより、データ線Xに供給されたデータ電圧 $V_{data(i)}$ が入力ノードNinに供給され、キャパシタC1には、電位差 $|V_{data(i)} - V_{ss}|$ に相当する電荷が蓄積される(データ書き込み)。それとともに、リセット信号R S T 1がHレベルになって、トランジスタT4がオンする。これにより、キャパシタC1の一方の電極に接続された積分ノードNintgには、オンしたトランジスタT4を介して基準電圧 $V_{ss}$ が印加され、キャパシタC1の電位差が0にリセットされる。なお、データ書き込み期間 $t_0 \sim t_1$ および次のリセット期間 $t_1 \sim t_2$ では、リセット信号R S T 1によって導通制御されるpチャネル型のトランジスタT3がオフしている。したがって、これら一連の期間 $t_0 \sim t_2$ では、コンパレータ20からの出力電圧 $V_{out}$ に関わりなく、トランジスタT3によって駆動電流 $I_{oled}$ の経路が遮断されるので、有機EL素子OLEDは発光しない。10

#### 【0048】

続くりセット期間 $t_1 \sim t_2$ では、ライト信号W R T 1がHレベルからLレベルに立ち下がってトランジスタT1がオフする。トランジスタC1には、先に書き込まれたデータが保持される。一方、この期間 $t_1 \sim t_2$ では、リセット信号R S T 1がHレベルのままであるから、キャパシタC2のリセット状態が維持されるとともに、駆動電流 $I_{oled}$ の経路が遮断され続ける。20

#### 【0049】

そして、駆動期間 $t_2 \sim t_4$ では、リセット信号R S T 1がLレベルに立ち下がって、発光素子である有機EL素子OLEDの発光が許容される。具体的には、タイミング $t_2$ において、オフだったトランジスタT3がオンし、かつ、コンパレータ20からの出力電圧 $V_{out}$ がHレベルでトランジスタT2もオンしているので、一定の駆動電流 $I_{oled}$ が有機EL素子OLEDに供給される。これにより、有機EL素子OLEDは、駆動電流 $I_{oled}$ (一定値)に応じた一定輝度で発光し始める。

#### 【0050】

同一の画素回路内のフォトダイオードPTDは、有機EL素子OLEDより放出された光を受光するとともに、受光した光を電流に変換し、光の強度に応じたレベルの光電流 $I_{ptd}$ を出力する。これにより、上述したリセット状態のキャパシタC1に、光電流 $I_{ptd}$ の積分値に相当する電荷がチャージされていく。光電流 $I_{ptd}$ の積分値は、積分電圧 $V_{intg}$ の経時的な変化となって表れる。積分電圧 $V_{intg}$ が入力電圧 $V_{in}$ (=  $V_{data(i)}$ )に達するまでの期間 $t_2 \sim t_3$ においては、出力電圧 $V_{out}$ がHレベルで、トランジスタT2がオンのままである。したがって、この期間 $t_2 \sim t_3$ では、駆動電流 $I_{oled}$ の経路が形成され続けるので、有機EL素子OLEDの発光が継続する。光電流 $I_{ptd}$ によるチャージが更に進み、積分電圧 $V_{intg}$ が入力電圧 $V_{in}$ (=  $V_{data(i)}$ )に達すると、そのタイミング $t_3$ で、出力電圧 $V_{out}$ がHレベルからLレベルに立ち下がる。これによって、トランジスタT2がオンからオフへと切り替わり、駆動電流 $I_{oled}$ の経路が遮断されるので、有機EL素子OLEDの発光が停止する。3040

#### 【0051】

有機EL素子OLEDの劣化が進んでおらず発光輝度が高い場合には、フォトダイオードPTDによって出力される光電流 $I_{ptd}$ が大きくなる。この場合、図8の一点鎖線(a)で示すように、積分電圧 $V_{intg}$ の変化量が大きく、 $V_{intg} = V_{data(i)}$ に到達するタイミング $t_3'$ がタイミング $t_3$ よりも早くなるので、有機EL素子OLEDの発光時間が短くなる。これに対して、有機EL素子OLEDの劣化が進んで発光輝度が低い場合には、フォトダイオードPTDによって出力される光電流 $I_{ptd}$ が小さくなる。この場合、図8の二点鎖線(b)で示すように、積分電圧 $V_{intg}$ の変化量が小さく、 $V_{intg} = V_{data(i)}$ に到達するタイミング $t_3''$ がタイミング $t_3$ よりも遅くなるので、有機EL素子OLEDの発光時間が長くなる。50

**【0052】**

本実施形態によれば、第1の実施形態と同様の理由で、発光素子の特性ばらつきや経時劣化等に依存することなく、表示の均一性を有効に確保できる。

**【0053】****(第5の実施形態)**

図9は、第5の実施形態にかかる光フィードバック型の画素回路である。この画素回路の特徴は、図2に示した画素回路をベースに、電圧プログラム方式における一般的な駆動系を追加した点にある。この駆動系は、キャパシタC3と、駆動素子であるトランジスタT5と、スイッチング素子であるトランジスタT6とで構成されている。具体的には、トランジスタT5の一方の端子は、キャパシタC3の一方の電極と共にVdd端子に接続されており、その他の端子は、トランジスタT3の一方の端子に接続されている。このトランジスタT5のゲートは、キャパシタC3の他方の電極と、トランジスタT6の一方の端子とに共通接続されている。トランジスタT6の他方の端子は、データ線Xに接続されており、そのゲートは、トランジスタT4と同様に、リセット信号RSTが供給される第1の走査線Yaに接続されている。なお、それ以外の点については、図2の画素回路と同様であるから、同一の符号を付してここでの説明を省略する。また、この画素回路の動作は、図3に示したタイミングチャートと基本的に同様である。10

**【0054】**

キャパシタC3およびトランジスタT5は、駆動電流Ioledを変調する手段（発光輝度を変調する手段）として機能する。具体的には、リセット信号RST1がHレベルになるデータ書込期間t0～t1において、トランジスタT6がオンする。これにより、データ線Xを介して供給されたデータ電圧Vdata(i)がキャパシタC3に保持される。そして、ライト信号WRがLレベルになってトランジスタT3がオンする駆動期間t2～t4において、キャパシタC3にゲート接続されたトランジスタT5は、駆動電流Ioledを生成し、これを有機EL素子OLEDに供給する。駆動電流Ioledは、トランジスタT5のチャネル電流に相当し、その電流レベルは、自己のゲートに印加される電圧、換言すれば、このゲート電圧を発生するキャパシタC3の保持データに応じて設定される。20

**【0055】**

本実施形態によれば、第1の実施形態と同様の効果を有するほか、電圧プログラム方式における駆動系を追加することにより、第1の実施形態よりも優れた階調制御性を実現できる。第1の実施形態では、コンパレータ20の応答速度が遅い場合、低階調側の微細な制御が困難になる。なぜなら、低階調になるほど、発光期間が短くなっているパルス的な発光になるが、コンパレータ20の応答がこれに追いつかないからである。本実施形態では、発光輝度の時間積分による発光停止に、発光輝度自体の変調を組み合わせることで、コンパレータ20の応答遅れによる制約を解消し、特に、低階調側において優れた階調制御性を実現できる。30

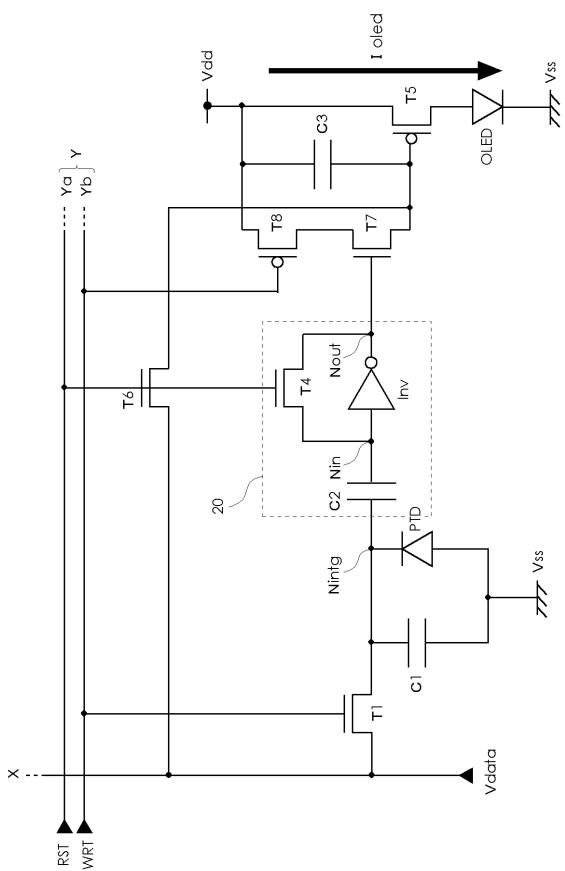

**【0056】****(第6の実施形態)**

上述した各実施形態では、スイッチング素子によって駆動電流Ioledの経路を遮断することで、有機EL素子OLEDの発光を停止する例について説明した。しかしながら、有機EL素子OLEDの発光停止は、この方法以外に、図9に示したキャパシタC3の保持データを非発光状態に充放電することによっても実現可能である。図10は、第6の実施形態にかかる光フィードバック型の画素回路図である。なお、トランジスタT1からコンパレータ20の出力ノードNoutに至るまでの構成については、図9に示した画素回路と同様であるから、同一の符号を付してここでの説明を省略する。また、この画素回路の動作は、図3に示したタイミングチャートと基本的に同様である。40

**【0057】**

駆動素子であるトランジスタT5の一方の端子は、キャパシタC3の一方の電極と共にVdd端子に接続されており、その他の端子は、有機EL素子OLEDのアノードに接続されている。有機EL素子OLEDのカソードは、Vss端子に接続されている。また、pチャネル型50

のトランジスタT5のゲートは、キャパシタC3の他方の端子と、nチャネル型のトランジスタT6の一方の端子と、nチャネル型のトランジスタT7の一方の端子とに共通接続されている。トランジスタT6の他方の端子は、データ線Xに接続されており、そのゲートは、ライト信号WRTが供給される第2の走査線Ybに接続されている。トランジスタT7のゲートは、コンパレータ20からの出力電圧Voutが供給される出力ノードNoutに接続されており、その他方の端子は、pチャネル型のトランジスタT8の一方の端子に接続されている。このトランジスタT8の他方の端子は、Vdd端子に接続されており、そのゲートは、トランジスタT6と同様に第2の走査線Ybに接続されている。

#### 【0058】

キャパシタC3およびトランジスタT5は、第5の実施形態と同様に、駆動電流Ioledを変調する手段として機能する。具体的には、リセット信号RST1がHレベルになるデータ書込期間t0~t1において、トランジスタT6がオンする。これにより、データ線Xを介して供給されたデータ電圧Vdata(i)がキャパシタC3に保持される。そして、ライト信号WRTがLレベルになってトランジスタT8がオンするタイミングt2において、キャパシタC3にゲート接続されたトランジスタT5は、キャパシタの保持データに応じた駆動電流Ioledを生成し、これを有機EL素子OLEDに供給する。これにより、有機EL素子OLEDが発光し始める。発光期間t2~t3では、出力電圧VoutがLレベルなので、キャパシタC3と並列に設けられたトランジスタT7がオフし、キャパシタC3の一対の電極を電気的に分離する。有機EL素子OLEDの発光は、図3に示したように、コンパレータからの出力電圧VoutがLレベルからHレベルに切り替わるタイミングt3で停止する。なぜなら、このタイミング3で、キャパシタC3と並列に設けられたトランジスタT7がオンし、キャパシタC3の一対の電極が短絡するため、キャパシタC3の保持データがディスチャージされるからである。

#### 【0059】

本実施形態によれば、電圧プログラム方式の駆動系を設け、この駆動系を構成するキャパシタC3の保持データを出力電圧Voutが切り替わるタイミングt3で非発光状態になるように設定する。これにより、第5の実施形態と同様の効果が得られる。

#### 【0060】

なお、上述した各実施形態では、発光素子として有機EL素子OLEDを用いた例について説明した。しかしながら、本発明はこれに限定されるものではなく、駆動電流に応じて輝度が設定される発光素子（無機LED表示装置、フィールド・エミッഷン表示装置等）、或いは、駆動電流に応じた透過率・反射率を呈する電気光学装置（エレクトロクロミック表示装置、電気泳動表示装置等）に対しても広く適用可能である。

#### 【0061】

また、上述した各実施形態にかかる電気光学装置は、例えば、テレビ、プロジェクタ、携帯電話、携帯端末、モバイル型コンピュータ、パーソナルコンピュータ等を含む様々な電子機器に実装可能である。図12は、一例として、上述した各実施形態にかかる電気光学装置を実装した携帯電話10の外観斜視図である。この携帯電話10は、複数の操作ボタン11のほか、受話口12、送話口13とともに、上述した表示部1を備えている。これらの電子機器に上述した電気光学装置を実装すれば、電子機器の商品価値を一層高めることができ、市場における電子機器の商品訴求力の向上を図ることができる。

#### 【図面の簡単な説明】

#### 【0062】

【図1】電気光学装置のブロック構成図

【図2】第1の実施形態にかかる画素回路図

【図3】第1の実施形態にかかる動作タイミングチャート

【図4】キャパシタおよびフォトダイオードを直列接続した回路図

【図5】第2の実施形態にかかる画素回路図

【図6】第3の実施形態にかかる画素回路図

【図7】第4の実施形態にかかる画素回路図

10

20

30

40

50

【図 8】第 4 の実施形態にかかる動作タイミングチャート

【図 9】第 5 の実施形態にかかる画素回路

【図 10】第 6 の実施形態にかかる画素回路図

【図 11】C M O S 構成のインバータの回路図

【図 12】電気光学装置を実装した携帯電話の外観斜視図

【符号の説明】

【0063】

1 表示部

2 画素

3 走査線駆動回路

4 データ線駆動回路

5 制御回路

20 コンパレータ

21 ソースフォロワ回路

T1 ~ T8 トランジスタ

C1 ~ C3 キャパシタ

OLED 有機 E L 素子

PTD フォトダイオード

INV インバータ

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(56)参考文献 特表2003-536115(JP,A)

特開2005-148286(JP,A)

特表2003-509728(JP,A)

国際公開第02/077957(WO,A1)

特開2003-255897(JP,A)

国際公開第2004/051852(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3 0

G 09 G 3 / 2 0

H 01 L 5 1 / 5 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于驱动像素电路的方法，像素电路，电光装置和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP4007336B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2007-11-14 |

| 申请号            | JP2004116778                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2004-04-12 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 当前申请(专利权)人(译)  | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 野澤俊之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 野澤 俊之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32 H04N3/14 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3258 G09G3/2014 G09G3/3233 G09G2300/0809 G09G2300/0819 G09G2300/0833 G09G2300/0852 G09G2300/0861 G09G2310/0251 G09G2320/043 G09G2320/045 G09G2360/148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/30.K G09G3/20.624.B G09G3/20.642.P G09G3/20.670.J H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/EE68 3K107/HH04 3K107/HH05 5C080/AA06 5C080/AA11 5C080/AA13 5C080/AA18 5C080/BB05 5C080/DD05 5C080/DD29 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK01 5C080/KK07 5C080/KK43 5C080/KK47 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB22 5C380/AB23 5C380/AB25 5C380/AC07 5C380/AC08 5C380/AC11 5C380/AC12 5C380/BA08 5C380/BA10 5C380/BA38 5C380/BA39 5C380/BB05 5C380/BC20 5C380/BD05 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CA17 5C380/CA26 5C380/CA32 5C380/CA54 5C380/CB01 5C380/CB14 5C380/CC03 5C380/CC07 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC48 5C380/CC50 5C380/CC52 5C380/CC53 5C380/CC63 5C380/CD024 5C380/CD025 5C380/CD026 5C380/CD036 5C380/CF07 5C380/CF09 5C380/CF22 5C380/CF23 5C380/CF27 5C380/CF41 5C380/CF43 5C380/CF51 5C380/CF54 5C380/CF61 5C380/DA02 5C380/DA06 5C380/DA07 5C380/DA16 5C380/DA35 5C380/DA47 5C380/DA50 5C380/FA03 5C380/FA05 5C380/HA11 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 其他公开文献         | <a href="#">JP2005300897A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

#### 摘要(译)

为了确保显示的均匀性，不依赖于发光元件等的特性变化或随时间的劣化。包含光电转换元件的光学反馈型像素电路包括电容器C1，其累积从光电转换元件输出的光电流的积分值作为电荷，电容器C1根据电容器C1中累积的电荷而设定。比较器20，其在第一电压达到根据经由数据线X提供的数据而设置的第二电压的时刻切换输出电压Vout的电平，以及比较输出电压Vout的比较器20当第一电压未达到第二电压时，使有机EL元件OLED发光，并且当第一电压达到第二电压时，有机EL元件OLED并且晶体管T2用于停止EL元件OLED的发光。.The

【図 1】