# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-334163 (P2004-334163A)

(43) 公開日 平成16年11月25日(2004.11.25)

| (51) Int.C1. <sup>7</sup> | F I                          |                     |                     | テーマコー    | ド (参考) |

|---------------------------|------------------------------|---------------------|---------------------|----------|--------|

| GO9G 3/30                 | GO9G                         | 3/30                | J                   | 3K007    |        |

| GO9G 3/20                 | GO9G                         | 3/30                | K                   | 5C080    |        |

| HO5B 33/14                | GO9G                         | 3/20 €              | 611A                |          |        |

|                           | GO9G                         | 3/20 €              | 621A                |          |        |

|                           | GO9G                         | 3/20 €              | 624B                |          |        |

|                           | 審查請才                         | 有 請求項               | iの数 24 O L          | (全 18 頁) | 最終頁に続く |

| (21) 出願番号                 | 特願2003-337939 (P2003-337939) | (71) 出願人            | 590002817           |          |        |

| (22) 出願日                  | 平成15年9月29日 (2003.9.29)       |                     | 三星エスディ              | アイ株式会社   |        |

| (31) 優先権主張番号              | 2003-027604                  | 大韓民国京畿道水原市靈通区▲しん▼洞5 |                     |          |        |

| (32) 優先日                  | 平成15年4月30日 (2003.4.30)       |                     | 75番地                |          |        |

| (33) 優先権主張国               | 韓国 (KR)                      | (74) 代理人            | 100095957           |          |        |

|                           |                              |                     | 弁理士 亀谷              | 美明       |        |

|                           |                              | (74) 代理人            | 100096389           |          |        |

|                           |                              |                     | 弁理士 金本              | 哲男       |        |

|                           |                              | (72) 発明者            | 鄭 寶容                |          |        |

|                           |                              |                     | 大韓民国ソウル市松坡区可樂2洞(番地な |          |        |

|                           |                              |                     | し) 173              | - 19号    |        |

|                           |                              | (72) 発明者            | 朴 鎔盛                |          |        |

|                           |                              |                     | 大韓民国ソウ              | ル市松坡区新川  | 洞(番地なし |

(54) 【発明の名称】画像表示パネル、画像表示装置、画像表示装置の駆動方法、および画素回路

# (57)【要約】

【課題】 駆動トランジスタのしきい電圧を補償するとともに ,表示素子に不必要な電流が流れないようにする

【解決手段】 有機EL表示装置の画素回路において,駆動トランジスタのしきい電圧を補償するために駆動トランジスタM1のゲートには,ダイオード構成された補償トランジスタM2のゲートが接続されている。直前走査線Sn・1に選択信号が伝送されている間,トランジスタM1のゲートにプリチャージ電圧が印加される。このプリチャージ電圧によって有機EL素子OLEDが発光しないように,トランジスタM5によってトランジスタM1と有機EL素子を電気的に切り離す。また,データ電圧がキャパシタCstに充電される間にも有機EL素子が発光しないように,トランジスタM5によってトランジスタM1と有機EL素子を電気的に切り離す。

【選択図】 図3

) ハンシンコアアパート1425号

最終頁に続く

#### 【特許請求の範囲】

## 【請求項1】

画像信号を示すデータ電圧を伝達する複数のデータ線と,選択信号を伝達する複数の走査線と,隣接する二つのデータ線と隣接する二つの走査線によって定義される各画素領域に形成される複数の画素回路と,を含む画像表示パネルにおいて,

前記各画素回路は,

印加される電流の量に対応して画像を表示する表示素子と、

主電極と制御電極の間にキャパシタが接続されており,前記主電極と前記制御電極の間の電圧に対応する電流を出力する第1トランジスタと,

前記第1トランジスタの制御電極に接続された制御電極を有し,ダイオードを構成する 第2トランジスタと,

前記第2トランジスタの主電極に接続されており,現在走査線から供給される選択信号 に応答して前記データ線から供給されるデータ電圧を前記第2トランジスタに伝達する第 1スイッチング素子と,

第 1 制御信号に応答してプリチャージ電圧を前記第 1 トランジスタの制御電極に伝達する第 2 スイッチング素子と,

第 2 制御信号に応答して前記第 1 トランジスタと前記発光素子を電気的に遮断する第 3 スイッチング素子と、

を含むことを特徴とする画像表示パネル。

#### 【請求項2】

前記第1制御信号は,直前走査線から供給される選択信号であることを特徴とする,請求項1に記載の画像表示パネル。

## 【請求項3】

前記第1制御信号に応じて前記プリチャージ電圧が前記第1トランジスタの制御電極に伝達される期間と前記現在走査線に選択信号が印加される期間に,前記データ電圧が前記データ線に印加されることを特徴とする,請求項2に記載の画像表示パネル。

## 【請求項4】

前記現在走査線に選択信号が印加される前に,前記データ線における前記データ電圧は,所定の値に調整されることを特徴とする,請求項3に記載の画像表示パネル。

#### 【請求項5】

前記第2制御信号は,前記第1制御信号と共通であることを特徴とする,請求項1に記載の表示パネル。

#### 【請求項6】

前記第 1 制御信号および第 2 制御信号は,直前走査線から供給される選択信号であり,前記第 2 スイッチング素子は,第 1 導電型のトランジスタであり,

前記第3スイッチング素子は,前記第1導電型と反対の第2導電型のトランジスタであることを特徴とする,請求項5に記載の画像表示パネル。

## 【請求項7】

前記第2制御信号は、前記現在走査線から供給される選択信号であり、

前記第2スイッチング素子は、第1導電型のトランジスタであり、

前記第3スイッチング素子は,前記第1導電型と反対の第2導電型のトランジスタであることを特徴とする,請求項1に記載の表示パネル。

## 【請求項8】

前記第1制御信号は,直前走査線から供給される選択信号であることを特徴とする,請求項7に記載の表示パネル。

# 【請求項9】

前記第3スイッチング素子は,前記第1制御信号に応じて前記プリチャージ電圧が前記第1トランジスタの制御電極に伝達される間と,前記現在走査線供給される選択信号に応じて前記データ電圧が前記第1トランジスタの制御電極に伝達される間に,遮断されることを特徴とする,請求項1に記載の画像表示パネル。

20

30

40

#### 【請求項10】

前 記 第 3 ス イ ッ チ ン グ 素 子 は , 直 列 に 接 続 さ れ る 第 3 ト ラ ン ジ ス タ と 第 4 ト ラ ン ジ ス タ を含み、

前 記 第 2 制 御 信 号 は , 前 記 プ リ チ ャ ー ジ 電 圧 が 伝 達 さ れ る 間 に 前 記 第 3 ト ラ ン ジ ス タ を 遮 断 さ せ る 第 3 制 御 信 号 と , 前 記 デ ー タ 電 圧 が 伝 達 さ れ る 間 に 前 記 第 4 ト ラ ン ジ ス タ を 遮 断させる第4制御信号と,を含むことを特徴とする,請求項9に記載の画像表示パネル。

#### 【請求項11】

前記第1制御信号および前記第3制御信号は,前記直前走査線から供給される選択信号 であり,

前記第2スイッチング素子は,第1導電型のトランジスタであり,

前 記 第 3 ト ラ ン ジ ス タ は , 前 記 第 1 導 電 型 と 反 対 の 第 2 導 電 型 の ト ラ ン ジ ス タ で あ る こ とを特徴とする,請求項10に記載の画像表示パネル。

## 【請求項12】

前記第4制御信号は,前記現在走査線から供給される選択信号であり,

前 記 第 4 ト ラ ン ジ ス タ は , 前 記 第 1 ト ラ ン ジ ス タ と 反 対 の 導 電 型 の ト ラ ン ジ ス タ で あ る ことを特徴とする,請求項10に記載の画像表示パネル。

### 【請求項13】

前 記 第 1 ス イ ッ チ ン グ 素 子 お よ び 前 記 第 2 ス イ ッ チ ン グ 素 子 は , 前 記 第 1 ト ラ ン ジ ス タ および前記第2トランジスタと同一の導電型のトランジスタであることを特徴とする,請 求項1に記載の画像表示パネル。

#### 【請求項14】

前 記 プリチャージ 電圧 は ,前 記 デー タ 線 か ら 供 給 さ れ る デ ー タ 電 圧 の 最 低 電 圧 よ り 低 い ことを特徴とする,請求項1に記載の画像表示パネル。

#### 【請求項15】

画像信号を示すデータ電圧を伝達する複数のデータ線と,選択信号を伝達する複数の走 査線と,隣接する二つのデータ線と隣接する二つの走査線によって定義される各画素領域 に形成される複数の画素回路と,を含む画像表示パネルを備えた表示装置において,

前記各画素回路は、

印加される電流の量に対応して画像を表示する表示素子と、

主電極と制御電極の間にキャパシタが接続されており,前記主電極と前記制御電極の間 の電圧に対応する電流を出力する第1トランジスタと,

前記第1トランジスタの制御電極に接続された制御電極を有し,ダイオードを構成する 第2トランジスタと,

前 記 第 2 ト ラ ン ジ ス タ の 主 電 極 に 接 続 さ れ て お り , 現 在 走 査 線 か ら 供 給 さ れ る 選 択 信 号 に応答して前記データ線から供給されるデータ電圧を前記第2トランジスタに伝達する第 1スイッチング素子と,

第 1 制 御 信 号 に 応 答 し て プ リ チ ャ ー ジ 電 圧 を 前 記 第 1 ト ラ ン ジ ス タ の 制 御 電 極 に 伝 達 す る第2スイッチング素子と、

第 2 制御信号に応答して前記第 1 トランジスタと前記発光素子を電気的に遮断する第 3 スイッチング素子と,

# を含み、

前 記 画 像 表 示 パ ネ ル に 装 着 さ れ , ま た は , 前 記 画 像 表 示 パ ネ ル に 電 気 的 に 接 続 さ れ て 前 記データ線に前記データ電圧を印加するデータ駆動部と、

前記画像表示パネルに装着され,または,前記画像表示パネルに電気的に接続されて前 記走査線に前記選択信号を印加する走査駆動部と、

を含むことを特徴とする、画像表示装置。

#### 【請求項16】

制 御 電 極 と 主 電 極 の 間 に キ ャ パ シ タ が 接 続 さ れ , 前 記 キ ャ パ シ タ に 充 電 さ れ た 電 圧 に 対 応する電流を出力する第1トランジスタと,前記第1トランジスタの制御電極に接続され た制御電極を備え,ダイオードを構成する第2トランジスタと,前記第1トランジスタか

10

20

30

40

ら出力される電流の量に対応して画像を表示する表示素子と,を含む画素回路を備えた画像表示装置の駆動方法において,

第 1 期間内に第 1 制御信号に応答して前記第 1 トランジスタの制御電極にプリチャージ電圧を伝達する段階と、

第2期間内に現在走査線から供給される選択信号に応答して前記第2トランジスタを通じて前記第1トランジスタの制御電極にデータ電圧を伝達する段階と, を含み,

前記第1期間および前記第2期間のうち少なくとも一つの期間で前記第1トランジスタと前記発光素子が電気的に遮断されることを特徴とする,画像表示装置の駆動方法。

#### 【請求項17】

前記第1制御信号は,直前走査線から供給される選択信号であることを特徴とする,請求項16に記載の画像表示装置の駆動方法。

#### 【請求項18】

前記第1期間において,前記第1制御信号に応答して,前記第1トランジスタと前記表示素子が電気的に遮断されることを特徴とする,請求項16または17に記載の画像表示装置の駆動方法。

## 【請求項19】

前記第2期間において,第2制御信号に応答して,前記第1トランジスタと前記表示素子が電気的に遮断されることを特徴とする,請求項16に記載の画像表示装置の駆動方法

#### 【請求項20】

前記第2制御信号は,前記現在走査線から供給される選択信号であることを特徴とする,請求項19に記載の画像表示装置の駆動方法。

# 【請求項21】

前記第1期間と前記第2期間において,

前記第1トランジスタの制御電極に前記プリチャージ電圧または前記データ電圧が伝達することを阻止する段階をさらに含むことを特徴とする,請求項16に記載の画像表示装置の駆動方法。

# 【請求項22】

前記第1制御信号は,直前走査線から供給される選択信号であり,

前記第1期間において,前記直前走査線から供給される選択信号に応答して前記第1トランジスタと前記表示素子が電気的に遮断され,

前記第2期間において,前記現在走査線から供給される選択信号に応答して前記第1トランジスタと前記表示素子が電気的に遮断されることを特徴とする,請求項21に記載の画像表示装置の駆動方法。

## 【請求項23】

プリチャージ電圧と画像を示すデータ電圧に応答する画素回路において,

制御電極と主電極の間にキャパシタが接続され前記キャパシタに充電された電圧に対応する電流を出力する第1トランジスタと、

前記第 1 トランジスタの制御電極に制御電極が接続され,ダイオードを構成する第 2 トランジスタと,

前記第1トランジスタから出力される電流の量に対応して画像を表示する表示素子と,前記第1トランジスタと前記表示素子の間に電気的に接続されるスイッチング部と, を含み,

第1期間内に制御信号に応答して前記プリチャージ電圧を前記第1トランジスタの制御電極に伝達させ,第2期間内に選択信号に応答して前記データ電圧を前記第1トランジスタの制御電極に伝達させ,

前記スイッチング部は,前記第1期間と前記第2期間のうち少なくとも一つの期間で前記第1トランジスタと前記表示素子を電気的に遮断することを特徴とする,画素回路。

## 【請求項24】

10

20

30

40

30

40

50

前記制御信号は,直前選択信号であることを特徴とする,請求項23に記載の画素回路

【発明の詳細な説明】

【技術分野】

[00001]

本発明は,画像表示パネル,画像表示装置,画像表示装置の駆動方法,および画素回路に関する。

# 【背景技術】

[00002]

一般に,有機電界発光(以下,「EL: Electro Luminescence」という)表示装置は,蛍光性有機化合物を電気的に励起して発光させる表示装置であって,N×M個の有機発光セルを電圧駆動あるいは電流駆動することによって映像を表現する。このような有機発光セルは,電子と正孔の均衡を保つことによって発光効率の向上を図っており,カソード(金属),電子注入層,電子輸送層,発光層,正孔輸送層,正孔注入層,アノード(ITO)を含む多層構造を有している。

[00003]

このように構成される有機発光セルを駆動する方式には,単純マトリックス方式と,トランジスタを利用した能動駆動方式がある。単純マトリックス方式は,正極線群と負極線群を直交するように形成し,両群から線を1本ずつ選択して,両線の交点に在る画素を直接駆動する方式である。これに対して,能動駆動方式は,トランジスタとキャパシタを各画素のITO電極に接続し,キャパシタを維持素子として,瞬間的に印加された電圧を,例えば1フレーム期間維持する駆動方式である。この能動駆動方式はさらに,キャパシタで電圧を維持するために用いられる信号の形態によって,電圧駆動方式と電流駆動方式に分けられる。

[0004]

電圧駆動方式は,階調度を示すデータ電圧を画素回路に供給して画像を表示する方式である。この電圧駆動方式を採用した場合,駆動トランジスタのしきい電圧および電子移動度の偏差によって画質が不均一となるおそれがある。一方の電流駆動方式は,階調度を示すデータ電流を画素回路に供給して画像を表示する方式である。この電流駆動方式によれば,電圧駆動方式で問題となる画質の均一性を確保することはできる。しかし,電流駆動方式では微小な電流で有機 E L 素子を制御しなければならないので,動作に必要な電圧にデータ線を充電するための充電時間を確保し難いという別の問題がある。

[00005]

下記特許文献 1 は, E L パネル等を駆動するトランジスタのしきい値特性のばらつきを ,比較的少ない数のトランジスタを用いて比較的小さな電力消費により補償することが可 能な電圧駆動方式のトランジスタ回路を開示している。

[0006]

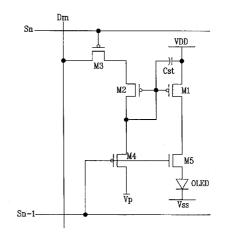

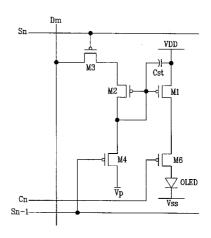

図 1 は,従来の画素回路であり, 4 個のトランジスタM 1 ~ M 4 および有機 E L 素子O L E D からなる。駆動トランジスタM 1 は,ゲートとソースの間の電圧に対応する電流を有機 E L 素子O L E D に伝達する。また,駆動トランジスタM 1 のゲートとソースの間には記憶キャパシタCstが接続されている。トランジスタM 2 は,ダイオードを構成しており,そのゲートがトランジスタM 1 のゲートに接続されている。また,スイッチングトランジスタM 3 は,そのゲートが走査線Snに接続されており,トランジスタM 4 は,そのゲートが走査線Snに接続されており,トランジスタM 4 は,そのゲートが走査線Sn:1 に接続されている。各トランジスタM 1 ~M 4 の極性に各種入力電圧の極性が合わせられる。

[0007]

トランジスタM3,M2,M4にデータ信号が流れている時,トランジスタM1,M2のしきい電圧が同一であれば,トランジスタM2によってトランジスタM1のしきい電圧が完全に補償される。しかし,駆動トランジスタM1のゲート電圧がトランジスタM3を

通じて印加されるデータ電圧より高い場合には,ダイオード構成のトランジスタM2は遮断状態になって,データ電圧が駆動トランジスタM1のゲートに伝達されなくなる。これを防止するためには,走査線Sn.1の選択信号が印加されている期間にプリチャージ電圧Vpを駆動トランジスタM1のゲートに印加して,プリチャージ電圧Vpを最も低いデータ電圧より小さい値とする。このようにすれば,データ電圧が印加される時,駆動トランジスタM1のゲート電圧がプリチャージ電圧Vpになるため,トランジスタM2によって構成されるダイオードは常に順方向となる。

[0008]

【特許文献1】特開平11-27233号公報

【発明の開示】

【発明が解決しようとする課題】

[0009]

しかし、プリチャージ電圧Vpが駆動トランジスタM1のゲートに伝達されれば、プリチャージ電圧Vpと電源電圧VDDの差に相当する電圧によって駆動トランジスタM1に電流が流れる。この電流によって有機EL素子OLEDは常に発光してしまい、ブラックレベルの階調を表現する場合には正常なブラックレベルを表現することができなくなる。また、従来の回路では、データ電圧が駆動トランジスタM1のゲートに伝達されてキャパシタCstに充電される間にも有機EL素子OLEDに電流が流れてしまい、結果的に回路全体の消費電力が増加するおそれがあった。

[0010]

本発明は,このような問題に鑑みてなされたもので,その目的は,駆動トランジスタのしきい電圧を補償すると共に,表示素子に不必要な電流が流れないように工夫された画像表示パネル,画像表示装置,画像表示装置の駆動方法,および画素回路を提供することにある。

【課題を解決するための手段】

[0011]

上記課題を解決するために,本発明によれば,駆動トランジスタと表示素子の間にトランジスタが追加される。

[0012]

そして,本発明の第1の観点によれば,画像信号を示すデータ電圧を伝達する複数のデータ線と,選択信号を伝達する複数の走査線と,隣接する二つのデータ線と隣接する二のの走査線間に形成される名画素領域に形成される複数の画素回路と,を含む画像表示パお提供される。各画素可とは、素示素・第1トランジスタは,を含む画像を表示のでいません。第1トランジスタは、主電極と制御電極の間にキャパシタででいる。第2トランジスタの制御電極が第1トランジスタの制御電をはいる。第1スイッチング素子は、その制御電極が第1トランジスタの制御電圧を第2トランジスタに伝達する。第2スイッチング素子は、データ電圧が供給される前に第1トランジスタに伝達する。第2スイッチング素子は、データ電圧が供給される前に第1十一の制御電極に伝達する。第3スイッチング素子は、第2トランジスタに伝達する。第3スイッチング素子は、第1トランジスタと表示素子を電気的に遮断する(切り離す)。

[0013]

ここで,第1制御信号に応じてプリチャージ電圧が伝達される期間と現在走査線に選択信号が印加される期間において,データ電圧がデータ線に印加されることが好ましい。

[0014]

第2制御信号は,第1制御信号であることが好ましい。また,第1制御信号および第2制御信号は,直前走査線から供給される選択信号であり,第2スイッチング素子と第3スイッチング素子は互いに,反対の導電型のトランジスタであることが好ましい。

[0015]

50

10

20

30

20

30

40

50

また,第 2 制御信号は,現在走査線から供給される選択信号であることが好ましい。さらに,第 2 スイッチング素子と第 3 スイッチング素子は,互いに反対の導電型のトランジスタであることが好ましい。そして,第 1 制御信号は,直前走査線から供給される選択信号であることが好ましい。

[0016]

上記課題を解決するために,本発明の第2の観点によれば,上述した画像表示パネルを含む画像表示装置が提供される。

[0017]

また,上記課題を解決するために,本発明の第3の観点によれば,制御電極と主電極の間にキャパシタが接続され,キャパシタに充電された電圧に対応する電流を出力する第1トランジスタと,第1トランジスタの制御電極に接続された制御電極を備え,かつダイオードを構成する第2トランジスタと,第1トランジスタから出力される電流の量に対応して画像を表示する表示素子と,を含む画素回路を備えた画像表示装置の駆動方法が提供される。この方法によれば,第1期間において,第1制御信号に応答して第1トランジスタの制御電極にプリチャージ電圧が伝達される。また,第2期間において,現在走査線から供給される選択信号に応答して第2トランジスタを通じて第1トランジスタの制御電極にデータ電圧が伝達される。そして,データ電圧が遮断される。第1期間および第2期間のうち少なくとも一つの期間で第1トランジスタと表示素子は電気的に遮断される。

[0018]

第1制御信号は,直前走査線から供給される選択信号であることが好ましい。また,第1期間において,第1制御信号に応答して,第1トランジスタと表示素子が電気的に遮断されることが好ましい。

[0019]

第2期間において,第2制御信号に応答して,第1トランジスタと表示素子が電気的に遮断される。第2制御信号は,現在走査線から供給される選択信号であることが好ましい

[0020]

そして,第1期間内または第2期間内に,第1トランジスタの制御電極にプリチャージ電圧またはデータ電圧が伝達されることを阻止する期間を含ませることが好ましい。

[0021]

また、上記課題を解決するために、本発明の第4の観点によれば、第1信号線から供給されるプリチャージ電圧と第2信号線から供給される画像を示すデータ電圧に応答する画素回路が提供される。この画素回路は、第1トランジスタ、第2トランジスタ、表示素子、およびスイッチング部を含む。第1トランジスタは、キャパシタに充電された電圧に対応する電流を出力し、制御電極と主電極の間にキャパシタが接続されている。ダイオードを構成する第2トランジスタの制御電極は、第1トランジスタの制御電極に接続されている。第1期間内に制御信号に応答してプリチャージ電圧が第1トランジスタの制御電極に伝達され、第2期間内に選択信号に応答してデータ電圧が第1トランジスタの制御電極に伝達される。そして、スイッチング部は、第1期間と第2期間のうち少なくとも一つの期間で第1トランジスタと表示素子を電気的に遮断する。

【発明の効果】

[0022]

本発明によれば,第1トランジスタ(駆動トランジスタ)と第2トランジスタ(補償トランジスタ)の各しきい電圧が同一であれば,第1トランジスタのしきい電圧の偏差を補償することができる。また,本発明によれば,キャパシタにプリチャージ電圧が充電される間に,このプリチャージ電圧によって形成された電流が第1トランジスタに流れなくなる。これによって,ブラックレベル階調が一層暗く表示され,コントラストが向上する。また,キャパシタにデータ電圧が充電される間に,第1トランジスタに電流が流れなくなるため消費電力を減らすことができる。

20

30

40

50

# 【発明を実施するための最良の形態】

## [0023]

以下に添付図面を参照しながら,本発明の好適な実施の形態について詳細に説明する。なお,本明細書および図面において,実質的に同一の機能構成を有する構成要素については,同一の符号を付することにより重複説明を省略する。また,ある部分が他の部分と接続されていると説明されている場合,これは直接的な接続だけでなく,その中間に他の素子が介在する間接的な電気的接続も含む。

## [0024]

(第1の実施の形態)

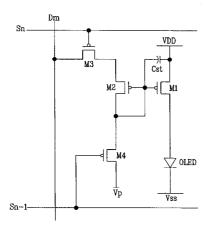

まず、図2を参照して本発明の第1の実施の形態にかかる有機EL表示装置について説明する。図2は、本実施の形態にかかる有機EL表示装置の概略的な平面図である。

[0025]

図 2 に示したように,本実施の形態にかかる有機 E L 表示装置は,有機 E L 表示パネル 1 0 ,走査駆動部 2 0 ,およびデータ駆動部 3 0 を含む。

[0026]

有機EL表示パネル10は,列方向に延びる複数のデータ線D1~Dm,行方向に延びる複数の走査線S1~Sn,および複数の画素回路11を含む。データ線D1~Dmは,各画素の輝度を決めるデータ電圧を画素回路11に伝達し,走査線S1~Snは,特定の画素回路11を選択するための選択信号を画素回路11に伝達する。画素回路11は,隣接した二つのデータ線D1~Dmと隣接した二つの走査線S1~Snによって定義される画素領域に形成されている。

[0027]

走査駆動部 2 0 は,走査線 S 1 ~ S n に選択信号を順次に出力し,データ駆動部 3 0 は,データ線 D 1 ~ D m に画像信号としてのデータ電圧を印加する。

[0028]

走査駆動部20とデータ駆動部30の両方またはいずれか一方は,表示パネル10に直接電気的に接続されるか,あるいは,テープキャリアパッケージ(TCP)などにチップなどの形態で装着された状態で表示パネル10に接着され,電気的に接続され得る。また,表示パネル10に接着されて電気的に接続されている可撓性印刷回路基板(FPC)またはフィルムなどに,走査駆動部20とデータ駆動部30の両方またはいずれか一方をチップなどの形態で装着することも可能である。これをCoF(chip on fle×ible board/chip on film)方式という。この他,走査駆動部20とデータ駆動部30の両方またはいずれか一方を,表示パネル10のガラス基板上に直接装着すること,またはガラス基板上に走査線,データ線,および薄膜トランジスタと共通の層で形成されている駆動回路に置き換えて直接装着することもできる。これをCoG(chip on glass)方式という。

[0029]

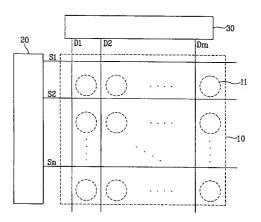

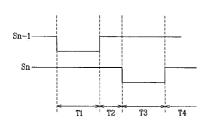

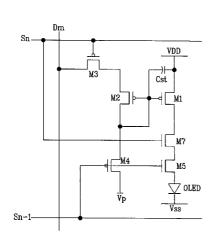

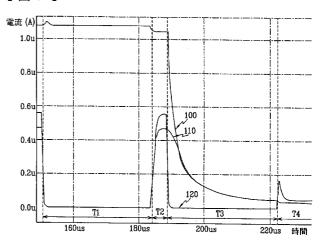

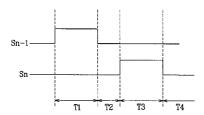

次に、図3および図4を参照して、本実施の形態にかかる有機 E L 表示装置の画素回路 1 1について詳細に説明する。図3は、本本実施の形態にかかる画素回路 1 1 の等価回路 図であり、図4は、図3の画素回路 1 1を駆動するための駆動信号の波形図である。図3では説明の便宜上、m番目データ線 D m と n 番目走査線 S n に接続された画素回路 1 1 だけを示した。そして走査線に関する用語を定義すれば、現在選択信号を伝達しようとする走査線を"現在走査線"とし、現在選択信号が伝達される直前に選択信号を伝達した走査線を"直前走査線"とする。

[0030]

図 3 に示したように,本発実施の形態にかかる画素回路 1 1 は,有機 E L 素子(表示素子) O L E D ,トランジスタ M 1 ~ M 5 ,およびキャパシタ C s t を含む。トランジスタ M 1 ~ M 4 は P チャネル型 M O S (Metal Oxide Semiconductor)トランジスタで形成され,トランジスタ M 5 は,N チャネル型 M O S トランジスタで形成されている。このようなトランジスタ M 1 ~ M 5 は,表示パネル 1 0 のガラス基板上

30

40

50

に形成されるゲート電極 , ドレーン電極 , およびソース電極をそれぞれ制御電極および 2 つの主電極とする薄膜トランジスタであることが好ましい。

### [0031]

駆動トランジスタ(第1トランジスタ)M1は,電源電圧VDDにソース(主電極)が接続され,ゲート(制御電極)とソースの間にキャパシタCstが接続されている。キャパシタCstは,トランジスタM1のゲート・ソース電圧Vgsを一定期間維持する。ダイオードとして構成された補償トランジスタ(第2トランジスタ)M2のゲートには,トランジスタM1のゲート(制御電極)が接続されている。スイッチングトランジスタ(第1スイッチング素子)M3は,現在走査線Snからの選択信号に応答してデータ線Dmからのデータ電圧をトランジスタM2に伝達する。トランジスタM2のゲートとドレインにはトランジスタ(第2スイッチング素子)M4のソースが接続されている。トランジスタM4は,期間T1に直前走査線Sn・1から印加される論理的低レベル(ローレベル)選択信号に応答して,トランジスタM1とトランジスタM2の各ゲート電圧を引き下げる。

## [0032]

トランジスタ(第3スイッチング素子,第3トランジスタ,スイッチング部)M5は,トランジスタM1のドレインと有機EL素子OLEDのアノードの間に接続されており,直前走査線Sn-1からのローレベル選択信号に応答してトランジスタM1と有機EL素子OLEDを電気的に遮断する(切り離す)。有機EL素子OLEDは,カソードが負電位源Vssに接続されており,印加される電流に対応する輝度の光を発する。負電位源Vssとしては,電源電圧(正電位源)VDDより低電位のもの,例えば接地電位などを用いることができる。

#### [0033]

以下,図 4 を参照して,本実施の形態にかかる画素回路 1 1 の動作について詳細に説明する。

## [0034]

図4に示すように,まず,プリチャージ期間(第1期間)T1において,直前走査線Sn・1からの選択信号がローレベルになって,トランジスタM4は導通(オン)して位立って,プリチャージ電圧Vpが十分に低い電位きれば,導通したトランジスタM4は,"直前走査線Sn・1のローレベル電圧+したいである。対して,プリチャージ電圧Vpが"直前走査線Sn・1のローレベル電圧+しきい電圧VTн"をトランジスタM1のゲートに伝達する。対して,プリチャージ電圧Vpが"直たトランジスタM4は,プリチャージ電圧VpをトランジスタM1のゲートに伝達印にたトランジスタM4は,プリチャージ電圧Vpをトランジスタのゲートに伝達印によりチャージ電圧Vpは,最大階調レベルを得るために,トランジスタのゲートに低い値であることが好ましい。このようにすれば,データ線Dmを通じてデータ電圧が印に加値であることが好ましい。このようにすれば,データ線ロで表近に大きくなる。したでったとき,このデータ電圧はトランジスタM1のゲート電圧より常に大きくなる。したで、トランジスタM1は順方向に連結されて,データ電圧がキャパシタCstに充電される。

# [0035]

このとき,プリチャージ電圧Vpによって,トランジスタM1のゲート・ソース電圧Vgsが増加すると,トランジスタM1に大きい電流が流れようとする。このような電流が有機EL素子OLEDに供給されると,発光すべきではない期間にあるにも関わらず,有機EL素子OLEDが発光してしまうことになる。この結果,正確なブラック階調が表現できなくなる。この点,本実施の形態によれば,プリチャージ期間T1においてトランジスタM5はオフ状態であるため,トランジスタM1と有機EL素子OLEDが電気的に遮断され,有機EL素子OLEDにプリチャージ電圧Vpによる電流が流れなくなる。したがって,ブラック階調を正確に表現できるようになる。また,トランジスタM1と有機EL素子OLEDに不必要な電流が流れなくなるため,消費電力が低減する。

# [0036]

次のブランキング期間T2では,現在走査線Snからの選択信号が論理的高レベル(ハ

イレベル)に維持された状態で直前走査線Sn‐1からの選択信号がハイレベルになる。そして,このブランキング期間T2内に,データ線Dmから供給されるデータ電圧は,現在走査線Snに接続された画素回路11に対応するレベルに変更される。このデータ電圧は,実際に画素回路に印加されるレベルに調整されることが好ましい。もし,ブランキング期間T2がなければ,現在のデータ電圧がトランジスタM1のゲートに印加される前に,現在走査線Snからの選択信号がローレベルになってしまい,データ線Dmに印加された直前データ電圧がトランジスタM3を通じてトランジスタM1に伝達するおそれがある。本実施の形態では,ブランキング期間T2が存在するため,このような問題は生じず,いわゆるクロストークも回避される。

#### [0037]

続くデータ充電期間T3では,現在走査線Snから供給される選択信号がローレベルになってトランジスタM3が導通(オン)する。これによって,トランジスタM3を通じてデータ線Dmから供給されるデータ電圧がトランジスタM2に伝達される。トランジスタM2はダイオードを構成しているため,データ電圧からトランジスタM2のしきい電圧VTH2を差し引いた電圧がトランジスタM1のゲートに伝達される。この電圧はキャパシタCstに充電されて一定期間維持される。そして,直前走査線Sn-1からの選択信号はハイレベルであるのでトランジスタM5は導通(オン)している。

## [0038]

続く発光期間 T 4 において,トランジスタ M 1 のゲート・ソース電圧 V  $_G$   $_S$  に対応する電流 I  $_O$   $_L$   $_E$   $_D$  が有機 E L 素子 O L E D に供給されて,有機 E L 素子 O L E D が発光する。この電流 I  $_O$   $_L$   $_E$   $_D$  は式 1 のようになる。

[0039]

【数1】

$$I_{OLED} = \frac{\beta}{2} (|V_{GS}| - |V_{TH}|)^2 = \frac{\beta}{2} (V_{DD} - (V_{DATA} - |V_{TH2}|) - |V_{TH1}|)^2 \cdot \cdot \cdot ( \pm 1 )$$

# [0040]

ここで ,  $V_{TH1}$  はトランジスタM 1 のしきい電圧であり ,  $V_{DATA}$  はデータ線 D m から供給されるデータ電圧であり , は定数である。

# [0041]

このとき,トランジスタ M 1 のしきい電圧 V  $_{\text{T} \text{ H} \text{ 1}}$  とトランジスタ M 2 のしきい電圧 V  $_{\text{T} \text{ H} \text{ 2}}$  が同一であれば,式 1 は式 2 のようになる。

[0042]

【数2】

$$I_{OLED} = \frac{\beta}{2} (V_{DD} - V_{DATA})^2 \cdot \cdot \cdot (\vec{x} \ 2)$$

40

10

20

30

## [0043]

式 2 から明らかなように,トランジスタM 1 のしきい電圧 V <sub>T н 1</sub> に関係なくデータ線 D m を通じて印加されるデータ電圧に対応する電流が,有機 E L 素子 O L E D に流れる。

# [0044]

このように,本実施の形態によれば,駆動用トランジスタM1のしきい電圧の偏差を補償することができ,また,プリチャージ電圧Vpに応じて,所定期間,有機EL素子OLEDに電流が流れないようにすることが可能となる。

[0045]

30

40

50

また,本実施の形態にかかる画素回路11では,トランジスタM4,M5を制御するために直前走査線Sn-1を用いたが,プリチャージ期間T1内にトランジスタM4を導通させ,トランジスタM5を遮断させる制御信号を伝達する別途の制御線(図示せず)を備えるようにしてもよい。

## [0046]

(第2の実施の形態)

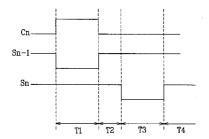

第1の実施の形態では,プリチャージ期間T1において,トランジスタM1と有機EL素子OLEDを遮断するために,トランジスタM4とは反対導電型のトランジスタM5を用いた。これに対して,トランジスタM5をトランジスタM4と同一導電型のトランジスタに置き換えることも可能である。以下,このような回路構成を有する本発明の第2の実施の形態について,図5および図6を参照しながら詳細に説明する。

[0047]

図 5 は,本実施の形態にかかる画素回路の等価回路図であり,図 6 は,図 5 の画素回路を駆動するための駆動信号の波形図である。

[0048]

図5に示したように,本実施の形態にかかる画素回路は,第1の実施の形態にかかる画素回路に対して,トランジスタM5がトランジスタM6に置き換えられ,制御線Cnが追加された構成を有する。詳しく説明すれば,トランジスタM6は,トランジスタM1~M4と同様にPチャネル型MOSトランジスタであり,制御線Cnからのハイレベルの制御信号に応答して遮断(オフ)する。そして制御線Cnに印加される制御信号は,図6に示したように,直前走査線Sn-1に流れる選択信号の論理反転信号(相補信号)である。この構成によって,第1の実施の形態と同様にプリチャージ期間T1内にトランジスタM6が遮断されて,有機EL素子OLEDに電流が流れることが防止される。なお,プランキング期間T2においても,制御線Cnに流れる制御信号をハイレベルにすることが望ましい。

[0049]

このように,本実施の形態によれば,同一タイプのトランジスタで画素回路を実現する ことができるため,第1の実施の形態に比べて製造工程が簡略化される。

[0050]

(第3の実施の形態)

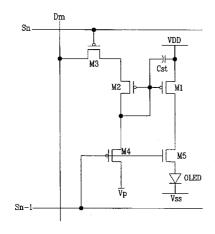

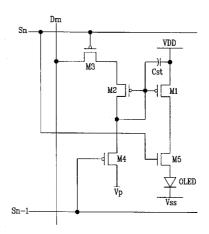

第1の実施の形態にかかる画素回路は,プリチャージ期間T1に有機EL素子OLEDに電流を流さないようにするために,トランジスタM5を備えているが,このトランジスタM5を用いて,データ充電期間(第2期間)T3に有機EL素子OLEDに電流を流さないようにすることもできる。次に,このような回路構成を有する本発明の第3の実施の形態について,図7を参照しながら詳細に説明する。

[0051]

図7は,本実施の形態にかかる画素回路の等価回路図である。

[0052]

図 7 に示すように,本実施の形態にかかる画素回路は,第 1 の実施の形態にかかる画素 回路に対して,トランジスタ M 5 のゲートの接続先が直前走査線 S n - 1 から現在走査線 S n に変更された構成を有する。そして,本実施の形態にかかる画素回路は,図 4 に示し た駆動信号によって駆動される。

[0053]

本実施の形態にかかる画素回路によれば,データ充電期間T3において,データ線Dmから供給されたデータ電圧がキャパシタCstに充電される間に,現在走査線Snから供給される選択信号によってトランジスタM5が遮断されて,トランジスタM1と有機EL素子OLEDが電気的に切り離される。したがって,キャパシタCstにデータ電圧が充電される間に有機EL素子OLEDには電流が流れない。

[0054]

次に,現在走査線Snからの選択信号がハイレベルになれば,トランジスタM5は導通

20

30

40

50

して,トランジスタM1と有機EL素子OLEDは電気的に接続される。この結果,キャパシタCstに充電された電圧に対応する電流I<sub>OLED</sub>が有機EL素子OLEDに流れて有機EL素子OLEDは発光する(発光期間T4)。

#### [0055]

本実施の形態によれば,データ電圧がキャパシタCstに充電される間に有機EL素子OLEDには電流が流れないため,消費電力が低減する。

#### [0056]

また,本実施の形態にかかる画素回路において,トランジスタM5をトランジスタM1~M4と同一導電型とすることもできる。このような場合,走査線Snに流れる選択信号の論理反転信号(相補信号)でトランジスタM5を駆動する。

[0057]

(第4の実施の形態)

第3の実施の形態では,データ充電期間 T 3 において,有機 E L 素子 O L E D に電流が流れないようにしたが,これに加えてプリチャージ期間 T 1 においても,有機 E L 素子 O L E D に電流が流れないようにすることもできる。以下,このような回路構成を有する本発明の第4の実施の形態について,図8および図9を参照しながら詳細に説明する。

[0058]

図8は,本実施の形態にかかる画素回路の等価回路図であり,図9は,図8の画素回路に属する有機EL素子OLEDに流れる電流を示す図面である。

[0059]

図8に示すように、本実施の形態にかかる画素回路は、図3に示した第1の実施の形態にかかる画素回路に対して、トランジスタ(第4トランジスタ)M7が追加された構成を有する。この追加されたトランジスタM7は、Nチャネル型MOSトランジスタであって、トランジスタM5とともに、トランジスタM1と有機EL素子OLEDのアノードの間に直列に接続されている。そして、トランジスタM5のゲートは、直前走査線Sn・1に接続されており、トランジスタM7のゲートは、現在走査線Snに接続されている。なお、トランジスタM5とトランジスタM7の位置は、互いに入れ替えることも可能である。図8に示した本実施の形態にかかる画素回路は、第1、3の実施の形態にかかる画素回路と同様に、図4に示した駆動信号によって駆動される。

[0060]

このような構成を有する本実施の形態にかかる画素回路によれば,プリチャージ期間T1において,直前走査線Sn‐1から供給される選択信号によってトランジスタM5が遮断され,プリチャージ電圧Vpに応じて有機EL素子OLEDに電流が流れなくなる。また,データ充電期間T4において,現在走査線Snから供給される選択信号によって,トランジスタM7が遮断され,データ電圧がキャパシタCstに充電される間に有機EL素子OLEDに電流が流れなくなる。発光期間T4では,トランジスタM5とトランジスタM7は共に導通しているので,キャパシタCstに充電された電圧に対応する電流が有機EL素子OLEDに流れる。

[0061]

本実施の形態にかかる画素回路において,トランジスタM5をトランジスタM4と同じ導電型のトランジスタに置き換えることも可能である。この場合,置き換えられたトランジスタのゲートには,直前走査線Sn・1に流れる選択信号の論理反転信号を入力する。同様に,トランジスタM7をトランジスタM3と同じ導電型のトランジスタに置き換えることも可能である。この場合,置き換えられたトランジスタのゲートには,現在走査線Snに流れる選択信号の論理反転信号を入力する。

[0062]

図9から明らかなように,図1の従来の画素回路によれば,プリチャージ期間 T 1 において,有機 E L 素子 O L E D に大きい電流が流れ,同様にデータ充電期間 T 3 においても有機 E L 素子 O L E D に電流が流れる(図 9 中," 1 0 0 ")。これに対して,図 3 に示した第 1 の実施の形態にかかる画素回路によれば,プリチャージ期間 T 1 において,有機

E L 素子 O L E D に電流が流れない。ただし,データ充電期間 T 3 では有機 E L 素子 O L E D に電流が流れる(図 9 中," 1 1 0 ")。そして,図 8 に示した第 4 の実施の形態にかかる画素回路によれば,プリチャージ期間 T 1 とデータ充電期間 T 3 の両期間において,有機 E L 素子 O L E D に電流が流れない(図 9 中," 1 2 0 ")。

#### [0063]

(第5の実施の形態)

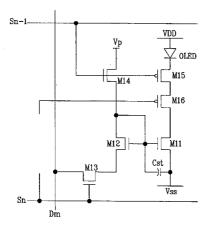

第4の実施の形態にかかる画素回路は,Pチャネル型のトランジスタM1~M4を備えているが,これらをNチャネル型MOSトランジスタに置き換えることも可能である。このような回路構成を有する本発明の第5の実施の形態について,図10および図11を参照しながら詳細に説明する。

[0064]

図 1 0 は,本実施の形態にかかる画素回路の等価回路図であり,図 1 1 は,図 1 0 の画素回路の駆動信号の波形図である。

[0065]

図10に示したように、本実施の形態にかかる画素回路は、図8に示した第4の実施の形態にかかる画素回路に対して、Pチャネル型MOSトランジスタM1~M4がNチャネル型MOSトランジスタM11~M14に置き換えられ、Nチャネル型MOSトランジスタM15、M16に置き換えられた構成を有する。そして、図10に示した本実施の形態にかかる画素回路は、図8に示した第4の実施の形態にかかる画素回路と対称の回路構造を有する。詳しく説明すれば、トランジスタM11は、基準電圧Vssにソースが接続されており、有機EL素子OLEDは、アノードが電源電圧VDDに接続されている。そして、トランジスタM11のドレインの間に直列に接続されている。

[0066]

図11と図4を比較すれば明らかなように、図10に示した本実施の形態にかかる画素回路の駆動信号(図11)は、図8に示した第4の実施の形態にかかる画素回路の駆動信号(図4)を論理反転させたものである。このような駆動信号によって、図10に示した本実施の形態にかかる画素回路は、図8に示した第4の実施の形態にかかる画素回路と略同一に動作する。そして、本実施の形態によれば、第4の実施の形態と同様の効果が得られる。

[0067]

以上,添付図面を参照しながら本発明の好適な実施形態について説明したが,本発明は係る例に限定されない。当業者であれば,特許請求の範囲に記載された範疇内において,各種の変更例または修正例に想到し得ることは明らかであり,それらについても当然に本発明の技術的範囲に属するものと了解される。

[0068]

例えば,第5の形態にかかる画素回路と第4の実施の形態にかかる画素回路との関係のように,構成トランジスタをNチャネル型からPチャネル型に置き換えること,また,Pチャネル型からNチャネル型に置き換えることは,全ての実施の形態に適用可能である。また,上述したトランジスタと実質的に同一の機能を有するものであれば,Pチャネル型とNチャネル型の組み合わせに制限はない。また,MOSトランジスタの他のスイッチング素子を使用して画素回路を実現することもできる。

[0069]

また,有機EL表示装置を例に挙げて本発明の実施の形態を説明したが,本発明は,有機EL素子に限定されず,電流によって光を発光する他の発光表示装置にも適用できる。

【産業上の利用可能性】

[0070]

本発明は,例えば,電圧駆動方式の有機電界発光表示装置に適用可能である。

【図面の簡単な説明】

50

10

20

30

## [0071]

- 【図1】従来の画素回路の等価回路図である。

- 【図2】本発明の実施の形態にかかる有機EL表示装置の概略的な平面図である。

- 【図3】本発明の第1の実施の形態にかかる画素回路の等価回路図である。

- 【図4】図3の画素回路を駆動する駆動信号の波形図である。

- 【図5】本発明の第2の実施の形態にかかる画素回路の等価回路図である。

- 【図6】図5の画素回路を駆動する駆動信号の波形図である。

- 【図7】本発明の第3の実施の形態にかかる画素回路の等価回路図である。

- 【図8】本発明の第4の実施の形態にかかる画素回路の等価回路図である。

- 【図9】図1,図3,図8に示した各画素回路に属する有機 EL素子に流れる電流の特性 を示すグラフである。

- 【図10】本発明の第5の実施の形態にかかる画素回路の等価回路図である。

- 【図11】図10の画素回路を駆動する駆動信号の波形図である。

# 【符号の説明】

## [0072]

10:有機 E L 表示パネル

1 1: 画素回路

2 0 : 走査駆動部

3 0 : データ駆動部

C n : 制御線

D 1 ~ D m : データ線

S 1 ~ S n : 走査線

M 1 ~ M 6 : トランジスタ

V D D : 電源電圧

Cst:キャパシタ

I<sub>O</sub>LE<sub>D</sub>:電流

OLED:有機EL素子

T 1 : プリチャージ期間

T2:ブランキング期間

T 3 : データ充電期間

T 4: 発光期間

Vgs:ゲート-ソース電圧

Vp: プリチャージ用電圧

V s s : 基準電圧

20

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

# 【図10】

# 【図11】

# フロントページの続き

(51) Int.CI.<sup>7</sup> FΙ テーマコード(参考)

> G 0 9 G 3/20 6 4 1 D H 0 5 B 33/14 Α

(72)発明者 郭 源奎

大韓民国京畿道城南市盆唐区九美洞88番地 カチ住公アパート207-903号

(72) 発明者 呉 春烈

大韓民国京畿道軍浦市堂洞886番地 住公アパート310-1202

(72)発明者 梁 善芽

大韓民国京畿道水原市八達区霊通洞(番地なし) ビョクゾクゴル9団地アパート912-110

(72)発明者 柳 道亨

大韓民国釜山市南区ムンヒョン3洞97-1番地 15/5

F ターム(参考) 3K007 AB05 AB17 BA06 DB03 GA00 GA04

5C080 AA06 BB05 DD26 EE29 FF11 JJ02 JJ03 JJ04 JJ05

| 专利名称(译)        | 图像显示面板,图像显示装置,图像显示装置的驱动方法和像素电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |            |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|--|--|

| 公开(公告)号        | <u>JP2004334163A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日            | 2004-11-25 |  |  |

| 申请号            | JP2003337939                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日                | 2003-09-29 |  |  |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |            |  |  |

| 申请(专利权)人(译)    | 三星エスディアイ株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |  |  |

| [标]发明人         | 鄭寶容<br>朴鎔盛<br>郭源奎<br>呉春烈<br>梁善芽<br>柳道亨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |            |  |  |

| 发明人            | 鄭 寶容<br>朴 鎔盛<br>郭 源奎<br>呉 春烈<br>梁 善芽<br>柳 道亨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |            |  |  |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G09G3/32 H05B33/14 |            |  |  |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.611.A G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291 G11C19/28.230                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |            |  |  |

| F-TERM分类号      | 3K007/AB05 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080 /BB05 5C080/DD26 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 3K107 /AA01 3K107/BB01 3K107/CC14 3K107/EE03 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB18 5C380/BA01 5C380/BA10 5C380/BA38 5C380/BA39 5C380/BB08 5C380/BC02 5C380 /BC03 5C380/BC13 5C380/BC15 5C380/CA12 5C380/CA54 5C380/CB01 5C380/CB33 5C380/CC01 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC53 5C380/CC55 5C380 /CC62 5C380/CC63 5C380/CD014 5C380/CD015 5C380/CD016 5C380/DA02 5C380/DA06 5C380 /HA03 5C380/HA05 |                    |            |  |  |

| 优先权            | 1020030027604 2003-04-30 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |            |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |            |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |            |  |  |

# 摘要(译)

要解决的问题:补偿驱动晶体管的阈值电压并防止不必要的电流流过显示元件。 在有机EL显示装置的像素电路中,为了补偿驱动晶体管的阈值电压,驱动晶体管M1的栅极连接至具有二极管结构的补偿晶体管M2的栅极。 在选择信号被传输到紧接在前的扫描线Sn-1的同时,预充电电压被施加到晶体管M1的栅极。 晶体管M5使晶体管M1与有机EL元件电断开,使得有机EL元件OLED由于该预充电电压而不发光。 此外,晶体管M5将有机EL元件与晶体管M1电隔离,使得当在电容器Cst中充电数据电压时有机EL元件不发光。 [选择图]图3