(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-213004

(P2004-213004A)

(43) 公開日 平成16年7月29日(2004.7.29)

(51) Int.Cl.<sup>7</sup>G09F 9/30

H05B 33/06

H05B 33/10

H05B 33/14

F 1

G09F 9/30

G09F 9/30

H05B 33/06

H05B 33/10

H05B 33/14

テーマコード(参考)

3K007

5C094

審査請求 有 請求項の数 25 O L (全 32 頁)

(21) 出願番号 特願2003-433282 (P2003-433282)

(22) 出願日 平成15年12月26日 (2003.12.26)

(31) 優先権主張番号 2002-086106

(32) 優先日 平成14年12月28日 (2002.12.28)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー・フィリップス エルシーデー

カンパニー、リミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100091889

弁理士 藤野 育男

最終頁に続く

(54) 【発明の名称】デュアルパネルタイプ有機電界発光素子及びその製造方法

## (57) 【要約】

【課題】 生産收率が向上された高解像度 / 高開口率構造アクティブマトリックス型有機電界発光素子を提供する。

【解決手段】 アレイ素子と有機電界発光ダイオードを相互に異なる基板に形成して、アレイ素子の駆動薄膜トランジスタと、有機電界発光ダイオード素子の第2電極を別途の電気的連結電極を通じて連結したデュアルパネルタイプ (Dual Panel Type) 有機電界発光素子とする。また、非晶質シリコン物質を利用する逆スタッガード型 (Inverted Staggered Type) 薄膜トランジスタ構造の採択によって、少ないマスク工程の数で製作されたデュアルパネルタイプ有機電界発光素子用の下部基板を実現する。

【選択図】 図7

## 【特許請求の範囲】

## 【請求項 1】

第1基板上に第1方向へ形成されたゲート配線と；

前記第1基板の上部に第1方向と垂直な第2方向へ形成されたデータ配線と；

前記第1基板の上部に第2方向へ前記ゲート配線と同一物質、同一工程により形成され、前記データ配線及びゲート配線と共に画素領域を定義する電力供給配線と；

前記データ配線と同一物質で、ゲート配線を横切るように形成され、前記電力供給配線を連結する第1リンク配線と；

前記ゲート配線及びデータ配線の交差領域の第1基板の上部に形成されたスイッチング薄膜トランジスタと；

前記ゲート配線及び電力供給配線の交差領域の第1基板の上部に形成された駆動薄膜トランジスタと；

第2基板上の画素領域に対応するように形成された有機電界発光ダイオードと；

絶縁物質であって、前記第1基板の上部の画素領域に形成された連結パターンと；

前記連結パターンが形成された第1基板の上部の画素領域に形成され、前記駆動薄膜トランジスタと有機電界発光ダイオードを電気的に連結する連結電極と；

前記連結電極と同一物質、同一工程でゲート配線の周りに形成されて、前記第1リンク配線と共に前記電力供給配線を連結する第2リンク配線と；

前記電力供給配線を前記駆動薄膜トランジスタと連結するパワー電極を含むデュアルパネルタイプ有機電界発光素子。

10

20

30

40

## 【請求項 2】

前記ゲート配線、データ配線、電力供給配線の一端に各々ゲートパッド、データパッド、電力供給パッドをさらに含むことを特徴とする請求項1に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 3】

前記ゲートパッド、データパッド、電力供給パッドを覆う領域で、前記連結電極と同一工程、同一物質で構成されて、ゲートパッド、データパッド及び電力供給パッドと各々連結されるゲートパッド電極、データパッド電極及び電力供給パッド電極をさらに含むことを特徴とする請求項2に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 4】

純粋非晶質シリコンで構成された第1パターンと、不純物非晶質シリコンで構成された第2パターンを含み、かつ前記データパッドの下部に形成された半導体パターンをさらに含むことを特徴とする請求項2に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 5】

前記パワー電極は、前記連結電極と同一物質、同一工程により形成されることを特徴とする請求項1に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 6】

前記スイッチング薄膜トランジスタには、前記ゲート配線から分岐されたスイッチング用ゲート電極と、前記ゲート電極を覆う領域に位置して純粋非晶質シリコン物質で構成されたアクティブ層及び不純物非晶質シリコン物質で構成されたオーミックコンタクト層の積層構造で構成されたスイッチング用半導体層と、前記スイッチング用半導体層の上部で、相互離隔されるように位置するスイッチング用ソース電極及びスイッチング用ドレイン電極とを含むことを特徴とする請求項1に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 7】

前記スイッチング用ドレイン電極であって、前記電力供給配線の上部へ延長して形成されたキャパシター電極をさらに含むことを特徴とする請求項6に記載のデュアルパネルタイプ有機電界発光素子。

## 【請求項 8】

前記駆動薄膜トランジスタには、前記スイッチング用ドレイン電極と連結される駆動用

50

ゲート電極と、前記駆動用ゲート電極を覆う位置にある駆動用半導体層と、前記駆動用半導体層の上部で、相互に離隔されるように位置する駆動用ソース電極及び駆動用ドレイン電極とを含むことを特徴とする請求項7に記載のデュアルパネルタイプ有機電界発光素子。

【請求項9】

前記キャパシター電極、データ配線、スイッチング用ソース電極及びスイッチング用ドレイン電極、駆動用ソース電極及び駆動用ドレイン電極の下部に純粋非晶質シリコンと不純物非晶質シリコンの二重層構造で形成された半導体層をさらに含むことを特徴とする請求項8に記載のデュアルパネルタイプ有機電界発光素子。

【請求項10】

前記駆動用半導体層は、純粋非晶質シリコン物質で構成されたアクティブ層と不純物非晶質シリコン物質で構成されたオーミックコンタクト層の二重構造になっていることを特徴とする請求項9に記載のデュアルパネルタイプ有機電界発光素子。

【請求項11】

基板上に第1金属層を形成しパターニングして、ゲート電極、ゲート配線、電力供給配線、ゲートパッド、電力供給パッドを形成する段階と；

前記パターニングされた第1金属層の上部に、第1絶縁膜を形成する段階と；

純粋非晶質シリコン物質で構成されたアクティブ層と不純物非晶質シリコン物質で構成されたオーミックコンタクト層とで構成された半導体層をゲート電極の上部の第1絶縁膜上に形成する段階と；

第2金属層を利用してオーミックコンタクト層の上部に相互に離隔されたソース電極及びドレイン電極を形成して、第1絶縁膜上にデータ配線、データパッドとゲート配線を横切る第1リンク配線を形成する段階と；

前記ソース電極及びドレイン電極の間に露出されたオーミックコンタクト層をエッチングして、前記アクティブ層にチャンネルを形成して、ゲート電極、半導体層、ソース電極及びドレイン電極を含む薄膜トランジスタを完成する段階と；

前記薄膜トランジスタ、データ配線、データパッドを覆うように、第1絶縁膜の上部に第2絶縁膜を形成する段階と；

前記第1絶縁膜及び第2絶縁膜をエッチングして、前記第2絶縁膜を貫通するソースコンタクトホール、ドレインコンタクトホール、データパッドコンタクトホールを形成して、共に前記第1絶縁膜及び第2絶縁膜を貫通するゲートパッドコンタクトホール及び電力供給配線コンタクトホールを形成する段階と；

絶縁物質を利用して、前記第2絶縁膜上の画素領域に柱形状の連結パターンを形成する段階と；

第3金属物質を利用して前記連結パターンを覆い、ドレインコンタクトホールを通じてドレイン電極と連結される連結電極と、前記ソースコンタクトホールを通じてソース電極と連結されて、前記薄膜トランジスタを電力供給配線に連結するパワー電極と、前記ゲート配線の周りで、第1リンク配線と共に電力供給配線を連結する第2リンク配線と、前記データパッドの上部で、データパッドコンタクトホールを通じて、これと接触するデータパッド電極と、前記データパッドの上部で、ゲートパッドコンタクトホールを通じて、これと接触するゲートパッド電極と、電力供給パッドの上部で、電力供給パッドコンタクトホールを通じて、これと接触する電力供給パッド電極を形成する段階を含むデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項12】

前記ゲート配線及び電力供給配線を形成する段階は第1マスクを利用して行い、前記半導体層を形成する段階は第2マスクを利用して行い、前記ソース電極及びドレイン電極を形成する段階は第3マスクを利用して行い、前記ソースコンタクトホール及びドレインコンタクトホールを形成する段階は第4マスクを利用して行い、前記連結パターンを形成する段階は第5マスクを利用して行い、前記連結電極を形成する段階は第6マスクを利用して行うことを特徴とする請求項11に記載のデュアルパネルタイプ有機電界発光素子の製

10

20

30

40

50

造方法。

【請求項 1 3】

前記ソース電極及びドレイン電極を形成する段階は、電力供給配線の上部に、キャパシター電極を形成する段階を含み、前記キャパシター電極は、前記電力供給配線及びこれらの間に介在された第1絶縁膜及び第2絶縁膜と共にストレージキャパシターを構成することを特徴とする請求項11に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項 1 4】

他の基板上に有機電界発光ダイオードを形成する段階を含み、前記連結電極は、前記薄膜トランジスタと前記有機電界発光ダイオードを電気的に連結することを特徴とする請求項11に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

10

【請求項 1 5】

前記ゲート配線は、基板上に第1方向へ形成されて、前記データ配線と電力供給配線は、相互に離隔し前記第1方向と垂直に第2方向へ形成されて画素領域を定義することを特徴とする請求項11に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項 1 6】

前記連結パターンのための絶縁物質は、有機絶縁物質であることを特徴とする請求項11に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項 1 7】

基板上に第1金属層を形成しパターニングして、ゲート電極、ゲート配線、電力供給配線、ゲートパッド、電力供給パッドを形成する段階と；

20

前記パターニングされた第1金属層の上部に第1絶縁膜、純粋非晶質シリコン、不純物非晶質シリコン、第2金属層を順に積層する段階と；

前記第2金属層上に感光性フォトレジストを形成する段階と；

前記感光性フォトレジストの上部に、半透過部を持つマスクを位置させる段階と；

前記マスクを通じた回折露光法を利用して、前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングして、アクティブ層、オーミックコンタクト層、ソース電極及びドレイン電極、データ配線、第1リンク配線、データパッドを形成する段階と；

前記ソース電極及びドレイン電極の間に露出されたオーミックコンタクト層をエッチングして、前記アクティブ層にチャンネルを形成して、ゲート電極、半導体層、ソース電極及びドレイン電極を含む薄膜トランジスタを完成する段階と；

30

前記薄膜トランジスタ、データ配線、データパッドを覆うように、第1絶縁膜の上部に第2絶縁膜を形成する段階と；

前記第1絶縁膜及び第2絶縁膜をエッチングして、前記第2絶縁膜を貫通するソースコンタクトホール、ドレインコンタクトホール、データパッドコンタクトホールを形成して、共に前記第1絶縁膜及び第2絶縁膜を貫通するゲートパッドコンタクトホール及び電力供給配線コンタクトホールを形成する段階と；

絶縁物質を利用して、前記第2絶縁膜上の画素領域に柱形状の連結パターンを形成する段階と；

第3金属物質を利用して前記連結パターンを覆い、ドレインコンタクトホールを通じてドレイン電極と連結される連結電極と、前記ソースコンタクトホールを通じてソース電極と連結されて、前記薄膜トランジスタを電力供給配線に連結するパワー電極と、前記ゲート配線の周りで、第1リンク配線と共に電力供給配線を連結する第2リンク配線と、前記データパッドの上部で、データパッドコンタクトホールを通じて、これと接触するデータパッド電極と、前記ゲートパッドの上部で、ゲートパッドコンタクトホールを通じて、これと接触するゲートパッド電極と、電力供給パッドの上部で、電力供給パッドコンタクトホールを通じて、これと接触する電力供給パッド電極を形成する段階を含むデュアルパネルタイプ有機電界発光素子の製造方法。

40

【請求項 1 8】

前記ゲート配線及び電力供給配線を形成する段階は第1マスクを利用して行い、前記純

50

粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は第2マスクを利用して行い、前記ソースコンタクトホール及びドレインコンタクトホールを形成する段階は第3マスクを利用して行い、前記連結パターンを形成する段階は第4マスクを利用して行い、前記連結電極を形成する段階は第5マスクを利用して行うことの特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項19】

前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は、電力供給配線の上部に、キャパシター電極を形成する段階を含むことを特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項20】

前記キャパシター電極は、前記電力供給配線及びこれらの間に介在された第1絶縁膜及び第2絶縁膜と共にストレージキャパシターを構成することを特徴とする請求項19に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項21】

前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は、前記データ配線、第1リンク配線、データパッドの下部に、半導体パターン層をさらに形成することを特徴とする請求項19に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項22】

他の基板上に有機電界発光ダイオードを形成する段階をさらに含み、前記連結電極は、前記薄膜トランジスタと前記有機電界発光ダイオードを電気的に連結することを特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項23】

前記ゲート配線は、基板上に第1方向へ形成されて、前記データ配線と電力供給配線は、相互に離隔され前記第1方向と垂直に第2方向へ形成され画素領域を定義することを特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項24】

前記連結パターンのための絶縁物質は、有機絶縁物質であることを特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【請求項25】

前記感光性フォトレジストは露光された所が現像工程により除去されるポジティブタイプであることを特徴とする請求項17に記載のデュアルパネルタイプ有機電界発光素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は有機電界発光素子(Organic Electroluminescent Device)に係り、特に、デュアルパネルタイプのアクティブマトリックス型有機電界発光素子(Dual Panel Type Active-Matrix Organic Electroluminescent Device)及びその製造方法に関する。

【背景技術】

【0002】

新たな平板ディスプレー素子のうちの一つである有機電界発光素子は、自己発光型であるために液晶表示装置に比べて視野角、コントラストなどが優秀であり、バックライトが要らないために軽量薄形が可能であって、消費電力側面でも有利である。そして、直流低電圧駆動が可能であって応答速度が速くて、全部固体であるために外部衝撃に強くして使用温度範囲も広い。さらに製造費用の面でも低廉であるという長所がある。

【0003】

前記有機電界発光素子は、液晶表示装置やプラズマ表示装置(PDP)の場合とは異なり工程が非常に単純であるため、蒸着及びカプセル封止装備が製造設備の殆ど全体を占めている。特に、アクティブマトリックス方式においては、画素に印加された電圧がストレー

10

20

30

40

50

ジキャパシター  $C_{st}$  に充電されていて、その次のフレーム信号が印加される時まで電源を印加することによって、ゲート配線の数に関係なく、一画面期間中引き続き駆動することができる。従って、アクティブマトリックス方式によると、低い電流を印加しても同一の輝度を示すので低消費電力、高精細、大型化が可能となる長所がある。

【0004】

以下、このようなアクティブマトリックス型有機電界発光素子の基本的な構造及び動作特性について図面を参照しながら詳しく説明する。

【0005】

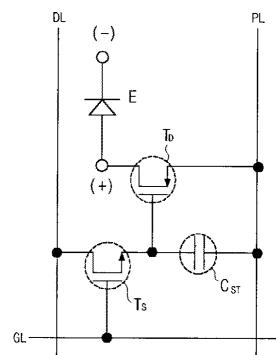

図1は、一般的なアクティブマトリックス型有機電界発光素子の基本画素構造を示した図である。

10

【0006】

図示したように、第1方向へ走査線  $G_L$  が形成されていて、この第1方向と交差する第2方向に相互一定間隔離隔された信号線  $D_L$  及び電力供給線  $P_L$  が形成されていて、一つの画素領域を定義する。

【0007】

前記走査線  $G_L$  及び信号線  $D_L$  の交差地点にはアドレッシングエレメント(Addressing Element)であるスイッチング薄膜トランジスタ  $T_s$  が形成されていて、このスイッチング薄膜トランジスタ  $T_s$  と連結されてストレージキャパシター  $C_{sT}$  が形成されている。前記スイッチング薄膜トランジスタ  $T_s$  及びストレージキャパシター  $C_{sT}$  の連結部と電力供給線  $P_L$  と連結されて、電流源エレメントである駆動薄膜トランジスタ  $T_D$  が形成されている。この駆動薄膜トランジスタ  $T_D$  には、有機電界発光ダイオード  $E$  の陽極(+)が連結されていて、陽極(+)は、定電流駆動方式の有機電界発光ダイオード  $E$  の陰極(-)と連結されている。前記有機電界発光ダイオード  $E$  の陽極(+)及び陰極(-)は有機電界発光ダイオード  $E$  を構成する。

20

【0008】

前記スイッチング薄膜トランジスタ  $T_s$  は電圧を制御して、ストレージキャパシター  $C_{sT}$  は電流源を貯蔵する役割をする。

【0009】

以下、前記アクティブマトリックス型有機電界発光素子の駆動の原理に関して説明する。

30

【0010】

前記アクティブマトリックス方式では、選択信号により該当電極に走査信号を印加するとスイッチング薄膜トランジスタ  $T_s$  がオン状態になり、信号線  $S_L$  のデータ信号がこのスイッチング薄膜トランジスタ  $T_s$  を通過して、駆動薄膜トランジスタと  $T_D$ 、ストレージキャパシター  $C_{sT}$  に印加される。駆動薄膜トランジスタ  $T_D$  がオン状態になると、電源供給線から電流が駆動薄膜トランジスタ  $T_D$  を通じて有機電界発光ダイオード  $E$  に印加されて発光する。この時、前記データ信号の大きさにより駆動薄膜トランジスタ  $T_D$  のゲートの開閉程度が違って、駆動薄膜トランジスタ  $T_D$  を通じて流れる電流量を調節するようになり、階調の表示ができる。そして、非選択区間には、ストレージキャパシター  $C_{sT}$  に充填されたデータが駆動薄膜トランジスタ  $T_D$  に引き続き印加され、次の画面の信号が印加されるまで、持続的に有機電界発光ダイオード  $E$  を発光させることができる。

40

【0011】

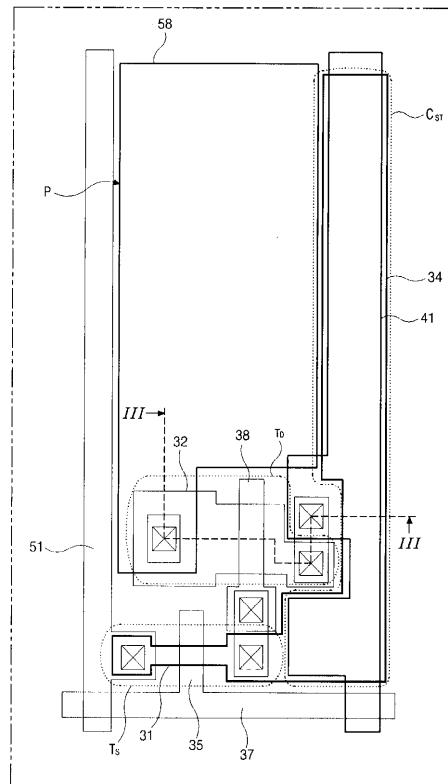

図2は、従来のアクティブマトリックス型有機電界発光素子の一画素部に関する平面図であって、スイッチング薄膜トランジスタと駆動薄膜トランジスタを各々一つずつ持つ2 TFT構造を一例として説明する。

【0012】

図示したように、第1方向へゲート配線  $3_7$  が形成されていて、ゲート配線  $3_7$  と交差するようにデータ配線  $5_1$  及び電力供給配線  $4_1$  が形成されている。前記ゲート配線  $5_1$  と電力供給配線  $4_1$  は、相互に離隔されゲート配線  $3_7$  と共に画素領域  $P$  を定義する。すなわち、ゲート配線  $3_7$  及びデータ配線  $5_1$ 、電力供給配線  $4_1$  の相互交差領域は画素領

50

域 P を構成する。

【 0 0 1 3 】

前記ゲート配線 3 7 及びデータ配線 5 1 の交差領域には、スイッチング薄膜トランジスタ T<sub>s</sub> が位置しており、ゲート配線 3 7 及び電力供給配線 4 1 の交差領域には、駆動薄膜トランジスタ T<sub>D</sub> が位置する。前記スイッチング薄膜トランジスタ T<sub>s</sub> の半導体層 3 1 と一体形で形成されたキャパシター電極 3 4 が電力供給配線 4 1 の上部へ延長して形成されている。前記キャパシター電極 3 4 と上部の電力供給配線 4 1 はストレージキャパシタ - C<sub>ST</sub> を構成する。

【 0 0 1 4 】

前記駆動薄膜トランジスタ T<sub>D</sub> と連結され第 1 電極 5 8 が形成されていて、図面に示してはいるが、第 1 電極 5 8 を覆う領域には、有機電界発光層及び第 2 電極が順に形成される。前記第 1 電極 5 8 の形成部は、画素領域 P として定義される。また、駆動薄膜トランジスタ T<sub>D</sub> は、駆動用半導体層 3 2 及び駆動用ゲート電極 3 8 を含み、スイッチング薄膜トランジスタ T<sub>s</sub> もスイッチング用半導体層 3 1 及びスイッチング用ゲート電極 3 5 を含む。

【 0 0 1 5 】

以下、前記有機電界発光部、駆動薄膜トランジスタ T<sub>D</sub>、ストレージキャパシタ - C<sub>ST</sub> の積層構造を図面を参照しながら、詳しく説明する。

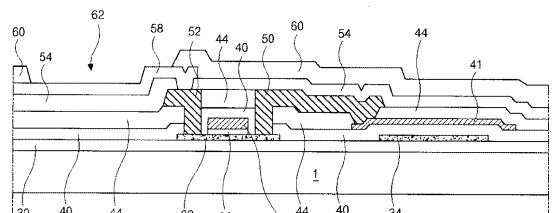

【 0 0 1 6 】

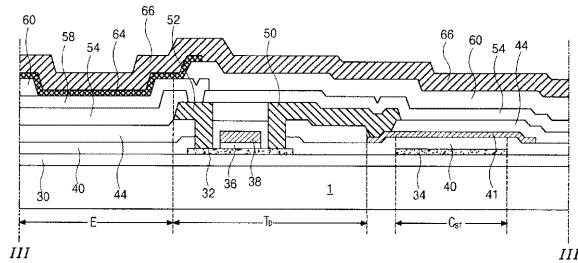

図 3 は、前記図 2 の III - III 線に沿って切断した断面を示した図である。

図示したように、半導体層 3 2 、ゲート電極 3 8 、ソース電極 5 0 及びドレイン電極 5 2 とで構成された駆動薄膜トランジスタ T<sub>D</sub> が絶縁基板 1 上に形成されていて、前記ソース電極 5 0 には、電力供給配線 4 1 が連結されていて、前記ドレイン電極 5 2 には、透明導電性物質で構成された第 1 電極 5 8 が連結されている。

【 0 0 1 7 】

前記電力供給配線 4 1 と対応する下部には、前記半導体層 3 2 と同一物質で構成されたキャパシター電極 3 4 が形成されていて、電力供給配線 4 1 及びキャパシター電極 3 4 が重なる領域はストレージキャパシタ - C<sub>ST</sub> を構成する。そして、前記第 1 電極 5 8 の上部には、有機電界発光層 6 4 及び不透明金属物質で構成される第 2 電極 6 6 が順に積層され、有機電界発光部 E を構成する。前記有機電界発光部 E で、第 1 電極 5 8 は陽極としての役割をし、第 2 電極 6 6 は陰極としての役割をする。

【 0 0 1 8 】

前記有機電界発光部 E に位置する絶縁層等の積層構造をみると、前記絶縁基板 1 と半導体層 3 2 の間で緩衝作用をするバッファ層 3 0 が位置しており、前記ストレージキャパシタ - C<sub>ST</sub> 用絶縁体として利用される第 1 保護層 4 0 がキャパシター電極 3 4 と電力供給配線 4 1 の間に位置する。また、ゲート電極 3 8 と半導体層 3 2 の間には、ゲート絶縁膜 3 6 が位置しており、前記ソース電極 5 0 と電力供給配線 4 1 の間に第 2 保護層 4 4 が位置する。前記第 1 電極 5 8 とドレイン電極 5 2 の間には、第 3 保護層 5 4 が介在されていて、前記第 1 電極 5 0 と第 2 電極 6 6 の間には、第 4 保護層 6 0 が介在されている。前記第 1 保護層 4 0 、第 2 保護層 4 4 、第 3 保護層 5 4 、第 4 保護層 6 0 には、それぞれ各伝導体等の間の電気的連結のため、コンタクトホールが形成されている。

【 0 0 1 9 】

図 4 A ないし図 4 I は、前記図 2 の III - III 線に沿って切断した断面を製造工程別に各々示した図である。各々の構成層等は、感光性物質であるフォトレジスト ( P R ) を利用したフォトエッチング工程によりパターニングして形成されており、以下の図 4 A ないし図 4 I では、このような一連のパターニング工程を工程順に説明する。

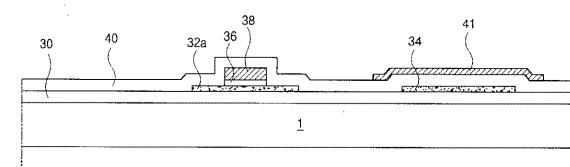

【 0 0 2 0 】

図 4 A では、絶縁基板 1 上に、第 1 絶縁物質を利用してバッファ層 3 0 を基板全面にかけて形成して、このバッファ層 3 0 の上部に、ポリシリコン層を形成し、第 1 マスク工程によりポリシリコン層をパターニングしてアクティブ層 3 2 及びキャパシター電極 3 4 を

10

20

30

40

50

形成する。

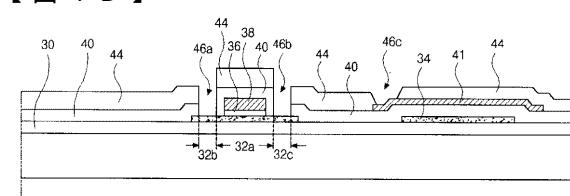

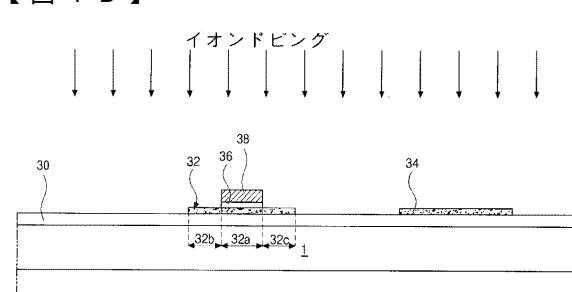

【0021】

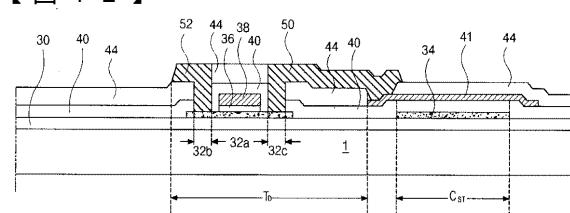

図4Bでは、前記図4Aの段階を経た基板上に、第2絶縁物質及び第1金属を連続的に蒸着した後、第2マスク工程により前記アクティブ層32の中央部に各々ゲート絶縁膜36及びゲート電極38が形成される。

【0022】

このようなゲート絶縁膜36及びゲート電極38を形成した以後には、前記アクティブ層32の露出された両端部及びキャパシター電極34にイオンドーピング(Ion Doping)処理をする。このイオンドーピング処理された部分は、不純物が含まれたポリシリコン層になり、不純物が含まれたアクティブ層はドレイン領域32b及びソース領域32cとして定義される。また、このイオンドーピング工程で、前記ゲート電極38はイオンストッパー(Ion Stopper)としての役割を行ない、下部のアクティブ層32にアクティブ領域32aを構成する。従って、前記アクティブ層32は、不純物がドーピングされてないアクティブ領域32aと、アクティブ領域32aの右左に不純物がドーピングされたドレイン領域32b及びソース領域32cを持つ。

【0023】

図4Cでは、前記図4Bの段階を経た基板上に、第3絶縁物質で構成された第1保護層40を形成する。この第1保護層40の上部に、第2金属を蒸着した後、第3マスク工程により前記キャパシター電極34を覆う位置に電力供給配線41を形成する。

【0024】

図4Dでは、前記図4Cの段階を経た基板上に、第4絶縁物質を蒸着する。そして、第4マスク工程により前記アクティブ領域32aの両端部であるドレイン領域32b及びソース領域32cを露出する第1コンタクトホール46a及び第2コンタクトホール46Bを形成すると同時に、電力供給配線41の一部を露出する第3コンタクトホール46cを形成する。前記アクティブ領域32aの両端部には、以後の工程で形成されるソース電極及びドレイン電極と連結されるようにするため、第1コンタクトホール46a及び第2コンタクトホール46bを形成した。

【0025】

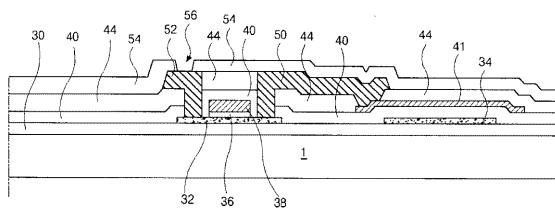

図4E段階では、第3金属を蒸着した後、第5マスク工程により前記第3コンタクトホール(図4Dの46c)及び第2コンタクトホール(図4Dの46b)を通じて、電力供給配線41及びソース領域32cと連結されるソース電極50を形成すると同時に、このソース電極50と一定間隔離隔させて、第1コンタクトホール(図4Dの46a)を通じて、ドレイン領域32bと連結されるドレイン電極52を形成する。従って、この段階では、前記半導体層32、ゲート電極38、ソース電極50及びドレイン電極52を含む駆動薄膜トランジスタT<sub>D</sub>が完成される。

【0026】

一方、前記キャパシター電極34は、図示していないスイッチング薄膜トランジスタT<sub>S</sub>の半導体層と電気的に連結されて、前記第1保護層40を絶縁体にして、上部の電力供給配線41と共にストレージキャパシターC<sub>ST</sub>を形成する。

【0027】

図4Fでは、前記図4Eの段階を経た基板上に、第5絶縁物質を蒸着して第3保護層54を形成する。そして、第6マスク工程によりドレイン電極52の一部を露出させるドレインコンタクトホール56を形成する。

【0028】

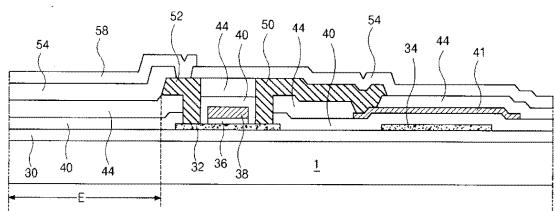

図4G段階では、前記ドレインコンタクトホール(図4Fの56)を通じて、ドレイン電極52と連結されるように透明導電性物質を蒸着して、これを第7マスク工程によりパターニングする。それ故に、有機電界発光部Eに透明な第1電極58を形成する。

【0029】

図4Hでは、前記図4Gの段階を経た基板上に、第6絶縁物質を蒸着して第4保護層60を形成する。以後第8マスク工程により前記有機電界発光部Eと対応して、第1電極5

10

20

30

40

50

8を露出させる電極露出部62を第4保護層60に形成する。この第4保護層60は、駆動薄膜トランジスタT Dを水分及び異物質から保護する役割をする。

#### 【0030】

これによって、マスク工程が伴う製造工程は終了し、続いて図4I段階では、前記電極露出部(図4Hの62)を通じて第1電極58と連結される有機電界発光層64と、この有機電界発光層64の上部に第4金属を利用して第2金属66を基板全面にかけて形成する。

#### 【0031】

前記第1電極58が陽極として利用される場合、第2電極は前記有機電界発光層64から放出される光を第1電極58へ反射させて、有機電界発光素子の画面を具現しなければならないので、第4金属は反射特性の優れた電子を簡単に出せる仕事関数(Work Function)値の低い金属物質のうちから選択する。

#### 【0032】

以下、従来の有機電界発光素子パネルの積層構造を図面を参照しながら、詳しく説明する。

#### 【0033】

図5は、従来の有機電界発光素子の全体断面図であって、有機電界発光部と駆動薄膜トランジスタの連結部を中心にカプセル化(Encapsulation)構造を持つ有機電界発光素子に関する示した。

#### 【0034】

図示したように、相互に一定間隔離隔されるように第1基板70及び第2基板90が配置されていて、第1基板70の内部面には、画面を具現する最小単位であるサブピクセル(Sub-Pixel)単位で形成された駆動薄膜トランジスタT Dを含むアレイ素子層80が形成されている。アレイ素子層80の上部には、駆動薄膜トランジスタT Dと連結されサブピクセル単位で第1電極72が形成されていて、第1電極72の上部には、サブピクセル単位で赤、緑、青のカラーを発光させる有機電界発光層74が形成されていて、有機電界発光層74の上部全面には、第2電極76が形成されている。

#### 【0035】

前記第1電極72及び第2電極76と、これらの間に介在された有機電界発光層74は、有機電界発光ダイオードEを構成する。有機電界発光層74から発光された光は第1電極72の方へ発光されるので、図5に示した有機電界発光素子は、下部発光方式(Bottom Emission Type)であることを特徴とする。

#### 【0036】

そして、前記第2基板90は、カプセル化基板として利用されて、このような第2基板90の内部中央部には、凹部92が形成されていて、凹部92内には、外部からの水分を遮断して、有機電界発光ダイオードEを保護するための吸湿剤94が封入されている。

#### 【0037】

前記吸湿剤94が封入された第2基板90の内部面と第2電極76は相互に一定間隔離隔されるように位置する。そして、前記第1基板70及び第2基板90の端は、シールパターン(Seal Pattern)85によりカプセル化されている。

#### 【0038】

このように、既存の下部発光方式の有機電界発光素子は、アレイ素子及び有機電界発光ダイオードEが形成された基板とは別途のカプセル化用基板の合着を通じて素子を制作した。この場合、アレイ素子の収率と有機電界発光ダイオードEの収率の倍が有機電界発光素子の収率を決めるので、既存の有機電界発光素子構造では、後半工程に当たる有機電界発光ダイオードEの形成工程により全体の工程収率が大変限られる問題があった。例えば、アレイ素子が良好に形成されたとしても、1,000程度の薄膜を使用する有機電界発光層の形成時に異物やまた他の要素により不良が発生すると、有機電界発光素子は全体的に不良等級に定められる。これによって、良品のアレイ素子を製造するのにかかる諸般経

10

20

30

40

50

費及び材料費の損失が生じて、結果的には非効率的で生産収率が低下する問題があった。そして、下部発光方式は、カプセル化による安定性及び工程の自由度が高い特徴を持つ反面、開口率が限られていて、高解像度製品に適用し難い問題がある。下部発光方式と異なる上部発光方式は、薄膜トランジスタの設計が容易で、開口率が向上して、製品の寿命側にとっては有利であるが、既存の上部発光方式構造では、有機電界発光層の上部に、通常に陰極があるので、材料選択の幅が狭く、透過度が限られ光効率が低下する問題があった。また、上部発光方式では、光透過度の低下を最小化するために、薄膜型保護膜を構成する場合、外気を充分に遮断できない問題があった。

【発明の開示】

【発明が解決しようとする課題】

10

【0039】

前記問題点を解決するために、本発明では生産収率が向上された高解像度／高開口率構造アクティブマトリックス型有機電界発光素子を提供する。このために、本発明ではアレイ素子と有機電界発光ダイオードを相互に異なる基板に形成して、アレイ素子の駆動薄膜トランジスタT Dと、有機電界発光ダイオード素子の第2電極を別途の電気的連結電極を通じてデュアルパネルタイプ(Dual Panel Type)有機電界発光素子を提供する。

【0040】

本発明のまた他の特徴は、非晶質シリコン物質を利用する逆スタッガード型(Invetered Staggered Type)薄膜トランジスタ構造の採択によって、少ないマスク工程の数で制作されたデュアルパネルタイプ有機電界発光素子用の下部基板を提供する。

20

【0041】

逆スタッガード型(Invetered Staggered Type)薄膜トランジスタを含んだ工程を行なうと、低温条件下で工程が行われて、電気的連結電極を含む工程を行なっても、既存よりマスク工程の数を減らせる長所がある。

【課題を解決するための手段】

【0042】

前記目的を達成するために、本発明によるデュアルパネルタイプ有機電界発光素子は、第1基板上に第1方向へ形成されたゲート配線と；前記第1基板の上部に第1方向と垂直な第2方向へ形成されたデータ配線と；前記第1基板の上部に第2方向へ前記ゲート配線と同一物質、同一工程により形成され、前記データ配線及びゲート配線と共に画素領域を定義する電力供給配線と；前記データ配線と同一物質で、ゲート配線を横切るように形成され、前記電力供給配線を連結する第1リンク配線と；前記ゲート配線及びデータ配線の交差領域の第1基板の上部に形成されたスイッチング薄膜トランジスタと；前記ゲート配線及び電力供給配線の交差領域の第1基板の上部に形成された駆動薄膜トランジスタと；第2基板上の画素領域に対応するように形成された有機電界発光ダイオードと；絶縁物質であって、前記第1基板の上部の画素領域に形成された連結パターンと；前記連結パターンが形成された第1基板の上部の画素領域に形成され、前記駆動薄膜トランジスタと有機電界発光ダイオードを電気的に連結する連結電極と；前記連結電極と同一物質、同一工程でゲート配線の周りに形成されて、前記第1リンク配線と共に前記電力供給配線を連結する第2リンク配線と；前記電力供給配線を前記駆動薄膜トランジスタと連結するパワー電極を含むことを特徴とする。

30

【0043】

デュアルパネルタイプ有機電界発光素子は、前記ゲート配線、データ配線、電力供給配線の一端に各々ゲートパッド、データパッド、電力供給パッドをさらに含むことを特徴とする。デュアルパネルタイプ有機電界発光素子は、前記ゲートパッド、データパッド、電力供給パッドを覆う領域で、前記連結電極と同一工程、同一物質で構成されて、ゲートパッド、データパッド及び電力供給パッドと各々連結されるゲートパッド電極、データパッド電極及び電力供給パッド電極をさらに含むことを特徴とする。デュアルパネルタイプ有機電界発光素子は、純粋非晶質シリコンで構成された第1パターンと、不純物非晶質シリコンで構成された第2パターンを含み、かつ前記データパッドの下部に形成された半導体

40

50

パターンをさらに含む。前記パワー電極は、前記連結電極と同一物質、同一工程により形成される。前記スイッチング薄膜トランジスタには、前記ゲート配線から分岐されたスイッチング用ゲート電極と、前記ゲート電極を覆う領域に位置して純粋非晶質シリコン物質で構成されたアクティブ層及び不純物非晶質シリコン物質で構成されたオーミックコンタクト層の積層構造で構成されたスイッチング用半導体層と、前記スイッチング用半導体層の上部で、相互離隔されるように位置するスイッチング用ソース電極及びスイッチング用ドレイン電極とを含む。前記デュアルパネルタイプ有機電界発光素子は、スイッチング用ドレイン電極であって、前記電力供給配線の上部へ延長して形成されたキャパシター電極をさらに含む。前記駆動薄膜トランジスタには、前記スイッチング用ドレイン電極と連結される駆動用ゲート電極と、前記駆動用ゲート電極を覆う位置にある駆動用半導体層と、前記駆動用半導体層の上部で、相互に離隔されるように位置する駆動用ソース電極及び駆動用ドレイン電極とを含む。前記デュアルパネルタイプ有機電界発光素子は、キャパシター電極、データ配線、スイッチング用ソース電極及びスイッチング用ドレイン電極、駆動用ソース電極及び駆動用ドレイン電極の下部に純粋非晶質シリコンと不純物非晶質シリコンの二重層構造で形成された半導体層をさらに含む。前記駆動用半導体層は、純粋非晶質シリコン物質で構成されたアクティブ層と不純物非晶質シリコン物質で構成されたオーミックコンタクト層の二重構造になっている。

#### 【0044】

本発明によるデュアルパネルタイプ有機電界発光素子の製造方法は、基板上に第1金属層を形成しパターニングして、ゲート電極、ゲート配線、電力供給配線、ゲートパッド、電力供給パッドを形成する段階と；前記パターニングされた第1金属層の上部に、第1絶縁膜を形成する段階と；純粋非晶質シリコン物質で構成されたアクティブ層と不純物非晶質シリコン物質で構成されたオーミックコンタクト層とで構成された半導体層をゲート電極の上部の第1絶縁膜上に形成する段階と；第2金属層を利用してオーミックコンタクト層の上部に相互に離隔されたソース電極及びドレイン電極を形成して、第1絶縁膜上にデータ配線、データパッドとゲート配線を横切る第1リンク配線を形成する段階と；前記ソース電極及びドレイン電極の間に露出されたオーミックコンタクト層をエッチングして、前記アクティブ層にチャンネルを形成して、ゲート電極、半導体層、ソース電極及びドレイン電極を含む薄膜トランジスタを完成する段階と；前記薄膜トランジスタ、データ配線、データパッドを覆うように、第1絶縁膜の上部に第2絶縁膜を形成する段階と；前記第1絶縁膜及び第2絶縁膜をエッチングして、前記第2絶縁膜を貫通するソースコンタクトホール、ドレインコンタクトホール、データパッドコンタクトホールを形成して、共に前記第1絶縁膜及び第2絶縁膜を貫通するゲートパッドコンタクトホール及び電力供給配線コンタクトホールを形成する段階と；絶縁物質を利用して、前記第2絶縁膜上の画素領域に柱形状の連結パターンを形成する段階と；第3金属物質を利用して前記連結パターンを覆い、ドレインコンタクトホールを通じてドレイン電極と連結される連結電極と、前記ソースコンタクトホールを通じてソース電極と連結されて、前記薄膜トランジスタを電力供給配線に連結するパワー電極と、前記ゲート配線の周りで、第1リンク配線と共に電力供給配線を連結する第2リンク配線と、前記データパッドの上部で、データパッドコンタクトホールを通じて、これと接触するデータパッド電極と、前記データパッドの上部で、ゲートパッドコンタクトホールを通じて、これと接触するゲートパッド電極と、電力供給パッドの上部で、電力供給パッドコンタクトホールを通じて、これと接触する電力供給パッド電極を形成する段階を含むことを特徴とする。

#### 【0045】

前記デュアルパネルタイプ有機電界発光素子の製造方法で、ゲート配線及び電力供給配線を形成する段階は第1マスクを利用して行い、前記半導体層を形成する段階は第2マスクを利用して行い、前記ソース電極及びドレイン電極を形成する段階は第3マスクを利用して行い、前記ソースコンタクトホール及びドレインコンタクトホールを形成する段階は第4マスクを利用して行い、前記連結パターンを形成する段階は第5マスクを利用して行い、前記連結電極を形成する段階は第6マスクを利用して行うことを特徴とする。前記ソ

10

20

30

40

50

ース電極及びドレイン電極を形成する段階は、電力供給配線の上部に、キャパシター電極を形成する段階を含み、前記キャパシター電極は、前記電力供給配線及びこれらの間に介在された第1絶縁膜及び第2絶縁膜と共にストレージキャパシターを構成する。前記デュアルパネルタイプ有機電界発光素子の製造方法で、他の基板上に有機電界発光ダイオードを形成する段階を含み、この時、前記連結電極は、前記薄膜トランジスタと前記有機電界発光ダイオードを電気的に連結する。前記ゲート配線は、基板上に第1方向へ形成されて、前記データ配線と電力供給配線は、相互に離隔し前記第1方向と垂直に第2方向へ形成されて画素領域を定義する。前記連結パターンのための絶縁物質は、有機絶縁物質であることを特徴とする。

## 【0046】

10

本発明のまた他の特徴によるデュアルパネルタイプ有機電界発光素子の製造方法は、基板上に第1金属層を形成しパターニングして、ゲート電極、ゲート配線、電力供給配線、ゲートパッド、電力供給パッドを形成する段階と；前記パターニングされた第1金属層の上部に第1絶縁膜、純粋非晶質シリコン、不純物非晶質シリコン、第2金属層を順に積層する段階と；前記第2金属層上に感光性フォトレジストを形成する段階と；前記感光性フォトレジストの上部に、半透過部を持つマスクを位置させる段階と；前記マスクを通じた回折露光法を利用して、前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングして、アクティブ層、オーミックコンタクト層、ソース電極及びドレイン電極、データ配線、第1リンク配線、データパッドを形成する段階と；前記ソース電極及びドレイン電極の間に露出されたオーミックコンタクト層をエッチングして、前記アクティブ層にチャンネルを形成して、ゲート電極、半導体層、ソース電極及びドレイン電極を含む薄膜トランジスタを完成する段階と；前記薄膜トランジスタ、データ配線、データパッドを覆うように、第1絶縁膜の上部に第2絶縁膜を形成する段階と；前記第1絶縁膜及び第2絶縁膜をエッチングして、前記第2絶縁膜を貫通するソースコンタクトホール、ドレインコンタクトホール、データパッドコンタクトホールを形成して、共に前記第1絶縁膜及び第2絶縁膜を貫通するゲートパッドコンタクトホール及び電力供給配線コンタクトホールを形成する段階と；絶縁物質を利用して、前記第2絶縁膜上の画素領域に柱形状の連結パターンを形成する段階と；第3金属物質を利用して前記連結パターンを覆い、ドレインコンタクトホールを通じてドレイン電極と連結される連結電極と、前記ソースコンタクトホールを通じてソース電極と連結されて、前記薄膜トランジスタを電力供給配線に連結するパワー電極と、前記ゲート配線の周りで、第1リンク配線と共に電力供給配線を連結する第2リンク配線と、前記データパッドの上部で、データパッドコンタクトホールを通じて、これと接触するデータパッド電極と、前記ゲートパッドの上部で、ゲートパッドコンタクトホールを通じて、これと接触するゲートパッド電極と、電力供給パッドの上部で、電力供給パッドコンタクトホールを通じて、これと接触する電力供給パッド電極を形成する段階を含むことを特徴とする。

20

30

30

## 【0047】

40

前記デュアルパネルタイプ有機電界発光素子の製造方法で、ゲート配線及び電力供給配線を形成する段階は第1マスクを利用して行い、前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は第2マスクを利用して行い、前記ソースコンタクトホール及びドレインコンタクトホールを形成する段階は第3マスクを利用して行い、前記連結パターンを形成する段階は第4マスクを利用して行い、前記連結電極を形成する段階は第5マスクを利用して行う。前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は、電力供給配線の上部に、キャパシター電極を形成する段階を含む。前記キャパシター電極は、前記電力供給配線及びこれらの間に介在された第1絶縁膜及び第2絶縁膜と共にストレージキャパシターを構成する。前記純粋非晶質シリコン層、不純物非晶質シリコン層、第2金属層を同時にパターニングする段階は、前記データ配線、第1リンク配線、データパッドの下部に、半導体パターン層をさらに形成する。前記デュアルパネルタイプ有機電界発光素子の製造方法は、他の基板上に有機電界発光ダイオードを形成する段階をさらに含み、前記連結電極は

50

、前記薄膜トランジスタと前記有機電界発光ダイオードを電気的に連結する。前記ゲート配線は、基板上に第1方向へ形成されて、前記データ配線と電力供給配線は、相互に離隔され前記第1方向と垂直に第2方向へ形成され画素領域を定義する。前記連結パターンのための絶縁物質は、有機絶縁物質であることを特徴とする。前記感光性フォトレジストは露光された所が現像工程により除去されるポジティブタイプであることを特徴とする。

【0048】

以下、本発明による望ましい実施例を図面を参照しながら詳しく説明する。

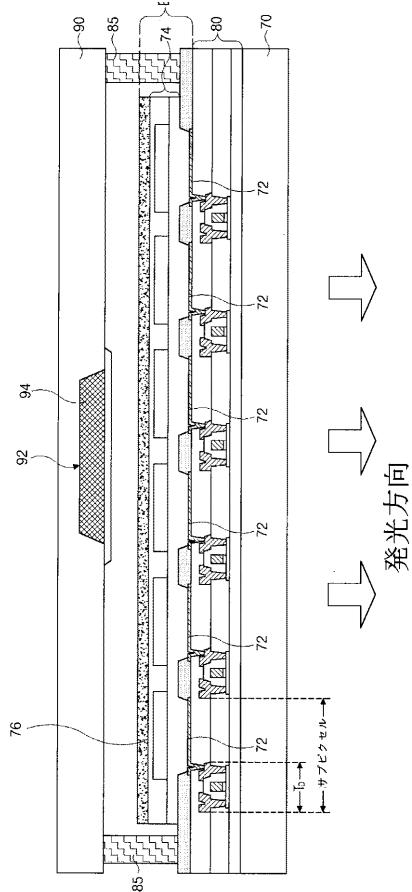

図6は、本発明によるデュアルパネルタイプ有機電界発光素子の断面図であって、上板と下板の電気的連結構造を中心に概略的に示した。

【0049】

図示したように、画面を具現する最小単位であるサブピクセル単位で、第1基板110及び第2基板150が相互に一定間隔を維持しながら対向するように配置されている。

【0050】

前記第1基板110の内部面には、サブピクセル単位で形成された多数個の駆動薄膜トランジスタTDを含むアレイ素子層140が形成されていて、アレイ素子層140の上部には、駆動薄膜トランジスタTDと連結されて電気的連結パターン142が形成されている。

【0051】

前記電気的連結パターン142は、伝導性物質から選択されて、前記電気的連結パターン142は厚く形成するために、絶縁物質を含む多重層で形成されたり、別途の連結電極を通じて駆動薄膜トランジスタTDと連結されたりする。そして、前記駆動薄膜トランジスタTDは、ゲート電極112、半導体層114、ソース電極116及びドレイン電極118とで構成されて、実質的に前述した電気的連結パターン142はドレイン電極118と連結されている。

【0052】

前記第2基板150の内部面には、第1電極152が全面に形成されていて、第1電極152の下部には、サブピクセル単位で繰り返し配置される赤、緑、青の発光層156a, 156b, 156cを含む有機電界発光層160が形成されていて、有機電界発光層160の下部にはサブピクセル単位で第2電極162が形成されている。より詳しくは、前記有機電界発光層160には、第1電極152の下部面と接触される第1キャリア伝達層(First Carrier Transporting Layer)154と、赤、緑、青の発光層156a, 156b, 156cの下部に位置して、第2電極162の上部面と接触される第2キャリア伝達層(Second Carrier Transporting Layer)158がさらに含まれている。

【0053】

一例として、前記第1電極152を陽極、第2電極162が陰極に当たる場合、第1キャリア伝達層154は順に正孔注入層(Hole Injecting Layer)及び正孔輸送層(Hole Transporting Layer)を含み、第2キャリア伝達層158は順に電子輸送層(Electron Transporting Layer)及び電子注入層(Electron Injecting Layer)を含む。そして、前記第1電極152及び第2電極162と、これらの間に介在された有機電界発光層160は有機電界発光ダイオードEを構成する。

【0054】

本発明では、前記電気的連結パターン142の最上部面が第2電極162の下部面と連結され、駆動薄膜トランジスタTDから供給される電流が電気的連結パターン142を通じて第2電極162へ伝達されることを特徴とする。そして、前記第1基板110及び第2基板150の端部には、シールパターン170が位置しており、前記第1基板110及び第2基板150を合着させている。

【0055】

本発明では、有機電界発光ダイオードEとアレイ素子層140を相互に異なる基板に形成するが、電気的連結パターン142を利用して、二つの素子を連結させる方式のデュアルパネルタイプで構成することを特徴とする。

10

20

30

40

50

## 【0056】

図6では、説明の便宜上、三つのサブピクセルが一つのピクセルを構成する2ピクセル構造を一例として図示したが、薄膜トランジスタの構造及び電気的連結パターンの連結方式は多様に変更される。また、本発明によるデュアルパネルタイプ有機電界発光素子は、図面上の発光方向のように、上部発光方式であるために、薄膜トランジスタの設計が容易であり、高開口率／高解像度の具現が可能となる長所がある。

## 【発明の効果】

## 【0057】

以上のように、本発明によるデュアルパネルタイプ有機電界発光素子及びその製造方法によると次のような長所がある。第1に、アレイ素子と有機電界発光ダイオード素子を相互に異なる基板上に形成するために、生産収率及び生産管理効率を向上させて、製品の寿命を伸ばせる。第2に、上部発光方式であるため、薄膜トランジスタの設計がし易くなり、高開口率及び高解像度の具現が可能になる。第3に、非晶質シリコン物質を利用した逆スタッガード型(Invetered Staggered Type)薄膜トランジスタ構造の採択によって低温工程が可能となり、別途の電気的連結パターンを加えたとしても、マスク工程数が少ない製造方法で制作できて、工程単純化を通じて生産収率の高い製品を提供する。

10

## 【実施例1】

## 【0058】

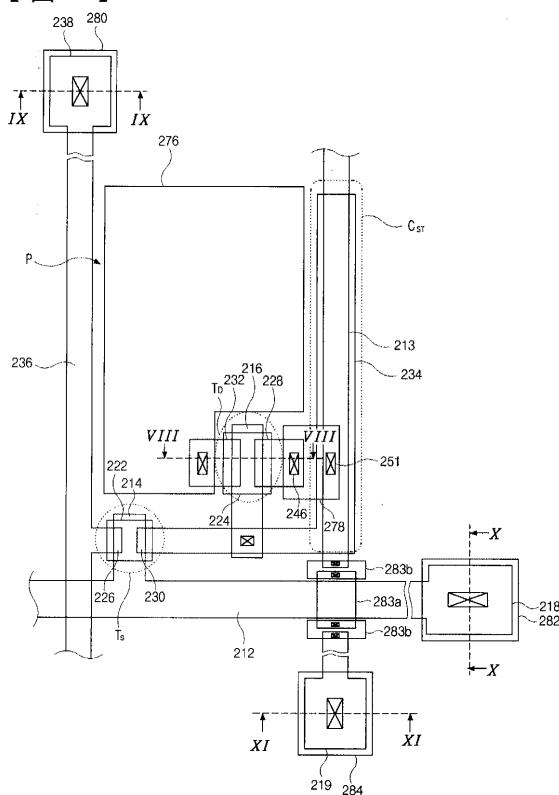

図7は、本発明の実施例1によるデュアルパネルタイプ有機電界発光素子に関する平面図である。

20

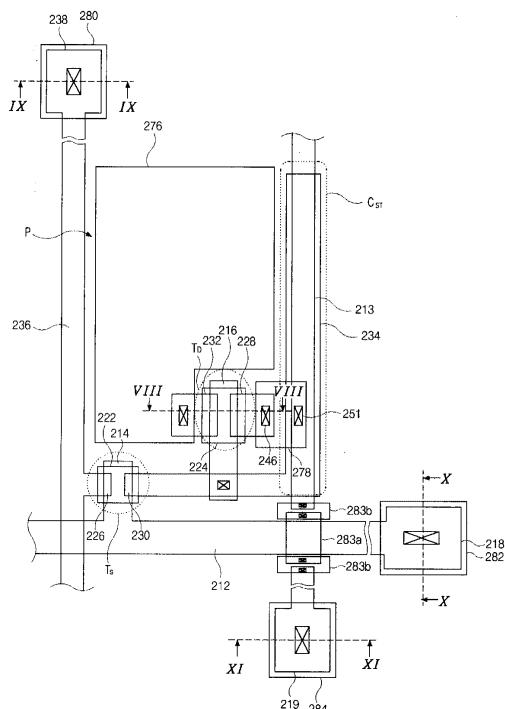

## 【0059】

図示したように、第1方向へゲート配線212が形成されていて、第1方向と交差される第2方向へデータ配線236及び電力供給配線213が相互に離隔して形成されている。ゲート配線212及びこれと交差するデータ配線236及び電力供給配線213は、画素領域Pを定義する。前記ゲート配線212及びデータ配線236の交差地点には、スイッチング薄膜トランジスタTs(Switching Thin Film Transistor)が形成されている。前記スイッチング薄膜トランジスタTsは、ゲート配線212から分岐されたスイッチング用ゲート電極214と、データ配線236から分岐されたスイッチング用ソース電極226と、前記スイッチング用ソース電極226と離隔して配置されたスイッチング用ドレイン電極230と、スイッチング用ゲート電極214を覆う領域に位置したスイッチング用半導体222を含む。

30

## 【0060】

前記電力供給配線213は、ゲート配線212と同一工程、同一物質で構成することを特徴とする。そして、前記スイッチング薄膜トランジスタTs及び電力供給配線213と連結されて、駆動薄膜トランジスタTDが形成されている。前記駆動薄膜トランジスタTDには、前記ゲート配線212と同一工程、同一物質で構成されて、前記スイッチング用ドレイン電極230と連結される駆動用ゲート電極216と、前記駆動用ゲート電極216の両側と一定間隔重なり合い、相互に離隔して配置され、前記データ配線236と同一工程、同一物質で構成された駆動用ソース電極228及び駆動用ドレイン電極232と、前記駆動用ゲート電極216を覆う領域に駆動用半導体層224とが位置する。

40

## 【0061】

前記駆動用ソース電極228とソースコンタクトホール246を通じて連結されたパワー電極278が形成されていて、パワー電極278の一側は電力供給コンタクトホール251を通じて電力供給配線213と連結される。そして、前記駆動用ドレイン電極232と連結され画素領域Pに連結電極276が形成されている。前記パワー電極278及び連結電極276は同一工程、同一物質で構成される。

## 【0062】

前記画素領域Pは、図示していない有機電界発光ダイオードの第2電極と対応する領域に当たる。図面に示してはいるが、前記画素領域Pには、柱形状の電気的連結パターンが含まれており、電気的連結パターンに関しては、断面積層構造を通じてより詳しく説明する

50

。そして、前記スイッチング用ドレイン電極 230 には、前記電力供給配線 213 と重なるように電力供給配線 213 の上部へ連結形成されたキャパシター電極 234 が一体形で連結されていて、前記キャパシター電極 234 及び電力供給配線 213 が重ねる領域はストレージキャパシター  $C_{ST}$  を構成する。

【0063】

前記データ配線 236、ゲート配線 212、電力供給配線 213 の各々の一端には、データパッド 238、ゲートパッド 218、電力供給パッド 219 が形成されていて、前記データパッド 238、ゲートパッド 218、電力供給パッド 219 を覆う位置には、前記連結電極 276 と同一工程、同一物質で構成されたデータパッド電極 280、ゲートパッド電極 282、電力供給パッド電極 284 が各々形成されている。特に、本実施例では、ゲート配線 212 と電力供給配線 213 を同一工程で形成するため、ゲート配線 212、電力供給配線 213 が交差部で短絡されることを防ぐために、電力供給配線 213 はゲート配線 212 の部分を通さずに、その代り、データ配線 236 と同一工程、同一物質で構成された電力供給第1リンク配線 283a をゲート配線 212 との交差するように形成して、電力供給配線 213 の連結配線とする。より詳しくは、前記電力供給第1リンク配線 283a の両側には、連結電極 276 と同一工程、同一物質で構成された電力供給第2リンク配線 283b を形成して、電力供給第2リンク配線 283b を通じて電力供給第1リンク配線 283a と電力供給配線 213 を実質的に連結する。従って、前記画素領域 P に形成された各々の電力供給配線 213 は実質的に相互に連結する。また、前記データパッド 238 及び電力供給パッド 219 は、相互異なる信号電圧が印加されるので、図面のように、相互に逆方向の一端に形成することが望ましい。

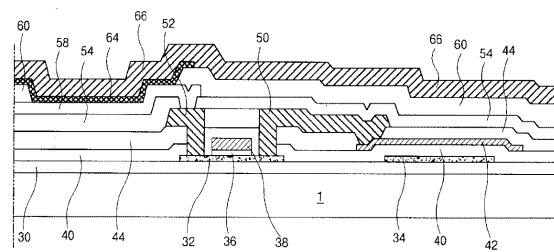

【0064】

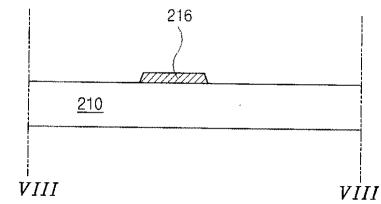

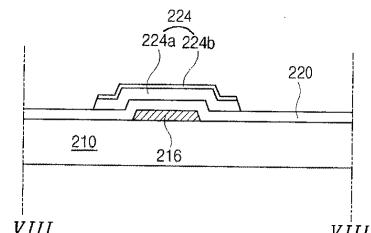

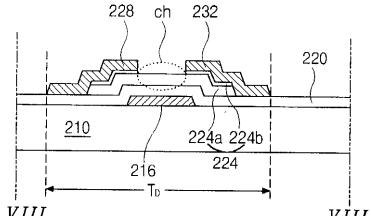

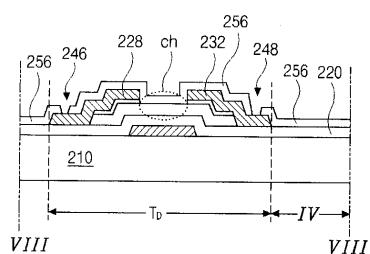

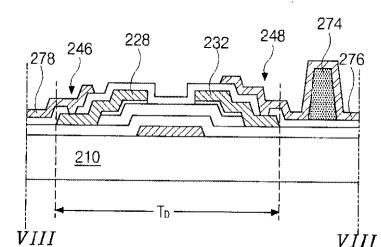

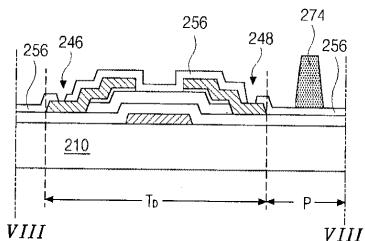

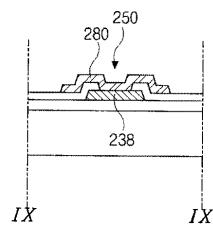

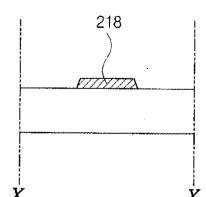

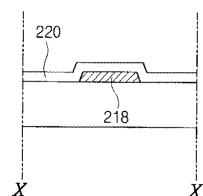

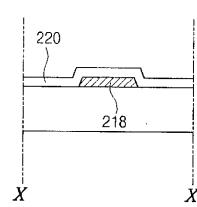

図 8A ないし図 8F、図 9A ないし図 9F、図 10A ないし図 10F 及び図 11A ないし図 11F は、それぞれ前記図 7 の VIII - VIII、IX - IX、X - X 及び XI - XI 線に沿って切断した断面を製造段階別に示した断面図であって、VIII - VIII は駆動用薄膜トランジスタ部、IX - IX はデータパッド部、X - X はゲートパッド部、XI - XI は電力供給パッド部の図である。説明の便宜上、駆動用ゲート電極、駆動用半導体層、駆動用ソース電極及びドレイン電極は、ゲート電極、半導体層、ソース電極及びドレイン電極と略称して説明する。

【0065】

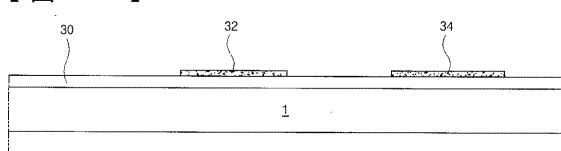

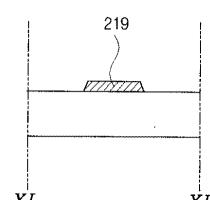

図 8A, 9A, 10A 及び 11A は、基板 210 上に第1金属物質を利用した第1マスク工程により、ゲート電極 216、ゲートパッド 218、電力供給パッド 219 を形成する段階である。図面に示してはないが、この段階では、前記電力供給パッド 219 と一体形で電力供給配線(図 7 の 213)が形成されて、ゲート電極 216 及びゲートパッド 218 と一体形でゲート配線(図 7 の 212)が形成される。

【0066】

前記第1金属物質は、比抵抗が低い金属物質から選択されて、望ましくは、アルミニウムを含む金属物質から選択する。

【0067】

図面に詳しくは示していないが、本発明に利用されるマスク工程は、感光性物質である PR を塗布した後、望むパターンを持つマスクを配置して、露光 - 現像処理を通じて形成された PR パターンをマスクを利用して露出させた被エッチング層をエッチングする方法でパターンングする。

【0068】

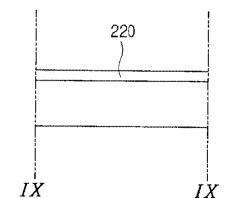

図 8B, 9B, 10B, 11B は、前記ゲート電極 216、ゲートパッド 218、電力供給パッド 219 を覆う領域に、第1絶縁物質であるゲート絶縁膜 220、純粋非晶質シリコン物質(a-Si)、不純物非晶質シリコン物質(n+a-Si)を順に形成した後、前記純粋非晶質シリコン物質(a-Si)及び不純物非晶質シリコン物質(n+a-Si)を第2マスク工程によりパターンングする段階である。このようなパターンングの結果として、ゲート電極 216 を覆う領域のゲート絶縁膜 220 上に半導体層 224 を形成する。

10

20

30

40

50

## 【0069】

前記半導体層224は、純粋非晶質シリコン物質(a-Si)で構成されたアクティブ層224aと、不純物非晶質シリコン物質(n+a-Si)で構成されたオーミックコンタクト層224bを含む。そして、前記第1絶縁物質は、絶縁物質から選択されて、望ましくは、シリコン窒化膜(SiNx)にする。

## 【0070】

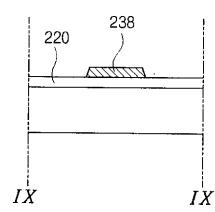

図8C, 9C, 10C, 11Cは、前記半導体層224を覆う領域に第2金属物質を形成した後、第3マスク工程により半導体層224の上部には、相互に離隔されて位置するソース電極228及びドレイン電極232と、データパッド形成部に位置するデータパッド238を形成する段階である。

10

## 【0071】

図面には示していないが、この段階では、第2方向へデータ配線(図7の236)を形成する段階を含み、前記データパッド238は、データ配線の一端部領域に形成される。望ましくは、前記電力供給パッド219と相互に逆方向の一端部に形成される。この段階で、第1リンク配線(図7の283a)はゲート配線212を横切るように形成される。また、図7に示したように、キャパシター電極234をこの段階で形成するが、キャパシター電極234は、スイッチング用ドレイン電極230から延長されて電力供給配線213の上部に形成される。

## 【0072】

前記第2金属物質は、化学的耐食性の強い金属物質から選択されて、望ましくは、モリブデン(Mo)、チタン(Ti)、クロム(Cr)、タンゲステン(W)のうちから選択される。また、この段階では、前記ソース電極228及びドレイン電極232の間区間のオーミックコンタクト層224bを除去して、その下部層を構成するアクティブ層224aを露出させる段階を含み、露出されたアクティブ層224a領域はチャンネル(Ch)を構成する。

20

## 【0073】

前記ゲート電極216、半導体層224、ソース電極228及びドレイン電極232は駆動薄膜トランジスタTDを構成する。

## 【0074】

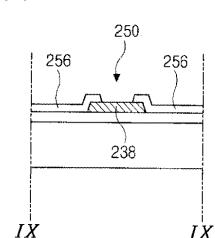

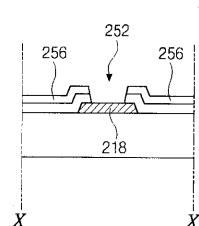

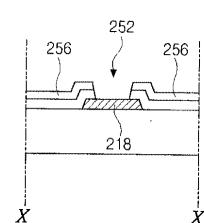

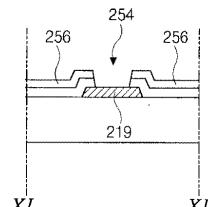

図8D, 9D, 10D, 11Dでは、前記駆動用薄膜トランジスタTD及びデータパッド238、ゲートパッド218、電力供給パッド219を覆う領域に、第2絶縁物質を形成する。第4マスク工程により、前記ソース電極228、ドレイン電極232、データパッド238、ゲートパッド218、電力供給パッド219を各々一部露出させるソースコンタクトホール246、ドレインコンタクトホール248、データパッドコンタクトホール250、ゲートパッドコンタクトホール252、電力供給パッドコンタクトホール254を保護層256に形成する。この時、前記ゲートパッドコンタクトホール252及び電力供給パッドコンタクトホール254は、ゲートパッド218及び電力供給パッド219を覆う領域にゲート絶縁膜220及び保護層256を共通に通過して形成され、ソースコンタクトホール246、ドレインコンタクトホール248及びデータパッドコンタクトホール250は、ただ保護層256だけを通過して形成される。

30

## 【0075】

前記第2絶縁物質は、有機絶縁物質または、無機絶縁物質から選択されて、単一層または、複数層で構成されたりするが、薄膜トランジスタと接する絶縁物質は無機絶縁物質から選択されるのが望ましい。

## 【0076】

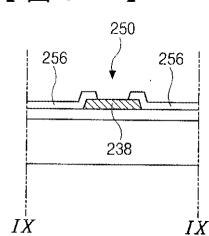

図8E, 9E, 10E, 11Eでは、前記保護層256の上部に第3絶縁物質を形成して、第5マスク工程により、画素領域Pに柱形状の電気的連結パターン274を形成する段階である。前記画素領域Pは、図示していない有機電界発光ダイオードの第2電極と対応する領域に当たる。前記第3絶縁物質は、厚く形成するのに適した有機絶縁物質から選択されるのが望ましい。

40

50

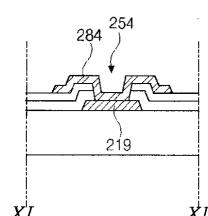

## 【0077】

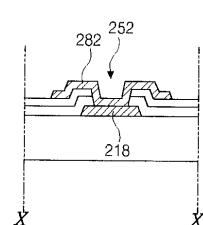

図8F, 9F, 10F, 11Fは、前記電気的連結パターン274を覆う領域に第3金属物質を利用して金属層を形成した後、第5マスク工程により、前記ドレインコンタクトホール248を通じてドレイン電極232と連結され、前記電気的連結パターン274を覆い、画素領域Pに位置する連結電極276を形成する段階である。この時、ソースコンタクトホール246を通じてソース電極228と連結されるパワー電極278と、データパッドコンタクトホール250を通じてデータパッド238と連結されるデータパッド電極280と、ゲートパッドコンタクトホール252を通じてゲートパッド218と連結されるゲートパッド電極282と、電力供給パッドコンタクトホール254を通じて電力供給パッド219と連結される電力供給パッド電極284を形成する。また、この工程において、ゲート配線212の周りに第2リンク配線(図7の283b)を形成して、第2リンク配線は、第1リンク配線と共に電力供給配線213を連結させる役割を行う。図面に示してはいるが、前記パワー電極278はゲート工程で形成された電力供給配線(図7の213)とは別途にコンタクトホールを通じて連結構成される。

10

## 【実施例2】

## 【0078】

図12は、本発明の実施例2によるデュアルパネルタイプ有機電界発光素子に関する平面図である。

図12に示したように、第1方向へゲート配線312が形成されていて、第1方向と交差される第2方向へデータ配線336及び電力供給配線313が相互に離隔して形成されている。前記ゲート配線312及びデータ配線336の交差地点には、スイッチング薄膜トランジスタTsが形成されている。前記スイッチング薄膜トランジスタTsには、ゲート配線312から分岐されたスイッチング用ゲート電極314と、データ配線336から分岐されたスイッチング用ソース電極326と、ソース電極326と離隔して配置されたスイッチング用ドレイン電極330と、スイッチング用ゲート電極314を覆う領域にはスイッチング用半導体322が形成されている。本実施例では、スイッチング用半導体322がスイッチング用ソース電極326の下段部はもちろん、スイッチング用ドレイン電極330の下段部まで延長して形成されている。

20

## 【0079】

前記電力供給配線313は、ゲート配線312と同一工程、同一物質で構成することを特徴とする。電力供給配線313の上部には、スイッチング用ドレイン電極330から延長して形成されたキャパシター電極334が形成されている。キャパシター電極334は、これと重なった電力供給配線313とストレージキャパシターCsTを構成する。また、データ配線336とキャパシター電極334の下段には、半導体パターン321が形成されているが、この半導体パターン321は、ソース電極326及びドレイン電極330の下段に形成された半導体層のような物質で構成されている。このような半導体パターン321は、上部に形成される金属層のような工程によりパターニングされ、上部の金属層のようなパターンを持つ。

30

## 【0080】

前記スイッチング薄膜トランジスタTs及び電力供給配線313と連結されて、駆動薄膜トランジスタTDが形成されている。前記駆動薄膜トランジスタTDは、前記スイッチング用ゲート配線312と同一工程、同一物質で構成されて、前記スイッチング用ドレイン電極330と連結される駆動用ゲート電極316を含み、前記駆動用ゲート電極316の両側と一定間隔重なり合い、相互に離隔して配置され、前記データ配線336と同一工程、同一物質で構成された駆動用ソース電極328及びドレイン電極332を含む。また、駆動薄膜トランジスタTDは、前記駆動用ゲート電極316を覆う領域に駆動用半導体層324が位置する。

40

## 【0081】

前記電力供給配線313と駆動用ソース電極328の間には、ソースコンタクトホール346及び電力供給コンタクトホール351を通じて駆動用ソース電極328及び電力供

50

給配線 313 と連結されるパワー電極 378 が形成されている。パワー電極 378 は、駆動薄膜トランジスタ T D と電力供給配線 313 を連結する役割を行う。そして、前記駆動用ドレイン電極 332 と連結されて、画素領域 P に連結電極 376 が形成されている。前記パワー電極 378 及び連結電極 376 は同一工程、同一物質で構成される。

【 0082 】

前記画素領域 P は、図示していない有機電界発光ダイオードの第 2 電極と対応する領域に当たる。図面に示してはいるが、前記画素領域 P の連結電極 376 の下部には、柱形状の絶縁物質で構成された連結パターンが含まれており、連結パターンに関しては、断面積層構造を通じてより詳しく説明する。

【 0083 】

前記データ配線 336、ゲート配線 312、電力供給配線 313 の各々の一端には、データパッド 338、ゲートパッド 318、電力供給パッド 319 が形成されている。前記データパッド 338、ゲートパッド 318、電力供給パッド 319 を覆う位置には、前記連結電極 376 と同一工程、同一物質で構成されたデータパッド電極 380、ゲートパッド電極 382、電力供給パッド電極 384 が各々形成されている。特に、本実施例では、ゲート配線 312 と電力供給配線 313 を同一工程で形成するため、ゲート配線 312、電力供給配線 313 が交差部で短絡されることを防ぐために、データ配線 336 と同一工程、同一物質で構成された電力供給第 1 リンク配線 383a をゲート配線 312 と交差するように形成して、電力供給配線 313 の連結配線とする。より詳しくは、前記電力供給第 1 リンク配線 383a の両側には、連結電極 376 と同一工程、同一物質で構成された電力供給第 2 リンク配線 383b を形成して、上下画素領域 P に各々形成された電力供給配線 313 は、前記電力供給第 1 リンク配線 383a 及び電力供給第 2 リンク配線 383b を通じて相互に実質的に連結される。この時、前記データパッド 338 及び電力供給パッド 319 は、相互に異なる信号電圧が印加されるので、図面でのように、相互に逆方向の一端に形成することが望ましい。

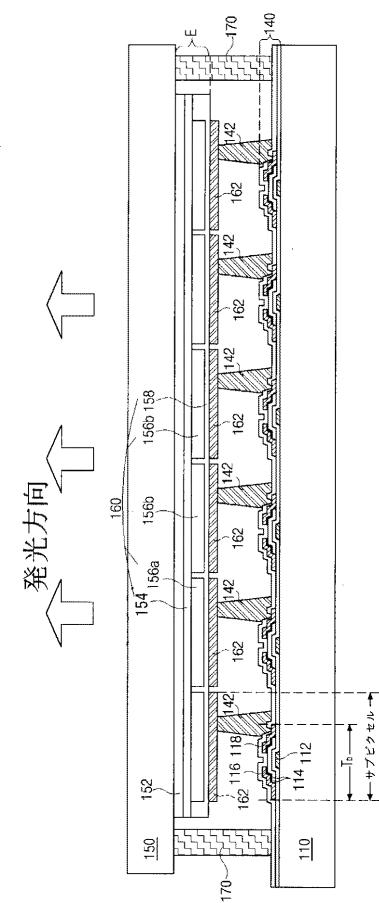

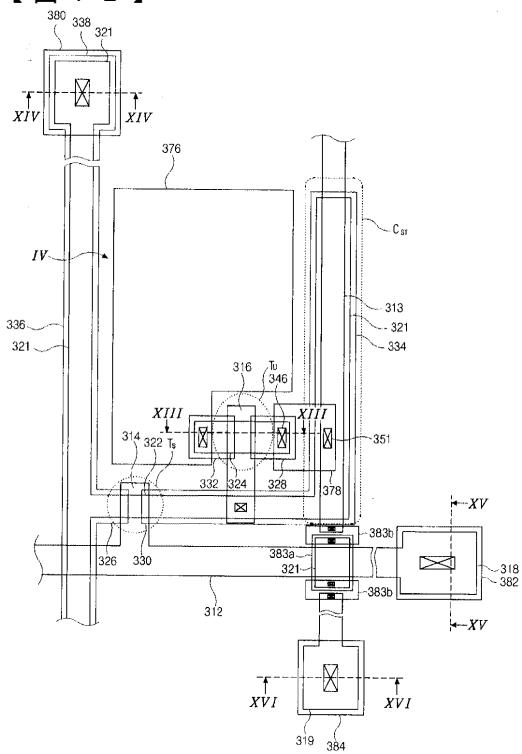

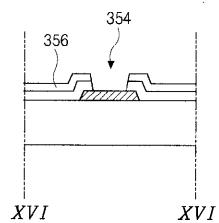

【 0084 】

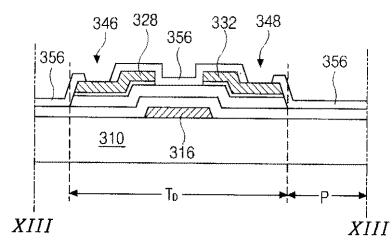

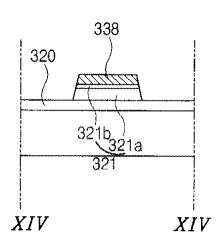

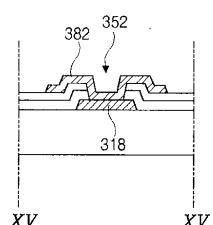

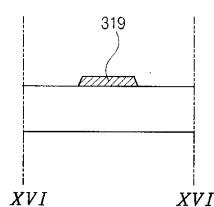

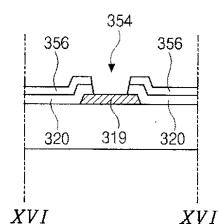

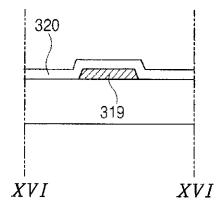

図 13A ないし図 13E、図 14A ないし図 14E、図 15A ないし図 15E、図 16A ないし図 16E は、前記図 12 の X III - X III、X IV - X IV、X V - X V、X VI - X VI 線に沿って切断した各々の断面を製造段階別に示した断面図であって、X III - X III は駆動用薄膜トランジスタ部、X IV - X IV はデータパッド部、X V - X V はゲートパッド部、X VI - X VI は電力供給パッド部の図である。説明の便宜上、駆動用ゲート電極、駆動用半導体層、駆動用ソース電極及びドレイン電極は、ゲート電極、半導体層、ソース電極及びドレイン電極と略称して説明する。

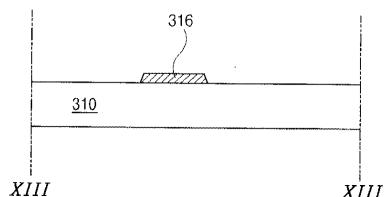

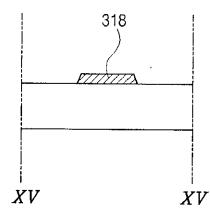

【 0085 】

図 13A、14A、15A、16A は、基板 310 上に第 1 金属物質を利用した第 1 マスク工程により、ゲート電極 316、ゲートパッド 318、電力供給パッド 319 を形成する段階である。図面に示してはいるが、この段階では、前記電力供給パッド 319 と一体形で電力供給配線(図 12 の 313)が形成されて、ゲート電極 316 及びゲートパッド 318 と一体形でゲート配線(図 12 の 312)が形成される。

【 0086 】

前記第 1 金属物質は、比抵抗が低い金属物質から選択されて、望ましくは、アルミニウムを含む金属物質から選択する。

【 0087 】

図面に詳しくは示してはいるが、本発明に利用されるマスク工程は、感光性物質である P R を塗布した後、望むパターンを持つマスクを配置して、露光 - 現像処理を通じて形成された P R パターンをマスクに利用して露出された被エッチング層をエッチングする方法でパターンングする。

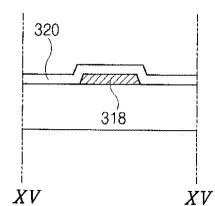

【 0088 】

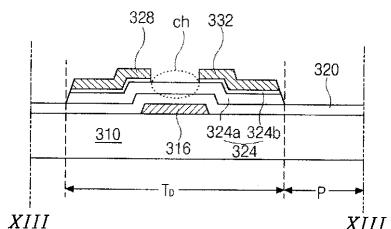

図 13B、14B、15B、16B は、前記ゲート電極 316、ゲートパッド 318、電力供給パッド 319 を覆う領域に、第 1 絶縁物質であるゲート絶縁膜 320、純粋非晶

10

20

30

40

50

質シリコン物質(a-Si)、不純物非晶質シリコン物質(n+a-Si)、第2金属物質を順に積層する。第2マスク工程により前記第2金属物質、不純物非晶質シリコン物質(n+a-Si)、純粋非晶質シリコン物質(a-Si)を連続的にエッティングして、ゲート電極316を覆う領域に位置する半導体層324と、前記半導体層324と対応されるパターン構造を持ち、前記半導体層324の上部で、相互に離隔されて位置するソース電極328及びドレイン電極332と、データパッド形成部にデータパッド338を形成する。

【0089】

図面には示していないが、この段階は、第2方向へデータ配線を形成する段階を含み、前記データパッド形成部はデータ配線の一端に形成されて、望ましくは、前記電力供給パッド319と相互に逆方向の一端部に位置する。

10

【0090】

図13Bで、前記ゲート電極316、半導体層324、ソース電極328及びドレイン電極332は駆動薄膜トランジスタT Dを構成する。

【0091】

前記半導体層324は、純粋非晶質シリコン物質で構成されたアクティブ層324aと、不純物非晶質シリコン物質で構成されたオーミックコンタクト層324bが順に積層された構造である。また、前記ソース電極328及びドレイン電極332を形成した後、前記ソース電極328及びドレイン電極332をマスクを利用して、前記ソース電極328及びドレイン電極332の間の区間に位置するオーミックコンタクト層324bを除去して、前記離隔区間に露出されたアクティブ層324a領域をチャンネル(Ch)として構成する。

20

【0092】

図13B, 14B, 15B及び16Bには示していないが、図12に示したデータ配線336及びキャパシター電極334をソース電極328及びドレイン電極332と共に形成する。また、データパッド338の下部、データ配線336の下部、キャパシター電極334の下部には、前記半導体パターン321を同一マスク工程により形成する。前記半導体パターン321は純粋非晶質シリコン物質層及び不純物非晶質シリコン物質層が順に積層された構造で、上部の金属層と同一な形のパターンを持つ。また、この段階では、ソース電極328及びドレイン電極332と半導体層324を同一マスク工程により形成して、前記チャンネル(Ch)の上部の金属物質層だけを選択的に除去することを特徴とするが、このような一つのマスク工程を利用して選択的にエッティングするためには、光の露光量を調節できる回折露光法を利用するが望ましい。回折露光法に関しては、図17Aないし図17Dを参照しながら、より詳しく説明する。

30

【0093】

前記第1絶縁物質であるゲート絶縁膜320は、シリコン絶縁物質から選択されることが望ましくて、さらに望ましくは、シリコン窒化膜(SiNx)にする。前記第2金属物質は、化学的耐食性の強い金属物質から選択されて、望ましくは、モリブデン(Mo)、チタン(Ti)、クロム(Cr)、タングステン(W)のうちから選択する。

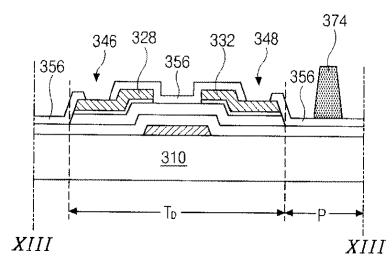

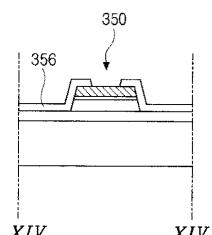

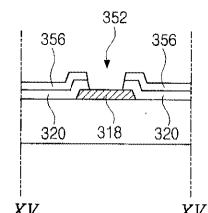

【0094】

図13C, 14C, 15C, 16Cは、前記駆動用薄膜トランジスタT D及びデータパッド338、ゲートパッド318、電力供給パッド319を覆う領域に、第2絶縁物質を形成する。第3マスク工程により、前記ソース電極328、ドレイン電極332、データパッド338、ゲートパッド318、電力供給パッド319を各々一部露出させるソースコンタクトホール346、ドレインコンタクトホール348、データパッドコンタクトホール350、ゲートパッドコンタクトホール352、電力供給パッドコンタクトホール354を保護層356及び下部のゲート絶縁膜320に形成する。この時、前記ゲートパッドコンタクトホール352及び電力供給パッドコンタクトホール354は、ゲートパッド318及び電力供給パッド319を覆う領域にゲート絶縁膜320及び保護層356を共通に形成されたコンタクトホールに該当し、ソースコンタクトホール346、ドレインコンタクトホール348及びデータパッドコンタクトホール350は、ただ保護層356

40

50

にだけ形成されたコンタクトホールに該当する。

【0095】

前記第2絶縁物質は、有機絶縁物質または、無機絶縁物質から選択されて、単一層または、複数層で構成されたりするが、薄膜トランジスタと接する絶縁物質は無機絶縁物質から選択されるのが望ましい。

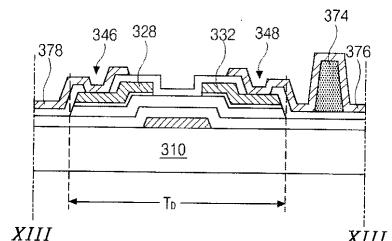

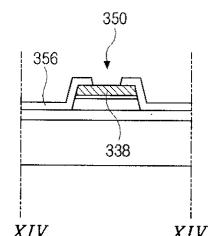

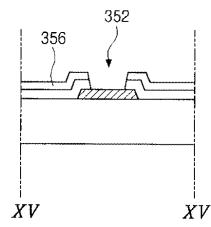

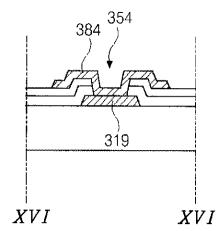

【0096】

図13D, 14D, 15D, 16Dは、前記保護層356上に、第3絶縁物質を利用して、第4マスク工程により、画素領域Pに柱形状の連結パターン374を形成する段階である。前記画素領域Pは、図示していない有機電界発光ダイオードの第2電極と対応する領域に当たる。前記第3絶縁物質は、厚く形成するのに適した有機絶縁物質から選択されるのが望ましい。

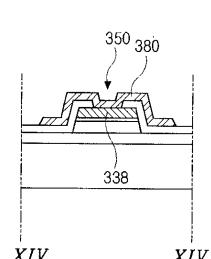

【0097】

図13E, 14E, 15E, 16Eは、前記電気的連結パターン374を覆う領域に第3金属物質を利用して金属層を形成した後、第5マスク工程により、前記ドレインコンタクトホール348を通じてドレイン電極332と連結され、前記電気的連結パターン374を覆い、画素領域Pに位置する連結電極376を形成する段階である。この時、ソースコンタクトホール346を通じてソース電極328と連結されるパワー電極378と、データパッドコンタクトホール350を通じてデータパッド338と連結されるデータパッド電極380と、ゲートパッドコンタクトホール352を通じてゲートパッド318と連結されるゲートパッド電極382と、電力供給パッドコンタクトホール354を通じて電力供給パッド319と連結される電力供給パッド電極384を形成する。また、この工程において、ゲート配線312の周りに第2リンク配線(図12の383b)を形成して、第2リンク配線は、第1リンク配線と共に電力供給配線313を連結させる役割を行う。図面に示してはいるが、前記パワー電極378はゲート工程で形成された電力供給配線(図12の313)とは別途にコンタクトホールを通じて連結構成される。

【0098】

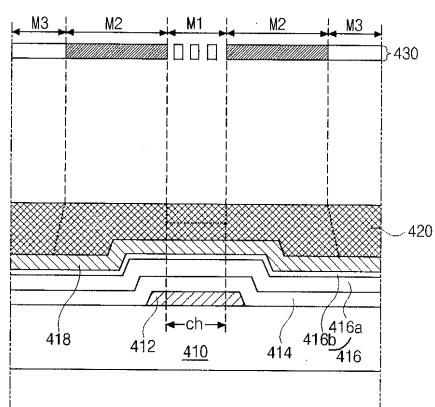

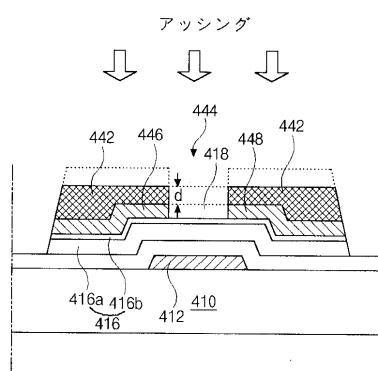

図17Aないし図17Dは、本発明による回折露光工程を利用した薄膜トランジスタの製造工程を段階別に示した断面図である。

【0099】

図17Aに示したように、基板410の上部に第1金属層をパターニングしてゲート電極412を形成する。そして、ゲート電極412が形成された基板410全面に、ゲート絶縁膜414、半導体層416、第2金属層を連続に積層する。前記半導体層416は、純粋非晶質シリコン層416aと不純物非晶質シリコン層416bで構成されている。このような層を連続に形成した後、感光性物質で構成されたフォトトレジスト420を第2金属層418上に形成する。フォトトレジスト420の上部に、回折露光処理のために、マスク430が位置する。

【0100】

前記フォトトレジスト420は、光が照射された部分が現像工程を通じて除去されるポジティブタイプ(Positive Type)感光性物質から選択される。前記マスク430は、ゲート電極412の上部のチャンネル部(Ch)と対応するように配置される半透過部(M1)、半透過部(M1)の両側に位置する光遮断部(M2)、光遮断部(M2)の両側に位置する光透過部(M3)で構成される。前記半透過部(M1)は、多数のスリット(Slits)や半透過性物質で構成されていて、光の一部だけを透過する性質を有する。すなわち、半透過部(M1)がスリット(Slits)で構成されている場合、半透過部(M1)領域では、光の回折現像により光透過部(M3)での光の照射量より少ない量の光がフォトトレジスト420に当る。従って、半透過部(M1)と対応する領域のフォトトレジスト420は、光透過部(M3)と対応する領域より薄い厚さで露光される。前記光遮断部(M2)は、以後形成されるソース電極及びドレイン電極と対応する領域に配置される。

【0101】

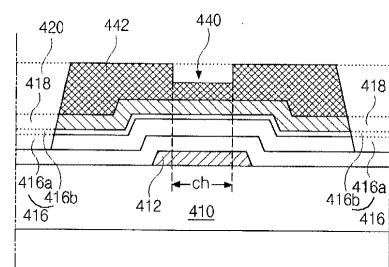

図17Bは、前記露光されたフォトトレジスト420を現像工程を通じて形成された以後

10

20

30

40

50

の状態である。フォトレジスト 420 を現像すると、光により完全に露出された部分は完全に除去されて、マスク 430 の光遮断部(M2)に対応していたフォトレジストはそのまま残って、チャンネル部(Ch)で凹部 440 を持つ PR パターン 442 が完成する。

【0102】

前記 PR パターン 442 は、マスクを利用して露出された金属層 418 及び半導体物質層 416 を連続にエッティングすると、PR パターン 442 の下部に半導体物質層と金属層のパターンが形成される。

【0103】

図 17C に示したように、チャンネル部(Ch)の金属層 418 を露出させる厚さ(D)ほど PR パターン 442 をアッシング処理する。それ故に、前記 PR パターン 442 にチャンネル部(Ch)の金属層 418 を露出させるオープン部 444 を PR パターン 442 に形成する。

【0104】

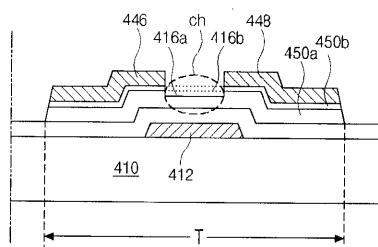

前記アッシング処理された PR パターン 442 をマスクを利用して、前記オープン部 444 に露出された金属層 418 をエッティングして、前記半導体層 416 の上部で、相互に離隔されて位置するソース電極 446 及びドレイン電極 448 を完成する。その後前記 PR パターン 442 をストリップ(Strip)して除去する。

【0105】

図 17D では、前記ソース電極 446 及びドレイン電極 448 をマスクを利用して、前記チャンネル部(Ch)に位置する第 2 半導体層 416b を除去して、その下部層を構成する第 1 半導体層 416a 露出させる。それ故に、前記第 1 半導体物質層 416a 領域にチャンネル(Ch)を構成する。この段階で、前記離隔区間の第 2 半導体層 416b を完全に除去するために、過エッティング処理をして、その下部層を構成する第 1 半導体層 416a も一部エッティングされる。この段階により、前記第 1 半導体物質層 416a はアクティブ層 450a を構成して、第 2 半導体層 416b はオーミックコンタクト層 450b を構成する。

【0106】

前記ゲート電極 412、アクティブ層 450a、オーミックコンタクト層 450b、ソース電極 446 及びドレイン電極 448 は薄膜トランジスタを構成する。このように、回折露光法によると、一つのマスク工程により半導体層、ソース電極及びドレイン電極を一括に形成する。本発明は、前記実施例で限定しないで、本発明の趣旨に反しない限度内で多様に変形して実施できる。

【図面の簡単な説明】

【0107】

【図 1】一般的なアクティブマトリックス型有機電界発光素子の基本画素の構造を示した回路である。

【図 2】従来のアクティブマトリックス型有機電界発光素子のひと画素部に関する平面図である。

【図 3】図 2 の III-III 線に沿って切断した断面を示した断面図である。

【図 4 A】図 2 の III-III 線に沿って切断した断面を製造工程の段階別に各々示した断面図である。

【図 4 B】図 4 A に続く製造工程を示す断面図である。

【図 4 C】図 4 B に続く製造工程を示す断面図である。

【図 4 D】図 4 C に続く製造工程を示す断面図である。

【図 4 E】図 4 D に続く製造工程を示す断面図である。

【図 4 F】図 4 E に続く製造工程を示す断面図である。

【図 4 G】図 4 F に続く製造工程を示す断面図である。

【図 4 H】図 4 G に続く製造工程を示す断面図である。

【図 4 I】図 4 H に続く製造工程を示す断面図である。

【図 5】従来の有機電界発光素子の全体の断面図である。

10

20

30

40

50

【図6】本発明によるデュアルパネルタイプ有機電界発光素子に関する断面図である。

【図7】本発明の実施例1によるデュアルパネルタイプ有機電界発光素子に関する断面図である。

【図8A】図7のVIII-VIII、IX-IX、X-X及びXI-XI線に沿って切断した各々の断面を製造段階別に示した断面図であって、VIII-VIIIは駆動用薄膜トランジスタ部、IX-IXはデータパッド部、X-Xはゲートパッド部、XI-XIは電力供給パッド部に関する断面図である。

【図8B】図8Aに続く製造工程を示す断面図である。

【図8C】図8Bに続く製造工程を示す断面図である。

【図8D】図8Cに続く製造工程を示す断面図である。

10

【図8E】図8Dに続く製造工程を示す断面図である。

【図8F】図8Eに続く製造工程を示す断面図である。

【図9A】図7のVIII-VIII、IX-IX、X-X及びXI-XI線に沿って切断した各々の断面を製造段階別に示した断面図であって、VIII-VIIIは駆動用薄膜トランジスタ部、IX-IXはデータパッド部、X-Xはゲートパッド部、XI-XIは電力供給パッド部に関する断面図である。

【図9B】図9Aに続く製造工程を示す断面図である。

【図9C】図9Bに続く製造工程を示す断面図である。

【図9D】図9Cに続く製造工程を示す断面図である。

20

【図9E】図9Dに続く製造工程を示す断面図である。

【図9F】図9Eに続く製造工程を示す断面図である。

【図10A】図7のVIII-VIII、IX-IX、X-X及びXI-XI線に沿って切断した各々の断面を製造段階別に示した断面図であって、VIII-VIIIは駆動用薄膜トランジスタ部、IX-IXはデータパッド部、X-Xはゲートパッド部、XI-XIは電力供給パッド部に関する断面図である。

【図10B】図10Aに続く製造工程を示す断面図である。

【図10C】図10Bに続く製造工程を示す断面図である。

【図10D】図10Cに続く製造工程を示す断面図である。

【図10E】図10Dに続く製造工程を示す断面図である。

30

【図10F】図10Eに続く製造工程を示す断面図である。

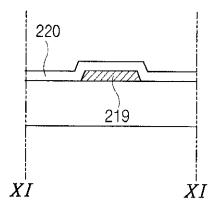

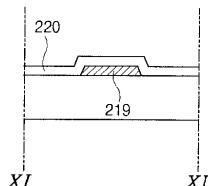

【図11A】図7のVIII-VIII、IX-IX、X-X及びXI-XI線に沿って切断した各々の断面を製造段階別に示した断面図であって、VIII-VIIIは駆動用薄膜トランジスタ部、IX-IXはデータパッド部、X-Xはゲートパッド部、XI-XIは電力供給パッド部に関する断面図である。

【図11B】図11Aに続く製造工程を示す断面図である。

【図11C】図11Bに続く製造工程を示す断面図である。

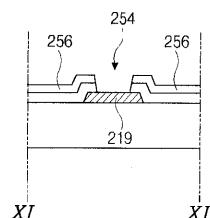

【図11D】図11Cに続く製造工程を示す断面図である。

【図11E】図11Dに続く製造工程を示す断面図である。

【図11F】図11Eに続く製造工程を示す断面図である。

【図12】本発明の実施例2によるデュアルパネルタイプ有機電界発光素子に関する平面図である。

40

【図13A】図12のXIII-XIII、XIV-XIV、XV-XV、XVI-XVI線に沿って切断した各々の断面を製造段階別に示した断面図であって、XIII-XIIIは駆動用薄膜トランジスタ部、XIV-XIVはデータパッド部、XV-XVはゲートパッド部、XVI-XVIは電力供給パッド部の断面図である。

【図13B】図13Aに続く製造工程を示す断面図である。

【図13C】図13Bに続く製造工程を示す断面図である。

【図13D】図13Cに続く製造工程を示す断面図である。

【図13E】図13Dに続く製造工程を示す断面図である。

【図14A】図12のXIII-XIII、XIV-XIV、XV-XV、XVI-XVI線に沿っ

50

て切断した各々の断面を製造段階別に示した断面図であって、X III - X IIIは駆動用薄膜トランジスタ部、X IV - X IVはデータパッド部、X V - X Vはゲートパッド部、X VI - X VIは電力供給パッド部の断面図である。

【図14B】図14Aに続く製造工程を示す断面図である。

【図14C】図14Bに続く製造工程を示す断面図である。

【図14D】図14Cに続く製造工程を示す断面図である。

【図14E】図14Dに続く製造工程を示す断面図である。

【図15A】図12のX III - X III、X IV - X IV、X V - X V、X VI - X VI線に沿って切断した各々の断面を製造段階別に示した断面図であって、X III - X IIIは駆動用薄膜トランジスタ部、X IV - X IVはデータパッド部、X V - X Vはゲートパッド部、X VI - X VIは電力供給パッド部の断面図である。

10

【図15B】図15Aに続く製造工程を示す断面図である。

【図15C】図15Bに続く製造工程を示す断面図である。

【図15D】図15Cに続く製造工程を示す断面図である。

【図15E】図15Dに続く製造工程を示す断面図である。

【図16A】図12のX III - X III、X IV - X IV、X V - X V、X VI - X VI線に沿って切断した各々の断面を製造段階別に示した断面図であって、X III - X IIIは駆動用薄膜トランジスタ部、X IV - X IVはデータパッド部、X V - X Vはゲートパッド部、X VI - X VIは電力供給パッド部の断面図である。

【図16B】図16Aに続く製造工程を示す断面図である。

【図16C】図16Bに続く製造工程を示す断面図である。

【図16D】図16Cに続く製造工程を示す断面図である。

【図16E】図16Dに続く製造工程を示す断面図である。

【図17A】本発明による回折露光工程を利用した薄膜トランジスタ素子の製造工程を段階別に示した断面図である。

【図17B】図17Aに続く製造工程を示す断面図である。

【図17C】図17Bに続く製造工程を示す断面図である。

【図17D】図17Cに続く製造工程を示す断面図である。

#### 【符号の説明】

【0108】

20

30

210 : 基板

216 : ゲート電極

220 : ゲート絶縁膜

224a : アクティブ層

224b : オーミックコンタクト層

224 : 半導体層

228 : ソース電極

232 : ドレイン電極

246 : ソースコンタクトホール

248 : ドレインコンタクトホール

40

256 : 保護層

274 : 連結パターン

276 : 連結電極

278 : 電力供給配線

C h : チャンネル

T D : 駆動用薄膜トランジスタ

【図1】

【図2】

【図3】

【図4C】

【図4D】

【図4A】

【図4B】

【図4E】

【図4F】

【図4G】

## 【図4-H】

### 【 図 4 】

【 図 5 】

【 6 】

【図7】

【 図 8 A 】

【 図 8 B 】

【 図 8 C 】

( 8 D )

【 8 F 】

〔 四 8 E 〕

【 义 9 A 】

【 図 9 B 】

【図 9 C】

【図 9 D】

【図 9 E】

【図 9 F】

【図 10 A】

【図 10 B】

【図 10 C】

【図 10 F】

【図 10 D】

【図 11 A】

【図 10 E】

【 図 1 1 B 】

【図11C】

〔 図 1 1 D 〕

【 図 1 2 】

【 図 1 1 E 】

【 図 1 1 F 】

【 図 1 3 A 】

【 図 1 3 B 】

【図 1 3 C】

【図 1 3 E】

【図 1 3 D】

【図 1 4 A】

【図 1 4 B】

【図 1 4 D】

【図 1 4 C】

【図 1 4 E】

【図 1 5 A】

【図 1 5 B】

【図 1 5 C】

【図 1 5 D】

【図 1 5 E】

【図 1 6 A】

【図 1 6 C】

【図 1 6 B】

【図 1 6 D】

【図16E】

【図17A】

【図17B】

【図17C】

【図17D】

---

フロントページの続き

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100102808

弁理士 高梨 憲通

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100107401

弁理士 高橋 誠一郎

(74)代理人 100106183

弁理士 吉澤 弘司

(72)発明者 パク チェ-ヨン

大韓民国 431-070, キョンギ-ド, アニヤン-シ, ドンアン-グ, ピヨンチョン-ドン,

クムマウル, キヨニヨン アパート, 305-ドン, 701-ホ

(72)発明者 チョ ソ-ヘン

大韓民国 431-060, キョンギ-ド, アニヤン-シ, ドンアン-グ, クワニヤン-ドン,

1488-39, チャンドク-エヴァービル, 502-ホ

F ターム(参考) 3K007 AB03 AB17 AB18 BA06 BB07 CC05 DB03 FA00 FA02 GA00

5C094 AA10 AA15 AA43 BA03 BA29 CA19

|                |                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 双面板型有机电致发光器件及其制造方法                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2004213004A</a>                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2004-07-29 |

| 申请号            | JP2003433282                                                                                                                                                                                                                                                                                                                              | 申请日     | 2003-12-26 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | パク チェヨン<br>チヨソヘン                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | パク チェヨン<br>チヨソヘン                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | H05B33/06 G09F9/30 G09F9/33 G09G3/30 G09G3/32 H01J1/62 H01L27/15 H01L27/32 H01L51/00<br>H01L51/40 H01L51/50 H05B33/00 H05B33/10 H05B33/14                                                                                                                                                                                                 |         |            |

| CPC分类号         | H01L27/3253 H01L27/3276 H01L2227/323 H01L2251/5315                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H05B33/06 H05B33/10 H05B33/14.A G09F9/30.365 H01L27/32                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB03 3K007/AB17 3K007/AB18 3K007/BA06 3K007/BB07 3K007/CC05 3K007/DB03 3K007<br>/FA00 3K007/FA02 3K007/GA00 5C094/AA10 5C094/AA15 5C094/AA43 5C094/BA03 5C094/BA29<br>5C094/CA19 3K107/AA01 3K107/BB01 3K107/CC35 3K107/CC36 3K107/CC45 3K107/DD38 3K107<br>/DD39 3K107/DD89 3K107/DD92 3K107/DD97 3K107/EE04 3K107/EE05 3K107/GG00 |         |            |

| 代理人(译)         | 臼井伸一<br>藤野郁夫<br>朝日伸光<br>高桥诚一郎<br>吉泽博                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 1020020086106 2002-12-28 KR                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | <a href="#">JP3779972B2</a>                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

解决的问题：提供一种具有高分辨率/高开口率结构并具有提高的成品率的有源矩阵有机电致发光器件。双面板型，其中阵列器件和有机发光二极管形成在不同的基板上，并且阵列器件的驱动薄膜晶体管和有机发光二极管器件的第二电极通过单独的电连接电极连接。（双面板型）有机电致发光器件。此外，通过采用使用非晶硅材料的倒置交错型薄膜晶体管结构，实现了通过少量掩模工艺制造的用于双面板型有机电致发光器件的下基板。[选择图]图7