(12)发明专利申请

(10)申请公布号 CN 111435675 A

(43)申请公布日 2020.07.21

(21)申请号 202010026337.5

(22)申请日 2020.01.10

(30)优先权数据

2019-003253 2019.01.11 JP

(71)申请人 株式会社日本显示器

地址 日本东京都

(72)发明人 前田典久

(74)专利代理机构 北京尚诚知识产权代理有限公司 11322

代理人 邸万杰 徐飞跃

(51)Int.Cl.

H01L 27/32(2006.01)

H01L 51/56(2006.01)

权利要求书1页 说明书9页 附图7页

(54)发明名称

电致发光显示装置和电致发光显示装置的制造方法

(57)摘要

本发明提供一种电致发光显示装置，其具有将以特定的颜色发光的像素规则地排列而构成的像素阵列，并且该像素阵列是彼此以不同的颜色发光的至少多个像素的阵列，在从观看方向看时，所述像素中依次层叠有共用电极(10)、第一阻挡层、发光层(7)、第二阻挡层和像素电极(3)，至少发光层(7)、所述第二阻挡层和像素电极(3)按每一个所述像素独立地设置，相邻的像素由隔堤(4)分隔，至少在所述像素阵列的一部分中，在隔堤(4)上，在属于一个像素的发光层(7)之上局部地重叠属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。根据本发明，能够降低相邻像素色的非意图的发光导致的混色和在隔堤上的原色发光的产生。

1. 一种电致发光显示装置,其特征在于:

具有将以特定的颜色发光的像素规则地排列而构成的像素阵列,并且该像素阵列是彼此以不同的颜色发光的至少多个像素的阵列,

从观察方向看时,所述像素中依次层叠有共用电极、第一阻挡层、发光层、第二阻挡层和像素电极,

至少所述发光层、所述第二阻挡层和所述像素电极按每一个所述像素独立地设置,相邻的像素由隔堤分隔,

至少在所述像素阵列的一部分中,在所述隔堤上,在属于一个像素的所述发光层之上局部地重叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。

2. 如权利要求1所述的电致发光显示装置,其特征在于:

至少在所述像素阵列的一部分中,在所述隔堤上,在属于一个像素的所述发光层之上局部地重叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层,进一步在该第二阻挡层之上局部地重叠属于所述另一像素的所述发光层。

3. 如权利要求1所述的电致发光显示装置,其特征在于:

至少在具有一个发光色的属于所述像素阵列的像素中,所述第二阻挡层的面积大于所述发光层的面积。

4. 如权利要求3所述的电致发光显示装置,其特征在于:

在具有不同于所述一个发光色的另一发光色的属于所述像素阵列的像素中,所述第二阻挡层的面积与所述发光层的面积相等。

5. 如权利要求3所述的电致发光显示装置,其特征在于:

至少在所述像素阵列的一部分中,在所述隔堤上,在属于一个像素的所述第二阻挡层之上局部地重叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。

6. 如权利要求3所述的电致发光显示装置,其特征在于:

在具有所述一个发光色的属于所述像素阵列的像素中,所述第二阻挡层的重心位置从所述发光层的重心位置偏离。

7. 一种电致发光显示装置的制造方法,其特征在于,包括:

在基板上形成像素电极和将相邻的像素隔开的隔堤的步骤;

关于一个发光色,使用第一掩模形成第二阻挡层之后,使用不同于所述第一掩模的第二掩模形成功能发光层的步骤;

之后,至少关于不同于所述一个发光色的另一发光色,使用第三掩模形成第二阻挡层之后,使用与所述第三掩模不同的第四掩模形成功能发光层的步骤;和

形成第一阻挡层和共用电极的步骤。

8. 如权利要求7所述的电致发光显示装置的制造方法,其特征在于:

至少关于所述另一发光色的所述第二阻挡层的面积比关于所述另一发光色的所述发光层的面积大。

## 电致发光显示装置和电致发光显示装置的制造方法

### 技术领域

[0001] 本发明涉及电致发光显示装置和电致发光显示装置的制造方法。

### 背景技术

[0002] 在W02012/039213A1中记载有多个电荷产生层与有机层以相互重叠的方式层叠的有机发光装置。特别是在其图3中公开了表示第一有机层、第一电荷产生层、第二有机层、第二电荷产生层和第三有机层依次层叠的一个实施方式的截面图。

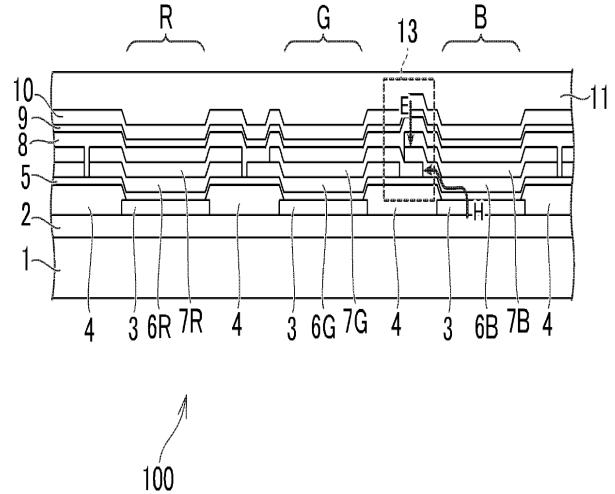

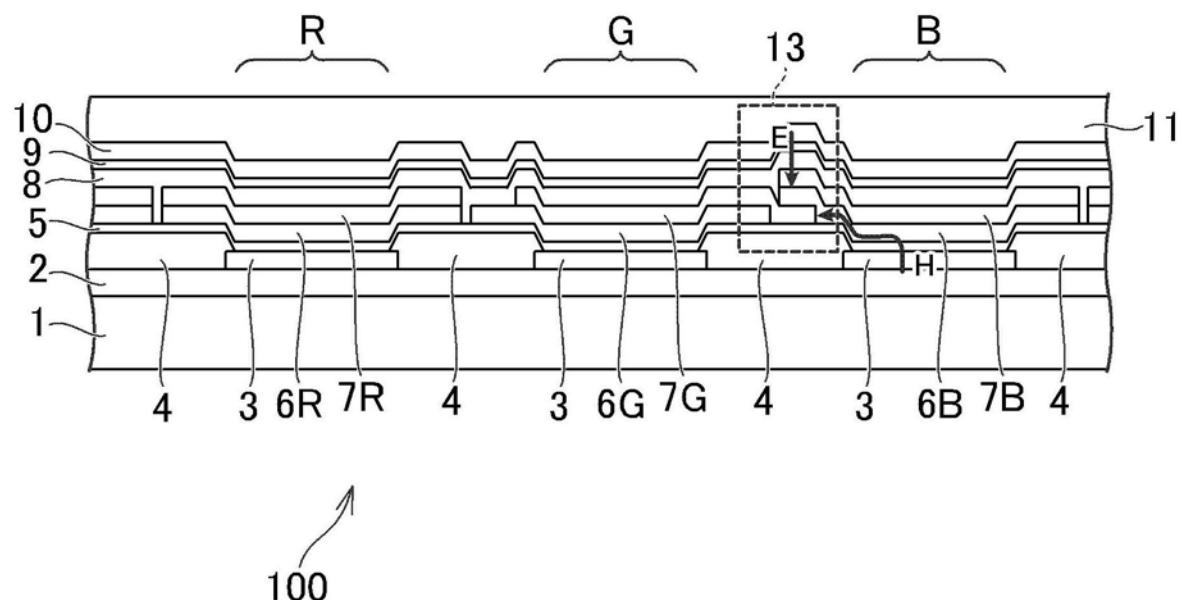

[0003] 图1是表示顶部发射型的电致发光显示装置400的代表性构造的示意截面图。电致发光显示装置400为将基板1、形成在基板1上的电路层2、按每一个像素形成的像素电极3、隔开像素的隔堤4、跨像素电极3和隔堤4上而形成的空穴注入层5、按每一个像素独立地形成的电子阻挡层6R、6G、6B及发光层7R、7G、7B、空穴阻挡层8、电子注入层9、共用电极10和密封层11依次层叠而成的构造。

[0004] 在图1所示的电致发光显示装置400中,各像素具有RGB三色中的任意者的发光色,由隔堤4划分的区域各自成为一个像素。在图1中,将各像素根据其颜色标注R、G、B的符号来表示。此外,有时将由隔堤4划分的像素的区域称为开口区域,而由隔堤4形成的像素以外的区域称为矩阵区域。

[0005] 另外,按每一个像素独立地形成的电子阻挡层6和发光层7,符号的末尾标注R、G、B任意一者的文字来表示是属于哪一个发光色的像素。此外,在没有特别地特定是属于哪一个像素的情况下,就不标注R、G、B任意一者的文字,仅表示为电子阻挡层6和发光层7。

[0006] 另外,在图1所示的例子中,空穴注入层5和电子注入层9不是按每一个像素独立设置而是共用地设置,但这两者或者任意一者按每一个像素独立地设置也是可以的。

[0007] 在图1的电致发光显示装置400中,使任意的像素发光的情况下,例如,以像素B为例进行说明,当对属于像素B的像素电极3施加正电压时,经由空穴注入层5、电子阻挡层6B到达发光层7B的空穴,与从共用电极10经由电子注入层9、空穴阻挡层8到达发光层7B的电子结合,产生对应于发光层7B的材质的蓝色的光。在该图中,空穴的移动路径由箭头H表示,电子的移动路径由箭头E表示。

[0008] 构成图1所示的电致发光显示装置400的各层通常通过使用了光刻和精细掩模的蒸镀等的制膜工艺来形成。这时,由于机械的定位精度和材料的尺寸误差等的影响,各层形成的位置存在在水平方向上偏离数 $\mu\text{m}$ 的情况。并且,该偏离在考虑到像素的尺寸通常为数十 $\mu\text{m}$ ~数百 $\mu\text{m}$ 程度时,是不能被无视的。

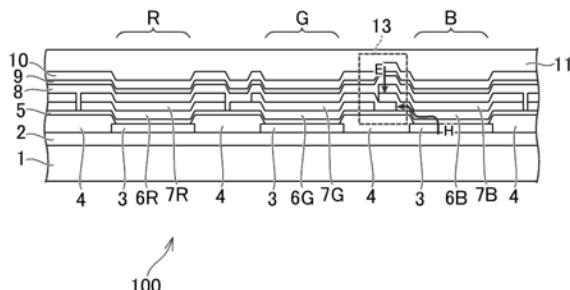

[0009] 由于这样的偏离,考虑例如如图2所示,像素G的发光层7G向图中右侧偏离地形成,在隔堤4上的区域13中,重叠于相邻的像素B的电子阻挡层6B的情况下。在该图中,在区域13,在发光层7G之上进一步重叠发光层7B。这时,当使像素G或者像素B发光的情况下,这里可以认为使像素B发光的情况。

[0010] 当对属于像素B的像素电极3施加正电压时,所产生的空穴与电子的几乎全部在像素B的范围内结合,使像素B发出蓝色光。但是,一部分的空穴如箭头H所示在电子阻挡层6B

内向像素B的外侧移动，并侵入区域13。该空穴如箭头E所示与从共用电极10导入的电子在发光层7G内结合，产生了非意图的绿色的发光。

[0011] 像这样，由于构成电致发光显示装置400的各层的水平方向的偏离，存在在隔堤4上产生非意图的颜色的发光的情况。当产生了这样的发光时，由于混色而导致色纯度降低，造成电致发光显示装置400的显示图像的品质降低。

[0012] 如果构成电致发光显示装置400的各层没有产生在水平方向上的偏离，上述的混色通常不会发生，但与图2中所说明的情况同样地，产生的空穴的一部分在电子阻挡层6内向像素的外侧移动，在隔堤4上与电子结合，由此虽然是同色，但产生了在像素外的发光。这样的发光对显示图像的品质造成并不那么大的影响，但是由于没有考虑在隔堤4上的发光，这样的发光大多无益，成为发光效率降低的原因之一。

[0013]

## 发明内容

[0014] 发明要解决的技术问题

[0015] 本发明是为了改善上述的诸问题而完成的发明，目的在于在电致发光显示装置中，降低相邻像素色的非意图的发光导致的混色和在隔堤上的原色发光的产生。

[0016] 为了解决上述问题，本申请中公开的发明具有各个方面，这些方面的代表性的内容的概要如下所述。

[0017] (1)一种电致发光显示装置，其具有将以特定的颜色发光的像素规则地排列而构成的像素阵列，并且该像素阵列是彼此以不同的颜色发光的至少多个像素的阵列，从观察方向看时，所述像素中依次层叠有共用电极、第一阻挡层、发光层、第二阻挡层和像素电极，至少所述发光层、所述第二阻挡层和所述像素电极按每一个所述像素独立地设置，相邻的像素由隔堤分隔，至少在所述像素阵列的一部分中，在所述隔堤上，在属于一个像素的所述发光层之上局部地重叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。

[0018] (2)一种电致发光显示装置，其为在(1)中，至少在所述像素阵列的一部分中，在所述隔堤上，在属于一个像素的所述发光层之上局部地重叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层，进一步在该第二阻挡层之上局部地重叠属于所述另一像素的所述发光层。

[0019] (3)一种电致发光显示装置，其为在(1)或者(2)中，至少在具有一个发光色的属于所述像素阵列的像素中，所述第二阻挡层的面积大于所述发光层的面积。

[0020] (4)一种电致发光显示装置，其为在(3)中，在具有不同于所述一个发光色的另一发光色的属于所述像素阵列的像素中，所述第二阻挡层的面积与所述发光层的面积相等。

[0021] (5)一种电致发光显示装置，其为在(3)或者(4)，至少在所述像素阵列的一部分中，在所述隔堤上，在属于一个像素的所述第二阻挡层之上局部地层叠有属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。

[0022] (6)一种电致发光显示装置，其为在(3)或者(4)中，在具有所述一个发光色的属于所述像素阵列的像素中，所述第二阻挡层的重心位置从所述发光层的重心位置偏离。

[0023] (7)一种电致发光显示装置的制造方法，其包括：在基板上形成像素电极和将相邻

的像隔开素的隔堤的步骤；关于一个发光色，使用第一掩模形成第二阻挡层之后，使用不同于所述第一掩模的第二掩模形成发光层的步骤；之后，至少关于不同于所述一个发光色的另一发光色，使用第三掩模形成第二阻挡层之后，使用与所述第三掩模不同的第四掩模形成发光层的步骤；和形成第一阻挡层和共用电极的步骤。

[0024] (8) 一种电致发光显示装置的制造方法，其为在(7)中，至少关于所述另一发光色的所述第二阻挡层的面积比关于所述另一发光色的所述发光层的面积大。

[0025] 根据本发明，在电致发光显示装置中，能够降低相邻像素色的非意图的发光导致的混色和在隔堤上的原色发光的产生。

## 附图说明

[0026] 图1是表示顶部发射型的电致发光显示装置的代表性的构造的示意截面图。

[0027] 图2是表示像素G的发光层向图中右侧偏离地形成的情况下电致发光显示装置的构造的截面示意图。

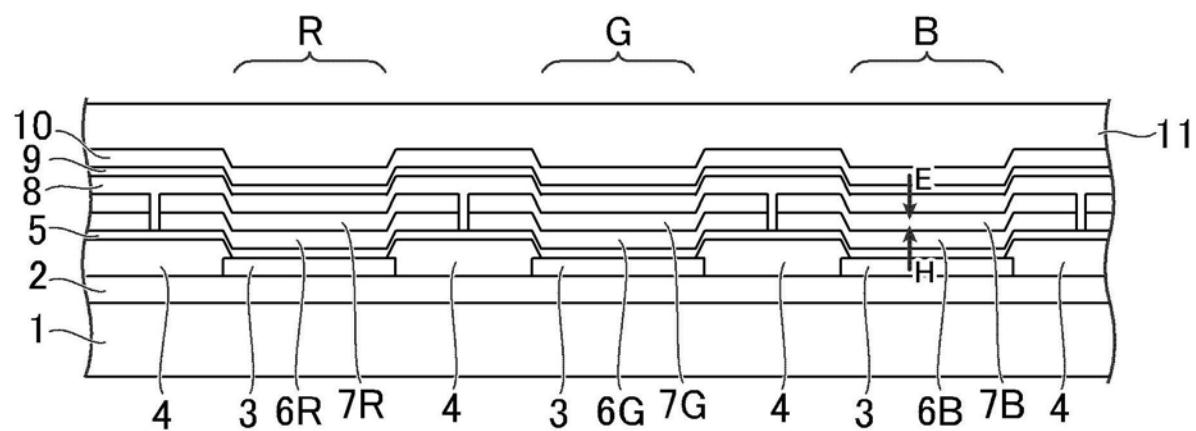

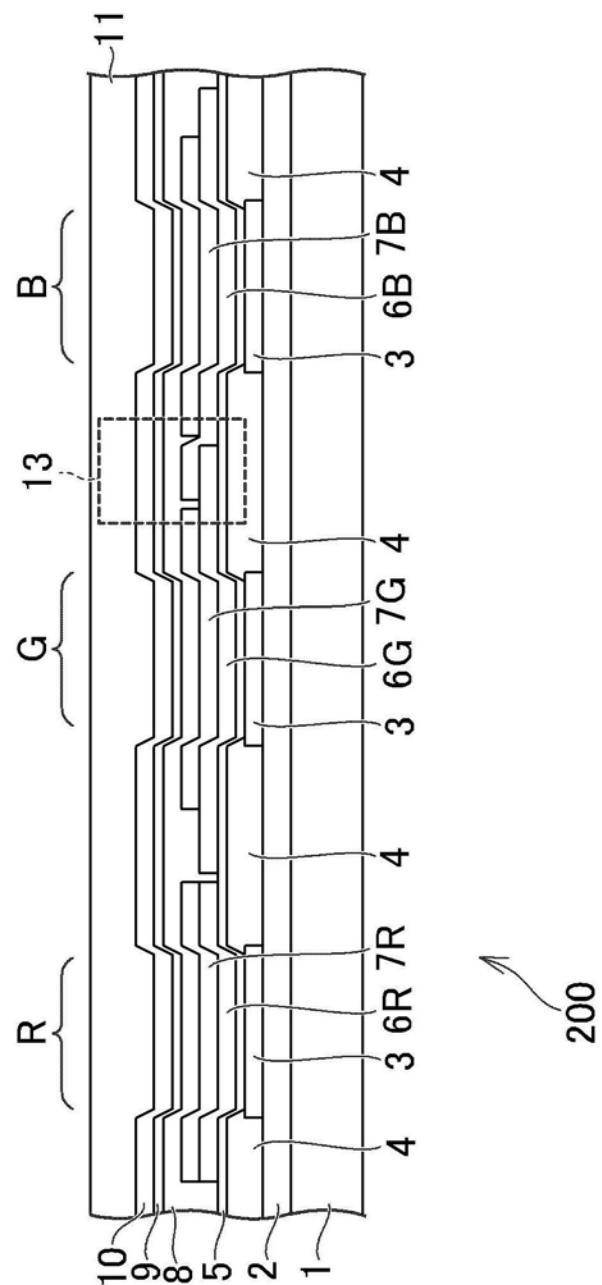

[0028] 图3是表示像素G的发光层向图中右侧偏离地形成的情况下、本发明的第一实施方式的电致发光显示装置的构造的截面示意图。

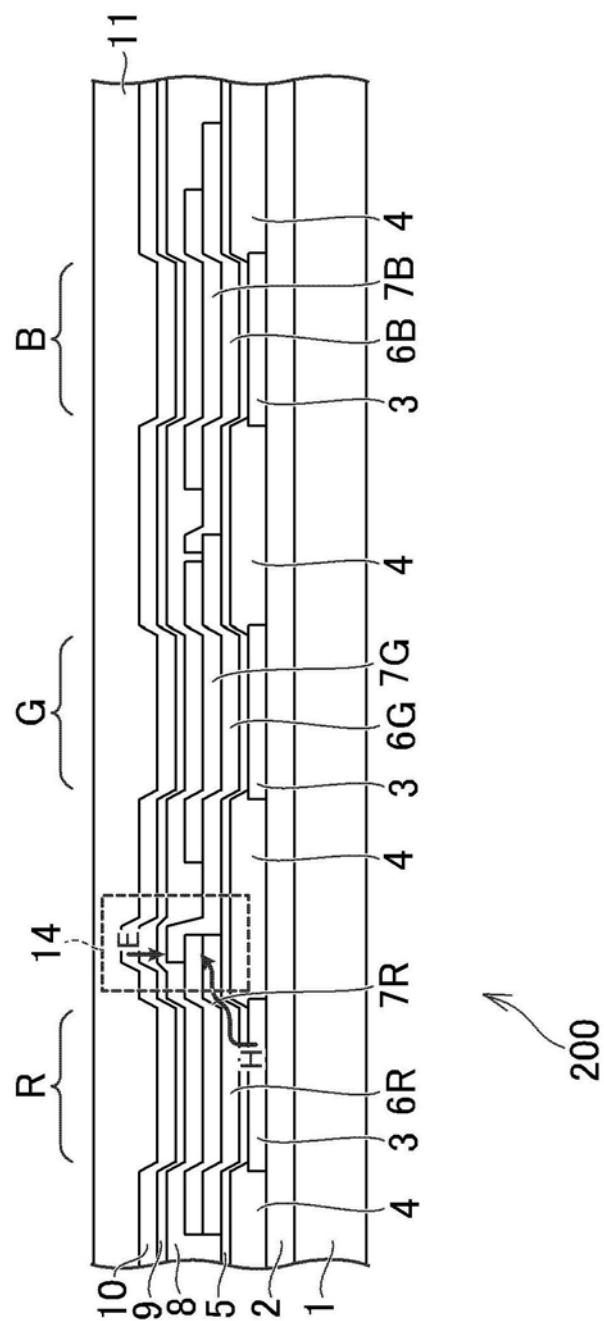

[0029] 图4是表示本发明的第二实施方式的电致发光显示装置的构造的截面示意图。

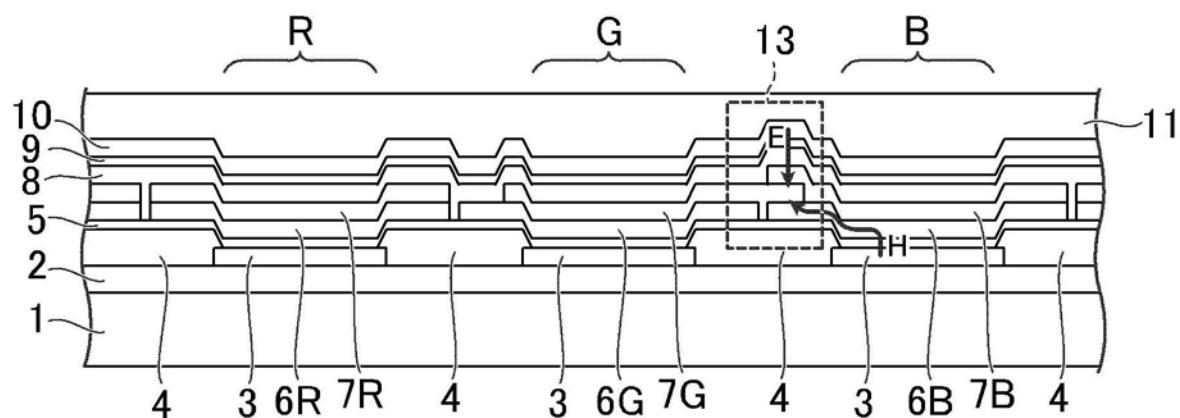

[0030] 图5是表示像素G的电子阻挡层向图中左侧偏离地形成的情况下、本发明的第二实施方式的电致发光显示装置的构造的截面示意图。

[0031] 图6是说明本发明的第二实施方式中，减少在隔堤上的相邻像素色的非意图的发光导致的混色的例子的图。

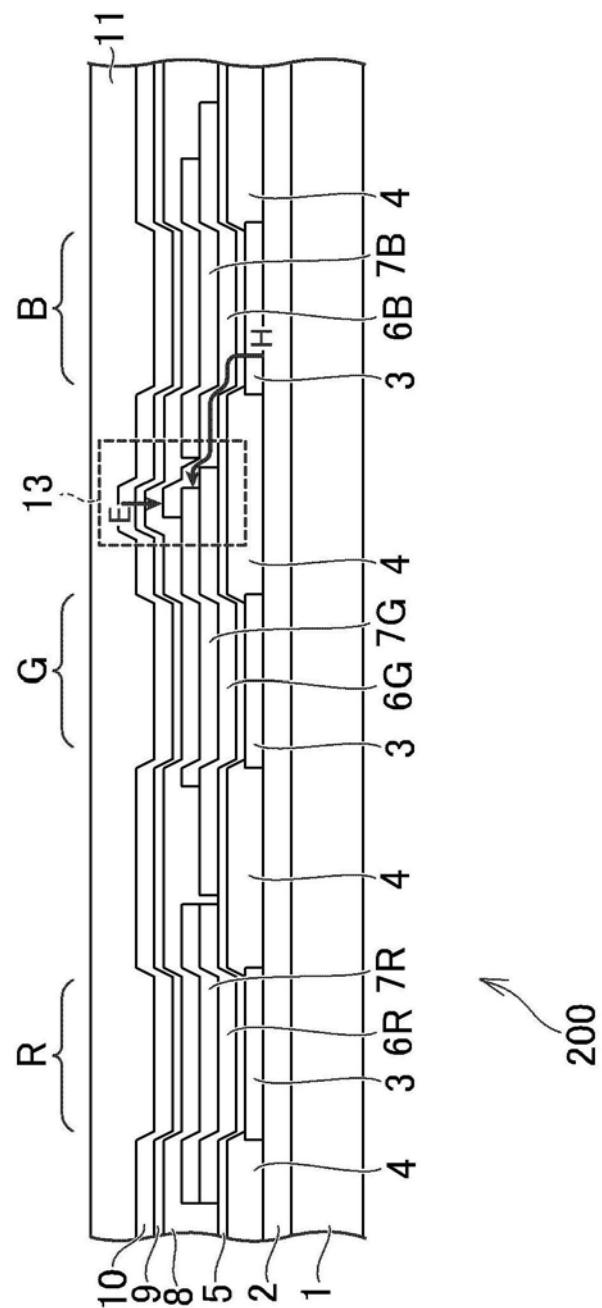

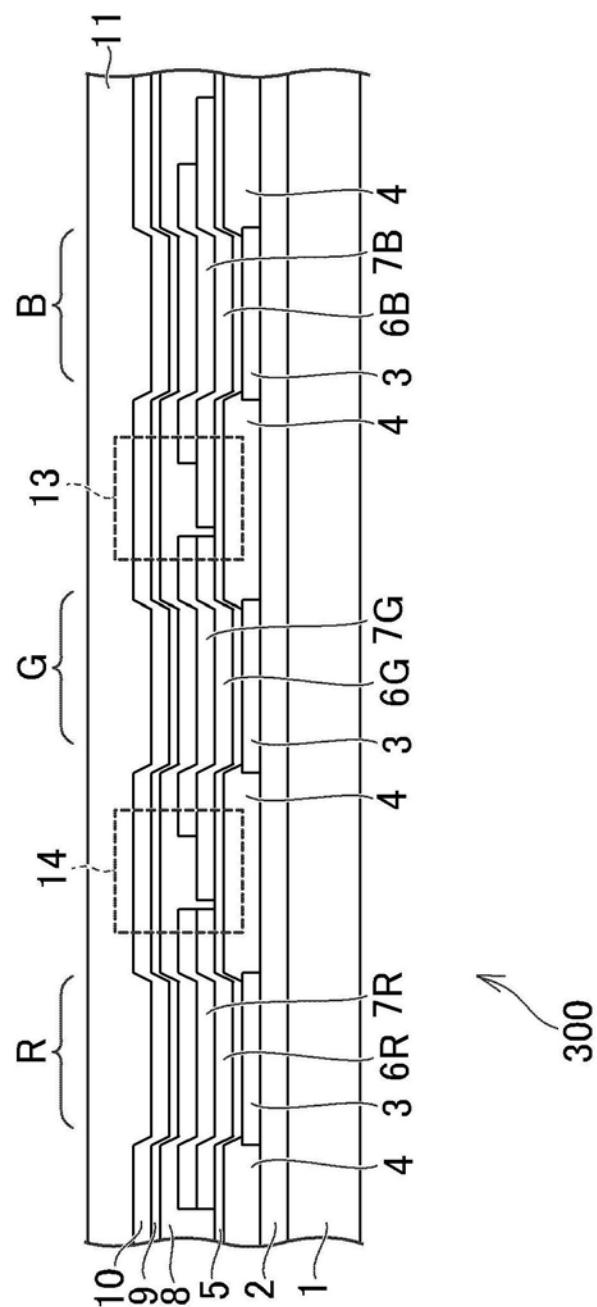

[0032] 图7是表示本发明的第三实施方式的电致发光显示装置的构造的截面示意图。

[0033] 图8是说明本发明的第三实施方式中的减少在隔堤上的相邻像素色的非意图的发光导致的混色和非意图的原色发光的例子的图。

## 具体实施方式

[0034] 本发明的第一实施方式的电致发光显示装置100，在其制造工序和由其制造工序产生的构造中具有特征。因此，以下，首先说明第一实施方式的电致发光显示装置100的制造方法。此外，电致发光显示装置100的结构本身，由于与参照图1已经说明的电致发光显示装置400是相同的，所以可以引用图1的内容。

[0035] 首先，对已经说明的电致发光显示装置400的制造方法进行说明。

[0036] 在基板1上制作包括薄膜晶体管及其配线等的电路层2。关于电路层2的构造及其制作方法，由于其各种内容是公知的，所以在本说明书中省略关于其详细内容的说明。

[0037] 接着，在电路层2上形成像素电极3、隔堤4。隔堤4以覆盖像素电极3的端部的方式形成。该形成可以适当使用光刻等公知的方法。

[0038] 并且，以跨像素电极3和隔堤4上的方式形成空穴注入层5。关于空穴注入层5的材质和形成方法可以使用公知的材料和方法。另外，空穴注入层5也可以作为按各像素的每一个独立的形状来形成。

[0039] 以覆盖各像素的开口区域的方式形成电子阻挡层6、发光层7。电子阻挡层6可以作为在各像素共同的部件一并地制成，但由于发光层7的材质、即按每一发光色采用适当的材

质和成膜条件,所以按每一像素的发光色通过不同的工序制成。

[0040] 这时,如图1所示,当电致发光显示装置400采用红、绿、蓝的三色发光的显示装置时,电子阻挡层6和发光层7制作顺序如下所述。

[0041] 1) 电子阻挡层6R

[0042] 2) 电子阻挡层6G

[0043] 3) 电子阻挡层6B

[0044] 4) 发光层7R

[0045] 5) 发光层7G

[0046] 6) 发光层7B

[0047] 电子阻挡层6和发光层7的制作按每一层的种类进行,另外,由于这些层在大多情况下会由于环境中的水分等的杂质的混入或接触而导致发生劣化,因此选择使用掩模的真空蒸镀。掩模由于是使用对各层专用的部件,例如,在电子阻挡层6R的形成中使用的掩模与电子阻挡层6G的形成中使用的掩模是不同的,所以需要每次进行掩模与基板1的对位。

[0048] 之后,依次制作空穴阻挡层8、电子注入层9、共用电极10,并且形成密封层11,由此制造电致发光显示装置400。

[0049] 此外,在发光层7的上下也可以使极性颠倒。在图1中,作为电致发光显示装置400的观看方向、从图中上方起依次地将共用电极10、电子注入层9、空穴阻挡层8、发光层7、电子阻挡层6、空穴注入层5和像素电极3按该顺序排列,如果是极性反转,则电子注入层9与空穴注入层5、以及空穴阻挡层8与电子阻挡层6的位置分别调换。因此,从电致发光显示装置400的观看方向看,将位于发光层7的跟前侧的层称为第一阻挡层,将位于发光层7的进深侧的层称为第二阻挡层时,在图1所示的例子中,空穴阻挡层8对应于第一阻挡层,电子阻挡层6对应于第二阻挡层。

[0050] 相对于此,在第一实施方式的电致发光显示装置100中,电子阻挡层6和发光层7的制作按以下的顺序进行。

[0051] 1) 电子阻挡层6R

[0052] 2) 发光层7R

[0053] 3) 电子阻挡层6G

[0054] 4) 发光层7G

[0055] 5) 电子阻挡层6B

[0056] 6) 发光层7B

[0057] 即,将关于单色形成电子阻挡层6、接着形成关于相同颜色的发光层7的处理以色数反复进行。

[0058] 将该处理更一般地说明,可以说是关于一个发光色使用第一掩模形成第二阻挡层之后,使用第二掩模形成发光层7,并且,之后关于其它的发光色使用第三掩模形成第二阻挡层之后,使用第四掩模形成发光层7的处理。

[0059] 在此,将一个发光色采用红色时,在本实施方式中,利用第一掩模形成电子阻挡层6R,并且利用第二掩模形成发光层7R,之后,利用第三掩模形成电子阻挡层6G,进而利用第四掩模形成发光层7G。

[0060] 另外,将一个发光色采用绿色时,在本实施方式中,利用第一掩模形成电子阻挡层

6G,进而利用第二掩模形成发光层7G,之后,利用第三掩模形成电子阻挡层6B,进而利用第四掩模形成发光层7B。

[0061] 即,在本处理不依赖于电致发光显示装置100的色数(但是,是多个色),另外,也不依赖于形成各色的顺序。

[0062] 像这样制作的电致发光显示装置100中,在各层制造的过程中,在不发生位置偏离地准确形成的情况下,做成的电致发光显示装置100与图1所示的装置相同,没有差异。

[0063] 但是,在显示中,如上所述,在各层的制造过程中,其水平方向的位置可能产生数μm程度的偏离。该偏离发生在哪一层,另外其方向和偏离的量随机地确定,因此其结果一概不能预测。因此,这里作为一个例子,考虑与图2所示同样地像素G的发光层7G向图中右侧偏离地形成的情况。

[0064] 图3是表示像素G的发光层7G向图中右侧偏离地形成的情况下的电致发光显示装置100的构造的截面示意图。在区域13中,与图2的例同样地,发光层7G在隔堤4上与像素B的发光层7B重叠。

[0065] 但是,在电致发光显示装置100中,在形成发光层7G之后形成像素B的电子阻挡层6B,然后形成发光层7B,因此,如图3所示,在隔堤4上在向像素B侧延伸的发光层7G之上形成电子阻挡层6B,发光层7B隔着电子阻挡层6B与发光层7G重叠。

[0066] 在该情况下,一部分的空穴如箭头H所示在电子阻挡层6B内向像素B的外侧移动,侵入到区域13中,并且能够到达发光层7G。但是,从共用电极10导入的电子如箭头E所示,由电子阻挡层6B阻挡,不能到达发光层7G。因此,在发光层7G内空穴不能与电子结合,从而能够防止隔堤4上的非意图的发光。

[0067] 图3中所说明的情况是例示了在各层中发生的各种偏离之中的一例,并不是包括全部的各种情况。因此,如图2中所说明,在隔堤4上也可能发生发光层7G与发光层7B直接接触地重叠的情况(例如,像素G的发光层7G向图中右侧偏离地形成的同时,像素B的电子阻挡层6B也向图中右偏离地形成的情况等)。在这样的情况下,并不能完全地防止在隔堤4上的非意图的发光。

[0068] 但是,如图3所例示,在隔堤4上,电子阻挡层6B局部地重叠在发光层7G的情况下,能够防止在隔堤4上的非意图的发光。将其一般化地表现的话,在将以特定的颜色发光的像素规则地排列而成的像素阵列的至少一部分中,以在隔堤4上在属于一个像素的发光层7之上局部地重叠属于具有与该一个像素不同的发光色的另一像素的第二阻挡层6的方式,形成电致发光显示装置100的情况下,能够防止在隔堤4上的非意图的发光,这样的构造按一定概率发生。

[0069] 也就是说,即使在构成电致发光显示装置100的各层的水平方向的位置偏离地形成的情况下,也能够以一定概率防止隔堤4上的非意图的发光,作为整体来看,隔堤4上的非意图的发光降低,对于显示装置的面内不均的降低和产品成品率提高是有贡献的。

[0070] 此外,在图3所示的情况下,在隔堤4上,在属于一个像素的发光层7之上局部地重叠属于具有与该一个像素不同的发光色的另一像素的第二阻挡层6,并进一步在其之上局部地重叠属于该另一像素的发光层7,即使在这样的情况下,也能够防止隔堤4上的非意图的发光。

[0071] 在至此所说明的第一实施方式中,关于各色,第二阻挡层6与发光层7的平面形状

是大致相同的,因此,是以其面积彼此大致相等的情况进行说明的,但是也可以使其不同。

[0072] 图4是表示本发明的第二实施方式的电致发光显示装置200的构造的截面示意图。在本实施方式中,像素G的电子阻挡层6G和像素B的电子阻挡层6B的俯视的面积分别大于像素G的发光层7G和像素B的发光层7B,以电子阻挡层6G、6B向发光层7G、7B的周围突出的方式形成,这一点与第一实施方式的电致发光显示装置不同。其它的方面是相同的。

[0073] 如图4所示,在电致发光显示装置200中,像素R与先前的电致发光显示装置100在构造上没有差异,电子阻挡层6R与发光层7R的平面形状是相同的,其面积相等。因此,在这些层没有从设计上的位置偏离而准确地形成的情况下,如该图所示,彼此没有突出地重叠。

[0074] 另一方面,像素G形成为电子阻挡层6G比发光层7G的平面形状大,电子阻挡层6G的面积比发光层7G的面积大。并且,在本实施方式中,由于设计上的位置为,电子阻挡层6G的中心位置与发光层7G的中心位置相等地设计,在这些层没有从设计上的位置偏离地准确形成的情况下,如该图所示,电子阻挡层6G的外周部分以从发光层6G的周边缘左右均等地突出的方式配置。考虑到制膜装置和部件的精度,优选该突出量形成为俯视时发光层7G不突出到电子阻挡层6G的外侧、或者事实上能够无视突出的可能性的长度。

[0075] 关于像素B也与像素G同样地形成,电子阻挡层6B相比发光层7B的平面形状更大,电子阻挡层6B的面积比发光层7B的面积大。并且,电子阻挡层6G的中心位置与发光层7G的中心位置相等地设计,在这些层没有从设计上的位置偏离地准确地形成的情况下,以电子阻挡层6B的外周部分从发光层6B的周边缘均等地突出的方式配置。其结果是,在图中区域13所看到那样,在设计时的状态下,在隔堤4上电子阻挡层6B的一部分重叠在电子阻挡层6G上。关于其突出量,优选形成为俯视时发光层7B没有突出到电子阻挡层6B的外侧、或者事实上能够无视突出的可能性的长度。

[0076] 通过采用像这样的设计,能够防止在像素R、G、B间发光层7彼此重叠,或者尽力降低其可能性。此外,关于像素R也采用与像素G、像素B同样的设计,可以使电子阻挡层6R的平面形状比发光层7R大,其面积比发光层7R的面积大。但是,如先前所述,由于电子阻挡层6R和发光层7R比像素G的电子阻挡层6G和发光层7G以及像素B的电子阻挡层6B和发光层7B提前地形成,即使使电子阻挡层6R的面积增大,电子阻挡层6R也不会重叠在发光层7G或者发光层7B上,不能抑制隔堤4上的非意图的发光。因此,采用使电子阻挡层6R的平面形状比发光层7R大的结构在技术上的意义不大,从减少制造上的材料的观点考虑,优选形成为与发光层6R相同形状、即使面积相等的结构。

[0077] 另外,本实施方式的电致发光显示装置200中,也能够期待进一步的效果。将其说明参照图5在下文中进行说明。

[0078] 图5是表示像素G的电子阻挡层6G向图中左侧偏离地形成的情况下电致发光显示装置200的构造的截面示意图。此外,为了说明的方便,其它的层中没有发生偏离而形成于设计上的位置。

[0079] 在该情况下,如果按照上述的各层的形成顺序,如该图所示,电子阻挡层6G的一部分在隔堤4上重叠于像素R的电子阻挡层6R和发光层7R上。该重叠并没有涉及到像素R的开口区域,因此对于像素R的发光本身没有造成不好的影响。

[0080] 另一方面,为了使像素R点亮,当对像素R的像素电极3施加正电压时,所产生的空穴的一部分通过电子阻挡层6R向像素R的外侧区域移动。这里,认为是像素R的向图中右侧

移动的空穴。

[0081] 该空穴理论上如箭头H所示在电子阻挡层6R中移动,能够侵入像素R的外侧、在隔堤4上能够侵入发光层7R。但是,如图5所示的情况下,以在区域14所示的隔堤4上的发光层7R上,进一步重叠有像素G的电子阻挡层6G的方式形成。因此,从共用电极10导入的电子如该图中箭头E所示,由电子阻挡层6G阻挡,不能进入到发光层7中。因此,至少在与电子阻挡层6G重叠的区域中,在发光层7R中空穴与电子没有结合而没有产生发光。

[0082] 这意味着,当电子阻挡层6G重叠于在隔堤4上相邻的像素R的发光层7R之上时,能够降低像素R的范围外即隔堤4上的原色发光。

[0083] 该原色发光的降低效果并不是一定发生,而是概率性地发生的各层的位置偏离成为图5那样的配置的情况下而引起的效果,因此这样的构造是按一定概率发生的。也就是说,即使在构成电致发光显示装置200的各层的水平方向的位置偏离地形成了的情况下,也能够以一定的概率防止在隔堤4上的非意图的原色发光,作为整体来看,能够降低在隔堤4上的非意图的原色发光,能够使显示特性提高。

[0084] 当然,在图4和图5所示的第二实施方式中,与先前所示的第一实施方式同样地,作为整体来看能够降低隔堤4上的相邻像素色的非意图的发光导致的混色。在第二实施方式中,以图6所示说明降低在隔堤4上的相邻像素色的非意图的发光导致的混色的例子。

[0085] 图6中表示了像素G的发光层7G向图中右侧偏离地形成的情况。此外,为了说明的方便,其它层没有偏离地按照设计的位置(即,与图4所示的同样的位置)形成。这时,在电致发光显示装置200的截面的区域13中,发光层7G在隔堤4上与像素B的电子阻挡层6B重叠。但是,由于在电致发光显示装置200中,在形成像素G的发光层7G之后形成像素B的电子阻挡层6B,因此如图6所示,在隔堤4上在向像素B侧延伸出的发光层7G上形成有电子阻挡层6B,像素G的发光层7G与空穴阻挡层8不直接接触。

[0086] 在该情况下,从像素B的像素电极3导入的空穴的一部分,如箭头H所示在电子阻挡层6B内向像素B的外侧移动,并侵入到区域13,能够到达发光层7G。但是,从共用电极10导入的电子如箭头E所示,由电子阻挡层6B阻挡,不能够到达发光层7G。因此,在发光层7G内空穴与电子没有结合,能够防止在隔堤4上的非意图的发光。

[0087] 将第二实施方式中所示的电致发光显示装置200的构造更一般化地来表现的话,可以说至少在具有一个发光色的属于像素阵列的像素中,第二阻挡层的面积比发光层7的面积大。另外,由于具有这样的关系的像素阵列,在关于具有另一发光色的像素阵列的第二阻挡层和发光层7被形成之后形成,因此当将先形成的像素阵列的发光色称为一个发光色、而将在后形成的像素阵列的发光色称为另一发光色来表达时,在属于关于另一发光色的像素阵列的像素中,第二阻挡层的面积比发光层7的面积大。另外,此时,在属于关于一个发光色的像素阵列的像素中,第二阻挡层的面积可以与发光层7的面积相等。并且,其结果是,在隔堤4上,在属于以一个发光色发光的一个像素的发光层上局部地重叠属于以另一发光色发光的另一像素的第二阻挡层,由此能够降低隔堤4上的非意图的原色发光。另外,在设计上,在属于以一个发光色发光的一个像素的第二阻挡层上局部地重叠属于以另一发光色发光的另一像素的第二阻挡层(基于图4所示的例子来说明时,是指当将“以一个发光色发光的位置的像素”作为像素G、将“以另一发光色发光的另一像素”作为像素B时,在区域13中,电子阻挡层6G与电子阻挡层6B重叠)。

[0088] 图7是表示本发明的第三实施方式的电致发光显示装置300的构造的截面示意图。在本实施方式中,像素G的电子阻挡层6G和像素B的电子阻挡层6B的俯视时的面积,分别比像素G的发光层7G和像素B的发光层7B大,电子阻挡层6G、6B以向发光层7G、7B的周围突出的方式形成,这一点与第二实施方式的电致发光显示装置200相同。但是,仅电子阻挡层6G的形状与第二实施方式的电致发光显示装置200不同。

[0089] 如在图7所示的区域13所看到,像素G的电子阻挡层6G在与像素B相邻的部分中在设计上不从发光层7G突出,是相对于像素G的中心非对称的形状。另一方面,如在区域14所看到,像素G的电子阻挡层6G在与像素R相邻的部分中从发光层7G突出,变成与先前的第二实施方式的电致发光显示装置200相同(参照图4)。

[0090] 如先前所说明,由于像素G的电子阻挡层6G比像素B的电子阻挡层6B和发光层7B提前形成,电子阻挡层6G不会以重叠在电子阻挡层6B或发光层7B之上的方式形成。因此,即使电子阻挡层6G以从发光层7G向像素B侧突出的方式延长,也不能期待防止或者减少隔堤4上的相邻像素色的非意图的发光导致的混色、和非意图的原色发光的降低这样的效果,缺乏技术上的意义。因此,从减少制造上的材料的观点考虑,优选在与像素B相邻的区域中,将像素G的电子阻挡层6G的形状形成为与发光层6G相同形状。采用这样的设计的结果是,如图6所示,像素G的发光层7G的重心位置与像素G的重心位置一致,而电子阻挡层6G的重心位置向像素R侧偏置。

[0091] 当然,在此所说明的第三实施方式的电致发光显示装置300与第一实施方式的电致发光显示装置100、第二实施方式的电致发光显示装置200同样地,具有概率性地使隔堤4上的相邻像素色的非意图的发光导致的混色和非意图的原色发光减少的效果,并且,使电子阻挡层6的材料的使用量减少。在第三实施方式中,按图8所示说明使隔堤4上的相邻像素色的非意图的发光导致的混色和非意图的原色发光减少的例子。

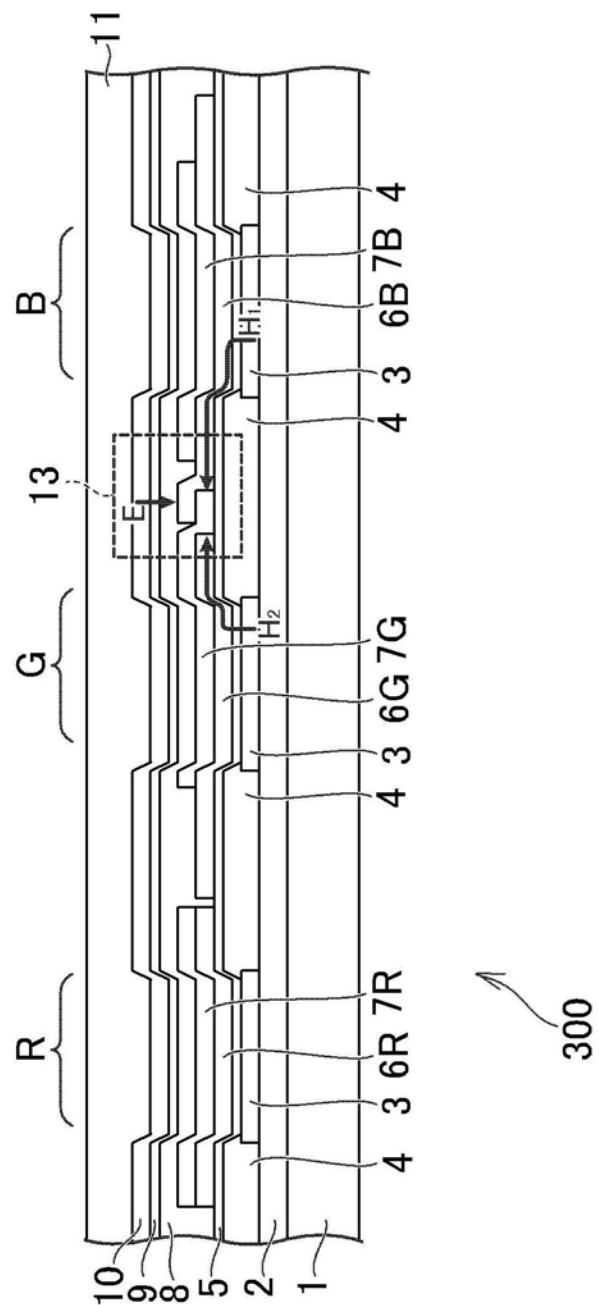

[0092] 图8中表示像素G的发光层7G向图中右侧偏离地形成的情况。此外,为了说明的方便,使其它的层中没有偏离地按照设计的位置(即,与图7所示的同样的位置)形成。这时,在电致发光显示装置300的截面的区域13中,发光层7G在隔堤4上与像素B的电子阻挡层6B重叠。但是,由于在电致发光显示装置300中,也是在形成像素G的发光层7G之后形成像素B的电子阻挡层6B,因此如图6所示,在隔堤4上,在向像素B侧延伸出的发光层7G之上形成电子阻挡层6B,像素G的发光层7G与空穴阻挡层8不直接接触。

[0093] 在该情况下,认为从像素B的像素电极3导入的空穴的一部分如箭头H1所示在电子阻挡层6B内向像素B的外侧移动,并侵入到区域13,能够到达发光层7G。但是,从共用电极10导入的电子如箭头E所示,由电子阻挡层6B阻挡,不能到达发光层7G。因此,在发光层7G内空穴与电子没有结合,能够防止隔堤4上的相邻像素色(这里说明的例子中是绿色)的非意图的发光。

[0094] 并且,认为从像素G的像素电极3导入的空穴的一部分,如箭头H2所示在电子阻挡层6G内向像素B侧移动,侵入到区域13中,并且在隔堤4上能够到达从电子阻挡层6G突出的发光层7G的部分。但是,在该情况下,从共用电极10导入的电子如箭头E所示,也由电子阻挡层6B阻挡,不能到达发光层7G。因此,在隔堤4上在从电子阻挡层6G突出的发光层7G内空穴与电子没有结合,能够减少隔堤4上的非意图的原色发光。

[0095] 本发明并不限于上述实施方式,能够进行各种变形。例如,能够用与上述实施方

式中所示的结构实质上相同的结构、起到相同的作用效果的结构、或者能够达成相同的目的的结构来置换。

[0096] 在本发明的思想范畴内,只要是作为本领域技术人员能够想到的各种变更例和修正例,关于这些变更例和修正例也理解为属于本发明的范围内。例如,对于上述的各实施方式,本领域技术人员进行了适当的构成要素的追加、删除或者设计变更而得的实施方式,或者工序的追加、省略或者条件变更而得的实施方式,只要具有本发明的主旨,也包括在本发明的范围内。

[0097] 尽管已经描述了当前被认为是本发明的一些实施例,但应该理解可以对其进行各种修改,旨在使落入本发明的真实精神和范围内的所有此类修改都包括在所附权利要求范围内。

相关技术

图1

相关技术

图2

图3

图4

图5

图6

图7

图8

|                |                                                                        |         |            |

|----------------|------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光显示装置和电致发光显示装置的制造方法                                                 |         |            |

| 公开(公告)号        | <a href="#">CN111435675A</a>                                           | 公开(公告)日 | 2020-07-21 |

| 申请号            | CN202010026337.5                                                       | 申请日     | 2020-01-10 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                              |         |            |

| 申请(专利权)人(译)    | 株式会社日本显示器                                                              |         |            |

| 当前申请(专利权)人(译)  | 株式会社日本显示器                                                              |         |            |

| [标]发明人         | 前田典久                                                                   |         |            |

| 发明人            | 前田典久                                                                   |         |            |

| IPC分类号         | H01L27/32 H01L51/56                                                    |         |            |

| CPC分类号         | H01L27/3246 H01L51/0011 H01L51/5036 H01L51/5096 H01L51/56 H01L2227/323 |         |            |

| 代理人(译)         | 徐飞跃                                                                    |         |            |

| 优先权            | 2019003253 2019-01-11 JP                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                         |         |            |

### 摘要(译)

本发明提供一种电致发光显示装置，其具有将以特定的颜色发光的像素规则地排列而构成的像素阵列，并且该像素阵列是彼此以不同的颜色发光的至少多个像素的阵列，在从观看方向看时，所述像素中依次层叠有共用电极(10)、第一阻挡层、发光层(7)、第二阻挡层和像素电极(3)，至少发光层(7)、所述第二阻挡层和像素电极(3)按每一个所述像素独立地设置，相邻的像素由隔堤(4)分隔，至少在所述像素阵列的一部分中，在隔堤(4)上，在属于一个像素的发光层(7)之上局部地重叠属于具有不同于所述一个像素的发光色的另一像素的所述第二阻挡层。根据本发明，能够降低相邻像素色的非意图的发光导致的混色和在隔堤上的原色发光的产生。