(12)发明专利申请

(10)申请公布号 CN 107665667 A

(43)申请公布日 2018.02.06

(21)申请号 201711034380.0

(22)申请日 2017.10.30

(71)申请人 王才旺

地址 452470 河南省郑州市登封市大金店

镇南寨村16号

(72)发明人 王才旺

(74)专利代理机构 郑州铭晟知识产权代理事务

所(特殊普通合伙) 41134

代理人 赵伦

(51)Int.Cl.

G09G 3/3216(2016.01)

权利要求书2页 说明书4页 附图1页

(54)发明名称

一种OLED显示屏无源交流驱动系统

(57)摘要

本发明公开了一种OLED显示屏无源交流驱动系统,包括依次相连的控制装置及驱动装置,驱动装置包括行驱动模块和列驱动模块,行驱动模块和列驱动模块分别产生行驱动信号和列驱动信号,控制装置的输出端分别与行驱动模块和列驱动模块相连,行驱动模块和列驱动模块的输出端分别与OLED显示屏相连;控制装置采用单片机,单片机用于产生点亮OLED显示屏的控制信号和显示信号,单片机向驱动装置传输所需的控制信号和显示数据,驱动装置用于产生行驱动信号和列驱动信号,并把显示数据输出到OLED显示屏上显示。本发明不仅制作工艺简单,而且能够很好地解决OLED显示屏显示亮度不均匀的问题,保证OLED显示屏安全稳定地工作。

1. 一种OLED显示屏无源交流驱动系统,其特征在于:包括依次相连的控制装置及驱动装置,驱动装置包括行驱动模块和列驱动模块,行驱动模块和列驱动模块分别产生行驱动信号和列驱动信号,控制装置的输出端分别与行驱动模块和列驱动模块相连,行驱动模块和列驱动模块的输出端分别与OLED显示屏相连。

2. 如权利要求1所述的一种OLED显示屏无源交流驱动系统,其特征在于:所述控制装置采用单片机,单片机用于产生点亮OLED显示屏的控制信号和显示信号,单片机向驱动装置传输所需的控制信号和显示数据,驱动装置用于产生行驱动信号和列驱动信号,并把显示数据输出到OLED显示屏上显示。

3. 如权利要求2所述的一种OLED显示屏无源交流驱动系统,其特征在于:所述行驱动模块采用6-64译码器,所述6-64译码器采用4片带两位锁存输入端的4-16译码器级联形成,行号的输入通过6位地址线实现,将行号的低四位并联作为统一的输入端与各片的A、B、C、D端相连,行号的高四位通过两个非门组合变换为四种不同的逻辑,将这四种不同逻辑作为四片译码器的片选信号。

4. 如权利要求2所述的一种OLED显示屏无源交流驱动系统,其特征在于:所述列驱动模块包括并串转换电路、数据传输电路及驱动输出电路,所述并串转换电路采用输出移位寄存器,输出移位寄存器的并行异步输入端与单片机的输出端相连,输出移位寄存器的串行输入端和输出端分别与数据传输电路相连;

所述数据传输电路采用4片存储状态寄存器级联,分别为第一存储状态寄存器、第二存储状态寄存器、第三存储状态寄存器及第四存储状态寄存器,所述第一存储状态寄存器、第二存储状态寄存器、第三存储状态寄存器及第四存储状态寄存器的串行数据输入端分别与输出移位寄存器的输出端相连,所述第一存储状态寄存器的串行输出端与第二存储状态寄存器的串行数据输入端相连,第二存储状态寄存器的串行输出端与第三存储状态寄存器的串行数据输入端相连,第三存储状态寄存器的串行输出端与第四存储状态寄存器的串行数据输入端相连,第四存储状态寄存器的串行数据输出端与驱动输出电路相连;

所述驱动输出电路包括MOSFET管、第一三极管、第二三极管、第三三极管及第四三极管,所述MOSFET管的栅极与第四存储状态寄存器的串行数据输出端相连,MOSFET管的源极接地,MOSFET管的漏极依次经第一电阻和第二电阻与第一三极管的集电极相连,第一电阻与第二电阻的公共端连接电源正极,第一三极管的发射极经第三电阻接地,第一三极管的基极与第一三极管的发射极相连,第一三极管的基极还与第二三极管的基极相连,第二三极管的发射极经第四电阻与第一电阻和第二电阻的公共端相连,第二三极管的集电极与第三三极管的发射极相连,第三三极管的基极经第五电阻与MOSFET管的漏极相连,第三三极管的集电极与第四三极管的集电极相连,第四三极管的基极经第六电阻与MOSFET管的漏极相连,所述第四三极管的发射极与OLED显示屏相连。

5. 如权利要求4所述的一种OLED显示屏无源交流驱动系统,其特征在于:所述并串转换电路还包括第一非门、第二非门、第一与门、第二与门、第三与门及第四与门,第一非门的输入端与输出移位寄存器的串行数据输入端相连,第一非门的输出端与第一与门的第一输入端相连,第一与门的第二输入端与第二与门的第一输入端相连,第二与门的第二输入端与输出移位寄存器的串行数据输入端相连,所述第一与门和第二与门的输出端分别与第一存储状态寄存器的移位寄存器时钟输入端和第二存储状态寄存器的移位寄存器时钟输入端

相连；所述第二非门的输入端与输出移位寄存器的串行数据输入端相连，第二非门的输出端与第三与门的第一输入端相连，第三与门的第二输入端与第四与门的第一输入端相连，第四与门的第二输入端与输出移位寄存器的串行数据输入端相连，所述第三与门和第四与门的输出端分别与第三存储状态寄存器的移位寄存器时钟输入端和第四存储状态寄存器的移位寄存器时钟输入端相连。

6. 如权利要求5所述的一种OLED显示屏无源交流驱动系统，其特征在于：所述输出移位寄存器采用74HC165系列移位寄存器，存储状态寄存器采用74HC595系列数据存储器。

## 一种OLED显示屏无源交流驱动系统

### 技术领域

[0001] 本发明涉及有机发光二极管领域,尤其涉及一种OLED显示屏无源交流驱动系统。

### 背景技术

[0002] OLED(有机发光二极管)是一种新型的显示器件,具有主动发光、重量轻、厚度薄、响应快及效率高的优点,可以在各种恶劣环境下工作,近几年在显示技术领域得到了广泛的应用。

[0003] OLED显示屏为了能灵活地显示更多的图像和文字信息,通常把屏幕制作成点阵结构,通过控制每个点的亮度来构成具有灰度的点阵图像。为了节约驱动电路的硬件开销,目前多有OLED显示屏的驱动均采用矩阵驱动方式,根据每个像素中未引入和引入开关元器件将屏幕分为无源矩阵和有源矩阵。有源矩阵需要为每个像素设置一个薄膜晶体管,工作效率高,工作电流小,但是对于设备要求较高,且工艺复杂,不适合大范围使用。

### 发明内容

[0004] 本发明的目的在于提供一种OLED显示屏无源交流驱动系统,不仅制作工艺简单,而且能够很好地解决OLED显示屏显示亮度不均匀的问题,保证OLED显示屏安全稳定地工作。

[0005] 为实现上述目的,本发明采用如下技术方案:

一种OLED显示屏无源交流驱动系统,包括依次相连的控制装置及驱动装置,驱动装置包括行驱动模块和列驱动模块,行驱动模块和列驱动模块分别产生行驱动信号和列驱动信号,控制装置的输出端分别与行驱动模块和列驱动模块相连,行驱动模块和列驱动模块的输出端分别与OLED显示屏相连。

[0006] 优选地,所述控制装置采用单片机,单片机用于产生点亮OLED显示屏的控制信号和显示信号,单片机向驱动装置传输所需的控制信号和显示数据,驱动装置用于产生行驱动信号和列驱动信号,并把显示数据输出到OLED显示屏上显示。

[0007] 优选地,所述行驱动模块采用6-64译码器,所述6-64译码器采用4片带两位锁存输入端的4-16译码器级联形成,行号的输入通过6位地址线实现,将行号的低四位并联作为统一的输入端与各片的A、B、C、D端相连,行号的高四位通过两个非门组合变换为四种不同的逻辑,将这四种不同逻辑作为四片译码器的片选信号。

[0008] 优选地,所述列驱动模块包括并串转换电路、数据传输电路及驱动输出电路,所述并串转换电路采用输出移位寄存器,输出移位寄存器的并行异步输入端与单片机的输出端相连,输出移位寄存器的串行输入端和输出端分别与数据传输电路相连;

所述数据传输电路采用4片存储状态寄存器级联,分别为第一存储状态寄存器、第二存储状态寄存器、第三存储状态寄存器及第四存储状态寄存器,所述第一存储状态寄存器、第二存储状态寄存器、第三存储状态寄存器及第四存储状态寄存器的串行数据输入端分别与输出移位寄存器的输出端相连,所述第一存储状态寄存器的串行输出端与第二存储状态寄

存器的串行数据输入端相连,第二存储状态寄存器的串行输出端与第三存储状态寄存器的串行数据输入端相连,第三存储状态寄存器的串行输出端与第四存储状态寄存器的串行数据输入端相连,第四存储状态寄存器的串行数据输出端与驱动输出电路相连;

所述驱动输出电路包括MOSFET管、第一三极管、第二三极管、第三三极管及第四三极管,所述MOSFET管的栅极与第四存储状态寄存器的串行数据输出端相连,MOSFET管的源极接地,MOSFET管的漏极依次经第一电阻和第二电阻与第一三极管的集电极相连,第一电阻与第二电阻的公共端连接电源正极,第一三极管的发射极经第三电阻接地,第一三极管的基极与第一三极管的发射极相连,第一三极管的基极还与第二三极管的基极相连,第二三极管的发射极经第四电阻与第一电阻和第二电阻的公共端相连,第二三极管的集电极与第三三极管的发射极相连,第三三极管的基极经第五电阻与MOSFET管的漏极相连,第三三极管的集电极与第四三极管的集电极相连,第四三极管的基极经第六电阻与MOSFET管的漏极相连,所述第四三极管的发射极与OLED显示屏相连

优选地,所述并串转换电路还包括第一非门、第二非门、第一与门、第二与门、第三与门及第四与门,第一非门的输入端与输出移位寄存器的串行数据输入端相连,第一非门的输出端与第一与门的第一输入端相连,第一与门的第二输入端与第二与门的第一输入端相连,第二与门的第二输入端与输出移位寄存器的串行数据输入端相连,所述第一与门和第二与门的输出端分别与第一存储状态寄存器的移位寄存器时钟输入端和第二存储状态寄存器的移位寄存器时钟输入端相连;所述第二非门的输入端与输出移位寄存器的串行数据输入端相连,第二非门的输出端与第三与门的第一输入端相连,第三与门的第二输入端与第四与门的第一输入端相连,第四与门的第二输入端与输出移位寄存器的串行数据输入端相连,所述第三与门和第四与门的输出端分别与第三存储状态寄存器的移位寄存器时钟输入端和第四存储状态寄存器的移位寄存器时钟输入端相连。

[0009] 优选地,所述输出移位寄存器采用74HC165系列移位寄存器,存储状态寄存器采用74HC595系列数据存储器。

[0010] 本发明通过控制装置产生用于点亮OLED显示屏的控制信号和显示信号,驱动装置产生行驱动信号和列驱动信号,并把显示数据输出到OLED显示屏上显示,不仅制作工艺简单,而且能够很好地解决OLED显示屏显示亮度不均匀的问题,保证OLED显示屏安全稳定地工作。

## 附图说明

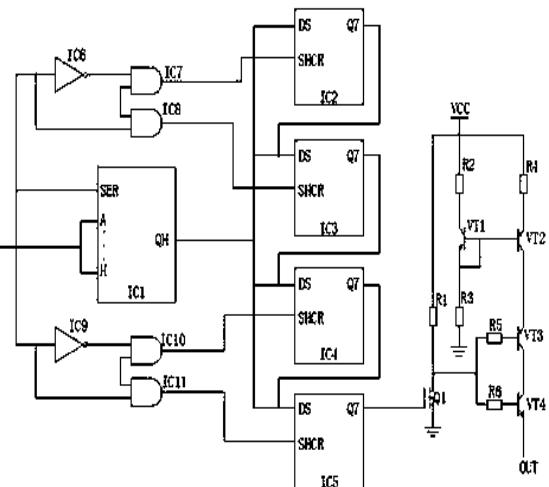

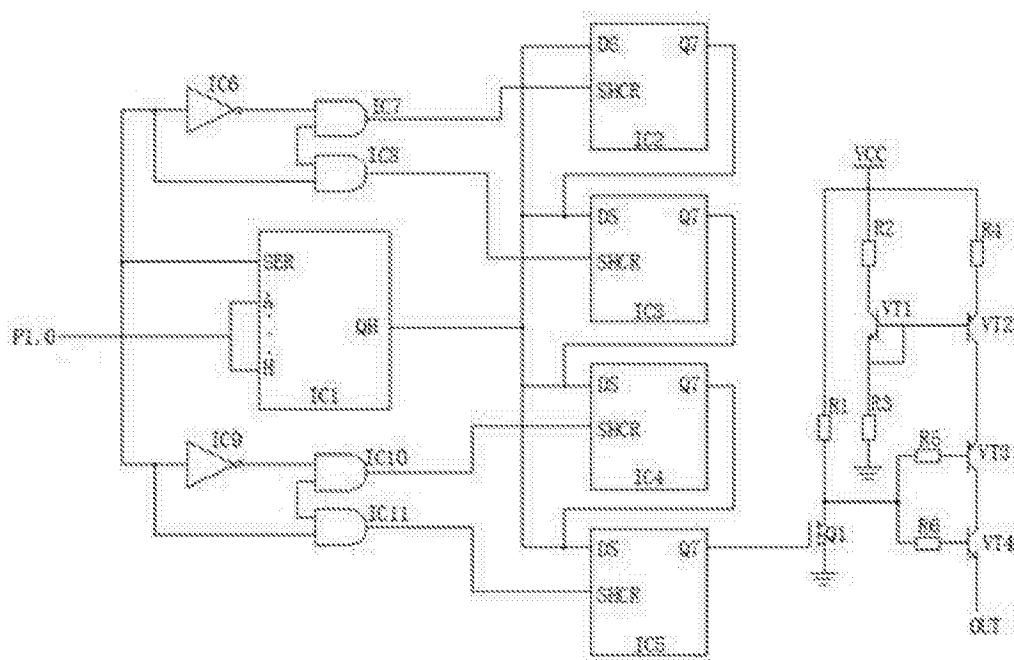

[0011] 图1为本发明所述列驱动模块的电路原理图。

## 具体实施方式

[0012] 以下结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的其他所有实施例,都属于本发明的保护范围。

[0013] 如图1所示,本发明所述的一种OLED显示屏无源交流驱动系统,包括依次相连的控制装置及驱动装置,驱动装置包括行驱动模块和列驱动模块,行驱动模块和列驱动模块分

别产生行驱动信号和列驱动信号,控制装置的输出端分别与行驱动模块和列驱动模块相连,行驱动模块和列驱动模块的输出端分别与OLED显示屏相连;控制装置采用单片机,单片机用于产生点亮OLED显示屏的控制信号和显示信号,单片机向驱动装置传输所需的控制信号和显示数据,驱动装置用于产生行驱动信号和列驱动信号,并把显示数据输出到OLED显示屏上显示。

[0014] 行驱动模块采用6-64译码器,所述6-64译码器采用4片带两位锁存输入端的4-16译码器级联形成,行号的输入通过6位地址线实现,将行号的低四位并联作为统一的输入端与各片的A、B、C、D端相连,行号的高四位通过两个非门组合变换为四种不同的逻辑,将这四种不同逻辑作为四片译码器的片选信号。

[0015] 列驱动模块包括依次相连的并串转换电路、数据传输电路及驱动输出电路,并串转换电路包括输出移位寄存器IC1、第一非门IC6、第二非门IC9、第一与门IC7、第二与门IC8、第三与门IC10及第四与门IC11,输出移位寄存器IC1的并行异步输入端A-H与单片机的输出端相连,输出移位寄存器IC1的输出端QH与数据传输电路相连,输出移位寄存器IC1的串行数据输入端SER与第一非门IC6的输入端与相连,第一非门IC6的输出端与第一与门IC7的第一输入端相连,第一与门IC7的第二输入端与第二与门IC8的第一输入端相连,第二与门IC8的第二输入端与输出移位寄存器IC1的串行数据输入端SER相连,第一与门IC7和第二与门IC8的输出端分别与数据传输电路相连,输出移位寄存器IC1的串行数据输入端SER还与第二非门IC9的输入端相连,第二非门IC9的输出端与第三与门IC10的第一输入端相连,第三与门IC10的第二输入端与第四与门IC11的第一输入端相连,第四与门IC11的第二输入端与输出移位寄存器IC1的串行数据输入端SER相连,第三与门IC10和第四与门IC11的输出端分别与数据传输电路相连。

[0016] 数据传输电路采用4片存储状态寄存器级联,分别为第一存储状态寄存器IC2、第二存储状态寄存器IC3、第三存储状态寄存器IC4及第四存储状态寄存器IC5,一存储状态寄存器IC2、第二存储状态寄存器IC3、第三存储状态寄存器IC4及第四存储状态寄存器IC5的串行数据输入端DS分别与输出移位寄存器IC1的输出端QH相连,第一存储状态寄存器IC2的串行输出端Q7与第二存储状态寄存器IC3的串行数据输入端DS相连,第二存储状态寄存器IC3的串行输出端Q7与第三存储状态寄存器IC4的串行数据输入端DS相连,第三存储状态寄存器IC4的串行输出端Q7与第四存储状态寄存器IC5的串行数据输入端DS相连,第四存储状态寄存器IC5的串行数据输出端Q7与驱动输出电路相连,第一存储状态寄存器IC2的移位寄存器时钟输入端SHCR与第一与门IC7的输出端相连,第二存储状态寄存器IC3的移位寄存器时钟输入端SHCR与第二与门IC8的输出端相连,第三存储状态寄存器IC4的移位寄存器时钟输入端SHCR与第三与门IC10的输出端相连,第四存储状态寄存器IC5的移位寄存器时钟输入端SHCR与第四与门IC11的输出端相连。

[0017] 驱动输出电路包括MOSFET管Q1、第一三极管VT1、第二三极管VT2、第三三极管VT3及第四三极管VT4,MOSFET管Q1的栅极与第四存储状态寄存器IC5的串行数据输出端Q7相连,MOSFET管Q1的源极接地,MOSFET管Q1的漏极依次经第一电阻R1和第二电阻R2与第一三极管VT1的集电极相连,第一电阻R1与第二电阻R2的公共端连接电源正极VCC,第一三极管VT1的发射极经第三电阻R3接地,第一三极管VT1的基极与第一三极管VT1的发射极相连,第一三极管VT1的基极还与第二三极管VT2的基极相连,第二三极管VT2的发射极经第四电阻

R4与第一电阻R1和第二电阻R2的公共端相连,第二三极管VT2的集电极与第三三极管VT3的发射极相连,第三三极管VT3的基极经第五电阻R5与MOSFET管Q1的漏极相连,第三三极管VT3的集电极与第四三极管VT4的集电极相连,第四三极管VT4的基极经第六电阻R6与MOSFET管Q1的漏极相连,第四三极管VT4的发射极与OLED显示屏相连。

[0018] 在本实施例中,输出移位寄存器IC1采用74HC165系列移位寄存器,存储状态寄存器IC2-IC5均采用74HC595系列数据存储器。

[0019] 本发明能够很好地解决OLED显示屏显示亮度不均匀的问题,保证OLED显示屏安全稳定地工作。

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 一种OLED显示屏无源交流驱动系统                              |         |            |

| 公开(公告)号 | <a href="#">CN107665667A</a>                   | 公开(公告)日 | 2018-02-06 |

| 申请号     | CN201711034380.0                               | 申请日     | 2017-10-30 |

| [标]发明人  | 王才旺                                            |         |            |

| 发明人     | 王才旺                                            |         |            |

| IPC分类号  | G09G3/3216                                     |         |            |

| CPC分类号  | G09G3/3216                                     |         |            |

| 代理人(译)  | 赵伦                                             |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种OLED显示屏无源交流驱动系统，包括依次相连的控制装置及驱动装置，驱动装置包括行驱动模块和列驱动模块，行驱动模块和列驱动模块分别产生行驱动信号和列驱动信号，控制装置的输出端分别与行驱动模块和列驱动模块相连，行驱动模块和列驱动模块的输出端分别与OLED显示屏相连；控制装置采用单片机，单片机用于产生点亮OLED显示屏的控制信号和显示信号，单片机向驱动装置传输所需的控制信号和显示数据，驱动装置用于产生行驱动信号和列驱动信号，并把显示数据输出到OLED显示屏上显示。本发明不仅制作工艺简单，而且能够很好地解决OLED显示屏显示亮度不均匀的问题，保证OLED显示屏安全稳定地工作。