(12)发明专利申请

(10)申请公布号 CN 109166865 A

(43)申请公布日 2019.01.08

(21)申请号 201810896463.9

H01L 51/56(2006.01)

(22)申请日 2018.08.08

H01L 21/84(2006.01)

(71)申请人 深圳市华星光电技术有限公司

H01L 21/44(2006.01)

地址 518132 广东省深圳市光明新区塘明

大道9-2号

H01L 21/34(2006.01)

(72)发明人 周星宇

(74)专利代理机构 深圳市威世博知识产权代理

事务所(普通合伙) 44280

代理人 钟子敏

(51)Int.Cl.

H01L 27/12(2006.01)

H01L 27/32(2006.01)

H01L 29/417(2006.01)

H01L 29/786(2006.01)

H01L 51/52(2006.01)

权利要求书2页 说明书6页 附图4页

(54)发明名称

阵列基板及其制造方法、显示面板

(57)摘要

本申请公开一种阵列基板及其制造方法、显示面板。本申请设计源极图案和漏极图案直接形成于介电层上，通过介电层取代传统的平坦层和钝化层，且所述漏极图案同时也作为OLED器件的阳极图案，从而能够减少光罩制程，并且所述介电层采用遮光材料制得，能够保护TFT的沟道层不受到光照影响，有利于确保其性能稳定。

1. 一种阵列基板的制造方法,其特征在于,所述方法包括:

提供一衬底基板,所述衬底基板的上方包括沿平行于衬底基板的方向相邻的第一区域和第二区域;

在衬底基板上依次形成第一导电层和缓冲层,所述第一导电层包括位于第一区域的第一遮光图案和第二区域的第二遮光图案;

在所述缓冲层上形成位于第一遮光图案上方的半导体图案;

依次形成绝缘层和第二导电层,所述绝缘层包括位于第一区域的第一绝缘图案,所述第二导电层包括位于第一区域的第一栅极图案,所述第一绝缘图案位于所述半导体图案上;

形成覆盖所述第二导电层、半导体图案和缓冲层的介电层,所述介电层采用遮光材料制得且在第一区域设有第一接触孔和第二接触孔、在第二区域设有开口区,所述缓冲层在所述开口区暴露其表面;

在所述介电层上形成第三导电层,所述第三导电层包括位于第一区域的源极图案及跨越第一区域和第二区域的漏极图案,所述源极图案和漏极图案分别覆盖所述第一接触孔和第二接触孔并与半导体图案接触,所述漏极图案还覆盖所述开口区并与缓冲层接触,所述漏极图案与第二遮光图案至少部分重叠并通过夹设于两者之间的缓冲层形成一电容;

在所述源极图案和漏极图案上形成像素定义层,所述像素定义层设有用于限定所述阵列基板的发光区;

在所述发光区依次形成位于漏极图案上的发光层和阴极图案。

2. 根据权利要求1所述的方法,其特征在于,所述衬底基板的上方还包括与所述第二区域相邻且远离所述第一区域的第三区域,所述第二遮光图案跨越所述第二区域和第三区域,所述绝缘层还包括位于第三区域且位于所述缓冲层上的第二绝缘图案,所述第二导电层还包括位于第三区域的第二栅极图案,所述介电层在所述第三区域设有第三接触孔和第四接触孔,所述第三导电层还包括位于第三区域的桥接图案,所述桥接图案覆盖所述第三接触孔与所述第二栅极图案接触以及覆盖所述第四接触孔与所述第二遮光图案接触。

3. 根据权利要求2所述的方法,其特征在于,形成覆盖所述第二导电层、半导体图案和缓冲层的介电层这一步骤,包括:

形成覆盖所述第二导电层、半导体图案和缓冲层的一整面介电层;

在所述一整面介电层上形成一整面光刻胶;

采用半色调光罩对所述一整面光刻胶进行曝光及显影处理,所述半色调光罩包括完全曝光区、半曝光区和非曝光区,在显影处理之后,位于所述完全曝光区下方的光刻胶被去除,位于所述半曝光区下方的光刻胶的厚度小于位于所述非曝光区下方的光刻胶的厚度;

刻蚀去除所述完全曝光区下方的介电层,以形成所述第一接触孔、第二接触孔、开口区和第三接触孔;

灰化去除所述半曝光区下方的光刻胶;

刻蚀去除所述半曝光区下方的介电层和缓冲层,以形成所述第四接触孔;

灰化去除所述非曝光区下方的光刻胶。

4. 根据权利要求2所述的方法,其特征在于,形成覆盖所述第二导电层、半导体图案和缓冲层的介电层这一步骤,包括:

采用第一道光罩制程形成所述第一接触孔、第二接触孔、开口区和第三接触孔；

采用第二道光罩制程形成所述第四接触孔。

5. 根据权利要求2所述的方法，其特征在于，依次形成绝缘层和第二导电层这一步骤，包括：

在所述缓冲层上依次形成覆盖所述半导体图案的一整面绝缘层和一整面第二导电层；

利用一道光罩制程对所述一整面第二导电层进行图案化处理；

利用经过图案化处理的第二导电层为刻蚀屏蔽对所述一整面绝缘层进行刻蚀。

6. 根据权利要求1～5任一项所述的方法，其特征在于，采用黑色光阻、丙烯酸树脂及聚酰亚胺中至少一者形成所述介电层。

7. 一种阵列基板，其特征在于，所述阵列基板包括：

衬底基板，所述衬底基板的上方包括沿平行于衬底基板的方向依次相邻的第一区域和第二区域；

依次形成于衬底基板上的第一导电层和缓冲层，所述第一导电层包括位于第一区域的第一遮光图案和第二区域的第二遮光图案；

形成于所述缓冲层上且位于第一遮光图案上方的半导体图案；

绝缘层和位于所述绝缘层上的第二导电层，所述绝缘层包括位于第一区域的第一绝缘图案，所述第二导电层包括位于第一区域的第一栅极图案，所述第一绝缘图案位于所述半导体图案上；

覆盖所述第二导电层、半导体图案和缓冲层的介电层，所述介电层采用遮光材料制得且在第一区域设有第一接触孔和第二接触孔、在第二区域设有开口区，所述缓冲层在所述开口区暴露其表面；

位于所述介电层上的第三导电层，所述第三导电层包括位于第一区域的源极图案及跨越第一区域和第二区域的漏极图案，所述源极图案和漏极图案分别覆盖第一接触孔和第二接触孔并与半导体图案接触，所述漏极图案还覆盖所述开口区并与缓冲层接触，所述漏极图案与第二遮光图案至少部分重叠并通过夹设于两者之间的缓冲层形成一电容；

形成于所述源极图案和漏极图案上的像素定义层，所述像素定义层设有用于限定所述阵列基板的发光区；

形成于所述发光区且依次位于漏极图案上的发光层和阴极图案。

8. 根据权利要求7所述的阵列基板，其特征在于，所述衬底基板的上方还包括与所述第二区域相邻且远离所述第一区域的第三区域，所述第二遮光图案跨越所述第二区域和第三区域，所述绝缘层还包括位于第三区域且位于所述缓冲层上的第二绝缘图案，所述第二导电层还包括位于第三区域的第二栅极图案，所述介电层在所述第三区域设有第三接触孔和第四接触孔，所述第三导电层还包括位于第三区域的桥接图案，所述桥接图案覆盖所述第三接触孔与所述第二栅极图案接触以及覆盖所述第四接触孔与所述第二遮光图案接触。

9. 根据权利要求7所述的阵列基板，其特征在于，所述介电层的材料包括黑色光阻、丙烯酸树脂及聚酰亚胺中的至少一者。

10. 一种显示面板，其特征在于，所述显示面板包括如上述权利要求7～9任一项所述的阵列基板。

## 阵列基板及其制造方法、显示面板

### 技术领域

[0001] 本申请涉及显示领域,具体涉及一种阵列基板及其制造方法、显示面板。

### 背景技术

[0002] 当前,以金属氧化物(Oxide)半导体来制备沟道层的TFT(Thin Film Transistor,薄膜晶体管),已广泛应用于OLED(Organic Light-Emitting Diode,有机发光二极管)显示面板中,这其中顶栅型TFT由于寄生电容小更是成为业界首选。但是制备顶具有栅型TFT的阵列基板(Array基板)所需的光罩(Mask)制程较多,导致制造流程繁多,无法降低生产成本,并且,沟道层容易受到光照影响而性能不稳定。

### 发明内容

[0003] 有鉴于此,本申请提供一种阵列基板及其制造方法、显示面板,能够减少光罩制程,并有利于减少光照对TFT的沟道层的影响。

[0004] 本申请一实施例的阵列基板的制造方法,包括:

[0005] 提供一衬底基板,所述衬底基板的上方包括沿平行于衬底基板的方向相邻的第一区域和第二区域;

[0006] 在衬底基板上依次形成第一导电层和缓冲层,所述第一导电层包括位于第一区域的第一遮光图案和第二区域的第二遮光图案;

[0007] 在所述缓冲层上形成位于第一遮光图案上方的半导体图案;

[0008] 依次形成绝缘层和第二导电层,所述绝缘层包括位于第一区域的第一绝缘图案,所述第二导电层包括位于第一区域的第一栅极图案,所述第一绝缘图案位于所述半导体图案上;

[0009] 形成覆盖所述第二导电层、半导体图案和缓冲层的介电层,所述介电层采用遮光材料制得且在第一区域设有第一接触孔和第二接触孔、在第二区域设有开口区,所述缓冲层在所述开口区暴露其表面;

[0010] 在所述介电层上形成第三导电层,所述第三导电层包括位于第一区域的源极图案及跨越第一区域和第二区域的漏极图案,所述源极图案和漏极图案分别覆盖所述第一接触孔和第二接触孔并与半导体图案接触,所述漏极图案还覆盖所述开口区并与缓冲层接触,所述漏极图案与第二遮光图案至少部分重叠并通过夹设于两者之间的缓冲层形成一电容;

[0011] 在所述源极图案和漏极图案上形成像素定义层,所述像素定义层设有用于限定所述阵列基板的发光区;

[0012] 在所述发光区依次形成位于漏极图案上的发光层和阴极图案。

[0013] 本申请一实施例的阵列基板,包括:

[0014] 衬底基板,所述衬底基板的上方包括沿平行于衬底基板的方向依次相邻的第一区域和第二区域;

[0015] 依次形成于衬底基板上的第一导电层和缓冲层,所述第一导电层包括位于第一区

域的第一遮光图案和第二区域的第二遮光图案；

[0016] 形成于所述缓冲层上且位于第一遮光图案上方的半导体图案；

[0017] 绝缘层和位于所述绝缘层上的第二导电层，所述绝缘层包括位于第一区域的第一绝缘图案，所述第二导电层包括位于第一区域的第一栅极图案，所述第一绝缘图案位于所述半导体图案上；

[0018] 覆盖所述第二导电层、半导体图案和缓冲层的介电层，所述介电层采用遮光材料制得且在第一区域设有第一接触孔和第二接触孔、在第二区域设有开口区，所述缓冲层在所述开口区暴露其表面；

[0019] 位于所述介电层上的第三导电层，所述第三导电层包括位于第一区域的源极图案及跨越第一区域和第二区域的漏极图案，所述源极图案和漏极图案分别覆盖第一接触孔和第二接触孔并与半导体图案接触，所述漏极图案还覆盖所述开口区并与缓冲层接触，所述漏极图案与第二遮光图案至少部分重叠并通过夹设于两者之间的缓冲层形成一电容；

[0020] 形成于所述源极图案和漏极图案上的像素定义层，所述像素定义层设有用于限定所述阵列基板的发光区；

[0021] 形成于所述发光区且依次位于漏极图案上的发光层和阴极图案。

[0022] 本申请一实施例的显示面板，包括上述阵列基板。

[0023] 有益效果：本申请设计源极图案和漏极图案直接形成于介电层上，通过介电层取代传统的平坦层和钝化层，且漏极图案同时也作为阳极图案，从而能够减少光罩制程，并且所述介电层采用遮光材料制得，能够保护TFT的沟道层不受到光照影响，有利于确保其性能稳定。

## 附图说明

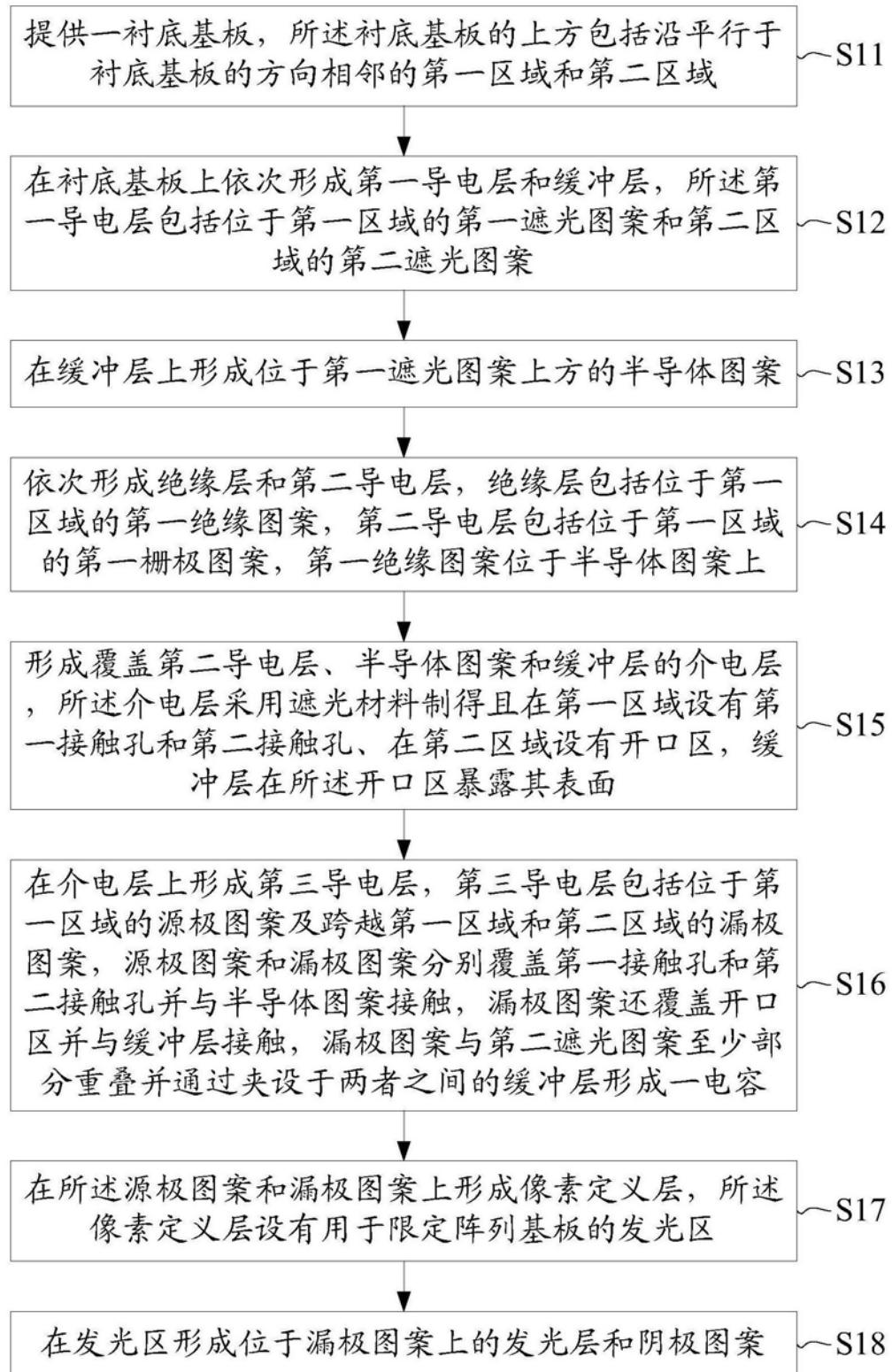

[0024] 图1是本申请的阵列基板的制造方法一实施例的流程示意图；

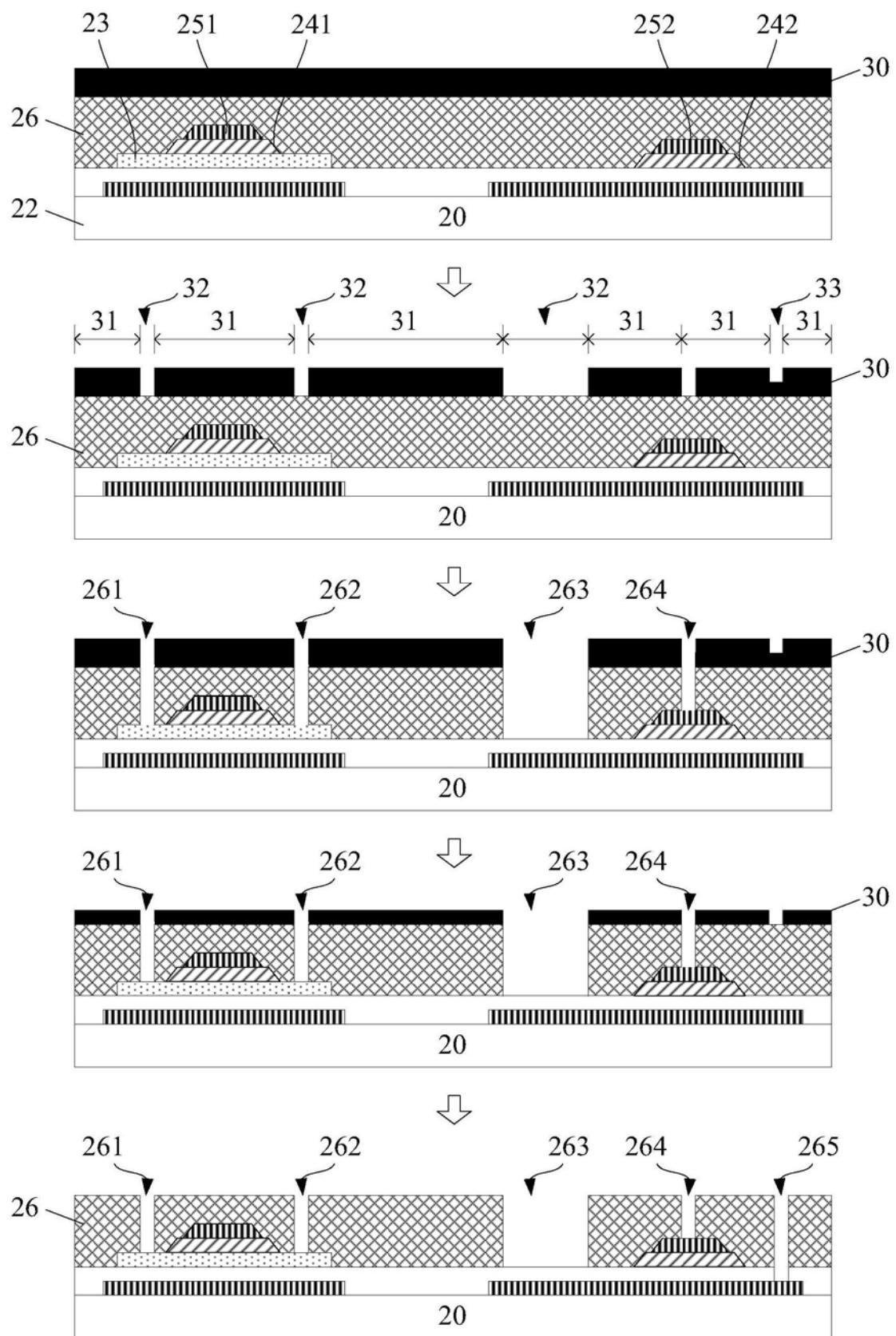

[0025] 图2是基于图1所示方法制造阵列基板的场景示意图；

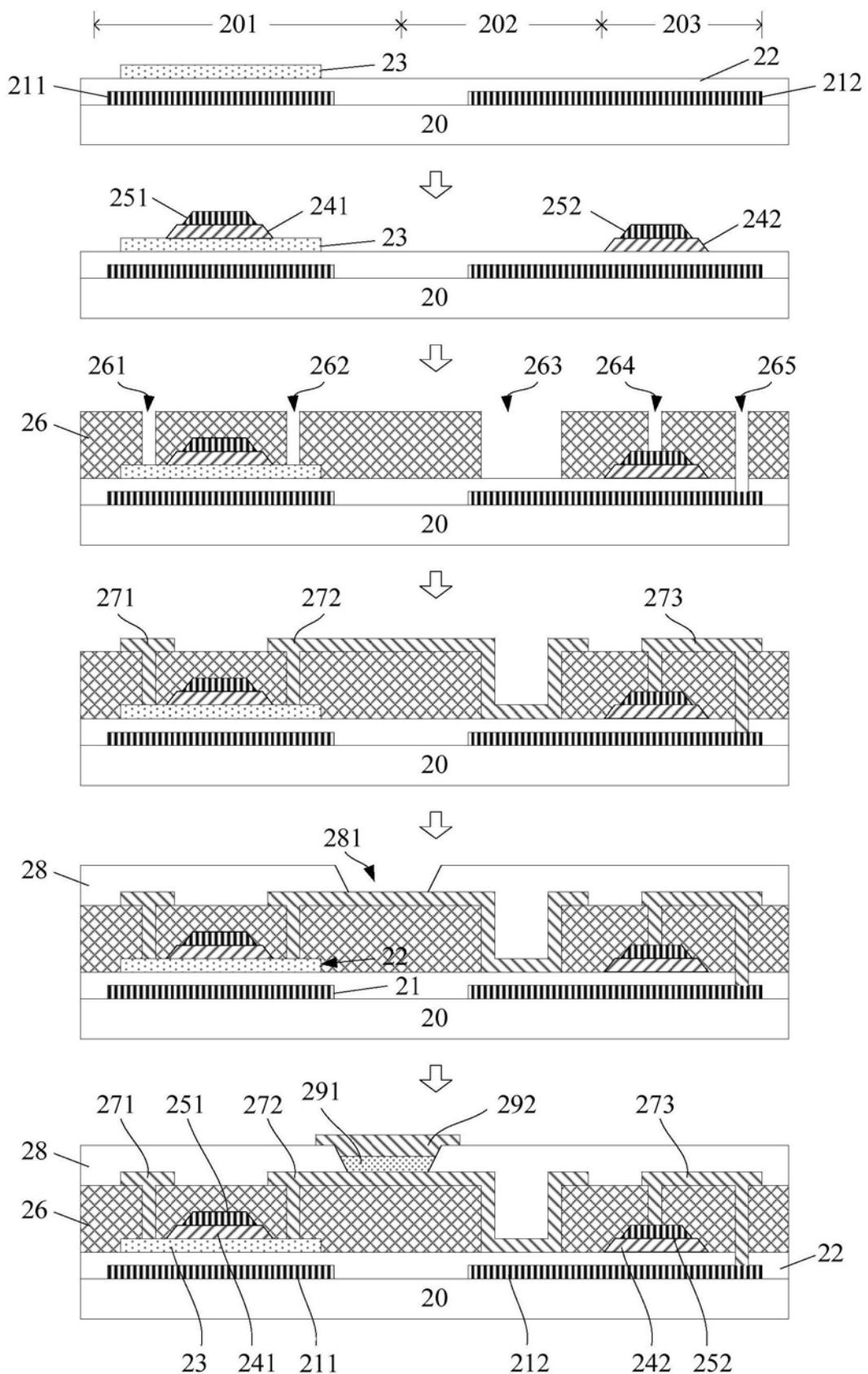

[0026] 图3是本申请形成图2所示的介电层的场景示意图；

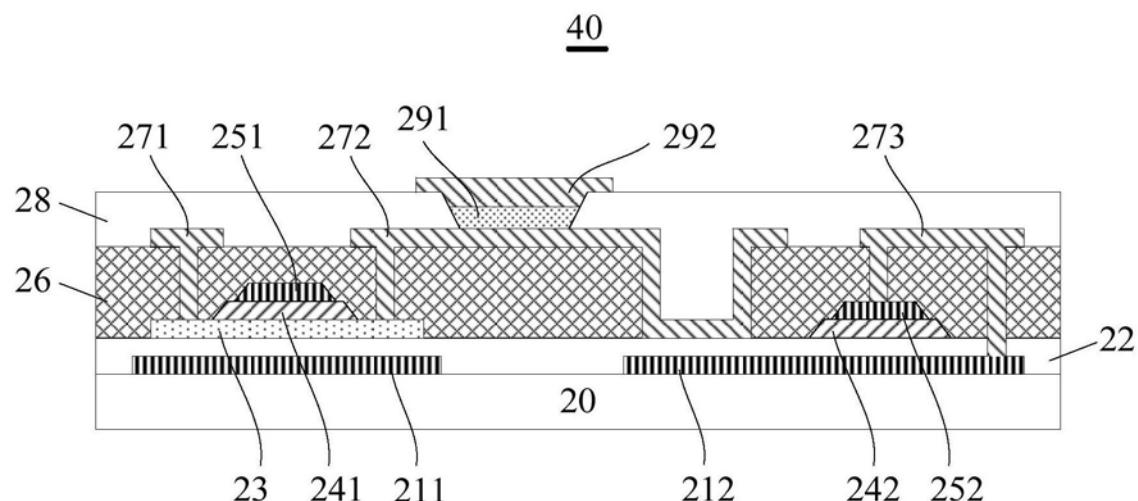

[0027] 图4是本申请一实施例的阵列基板的结构示意图。

## 具体实施方式

[0028] 下面结合本申请实施例中的附图，对本申请所提供的各个示例性的实施例的技术方案进行清楚、完整地描述。在不冲突的情况下，下述各个实施例以及实施例中的特征可以相互组合。并且，本申请全文所采用的方向性术语，例如“上”、“下”等，均是为了更好的描述各个实施例的技术方案，并非用于限制本申请的保护范围。

[0029] 图1是本申请的阵列基板的制造方法一实施例的流程示意图，图2是基于图1所示方法制造阵列基板的场景示意图。结合图1和图2所示，所述制造方法可以包括如下步骤S11～S18。

[0030] S11：提供一衬底基板，所述衬底基板的上方包括沿平行于衬底基板的方向相邻的第一区域和第二区域。

[0031] 所述衬底基板20可以为玻璃基体、塑料基体或可挠式基体，而对于制造柔性OLED显示面板的阵列基板的场景，该衬底基板20也可以为柔性基板，例如PI (Polyimide, 聚酰亚

胺)基板。

[0032] 所述衬底基板20的上方包括相邻的第一区域201和第二区域202,该第一区域201为阵列基板的TFT区,第二区域202为阵列基板的电容区,该电容区的存储电容可用于补偿像素区域的漏电。

[0033] S12:在衬底基板上依次形成第一导电层和缓冲层,所述第一导电层包括位于第一区域的第一遮光图案和第二区域的第二遮光图案。

[0034] 所述第一遮光图案(Light Shielding Metal,LS)211和第二遮光图案212的材质可以相同,例如均为钼、铝、铜或钛,也可以为金属合金,两者的厚度也可以相同,例如厚度均为500~2000Å。

[0035] 本申请可以通过一道光罩制程Mask-1形成该第一遮光图案211和第二遮光图案212。具体地,对衬底基板20进行清洗及烘干后,在衬底基板20上形成一整面导电层,接着在导电层上涂布一整面光刻胶,然后采用光罩对所述一整面光刻胶进行曝光及显影处理,被曝光的光刻胶在显影时被灰化去除,而未被曝光的光刻胶在显影之后仍被保留于衬底基板20上,接着,刻蚀去除未被光刻胶覆盖的导电层,最后去除剩余的光刻胶,即可得到具有预定图案的第一导电层。

[0036] 所述缓冲层22覆盖第一导电层,其厚度可以为1000~5000 Å。所述缓冲层(buffer layer)22可用于防止衬底基板20表面的杂质在后续工艺中向上扩散而影响之后形成的半导体图案23的品质。该缓冲层22可以为硅氧化合物层,例如氧化硅(SiO<sub>2</sub>)层,或者包括依次覆盖所述第一导电层的硅氧化合物层和硅氮化合物层,例如Si<sub>3</sub>N<sub>4</sub>(三氮化硅)层,又或者其他非导电材料的组合。其中,所述缓冲层22可采用化学气相沉积(CVD)、等离子化学气相沉积(PACVD)、溅射、真空蒸镀以及低压化学气相沉积(LPCVD)中的任一方法形成。

[0037] S13:在缓冲层上形成位于第一遮光图案上方的半导体图案。

[0038] 首先,在缓冲层22上形成一整面半导体层,然后通过一道光罩制程Mask-2对这一整面半导体层进行图案化处理,以得到仅形成于第一遮光图案211正上方的半导体图案23。所述光罩制程Mask-2与光罩制程Mask-1的原理及过程相似,此处不再赘述。

[0039] 半导体图案23为金属氧化物半导体图案,其厚度可以为100~1000 Å,其材质包括但不限于为IGZO(Indium Gallium Zinc Oxide,铟镓锌氧化物),IZTO(Indium Zinc Tin Oxide,铟锌锡氧化物),IGZTO(Indium Gallium Zinc Tin Oxide,铟镓锌锡氧化物)中的一者。

[0040] S14:依次形成绝缘层和第二导电层,绝缘层包括位于第一区域的第一绝缘图案,第二导电层包括位于第一区域的第一栅极图案,第一绝缘图案位于半导体图案上。

[0041] 本申请可采用CVD、PECVD、溅射、真空蒸镀等任一方法在缓冲层22上依次形成覆盖半导体图案23的一整面绝缘层和一整面导电层,该绝缘层的厚度可以为1000~3000Å,所述第二导电层的厚度可以为2000~8000Å,所述一整面导电层可由金属,例如铝、钼、钛、铬、铜,或者金属氧化物,例如氧化钛,又或者金属的合金或其它导电材料构成,然后利用一道光罩制程Mask-3对这一整面导电层进行图案化处理,以得到位于半导体图案23正上方的第一栅极图案251,再利用第一栅极图案251为刻蚀屏蔽对所述一整面绝缘层进行刻蚀,位于第一栅极图案251下方的绝缘层被保留,从而得到所述第一绝缘图案241。

[0042] 所述光罩制程Mask-3与光罩制程Mask-1的原理及过程相似。所述光罩制程Mask-3可以利用包含有磷酸、硝酸、醋酸或者去离子水的蚀刻液蚀刻所述导电层,当然也可以采用干法蚀刻。

[0043] 所述第一栅极图案251又称栅极绝缘层(Gate Insulation Layer, GI层),其材质可以为硅氧化物,或者该第一栅极图案251包括依次覆盖半导体图案23的硅氧化合物层和硅氮化合物层。

[0044] 继而,以第一栅极图案251和第一绝缘图案241为屏蔽,对半导体图案23的两端进行离子掺杂,例如N型掺杂,即可得到位于半导体图案23两端的源极接触区和漏极接触区。位于第一绝缘图案241下方的半导体图案23未被掺杂,成为TFT的沟道层。

[0045] S15:形成覆盖第二导电层、半导体图案和缓冲层的介电层,所述介电层采用遮光材料制得且在第一区域设有第一接触孔和第二接触孔、在第二区域设有开口区,缓冲层在所述开口区暴露其表面。

[0046] 除了开口区263和各个接触孔的开口外,所述介电层(又称层间介质隔离层, Interlayer dielectric isolation layer, ILD) 26的上表面为平坦面,其厚度可以为1~4  $\mu\text{m}$ 。该介电层26采用不透光材质制得,例如其可以采用黑色光阻、丙烯酸树脂以及聚酰亚胺中至少一者形成。

[0047] 本申请可以采用一道光罩制程Mask-4在一整面介电层上开设所述第一接触孔261、第二接触孔262和开口区263。具体地,本申请可以首先采用CVD、PECVD、溅射、真空蒸镀等任一方法形成覆盖第二导电层、半导体图案23和缓冲层22的一整面介电层,接着在所述一整面介电层上涂布一整面光刻胶,其中该光刻胶与所述介电层26所采用的黑色光阻的正负性相反,然后采用光罩对这一整面光刻胶进行曝光及显影处理,被曝光(即第一接触孔261、第二接触孔262和开口区263所对应区域)的光刻胶在显影时被灰化去除,而未被曝光的光刻胶在显影之后仍被保留于介电层上,接着,刻蚀去除未被光刻胶覆盖的介电层,最后去除剩余的光刻胶,即可得到所述介电层26。

[0048] 其中,第一接触孔261为源极接触孔,半导体图案23的源极接触区通过第一接触孔261暴露,第二接触孔262为漏极接触孔,半导体图案23的漏极接触区通过第二接触孔262暴露。

[0049] S16:在介电层上形成第三导电层,第三导电层包括位于第一区域的源极图案及跨越第一区域和第二区域的漏极图案,源极图案和漏极图案分别覆盖第一接触孔和第二接触孔并与半导体图案接触,漏极图案还覆盖开口区并与缓冲层接触,漏极图案与第二遮光图案至少部分重叠并通过夹设于两者之间的缓冲层形成一电容。

[0050] 源极图案271和漏极图案272位于介电层26上的厚度可以为2000~8000  $\text{\AA}$ ,并且两者的制造材料包括但不限于为铝、钼、钛、铬、铜、金属氧化物、或者金属的合金或其它导电材料,当然也可以为ITO(Indium tin oxide, 氧化铟锡),或者依次包括ITO、银及ITO这三层结构。本申请可通过一道光罩制程Mask-5对一整面导电层进行图案化处理,以此得到源极图案271和漏极图案272。所述光罩制程Mask-5与光罩制程Mask-3的原理及过程相似,此处不再赘述。

[0051] 其中,源极图案271通过所述第一接触孔261与半导体图案23的源极接触区接触,漏极图案272通过所述第二接触孔262与半导体图案23的漏极接触区接触,同时所述漏极图

案272还覆盖所述开口区263并在该开口区263内与缓冲层22接触,于此,漏极图案272与第二遮光图案212之间夹设有绝缘的缓冲层22且两者至少部分重叠,当漏极图案272与第二遮光图案212均通电时,漏极图案272与第二遮光图案212通过夹设于两者之间的缓冲层22形成一电容。

[0052] 应该理解到,本申请通过所述光罩制程Mask-5也可以同步在所述介电层26上形成阵列基板的各类信号走线,例如数据线等。所述信号走线与源极图案271和漏极图案272的材质相同。

[0053] 通过上述方式,即可制得本申请阵列基板的TFT。

[0054] 进一步地,对于制造OLED显示面板的阵列基板的应用场景,所述漏极图案272还作为OLED显示面板的阳极图案(Anode)。并基于此,在步骤S16之后,所述制造方法还包括:

[0055] S17:在所述源极图案和漏极图案上形成像素定义层,所述像素定义层设有用于限定阵列基板的发光区。

[0056] 所述像素定义层(Pixel Define Layer, PDL)28用于围设形成阵列基板的发光区281,即用于限定像素开口区。

[0057] S18:在发光区依次形成位于漏极图案上的发光层和阴极图案。

[0058] 当然,本申请的阵列基板还包括依次形成于阳极图案(即漏极图案)272和发光层273之间的电子注入层和电子传输层,以及依次形成于发光层273和阴极图案274之间的空穴传输层和空穴注入层。

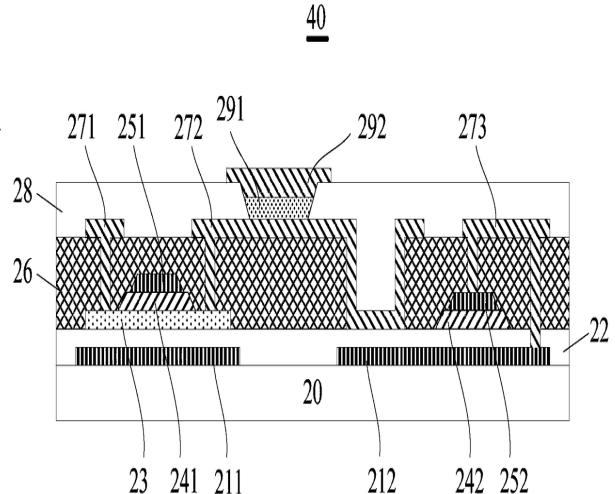

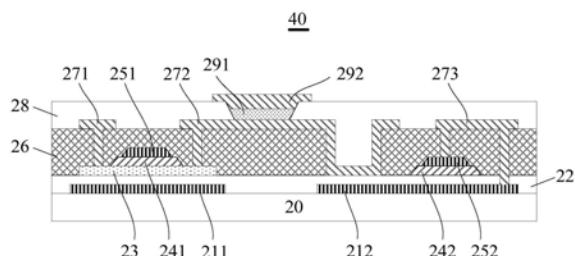

[0059] 通过上述方法即可制得本申请如图4所示的阵列基板40,结合图2和图4所示,源极图案271和漏极图案272直接形成于介电层26上,通过介电层26取代传统的平坦层(PLN)和钝化层(PV),即无需设置平坦层和钝化层,且该漏极图案272同时也作为阳极图案,从而能够减少光罩制程,并且该介电层26采用遮光材料制得,能够保护TFT的沟道层不受到光影响,有利于确保其性能稳定。

[0060] 请继续参阅图2和图4,所述漏极图案272与第二遮光图案212通过夹设于两者之间的缓冲层22形成一电容,而要形成该电容,第二遮光图案212必须被施加电压,本申请可以在所述阵列基板40的过孔区203形成用于为第二遮光图案212通电的结构。

[0061] 具体地,如图2所示,所述衬底基板20的上方还包括第三区域203,第一区域201、第二区域202和第三区域203沿平行于衬底基板20的方向依次相邻。第二遮光图案212跨越第二区域202和第三区域203。绝缘层还包括位于第三区域203且位于缓冲层22上的第二绝缘图案242。所述第二导电层还包括位于第三区域203的第二栅极图案252,且该第二栅极图案252仅位于第二绝缘图案242的正上方。另外,介电层26在第三区域203还开设有第三接触孔264和第四接触孔265,第二栅极图案252在第三接触孔264内暴露其上表面,第二遮光图案212在第四接触孔265内暴露其上表面。所述第三导电层还包括位于第三区域203的桥接图案273,该桥接图案273覆盖第三接触孔264并在第三接触孔264内与第二栅极图案252接触,该桥接图案273还覆盖第四接触孔265并在第四接触孔265内与第二遮光图案212接触。

[0062] 本申请可以通过一道光罩制程形成具有第一接触孔261、第二接触孔262、开口区263、第三接触孔264和第四接触孔265的介电层26,即,步骤S15的光罩制程Mask-4可以为Half-tone(半色调)光罩制程。具体地,结合图2和图3所示,首先形成覆盖所述第二导电层、半导体图案23和缓冲层22的一整面介电层;接着在这一整面介电层上涂布一整面光刻胶

30，并采用Half-tone光罩对这一整面光刻胶30进行曝光及显影处理，所述Half-tone光罩包括完全曝光区32、半曝光区33和非曝光区31，在显影处理之后，位于完全曝光区32下方的光刻胶30被完全去除，位于半曝光区33下方的光刻胶30的厚度小于位于非曝光区31下方的光刻胶30的厚度；再刻蚀去除完全曝光区32下方的介电层，以形成所述第一接触孔261、第二接触孔262、开口区263和第三接触孔264；然后，灰化去除半曝光区33下方的光刻胶30，此时非曝光区31下方的光刻胶30厚度变薄但仍保留；进一步地，刻蚀去除半曝光区33下方的介电层和缓冲层22，以形成第四接触孔265；最终灰化去除非曝光区31下方的光刻胶30，即可得到所述介电层26。

[0063] 当然，本申请可以通过两道光罩制程形成所述介电层26。具体地，在步骤S15中，通过光罩制程Mask-4形成所述介电层26的第一接触孔261、第二接触孔262、开口区263和第三接触孔264，然后采用另一道光罩制程Mask-4-1形成所述第四接触孔265。

[0064] 由于所述桥接图案273覆盖第三接触孔264并在第三接触孔264内与第二栅极图案252接触，同时该桥接图案273还覆盖第四接触孔265并在第四接触孔265内与第二遮光图案212接触，第二遮光图案212可以通过桥接图案273从第二栅极图案252获取电压。

[0065] 本申请还提供一种显示面板。所述显示面板可以包括前述实施例所制得的阵列基板，因此具有与其相同的有益效果。

[0066] 综上所述，本申请的主要目的是：设计源极图案和漏极图案直接形成于介电层上，通过介电层取代传统的平坦层和钝化层，即无需设置平坦层和钝化层，且所述漏极图案同时也作为OLED器件的阳极图案，以此减少光罩制程，并且所述介电层采用遮光材料制得，以保护TFT的沟道层不受到光照影响，有利于确保其性能稳定。

[0067] 在此基础上，以上所述仅为本申请的实施例，并非因此限制本申请的专利范围，凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换，例如各实施例之间技术特征的相互结合，或直接或间接运用在其他相关的技术领域，均同理包括在本申请的专利保护范围内。

图1

图2

图3

图4

|                |                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 阵列基板及其制造方法、显示面板                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">CN109166865A</a>                                                                                             | 公开(公告)日 | 2019-01-08 |

| 申请号            | CN201810896463.9                                                                                                         | 申请日     | 2018-08-08 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                                                                                            |         |            |

| 申请(专利权)人(译)    | 深圳市华星光电技术有限公司                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 深圳市华星光电技术有限公司                                                                                                            |         |            |

| [标]发明人         | 周星宇                                                                                                                      |         |            |

| 发明人            | 周星宇                                                                                                                      |         |            |

| IPC分类号         | H01L27/12 H01L27/32 H01L29/417 H01L29/786 H01L51/52 H01L51/56 H01L21/84 H01L21/44 H01L21/34                              |         |            |

| CPC分类号         | H01L27/1248 H01L27/1259 H01L27/3262 H01L29/401 H01L29/41733 H01L29/66969 H01L29/78633 H01L51/5206 H01L51/56 H01L2227/323 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                           |         |            |

#### 摘要(译)

本申请公开一种阵列基板及其制造方法、显示面板。本申请设计源极图案和漏极图案直接形成于介电层上，通过介电层取代传统的平坦层和钝化层，且所述漏极图案同时也作为OLED器件的阳极图案，从而能够减少光罩制程，并且所述介电层采用遮光材料制得，能够保护TFT的沟道层不受到光照影响，有利于确保其性能稳定。