(12)发明专利申请

(10)申请公布号 CN 109599061 A

(43)申请公布日 2019.04.09

(21)申请号 201811343362.5

(22)申请日 2018.11.13

(71)申请人 中国电子科技集团公司第五十五研究所

地址 210016 江苏省南京市中山东路524号

(72)发明人 张白雪 秦昌兵 陈啟宏 杨建兵

陈建军

(74)专利代理机构 南京天华专利代理有限责任

公司 32218

代理人 瞿网兰 徐冬涛

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书1页 说明书2页 附图1页

(54)发明名称

一种硅基微显示像素电路

(57)摘要

一种硅基微显示像素电路,其特征是它包括驱动管P3、开关管P1、开关管P2、开关管P4、存储电容C1。在不同的工艺偏差下,驱动管P3阈值电压变化时,晶体管P4阻值跟随变化,最终减弱了由于阈值电压漂移带来的OLED两端电压差的变化量。增加了OLED发光的均匀性。在一帧时间内,行选控制信号SEL为高电平时,增加的晶体管P2在VN和VP之间有一个寄生的反向二极管,会使VN点的漏电减小,VN电压相对更稳定。可维持的发光时间更长。

1. 一种硅基微显示像素电路,其特征是:它包括驱动管P3、开关管P1、开关管P2、开关管P4、存储电容C1;开关管P1的漏极与输入电压源Vdata正向端相连,电压源Vdata负向端与地GND相连;开关管P1的栅极与行选控制信号SEL相连,开关管P1的衬底与电源电压VDD相连,开关管P1的源极与开关管P2的漏极相连;开关管P2的栅极、衬底、源极、电容C1的一端与驱动管P3的栅极相连;驱动管P3的源极、开关管P4的漏极、栅极与电容C1的另一端相连;驱动管P3的衬底与电压源VDD相连,开关管P4的衬底与电压源VDD相连,开关管P4的源极与OLED阴极相连,OLED阳极与公共阳极Vcom相连。

2. 根据权利要求1所述的硅基微显示像素电路,其特征在于所述的开关管P4采用P型MOS管,并且开关管P4连接成二极管形式,改善了因驱动管P3阈值电压漂移带来的不均匀性;驱动管P3阈值电压增大时,开关管P4电阻值减小,从而减弱了OLED两端电压差VCOM-V0的减小量;驱动管P3阈值电压减小时,开关管P4电阻值增大,从而减弱了OLED两端电压差VCOM-V0的增大量;最终减弱了由于驱动管P3阈值电压漂移带来的OLED两端电压差的变化量。

3. 根据权利要求1所述的硅基微显示像素电路,其特征在于所述的开关管P2采用P型MOS管,并连接成二极管形式。

4. 根据权利要求1所述的硅基微显示像素电路,其特征在于所述的开关管P1为P型MOS管。

5. 根据权利要求1所述的硅基微显示像素电路,其特征在于所述的驱动管P3为P型MOS管。

## 一种硅基微显示像素电路

### 技术领域

[0001] 本发明涉及微电子及显示技术领域。尤其是应用于AMOLED硅基微显示驱动芯片的像素电路，具体地说是一种硅基微显示像素电路。

### 背景技术

[0002] 有源有机发光二极管(AMOLED)作为新一代显示技术，具有主动发光、视角宽、驱动电压低、发光效率高、响应速度快、功耗低、工作温度适应范围广、体积轻薄并且能够实现柔性显示等特点，具有很广阔的应用前景。目前的主要应用包括头盔显示器、眼镜式显示；也可用在其他移动终端显示器，比如可穿戴式计算机等移动信息产品提供高画质的视频显示效果，以及应用在一些AR、VR产品中。随着分辨率不断提高，像素尺寸的减小，像素与像素之间由于半导体制造工艺的偏差带来的MOS管的阈值电压的漂移也越发的明显，因此在输入相同的数据信号电压下，每个像素单元的电流大小不同，这会导致同一灰度级在屏的不同位置显示的亮度不均匀。为了提高亮度均匀性，有必要对驱动管阈值电压的漂移进行补偿。同时，在一帧时间内，由于像素单元中存储电容上的电压通过MOS开关不断的漏电，显示亮度也会不断变化，最终均匀性和亮度都会影响OLED显示质量。

### 发明内容

[0003] 本发明的目的是针对由于分辨率提高导致OLED显示亮度不均匀的问题，为AMOLED硅基微显示驱动电路提供一种能够改善采用公共阳极制作的AMOLED发光的均匀性以及减小漏电的像素电路，以达到更好的显示效果。

[0004] 本发明的技术方案是：

一种硅基微显示像素电路，其特征是：它包括驱动管P3、开关管P1、开关管P2、开关管P4、存储电容C1；开关管P1的漏极与输入电压源Vdata正向端相连，电压源Vdata负向端与地GND相连；开关管P1的栅极与行选控制信号SEL相连，开关管P1的衬底与电源电压VDD相连，开关管P1的源极与开关管P2的漏极相连；开关管P2的栅极、衬底、源极、电容C1的一端与驱动管P3的栅极相连；驱动管P3的源极、开关管P4的漏极、栅极与电容C1的另一端相连；驱动管P3的衬底与电压源VDD相连，开关管P4的衬底与电压源VDD相连，开关管P4的源极与OLED阴极相连，OLED阳极与公共阳极Vcom相连。

[0005] 所述的开关管P4采用P型MOS管，并且开关管P4连接成二极管形式，改善了因驱动管P3阈值电压漂移带来的不均匀性；驱动管P3阈值电压增大时，开关管P4电阻值减小，从而减弱了OLED两端电压差VCOM-VO的减小量；驱动管P3阈值电压减小时，开关管P4电阻值增大，从而减弱了OLED两端电压差VCOM-VO的增大量；最终减弱了由于驱动管P3阈值电压漂移带来的OLED两端电压差的变化量。

[0006] 所述的开关管P2采用P型MOS管，并连接成二极管形式。

[0007] 所述的开关管P1为P型MOS管。

[0008] 所述的驱动管P3为P型MOS管。

[0009] 本发明的有益效果是：

(1) 本发明的像素电路采用晶体管P4连接成二极管形式改善了因驱动管P3阈值电压漂移带来的不均匀性。

[0010] (2) 本发明采用晶体管P2连接成二极管形式，减小了驱动管P3栅极电容的漏电，稳定了驱动管P3的栅极的电压，使显示亮度的变化得到改善。

## 附图说明

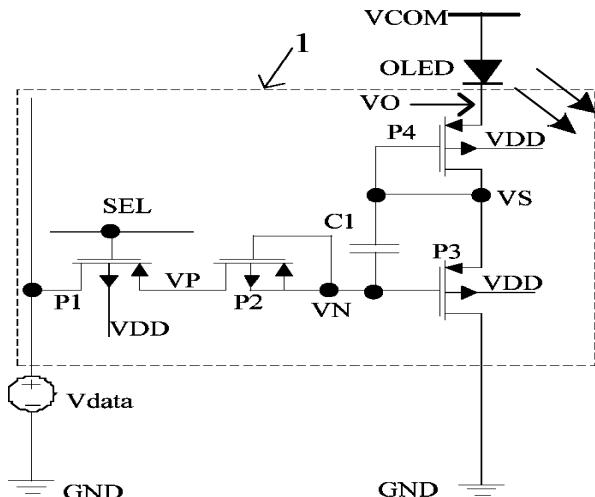

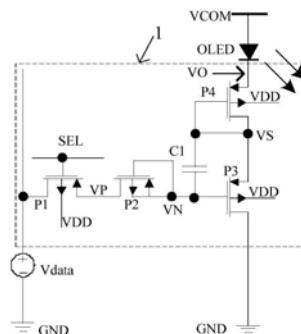

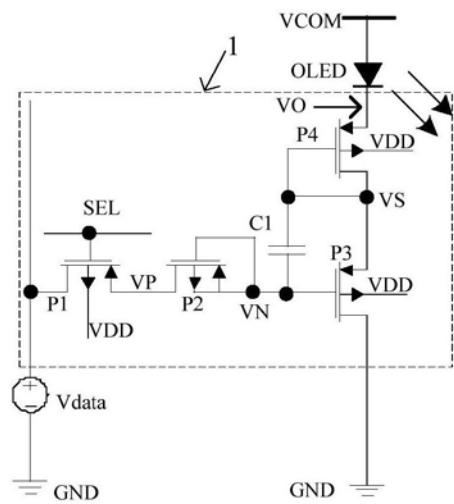

[0011] 图1是本发明的像素电路图。

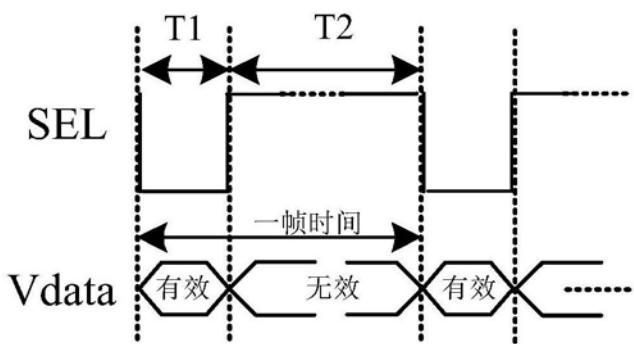

[0012] 图2是本发明像素电路时序图。

## 具体实施方式

[0013] 下面结合附图和具体实施例对本发明进行详细说明。

[0014] 参见图1，是本发明像素电路图，由虚线框1内的具体像素电路、外接电压源Vdata、外接OLED构成。P型MOS管P1的漏极与输入电压源Vdata正向端相连，电压源Vdata负向端与地GND相连。P型MOS管P1的栅极与行选控制信号SEL相连，P型MOS管P1的衬底与电源电压VDD相连，P型MOS管P1的源极与P型MOS管P2的漏极相连。P型MOS管P2的栅极、衬底、源极、电容C1的一端、P型MOS管P3的栅极相连。P型MOS管P3的源极与P型MOS管P4的漏极、栅极、电容C1的另一端相连。P型MOS管P3的衬底与电压源VDD相连，P型MOS管P4的衬底与电压源VDD相连，P型MOS管P4的源极与OLED阴极相连，OLED阳极与公共阳极Vcom相连。

[0015] 下面结合图2，对图1所示电路的工作过程进行详细描述：

T1阶段代表驱动电路充电阶段，T1阶段时，SEL为低电平，P1导通，驱动信号数据电压Vdata通过开关管P2写入存储电容C1中，使驱动管P3导通，同时P4也导通。P3、P4导通使驱动电流流过OLED，驱动OLED发光。T2阶段代表驱动电路发光阶段，行选控制信号SEL为高电平时，在VN和VP之间有一个寄生的反向二极管，会使VN点的漏电减小，在一帧时间内，减小了驱动管P3栅极电容的漏电，稳定了驱动管P3的栅极的电压，使显示亮度的变化得到改善。

[0016] 另外在不同半导体的工艺偏差下，驱动管P3阈值电压增大时，VS增大，导致VCOM-VS的差值减小，同时MOS管P4电阻值减小，从而减弱了OLED两端电压差VCOM-VO的减小量；驱动管P3阈值电压减小时，VS减小，MOS管P4的V<sub>SD</sub>增大，导致P4管的电阻值增大，从而减弱了OLED两端电压差VCOM-VO的增大量；OLED发光亮度与OLED两端电压差成正比，MOS管P4的存在，使OLED在不同工艺偏差下两端电压差变化减小，亮度变化减小，最终减弱了由于P3阈值电压漂移带来的OLED阴极电压的变化量。增加了OLED发光的均匀性。

[0017] 本发明不局限于上述实施方式，不论其实现形式作任何变化，凡是采用公共阳极制作的AMOLED像素电路用二极管连接方式来改善漏电和均匀性，均应落在本发明保护范围之内。

[0018] 本发明未涉及部分与现有技术相同或可采用现有技术加以实现。

图1

图2

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种硅基微显示像素电路                                    |         |            |

| 公开(公告)号        | <a href="#">CN109599061A</a>                   | 公开(公告)日 | 2019-04-09 |

| 申请号            | CN201811343362.5                               | 申请日     | 2018-11-13 |

| [标]申请(专利权)人(译) | 中国电子科技集团公司第五十五研究所                              |         |            |

| 申请(专利权)人(译)    | 中国电子科技集团公司第五十五研究所                              |         |            |

| 当前申请(专利权)人(译)  | 中国电子科技集团公司第五十五研究所                              |         |            |

| [标]发明人         | 张白雪<br>秦昌兵<br>陈啟宏<br>杨建兵<br>陈建军                |         |            |

| 发明人            | 张白雪<br>秦昌兵<br>陈啟宏<br>杨建兵<br>陈建军                |         |            |

| IPC分类号         | G09G3/3225                                     |         |            |

| CPC分类号         | G09G3/3225                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

### 摘要(译)

一种硅基微显示像素电路，其特征是它包括驱动管P3、开关管P1、开关管P2、开关管P4、存储电容C1。在不同的工艺偏差下，驱动管P3阈值电压变化时，晶体管P4阻值跟随变化，最终减弱了由于阈值电压漂移带来的OLED两端电压差的变化量。增加了OLED发光的均匀性。在一帧时间内，行选控制信号SEL为高电平时，增加的晶体管P2在VN和VP之间有一个寄生的反向二极管，会使VN点的漏电减小，VN电压相对更稳定。可维持的发光时间更长。