(12)发明专利申请

(10)申请公布号 CN 110224005 A

(43)申请公布日 2019.09.10

(21)申请号 201910388679.9

(22)申请日 2019.05.10

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明

街道塘明大道9-2号

(72)发明人 唐甲

(74)专利代理机构 深圳翼盛智成知识产权事务所(普通合伙) 44300

代理人 黄威

(51)Int.Cl.

H01L 27/32(2006.01)

权利要求书2页 说明书5页 附图5页

(54)发明名称

显示器及其制备方法

(57)摘要

本发明提供了一种显示器，包括：薄膜电晶体管基板，包括多个薄膜电晶体管；平坦层；多个阳极及多个辅助源走线，所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接；像素定义层，具有多个第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；多个导电体，填充于所述多个第一开口内以及配置于所述多个第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；电致发光层，覆盖在所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及多个阴极，覆盖所述电致发光层，分别与所述多个导电体的侧壁电性相接。

1. 一种显示器，其特征在于，包括：

薄膜电晶体管基板，包括多个薄膜电晶体管；

平坦层，配置于所述薄膜电晶体管基板上；

多个阳极及多个辅助源走线，配置于所述平坦层上，所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接；

像素定义层，配置于所述多个阳极、所述多个辅助源走线、以及未被所述多个阳极及所述多个辅助源走线覆盖的所述平坦层上，其中所述像素定义层具有多个第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；

多个导电体，填充于所述多个第一开口内以及配置于所述多个第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；

电致发光层，覆盖在所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及

多个阴极，覆盖所述电致发光层，分别与所述多个导电体的侧壁电性相接。

2. 根据权利要求1所述的显示器，其特征在于，所述多个导电体包括金属或有机导电材料，以及所述电致发光层包括有机材料。

3. 根据权利要求1所述的显示器，其特征在于，所述多个导电体高于所述多个阴极的上表面。

4. 根据权利要求1所述的显示器，其特征在于，所述多个凸出部分的侧壁与所述像素定义层的上表面之夹角小于或等于90度。

5. 根据权利要求1所述的显示器，其特征在于，所述多个凸出部分为矩形、倒梯形、或上宽下窄的不规则形。

6. 根据权利要求1所述的显示器，其特征在于，所述电致发光层发出的光为白光。

7. 一种显示器的制备方法，包括：

S10提供薄膜电晶体管基板，其中所述薄膜电晶体管基板包括多个薄膜电晶体管；

S20形成平坦层于所述薄膜电晶体管基板上；

S30分别形成多个阳极及多个辅助源走线于部分所述平坦层上，所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接；

S40形成像素定义层于所述多个阳极、所述多个辅助源走线、以及未被所述多个阳极及所述多个辅助源走线覆盖的所述平坦层上，其中所述像素定义层具有多个第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；

S50形成多个导电体填充于所述多个第一开口内以及配置于第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；

S60形成电致发光层于所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及

S70形成多个阴极于所述电致发光层上，所述多个阴极分别与所述多个凸出部分的侧壁电性相接。

8. 根据权利要求7所述的显示器的制备方法，其特征在于，步骤S60中，形成所述电致发光层的方法包括蒸镀，且所述电致发光层的材料在蒸镀时于所述凸出部分的所述侧壁处自然断开，于断开处露出所述凸出部分的所述侧壁。

9. 根据权利要求8所述的显示器的制备方法，其特征在于，所述多个凸出部分的侧壁与

所述像素定义层的上表面之夹角小于或等于90度,且所述多个凸出部分为矩形、倒梯形、或上宽下窄的不规则形。

10.根据权利要求8所述的显示器的制备方法,其特征在于,步骤S70中,形成所述多个阴极的方法包括配合所述夹角选择特定角度进行蒸镀,以实现所述多个阴极与所述凸出部分在所述断开处的侧壁电性相接。

## 显示器及其制备方法

### 技术领域

[0001] 本发明涉及一种显示器,尤其涉及一种大尺寸高分辨率的显示器及其制备方法。

### 背景技术

[0002] 目前小尺寸主动矩阵有机发光二极体(active-matrix organic light-emitting diode, AMOLED),一般采用红绿蓝有机发光二极体(RGBOLED)及精细金属屏蔽(fine metal shadow mask, FMM)制程,其电压衰退(IR drop)的现象不明显,,而大尺寸AMOLED面板,采用白光有机发光二极体加上彩膜(white organic light-emitting diode+color filter, WOLED+CF)制程,对于顶发光、高分辨率,其阴极需要高透明度,因此膜厚必须很薄,这导致阻抗很大,基于目前材料、设计限制,面板在工作时显示中心与中心以外、四周边缘会有IR drop的问题,针对量产目标,特别说G8.5或以上,需进行辅助电极设计,给压降较大的区域额外施加辅助,使整个面板工作时画面显示均一稳定。目前辅助电极的主要方案是制作倒梯形隔离柱来实现,成本高及工艺制程复杂,是电致发光/喷墨打印(electroluminescence/ink-jet printing organic light-emitting diode, EL/IJP-OLED)背板的工艺实现更加困难,另外还需要设计一个接触通孔,对于电路设计以及背板高分辨率(每英寸像素,pixels per inch,PPI)的设计都是不利的。

[0003] 为了解决上述传统显示器的问题,亟需开发一种大尺寸高分辨率的显示器。

### 发明内容

[0004] 有鉴于此,本发明提供一种显示器,利用大尺寸蒸镀或打印有机发光二极体(organic light-emitting diode,OLED)面板的辅助电极的设计,通过改变背板设计,在阳极制程时,提前制作辅助源走线,走线位于像素定义层(pixel define layer, PDL)底部,在PDL层制程时,沿子像素长度方向制作开孔,并作凸出导电体,导电体与辅助源走线搭接,根据蒸镀电致发光(electroluminescence, EL)层及阴极厚度确定导电体凸出PDL的高度,将凸出导电体的侧壁设计成陡直,使蒸镀EL材料在导电体顶部与底部之间自然断开,断开的区域在蒸镀阴极材料时搭接在导电体侧壁上;由于导电体沿子画素的长轴方向,长度很大,阴极与导电体的搭接面积变为二维搭接,导通面积大大提高,改善以往点接触辅助电极设计效果不明显的弊端。此外,本发明所提出的辅助电极设计不占用额外的空间,即在增大发光面积设计空间的同时,解决大尺寸高分辨率主动矩阵有机发光二极体(active-matrix organic light-emitting diode, AMOLED)面板,在点亮顶发光背板时的电压衰退(IR drop)问题。

[0005] 据此,依据本发明的一实施例,本发明提供了一种显示器,其特征在于,包括;薄膜电晶体管基板,包括多个薄膜电晶体管;平坦层,配置于所述薄膜电晶体管基板上;多个阳极及多个辅助源走线,配置于所述平坦层上,所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接;像素定义层,配置于所述多个阳极、所述多个辅助源走线、以及未被所述多个阳极及所述多个辅助源走线覆盖的所述平坦层上,其中所述像素定义层具有多个

第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；多个导电体，填充于所述多个第一开口内以及配置于所述多个第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；电致发光层，覆盖在所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及多个阴极，覆盖所述电致发光层，分别与所述多个导电体的侧壁电性相接。

- [0006] 依据本发明的另一实施例，本发明还提供了一种显示器的制备方法，包括：

- [0007] S10提供薄膜电晶体基板，其中所述薄膜电晶体基板包括多个薄膜电晶体管；

- [0008] S20形成平坦层于所述薄膜电晶体基板上；

- [0009] S30分别形成多个阳极及多个辅助源走线于部分所述平坦层上，所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接；

- [0010] S40形成像素定义层于所述多个阳极、所述多个辅助源走线、以及未被所述多个阳极及所述多个辅助源走线覆盖的所述平坦层上，其中所述像素定义层具有多个第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；

- [0011] S50形成多个导电体填充于所述多个第一开口内以及配置于第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；

- [0012] S60形成电致发光层于所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及

- [0013] S70形成多个阴极于所述电致发光层上，所述多个阴极分别与所述多个凸出部分的侧壁电性相接。

- [0014] 在本发明的一实施例中，步骤S60中，形成所述电致发光层的方法包括蒸镀，且所述电致发光层的材料在蒸镀时于所述凸出部分的所述侧壁处自然断开，于断开处露出所述凸出部分的所述侧壁。

- [0015] 在本发明的一实施例中，步骤S70中，形成所述多个阴极的方法包括配合所述夹角选择特定角度进行蒸镀，以实现所述多个阴极与所述断开处的侧壁电性相接。

- [0016] 在本发明的一实施例中，所述多个导电体包括金属或有机导电材料，以及所述电致发光层包括有机材料。

- [0017] 在本发明的一实施例中，所述多个导电体高于所述多个阴极的上表面。

- [0018] 在本发明的一实施例中，所述多个凸出部分的侧壁与所述像素定义层的上表面之夹角小于或等于90度。

- [0019] 在本发明的一实施例中，所述多个凸出部分为矩形、倒梯形、或上宽下窄的不规则形。

- [0020] 在本发明的一实施例中，所述多个凸出部分的侧壁为平整或具有不规则形状的表面。

- [0021] 在本发明的一实施例中，所述电致发光层发出的光为白光。

## 附图说明

- [0022] 为了更清楚地说明实施例或现有技术中的技术方案，下面将对实施例或现有技术描述中所需要使用的附图作简单介绍，显而易见地，下面描述中的附图仅仅是发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附

图获得其他的附图。

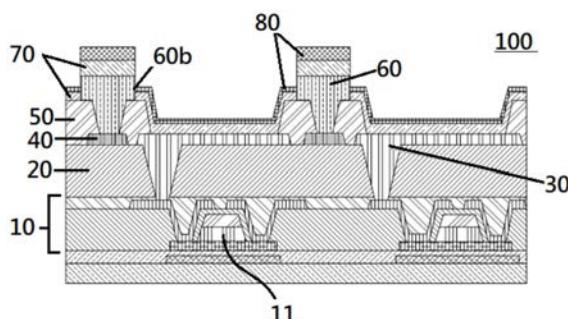

[0023] 图1为依据本发明一实施例的显示器的制备方法流程图。

[0024] 图2A至2E为依据本发明一实施例的显示器的制备方法,各步骤中的显示器的结构示意图。

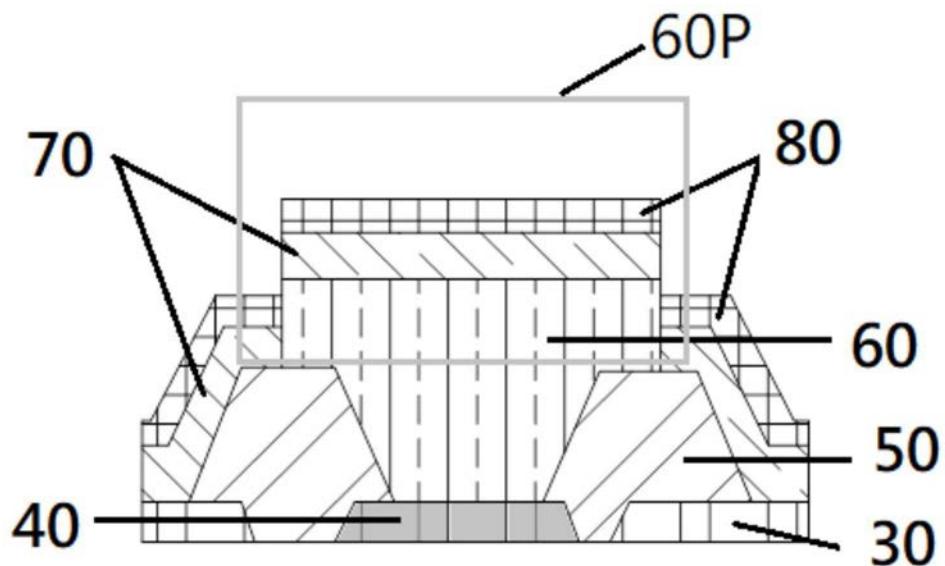

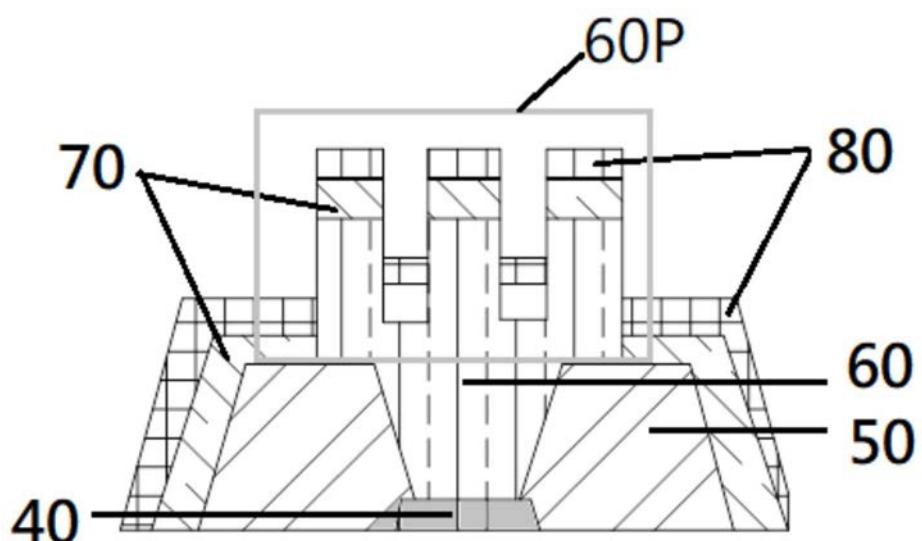

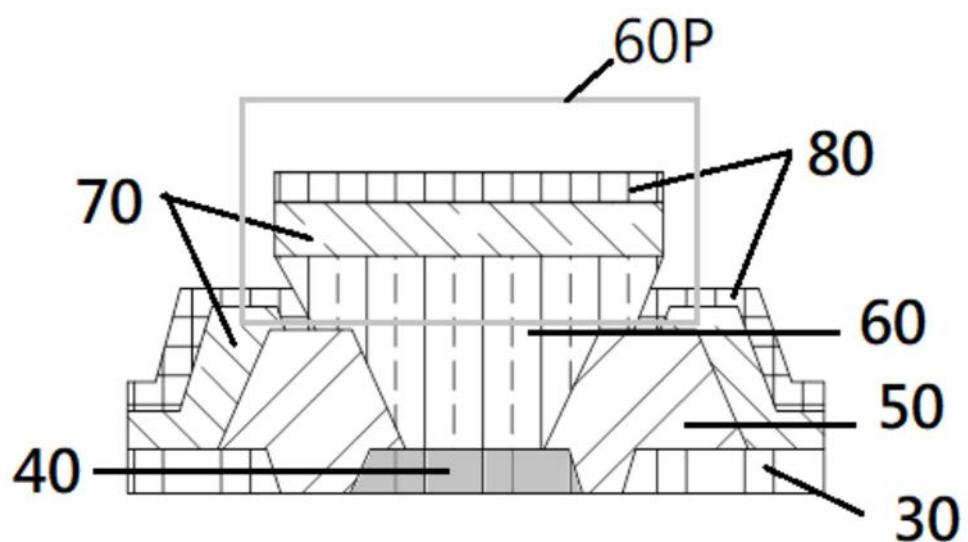

[0025] 图3为依据本发明一实施例的显示器的导电体结构示意图。

[0026] 图4为依据本发明另一实施例的显示器的导电体结构示意图。

[0027] 图5为依据本发明再一实施例的显示器的导电体结构示意图。

## 具体实施方式

[0028] 为让本发明的上述内容能更明显易懂,下文特举优选实施例,并配合所附图式作详细说明。

[0029] 以下各实施例的说明是参考附加的图示,用以例示本发明可用以实施的特定实施例。本发明所提到的方向用语,例如[纵向]、[横向]、[上]、[下]、[前]、[后]、[左]、[右]、[内]、[外]、[侧面]等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明及理解本发明,而非用以限制本发明。在图中,结构相似的单元是用以相同标号表示。

[0030] 本发明提供一种显示器,利用大尺寸蒸镀或打印有机发光二极体(organic light-emitting diode,OLED)面板的辅助电极的设计,通过改变背板设计,在阳极制程时,提前制作辅助源走线,走线位于像素定义层(pixel define layer,PDL)底部,在PDL层制程时,沿子像素长度方向制作开孔,并作凸出导电体,导电体与辅助源走线搭接,根据蒸镀电致发光(electroluminescence,EL)层及阴极厚度确定导电体凸出PDL的高度,将凸出导电体的侧壁设计成陡直,使蒸镀EL材料在导电体顶部与底部之间自然断开,断开的区域在蒸镀阴极材料时搭接在导电体侧壁上;由于导电体沿子画素的长轴方向,长度很大,阴极与导电体的搭接面积变为二维搭接,导通面积大大提高,改善以往点接触辅助电极设计效果不明显的弊端。此外,本发明所提出的辅助电极设计不占用额外的空间,即在增大发光面积设计空间的同时,解决大尺寸高分辨率主动矩阵有机发光二极体(active-matrix organic light-emitting diode,AMOLED)面板,在点亮顶发光背板时的电压衰退(IR drop)问题。

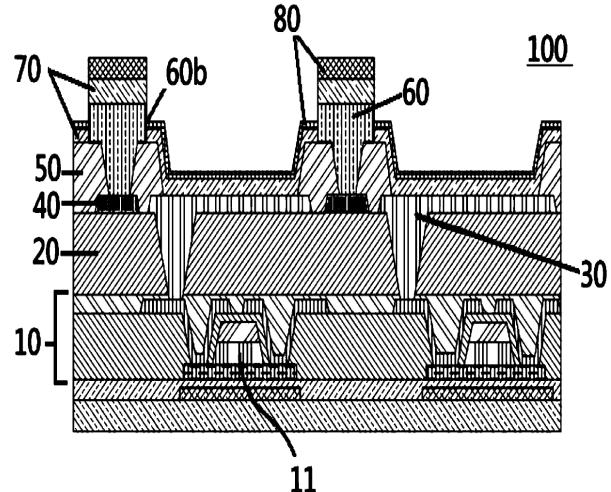

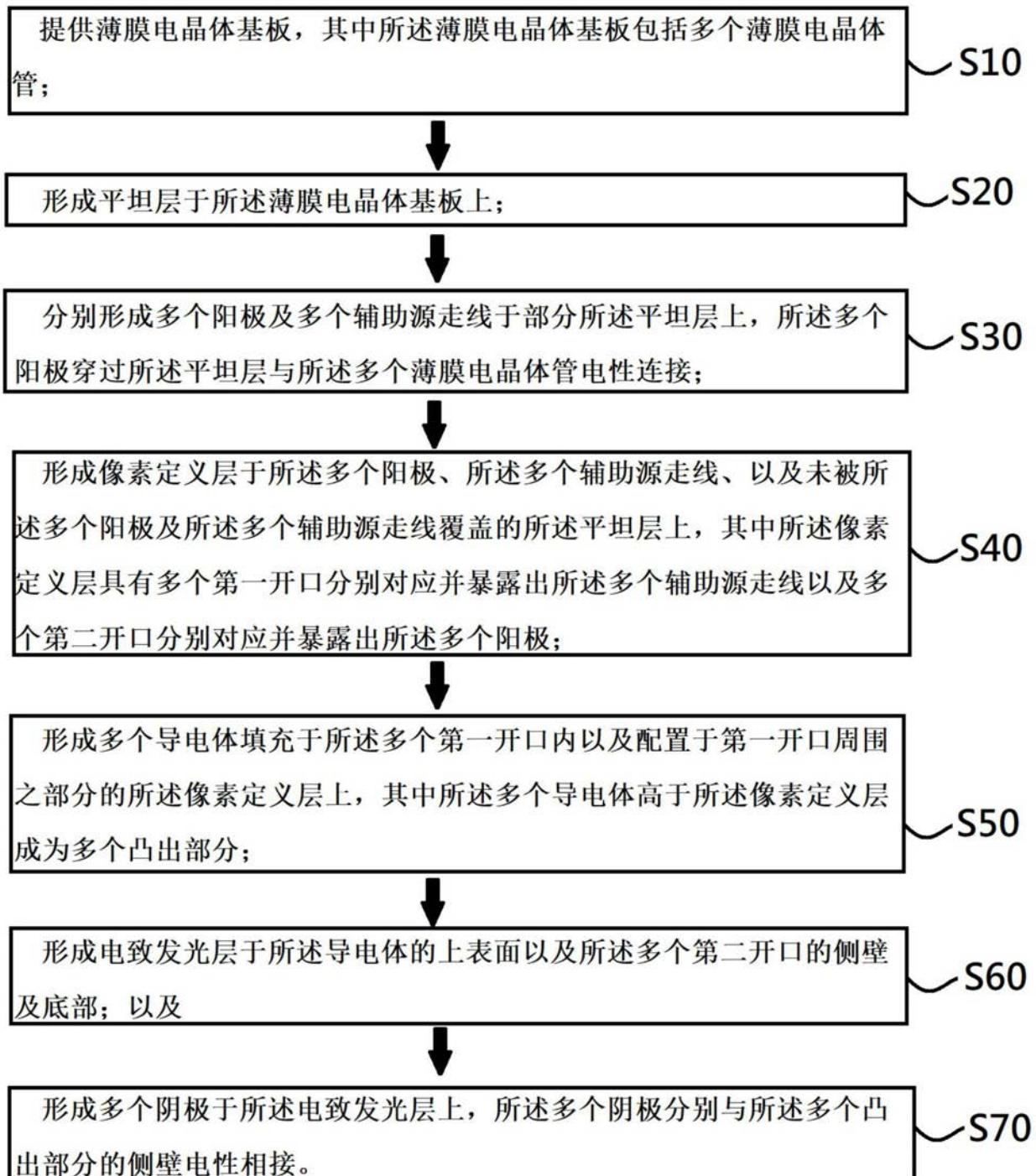

[0031] 图1为依据本发明一实施例的显示器的制备方法流程图。图2A至2E为依据本发明一实施例的显示器的制备方法,各步骤中的显示器的结构示意图。如图1及图2A至2E所示,具体而言,依据本发明的另一实施例,本发明提供了一种显示器100的制备方法,包括:

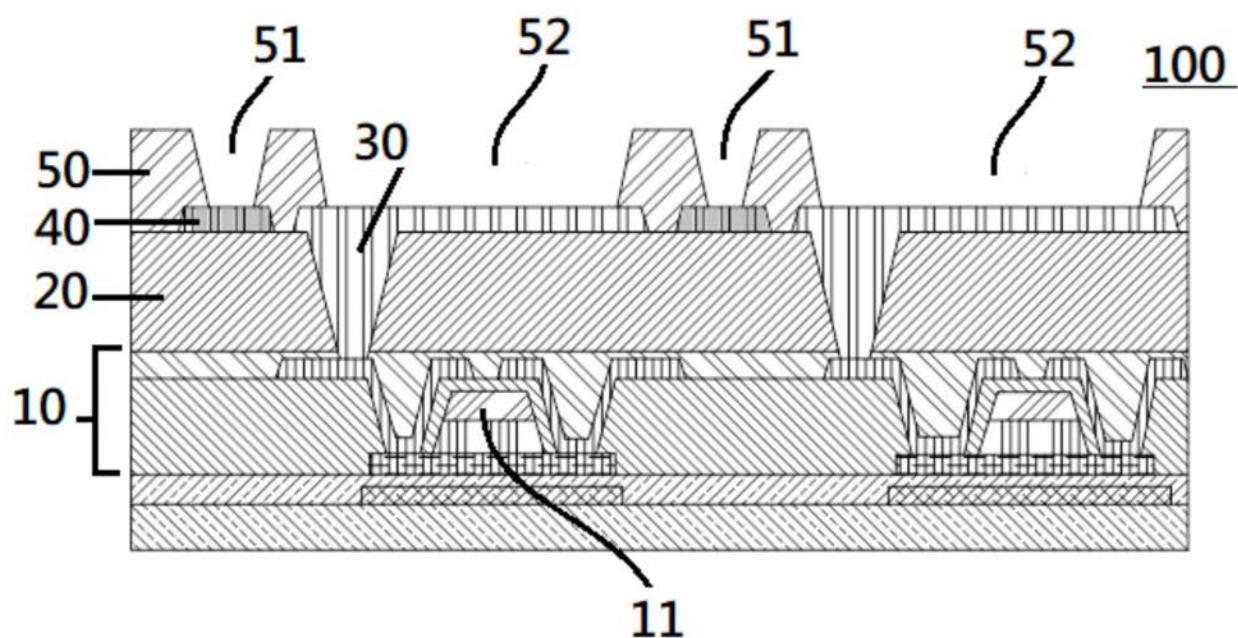

[0032] S10提供薄膜电晶体基板10,其中所述薄膜电晶体基板10包括多个薄膜电晶体管11,如图2A所示;

[0033] S20形成平坦层20于所述薄膜电晶体基板10上,如图2A所示;

[0034] S30分别形成多个阳极30及多个辅助源走线40于部分所述平坦层20上,所述多个阳极30穿过所述平坦层20与所述多个薄膜电晶体管11电性连接,如图2A所示;

[0035] S40形成像素定义层50于所述多个阳极30、所述多个辅助源走线40、以及未被所述多个阳极30及所述多个辅助源走线40覆盖的所述平坦层20上,其中所述像素定义层50具有多个第一开口51分别对应并暴露出所述多个辅助源走线40以及多个第二开口52分别对应并暴露出所述多个阳极30;,如图2B所示

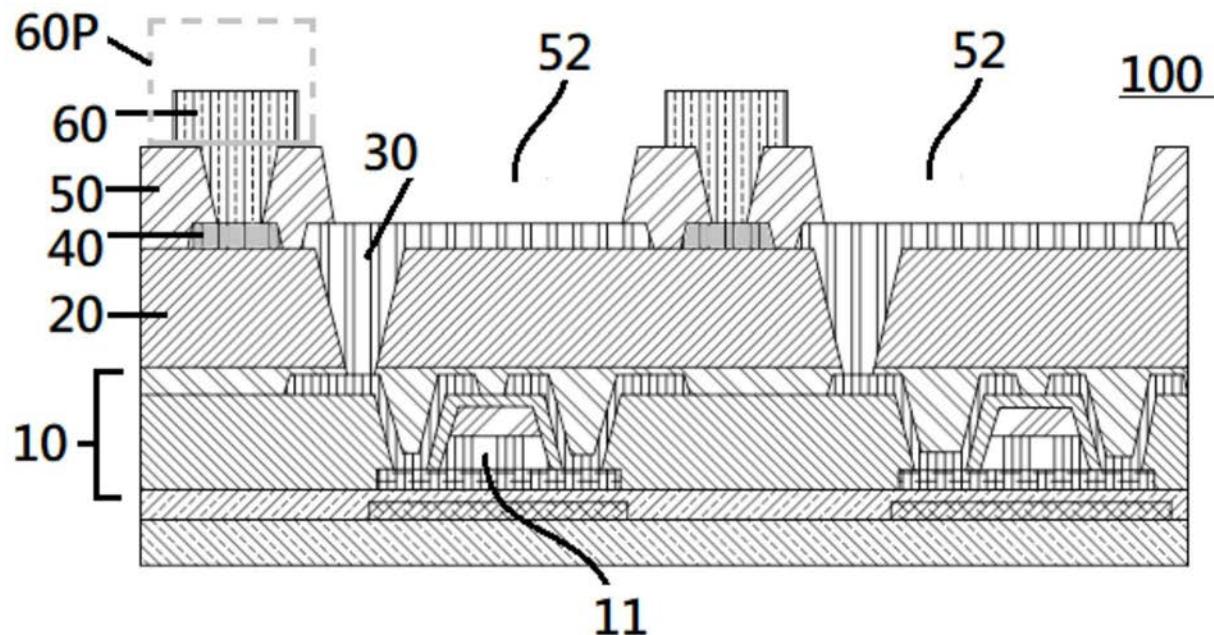

[0036] S50形成多个导电体60填充于所述多个第一开口51内以及配置于第一开口51周围

之部分的所述像素定义层50上,其中所述多个导电体60高于所述像素定义层50成为多个凸出部分60P,如图2C所示;

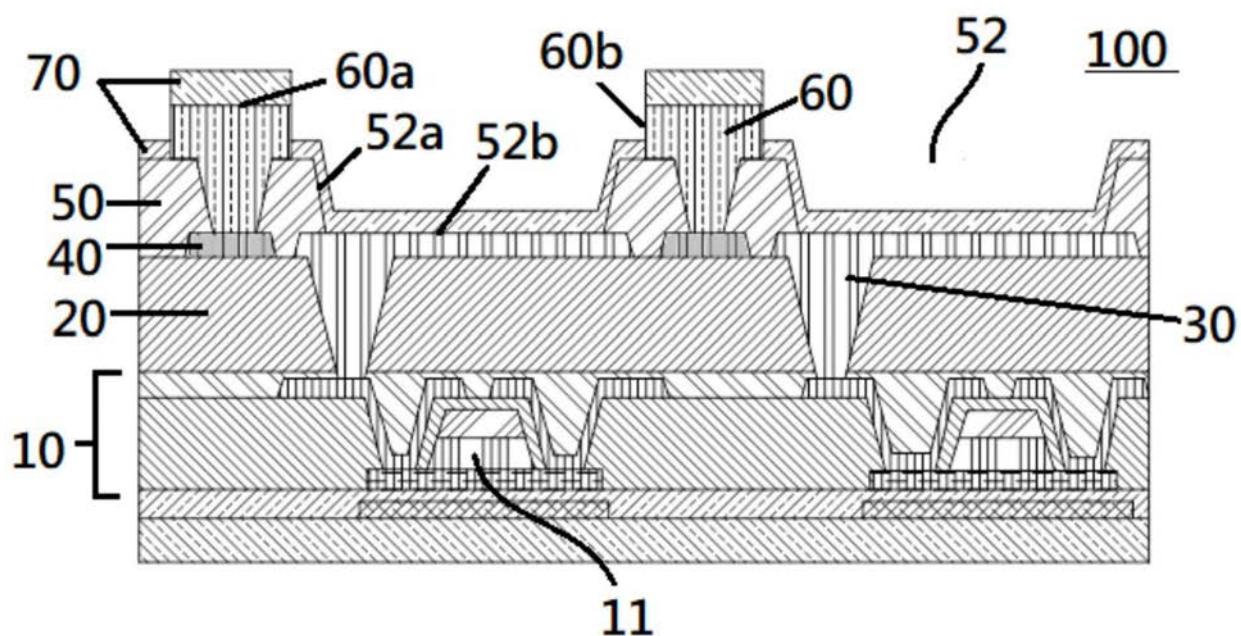

[0037] S60形成电致发光层70于所述导电体60的上表面60a以及所述多个第二开口52的侧壁52a及底部52b,如图2D所示;以及

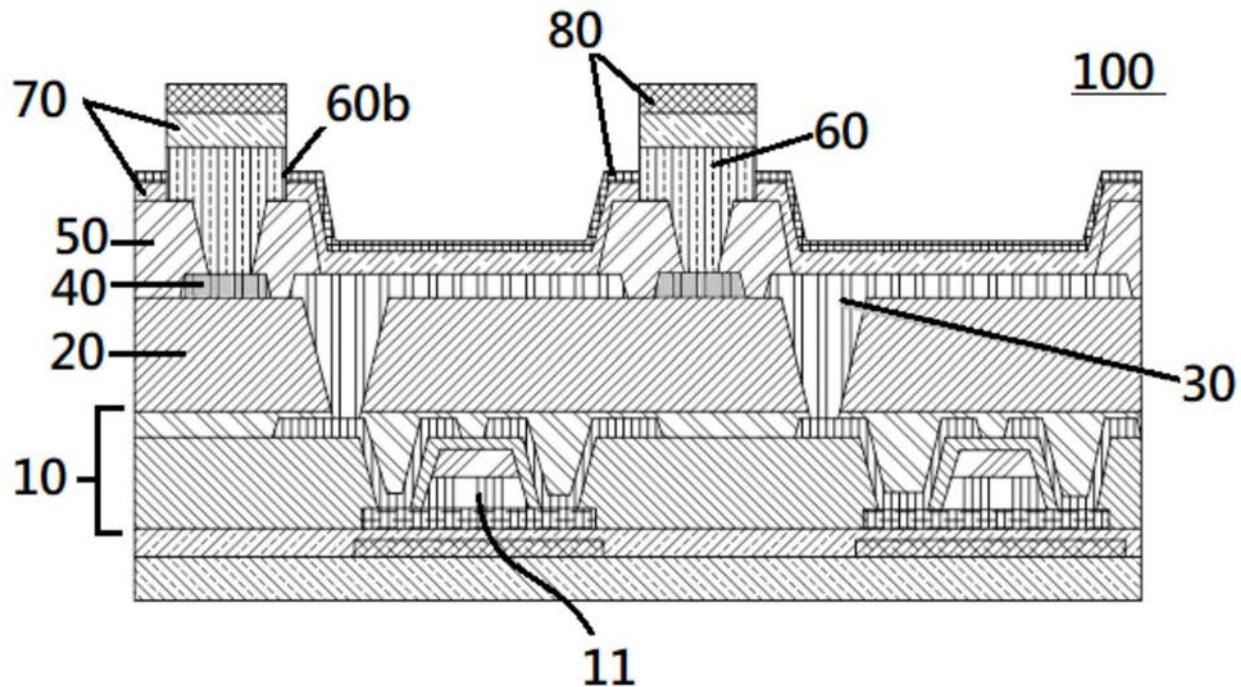

[0038] S70形成多个阴极80于所述电致发光层70上,所述多个阴极80分别与所述多个凸出部分60P的侧壁60b电性相接,如图2E所示。

[0039] 在上述实施例中,在制作像素定义层50时,具体乃沿着子画素(图未示)的长度方向制作开孔,再制作凸出的导电体60,导电体60与辅助源走线40搭接,凸出的导电体60由于厚度大,侧壁陡,使蒸镀的电致发光层70材料(一般厚度为4500Å以内)在导电体60顶部与底部自然断开,在蒸镀阴极80材料时,阴极80材料能在断开的区域搭接在导电体60侧壁60b上,阴极80与导电体60沿子画素的长轴方向的搭接面积变为二维搭接,导通面积大大提高。如此一来,本发明设计的辅助电极不会占用额外的空间,即在增大发光面积设计空间的同时解决大尺寸高分辨率AMOLED面板,顶发光背板点亮时的IR drop问题。

[0040] 如图2C与2D所示,在本发明的一实施例中,步骤S70中,形成所述电致发光层70的方法包括蒸镀,且所述电致发光层70的材料在蒸镀时于所述凸出部分60P的所述侧壁60b处自然断开,于断开处露出所述凸出部分60P的所述侧壁60b。

[0041] 如图2E所示,在本发明的一实施例中,步骤S80中,形成所述多个阴极80的方法包括配合所述夹角选择特定角度进行蒸镀,以实现所述多个阴极80与所述断开处的所述侧壁60b电性相接。

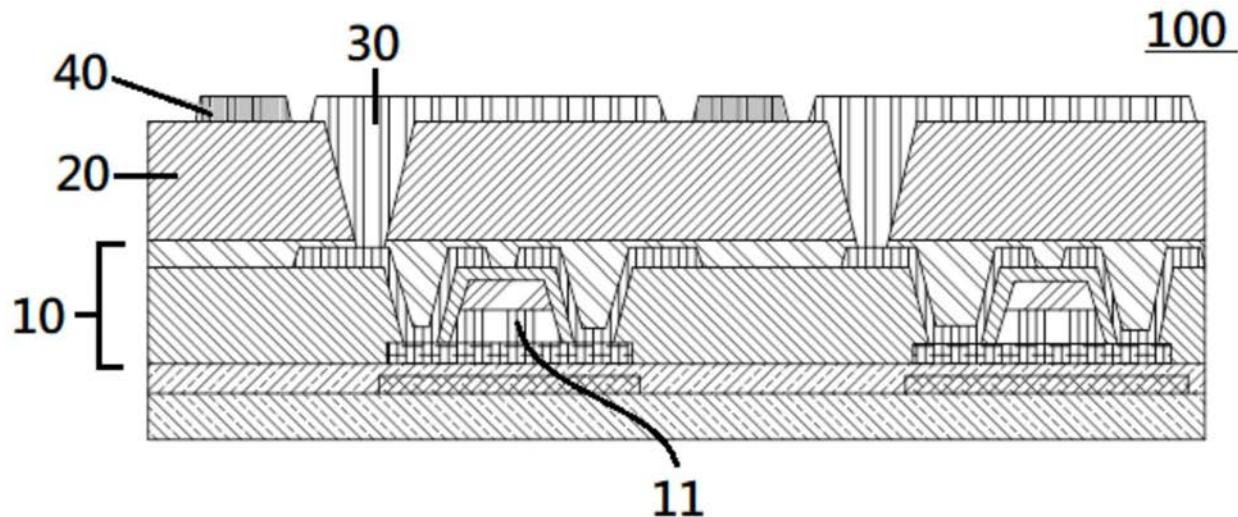

[0042] 参见图2E,依据本发明的一实施例,本发明所提供的显示器100,其特征在于,包括;薄膜电晶体基板10,包括多个薄膜电晶体管11;平坦层20,配置于所述薄膜电晶体基板10上;多个阳极30及多个辅助源走线40,配置于所述平坦层20上,所述多个阳极30穿过所述平坦层20与所述多个薄膜电晶体管11电性连接;像素定义层50,配置于所述多个阳极30、所述多个辅助源走线40、以及未被所述多个阳极30及所述多个辅助源走线40覆盖的所述平坦层20上,其中所述像素定义层50具有多个第一开口51分别对应并暴露出所述多个辅助源走线40以及多个第二开口52分别对应并暴露出所述多个阳极30;多个导电体60,填充于所述多个第一开口51内以及配置于所述多个第一开口51周围之部分的所述像素定义层50上,其中所述多个导电体60高于所述像素定义层50成为多个凸出部分60P;电致发光层70,覆盖在所述导电体60的上表面以及所述多个第二开口52的侧壁及底部;以及多个阴极80,覆盖所述电致发光层70,分别与所述多个导电体60的所述侧壁60b电性相接。

[0043] 如图2E所示,在本发明的一实施例中,所述电致发光层70更覆盖在所述多个第二开口周围的所述像素定义层上。

[0044] 如图2E所示,在本发明的一实施例中,所述多个导电体60高于所述多个阴极80的上表面。本发明所提供的显示器100的多个导电体60优选为高于所述多个阴极80或与其等高,然不排除阴极80高于导电体60的字样。

[0045] 参见图3至图5,在本发明的实施例中,所述多个凸出部分60P可为矩形(参见图3)、不规则形(参见图4)、或倒梯形(参见图5),亦可为上宽下窄的几何图形(图未示)。如此一来,在本发明的实施例中,所述多个凸出部分60P的侧壁与所述像素定义层50的上表面之夹角小于或等于90度。

[0046] 具体而言,在本发明的一实施例中,所述多个凸出部分60P的侧壁可为平整或具有不规则形状的表面。在本发明的其他实施例中,为了尽可能增大阴极80与导电体60的搭接面积,可将导电体60的形状设计成各种不规则形,以及将导电体60侧壁60b边缘制作成具有规则或不规则曲线,以增大导通路径。

[0047] 在本发明的一实施例中,所述多个导电体包括金属或有机导电材料,以及所述电致发光层70包括有机材料。所述电致发光层70发出的光为白光。

[0048] 在本发明的一实施例中,薄膜电晶体基板10可为低温多晶硅 (low temperature poly-silicon,LTPS)、氧化物薄膜电晶体、或固态多晶硅 (solid phase crystallization poly-Si,SPC) 薄膜电晶体等任何晶体管,在此处并不需要特别限制。

[0049] 据此,本发明提供一种显示器,利用大尺寸蒸镀或打印有机发光二极体 (organic light-emitting diode,OLED) 面板的辅助电极的设计,通过改变背板设计,在阳极制程时,提前制作辅助源走线,走线位于像素定义层 (pixel define layer,PDL) 底部,在PDL层制程时,沿子像素长度方向制作开孔,并作凸出导电体,导电体与辅助源走线搭接,根据蒸镀电致发光 (electroluminescence,EL) 层及阴极厚度确定导电体凸出PDL的高度,将凸出导电体的侧壁设计成陡直,使蒸镀EL材料在导电体顶部与底部之间自然断开,断开的区域在蒸镀阴极材料时搭接在导电体侧壁上;由于导电体沿子画素的长轴方向,长度很大,阴极与导电体的搭接面积变为二维搭接,导通面积大大提高,改善以往点接触辅助电极设计效果不明显的弊端。此外,本发明所提出的辅助电极设计不占用额外的空间,即在增大发光面积设计空间的同时,解决大尺寸高分辨率主动矩阵有机发光二极体 (active-matrix organic light-emitting diode,AMOLED) 面板,在点亮顶发光背板时的电压衰退 (IR drop) 问题。

[0050] 综上所述,虽然本发明已以优选实施例揭露如上,但上述优选实施例并非用以限制本发明,本领域的普通技术人员,在不脱离本发明的精神和范围内,均可作各种更动与润饰,因此本发明的保护范围以权利要求界定的范围为准。

图1

图2A

图2B

图2C

图2D

图2E

图3

图4

图5

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示器及其制备方法                                      |         |            |

| 公开(公告)号        | <a href="#">CN110224005A</a>                   | 公开(公告)日 | 2019-09-10 |

| 申请号            | CN201910388679.9                               | 申请日     | 2019-05-10 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                  |         |            |

| [标]发明人         | 唐甲                                             |         |            |

| 发明人            | 唐甲                                             |         |            |

| IPC分类号         | H01L27/32                                      |         |            |

| CPC分类号         | H01L27/3244 H01L2227/323                       |         |            |

| 代理人(译)         | 黄威                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供了一种显示器，包括：薄膜电晶体管基板，包括多个薄膜电晶体管；平坦层；多个阳极及多个辅助源走线，所述多个阳极穿过所述平坦层与所述多个薄膜电晶体管电性连接；像素定义层，具有多个第一开口分别对应并暴露出所述多个辅助源走线以及多个第二开口分别对应并暴露出所述多个阳极；多个导电体，填充于所述多个第一开口内以及配置于所述多个第一开口周围之部分的所述像素定义层上，其中所述多个导电体高于所述像素定义层成为多个凸出部分；电致发光层，覆盖在所述导电体的上表面以及所述多个第二开口的侧壁及底部；以及多个阴极，覆盖所述电致发光层，分别与所述多个导电体的侧壁电性相接。