(12)实用新型专利

(10)授权公告号 CN 206506748 U

(45)授权公告日 2017.09.19

(21)申请号 201720140079.7

(22)申请日 2017.02.16

(73)专利权人 宗仁科技(平潭)有限公司

地址 350400 福建省福州市平潭县北厝镇

台湾创业园17号楼6层B区

(72)发明人 蔡荣怀 陈孟邦 乔世成 卢玉玲

张丹丹

(74)专利代理机构 深圳中一专利商标事务所

44237

代理人 阳开亮

(51)Int.Cl.

H05B 33/08(2006.01)

权利要求书2页 说明书4页 附图1页

(54)实用新型名称

用于电致发光板的驱动集成电路及驱动集成装置

(57)摘要

本实用新型属于集成电路技术领域,提供了一种用于电致发光板的驱动集成电路及驱动集成装置,驱动集成电路与外围电路相连接,外围电路包括电致发光板,该驱动集成电路包括主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管,主控模块输出时钟信号给占空比调节模块,以及输出电平信号给驱动模块;时钟信号经过占空比调节模块进行占空比调节后与电平信号一并控制第一开关管和第二开关管的工作状态,以使电致发光板发光。由此实现了将开关管整合到驱动集成电路中,减少了外围电路的元器件,降低了生产成本,提高了加工良率,解决了现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。

CN 206506748 U

1. 一种用于电致发光板的驱动集成电路,所述驱动集成电路与外围电路相连接,所述外围电路包括所述电致发光板,其特征在于,所述驱动集成电路包括:

主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管;

所述主控模块的第一输出端接所述占空比调节模块的输入端,所述占空比调节模块的第一输出端接所述驱动模块的第一输入端,所述占空比调节模块的第二输出端接所述驱动模块的第二输入端,所述主控模块的第二输出端接所述驱动模块的第三输入端,所述主控模块的控制端接所述驱动模块的第四输入端,所述驱动模块的第一输出端接所述第一开关管的受控端,所述驱动模块的第二输出端接所述第二开关管的受控端,所述第一开关管的输入端接所述外围电路的第一连接端,所述第二开关管的输入端接所述外围电路的第二连接端,所述第一开关管的输出端和所述第二开关管的输出端接地;

所述主控模块输出时钟信号给所述占空比调节模块,以及输出电平信号给所述驱动模块;所述时钟信号经过所述占空比调节模块进行占空比调节后与所述电平信号一并控制所述第一开关管和所述第二开关管的工作状态,以使所述电致发光板发光;

当所述主控模块输出高电平信号给所述驱动模块时,所述第一开关管打开,所述第二开关管关闭;

当所述主控模块输出低电平信号给所述驱动模块时,所述第一开关管关闭,所述第二开关管打开。

2. 如权利要求1所述的驱动集成电路,其特征在于,所述第一开关管和所述第二开关管为三极管或者场效应管。

3. 如权利要求2所述的驱动集成电路,其特征在于,所述第一开关管为第一PNP型三极管,所述第一PNP型三极管的基极、发射极以及集电极分别为所述第一开关管的受控端、输入端以及输出端;或者

所述第一开关管为第一NPN型三极管,所述第一NPN型三极管的基极、集电极以及发射极分别为所述第一开关管的受控端、输入端以及输出端;或者

所述第一开关管为第一P沟道MOS管,所述第一P沟道MOS管的栅极、漏极以及源极分别为所述第一开关管的受控端、输入端以及输出端;或者

所述第一开关管为第一N沟道MOS管,所述第一N沟道MOS管的栅极、漏极以及源极分别为所述第一开关管的受控端、输入端以及输出端。

4. 如权利要求2所述的驱动集成电路,其特征在于,所述第二开关管为第二PNP型三极管,所述第二PNP型三极管的基极、发射极以及集电极分别为所述第二开关管的受控端、输入端以及输出端;或者

所述第二开关管为第二NPN型三极管,所述第二NPN型三极管的基极、集电极以及发射极分别为所述第二开关管的受控端、输入端以及输出端;或者

所述第二开关管为第二P沟道MOS管,所述第二P沟道MOS管的栅极、漏极以及源极分别为所述第二开关管的受控端、输入端以及输出端;或者

所述第二开关管为第二N沟道MOS管,所述第二N沟道MOS管的栅极、漏极以及源极分别为所述第二开关管的受控端、输入端以及输出端。

5. 如权利要求1所述的驱动集成电路,其特征在于,所述主控模块包括控制芯片;

所述控制芯片的第一输出端、第二输出端以及控制端分别为所述主控模块的第一输出

端、第二输出端以及控制端。

6. 如权利要求1所述的驱动集成电路，其特征在于，所述驱动模块包括：

第一反相器INV1、第二反相器INV2、第三反相器INV3、第四反相器INV4、第五反相器INV5、或门NOR1、第一与非门NAND1以及第二与非门NAND2；

所述或门NOR1的第一输入端为所述驱动模块的第一输入端，所述第一反相器INV的输入端为所述驱动模块的第三输入端，所述第一反相器INV的输出端与所述或门NOR1的第二输入端以及所述第二与非门NAND2的第一输入端共接，所述或门NOR1的输出端接所述第一与非门NAND1的第一输入端，所述第二反相器INV2的输入端为所述驱动模块的第四输入端，所述第二反相器INV2的输出端接所述第三反相器INV3的输入端，所述第三反相器INV3的输出端与所述第一与非门NAND1的第二输入端以及所述第二与非门NAND2的第二输入端共接并作为所述驱动模块的第二输入端，所述第一与非门NAND1的输出端接所述第四反相器INV4的输入端，所述第四反相器INV4的输出端为所述驱动模块的第一输出端，所述第二与非门NAND2的输出端接所述第五反相器INV5的输入端，所述第五反相器INV5的输出端为所述驱动模块的第二输出端。

7. 一种用于电致发光板的驱动集成装置，包括外围电路，其特征在于，所述驱动集成装置还包括如权利要求1-6任一项所述的驱动集成电路。

8. 如权利要求7所述的驱动集成装置，其特征在于，所述外围电路的电致发光板包括：

电源VDD、电感L1、二极管D1以及电致发光片EL；

所述电感L1的第一端接所述电源VDD，所述电感L1的第二端与所述二极管D1的第一端共接并作为所述外围电路的第一连接端，所述二极管D1的第二端与所述电致发光片EL的第一端共接并作为所述外围电路的第二连接端，所述电致发光片EL的第二端接地。

## 用于电致发光板的驱动集成电路及驱动集成装置

### 技术领域

[0001] 本实用新型属于集成电路技术领域,特别是涉及一种用于电致发光板的驱动集成电路及驱动集成装置。

### 背景技术

[0002] 传统应用中,在LCD显示驱动、钟表等领域的集成电路,均需要在该集成电路的外部增加开关管,例如:高压三极管,其用于驱动电致发光板以及承受驱动电致发光板所需要的高电压。但是,在集成电路的外部增加高压三极管,会使外围电路的元器件繁多复杂、生产成本高,以及外置的高压三极管会造成产品体积大,导致产品无法朝着体积小、高度集成化的方向发展。

[0003] 因此,现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。

### 实用新型内容

[0004] 本实用新型目的在于提供一种用于电致发光板的驱动集成电路及驱动集成装置,旨在解决现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。

[0005] 本实用新型提供了一种用于电致发光板的驱动集成电路,所述驱动集成电路与外围电路相连接,所述外围电路包括所述电致发光板,所述驱动集成电路包括:

[0006] 主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管;

[0007] 所述主控模块的第一输出端接所述占空比调节模块的输入端,所述占空比调节模块的第一输出端接所述驱动模块的第一输入端,所述占空比调节模块的第二输出端接所述驱动模块的第二输入端,所述主控模块的第二输出端接所述驱动模块的第三输入端,所述主控模块的控制端接所述驱动模块的第四输入端,所述驱动模块的第一输出端接所述第一开关管的受控端,所述驱动模块的第二输出端接所述第二开关管的受控端,所述第一开关管的输入端接所述外围电路的第一连接端,所述第二开关管的输入端接所述外围电路的第二连接端,所述第一开关管的输出端和所述第二开关管的输出端接地;

[0008] 所述主控模块输出时钟信号给所述占空比调节模块,以及输出电平信号给所述驱动模块;所述时钟信号经过所述占空比调节模块进行占空比调节后与所述电平信号一并控制所述第一开关管和所述第二开关管的工作状态,以使所述电致发光板发光;

[0009] 当所述主控模块输出高电平信号给所述驱动模块时,所述第一开关管打开,所述第二开关管关闭;

[0010] 当所述主控模块输出低电平信号给所述驱动模块时,所述第一开关管关闭,所述第二开关管打开。

[0011] 本实用新型提供了一种用于电致发光板的驱动集成装置,包括外围电路,所述驱动集成装置还包括如上述所述的驱动集成电路。

[0012] 本实用新型实施例提供了一种用于电致发光板的驱动集成电路及驱动集成装置，驱动集成电路与外围电路相连接，外围电路包括电致发光板，该驱动集成电路包括主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管，主控模块输出时钟信号给占空比调节模块，以及输出电平信号给驱动模块；时钟信号经过占空比调节模块进行占空比调节后与电平信号一并控制第一开关管和第二开关管的工作状态，以使电致发光板发光；当主控模块输出高电平信号给驱动模块时，第一开关管打开，第二开关管关闭；

[0013] 当主控模块输出低电平信号给驱动模块时，第一开关管关闭，第二开关管打开。由此实现了将开关管整合到驱动集成电路中，减少了外围电路的元器件，降低了生产成本，提高了加工良率，解决了现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。

## 附图说明

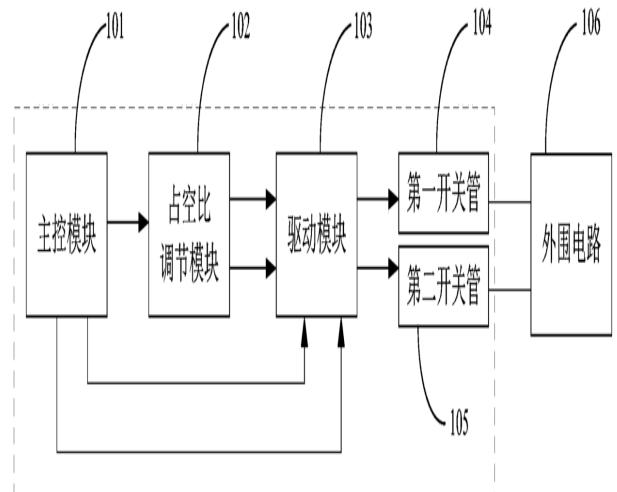

[0014] 图1为本实用新型实施例提供的用于电致发光板的驱动电路的模块结构示意图。

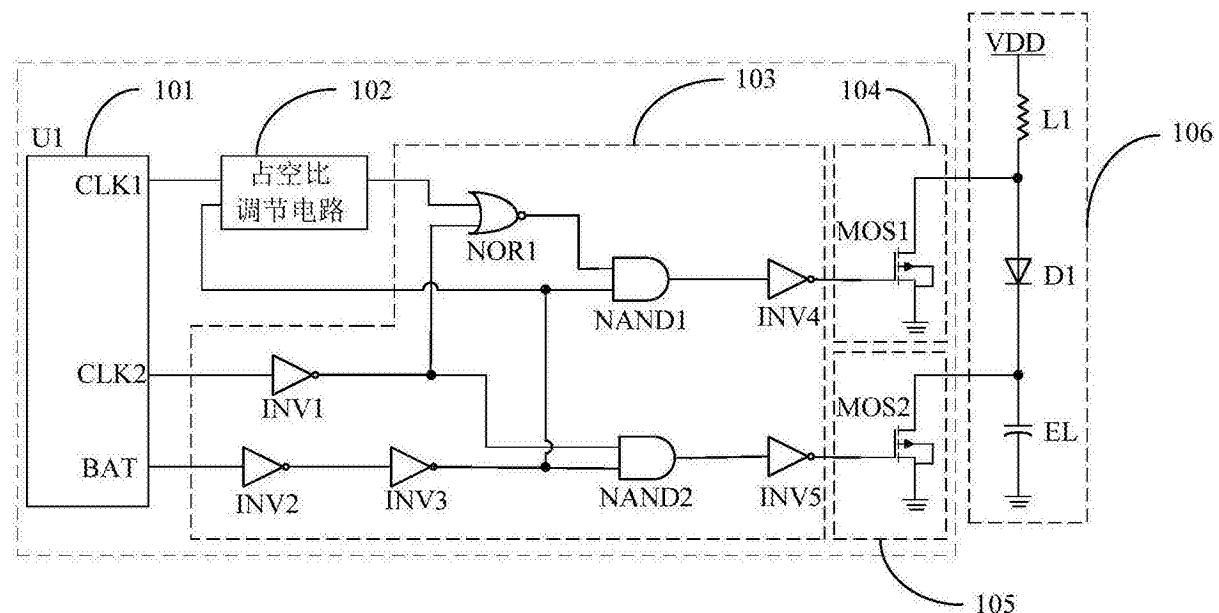

[0015] 图2为本实用新型实施例提供的用于电致发光板的驱动电路的电路连接结构示意图。

## 具体实施方式

[0016] 为了使本实用新型要解决的技术问题、技术方案及有益效果更加清楚明白，以下结合附图及实施例，对本实用新型进行进一步详细说明。应当理解，此处所描述的具体实施例仅仅用以解释本实用新型，并不用于限定本实用新型。

[0017] 本实用新型实施例提供的一种用于电致发光板的驱动集成电路，主要应用于驱动集成装置上，通过主控模块输出时钟信号给占空比调节模块，以及输出电平信号给驱动模块；时钟信号经过占空比调节模块进行占空比调节后与电平信号一并控制第一开关管和第二开关管的工作状态，以使电致发光板发光；当主控模块输出高电平信号给驱动模块时，第一开关管打开，第二开关管关闭；当主控模块输出低电平信号给驱动模块时，第一开关管关闭，第二开关管打开。由此实现了将开关管整合到驱动集成电路中，减少了外围电路的元器件，降低了生产成本，提高了加工良率。

[0018] 图1和图2分别示出了本实用新型实施例提供的用于电致发光板的驱动电路的模块结构和电路连接结构，为了便于说明，仅示出了与本实用新型实施例相关的部分，详述如下：

[0019] 该种用于电致发光板的驱动集成电路，与外围电路106相连接，外围电路106包括电致发光板，该驱动集成电路包括主控模块101、占空比调节模块102、驱动模块103、第一开关管104以及第二开关管105。

[0020] 主控模块101的第一输出端接占空比调节模块102的输入端，占空比调节模块102的第一输出端接驱动模块103的第一输入端，占空比调节模块102的第二输出端接驱动模块103的第二输入端，主控模块101的第二输出端接驱动模块103的第三输入端，主控模块101的控制端接驱动模块103的第四输入端，驱动模块103的第一输出端接第一开关管104的受控端，驱动模块103的第二输出端接第二开关管105的受控端，第一开关管104的输入端接外围电路106的第一连接端，第二开关管105的输入端接外围电路106的第二连接端，第一开关

管104的输出端和第二开关管105的输出端接地。

[0021] 主控模块101输出时钟信号给占空比调节模块102,以及输出电平信号给驱动模块103;时钟信号经过占空比调节模块102进行占空比调节后与电平信号一并控制第一开关管104和第二开关管105的工作状态,以使电致发光板发光;

[0022] 当主控模块101输出高电平信号给驱动模块103时,第一开关管104打开,第二开关管105关闭;

[0023] 当主控模块101输出低电平信号给驱动模块103时,第一开关管104关闭,第二开关管105打开。

[0024] 作为本实用新型一实施例,上述第一开关管104(图2采用场效应管MOS1表示)具体为三极管或者场效应管,只要能达到开关的功能作用亦可。第一开关管104为第一PNP型三极管,第一PNP型三极管的基极、发射极以及集电极分别为第一开关管104的受控端、输入端以及输出端;或者第一开关管104为第一NPN型三极管,第一NPN型三极管的基极、集电极以及发射极分别为第一开关管104的受控端、输入端以及输出端;或者第一开关管104为第一P沟道MOS管,第一P沟道MOS管的栅极、漏极以及源极分别为第一开关管104的受控端、输入端以及输出端;或者第一开关管104为第一N沟道MOS管,第一N沟道MOS管的栅极、漏极以及源极分别为第一开关管104的受控端、输入端以及输出端。

[0025] 作为本实用新型一实施例,上述第二开关管105(图2采用场效应管MOS2表示)具体为三极管或者场效应管,只要能达到开关的功能作用亦可。第二开关管105为第二PNP型三极管,第二PNP型三极管的基极、发射极以及集电极分别为第二开关管105的受控端、输入端以及输出端;或者第二开关管105为第二NPN型三极管,第二NPN型三极管的基极、集电极以及发射极分别为第二开关管105的受控端、输入端以及输出端;或者第二开关管105为第二P沟道MOS管,第二P沟道MOS管的栅极、漏极以及源极分别为第二开关管105的受控端、输入端以及输出端;或者第二开关管105为第二N沟道MOS管,第二N沟道MOS管的栅极、漏极以及源极分别为第二开关管105的受控端、输入端以及输出端。

[0026] 作为本实用新型一实施例,上述主控模块101包括控制芯片U1;所述控制芯片U1的第一输出端CLK1、第二输出端CLK2以及控制端BAT分别为所述主控模块的第一输出端、第二输出端以及控制端。在本实施例中,控制芯片U1采用了型号TB67S109AFNAG的控制芯片,当然,控制芯片的型号不做限定,只要能达到与本实施例控制芯片U1所述的功能作用亦可。

[0027] 作为本实用新型一实施例,上述占空比调节模块101具体为占空比调节电路。占空比调节电路将主控模块101输出的时钟信号进行占空比调节,使得输出的电信号能与驱动模块103进行逻辑功能匹配,并控制开关模块104的工作状态。当然,占空比调节模块101具体也可为占空比可调芯片,只要能达到与本实施例占空比调节电路所述的功能作用亦可。

[0028] 作为本实用新型一实施例,上述驱动模块103包括第一反相器INV1、第二反相器INV2、第三反相器INV3、第四反相器INV4、第五反相器INV5、或门NOR1、第一与非门NAND1以及第二与非门NAND2。

[0029] 或门NOR1的第一输入端为驱动模块103的第一输入端,第一反相器INV的输入端为驱动模块103的第三输入端,第一反相器INV的输出端与或门NOR1的第二输入端以及第二与非门NAND2的第一输入端共接,或门NOR1的输出端接第一与非门NAND1的第一输入端,第二反相器INV2的输入端为驱动模块103的第四输入端,第二反相器INV2的输出端接第三反相

器INV3的输入端,第三反相器INV3的输出端与第一与非门NAND1的第二输入端以及第二与非门NAND2的第二输入端共接并作为驱动模块103的第二输入端,第一与非门NAND1的输出端接第四反相器INV4的输入端,第四反相器INV4的输出端为驱动模块103的第一输出端,第二与非门NAND2的输出端接第五反相器INV5的输入端,第五反相器INV5的输出端为驱动模块103的第二输出端。

[0030] 作为本实用新型一实施例,上述外围电路106包括电致发光板,电致发光板上包括电源VDD、电感L1、二极管D1以及电致发光片EL,电感L1的第一端接电源VDD,电感L1的第二端与二极管D1的第一端共接并作为外围电路106的第一连接端,二极管D1的第二端与电致发光片EL的第一端共接并作为外围电路106的第二连接端,电致发光片EL的第二端接地。

[0031] 以下结合图1和图2对上述一种用于电致发光板的驱动集成电路及驱动集成装置的工作原理进行描述:

[0032] 首先,控制芯片U1通过输出时钟信号给占空比调节电路,并且输出电平信号给驱动模块103;当控制芯片U1输出高电平信号给驱动模块103时,占空比调节电路开始工作,并输出频率为32Khz、占空比为90%左右的信号;接着,控制芯片U1通过第二输出端CLK2输出频率为512Hz的方波(即是CLK\_512信号),当CLK\_512信号为高电平时,经过一系列的功能逻辑之后,使得场效应管MOS2为关闭状态,场效应管MOS1开始接收上述频率为32Khz、占空比为90%的信号,由于外围电路105是一个正常工作的开关直流升压电路,此时场效应管MOS2给外围电路105中的电感L1充电,使得电感L1端口的电压抬高;当CLK\_512信号为低电平时,经过一系列的功能逻辑之后,使得场效应管MOS2打开,场效应管MOS1处于关闭状态,电感L1通过场效应管MOS2放电,端口电压下降;场效应管MOS1与场效应管MOS2以背光工作所需要的频率各自不断地开关,分别给电感L1充放电,利用电感的延时特性,在电致发光板两端产生几十伏或者上百伏的高压,使得电致发光板发光。

[0033] 综上所述,本实用新型实施例提供了一种用于电致发光板的驱动集成电路及驱动集成装置,驱动集成电路与外围电路相连接,外围电路包括电致发光板,该驱动集成电路包括主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管,主控模块输出时钟信号给占空比调节模块,以及输出电平信号给驱动模块;时钟信号经过占空比调节模块进行占空比调节后与电平信号一并控制第一开关管和第二开关管的工作状态,以使电致发光板发光;当主控模块输出高电平信号给驱动模块时,第一开关管打开,第二开关管关闭;当主控模块输出低电平信号给驱动模块时,第一开关管关闭,第二开关管打开。由此实现了将开关管整合到驱动集成电路中,减少了外围电路的元器件,降低了生产成本,提高了加工良率,解决了现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。本实用新型实施例实现简单,不需要增加额外的硬件,可有效降低成本,具有较强的易用性和实用性。

[0034] 以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

图 1

图2

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于电致发光板的驱动集成电路及驱动集成装置                          |         |            |

| 公开(公告)号        | <a href="#">CN206506748U</a>                   | 公开(公告)日 | 2017-09-19 |

| 申请号            | CN201720140079.7                               | 申请日     | 2017-02-16 |

| [标]申请(专利权)人(译) | 宗仁科技(平潭)有限公司                                   |         |            |

| 申请(专利权)人(译)    | 宗仁科技(平潭)有限公司                                   |         |            |

| 当前申请(专利权)人(译)  | 宗仁科技(平潭)有限公司                                   |         |            |

| [标]发明人         | 蔡荣怀<br>陈孟邦<br>乔世成<br>卢玉玲<br>张丹丹                |         |            |

| 发明人            | 蔡荣怀<br>陈孟邦<br>乔世成<br>卢玉玲<br>张丹丹                |         |            |

| IPC分类号         | H05B33/08                                      |         |            |

| CPC分类号         | Y02B20/32 Y02B20/346                           |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本实用新型属于集成电路技术领域，提供了一种用于电致发光板的驱动集成电路及驱动集成装置，驱动集成电路与外围电路相连接，外围电路包括电致发光板，该驱动集成电路包括主控模块、占空比调节模块、驱动模块、第一开关管以及第二开关管，主控模块输出时钟信号给占空比调节模块，以及输出电平信号给驱动模块；时钟信号经过占空比调节模块进行占空比调节后与电平信号一并控制第一开关管和第二开关管的工作状态，以使电致发光板发光。由此实现了将开关管整合到驱动集成电路中，减少了外围电路的元器件，降低了生产成本，提高了加工良率，解决了现有的用于电致发光板的驱动技术存在着外围电路的元器件繁多复杂以及生产成本高的问题。