## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110047435 A (43)申请公布日 2019.07.23

(21)申请号 201910331176.8

(22)申请日 2019.04.23

(71)申请人 京东方科技集团股份有限公司 地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 成军 闫梁臣 王东方

(74)专利代理机构 中科专利商标代理有限责任 公司 11021

代理人 黄亮

(51) Int.CI.

G09G 3/3225(2016.01)

权利要求书2页 说明书11页 附图6页

## (54)发明名称

像素驱动电路及其驱动方法、显示面板和显 示装置

#### (57)摘要

本公开的实施例提出了像素驱动电路及其驱动方法、显示面板和显示装置。该像素驱动电路包括:充电控制模块,被配置为能够在来自扫描信号端的扫描信号的控制下向第一节点传输来自数据信号端的数据信号;信号存储模块,被配置为能够存储来自第一节点的信号或向第一节点传输所存储的信号;第一驱动模块,被配置为能够在第一节点的电平的控制下向有机发光二极管(OLED)元件传输来自第一电压信号端的第一电压信号;以及第二驱动模块,被配置为能够在第一节点的电平的控制下向OLED元件传输来自第二电压信号端的第二电压信号端的第二电压信号。

CN 110047435 A

1.一种像素驱动电路,包括:

充电控制模块,与扫描信号端、数据信号端和第一节点耦接,并被配置为能够在来自所述扫描信号端的扫描信号的控制下向所述第一节点传输来自所述数据信号端的数据信号;

信号存储模块,与所述第一节点和有机发光二极管"OLED"元件耦接,并被配置为能够存储来自所述第一节点的信号或向所述第一节点传输所存储的信号;

第一驱动模块,与所述第一节点、第一电压信号端和所述OLED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述OLED元件传输来自所述第一电压信号端的第一电压信号;以及

第二驱动模块,与所述第一节点、第二电压信号端和所述OLED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述OLED元件传输来自所述第二电压信号端的第二电压信号。

2.根据权利要求1所述的像素驱动电路,其中,所述充电控制模块包括:

第一晶体管,其控制端与所述扫描信号端耦接,第一端与所述数据信号端耦接,以及第二端与所述第一节点耦接。

- 3.根据权利要求1所述的像素驱动电路,其中,所述信号存储模块包括:

- 第一电容器,其第一端与所述第一节点耦接,以及第二端与所述OLED元件耦接。

- 4.根据权利要求1所述的像素驱动电路,其中,所述第一驱动模块包括:

第二晶体管,其控制端与所述第一节点耦接,第一端与所述第一电压信号端耦接,以及第二端与所述OLED元件耦接。

5.根据权利要求1所述的像素驱动电路,其中,所述第二驱动模块包括:

第三晶体管,其控制端与所述第一节点耦接,第一端与所述第二电压信号端耦接,以及第二端与所述OLED元件耦接。

6.根据权利要求1所述的像素驱动电路,还包括:

感测模块,与感测扫描信号端、所述OLED元件、感测输出信号端耦接,并被配置为能够在来自所述感测扫描信号端的感测扫描信号的控制下向所述感测输出信号端传输用于驱动所述OLED元件的驱动信号作为感测输出信号。

7.根据权利要求6所述的像素驱动电路,其中,所述感测模块包括:

第四晶体管,其控制端与所述感测扫描信号端耦接,第一端与所述OLED元件耦接,以及第二端与所述感测输出信号端耦接。

- 8.根据权利要求1所述的像素驱动电路,还包括:

- 一个或多个第三驱动模块,每个所述第三驱动模块与所述第一节点、相应的第三电压信号端和所述OLED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述OLED元件传输来自相应的第三电压信号端的第三电压信号。

- 9.一种显示面板,包括根据权利要求1~8中任一项所述的像素驱动电路。

- 10.一种显示装置,包括根据权利要求9所述的显示面板。

- 11.一种用于驱动根据权利要求1~8中任一项所述的像素驱动电路的方法,在一帧周期中包括以下操作:

在信号写入阶段,扫描信号端输入高电平的扫描信号,数据信号端输入数据信号,第一电压信号端和第二电压信号端分别输入低电平的第一电压信号和第二电压信号,以及所述

像素驱动电路向相应的有机发光二极管"OLED"元件输出低电平的驱动信号;以及

在发光阶段,扫描信号端输入低电平的扫描信号,第一电压信号端输入高电平或低电平的第一电压信号,第二电压信号端相应输入低电平或高电平的第二电压信号,以及所述像素驱动电路向所述OLED元件输出与所述数据信号相对应的驱动信号,以驱动所述OLED元件以相应灰阶发光。

12.根据权利要求11所述的方法,其中,在一帧周期中所述方法还包括以下操作:

在感测阶段,扫描信号端输入低电平的扫描信号,感测扫描信号端输入高电平的感测扫描信号,第一电压信号端输入高电平或低电平的第一电压信号,第二电压信号端相应输入低电平或高电平的第二电压信号,以及感测信号输出端输出与所述数据信号相对应的驱动信号,作为感测输出信号。

## 像素驱动电路及其驱动方法、显示面板和显示装置

## 技术领域

[0001] 本公开涉及显示技术领域,且更具体地涉及像素驱动电路及其驱动方法、显示面板和显示装置。

## 背景技术

[0002] 近年来,随着显示技术的快速发展,薄膜晶体管(TFT)技术由原来的非晶硅(a-Si)薄膜晶体管发展到现在的低温多晶硅(LTPS)薄膜晶体管、金属诱导横向晶化(MILC)薄膜晶体管、氧化物(0xide)薄膜晶体管等,而发光技术也由原来的液晶显示器(LCD)、等离子显示面板(PDP)发展为现在的有机发光二极管(OLED)显示器。

[0003] OLED是新一代的显示器件,其与液晶显示器相比,具有很多优点,例如:自发光、响应速度快、宽视角等等。其可以用于柔性显示、透明显示、3D显示等。有源矩阵有机发光显示器 (AMOLED) 为每一个像素配备了用于控制该像素的开关,例如薄膜晶体管。因此,通过驱动电路,可以独立控制每一个像素,同时不会对其它像素造成串扰等的影响。薄膜晶体管通常至少包含栅极、源极和漏极以及栅绝缘层和有源层。

[0004] 目前,薄膜晶体管的有源层主要为硅,其可以是非晶硅或者多晶硅。采用非晶硅作为有源层的薄膜晶体管,因其特性的限制(如迁移率、开态电流等),难以用于需要较大电流和快速响应的场合,如有机发光显示器和大尺寸、高分辨率、高刷新频率的显示器等。相对地,采用多晶硅作为有源层的薄膜晶体管,其特性优于非晶硅,可以用于有机发光显示器。但是,因其均匀性不佳,制备中大尺寸的面板仍有困难。为此,可以用增加补偿电路的方式来处理多晶硅特性不均匀的问题,但这同时也增加了像素中的薄膜晶体管和电容的数量,增加了掩膜数量和制作难度,造成产量减低和良率下降。另外,如果采用诸如准分子激光退火(ELA)等的LTPS技术来对非晶硅进行晶化,还将需要增加昂贵的设备和维护费用。

[0005] 因此,氧化物半导体日益受到重视。以氧化物半导体为有源层的薄膜晶体管的特性优于非晶硅,如迁移率、开态电流、开关特性等。虽然特性不如多晶硅,但足以用于需要快速响应和较大电流的应用,如高频、高分辨率、大尺寸的显示器以及有机发光显示器等。此外,氧化物的均匀性较好,与多晶硅相比,由于没有均匀性问题,不需要增加补偿电路,在掩膜数量和制作难度上均有优势。在制作大尺寸的显示器方面也没有难度。而且采用溅射等方法就可以制备,不需增加额外的设备,具有成本优势。氧化物薄膜晶体管所采用的氧化物半导体材料,具有高氧含量时能表现很好的半导体特性,具有较低氧含量时具有较低的电阻率,因此可作为透明电极使用。

[0006] 然而,氧化物薄膜晶体管的缺点是稳定性较差,在驱动过程中其阈值电压(Vth)会发生漂移,使画面显示出现如残像、不均匀光斑(Mura)等缺陷,导致产品良率大幅度降低。

## 发明内容

[0007] 为了至少解决或减轻上述技术问题,根据本公开一些实施例,提供了像素驱动电路及其驱动方法、显示面板和显示装置。

[0008] 根据一个方面,本公开的实施例提供了一种像素驱动电路。该像素驱动电路包括: 充电控制模块,与扫描信号端、数据信号端和第一节点耦接,并被配置为能够在来自所述扫描信号端的扫描信号的控制下向所述第一节点传输来自所述数据信号端的数据信号;信号存储模块,与所述第一节点和有机发光二极管"OLED"元件耦接,并被配置为能够存储来自所述第一节点的信号或向所述第一节点传输所存储的信号;第一驱动模块,与所述第一节点、第一电压信号端和所述OLED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述OLED元件传输来自所述第一电压信号端的第一电压信号;以及第二驱动模块,与所述第一节点、第二电压信号端和所述OLED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述OLED元件传输来自所述第二电压信号端的第二电压信号。

[0009] 在一些实施例中,所述充电控制模块包括:第一晶体管,其控制端与所述扫描信号端耦接,第一端与所述数据信号端耦接,以及第二端与所述第一节点耦接。在一些实施例中,所述信号存储模块包括:第一电容器,其第一端与所述第一节点耦接,以及第二端与所述第一节点耦接,等一端与所述第一电压信号端耦接,以及第二端与所述0LED元件耦接。在一些实施例中,所述第一驱动模块包括:第二晶体管,其控制端与所述0LED元件耦接。在一些实施例中,所述第二驱动模块包括:第三晶体管,其控制端与所述第一节点耦接,第一端与所述第二电压信号端耦接,以及第二端与所述0LED元件耦接。在一些实施例中,所述像素驱动电路还包括:感测模块,与感测扫描信号端、所述0LED元件、感测输出信号端耦接,并被配置为能够在来自所述感测扫描信号端的感测扫描信号的控制下向所述感测输出信号端传输用于驱动所述0LED元件的驱动信号作为感测输出信号。在一些实施例中,所述感测模块包括:第四晶体管,其控制端与所述感测扫描信号端耦接,第一端与所述0LED元件耦接,以及第二端与所述感测知出信号端耦接。在一些实施例中,所述像素驱动电路还包括:一个或多个第三驱动模块,每个所述第三驱动模块与所述第一节点、相应的第三电压信号端和所述0LED元件耦接,并被配置为能够在所述第一节点的电平的控制下向所述0LED元件传输来自相应的第三电压信号端的第三电压信号。

[0010] 根据另一方面,提供了一种显示面板。该显示面板包括上述像素驱动电路。

[0011] 根据又一方面,提供了一种显示装置,包括上述显示面板。

[0012] 根据再一方面,提供了一种用于驱动上述像素驱动电路的方法。在一帧周期中,该方法包括以下操作:在信号写入阶段,扫描信号端输入高电平的扫描信号,数据信号端输入数据信号,第一电压信号端和第二电压信号端分别输入低电平的第一电压信号和第二电压信号,以及所述像素驱动电路向相应的有机发光二极管"OLED"元件输出低电平的驱动信号;以及在发光阶段,扫描信号端输入低电平的扫描信号,第一电压信号端输入高电平或低电平的第一电压信号,第二电压信号端相应输入低电平或高电平的第二电压信号,以及所述像素驱动电路向所述OLED元件输出与所述数据信号相对应的驱动信号,以驱动所述OLED以相应灰阶发光。

[0013] 在一些实施例中,在一帧周期中所述方法还包括以下操作:在感测阶段,扫描信号端输入低电平的扫描信号,感测扫描信号端输入高电平的感测扫描信号,第一电压信号端输入高电平或低电平的第一电压信号,第二电压信号端相应输入低电平或高电平的第二电压信号,以及感测信号输出端输出与所述数据信号相对应的驱动信号,作为感测输出信号。 [0014] 通过使用根据本公开实施例的像素驱动电路及其驱动方法、显示面板和显示装 置,可以有效抑制氧化物薄膜晶体管乃至各种薄膜晶体管的阈值电压漂移,进而减少显示器中出现残像、Mura等问题的可能性,提升产品良率、寿命等。

#### 附图说明

[0015] 通过下面结合附图说明本公开的优选实施例,将使本公开的上述及其它目的、特征和优点更加清楚,其中:

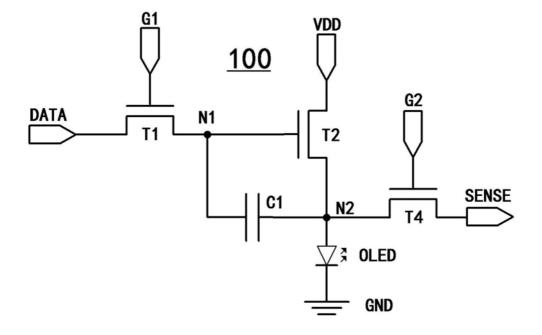

[0016] 图1是示出了根据相关技术的像素驱动电路的示例具体构造的示意图。

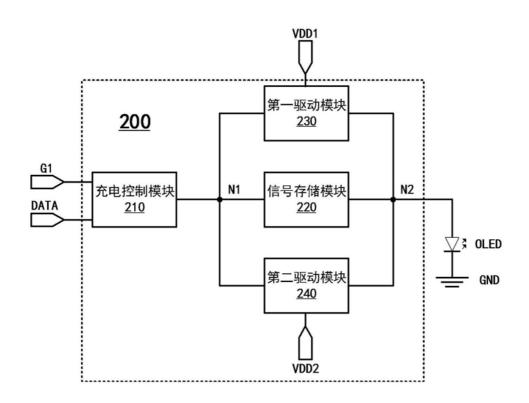

[0017] 图2是示出了根据本公开实施例的像素驱动电路的示例构造的示意图。

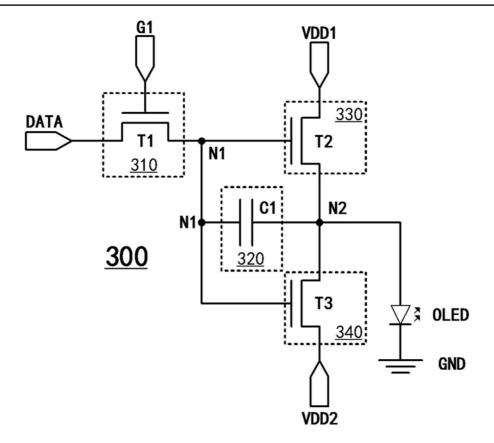

[0018] 图3是示出了图2所示的像素驱动电路的示例具体构造的示意图。

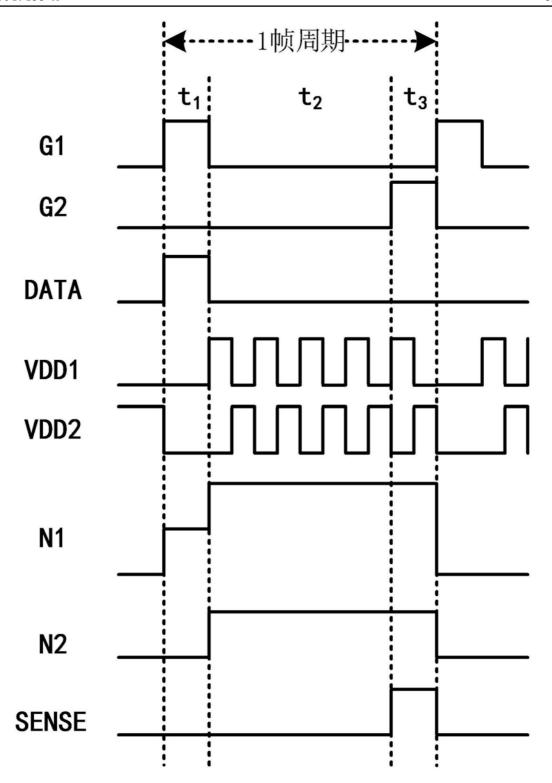

[0019] 图4是示出了图3所示的像素驱动电路的示例工作时序图。

[0020] 图5是示出了根据本公开另一实施例的像素驱动电路的示例构造的示意图。

[0021] 图6是示出了图5所示的像素驱动电路的示例具体构造的示意图。

[0022] 图7是示出了图6所示的像素驱动电路的示例工作时序图。

[0023] 图8是示出了根据本公开实施例的用于驱动像素驱动电路的示例方法的流程图。

## 具体实施方式

[0024] 下面参照附图对本公开的部分实施例进行详细说明,在描述过程中省略了对于本公开来说是不必要的细节和功能,以防止对本公开的理解造成混淆。在本说明书中,下述用于描述本公开原理的各种实施例只是说明,不应该以任何方式解释为限制公开的范围。参照附图的下述描述用于帮助全面理解由权利要求及其等同物限定的本公开的示例性实施例。下述描述包括多种具体细节来帮助理解,但这些细节应认为仅仅是示例性的。因此,本领域普通技术人员应认识到,在不脱离本公开的范围和精神的情况下,可以对本文中描述的实施例进行多种改变和修改。此外,为了清楚和简洁起见,省略了公知功能和结构的描述。此外,贯穿附图,相同的附图标记用于相同或相似的功能、器件和/或操作。此外,在附图中,各部分并不一定按比例来绘制。换言之,附图中的各部分的相对大小、长度等并不一定与实际比例相对应。

[0025] 在本公开中,术语"包括"和"含有"及其派生词意为包括而非限制;术语"或"是包含性的,意为和/或。此外,在本公开的以下描述中,所使用的方位术语,例如"上"、"下"、"左"、"右"等均用于指示相对位置关系,以辅助本领域技术人员理解本公开实施例,且因此本领域技术人员应当理解:在一个方向上的"上"/"下",在相反方向上可变为"下"/"上",且在另一方向上,可能变为其它位置关系,例如"左"/"右"等。

[0026] 以下,以本公开实施例应用于0LED显示装置的像素驱动电路为例来详细说明。然而本领域技术人员应当理解本公开的应用领域不限于此。事实上,根据本公开实施例的像素驱动电路等可以应用于其它需要使用像素驱动电路的领域中,例如LCD显示装置等。

[0027] 此外,尽管在以下描述中以晶体管为N型晶体管为例进行了描述,然而本公开不限于此。事实上,如本领域技术人员所能够理解的:当以下提及的各个晶体管中的一个或多个为P型晶体管时同样可以实现本申请的技术方案,只需对电平设置/耦接关系进行相应的调整即可。

[0028] 图1是示出了根据相关技术的像素驱动电路100的示例具体构造的示意图。如图1

所示,像素驱动电路100包括第一晶体管T1、第二晶体管T2、第四晶体管T4和第一电容器C1。[0029] 第一晶体管T1的控制端与扫描信号端G1耦接,其第一端与数据信号端DATA耦接,以及第二端与第一节点N1耦接。第一晶体管T1可以在来自扫描信号端G1的扫描信号的控制下将来自数据信号端DATA的数据信号写入第一节点N1。

[0030] 第一电容器C1的一端与第一节点N1耦接,以及另一端与第二节点N2耦接。第一电容器C1可以用于保存被写入第一节点N1的数据信号,并在第一晶体管T1关断时维持第一节点N1的信号电平。

[0031] 第二晶体管T2的控制端与第一节点N1耦接,其第一端与第一电压信号端VDD耦接,以及第二端与第二节点N2耦接。第二晶体管T2可以在第一节点N1的电平的控制下向第二节点N2(进而向OLED元件)提供来自电压信号端VDD的电压/电流信号,以驱动OLED元件正常工作。

[0032] 第四晶体管T4的控制端与感测扫描信号端G2耦接,其第一端与第二节点N2耦接,以及第二端与感测输出信号端SENSE耦接。第四晶体管T4可以在来自感测扫描信号端G2的感测扫描信号的控制下,向感测输出信号端SENSE输出其感测到的通过第二节点N2的驱动电流,以使得与感测输出信号端SENSE耦接的外部补偿电路能够根据该驱动电流对后续帧的驱动电流加以补偿,从而避免或减少由于第二晶体管T2在长期导通状态下发生的阈值漂移所引起的工作不良。这样。通过采用这样的电路结构,可以实现对OLED元件的驱动。

[0033] 然而,如前所述,由于在此过程中随着第二晶体管T2工作时间的延长,其阈值电压会发生漂移。特别是如果其一直处于导通状态且电流极性一直不变,则更容易发生阈值电压的单向漂移,进而使OLED元件表现出变暗或者变亮。在大尺寸上应用时,由于在不同区域的像素驱动电路中的温度、电流不同,使屏幕的不同区域处显示出残像、Mura、亮暗不均等缺陷。

[0034] 为了解决或至少部分既减轻上述问题,提出了根据本公开实施例的像素驱动电路及其驱动方法、以及包括像素驱动电路在内的显示面板和显示装置。总体上,可以通过设置多个驱动晶体管来减少单个驱动晶体管的驱动时间,从而避免或减少单个驱动晶体管出现阈值电压漂移的现象,由此提升像素驱动电路乃至显示面板、显示装置的寿命。更具体地,在一些实施例中,当第一驱动晶体管工作时第二驱动晶体管可处于休息状态,而当第二驱动晶体管工作时第一驱动管可处于休息状态。

[0035] 以下,将结合图2~图4来描述根据本公开实施例的示例像素驱动电路的构造和工作原理。

[0036] 图2是示出了根据本公开实施例的像素驱动电路200的示例构造的示意图。根据图 2所示的像素驱动电路200可以包括充电控制模块210、信号存储模块220、第一驱动模块230 和第二驱动模块240。其可以如图2所示与0LED元件耦接,并驱动0LED元件工作。

[0037] 如图2所示,充电控制模块210可以与扫描信号端G1、数据信号端DATA和第一节点N1耦接,并被配置为能够在来自扫描信号端G1的扫描信号的控制下向第一节点N1传输来自数据信号端DATA的数据信号。信号存储模块220可以与第一节点N1和0LED元件耦接,并被配置为能够存储来自第一节点N1的信号或向第一节点N1传输所存储的信号。第一驱动模块230可以与第一节点N1、第一电压信号端VDD1和0LED元件(或第二节点N2)耦接,并被配置为能够在第一节点N1的电平的控制下向0LED元件传输来自第一电压信号端VDD1的第一电压

信号。第二驱动模块240可以与第一节点N1、第二电压信号端VDD2和0LED元件(或第二节点N2) 耦接,并被配置为能够在第一节点N1的电平的控制下向0LED元件传输来自第二电压信号端VDD2的第二电压信号。

[0038] 通过采用如图2所示的电路设计,可以在第一驱动模块230和第二驱动模块240之间切换,实现多个驱动模块协同工作,减少单个驱动模块的驱动时间,避免或减少驱动模块中的TFT的阈值漂移现象,从而提升显示器的显示质量。接下来,将结合图3来详细描述图2所示的像素驱动电路的具体构造。

[0039] 图3是示出了根据本公开实施例的像素驱动电路300(例如,图2所示的像素驱动电路200)的示例具体构造的示意图。与图2所示的像素驱动电路200类似,图3所示的像素驱动电路300也可以相应包括充电控制模块310、信号存储模块320、第一驱动模块330和第二驱动模块340。其可以如图3所示与0LED元件耦接,并驱动0LED元件工作。

[0040] 在图3所示实施例中,充电控制模块310可以包括第一晶体管T1,其控制端可以与扫描信号端G1耦接,第一端可以与数据信号端DATA耦接,以及第二端可以与第一节点N1耦接。换言之,充电控制模块310能够在来自扫描信号端G1的扫描信号的控制下向第一节点N1传输来自数据信号端DATA的数据信号。

[0041] 信号存储模块320可以包括第一电容器C1,其第一端可以与第一节点N1耦接,以及第二端可以与0LED元件耦接。换言之,信号存储模块320能够存储来自第一节点N1的信号或向第一节点N1传输所存储的信号。

[0042] 第一驱动模块330可以包括第二晶体管T2,其控制端可以与第一节点N1耦接,第一端可以与第一电压信号端VDD1耦接,以及第二端可以与0LED元件(或第二节点N2)耦接。换言之,第一驱动模块330能够在第一节点N1的电平的控制下向0LED元件传输来自第一电压信号端VDD1的第一电压信号。

[0043] 第二驱动模块340可以包括第三晶体管T3,其控制端与第一节点N1耦接,第一端与第二电压信号端VDD2耦接,以及第二端可以与0LED元件(或第二节点N2)耦接。换言之,第二驱动模块340能够在第一节点N1的电平的控制下向0LED元件传输来自第二电压信号端VDD2的第二电压信号。

[0044] 同样地,通过采用如图3所示的电路设计,可以在第一驱动模块330和第二驱动模块340之间切换,实现多个驱动模块协同工作,减少单个驱动模块的驱动时间,避免或减少驱动模块中的TFT的阈值漂移现象,从而提升显示器的显示质量。接下来,将结合图4来详细描述图3所示的像素驱动电路300的工作流程。

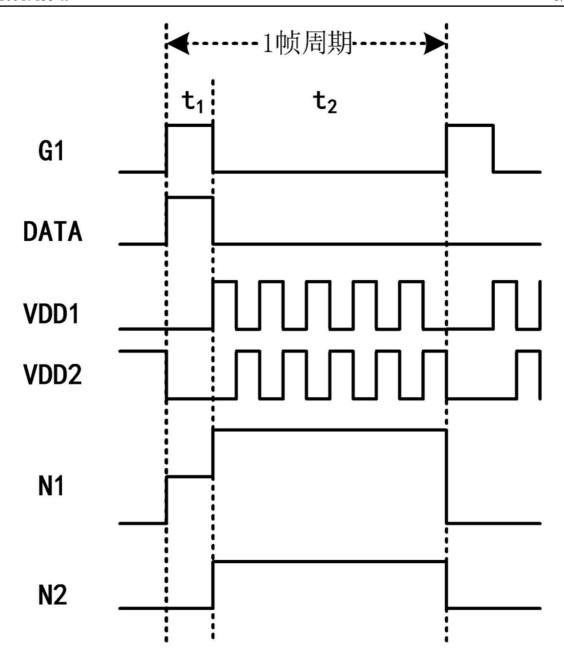

[0045] 图4是示出了根据图3所示的像素驱动电路300的示例工作时序图。以下将结合图3来详细说明图4所示的像素驱动电路300的驱动方法。图4所示的驱动像素驱动电路300的方法在一帧周期中包括以下操作。

[0046] 在信号写入阶段(t<sub>1</sub>),扫描信号端G1可输入高电平的扫描信号,数据信号端DATA可输入数据信号(例如,在图4所示实施例中,与最高灰阶(例如,255)相对应的高电平数据信号),第一电压信号端VDD1和第二电压信号端VDD2可分别输入低电平的第一电压信号和第二电压信号,从而像素驱动电路300可向相应的OLED元件输出低电平的驱动信号。

[0047] 具体地,在阶段 $t_1$ 中,扫描信号端G1针对当前像素的像素驱动电路300输入高电平的扫描信号(例如,对当前像素所属的像素行进行扫描),所以第一晶体管T1导通,从而使得

来自数据信号端DATA的数据信号传输至(或写入)第一节点N1,并进而在第一电容器C1中充电,使得第一电容器C1两端的电压与数据信号相同。此外,当数据信号的电平高于第二晶体管T2的阈值电压(Vth)时,第二晶体管T2导通,从而使得来自第一电压信号端VDD1的第一电压信号传输至第二节点N2,并使得来自第二电压信号端VDD2的第二电压信号也传输至第二节点N2。如图4所示,在阶段t1中,第一电压信号和第二电压信号都可以是低电平(例如,零电平)电压信号,且因此第一电容器C1可不受影响,进而不对第一节点N1的电平产生影响,如图4所示。

[0048] 然而,需要注意的是:在另一些实施例中,在阶段t<sub>1</sub>中,第一电压信号和第二电压信号也不一定是低电平电压信号。例如,这二者之一可以是高电平电压信号,从而通过第一电容器C1的自举作用,将第一节点N1的电平拉升至更高的电平,从而与图4所示的时序图相比,提前将第一节点N1的电平拉升至更高的电平,这同样可以使得像素驱动电路300能够工作。

[0049] 回到图4,由于第一电压信号和第二电压信号在阶段 $t_1$ 都是低电平电压信号,因此第二节点N2的电平同样为低电平,且0LED元件在该阶段中不发光或以最低限度的灰阶发光。

[0050] 此外,在发光阶段(t<sub>2</sub>),扫描信号端G1可输入低电平的扫描信号,第一电压信号端 VDD1可输入高电平或低电平的第一电压信号,第二电压信号端VDD2可相应输入低电平或高电平的第二电压信号,以及像素驱动电路300可向0LED元件输出与数据信号相对应的驱动信号,以驱动0LED元件以相应灰阶发光。

[0051] 具体地,扫描信号端G1针对当前像素的像素驱动电路300输入低电平的扫描信号(例如,对除了当前像素所属的像素行之外的其它像素行进行扫描),所以第一晶体管T1关断。在第一晶体管T1关断的情况下,第一电容器C1可保持第一节点N1的电平。换言之,当在前一阶段 $t_1$ 中数据信号的电平高于第二晶体管T2的阈值电压时,在本阶段 $t_2$ 中第一节点N1的电平依然保持高于第二晶体管T2的阈值电压,使得第二晶体管T2导通,进而使得来自第一电压信号端VDD1的第一电压信号和来自第二电压信号端VDD2的第二电压信号传输至第二节点N2。如图4所示,在阶段 $t_2$ 中,第一电压信号和第二电压信号之一可始终保持高电平信号,同时另一个呈开路状态或低电平信号状态,即第一电压信号端VDD1或第二电压信号端VDD2中的相应一个保持浮置(floating)状态。

[0052] 例如,当第一电压信号端VDD1输入高电平的第一电压信号且第二电压信号端VDD2 浮置时,第一电压信号经过第二晶体管T2传输至第二节点N2并进而驱动OLED元件发光。同时,由于此时第三晶体管T3在第一节点N1的控制下也导通,从而第一电压信号也会传输到第三晶体管T3,然而由于第二电压信号端VDD2此时浮置,因此在第一电压信号的作用下所形成的全部电流都会流经OLED元件,用于驱动其发光。虽然电流全部流经OLED元件,但对于第三晶体管T3而言,其源漏电压方向与在第一电压信号端VDD1浮置情况下的源漏电压方向相反,从而在一定程度上对第二晶体管T2和第三晶体管T3可能出现的阈值电压漂移进行了补偿。

[0053] 此外,当第一电压信号端VDD1浮置且第二电压信号端VDD2输入高电平的第二电压信号时,第二电压信号经过第三晶体管T3传输至第二节点N2并进而驱动OLED元件发光。同时,由于此时第二晶体管T2在第一节点N1的控制下也导通,从而第二电压信号也会传输到

第二晶体管T2,然而由于第一电压信号端VDD1此时浮置,因此在第二电压信号的作用下所形成的全部电流都会流经OLED元件,用于驱动其发光。虽然电流全部流经OLED元件,但对于第二晶体管T2而言,其源漏电压方向与在第二电压信号端VDD2浮置情况下的源漏电压方向相反,从而在一定程度上对第二晶体管T2和第三晶体管T3可能出现的阈值电压漂移进行了补偿。

[0054] 换言之,在阶段 $t_2$ 中,由于第二晶体管 $T_2$ 和第三晶体管 $T_3$ 的源漏电压方向周期性改变,因此减轻了其长期处于单向加压状态下所可能出现的阈值电压漂移的问题。或者从电流的角度来看,第二晶体管 $T_2$ 和第三晶体管 $T_3$ 在阶段 $t_2$ 中周期性处于工作或休息状态,且因此减轻了其长期处于单向电流工作状态下所可能出现的阈值电压漂移的问题。

[0055] 此外,由于第二节点N2在阶段 $t_2$ 中始终保持高电平,因此在第一电容器C1的自举作用下,第一节点N1的电平如图4所示进一步增高,并保持第二晶体管T2和第三晶体管T3处于导通状态,使得,第一电压信号端VDD1和第二电压信号端的电压信号能够持续向0LED元件输出,直至一帧周期结束。

[0056] 接下来,可以开始下一帧的工作周期,与前面描述的类似。然而,如果如图4所示,在下一帧画面中相应子像素不发光(例如,由于画面为纯红色,则相应像素内的蓝色子像素和绿色子像素都不发光),从而来自数据信号端DATA的数据信号为低电平,则第一节点N1始终保持低电平,第二晶体管T2和第三晶体管T3也都在该下一帧中保持关断状态,从而使得相应OLED元件不发光。

[0057] 需要注意的是:图4所示的工作时序图仅仅是用于说明的一个实施例,其与实际的工作时序图可能并不相同。例如,在一些实施例中,各输入/输出电压信号可能不像图4所示的那样为方波,而是会出现随时间发生微小抖动的波形,或者脉冲的上升沿/下降沿并非如图4一样竖直,而是存在一定斜率变化。此外,在图4所示实施例中,第一电压信号和第二电压信号在发光阶段t2中的占空比大体上各50%,然而本公开不限于此。换言之,在另一些实施例中,可以存在具有不同占空比的两个电压信号。在一些极端的示例中,只要存在两个电压信号交替驱动0LED元件,都可以实现减轻单一驱动晶体管的阈值漂移问题的效果。

[0058] 此外,尽管图2~图4所示的实施例中仅示出了两个驱动模块(例如,第一驱动模块230/330和第二驱动模块240/340),然而本公开不限于此。例如,在一些实施例中,像素驱动电路200或300还可以包括一个或多个第三驱动模块。每个第三驱动模块可以与第一节点N1、相应的第三电压信号端和OLED元件(或第二节点N2) 耦接,并被配置为能够在第一节点N1的电平的控制下向OLED元件传输来自相应的第三电压信号端的第三电压信号。

[0059] 具体地,在例如图3所示的像素驱动电路300中,可以在第一节点N1和第二节点N2之间增加与第二晶体管T2和第三晶体管T3并联的一个或多个晶体管,使得这些晶体管的控制端耦接到第一节点N1,第一端耦接到各自的第三电压信号端,且第二端耦接到第二节点N2。此外,可以对图4所示的工作时序进行修改,使得第一电压信号端VDD1、第二电压信号端VDD2和一个或多个第三电压信号端在第二阶段t2中始终保持其中一个为高电平,而其余保持浮置或低电平,从而使得相应像素驱动电路能够实现进一步减少单个驱动晶体管的工作时间,避免或至少减轻单个驱动晶体管的阈值电压漂移问题的出现。

[0060] 此外,尽管在图4所示实施例中,在一帧期间在第一电压信号端VDD1和第二电压信号端VDD2之间进行多次切换,其切换周期可以是几毫秒、零点几毫秒或更短等,但本公开不

限于此。在另一些实施例中,在来自第一电压信号端VDD1的第一电压信号和来自第二电压信号端VDD2的第二电压信号之间进行切换的周期可以从1秒钟到数小时不等,例如每隔多个帧来切换用于驱动OLED元件的电压信号端。此外,在一些实施例中,第一电压信号端VDD1和第二电压信号端VDD2的交替开和闭可通过采用外围电路、芯片、电容器、脉冲开关等中的一项或多项来进行周期性控制。

[0061] 此外,尽管在图4所示实施例中,仅示出了来自数据信号端DATA在一帧中输入与最大灰阶相对应的数据信号以及在下一帧中输入与最小灰阶相对应的数据信号,但本公开不限于此。换言之,在另一些实施例中,完全可以从数据信号端DATA输入与当前像素/子像素所应当显示的灰阶相对应的数据信号。例如,在采用256等级灰阶(0~255)的情况下,可以输入与灰阶0、1、2、...、255中任一个相对应的数据信号,以使得与该像素驱动电路200/300相关联的0LED元件(或任何其它显示元件)能够以相应灰阶发光。

[0062] 此外,在一些实施例中,由于存在多个驱动晶体管(例如,第二晶体管T2和第三晶体管T3),则在这些驱动晶体管中的一些驱动晶体管出现问题时,通过修改相应驱动电压信号端的电压信号,可以让显示器继续正常工作。例如,可以将与出现问题的驱动晶体管相对应的电压信号端长期关闭,而只用其余的驱动晶体管来驱动OLED元件。换言之,在减轻了阈值电压漂移问题的同时,为显示面板提供了冗余性和鲁棒性。

[0063] 此外,尽管在图3所示实施例中,采用了N型晶体管作为示例之用,但本公开不限于此。在另一些实施例中,也可以采用P型晶体管。在又一些实施例中,一个驱动晶体管可以是N型晶体管,而另一个驱动晶体管可以是P型晶体管。

[0064] 此外,需要注意的是:图3所示的像素驱动电路300仅是实现图2所示的像素驱动电路200的一种方式,而本公开不限于此。例如,除了通过控制第一电压信号端VDD1和第二电压信号端VDD2各自的电压信号之外,也可以通过设置单独的切换模块来控制第一驱动模块230和第二驱动模块240轮流驱动OLED元件来使得每个驱动模块单独驱动OLED元件的时间减少,从而避免或减轻其薄膜晶体管长时间处于单向导通状态下所产生的阈值电压漂移问题。

[0065] 此外,在一些实施例中,上述薄膜晶体管的半导体活化层材料可以是任何可以作为半导体的材料。例如,对于氧化物薄膜晶体管,其半导体材料可以是包含以下中至少一项在内的薄膜:In(铟)、Ga(镓)、Zn(锌)、0(氧)、Sn(锡)等元素。此外,对于其它材料如a-Si、P-Si等,本公开所述方案同样适用。换言之,根据本公开实施例的像素驱动电路可以用于氧化物薄膜晶体管、非晶硅薄膜晶体管、多晶硅薄膜晶体管、有机薄膜晶体管等的任何一种形成的驱动电路。

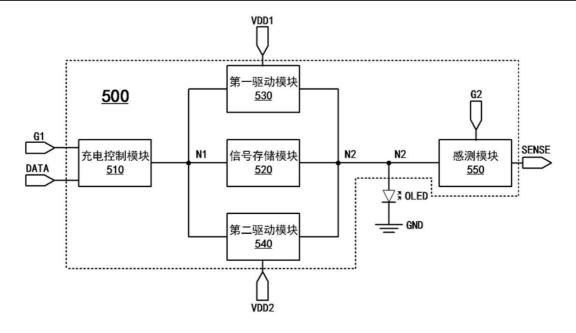

[0066] 接下来,将结合图5~图7来描述根据本公开另一实施例的示例像素驱动电路的构造和工作原理。与图2~4所示的像素驱动电路相比,图5~图7的像素驱动电路进一步增加了用于补偿的感测模块,其可以通过检测用于驱动OLED元件的实际驱动电流并向外部的感测补偿模块报告,以使得感测补偿模块能够调整在下一帧中提供的数据电压,进而对像素驱动电路中的驱动晶体管的阈值电压加以补偿,使得显示效果更加稳定,进一步避免出现残像、Mura等现象,提升产品良率。

[0067] 图5是示出了根据本公开另一实施例的像素驱动电路500的示例构造的示意图。与图2所示的像素驱动电路200类似,图5所示的像素驱动电路500也可以包括充电控制模块

510、信号存储模块520、第一驱动模块530和第二驱动模块540。其可以如图5所示与0LED元件耦接,并驱动0LED元件工作。鉴于充电控制模块510、信号存储模块520、第一驱动模块530和第二驱动模块540与图2所示的充电控制模块210、信号存储模块220、第一驱动模块230和第二驱动模块240大体相似,且因此省略对其的详细描述。

[0068] 此外,在图5所示实施例中,像素驱动电路500还可以包括感测模块550。如图5所示,感测模块550可以与感测扫描信号端G2、0LED元件(或第二节点N2)、感测输出信号端SENSE耦接,并被配置为能够在来自感测扫描信号端G2的感测扫描信号的控制下向感测输出信号端SENSE传输(原本)用于驱动OLED元件的驱动信号作为感测输出信号。

[0069] 通过如下面结合图7所描述的工作流程,感测模块550可以感测用于驱动0LED元件的实际驱动信号,并向外部的感测补偿模块反馈,以调整后续的数据信号,进而补偿驱动晶体管的阈值电压漂移,进一步避免出现残像、Mura等现象,提升产品良率。接下来,将结合图6来详细描述图5所示的像素驱动电路的具体构造。

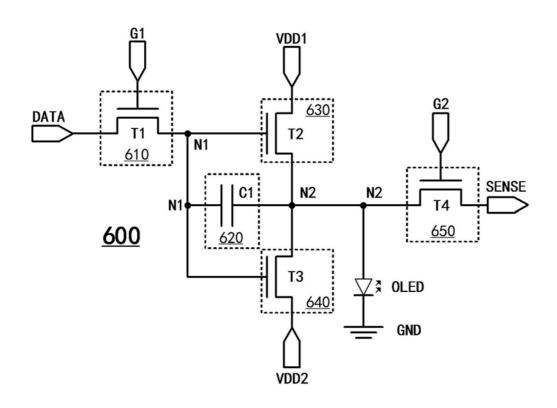

[0070] 图6是示出了根据本公开另一实施例的像素驱动电路600(例如,图5所示的像素驱动电路500)的示例具体构造的示意图。与图5所示的像素驱动电路500类似,图6所示的像素驱动电路600也可以相应包括充电控制模块610、信号存储模块620、第一驱动模块630、第二驱动模块640和感测模块650。其可以如图6所示与0LED元件耦接,并驱动0LED元件工作。

[0071] 如前所述,充电控制模块610、信号存储模块620、第一驱动模块630和第二驱动模块640的具体构造(例如,第一晶体管T1、第二晶体管T2、第三晶体管T3和第一电容器C1等)与图3所示的相应充电控制模块310、信号存储模块320、第一驱动模块330和第二驱动模块340的具体构造大体相同,且因此这里省略对其的详细描述,而仅详细描述与感测模块650有关的元件。

[0072] 如图6所示,感测模块650可以包括第四晶体管T4,其控制端可以与感测扫描信号端G2耦接,第一端可以与OLED元件(或第二节点N2)耦接,以及第二端可以与感测输出信号端SENSE耦接。换言之,感测模块650能够在来自感测扫描信号端G2的感测扫描信号的控制下向感测输出信号端SENSE传输(原本)用于驱动OLED元件的驱动信号作为感测输出信号。

[0073] 同样地,通过采用如图6所示的电路设计,可以在第一驱动模块630和第二驱动模块640之间切换,实现多个驱动模块协同工作,减少单个驱动模块的驱动时间,避免或减少驱动模块中的TFT的阈值漂移现象,从而提升显示器的显示质量。此外,通过设置感测模块650,可以通过对感测到的驱动信号进行补偿来进一步避免或减少驱动模块中的TFT的阈值漂移现象,从而进一步提升显示器的显示质量。接下来,将结合图7来详细描述图6所示的像素驱动电路的工作流程。

[0074] 图7是示出了根据图6所示的像素驱动电路600的示例工作时序图。以下将结合图6来详细说明图7所示的像素驱动电路600的驱动方法。与图4所示的方法类似,图7所示的驱动像素驱动电路600的方法在一帧周期中也包括以下操作:

[0075] 在信号写入阶段  $(t_1)$ ,扫描信号端G1可输入高电平的扫描信号,数据信号端DATA 可输入数据信号,第一电压信号端VDD1和第二电压信号端VDD2可分别输入低电平的第一电压信号和第二电压信号,从而像素驱动电路600可向相应的0LED元件输出低电平的驱动信号。

[0076] 在发光阶段(t<sub>2</sub>),扫描信号端G1可输入低电平的扫描信号,第一电压信号端VDD1

可输入高电平或低电平的第一电压信号,第二电压信号端VDD2可相应输入低电平或高电平的第二电压信号,从而像素驱动电路600可向OLED元件输出与数据信号相对应的驱动信号,以驱动OLED元件以相应灰阶发光。

[0077] 鉴于图7所示的这两个阶段与图4所示的相应阶段类似,因此这里不再对其进行详细描述。以下,将仅详细描述与感测模块650有关的阶段。

[0078] 如图7所示,在一帧周期中方法还包括感测阶段(t<sub>3</sub>)。

[0079] 在感测阶段(t<sub>3</sub>),扫描信号端G1输入低电平的扫描信号,感测扫描信号端G2可输入高电平的感测扫描信号,第一电压信号端VDD1可输入高电平或低电平的第一电压信号,第二电压信号端VDD2可相应输入低电平或高电平的第二电压信号,以及感测信号输出端SENSE可输出与数据信号相对应的驱动信号,作为感测输出信号。

[0080] 具体地,在阶段 $t_3$ 中,由于扫描信号端G1、第一电压信号端VDD1和第二电压信号端VDD2与阶段 $t_2$ 中输入相同的信号,因此第一晶体管T1、第二晶体管T2、第三晶体管T3、第一电容器C1等的工作状态与阶段 $t_2$ 中类似,在此不再详细描述。此外,由于感测扫描信号端G2输入高电平的感测扫描信号,因此第四晶体管T4导通,所以在阶段 $t_2$ 中原本用于驱动OLED元件的驱动电流在阶段 $t_3$ 中可通过第四晶体管T4从感测输出信号端SENSE向外输出,以使得外部的感测补偿模块能够根据该感测输出信号来调整后续的数据信号。

[0081] 接下来,开始下一帧的工作周期,与前面描述的类似。然而,如果如图7所示,在下一帧画面中相应子像素不发光(例如,由于画面为纯紫色,则相应像素内的绿色子像素不发光),从而来自数据信号端DATA的数据信号为低电平,则第一节点N1始终保持低电平,第二晶体管T2和第三晶体管T3也都在该下一帧中保持关断状态,从而使得相应0LED元件不发光,而感测模块650所感测并输出的感测输出信号也相应地为指示不发光的低电平。

[0082] 需要注意的是:图7所示的工作时序图仅仅是用于说明的一个实施例,其与实际的工作时序图可能并不相同。例如,在一些实施例中,各输入/输出电压信号可能不像图7所示的那样为方波,而是会出现随时间发生微小抖动的波形,或者脉冲的上升沿/下降沿并非如图7一样竖直,而是存在一定斜率变化。此外,在图7所示实施例中,第一电压信号和第二电压信号在发光阶段t2和感测阶段t3中的占空比大体上各50%,然而本公开不限于此。换言之,在另一些实施例中,可以存在具有不同占空比的两个电压信号。在一些极端的示例中,只要存在两个电压信号交替驱动OLED元件,都可以实现减轻单一驱动晶体管的阈值漂移问题的效果。

[0083] 以下,将结合图8来详细描述根据本公开实施例的用于驱动像素驱动电路的方法。 [0084] 图8是示出了根据本公开实施例的驱动像素驱动电路200、300、500和/或600的示例方法800的流程图。如图8所示,方法800可以包括步骤S810和S820。根据本公开,方法800的一些步骤可以单独执行或组合执行,以及可以并行执行或顺序执行,并不局限于图8所示的具体操作顺序。在一些实施例中,方法800可以由本文所述各像素驱动电路或另一外部设备执行。

[0085] 方法800可以开始于步骤S810,在步骤S810中,在信号写入阶段,扫描信号端可输入高电平的扫描信号,数据信号端可输入数据信号,第一电压信号端和第二电压信号端可分别输入低电平的第一电压信号和第二电压信号,以及像素驱动电路可向相应的OLED元件输出低电平的驱动信号。

[0086] 在步骤S820中,在发光阶段,扫描信号端可输入低电平的扫描信号,第一电压信号端可输入高电平或低电平的第一电压信号,第二电压信号端可相应输入低电平或高电平的第二电压信号,以及像素驱动电路可向OLED元件输出与数据信号相对应的驱动信号,以驱动OLED元件以相应灰阶发光。

[0087] 在一些实施例中,对于例如具有感测模块的像素驱动电路(例如,像素驱动电路500或600),方法800还可以包括感测阶段。在该感测阶段中,扫描信号端可输入低电平的扫描信号,感测扫描信号端可输入高电平的感测扫描信号,第一电压信号端可输入高电平或低电平的第一电压信号,第二电压信号端可相应输入低电平或高电平的第二电压信号,以及感测信号输出端可输出与数据信号相对应的驱动信号,作为感测输出信号。

[0088] 此外,根据本公开的一些实施例,还提供了显示面板,其可以包括如上所述的任一种或多种像素驱动电路。

[0089] 此外,根据本公开的一些实施例,还提供了显示装置,其可以包括如上所述的显示面板。

[0090] 通过使用根据本公开实施例的像素驱动电路及其驱动方法、显示面板和显示装置,可以有效抑制氧化物薄膜晶体管的阈值电压漂移,进而减少显示器中出现残像、Mura等问题的可能性,提升产品良率、寿命等。

[0091] 至此已经结合优选实施例对本公开进行了描述。应该理解,本领域技术人员在不脱离本公开的精神和范围的情况下,可以进行各种其它的改变、替换和添加。因此,本公开的范围不局限于上述特定实施例,而应由所附权利要求所限定。

[0092] 此外,在本文中被描述为通过纯硬件、纯软件和/或固件来实现的功能,也可以通过专用硬件、通用硬件与软件的结合等方式来实现。例如,被描述为通过专用硬件(例如,现场可编程门阵列(FPGA)、专用集成电路(ASIC)等)来实现的功能,可以由通用硬件(例如,中央处理单元(CPU)、数字信号处理器(DSP))与软件的结合的方式来实现,反之亦然。

图1

图2

图3

图4

图5

图6

图7

800

在信号写入阶段,扫描信号端输入高电平的扫描信号,数据信号端输入数据信号,第一电压信号端和第二电压信号端分别输入低电平的第一电压信号和第二电压信号,以及像素驱动电路向相应的OLED元件输出低电平的驱动信号

<u>810</u>

在发光阶段,扫描信号端输入低电平的扫描信号,第一电压信号端输入高电平或低电平的第一电压信号,第二电压信号端相应输入低电平或高电平的第二电压信号,以及像素驱动电路向OLED元件输出与数据信号相对应的驱动信号,以驱动OLED元件以相应灰阶发光

<u>820</u>

图8

| 专利名称(译)        | 像素驱动电路及其驱动方法、显示面板和显示装置 |         |            |  |

|----------------|------------------------|---------|------------|--|

| 公开(公告)号        | <u>CN110047435A</u>    | 公开(公告)日 | 2019-07-23 |  |

| 申请号            | CN201910331176.8       | 申请日     | 2019-04-23 |  |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司          |         |            |  |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司          |         |            |  |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司          |         |            |  |

| [标]发明人         | 成军<br>闫梁臣<br>王东方       |         |            |  |

| 发明人            | 成军<br>闫梁臣<br>王东方       |         |            |  |

| IPC分类号         | G09G3/3225             |         |            |  |

| CPC分类号         | G09G3/3225             |         |            |  |

| 代理人(译)         | 黄亮                     |         |            |  |

| 外部链接           | Espacenet SIPO         |         |            |  |

|                |                        |         |            |  |

## 摘要(译)

本公开的实施例提出了像素驱动电路及其驱动方法、显示面板和显示装置。该像素驱动电路包括:充电控制模块,被配置为能够在来自扫描信号端的扫描信号的控制下向第一节点传输来自数据信号端的数据信号;信号存储模块,被配置为能够存储来自第一节点的信号或向第一节点传输所存储的信号;第一驱动模块,被配置为能够在第一节点的电平的控制下向有机发光二极管(OLED)元件传输来自第一电压信号端的第一电压信号;以及第二驱动模块,被配置为能够在第一节点的电平的控制下向OLED元件传输来自第二电压信号端的第二电压信号。