(12)发明专利申请

(10)申请公布号 CN 109742131 A

(43)申请公布日 2019.05.10

(21)申请号 201910149465.6

(22)申请日 2019.02.28

(71)申请人 上海天马微电子有限公司

**地址** 201201 上海市浦东新区汇庆路888、

889号

(72)发明人 张卿 姚绮君 苏晓越

(74)专利代理机构 北京晟睿智杰知识产权代理

事务所(特殊普通合伙)

11603

代理人 于淼

(51) Int.Cl.

H01L 27/32(2006.01)

G09G 3/3225(2016.01)

权利要求书2页 说明书9页 附图10页

(54)发明名称

显示面板及显示装置

## (57) 摘要

本发明公开了一种显示面板及显示装置，涉及显示技术领域，包括：衬底基板，设置在衬底基板上的多个像素单元，各像素单元包括驱动薄膜晶体管、开关薄膜晶体管、重置薄膜晶体管和有机发光器件；在沿垂直于衬底基板所在平面的方向，开关薄膜晶体管的源极和漏极分别位于该开关薄膜晶体管的栅极的两侧，重置薄膜晶体管的源极和漏极分别位于该重置薄膜晶体管的栅极的两侧；开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极电连接，重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极电连接，驱动薄膜晶体管的漏极与有机发光器件耦接。如此方案，有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积，有利于实现高PPI设计。

100

1. 一种显示面板，其特征在于，包括：

衬底基板，

设置在所述衬底基板上的多个像素单元，各所述像素单元包括驱动薄膜晶体管、开关薄膜晶体管、重置薄膜晶体管和有机发光器件；

在沿垂直于所述衬底基板所在平面的方向，所述开关薄膜晶体管的源极和漏极分别位于该开关薄膜晶体管的栅极的两侧，所述重置薄膜晶体管的源极和漏极分别位于该重置薄膜晶体管的栅极的两侧；所述开关薄膜晶体管的漏极与所述驱动薄膜晶体管的栅极电连接，所述重置薄膜晶体管的漏极与所述驱动薄膜晶体管的漏极电连接，所述驱动薄膜晶体管的漏极与所述有机发光器件耦接。

2. 根据权利要求1所述的显示面板，其特征在于，所述开关薄膜晶体管和所述重置薄膜晶体管为氧化物薄膜晶体管，所述驱动薄膜晶体管为低温多晶硅薄膜晶体管。

3. 根据权利要求1所述的显示面板，其特征在于，还包括相互绝缘的多条栅极线、多条数据线、多条重置信号线和多条电源信号线；

各所述开关薄膜晶体管的栅极连接所述栅极线，各所述开关薄膜晶体管的源极连接所述数据线；各所述驱动薄膜晶体管的源极连接所述电源信号线；各所述重置薄膜晶体管的栅极连接所述重置信号线，各所述重置薄膜晶体管的源极连接重置电压信号。

4. 根据权利要求3所述的显示面板，其特征在于，还包括沿垂直于所述衬底基板的方向依次设置于所述衬底基板上的第一金属层、第二金属层、第三金属层、氧化物沟道层、第四金属层和第五金属层；

所述驱动薄膜晶体管的栅极位于所述第一金属层，源极和漏极位于所述第二金属层；所述开关薄膜晶体管和所述重置薄膜晶体管的栅极位于所述第三金属层，所述开关薄膜晶体管的源极位于所述第四金属层，所述重置薄膜晶体管的源极位于所述第五金属层；所述开关薄膜晶体管的漏极位于所述氧化物沟道层与所述衬底基板之间，所述重置薄膜晶体管的漏极位于所述氧化物沟道层与所述第一金属层之间。

5. 根据权利要求4所述的显示面板，其特征在于，还包括第一金属线，所述第一金属线位于所述开关薄膜晶体管的氧化物沟道层远离所述衬底基板的一侧；

所述第一金属线通过第一过孔与所述开关薄膜晶体管的氧化物沟道层电连接，所述第一金属线与所述开关薄膜晶体管的栅极和漏极在所述衬底基板所在平面的正投影交叠，所述开关薄膜晶体管的源极和栅极在所述衬底基板所在平面的正投影交叠。

6. 根据权利要求5所述的显示面板，其特征在于，所述第一金属线在所述衬底基板所在平面的正投影覆盖所述开关薄膜晶体管的漏极。

7. 根据权利要求5所述的显示面板，其特征在于，所述第一金属线与所述开关薄膜晶体管的源极位于不同膜层。

8. 根据权利要求7所述的显示面板，其特征在于，所述第一金属线位于所述第五金属层。

9. 根据权利要求4所述的显示面板，其特征在于，所述驱动薄膜晶体管的栅极复用为所述开关薄膜晶体管的漏极。

10. 根据权利要求4所述的显示面板，其特征在于，还包括第二金属线，所述第二金属线位于所述重置薄膜晶体管的氧化物沟道层远离所述衬底基板的一侧；

所述第二金属线通过第二过孔与所述重置薄膜晶体管的氧化物沟道层电连接，所述第二金属线与所述重置薄膜晶体管的栅极和漏极在所述衬底基板所在平面的正投影交叠，所述重置薄膜晶体管的源极和栅极在所述衬底基板所在平面的正投影交叠。

11. 根据权利要求10所述的显示面板，其特征在于，所述第二金属线在所述衬底基板所在平面的正投影覆盖所述重置薄膜晶体管的漏极。

12. 根据权利要求10所述的显示面板，其特征在于，所述第二金属线与所述重置薄膜晶体管的源极位于不同膜层。

13. 根据权利要求12所述的显示面板，其特征在于，所述第二金属线位于所述第四金属层。

14. 根据权利要求10所述的显示面板，其特征在于，所述驱动薄膜晶体管的漏极复用为所述重置薄膜晶体管的漏极。

15. 根据权利要求4所述的显示面板，其特征在于，所述有机发光器件位于所述第四金属层远离所述衬底基板的一侧，所述有机发光器件包括依次设置的阳极、发光层和阴极，所述阳极与所述驱动薄膜晶体管的漏极耦接。

16. 根据权利要求4所述的显示面板，其特征在于，还包括多晶硅层，所述多晶硅层位于所述第一金属层朝向所述衬底基板的一侧，所述驱动薄膜晶体管的栅极、源极和漏极在所述衬底基板所在平面的正投影覆盖所述多晶硅层。

17. 根据权利要求4所述的显示面板，其特征在于，所述氧化物沟道层的厚度为 $D1, 20\text{nm} \leq D1 \leq 80\text{nm}$ 。

18. 根据权利要求3所述的显示面板，其特征在于，所述像素单元形成多个沿第一方向延伸的像素单元列，所述像素单元列包括奇数列和偶数列，所述奇数列和所述偶数列沿第二方向交替排布，所述第一方向和所述第二方向交叉；

沿所述第一方向，所述奇数列和所述偶数列错位排布，错位距离小于所述第一方向上两个相邻所述子像素单元之间的距离。

19. 根据权利要求18所述的显示面板，其特征在于，至少部分相邻的所述奇数列和所述偶数列中，各所述开关薄膜晶体管连接同一所述数据线，所述数据线向所述奇数列和所述偶数列的像素单元提供数据信号。

20. 根据权利要求18所述的显示面板，其特征在于，至少部分位于所述奇数列的子像素对应的重置信号线复用为位于所述偶数列的子像素对应的栅极线，至少部分位于所述奇数列的子像素对应的栅极线复用为位于所述偶数列的子像素对应的重置信号线。

21. 一种显示装置，其特征在于，包括权利要求1至20之任一所述的显示面板。

## 显示面板及显示装置

### 技术领域

[0001] 本发明涉及显示技术领域,更具体地,涉及一种显示面板及显示装置。

### 背景技术

[0002] 随着科学技术的发展,带有显示面板的显示装置的用途越来越广泛,使得人们对显示面板的要求越来越多样化,不再只满足于显示面板的大尺寸、高清晰度等常规的性能指标,也对显示面板的PPI (Pixels Per Inch) 有了较高的要求。

[0003] 显示面板的PPI是图像分辨率的单位,表示的是显示面板的每英寸所拥有的像素(Pixel)数目,当显示面板的PPI达到一定数值时,人眼就分辨不出颗粒感了。现有技术中,为配合像素正常发光,会在显示面板上引入一系列的电路结构,电路结构所占用的空间对PPI有直接的影响,因此,如何实现显示面板的高PPI设计成为现阶段亟待解决的技术问题之一。

### 发明内容

[0004] 有鉴于此,本发明提供了一种显示面板及显示装置,将开关薄膜晶体管和重置薄膜晶体管的源漏极设置在栅极的两侧,有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积,节约的空间使显示面板能够设置更多的像素单元,因而有利于实现显示面板及显示装置的高PPI设计。

[0005] 第一方面,本申请提供了一种显示面板,包括:

[0006] 衬底基板,

[0007] 设置在所述衬底基板上的多个像素单元,各所述像素单元包括驱动薄膜晶体管、开关薄膜晶体管、重置薄膜晶体管和有机发光器件;

[0008] 在沿垂直于所述衬底基板所在平面的方向,所述开关薄膜晶体管的源极和漏极分别位于该开关薄膜晶体管的栅极的两侧,所述重置薄膜晶体管的源极和漏极分别位于该重置薄膜晶体管的栅极的两侧;所述开关薄膜晶体管的漏极与所述驱动薄膜晶体管的栅极电连接,所述重置薄膜晶体管的漏极与所述驱动薄膜晶体管的漏极电连接,所述驱动薄膜晶体管的漏极与所述有机发光器件耦接。

[0009] 第二方面,本申请提供了一种显示装置,包括显示面板,该显示面板为本申请实所提供的任意显示面板。

[0010] 与现有技术相比,本发明提供的显示面板及显示装置,至少实现了如下的有益效果:

[0011] 本申请所提供的显示面板及显示装置,在每个像素单元中设置有驱动薄膜晶体管、开关薄膜晶体管和重置薄膜晶体管,由于开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极电连接,重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极电连接,本申请将开关薄膜晶体管的源极和漏极分别位于其栅极的两侧,并将重置薄膜晶体管的源极和漏极也分别位于其栅极的两侧时,开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极之间无需通过跨桥进

行连接，重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极之间也无需通过跨桥进行连接，如此有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积，节约的空间使显示面板能够设置更多的像素单元，因而有利于实现显示面板及显示装置的高PPI设计，进而有利于提升显示面板及显示装置的分辨率，使显示图像更加精细、清晰。

[0012] 当然，实施本发明的任一产品必不特定需要同时达到以上所述的所有技术效果。

[0013] 通过以下参照附图对本发明的示例性实施例的详细描述，本发明的其它特征及其优点将会变得清楚。

## 附图说明

[0014] 被结合在说明书中并构成说明书的一部分的附图示出了本发明的实施例，并且连同其说明一起用于解释本发明的原理。

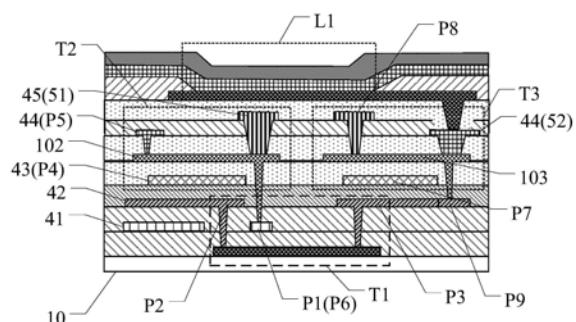

[0015] 图1所示为本申请实施例所提供的显示面板的一种俯视图；

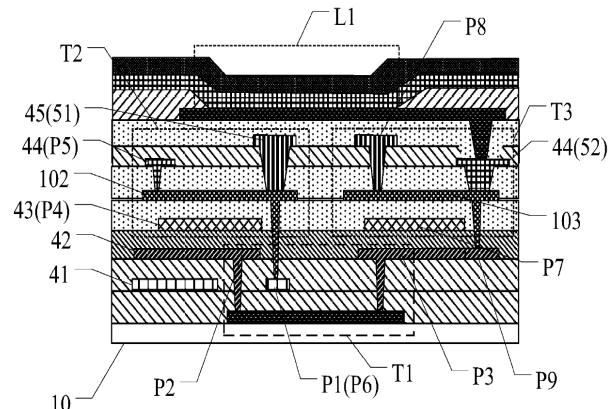

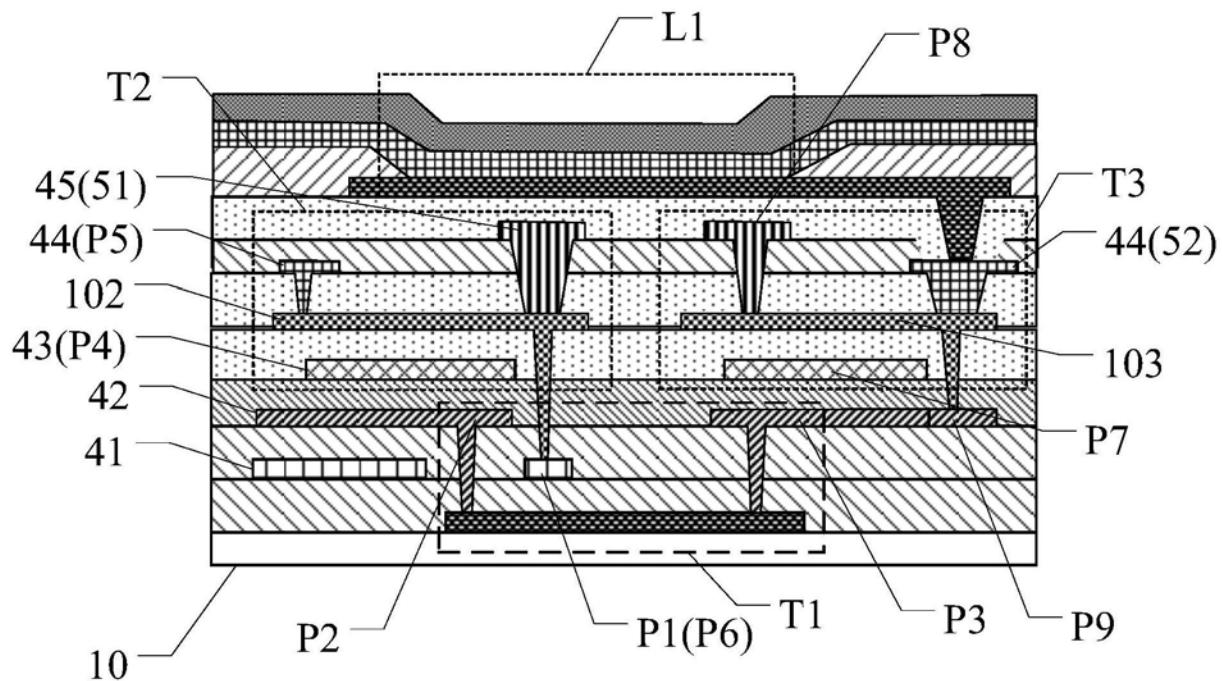

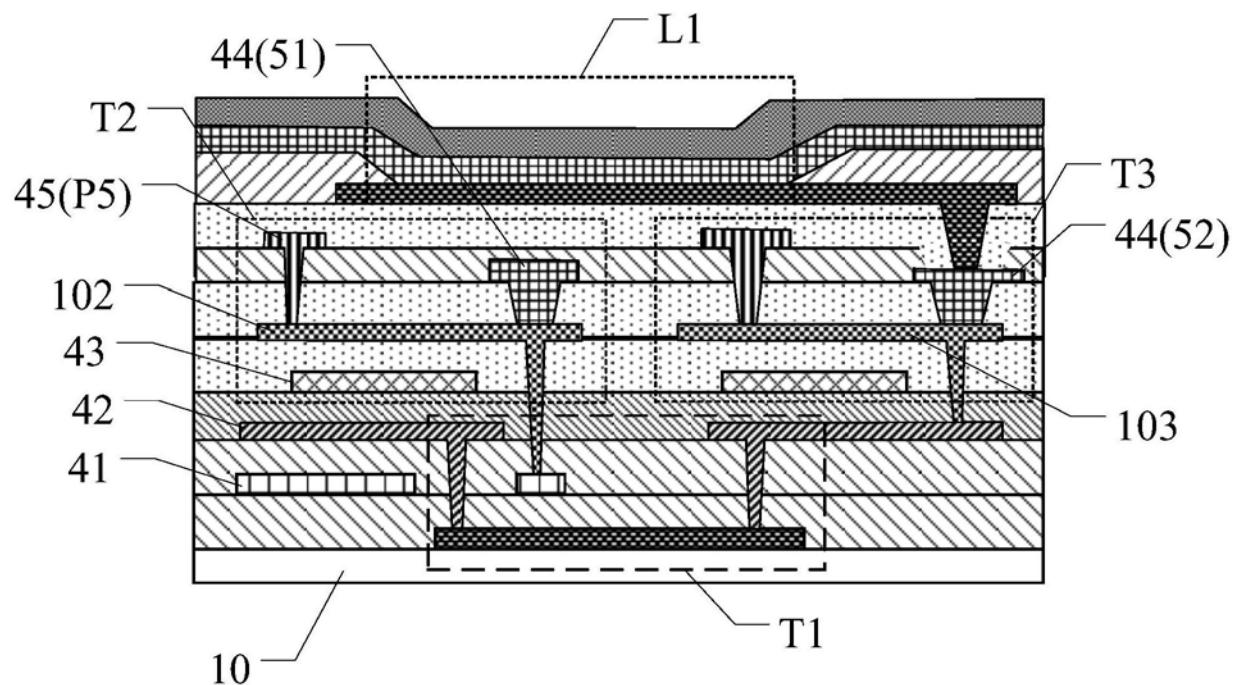

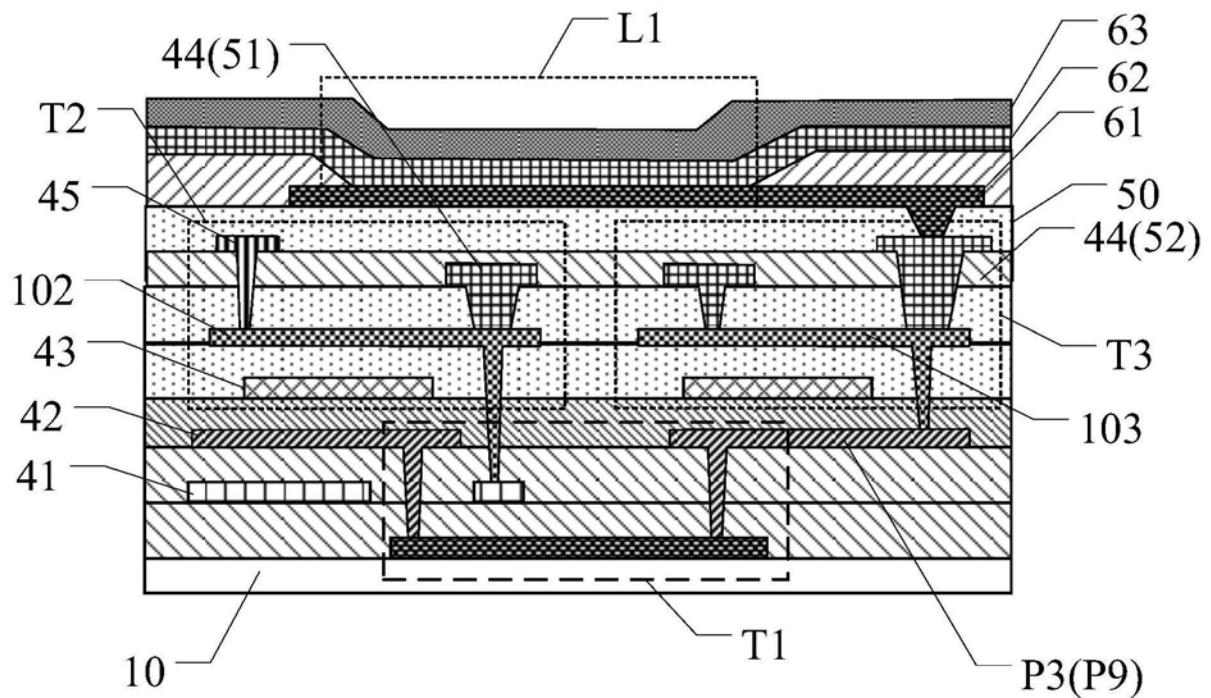

[0016] 图2所示为图1实施例所提供的显示面板的一种AA' 截面图；

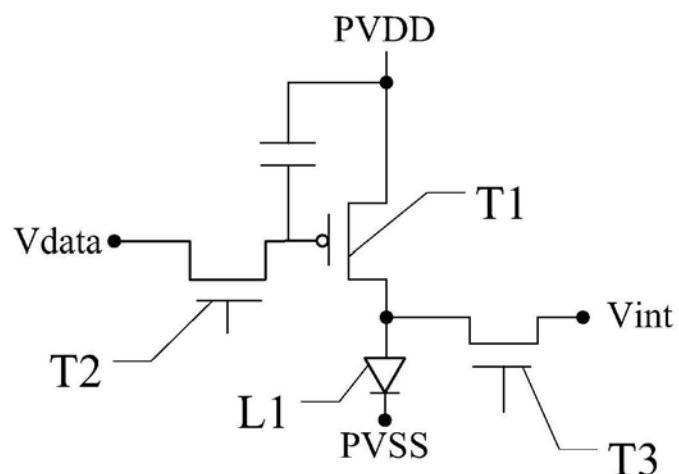

[0017] 图3所示为本申请实施例所提供显示面板中像素单元内的一种电路示意图；

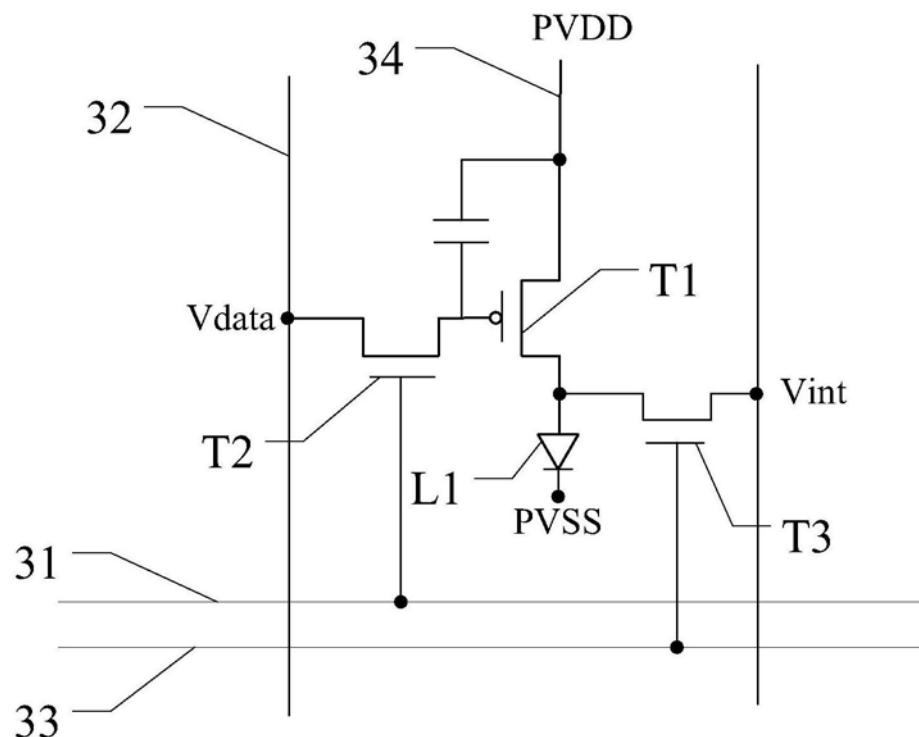

[0018] 图4所示为本申请实施例所提供的显示面板中1个像素单元的一种电路结构图；

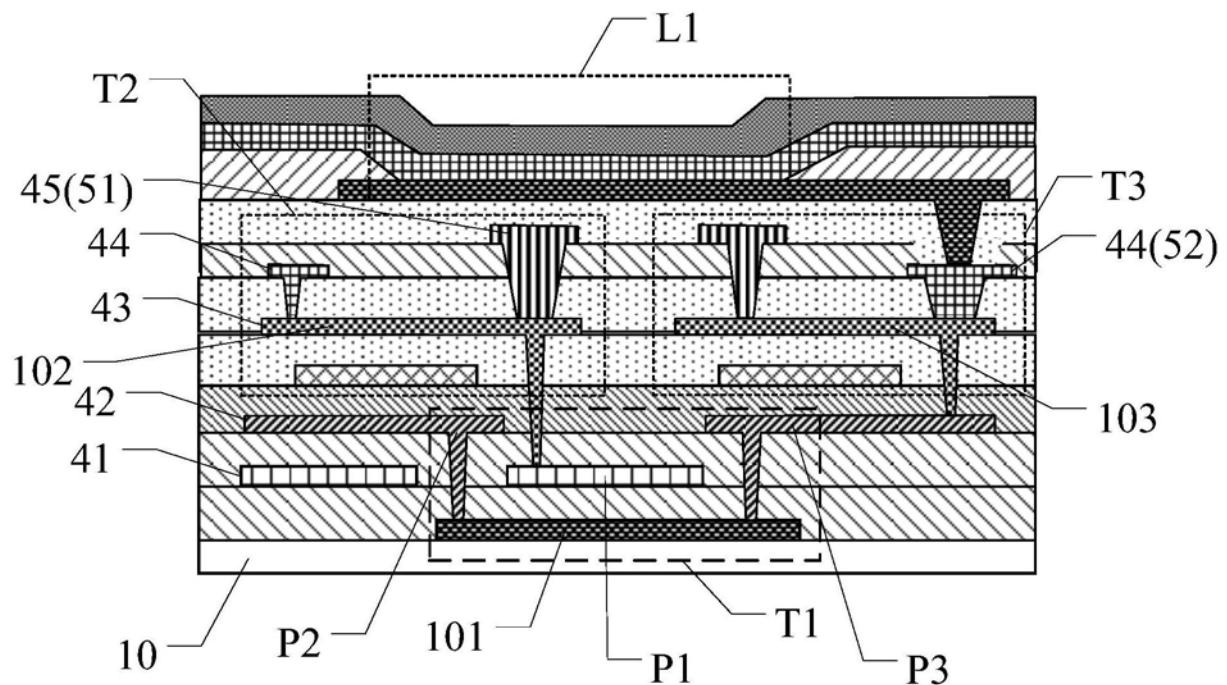

[0019] 图5所示为图1实施例所提供的显示面板的另一种AA' 截面图；

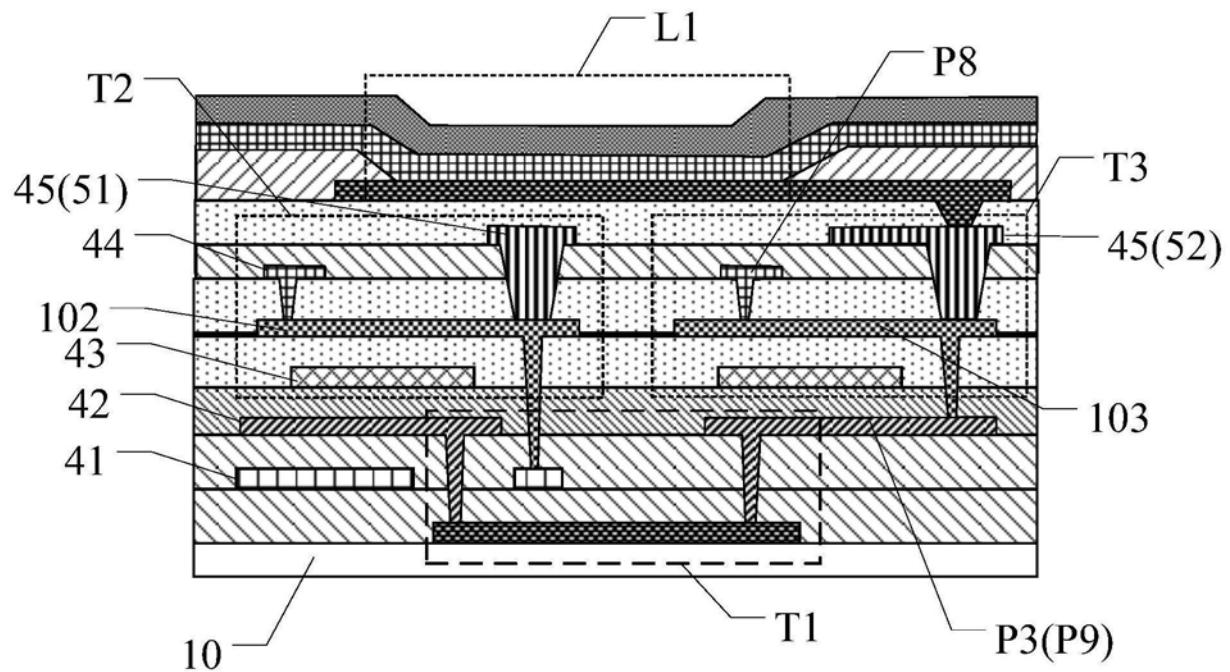

[0020] 图6所示为图1实施例所提供的显示面板的另一种AA' 截面图；

[0021] 图7所示为图1实施例所提供的显示面板的另一种AA' 截面图；

[0022] 图8所示为图1实施例所提供的显示面板的另一种AA' 截面图；

[0023] 图9所示为本申请实施例所提供的显示面板中部分像素单元的一种排布示意图；

[0024] 图10所示为与图9中的像素单元对应的一种电路结构图；

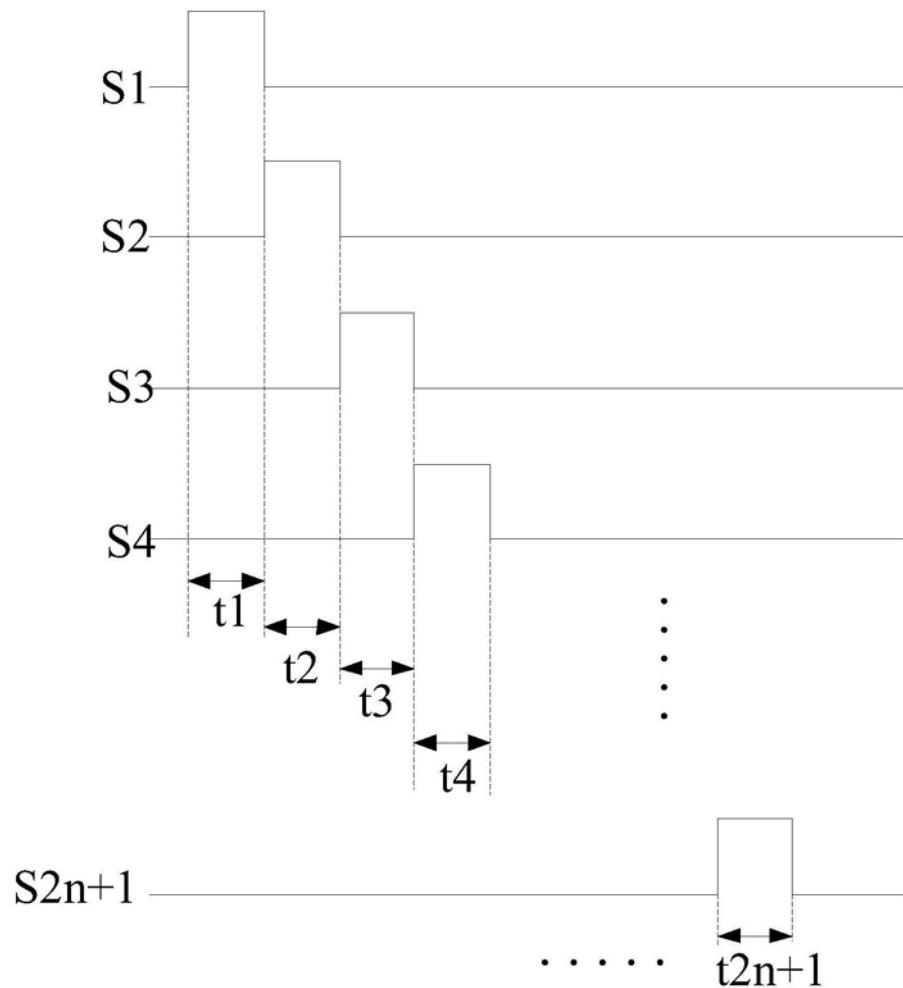

[0025] 图11所示为本申请实施例所提供的显示面板的一种工作时序图；

[0026] 图12所示为本申请实施例所提供的显示装置的一种俯视图。

## 具体实施方式

[0027] 现在将参照附图来详细描述本发明的各种示例性实施例。应注意到：除非另外具体说明，否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本发明的范围。

[0028] 以下对至少一个示例性实施例的描述实际上仅仅是说明性的，决不作为对本发明及其应用或使用的任何限制。

[0029] 对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论，但在适当情况下，所述技术、方法和设备应当被视为说明书的一部分。

[0030] 在这里示出和讨论的所有例子中，任何具体值应被解释为仅仅是示例性的，而不是作为限制。因此，示例性实施例的其它例子可以具有不同的值。

[0031] 应注意到：相似的标号和字母在下面的附图中表示类似项，因此，一旦某一项在一个附图中被定义，则在随后的附图中不需要对其进行进一步讨论。

[0032] 显示面板的PPI是图像分辨率的单位，表示的是显示面板的每英寸所拥有的像素(Pixel)数目，当显示面板的PPI达到一定数值时，人眼就分辨不出颗粒感了。现有技术中，为配合像素正常发光，会在显示面板上引入一系列的电路结构，电路结构所占用的空间对

PPI有直接的影响,因此,如何实现显示面板的高PPI设计成为现阶段亟待解决的技术问题之一。

[0033] 有鉴于此,本发明提供了一种显示面板及显示装置,将开关薄膜晶体管和重置薄膜晶体管的源漏极设置在栅极的两侧,有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积,节约的空间使显示面板能够设置更多的像素单元,因而有利于实现显示面板及显示装置的高PPI设计。

[0034] 本申请提供一种显示面板,包括:

[0035] 衬底基板,

[0036] 设置在衬底基板上的多个像素单元,各像素单元包括驱动薄膜晶体管、开关薄膜晶体管、重置薄膜晶体管和有机发光器件;

[0037] 在沿垂直于衬底基板所在平面的方向,开关薄膜晶体管的源极和漏极分别位于该开关薄膜晶体管的栅极的两侧,重置薄膜晶体管的源极和漏极分别位于该重置薄膜晶体管的栅极的两侧;开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极电连接,重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极电连接,驱动薄膜晶体管的漏极与有机发光器件耦接。

[0038] 以下将结合附图和具体实施例进行详细说明。

[0039] 图1所示为本申请实施例所提供的显示面板的一种俯视图,图2所示为图1实施例所提供的显示面板的一种AA'截面图,图3所示为本申请实施例所提供显示面板中像素单元内的一种电路示意图,请结合图1-图3,本申请实施例所提供的显示面板100中,设置有多个像素单元20,各像素单元20包括驱动薄膜晶体管T1、开关薄膜晶体管T2、重置薄膜晶体管T3和有机发光器件L1,对于单个像素单元20而言,在工作时,请参见图3,首先将重置薄膜晶体管T3开启、开关薄膜晶体管T2和驱动薄膜晶体管T1关闭,使得有机发光器件L1上阳极的信号复位;其次,将重置薄膜晶体管T3关闭,开关薄膜晶体管T2开启,数据信号Vdata通过开关薄膜晶体管T2传输至驱动薄膜晶体管T1的栅极,使驱动薄膜晶体管T1开启,驱动像素单元20中的有机发光器件L1发光。特别是,请参见图2和图3,由于开关薄膜晶体管T2的漏极P6与驱动薄膜晶体管T1的栅极P1电连接,重置薄膜晶体管T3的漏极P9与驱动薄膜晶体管T1的漏极P3电连接,本申请将开关薄膜晶体管T2的源极P5和漏极P6分别位于其栅极P4的两侧,并将重置薄膜晶体管T3的源极P8和漏极P9也分别位于其栅极P7的两侧时,开关薄膜晶体管T2的漏极P6与驱动薄膜晶体管T1的栅极P1之间无需通过跨桥进行连接,二者之间通过过孔即可实现电连接;需要说明的是,本申请实施例所提及的栅极P4的两侧或栅极P7的两侧,为膜层堆叠方向上的两侧。同时,重置薄膜晶体管T3的漏极P9与驱动薄膜晶体管T1的漏极P3之间也无需通过跨桥进行连接,二者之间通过过孔即可实现电连接;如此有利于减小开关薄膜晶体管T2和重置薄膜晶体管T3在显示面板100上所占用的面积,在显示面板100上可节约出一定的空间,节约的空间使显示面板100能够设置更多的像素单元20,因而有利于实现显示面板100的高PPI设计,进而有利于提升显示面板100的分辨率,使显示图像更加精细、清晰,有利于提升显示面板100的图像显示质量。

[0040] 需要说明的是,图1所示的显示面板100中,栅极线31和数据线32交叉限定多个像素单元20,图1仅为示意性说明,并不代表栅极线31、数据线32和像素单元20的实际尺寸和数量。图2中的截面图也仅为示意性说明,仅说明各膜层之间的相对位置关系,并不代表实际的尺寸及结构。

[0041] 可选地，本申请实施例所提供的显示面板100中，开关薄膜晶体管T2和重置薄膜晶体管T3为氧化物薄膜晶体管，驱动薄膜晶体管T1为低温多晶硅薄膜晶体管。

[0042] 具体地，采用氧化物薄膜晶体管作为开关薄膜晶体管T2和重置薄膜晶体管T3时，使开关薄膜晶体管T2和重置薄膜晶体管T3具有较低的电子迁移率，漏电较小，有利于提升显示面板100的分辨率，使显示面板100的图像更逼真，刷新频率更高，同时还能使光透过率得到提升，能耗进一步降低。采用低温多晶硅薄膜晶体管作为驱动薄膜晶体管T1时，使得驱动薄膜晶体管T1具有较高的电子迁移率，响应速度快，易高度集成化，省电且抗光干扰能力强。本申请将开关薄膜晶体管T2和重置薄膜晶体管T3设置为氧化物薄膜晶体管的同时，还将开关薄膜晶体管T2和重置薄膜晶体管T3的源漏极分别置于栅极的两侧，从而更加有利于提升显示面板100的分辨率，进而提升显示面板100的画面显示效果。

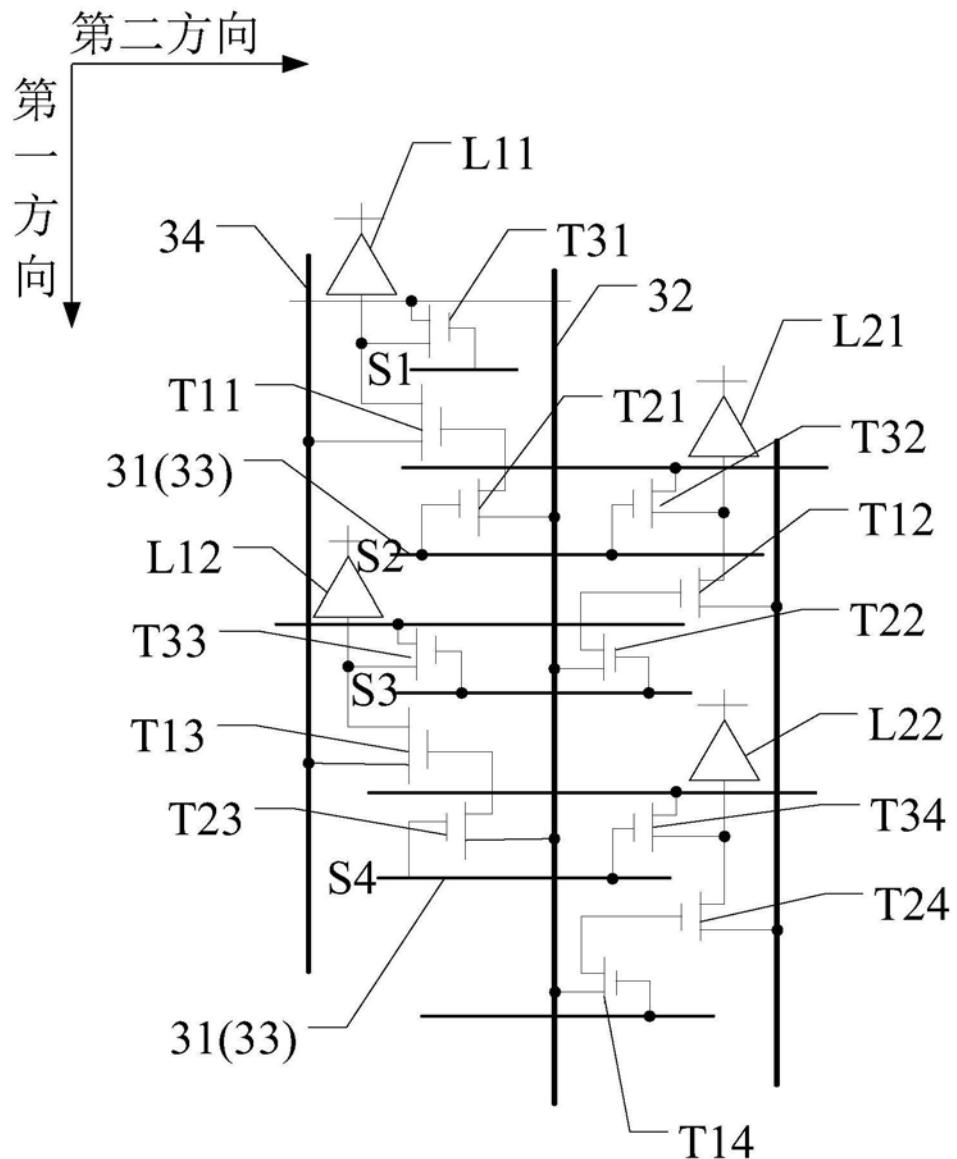

[0043] 可选地，请参见图4，图4所示为本申请实施例所提供的显示面板100中1个像素单元20的一种电路结构图，显示面板100还包括相互绝缘的多条栅极线31、多条数据线32、多条重置信号线33和多条电源信号线34。

[0044] 各开关薄膜晶体管T2的栅极连接栅极线31，各开关薄膜晶体管T2的源极连接数据线32；各驱动薄膜晶体管T1的源极连接电源信号线34；各重置薄膜晶体管T3的栅极连接重置信号线33，各重置薄膜晶体管T3的源极连接重置电压信号。

[0045] 具体地，本申请实施例所提供的显示面板100中，开关薄膜晶体管T2的栅极连接栅极线31，接收通过栅极线31传输的栅极控制信号，并在栅极控制信号的控制下开启或关闭；开关薄膜晶体管T2的源极连接数据线32，漏极连接驱动薄膜晶体管T1的栅极，当开关薄膜晶体管T2开启时，数据线32中的数据信号将通过开关薄膜晶体管T2传输至驱动薄膜晶体管T1，驱动薄膜晶体管T1开启，电源信号线34中的电源信号将传输至有机发光器件L1，使有机发光器件L1得以发光。重置薄膜晶体管T3的源极连接重置电压信号，在对某一子像素单元20进行扫描之前，首先将重置薄膜晶体管T3开启，然后将重置电压信号发送至有机发光器件L1，以使得有机发光器件L1重置至初始状态，避免上一帧的显示数据对当前帧的显示造成影响。

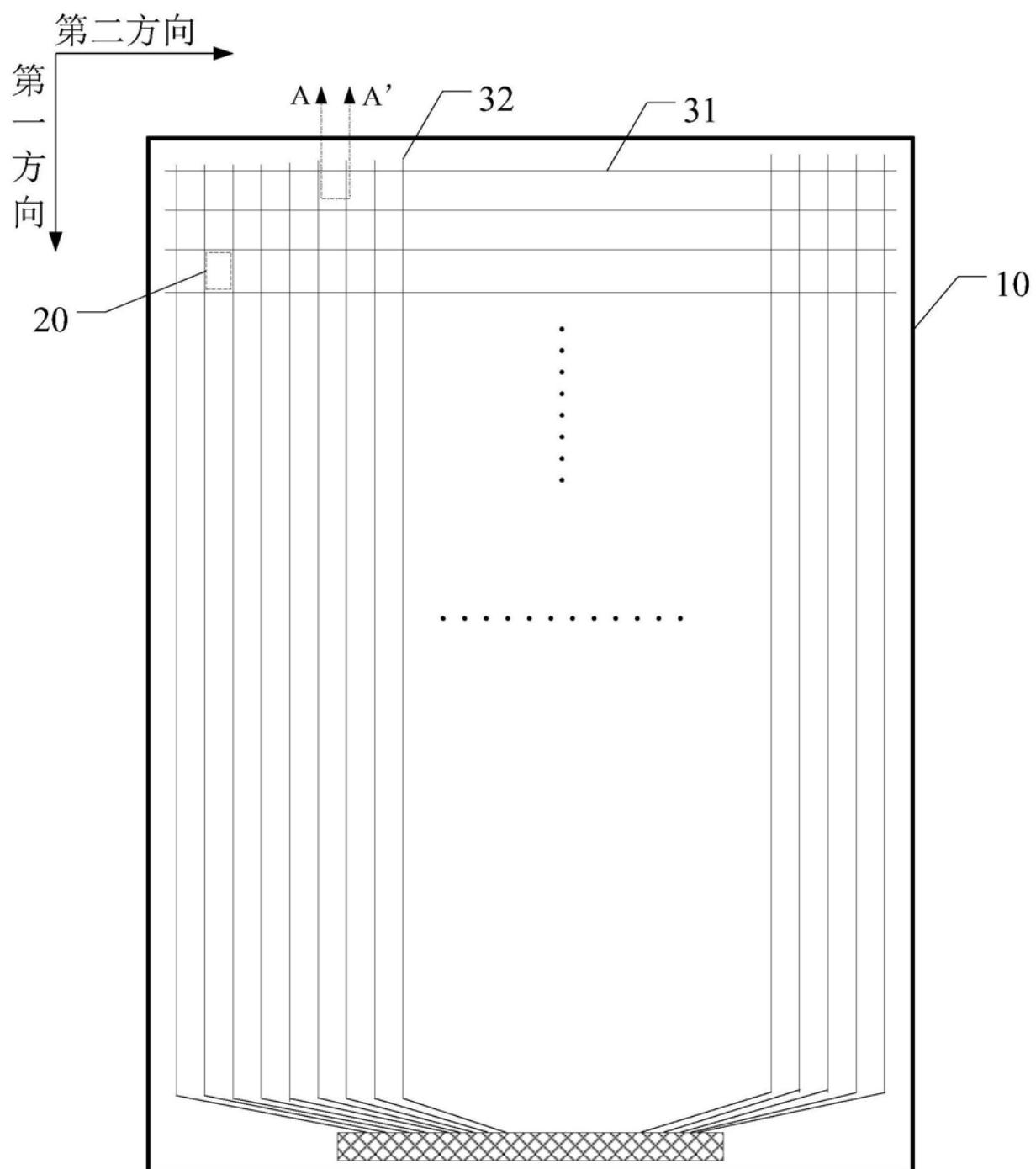

[0046] 可选地，请继续参见图2，本申请实施例所提供的显示面板100中，还包括沿垂直于衬底基板的方向依次设置于衬底基板上的低温多晶硅沟道层、第一金属层41、第二金属层42、第三金属层43、氧化物沟道层102/103、第四金属层44和第五金属层45。

[0047] 驱动薄膜晶体管T1的栅极P1位于第一金属层41，源极P2和漏极P3位于第二金属层42；开关薄膜晶体管T2的栅极P4和重置薄膜晶体管T3的栅极P7位于第三金属层43，开关薄膜晶体管T2的源极P5位于第四金属层44，重置薄膜晶体管T3的源极P8位于第五金属层45；开关薄膜晶体管T2的漏极P6位于氧化物沟道层102与衬底基板10之间，重置薄膜晶体管T3的漏极P9位于氧化物沟道层103与第一金属层41之间。

[0048] 具体地，本申请实施例所提供的显示面板100中，当在像素单元20中同时引入驱动薄膜晶体管T1、开关薄膜晶体管T2和重置薄膜晶体管T3时，三种晶体管的膜层的一种膜层排布关系可参见图2，将驱动薄膜晶体管T1设置在最靠近衬底基板的一侧，即低温多晶硅沟道层，其栅极P1位于第一金属层41，源极P2和漏极P3位于第二金属层42；开关薄膜晶体管T2和重置薄膜晶体管T3分别位于驱动薄膜晶体管T1远离衬底基板的一侧，其中，开关薄膜晶体管T2的栅极P4和重置薄膜晶体管T3的栅极P7位于第三金属层43，开关薄膜晶体管T2的源

极P5位于第四金属层44，漏极P6位于氧化物沟道层102与衬底基板10之间；重置薄膜晶体管T3的源极P8位于第五金属层45，漏极P9位于氧化物沟道层103与第一金属层41之间。如此，将开关薄膜晶体管T2和重置薄膜晶体管T3的源极设置在氧化物沟道层102/103远离衬底基板的一侧，将漏极设置在氧化物沟道层102/103靠近衬底基板的一侧，避免了开关薄膜晶体管T2和重置薄膜晶体管T3在分别与驱动薄膜晶体管T1形成电连接时形成跨桥的结构，因而有利于减小开关薄膜晶体管T2和重置薄膜晶体管T3在显示面板100上所占用的面积，进而有利于实现显示面板100的高PPI设计。

[0049] 需要说明的是，图2所示实施例中，各个金属层之间是通过绝缘层来实现隔离的。另外，图2仅示出了将驱动薄膜晶体管T1、开关薄膜晶体管T2和重置薄膜晶体管T3集成的一种膜层堆叠图，在本申请的一些其他实施例中，三者还可采用其他的膜层堆叠结构，本申请对此不进行具体限定。

[0050] 可选地，请参见图2，本申请实施例所提供的显示面板100还包括第一金属线51，第一金属线51位于开关薄膜晶体管T2的氧化物沟道层102远离衬底基板10的一侧。

[0051] 第一金属线51通过第一过孔与开关薄膜晶体管T2的氧化物沟道层102电连接，第一金属线51与开关薄膜晶体管T2的栅极P4和漏极P6在衬底基板10所在平面的正投影交叠，开关薄膜晶体管T2的源极P5和栅极P4在衬底基板所在平面的正投影交叠。

[0052] 具体地，请继续参见图2，在开关薄膜晶体管T2的氧化物沟道层102远离衬底基板10的一侧引入了第一金属线51，该第一金属线51在衬底基板的正投影与开关薄膜晶体管T2的栅极P4和漏极P6交叠，并且通过过孔与开关薄膜晶体管T2的氧化物沟道层102电连接。本申请在引入第一金属线51后，使得开关薄膜晶体管T2源极P5的电压能够经过氧化物沟道层102传输至第一金属线51，进而从第一金属线51传输至开关薄膜晶体管T2的漏极P6，从而有利于提升开关薄膜晶体管T2的电子迁移率，进而有利于提升开关薄膜晶体管T2的响应速率。

[0053] 可选地，请继续参见图2，本申请实施例所提供的显示面板100中，第一金属线51在衬底基板10所在平面的正投影覆盖开关薄膜晶体管T2的漏极P6。通常，引入第一金属线51后，第一金属线51对开关薄膜晶体管T2的电子迁移率的提升情况与第一金属线51与开关薄膜晶体管T2的栅极P4和漏极P6的交叠面积有关，交叠面积越大，提升效果越明显，本申请利用第一金属线51将开关薄膜晶体管T2的漏极P6进行覆盖后，增加了第一金属线51与开关薄膜晶体管T2的漏极P6的交叠面积，因而更加有利于提升开关薄膜晶体管T2的电子迁移率，进而有利于提升开关薄膜晶体管T2的响应速率。

[0054] 可选地，请继续参见图2，第一金属线51与开关薄膜晶体管T2的源极P5位于不同膜层。

[0055] 具体地，考虑到膜层工艺问题，显示面板100上相邻金属线之间的线距优选大于 $3\mu m$ ，因此，为保证工艺可行性，图2所示实施例中，将第一金属线51与开关薄膜晶体管T2的源极P5设置在不同的膜层时，能够有效避免第一金属线51与开关薄膜晶体管T2的源极P5之间发生短路的现象，同时此种设计也有利于减小开关薄膜晶体管T2在显示面板100上所占的面积，因而同样有利于实现显示面板100的高PPI设计。

[0056] 可选地，第一金属线51位于第五金属层45。需要说明的是，图2仅示出了开关薄膜晶体管T2的源极位于第四金属层44、第一金属线51位于第五金属层45的情形，在本申请的

一些其他实施例中,例如,请参见图5,图5所示为图1实施例所提供的显示面板100的另一种AA'截面图,该实施例中,开关薄膜晶体管T2的源极P5位于第五金属层45,第一金属线51位于第四金属层44,此种结构同样有利于减小开关薄膜晶体管T2在显示面板100上所占的面积,同样有利于实现显示面板100的高PPI设计。

[0057] 可选地,请参见图2,本申请实施例所提供的显示面板100中,驱动薄膜晶体管T1的栅极P1复用为开关薄膜晶体管T2的漏极P6。

[0058] 具体地,由于开关薄膜晶体管T2的漏极P6是与驱动薄膜晶体管T1的栅极P1电连接的,本申请将驱动薄膜晶体管T1的栅极P1直接复用为开关薄膜晶体管T2的漏极P6时,使得该漏极P6通过过孔与开关薄膜晶体管T2的氧化物沟道层102电连接,避免了单独为开关薄膜晶体管T2的漏极P6设置膜层结构的步骤,既有利于节约生产工序、提升生产效率,又有利于简化显示面板100的膜层结构。

[0059] 可选地,请继续参见图2,本申请实施例所提供的显示面板100中还包括第二金属线52,第二金属线52位于重置薄膜晶体管T3的氧化物沟道层103远离衬底基板10的一侧;

[0060] 第二金属线52通过第二过孔与重置薄膜晶体管T3的氧化物沟道层103电连接,第二金属线52与重置薄膜晶体管T3的栅极P7和漏极P9在衬底基板10所在平面的正投影交叠,重置薄膜晶体管T3的源极P8和栅极P7在衬底基板10所在平面的正投影交叠。

[0061] 具体地,请继续参见图2,在重置薄膜晶体管T3的氧化物沟道层103远离衬底基板10的一侧引入了第二金属线52,该第二金属线52在衬底基板的正投影与重置薄膜晶体管T3的栅极P7和漏极P9交叠,并且通过过孔与重置薄膜晶体管T3的氧化物沟道层103电连接。本申请在引入第二金属线52后,使得重置薄膜晶体管T3源极P8的电压能够经过氧化物沟道层103传输至第二金属线52,进而从第二金属线52传输至重置薄膜晶体管T3的漏极P9,从而有利于提升重置薄膜晶体管T3的电子迁移率,进而有利于提升重置薄膜晶体管T3的响应速率。

[0062] 可选地,请继续参见图2,第二金属线52在衬底基板10所在平面的正投影覆盖重置薄膜晶体管T3的漏极P9。通常,引入第二金属线52后,第二金属线52对重置薄膜晶体管T3的电子迁移率的提升情况与第二金属线52与重置薄膜晶体管T3的栅极P7和漏极P9的交叠面积有关,交叠面积越大,提升效果越明显,本申请利用第二金属线52将重置薄膜晶体管T3的漏极P9进行覆盖后,增加了第二金属线52与重置薄膜晶体管T3的漏极P9的交叠面积,因而更加有利于提升重置薄膜晶体管T3的电子迁移率,进而有利于提升重置薄膜晶体管T3的响应速率。

[0063] 可选地,第二金属线52与重置薄膜晶体管T3的源极P8位于不同膜层。

[0064] 具体地,考虑到膜层工艺问题,显示面板100上相邻金属线之间的线距优选大于 $3\mu m$ ,因此,为保证工艺可行性,图2所示实施例中,将第二金属线52与重置薄膜晶体管T3的源极P8设置在不同的膜层时,能够有效避免第二金属线52与重置薄膜晶体管T3的源极P8之间发生短路的现象,同时此种设计也有利于减小重置薄膜晶体管T3在显示面板100上所占的面积,因而同样有利于实现显示面板100的高PPI设计。

[0065] 可选地,第二金属线52位于第四金属层44。需要说明的是,图2仅示出了重置薄膜晶体管T3的源极P8位于第五金属层45,第二金属线52位于第四金属层44的情形,在本申请的一些其他实施例中,例如,请参见图6,图6所示为图1实施例所提供的显示面板100的另一

种AA' 截面图,该实施例中,重置薄膜晶体管T3的源极P8位于第四金属层44,第二金属线52位于第五金属层45,此种结构同样有利于减小开关薄膜晶体管T2在显示面板100上所占的面积,同样有利于实现显示面板100的高PPI设计。

[0066] 可选地,请参见图6,驱动薄膜晶体管T1的漏极复用为重置薄膜晶体管T3的漏极。

[0067] 具体地,由于重置薄膜晶体管T3的漏极P9与驱动薄膜晶体管T1的漏极P3是电连接的,本申请将驱动薄膜晶体管T1的漏极P3复用为重置薄膜晶体管T3的漏极P9时,使得该漏极P9通过过孔与重置薄膜晶体管T3的氧化物沟道层103电连接,避免了单独为重置薄膜晶体管T3的漏极P9设置膜层结构的步骤,既有利于节约生产工序、提升生产效率,又有利于简化显示面板100的膜层结构。

[0068] 可选地,图7所示为图1实施例所提供的显示面板100的另一种AA' 截面图,请参见图7,有机发光器件L1位于第四金属层44远离衬底基板的一侧,有机发光器件L1包括依次设置的阳极61、发光层62和阴极63,阳极61与驱动薄膜晶体管T1的漏极耦接。

[0069] 具体地,请参见图7,图7示出了驱动薄膜晶体管T1、开关薄膜晶体管T2和重置薄膜晶体管T3与有机发光器件L1的电连接关系,在第四金属层44和第五金属层45远离衬底基板的一侧,可通过绝缘层形成平坦化膜层50,然后再在平坦化膜层50上形成有机发光器件L1,包括从靠近衬底基板的一侧到远离衬底基板的一侧依次设置的阳极61、发光层62和阴极63,其中,阳极61通过过孔与驱动薄膜晶体管T1的漏极P2耦接,即,阳极61通过过孔首先与第二金属线52电连接,由于氧化物沟道层103的厚度很薄,使得第二金属线52与重置薄膜晶体管T3的漏极P9实现了电连接,由于驱动薄膜晶体管T1的漏极P3复用为重置薄膜晶体管T3的漏极P9,进而使得有机发光器件L1的阳极61与驱动薄膜晶体管T1的漏极P3实现了电连接,在驱动薄膜晶体管T1、开关薄膜晶体管T2和重置薄膜晶体管T3的共同作用下,使得有机发光器件L1得以正常发光。

[0070] 可选地,图8所示为图1实施例所提供的显示面板100的另一种AA' 截面图,请参见图8,本申请实施例所提供的显示面板100中还包括多晶硅层101,多晶硅层101位于第一金属层41朝向衬底基板10的一侧,驱动薄膜晶体管T1的栅极P1、源极P2和漏极P3在衬底基板所在平面的正投影覆盖多晶硅层101。

[0071] 具体地,请继续参见图8,本申请实施例所提供的显示面板100中,驱动薄膜晶体管T1体现为顶栅结构,即驱动薄膜晶体管T1的栅极P1位于多晶硅层101远离衬底基板10的一侧,且在垂直于衬底基板的方向,驱动薄膜晶体管T1中的多晶硅层101由驱动薄膜晶体管T1的栅极P1、源极P2和漏极P3覆盖,由于多晶硅层101在受到光照时会产生电流,影响驱动薄膜晶体管T1正常发挥驱动功能,因此利用其栅极P1、源极P2和漏极P3将多晶硅层101进行覆盖时,可大大减小反射至多晶硅层101的光线的量,因而有利于减小多晶硅层101由于光照而产生的电流的量,有利于提升驱动薄膜晶体管T1工作的可靠性。

[0072] 可选地,本申请实施例所提供的显示面板100中,开关薄膜晶体管T2的氧化物沟道层102和重置薄膜晶体管T3的氧化物沟道层103的厚度为D1,20nm≤D1≤80nm。

[0073] 具体地,请参见图2,本申请在显示面板100中引入了第一金属线51和第二金属线52,第一金属线51通过开关薄膜晶体管T2的氧化物沟道层102与开关薄膜晶体管T2的漏极电连接,第二金属线52通过重置薄膜晶体管T3的氧化物沟道层103与重置薄膜晶体管T3的漏极电连接,当将氧化物沟道层102/103的厚度设置的小于20nm时,其厚度太薄,很容易发

生断裂风险,不利于成膜;当将氧化物沟道层102/103的度设置的大于80nm时,会削弱第一金属线51与开关薄膜晶体管T2的漏极之间的电连接关系,同时还会削弱第二金属线52与重置薄膜晶体管T3之间的电连接关系。因此,本申请将氧化物沟道层102/103的厚度设置为 $20\text{nm} \leq D1 \leq 80\text{nm}$ 时,使得开关薄膜晶体管T2和重置薄膜晶体管T3的性能较佳,成膜工艺更为成熟。

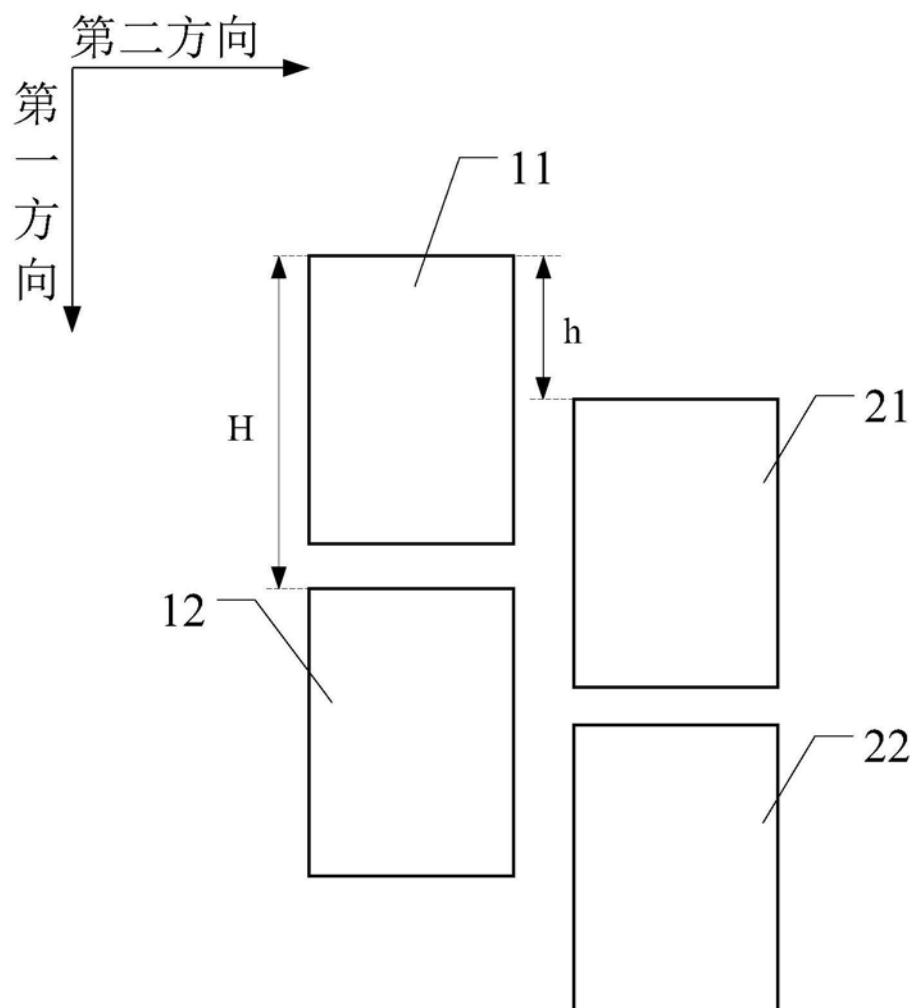

[0074] 可选地,图9所示为本申请实施例所提供的显示面板100中部分像素单元20的一种排布示意图,图10所示为与图9中的像素单元20对应的一种电路结构图,请结合图9和图10,像素单元20形成多个沿第一方向延伸的像素单元列,像素单元20列包括奇数列和偶数列,奇数列和偶数列沿第二方向交替排布,第一方向和第二方向交叉;

[0075] 沿第一方向,奇数列和偶数列错位排布,错位距离小于第一方向上两个相邻子像素单元之间的距离。例如,请参见图9,沿第一方向,相邻的两个像素单元之间的距离为H,奇数列和偶数列的错位距离为h,其中, $0 < h < H$ 。

[0076] 可选地,至少部分相邻的奇数列和偶数列中,各开关薄膜晶体管T2连接同一数据线32,数据线32向奇数列和偶数列的像素单元20提供数据信号。

[0077] 具体地,请继续参见图9和图10,本申请将像素单元20构成的奇数列和偶数列错位排布时,可以使得相邻的奇数列和偶数列共用同一数据线32,以图10为例,奇数列中,像素单元11和12中的开关薄膜晶体管T21和T22,以及偶数列中,像素单元21和22中的开关薄膜晶体管T23和T24,同时与同一条数据线32电连接,数据线32可分时向不同的像素单元提供数据信号,以实现不同像素单元的正常显示功能。奇数列和偶数列的像素单元共用数据线32的方式,有利于简化显示面板100上的布线复杂度,提升显示面板100的空间利用率。

[0078] 可选地,请继续参见图9和图10,至少部分位于奇数列的子像素对应的重置信号线33复用为位于偶数列的子像素对应的栅极线31,至少部分位于奇数列的子像素对应的栅极线31复用为位于偶数列的子像素对应的重置信号线33。

[0079] 具体地,请结合图9和图10,像素单元11中的开关薄膜晶体管T21的栅极与栅极线31电连接,该栅极线31同时作为像素单元21中与重置薄膜晶体管T32电连接的重置信号线33;像素单元12中的开关薄膜晶体管T23的栅极与栅极线31电连接,该栅极线31同时作为像素单元22中与重置薄膜晶体管T34电连接的重置信号线33。如此,将栅极线31与重置信号线33复用,同样有利于简化显示面板100上的布线复杂度,提升显示面板100的空间利用率。

[0080] 以下将结合图9、图10和图11对各像素单元20的工作时序进行说明,其中图11所示为本申请实施例所提供的显示面板100的一种工作时序图,其中,S1为输入像素单元11的阳极重置信号,S2为输入至像素单元11中开关薄膜晶体管T21的栅极信号以及输入至像素单元21中的阳极重置信号,S3为输入至像素单元21中开关薄膜晶体管T22的栅极信号以及输入至像素单元12中的阳极重置信号,S4为输入至像素单元12中开关薄膜晶体管T23的栅极信号以及输入至像素单元22中的阳极重置信号。

[0081] 在t1时间段,奇数列像素单元11中的重置薄膜晶体管T31开启,对像素单元11中有机发光器件L11的阳极61电压进行重置;

[0082] 在t2时间段,奇数列像素单元11中的开关薄膜晶体管T21开启,数据信号(Data信号)通过开关薄膜晶体管T21输入至驱动薄膜晶体管T11的栅极,使得驱动薄膜晶体管T11开启,进而控制像素单元11中的有机发光器件L11发光;同时,由于像素单元11中的栅极线31

复用为像素单元21中的重置信号线34,偶数列像素单元21中的重置薄膜晶体管T32开启,像素单元21中有机发光器件L21的阳极电压进行重置;

[0083] 在t3时间段,像素单元21中的开关薄膜晶体管T22开启,数据信号通过开关薄膜晶体管T22输入至驱动薄膜晶体管T12的栅极,使得驱动薄膜晶体管T12开启,进而控制像素单元21中的有机发光器件L21发光;同时,由于像素单元21中的栅极线31复用为像素单元12中的重置信号线33,奇数列像素单元12中的重置薄膜晶体管T33开启,像素单元12中的有机发光器件L12的阳极电压进行重置;

[0084] 在t4时间段,像素单元12中的开关薄膜晶体管T23开启,数据信号通过开关薄膜晶体管T23输入至驱动薄膜晶体管T13的栅极,使得驱动薄膜晶体管T13开启,进而控制像素单元12中的有机发光器件L12发光;同时,由于像素单元12中的栅极线31复用为像素单元22中的重置信号线33,偶数列像素单元22中的重置薄膜晶体管T34开启,像素单元22中的有机发光器件L22的阳极电压进行重置。

[0085] 由于最终需要有一条单独的栅极线来控制最后一个发光的像素单元进行发光,因此,时序图中引入了S2n+1,作为输入至最后一个像素单元中开关薄膜晶体管的栅极信号。

[0086] 如此循环,实现显示面板100的正常显示。

[0087] 可选地,本申请实施例所提供的显示面板100中,驱动薄膜晶体管T1为PMOS管或NMOS管,本申请对此不进行具体限定。

[0088] 需要说明的是,对于开关薄膜晶体管、驱动薄膜晶体管和重置薄膜晶体管,本申请实施例所提及的源极指的是信号输入的一极,漏极指的是信号输出的一极。

[0089] 基于同一发明构思,本申请还提供一种显示装置,图12所示为本申请实施例所提供的显示装置200的一种俯视图,该显示装置200包括显示面板100,该显示面板100为本申请实施例所提供的任一显示面板。本申请实施例所提供的显示装置的实施例可参见上述显示面板100的实施例,重复之处不再赘述。本申请所提供的显示装置可以为:手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

[0090] 通过上述实施例可知,本发明提供的显示面板及显示装置,至少实现了如下的有益效果:

[0091] 本申请所提供的显示面板及显示装置,在每个像素单元中设置有驱动薄膜晶体管、开关薄膜晶体管和重置薄膜晶体管,由于开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极电连接,重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极电连接,本申请将开关薄膜晶体管的源极和漏极分别位于其栅极的两侧,并将重置薄膜晶体管的源极和漏极也分别位于其栅极的两侧时,开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极之间无需通过跨桥进行连接,重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极之间也无需通过跨桥进行连接,如此有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积,节约的空间使显示面板能够设置更多的像素单元,因而有利于实现显示面板及显示装置的高PPI设计,进而有利于提升显示面板及显示装置的分辨率,使显示图像更加精细、清晰。

[0092] 虽然已经通过例子对本发明的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上例子仅是为了进行说明,而不是为了限制本发明的范围。本领域的技术人员应该理解,可在不脱离本发明的范围和精神的情况下,对以上实施例进行修改。本发明的范围由所附权利要求来限定。

**100**

图1

100

图2

图3

图4

100

图5

100

图6

100

图7

100

图8

图9

图10

图11

**200**

图12

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示面板及显示装置                                      |         |            |

| 公开(公告)号        | <a href="#">CN109742131A</a>                   | 公开(公告)日 | 2019-05-10 |

| 申请号            | CN201910149465.6                               | 申请日     | 2019-02-28 |

| [标]申请(专利权)人(译) | 上海天马微电子有限公司                                    |         |            |

| 申请(专利权)人(译)    | 上海天马微电子有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 上海天马微电子有限公司                                    |         |            |

| [标]发明人         | 张卿<br>姚绮君<br>苏晓越                               |         |            |

| 发明人            | 张卿<br>姚绮君<br>苏晓越                               |         |            |

| IPC分类号         | H01L27/32 G09G3/3225                           |         |            |

| 代理人(译)         | 于淼                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

100

本发明公开了一种显示面板及显示装置，涉及显示技术领域，包括：衬底基板，设置在衬底基板上的多个像素单元，各像素单元包括驱动薄膜晶体管、开关薄膜晶体管、重置薄膜晶体管和有机发光器件；在沿垂直于衬底基板所在平面的方向，开关薄膜晶体管的源极和漏极分别位于该开关薄膜晶体管的栅极的两侧，重置薄膜晶体管的源极和漏极分别位于该重置薄膜晶体管的栅极的两侧；开关薄膜晶体管的漏极与驱动薄膜晶体管的栅极电连接，重置薄膜晶体管的漏极与驱动薄膜晶体管的漏极电连接，驱动薄膜晶体管的漏极与有机发光器件耦接。如此方案，有利于减小开关薄膜晶体管和重置薄膜晶体管在显示面板上所占用的面积，有利于实现高PPI设计。