(12)发明专利申请

(10)申请公布号 CN 109584810 A

(43)申请公布日 2019.04.05

(21)申请号 201710909436.6

(22)申请日 2017.09.29

(71)申请人 昆山工研院新型平板显示技术中心

有限公司

地址 215300 江苏省苏州市昆山市昆山高

新区晨丰路188号

申请人 昆山国显光电有限公司

(72)发明人 文国哲 张九占 吴剑龙 胡思明

朱晖 朱修剑

(74)专利代理机构 上海思微知识产权代理事务

所(普通合伙) 31237

代理人 智云

(51)Int.Cl.

G09G 3/3291(2016.01)

H01L 27/32(2006.01)

权利要求书2页 说明书6页 附图2页

(54)发明名称

像素电路及其驱动方法有机电致发光器件、

显示装置

(57)摘要

本发明提供了一种像素电路及其驱动方法、

有机电致发光器件、显示装置，像素电路包括第

一晶体管、第二晶体管、第三晶体管、第四晶体

管、第五晶体管和存储元件，第一晶体管的栅极

电连接存储元件，第一电极电连接第一电源电

压，第二电极电连接第二晶体管的第二电极；第

二晶体管的栅极电连接扫描线，第一电极电连

接第一晶体管的栅极，第二电极电连接第一晶体

管的第二电极；第三晶体管的栅极电连接扫描线，

第一电极电连接数据线，第二电极电连接存储元

件；第四晶体管的栅极电连接扫描线，第一电极

电连接第一晶体管的第二电极，第二电极电连接

一发光器件；第五晶体管的栅极电连接扫描线，

第一电极电连接第一电源电压，第二电极电连接

存储元件。

1. 一种像素电路，其特征在于，所述像素电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和存储元件，其中：

所述第一晶体管的栅极电连接至所述存储元件的第二端，所述第一晶体管的第一电极电连接至一第一电源电压，所述第一晶体管的第二电极电连接至所述第二晶体管的第二电极；

所述第二晶体管的栅极电连接至一扫描线，所述第二晶体管的第一电极电连接至所述第一晶体管的栅极，所述第二晶体管的第二电极电连接至所述第一晶体管的第二电极；

所述第三晶体管的栅极电连接至所述扫描线，所述第三晶体管的第一电极电连接至一数据线，所述第三晶体管的第二电极电连接至所述存储元件的第一端；

所述第四晶体管的栅极电连接至所述扫描线，所述第四晶体管的第一电极电连接至所述第一晶体管的第二电极，所述第四晶体管的第二电极电连接至一发光器件；

所述第五晶体管的栅极电连接至所述扫描线，所述第五晶体管的第一电极电连接至所述第一电源电压，所述第五晶体管的第二电极电连接至所述存储元件的第一端。

2. 如权利要求1所述的像素电路，其特征在于，

所述第一晶体管、所述第二晶体管和所述第三晶体管为P型薄膜晶体管，所述第四晶体管和所述第五晶体管为N型薄膜晶体管；

或者，所述第一晶体管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管，所述第二晶体管和所述第三晶体管为N型薄膜晶体管。

3. 如权利要求1所述的像素电路，其特征在于，所述扫描线包括第一扫描线和第二扫描线，所述第二晶体管的栅极和所述第三晶体管的栅极电连接至所述第一扫描线，所述第四晶体管的栅极和所述第五晶体管的栅极电连接至所述第二扫描线。

4. 如权利要求3所述的像素电路，其特征在于，所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管；

或者，所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管和所述第五晶体管为N型薄膜晶体管。

5. 如权利要求1所述的像素电路，其特征在于，所述存储元件包括电容元件。

6. 一种有机电致发光器件，其特征在于，包括：

多个如权利要求1-5任一项所述的像素电路以及与多个所述像素电路对应的多个发光器件；

数据驱动电路，用于产生数据信号电压，通过多条数据线向所述像素电路提供所述数据信号电压；

扫描电路，用于产生扫描信号，通过多条扫描线向所述像素电路提供所述扫描信号。

7. 一种如权利要求1-5任一项中所述的像素电路的驱动方法，其特征在于，包括：

在第一阶段，所述第二晶体管和所述第三晶体管导通，所述第四晶体管和所述第五晶体管关断，所述数据线上的数据信号电压被写入所述存储元件的第一端，所述第一电源电压叠加所述第一晶体管的阈值电压耦合到所述存储元件的第二端；

在第二阶段，所述第二晶体管和所述第三晶体管关断，所述第四晶体管和所述第五晶体管导通，所述发光器件发光，所述第一电源电压耦合到所述存储元件的第一端，以使两倍所述第一电源电压叠加所述第一晶体管的阈值电压和负的数据信号电压耦合到所述存储

元件的第二端，所述存储元件上的电压为所述第一电源电压减去数据信号电压。

8. 如权利要求7所述的像素电路的驱动方法，其特征在于，在所述发光器件被驱动时，在放电阶段，所述第二晶体管、所述第三晶体管、所述第四晶体管和所述第五晶体管导通，所述存储元件上的电流放电，所述放电阶段在第一阶段发生前。

9. 如权利要求8所述像素电路的驱动方法，其特征在于，在所述发光器件被驱动时，在重置阶段，所述第二晶体管和所述第三晶体管关断，所述第四晶体管和所述第五晶体管导通，所述重置阶段在所述放电阶段发生前。

10. 一种显示装置，其特征在于，包括如权利要求6所述的有机电致发光器件。

## 像素电路及其驱动方法有机电致发光器件、显示装置

### 技术领域

[0001] 本发明涉及显示技术领域,特别涉及一种像素电路、有机电致发光器件及其驱动方法、显示装置。

### 背景技术

[0002] 虚拟现实 (Virtual Reality, 简称VR) 概念是在80年代初提出来的,其具体是指借助计算机及最新传感器技术创造的一种崭新的人机交互手段。增强现实 (Augmented Reality, 简称AR), 是一种实时地计算摄影机影像的位置及角度并加上相应图像的技术,这种技术的目标是在屏幕上把虚拟世界套在现实世界并进行互动。有机电致发光领域为适应AR、VR产品需求,对像素PPI要求越来越高。

### 发明内容

[0003] 本发明的目的在于提供一种像素电路及其驱动方法、有机电致发光器件、显示装置,以解决现有的像素电路工艺要求高的问题。

[0004] 为解决上述技术问题,本发明提供一种像素电路,所述像素电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和存储元件,其中:

[0005] 所述第一晶体管的栅极电连接至所述存储元件的第二端,所述第一晶体管的第一电极电连接至一第一电源电压,所述第一晶体管的第二电极电连接至所述第二晶体管的第二电极;

[0006] 所述第二晶体管的栅极电连接至一扫描线,所述第二晶体管的第一电极电连接至所述第一晶体管的栅极,所述第二晶体管的第二电极电连接至所述第一晶体管的第二电极;

[0007] 所述第三晶体管的栅极电连接至所述扫描线,所述第三晶体管的第一电极电连接至一数据线,所述第三晶体管的第二电极电连接至所述存储元件的第一端;

[0008] 所述第四晶体管的栅极电连接至所述扫描线,所述第四晶体管的第一电极电连接至所述第一晶体管的第二电极,所述第四晶体管的第二电极电连接至一发光器件;

[0009] 所述第五晶体管的栅极电连接至所述扫描线,所述第五晶体管的第一电极电连接至所述第一电源电压,所述第五晶体管的第二电极电连接至所述存储元件的第一端。

[0010] 可选的,在所述的像素电路中,所述第一晶体管、所述第二晶体管和所述第三晶体管为P型薄膜晶体管,所述第四晶体管和所述第五晶体管为N型薄膜晶体管;

[0011] 或者,所述第一晶体管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管,所述第二晶体管和所述第三晶体管为N型薄膜晶体管。

[0012] 可选的,在所述的像素电路中,所述扫描线包括第一扫描线和第二扫描线,所述第二晶体管的栅极和所述第三晶体管的栅极电连接至所述第一扫描线,所述第四晶体管的栅极和所述第五晶体管的栅极电连接至所述第二扫描线。

[0013] 可选的,在所述的像素电路中,所述第一晶体管、所述第二晶体管、所述第三晶体

管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管；

[0014] 或者，所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管和所述第五晶体管为N型薄膜晶体管。

[0015] 可选的，在所述的像素电路中，所述存储元件包括电容元件。

[0016] 本发明还提供一种有机电致发光器件，包括多个如上述任一项所述的像素电路以及与多个所述像素电路对应的多个发光器件；

[0017] 数据驱动电路，用于产生数据信号电压，通过多条数据线向所述像素电路提供所述数据信号电压；

[0018] 扫描电路，用于产生扫描信号，通过多条扫描线向所述像素电路提供所述扫描信号。

[0019] 本发明还提供一种像素电路的驱动方法，包括：

[0020] 在第一阶段，所述第二晶体管和所述第三晶体管导通，所述第四晶体管和所述第五晶体管关断，所述数据线上的数据信号电压被写入所述存储元件的第一端，所述第一电源电压叠加所述第一晶体管的阈值电压耦合到所述存储元件的第二端；

[0021] 在第二阶段，所述第二晶体管和所述第三晶体管关断，所述第四晶体管和所述第五晶体管导通，所述发光器件发光，所述第一电源电压耦合到所述存储元件的第一端，以使两倍所述第一电源电压叠加所述第一晶体管的阈值电压和负的数据信号电压耦合到所述存储元件的第二端，所述存储元件上的电压为所述第一电源电压减去数据信号电压电压。

[0022] 可选的，在所述的像素电路的驱动方法中，在所述发光器件被驱动时，

[0023] 在放电阶段，所述第二晶体管、所述第三晶体管、所述第四晶体管和所述第五晶体管导通，所述存储元件上的电流放电，所述放电阶段在第一阶段发生前。

[0024] 可选的，在所述的像素电路的驱动方法中，在所述发光器件被驱动时，

[0025] 在重置阶段，所述第二晶体管和所述第三晶体管关断，所述第四晶体管和所述第五晶体管导通，所述重置阶段在所述放电阶段发生前。

[0026] 本发明还提供一种显示装置，包括如上述所述的有机电致发光器件以及封装层。

[0027] 在本发明提供的像素电路、及其驱动方法、显示装置中，所述像素电路包括五个晶体管，电路结构简单，且只需要输入两个控制时序，发光器件发光时所述存储元件上的电压为所述第一电源电压减去数据信号电压，达到在保持阈值补偿等像素电路功能的同时，简化像素电路架构和驱动时序的效果。

## 附图说明

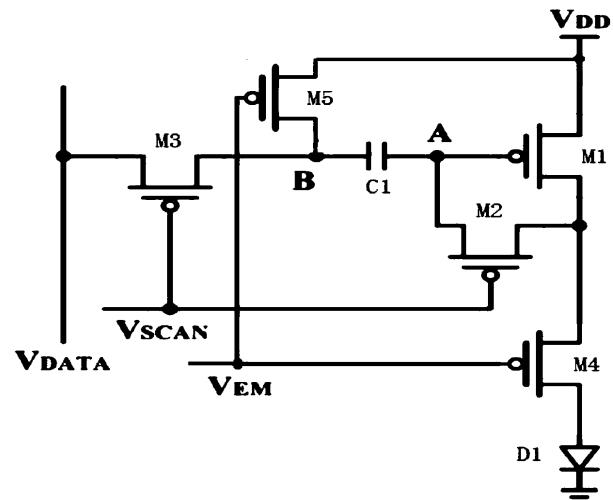

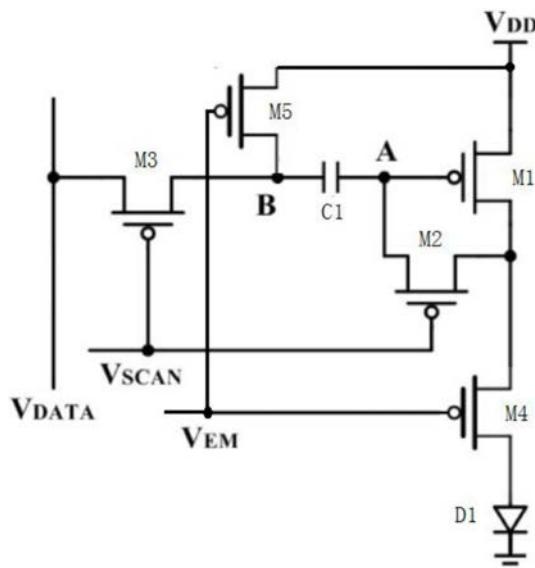

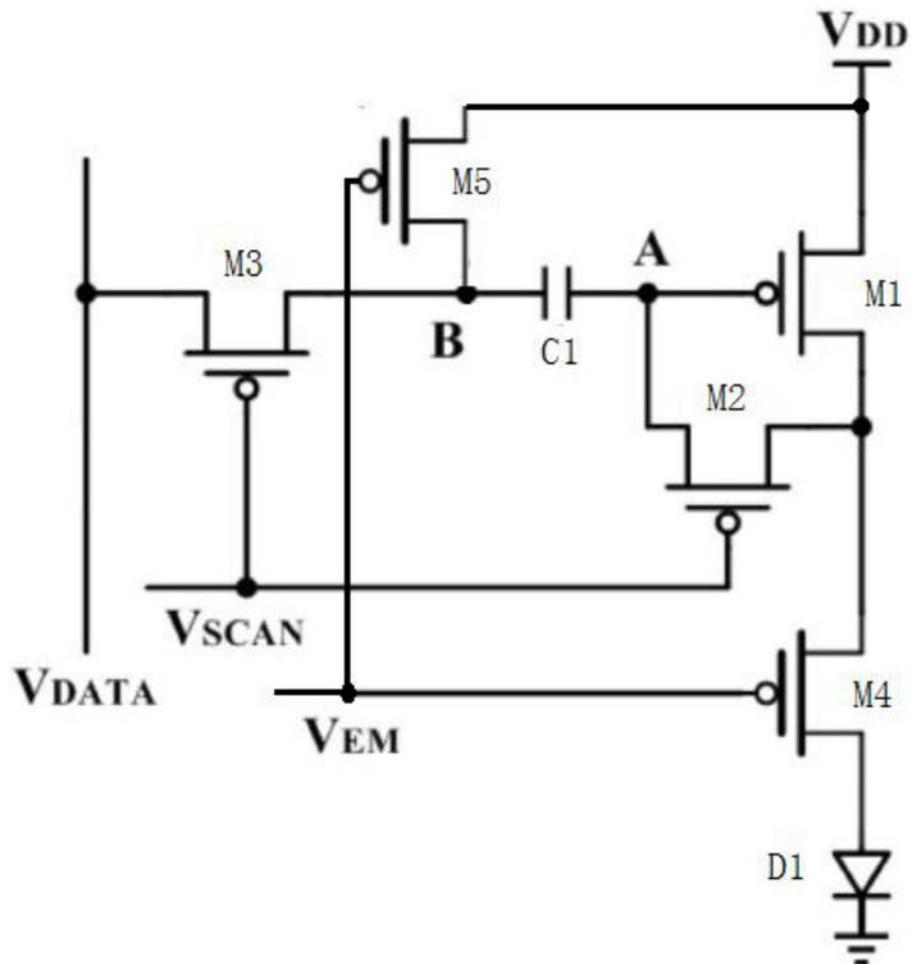

[0028] 图1是本发明一实施例中的像素电路示意图；

[0029] 图2是本发明一实施例中的像素电路的扫描线时序示意图；

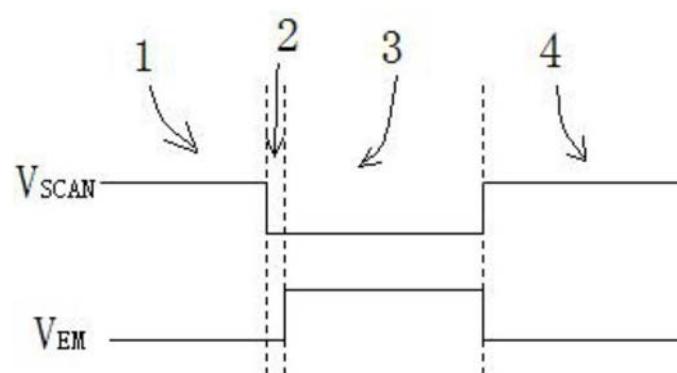

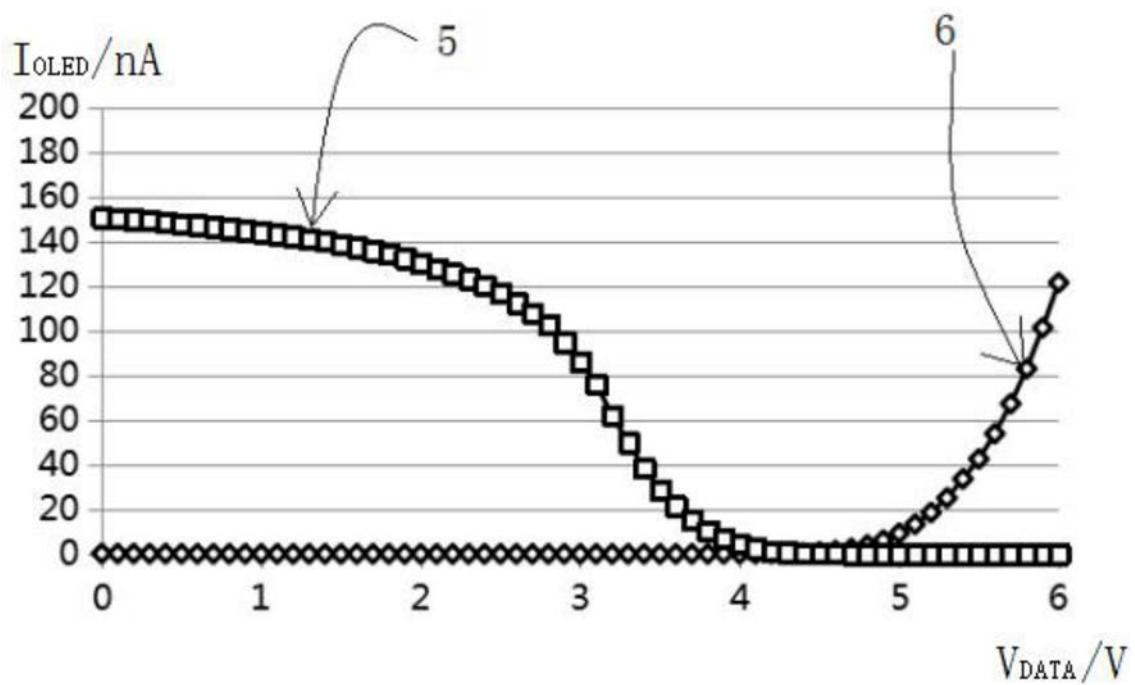

[0030] 图3是本发明一实施例中的像素电路发光器件的电流与数据信号电压关系示意图。

## 具体实施方式

[0031] 以下结合附图和具体实施例对本发明提出的像素电路、及其驱动方法、显示装置

作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0032] 发明人发现,现有的像素电路,由于器件数量多,控制时序复杂,因此很难克服工艺的诸多要求,实现量产。因此需要提供一种像素电路、及其驱动方法、显示装置,以解决现有的像素电路工艺要求高的问题。

[0033] 下面结合图1~3对本发明实施例提供的网版结构及其制作方法作进一步说明。

[0034] <实施例一>

[0035] 如图1~2所示,本实施例提供一种像素电路,所述像素电路被布置在以第一方向排列的供应控制信号的扫描线和以第二方向排列的供应数据信号电压的数据线之间,包括第一晶体管M1、第二晶体管M2、第三晶体管M3、第四晶体管M4、第五晶体管M5和存储元件C1,优选的存储元件包括电容元件,其中:所述第一晶体管M1的栅极电连接至所述存储元件C1的第二端,所述第一晶体管M1的第一电极电连接至第一电源电压V<sub>DD</sub>,所述第一晶体管M1的第二电极电连接至所述第二晶体管M2的第二电极;

[0036] 所述第二晶体管M2的栅极电连接至所述扫描线,所述第二晶体管M2的第一电极电连接至所述第一晶体管M1的栅极,所述第二晶体管M2的第二电极电连接至所述第一晶体管M1的第二电极;

[0037] 所述第三晶体管M3的栅极电连接至所述扫描线,所述第三晶体管M3的第一电极电连接至所述数据线,所述第三晶体管M3的第二电极电连接至所述存储元件C1的第一端;

[0038] 所述第四晶体管M4的栅极电连接至所述扫描线,所述第四晶体管M4的第一电极电连接至所述第一晶体管M1的第二电极,所述第四晶体管M4的第二电极电连接至发光器件D1;

[0039] 所述第五晶体管M5的栅极电连接至所述扫描线,所述第五晶体管M5的第一电极电连接至所述第一电源电压V<sub>DD</sub>,所述第五晶体管M5的第二电极电连接至所述存储元件C1的第一端。

[0040] 有两种驱动方式,第一种驱动方式是第四晶体管和第五晶体管的类型与第一晶体管和第二晶体管的类型不同,例如,所述第一晶体管M1、所述第二晶体管M2和所述第三晶体管M3为P型薄膜晶体管,所述第四晶体管M4和所述第五晶体管M5为N型薄膜晶体管;或者,所述第一晶体管M1、所述第四晶体管M4和所述第五晶体管M5为P型薄膜晶体管,所述第二晶体管M2和所述第三晶体管M3为N型薄膜晶体管,这样扫描线发出信号使第四晶体管和第五晶体管的导通时序与第一晶体管和第二晶体管的导通时序相反,例如在所述发光器件被驱动时,在第一阶段,所述第二晶体管M2和所述第三晶体管M3由所述扫描线控制在导电状态,所述第四晶体管M4和所述第五晶体管M5由所述扫描线控制在不导电状态,所述第一晶体管M1成为二极管接法,传播在所述数据线上的数据信号电压V<sub>DATA</sub>被写入所述存储元件C1;在第二阶段,所述第二晶体管M2和所述第三晶体管M3由所述扫描线控制在不导电状态,所述第四晶体管M4和所述第五晶体管M5由所述扫描线控制在导电状态,所述发光器件发光。如前所述的不导电状态即关断,导电状态即导通。

[0041] 还有另一种驱动方式,在所述的像素电路中,所述扫描线包括第一扫描线和第二扫描线,第一扫描线发出的信号为V<sub>SCAN</sub>,第二扫描线发出的信号为V<sub>EM</sub>,两者控制时序相反,

所述第二晶体管M2的栅极和所述第三晶体管M3的栅极电连接至所述第一扫描线,所述第一扫描线输出扫描电路发出的扫描信号V<sub>SCAN</sub>,所述第四晶体管M4的栅极和所述第五晶体管M5的栅极电连接至所述第二扫描线,其中所述第二扫描线优选的输出发射控制电路发出的驱动信号V<sub>EM</sub>,此时,即使第四晶体管和第五晶体管的类型与第一晶体管和第二晶体管的类型相同,(例如:所述第一晶体管M1、所述第二晶体管M2、所述第三晶体管M3、所述第四晶体管M4和所述第五晶体管M5均为P型薄膜晶体管;或者,所述第一晶体管M1、所述第二晶体管M2、所述第三晶体管M3、所述第四晶体管M4和所述第五晶体管M5均为N型薄膜晶体管),也可以因为V<sub>SCAN</sub>和V<sub>EM</sub>控制时序相反,而使第四晶体管和第五晶体管的导通时序与第一晶体管和第二晶体管的导通时序相反,例如:在所述发光器件D1被驱动时,在第一阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线发出的V<sub>SCAN</sub>控制在导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线发出的V<sub>EM</sub>控制在不导电状态,所述第一晶体管M1成为二极管接法,传播在所述数据线上的数据信号电压V<sub>DATA</sub>被写入所述存储元件C1;在第二阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线V<sub>SCAN</sub>控制在不导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线V<sub>EM</sub>控制在导电状态,所述发光器件D1发光。

[0042] 进一步的,为了使发光器件在进入第一阶段的数据信号电压写入之前,存储元件可以充分放电,避免存储元件本身的电压干扰数据信号电压写入,在第一阶段前还设置有放电阶段,在放电阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线发出的V<sub>SCAN</sub>控制在导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线发出的V<sub>EM</sub>控制在导电状态,所述存储元件C1上的电流放电,所述放电阶段在第一阶段发生前。

[0043] 更进一步的,在所述的像素电路中,在所述发光器件被驱动时,在整个像素电路开启时,需要进行电路的重置,在重置阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线发出的V<sub>SCAN</sub>控制在不导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线发出的V<sub>EM</sub>控制在导电状态,所述重置阶段在所述放电阶段发生前。

[0044] 本实施例还提供一种有机电致发光器件,包括:以第一方向排列的多条扫描线;扫描电路,用于产生扫描信号,通过多条扫描线向所述像素电路提供所述扫描信号,包括第一扫描线发出的信号V<sub>SCAN</sub>和第二扫描线发出的信号V<sub>EM</sub>,扫描电路通过第二扫描线发出的信号V<sub>EM</sub>也可以由另一种实施方式进行替代,例如,通过发射控制驱动电路替代扫描电路,产生发射驱动信号V<sub>EM</sub>,并通过控制线向像素电路提供发射驱动信号V<sub>EM</sub>,与多条扫描线分别连接;以第二方向排列的多条数据线;数据驱动电路,用于产生数据信号电压V<sub>DATA</sub>,与多条数据线分别连接,通过多条数据线向所述像素电路提供所述数据信号电压;还包括多个如上述所述的像素电路以及与多个所述像素电路对应的多个发光器件D1,所述像素电路和发光器件D1被布置在相交叉的所述扫描线和所述数据线之间。

[0045] 本实施例还提供一种显示装置,包括如上所述的有机电致发光器件。

[0046] 综上,上述实施例对像素电路及有机电致发光器件的不同构型进行了详细说明,当然,本发明包括但不局限于上述实施中所列举的构型,任何在上述实施例提供的构型基础上进行变换的内容,均属于本发明所保护的范围。本领域技术人员可以根据上述实施例的内容举一反三。

[0047] <实施例二>

[0048] 如图1~2所示,本实施例提供一种像素电路的驱动方法,包括:在第一阶段,所述第二晶体管M2和所述第三晶体管M3由所述扫描线控制在导电状态,所述第四晶体管M4和所述第五晶体管M5由所述扫描线控制在不导电状态,所述第一晶体管M1成为二极管接法,传播在所述数据线上的数据信号电压V<sub>DATA</sub>被写入所述存储元件C1的第一端,所述第一电源电压V<sub>DD</sub>叠加所述第一晶体管M1的阈值电压耦合到所述存储元件C1的第二端,即电容元件第二端的电位V<sub>c1</sub>=V<sub>DATA</sub>,电容元件第一端的电位V<sub>c2</sub>=V<sub>DD</sub>+V<sub>th</sub>;

[0049] 在第二阶段,所述第二晶体管M2和所述第三晶体管M3由所述扫描线控制在不导电状态,所述第四晶体管M4和所述第五晶体管M5由所述扫描线控制在导电状态,所述发光器件D1发光,所述第一电源电压V<sub>DD</sub>耦合到所述存储元件C1的第一端,两倍所述第一电源电压V<sub>DD</sub>叠加所述第一晶体管M1的阈值电压V<sub>th</sub>和负的数据信号电压耦合到所述存储元件C1的第二端;所述存储元件C1上的电压为所述第一电源电压V<sub>DD</sub>减去数据信号电压V<sub>DATA</sub>,电容元件第二端的电位V<sub>c1</sub>=V<sub>DD</sub>,电容元件第一端的电位V<sub>c2</sub>=2V<sub>DD</sub>+V<sub>th</sub>-V<sub>DATA</sub>。从第一阶段到第二阶段,存储元件的放电电流与电容元件第一端的电位的变化有关,为I<sub>OLED</sub>=K(2V<sub>DD</sub>-V<sub>DATA</sub>+V<sub>th</sub>-V<sub>DD</sub>)<sup>2</sup>=K(V<sub>DD</sub>-V<sub>DATA</sub>)<sup>2</sup>。其中,K为根据薄膜晶体管的性能而确定的常数。

[0050] 如图3所示,存储元件的放电电流即为流过发光器件的电流,现有技术流过发光器件的电流与数据信号电压的关系曲线5为流过发光器件的电流I<sub>OLED</sub>随着数据信号电压V<sub>DATA</sub>增加而减小,本实施例流过发光器件的电流I<sub>OLED</sub>与数据信号电压V<sub>DATA</sub>的关系曲线6为流过发光器件的电流I<sub>OLED</sub>随着数据信号电压增加而增加,数据信号电压与像素电路的灰度呈正比,即本实施例像素电路的灰度随着流过发光器件的电流I<sub>OLED</sub>增加而增加,0~255的灰阶值对应0~64nA的数据信号电压的电压值,由图3可知,本实施例的发光器件的电流I<sub>OLED</sub>可以覆盖所有的灰阶值,最小的发光器件的电流为2pA,可以满足最低灰阶值的要求。

[0051] 进一步的,为了使发光器件在进入第一阶段的数据信号电压写入之前,存储元件可以充分放电,避免存储元件本身的电压干扰数据信号电压写入,在第一阶段前还设置有放电阶段,在放电阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线发出的V<sub>SCAN</sub>控制在导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线发出的V<sub>EM</sub>控制在导电状态,所述存储元件C1上的电流放电,所述放电阶段在第一阶段发生前。

[0052] 更进一步的,在所述的像素电路中,在所述发光器件被驱动时,在整个像素电路开启时,需要进行电路的重置,在重置阶段,所述第二晶体管M2和所述第三晶体管M3由所述第一扫描线发出的V<sub>SCAN</sub>控制在不导电状态,所述第四晶体管M4和所述第五晶体管M5由所述第二扫描线发出的V<sub>EM</sub>控制在导电状态,所述重置阶段在所述放电阶段发生前。

[0053] 在本发明提供的像素电路、及其驱动方法、显示装置中,所述像素电路包括五个晶体管,电路结构简单,通过输入两个控制时序,发光器件发光时所述存储元件C1上的电压为所述第一电源电压V<sub>DD</sub>减去数据信号电压V<sub>DATA</sub>,达到在保持阈值补偿等像素电路功能的同时,简化像素电路架构和驱动时序的效果。

[0054] 本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

[0055] 上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发

明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

图1

图2

图3

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路及其驱动方法有机电致发光器件、显示装置                        |         |            |

| 公开(公告)号        | <a href="#">CN109584810A</a>                   | 公开(公告)日 | 2019-04-05 |

| 申请号            | CN201710909436.6                               | 申请日     | 2017-09-29 |

| [标]申请(专利权)人(译) | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| 申请(专利权)人(译)    | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| 当前申请(专利权)人(译)  | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| [标]发明人         | 文国哲<br>张九占<br>吴剑龙<br>胡思明<br>朱晖<br>朱修剑          |         |            |

| 发明人            | 文国哲<br>张九占<br>吴剑龙<br>胡思明<br>朱晖<br>朱修剑          |         |            |

| IPC分类号         | G09G3/3291 H01L27/32                           |         |            |

| CPC分类号         | G09G3/3291 H01L27/3276                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供了一种像素电路及其驱动方法、有机电致发光器件、显示装置，像素电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和存储元件，第一晶体管的栅极电连接存储元件，第一电极电连接第一电源电压，第二电极电连接第二晶体管的第二电极；第二晶体管的栅极电连接扫描线，第一电极电连接第一晶体管的栅极，第二电极电连接第一晶体管的第二电极；第三晶体管的栅极电连接扫描线，第一电极电连接数据线，第二电极电连接存储元件；第四晶体管的栅极电连接扫描线，第一电极电连接第一晶体管的第二电极，第二电极电连接一发光器件；第五晶体管的栅极电连接扫描线，第一电极电连接第一电源电压，第二电极电连接存储元件。