(12) 发明专利申请

(10) 申请公布号 CN 102074194 A

(43) 申请公布日 2011.05.25

(21) 申请号 201010623536.0

(22) 申请日 2010.12.29

(71) 申请人 广东中显科技有限公司

地址 528225 广东省佛山市南海区狮山经济

开发区北园中路 11 号

(72) 发明人 郭海成 代永平 凌代年 邱成峰

彭华军 黄飚

(74) 专利代理机构 北京瑞恒信达知识产权代理

事务所（普通合伙） 11382

代理人 王凤华

(51) Int. Cl.

G09G 3/32 (2006.01)

权利要求书 1 页 说明书 7 页 附图 6 页

(54) 发明名称

一种单色硅基 OLED 显示器的驱动电路

(57) 摘要

本发明公开了一种单色硅基 OLED 显示器的驱动电路，包括：像素单元电路矩阵、行驱动器电路、列驱动器电路、分频分流器电路、Vcom 反转开关电路和 OLED 发光层测试区；其中列驱动器电路分为镜像对称的上下两组电路，分别驱动奇偶数据线。

1. 一种单色硅基 OLED 显示器的驱动电路,包括:像素单元电路矩阵、行驱动器电路、列驱动器电路、分频分流器电路、Vcom 反转开关电路和 OLED 发光层测试区;其中列驱动器电路分为镜像对称的上下两组电路,分别驱动奇偶数据线。

2. 权利要求 1 所述的驱动电路,其中,所述分频分流器电路用于实现 32 组数据并行输入到像素单元显示矩阵。

3. 权利要求 1 所述的驱动电路,其中,所述像素单元电路矩阵包括多个像素单元电路,所述像素单元电路包括 4 个 PMOS 管,用于向 OLED 发光层提供驱动脉冲电流。

4. 权利要求 3 所述的驱动电路,其中,所述像素单元电路通过电流脉冲宽度的累积来实现灰度调制。

5. 权利要求 3 所述的驱动电路,其中,所述像素单元电路中,第一 PMOS 管用作 OLED 发光层的驱动管,第二 PMOS 管为像素单元矩阵寻址开关管,第三 PMOS 管为驱动开关管,第四 PMOS 管为像素单元电路保护管。

6. 权利要求 5 所述的驱动电路,其中,第一 PMOS 管的漏极连接电源 VCC,第一 PMOS 管的栅极和 VCC 之间连接电容器 C1,第一 PMOS 管的源级连接第三 PMOS 管的漏极,第一 PMOS 管的栅极连接第二 PMOS 管的漏极;第二 PMOS 管的源级连接数字视频位信号 VD,第二 PMOS 管的栅极连接扫描寻址信号 SV;第三 PMOS 管的栅极连接扫描寻址信号 SVB,第三 PMOS 管的源级连接到 OLED 发光层到 Vcom,第三 PMOS 管的源级还连接第四 PMOS 管的栅极和源级,第四 PMOS 管的漏极接地。

7. 权利要求 6 所述的驱动电路,其中,当扫描寻址信号 SV 为低电平时,第二 PMOS 管导通,VD 对 C1 进行充放电。

8. 权利要求 7 所述的驱动电路,其中,当对 C1 充入高电位时,第一 PMOS 管工作在截止状态,不向 OLED 发光层提供驱动电流;当对 C1 充入低电位时,第一 PMOS 管工作在亚阈值状态,向 OLED 发光层提供几十纳安的微驱动电流。

9. 权利要求 6 所述的驱动电路,其中,在第二 PMOS 管导通期间,第三 PMOS 管截止,防止在第一 PMOS 管工作状态发生变化时产生的瞬变电流激发 OLED 发光层出现意外闪烁现象。

10. 权利要求 9 所述的驱动电路,其中,第二 PMOS 管从 VD 取样截止后,第三 PMOS 管立即导通;第四 PMOS 管用作像素单元电路的保护管,当第三 PMOS 管的输出电位低于 0V 时,第四 PMOS 管导通,透过 OLED 发光层 Vcom 公共电极接入 -3V 电位,使得施加到 OLED 发光层上的最大电压为 8V。

## 一种单色硅基 OLED 显示器的驱动电路

### 技术领域

[0001] 本申请涉及微电子显示技术,更具体地,本申请涉及一种硅基 OLED 显示屏和驱动电路。

### 背景技术

[0002] 有机发光二极管 (Organic Light Emitting Diode, OLED) 为电流驱动器件,要求背板电路能提供精确、稳定的电流控制。早期的有源背板采用的是非晶硅 (amorphous silicon, a-Si) TFT 技术,但是由于非晶硅的迁移率较低及阈值电压的不稳定等原因,使其没有获得成功。相比非晶硅而言,低温多晶硅 (Low Temperature Poly-Silicon, LTPS) TFT 的迁移率要高得多,但是阈值电压仍存在均匀性不一致的问题,所以需要在像素电路的设计中进行一定的电路补偿,目前已有的 OLED 显示器大部分采用的都是 LTPS TFT 背板技术。而在大尺寸 OLED 量产方面, LTPS 的制造技术尚不成熟,没有统一的标准生产线,要制备 LTPS TFT 背板必须投巨资建造专用生产线。

[0003] 硅基 OLED 微型显示器件采用单晶硅 CMOS 基板技术,相比其他基板技术而言,单晶硅具有载流子迁移率高、阈值电压稳定等优点,可以将像素矩阵及周边驱动电路等都集成在显示屏上,大大减小整个显示系统的体积及成本,同时成熟的 CMOS 集成电路工艺也为硅基 OLED 微型显示器件的基板制作提供了便利,且单晶硅 CMOS 基板生产工艺流程标准化,仅需支付小额的加工费用就可以在任何一家标准的单晶硅 CMOS 基板生产线上制备基板;同时硅基 OLED 基板上的每个像素面积可以做得很小,利于显示分辨率的提高。在单晶硅 CMOS 基板芯片的设计上,主要考虑的是如何精确控制流过 OLED 的电流,从而实现良好的灰度图象显示。同时芯片功耗也非常重要,因为硅基 OLED 微型显示器件也就可以用于便携式近眼显示,由普通手机电池供电,低功耗电路可延长电池的使用寿命。

### 发明内容

[0004] 为精确控制 OLED 的电流并且降低电路功耗,克服上述的现有 LTPS TFT 背板像素电路存在的缺陷,本申请提供一种基于单晶硅 CMOS 基板技术的一种硅基 OLED 显示屏和驱动电路。

[0005] 根据本申请的一个方面,提供一种单色硅基 OLED 显示器的驱动电路,包括:像素单元电路矩阵、行驱动器电路、列驱动器电路、分频分流器电路、Vcom 反转开关电路和 OLED 发光层测试区;其中列驱动器电路分为镜像对称的上下两组电路,分别驱动奇偶数据线。

[0006] 综上所述,通过应用本发明,可以减少整机空间的尺寸,降低整机功耗。

### 附图说明

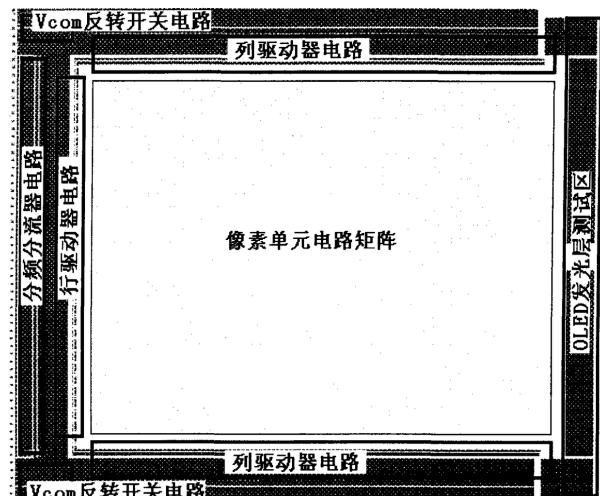

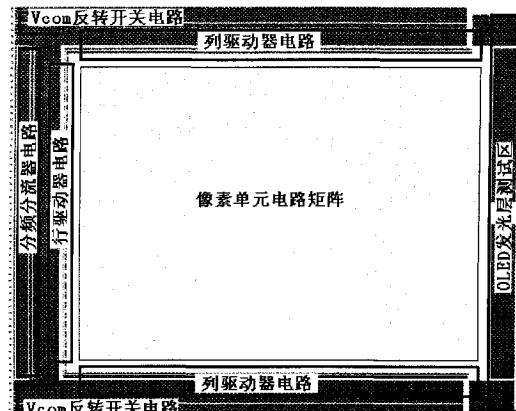

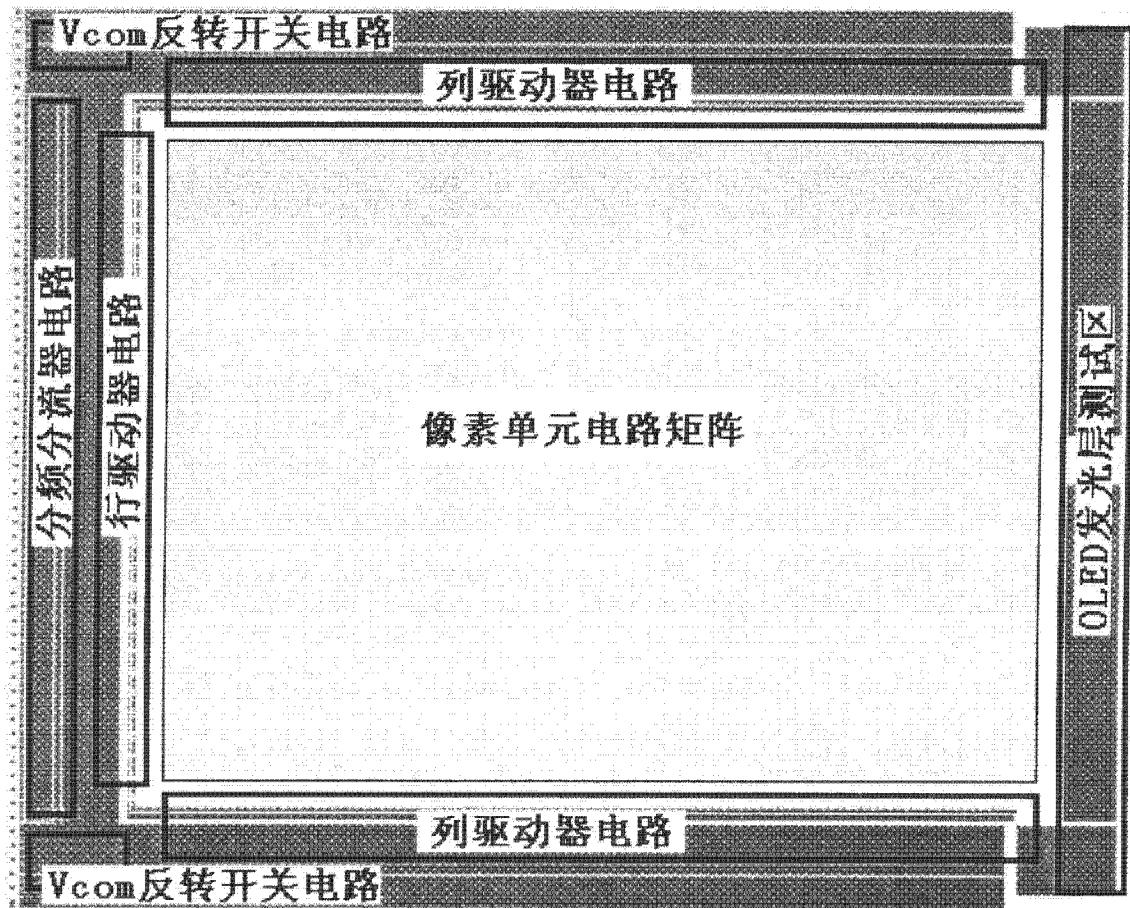

[0007] 图 1 示出根据本发明的显示屏区域示意图;

[0008] 图 2 示出时分脉宽调制帧周期的示意图;

[0009] 图 3 示出显示屏的功能结构示意图;

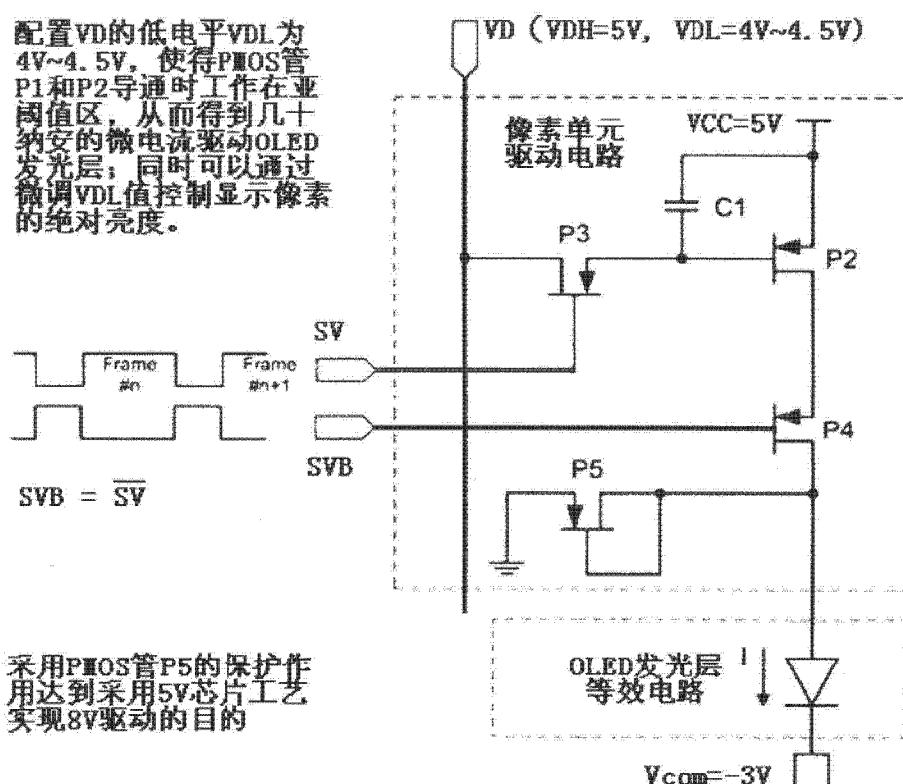

- [0010] 图 4 示出像素单元电路的示意图；

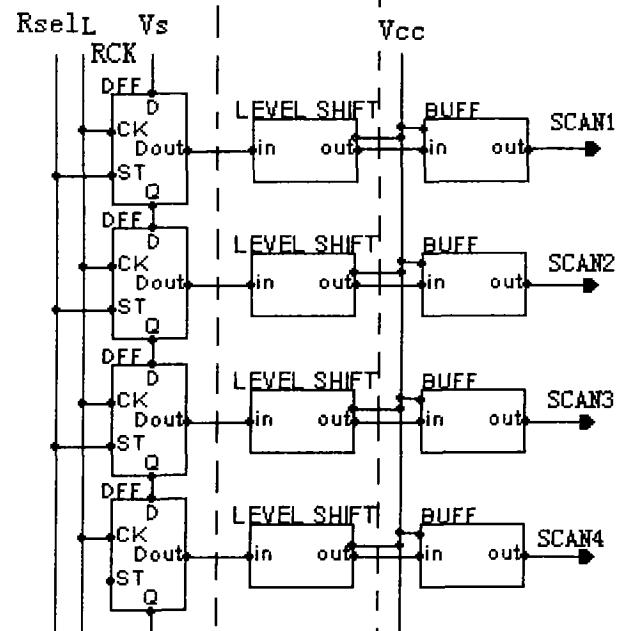

- [0011] 图 5 示出行扫描器电路的示意图；

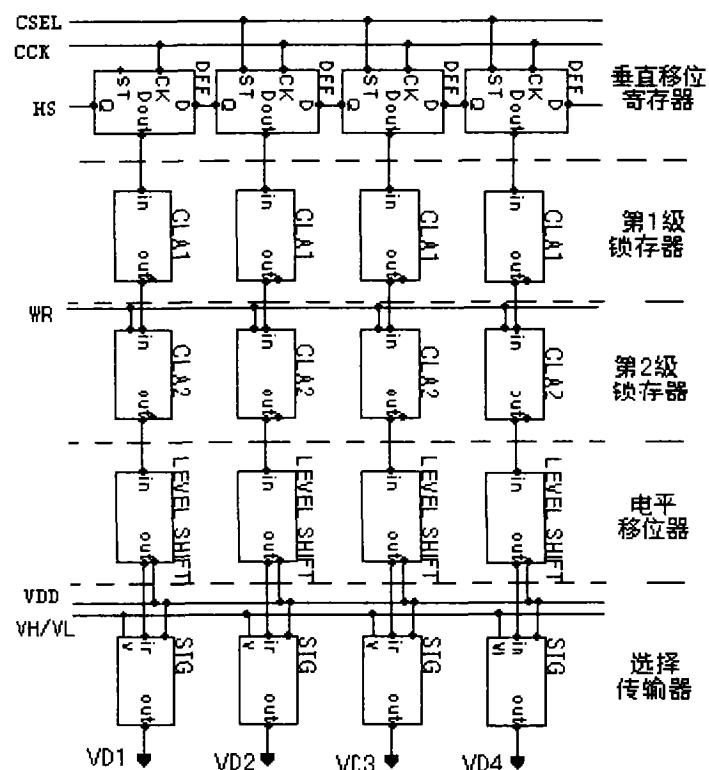

- [0012] 图 6 示出列扫描器电路的示意图；

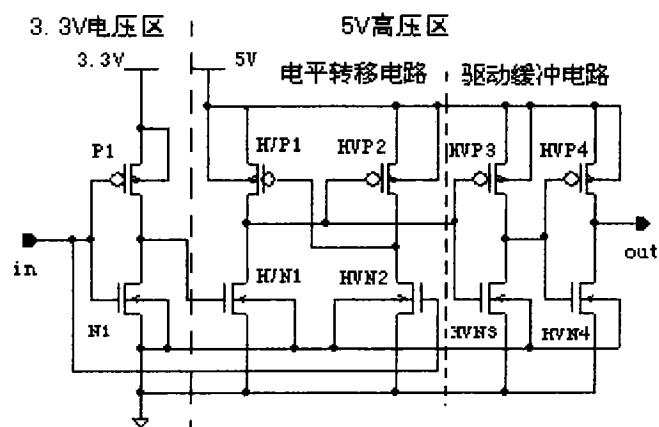

- [0013] 图 7 示出电平移位器电路的示意图；

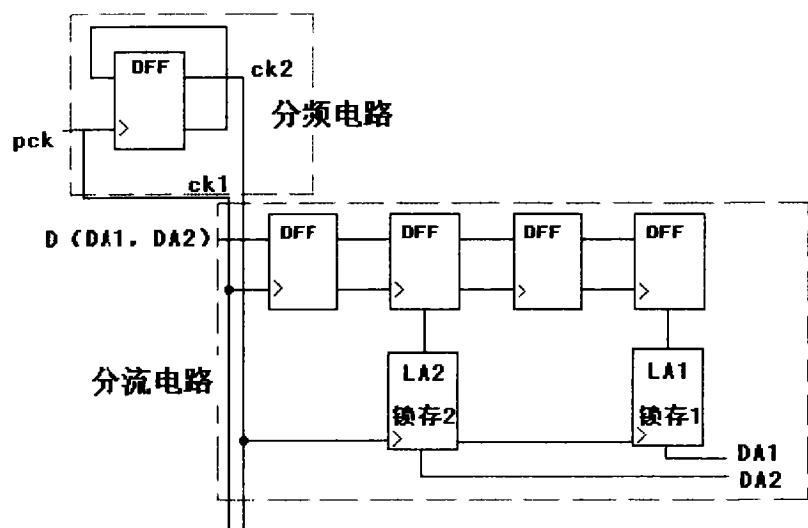

- [0014] 图 8 示出分频分流器电路的示意图；

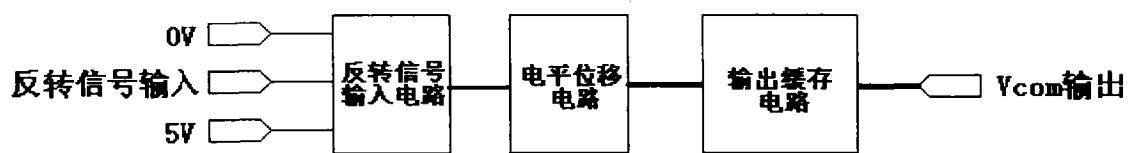

- [0015] 图 9 示出 Vcom 反转开关电路的示意图；

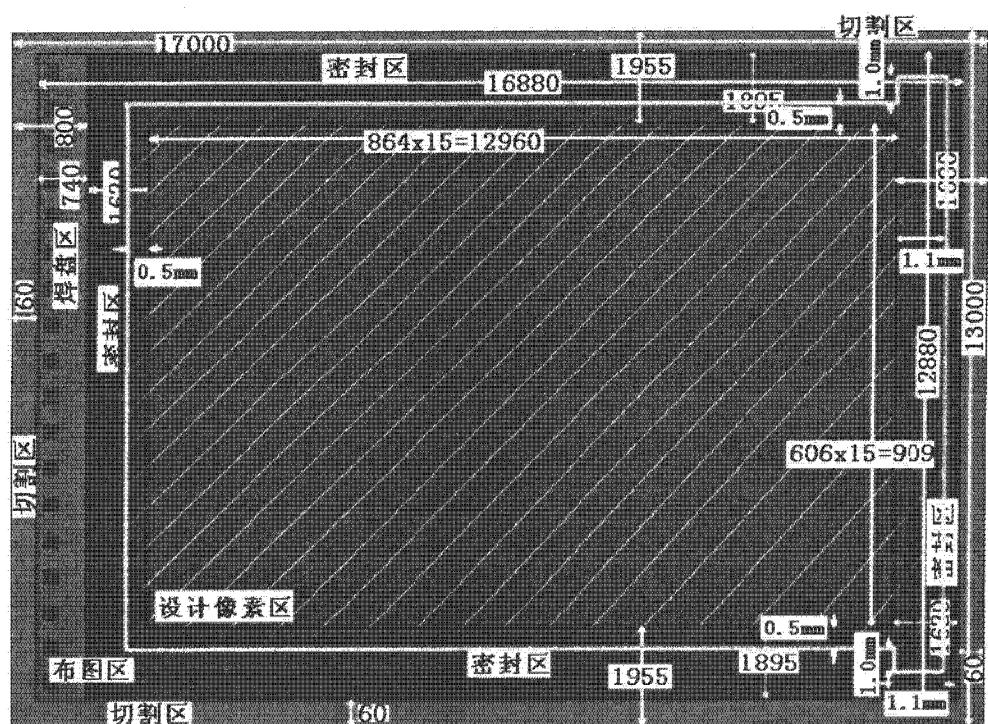

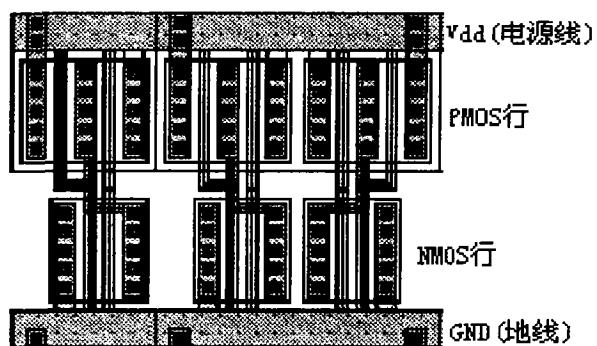

- [0016] 图 10 示出图 3 所示结构的版图布图；

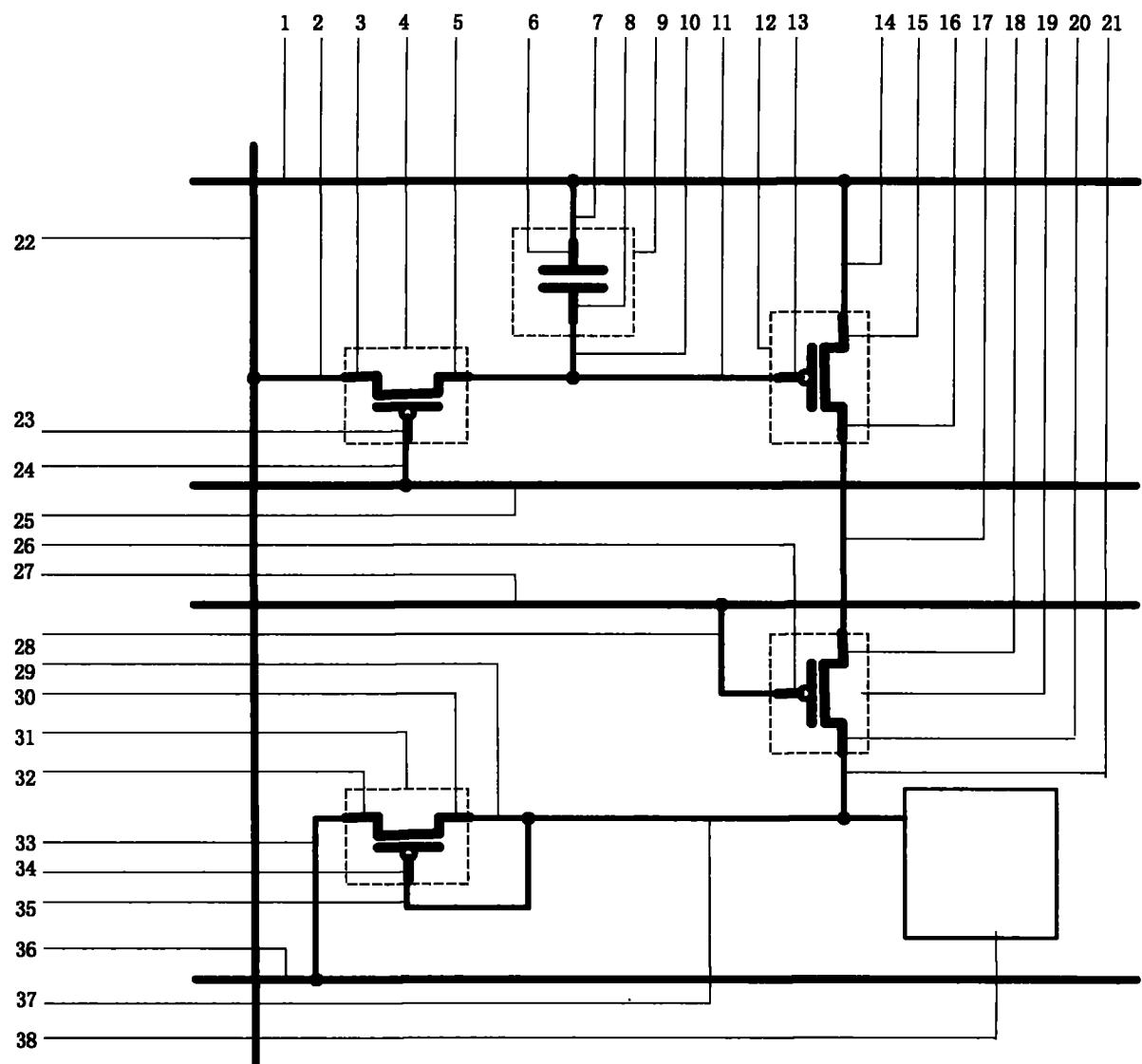

- [0017] 图 11 示出图 4 所示的像素电路的详细结构。

## 具体实施方式

[0018] 下面结合附图和具体实施例对本发明提供的一种硅基 OLED 显示屏和驱动电路进行详细描述。

[0019] 对于本申请所述的单色 OLEDoS 显示芯片 (SVGA) 的规格,其一般特征包括:单色硅基 OLED(OLEDoS) 显示芯片拥有  $864 \times 606$  像素分辨率,按照时分脉宽调制模式实现灰度显示,以备近眼显示应用。输入该芯片的视频数字信号为 16b 子场数据流,即按照子场数目从 1-8 的不同设置,灰度可实现 2-256 级灰度显示。OLEDoS 芯片可输入的数字信号的低电位为  $V_L$ ,可以取 0V,高电位为  $V_H$ ,可以取 3.3V。

[0020] 总的来说,本申请的显示芯片具有的特征包括:适合于单色显示用途的 SVGA 像素分辨率;根据接口电路输入信号子场设置可进行 2-256 级灰度显示;采用 CMOS 工艺实现 OLED 发光层负载驱动;像素单元中 OELD 发光层驱动管的工作状态可自由外置;对 OLED 发光层实现了脉冲驱动模式;无固定像素时钟设置要求,形成视频数据传输通道;OLEDoS 芯片上集成行列驱动器,其中包括输入信号缓存电路模块、电压分配电路模块、接口静电防护电路模块,分频器电路模块,行存储器模块等;显示图像可跟随输入数据输入方式进行对称镜面转换。

[0021] 图 1 示出显示屏区域的规划图,如图 1 所示,该区域包括切割区和布图区,布图区中包括焊盘区、密封区以及设计像素区,设计像素区域也就是显示区域。图中所示尺寸为设计的最优尺寸,但这并不是对于本申请功能区划的限制,在实际的布图设计中,可以根据显示需要进行调整,并且根据电子功能的划分,可以改变布图区和切割区的尺寸设计。

[0022] 在图 1 所示的实施例中,该布图区由切割区四周围绕,焊盘区位于布图区的左侧,焊盘区在布图区中所占面积小,沿着左侧的切割区成竖条状,焊盘区与左侧的切割区直接相邻。设计像素区占到布图区的大部分面积,设计像素区的四周由密封区围绕,将设计像素区和焊盘区以及切割区隔离。密封区在右侧和切割区直接相邻。密封区在左侧位于焊盘区和设计像素区之间。

[0023] 在优选的实施例中,芯片类型为双阱 CMOS 工艺芯片;功能类型为全数字式;应用途径为时分脉宽调制模式硅基 OLED 微型显示器;驱动负载为 OLED 有机发光薄膜层;设计像素区的像素数为  $864 \times 606$  (523,584 个像素);像素间距: $15 \mu m \times 15 \mu m$ ;显示面积: $12.96mm H \times 9.09mm V$  (0.62 英寸);总的芯片面积: $17.00mm H \times 13.00mm V$  (0.84 英寸)。

[0024] 本申请的 OLEDoS 显示芯片采用时分脉宽调制灰度显示模式,其基本原理是运用人眼视网膜在视觉暂略时间范围内对亮度感觉具有类似于时间积分的物理效应,将每帧图

像数据划分成  $n$  ( $n = 1-8$ ) 个子场 (Sub-Fields)，每个子场像素的点亮时间对应不同权值，通过 OLED 显示芯片像素单元电路的调制驱动过程，将每个像素区内的 OLED 发光区域控制在“亮”和“暗”两种状态，可采用二进制表示，这样就组合成  $2^n$  灰度级数。

[0025] 每个二进制的灰度值的每一位对应一段基二权重的时间段，并按对应时间被显示出来，因此人眼视网膜所接收到的是一系列的光脉冲。因为光脉冲是微秒级，远小于视觉暂略时间（约 20ms），人眼视网神经不能区分出每个光脉冲，视网神经所感受的光强度是这些光脉冲积分后的结果。

[0026] 图 2 示出时分脉宽调制帧周期，如图 2 所示，一个值为 10110 的二进制 32 灰度级数的像素显示值，其中 1 代表开态，0 代表关态；假设最低位对应的显示时间间隔为 1，那么从右到左的第二、三、四、五位的时间间隔分别是 2、4、8、16，开态显示的时间为： $16+0+4+2+0 = 22$ ，因此人眼感受到的光强度是全亮态强度的  $22/(16+8+4+2+1) = 22/31$ 。

[0027] 假设  $n = 8$ ，则可以实现 256 灰度级数，这里指每帧图像分成 8 个子场，各子场发光时间与数据比特位的权值比重相对应，即得到公式 (1)：

[0028] SF8 : SF7 : SF6 : SF5 : SF4 : SF3 : SF2 : SF1 = 27 : 26 : 25 : 24 : 23 : 22 : 21 : 20 (1)

[0029] 按灰度级数  $2^n$  来分割每场的像素有效发光时间  $T_{eff}$ ，则第  $n$  个子场 SF $n$  的显示时间  $t_n$  遵循公式 (2)：

$$[0030] t^n = \frac{2^{n-1} T_{eff}}{2^n - 1}$$

[0031] 那么，对于每帧图像中个像素的亮态时间  $T_p$  遵循公式 (3)：

$$[0032] T_p = \left( \sum_{n=8} B 2^{n-1} \right)^{\frac{T_{eff}}{2^n - 1}}$$

[0033] 其中 B 为比特位位置，该位数值为 0、1，分别确定在 SF $n$  内像素处于暗态还是亮态。

[0034] 8 位时分脉宽调制灰度显示模式估算

[0035] 在假设 OLED 响应时间为零的理想情况下， $800 \times 600$  分辨率 8 位时分模式时序中，75Hz 对应于 13.333ms，即  $13333 \mu s$ ， $1 \mu s$  写入 1 行，写满一场用  $600 \mu s$ ，一幅图的写入时间为  $600 \times 8 = 4800 \mu s$ 。有效显示时间为  $13333 - 4800 = 8533 \mu s$ ，分割为 255 份，每份  $8533/255 = 33 \mu s$ ，有效发光时间占空比为  $8533/13333 = 64\%$ 。考虑到逐行写入模式，重新计算有效时间为  $13333 - 8 = 13325 \mu s$ ，分为 255 份为  $13325/255 = 52 \mu s$ ，有效发光时间占空比为  $13324/13333 = 99.9\%$ 。实际应用中考虑到 OLED 的寿命等因素，加入电位反转黑场，将 8 个子场增加到 9 个子场。

[0036] 外部并行 16 位数据输入频率为 50M，考虑到实际物理像素为  $864 \times 606$ ，插入黑场后，实际时序如下：

[0037] 写入 1 行所用时间： $864 \times 20 \mu s / 16 = 1.08 \mu s$

[0038] 写满 1 场所用时间： $1.08 \mu s \times 606 = 655 \mu s$

[0039] 有效显示时间： $13333 \mu s - (655 \mu s \times 9) = 7438 \mu s$

[0040] 分割为 255 份： $7438 \mu s / 255 = 29.169 \mu s$  调整为： $28 \mu s$

[0041] 黑场显示时间： $7438 \mu s - (28 \times 255) \mu s = 298 \mu s$

[0042] 有效发光时间占空比： $(7438 \mu s - 298 \mu s) / 13333 \mu s = 53.6\%$

[0043] 各分场的周期:  $28 \times 128 = 3584 \mu s$ ;  $28 \times 64 = 1792 \mu s$ ;  $28 \times 32 = 896 \mu s$ ;  $28 \times 16 = 448 \mu s$ ;  $28 \times 8 = 224 \mu s$ ;  $28 \times 4 = 112 \mu s$ ;  $28 \times 2 = 56 \mu s$ ;  $28 \mu s$ ; 黑场 =  $298 \mu s$ 。

[0044] 图 3 是根据本发明的显示器的驱动电路的示意图, 如图 3 所示, 其中 OLEDoS 显示芯片采用双阱 CMOS 硅器件工艺, 输入视频数字处理电路和像素单元 OLED 发光层驱动阵列同基底集成。根据前面显示性能的要求, 图 3 示意了整个 OLEDoS 芯片的电路结构, 包括: 像素单元电路矩阵、行驱动器电路、列驱动器电路、分频分流器电路、Vcom 反转开关电路和 OLED 发光层测试区。

[0045] 为了降低芯片工作频率, 不仅把列驱动器分为电学结构镜像对称的上下两组电路, 分别驱动奇偶数据线, 而且采用分频分流器电路实现 32 组数据并行输入像素单元显示矩阵的方式。另外, 这种电路结构可以使芯片面积变小, 显示效果均衡。

[0046] 像素单元电路矩阵包括多个像素单元电路, 其中图 4 示出一个像素单元电路。像素单元电路包括 4 个 PMOS 管 (图 4 中的 P2\P3\P4\P5), 用于向 OLED 发光层提供驱动脉冲电流, 通过电流脉冲宽度的累积实现灰度调制。

[0047] 如图 4 所示, P2 用作 OLED 发光层的驱动管, P3 为像素单元矩阵寻址开关管, P4 为驱动开关管, P5 为像素单元电路保护管, C1 为存储电容器, SV 与 SVB 为一对互不交叠得到扫描寻址信号, VD 为数字视频位信号, 其中 VDH 为“暗”信号, VDL 为“亮”信号, Vcom 为 -3V 的公共电位。

[0048] 其中, P2 的漏极连接电源 VCC, P2 的栅极和 VCC 之间连接电容 C1, P2 的源级连接 P4 的漏极。P2 的栅极连接 P3 的漏极, P3 的源级连接 VD, P3 的栅极连接扫描寻址信号 SV。P4 的栅极连接扫描寻址信号 SVB, P4 的源级连接到 OLED 发光层到 Vcom。P4 的源级还连接 P5 的栅极和源级, P5 的漏极接地。

[0049] 当扫描寻址信号 SV 为低电平时, P3 管导通, VD 对 C1 进行充放电, 当充入 VDH 电位时, P2 驱动管工作在截止状态, 即不向 OLED 发光层提供驱动电流; 当充入 VDL 电位时, P2 驱动管工作在亚阈值状态, 即向 OLED 发光层提供几十纳安的微驱动电流。

[0050] 在 P3 导通期间, P4 截止, 从而防止在 P2 驱动管工作状态发生变化时产生的瞬变电流激发 OLED 发光层出现意外闪烁现象。P3 从 VD 取样截止后, P4 立即导通; PMOS 管 P5 用作像素单元电路的保护管, 当 P4 管的输出电位低于 0V 时, P5 开始导通, 从而可以保持 P1\P2\P3\P4 施加电位差为 5V。透过 OLED 发光层 Vcom 公共电极接入 -3V 电位, 最终能够施加到 OLED 发光层上的最大电压为 8V, 从而达到了使用低电压 CMOS 工艺芯片驱动高电压 (比如 8V) OLED 发光层的目的。

[0051] 图 5 示出行扫描器电路的电路结构。显示芯片电路的行扫描驱动器位于芯片左边, 它有 606 个驱动单元, 依照帧触发时钟 Vs 和扫描时钟脉冲 RCK 同步控制, 它们从第一行到最后一个行依次驱动。

[0052] 如图 5 所示, 行驱动器电路由水平移位寄存器, 电平移位器和扫描缓冲驱动器组成。水平移位寄存器是一个单相输入的 606 位移位寄存器, 在水平移位脉冲 RCK 和帧触发时钟 Vs 的作用下, 依次产生从第 1 行到第 606 行的扫描信号。扫描信号通过电平移位器的作用, 产生  $VL = 0V/VH = 5V$  的扫描电平, 进一步由扫描缓冲驱动器增强驱动能力, 用于寻址每一行中的 864 个像素单元电路。具体地说, 水平移位寄存器扫描到第 i 行时, 通过该行

扫描缓冲驱动器的作用,象素矩阵中与第  $i$  条扫描电极连接的 864 个 PMOS 开关管导通。因为是逐行扫描,这时其它扫描电极皆为 5V 电位,其余的 PMOS 开关管均截止。随着水平移位脉冲 RCK 的作用,被选取的扫描电极将依次改变。

[0053] 图 6 示出列扫描器电路的电路结构。并行输入的 16 位视频信号分成两个 16 组,向列扫描器串行输入数字视频信号,在串入并出的垂直移位寄存器作用下,依次存入第 1 级锁存器。第 1 级锁存器在读入数据前,把所存数据写入第 2 级锁存器,然后第 1 级锁存器在读入数据时,第 2 级锁存器同时通过电平移位器向存储信号数值的选择传输器 (STG) 写出数据,这两组锁存器实现边读入边写出的功能。第 2 级锁存器存满一行后在读出信号作用下,配合行扫描信号,同时输入到各列数值的选择传输器,则每列的 1 位数字信号同步转换成一个调控电压信号 (VH/VL) 作用到象素上,而整体效应则是串行数字视频信号转化成并行视频。调控电压信号,逐行写入每个像素矩阵,驱动其间的 4 个 PMOS 管协同工作。

[0054] 图 7 示出电平移位器电路的结构。其中,无论行驱动器还是列驱动器的电路结构中都采用了电平移位器,其目的是通过标准 3.3V 低电压逻辑控制实现 5V 高压输出,驱动象素显示矩阵工作,这样做可以降低芯片中逻辑处理部分电路 55% 的功耗。

[0055] 图 7 中, P1、P2 为由低压器件组成的反相器,用于产生反相输入信号  $\overline{in}$ 。HVP1-4 和 HVN1-4 采用高压 CMOS 工艺制作,这些高压器件组成电平转移和驱动缓冲两个电路。电平移位电路工作原理:当  $in = 5V$  时, HVN2 和 HVP1 导通, HVN1 和 HVP2 截止,  $out = HVDD$ ; 相反,  $in = 0V$  时,  $out = 0V$ 。可见,该电路结构实现了信号电压从低电平向高电平的位移。

[0056] 图 8 示出分频分流器电路的结构。如图 8 所示,该电路模块由分频电路和分流电路两部分构成。分频电路将显示时钟  $pck$  的频率减半,从而使得整个显示芯片的工作频率减半。分流电路内置两级锁存器,完成对串行输入的两位数据实现同步并行输入,配合了工作频率减半的设置。

[0057] 图 9 示出  $V_{com}$  反转开关电路的结构。反转开关电路包括反转信号输入电路、电平移位电路、输出缓存电路三部分。 $V_{com}$  的输出电压值为 0V 和 5V。应当注意的是,由于采用的是 5V\_CMOS 制备工艺,故该开关有效转换电压为 0V 到 5V 之间,若  $V_{com}$  使用 -3V, 则需外接转换开关。

[0058] 图 10 为版图布图的示意。其中, OLEDoS 芯片电路由 50 余万个 MOS 晶体管组成,采用一维布图样式来合理地放置这些 PMOS 与 NMOS, 单元版图包括 p 型和 p 型两排水平扩散条, PMOS 晶体管位于 P 型条, NMOS 晶体管位于 n 型条。

[0059] 共栅的 PMOS 管和 NMOS 管垂直对齐放置,共用一条多晶栅,这样一对 PMOS 管和 NMOS 管称为一个晶体管对,而不共栅但垂直对齐放置的一对 PMOS 管和 NMOS 管也称为一个晶体管对。

[0060] 电路中相连 MOS 管的源漏区如相邻,则用扩散区相连,称为源漏共用,多个连续排列且源漏共用的 MOS 管称为扩散链,由于 MOS 管常常 P、N 成对排列,所以扩散链又称晶体管对链。电源 / 地线平行地布于两排水平条以外。电源 / 地线以外的线网布在 P 型和 N 型水平条之间。

[0061] 芯片版图结构应具有如下特征:PMOS 像素驱动矩阵可视为一个象素单元的版图作  $864 \times 606$  的阵列展开;周边驱动电路也具有一维高度重复性,即各行扫描驱动器电路结构完全一致,各列也是电路结构完全一致。因此,对于 PMOS 显示矩阵只要设计出一个象素

对称重复单元体,然后按二维平面布图则可;周边驱动电路按照一维布图样式布局出一列或一行的版图,然后相邻行或列作镜相复制,这样可以使相邻的行或列共用电源线或地线,则能设计出最紧凑的版图。

[0062] 设计行或列的版图采用核心生长法。首先将像素驱动矩阵安置在芯片的中部,然后以这些单元为核心放置行或列的相关单元,接着是时钟树和输入数据线,逐渐向芯片的四周扩展和生长,直至单元全部安置完毕。另外,显示芯片对 PAD 的位置没有限制,则引出接点的位置可取决于芯片内部单元的安置结果。最后再考虑放置陪管、测试点、测试电路以及 Vcom 公共电极的预留空间。

[0063] 图 11 示出详细的硅基 OLED 显示芯片像素电路结构。其中,该硅基 OLED 显示芯片像素电路结构包括:至少由读入 PMOS 管源极以及读入 PMOS (P-channel Metal Oxide Semiconductor, P 型沟道金属氧化物半导体) 管栅极以及读入 PMOS 管漏极构成的读入 PMOS 管、至少由 PIP 电容器低阻多晶硅上电极以及 PIP 电容器高阻多晶硅下电极构成的 PIP (Poly Si-insulator-Poly Si, 多晶硅 - 绝缘层 - 多晶硅) 电容器、至少由驱动 PMOS 管源极以及驱动 PMOS 管栅极以及驱动 PMOS 管漏极构成的驱动 PMOS 管、至少由写出 PMOS 管源极以及写出 PMOS 管栅极以及写出 PMOS 管漏极构成的写出 PMOS 管、至少由地线保护 PMOS 管源极以及地线保护 PMOS 管栅极以及地线保护 PMOS 管漏极构成的地线保护 PMOS 管、通过读入 PMOS 管源极连线与所述读入 PMOS 管源极相连接的视频数据串行位线、同时连接 PIP 上电极连线和驱动 PMOS 管源极连线的电源线、通过地线保护 PMOS 管漏极连线与所述地线保护 PMOS 管漏极相连接的 OV 地线、通过读入 PMOS 管栅极连线与所述读入 PMOS 管栅极相连接的正相行选通线、通过写出 PMOS 管栅极连线与所述写出 PMOS 管栅极相连接的负相行选通线、与驱动电极连接线相连接的 OLED 发光层驱动电极。

[0064] 所述 PIP 上电极连线连接到所述 PIP 电容器低阻多晶硅上电极,所述驱动 PMOS 管源极连线连接到所述驱动 PMOS 管源极;所述 PIP 电容器高阻多晶硅下电极通过 PIP 下电极连线连接到把所述读入 PMOS 管漏极与所述驱动 PMOS 管栅极连通的漏栅极连接线上;所述驱动 PMOS 管漏极与所述写出 PMOS 管源极通过源漏极连接线相连通;所述地线保护 PMOS 管栅极、所述地线保护 PMOS 管源极、所述写出 PMOS 管漏极分别通过地线保护 PMOS 管栅极连线、地线保护 PMOS 管源极连线、写出 PMOS 管漏极连线与所述驱动电极连接线相连接;所述电源线、所述正相行选通线、所述负相行选通线、所述 OV 地线沿水平方向设置,且互不相交连通;所述视频数据串行位线沿垂直方向设置,且与所述电源线、所述正相行选通线、所述负相行选通线、所述 OV 地线互不连通。

[0065] 所述 OLED 发光层驱动电极由金属或金属合金制成,常用的金属为铝、铜、金、银等,但不限于这几种,为提高 OLED 稳定性和增强表面发射率,金属电极表面可采用化学机械抛光法 (CMP) 进行抛光处理。所述 OLED 发光层驱动电极覆盖的面积不超过所述硅基 OLED 显示芯片像素电路结构面积的 90%。所述电源线上承载不低于 3.3V 的恒定电位值;所述视频数据串行位线中交替承载高电位信号和低电位信号,且所述高电位信号数值不低于所述电源线上承载的不低于 3.3V 的恒定电位值,所述低电位信号数值不高于比所述高电位信号数值低 0.5V 的数值;所述正相选通线和所述负相选通线上承载的信号为互不交叠反相电压信号;所述一种硅基 OLED 显示芯片像素电路结构采用 PMOS 制程工艺在 N 型单晶硅衬底上生产实现。

[0066] 最后应说明的是,以上实施例仅用以描述本发明的技术方案而不是对本技术方法进行限制。

冬 1

|                                     |    |     |    |    |     |

|-------------------------------------|----|-----|----|----|-----|

| 时间权重                                | 16 | 8   | 4  | 2  | 1   |

| 开关态                                 | ON | OFF | ON | ON | OFF |

| 位数据                                 | 1  | 0   | 1  | 1  | 0   |

| ← 一个 $2^5=32$ 灰度级数(n=5)的时分脉宽调制帧周期 → |    |     |    |    |     |

冬 2

图 3

配置VD的低电平VDL为4V~4.5V，使得PMOS管P1和P2导通时工作在亚阈值区，从而得到几十纳安的微电流驱动OLED发光层；同时可以通过微调VDL值控制显示像素的绝对亮度。

图 4

水平移位寄存器 | 电平移位器 | 扫描缓冲驱动器

图 5

图 6

图 7

图 8

图 9

图 10

图 11

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 一种单色硅基OLED显示器的驱动电路                             |         |            |

| 公开(公告)号 | <a href="#">CN102074194A</a>                   | 公开(公告)日 | 2011-05-25 |

| 申请号     | CN201010623536.0                               | 申请日     | 2010-12-29 |

| [标]发明人  | 郭海成<br>代永平<br>凌代年<br>邱成峰<br>彭华军<br>黄飚          |         |            |

| 发明人     | 郭海成<br>代永平<br>凌代年<br>邱成峰<br>彭华军<br>黄飚          |         |            |

| IPC分类号  | G09G3/32 G09G3/3208                            |         |            |

| 代理人(译)  | 王凤华                                            |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本发明公开了一种单色硅基OLED显示器的驱动电路，包括：像素单元电路矩阵、行驱动器电路、列驱动器电路、分频分流器电路、Vcom反转开关电路和OLED发光层测试区；其中列驱动器电路分为镜像对称的上下两组电路，分别驱动奇偶数据线。