# 「19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G09G 3/00 (2006.01)

G02F 1/061 (2006.01)

# 「12〕发明专利说明书

专利号 ZL 01132557.7

[45] 授权公告日 2007 年 8 月 29 日

[11] 授权公告号 CN 100334607C

[22] 申请日 2001.9.4 [21] 申请号 01132557.7 [30] 优先权

[32] 2000. 9. 4 [33] JP [31] 267164/00

[73] 专利权人 株式会社半导体能源研究所 地址 日本神奈川县

[72] 发明人 犬饲和隆 纳光明 岩渕友幸

[56] 参考文献

US6091203A 2000.7.18 US6040819A 2000.3.21 WO9965012A 1999.12.16

审查员 贾 允

[74] 专利代理机构 中国专利代理(香港)有限公司 代理人 王 岳 张志醒

权利要求书6页说明书43页附图20页

#### [54] 发明名称

驱动电致发光显示装置的方法

#### [57] 摘要

提供了其中很难看到虚假轮廓线的驱动 EL 显示装置的方法。 驱动 EL 显示装置的方法,其中形成多个象素,每个象素具有第一 TFT (薄膜晶体管),第二 TFT,第三 TFT,和有机 EL 元件,具有以下特征:在一个帧周期内出现 n+m 个显示时间间隔(其中 n和 m 都是自然数); n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;在 n+m 个显示时间间隔中间,多个显示时间间隔相应于数字视频信号的同一个比特;以及在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的显示时间间隔在多个显示时间间隔期间出现。

1. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个象素具有第一薄膜晶体管,第二薄膜晶体管,第三薄膜晶体管,和有机电致发光元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔;

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在n+m个显示时间间隔中间,多个显示时间间隔相应于数字视频信号的同一个比特:

在 n+m 个显示时间间隔中间, 相应于数字视频信号的其它比特的其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间间隔的每个显示时间间隔,数字视频信号的相应的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极,以及各个显示时间间隔通过第三薄膜晶体管关断而开始;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时或在第三薄膜晶体管接通时结束的;

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二 薄膜晶体管被关断时有机电致发光元件不发光;以及

- n和m都是自然数。

- 2. 按照权利要求1的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 3. 按照权利要求 1 的方法, 其中  $Tr_1: Tr_2: Tr_3: ...: Tr_{n-1}: Tr_n$  =  $2^0: 2^1: 2^2: ...: 2^{n-2}: 2^{n-1}$ , 其中在 n+m 个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1, Tr_2$ ,  $Tr_3, ..., Tr_{n-1}, Tr_n$ .

- 4. 按照权利要求1的方法,其中第一薄膜晶体管用作为开关薄膜晶体管,第二薄膜晶体管用作为电致发光驱动器薄膜晶体管,以及第三薄膜晶体管用作为擦除薄膜晶体管。

- 5. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个象素具有第一薄膜晶体管,第二薄膜晶体管,第三薄膜晶体管,和有机电致发光元件,其中:

在一个帧周期内出现 11+111 个显示时间间隔;

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间, 多个显示时间间隔相应于数字视频信号的最高位;

在 n+m 个显示时间间隔中间, 相应于数字视频信号的其它比特的其它的显示时间间隔出现在多个显示时间间隔之间:

对于n+m个显示时间间隔的每个显示时间间隔,数字视频信号的相应的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极,以及各个显示时间间隔通过第三薄膜晶体管关断而开始;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时或在第三薄膜晶体管接通时结束的;

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二 薄膜晶体管被关断时有机电致发光元件不发光;以及

其中几和四都是自然数。

- 6. 按照权利要求 5 的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 7. 按照权利要求 5 的方法,其中  $Tr_1: Tr_2: Tr_3: ...: Tr_{n-1}: Tr_n = 2^0: 2^1: 2^2: ...: 2^{n-2}: 2^{n-1},其中在 <math>n+m$  个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1, Tr_2, Tr_3, ..., Tr_{n-1}, Tr_n$ .

- 8. 按照权利要求 5 的方法,其中第一薄膜晶体管用作为开关薄膜晶体管,第二薄膜晶体管用作为电致发光驱动器薄膜晶体管,以及第三薄膜晶体管用作为擦除薄膜晶体管。

- 9. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个 象素具有第一薄膜晶体管,第二薄膜晶体管,第三薄膜晶体管,和有 机电致发光元件,其中:

在一个帧周期内出现 11+11 个显示时间间隔;

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

数字视频信号的一些较高位分别相应于在 n+m 个显示时间间隔中

间的多个显示时间间隔;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间间隔的每个显示时间间隔,数字视频信号的相应的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极,以及各个显示时间间隔通过第三薄膜晶体管关断而开始;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时或在第三薄膜晶体管接通时结束的;

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二 薄膜晶体管被关断时有机电致发光元件不发光;以及

其中几和四都是自然数。

- 10. 按照权利要求 9 的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 11. 按照权利要求 9 的方法, 其中  $Tr_1$ :  $Tr_2$ :  $Tr_3$ : ...:  $Tr_{n-1}$ :  $Tr_n$  =  $2^0$ :  $2^1$ :  $2^2$ : ...:  $2^{n-2}$ :  $2^{n-1}$ , 其中在 n+m 个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1$ ,  $Tr_2$ ,  $Tr_3$ , ...,  $Tr_{n-1}$ ,  $Tr_n$ .

- 12. 按照权利要求 9 的方法,其中第一薄膜晶体管用作为开关薄膜晶体管,第二薄膜晶体管用作为电致发光驱动器薄膜晶体管,以及第三薄膜晶体管用作为擦除薄膜晶体管。

- 13. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个象素具有第一薄膜晶体管,第二薄膜晶体管,和有机电致发光元件,其中;

在一个帧周期内出现 11+11 个显示时间间隔;

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在n+m个显示时间间隔中间,多个显示时间间隔相应于数字视频信号的同一个比特;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于 n+m 个显示时间间隔的每个显示时间间隔,数字视频信号的相应

的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时结束的;

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二 薄膜晶体管被关断时有机电致发光元件不发光;以及

其中几和四都是自然数。

- 14. 按照权利要求13的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 15. 按照权利要求 13 的方法, 其中  $Tr_1$ :  $Tr_2$ :  $Tr_3$ : ...:  $Tr_{n-1}$ :  $Tr_n = 2^0$ :  $2^1$ :  $2^2$ : ...:  $2^{n-2}$ :  $2^{n-1}$ , 其中在 n+m 个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1$ ,  $Tr_2$ ,  $Tr_3$ , ...,  $Tr_{n-1}$ ,  $Tr_n$ .

- 16. 按照权利要求13的方法,其中第一薄膜晶体管用作为开关薄膜晶体管以及第二薄膜晶体管用作为电致发光驱动器薄膜晶体管。

- 17. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个象素具有第一薄膜晶体管,第二薄膜晶体管,和有机电致发光元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔:

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间, 多个显示时间间隔相应于数字视频信号的最高位;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于 n+m 个显示时间间隔的每个显示时间间隔,数字视频信号的相应的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时结束的;

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二 薄膜晶体管被关断时有机电致发光元件不发光;以及

其中п和四都是自然数。

- 18. 按照权利要求 17 的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 19. 按照权利要求 17 的方法, 其中  $Tr_1$ :  $Tr_2$ :  $Tr_3$ : ...:  $Tr_{n-1}$ :  $Tr_n$  =  $2^0$ :  $2^1$ :  $2^2$ : ...:  $2^{n-2}$ :  $2^{n-1}$ , 其中在 n+m 个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1$ ,  $Tr_2$ ,  $Tr_3$ , ...,  $Tr_{n-1}$ ,  $Tr_n$ .

- 20. 按照权利要求17的方法,其中第一薄膜晶体管用作为开关薄膜晶体管以及第二薄膜晶体管用作为电致发光驱动器薄膜晶体管。

- 21. 一种驱动电致发光显示装置的方法,其中形成多个象素,每个象素具有第一薄膜晶体管,第二薄膜晶体管,和有机电致发光元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔;

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

数字视频信号的一些较高位分别相应于在 n+m 个显示时间间隔中间的多个显示时间间隔;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于 n+m 个显示时间间隔的每个显示时间间隔,数字视频信号的相应的比特通过第一薄膜晶体管接通而被输入到第二薄膜晶体管的栅电极;

在 n+m 个显示时间间隔的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始时结束的;以及

当第二薄膜晶体管被接通时有机电致发光元件发光,以及当第二薄膜晶体管被关断时有机电致发光元件不发光;以及

其中n和m都是自然数。

- 22. 按照权利要求 21 的方法,其中第一薄膜晶体管和第二薄膜晶体管具有相同的极性。

- 23. 按照权利要求 21 的方法,其中  $Tr_1$ :  $Tr_2$ :  $Tr_3$ : ...:  $Tr_{n-1}$ :  $Tr_n$  =  $2^0$ :  $2^1$ :  $2^2$ : ...:  $2^{n-2}$ :  $2^{n-1}$ ,其中在 n+m 个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为  $Tr_1$ ,  $Tr_2$ ,  $Tr_3$ , ...,  $Tr_{n-1}$ ,  $Tr_n$ .

24. 按照权利要求 21 的方法,其中第一薄膜晶体管用作为开关薄膜晶体管以及第二薄膜晶体管用作为电致发光驱动器薄膜晶体管。

# 驱动电致发光显示装置的方法

# 技术领域

本发明涉及驱动具有执行灰度等级显示的平板的 EL(电致发光)显示装置的方法,在显示平板上多个象素被安排成矩阵形状,以及每个象素被接通的时间长度是可控制的。具体地,本发明涉及驱动具有使用有机 EL 元件的 EL 平板的 EL 显示装置的方法。

## 背景技术

广播电台所使用的设备和系统中数字技术的引用正不断地增长,近年来,广播无线电波的数字化,也就是,对于数字广播的实现的研究和开发,正在全世界范围内进行。

而且,对待广播无线电波的数字化、研究和开发,近年来在有源矩阵显示装置方面一直很兴旺繁荣,在这种显示装置中,具有图象信息的数字视频信号,不用变换成模拟信号,就可被使用来显示图象。

作为用于按照数字视频信号的两个电压值来执行灰度等级显示的 方法,可以给出表面积划分驱动方法和时间划分驱动方法。

表面积划分驱动方法是通过把一个象素划分成多个子象素以及根据数字视频信号独立地驱动每个子象素而执行灰度等级显示的驱动方法。在这个表面积划分驱动方法中,一个象素必须被划分成多个子象素。另外,也必须形成相应于各个子象素的象素电极,以便独立地驱动划分的子象素。因此,带来一个难题,象素结构很复杂。

另一方面,时间划分驱动方法是通过控制象素被接通的时间长度 而执行灰度等级显示的驱动方法。具体地,一个帧的时间间隔被划分成多个显示时间间隔。每个象素然后在每个显示时间间隔按照数字显示信号被设置成接通或关断状态。某个象素的灰度等级是通过把在一个帧周期内出现的所有的显示时间间隔内该象素被接通的显示时间间隔的长度相加而被确定的。

通常,有机 EL 材料的响应速度比液晶更快,所以有机 EL 材料适合于时间划分驱动(时分驱动)。

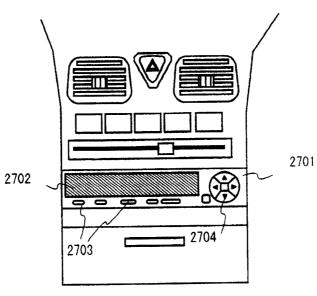

当执行时分驱动时,二进制码在实现高级别灰度等级时是方便的。下面通过图 19A 和 19B 来说明按照简单的二进制码方法用时分驱

动来显示中等级别的灰度等级的情形。

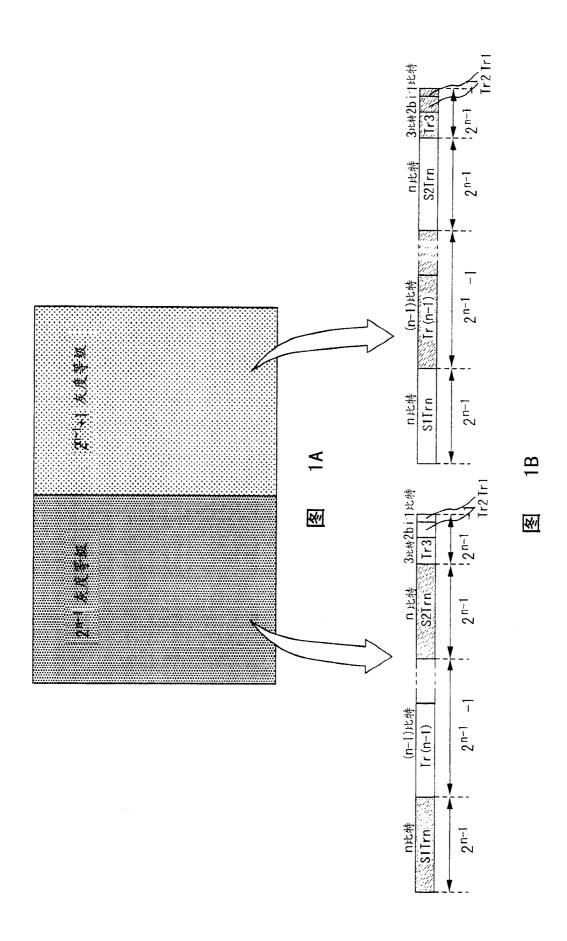

图 19A 显示一个显示装置的象素部分,以及图 19B 上显示在象素部分中一个帧周期内出现的所有的显示时间间隔的长度。

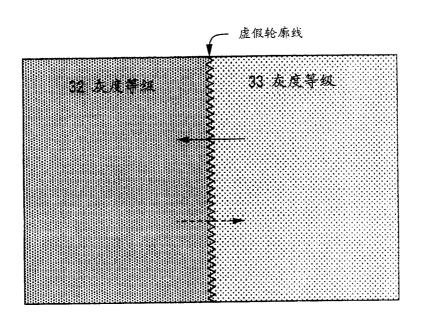

在图 19A 和 19B上,图象是通过使用能够显示灰度等级 1 到 64 的 6 比特数字视频信号被显示的。象素部分的右半部分执行 33 (32+1)等级的显示,以及象素部分的左半部分执行 32 (31+1)等级的显示。

当使用 6 比特数字视频信号时,通常在一个帧周期内出现六个显示时间间隔(显示时间间隔 Tr1 到 Tr6)。数字视频信号的第一到第六比特分别相应于显示时间间隔 Tr1 到 Tr6。

显示时间间隔 Tr1 到 Tr6 的长度的比值变成为 2°: 2¹: 2²: 2³: 2⁴: 2⁵。 相应于数字视频信号的最高位(在本例中是第六比特)的显示时间间隔 Tr6 的长度是最长的,以及相应于数字视频信号的最低位(第一比特)的显示时间间隔的长度是最短的。

对于执行第 32 等级的显示的情形,在显示时间间隔 Tr1 到 Tr5 中象素被设置为接通状态以及在显示时间间隔 Tr6 期间象素被设置为关断状态。而且,对于执行第 33 等级的显示的情形,在显示时间间隔 Tr1 到 Tr5 中象素被设置为关断状态以及在显示时间间隔 Tr6 期间象素被设置为接通状态。

在用于执行第 32 等级的显示的部分与用于执行第 33 等级的显示的部分之间的边界部分处,可以看到虚假轮廓线。

术语虚假轮廓线是指当按照二进制码方法执行时间灰度等级显示时,可重复看到的非自然的轮廓线,也就是说,虚假轮廓线的主要原因是由于人的视觉特性在感觉到的亮度上形成的起伏。产生虚假轮廓线的机制可通过图 20A 和 20B 进行说明。

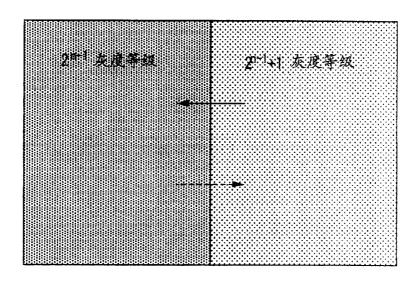

图 20A 显示其中形成虚假轮廓线的显示装置的象素部分,以及图 20B 显示在象素部分内一个帧周期内出现的显示时间间隔长度的比值。

在图 20A 和 20B 上,图象是通过使用能够显示灰度等级 1 到 64 的 6 比特数字视频信号被显示的。象素部分的右半部分执行 33 个等级的显示,以及象素部分的左半部分执行 32 个等级的显示。

在执行第 32 等级的显示的象素部分的部分中,在一个帧周期的 31/63 期间象素被设置为接通状态以及在一个帧周期的 32/63 期间象

素被设置为关断状态。其间象素被接通的时间间隔与其间象素被关断的时间间隔交替地出现。

而且,在执行第 33 等级的显示的象素部分的部分中,在一个帧周期的 32/63 期间象素被设置为接通状态以及在一个帧周期的 31/63 期间象素被设置为关断状态。其间象素被接通的时间间隔与其间象素被关断的时间间隔交替地出现。

对于执行活动图象的情形,在显示第 32 灰度等级的部分与显示第 33 灰度等级的部分之间的交界面在图 20A 上被取为沿虚线方向运动。即,靠近边界的象素在显示第 32 灰度等级与显示第 33 灰度等级之间转换。通过这样做,在靠近边界的象素中,用于显示第 33 灰度等级的接通时间隔紧接在用于显示第 32 灰度等级的接通时间间隔后面立即开始。这样,人的眼睛可以看见在一个帧周期期间连续被接通的象素。这在屏幕上感觉到非自然的亮线。

反之,在显示第 32 灰度等级的部分与显示第 33 灰度等级的部分之间的交界面在图 20A 上被取为沿实线方向运动。即,靠近边界的象素在显示第 33 灰度等级与显示第 32 灰度等级之间转换。通过这样做,在靠近边界的象素中,用于显示第 33 灰度等级的接通时间间隔紧接在用于显示第 32 灰度等级的接通时间间隔后面立即开始。这样,人的眼睛可以看见在一个帧周期期间连续被关断的象素。这在屏幕上感觉到非自然的暗线。

屏幕上出现的这些类型的非自然亮线和暗线是显示的障碍,被称为虚假轮廓线(活动的虚假轮廓线)。

显示的障碍在静止图象中,由于与在活动图象中形成活动的虚假轮廓线的情形中相同的原因,也成为可看见的。显示静止图象的障碍在于,在灰度等级的边界处可以看见闪烁的运动。下面来解释在静止图象中可以看到这种类型的显示障碍的原因。

即使人的眼睛固定在一点,但视点仍旧轻微移动,很难不动地盯在一点上。所以,即使人的打算是注视其中象素正在执行第 32 等级的显示的象素部分的部分与其中象素正在执行第 33 等级的显示的象素部分的部分之间的边界,但视点实际上稍微地上下和左右移动。

例如,假设视点从执行第 32 等级的显示的部分移到执行第 33 等级的显示的部分,如图上虚线所表示的。对于其中当视点位于显示第

32 等级的部分时象素处在关断状态和当视点位于显示第 33 等级的部分时象素处在关断状态的情形下,象素被人的眼睛看作为在整个一个帧周期内处在关断状态。

反之,例如,假设视点从执行第 33 等级的显示的部分移到执行第 32 等级的显示的部分,如图上实线所表示的。对于其中当视点位于显示第 33 等级的部分时象素处在接通状态和当视点位于显示第 32 等级的部分时象素处在接通状态的情形下,象素被人的眼睛看作为在整个一个帧周期内处在接通状态。

因为视点的左右和上下的细小的移动,所以在一个帧周期内,象 素被人的眼睛看作为或者处在接通状态,或处在关断状态,因此看见 了其中边界部分被看成来回摇摆的、显示的障碍。

## 发明内容

本发明的申请人按照固定的法则把最长的显示时间间隔划分成多个显示时间间隔(划分的显示时间间隔),以防止看到虚假的轮廓线。 多个划分的显示时间间隔然后被分布在一个帧周期内,以免接连地出现。

可以有一个划分的显示时间间隔,以及可以有多个划分的显示时间间隔。然而,优选地,显示时间间隔相应于最高位,换句话说,最长的显示时间间隔按照固定的法则按次序地被划分。

而且,有可能设计者适当地选择划分的显示时间间隔的数目,但 优选地,划分的量是通过用于显示装置的驱动速度与所需要的图象显 示量的平衡而被确定。

而且,优选地,相应于数字视频信号的同一个比特的划分的显示 时间间隔的长度是相同的,但本发明并不限于此。不一定总是使得划 分的显示时间间隔是相同的。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

下面讨论本发明的结构。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT (薄膜晶体管),第二 TFT,第三 TFT,和有机 EL 元件,其特征在于:

在一个帧周期内出现 n+m 个显示时间间隔 (其中 n 和 m 都是自然

# 数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间,多个显示时间间隔相应于数字视频信号的同一个比特;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于 n+m个显示时间的每个显示时间间隔,数字视频信号的相应的比特通过第一 TFT 接通而被输入到第二 TFT 的栅极,以及各个显示时间间隔通过第三 TFT 关断而开始;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始前或在第三 TFT 接通前结束的;以及

当第二 TFT 被接通时有机 BL 元件发光,以及当第二 TFT 被关断时有机 BL 元件不发光。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT,第二 TFT,第三 TFT,和有机 EL 元件,其特征在于:

在一个帧周期内出现 n+m 个显示时间间隔 (其中 n 和 m 都是自然数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间, 多个显示时间间隔相应于数字视频信号的最高位;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间的每个显示时间间隔,数字视频信号的相应的比特通过第一 TFT 接通而被输入到第二 TFT 的栅极,以及各个显示时间间隔通过第三 TFT 关断而开始;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始前或在第三 TFT 接通前结束的;以及

当第二 TFT 被接通时有机 EL 元件发光, 以及当第二 TFT 被关断时有机 EL 元件不发光。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT,第二 TFT,第三 TFT,和 有机 EL 元件,其特征在于:

在一个帧周期内出现 n+m 个显示时间间隔 (其中 n 和 m 都是自然数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

数字视频信号的一些较高位分别相应于在 n+m 个显示时间间隔中间的多个显示时间间隔;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于 n+m 个显示时间的每个显示时间间隔, 数字视频信号的相应的比特通过第一 TFT 接通而被输入到第二 TFT 的栅极, 以及各个显示时间间隔通过第三 TFT 关断而开始;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始前或在第三 TFT 接通前结束的;以及

当第二 TFT 被接通时有机 EL 元件发光,以及当第二 TFT 被关断时有机 EL 元件不发光。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT,第二 TFT,和有机 EL 元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔 (其中 n 和 m 都是自然数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间, 多个显示时间间隔相应于数字视频信号的同一个比特;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间的每个显示时间间隔,数字视频信号的相应的比特通过第一TFT接通而被输入到第二TFT的栅极;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间

隔是在另一个显示时间间隔开始前结束的; 以及

当第二 TFT 被接通时有机 EL 元件发光,以及当第二 TFT 被关断时有机 EL 元件不发光。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT,第二 TFT,和有机 EL 元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔 (其中 n 和 m 都是自然数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

在 n+m 个显示时间间隔中间, 多个显示时间间隔相应于数字视频信号的最高位;

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间的每个显示时间间隔,数字视频信号的相应的比特通过第一TFT接通而被输入到第二TFT的栅极;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始前结束的;以及

当第二 TFT 被接通时有机 EL 元件发光,以及当第二 TFT 被关断时有机 EL 元件不发光。

按照本发明,提供了用于驱动 EL 显示装置的方法,在 EL 显示装置中形成多个象素,每个象素具有第一 TFT,第二 TFT,和有机 EL 元件,其中:

在一个帧周期内出现 n+m 个显示时间间隔(其中 n 和 m 都是自然数);

n+m 个显示时间间隔,每个相应于在数字视频信号的 n 比特中间的数字视频信号的一个比特;

数字视频信号的一些较高位分别相应于在 n+m 个显示时间间隔中间的多个显示时间间隔:

在 n+m 个显示时间间隔中间,相应于数字视频信号的其它比特的、 其它的显示时间间隔出现在多个显示时间间隔之间;

对于n+m个显示时间的每个显示时间间隔,数字视频信号的相应的

比特通过第一 TFT 接通而被输入到第二 TFT 的栅极;

在 n+m 个显示时间的每个显示时间间隔开始后,各个显示时间间隔是在另一个显示时间间隔开始前结束的;以及

当第二 TFT 被接通时有机 EL 元件发光,以及当第二 TFT 被关断时有机 EL 元件不发光。

在本发明中,方法的特征在于,第一 TFT 和第二 TFT 具有相同的极性。

在本发明中,方法的特征在于, $Tr_1, Tr_2, Tr_3, ..., Tr_{n-1}, Tr_n=2^0, 2^1, 2^2, ..., 2^{n-2}, 2^{n-1},$ 其中在n+m个显示时间间隔中间、相应于数字视频信号的各个比特的显示时间间隔的长度被取为 $Tr_1, Tr_2, Tr_3, ..., Tr_{n-1}, Tr_n$

附图说明

在附图中:

图 1A 和 1B 是分别显示使用本发明的驱动方法的 EL 显示器的象素部分,以及显示时间间隔与划分的显示时间间隔的长度的比值的图;

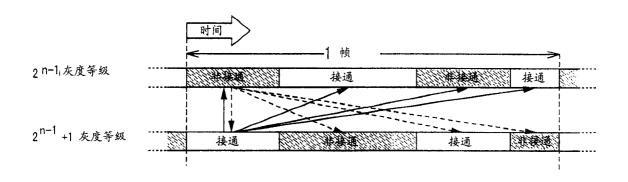

图 2A 和 2B 是分别显示使用本发明的驱动方法的 EL 显示器的象素部分,以及显示时间间隔与非显示时间间隔的长度的比值的图;

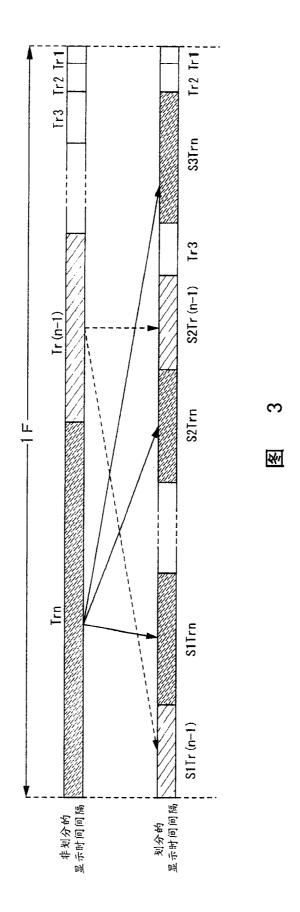

- 图 3 是显示对于把多个显示时间间隔划分成划分的显示时间间隔的情形,显示时间间隔与划分的显示时间间隔的长度的比值的图:

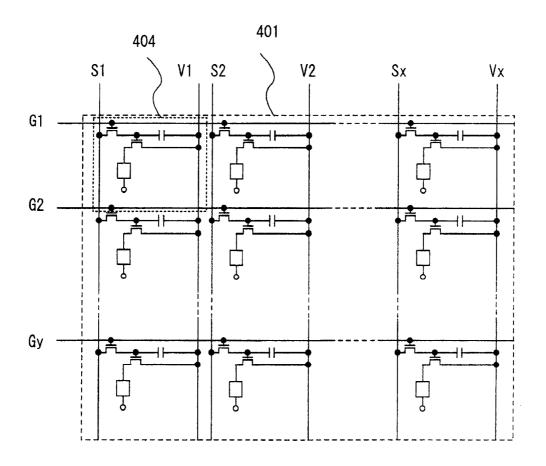

- 图 4 是使用本发明的驱动方法的象素部分的电路图;

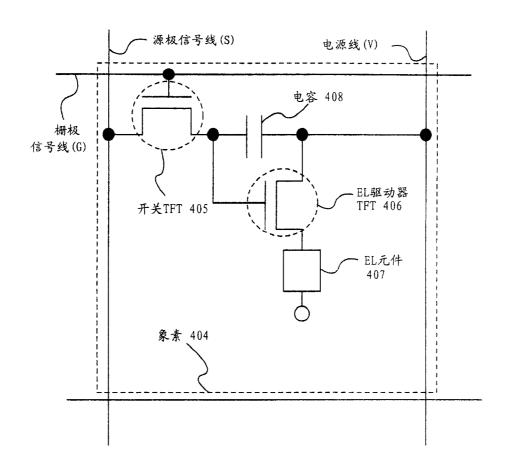

- 图 5 是使用本发明的驱动方法的象素的电路图;

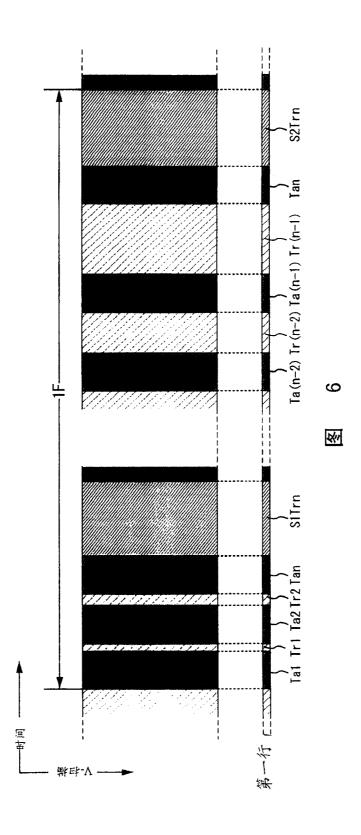

- 图 6 是显示本发明的驱动方法的图;

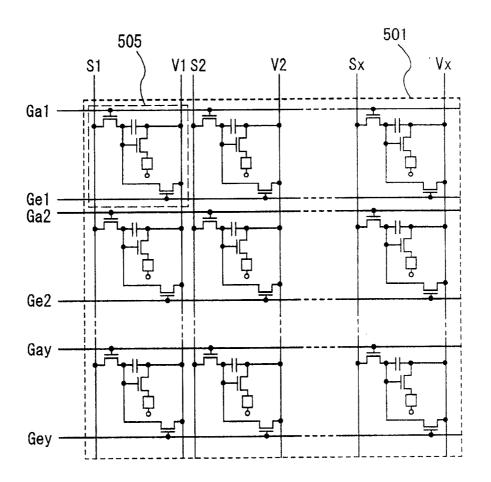

- 图 7 是使用本发明的驱动方法的象素部分的电路图;

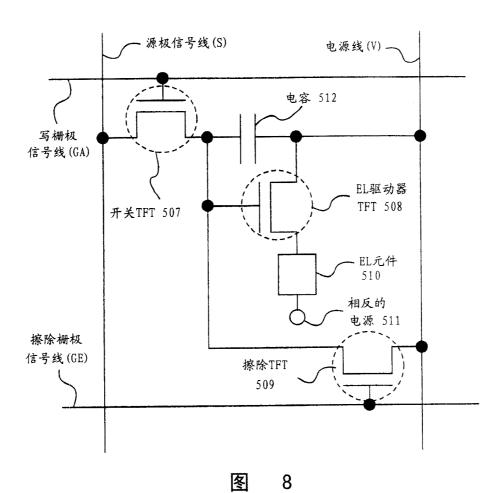

- 图 8 是使用本发明的驱动方法的象素的电路图;

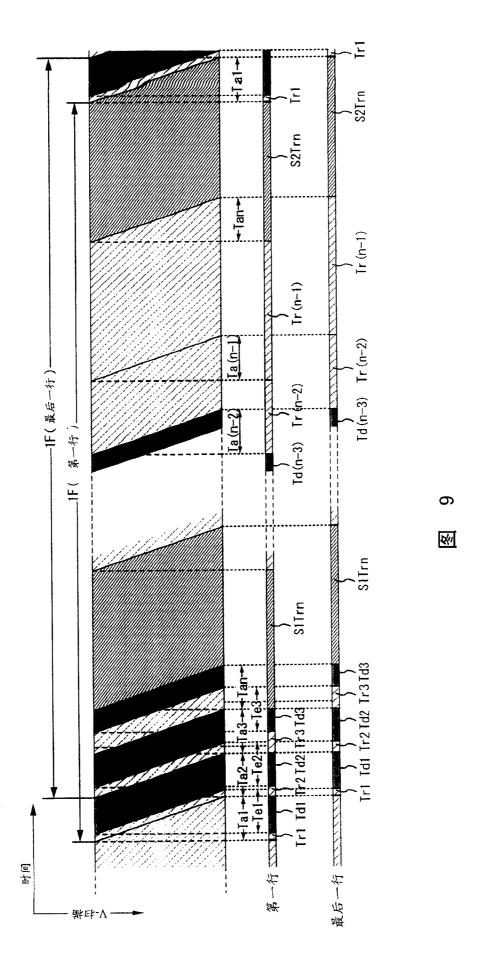

- 图 9 是显示本发明的驱动方法的图;

- 图 10A 和 10B 是驱动器电路的方框图;

- 图 11A 和 11B 是 EL 显示器的顶面图;

- 图 12A 到 12C 分别是 EL 显示器的顶面图和截面图;

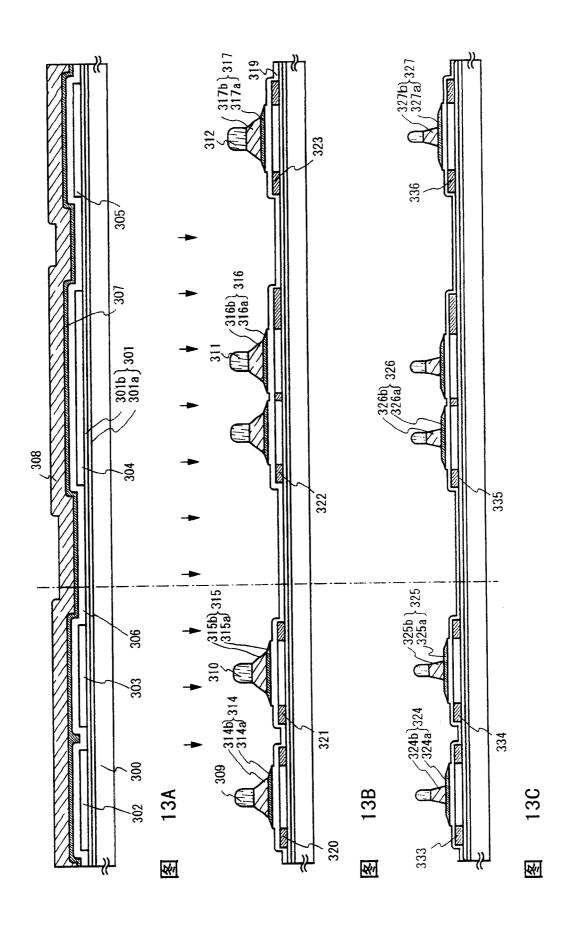

- 图 13A 到 13C 是显示制造 EL 显示器的方法的图;

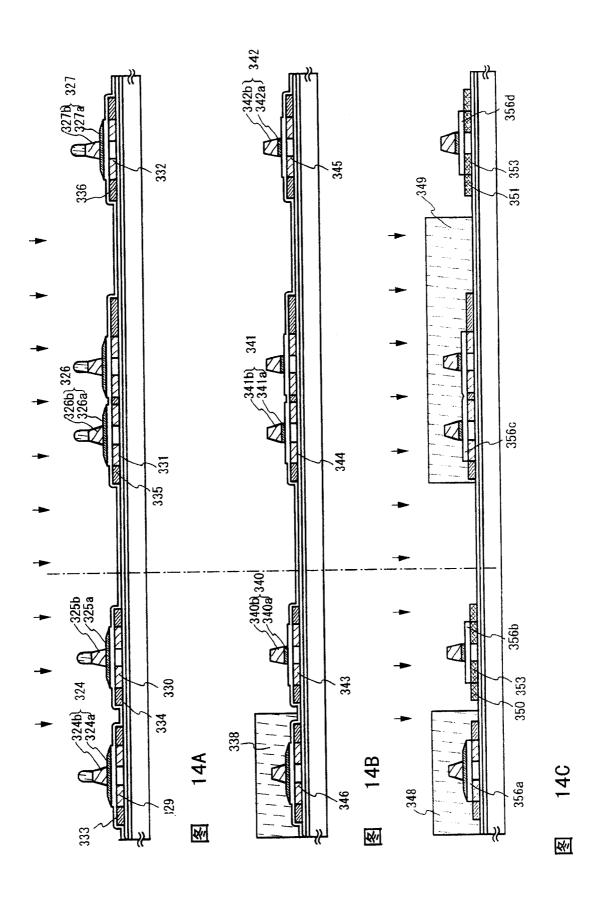

- 图 14A 到 14C 是显示制造 BL 显示器的方法的图;

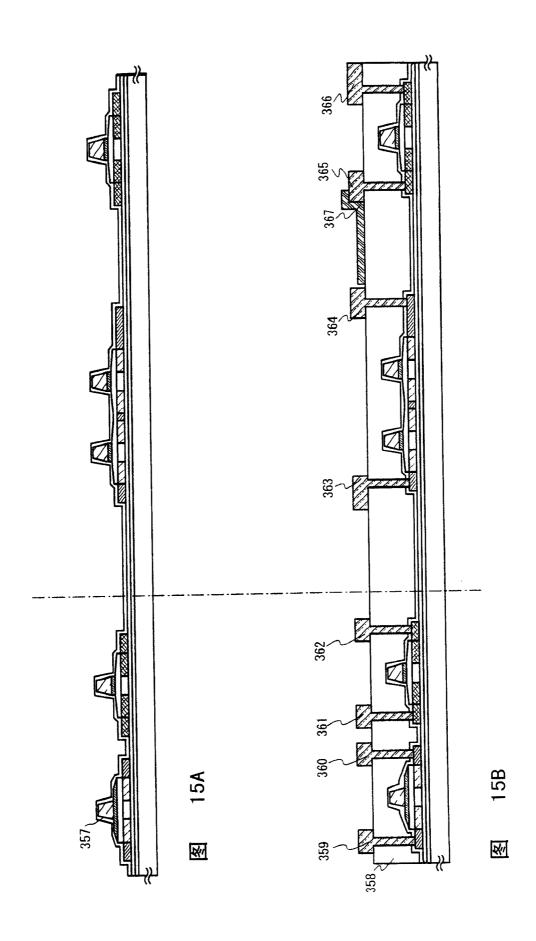

- 图 15A 和 15B 是显示制造 EL 显示器的方法的图;

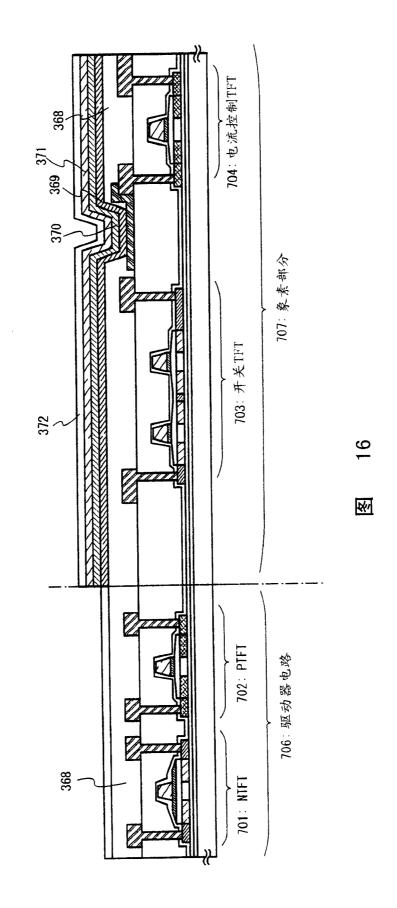

- 图 16 是显示制造 EL 显示器的方法的图;

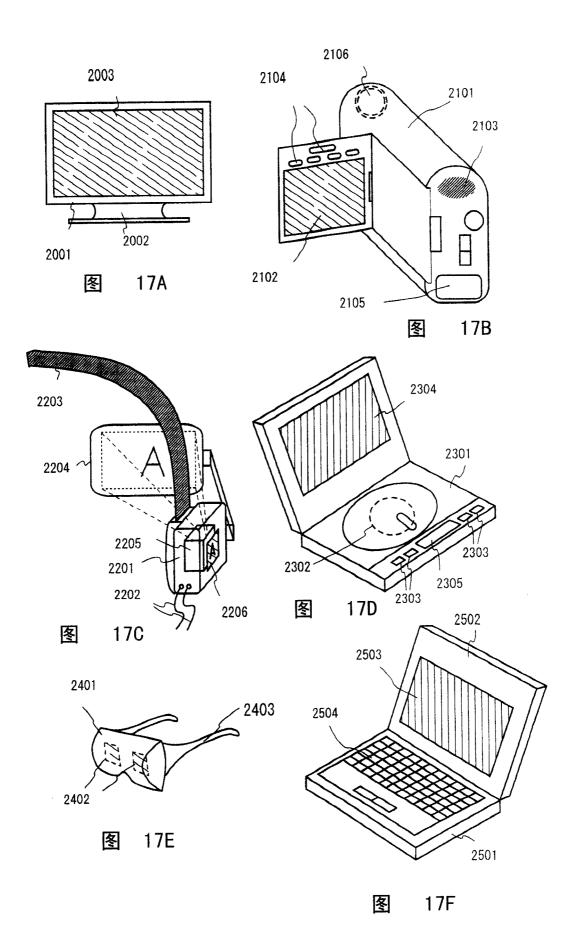

图 17A 到 17F 是具有使用本发明的驱动方法的 EL 显示器的电子设备;

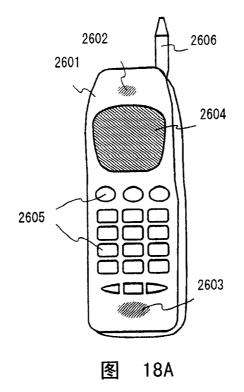

图 18A 和 18B 是具有使用本发明的驱动方法的 EL 显示器的电子设备;

图 19A 和 19B 是分别显示使用传统的驱动方法的 EL 显示器的象素部分,以及显示时间间隔与划分的显示时间间隔的长度的比值的图;以及

图 20A 和 20B 是分别显示使用传统的驱动方法的 EL 显示器的象素部分,以及显示时间间隔与非显示时间间隔的长度的比值的图。

具体实施方式

[实施例模式1]

下面通过图 1A 和 1B 详细说明借助于本发明的时分驱动方法的、显示中等灰度等级的情形。

图 1A 显示显示装置的象素部分,以及在图 1B 上一个帧周期 F 中出现的显示时间间隔 Tr 的长度的比值。

在图 1A 和 1B 上,图象是通过使用能够显示从 1 到 2°的灰度等级的 n 比特数字视频信号而显示的。象素部分的右半部分显示 2°-1+1 个灰度等级,以及左半部分显示 2°-1+1 个灰度等级。

对于使用按照简单的二进制码方法的 n 比特数字视频信号的情形,在一个帧周期内出现 N 个显示时间间隔(显示时间间隔 Tr1 到 Trn)。数字视频信号的第一比特到数字视频信号的第 n 比特分别相应于显示时间间隔 Tr1 到 Trn。

显示时间间隔 Tr1 到 Trn 的长度的比值成为 2°: 2¹: 2²: ...: 2°⁻²: 2°⁻¹。相应于数字视频信号的最高位(在本例中是第 n 比特)的显示时间间隔 Trn 的长度是最长的,以及相应于数字视频信号的最低位(第 一比特)的显示时间间隔 Tr1 的长度是最短的。

对于执行 2<sup>n-1</sup>个等级的显示的情形,在显示时间间隔 Tr 1 到 Tr (n-1)中象素被设置为接通状态以及在显示时间间隔 Tr n 期间象素被设置为关断状态。而且,当执行 2<sup>n+1</sup>+1 个等级的显示时,在显示时间间隔 Tr 1 到 Tr (n-1) 期间象素被设置为关断状态以及在显示时间间

隔Trn期间象素被设置为接通状态。

在本实施例模式中,具有最长时间间隔的显示时间间隔 Tr 然后被划分成两个划分的显示时间间隔 (S1Trn 和 S2Trn)。应当指出,虽然在本实施例模式中,显示时间间隔 Trn 被划分成两个划分的显示时间间隔,但本发明并不限于此。只要有两个或多个划分的显示时间间隔,可以提供任何数目的划分的显示时间间隔,这由驱动电路和象素 TFT 的运行速度限制。

划分的显示时间间隔没有接连地出现。相应于数字视频信号的另一个比特的显示时间间隔总是出现在两个划分的显示时间间隔之间。

应当指出,划分的显示时间间隔的长度不一定是相同的。而且,对于没有被划分的显示时间间隔的次序也不一定设置任何限制。对于设置从相应于最高位的显示时间间隔到相应于最低位的次序也没有限制。

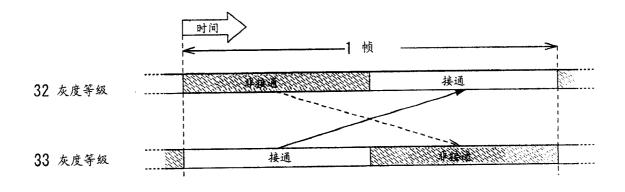

接着,通过图 2A 和 2B 来讨论在本发明的驱动方法中很难看到显示障碍(诸如虚假轮廓线)的理由。

图 2A 显示用于借助于本发明的驱动方法执行显示的显示装置的象素部分,以及图 2B 显示按照象素的接通时间间隔和关断(非接通)时间间隔,在一个帧周期内出现的显示时间间隔和划分的显示时间间隔的长度。

象素部分的右半部分显示 2<sup>n-1</sup>+1 个灰度等级,以及左半部分显示 2<sup>n-1</sup>个灰度等级。

在执行 2<sup>n-1</sup> 个等级的显示的象素部分的部分中,在一个帧周期内的 2<sup>n-1</sup>-1/2<sup>n</sup> 时间间隔中象素被设置为接通状态以及在一个帧周期内的 2<sup>n-1</sup>/2<sup>n</sup> 时间间隔中象素被设置为关断状态。象素处在接通状态时的时间隔和象素处在关断状态时的时间间隔然后交替地出现。

而且,在执行 2<sup>n-1</sup>+1 个等级的显示的象素部分的部分中,在一个帧周期内的 2<sup>n-1</sup>/2<sup>n</sup>时间间隔中象素被设置为接通状态以及在一个帧周期内的 2<sup>n-1</sup>-1/2<sup>n</sup>时间间隔中象素被设置为关断状态。象素处在接通状态时的时间间隔和象素处在关断状态时的时间间隔然后交替地出现。

接通时间间隔和关断时间间隔在一个帧周期内被划分和交替地

出现,以及人的视点轻微地左右和上下移动,所以,完全可能横跨其它的显示时间间隔或划分的显示时间间隔。在这种情形下,即使观察者的视点不断地固定在只是关断的象素上,以及相反地,不断地固定在只是接通的象素上,仍旧可以防止看见虚假轮廓线,因为接连的接通时间间隔或关断时间间隔的长度,比起按照简单的二进制码方法的传统的驱动时更短。

例如,视点被取为从显示 2<sup>n-1</sup>个灰度等级的部分移动到显示 2<sup>n-1</sup>+1个灰度等级的部分,如由虚线表示的。对于本发明的驱动方法,即使当视点位于显示 2<sup>n-1</sup>个灰度等级的部分时象素处在关断状态,以及即使当视点移动到显示 2<sup>n-1</sup>+1个灰度等级的部分时象素处在关断状态,接连地出现的两个关断时间间隔的总和仍变成为短于在传统驱动方法时的这个总和。所以,可以避免由人的眼睛看见在一个帧周期内象素总是处在关断状态。

反之,例如,视点被取为从显示 2<sup>n-1</sup>+1 个灰度等级的部分移动到显示 2<sup>n-1</sup>个灰度等级的部分。对于本发明的驱动方法,即使当视点位于显示 2<sup>n-1</sup>+1 个灰度等级的部分时象素处在接通状态,以及即使当视点移动到显示 2<sup>n-1</sup> 个灰度等级的部分时象素处在接通状态,接连地出现的两个接通时间间隔的总和仍变成为短于在传统驱动方法时的这个总和。所以,可以避免由人的眼睛看见在一个帧周期内象素总是处在接通状态。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

## [实施例模式 2]

在实施例模式 1 中,只有相应于数字视频信号的最高位的显示时间隔被划分成划分的显示时间间隔。在实施例模式 2 中,显示了分别把相应于从最高位接连地按次序被选择的、数字视频信号的多个较高位的显示时间间隔划分成多个划分的显示时间间隔的例子。应当指出,在本技术说明中,术语较高位相应于被划分成划分的显示时间隔的显示时间间隔,以及术语较低位相应于不被划分成划分的显示时间间隔的显示时间间隔。

现在通过图 3 来说明实施例模式 2 的驱动方法。图 3 显示当使用 n 比特数字视频信号来执行时分灰度等级显示时,在象素部分中在一

个帧周期 F 内出现的显示时间间隔 Tr 和划分的显示时间间隔 STr 的长度的比值。

在实施例模式 2 中,显示时间间隔 Ttn 和显示时间间隔 Tr (n-1)被取为相应于数字视频信号的较高位的显示时间间隔。应当指出,在实施例模式 2 中,虽然驱动方法被显示为其中两个比特,即第 n 号比特和第 (n-1)号比特,被取为较高位,但本发明并不限于此。较高位的数目可以设置为 1,当然它也可被设置为 2 或更多。然而,所有的较高位必须是接连的,以及是从最高位按次序的。例如,在三个较高位的情形下,数字视频信号的第 n 号比特,第 (n-1)号比特,和第 (n-2)号比特相应于较高位。

显示时间间隔 Tr1 到 Trn 的长度的比值成为  $2^{0}:2^{1}:2^{2}:...:2^{n-2}:2^{n-1}$ .

当执行 2<sup>n-1</sup> 个等级的显示的情形时,在显示时间间隔 Tr1 到 Tr (n-1) 中象素被设置为接通状态以及在显示时间间隔 Trn 期间象素被设置为关断状态。而且,当执行 2<sup>n+1</sup>+1 个等级的显示时,在显示时间间隔 Tr1 到 Tr (n-1) 期间象素被设置为关断状态以及在显示时间间隔 Trn 期间象素被设置为接通状态。

在实施例模式 2 中,相应于较高位的显示时间间隔,即实施例模式 2 中的显示时间间隔 Trn 和显示时间间隔 Tr (n-1),分别被划分成三个划分的显示时间间隔 (S1Trn, S2Trn 和 S3Trn)和两个划分的显示时间间隔 (S1Tr (n-1)和 S2Tr (n-1))。应当指出,虽然在实施例模式 2 中,形成显示时间间隔 Trn 的三个划分段和显示时间间隔 Tr (n-1)的两个划分段,但本发明并不限于此。相应于较高位的显示时间间隔的划分段的数目不限于这些数值,以及只要该数目等于或大于二,有可能形成任何数目的划分的显示时间间隔,只由驱动器电路和象素 TFT 的运行速度限制。

相应于数字视频信号的同一个比特的、划分的显示时间间隔并不接连地出现。相应于数字视频信号的另一个比特的子帧时间间隔或显示时间间隔总是出现在两个划分的显示时间间隔之间。

应当指出,相应于数字视频信号的同一个比特的、划分的显示时间间隔的长度不一定都是相同的。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱

动中很显著的、诸如虚假轮廓线那样的显示的障碍。

# [实施例模式 3]

在实施例模式 3 中说明其中显示时间间隔根据固定的法则被划分成多个划分的显示时间间隔的驱动方法。为了简化说明,在实施例模式 3 中说明使用 8 比特数字视频信号执行灰度等级显示的情形。

相应于数字视频信号的第 n 号比特 (其中 n=1 到 8) 的显示时间间隔的长度被取为 Ln,以及显示时间间隔的划分段的数目被取为  $m_n$ 。如果在这时,对于其中  $m_n=1$ , 2, 3, 4, ...的情形,找到  $Ln/m_n$ 3的数值,则结果为下面的表 1 所示。

[表 1]

| ~ 1]                           |                          |                          |                   |                          |  |  |

|--------------------------------|--------------------------|--------------------------|-------------------|--------------------------|--|--|

| Ln/m <sub>n</sub> <sup>3</sup> | <b>m</b> <sub>n</sub> =1 | <b>m</b> <sub>n</sub> =2 | m <sub>n</sub> =3 | <b>m</b> <sub>n</sub> =4 |  |  |

| L8=128                         | 128                      | 16                       | 4. 74             | 2                        |  |  |

| L7=64                          | 64                       | 8                        | 2. 37             | 1                        |  |  |

| L6=32                          | 32                       | 4                        | 1.18              |                          |  |  |

| L5=16                          | 16                       | 2                        | 0. 59             |                          |  |  |

| L4=8                           | 8                        | 1                        |                   |                          |  |  |

| L3=4                           | 4                        |                          |                   |                          |  |  |

| L2=2                           | 2                        |                          |                   |                          |  |  |

| L1=1                           | 1                        |                          |                   |                          |  |  |

在实施例模式 3 中,在一个帧周期内形成的显示时间间隔和划分的显示时间间隔的总的数目被设置为 13。最好是所有的显示时间间隔和划分的显示时间间隔的长度尽可能相等。只要所有的显示时间间隔和划分的显示时间间隔的长度是相等的,就可有效地防止看见诸如虚假轮廓线那样的显示的障碍。所以,每个显示时间间隔的划分段的数目被选择成使得 Ln/m³的数值尽可能相等以及使得在一个帧周期内形成的显示时间间隔和划分的显示时间间隔的总的数目是 13。而且,最好是相应于较高位的显示时间间隔从具有较长的长度的显示时间隔中按次序被划分。在实施例模式 3 中,划分是如表 2 中画底线的数值所显示的那样进行的。

| 「表 | 2] |

|----|----|

|    | ~  |

| Ln/m <sub>n</sub> <sup>3</sup> | m <sub>n</sub> =1 | m <sub>n</sub> =2 | <b>m</b> <sub>n</sub> =3 | <b>m</b> <sub>n</sub> =4 |

|--------------------------------|-------------------|-------------------|--------------------------|--------------------------|

| L8=128                         | 128               | 16                | 4.74                     | 2                        |

| L7=64                          | 64                | 8                 | 2. 37                    | 1                        |

| L6=32                          | 32                | 4                 | 1.18                     |                          |

| L5=16                          | 16                | <u>2</u>          | 0. 59                    |                          |

| L4=8                           | 8                 | 1                 |                          |                          |

| L3=4                           | 4                 |                   |                          |                          |

| L2=2                           | <u>2</u>          |                   |                          |                          |

| L1=1                           | 1                 |                   |                          |                          |

即,显示时间间隔 Tr1 到 Tr4 不被划分,显示时间间隔 Tr5 到 Tr7 被划分成两段,以及显示时间间隔 Tr8 被划分成三段。而且,在一个时间帧中,相应于数字视频信号的同一个比特的显示时间间隔被驱动,以免接连地出现。

设计者有可能适当地选择显示时间间隔的划分段的数目,但最好是该数目按照在显示装置的驱动速度与图象所需要的显示质量之间的平衡来确定。

而且,最好是相应于数字视频信号的同一个比特的划分的显示时间间隔的长度是相同的,但本发明并不限于此。划分的显示时间间隔的长度并不总是必须相等的。

应当指出,也有可能根据条件通过使用 Ln/mn² 作为对于上述的 Ln/mn³ 的替换物,有效地阻止看见虚假轮廓线。设计者有可能适当地 选择用作为决定驱动方法时的标准的那个数值。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

下面说明本发明的实施例。

# 「实施例 1]

在实施例 1 中,说明使用在每个象素上形成的两个薄膜晶体管 (TFT)的、用于控制有机 EL 元件发射的光的 EL 显示装置的象素部分的结构,以及驱动方法。

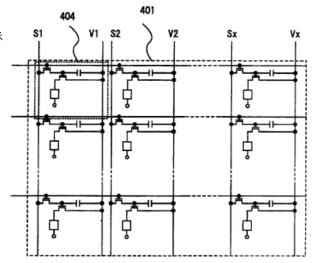

图 4 上显示实施例 1 的 EL 显示装置的象素部分 401 的放大图。

源极信号线 S1 到 Sx, 电源线 V1 到 Vx, 以及栅极信号线 G1 到 Gy 被形成在象素部分 401 中。

在实施例 1 中,具有源极信号线 S1 到 Sx 之一,电源线 V1 到 Vx 之一,以及栅极信号线 G1 到 Gy 之一的区域表示象素 404。多个象素 404 以矩阵形式被排列在象素部分 401 中。

图 5 上显示象素 404 的放大图。图 5 上参考数字 405 表示开关 TFT。开关 TFT 405 的栅极被连接到栅极信号线 G (栅极信号线 G1 到 Gy 中的任一条)。开关 TFT 405 的源极区和漏极区被连接到源极信号线 S (源极信号线 S1 到 Sx 中的任一条),以及其它区被连接到 EL 驱动器 TFT 406 的栅极和每个象素的电容 408。

电容 408 被形成来当开关 TFT 405 处在非选择状态(关断状态)时,存储 EL 驱动器 TFT 406 的栅极电压(在栅极与源极区之间的电位差)。应当指出,虽然在实施例 1 中显示其中形成电容 408 的结构,但本发明并不限于这种结构,以及也可以使用其中不形成电容 408 的结构。

而且, EL 驱动器 TFT 406 的源极区和漏极区之一被连接到电源线 V(电源线 V1 到 Vx 中的任一条),而其它区被连接到有机 EL 元件 407。 电源线 V1 被连接到电容 408。

有机 EL 元件 407 包括正极,负极,以及被形成在正极与负极之间的 EL 层。如果正极被连接到 EL 驱动器 TFT 406 的源极区或漏极区,则正极成为象素电极以及负极成为相对的电极。反之,如果负极被连接到 EL 驱动器 TFT 406 的源极区或漏极区,则负极成为象素电极以及正极成为相对的电极。

一个相反的电位被加到有机 EL 元件 407 的相对的电极。而且,电源电位被加到电源线 V。电源电位和相反的电位被由外部 IC 等形成的电源加到使用本发明的驱动方法的 EL 显示装置。电源线的电源电位被保持在一个电位上,它与相对电极有这样一个电位差,以使得当电源电位被施加到有机 EL 元件的象素电极时有机 EL 元件发光。

对于当前典型地有机 EL 显示装置其中象素的每个面积的发光量是 200cd/m2 的情形, 几 mA/cm2 的电流密度对于象素部分是必须的。所以,如果屏幕尺寸变为很大,则很难通过一个开关控制从在 IC 中形成的电源施加的电位的大小。在实施例 1 中,电源电位和相反电位

常常保持为恒定的电平,所以不必通过使用一个开关来控制从在 IC 中形成的电源施加的电位的大小。这在实现更大尺寸的屏幕板时是有用的。

开关 TFT 405 和 EL 驱动器 TFT 406 可以通过使用 n 沟道 TFT 或 p 沟道 TFT 来构成。然而,如果 EL 驱动器 TFT 406 的源极区或漏极区被连接到有机 EL 元件 407 的正极,则最好是 EL 驱动器 TFT 406 是 p 沟道 TFT。而且,如果 EL 驱动器 TFT 406 的源极区或漏极区被连接到有机 EL 元件 407 的负极,则最好是 EL 驱动器 TFT 406 是 n 沟道 TFT。

除了单栅极结构以外, 开关 TFT 405 与 EL 驱动器 TFT 406 也可以具有多栅极结构, 诸如双栅极结构或三栅极结构。

接着,通过图 6 说明驱动具有上述结构的、本发明的 EL 显示装置的方法。在图 6 上,水平轴表示时间,而垂直轴表示选择的栅极信号线的安排。

首先,栅极信号线 G1 被从栅极信号线驱动器电路输入到栅极信号线 G1 的栅极信号选择。应当指出,在本技术说明中,所谓栅极信号线被选择,表示被连接到栅极信号线的所有的开关 TFT 405 都被设置为接通状态。换句话说,被连接到栅极信号线 G1 的所有的象素(第一行象素)的开关 TFT 405 处在接通状态。

数字视频信号的第一比特同时从源极信号线驱动器电路被输入到源极信号线 S1 到 Sx。数字视频信号通过开关 TFT 405 被输入到 EL 驱动器 TFT 406 的栅极。

在本实施例中,对于数字视频信号具有"0"信息的情形,EL驱动器TFT 406 被设置为关断状态。所以电源电位没有被施加到有机EL元件 407 的象素电极。结果,其中输入具有"0"信息的数字视频信号的象素的有机EL元件 407 不发光。

应当指出,所谓数字视频信号被输入到象素,在本技术说明中, 表示数字视频信号被输入到象素的有机 EL 驱动器 TFT 的栅极。

反之,如果在数字视频信号中包含"1"信息,则 EL 驱动器 TFT 406 被设置为接通状态。所以电源电位被施加到有机 EL 元件 407 的象素电极。结果,其中输入具有"1"信息的数字视频信号的象素的有机 EL 元件 407 发光。

有机 EL 元件 407 因此被被设置为发光或不发光状态,以及第一行象素实行显示。

在完成栅极信号线 G1 的选择的同时,栅极信号线 G2 被栅极信号选择。被连接到栅极信号线 G2 的所有的象素的开关 TFT 405 然后被设置为接通状态,以及数字视频信号的第一比特从源极信号线 S1 到Sx 被输入到第二行象素。

所有的栅极信号线 G1 到 Gy 然后按次序被选择。直至所有的栅极信号线 G1 到 Gy 被选择以及数字视频信号的第一比特被输入到所有行的象素为止的时间间隔,被称为写入周期 Ta1。

应当指出,从写入周期 Ta1 的开始点直至下一个写入周期(在本例中是 Ta2)的开始点出现为止的时间间隔,被称为显示时间间隔 Tr1。

当显示时间间隔 Tr1 完成时写入周期 Ta2 开始,以及类似于写入周期 Ta1 的情形,所有的栅极信号线按次序被选择。数字视频信号的第二比特被输入到所有的象素。其中数字视频信号的第二比特被输入到所有行的象素的时间间隔,被称为写入周期 Ta2。

从写入周期 Ta2 的开始点直至下一个写入周期(在本例中是写入周期 Tan)的开始点出现为止的时间间隔,被称为显示时间间隔 Tr2。

当显示时间间隔 Tr2 完成时写入周期 Ta2 开始。类似于写入周期 Ta1 的情形,所有的栅极信号线按次序被选择,以及数字视频信号的第 n 号比特被输入到所有的象素。其中数字视频信号的第 n 号比特被输入到所有行的象素的时间间隔,被称为写入周期 Tan。

从写入周期 Tan 的开始点直至下一个写入周期(在本例中是写入周期 Ta3)的开始点出现为止的时间间隔,被称为划分的显示时间间隔 S1Trn。

当显示时间间隔 S1Trn 完成时显示时间间隔 Tr3, Tr4, ..., Tr (n-1)按次序出现,以及数字视频信号的相应的比特在各个时间间隔中同样地被输入到象素。

当显示时间间隔 Tr (n-1) 完成时写入周期 Tan 开始。类似于写入周期 Tal 的情形,所有的栅极信号线按次序被选择,以及数字视频信号的第 n 号比特被输入到所有的象素。其中数字视频信号的第 n 号比特被输入到所有行的象素的时间间隔,被称为写入周期 Tan。

从写入周期 Tan 的开始点直至下一个写入周期(在本例中是下一个帧周期的写入周期 Ta1)的开始点出现为止的时间间隔,被称为划分的显示时间间隔 S2Trn。

应当指出,被组合的、划分的显示时间间隔 S1Trn 和划分的显示时间间隔 S2Tr,被称为显示时间间隔 Trn。

当所有的显示时间间隔 Tr1 到 Trn 完成时,可以显示一个图象。用于显示一个图象的时间间隔,在本发明的驱动方法中,被称为一个帧周期 F。当一个帧周期完成时,下一个帧周期开始。然后,写入周期 Ta1 再次出现,以及上述的操作重复进行。

在实施例 1 中,所有写入周期的长度的总和必须短于一个帧周期 , 以 及 显 示 时 间 间 隔 的 长 度 的 比 值 被 设 置 为  $Tr1:Tr2:Tr3:...:Tr(n-1):Trn= 2^0:2^1:2^2:...:2^{n-2}:2^{n-1}$ 。 在灰度等级 1 到  $2^n$ 之间的、想要的灰度等级显示可以通过组合显示时间间隔而被执行。

在一个帧周期期间在象素中显示的灰度等级是通过找到在帧周期内象素的有机 EL 单元发光时的显示时间间隔的长度的总和而被确定的。例如,当 n=8 时,如果在所有的显示时间间隔期间象素发光的情形下的亮度被取为 100%,则 1%的亮度可被表示为其中只在 Tr1 和 Tr2 期间象素发光的情形,以及如果在 Tr3, Tr5 和 Tr8 中象素发光,则可以表示 60%的亮度。

而且,显示时间间隔 Tr1 到 Trn 可以按任何次序出现。例如,有可能显示时间间隔在一个帧周期内在 Tr1 后按 Tr3, Tr5, Tr2, ...的次序出现。然而,重要的是,相应于数字视频信号的相同的第 n 号比特的划分的显示时间间隔 S1Trn 和划分的显示时间间隔 S2Trn 并不接连地出现。

应当指出,虽然电源电位和相反电位的大小在实施例 1 中总是固定的,但本发明并不限于此。电源电位和相反电极的电位的大小,在写入周期内被保持为相同的。以及电源电位和相反电极的电位可能总是具有电位差,这样,当电源电位在其中写入周期完成的同时被施加到有机 EL 元件的象素电极上时,有机 EL 元件发光。

在这种情形下,写入周期不包括在显示时间间隔内。显示时间间隔相应于从写入周期完成直至下一个写入周期的开始点出现为止的

时间间隔。例如,显示时间间隔 Tr1 是从写入周期 Ta1 完成直至下一个写入周期在写入周期 Ta1 后出现(例如, Ta2)为止的时间间隔。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

应当指出,虽然在实施例 1 中,显示时间间隔 Trn 被划分成两段,即划分的显示时间间隔 S1Trn 和 S2Trn,但实施例 1 并不限于此。可以有一个显示时间间隔被进行划分,或有多个显示时间间隔被进行划分。然而,最好是,它们从相应于较高位的显示时间间隔(即,具有较长的长度的显示时间间隔)按次序被划分。而且,设计者有可能适当地选择显示时间间隔的划分段的数目,但最好是划分段的数目按照在显示装置的驱动速度与图象的需要的显示质量之间的平衡来确定。

而且,虽然最好是相应于数字视频信号的同一个比特的划分的显示时间间隔的长度是相同的,但本发明并不限于此。划分的显示时间间隔的长度并不总是必须相等的。

## [实施例 2]

在本实施例中,通过使用被提供在每个象素中的三个薄膜晶体管来说明控制有机 EL 元件的发光的 EL 显示装置的象素部分的结构和驱动方法。

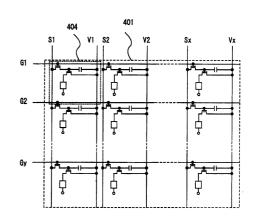

在图 7 上,以放大的尺度显示本发明的 EL 显示装置的象素部分501。这个象素部分501 配备有:源极信号线(S1 到 Sx);电流源线(V1 到 Vx);写栅极信号线(或第一栅极信号线)(Ga1 到 Gay);以及擦除栅极信号线(或第二栅极信号线)(Ge1 到 Gey)。

象素 505 是配备有源极信号线 (S1 到 Sx) 之一, 电流源线 (V1 到 Vx)之一, 写栅极信号线 (Ga1 到 Gay)之一和擦除栅极信号线 (Ge1 到 Gey) 之一的区域。在象素部分 501 中, 有多个象素 505 以矩阵形式排列在其中。

在图 8 上,以放大的尺度显示象素 505。在图 8 上,数字 507 表示开关 TFT。开关 TFT 507 与写栅极信号线 Ga (Ga1 到 Gay 中间的一条线)相连接。开关 TFT 507 的源极区和漏极区中的一个区与源极信号线 S(S1 到 Sx 中间的一条线)相连接,而另一个区与 EL 驱动器 TFT 508 的栅极、每个象素拥有的电容 512 和擦除 TFT 509 的源极区或漏

极区相连接。

电容 512 用来当开关 TFT 505 处在未选择状态(或关断状态)时,保持 EL 驱动器 TFT 508 的栅极电压。在本实施例中,显示了具有电容 512 的结构,但本发明并不限于此,而是可被修改为不具有电容 512 的结构。

另一方面, EL 驱动器 TFT 508 的源极区和漏极区中的一个区与电流源线 V(V1 到 Vx 中间的一条线) 相连接, 而另一个区与有机 EL 元件 510 相连接。电流源线 V与电容 512 相连接。

另一方面, 擦除 TFT 509 的源极区和漏极区中, 不与开关 TFT 507 的源极区或漏极区相连接的一个区与电流源线 V 相连接。而且, 擦除 TFT 509 的栅极与擦除栅极信号线 Ge (Ge1 到 Gex 中的一条线) 相连接。

有机 EL 元件 510 包括正极、负极、和在正极与负极之间形成的 EL 层。在正极与 EL 驱动器 TFT 508 的源极区或漏极区相连接的情况下,正极起到象素电极的作用,而负极起相对的电极的作用。反之,在负极与 EL 驱动器 TFT 508 的源极区或漏极区相连接的情况下,负极起到象素电极的作用,而正极起相对的电极的作用。

有机 EL 元件 510 在它的相对的电极上被加上相反的电位。而且,在相反电位和电源电位之间的电位差总是保持在这样的一个电平,以使得当电源电位被加到象素电极时有机 EL 元件发光。这些电源电位和相反电位都是由外部 IC 等通过使用本发明的驱动方法在 EL显示装置中提供的电源加上的。这里,相反电位的电源将特别地称为"相反电源 511"。

在本阶段典型的 EL 装置需要具有每个象素单元面积几个 mA/cm² 的电流,其中每个象素发光面积的发光量是 200cd/m²。所以,当屏幕尺寸变为更大时,就更难用开关控制从 IC 的电源加上的电位电平。在本发明中,电源电位和相反电位总是保持为常数,以及从 IC 的电源加上的电位电平不需要用开关控制,这样,本发明对于实现具有更大的屏幕尺寸的显示板是有用的。

要被使用的开关 TFT 507、EL 驱动器 TFT 508 和擦除 TFT 509 可以是n沟道 TFT 或p沟道 TFT。另一方面,开关 TFT 507、EL 驱动器 TFT 508 和擦除 TFT 509 不应当被限于具有单栅极结构,而是可以

具有多栅极结构,诸如双栅极结构或三栅极结构。

下面将参照图 9 描述,如图所示的,按照本发明的 EL 显示装置的驱动方法。水平轴表示时间,而垂直轴表示栅极信号线的位置。

首先,显示时间间隔 Tr1 从第一行象素开始,写栅极信号线 Ga1 被从写栅极信号线驱动器电路(未示出)输入到写栅极信号线 Ga1 的写栅极信号(或第一栅极信号)选择。以及被连接到写栅极信号线 Ga1 的所有的象素(即,第一行象素)的开关 TFT 507 都被接通(0N)。

与此同时地,第一比特的数字视频信号,当从源极信号线驱动器 电路 502 被输入到源极信号线 S1 到 Sx 时,通过开关 TFT 507 被输入 到 EL 驱动器 TFT 508。

数字视频信号具有信息"0"或"1", 数字视频信号"0"或"1"中的一个具有"高"电平, 而另一个具有"低"电平。

在本实施例中,在数字视频信号具有信息"0"的情况下,EL驱动器 TFT 508 被关断(OFF)。所以,电源电位不加到有机 EL 元件510 的象素电极。结果,被输入具有信息"0"的数字视频信号的有机EL 元件510 不发光。

反之,在数字视频信号具有信息"1"的情况下,EL 驱动器 TFT 508 被接通(ON)。所以,电源电位加到有机 EL 元件 510 的象素电极。结果,被输入具有信息"1"的数字视频信号的有机 EL 元件 510 发光。

在本实施例中,在数字视频信号具有信息"0"的情况下,EL驱动器TFT 508被关断(0FF)。在数字视频信号具有信息"1"的情况下,EL驱动器TFT 508被接通(ON)。然而,本发明并不限于这种结构。在数字视频信号具有信息"0"的情况下,EL驱动器TFT 508可以被接通(ON),以及在数字视频信号具有信息"1"的情况下,EL驱动器TFT 508可以被关断(OFF)。

因此,与数字视频信号输入到第一行象素的同时,有机 EL 元件510 发光或不发光,以及第一行象素进行显示。

在写栅极信号线 Ga1 的选择结束的情况下,写栅极信号线 Ga2 由写栅极信号被选择。然后,与写栅极信号线 Ga2 相连接的所有的象素的开关 TFT 507 都被接通,这样,第一比特的数字视频信号从源极信号线 S1 到 Sx 被输入到第二行象素。

然后,所有的写栅极信号线 Gal 到 Gay 被顺序地选择,以使得第

一比特的数字视频信号被输入到所有的象素。直至第一比特的数字视频信号被输入到所有的象素为止的时间间隔是写周期 Ta1。在每行象素中, 开始写周期 Ta1 的时间具有一个时间差。

而且, 其间象素正在显示的时间间隔被称为显示时间间隔 Tr。例如, 在第一行象素的情况下, 显示时间间隔 Tr 与写栅极信号 Ga1 被选择的时间同时开始。开始每行的显示时间间隔的时间是不同的。

另一方面, 在第一比特的数字视频信号被输入到所有的象素之前, 即写周期 Ta1 结束之前, 擦除栅极信号线 Ge1 与第一比特的数字视频信号输入到象素并行地, 由擦除栅极信号(或第二栅极信号)被选择, 该擦除栅极信号是从擦除栅极信号线驱动器电路(未示出)被输入到擦除栅极信号线 Ge1 的。然后, 与擦除栅极信号线 Ge1 相连接的所有的象素(即, 第一行象素)的擦除 TFT 509 被接通 ON。然后, 电流源线 V1 到 Vx 的电源电位通过擦除 TFT 509 被加到 EL 驱动器 TFT 508 的栅极。

当电源电位被加到 EL 驱动器 TFT 508 的栅极时,EL 驱动器 TFT 508 的栅极和源极区取同一个电位,这样栅极电压是 0 伏。EL 驱动器 TFT 508 被关断 0FF。具体地,在写栅极信号线 Ga1 由写栅极信号选择后被 EL 驱动器 TFT 508 的栅极保持的数字视频信号,通过把电源电位加到 EL 驱动器 TFT 的栅极而被擦除。结果,电源电位不加到有机 EL 元件 510 的象素电极,以及第一行象素所拥有的有机 EL 元件510 不发光,这样,第一行象素不显示。

而且, 当擦除栅极信号线 De1 的选择结束时, 擦除栅极信号线 Ge2 被选择, 以使得与擦除栅极信号线 Ge2 相连接的所有的象素的擦除 TFT 509 被接通 ON、然后电流源线 V1 到 Vx 的电源电位通过擦除 TFT 509 加到 EL 驱动器 TFT 508 的栅极。当电源电位被加到 EL 驱动器 TFT 508 的栅极时, 这个 EL 驱动器 TFT 508 被关断 OFF。电源电位不加到有机 EL 元件 510 的象素电极。结果, 第二行象素所拥有的有机 EL 元件 510 不发光, 这样, 建立了其中第二行象素不发光的状态。

然后,擦除栅极信号被顺序地输入到所有的擦除栅极信号线。直至所有的擦除栅极信号线 Ge1Gey 被选择以使得被所有的象素保持的数字视频信号被擦除为止的时间间隔是"擦除周期 Te1"。在每行象素中,开始擦除周期 Te1 的时间具有一个时间差。

而且,其间象素不显示的时间间隔被称为非显示时间间隔 Td。例如,对于第一行象素,当擦除栅极信号 Ge1 被选择时同时结束显示时间间隔 Tr1,进入非显示时间间隔。像显示时间间隔那样,开始每行的非显示时间间隔的时间是不同的。

另一方面,在由所有的象素保持的第一比特的数字视频信号被擦除之前,即,擦除周期 Te1 结束之前,写栅极信号线 Ga1 再次由写栅极信号与由象素保持的第一比特的数字视频信号的擦除并行地被选择。然后,第二比特的数字视频信号被输入到第一行象素。结果,第一行象素再次显示,这样,非显示时间间隔 Td1 结束。

从写周期 Ta1 开始直至下一次将存在的写周期(在本例中是写周期 Ta2)为止的时间间隔被称为显示时间间隔 Tr1。

接着,显示时间间隔 Tr2 开始进到写周期 Ta2。同样地,所有的写栅极信号线被顺序地选择,以及第二比特的数字视频信号被输入到所有的象素。

另一方面,在第二比特的数字视频信号被输入到所有的象素之前,即,写周期 Ta2 结束之前,擦除栅极信号线 Ge1 由擦除栅极信号与第二比特的数字视频信号输入到象素并行地被选择。所以,第一行象素所拥有的 EL 元件不发光,这样,第一行象素不显示。所以,显示时间间隔 Tr2 在第一行象素中结束,进到非显示时间间隔 Td2。

然后所有的擦除栅极信号线 Ge2 到 Gey 被顺序地选择,以使得在所有象素中保存的第二比特的数字视频信号被擦除。直至由所有象素保存的第二比特的数字视频信号被擦除为止的时间间隔被称为"擦除周期 Te2"。

接着,显示时间间隔 Tr2 被结束,进到显示时间间隔 Tr3。同样地,所有的写栅极信号线被顺序地选择,以及第三比特的数字视频信号被输入到所有的象素。

另一方面,在第三比特的数字视频信号被输入到所有的象素之前,即,在写周期 Ta3 结束之前,擦除栅极信号线 Ge1 由擦除栅极信号与第三比特的数字视频信号输入到象素并行地被选择。所以,第一行象素所拥有的有机 EL 元件不发光,这样,第一行象素不显示。所以,显示时间间隔 Tr3 在第一行象素中结束,进到非显示时间间隔 Td3。

然后所有的擦除栅极信号线 Ge2 到 Gey 被顺序地选择,以使得在所有象素中保存的第三比特的数字视频信号被擦除。直至由所有象素保存的第三比特的数字视频信号被擦除为止的时间间隔被称为"擦除周期 Te3"。

接着,显示时间间隔 Tr3 被结束,进到划分的显示时间间隔 S1Trn。同样地,所有的写栅极信号线被顺序地选择,这样,第 n 比特的数字视频信号被输入到所有的象素。

另一方面, 在第 n 比特的数字视频信号被输入到所有的象素之前, 即, 写周期 Tan 结束之前, 擦除栅极信号线 Ge1 由擦除栅极信号与把第 n 比特的数字视频信号输入到象素并行地被选择。所以, 第一行象素所拥有的有机 EL 元件不发光, 这样, 第一行象素不显示。所以, 显示时间间隔 Trn 在第一行象素中结束, 进到非显示时间间隔 Td3。

然后所有的擦除栅极信号线 Ge2 到 Gey 被顺序地选择,以使得在所有象素中保存的第 n 比特的数字视频信号被擦除。直至由所有象素保存的第 n 比特的数字视频信号被擦除为止的时间间隔被称为"擦除周期 Ten"。

上述的动作重复进行,直至第 m 比特的数字视频信号被输入到象素为止,这样,显示时间间隔 Tr、划分的显示时间间隔 STr 和非显示时间间隔 Td 重复出现。显示时间间隔 Tr1 从写周期 Ta1 的开始点继续到擦除周期 Te1 的开始点。另一方面,非显示时间间隔 Tr1 从擦除周期 Te1 的开始点继续到下一次出现的写周期(即,本例中的写周期 Ta2)的开始点。而且,显示时间间隔 Tr2, Tr3, ...,和 Tr (m-1)以及非显示时间间隔 Td2, Td3, ...,和 Td (m-1),像显示时间间隔 Tr1 和非显示时间间隔 Td1 那样,由写周期 Ta1, Ta2, ...,和 Tam 以及擦除周期 Te1, Te2, ...,和 Te (m-1)各个确定。

为了描述方便起见,图 9 举例说明 m=n-2 的情形。然而,当然,本发明并不限于此。在本发明中,对于 m,可以任意选择从 1 到 n 的数值。

当第 m[第 (n-2), (以下的括号的情形是对于 m=n-2)]比特的数字视频信号被输入到第一行象素时,这些第一行象素在显示时间间隔 Trm[n-2]内显示。然后,第 m[n-2]比特的数字视频信号内保持在象

素中, 直至下一个比特的数字视频信号被输入为止。

当显示时间间隔 Tr(m+1)(n-1)开始时和当第(m+1)[n-1]比特的数字视频信号然后被输入到第一行象素时,在象素中保持的 m[n-2]的数字视频信号被重新写到第(m+1)[n-1]比特的数字视频信号中。然后,第一行象素在显示时间间隔 Tr(m+1)[n-1]内被显示。第(m+1)[n-1]比特的数字视频信号内保持在象素中,直至下一个比特的数字视频信号被输入为止。

当划分的显示时间间隔 S1Trn 开始时和当第 n 比特的数字视频信号然后被输入到第一行象素时,在象素中保持的 (m+1) [n-1] 的数字视频信号被重新写到第 n 比特的数字视频信号中。然后,第一行象素在显示时间间隔 Trn 内被显示。第 n 比特的数字视频信号内保持在象素中,直至下一个比特的数字视频信号被输入为止。

显示时间间隔 Trm[n-2],...,和 Trn 从写周期 Tam[n-2],...,和 Tan 的开始点继续到下一次出现的写周期的开始点。

当所有的显示时间间隔 Tr1 到 Trn 结束时, 一个图象可被显示。 在本发明中, 要被显示的一个图象的时间间隔被称为"一个帧周期 (F)"。

而且,在一个帧周期结束后,写栅极信号线 Ga1 再次由写栅极信号选择。然后,第一比特的数字视频信号被输入到在显示时间间隔 Tr1 时再次取的第一行象素。然后,上述的动作再次重复进行。

在实施例 2 的驱动方法中,重要的是,所有的写入周期的长度的总和短于一个帧周期。而且,显示时间间隔 Trn 用实施例 2 的驱动方法被划分成两个划分的显示时间间隔 S1Trn 和 S2Trn。所以,显示时间间隔 的长度必须被设置为  $Tr1:Tr2:Tr3:...:Tr(n-1):2xTrn=2^0:2^1:2^2:...:2^{n-2}:2^{n-1}$ 。在灰度等级 1 到  $2^n$ 之间的、想要的灰度等级显示可以通过组合显示时间间隔而被执行。

在一个帧周期期间在象素中显示的灰度等级是通过找到在帧周期内象素的有机 EL 单元发光时的显示时间间隔的长度的总和而被确定的。例如,当 n=8 时,如果在所有的显示时间间隔期间象素发光的情形下的亮度被取为 100%,则 1%的亮度可被表示为其中只在 Tr1 和 Tr2 期间象素发光的情形,以及如果在 Tr3, Tr5 和 Tr8 中象素发光,则可以表示 60%的亮度。

重要的是,用于写入数字视频信号的第 m 号比特到象素的写入周期 Tam 必须短于显示时间间隔 Trm。所以,比特号 m 的数值必须是在1 到 n 之间的一个数值,这样,写入周期 Tam 短于显示时间间隔 Trm。

而且,显示时间间隔 Tr1 到 Trn 可以按任何次序出现。例如,有可能显示时间间隔在一个帧周期内在 Tr1 后按 Tr3, Tr5, Tr2, ...的次序出现。然而,最好是,显示时间间隔 Tr1 到 Trn 具有一个免得互相重叠的次序。而且,也最好是,擦除周期 Te1 到 Ten 具有一个免得互相重叠的次序。

按照以上的结构,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

应当指出,虽然在实施例 2 中,显示时间间隔 Trn 被划分成两段,即划分的显示时间间隔 S1Trn 和 S2Trn,但实施例 2 并不限于此。可以有一个显示时间间隔被进行划分,或有多个显示时间间隔被进行划分。然而,最好是,它们从相应于较高位的显示时间间隔(即,具有较长的长度的显示时间间隔)按次序被划分。而且,设计者有可能适当地选择显示时间间隔的划分段的数目,但最好是划分段的数目按照在显示装置的驱动速度与图象的需要的显示质量之间的平衡来确定。

而且,虽然最好是相应于数字视频信号的同一个比特的划分的显示时间间隔的长度是相同的,但本发明并不限于此。划分的显示时间间隔的长度并不总是必须相等的。

应当指出,不同于实施例 1 中显示的驱动方法,在实施例 2 中,有可能使得其间有机 EL 元件发光的时间间隔短于写入周期。在一个帧周期中显示时间间隔的长度的总和的比值(工作比)所以不仅仅由写入周期的长度确定。

应当指出,虽然实施例 2 中显示了其中形成电容的结构,用来保持加到 EL 驱动器 TFT 的栅极上的电压,但也有可能省略该电容。对于其中 EL 驱动器 TFT 具有 LDD 区域被形成来通过栅极绝缘膜与栅极重叠的情形,在该区域形成通常被称为栅极电容的寄生电容。这个栅极电容也可主动地用作为用于存储加到 EL 驱动器 TFT 的栅极上的电压的电容。

栅极电容的电容值按照栅极与 LDD 区重叠的表面积而改变, 所以

电容值由被包括在重叠区域中的 LDD 区的长度确定。

## [实施例 3]

在本实施例中,说明用来驱动图 4 所示的象素部分的、源极信号 线驱动器电路和栅极信号线驱动器电路的详细结构。

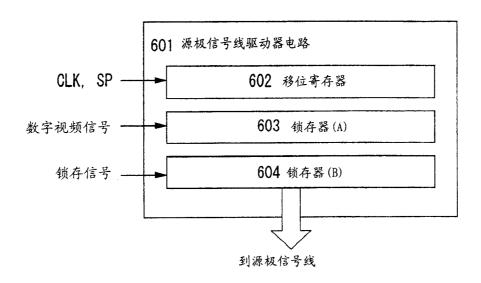

在图 10A 和 10B 是实施例 3 的 EL 显示装置的驱动器电路的方框图。图 10A 是源极信号线驱动器电路 601, 具有移位寄存器 602, 锁存器 (A) 603 和锁存器 (B) 604。

时钟信号 CLK 和启动脉冲 SP被输入到源极信号线驱动器电路 601 中的移位寄存器 602。移位寄存器 602 根据时钟信号 CLK 和启动脉冲 SP 按次序产生定时信号,以及通过诸如缓冲器那样的电路(图上未示出)把定时信号逐个地提供给下游电路。

来自移位寄存器 602 的定时信号可由诸如缓冲器的电路被缓冲放大。用来提供定时信号的连线的负载电容(寄生电容)很大,因为许多电路或元件被连接到该连线。缓冲器被用来防止在定时信号上升和下降时由于大的负载电容形成的波形圆滑化。应当指出,并不总是必须形成缓冲器。

由缓冲器缓冲放大的定时信号被提供给锁存器(A)603。锁存器(A)603 具有多个锁存器级,用于处理 n 比特数字视频信号。当定时信号被输入时,锁存器(A)603 写入和保存从源极信号线驱动器电路601 外部提供的 n 比特数字视频信号。

应当指出,当把数字视频信号写入到锁存器(A)603时,数字视频信号也可按次序被输入到锁存器(A)603的多个锁存器级。然而,本发明并不限于这种结构。锁存器(A)603的多个锁存器级可被划分成一些组,也就是,可以执行分组驱动。应当指出,这时的组的数目被称为分段数。例如,当锁存器按每四级的锁存器被划分成一个组时,这被称为具有四个分段的灰度等级驱动。

直至数字视频信号被完全写入到所有的锁存器(A)603的所有锁存器级为止的时间间隔被称为行周期。实际上,可能有一种情形,其中行周期包括把水平回扫周期加到以上行周期的周期。

当一个行周期完成时,一个锁存信号被加到锁存器(B)604。被写入和被存储在锁存器(A)603中的数字视频信号在这个时刻全都同时发送到锁存器(B)604,以及被写入和被存储在锁存器(B)604

中。

根据来自移位寄存器 602 的定时信号,再次执行按次序把数字视频信号写入到已完成发送数字视频信号到锁存器(B)604 的锁存器(A)603 中。

被写入和被存储到锁存器(B)604的数字视频信号在第二行周期期间被输入到源极信号线。

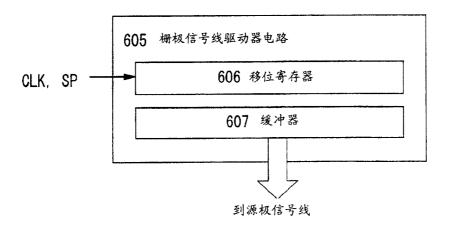

图 10B 是显示栅极信号线驱动器电路的结构的方框图。

栅极信号线驱动器电路 605 具有移位寄存器 606 和缓冲器 607。 而且,栅极信号线驱动器电路 605 也可以具有电平移动二极管,取决于实际情况。

来自移位寄存器 606 的定时信号被提供给栅极信号线驱动器电路 605 中的缓冲器 607,以及定时信号被提供给相应的栅极信号线。用于一行的象素的开关 TFT 的栅极被连接到栅极信号线。所有一行的象素的开关 TFT 必须同时设置为接通状态,所以使用可以流过大的电流的缓冲器。

## [实施例 4]

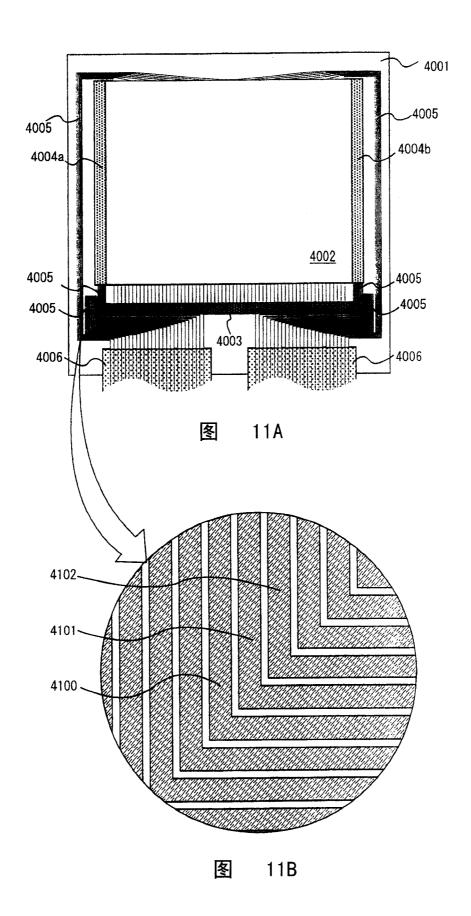

在实施例 4 中,通过图 11A,11B和 12A 到 12C,说明制造使用本发明的驱动方法的 EL显示装置的例子。

图 11A 是使用本发明的驱动方法的 EL 显示装置的 TFT 基片的上表面图。应当指出,在本技术说明中,术语 TFT 基片表示在其上形成象素部分的基片。

象素部分 4002,源极信号线驱动器电路 4003,第一栅极信号线驱动器电路 4004a,和第二栅极信号线驱动器电路 4004b 被形成在基片 4001 上。应当指出,本发明中源极信号线驱动器电路和栅极信号线驱动器电路的数目并不限于图 11A 上所显示的数目。设计有可能设置源极信号线驱动器电路和栅极信号线驱动器电路的数目。而且,在实施例 4 中,源极信号线驱动器电路和栅极信号线驱动器电路被形成在 TFT 基片上,但本发明并不限于此。被形成在与 TFT 基片分开的基片上的源极信号线驱动器电路和栅极信号线驱动器电路也可以通过诸如 FPC 的装置被电连接到象素部分。

参考数字 4005 表示提取连线。提取连线 4005 通过 FPC 4006 被连接到外部地形成在基片 4001 上的 IC 等。

图 11B上显示了提取连线 4005 的放大图。参考数字 4100 表示 R 提取连线,参考数字 4101 表示 G提取连线,以及参考数字 4102 表示 B提取连线。

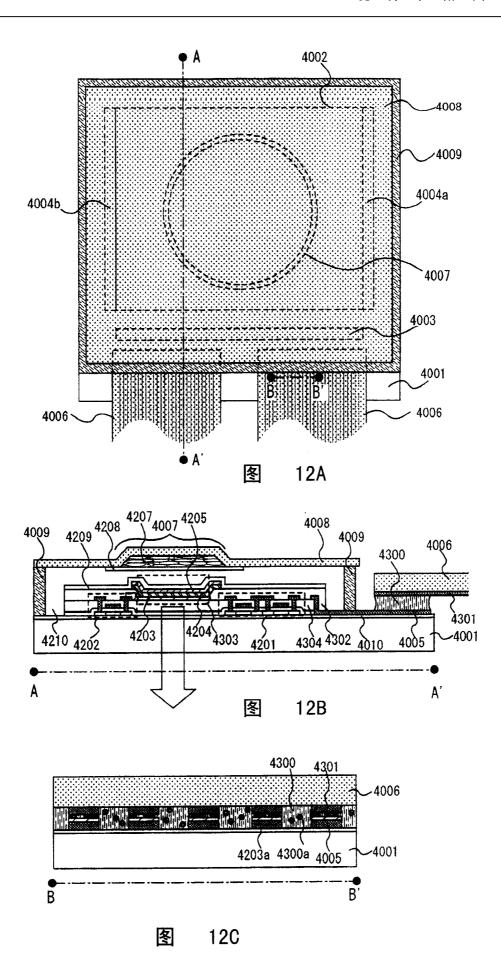

图 12A 是通过用密封材料密封图 11A 所示的 TFT 基片而形成的 EL显示装置的顶视图。图 12B 是沿线段 A-A'截取的图 12A 的截面图,以及图 12C 是沿线段 B-B'截取的图 12A 的截面图。应当指出,在图 12A 到 12C 中,相同的参考数字被使用于在图 11A 和 11B 上已显示的部分。

密封剂 4009 被形成来包围被形成在基片上的象素部分 4002,源 极信号线驱动器电路 4003,以及第一和第二栅极信号线驱动器电路 4004a 和 4004b。而且,密封材料 4008 被形成在象素部分 4002,源 极信号线驱动器电路 4003,以及第一和第二栅极信号线驱动器电路 4004a 和 4004b。象素部分 4002,源极信号线驱动器电路 4003,以及第一和第二栅极信号线驱动器电路 4004b 所以借助于填充材料 4210 与基片 4001,密封剂 4009,和密封材料 4008 气密地粘接。

而且,被形成在基片 4001 时的象素部分 4002,源极信号线驱动器电路 4003,以及第一和第二栅极信号线驱动器电路 4004a 和 4004b 具有多个 TFT。典型地,被包含在源极信号线驱动器电路 4003 中的驱动器 TFT (注意,这里在图上显示一个n沟道 TFT 和一个p沟道 TFT) 4201,和 EL 驱动器 TFT (用于控制流到有机 EL 元件的电流的 TFT) 4202 被形成在基本薄膜 4010 上,如图 12B 所示。

在实施例 4 中,在驱动器 TFT 4201 中使用通过已知的方法制造的 p 沟道 TFT 或 n 沟道 TFT,以及在 EL 驱动器 TFT 4202 中使用通过已知的方法制造的 p 沟道 TFT。而且,提供了被连接到 EL 驱动器 TFT 4202 的栅极的贮存电容(图上未示出)。

层间绝缘薄膜(分层薄膜) 4304被形成在驱动器 TFT 4201和 EL 驱动器 TFT 4202上,以及被电连接到 EL 驱动器 TFT 4202的漏极的象素电极(正极) 4203被形成在层间绝缘薄膜 4304上。具有大的工作功能的透明导电薄膜被使用于象素电极 4203。氧化碘和氧化锡的化学混合物、氧化碘和氧化锌的化学混合物、氧化锌、氧化锡、和氧化碘可被使用于透明导电薄膜。而且,也可以使用其中加上镓的透明导电薄膜。

绝缘薄膜 4302 然后被形成在象素电极 4203 上, 以及在绝缘薄膜

4302 中形成一个通孔部分通过象素电极 4203。EL(场致发光)层 4204 被形成在通孔部分在象素电极 4203 上。已知的有机 EL 材料可被使用于 EL 层 4204。而且,有低分子量(单体)有机 EL 材料和高分子量(聚合体)有机 EL 材料,以及可以使用任一种材料。

已知的蒸发技术或已知的应用技术可被用作为形成 EL 层 4204的方法。而且, EL 层可以具有单层结构或叠层结构, 其中空穴注入层、空穴输送层、光发射层、电子输送层、和电子注入层自由地组合。

由具有光屏蔽性质的导电薄膜(典型地,具有铝、铜、或银作为它的主要成份的导电薄膜,或这样的导电薄膜与另一种导电薄膜的叠层薄膜)制成的负极 4205 被形成在 EL 层 4204 上。而且,最好尽可能多地去除在负极 4205 与 EL 层 4204 之间的交界区中存在的任何湿气和氧气。所以,必须利用用于在氮气或惰性气体中形成 EL 层 4204、然后在不暴露在氧气或湿气的条件下形成负极 4205 的机构。上述的薄膜沉积在实施例 4 中通过使用多沉淀槽方法(集聚工具方法)的薄膜沉积设备而是可能的。预定的电压然后被施加到负极 4205。

包括象素电极(正极)4203、EL层 4204、和负极 4205 的有机 EL元件 4303,这样被形成。保护薄膜 4303 然后被形成在绝缘薄膜 4302上,以便保护有机 EL元件 4303。保护薄膜 4303 在防止诸如氧和湿气等污染物进入有机 EL元件 4303 方面是有效的。

标号 4005a 表示被连接到电源线的提取连线,以及提取连线4005a被电连接到 EL 驱动器 TFT 4202 的源极区。提取连线4005a穿过密封剂4009 与基片4001之间,以及通过各向异性导电薄膜4300被电连接到 FPC 4006 的 FPC 连线4301。

玻璃材料、金属材料(典型地不锈钢材料)、陶瓷材料、和塑料材料(包括塑料薄膜)可被用作为密封材料 4008。FPR(玻璃纤维加强的塑料)板、PVF(聚氯乙烯)薄膜、聚酯 (mylar)薄膜、聚酯 (polyester)薄膜、和丙烯酸树脂薄膜可被用作为塑料材料。而且,具有用 PVF 薄膜或聚酯 (mylar)薄膜夹心铝箔的结构的薄片也可被使用。

然而,如果从有机 EL 元件发射的光的方向是朝向覆盖材料,则 覆盖材料必须是透明的。在这种情形下,使用透明物质,诸如玻璃板、 塑料板、聚酯薄膜或丙烯酸薄膜。 而且,除了惰性气体(诸如氮或氩)以外,紫外线固化树脂或红外线固化树脂可被用作为填充材料 4210。PVC(聚氯乙烯)、丙烯酸、聚酰亚胺、环氧树脂、硅树脂、PVB(聚乙烯醇缩丁醛)和 EVA(醋酸乙烯酯)可被使用。在实施例 4 中,氮被用作为填充材料。

为了把填充材料 4210 放置在吸湿物质(优选地氧化钡)或能吸收氧的物质中,在密封材料 4008的、基片 4001 侧的表面上形成凹槽部分 4007,以及吸湿物质或能吸收氧的物质 4207 可被放置在凹槽部分 4007中。吸湿物质或能吸收氧的物质 4207 通过凹槽部分覆盖材料 4208 被保持在凹槽部分 4007中,这样,吸湿物质或能吸收氧的物质 4207不会飞应当指出,凹槽部分覆盖材料 4208 具有带细网格形状的结构,以及空气和湿气能穿过,但吸湿物质或能吸收氧的物质 4207不会通过。有机 EL 元件 4303 的老化可以通过形成吸湿物质或能吸收氧的物质 4207,而被抑制。

在形成象素电极 4203 的同时, 导电薄膜 4203a 被形成为接触提取连线 4005a, 如图 12C 所示。

而且,各向异性导电薄膜 4300 具有导电的填料 4300a。通过基片 4001 和 FPC 4006 的热塑配合,在基片 4001 上的导电薄膜 4203a 与在 FPC 4006 上的 FPC 连线 4301 通过导电填料 4300a 被电连接。

应当指出,有可能通过把实施例 4 与实施例 1 到 3 的任何部分自由地组合而实施实施例 4。

## [实施例 5]

在本实施例中,通过图 13 到 16 详细地描述在本发明的 EL 显示装置中,在同一个基片上同时形成象素部分和被形成在象素部分的外围的驱动器电路的 TFT (n 沟道 TFT 和 p 沟道 TFT) 的方法。

首先,在本实施例中,使用基片 300,它是由玻璃制成的,诸如硼硅酸钡玻璃或硼硅酸铝,由诸如 Corning #7059 玻璃和#1737 代表。应当指出,作为基片 300,可以使用石英基片,或硅基片,金属基片,或其上形成绝缘薄膜的不锈钢基片,作为代替品。也可以使用具有热对抗本实施例的处理温度的塑料基片。

然后,基本薄膜 301 由绝缘薄膜形成,诸如氧化硅薄膜,氮化硅薄膜,或氮氧化硅薄膜。在本实施例中,二层结构被用作为基本薄膜 301。然而,可以使用单层薄膜,或由两层或多层绝缘薄膜组成的叠

层结构。作为第一层基本薄膜 301, 氮氧化硅薄膜 301a 可以借助于等离子体 CVD (化学汽相沉淀) 方法使用 SiH<sub>4</sub>,NH<sub>3</sub>和 N<sub>2</sub>O 作为反应气体而被形成为 10 到 200nm (纳米) 的厚度 (优选地 50 到 100nm)。在本实施例中,形成具有 50nm 薄膜厚度的氮氧化硅薄膜 301a(组成比例为: Si=32%, 0=27%, N=24%, 和 H=17%)。然后,作为第二层基本薄膜 301,氮氧化硅薄膜 301b 可以借助于等离子体 CVD 方法使用 SiH<sub>4</sub>和 N<sub>2</sub>O 作为反应气体而被形成为叠层在其上的 50 到 200nm 的厚度 (优选地 100 到 150nm)。在本实施例中,形成具有 100nm 薄膜厚度的氮氧 化硅薄膜 301b (组成比例为: Si=32%, 0=59%, N=7%, 和 H=2%)。

随后,半导体层 302 到 305 被形成在基本薄膜上。半导体层 302 到 305 是通过已知的方法(溅射方法,LPCVD 方法或等离子体 CVD 方法)从具有非结晶结构的半导体薄膜形成的,然后经过一个已知的晶体化处理过程(激光晶体化方法,热晶体化方法,或使用诸如镍的催化剂的热晶体化方法)。这样得到的晶体化的半导体薄膜被成形为想要的形状,得到半导体层。半导体层 302 到 305 被形成为从 25 到 80nm的厚度(优选地使用硅、硅锗合金(Si,Ge<sub>1-x</sub>(x=0.001 到 0.02))等形成薄膜。在本实施例中,通过等离子体 CVD 方法形成 55nm 厚度非结晶硅薄膜,然后在非结晶硅薄膜上保持含镍的溶液。执行非结晶硅薄膜的去氢化处理(500℃一小时),此后在其上进行热晶体化处理(550℃四小时)。而且,为了改进它的结晶度,执行激光退火处理,形成结晶的硅薄膜。然后,这个晶体硅薄膜通过使用光刻方法进行成形处理、得到半导体层 302 到 305。

而且,在形成半导体层 302 到 305 以后,可以掺杂小量杂质元素 (硼或磷),以便控制 TFT 的门限值。

此外,在晶体硅半导体薄膜是用激光器晶体化方法制造的情况下,可以使用脉冲振荡型或连续波型激态复合物激光器,YAG(钇铝柘榴石)激光器,或YVO4激光器。在使用那些激光器的情况下,最好使用一种方法,其中从激光器振荡器发射的激光被光学系统聚合成直线波束,以及被辐射到非晶体半导体薄膜。虽然晶体化的条件应当由操作者适当地选择,在使用激态复合物激光器的情况下,脉冲振荡频率被设置为300Hz,以及激光器能量密度为100到400mJ/cm²(典型地

200 到 300mJ/cm²)。在使用 YAG 激光器的情况下,最好是使用二次谐波,其脉冲振荡频率设置为 30 到 300kHz,以及激光器能量密度被设置为 300 到 600mJ/cm²(典型地 350 到 500mJ/cm²)。然后,被聚合成直线形状的、宽度为 100 到 1000μm 的激光,例如 400μm,被辐射到基片的整个表面,以及这时的线性激光的重叠比可被设置为 50 到 90%。

栅极绝缘薄膜 306 然后被形成用来覆盖半导体层 302 到 305。栅极绝缘薄膜 306 是通过等离子体 CVD 或溅射方法从包含硅的绝缘薄膜 被形成为从 40 到 150nm 的薄膜厚度。在实施例中,栅极绝缘薄膜 306 是通过等离子体 CVD 方法从氮氧化硅薄膜被形成为 110nm 的厚度(组成比例为: Si=32%, 0=59%, N=7%, 和 H=2%)。 当然,栅极绝缘薄膜不限于氮氧化硅薄膜,包含气体硅的绝缘薄膜可被形成为叠层结构的单个层。

此外,当使用氧化硅薄膜时,它可以通过等离子体 CVD 方法而被形成,其中 TEOS(四乙基原硅酸盐)和  $0_2$  被混合,具有 40 帕 (Pa)的反应压力,从 300 到 400 °C 的基片温度,以及以 0.5 到 0.8 W/cm²的高频(13.56MHz)功率密度被放电。在通过随后的、在 400 到 500 °C 的热退火方法制造的氧化硅薄膜中,可以得到作为栅极绝缘薄膜的良好的特性。

然后,如图 13A 所示,在栅极绝缘薄膜 306 上,第一导电薄膜 307 和第二导电薄膜 308 被形成为分别具有 20 到 100nm 和 100 到 400nm 的薄膜厚度叠层结构。在本实施例中,由厚度为 30nm 的 TaN(氮化钽)薄膜制成的第一导电薄膜 307 和由厚度为 370nm 的 W (钨)薄膜制成的第二导电薄膜 308 被形成为叠层结构。Ta 薄膜是通过在包含氮的气体下用 Ta 靶极溅射而形成的。此外,W 薄膜是通过用 W 靶极溅射而形成的。W 薄膜可以通过热 CVD 方法使用六氟化钨 (WF6) 而被形成。无论使用哪种方法,必须使得材料具有低的电阻以便用作为栅极,最好是,W 薄膜的电阻率被设置为小于或等于 20 μ Ω cm。通过把晶粒制做得很大,有可能使得 W 薄膜具有较低的电阻率。然而,在许多杂质元素,诸如氧,被包含在 W 薄膜内的情况下,晶体化被禁止,以及电阻变为较高的。所以,在本实施例中,通过使用具有 99 的纯度的目标进行溅射而形成具有高纯度的 W 薄膜,以及此外,通过充分考虑阻止

汽相内的杂质在薄膜形成期间混合在其中,可以实现从 9 到 20 μ Ω cm 的电阻率。

应当指出,在本实施例中,第一导电薄膜 307 由 TaN 制成,以及第二导电薄膜 308 由 W 制成,但材料并不具体限于此,任一个薄膜可以由从 Ta, W, Ti, Mo, A1, Cu, Cr, 和 Nd 中选择的元素或包含以上的元素作为它的主要成份的合金材料或化合物材料来形成。此外,可以使用由用杂质元素(诸如磷)掺杂的多晶硅薄膜表征的半导体薄膜。此外,利用采用任何的组合,诸如其中第一导电薄膜由钽(Ta)制成以及第二导电薄膜由钨(W)制成的组合,其中第一导电薄膜由氮化钽(TaN)制成以及第二导电薄膜由铝(A1)制成的组合,或其中第一导电薄膜由氮化钽(TaN)制成以及第二导电薄膜由铜(Cu)制成的组合。

接着,通过使用光刻法形成由保护膜制成的掩膜 309 到 312,以及执行第一蚀刻处理过程,以便形成如图 13B 所示的电极和连线。这个第一蚀刻处理过程按照第一和第二蚀刻条件来执行。在本实施例中,作为第一蚀刻条件,使用 ICP (感性耦合的等离子体)蚀刻方法, $CF_4$ ,  $CI_2$  和  $O_2$  的气体混合物被用作为蚀刻气体,气流速率被设置为25/25/20 sccm,以及等离子体是通过在 1 帕下施加 500 瓦射频(13.56 MHz)功率到线圈形状电极而产生的。这里使用由 Matsushita电子工业有限公司生产的带有 ICP(Model  $E645-\Box ICP$ )的干性蚀刻设备。150 瓦射频(13.56 MHz)功率电被加到基片侧(测试片阶段),有效地加上负的自偏置电压。W 薄膜用第一蚀刻条件被蚀刻,第二导电层的末端部分被形成为变尖的形状。在第一蚀刻条件中,对于W 的蚀刻速度是W 200. W 39 nm/min(W 40 ,对于W 70 个数),对于W 70 个数),对于W 70 个数),对于W 70 个数)。

此后,第一蚀刻条件变为第二蚀刻条件,而不去除由保护膜制成的掩膜 309 到 312。CF4和 Cl2的混合气体被用作为蚀刻气体,气流速率被设置为 30/30sccm,以及等离子体是通过在 1 帕下施加 500 瓦射频 (13.56MHz) 功率到线圈形状电极而产生的,由此执行约 30 秒的蚀刻。20 瓦射频 (13.56MHz) 功率也被加到基片侧(测试片阶段),有效地加上负的自偏置电压。W薄膜和 TaN 薄膜用第二蚀刻条件以同一个次序被蚀刻,其中 CF4和 C12 被混合。在第二蚀刻条件中,对于

W的蚀刻速度是 58.97nm/min, 对于 TaN 的蚀刻速度是 66.43nm/min。 应当指出,蚀刻时间可以增加约 10 到 20%,以便在栅极绝缘薄膜上执行蚀刻而没有任何残余物。

在第一蚀刻处理过程中,通过采用具有适当的形状的保护膜的掩膜,由于加到基片侧的偏置电压的影响,第一和第二导电层的末端部分被形成为具有变尖的形状。变尖部分的角度可被设置为 15°到 45°。因此,由第一导电层和第二导电层构成的第一形状的导电层 314 到 317 (第一导电层 314a 到 317a 和第二导电层 314b 到 317b)通过第一蚀刻处理过程被形成。参考数字 319表示栅极绝缘薄膜,以及没有被第一形状导电层 314 到 317 覆盖的栅极绝缘薄膜的区域通过蚀刻被做得更薄约 20 到 50nm。

然后,执行第一掺杂处理,加上杂质元素,以便授予 n 型导电性 给半导体层而不去除由保护膜制成的掩膜(图 13B)。掺杂是通过离子掺杂方法或离子注入方法实行的。离子掺杂方法的条件是,剂量为 1x10<sup>13</sup>到 5x10<sup>15</sup>原子/cm²,以及加速电压是 60 到 100keV(千电子伏)。在本实施例中,剂量为 1.5x10<sup>15</sup>原子/cm²,以及加速电压是 80keV。作为用于授予 n 型导电性的杂质元素,使用属于周期表的第 15 组的元素,典型地是磷 (P) 或砷 (As),在这里使用磷。在这种情形下,导电层 314 到 317 成为对于用于授予 n 型导电性的杂质元素的掩膜,以及高浓度杂质区 320 到 323 以自对准方式被形成。用于授予 n 型导电性的杂质元素以 1x10<sup>13</sup>到 5x10<sup>15</sup>原子/cm³的浓度范围被加到高浓度杂质区 320 到 323。

此后,执行第二蚀刻处理过程,而不去除由保护膜制成的掩膜,如图所 13C 示。这里, $CF_4$ , $CI_2$ 和  $O_2$ 的混合气体被用作为蚀刻气体,气流速率被设置为 20/20/20sccm,以及等离子体是通过在 1 帕下施加 500 瓦射频(13.56MHz)功率到线圈形状电极而产生的,由此执行蚀刻。20 瓦射频(13.56MHz)功率也被加到基片侧(测试片级),有效地加上负的自偏置电压。在第二蚀刻处理过程中,对于  $\mathbb{V}$  的蚀刻速度是 124.62nm/min,对于  $\mathbb{V}$  TaN 的蚀刻速度是 20.67nm/min,以及  $\mathbb{V}$  对  $\mathbb{V}$  TaN 的选择性是 6.05。因此,  $\mathbb{V}$  薄膜被选择地蚀刻。在第二蚀刻处理过程中, $\mathbb{V}$  的变尖的角度是  $70^\circ$ 。第二导电层 324b 到 327b 通过第二蚀刻处理过程被形成。另一方面,第一导电层 314a 到 317a 很难被

蚀刻, 以及第一导电层 324a 到 327a 被形成。

接着,执行第二掺杂处理。第二导电层 324b 到 327b 被用作为成为对于杂质元素的掩膜,以及掺杂被实施,以使得杂质元素被加到在第一导电层变尖部分的下面的半导体层。在本实施例中,磷 (P) 被用作为杂质元素,以及等离子体掺杂是在 1.5x10<sup>15</sup> 原子/cm² 的剂量,0.5A 的电流密度和 80keV 的加速电压下进行的。因此,与第一导电层重叠的、低浓度杂质区 329 到 332 以自对准方式被形成。在低浓度杂质区 329 到 332 中的磷 (P) 的浓度是 1x10<sup>17</sup> 到 5x10<sup>18</sup> 原子/cm³,以及具有按照第一导电层的变尖部分的薄膜厚度的缓和的浓度梯度。应当指出,在与第一导电层的变尖部分重叠的半导体层中,杂质元素的浓度从第一导电层的变尖部分的末端部分向里面的部分稍微下降。然而,浓度几乎保持在相同的水平。而且,在高浓度杂质区 333 到 336中,加上高密度的杂质元素。

此后,如图 14B 所示,在去除由保护膜制成的掩膜后,通过使用光刻方法执行第三蚀刻处理过程。在第三蚀刻处理过程中,第一导电层的变尖部分被部分地蚀刻,以使得具有与第二导电层重叠的形状。偶尔地,如图 14B 所示,由保护膜制成的掩膜 338 被形成在其中不进行第三蚀刻处理过程的区域。

在第三蚀刻处理过程中的蚀刻条件是,使用 ICP 蚀刻,类似于第一和第二蚀刻处理过程,以及  $Cl_2$ 和  $SF_6$ 被用作为蚀刻气体,分别具有 10/50 sccm 的气流速率。应当指出,在第三蚀刻处理过程下, TaN 的 蚀刻速度是 111.2 nm/min,以及对于栅极绝缘薄膜的蚀刻速度是 12.8 nm/min.

在1.3 帕下500 瓦射频(13.56MHz)电功率被加到线圈形状电极,产生等离子体,以及执行蚀刻。10 瓦射频(13.56MHz)电功率被加到基片侧(样本阶段),有效地加上负的自偏置电压。这样,对于导电层340a到342a被形成。

与第一导电层 340a 到 342a 不重叠的杂质区(LDD 区) 343 到 345 按照第三蚀刻处理过程被形成。应当指出,杂质区(GOLD 区) 346 保持与第一导电层 324a 重叠。

而且, 由第一导电层 324a 和第二导电层 324b 形成的电极最后成为驱动器电路的 n 沟道 TFT 的栅极。由第一导电层 340a 和第二导电

层 340b 形成的电极最后成为驱动器电路的 p 沟道 TFT 的栅极。

同样地,由第一导电层 341a 和第二导电层 341b 形成的电极最后成为象素部分的 n 沟道 TFT 的栅极。由第一导电层 342a 和第二导电层 342b 形成的电极最后成为象素部分的 p 沟道 TFT 的栅极。

与第一导电层 340a 到 342a 不重叠的杂质区(LDD 区) 343 到 345 以及与第一导电层 324a 重叠的杂质区(GOLD 区) 346 到 345, 在实施例 5 中, 因此可同时被形成, 以及有可能根据 TFT 特性来制做区域。

接着, 蚀刻栅极绝缘薄膜 319。CHF<sub>3</sub>被用作为蚀刻气体, 以及对于这个蚀刻处理过程执行反应离子蚀刻(RIE)。在实施例 5 中, 蚀刻处理过程是在蚀刻槽压力设置为 6.7 帕, RF 电功率为 800 瓦和 CHF<sub>3</sub> 气流速率设置为 35sccm 的条件下进行的。

高浓度杂质区 333 到 336 的一部分因此被暴露,以及绝缘薄膜 356a 到 356b 被形成。

在去除包括保护膜的掩膜后,新的掩膜由保护膜被形成,以及执行第三掺杂处理过程。通过第三掺杂处理过程,其中从单个导电型(n型)加上授予相反的导电型(p型)的杂质元素的杂质区 350 到 353,被形成为半导体层,它成为 p 沟道 TFT 的工作层。(见图 14C)第一导电层 340a 和 342a 被用作为对于杂质元素的掩膜,授予 p 型导电性的杂质元素被加上,以及杂质区以自对准方式被形成。

在实施例 5 中,杂质区 350 到 353 是通过使用乙硼烷 (B<sub>2</sub>H<sub>6</sub>)的离子掺杂而被形成的。应当指出,在第三掺杂处理过程期间,形成 n 沟道 TFT 的半导体层被由保护膜形成的保护掩膜 348 和 349 覆盖。分别通过第一掺杂处理过程和通过第二掺杂处理过程以不同的浓度把磷加到杂质区 350 到 353。然而,掺杂被执行,以使得授予 p 型导电性给每个区的杂质的浓度成为从 2x10<sup>20</sup> 到 2x10<sup>21</sup> 原子/cm³,所以,对于用作为 p 沟道 TFT 的源极区和漏极区的区域,将没有问题。

通过至此为止的处理过程,杂质区被形成在各自的半导体层中。

保护掩膜 348 和 349 接着被去除,以及形成第一层间绝缘薄膜 357。通过等离子体 CVD 或溅射,保护硅的绝缘薄膜被形成为具有 100 到 200nm 的厚度。在实施例 5 中,通过等离子体 CVD, 氮氧化硅薄膜 被形成为具有 150nm 的厚度。第一层间绝缘薄膜 357 当然不限于氮氧化硅薄膜,其它的包含硅的绝缘薄膜可被使用于单层或叠层结构。

接着,如图 15A 所示,执行用于激活被加到每个半导体层的杂质元素的处理过程。对于激活处理过程,通过退火炉执行热退火。热退火可以在具有 1ppm 的氧浓度(优选地 0.1ppm 或更低)的氮气中在400 到 700℃下,典型地在 500 与 550℃之间进行。应当指出,除了热退火以外,也可以使用激光退火和快速热退火(RTA)。

还应当指出,在实施例 5 中,在与执行以上的激活处理过程的同时,被用作为催化剂的镍在晶体化期间被吸收到以高的浓度包含磷的杂质区 334 到 336, 350, 和 351。在主要变成为沟道形成区的半导体层内的镍浓度因此被减小。对于具有这样形成的沟道形成区的 TFT, 关断电流的数值被减小,以及因为良好的晶体性,得到高的电场有效迁移率。因此,可以得到良好的性质。

而且,激活处理过程也可以在形成第一层间绝缘薄膜之前执行。 然而,当使用对于热是很弱的连线材料时,最好是在形成层间绝缘薄膜后(例如,包含硅作为主要组成的绝缘薄膜,氮化硅薄膜)执行激活处理,以便保护连线等,正如实施例5中那样。

掺杂处理过程可被执行,以及第一层间绝缘薄膜克原子执行激活 处理过程之后被形成。

另外, 热处理在包含 3 到 100%的氢的大气中在 300 到 550℃下进行 1 到 12 小时, 执行半导体层的氢化。在实施例 5 中, 热处理在包含 3%的氢的氮气中在 410℃下进行 1 小时。这个处理过程是用于以被包含在层间绝缘薄膜中的氢来终结半导体层的悬挂键的处理过程。等离子体晶体化(使用由等离子体激励的氢)可以作为另一个氢化装置被执行。

而且,当使用激光退火方法作为激活处理过程,最好是在执行以上的氢化处理过程后发射激光,诸如来自激态复合物激光器或 YAG 激光器的激光。

第二层间绝缘薄膜 358 接着从有机绝缘材料被形成在第一层间绝缘薄膜 357, 如图 15B 所示。在实施例 5 中, 具有 1.6 μm 厚度的丙烯酸树脂层被形成。接着, 形成图案, 以便形成用于达到杂质区 333, 335, 350 和 351 的接触孔。

由包含硅或有机树脂的绝缘材料制成的薄膜被用作为第二层间绝缘薄膜 358。氧化硅,氮化硅,和氮氧化硅可被用作为包含硅的绝

缘材料,以及诸如聚酰亚胺、聚酰胺、丙烯酸或 BCB(苯并环丁烷)的材料可被用作为有机树脂。

在实施例 5 中,氮氧化硅薄膜是通过等离子体 CVD 被形成的。应当指出,最好是氮氧化硅的薄膜厚度是从 1 到 5 μ m (更优选地是在 2 个 4 μ m 之间)。氮氧化硅薄膜在抑制有机 EL 元件的量化方面是有效的,因为几乎没湿气包含在薄膜本身中。

而且,干法蚀刻或湿法蚀刻可被使用来形成接触孔,但考虑到在 蚀刻期间静态损坏的问题,最好是使用湿法蚀刻。另外,第一层间绝 缘薄膜和第二层间绝缘薄膜在形成接触孔时同时地被蚀刻。所以,最 好是使用用于形成第二层间绝缘薄膜的材料,它比起用来形成第一层 间绝缘薄膜,考虑接触孔的形状来说,具有更快的蚀刻速度。

然后,形成用于分别电连接到杂质区 333, 335, 350 和 351 的连线 359 到 366。连线是通过在 50nm 厚度 Ti 薄膜与 500nm 厚度合金薄膜(铝和钛合金薄膜)的叠层薄膜形成图案而被形成。也可以使用其它导电薄膜。

然后,在其上形成具有 80 到 120nm 厚度的透明的导电薄膜,以及透明的电极 367 是通过图案成形而形成的。(见图 15B)

应当指出,氧化铟锡(ITO)薄膜,或其中混合有2到20%氧化锌(ZnO)的氧化铟的透明导电薄膜,在实施例5中被用作为透明电极。

而且,透明电极 367 通过被形成接触和叠加漏极连线 365,而被电连接到电流控制 TFT 的漏极区。

接着,如图 16 所示,包含硅的绝缘薄膜(在实施例 5 中是氧化硅薄膜)被形成为具有 500nm 的薄膜厚度,以及开孔部分被形成在相应于透明电极 367 的位置。用作为存储库的第三层间绝缘薄膜 368 被形成。具有变尖形状的侧壁可以通过在形成开孔部分时使用湿法蚀刻容易地被形成。如果开孔部分的侧壁不够平缓,则由于台阶,EL层的老化变成为显著的问题。所以必须当心。

应当指出,虽然氧化硅在实施例 5 中被用作为第三层间绝缘薄膜 368,但诸如聚酰亚胺、聚酰胺、丙烯酸或 BCB(苯并环丁烷)的有机树脂也可被使用,取决于环境。

EL 层 369 接着被形成,如图 16 所示。另外,负极(MgAg(镁银)电极)370和保护电极371通过蒸发被形成。最好是在形成EL 层 369

和负极 370 之前对透明电极进行热处理,完全去除所有的湿气。应当指出,虽然在实施例 5 中, MgAg 电极被用作为有机 EL 元件的负极,但也可以使用其它的已知材料。

还应当指出,已知材料可被用作为 EL 层 369,包括空穴输送层和光发射层的两层结构在实施例 5 中被用作为 EL 层,但可以有其中形成空穴注入层,电子注入层,或电子输送层的情形。许多组合的例子已经给出报告,以及任何报告的结构可被使用。

在实施例 5 中,聚苯乙烯通过蒸发被形成为空穴输送层。而且,其中从 30 到 40%的 1,3,4-重氮氧化物介质 PBD 被分布在聚乙烯咔唑的材料,通过蒸发被形成为光发射层,以及约 1%的香豆素 6 被加上作为绿色光发射的中心。

而且,虽然有可能用保护电极 371 来防止 EL 层 369 受到湿气和氧的影响,板最好是形成钝化薄膜 372。300nm 厚度的氮化硅薄膜在实施例 5 中被形成为钝化薄膜 372。钝化薄膜也可以在形成保护电极371 后接连地被形成,而不暴露到大气中。

保护电极 371 被形成来防止负极 370 的老化,以及它典型地由具有铝作为它的主要组成的金属薄膜而被制成。当然,也可以使用其它材料。而且,EL层 369 和负极 370 对于湿气是极弱的,所以,最好是通过在保护电极 371 上接连地进行薄膜成形,不暴露到大气中,而防止 EL层受到外部大气影响。

应当指出, EL层 369 的薄膜厚度可以是从 10 到 400nm(典型地在 60 和 150nm 之间), 以及负极 370 的薄膜厚度可以是从 80 到 150nm(典型地在 100 和 150nm 之间)。

具有如图 16 所示的结构的 EL 显示装置因此被完成。应当指出,在实施例 5 中 EL 显示装置的制造过程中,虽然源极信号线是用 Ta 和 W(形成栅极的材料)形成的,以及虽然栅极信号线是用 Al(形成源极和漏极的连线材料)形成的,但相对于电路结构和处理过程,也可以使用其它材料。

而且,具有n沟道TFT 701和p沟道TFT 702的驱动器电路,以及具有开关TFT 703和EL驱动器TFT 704的象素部分707可被形成在同一个基片上。

驱动器电路 706 的 n 沟道 TFT 701 具有沟道形成区 333、与形成

栅极的一部分的第一导电层 324a 相重叠的低浓度杂质区 329 (GOLD 区)、和用作为源极区或漏极区的高浓度杂质区 333。p沟道 TFT 702 具有沟道形成区 373、不与构成栅极的一部分的第一导电层 324a 相重叠的杂质区 343、和用作为源极区或漏极区的杂质区 350 和 352。

象素部分 707 的开关 TFT 703 具有沟道形成区 374、被形成在栅极外部并且不与形成栅极的第一导电层 341a 相重叠的低浓度杂质区 344 (LDD区)、和用作为源极区或漏极区的高浓度杂质区 335。

象素部分 707 的 EL 驱动器 TFT 704 具有沟道形成区 375、和用作为源极区或漏极区的高浓度杂质区 351 和 353。

应当指出,有可能通过把实施例 5 与实施例 1 到 4 的任何部分自由地组合而实施实施例 4。

## [实施例 6]

通过实施本发明形成的 EL 显示装置,比起液晶显示装置来说,在亮的位置上具有卓越的可视性,因为它是自发射型装置,而且,它的视场很宽。因此,它可被用作为用于各种电子设备的显示部分。例如,最好是使用本发明的 EL 显示装置作为具有对角线等于 30 英寸或更大的(典型地,等于 40 英寸或更大)EL 显示装置的显示部分(把EL 显示装置引用到帧的电光器件),用大屏幕欣赏 TV 广播。

应当指出,显示信息的所有的显示器,诸如个人计算机显示器, TV 广播接收显示器或广告显示器,被包括在 EL 显示装置中。而且, 本发明的 EL 显示装置可被用作为其它各种电子设备的显示部分。

以下的应用项可以作为本发明的这样的电子设备的例子被给出:摄像机;数字照相机;防护镜型显示装置(头戴式显示装置);导航系统;音频重放设备(诸如,汽车音响系统,音频组合系统);笔记本个人电脑;游戏机设备;便携式信息终端(诸如,移动计算机,移动电话,移动游戏设备或电子图书);以及配备有记录媒体的图象重放设备(具体地,执行记录媒体的重放和配备有能够显示那些图象的显示装置的设备,诸如数字视盘(DVD))。具体地,因为便携式信息终端常常从对角线方向进行观看,视场的宽度被认为是非常重要的。因此,最好是利用EL显示装置。图 17 和 18 上显示了这些电子设备的例子。

图 17A 是 EL 显示装置,包含外壳 2001,支撑架 2002,和显示部

分 2003。本发明的 EL 显示装置可被使用于显示部分 2003。因为 EL 显示装置是不需要背光的自发射型器件,它的显示部分可以做得比液晶显示器件更薄。

图 17B 是摄像机,包含主体 2101,显示部分 2102,音频输入部分 2103,操作开关 2104,电池 2105,和图象接收部分 2106。本发明的 EL 显示部分可被使用于显示部分 2102。

图 17C 是头戴式电光设备(右面)的一部分,包含主体 2201,信号电缆 2202,头部固定带 2203,屏幕部分 2204,光学系统 2205,和显示部分 2206。本发明的 EL 显示部分可被使用于显示部分 2206。

图 17D 是配备有记录媒体的图象重放设备(具体地,DVD 重放设备),包含主体2301,记录媒体(诸如DVD)2302,操作开关2303,显示部分(a)2304 和显示部分(b)2305。显示部分(a)2304 主要用来显示图象信息,以及显示部分(b)2305 主要用来显示字符信息,本发明的EL显示部分可被使用于显示部分(a)2304 和显示部分(b)2305。

图 17E 是防护镜型显示装置(头戴式显示装置),包含主体 2401,显示部分 2402,和托架部分 2403。本发明的 EL显示部分可被使用于显示部分 2402。

图 17F 是个人计算机,包含主体 2501,保护套 2502,显示部分 2503,和键盘 2504。本发明的 EL 显示部分可被使用于显示部分 2503。

应当指出,如果 EL 材料的发射亮度在将来变成为更高,将有可能把本发明的 EL 显示装置使用于前向型或后向型投影仪中,通过投影包括输出图象的光,它可被透镜等放大。

以上的电子设备正变成为更经常用来显示通过电子电信线路(诸如互联网或 CATV(有线电视))所提供的信息,特别是,用于显示活动信息的机会正在增加。有机 EL 材料的响应速度是极高的,所以,EL 显示装置对于执行活动显示是有利的。

因为 EL 显示装置的光发射部分消耗功率,最好是显示信息,使得发射部分变为尽可能小。所以,当在主要显示字符信息的显示部分(诸如便携式信息终端,具体地,便携式电话和音频重放设备)中使用 EL 显示装置时,最好是通过把非发射部分设置为背景以及在发射部分中形成字符信息,而来驱动它。

图 18A 是便携式电话机,包含主体 2601,音频输出部分 2602,

音频输入部分 2603,显示部分 2604,操作开关 2605,和天线 2606。本发明的 EL显示部分可被使用于显示部分 2604。应当指出,通过在显示部分 2604 的黑色背景中显示白色字符,可以减小便携式电话机的功率消耗。

图 18B 是音频重放设备,具体地,汽车音响系统,包含主体 2701,显示部分 2702,和操作开关 2703 与 2704。本发明的 EL 显示部分可被使用于显示部分 2702。而且,在实施例 6 中显示了用于汽车的音频重放设备被显示,但它也可被使用于便携型和家用型音频重放设备。应当指出,通过在显示部分 2702 的黑色背景中显示白色字符,功率消耗可被减小。这在便携型音频重放设备中是特别有效的。

因此,本发明的应用范围极宽,以及有可能把本发明应用到所有领域中的电子设备。而且,实施例 6 能够以与实施例 1 到 5 的任何结构的组合形式被实施。

本发明的可应用范围极宽,以及有可能在所有领域中的电子设备中使用本发明。而且,实施例6中的电子设备也可使用具有实施例1到5所示的任何结构的EL显示装置。

在本发明中,接通时间间隔和关断时间间隔被划分,以及交替出现在一个帧周期内。所以,即使观察者的视点稍微左右和上下移动,观察者的视点不断地只固定在被关断的象素,或反之不断地只固定在被接通的象素的或然率,可被降低。所以,可以防止看见在由二进制码方法进行的时分驱动中很显著的、诸如虚假轮廓线那样的显示的障碍。

图 2A

图 2B

图 4

图 5

图 7

58

图 10A

图 10B

冬

18B

图 20A

图 20B

| 专利名称(译)        | 驱动电致发光显示装置的方法                                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | CN100334607C                                                                                                                                                        | 公开(公告)日 | 2007-08-29 |

| 申请号            | CN01132557.7                                                                                                                                                        | 申请日     | 2001-09-04 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                                                                                        |         |            |

| [标]发明人         | 犬饲和隆<br>纳光明<br>岩渕友幸                                                                                                                                                 |         |            |

| 发明人            | 犬饲和隆<br>纳光明<br>岩渕友幸                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/00 G02F1/061 G09G3/30 G09F9/30 G09G3/20 G09G3/32 H01L21/77 H01L21/84 H01L27/12 H01L27/32 H01L51/50 H05B33/14                                                  |         |            |

| CPC分类号         | G09G2310/0251 G09G2300/0809 G09G3/3275 G09G3/2022 G09G2300/0842 G09G2320/0266 G09G3 /3266 G09G3/2033 G09G2320/0247 G09G2310/027 H01L27/1214 G09G2320/0261 H01L27/12 |         |            |

| 代理人(译)         | 王岳                                                                                                                                                                  |         |            |

| 审查员(译)         | 贾允                                                                                                                                                                  |         |            |

| 优先权            | 2000267164 2000-09-04 JP                                                                                                                                            |         |            |

| 其他公开文献         | CN1342964A                                                                                                                                                          |         |            |

| 外部链接           | Espacenet SIPO                                                                                                                                                      |         |            |

## 摘要(译)

提供了其中很难看到虚假轮廓线的驱动EL显示装置的方法。驱动EL显示装置的方法,其中形成多个象素,每个象素具有第一TFT(薄膜晶体管),第二TFT,第三TFT,和有机EL元件,具有以下特征:在一个帧周期内出现n+m个显示时间间隔(其中n和m都是自然数);n+m个显示时间间隔,每个相应于在数字视频信号的n比特中间的数字视频信号的一个比特;在n+m个显示时间间隔中间,多个显示时间间隔相应于数字视频信号的同一个比特;以及在n+m个显示时间间隔中间,相应于数字视频信号的其它比特的显示时间间隔在多个显示时间间隔期间出现。