(12) 发明专利申请

(10) 申请公布号 CN 102097055 A

(43) 申请公布日 2011.06.15

(21) 申请号 201110065963.6

(22) 申请日 2007.10.01

(30) 优先权数据

2007-058021 2007.03.08 JP

(62) 分案原申请数据

200780049722.4 2007.10.01

(71) 申请人 夏普株式会社

地址 日本大阪府

(72) 发明人 岸宣孝

(74) 专利代理机构 上海专利商标事务所有限公司 31100

代理人 张鑫

(51) Int. Cl.

G09G 3/32 (2006.01)

权利要求书 2 页 说明书 15 页 附图 12 页

(54) 发明名称

显示装置及其驱动方法

(57) 摘要

本发明涉及一种显示装置及其驱动方法。使像素电路(10)内的开关用 TFT(12、13)导通,使开关用 TFT(14)截止,将与驱动用 TFT(11)的阈值电压对应的电压(VDD+Vx)输出到数据线(Sj),使源极驱动器电路的开关(21、22)导通,将电压(Vx)保持在电容(26)中。接着使开关用 TFT(13)截止,切换开关(21~24)的状态,向数据线(Sj)施加电压(Vdata+Vx)。进一步使开关用 TFT(12)截止,使开关用 TFT(14)导通,向有机 EL 元件(15)提供由驱动用 TFT(11)的栅极端子电压(Vdata+Vx)确定的电流。由此,来高效利用数据电压的振幅,并以高精度补偿驱动用 TFT(11)的阈值电压的偏差,而不使像素电路(10)的规模增大。

1. 一种显示装置,该显示装置是电流驱动型的,其特征在于,具有:

多个像素电路,该多个像素电路与多个扫描线和多个数据线的各交叉点对应配置,分别包含电光元件和驱动元件,所述驱动元件的控制端子通过开关元件与所述数据线连接;

扫描信号输出电路,该扫描信号输出电路使用所述扫描线来选择写入对象的像素电路,并且进行控制,从而使得在阈值校正期间施加到所述驱动元件的施加电压接近所述驱动元件的阈值电压,且使阈值校正期间结束时的所述施加电压从所选择的像素电路输出到所述数据线;及

显示信号输出电路,该显示信号输出电路根据输出到所述数据线的电压,将对数据电压加上或减去校正电压后的电压施加到所述数据线,所述数据电压与显示数据对应,所述校正电压与所述阈值电压对应,

所述阈值校正期间在所述施加电压到达所述阈值电压之前结束。

2. 如权利要求1所述的显示装置,其特征在于,

所述电光元件及所述驱动元件在所述像素电路内串联设置在两根电源布线之间,所述像素电路还包括:

第一开关元件,该第一开关元件与所述驱动元件的控制端子和所述数据线连接;

第二开关元件,该第二开关元件设置在所述驱动元件的控制端子和一侧的导通端子之间;

第三开关元件,该第三开关元件与所述电光元件及所述驱动元件一起串联设置在所述电源布线之间;及

电容,该电容的一端与所述驱动元件的控制端子连接。

3. 如权利要求2所述的显示装置,其特征在于,

所述扫描信号输出电路对写入对象的像素电路进行控制,在阈值校正期间,将所述第一及第二开关元件设定成导通状态,将所述第三开关元件设定成非导通状态,接着使所述第二开关元件变化成非导通状态,进一步使所述第一开关元件变化成非导通状态,使所述第三开关元件变化成导通状态,

所述显示信号输出电路根据所述第二开关元件处于导通状态时的所述数据线的电压,在所述第二开关元件变化成非导通状态后,将对所述数据电压加上或减去所述校正电压后的电压施加到所述数据线。

4. 如权利要求2所述的显示装置,其特征在于,

所述驱动元件及所述第一、第二、及第三开关元件为薄膜晶体管,

所述第一及第三开关元件中,一个为P沟道型,另一个为N沟道型,两者的控制端子与公共的布线连接。

5. 如权利要求2所述的显示装置,其特征在于,

所述驱动元件及所述第一、第二、及第三开关元件为薄膜晶体管,

所述第二及第三开关元件中,一个为P沟道型,另一个为N沟道型,两者的控制端子与公共的布线连接。

6. 如权利要求2所述的显示装置,其特征在于,

所述驱动元件为P沟道型的增强型晶体管,

由所述扫描信号输出电路所选择的像素电路,将从所述电源布线的电压中较高的电压

减去阈值校正期间结束时的所述施加电压的绝对值后的电压,输出到所述数据线。

7. 如权利要求 2 所述的显示装置,其特征在于,

所述驱动元件为 N 沟道型的增强型晶体管,

由所述扫描信号输出电路所选择的像素电路,将对所述电源布线的电压中较低的电压加上阈值校正期间结束时的所述施加电压的绝对值后的电压,输出到所述数据线。

8. 如权利要求 2 所述的显示装置,其特征在于,

所述显示信号输出电路在所述第一开关元件的导通期间的一部分期间,向所述数据线施加预定的固定电压。

9. 如权利要求 1 所述的显示装置,其特征在于,

所述显示信号输出电路包括多个模拟缓冲器、以及对每个所述数据线设置的多个校正用电容和多个开关电路,

所述开关电路进行切换,从而将所述校正用电容的一侧的电极与所述数据线连接,并向另一侧的电极施加预定的固定电压,或者将所述校正用电容的一侧的电极通过所述模拟缓冲器与所述数据线连接,并向另一侧的电极施加所述数据电压。

10. 如权利要求 9 所述的显示装置,其特征在于,

对每个所述数据线设置所述模拟缓冲器。

11. 一种显示装置的驱动方法,所述显示装置具有多个像素电路,该多个像素电路与多个扫描线和多个数据线的各交叉点对应配置,分别包含电光元件和驱动元件,所述驱动元件的控制端子通过开关元件与所述数据线连接,其特征在于,包括如下步骤:

使用所述扫描线来选择写入对象的像素电路,并且进行控制,从而使得在阈值校正期间施加到所述驱动元件的施加电压接近所述驱动元件的阈值电压,且使阈值校正期间结束时的所述施加电压从所选择的像素电路输出到所述数据线的步骤;及

根据输出到所述数据线的电压、将对数据电压加上或减去校正电压后的电压施加到所述数据线的步骤,所述数据电压与显示数据对应,所述校正电压与所述阈值电压对应,

所述阈值校正期间在所述施加电压到达所述阈值电压之前结束。

## 显示装置及其驱动方法

[0001] 本发明申请是申请人于 2009 年 7 月 7 日提交的,申请号为 200780049722.4,发明名称为“显示装置及其驱动方法”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及一种显示装置,更特别是涉及有机 EL 显示器或 FED 等使用了电流驱动元件的显示装置及其驱动方法。

### 背景技术

[0003] 近年来,随着对于薄型、质量轻、可高速响应的显示器的需求的增长,对于有机 EL(Electro Luminescence :电致发光) 显示器或 FED(FieldEmission Display :场致发射显示器) 的研发日益活跃。

[0004] 有机 EL 显示器中包含的有机 EL 元件其施加的电压越高,流过的电流越大,则其发光亮度越高。然而,有机 EL 元件的亮度和电压之间的关系容易受驱动时间或周边温度等的影响而变动。因此,若对有机 EL 显示器采用电压控制型的驱动方式,则要抑制有机 EL 元件的亮度的偏差是非常困难的。与此不同的是,有机 EL 元件的亮度与电流大致成正比,该正比关系不易受周边温度等外界因素的影响,因而,最好对有机 EL 显示器采用电流控制型的驱动方式。

[0005] 另一方面,显示装置的像素电路或驱动电路使用由非晶硅、低温多晶硅、CG(Continuous Grain :连续晶粒) 硅等构成的 TFT(Thin Film Transistor :薄膜晶体管) 来构成。然而,在 TFT 的特性(例如阈值电压或迁移率) 中容易产生偏差。因此,在有机 EL 显示器的像素电路中设置对 TFT 的特性的偏差进行补偿的电路,利用该电路的作用来抑制有机 EL 元件的亮度的偏差。

[0006] 在电流控制型的驱动方法中,对 TFT 的特性的偏差进行补偿的方式大致分为用电流信号来控制流过驱动用 TFT 的电流量的电流编程方式、和用电压信号来控制该电流量的电压编程方式。若使用电流编程方式,则能对阈值电压和迁移率的偏差进行补偿,若使用电压编程方式,则只能对阈值电压的偏差进行补偿。

[0007] 然而,电流编程方式中存在如下问题,第一,由于是处理非常微小量的电流,因此像素电路或驱动电路的设计较为困难,第二,由于在设定电流信号的期间受寄生电容的影响较大,因此难以将面积做大。与此不同的是,电压编程方式中,寄生电容等的影响很小,电路设计也比较容易。另外,迁移率的偏差对电流量带来的影响、相比阈值电压的偏差对电流量带来的影响要小,而迁移率的偏差可在 TFT 制造工艺中在某种程度上将其抑制住。因而,即使是采用电压编程方式的显示装置,也能得到相当好的显示品质。

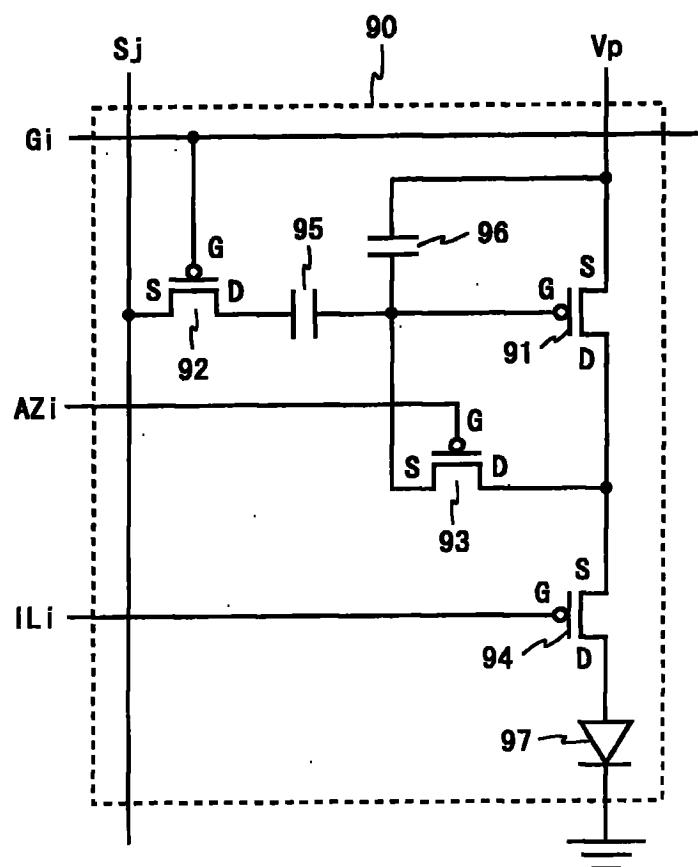

[0008] 对于采用电流驱动型的驱动方式的有机 EL 显示器,以往已知有如下所示的像素电路。图 11 是专利文献 1 所记载的像素电路的电路图。图 11 所示的像素电路 90 具有驱动用 TFT91、开关用 TFT92 ~ 94、电容 95、96、及有机 EL 元件 97(也称为 OLED :Organic Light Emitting Diode(有机发光二极管))。像素电路 90 中包含的 TFT 都为 P 沟道型。

[0009] 像素电路 90 中, 驱动用 TFT91、开关用 TFT94 及有机 EL 元件 97 以该顺序串联设置在电源布线 Vp (电位为 VDD) 和共用阴极 (GND) 之间。电容 95 和开关用 TFT92 以该顺序串联设置在驱动用 TFT91 的栅极端子和数据线 Sj 之间。开关用 TFT93 设置在驱动用 TFT91 的栅极端子和漏极端子之间, 电容 96 设置在驱动用 TFT91 的栅极端子和电源布线 Vp 之间。开关用 TFT92、93、94 的栅极端子分别与扫描线 Gi、自动归零线 AZi 及照明线 ILi 连接。

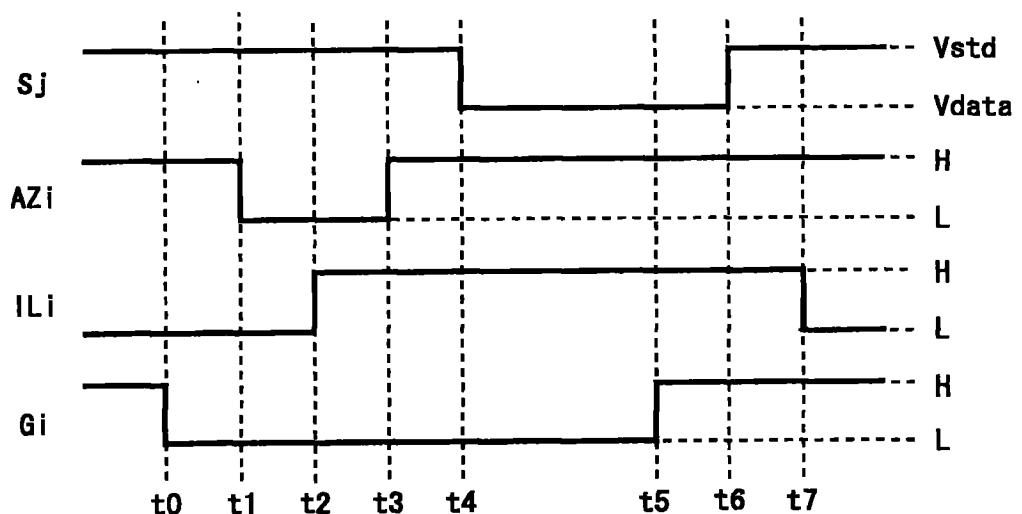

[0010] 图 12 是对像素电路 90 进行数据写入时的时序图。在时刻 t0 之前, 扫描线 Gi 和自动归零线 AZi 的电位被控制成高电平, 照明线 ILi 的电位被控制成低电平, 数据线 Sj 的电位被控制成基准电位 Vstd。在时刻 t0, 扫描线 Gi 的电位变化成低电位时, 则开关用 TFT92 变化成导通状态。接着在时刻 t1, 自动归零线 AZi 的电位变化成低电平时, 则开关用 TFT93 变化成导通状态。由此, 驱动用 TFT91 的栅极端子和漏极端子成为相同电位。

[0011] 接着在时刻 t2, 照明线 ILi 的电位变化成高电平时, 则开关用 TFT94 变化成非导通状态。此时, 电流从电源布线 Vp 经由驱动用 TFT91 和开关用 TFT93 流入到驱动用 TFT91 的栅极端子, 驱动用 TFT91 的栅极端子电位在驱动用 TFT91 为导通状态的期间上升。驱动用 TFT91 的栅极 - 源极之间的电压变成阈值电压 Vth (负值) (即栅极端子电位变成 (VDD+Vth)) 时, 则变化成非导通状态。因而, 驱动用 TFT91 的栅极端子电位上升直到 (VDD+Vth) 为止。

[0012] 接着在时刻 t3, 自动归零线 AZi 的电位变化成高电平时, 则开关用 TFT93 变化成非导通状态。此时在电容 95 中, 保持驱动用 TFT91 的栅极端子和数据线 Sj 之间的电位差 (VDD+Vth-Vstd)。

[0013] 接着在时刻 t4, 数据线 Sj 的电位从基准电位 Vstd 变成数据电位 Vdata 时, 则驱动用 TFT91 的栅极端子电位变化相同的量 (Vdata-Vstd), 成为 (VDD+Vth+Vdata-Vstd)。接着在时刻 t5, 扫描线 Gi 的电位变化成高电平时, 则开关用 TFT92 变化成非导通状态。此时在电容 96 中, 保持驱动用 TFT91 的栅极 - 源极之间的电压 (Vth+Vdata-Vstd)。接着在时刻 t6, 数据线 Sj 的电位从数据电位 Vdata 变成基准电位 Vstd。

[0014] 接着在时刻 t7, 照明线 ILi 的电位变化成低电平时, 则开关用 TFT94 变化成导通状态。由此, 电流从电源布线 Vp 经由驱动用 TFT91 和开关用 TFT94 流到有机 EL 元件 97。流过驱动用 TFT91 的电流量根据栅极端子电位 (VDD+Vth+Vdata-Vstd) 而增减, 但即使阈值电压 Vth 不同, 只要电位差 (Vdata-Vstd) 相同, 电流量便相同。因而, 与电位 Vdata 对应的量的电流流到有机 EL 元件 97, 有机 EL 元件 97 以和数据电压 Vdata 对应的亮度发光, 而不取决于阈值电压 Vth 的值。

[0015] 除此以外, 对于有机 EL 显示器而言, 还已知有在像素电路的外部设置阈值校正电路的方法、和将阈值校正期间设定得比像素电路的选择期间要长的方法。例如, 专利文献 2 中记载了如下方法, 即, 测定驱动元件的电流能力, 将其存储在设于像素电路的外部的存储器中, 根据存储的电流能力使提供给面板的电压变化 (参照图 13)。另外, 专利文献 3 中记载了如下方法, 即, 为了将阈值校正期间设定得比选择期间要长, 在耦合电容的一端设置用于提供初始电压的开关。

[0016] 专利文献 1 : 国际公开第 98/48403 号小册子

[0017] 专利文献 2 : 日本国专利特开 2002-278513 号公报

[0018] 专利文献 3 : 日本国专利特开 2004-133240 号公报

[0019] 如上所述,若使用图 11 所示的像素电路,则能够对驱动用 TFT91 的阈值电压的偏差进行补偿,并以所要的亮度使有机 EL 元件 97 发光。然而,该像素电路(以下称为现有的像素电路)中存在如下问题。

[0020] 第一个问题不能高效利用数据电压的振幅。现有的像素电路中,由于利用电容耦合进行数据写入,因此即使从像素电路的外部写入某一数据电压,作为过驱动电压实际施加到驱动用 TFT 的电压也变成其  $C_c / (C_c + C_s + C_{gs})$  倍(这里,  $C_c$  为电容 95 的电容量,  $C_s$  为电容 96 的电容量,  $C_{gs}$  为驱动用 TFT91 的栅极-源极之间的电容量)。由于这样不能高效利用数据电压,因此数据驱动器电路的功耗增大。若极端增大耦合电容  $C_c$ ,则虽然能高效利用数据电压的振幅,但那样的话像素电路的面积增大。另外,还存在如下问题,即,无法以高精度进行控制的寄生电容  $C_{gs}$  会给驱动电压带来影响。

[0021] 第二个问题是阈值校正的精度较低。如上所述,由于实际的驱动电压变成从外部提供的电压的  $C_c / (C_c + C_s + C_{gs})$  倍,因此阈值校正的效果也变成  $C_c / (C_c + C_s + C_{gs})$  倍。因此,难以完全校正阈值电压。

[0022] 第三个问题是像素电路的规模变大。如上所述,作为应对寄生电容的措施而使耦合电容  $C_c$  增大时,则像素电路的布局中电容 95 所占的面积增大。因此,在使光从基板下部射出的底部发光结构的有机 EL 显示器中,开口率降低。另外,由于电路面积的增大成为制造时的成品率降低的主要原因,因此需要减少像素电路的面积和元件数量。

[0023] 第四个问题是在制造时难以进行检查。现有的像素电路中,由于驱动用 TFT 的栅极端子通过电容与数据线连接,因此难以经由数据线检查驱动用 TFT 的电流。因此,难以通过检查来提高成品率。

[0024] 第五个问题是阈值校正期间被限制在较短的时间。现有的像素电路中,需要在像素电路的选择期间内进行阈值校正和数据写入。为了进行阈值校正,需要直到二极管连接的驱动元件的栅极-源极之间的电压与阈值电压充分接近为止所需的时间。然而,在高清晰的显示装置中,选择期间的长度变得极短。例如,在以 60 帧 / s 驱动分辨率为 VGA 的面板的情况下,选择期间约为 30  $\mu$  s。在这这么短的时间中要完成阈值校正和数据写入是困难的。

[0025] 根据专利文献 2 所记载的方法,虽然能解决上述第三个问题,但为了设置存储各驱动元件的电流能力的存储器,周边电路的成本和布局面积增大。另外,根据专利文献 3 所记载的方法,虽然能解决上述第五个问题,但为了设置提供初始电压的开关,像素电路的规模进一步变大。

## 发明内容

[0026] 因而,本发明的目的在于提供高效利用数据电压的振幅、并以高精度进行阈值校正、而不使像素电路的规模增大的显示装置。

[0027] 本发明的第 1 方面是电流驱动型的显示装置,具有:

[0028] 多个像素电路,该多个像素电路与多个扫描线和多个数据线的各交叉点对应配置,分别包含电光元件和驱动元件,所述驱动元件的控制端子通过开关元件与所述数据线连接;

[0029] 扫描信号输出电路,该扫描信号输出电路使用所述扫描线来选择写入对象的像素电路,并且进行控制,使得与所述驱动元件的阈值电压对应的电压从所选择的像素电路输

出到所述数据线；及

[0030] 显示信号输出电路，该显示信号输出电路根据输出到所述数据线的电压，将对与显示数据对应的数据电压加上或减去与所述阈值电压对应的校正电压后的电压施加到所述数据线。

[0031] 本发明的第 2 方面是在本发明的第 1 方面中，其特征为，

[0032] 所述电光元件及所述驱动元件在所述像素电路内串联设置在两根电源布线之间，

[0033] 所述像素电路还包括：

[0034] 第一开关元件，该第一开关元件与所述驱动元件的控制端子和所述数据线连接；

[0035] 第二开关元件，该第二开关元件设置在所述驱动元件的控制端子和一侧的导通端子之间；

[0036] 第三开关元件，该第三开关元件与所述电光元件及所述驱动元件一起串联设置在所述电源布线之间；及

[0037] 电容，该电容的一端与所述驱动元件的控制端子连接。

[0038] 本发明的第 3 方面是在本发明的第 2 方面中，其特征为，

[0039] 所述扫描信号输出电路对写入对象的像素电路进行控制，将所述第一及第二开关元件设定成导通状态，将所述第三开关元件设定成非导通状态，接着使所述第二开关元件变化成非导通状态，进一步使所述第一开关元件变化成非导通状态，使所述第三开关元件变化成导通状态，

[0040] 所述显示信号输出电路根据所述第二开关元件处于导通状态时的所述数据线的电压，在所述第二开关元件变化成非导通状态后，将对所述数据电压加上或减去所述校正电压后的电压施加到所述数据线。

[0041] 本发明的第 4 方面是在本发明的第 2 方面中，其特征为，

[0042] 所述驱动元件及所述第一、第二、及第三开关元件为薄膜晶体管，

[0043] 所述第一及第三开关元件中，一个为 P 沟道型，另一个为 N 沟道型，两者的控制端子与公共的布线连接。

[0044] 本发明的第 5 方面是在本发明的第 2 方面中，其特征为，

[0045] 所述驱动元件及所述第一、第二、及第三开关元件为薄膜晶体管，

[0046] 所述第二及第三开关元件中，一个为 P 沟道型，另一个为 N 沟道型，两者的控制端子与公共的布线连接。

[0047] 本发明的第 6 方面是在本发明的第 2 方面中，其特征为，

[0048] 所述驱动元件为 P 沟道型的增强型晶体管，

[0049] 由所述扫描信号输出电路所选择的像素电路，将从所述电源布线的电压中的较高的电压减去与所述驱动元件的阈值电压对应的电压的绝对值后的电压，输出到所述数据线。

[0050] 本发明的第 7 方面是在本发明的第 2 方面中，其特征为，

[0051] 所述驱动元件为 N 沟道型的增强型晶体管，

[0052] 由所述扫描信号输出电路所选择的像素电路，将对所述电源布线的电压中的较低的电压加上与所述驱动元件的阈值电压对应的电压的绝对值后的电压，输出到所述数据线。

[0053] 本发明的第 8 方面是在本发明的第 2 方面中,其特征为,

[0054] 所述显示信号输出电路在所述第一开关元件的导通期间的一部分期间,向所述数据线施加预定的固定电压。

[0055] 本发明的第 9 方面是在本发明的第 1 方面中,其特征为,

[0056] 所述显示信号输出电路包括多个模拟缓冲器、对每一所述数据线设置的多个校正用电容、及多个开关电路,

[0057] 所述开关电路进行切换,使得将所述校正用电容的一侧的电极与所述数据线连接,并向另一侧的电极施加预定的固定电压,或者将所述校正用电容的一侧的电极通过所述模拟缓冲器与所述数据线连接,并向另一侧的电极施加所述数据电压。

[0058] 本发明的第 10 方面是在本发明的第 9 方面中,其特征为,

[0059] 对每多个所述数据线设置所述模拟缓冲器。

[0060] 本发明的第 11 方面是显示装置的驱动方法,所述显示装置具有多个像素电路,该多个像素电路与多个扫描线和多个数据线的各交叉点对应配置,分别包含电光元件和驱动元件,所述驱动元件的控制端子通过开关元件与所述数据线连接,包括:

[0061] 使用所述扫描线来选择写入对象的像素电路、并且进行控制使得与所述驱动元件的阈值电压对应的电压从所选择的像素电路输出到所述数据线的步骤;及

[0062] 根据输出到所述数据线的电压、将对与显示数据对应的数据电压加上或减去与所述阈值电压对应的校正电压后的电压施加到所述数据线的步骤。

[0063] 根据本发明的第 1 或第 11 方面,能够从所选择的像素电路读出与驱动元件的阈值电压对应的电压,并将对数据电压加上或减去校正电压(与阈值电压对应的电压)后的电压提供给驱动元件的控制端子。因而,能够检测驱动元件的阈值电压以补偿阈值电压的偏差,并以所要的亮度使电光元件发光。另外,通过在像素电路的外部设置阈值校正电路,使用数据线检测阈值电压,从而能够缩小像素电路的规模和面积。另外,通过将阈值电压作为电压信号进行检测,从而与反馈电流信号的情况不同,无需电流电压变换元件,因此能够抑制校正效果的偏差。另外,由于不通过耦合电容而向驱动元件的控制端子提供所要的电压,因此能够有效利用数据电压的振幅,并减小功耗。

[0064] 根据本发明的第 2 方面,能够减少阈值校正中使用的电容,使开口率和成品率提高,并减小功耗。

[0065] 根据本发明的第 3 方面,能够将像素电路的选择期间分成检测阈值电压的期间和写入校正后的数据电压的期间,并使得用于读出阈值电压的反馈线和用于写入数据的数据线公用化。

[0066] 根据本发明的第 4 或第 5 方面,能够使得与第一、第二、及第三开关元件的控制端子连接的布线公用化以较少布线数,并进一步提高像素的开口率。

[0067] 根据本发明的第 6 方面,由于对 P 沟道型的驱动元件若将减去阈值电压的绝对值后的电压提供给控制端子便能补偿阈值电压的偏差,因此能够使用从所选择的像素电路输出的电压来对驱动电压的阈值电压的偏差进行补偿。

[0068] 根据本发明的第 7 方面,由于对 N 沟道型的驱动元件若将加上阈值电压的绝对值后的电压提供给控制端子便能补偿阈值电压的偏差,因此能够使用从所选择的像素电路输出的电压来对驱动电压的阈值电压的偏差进行补偿。

[0069] 根据本发明的第 8 方面,通过向驱动元件的控制端子提供适当的固定电压,从而能够缩短直到与驱动元件的阈值电压对应的电压被输出到数据线为止所需的时间。因而,即使在阈值校正期间较短的情况下,也能够抑制校正效果的偏差,并使画质提高。

[0070] 根据本发明的第 9 方面,显示信号输出电路能够将对数据线的电压加上“数据电压和固定电压之差”后的电压施加到数据线。因而,若适当地确定固定电压,便能够根据从像素电路输出到数据线的电压,将对数据电压加上或减去校正电压(与驱动元件的阈值电压对应的电压)后的电压施加到数据线。另外,通过在校正电容和数据线之间设置模拟缓冲器,从而能够减小像素电路的规模。另外,通过在校正电容和数据线之间设置模拟缓冲器,从而能够抑制因保持在校正用电容中的电压的耦合所造成的衰减,并实现高画质。

[0071] 根据本发明的第 10 方面,对每多个数据线配置为了对每一数据线配置而使得电路规模较大的模拟缓冲器,能够实现高清晰的显示面板。

## 附图说明

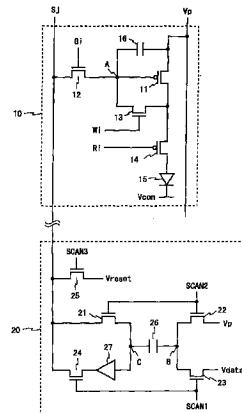

[0072] 图 1 是表示本发明的第一至第三实施方式的显示装置的结构的方框图。

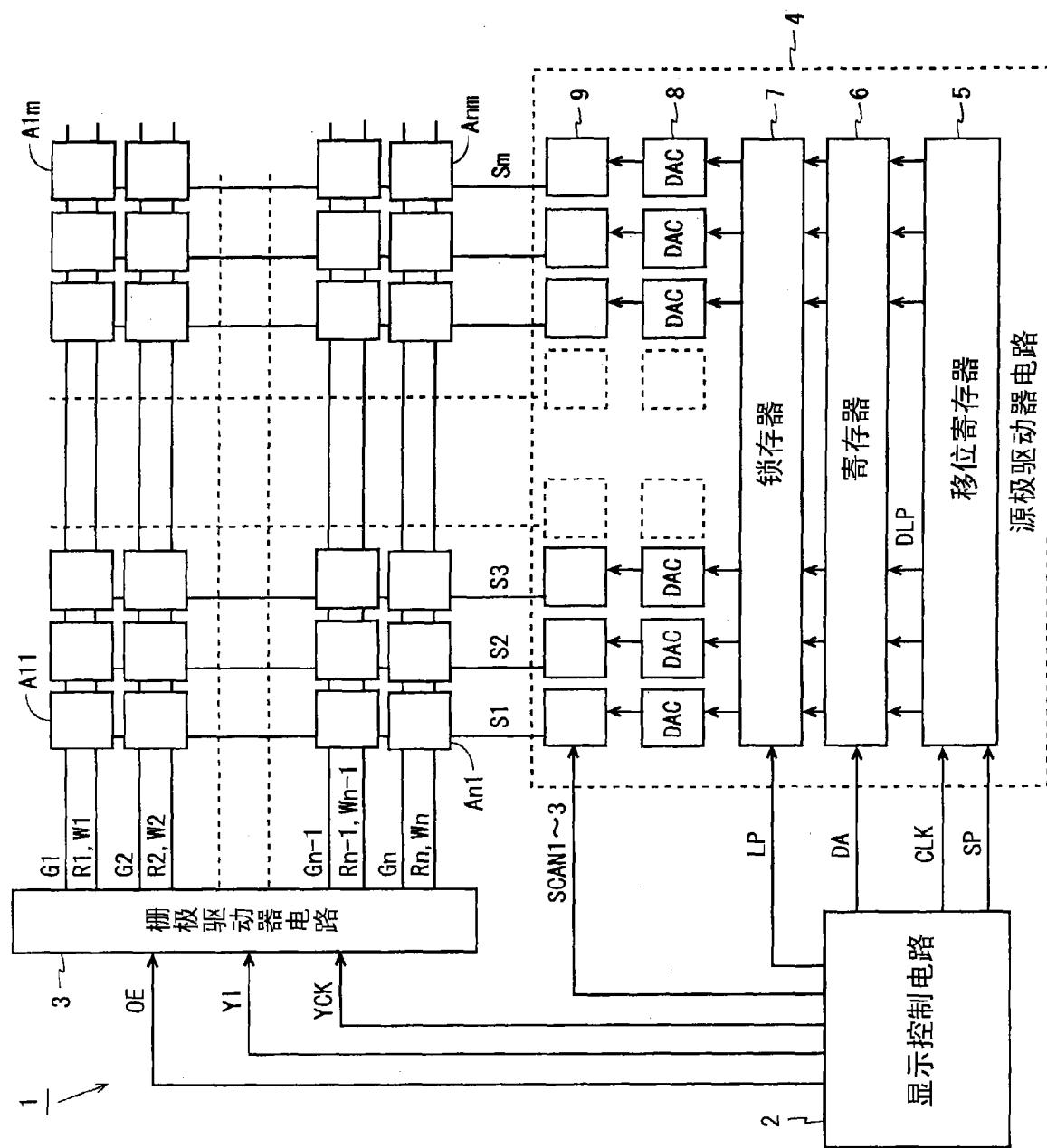

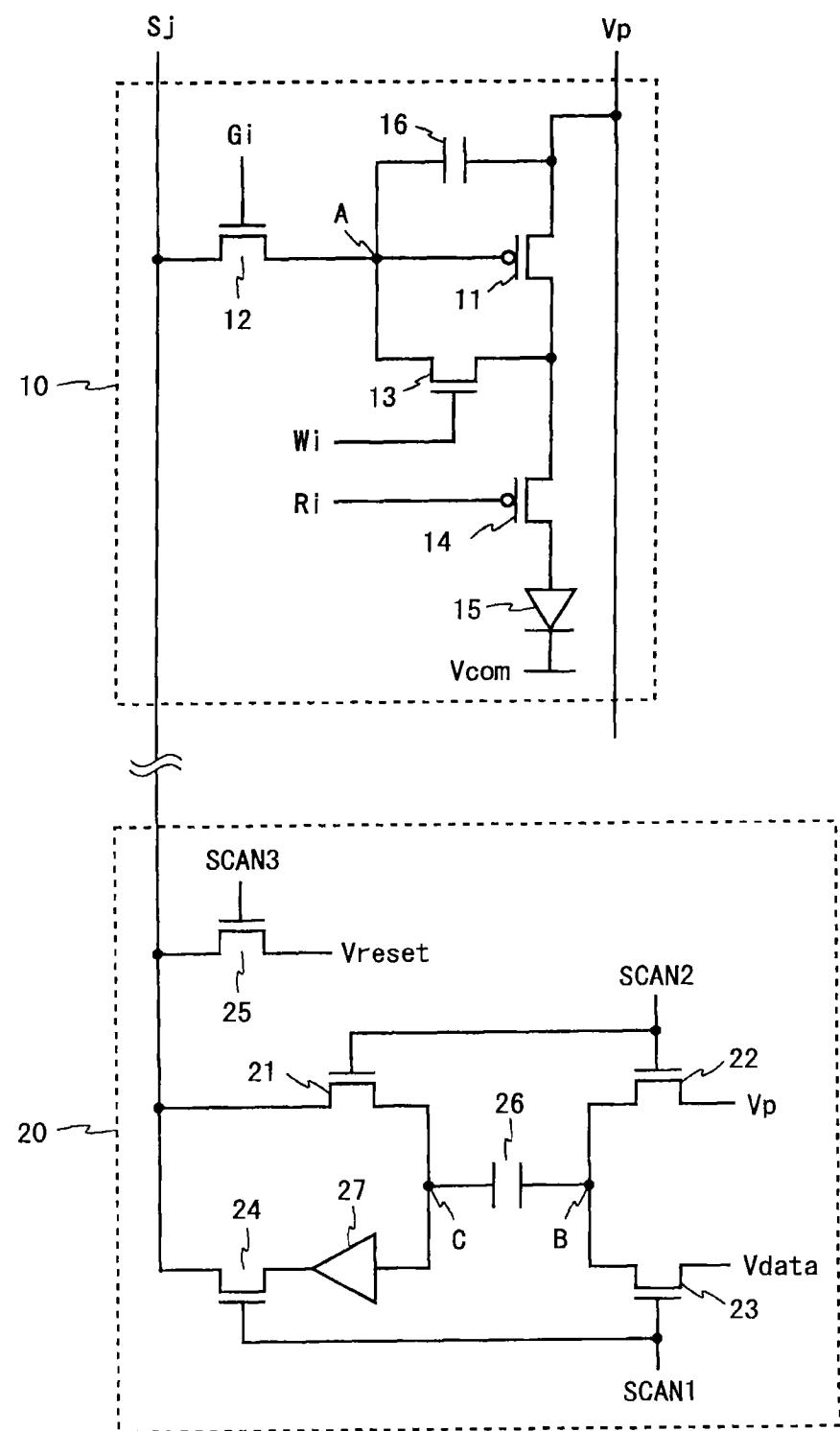

[0073] 图 2 是本发明的第一实施方式的显示装置中包含的像素电路和阈值校正电路的电路图。

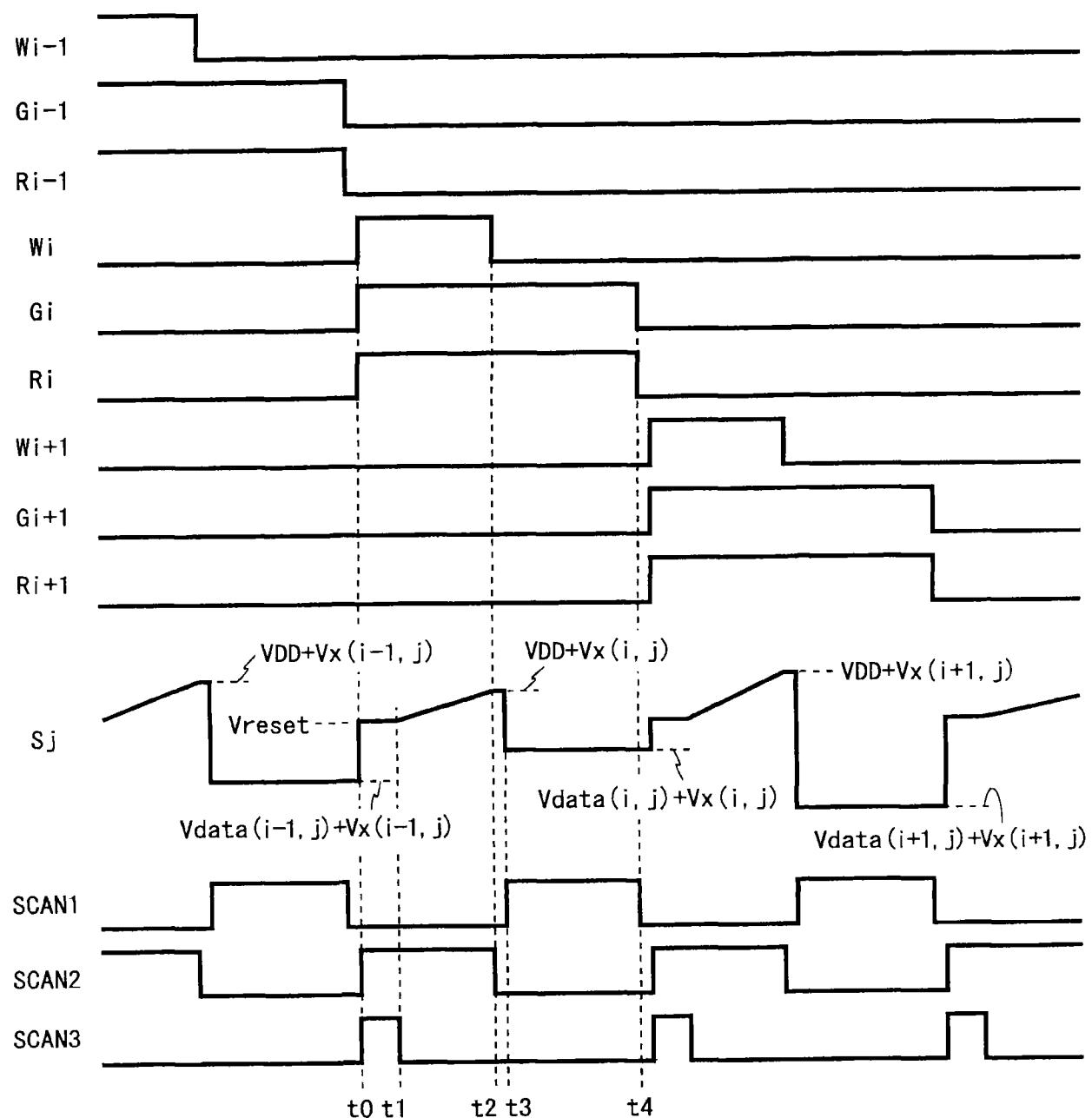

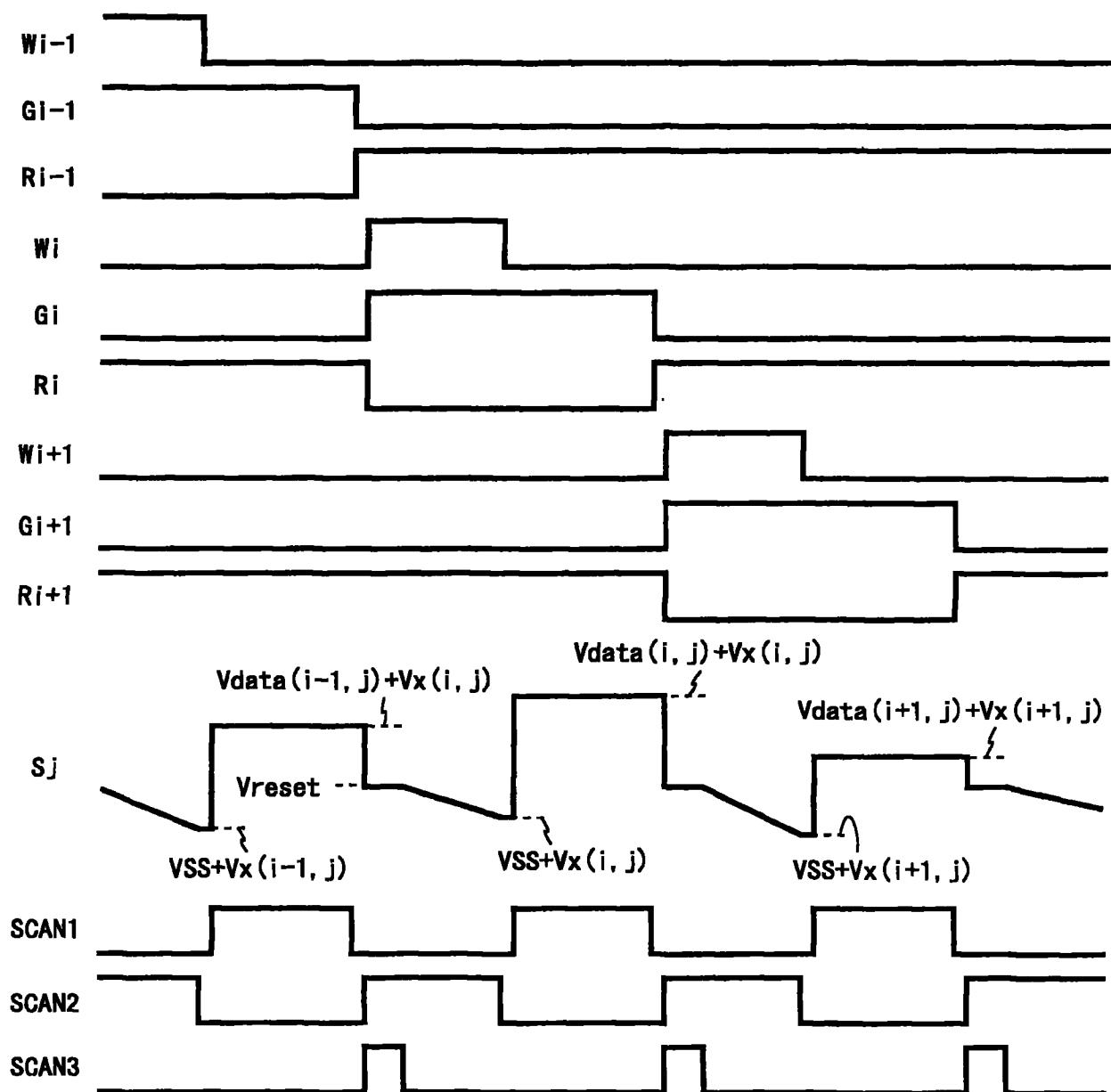

[0074] 图 3 是对本发明的第一实施方式的显示装置中的像素电路进行数据写入时的时序图。

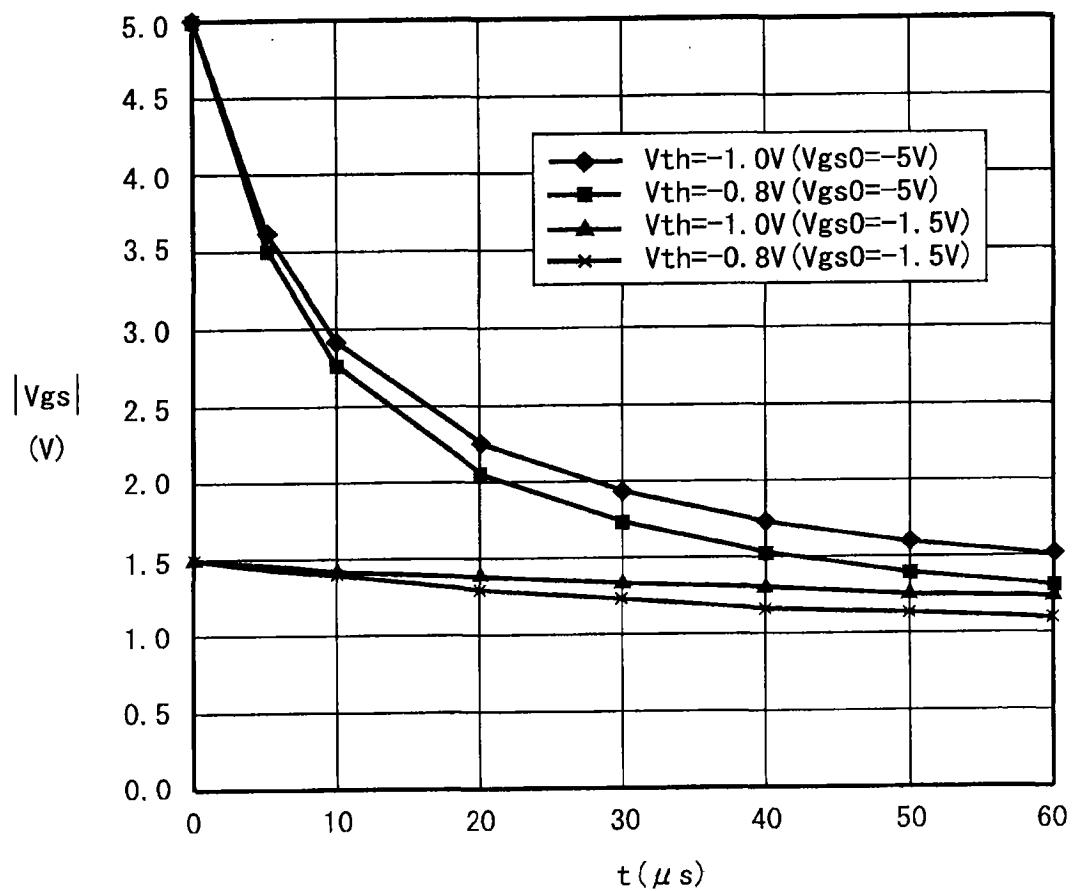

[0075] 图 4 是表示二极管连接的 TFT 中的栅极 - 源极之间的电压随时间变化的例子的图。

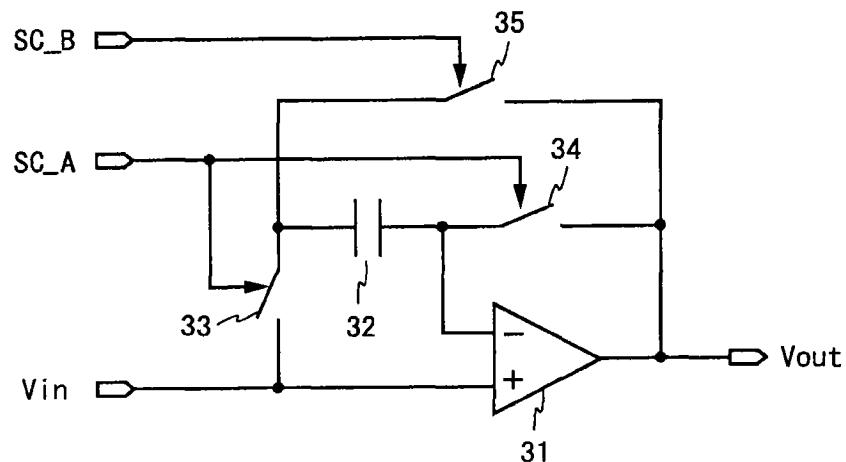

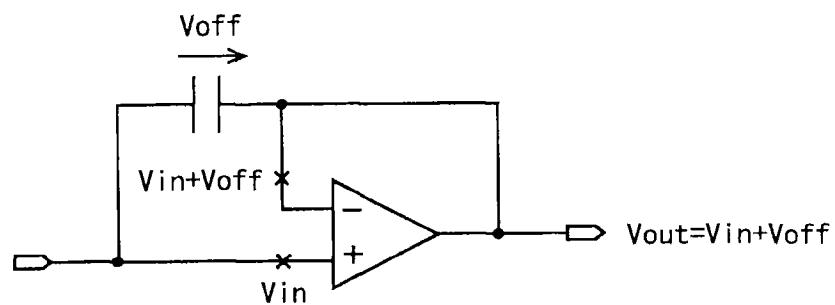

[0076] 图 5A 是具有偏移抵消功能的缓冲器的电路图。

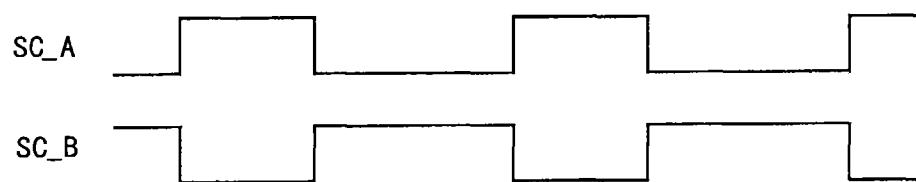

[0077] 图 5B 是图 5A 所示的缓冲器的时序图。

[0078] 图 5C 是用于说明图 5A 所示的缓冲器的动作的说明图。

[0079] 图 5D 是用于说明图 5A 所示的缓冲器的动作的说明图。

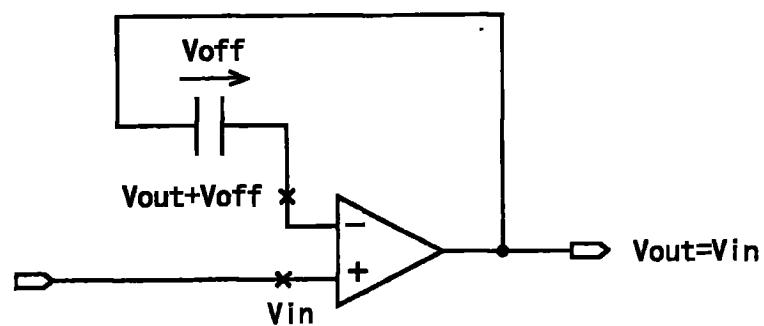

[0080] 图 6A 是本发明的第一实施方式的第一变形例的显示装置中包含的像素电路的电路图。

[0081] 图 6B 是本发明的第一实施方式的第二变形例的显示装置中包含的像素电路的电路图。

[0082] 图 7 是本发明的第二实施方式的显示装置中包含的像素电路和阈值校正电路的电路图。

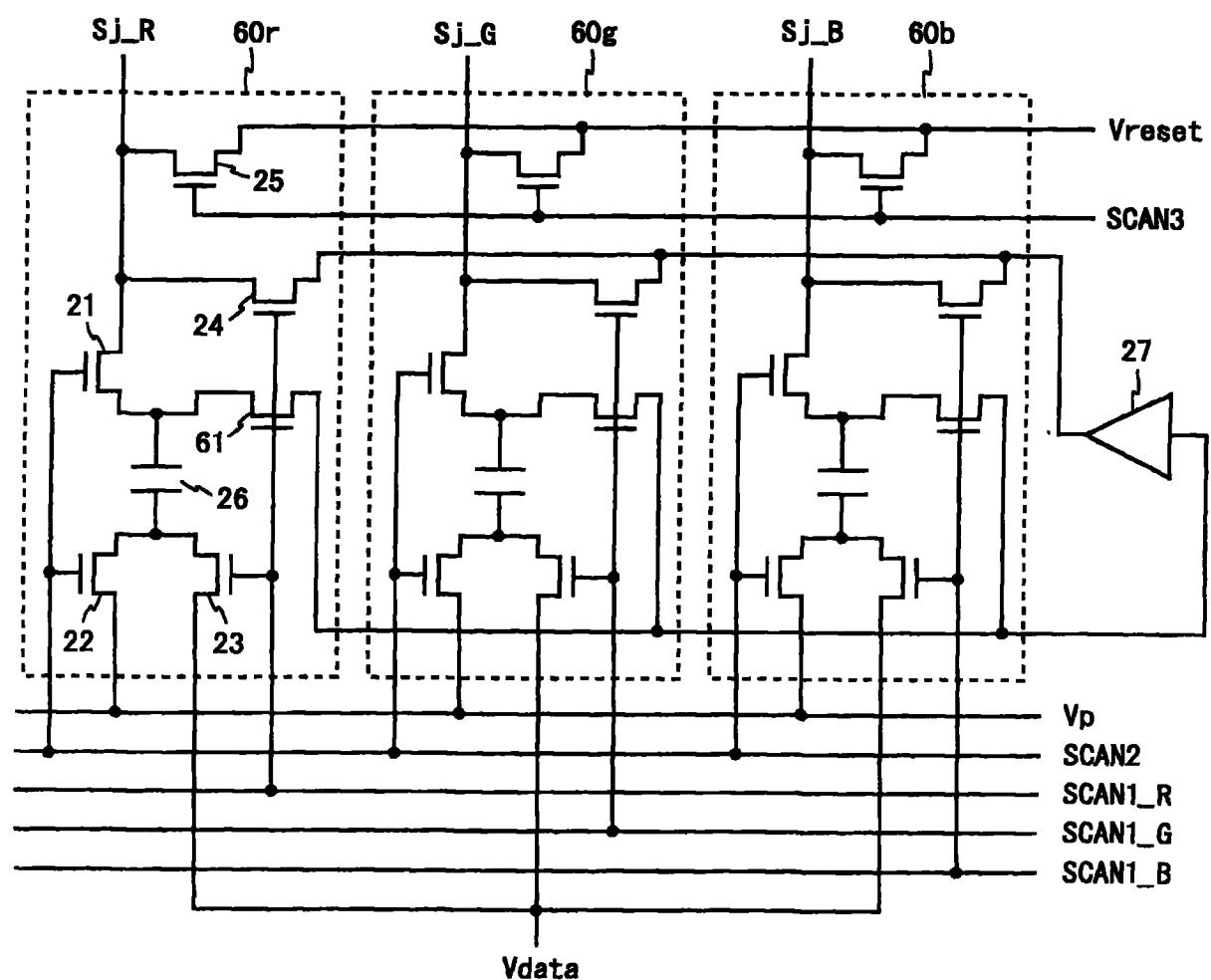

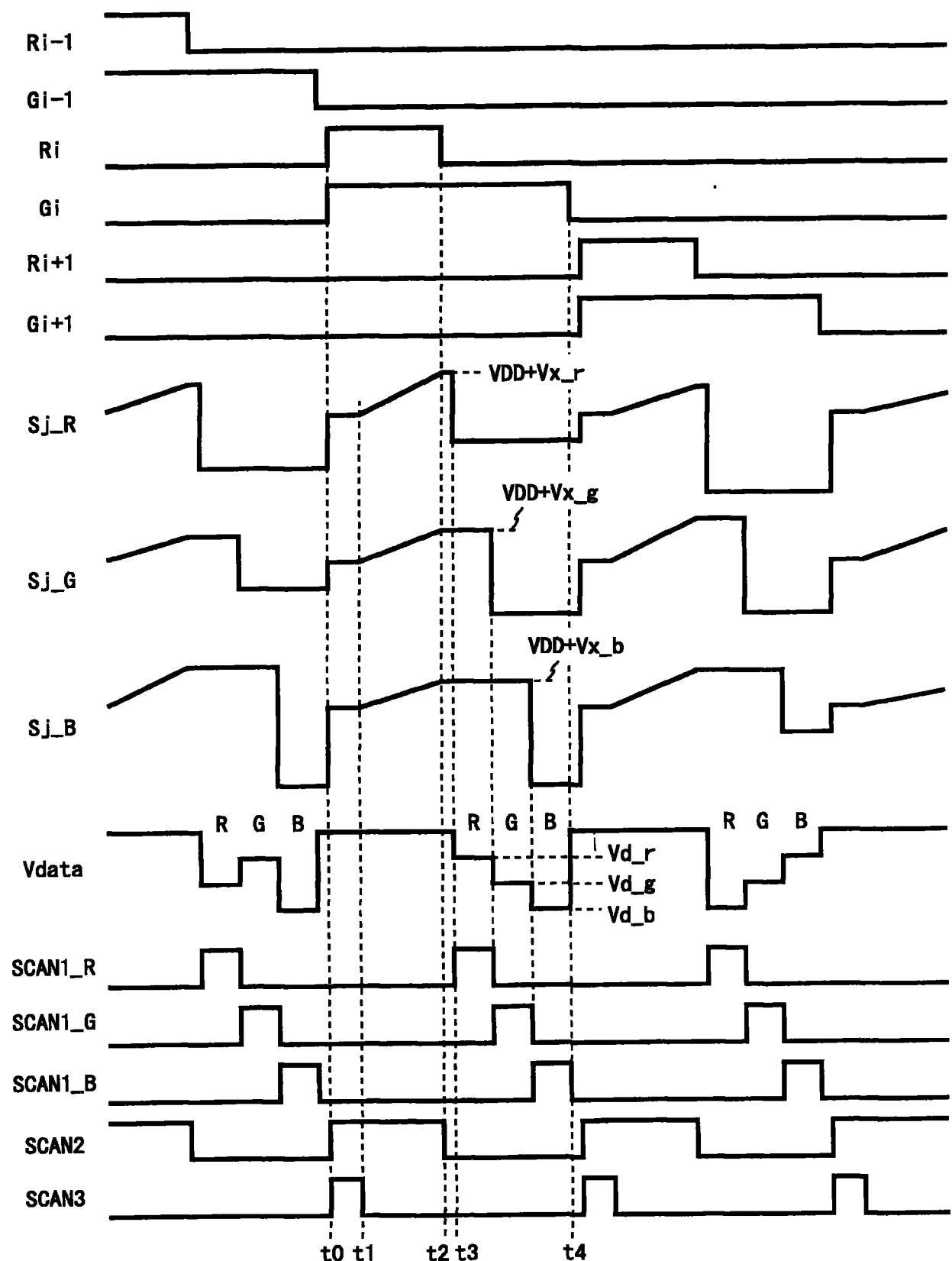

[0083] 图 8 是对本发明的第二实施方式的显示装置中的像素电路进行数据写入时的时序图。

[0084] 图 9 是本发明的第三实施方式的显示装置中包含的阈值校正电路的电路图。

[0085] 图 10 是对本发明的第三实施方式的显示装置中的像素电路进行数据写入时的时序图。

[0086] 图 11 是现有的显示装置中包含的像素电路的电路图。

[0087] 图 12 是对图 11 所示的像素电路进行数据写入时的时序图。

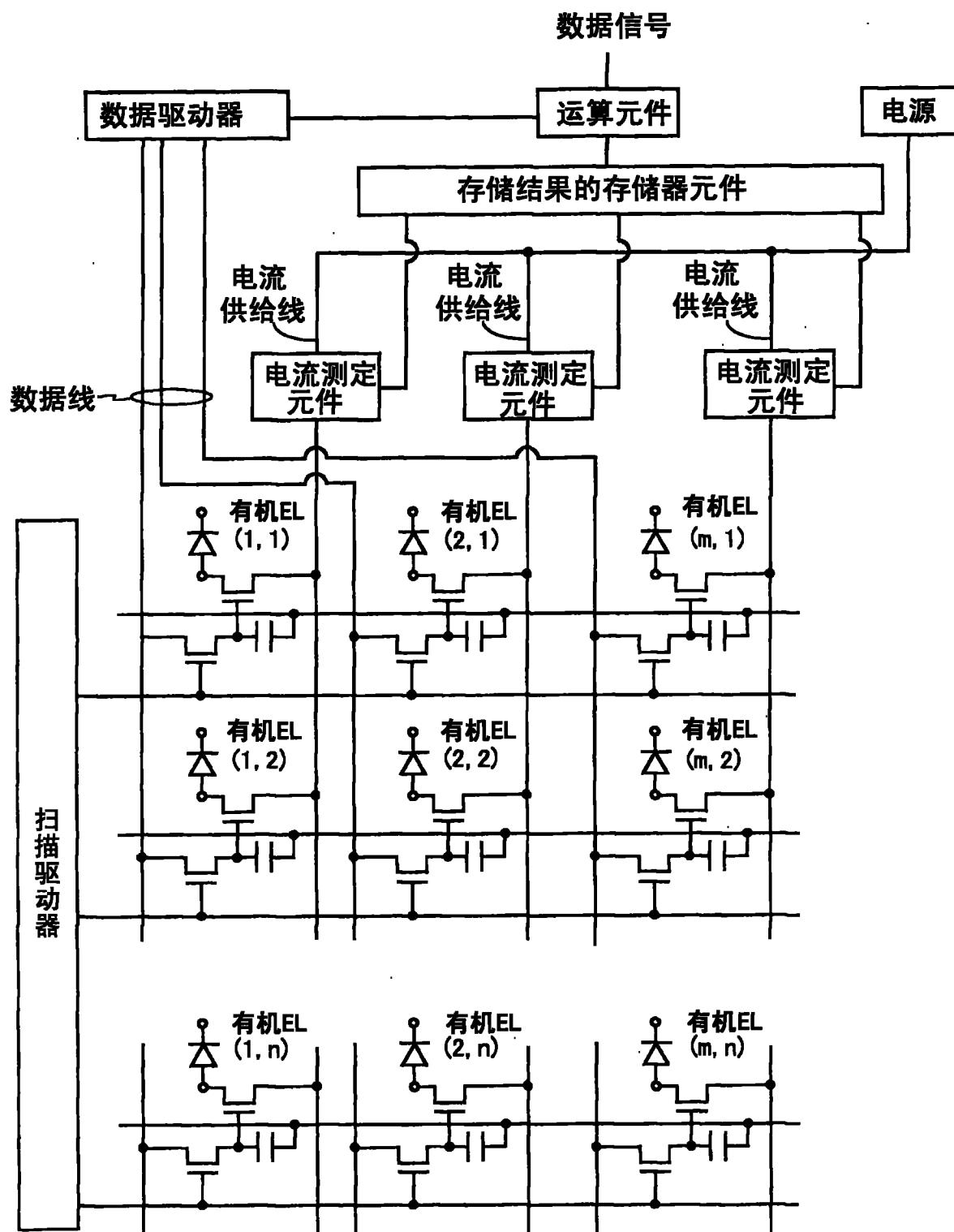

[0088] 图 13 是表示现有的显示装置的结构的方框图。

[0089] 标号说明

- [0090] 1…显示装置

- [0091] 2…显示控制电路

- [0092] 3…栅极驱动器电路

- [0093] 4…源极驱动器电路

- [0094] 5…移位寄存器

- [0095] 6…寄存器

- [0096] 7…锁存器

- [0097] 8…数模变换器

- [0098] 9、20、50、60…阈值校正电路

- [0099] Aij、10、17、18、40…像素电路

- [0100] 11、41…驱动用 TFT

- [0101] 12～14、42～44…开关用 TFT

- [0102] 15、45…有机 EL 元件

- [0103] 16、26、46…电容

- [0104] 21～25、61…开关

- [0105] 27…模拟缓冲器

### 具体实施方式

[0106] 参照图 1～图 10, 说明本发明的第一至第三实施方式的显示装置。以下所示的显示装置具有包括电光元件和多个开关元件在内的像素电路。像素电路中包含的开关元件可用低温多晶硅 TFT 或 CG 硅 TFT 或非晶硅 TFT 等构成。由于这些 TFT 的结构和制造工艺是公知的, 因此这里省略其说明。另外, 设像素电路中包含的电光元件为有机 EL 元件。由于有机 EL 元件的结构也是公知的, 因此这里省略其说明。下面, 说明第一至第三实施方式中共同的显示装置的整体结构, 然后说明各实施方式的显示装置的像素电路和阈值校正电路。

[0107] (显示装置的整体结构)

[0108] 图 1 是表示本发明的第一至第三实施方式的显示装置的结构的方框图。图 1 所示的显示装置 1 具有多个像素电路 Aij (i 为 1 以上 n 以下的整数, j 为 1 以上 m 以下的整数)、显示控制电路 2、栅极驱动器电路 3、及源极驱动器电路 4。栅极驱动器电路 3 起到作为扫描信号输出电路的功能, 源极驱动器电路 4 起到作为显示信号输出电路的功能。

[0109] 显示装置 1 中设置有相互平行的多个扫描线 Gi、及与之垂直且相互平行的多个数据线 Sj。像素电路 Aij 对应于扫描线 Gi 和数据线 Sj 的各交叉点呈矩阵状配置。另外, 与扫描线 Gi 平行配置有相互平行的多个控制线 Wi、Ri。扫描线 Gi 和控制线 Wi、Ri 与栅极驱动器电路 3 连接, 数据线 Sj 与源极驱动器电路 4 连接。而且在像素电路 Aij 的配置区域, 配置有未图示的电源布线 Vp 和共用阴极 Vcom。此外, 也可配置阴极布线 CAi, 以取代共用阴极 Vcom。

[0110] 显示控制电路 2 对栅极驱动器电路 3 输出时序信号 OE、起始脉冲 YI 及时钟 YCK, 对源极驱动器电路 4 输出起始脉冲 SP、时钟 CLK、显示数据 DA、及锁存脉冲 LP。另外, 显示控制电路 2 控制源极驱动器电路 4 的控制线 SCAN1～SCAN3 的电位。

[0111] 栅极驱动器电路 3 包含移位寄存器电路、逻辑运算电路、及缓冲器 (均未图示)。

移位寄存器电路与时钟 YCK 同步地依次传送起始脉冲 YI。运算逻辑电路在从移位寄存器电路的各级输出的脉冲和时序信号 OE 之间进行逻辑运算。逻辑运算电路的输出经由缓冲器, 提供给对应的扫描线 Gi 和控制线 Wi、Ri。一根扫描线 Gi 与 m 个像素电路 Aij 连接, 像素电路 Aij 使用扫描线 Gi 按每 m 个像素电路一起选择。

[0112] 源极驱动器电路 4 包含 m 位移位寄存器 5、寄存器 6、锁存器 7、m 个数模转换器 8、及 m 个阈值校正电路 9, 进行以相同时序向一行的像素电路 Aij 发送数据的线顺序扫描。更详细而言, 移位寄存器 5 具有级联连接的 m 个寄存器, 与时钟 CLK 同步地传送提供给第一级寄存器的起始脉冲 SP, 从各级的寄存器输出时序脉冲 DLP。对应于时序脉冲 DLP 的输出时序, 向寄存器 6 提供显示数据 DA。寄存器 6 按照时序脉冲 DLP, 存储显示数据 DA。当一行的显示数据 DA 被存储到寄存器 6 时, 则显示控制电路 2 对锁存器 7 输出锁存脉冲 LP。锁存器 7 接受锁存脉冲 LP 时, 则保持存储在寄存器 6 中的显示数据。

[0113] 数模转换器 8 和阈值校正电路 9 对应于数据线 Sj 设置。数模转换器 8 将锁存器 7 所保持的显示数据转换成模拟信号电压, 输出到对应的阈值校正电路 9。阈值校正电路 9 经由数据线 Sj 接受从由栅极驱动器电路 3 所选择的像素电路 Aij 输出的电压 (与驱动用 TFT 的阈值电压对应的电压), 根据该电压, 将对数模转换器 8 的输出电压加上或减去与驱动用 TFT 的阈值电压对应的校正电压后的电压施加到数据线 Sj。利用阈值校正电路 9 的作用, 能够对像素电路 Aij 中包含的驱动用 TFT 的阈值电压的偏差进行补偿 (详细情况将在后面阐述)。

[0114] 此外, 源极驱动器电路 4 也可进行向各像素电路逐个依次发送数据的点顺序扫描, 以取代线顺序扫描。进行点顺序扫描时, 在某一扫描线 Gi 被选择的期间, 数据线 Sj 的电压由数据线 Sj 的电容来保持。由于进行点顺序扫描的源极驱动器电路的结构是公知的, 因此这里省略说明。

[0115] (第一实施方式)

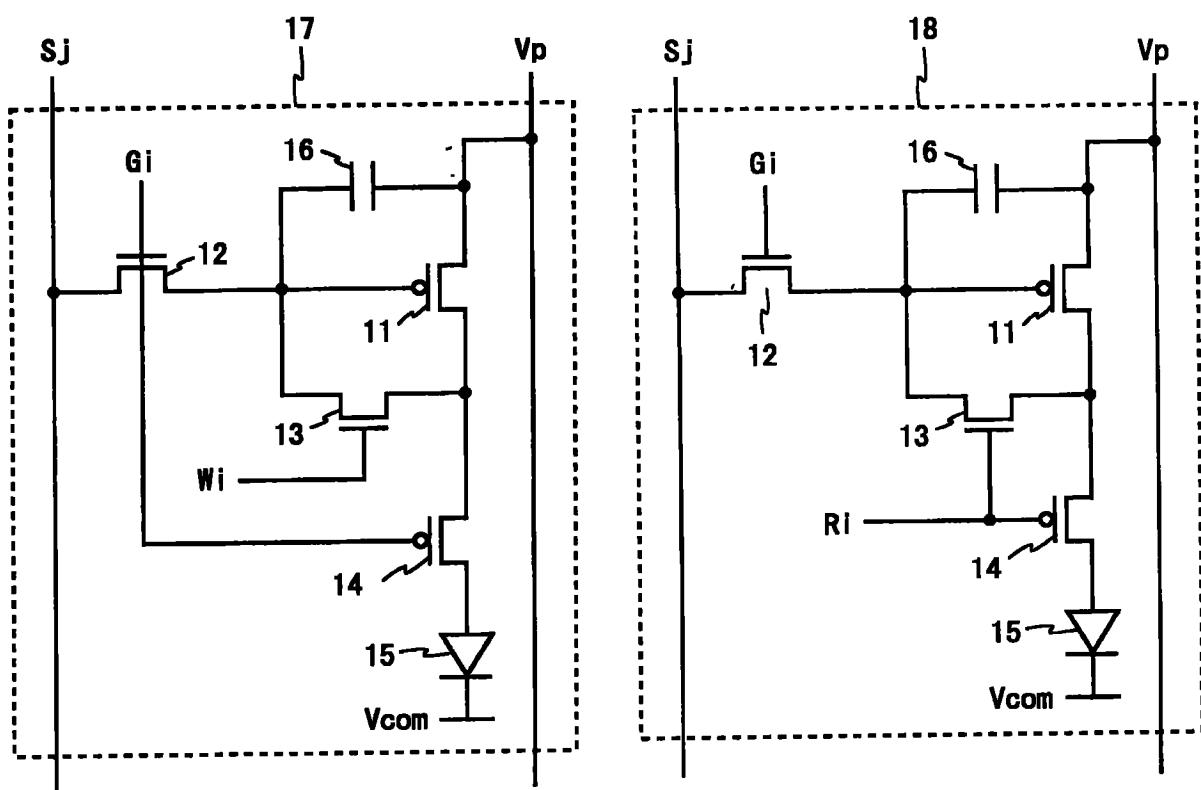

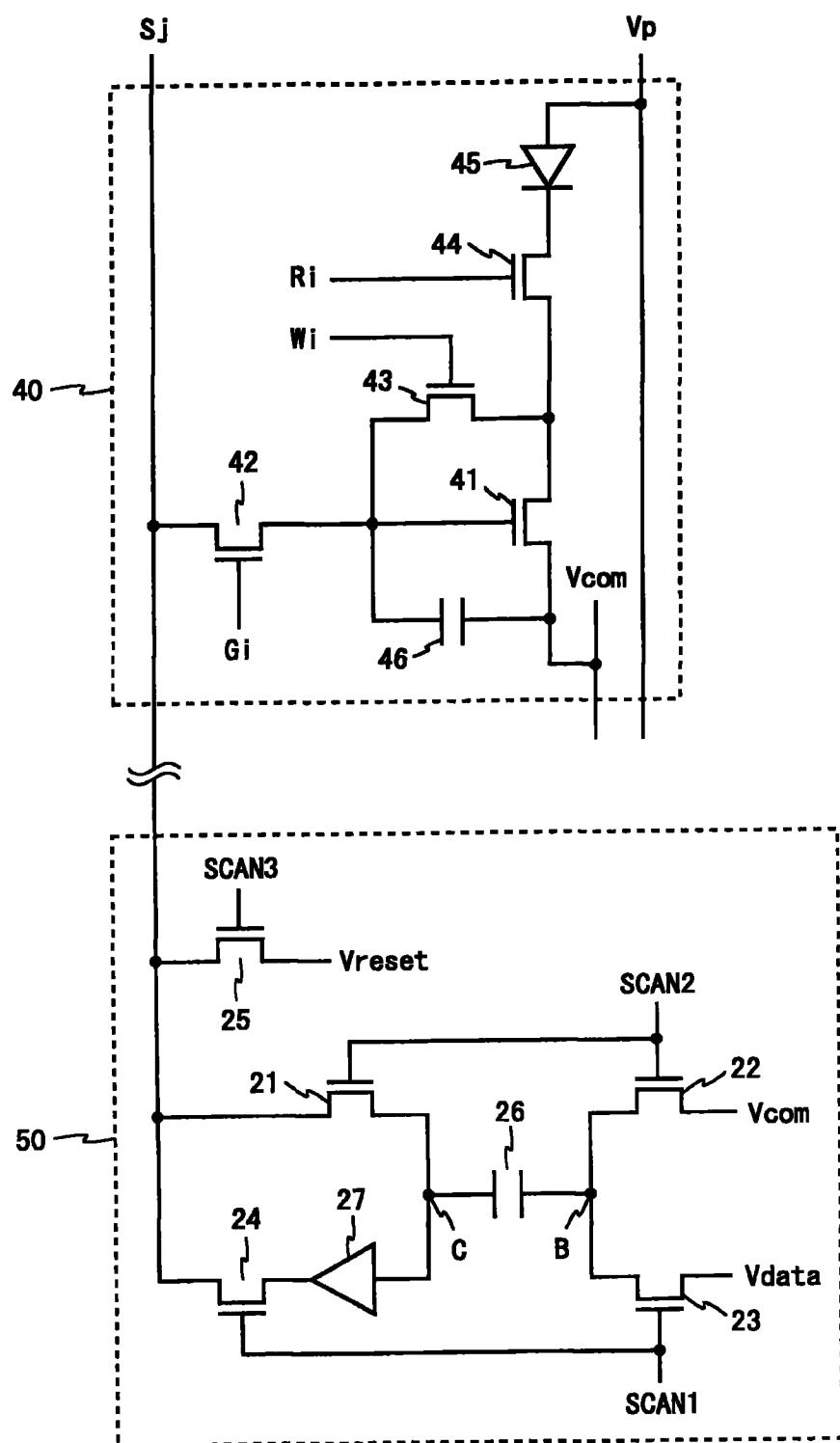

[0116] 图 2 是本发明的第一实施方式的显示装置中包含的像素电路和阈值校正电路的电路图。图 2 所示的像素电路 10 和阈值校正电路 20 与图 1 中的像素电路 Aij 和阈值校正电路 9 相当。如图 2 所示, 像素电路 10 具有驱动用 TFT11、开关用 TFT12 ~ 14、有机 EL 元件 15、及电容 16。驱动用 TFT11 为 P 沟道型的增强型, 开关用 TFT12、13 为 N 沟道型, 开关用 TFT14 为 P 沟道型。

[0117] 像素电路 10 与电源布线 Vp、共用阴极 Vcom、扫描线 Gi、控制线 Wi、Ri、及数据线 Sj 连接。以下, 设电源布线 Vp 的电位为 VDD, 设共用阴极 Vcom 的电位为 VSS (这里, VDD > VSS)。共用阴极 Vcom 成为显示装置内的所有的有机 EL 元件 15 的共用电极。

[0118] 像素电路 10 中, 在电源布线 Vp 和共用阴极 Vcom 之间, 从电源布线 Vp 一侧起依次串联设置有驱动用 TFT11、开关用 TFT14 及有机 EL 元件 15。在驱动用 TFT11 的栅极端子和数据线 Sj 之间设置有开关用 TFT12。在驱动用 TFT11 的栅极端子和漏极端子之间设置有开关用 TFT13, 在驱动用 TFT11 的栅极端子和电源布线 Vp 之间设置有电容 16。开关用 TFT12 ~ 14 的栅极端子分别与扫描线 Gi、控制线 Wi、及控制线 Ri 连接。扫描线 Gi 及控制线 Wi、Ri 的电位由栅极驱动器电路 3 来控制, 数据线 Sj 的电位由源极驱动器电路 4 来控制。以下将与驱动用 TFT11 的栅极端子连接的结点称为 A。

[0119] 阈值校正电路 20 具有开关 21 ~ 25、电容 26、及模拟缓冲器 27, 与数据线 Sj 连接。

开关 21 ~ 25 都为 N 沟道型的晶体管, 模拟缓冲器 27 为电压跟随器电路 (单位增益放大器)。

[0120] 将与电容 26 的一侧的电极 (图 2 中画在右侧的电极) 连接的结点称为 B, 将与另一侧的电极连接的结点称为 C。开关 21 设置在数据线 Sj 和结点 C 之间, 开关 22 设置在结点 B 和电源布线 Vp 之间。开关 23 的一端与结点 B 连接, 在结点 C 和数据线 Sj 之间, 从结点 C 一侧起依次串联设置有模拟缓冲器 27 和开关 24。开关 25 的一端与数据线 Sj 连接。

[0121] 向开关 23 的另一端提供从数模转换器 8 输出的数据电压 Vdata, 向开关 25 的另一端提供初始电压 Vreset (详细情况将在后面阐述)。开关 21、22 的栅极端子与控制线 SCAN2 连接, 开关 23、24 的栅极端子与控制线 SCAN1 连接, 开关 25 的栅极端子与控制线 SCAN3 连接。

[0122] 以下, 设驱动用 TFT11 的阈值电压为 Vth (负值)。如后所述, 电容 26 起到作为将与驱动用 TFT11 的阈值电压 Vth 对应的校正电压 Vx 加以保持的校正用电容的功能。另外, 开关 21 ~ 24 起到作为开关电路的功能, 该开关电路进行切换, 使得将电容 26 的一侧的电极与数据线 Sj 连接, 并向另一侧的电极施加固定电压 VDD, 或者将电容 26 的一侧的电极通过模拟缓冲器 27 与数据线 Sj 连接, 并向另一侧的电极施加数据电压 Vdata。

[0123] 图 3 是对像素电路 10 进行数据写入时的时序图。下面, 参照图 3, 说明对和扫描线 Gi 及数据线 Sj 连接的像素电路 10 写入数据电压 Vdata 时的动作。图 3 中, 从时刻 t0 起到时刻 t4 为止成为像素电路 10 的选择期间。在时刻 t2 之前, 进行检测驱动用 TFT11 的阈值电压的处理, 在时刻 t2 之后, 进行写入校正后的数据电压的处理。

[0124] 在时刻 t0 之前, 扫描线 Gi 和控制线 Wi、Ri 的电位被控制成低电平, 开关用 TFT12、13 处于非导通状态, 开关用 TFT14 处于导通状态。此时, 驱动用 TFT11 处于导通状态, 电流从电源布线 Vp 经由驱动用 TFT11 和开关用 TFT14 流到有机 EL 元件 15, 有机 EL 元件 15 发光。

[0125] 在时刻 t0, 扫描线 Gi 和控制线 Ri、Wi、SCAN3 的电位变化成高电平时, 则开关用 TFT12、13 及开关 25 变成导通状态, 开关用 TFT14 变成非导通状态。由此, 向数据线 Sj 施加初始电压 Vreset, 数据线 Sj 和结点 A 的电位成为 Vreset。时刻 t0 以后, 通过驱动用 TFT11 的电流经由开关用 TFT13 流入到结点 A。

[0126] 接着在时刻 t1, 控制线 SCAN3 的电位变化成低电平时, 则开关 25 变成非导通状态。时刻 t1 以后, 通过驱动用 TFT11 的电流也经由开关用 TFT13 流入到结点 A, 结点 A 的电位 (驱动用 TFT11 的栅极端子电位) 在驱动用 TFT11 处于导通状态的期间上升。此时由于开关用 TFT12 处于导通状态, 因此数据线 Sj 的电位与结点 A 的电位相等。

[0127] 在从时刻 t0 起到时刻 t2 为止的期间, 控制线 SCAN1 的电位被控制成低电平, 控制线 SCAN2 的电位被控制成高电平。因此, 开关 21、22 成为导通状态, 开关 23、24 成为非导通状态, 结点 B 与电源布线 Vp 连接, 结点 C 与数据线 Sj 连接。因而, 此时结点 B 的电位为 VDD, 结点 C 的电位与结点 A 及数据线 Sj 的电位相等。

[0128] 接着在时刻 t2, 控制线 Wi、SCAN2 的电位变化成低电平时, 则开关用 TFT13 及开关 21、22 变成非导通状态。设时刻 t2 时的结点 A 的电位为 (VDD+Vx) (这里, Vx 为负值, Vx 的绝对值比 Vth 的绝对值要大)。由于在时刻 t2 结点 C 的电位也为 (VDD+Vx), 因此在时刻 2, 开关 21、22 变成非导通状态时, 则电容 26 中保持电压 Vx。

[0129] 如上所述,结点 A 的电位在驱动用 TFT11 处于导通状态的期间上升。因而,若有足够的时间,则结点 A 的电位一直上升直到驱动用 TFT11 的栅极 - 源极之间的电压变成阈值电压  $V_{th}$  (负值) 为止,最终达到  $(VDD+V_{th})$ 。时刻  $t_2$  时的结点 A 的电位  $(VDD+V_x)$  比  $(VDD+V_{th})$  要低。另外,电压  $V_x$  根据阈值电压  $V_{th}$  而变化,阈值电压  $V_{th}$  的绝对值越大,则电压  $V_x$  的绝对值越大。

[0130] 接着在时刻  $t_3$ ,控制线 SCAN1 的电位变化成高电平时,则开关 23、24 变成导通状态。时刻  $t_3$  以后,向结点 B 施加从数模转换器 8 输出的数据电压  $V_{data}$ ,结点 C 通过模拟缓冲器 27 与数据线  $S_j$  连接。在电容 26 保持电压  $V_x$  的期间,结点 B 的电位从  $VDD$  变成  $V_{data}$  时,则结点 C 的电位也变化相同的量  $(V_{data}-VDD)$ ,成为  $(VDD+V_x)+(V_{data}-VDD) = (V_{data}+V_x)$ 。

[0131] 由于此时开关 24 处于导通状态,且模拟缓冲器 27 的输入电压和输出电压相等,因此数据线  $S_j$  的电位与结点 C 相同,成为  $(V_{data}+V_x)$ 。另外,由于此时开关用 TFT12 也处于导通状态,因此结点 A 的电位也和数据线  $S_j$  相同,成为  $(V_{data}+V_x)$ 。

[0132] 接着在时刻  $t_4$ ,扫描线  $G_i$  及控制线  $R_i$ 、SCAN1 的电位变化成低电平时,则开关用 TFT12 及开关 23、24 变成非导通状态,开关用 TFT14 变成导通状态。此时电容 16 中保持驱动用 TFT11 的栅极 - 源极之间的电压  $(VDD-V_{data}-V_x)$ 。此外,提供给控制线  $R_i$  的导通电位 (低电平电位) 被确定成使得开关用 TFT14 在线性区域动作。

[0133] 时刻  $t_4$  以后,由于电容 16 所保持的电压不变化,因此结点 A 的电压维持  $(V_{data}+V_x)$  不变。因而,时刻  $t_4$  以后,在直到下次控制线  $R_i$  的电位成为高电平之前,电流从电源布线  $V_p$  经由驱动用 TFT11 和开关用 TFT14 流到有机 EL 元件 15,有机 EL 元件 15 发光。此时流过驱动用 TFT11 的电流量根据结点 A 的电位  $(V_{data}+V_x)$  而增减,但如下所述,即使阈值电压  $V_{th}$  不同,只要电位  $V_{data}$  相同,便也能够使电流量相同。

[0134] 使驱动用 TFT11 在饱和区域动作时,若忽视沟道长度调制效应,则流过漏极 - 源极之间的电流  $I_{EL}$  由下式 (1) 给出。

$$I_{EL} = -1/2 \cdot W/L \cdot C_{ox} \cdot \mu (V_g - VDD - V_{th})^2 \dots (1)$$

[0135] 这里,上述 (1) 中,  $W/L$  为驱动用 TFT11 的长宽比,  $C_{ox}$  为栅极电容,  $\mu$  为迁移率,  $V_g$  为栅极端子电位 (结点 A 的电位)。

[0136] 式 (1) 所示的电流  $I_{EL}$  一般根据阈值电压  $V_{th}$  而变动。本实施方式的显示装置中,由于栅极端子电位  $V_g$  成为  $(V_{data}+V_x)$ ,因此电流  $I_{EL}$  如下式 (2) 所示。

$$I_{EL} = -1/2 \cdot W/L \cdot C_{ox} \cdot \mu \{V_{data} - VDD + (V_x - V_{th})\}^2 \dots (2)$$

[0137] 式 (2) 中,若电压  $V_x$  与阈值电压  $V_{th}$  一致,则电流  $I_{EL}$  不取决于阈值电压  $V_{th}$ 。另外,即使电压  $V_x$  与阈值电压  $V_{th}$  不一致,但若两者之差固定,则电流  $I_{EL}$  也不取决于阈值电压  $V_{th}$ 。

[0138] 本实施方式的显示装置中,是这样确定阈值校正期间 (从时刻  $t_1$  起到时刻  $t_2$  为止的期间) 的长度和初始电压  $V_{reset}$  的电平,使得在两个 TFT 之间的电压  $V_x$  之差与阈值电压  $V_{th}$  之差大致相同。因此,式 (2) 中包含的电压差  $(V_x - V_{th})$  大致固定。因而,与数据电压  $V_{data}$  对应的量的电流流到有机 EL 元件 15,有机 EL 元件 15 以与数据电压  $V_{data}$  对应的亮度发光,而不取决于阈值电压  $V_{th}$  的值。本实施方式的显示装置中,阈值校正由设置在

像素电路 10 的外部的阈值校正电路 20 来进行, 但无需在阈值校正电路 20 中设置复杂的逻辑电路或存储器等。

[0142] 这里, 对初始电压  $V_{reset}$  进行说明。在图 3 所示的时刻  $t_0$ , 开关用 TFT13 变成导通状态时, 则驱动用 TFT11 变成二极管连接的状态。现有的有机 EL 显示器中, 从驱动用 TFT 进行二极管连接起、直到驱动用 TFT 的栅极 - 源极之间的电压  $V_{gs}$  与阈值电压  $V_{th}$  充分接近为止所经过的期间成为阈值校正期间。这是因为若电压  $V_{gs}$  与阈值电压  $V_{th}$  充分接近, 便能够检测出两个驱动用 TFT 之间的阈值电压之差。

[0143] 然而, 在高清晰的显示装置中, 像素电路的选择期间较短, 有时无法在选择期间内使电压  $V_{gs}$  与阈值电压  $V_{th}$  充分接近。特别是, 在本实施方式的显示装置中, 由于在检测驱动用 TFT 的阈值电压  $V_{th}$  时, 需要对电容 26 和数据线  $S_j$  的寄生电容进行充电, 因此为了在选择期间内进行检测阈值电压的处理和写入校正后的电压的处理, 需要想办法。

[0144] 因此, 本实施方式的显示装置中, 为了在开始对校正后的数据电压进行写入的处理之前检测出阈值电压  $V_{th}$  的偏差, 利用开关 25 的作用向数据线  $S_j$  提供固定的初始电压  $V_{reset}$ 。由此, 能够缩短直到与驱动用 TFT11 的阈值电压  $V_{th}$  对应的电压 ( $V_{DD}+V_x$ ) 被输出到数据线  $S_j$  为止所需的时间。因而, 即使在阈值校正期间较短的情况下, 也能够抑制校正效果的偏差, 并使画质提高。

[0145] 初始电压  $V_{reset}$  根据阈值校正期间的长度或阈值校正所要求的精度等来确定。在开关用 TFT13 处于导通状态、驱动用 TFT11 进行二极管连接时, 对于驱动用 TFT11 的电流平衡关系, 满足下式 (3)。

[0146] [数学式 1]

$$[0147] k(V_{gs}(t) - V_{th})^2 = -C \frac{dV_{gs}(t)}{dt} \quad \cdots (3)$$

[0148] 这里, 式 (3) 中,  $k$  为常数,  $C$  为保持电容和信号线电容之和。

[0149] 求解该微分方程, 则可得到下式 (4)。

[0150] [数学式 2]

$$[0151] V_{gs}(t) = \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0} - V_{th}}} + V_{th} \quad \cdots (4)$$

[0152] 这里, 式 (4) 中,  $V_{gs0}$  为电压  $V_{gs}$  的初始值。

[0153] 考虑到阈值电压相差  $\Delta V_{th}$  的两个 TFT 时, 若经过预定时间后, 在两个 TFT 之间的电压  $V_{gs}$  之差与  $\Delta V_{th}$  接近, 则可以说能检测出各 TFT 的阈值电压。电压  $V_{gs}$  之差由下式 (5) 给出。

[0154] [数学式 3]

$$[0155] \Delta V_{gs}(t) = \Delta V_{th} + \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0} - V_{th} - \Delta V_{th}}} - \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs0} - V_{th}}} \quad \cdots (5)$$

[0156] 因而, 只要这样确定电压  $V_{gs}$  的初始值  $V_{gs0}$ , 使得在容许时间内使式 (5) 所示的  $\Delta V_{gs}(t)$  与  $\Delta V_{th}$  充分接近, 并据此求出初始电压  $V_{reset}$  即可。

[0157] 图 4 是表示二极管连接的驱动用 TFT 的栅极 - 源极之间的电压  $V_{gs}$  随时间变化的

例子。图 4 中记载了对阈值电压不同的两个 TFT ( $V_{th} = -0.8V$  和  $V_{th} = -1.0V$ )、提供两种初始电压  $V_{gs0}$  ( $V_{gs0} = -5V$  和  $V_{gs0} = -1.5V$ ) 时的结果。

[0158] 对两个 TFT 提供初始电压  $V_{gs0}$ , 比较经过  $30 \mu s$  后的电压  $V_{gs}$ 。在  $V_{gs0} = -5V$  的情况下,  $30 \mu s$  后, 虽然两个电压距各自的最终值 ( $-0.8V$  和  $-1.0V$ ) 有一定距离, 但两者之差已和最终值 ( $0.2V$ ) 大致相等。与此不同的是, 在  $V_{gs0} = -1.5V$  的情况下,  $30 \mu s$  后, 虽然两个电压与各自的最终值接近, 但两者之差却依然距最终值有一定距离。

[0159] 这样, 由于初始电压  $V_{gs0}$  的绝对值越大, 电压  $V_{gs}$  之差增大的速度越快, 因此能够缩短阈值校正期间。因而, 为了以高精度进行阈值校正, 最好增大初始电压  $V_{gs0}$  的绝对值。另一方面, 若增大初始电压  $V_{gs0}$  的绝对值, 则因数据线  $S_j$  和电容 26 的充放电而使功耗增加。因而, 只要考虑工艺中的阈值电压的偏差的程度和规格, 来确定初始电压  $V_{reset}$  即可。

[0160] 接着, 对模拟缓冲器 27 进行说明。在数据线  $S_j$  的电容量与电容 26 的电容量相比小到可忽视的程度的情况下, 无需在阈值校正电路 20 中设置模拟缓冲器 27。另一方面, 在数英寸以上的显示面板中, 由于数据线  $S_j$  的电容量为数 pF 以上的情况较多, 因此在这种情况下需要设置模拟缓冲器 27。此时, 若使用电压跟随器电路 (单位增益放大器) 作为模拟缓冲器 27, 则能够将电路规模的增大抑制到最低限度, 同时提高驱动能力。

[0161] 另外, 在模拟缓冲器 27 中使用一般的差分放大器的情况下, 有时形成差分对的晶体管的特性会发生偏差, 从而模拟缓冲器 27 的特性发生偏差。发生这样的偏差时, 则在显示画面上会出现条状的不均匀, 显示品质下降。因此, 为了防止该问题, 只要不在显示面板上形成模拟缓冲器 27, 而将其内置在显示面板外的周边 IC 内即可。内置在周边 IC 内的典型电路是由单晶硅的晶体管形成。因而, 若内置在周边 IC 内, 则能够得到特性偏差极小的模拟缓冲器 27。

[0162] 另外, 为了防止上述问题, 作为模拟缓冲器 27, 也可使用具有偏移抵消功能的缓冲器 (参照图 5A ~ 图 5D)。图 5A 所示的缓冲器中, 差分放大器 31 的正侧输入端子、负侧输入端子、及输出端子分别与缓冲器的输入端子、电容 32 的一侧的电极、及缓冲器的输出端子连接。在电容 32 的另一侧的电极和缓冲器的输入端子之间设置有开关 33。在差分放大器 31 的负侧输入端子和输出端子之间设置有开关 34。在电容 32 的另一侧的电极和差分放大器 31 的输出端子之间设置有开关 35。开关 33、34 由控制信号  $SC\_A$  来控制, 开关 35 由控制信号  $SC\_B$  来控制。

[0163] 控制信号  $SC\_A$ 、 $SC\_B$  为如图 5B 所示互相相反地使开关成为导通状态的电平 (这里, 设为高电平)。在控制信号  $SC\_A$  为高电平的期间 (参照图 5C), 开关 33、34 成为导通状态, 开关 35 成为非导通状态。此时, 在差分放大器 31 的正侧输入端子和负侧输入端子之间出现差分放大器 31 的偏移电压  $V_{off}$ 。偏移电压  $V_{off}$  保持在电容 32 中。

[0164] 在控制信号  $SC\_B$  为高电平的期间 (参照图 5D), 开关 33、34 成为非导通状态, 开关 35 成为导通状态。随之, 差分放大器 31 的负侧输入电压变化偏移电压  $V_{off}$  的大小, 差分放大器 31 的输出电压 (缓冲器的输出电压) 也变化相同的量, 变得与输入电压  $V_{in}$  相等。这样, 若使用图 5A 所示的缓冲器, 则能够抵消差分放大器 31 的偏移电压。此外, 也可将具有偏移抵消功能的缓冲器内置在显示面板外的周边 IC 内。

[0165] 下面, 说明本实施方式的显示装置的效果。根据本实施方式的显示装置, 能够从由栅极驱动器电路 3 所选择的像素电路 10 读出与驱动用 TFT11 的阈值电压  $V_{th}$  对应的电压

(VDD+Vx), 并将对数据电压 Vdata 加上校正电压 Vx (与阈值电压 Vth 对应的电压) 后的电压 (Vdata+Vx) 提供给驱动用 TFT11 的栅极端子。一般在 P 沟道型的驱动用 TFT 中, 若将减去阈值电压的绝对值后的电压提供给栅极端子, 则能够补偿阈值电压的偏差。因而, 根据本实施方式的显示装置, 能够检测驱动用 TFT11 的阈值电压以补偿阈值电压的偏差, 并使有机 EL 元件 15 以所要的亮度发光。

[0166] 另外, 通过将阈值校正电路 20 设置在像素电路的外部, 并使用数据线 Sj 来检测阈值电压, 从而能够缩小像素电路 10 的规模和面积。另外, 由于通过将阈值电压作为电压信号进行检测, 从而与反馈电流信号的情况不同, 无需电流电压变换元件, 因此能够抑制校正效果的偏差。另外, 通过将与阈值电压对应的校正电压 Vx 保持原样与数据电压 Vdata 相加, 从而能够以高精度进行阈值校正。另外, 由于不通过耦合电容而向驱动用 TFT11 的栅极端子提供所要的电压, 因此能够有效利用数据电压 Vdata 的振幅, 并减小功耗。另外, 由于在数据线 Sj 和驱动用 TFT11 之间未设置有电容, 因此能够容易检查驱动用 TFT11。在检查驱动用 TFT11 时, 只要使电流从电源布线 Vp 经由驱动用 TFT11 的漏极端子和栅极端子流到数据线 Sj 即可。

[0167] 此外, 本实施方式的显示装置还可具有图 6A 或图 6B 所示的像素电路, 以取代像素电路 10。图 6A 所示的像素电路 17 是对像素电路 10 实施如下更改, 即, 将开关用 TFT14 与扫描线 Gi 连接, 使扫描线 Gi 和控制线 Ri 公用化。像素电路 17 中, 开关用 TFT12、14 互相相反地成为导通状态。另外, 图 6B 所示的像素电路 18 是对像素电路 10 实施如下更改, 即, 将开关用 TFT13 与控制线 Ri 连接, 使控制线 Ri 和控制线 Wi 公用化。像素电路 18 中, 开关用 TFT13、14 互相相反地成为导通状态。

[0168] 这些变形例的显示装置与具有像素电路 10 的显示装置同样地进行动作, 起到同样的效果。在此基础上, 使与开关用 TFT12 ~ 14 的控制端子连接的布线公用化, 以将布线数从三根减少到两根, 能够进一步提高像素的开口率, 并使画面变亮。

[0169] (第二实施方式)

[0170] 图 7 是本发明的第二实施方式的显示装置中包含的像素电路和阈值校正电路的电路图。图 7 所示的像素电路 40 和阈值校正电路 50 与图 1 中的像素电路 Aij 和阈值校正电路 9 相当。如图 7 所示, 像素电路 40 具有驱动用 TFT41、开关用 TFT42 ~ 44、有机 EL 元件 45、及电容 46。驱动用 TFT41 为 N 沟道型的增强型, 开关用 TFT42 ~ 44 为 N 沟道型。

[0171] 像素电路 40 中, 在电源布线 Vp 和共用阴极 Vcom 之间, 从电源布线 Vp 一侧起依次串联设置有机 EL 元件 45、开关用 TFT44、及驱动用 TFT41。在驱动用 TFT41 的栅极端子和数据线 Sj 之间设置有开关用 TFT42。在驱动用 TFT41 的栅极端子和漏极端子之间设置有开关用 TFT43, 在驱动用 TFT41 的栅极端子和共用阴极 Vcom 之间设置有电容 46。开关用 TFT42 ~ 44 的栅极端子分别与扫描线 Gi 及控制线 Wi、Ri 连接。

[0172] 阈值校正电路 50 具有和第一实施方式的阈值校正电路 20 相同的结构。但是, 阈值校正电路 50 中, 开关 22 设置在结点 B 和共用阴极 Vcom 之间。除此以外, 阈值校正电路 50 与阈值校正电路 20 相同。

[0173] 图 8 是对像素电路 40 进行数据写入时的时序图。本实施方式的显示装置与第一实施方式的显示装置同样地进行动作, 起到同样的效果。此外, 一般在 N 沟道型的驱动用 TFT 中, 若将加上阈值电压的绝对值后的电压提供给栅极端子, 则能够补偿阈值电压的偏差。另

外,本实施方式中,也和第一实施方式相同,能够构成使得与开关用 TFT42 ~ 44 的控制端子连接的布线公用化的变形例。

[0174] 这样使驱动用 TFT41 和开关用 TFT42 ~ 44 都采用 N 沟道型的像素电路 40 能够适用于使用非晶硅的显示面板。

[0175] (第三实施方式)

[0176] 第一及第二实施方式的显示装置中,对每一数据线 Sj 设置模拟缓冲器 27。然而,在例如 2 英寸 QVGA 全彩色面板(具有 RGB 子像素)中,子像素的间距约为  $42 \mu\text{m}$ 。虽然保持与驱动用 TFT 的阈值电压对应的校正电压  $V_x$  的电容 26 能够以该间距进行配置,但有时高性能的模拟缓冲器 27 不能以该间距进行配置。因此,第三实施方式中,对减少模拟缓冲器 27 的数量的显示装置进行说明。

[0177] 图 9 是本发明的第三实施方式的显示装置中包含的阈值校正电路的电路图。图 9 所示的阈值校正电路 60r、60g、60b 与图 1 中的阈值校正电路 9 相当。另外,图 9 所示的数据线 Sj\_R、Sj\_G、Sj\_B 与图 1 中的数据线 Sj 相当。

[0178] 如图 9 所示,模拟缓冲器 27 与三根数据线 Sj\_R、Sj\_G、Sj\_B 对应设置。阈值校正电路 60r 是对第一实施方式的阈值校正电路 20(图 2)、添加使模拟缓冲器 27 共用的功能后的电路。具体来讲,阈值校正电路 60r 中,在电容 26 的一侧的电极(图 9 中画在上侧的电极)和模拟缓冲器 27 的输入端子之间设置开关 61。另外,开关 23、24、61 的栅极端子与控制线 SCAN1\_R 连接。阈值校正电路 60g、60b 的结构也与之相同。

[0179] 图 10 是对本实施方式的显示装置中的像素电路进行数据写入时的时序图。下面,参照图 10,说明对和扫描线 Gi 及数据线 Sj\_R、Sj\_G、Sj\_B 连接的三个像素电路写入数据时的动作。图 10 中,从时刻  $t_0$  起到时刻  $t_4$  为止成为三个像素电路的选择期间。在时刻  $t_2$  之前,进行并行地检测三个像素电路的驱动用 TFT 的阈值电压的处理,在时刻  $t_2$  之后,进行对三个像素电路依次写入校正后的数据电压的处理。此外,这里,设显示装置具有图 6B 所示的像素电路 18,但像素电路的种类可任意。

[0180] 在时刻  $t_0$  之前,扫描线 Gi 和控制线 Ri 的电位被控制成低电平。在时刻  $t_0$ ,扫描线 Gi 和控制线 Ri、SCAN3 的电位变化成高电平时,则数据线 Sj\_R、Sj\_G、Sj\_B 的电位,和三个像素电路的驱动用 TFT 的栅极端子电位成为  $V_{reset}$ 。

[0181] 接着在时刻  $t_1$ ,控制线 SCAN3 的电位变化成低电平时,则数据线 Sj\_R、Sj\_G、Sj\_B 的电位都上升。在从时刻  $t_0$  起到时刻  $t_2$  为止的期间,控制线 SCAN1\_R、SCAN1\_G、SCAN1\_B 的电位被控制成低电平,控制线 SCAN2 的电位被控制成高电平。

[0182] 设时刻  $t_2$  时的三个像素电路的驱动用 TFT 的栅极端子电位为  $(VDD+V_{x_r})$ 、 $(VDD+V_{x_g})$ 、 $(VDD+V_{x_b})$ (这里,  $V_{x_r}$ 、 $V_{x_g}$  及  $V_{x_b}$  为负值)。在时刻  $t_2$ ,控制线 Ri、SCAN2 的电位变化成低电平时,则阈值校正电路 60r、60g、60b 的电容 26 中分别保持电压  $V_{x_r}$ 、 $V_{x_g}$ 、 $V_{x_b}$ 。

[0183] 接着在从时刻  $t_3$  起到时刻  $t_4$  为止的期间,控制线 SCAN1\_R、SCAN1\_G、SCAN1\_B 的电位每隔预定时间成为高电平,与之同步地,从数模转换器 8 输出的数据电压  $V_{data}$  也变化为  $V_{d_r}$ 、 $V_{d_g}$ 、 $V_{d_b}$ 。由此,首先,与数据线 Sj\_R 连接的像素电路的驱动用 TFT 的栅极端子电位成为  $(V_{d_r}+V_{x_r})$ ,接着,与数据线 Sj\_G 连接的像素电路的驱动用 TFT 的栅极端子电位成为  $(V_{d_g}+V_{x_g})$ ,最后,与数据线 Sj\_B 连接的像素电路的驱动用 TFT 的栅极端子电位成为

(Vd\_b+Vx\_b),

[0184] 接着在时刻 t4, 扫描线 Gi 的电位变化成低电平时, 则三个像素电路的电容中分别保持电压 (VDD-Vd\_r-Vx\_r)、(VDD-Vd\_g-Vx\_g)、(VDD-Vd\_b-Vx\_b)。

[0185] 在时刻 t4 以后, 三个像素电路的驱动用 TFT 的栅极端子电位分别维持 (Vd\_r+Vx\_r)、(Vd\_g+Vx\_g)、(Vd\_b+Vx\_b) 不变。此时流过各驱动用 TFT 的电流量根据这些电位而增减, 但即使阈值电压不同, 只要数据电压相同, 电流量便相同。因而, 与数据电压 Vdata 对应的量的电流流到各像素电路的有机 EL 元件, 有机 EL 元件以与数据电压 Vdata 对应的亮度发光, 而不取决于阈值电压的值。

[0186] 此外, 以上的说明中, 虽然假设与三根数据线 Sj\_R、Sj\_G、Sj\_B 对应地设置模拟缓冲器, 但也可与 p 根 (p 为 2 以上的任意整数) 的数据线对应地设置模拟缓冲器。

[0187] 这样根据本实施方式的显示装置, 对每多个数据线配置为了对每一数据线配置而使得电路规模较大的模拟缓冲器, 能够实现高清晰的显示面板。

[0188] 此外, 上述的各实施方式中, 虽然假设像素电路包含有机 EL 元件以作为电光元件, 但也可包含有机 EL 元件以外的电流驱动型的电光元件 (例如半导体 LED 或 FED 的发光部等)。另外, 虽然假设像素电路包含形成在玻璃基板等绝缘基板上的 MOS 晶体管 (包括硅栅极 MOS 结构) 即 TFT, 以作为电光元件的驱动元件, 但也可包含具有阈值电压的任意的电压控制型的元件 (即根据施加到控制端子的控制电压使输出电流变化、若控制电压变成预定值以上或以下则使输出电流截止的元件)。因而, 像素电路也可包含包括形成在半导体基板上的 MOS 晶体管等在内的、一般的绝缘栅型场效应晶体管, 以作为驱动元件。

[0189] 另外, 第一实施方式中, 假设在与开关用 TFT12 变成导通状态大致相同的时刻, 开关用 TFT13 变成导通状态, 开关用 TFT14 变成非导通状态。也可在开关用 TFT12 变成导通状态之前, 开关用 TFT13 变成导通状态, 开关用 TFT14 变成非导通状态, 以作为取代上述第一实施方式中的情况。第二及第三实施方式中, 也与之相同。

[0190] 另外, 本发明并不局限于上述的各实施方式, 能进行各种变更。将不同的实施方式所分别披露的技术手段适当组合后得到的实施方式, 也包含在本发明的技术范围内。

[0191] 工业上的实用性

[0192] 本发明的显示装置由于起到如下效果, 即, 能够高效利用数据电压的振幅, 并以高精度进行阈值校正, 而不使像素电路的规模增大, 因此能够用作为各种电子设备的显示装置。

图 1

图 2

图 3

图 4

图 5A

图 5B

图 5C

图 5D

图 6A

图 6B

图 7

图 8

图 9

图 10

图 11

图 12

图 13

|                |                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                    |         |            |

| 公开(公告)号        | <a href="#">CN102097055A</a>                                                  | 公开(公告)日 | 2011-06-15 |

| 申请号            | CN201110065963.6                                                              | 申请日     | 2007-10-01 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                        |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                        |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                        |         |            |

| [标]发明人         | 岸宣孝                                                                           |         |            |

| 发明人            | 岸宣孝                                                                           |         |            |

| IPC分类号         | G09G3/32                                                                      |         |            |

| CPC分类号         | G09G3/3291 G09G2320/0295 G09G2320/0233 G09G3/3233 G09G2300/0819 G09G2300/0852 |         |            |

| 代理人(译)         | 张鑫                                                                            |         |            |

| 优先权            | 2007058021 2007-03-08 JP                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                |         |            |

### 摘要(译)

本发明涉及一种显示装置及其驱动方法。使像素电路(10)内的开关用TFT(12、13)导通，使开关用TFT(14)截止，将与驱动用TFT(11)的阈值电压对应的电压(VDD+Vx)输出到数据线(Sj)，使源极驱动器电路的开关(21、22)导通，将电压(Vx)保持在电容(26)中。接着使开关用TFT(13)截止，切换开关(21～24)的状态，向数据线(Sj)施加电压(Vdata+Vx)。进一步使开关用TFT(12)截止，使开关用TFT(14)导通，向有机EL元件(15)提供由驱动用TFT(11)的栅极端子电压(Vdata+Vx)确定的电流。由此，来高效利用数据电压的振幅，并以高精度补偿驱动用TFT(11)的阈值电压的偏差，而不使像素电路(10)的规模增大。