(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년05월13일

(11) 등록번호 10-1394105

(24) 등록일자 2014년05월07일

(51) 국제특허분류(Int. Cl.)

G02F 1/1368 (2006.01) H01L 29/786 (2006.01)

(21) 출원번호 10-2012-0098758(분할)

(22) 출원일자 2012년09월06일

심사청구일자 2012년09월06일

(65) 공개번호 10-2012-0105402

(43) 공개일자 2012년09월25일

(62) 원출원 특허 10-2011-0092425

원출원일자 2011년09월14일

(30) 우선권주장

JP-P-2010-206282 2010년09월15일 일본(JP)

(56) 선행기술조사문헌

JP2010156963 A\*

JP2004045662 A

KR1020040013401 A

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

미야케 히로유키

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 한도오따이 에네루기 켄큐쇼 내

(74) 대리인

장훈

전체 청구항 수 : 총 5 항

심사관 : 정구옹

(54) 발명의 명칭 표시 장치

**(57) 요 약**

본 발명은 프레임 주파수의 변화에 대응시켜서, 개구율을 저감시키지 않고 화소 내에 원하는 유지 용량을 확보할 수 있는 액정 표시 장치를 제공하는 것을 목적으로 한다.

산화물 반도체 재료를 사용한 화소 트랜지스터 및 2개의 용량 소자를 각 화소에 갖는 액정 표시 장치에 있어서, 한 쪽의 용량 소자는, 투광성을 갖는 재료로 구성하여, 화소의 개구율을 향상시킨다. 또한 투광성을 갖는 용량 소자의 특성을 이용하여, 화상의 표시 상태에 의존하여 변화하는 프레임 주파수에 대응시켜서 용량선의 전압값을 조정함으로써, 화소 내의 유지 용량의 크기를 변화시킨다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

삭제

### 청구항 2

삭제

### 청구항 3

표시 장치에 있어서:

절연 표면 상의 게이트 전극;

상기 절연 표면 상의 제 1 배선;

상기 게이트 전극 및 상기 제 1 배선 위의 제 1 절연막;

상기 제 1 절연막을 사이에 개재하는 상기 게이트 전극 위의 채널을 위한 제 산화물 반도체 층;

상기 제 1 산화물 반도체 층과 전기적 접촉하는 소스 전극;

상기 제 1 산화물 반도체 층과 전기적 접촉하는 드레인 전극;

상기 제 1 절연막 위의 제 2 산화물 반도체 층;

상기 제 2 산화물 반도체 층과 전기적 접촉하고, 상기 제 1 절연막 위에 형성되며, 상기 제 1 절연막의 개구를 통해 상기 제 1 배선에 전기적으로 접속되는 제 2 배선;

상기 제 1 산화물 반도체 층, 상기 소스 전극, 상기 드레인 전극, 상기 제 2 산화물 반도체 층 및 상기 제 2 배선 위의 제 2 절연막; 및

상기 제 2 절연막 위의 투명 도전막을 포함하고, 상기 제 2 절연막의 개구를 통해 상기 소스 전극 및 상기 드레인 전극 중 하나에 전기적으로 접속되는 화소 전극을 포함하며,

상기 화소 전극은 상기 제 2 절연막을 사이에 개재하는 상기 화소 전극과 상기 제 2 산화물 반도체 층 사이에 저장 캐퍼시터를 형성하기 위해 상기 제 2 산화물 반도체 층과 중첩하고 있는, 표시 장치.

### 청구항 4

제 3 항에 있어서,

상기 제 1 배선에 공급되는 전위는 상기 표시 장치의 프레임 주파수에 응답하여 가변하는, 표시 장치.

### 청구항 5

제 3 항에 있어서,

상기 제 1 산화물 반도체 층 및 상기 제 2 산화물 반도체 층 각각은 상기 제 1 절연막과 직접 접촉하는, 표시 장치.

### 청구항 6

제 3 항에 있어서,

상기 제 1 산화물 반도체 층 및 상기 제 2 산화물 반도체 층은,

산화물 반도체 막을 절연 표면 상에 형성하고,

상기 제 1 산화물 반도체 층 및 상기 제 2 산화물 반도체 층을 형성하기 위해 상기 산화물 반도체 막을 에칭하는 것을 포함하는 방법에 의해 형성되는, 표시 장치.

## 청구항 7

삭제

## 청구항 8

제 3 항에 있어서,

상기 제 1 산화물 반도체 층 및 상기 제 2 산화물 반도체 층 각각은 인듐, 아연 및 산소를 포함하는, 표시 장치.

## 명세서

### 기술 분야

[0001]

본 발명은 액정 표시 장치에 관한 것이다.

### 배경 기술

[0002]

최근, 액정 디스플레이(LCD) 등의 플랫 패널 디스플레이가 널리 보급되어 있다. 박막 트랜지스터의 반도체층 재료로서, 아모퍼스(비정질) 실리콘이나 폴리(다결정) 실리콘을 사용한 것이 많이 사용되고 있는 한편, 투광성을 갖는 금속 산화물도 주목을 받고 있다. 예를 들어, In-Ga-Zn-O계 산화물 등을, 박막 트랜지스터의 채널층에 적용함으로써, 개구율을 향상시키는 기술이 검토되고 있다. 또한, 특허문현 1에서는, 기생 용량을 저감시켜 박막의 박리에 기인하는 불량을 방지하는 박막 트랜지스터를 제작하는 기술을 개시하고 있다.

[0003]

비특허문현 1에서는, 액정 표시 장치의 저소비 전력화를 도모하기 위하여, 동화상 표시와 정지 화상 표시시의 프레임 주파수를 달리 하는 구성에 대하여 개시하고 있다.

### 선행기술문현

#### 특허문현

[0004]

(특허문현 0001) 일본국 특개2010-098305호 공보

#### 비특허문현

[0005]

(비특허문현 0001) Kazuhiko Tsuda et al., IDW' 02, pp 295-298

### 발명의 내용

#### 해결하려는 과제

[0006]

정지 화상 표시시에 프레임 주파수를 낮게 했을 경우(1/600Hz 내지 1Hz), 화상 신호 등의 전기 신호의 유지 시간을 보다 길게 하고, 보다 양호한 정지 화상 표시를 유지하기 위해서는, 화소 내에서의 유지 용량이 큰 편이 유리하다. 그러나 화소 내에 있어서 유지 용량을 크게 하려고 설계하면, 화소의 개구율이 저감되는 문제나, 화소 트랜지스터의 채널 폭을 크게 해야하는 문제가 있다. 또한, 플리커 노이즈(깜박임)를 방지하고, 보다 매끄러운 동화상 표시를 실현하기 위하여, 동화상 표시시에는 프레임 주파수를 높게 한다(60Hz 내지 180Hz). 컬러 시퀀셜 표시를 할 경우에는, 프레임 주파수를 더욱 높게 한다(180Hz 내지 480Hz). 이 때, 화상 신호 등의 전기 신호는 재빨리 바꿀 수 있으므로, 화소 내에 있어서 유지 용량을 크게 할 필요는 없다. 즉, 정지 화상 표시시 및 동화상 표시시의 어느 경우에 대하여도, 적절한 유지 용량을 좁은 면적의 화소 내에 동시에 확보하는 것은 매우 곤란하다.

[0007]

상기 문제를 감안하여, 개시하는 발명의 일 형태에서는, 프레임 주파수의 변화에 대응시켜서, 개구율을 저감시키지 않고 화소 내에 원하는 유지 용량을 확보할 수 있는 액정 표시 장치를 제공하는 것을 과제 중 하나로 한다. 또한 소비 전력을 저감시켜, 보다 고정밀의 화상 표시가 가능한 액정 표시 장치를 제공하는 것을 과제

중 하나로 한다.

### 과제의 해결 수단

[0008]

본 발명의 일 형태는, 게이트 전극이 주사선과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극이 신호선과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극이 화소 전극과 전기적으로 접속되는 화소 트랜지스터와, 한 쪽의 전극이 제 2 전극과 전기적으로 접속되고, 다른 쪽의 전극이 용량선에 전기적으로 접속되는 제 1 용량 소자와, 한 쪽의 전극이 제 2 전극과 전기적으로 접속되고, 다른 쪽의 전극이 용량선에 전기적으로 접속되는 제 2 용량 소자를 갖고, 제 2 용량 소자는, 한 쪽의 전극이 화소 전극과 같은 충으로 형성되고, 다른 쪽의 전극이 화소 트랜지스터의 반도체층과 같은 반도체 재료로 형성되고, 한 쪽의 전극과 다른 쪽의 전극과의 사이에 유전체층이 끼워진 MOS 커패시터 구조를 갖고, 용량선의 전위를 조정함으로써, 게이트 펄스의 시간간격에 따라 제 2 용량 소자의 용량값을 변화시키는 것을 특징으로 하는 액정 표시 장치이다.

[0009]

또한, 본 발명의 일 형태는, 게이트 전극이 주사선과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극이 신호선과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극이 화소 전극과 전기적으로 접속되는 화소 트랜지스터와, 한 쪽의 전극이 제 2 전극과 전기적으로 접속되고, 다른 쪽 전극이 차폐용 배선에 전기적으로 접속되는 제 1 용량 소자와, 한 쪽의 전극이 제 2 전극과 전기적으로 접속되고, 다른 쪽 전극이 용량선에 전기적으로 접속되는 제 2 용량 소자와, 게이트 전극이 차폐용 배선과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극이, 제 1 용량 소자의 한 쪽의 전극과 전기적으로 접속되고, 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극이 용량선에 전기적으로 접속되는 트랜지스터를 갖고, 제 2 용량 소자는, 한 쪽의 전극이 화소 전극과 같은 충으로 형성되고, 다른 쪽의 전극이 화소 트랜지스터의 반도체층과 같은 반도체 재료로 형성되고, 한 쪽의 전극과 다른 쪽의 전극과의 사이에 유전체층이 끼워진 MOS 커패시터 구조를 갖고, 용량선의 전위를 조정하고, 적어도 화상 표시시에 트랜지스터가 오프가 되도록 전위를 차폐용 배선에 공급함으로써, 게이트 펄스의 시간 간격에 따라서 제 2 용량 소자의 용량값을 변화시키는 것을 특징으로 하는 액정 표시 장치이다.

[0010]

또한 본 발명의 일 형태에 있어서, 화소 전극과 반도체층은, 투광성을 갖는 것을 특징으로 하는 액정 표시 장치이다.

[0011]

또한 본 발명의 일 형태에 있어서, 반도체층은, 산화물 반도체로 구성되어 있어도 좋다.

[0012]

또한, 본 명세서 등에 있어서 「상(上)」나 「하(下)」의 용어는, 구성 요소의 위치 관계가 「직상(直上)」 또는 「직하(直下)」임을 한정하는 것은 아니다. 예를 들어, 「게이트 절연층 상의 게이트 전극」의 표현이라면, 게이트 절연층과 게이트 전극과의 사이에 다른 구성 요소를 포함하는 것을 제외하지 않는다. 또한, 「상」「하」의 용어는 설명의 편의 때문에 사용하는 표현에 지나지 않는다.

[0013]

또한, 본 명세서 등에 있어서 「전극」이나 「배선」의 용어는, 이를 구성 요소를 기능적으로 한정하는 것은 아니다. 예를 들어, 「전극」은 「배선」의 일부로서 사용할 수 있는 경우가 있고, 그 반대도 또한 마찬가지다. 또한, 「전극」이나 「배선」의 용어는, 복수의 「전극」이나 「배선」이 일체가 되어서 형성되어 있을 경우 등도 포함한다.

[0014]

또한, 「소스」나 「드레인」의 기능은, 다른 극성의 트랜지스터를 채용할 경우나, 회로 동작에 있어서 전류의 방향이 변화될 경우 등에는 바뀔 수가 있다. 따라서, 본 명세서에 있어서는, 「소스」나 「드레인」의 용어는, 바꿔서 사용될 수도 있다.

[0015]

또한, 본 명세서 등에 있어서, 「전기적으로 접속」에는, 「어떠한 전기적 작용을 갖는 것」을 통하여 접속되는 경우가 포함된다. 여기서, 「어떠한 전기적 작용을 갖는 것」은, 접속 대상간에서의 전기 신호의 수수를 가능하게 하는 것이면, 특별히 제한을 받지 않는다.

[0016]

예를 들어, 「어떠한 전기적 작용을 갖는 것」에는, 전극이나 배선을 비롯해, 트랜지스터 등의 스위칭 소자, 저항 소자, 인덕터, 커패시터, 그 밖의 각종 기능을 갖는 소자 등이 포함된다.

### 발명의 효과

[0017]

본 발명의 일 형태에 의해, 프레임 주파수의 변화에 대응시켜서, 개구율을 저감시키지 않고 화소 내에 원하는 유지 용량을 확보할 수 있는 액정 표시 장치를 얻을 수 있다. 또한 소비 전력을 저감시켜, 보다 고정밀의 화상

표시가 가능한 액정 표시 장치를 얻을 수 있다.

### 도면의 간단한 설명

[0018]

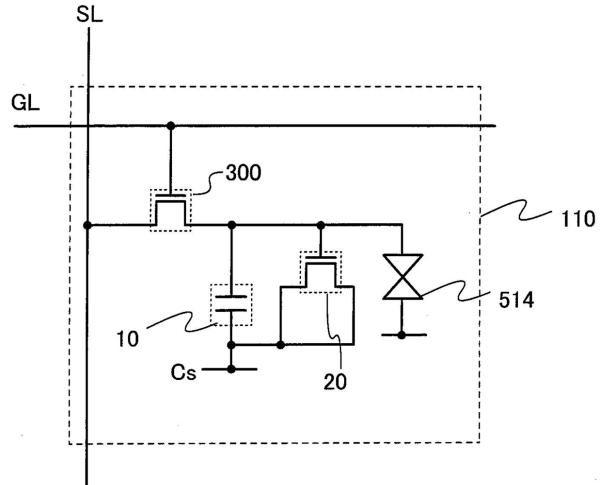

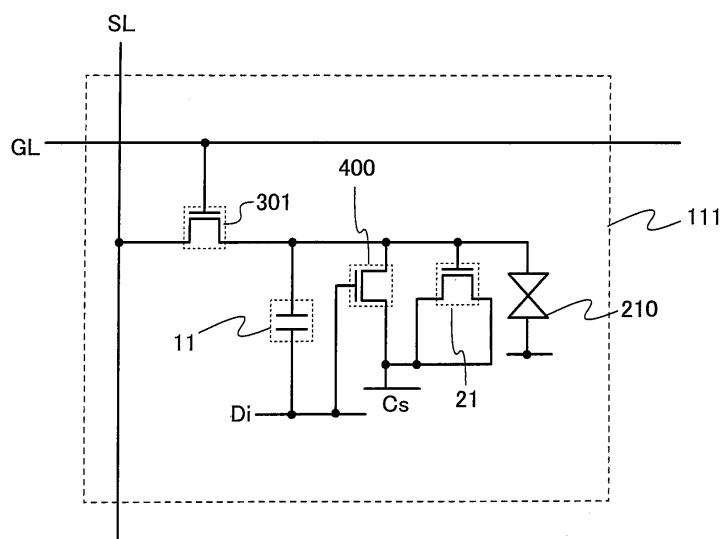

도 1은 액정 표시 장치의 화소 구성을 나타내는 회로도.

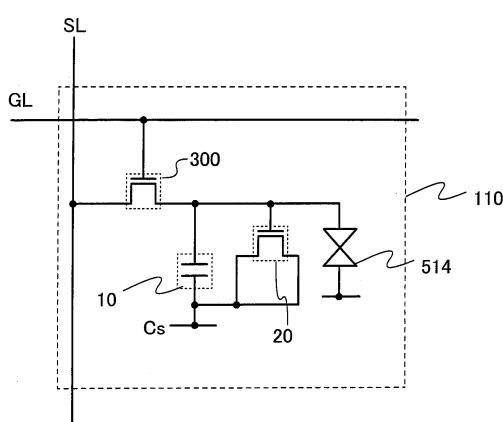

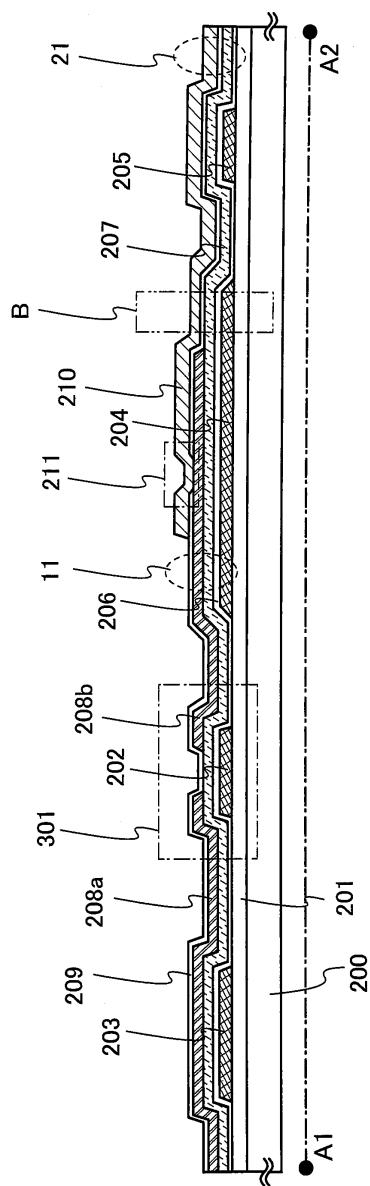

도 2는 액정 표시 장치의 화소 구성을 나타내는 상면도.

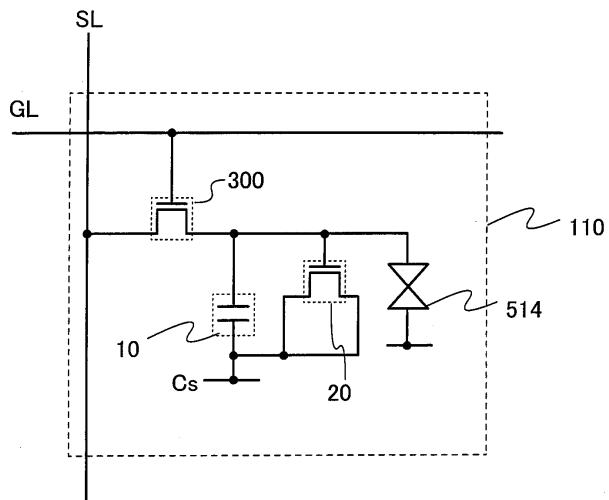

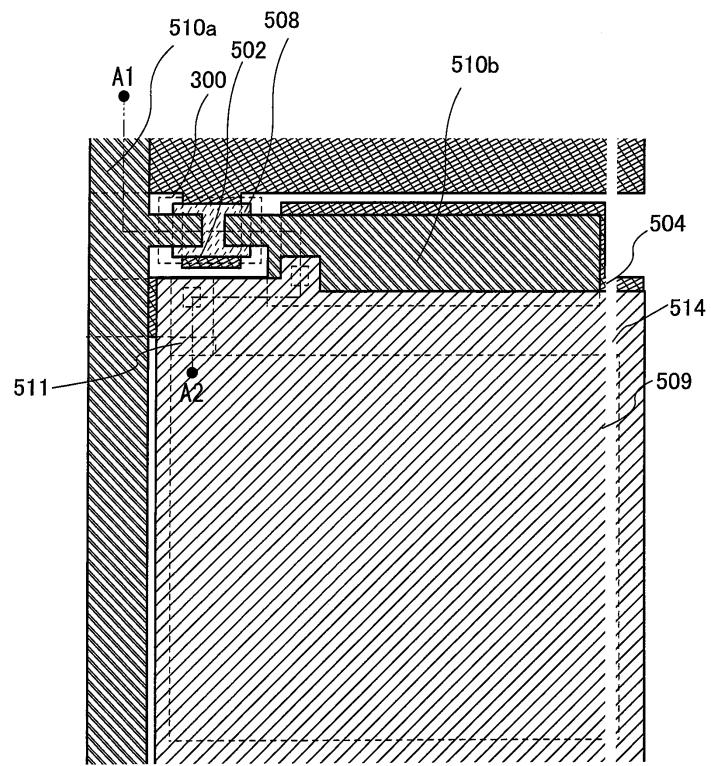

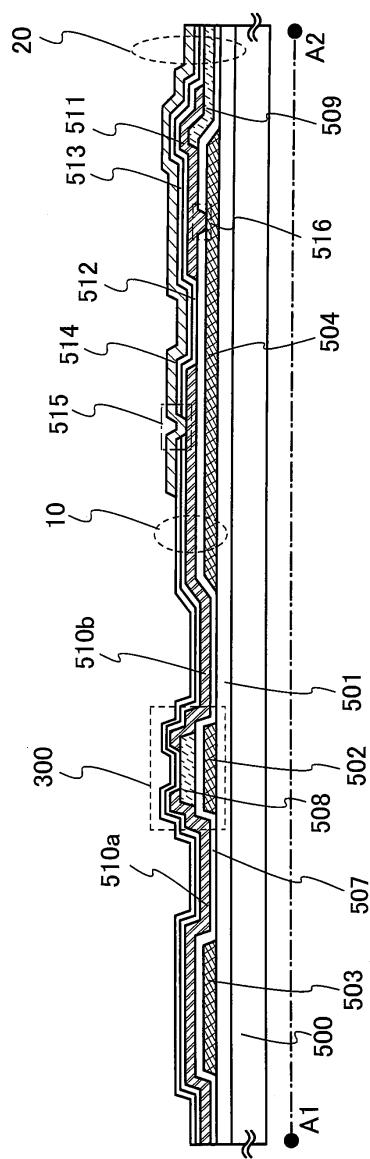

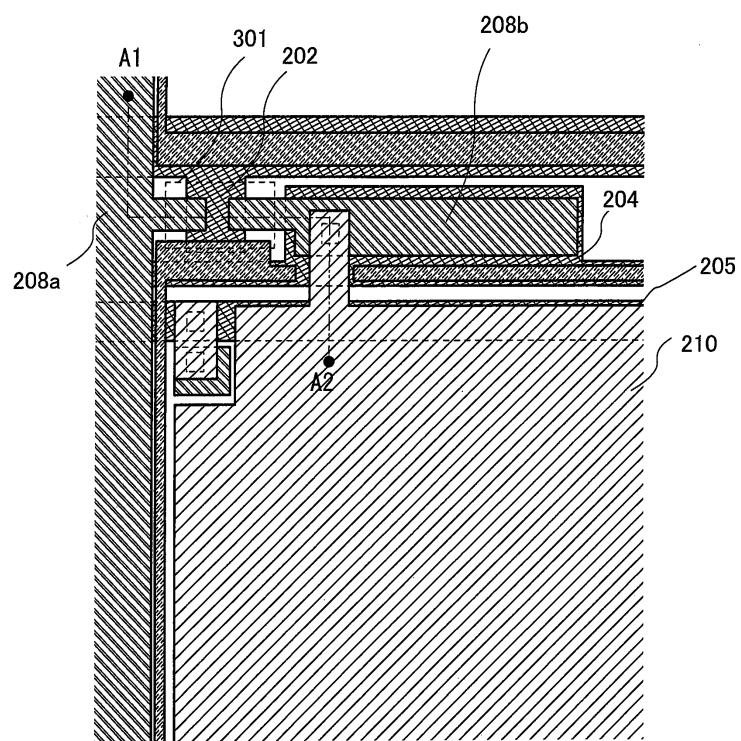

도 3은 액정 표시 장치의 화소 구성을 나타내는 단면도.

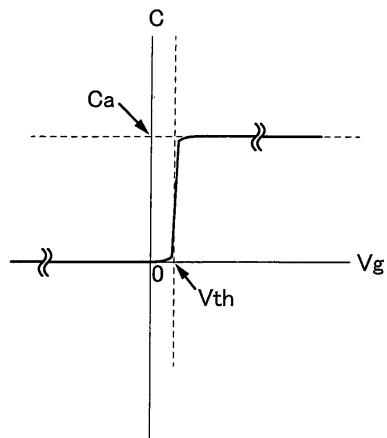

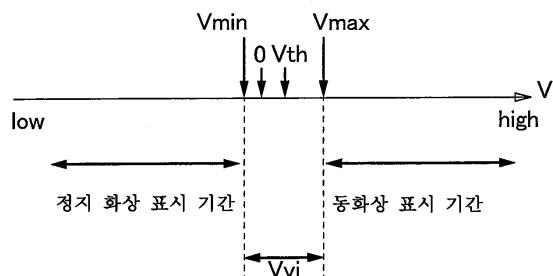

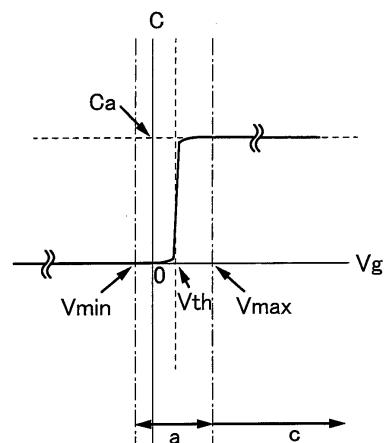

도 4는 용량-전압 특성 및 전압의 관계도.

도 5는 용량-전압특성.

도 6은 액정 표시 장치의 화소 구성을 나타내는 회로도.

도 7은 액정 표시 장치의 화소 구성을 나타내는 상면도.

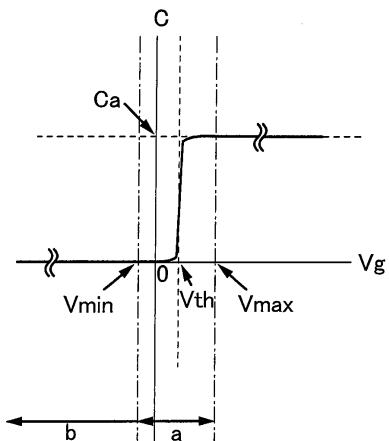

도 8은 액정 표시 장치의 화소 구성을 나타내는 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0019]

이하에서는, 본 발명의 실시형태에 대해서 도면을 사용하여 상세하게 설명한다. 단, 본 발명은 이하의 설명에 한정되지 않고, 그 형태 및 상세를 다양하게 변경할 수 있음은, 당업자라면 용이하게 이해할 수 있다. 또한, 본 발명은 이하에 나타내는 실시형태의 기재 내용에 한정하여 해석되는 것이 아니다.

[0020]

또한, 도면 등에 있어서 도시하는 각 구성의 위치, 크기, 범위 등을, 이해의 간단함을 도모하기 위해, 실제의 위치, 크기, 범위 등을 나타내지 않는 경우가 있다. 따라서, 개시하는 발명은 도면 등에 개시된 위치, 크기, 범위 등에 반드시 한정되지 않는다.

[0021]

또한, 본 명세서등에 있어서의 「제 1」, 「제 2」, 「제 3」 등의 서수는, 구성 요소의 혼동을 피하기 위하여 붙인 것이며, 수적으로 한정하는 것은 아님을 부기한다.

[0022]

(실시형태 1)

[0023]

본 실시형태에서는, 개시하는 발명의 일 형태에 따른 액정 표시 장치에 있어서의 화소의 구성 및 유지 용량을 바꾸는 방법에 대하여 설명한다. 또한 본 실시형태에서 설명하는 액정 표시 장치는, 화상의 표시 상태에 맞추어 용량값을 변화시킬 수 있는 화소를 갖는다.

[0024]

도 1은, 액정 표시 장치가 갖는 화소의 회로의 일례를 도시하는 도면이다.

[0025]

화소(110)는, 화소 트랜지스터(300), 제 1 용량 소자(10), 제 2 용량 소자(20)를 갖는다. 화소 트랜지스터(300)의 게이트 전극은, 주사선(GL)과 전기적으로 접속되고, 화소 트랜지스터(300)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극은, 신호선(SL)과 전기적으로 접속되어 있다. 그리고, 제 1 용량 소자(10)의 한 쪽의 전극과 제 2 용량 소자(20)의 한 쪽의 전극은 전기적으로 접속되고, 화소 트랜지스터(300)의 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극과, 제 1 용량 소자(10)의 다른 쪽의 전극과, 제 2 용량 소자(20)의 다른 쪽의 전극은 전기적으로 접속되어 있다. 또한 제 1 용량 소자(10)의 한 쪽의 전극, 및 제 2 용량 소자(20)의 한 쪽의 전극은 용량선(Cs)과 전기적으로 접속되어 있다.

[0026]

이어서, 도 1에 도시한 화소의 구체적인 구성의 일례를, 도 2 내지 도 3을 사용하여 설명한다. 도 2에 화소의 상면도를 도시한다. 또한, 도 3에 도 2의 쇄선 A1-A2에 있어서의 화소의 단면도를 도시한다.

[0027]

단면 A1-A2에 있어서, 기판(500) 위에 하지층(501)이 형성되고, 하지층(501) 위에 게이트 전극(502), 배선(503), 배선(504)이 형성되어 있다. 또한, 게이트 전극(502), 배선(503), 배선(504)을 덮도록 게이트 절연층(507)이 형성되어 있다. 또한, 반도체층(508)이, 게이트 전극(502)과 겹치도록 게이트 절연층(507) 위에 형성되고, 반도체층(509)이 게이트 절연층(507) 위에 형성되어 있다. 또한, 게이트 전극(502)의 단부와 겹치도록, 반도체층(508) 위에 소스 전극(510a) 및 드레인 전극(510b)이 형성되고, 배선(504)의 일부에 접하여, 게이트 절연층(507), 반도체층(509) 위에 배선(511)이 형성되어 있다. 또한, 배선(511)은, 게이트 절연층(507)에 형성된 콘택트 훌(516)을 통하여 배선(504)에 전기적으로 접속되어 있다. 또한, 반도체층(508)의 일부에 접하여, 소스 전극(510a), 드레인 전극(510b), 배선(511) 위에 절연층(512), 절연층(513)이 순서대로 형성되고, 절연층(513) 위에는 화소 전극(514)이 형성되어 있다. 또한, 화소 전극(514)은, 절연층(512), 절연층(513)에 형성된 콘택트

홀(515)을 통하여 드레인 전극(510b)에 전기적으로 접속되어 있다.

[0028] 배선(504)과 드레인 전극(510b)이, 게이트 절연층(507)을 사이에 끼워 겹치고 있는 부분이 제 1 용량 소자(10)로서 기능한다. 게이트 절연층(507)은 유전체층으로서 기능한다. 또한, 반도체층(509)과 화소 전극(514)이, 절연층(512)과 절연층(513)을 사이에 끼워서 겹치고 있는 부분이 제 2 용량 소자(20)로서 기능한다. 절연층(512)과 절연층(513)은 유전체층으로서 기능한다.

[0029] 유전체층을 다층 구조로 함으로써, 절연층에 형성되는 핀 홀 등에 의한 충간 쇼트를 방지할 수 있다. 즉, 하나의 유전체층에 핀 홀이 생겨도, 핀 홀은 다른 유전체층에서 피복되기 때문에, 제 2 용량 소자(20)의 기능을 향상시킬 수 있다.

[0030] 반도체층(508) 및 반도체층(509)은, 비정질 실리콘, 미결정 실리콘 및 다결정 실리콘을 사용하여 형성할 수 있다. 하지만, 낮은 프레임 주파수로 화소를 구동할 경우에는, 상술한 실리콘계 반도체 재료보다도 에너지 캡이 넓은 반도체 재료를 사용하는 것이 바람직하다. 에너지 캡이 넓은 반도체 재료로서, 적합하게는 산화물 반도체를 사용할 수 있다. 예를 들어, 산화 아연계의 산화물 반도체는 에너지 캡이 약3eV 있어, 가시광역에서 투과성이 뛰어나다. 이러한 산화물 반도체는 n형의 도전성을 나타내는 것이 많지만, 수소 등의 도너가 되는 불순물을 저감시키고, 또한 산소 결손에 기인하는 결함을 저감시킴으로써 보다 진성 반도체에 가깝게 할 수 있다. 이러한 고순도화된 산화물 반도체는, 에너지 캡이 넓고 또한, 트랜지스터의 오프 전류를 충분히 저감할 수 있다.

[0031] 반도체층(508)에 산화물 반도체를 사용하여 화소 트랜지스터(300)를 구성함으로써, 오프 전류를 저감할 수 있고, 화소에 형성한 유지 용량으로부터 전하가 소실되어 버리는 비율을 저감할 수 있다. 즉, 프레임 주파수를 낮게 했을 경우라도, 다음 기록 기간까지 유지 용량에 전하를 계속 보유할 수가 있다.

[0032] 사용하는 산화물 반도체로서는, 적어도 인듐(In) 혹은 아연(Zn)을 포함하는 것이 바람직하다. 특히 In과 Zn을 포함하는 것이 바람직하다. 또한, 상기 산화물을 사용한 트랜지스터의 전기 특성의 편차를 감소시키기 위한 스태빌라이저로서, 그것들에 추가하여 갈륨(Ga)을 갖는 것이 바람직하다. 또한, 스태빌라이저로서 주석(Sn)을 갖는 것이 바람직하다. 또한, 스태빌라이저로서 하프늄(Hf)을 갖는 것이 바람직하다. 또한, 스태빌라이저로서 알루미늄(Al)을 갖는 것이 바람직하다.

[0033] 또한, 다른 스태빌라이저로서, 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 호르뮴(Ho), 에르븀(Er), 토륨(Tm), 이테르븀(Yb), 루테티움(Lu)의 어느 1종 혹은 복수종을 가져도 좋다.

[0034] 예를 들어, 산화물 반도체로서, 산화 인듐, 산화 주석, 산화 아연, 2원계 금속의 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, 3원계 금속의 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, 4원계 금속의 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다.

[0035] 또한, 여기서, 예를 들어, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 갖는 산화물이란 의미이며, In과 Ga와 Zn의 비율은 따지지 않는다. 또한, In과 Ga와 Zn 이외의 금속 원소가 들어 있어도 좋다.

[0036] 또한, 산화물 반도체로서,  $InM_0_3(ZnO)_m$ ( $m > 0$ , 또한, m은 정수가 아님)로 표기되는 재료를 사용하여도 좋다. 또한, M은, Ga, Fe, Mn 및 Co로부터 선택된 1개의 금속 원소 또는 복수의 금속 원소를 나타낸다. 또한, 산화물 반도체로서,  $In_2Sn_0_5(ZnO)_n$ ( $n > 0$ , 또한, n은 정수)로 표기되는 재료를 사용하여도 좋다.

[0037] 예를 들어,  $In:Ga:Zn=1:1:1(=1/3:1/3:1/3)$  또는  $In:Ga:Zn=2:2:1(=2/5:2/5:1/5)$ 의 원자비의 In-Ga-Zn계 산화물이나 그 조성의 균방의 산화물을 사용할 수 있다. 또는,  $In:Sn:Zn=1:1:1(=1/3:1/3:1/3)$ ,  $In:Sn:Zn=2:1:3(=1/3:1/6:1/2)$  또는  $In:Sn:Zn=2:1:5(=1/4:1/8:5/8)$ 의 원자비의 In-Sn-Zn계 산화물이나 그 조성의 균방의 산화물을 사용하면 좋다.

[0038] 하지만, 이것들에 한정되지 않고, 필요로 하는 반도체 특성(이동도, 임계값, 편차 등)에 따라서 적절한 조성의 것을 사용하면 좋다. 또한, 필요로 하는 반도체특성을 얻기 위하여, 캐리어 농도나 불순물 농도, 결함 밀도,

금속 원소와 산소의 원자수 비, 원자간 결합 거리, 밀도 등을 적절한 것으로 하는 것이 바람직하다.

[0039] 또한, 화소 트랜지스터(300)의 반도체층(508)은, 게이트 전극(502)에 겹치는 구성을 사용하는 것이 바람직하다. 이러한 구성을 채용함으로써, 기판(500) 측에서 입사한 빛에 의해 반도체층(508) 중의 산화물 반도체가 열화하는 것을 방지할 수 있다. 따라서, 화소 트랜지스터(300)의 임계값 전압이 시프트하는 등의 특성의 열화가 일어나는 것을 방지할 수 있다.

[0040] 화소 전극(514)에는, 투광성을 갖는 도전 재료를 사용하는 것이 바람직하다. 투광성을 갖는 도전 재료로서는, 산화 규소를 함유하는 산화 인듐 주석(ITSO), 산화 인듐 주석(ITO), 산화 아연(ZnO), 산화 인듐 아연(IZO), 갈륨을 첨가한 산화 아연(GZO) 등의 재료를 사용할 수 있다. 또한 본 명세서에 있어서, 투광성을 갖는 도전 재료란 가시광의 투과율이 75 내지 100%인 재료를 가리킨다.

[0041] 반도체층(509)에 산화물 반도체를 사용하고, 화소 전극(514)에 투광성을 갖는 도전재료를 사용함으로써, 투광성을 갖는 제 2 용량 소자(20)를 형성할 수 있다. 따라서, 화소(110)의 개구율을 향상시킬 수 있다. 제 2 용량 소자(20)의 면적을 화소 피치의 7할 이상 또는 8할 이상으로 함으로써, 개구율을 보다 향상시킨 액정 표시 장치를 실현할 수 있다.

[0042] 이어서, 도 1 내지 도 3에 도시한 화소가, 유지 용량의 값을 변화시키는 구체적인 방법에 대하여 설명한다.

[0043] 도 4a에, MOS 커패시터의 용량(C)-전압(Vg) 특성을 나타낸다. 가로축은 게이트 전압(Vg), 세로축은 용량(C)이다. 반도체층(509)과 화소 전극(514)이, 절연층(512)과 절연층(513)을 사이에 끼워 겹쳐서 형성되어 있는 제 2 용량 소자(20)는, MOS 커패시터를 구성하고 있다. MOS 커패시터는, 도 4a에 도시한 바와 같이, 전압값이 어떤 일정한 임계값 전압(Vth)보다 낮을 경우는, 용량 소자로서 기능하지 않고, 전압값이 어떤 일정한 임계값 전압(Vth) 이상일 경우에만, 용량 소자로서 기능하는 특성을 가진다.

[0044] 도 4b에, 동화상 표시 기간과 정지 화상 표시 기간에 있어서, 용량선(Cs)의 전압값을 변화시켰을 경우, 용량선(Cs)가 취할 수 있는 전압값의 범위의 모식도를 도시한다. 비디오 데이터 전압(Vvi)은, 도 4b에 도시한 바와 같이, 최대치(Vmax)로부터, 최소값(Vmin)까지의 어떤 일정한 범위내의 값을 취한다. 따라서, 용량선(Cs)의 전압값을, 동화상 표시 기간에는, 비디오 데이터 전압(Vvi)의 최대치(Vmax) 이상으로 조정하고, 정지 화상 표시 기간에는, 비디오 데이터 전압(Vvi)의 최소값(Vmin) 이하로 조정한다.

[0045] 도 5에 있어서, 제 2 용량 소자(20)의 게이트 전극의 전압(Vg)이, 비디오 데이터 전압(Vvi)의 최대치(Vmax)로부터, 최소값(Vmin)까지의 값을 취할 경우의 범위를 a, 비디오 데이터 전압(Vvi)의 최소값(Vmin) 이하의 값을 취할 경우의 범위를 b, 비디오 데이터 전압(Vvi)의 최대치(Vmax) 이상의 값을 취할 경우의 범위를 c로 한다.

[0046] 용량선(Cs)의 전압값을 비디오 데이터 전압(Vvi)의 최대치(Vmax) 이상으로 조정했을 경우, 제 2 용량 소자(20)의 게이트 전극의 전압값(Vg)은, 비디오 데이터 전압(Vvi)의 최소값(Vmin) 이하의 값을 취한다. 도 5a로부터, 제 2 용량 소자(20)의 게이트 전극의 전압값(Vg)이, 범위 b 내의 어느 값을 취할 때, 제 2 용량 소자(20)의 용량값은, 값을 취하지 않는 것을 알 수 있다.

[0047] 즉, 동화상 표시 기간에는, 제 1 용량 소자(10)의 한 쪽의 전극, 및 제 2 용량 소자(20)의 한 쪽의 전극과 전기적으로 접속되는 용량선(Cs)의 전압값이, 비디오 데이터 전압(Vvi)의 최대치(Vmax) 이상의 값을 취하기 때문에, MOS 커패시터인 제 2 용량 소자(20)는 기능하지 않게 된다. 따라서, 화소(110)에 있어서는, 제 1 용량 소자(10)만이 기능한다.

[0048] 용량선(Cs)의 전압값을 비디오 데이터 전압(Vvi)의 최소값(Vmin)이하로 조정했을 경우, 제 2 용량 소자(20)의 게이트 전극의 전압값(Vg)은, 비디오 데이터 전압(Vvi)의 최대치(Vmax) 이상의 값을 취한다. 도 5b로부터, 제 2 용량 소자(20)의 게이트 전극의 전압값(Vg)이, 범위 c중 어느 값을 취할 때, 제 2 용량 소자(20)의 용량값은, 어떤 일정한 값(Ca)을 취하는 것을 알 수 있다.

[0049] 즉, 정지 화상 표시 기간에는, 제 1 용량 소자(10)의 한 쪽의 전극, 및 제 1 용량 소자(10)의 한 쪽의 전극과 전기적으로 접속되는 용량선(Cs)의 전압값이, 비디오 데이터 전압(Vvi)의 최소값(Vmin) 이하의 값을 취하기 때문에, MOS 커패시터인 제 2 용량 소자(20)는 기능한다. 따라서, 화소(110)에 있어서는, 제 1 용량 소자(10) 및 제 2 용량 소자(20)가 기능한다.

[0050] 이와 같이, 상기 구성에 따르면, 용량선(Cs)의 전압값을 조정함으로써, 동화상 표시 기간과, 정지 화상 표시 기간의 양 기간에서 용량값의 교체가 가능해진다. 즉, 화상의 표시 상태에 의존하여, 극단적으로 변화되는 프레임 주파수의 값에 대응시켜서, 그 때마다, 화소 내의 용량값을, 각 화소에 가장 적합하게 변화시킬 수 있다.

특히 컬러 시퀀셜 표시기와 같은 지극히 높은 프레임 주파수에서 화소를 구동할 경우에는, 한층 더 화소내의 용량값을 저감시킬 수 있기 때문에, 액정 표시 장치의 소형화, 고집적화가 실현된다. 즉, 화소에 대하여, 효율적으로 원하는 용량값을 설정할 수 있기 때문에, 액정 표시 장치 전체의 소비 전력을 저감시킬 수 있게 된다.

[0051] 또한, 상기 구성에 따르면, 제 1 용량 소자(10)의 한 쪽의 전극, 및 제 2 용량 소자(20)의 한 쪽의 전극과 전기적으로 접속되는 용량선(Cs)의 전압값을 조정 함으로써, 화소 전체의 용량값을 독립적으로 제어할 수 있으므로 배선을 쓸데없이 리드시킬 필요는 없다. 따라서, 인접 배선 간의 겹침으로 인해 생기는 기생 용량을 저감시킬 수 있고, 보다 고정밀의 액정 표시 장치를 얻을 수 있다. 또한, 화소 트랜지스터(300)의 채널 폭에 의존하지 않고, 적절한 유지 용량을 화소 내에 확보할 수 있으므로, 액정 표시 장치의 고집적화가 용이해진다.

[0052] (실시형태 2)

[0053] 본 실시형태에서는, 개시하는 발명의 일 형태에 따른 액정 표시 장치에 있어서의 다른 화소의 구성 및 유지 용량을 바꾸는 방법에 대하여 설명한다. 또한 본 실시형태에서 설명하는 액정 표시 장치는, 화상의 표시 상태에 맞춰서 용량값을 변화시킬 수 있는 화소를 갖는다.

[0054] 도 6은, 액정 표시 장치가 갖는 화소의 회로의 일례를 도시하는 도면이다.

[0055] 화소(111)는, 화소 트랜지스터(301), 트랜지스터(400), 제 1 용량 소자(11), 제 2 용량 소자(21)를 갖는다. 화소 트랜지스터(301)의 게이트 전극은, 주사선(GL)과 전기적으로 접속되고, 화소 트랜지스터(301)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극은, 신호선(SL)과 전기적으로 접속되어 있다. 그리고, 제 1 용량 소자(11)의 한 쪽의 전극과 트랜지스터(400)의 게이트 전극은 전기적으로 접속되고, 트랜지스터(400)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극과 제 2 용량 소자(21)의 한 쪽의 전극은 전기적으로 접속되고, 화소 트랜지스터(301)의 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극과, 제 1 용량 소자(11)의 다른 쪽의 전극과, 트랜지스터(400)의 소스 전극 또는 드레인 전극의 다른 쪽이 되는 제 2 전극과, 제 2 용량 소자(21)의 다른 쪽의 전극은 전기적으로 접속되어 있다.

[0056] 또한 트랜지스터(400)의 게이트 전극 및 제 1 용량 소자(11)의 한 쪽의 전극은, 차폐용 배선(Di)과 전기적으로 접속되고, 트랜지스터(400)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극 및 제 2 용량 소자(21)의 한 쪽의 전극은, 용량선(Cs)과 전기적으로 접속되어 있다. 또한, 차폐용 배선(Di)에는, 적어도 화상 표시시에 트랜지스터(400)가 오프가 되도록 전위가 공급되어 있다.

[0057] 이어서, 도 6에 도시한 화소의 구체적인 구성의 일례를, 도 7 내지 도 8을 사용하여 설명한다. 도 7에 화소의 상면도를 도시한다. 또한, 도 8에 도 7의 쇄선 A1-A2에서의 화소의 단면도를 도시한다.

[0058] 단면 A1-A2에 있어서, 기판(200) 위에 하지층(201)이 형성되고, 하지층(201) 위에 게이트 전극(202), 배선(203), 배선(204), 배선(205)이 형성되어 있다. 또한, 게이트 전극(202), 배선(203), 배선(204), 배선(205) 위에 게이트 절연층(206)과 반도체층(207)이 형성되어 있다. 또한, 반도체층(207) 위에 소스 전극(208a) 및 드레인 전극(208b)이 형성되어 있다. 또한, 반도체층(207)의 일부에 접하고, 소스 전극(208a) 및 드레인 전극(208b) 위에 절연층(209)이 형성되어 있다. 절연층(209) 위에는 화소 전극(210)이 형성되어 있다. 또한, 화소 전극(210)은, 절연층(209)에 형성된 콘택트 홀(211)을 통하여 드레인 전극(208b)에 전기적으로 접속되어 있다.

[0059] 배선(204)과 드레인 전극(208b)이, 게이트 절연층(206)과 반도체층(207)을 사이에 끼워서 겹치고 있는 부분이 제 1 용량 소자(11)로서 기능한다. 게이트 절연층(206)과 반도체층(207)은 유전체층으로서 기능한다. 또한, 반도체층(207)과 화소 전극(210)이, 절연층(209)을 사이에 끼워서 겹치고 있는 부분이 제 2 용량 소자(21)로서 기능한다. 절연층(209)은 유전체층으로서 기능한다.

[0060] 유전체층을 다층 구조로 함으로써, 절연층에 형성되는 핀 홀 등에 의한 충간 쇼트를 방지시킬 수 있다. 즉 하나의 유전체층에 핀 홀이 생겨도, 핀 홀은 다른 유전체층으로 피복되기 때문에, 제 1 용량 소자(11)의 기능을 향상시킬 수 있다.

[0061] 반도체층(207)에 산화물 반도체를 사용하여 화소 트랜지스터(301)를 구성함으로써 오프 전류를 저감할 수 있고, 화소에 설치한 유지 용량으로부터 전하가 소실되어 버리는 비율을 저감할 수 있다. 즉, 프레임 주파수를 낮게 한 경우에도, 다음 기록 기간까지 유지 용량에 전하를 계속 유지할 수 있다.

[0062] 화소 전극(210)에는, 투광성을 갖는 도전 재료를 사용하는 것이 바람직하다. 투광성을 갖는 도전 재료로서는, 산화 규소를 포함하는 산화 인듐 주석(ITSO), 산화 인듐 주석(ITO), 산화 아연(ZnO), 산화 인듐 아연(IZO), 갈륨을 첨가한 산화 아연(GZO) 등의 재료를 사용할 수 있다. 또한 본 명세서에 있어서, 투광성을 갖는 도전 재료란

가시광의 투과율이 75 내지 100%인 재료를 가리킨다.

[0063] 반도체층(207)에 산화물 반도체를 사용하고, 화소 전극(210)에 투광성을 갖는 도전 재료를 사용함으로써, 투광성을 갖는 제 2 용량 소자(21)를 형성할 수 있게 된다. 이로써, 화소(111)의 개구율을 향상시킬 수 있다. 제 2 용량 소자(21)의 면적을, 화소 피치의 7할 이상, 또는 8할 이상으로 함으로써, 개구율을 보다 향상시킨 액정 표시 장치를 실현할 수 있다. 또한, 화소 피치란, 이웃하는 신호선으로부터 신호선까지의 거리를 1번으로 하고, 이웃하는 주사선으로부터 주사선까지의 거리를 다른 1번으로 하고, 이를 양면에 둘러싸여진 부분의 면적을 나타내는 것이다.

[0064] 이어서, 도 6 내지 도 8에 나타낸 화소가, 유지 용량의 값을 변화시키는 구체적인 방법에 대하여 설명한다.

[0065] 반도체층(207)과 화소 전극(210)이, 절연층(209)을 사이에 끼워서 겹쳐서 형성되어 있는 제 2 용량 소자(21)는, MOS 커패시터를 구성한다. MOS 커패시터는, 도 4a에 도시한 바와 같이, 전압값이 어떤 일정한 임계값 전압( $V_{th}$ )보다 낮을 경우는, 용량 소자로서 기능하지 않고, 전압값이 어떤 일정한 임계값 전압( $V_{th}$ ) 이상의 경우에만 용량 소자로서 기능하는 특성을 갖는다.

[0066] 도 4b에, 동화상 표시 기간과 정지 화상 표시 기간에 있어서, 용량선(Cs)의 전압값을 변화시켰을 경우, 용량선(Cs)이 취할 수 있는 전압값의 범위의 모식도를 도시한다. 비디오 데이터 전압( $V_{vi}$ )은, 도 4b에 도시한 바와 같이, 최대치( $V_{max}$ )로부터 최소값( $V_{min}$ )까지의 어떤 일정한 범위 내의 값을 취한다. 따라서, 용량선(Cs)의 전압값을, 동화상 표시 기간에는, 비디오 데이터 전압( $V_{vi}$ )의 최대치( $V_{max}$ ) 이상으로 조정하고, 정지 화상 표시 기간에는 비디오 데이터 전압( $V_{vi}$ )의 최소값( $V_{min}$ ) 이하로 조정한다.

[0067] 또한, 화소(111)에 있어서, 차폐용 배선(Di)을 설치하는 것은, 도 8에 있어서의 영역(B)이 도통하는 것을 방지하기 위해서이다. 따라서, 트랜지스터(400)의 게이트 전극과 전기적으로 접속되는 차폐용 배선(Di)에는, 적어도 화상 표시시에는, 트랜지스터(400)가 오프가 되도록 전위를 공급할 필요가 있다.

[0068] 용량선(Cs)의 전압값을 비디오 데이터 전압( $V_{vi}$ )의 최대치( $V_{max}$ ) 이상으로 조정했을 경우, 제 2 용량 소자(21)의 게이트 전극의 전압값( $V_g$ )은, 비디오 데이터 전압( $V_{vi}$ )의 최소값( $V_{min}$ ) 이하의 값을 취한다. 도 5a로부터, 제 2 용량 소자(21)의 게이트 전극의 전압값( $V_g$ )이, 범위 b 내의 어느 값을 취할 때, 제 2 용량 소자(21)의 용량값은, 값을 취하지 않음을 알 수 있다.

[0069] 즉, 동화상 표시 기간에는, 제 2 용량 소자(21)의 한 쪽의 전극, 및 트랜지스터(400)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극과 전기적으로 접속되는 용량선(Cs)의 전압값이, 비디오 데이터 전압( $V_{vi}$ )의 최대치( $V_{max}$ ) 이상의 값을 취하기 때문에, MOS 커패시터인 제 2 용량 소자(21)는 기능하지 않게 된다. 따라서, 화소(111)에 있어서는, 제 1 용량 소자(11)만이 기능한다.

[0070] 용량선(Cs)의 전압값을 비디오 데이터 전압( $V_{vi}$ )의 최소값( $V_{min}$ ) 이하로 조정했을 경우, 제 2 용량 소자(21)의 게이트 전극의 전압값( $V_g$ )은, 비디오 데이터 전압( $V_{vi}$ )의 최대치( $V_{max}$ ) 이상의 값을 취한다. 도 5b로부터, 제 2 용량 소자(21)의 게이트 전극의 전압값( $V_g$ )이, 범위 c 중 어느 값을 취할 때, 제 2 용량 소자(21)의 용량값은 어떤 일정한 값 Ca를 취하는 것을 알 수 있다.

[0071] 즉, 정지 화상 표시 기간에는, 제 2 용량 소자(21)의 한 쪽의 전극, 및 트랜지스터(400)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극과 전기적으로 접속되는 용량선(Cs)의 전압값이, 비디오 데이터 전압( $V_{vi}$ )의 최소값( $V_{min}$ ) 이하의 값을 취하기 때문에, MOS 커패시터인 제 2 용량 소자(21)는 기능한다. 따라서, 화소(111)에 있어서는, 제 1 용량 소자(11) 및 제 2 용량 소자(21)가 기능한다.

[0072] 이와 같이, 상기 구성에 따르면, 용량선(Cs)의 전압값을 조정함으로써, 동화상 표시 기간과, 정지 화상 표시 기간의 양 기간에서 용량값의 교체가 가능해진다. 즉, 화상의 표시 상태에 의존하여, 극단적으로 변화되는 프레임 주파수의 값에 대응시켜서, 그 때마다, 화소 내의 용량값을, 각 화소에 가장 적합하게 변화시킬 수 있다. 특히 컬러 시원셜 표시시와 같은 지극히 높은 프레임 주파수에서 화소를 구동할 경우에는, 화소 내의 용량값을 한층 더 저감시킬 수 있기 때문에, 액정 표시 장치의 소형화, 고집적화가 실현된다. 즉, 화소에 대하여, 효율적으로 원하는 용량값을 설정할 수 있으므로, 액정 표시 장치 전체의 소비 전력을 저감시킬 수 있게 된다.

[0073] 또한, 상기 구성에 따르면, 제 2 용량 소자(21)의 한 쪽의 전극, 및 트랜지스터(400)의 소스 전극 또는 드레인 전극의 한 쪽이 되는 제 1 전극과 전기적으로 접속되는 용량선(Cs)의 전압값을 조정함으로써, 화소 전체의 용량값을 독립적으로 제어할 수 있기 때문에 쓸데없이 배선을 리드할 필요는 없다. 따라서, 인접 배선간의 겹침으로 인해 생기는 기생 용량을 저감시킬 수 있고, 보다 고정밀의 액정 표시 장치를 얻을 수 있다. 또한, 화소 트

랜지스터(301)의 채널 폭에 의존하지 않고, 적절한 유지 용량을 화소 내에 확보할 수 있기 때문에, 액정 표시 장치의 고집적화가 용이해진다.

### 부호의 설명

[0074]

|              |              |

|--------------|--------------|

| 10 용량 소자     | 11 용량 소자     |

| 20 용량 소자     | 21 용량 소자     |

| 110 화소       | 111 화소       |

| 200 기판       | 201 하지층      |

| 202 게이트 전극   | 203 배선       |

| 204 배선       | 205 배선       |

| 206 게이트 절연층  | 207 반도체층     |

| 209 절연층      | 210 화소 전극    |

| 211 콘택트 홀    | 300 화소 트랜지스터 |

| 301 화소 트랜지스터 | 400 트랜지스터    |

| 500 기판       | 501 하지층      |

| 502 게이트 전극   | 503 배선       |

| 504 배선       | 507 게이트 절연층  |

| 508 반도체층     | 509 반도체층     |

| 511 배선       | 512 절연층      |

| 513 절연층      | 514 화소 전극    |

| 515 콘택트 홀    | 516 콘택트 홀    |

| 208a 소스 전극   | 208b 드레인 전극  |

| 510a 소스 전극   | 510b 드레인 전극  |

### 도면

#### 도면1

도면2

## 도면3

## 도면4

(a)

(b)

## 도면5

(a)

(b)

## 도면6

도면7

도면8

|                |                                      |         |            |

|----------------|--------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的标题                              |         |            |

| 公开(公告)号        | KR101394105B1                        | 公开(公告)日 | 2014-05-13 |

| 申请号            | KR1020120098758                      | 申请日     | 2012-09-06 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                         |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                   |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                   |         |            |

| [标]发明人         | MIYAKE HIROYUKI                      |         |            |

| 发明人            | MIYAKE, HIROYUKI                     |         |            |

| IPC分类号         | G02F1/1368 H01L29/786                |         |            |

| CPC分类号         | H01L27/1225 H01L27/1255 G02F1/136213 |         |            |

| 代理人(译)         | 李昌勋                                  |         |            |

| 优先权            | 2010206282 2010-09-15 JP             |         |            |

| 其他公开文献         | KR1020120105402A                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>            |         |            |

#### 摘要(译)

本发明的一个目的是提供一种液晶显示装置，该液晶显示装置允许在像素中确保所需的存储电容器，而不会响应于帧频的变化而降低孔径比。在包括像素晶体管和在每个像素中使用氧化物半导体材料的两个电容元件的液晶显示装置中，一个电容元件包括透光材料以改善像素的孔径比。此外，通过使用透光电容元件的特性，通过响应于根据所显示的图像而变化的帧频调节电容值的电压值，改变像素中的存储电容器的尺寸。