(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0068936

(43) 공개일자 2010년06월24일

(51) Int. Cl.

G09G 3/36 (2006.01) G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

(21) 출원번호 10-2008-0127456

(22) 출원일자 2008년12월15일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

강필성

경북 구미시 구평동 부영아파트 308/105

박만규

서울 은평구 수색동 16-2번지 수색아파트 201호

(뒷면에 계속)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 10 항

#### (54) 액정표시장치

#### (57) 요 약

본 발명은 액정표시장치에 관한 것으로, 제1 단계에서 다수의 하이논리의 비트들이 연속된 후에 다수의 로우논리의 비트들이 연속되는 프리엠블신호를 데이터 배선쌍을 통해 전송하고 락 신호를 락 체크 배선을 통해 전송하며, 제2 단계에서 소스 콘트롤 패킷을 상기 데이터 배선쌍을 통해 전송하며, 제3 단계에서 RGB 데이터 패킷을 상기 데이터 배선쌍을 통해 전송하는 타이밍 콘트롤러; 및 상기 프리엠블신호에 따라 출력 클럭들을 락킹시키고 상기 출력 클럭이 락킹되면 상기 락 신호를 상기 타이밍 콘트롤러에 피드백 입력하고, 상기 소스 콘트롤 패킷을 이용하여 소스 콘트롤 데이터를 발생하며, 상기 출력 클럭에 따라 상기 RGB 데이터 패킷의 RGB 데이터를 샘플링하고 상기 소스 콘트롤 데이터에 따라 상기 RGB 데이터를 정극성/부극성 데이터전압으로 변환하여 출력하는 다수의 소스 드라이브 IC들을 구비한다.

#### 대 표 도 - 도6

(72) 발명자

고근우

경북 칠곡군 석적읍 남율리 우방신천지아파트 205

동 1501호

홍진철

경북 구미시 오태동 대동3차아파트 102/1105호

## 특허청구의 범위

### 청구항 1

제1 단계에서 다수의 하이논리의 비트들이 연속된 후에 다수의 로우논리의 비트들이 연속되는 프리앰블신호를 데이터 배선쌍을 통해 전송하고 락 신호를 락 체크 배선을 통해 전송하며, 제2 단계에서 소스 콘트롤 패킷을 상기 데이터 배선쌍을 통해 전송하며, 제3 단계에서 RGB 데이터 패킷을 상기 데이터 배선쌍을 통해 전송하는 타이밍 콘트롤러; 및

상기 프리앰블신호에 따라 출력 클럭들을 락킹시키고 상기 출력 클럭이 락킹되면 상기 락 신호를 상기 타이밍 콘트롤러에 피드백 입력하고, 상기 소스 콘트롤 패킷을 이용하여 소스 콘트롤 데이터를 발생하며, 상기 출력 클럭에 따라 상기 RGB 데이터 패킷의 RGB 데이터를 샘플링하고 상기 소스 콘트롤 데이터에 따라 상기 RGB 데이터를 정극성/부극성 데이터전압으로 변환하여 출력하는 다수의 소스 드라이브 IC들을 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 RGB 데이터 패킷은,

클럭 비트, 상기 클럭 비트 뒤에 할당된 전반부 RGB 데이터 비트들, 상기 전반부 RGB 데이터 비트들 뒤에 할당된 내부 데이터 인에이블 클럭 비트, 상기 내부 데이터 인에이블 클럭 비트 뒤에 할당된 후반부 RGB 데이터 비트들을 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 3

제 2 항에 있어서,

상기 소스 콘트롤 데이터는,

상기 극성/부극성 데이터전압의 극성을 결정하는 극성제어신호; 및

상기 소스 드라이브 IC들의 출력 타이밍을 결정하는 소스 출력 인에이블신호를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 4

제 3 항에 있어서,

상기 소스 콘트롤 데이터는,

상기 소스 출력 인에이블 신호의 활성화 정보;

상기 소스 출력 인에이블 신호의 펄스폭 정보; 및

상기 극성제어신호의 활성화 정보를 포함하는 것을 특징으로 하는 것을 특징으로 하는 액정표시장치.

### 청구항 5

제 4 항에 있어서,

상기 소스 출력 인에이블 신호의 펄스폭은 상기 펄스폭 정보에 따라 상기 소스 콘트롤 패킷과 상기 RGB 데이터 패킷 중 어느 한 패킷의 길이×i(i는 자연수) 단위로 결정되는 것을 특징으로 하는 액정표시장치.

### 청구항 6

제 1 항에 있어서,

상기 프리앰블신호는,

상기 출력 클럭보다 낮은 주파수로 발생되는 제1 펄스열; 및

상기 출력 클럭보다 낮고 상기 제1 펄스열의 주파수보다 높은 주파수로 상기 제1 펄스열에 이어서 발생되는 제2

펄스열을 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 7

제 6 항에 있어서,

상기 제2 펄스열은,

상기 제1 펄스열보다 주파수가 높은 제3 펄스열들; 및

상기 제3 펄스열들 사이에서 발생되고 상기 제3 펄스열들보다 주파수가 높은 상기 제4 펄스열들을 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 8

제 1 항에 있어서,

상기 타이밍 콘트롤러는,

상기 소스 드라이브 IC들의 출력 버퍼 증폭비를 결정하는 PWRC1/2 옵션정보, 상기 소스 드라이브 IC들의 차지웨어전압 출력을 결정하는 MODE 옵션정보, 상기 소스 출력 인에이블신호의 수신 경로를 결정하는 SOE\_EN 옵션정보, 상기 극성제어신호의 수신 경로를 결정하는 PACK\_EN 옵션정보, 상기 소스 드라이브 IC들의 출력 채널 수를 결정하는 CHMODE 옵션정보, 상기 소스 드라이브 IC 별로 고유의 칩 식별코드를 부여하여 상기 소스 드라이브 IC들을 독립적으로 제어할 수 있게 하는 CID1/2 옵션 정보, 상기 소스 드라이브 IC들로부터 출력되는 상기 정극성/부극성 데이터전압들의 수평 극성 반전 주기를 결정하는 H\_2DOT 옵션 정보 중 하나 이상의 옵션정보를 포함한 제2 소스 콘트롤 패킷을 발생하고,

상기 제2 단계에서 상기 제2 소스 콘트롤 패킷을 상기 데이터 배선쌍을 통해 상기 소스 드라이브 IC들에 전송하는 것을 특징으로 하는 액정표시장치.

### 청구항 9

제 1 항에 있어서,

상기 소스 드라이브 IC들은,

상기 출력 클럭이 락킹된 후에 상기 락 신호를 순차적으로 이웃하는 소스 드라이브 IC에 전달하고 마지막 소스 드라이브 IC는 상기 락 신호를 상기 타이밍 콘트롤러에 입력하며,

상기 타이밍 콘트롤러는 상기 마지막 소스 드라이브 IC와 테스트 모드 인에이블신호 중 적어도 어느 하나가 입력된 후에 상기 제2 단계로 이행하는 것을 특징으로 하는 액정표시장치.

### 청구항 10

제 1 항에 있어서,

상기 타이밍 콘트롤러와 상기 소스 드라이브 IC들을 병렬로 접속시키는 제어 배선쌍을 더 구비하고,

상기 타이밍 콘트롤러와 상기 제어 배선쌍을 통해 상기 소스 드라이브 IC들 각각을 식별하기 위한 칩 식별코드와 상기 소스 드라이브 IC들 각각의 기능들을 제어하는 제어 데이터들을 전송되는 것을 특징으로 하는 액정표시장치.

## 명세서

### 발명의 상세한 설명

#### 기술분야

[0001] 본 발명은 액정표시장치에 관한 것이다.

## 배경기술

[0002] 액티브 매트릭스(Active Matrix) 구동방식의 액정표시장치는 스위칭 소자로서 박막트랜지스터(Thin Film Transistor : 이하 "TFT"라 함)를 이용하여 동영상을 표시하고 있다. 이 액정표시장치는 음극선관(Cathode Ray Tube, CRT)에 비하여 소형화가 가능하여 휴대용 정보기기, 사무기기, 컴퓨터 등에서 표시기에 응용됨은 물론, 텔레비전에도 응용되어 빠르게 음극선관을 대체하고 있다.

[0003] 액정표시장치는 액정표시패널의 데이터라인들에 데이터전압을 공급하기 위한 다수의 소스 드라이브 접적회로(Integrated Circuit 이하, "IC"라 함), 액정표시패널의 게이트라인들에 게이트펄스(또는 스캔펄스)를 순차적으로 공급하기 위한 다수의 게이트 드라이브 IC, 및 드라이브 IC들을 제어하기 위한 타이밍 콘트롤러 등을 구비한다. 이러한 액정표시장치에서 디지털 비디오 데이터는 인터페이스를 통해 타이밍 콘트롤러에 입력된다. 타이밍 콘트롤러는 mini LVDS와 같은 인터페이스를 통해 디지털 비디오 데이터와, 디지털 비디오 데이터의 샘플링을 위한 클럭신호, 소스 드라이브 IC들의 동작을 제어하기 위한 제어신호 등을 소스 드라이브 IC들에 공급한다. 소스 드라이브 IC들은 타이밍 콘트롤러로부터 직렬로 입력되는 디지털 비디오 데이터를 병렬 체계로 변환한 후에 감마보상전압을 이용하여 아날로그 데이터전압을 변환하여 데이터라인들에 공급한다.

[0004] 타이밍 콘트롤러는 클럭과 디지털 비디오 데이터들을 소스 드라이브 IC들에 공통으로 인가하는 멀티 드롭(Multi Drop) 방식으로 소스 드라이브 IC들에 필요한 신호를 공급한다. 소스 드라이브 IC들은 종속적으로 접속되어 순차적으로 데이터들을 샘플링한 후에 1 라인의 데이터 전압들을 동시에 출력한다. 이러한 데이터 전송 방식은 타이밍 콘트롤러와 소스 드라이브 IC들 사이에 R 데이터 전송 배선, G 데이터 전송배선, B 데이터 전송배선, 소스 드라이브 IC들의 출력 및 극성변환 동작의 동작 타이밍 등을 제어하기 위한 제어배선들, 클럭 전송배선들 등 많은 배선이 필요하다. mini-LVDS 인터페이스 방식에서 RGB 데이터 전송의 예를 들면, mini-LVDS 인터페이스 방식은 RGB 디지털 비디오 데이터와 클럭 각각을 서로 역위상인 차신호(differential signal) 쌍으로 전송하므로 기수 데이터와 우수 데이터를 동시에 전송하는 경우에 타이밍 콘트롤러와 소스 드라이브 IC들 사이에는 RGB 데이터 전송을 위하여 최소 14 개의 배선들이 필요하다. 따라서, 타이밍 콘트롤러와 소스 드라이브 IC들 사이에 배치된 인쇄회로보드(Printed Circuit Board, PCB)에는 많은 배선들이 형성되어야 하므로 그 폭을 줄이기가 어렵다.

## 발명의 내용

### 해결 하고자하는 과제

[0005] 따라서, 본 발명의 목적은 상기 종래 기술의 문제점들을 해결하고자 안출된 발명으로써 타이밍 콘트롤러와 소스 드라이브 IC들 사이의 신호 전송 배선들을 최소화하도록 한 액정표시장치와 그 구동방법을 제공하는데 있다.

### 과제 해결수단

[0006] 상기 목적을 달성하기 위하여, 본 발명의 실시예에 따른 액정표시장치는 제1 단계에서 다수의 하이논리의 비트들이 연속된 후에 다수의 로우논리의 비트들이 연속되는 프리앰블신호를 데이터 배선쌍을 통해 전송하고 락 신호를 락 체크 배선을 통해 전송하며, 제2 단계에서 소스 콘트롤 패킷을 상기 데이터 배선쌍을 통해 전송하며, 제3 단계에서 RGB 데이터 패킷을 상기 데이터 배선쌍을 통해 전송하는 타이밍 콘트롤러; 및 상기 프리앰블신호에 따라 출력 클럭들을 락킹시키고 상기 출력 클럭이 락킹되면 상기 락 신호를 상기 타이밍 콘트롤러에 피드백 입력하고, 상기 소스 콘트롤 패킷을 이용하여 소스 콘트롤 데이터를 발생하며, 상기 출력 클럭에 따라 상기 RGB 데이터 패킷의 RGB 데이터를 샘플링하고 상기 소스 콘트롤 데이터에 따라 상기 RGB 데이터를 정극성/부극성 데이터전압으로 변환하여 출력하는 다수의 소스 드라이브 IC들을 구비한다.

## 효과

[0007] 본 발명의 액정표시장치는 소스 드라이브 IC들 내에 데이터를 샘플링하기 위한 클럭 발생회로를 내장시키고 데이터 배선쌍을 통해 소스 콘트롤 패킷과 RGB 데이터 패킷을 소스 드라이브 IC들에 전송함으로써 타이밍 콘트롤

터와 소스 드라이브 IC들 사이에서 데이터 배선 수를 최소화하고 소스 타이밍 제어신호 배선을 제거할 수 있다. 본 발명의 액정표시장치는 소스 드라이브 IC들의 옵션 동작을 제어하기 위한 옵션 정보를 상기 데이터 배선쌍을 통해 전송하여 소스 드라이브 IC들의 옵션핀을 제거하고 옵션핀에 접속되는 저항 및 배선을 제거할 수 있으며, 테스트 모드를 마련하여 소스 드라이브 IC들의 개별 구동 상태와 불령여부를 확인할 수 있다. 나아가, 본 발명의 액정표시장치는 상기 타이밍 콘트롤러와 상기 소스 드라이브 IC들 사이에 제어배선을 연결하고 상기 타이밍 콘트롤러와 상기 제어배선을 통해 칩 식별코드와 제어 데이터를 전송하여 상기 소스 드라이브 IC들을 개별 제어할 수 있어 상기 소스 드라이브 IC들을 독립적으로 디버깅할 수 있다.

[0008]

### 발명의 실시를 위한 구체적인 내용

[0009]

이하, 도 1 내지 도 24를 참조하여 본 발명의 바람직한 실시예에 대하여 설명하기로 한다.

[0010]

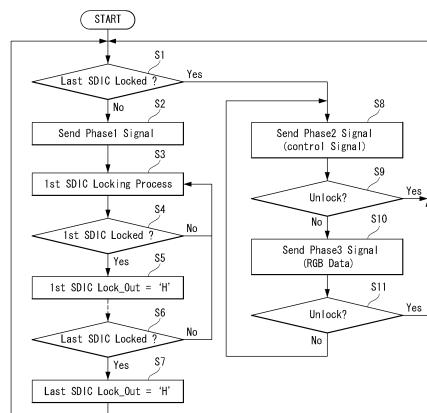

도 1을 참조하면, 본 발명의 실시예에 따른 액정표시장치는 액정표시패널(10), 타이밍 콘트롤러(TCON), 소스 드라이브 IC들(SDIC#1~SDIC#8), 및 게이트 드라이브 IC들(GDIC#1~GDIC#4)을 구비한다.

[0011]

액정표시패널(10)의 유리기판들 사이에는 액정층이 형성된다. 액정표시패널(10)은  $m$  개의 데이터라인들(DL)과  $n$  개의 게이트라인들(GL)의 교차 구조에 의해 매트릭스 형태로 배치된  $m \times n$  개의 액정셀들(Cl<sub>c</sub>)을 포함한다.

[0012]

액정표시패널(10)의 하부 유리기판에는 데이터라인들(DL), 게이트라인들(GL), TFT들, 및 스토리지 커패시터(Cst) 등을 포함한 화소 어레이가 형성된다. 액정셀들(Cl<sub>c</sub>)은 TFT를 통해 데이터전압이 공급되는 화소전극(1)과, 공통전압(Vcom)이 공급되는 공통전극(2) 사이의 전계에 의해 구동된다. TFT의 게이트전극은 게이트라인(GL)에 접속되고, 그 소스전극은 데이터라인(DL)에 접속된다. TFT의 드레인전극은 액정셀의 화소전극(1)에 접속된다. TFT는 게이트라인(GL)을 통해 공급되는 게이트펄스에 따라 턴-온되어 데이터라인(DL)으로부터의 정극성/부극성 아날로그 비디오 데이터전압을 액정셀(Cl<sub>c</sub>)의 화소전극(1)에 공급한다.

[0013]

액정표시패널(10)의 상부 유리기판 상에는 블랙매트릭스, 컬러필터 및 공통전극(2) 등이 형성된다.

[0014]

공통전극(2)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직전계 구동방식에서 상부 유리기판 상에 형성되며, IPS(In Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평전계 구동방식에서 화소전극(1)과 함께 하부 유리기판 상에 형성된다.

[0015]

액정표시패널(10)의 상부 유리기판과 하부 유리기판 각각에는 편광판이 부착되고 액정의 프리틸트각(pre-tilt angle)을 설정하기 위한 배향막이 형성된다. 액정표시패널(10)의 상부 유리기판과 하부 유리기판 사이에는 액정셀(Cl<sub>c</sub>)의 셀갭(cell gap)을 유지하기 위한 스페이서가 형성된다.

[0016]

본 발명에서 적용 가능한 액정표시패널의 액정모드는 TN 모드, VA 모드, IPS 모드, FFS 모드뿐 아니라 어떠한 액정모드로도 구현될 수 있다. 또한, 본 발명의 액정표시장치는 투과형 액정표시장치, 반투과형 액정표시장치, 반사형 액정표시장치 등 어떠한 형태로도 구현될 수 있다.

[0017]

타이밍 콘트롤러(TCON)는 LVDS(Low Voltage Differential Signaling) 인터페이스, TMDS(Transition Minimized Differential Signaling) 인터페이스 등의 인터페이스를 통해 수직/수평 동기신호(Vsync, Hsync), 외부 데이터 인에이블 신호(Data Enable, DE), 도트 클럭(CLK) 등의 외부 타이밍신호를 입력받아 소스 드라이브 IC들(SDIC#1~SDIC#8)과 게이트 드라이브 IC들(GDIC#1~GDIC#4)의 동작 타이밍을 제어하기 위한 타이밍 제어신호들을 발생한다. 타이밍 제어신호들은 게이트 드라이브 IC들(GDIC#1~GDIC#4)의 동작 타이밍을 제어하기 위한 게이트 타이밍 제어신호와, 소스 드라이브 IC들(SDIC#1~SDIC#8)의 동작 타이밍을 제어하기 위한 소스 타이밍 제어신호를 포함한다.

[0018]

타이밍 콘트롤러(TCON)는 후술되는 점 대 점(point to point) 방식으로 소스 드라이브 IC들(SDIC#1~SDIC#8)에 접속된다. 타이밍 콘트롤러(TCON)는 소스 드라이브 IC들(SDIC#1~SDIC#8)을 초기화하기 위한 프리앰블 신호(Preamble signal), 소스타이밍 제어신호, 클럭, RGB 디지털 비디오 데이터 등을 하나의 데이터 배선쌍을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다.

[0019]

게이트 타이밍 제어신호는 게이트 스타트 펄스(Gate Start Pulse, GSP), 게이트 쉬프트 클럭(Gate Shift Clock, GSC), 게이트 출력 인에이블신호(Gate Output Enable, GOE) 등을 포함한다. 게이트 스타트 펄스(GSP)는 제1 게이트 드라이브 IC(GDIC#1)에 인가된다. 게이트 스타트 펄스(GSP)는 제1 게이트 드라이브 IC(GDIC#1)로부터 첫 번째 게이트펄스가 발생되도록 스캔이 시작되는 시작 타임을 지시한다. 게이트 쉬프트 클럭(GSC)은

게이트 스타트 펄스(GSP)를 쉬프트시키기 위한 클럭신호이다. 게이트 드라이브 IC들(GDIC#1~GDIC#4)의 쉬프트 레지스터는 게이트 쉬프트 클럭(GSC)의 라이징 에지에서 게이트 스타트 펄스(GSP)를 쉬프트시킨다. 제2 내지 제4 게이트 드라이브 IC들(GDIC#1~GDIC#4)은 앞단 게이트 드라이브 IC의 캐리신호를 게이트 스타트 펄스로 입력 받아 동작하기 시작한다. 게이트 출력 인에이블신호(GOE)는 게이트 드라이브 IC들(GDIC#1~GDIC#4)의 출력 타이밍을 제어한다. 게이트 드라이브 IC들(GDIC#1~GDIC#4)은 게이트 출력 인에이블신호(GOE)의 로우논리기간 즉, 이전 펄스의 폴링타임 직후로부터 그 다음 펄스의 라이징 타임 직전까지의 기간 동안 게이트펄스를 출력한다. 게이트 출력 인에이블신호(GOE)의 1 주기는 대략 1 수평기간이다.

[0020] 소스 타이밍 제어신호는 프리앰블 신호 전송시간과 RGB 데이터 블록 전송시간 사이의 시간 동안 데이터 배선쌍을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송되며, 극성제어 관련 콘트롤 데이터와, 소스 출력 관련 콘트롤 데이터 등을 포함한다. 극성제어 관련 콘트롤 데이터는 소스 드라이브 IC들(SDIC#1~SDIC#8) 내에서 생성되는 펄스 형태의 극성제어신호(Polarity control signal, POL)를 제어하기 위한 제어정보를 포함한다. 소스 드라이브 IC들(SDIC#1~SDIC#8)의 디지털/아날로그 변환기(Digital to Analog Convertor 이하, "DAC"라 함)는 극성제어신호(POL)에 응답하여 RGB 디지털 비디오 데이터를 정극성 아날로그 비디오 데이터전압 또는 부극성 아날로그 비디오 데이터전압으로 변환한다. 소스 출력 관련 콘트롤 데이터는 소스 드라이브 IC들 내에서 생성되는 펄스 형태의 소스 출력 인에이블신호(Source Output Enable Signal, SOE)를 제어하기 위한 제어정보를 포함한다. 소스 출력 인에이블신호(SOE)는 소스 드라이브 IC들(SDIC#1~SDIC#8)로부터 정극성/부극성 아날로그 비디오 데이터전압이 출력되는 타이밍을 제어한다.

[0021] 게이트 드라이브 IC들(GDIC#1~GDIC#4) 각각은 게이트 타이밍 제어신호들에 응답하여 게이트펄스를 게이트라인들(GL)에 순차적으로 공급한다.

[0022] 소스 드라이브 IC들(SDIC#1~SDIC#8)은 데이터 배선쌍을 통해 타이밍 콘트롤러(TCON)로부터 공급되는 프리앰블 신호에 따라 내장된 클럭 분리 및 데이터 샘플링부의 출력 주파수와 위상을 고정(Locking)한다. 이어서, 소스 드라이브 IC들(SDIC#1~SDIC#8)은 클럭 분리 및 데이터 샘플링부의 출력 주파수와 위상이 고정된 후에, 상기 데이터 배선쌍을 통해 디지털 비트 스트림으로 입력되는 소스 콘트롤 패킷으로부터 클럭을 복원하여 직렬 클럭을 발생하고 소스 출력 관련 콘트롤 데이터와 소스 출력 관련 콘트롤 데이터를 샘플링한다. 그리고 소스 드라이브 IC들(SDIC#1~SDIC#8)은 콘트롤 데이터들을 이용하여 극성제어신호(POL)와 소스 출력 인에이블신호(SOE)를 출력한다.

[0023] 소스 드라이브 IC들(SDIC#1~SDIC#8)은 극성제어신호(POL)와 소스 출력 인에이블신호(SOE)를 복원한 후에, 상기 데이터 배선쌍을 통해 디지털 비트 스트림으로 입력되는 RGB 데이터 패킷으로부터 클럭을 분리하여 데이터 샘플링을 위한 직렬 클럭을 복원하고 그 직렬 클럭에 따라 직렬로 입력되는 RGB 디지털 비디오 데이터를 샘플링한다. 그리고 소스 드라이브 IC들(SDIC#1~SDIC#8)은 순차적으로 샘플링한 RGB 디지털 비디오 데이터들을 병렬 체계로 변환한 후에 극성제어신호(POL)에 응답하여 그 데이터들을 정극성/부극성 아날로그 비디오 데이터 전압으로 변환하고 소스 출력 인에이블신호(SOE)에 응답하여 데이터라인들(DL)에 공급한다.

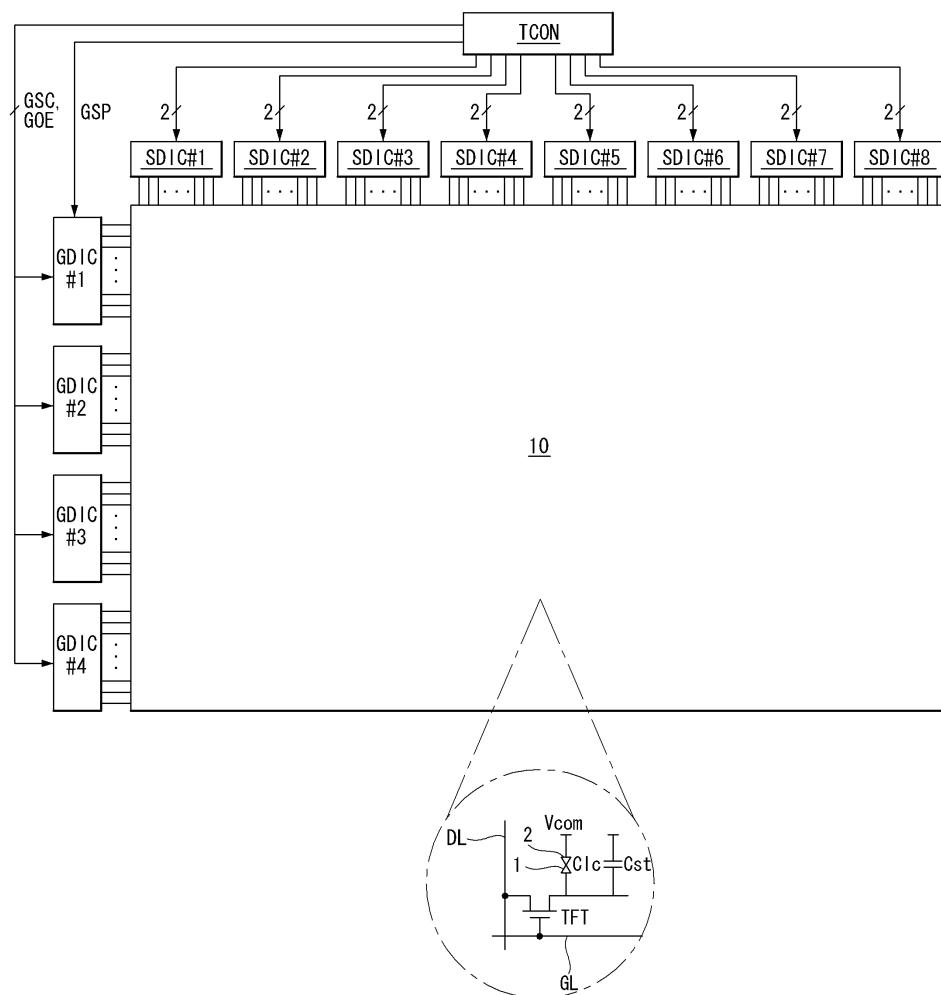

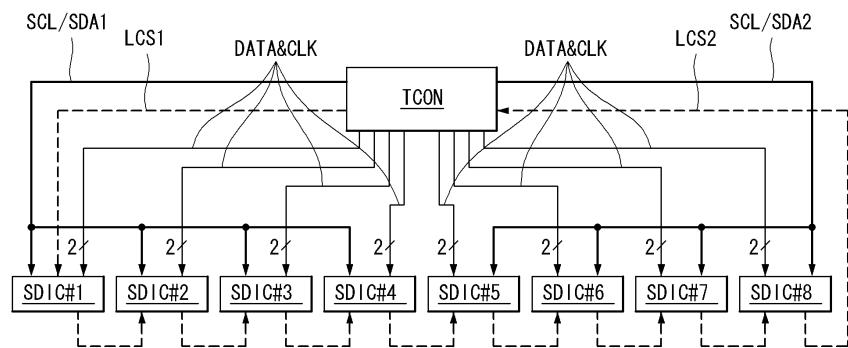

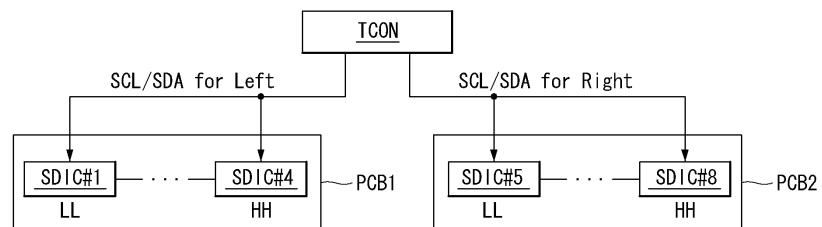

[0024] 도 2는 타이밍 콘트롤러(TCON)와 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이의 배선들을 보여주는 도면들이다.

[0025] 도 2를 참조하면, 타이밍 콘트롤러(TCON)와 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이에는 데이터 배선쌍 (DATA&CLK), 제어 배선쌍(SCL/SDA), 락체크 배선(LCS) 등의 배선들이 형성된다.

[0026] 타이밍 콘트롤러(TCON)는 데이터 배선쌍(DATA&CLK)을 통해 프리앰블신호, 소스 콘트롤 패킷, RGB 데이터 패킷을 순차적으로 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다. 소스 콘트롤 패킷은 클럭 비트, 극성제어 관련 콘트롤 데이터 비트, 소스 출력 관련 콘트롤 데이터 등을 포함한 비트 스트림이다. RGB 데이터 패킷은 클럭 비트, 내부 데이터 인에이블 비트, RGB 데이터 비트 등을 포함한 비트 스트림이다. 데이터 배선쌍(DATA&CLK)은 1:1 즉, 점 대 점(Point to Point) 방식으로 타이밍 콘트롤러(TCON)를 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각에 직렬 연결한다. 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각은 데이터 배선쌍(DATA&CLK)을 통해 입력되는 클럭들을 복원한다. 따라서, 이웃한 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이에는 클럭 캐리와 RGB 데이터를 전달하는 배선이 필요없다.

[0027] 타이밍 콘트롤러(TCON)는 소스 드라이브 IC들(SDIC#1~SDIC#8)의 칩 식별코드(CID)와 소스 드라이브 IC들(SDIC#1~SDIC#8)의 각 기능을 제어하기 위한 칩 개별 제어 데이터들을 제어 배선쌍(SCL/SDA)을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다. 제어 배선쌍(SCL/SDA)은 타이밍 콘트롤러(TCON)와 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이에 공통으로 접속된다. 칩 개별 제어 데이터에 대한 상세한 설명은 후술된다. 소스 드

이브 IC들(SDIC#1~SDIC#8)이 2 개의 그룹으로 분리되어 도 8과 같이 두 개의 소스 PCB(PCB1, PCB2)에 접속된다면, 제1 제어 배선쌍(SCL/SDA1)은 타이밍 콘트롤러(TCON)와 제1 내지 제4 소스 드라이브 IC들(SDIC#1~SDIC#4) 사이에 병렬 접속되고, 제2 제어 배선쌍(SCL/SDA2)은 타이밍 콘트롤러(TCON)와 제5 내지 제8 소스 드라이브 IC들(SDIC#5~SDIC#8) 사이에 병렬 접속된다.

[0028] 타이밍 콘트롤러(TCON)는 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부 출력이 안정하게 고정된지 여부를 확인하기 위한 락 신호(LOCK)를 락체크 배선(LCS1)을 통해 제1 소스 드라이브 IC(SDIC#1)에 공급한다. 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이에는 락 신호를 전달하기 위한 배선을 통해 캐스케이드(cascade)로 접속된다. 제1 소스 드라이브 IC(SDIC#1)는 데이터 샘플리를 위한 클럭 출력의 주파수 및 위상이 고정되면 하이 논리의 락신호(Lock)를 제2 소스 드라이브 IC(SDIC#2)에 전달되고, 제2 소스 드라이브 IC(SDIC#2)는 출력 클럭의 주파수 및 위상을 고정한 후에 하이 논리의 락신호(Lock)를 제2 소스 드라이브 IC(SDIC#2)에 전달한다. 이와 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 출력 주파수와 위상이 고정된 후에 마지막 소스 드라이브 IC(SDIC#8)의 클럭 출력 주파수와 위상이 고정되면 마지막 소스 드라이브 IC(SDIC#8)는 하이논리의 락 신호(Lock)를 피드백 락체크 배선(LCS2)을 통해 타이밍 콘트롤러(TCON)에 피드백 입력한다. 타이밍 콘트롤러(TCON)는 락 신호(Lock)의 피드백 입력을 수신 한 후에 소스 콘트롤 패킷과 RGB 데이터 패킷을 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다.

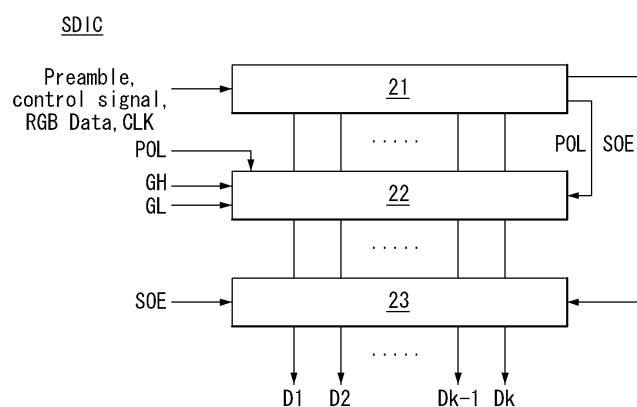

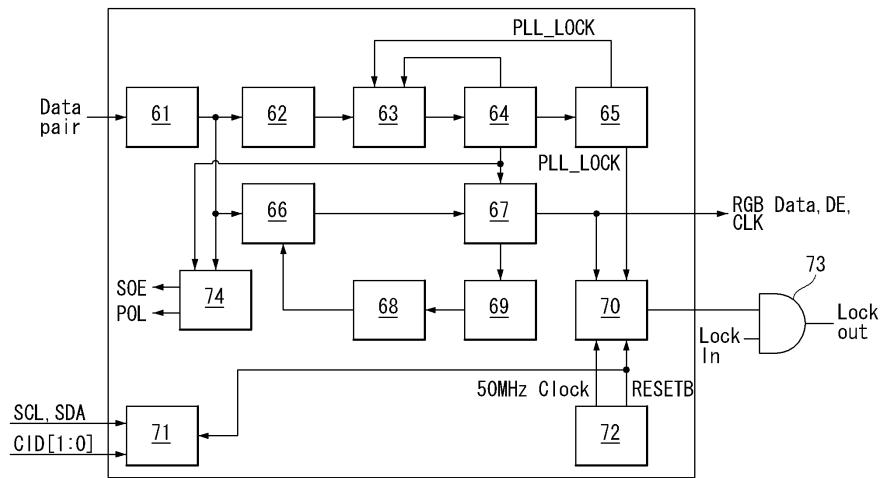

[0029] 도 3은 소스 드라이브 IC들(SDIC#1~SDIC#8)의 내부 구성을 보여 주는 블록도이다.

[0030] 도 3을 참조하면, 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각은  $k$ ( $k$ 는  $m$ 보다 작은 양의 정수) 개의 데이터라인들(D1~Dk)에 정극성/부극성 아날로그 비디오 데이터 전압들을 공급한다. 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각은 클럭 분리 및 데이터 샘플링부(21), DAC(22), 및 출력회로(23) 등을 구비한다.

[0031] 클럭 분리 및 데이터 샘플링부(21)는 제1 단계(Phase1)에서 데이터 배선쌍(DATA&CLK)을 통해 낮은 주파수의 비트 스트림으로 입력되는 프리앰블신호에 따라 출력의 위상과 주파수를 고정한다. 이어서, 클럭 분리 및 데이터 샘플링부(21)는 제2 단계(Phase2)에서 데이터 배선쌍(DATA&CLK)을 통해 비트 스트림으로 입력되는 소스 콘트롤 패킷으로부터 극성제어 관련 콘트롤 데이터를 분리하여 그 극성제어 관련 콘트롤 데이터에 기초하여 극성제어신호(POL)를 복원하고, 소스 콘트롤 패킷으로부터 소스 출력 관련 콘트롤 데이터를 분리하여 그 소스 출력 관련 데이터에 기초하여 소스 출력 인에이블신호(SOE)를 복원한다.

[0032] 클럭 분리 및 데이터 샘플링부(21)는 제3 단계(Phase3)에서 데이터 배선쌍(DATA&CLK)을 통해 입력되는 RGB 데이터 패킷으로부터 클럭을 분리하여 기준 클럭을 복원하고 그 기준 클럭에 따라 RGB 디지털 비디오 데이터의 비트 각각을 샘플링하기 위한 직렬 클럭신호들을 발생한다. 이를 위하여, 클럭 분리 및 데이터 샘플링부(21)는 안정된 위상과 주파수로 클럭을 출력할 수 있는 위상 고정 루프(Phase locked loop 이하, "PLL"이라 함), 지연 락 루프(Delay Locked loop, DLL) 등을 포함한다. 도 7 및 도 9는 PLL을 이용하여 클럭 분리 및 데이터 샘플링부(21)를 구현한 예를 보여 준다. 클럭 분리 및 데이터 샘플링부(21)는 PLL로 한정되는 것이 아니라 전술한 DLL로도 구현될 수 있다.

[0033] 또한, 클럭 분리 및 데이터 샘플링부(21)는 직렬 클럭에 따라 데이터 배선쌍(DATA&CLK)을 통해 직렬로 입력되는 RGB 데이터의 비트들 각각을 샘플링하여 래치한 다음 래치한 데이터들을 동시에 출력하여 직렬 전송 데이터 체계를 병렬 전송 데이터 체계로 변환한다.

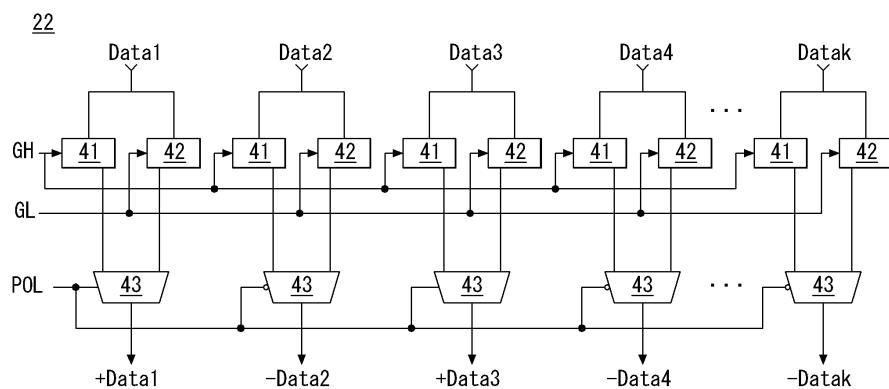

[0034] DAC(22)는 극성제어신호(POL)에 응답하여 클럭 분리 및 데이터 샘플링부(21)로부터의 RGB 디지털 비디오 데이터들을 정극성 감마보상전압(GH) 또는 부극성 감마보상전압(GL)으로 변환하여 정극성/부극성 아날로그 비디오 데이터전압으로 변환한다. 이를 위하여, DAC(22)는 도 4와 같이 정극성 감마기준전압(GH)이 공급되는 P-디코더(PDEC)(41), 부극성 감마기준전압(GL)이 공급되는 N-디코더(NDEC)(42), 극성제어신호(POL)에 응답하여 P-디코더(41)의 출력과 N-디코더(42)의 출력을 선택하는 멀티플렉서(43)를 포함한다. P-디코더(41)는 클럭 분리 및 데이터 샘플링부(21)로부터 입력되는 RGB 디지털 비디오 데이터를 디코드하여 그 데이터의 계조값에 해당하는 정극성 감마보상전압(GH)을 출력하고, N-디코더(32)는 클럭 분리 및 데이터 샘플링부(21)로부터 입력되는 RGB 디지털 비디오 데이터를 디코드하여 그 데이터의 계조값에 해당하는 부극성 감마보상전압(GL)을 출력한다. 멀티플렉서(43)는 극성제어신호(POL)에 응답하여 정극성 감마보상전압(GH)과 부극성 감마보상전압(GL)을 교대로 선택하고 선택된 정극성/부극성 감마보상전압을 정극성/부극성 아날로그 비디오 데이터전압으로써 출력한다.

[0035] 출력회로(23)는 소스 출력 인에이블신호(SOE)의 하이논리기간 동안 차지쉐어전압(Charge share voltage)이나 공통전압(Vcom)을 출력버퍼를 통해 데이터라인들(D1~Dk)에 공급한다. 또한, 출력회로(23)는 소스 출력 인에이블

신호(SOE)의 로우논리기간 동안 정극성/부극성 아날로그 비디오 데이전압을 출력버퍼를 통해 데이터라인들(D1~Dk)에 공급한다. 차지웨어전압은 정극성 전압이 공급되는 데이터라인과 부극성 전압이 공급되는 데이터라인이 단락될 때 발생되며, 그 정극성 전압과 부극성 전압의 평균 전압 레벨을 갖는다.

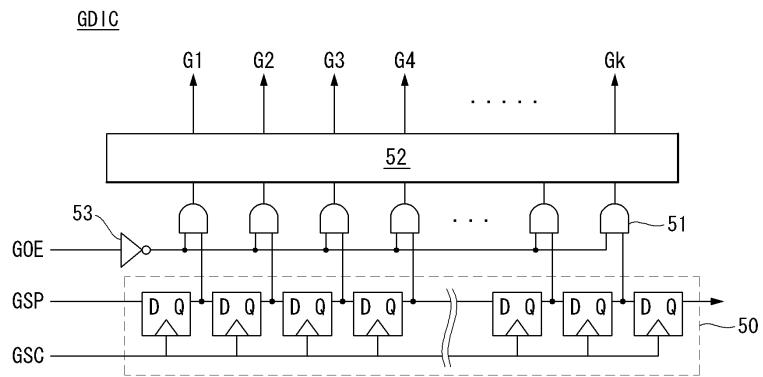

[0036] 도 5는 게이트 드라이브 IC들(GDIC#1~GDIC#4)의 내부 구성을 보여 주는 블록도이다.

[0037] 도 5를 참조하면, 게이트 드라이브 IC들(GDIC#1~GDIC#4) 각각은 쉬프트 레지스터(50), 레벨 쉬프터(52), 쉬프트 레지스터(50)와 레벨 쉬프터(52) 사이에 접속된 다수의 논리곱 게이트(이하, "AND 게이트"라 함)(51), 및 게이트 출력 인에이블신호(GOE)를 반전시키기 위한 인버터(53)를 구비한다.

[0038] 쉬프트 레지스터(50)는 종속적으로 접속된 다수의 D-플립플롭을 이용하여 게이트 스타트 펄스(GSP)를 게이트 쉬프트 클럭(GSC)에 따라 순차적으로 쉬프트시킨다. AND 게이트들(51) 각각은 쉬프트 레지스터(50)의 출력신호와 게이트 출력 인에이블신호(GOE)의 반전신호를 논리곱하여 출력을 발생한다. 인버터(53)는 게이트 출력 인에이블신호(GOE)를 반전시켜 AND 게이트들(51)에 공급한다. 따라서, 게이트 드라이브 IC들(GDIC#1~GDIC#4)은 게이트 출력 인에이블신호(GOE)가 로우논리구간일 때에 게이트펄스를 출력한다.

[0039] 레벨 쉬프터(52)는 AND 게이트(51)의 출력전압 스윙폭을 액정표시패널(10)의 화소 어레이에 형성된 TFT들의 동작이 가능한 스윙폭으로 쉬프트시킨다. 레벨 쉬프터(52)의 출력신호는 게이트라인들(G1 내지 Gk)에 순차적으로 공급된다.

[0040] 쉬프트 레지스터(50)는 화소 어레이의 TFT와 함께 액정표시패널(10)의 유리기판에 직접 형성될 수 있다. 이 경우에, 레벨 쉬프터(52)는 유리기판에 형성되지 않고 타이밍 콘트롤러(TCON), 감마전압 발생회로 등과 함께 콘트롤 보드 또는 소스 PCB 상에 형성될 수 있다.

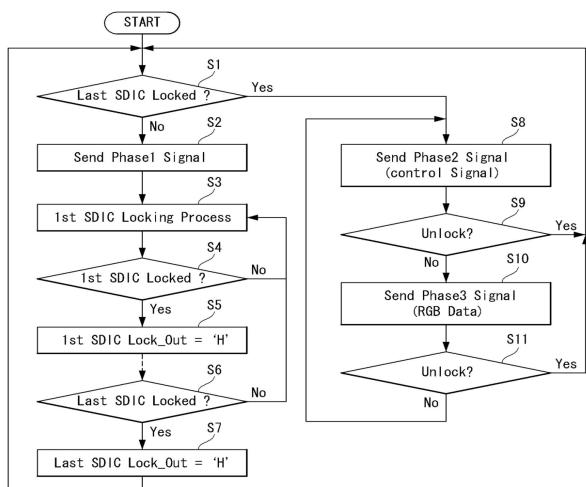

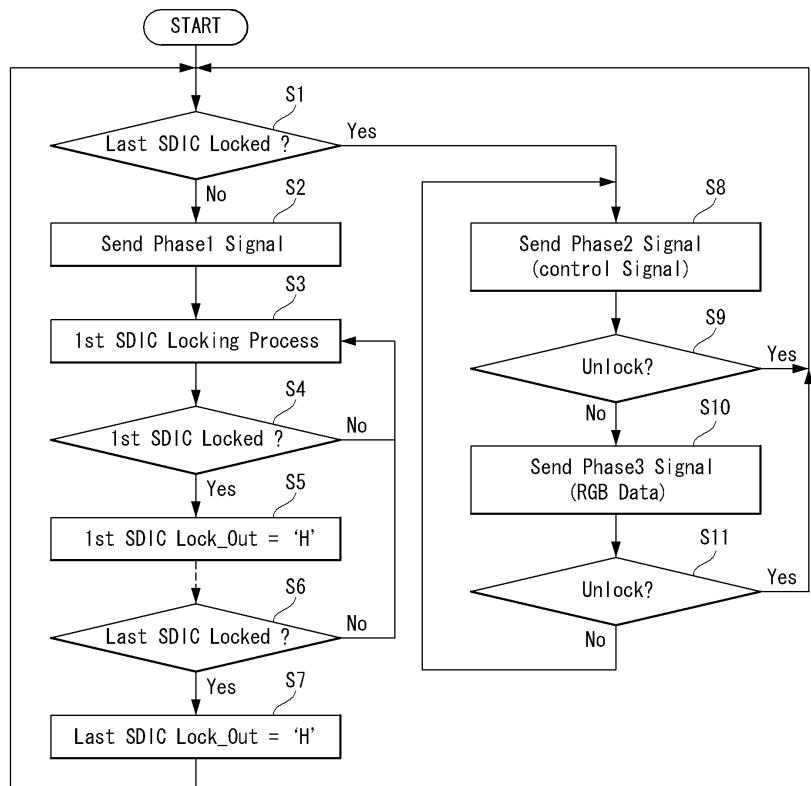

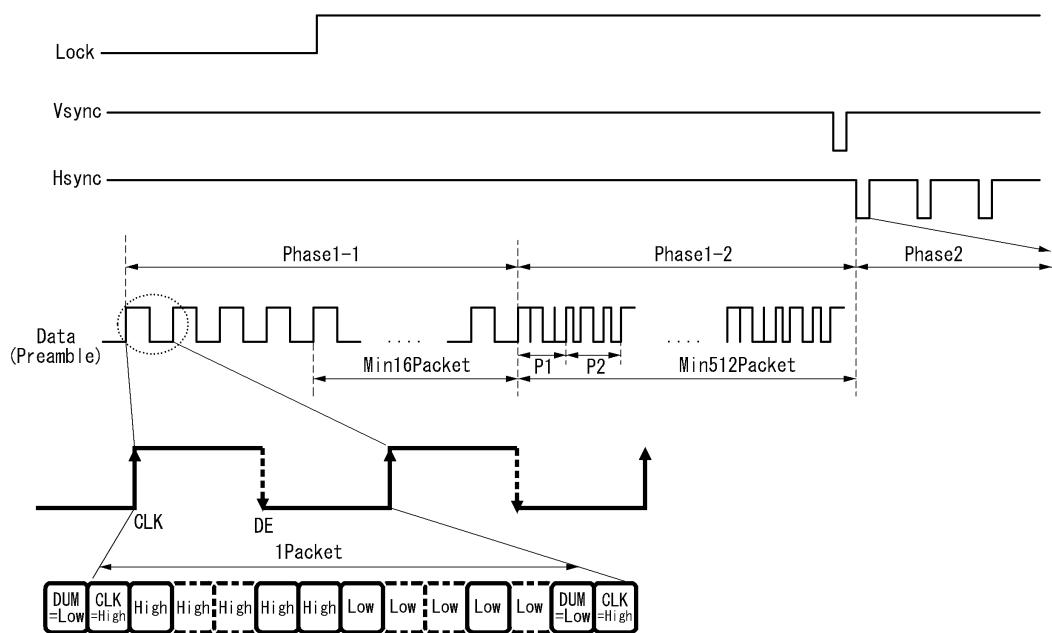

[0041] 도 6은 타이밍 콘트롤러(TCON)와 소스 드라이브 IC들(SDIC#1~SDIC#8) 사이의 신호 전송 과정을 보여주는 흐름도 들이다.

[0042] 도 6을 참조하면, 액정표시장치에 전원이 인가되면 타이밍 콘트롤러(TCON)는 데이터 배선쌍(DATA&CLK)을 통해 제1 단계(Phase 1)의 신호들을 소스 드라이브 IC들(SDIC#1~SDIC#8)에 공급한다. 제1 단계(Phase 1)의 신호는 낮은 주파수의 프리앰블신호와, 제1 소스 드라이브 IC(SDIC#1)에 공급되는 락신호(Lock)를 포함한다.

[0043] 제1 소스 드라이브 IC들(SDIC#1)의 클럭 분리 및 데이터 샘플링부(21)는 프리앰블신호를 PLL 기준 클럭으로 복원하고, 그 PLL 기준 클럭출력과 PLL 출력의 위상이 고정되면 하이논리의 락 신호(Lock)를 제2 소스 드라이브 IC들(SDIC#2)에 전달한다. 이어서, 제2 내지 제8 소스 드라이브 IC들(SDIC#2~SDIC#8)의 클럭 분리 및 데이터 샘플링부 출력이 순차적으로 안정되게 고정되면 제8 소스 드라이브 IC(SDIC#8)는 하이논리의 락 신호를 타이밍 콘트롤러(TCON)에 피드백 입력한다.(S3~S7)

[0044] 타이밍 콘트롤러(TCON)는 제8 소스 드라이브 IC(SDIC#1~SDIC#8)로부터 락 신호가 하이논리로 입력되면, 모든 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부 출력이 안정되게 락킹된 것으로 판단하여 데이터 배선쌍(DATA&CLK)을 통해 제2 단계(Phase 2)의 신호를 점 대 점 방식으로 소스 드라이브 IC들(SDIC#1~SDIC#8)에 공급한다.(S8) 제2 단계(phase 2)의 신호는 극성제어 관련 콘트롤 데이터 비트들과 소스 출력 관련 콘트롤 데이터 비트들을 포함한 다수의 소스 콘트롤 패킷을 포함한다.

[0045] 타이밍 콘트롤러(TCON)는 제2 단계(phase 2)의 신호에 이어서, 제3 단계(Phase 3)의 신호를 점 대 점 방식으로 소스 드라이브 IC들(SDIC#1~SDIC#8)에 공급한다.(S10) 제3 단계(phase3)의 신호는 1 수평기간 동안 액정표시패널의 1 라인의 액정셀들에 충전될 다수의 RGB 데이터패킷을 포함한다.

[0046] 제2 단계(phase 2) 또는 제3 단계(phase 3)의 출력 전송 과정 중에 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부(21)의 PLL 출력이 언락(Unlock) 즉, PLL 출력의 위상 및 주파수가 혼들릴 수 있다. 이 경우, 타이밍 콘트롤러(TCON)는 피드백된 락 신호의 논리가 로우 논리로 반전되면 소스 드라이브 IC들(SDIC#1~SDIC#8)의 PLL 출력이 언락된 것으로 판단하여 제1 단계(phase)의 신호를 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 PLL 출력을 락킹시킨 후에 제2 및 제3 단계(phase 2)의 신호 전송을 재개한다.(S9, S11)

[0047] 도 7은 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부(21)를 상세히 보여 주는 블록도이다.

[0048] 도 7을 참조하면, 클럭 분리 및 데이터 샘플링부(21)는 ODT(On die Terminator 이하 "ODT"라 함)부(61), 아날

로그 딜레이 레플리카(Analog Delay Replica 이하, "ADR"이라 함)(62), 클럭 분리부(Clock separator)(63), PLL(64), PLL 락 검출부(PLL Lock Detector)(65), 투너블 아날로그 딜레이(Tunable Analog Delay)(66), 직병렬 변환부(Deserializer)(67), 디지털 필터(Digital Filter)(68), 위상 검출부(Phase Detector)(69), 락 검출부(Lock Detector)(70),  $I^2C$  콘트롤러(71), 전원 리셋부(Power-On Reset 이하, "POR"이라 함)(72), AND 게이트(73), SOE&POL 복원부(74) 등을 구비한다.

[0049] ODT부(61)는 터미네이션 저항을 내장하여 데이터 배선쌍(DATA&CLK)을 통해 입력되는 프리앰블신호, 소스 콘트롤 패킷, RGB 데이터와 클럭을 포함한 비트 스트림에 혼입된 노이즈를 제거하여 신호 무결성(Signal Integrity)을 향상시킨다. 또한, ODT부(61)는 수신 버퍼 및 등화기(RX Buffer & Equation)를 내장하여 입력 차등신호를 증폭하고 디지털 데이터로 변환한다. ADR(62)은 투너블 아날로그 딜레이(66)의 지연값만큼 ODT부(61)로부터의 RGB 데이터 및 클럭을 지연시켜 클럭 패스(Clock Path)와 데이터 패스(Data Path) 간의 지연값을 동일하게 한다.

[0050] 클럭 분리부(63)는 ODT부(51)에 의해 복원된 RGB 데이터 패킷에는 클럭 비트들과 RGB 디지털 데이터들이 포함되어 있는데, 이 중에서 클럭 비트들을 분리하여 PLL(65)의 기준 클럭으로 복원한다. 클럭 비트들은 클럭, 더미 클럭, 내부 데이터 인에이블 비트 등을 포함한다. PLL(64)은 소스 콘트롤 패킷과 RGB 데이터 패킷의 데이터 비트들의 샘플링을 위한 클럭들을 발생한다. RGB 데이터 패킷에 각각 10 bits의 RGB 비트들을 포함하고 그 RGB 비트들을 사이에 두고 4 bits의 클럭 비트들이 할당되면, PLL(64)은 1 RGB 데이터 패킷 당 34개의 클럭들을 출력한다. PLL 락 검출부(65)는 주어진 입력 데이터 레이트(Data Rate)에 맞추어 PLL(64)의 출력 위상 및 주파수를 감시하여 PLL 출력 클럭의 락킹 여부를 검출한다.

[0051] 투너블 아날로그 딜레이(66)는 클럭 센터에서 데이터가 샘플링될 수 있도록 ODT부(61)로부터 입력된 RGB 데이터와 위상 검출부(69) 및 디지털 필터(68)를 거쳐 피드백 입력된 복원 클럭들 사이의 미세한 위상 차이를 보상하는 회로이다. 직병렬 변환부(67)는 플립 플롭들을 내장하여 PLL(64)로부터 출력된 직렬 클럭들에 맞추어 직렬로 입력되는 RGB 디지털 비디오 데이터의 비트들을 샘플링하고 샘플링한 데이터들을 병렬 데이터로 변환한다.

[0052] 디지털 필터(68)와 위상 검출부(69)는 샘플링된 RGB 디지털 비디오 데이터들을 입력받아 투너블 아날로그 딜레이(66)의 지연값을 결정한다. 락 검출부(70)는 직병렬 변환부(67)에 의해 복원된 RGB 병렬 데이터와 PLL 락 검출부(65)의 출력(PLL\_LOCK)을 비교하여 RGB 병렬 데이터의 데이터 인에이블 클럭의 에러양을 체크하여 그 클럭들의 에러양이 일정 수준 이상이면 PLL의 출력을 언락시켜 PHY(physical interface) 회로 전체를 다시 동작시킨다. 락 검출부(70)는 PLL 출력이 언락될 때 로우 논리의 출력을 발생하는 반면, PLL 출력이 락킹될 때 하이논리의 출력을 발생한다. AND 게이트(73)는 타이밍 콘트롤러(TCON)로부터 입력되는 락 신호(Lock In) 또는 앞단 소스 드라이브 IC들(SDIC#1~SDIC#7)로부터 전달된 락 신호(Lock In)와, 락 검출부(70)의 출력을 논리곱 연산하여 그 두 신호가 모두 하이논리일 때 하이논리의 락 신호(Lock Out)를 출력한다. 하이논리의 락 신호는 다음 단의 소스 드라이브 IC들(SDIC#2~SDIC#8)에 전달되고, 마지막 소스 드라이브 IC(SDIC#8)는 락 신호(Lock Out)를 타이밍 콘트롤러(TCON)에 피드백 입력한다.

[0053] POR(72)은 미리 설정된 파워 시퀀스(Power Sequence)에 따라 클럭 분리 및 데이터 샘플링부(21)를 초기화하기 위한 리셋신호(Reset)를 발생하고, 대략 50MHz의 클럭신호를 발생하여 그 클럭신호를 상기한 회로들을 포함한 디지털 회로들에 공급한다.

[0054]  $I^2C$  콘트롤러(71)는 제어 배선쌍(SCL/SDA)을 통해 직렬 데이터로 입력되는 칩 식별코드(CID) 및 칩 개별 제어 데이터들을 이용하여 상기한 각 회로 블록들의 동작을 제어한다. 칩 식별코드(CID)는 소스 드라이브 IC들(SDIC#1~SDIC#8)이 개별 제어될 수 있도록 도 8과 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)에 서로 다른 논리값(HH, LL)으로 부여된다.  $I^2C$  콘트롤러(71)는 타이밍 콘트롤러(TCON)와 제어 배선쌍의 직렬 데이터 버스(SD A)를 통해 입력된 칩 개별 제어 데이터에 따라 PLL 파워 다운(Power Down), ODT부(61)의 버퍼 파워 다운, ODT부(61)의 EQ On/Off 기능, PLL(65)의 차지 범프 전류값 조절, PLL(65)의 VCO 레인지 메뉴얼 셀렉션(Range Manual Selection) 조절,  $I^2C$  통신을 통한 PLL 락 신호 푸쉬, 아날로그 딜레이 제어값 조절, 락 검출부(70)의 디스에이블(DISABLE), 디지털 필터(68)의 계수 변경, 디지털 필터 계수 변경 기능,  $I^2C$ 를 통한 PHY(physical interface)\_RESETB 신호 푸쉬, 앞단 소스 드라이브 IC들(SDIC#1~SDIC#7)의 락 신호를 현재 소스 드라이브 IC들(SDIC#1~SDIC#8)의 리셋 신호로 대체하는 기능, 입력 영상의 수직 해상도(Vertical Resolution)값 설정, PHY RESET 발생의 원인 분석을 위한 데이터 인에이블 클럭 트랜지션(DE transition)에 대한 이력을 저장하는 등의 기능을 제어할 수 있다.

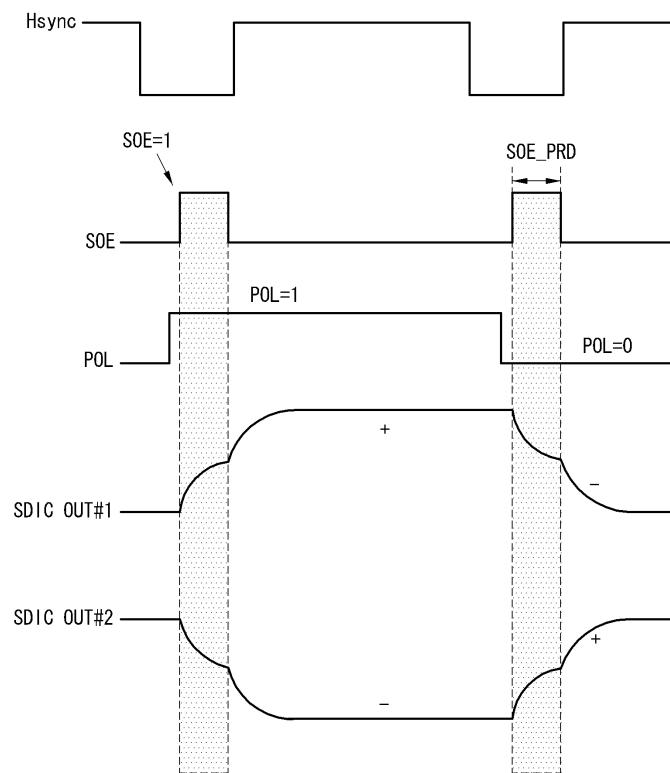

- [0055] SOE&POL 복원부(74)는 ODT부(61)로부터의 소스 콘트롤 패킷의 극성제어 관련 콘트롤 데이터를 PLL 출력 클럭에 따라 샘플링하여 극성 제어신호(POL)를 하이논리(또는 로우논리)로 발생한 후에  $i$ ( $i$ 는 자연수) 수평기간 단위로 논리가 반전시킨다. SOE&POL 복원부(74)는 ODT부(61)로부터의 소스 콘트롤 패킷의 소스 출력 관련 콘트롤 데이터를 PLL 출력 클럭에 따라 샘플링하고 그 소스 출력 관련 콘트롤 데이터 기초하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 출력 타이밍을 결정하는 소스 출력 인에이블신호(SOE)를 발생한다. SOE&POL 복원부(74)는 소스 출력 관련 콘트롤 데이터에서 펄스폭 정보를 검출하여 PLL에서 복원된 기준 클럭(SCLK)을 카운트하여 소스 출력 인에이블신호(SOE)의 펄스폭을 결정한다.

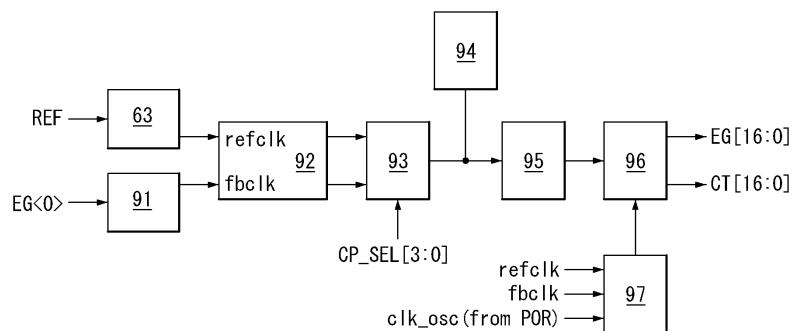

- [0056] 도 9는 PLL(64)을 상세히 보여 주는 블록도이다.

- [0057] 도 9를 참조하면, PLL(64)은 위상 비교부(92), 차지펌프(Charge Pump)(93), 루프필터(94), 펄스-전압 변환기(95), VCO(Voltage Controlled Oscillator)(96), 및 디지털 콘트롤러(97)를 구비한다.

- [0058] 위상 비교부(92)는 클럭 분리부(63)로부터 입력된 기준 클럭(refclk)과 클럭 분리부 레플리카(Clock Separator Replica) 이하, "CSR"이라 함(63)로부터의 피드백 에지클럭(fbclk)의 위상을 비교한다. 그 비교 결과, 위상 비교부(92)는 기준 클럭(refclk)과 피드백 에지클럭(EG[0])의 차이만큼의 펄스폭을 가지며, 기준 클럭이 피드백 에지 클럭에 비하여 빠르면 정극성 펄스를 출력하는 반면, 피드백 에지 클럭이 기준 클럭보다 빠르면 부극성 펄스를 출력한다.

- [0059] 차지펌프(93)는 위상 비교부(92)의 출력 펄스폭과 극성에 따라 루프 필터(94)에 공급되는 전하량을 다르게 공급한다. 루프필터(94)는 차지펌프(93)의 전하양에 따라 그 전하를 축적하거나 방전시키며 펄스-전압 변환기(95)에 입력되는 클럭에서 하모닉(harmonic) 성분을 포함한 고주파 노이즈를 제거한다.

- [0060] 펄스-전압 변환기(95)는 루프필터(94)로부터 입력되는 펄스를 VCO(96)의 제어전압(Control voltage)으로 변환하며, 루프필터(94)로부터 입력되는 펄스의 펄스폭과 부호에 따라 VCO(96)의 제어전압(Control voltage)의 전압레벨을 조정한다. VCO(96)는 1 RGB 데이터 패킷의 비트 스트림에 각각 10 bits의 RGB 비트들과 4 개의 클럭 비트들이 포함될 때 그 1 소스 콘트롤 패킷/RGB 데이터 패킷당 34 개의 에지 클럭과 34 개의 센터 클럭을 발생하며, 펄스-전압 변환기(95)로부터의 제어전압과 디지털 콘트롤러(97)로부터의 제어 데이터에 따라 클럭들의 위상 자연양을 조절한다.

- [0061] VCO(96)로부터 출력된 첫 번째 에지클럭(EG[0])은 피드백 에지클럭으로써 클럭 분리부 레플리카(91)에 입력된다. 피드백 에지클럭(EG[0])은 VCO(96)의 출력 주파수의 1/34 만큼 분주된 주파수로 발생된다. 디지털 콘트롤러(97)는 펄스 분리부(63)로부터의 기준 클럭(refclk), 피드백 에지클럭(fbclk)을 입력 받아 그 클럭들의 위상차를 비교하고 또한, 그 위상차와 POR(72)로부터의 50MHz 클럭신호(clk\_osc)의 위상차를 비교한다. 디지털 콘트롤러(97)는 클럭들의 위상차 비교 결과에 따라 VCO(96)의 출력 자연양을 조절하여 VCO(96)의 발진 영역을 선택한다.

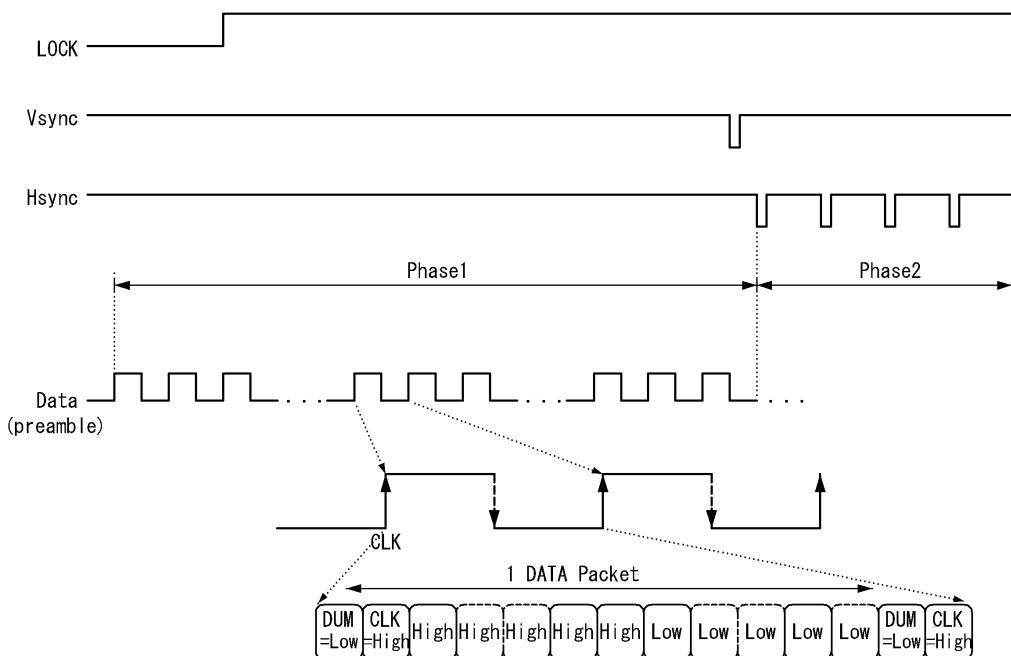

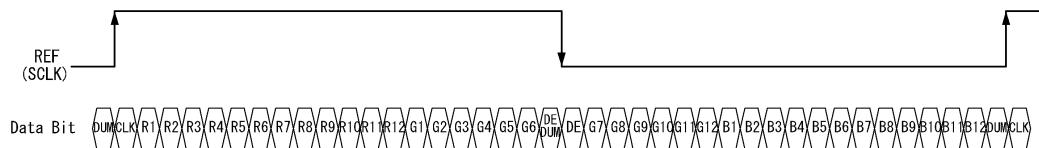

- [0062] 도 10은 제1 단계(Phase1)에서 타이밍 콘트롤러(TCON)로부터 발생되는 신호들을 보여 주는 파형도이다.

- [0063] 도 10을 참조하면, 타이밍 콘트롤러(TCON)는 제1 단계(Phase1)에서 락 신호(Lock)와 낮은 주파수의 프리앰블 신호(preamble)를 발생한다. 프리앰블 신호(preamble)는 다수의 하이논리의 비트들이 연속된 후에 다수의 로우논리의 비트들이 연속되는 신호로써 주파수가 낮다. 프리앰블 신호(preamble)의 주파수는 1 RGB 데이터 패킷의 비트 스트림에 각각 10 bits의 RGB 비트들과 4 개의 클럭 비트들이 포함될 때 클럭 분리 및 데이터 샘플링부(21)의 PLL 출력 클럭 주파수의 1/34 만큼 분주된 주파수이다. 클럭 분리 및 데이터 샘플링부(21)의 클럭 분리부(63)는 프리앰블 신호(preamble)의 하이논리 비트에 동기하여 기준 클럭(refclk)을 하이논리로 트랜지션시키고 프리앰블 신호(preamble) 로우논리의 비트에 기준 클럭(refclk)을 로우논리로 트랜지션시킨다.

- [0064] 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각의 클럭 분리 및 데이터 샘플링부(21)는 프리앰블 신호(preamble)에 따라 발생되는 기준 클럭(refclk)과 피드백 에지 클럭의 위상을 비교하면서 출력을 락킹하는 동작을 반복하고 출력이 안정되게 락킹되면 락 신호(Lock)를 다음 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전달한다.

- [0065] 액정표시장치의 최초 파워 온(Power On) 단계에서, 타이밍 콘트롤러(TCON)는 마지막 소스 드라이브 IC(DIS#8)로부터 입력된 락 신호를 입력받아 클럭 분리 및 데이터 샘플링부(21)의 출력 락킹을 확인한 후에 수직 동기신호(Vsync)의 블랭킹기간(Blanking) 내에서 제2 단계(phase2)의 신호들을 출력한다. 액정표시장치에서 비디오 데이터가 표시되는 동안에 클럭 분리 및 데이터 샘플링부(21)의 출력이 언락되면, 타이밍 콘트롤러(TCON)는 마지막 소스 드라이브 IC(DIS#8)로부터 입력된 락 신호를 입력받아 클럭 분리 및 데이터 샘플링부(21)의 출력이 락

킹된 것을 확인한 후에 수직 동기신호(Vsync)와 수평 동기신호(Hsync) 중에서 첫 번째 블랭킹 기간에 제2 단계(phase 2)의 신호를 출력한다.

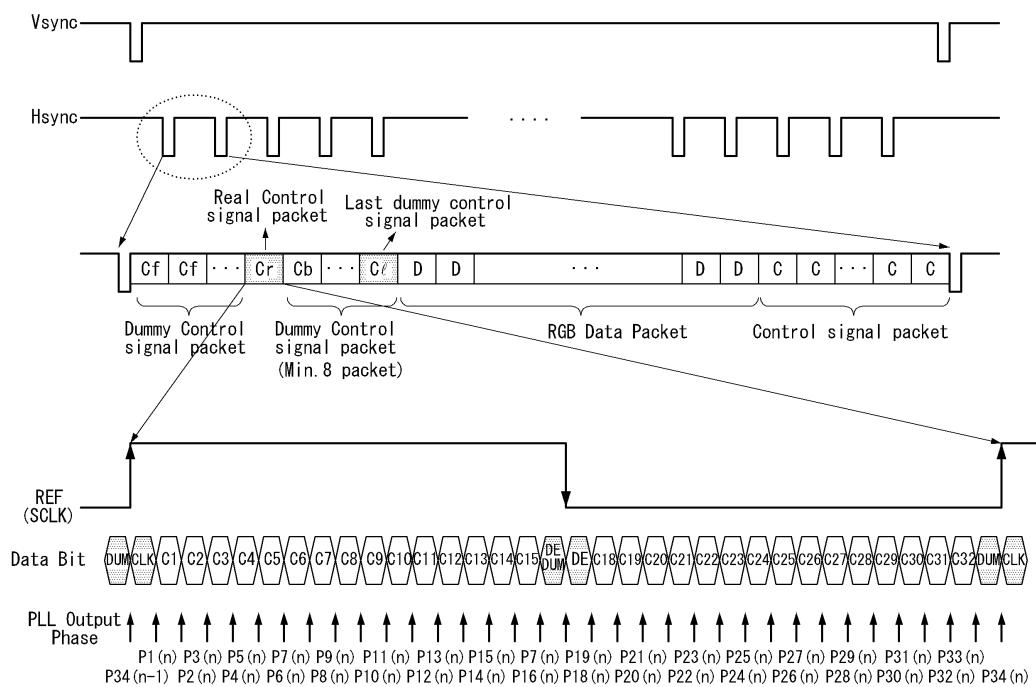

[0066] 도 11은 제2 단계(Phase 2)에서 타이밍 콘트롤러(TCON)로부터 발생되는 신호들을 보여 주는 과정도이다.

[0067] 도 11을 참조하면, 타이밍 콘트롤러(TCON)는 제2 단계(Phase 2)에서 수평 동기신호(Hsync)의 1 주기(1 수평기간) 내에서 데이터가 없는 블랭킹기간 동안 다수의 프론트 더미 소스 콘트롤 패킷들(Cf), 하나 이상의 리얼 소스 콘트롤 패킷(Cr), 다수의 백 더미 소스 콘트롤 패킷들(Cb, C1) 순으로 그 소스 콘트롤 패킷들(Cf, Cr, Cb, C1)을 데이터 배선쌍(DATA&CLK)을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다.

[0068] 다수의 프론트 더미 소스 콘트롤 패킷들(Cf)은 클럭 분리 및 데이터 샘플링부(21)의 안정적인 리얼 소스 콘트롤 패킷 수신 동작을 위하여, 리얼 소스 콘트롤 패킷(Cr)에 앞서 소스 드라이브 IC들(SDIC#1~SDIC#8)에 연속으로 전송된다. 리얼 콘트롤 패킷(Cr)은 소스 드라이브 IC들(SDIC#1~SDIC#8)의 구성 반전 동작과 데이터 출력을 제어하기 위한 구성제어 관련 콘트롤 데이터 비트들과 소스 출력 관련 콘트롤 데이터 비트들을 포함한다. 다수의 백 더미 소스 콘트롤 패킷들(Cb, C1)은 클럭 분리 및 데이터 샘플링부(21)의 리얼 소스 콘트롤 패킷 수신 검증 과정을 확보하고 제3 단계 신호의 안정적인 수신 동작을 위하여, 리얼 소스 콘트롤 패킷(Cr) 뒤에 소스 드라이브 IC들(SDIC#1~SDIC#8)에 연속으로 전송된다. 백 더미 소스 콘트롤 패킷들(Cb) 중 마지막 소스 콘트롤 패킷(C1)은 그 뒤에 제3 단계(phase 3)의 신호들이 전송된다는 것을 지시하는 비트값이 할당된다.

[0069] 프론트 더미 소스 콘트롤 패킷들(Cf), 리얼 소스 콘트롤 패킷(Cr), 백 더미 소스 콘트롤 패킷들(Cb, C1)들은 도 15와 같은 테이블과 같이 특정 비트들의 값들로 구분될 수 있다. 따라서, 클럭 분리 및 데이터 샘플링부(21)의 SOE&POL 복원부(74)는 소스 콘트롤 패킷들(Cf, Cr, Cb, C1)을 특정 위치의 비트값으로 구분하여 리얼 소스 콘트롤 패킷(Cr)의 구성제어 관련 콘트롤 데이터와 소스 출력 관련 콘트롤 데이터를 식별할 수 있다.

[0070] 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부(21)는 소스 콘트롤 패킷으로부터 클럭들을 분리하여 기준 클럭을 복원하고 그 기준 클럭과 높은 주파수의 출력 클럭들의 위상을 비교하면서 구성제어 관련 콘트롤 데이터와 소스 출력 관련 콘트롤 데이터의 비트 각각을 샘플링하기 위한 직렬 클럭들을 출력한다. 그리고 클럭 분리 및 데이터 샘플링부(21)는 샘플링한 구성제어 관련 콘트롤 데이터에 따라 구성제어신호(POL)를 발생하고 소스 출력 관련 콘트롤 데이터에 따라 소스 출력 인에이블신호(SOE)를 발생한다.

[0071] 도 11과 같이 1 수평기간 내에 다수의 소스 콘트롤 패킷들(Cf, Cr, Cb, C1)에 이어서 RGB 데이터 패킷이 전송된다 다음, 그 RGB 데이터 패킷에 이어서 다수의 소스 콘트롤 패킷들이 더 전송될 수 있다. RGB 데이터 패킷에 이어서 전송되는 소스 콘트롤 패킷들은 하나 이상의 리얼 소스 콘트롤 패킷과 다수의 더미 소스 콘트롤 패킷들을 포함할 수 있는데, 리얼 소스 콘트롤 패킷은 다음 수평기간의 RGB 데이터 패킷에 영향을 미친다.

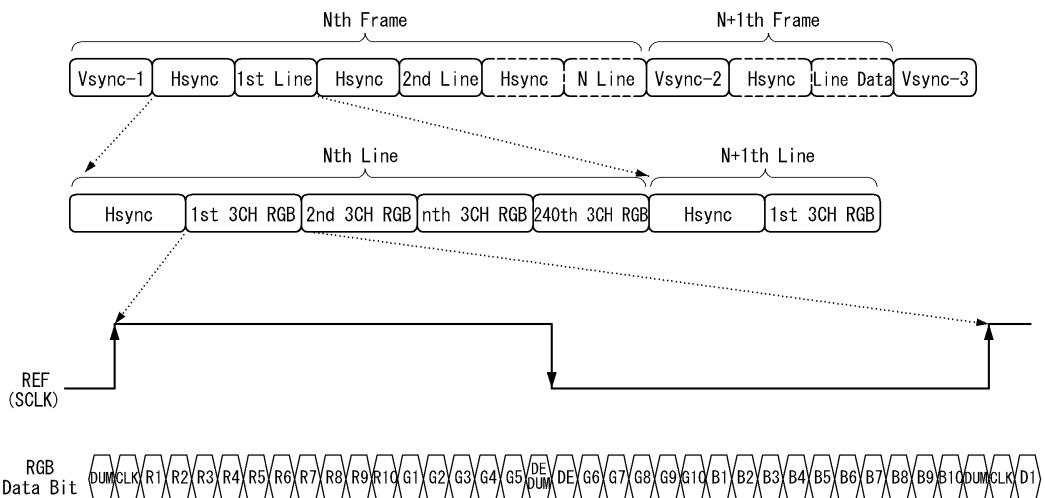

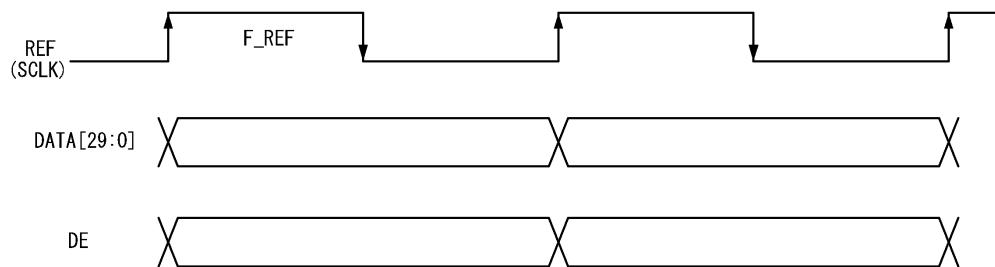

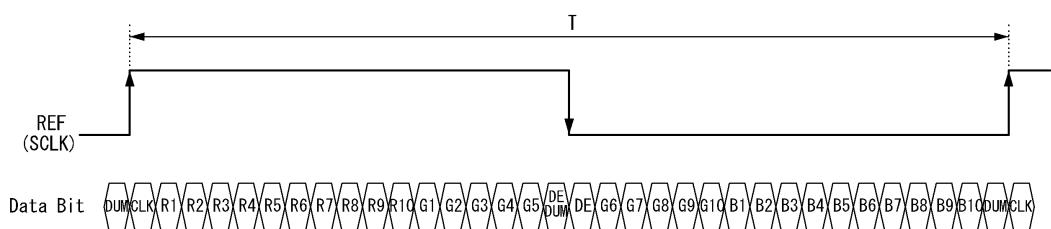

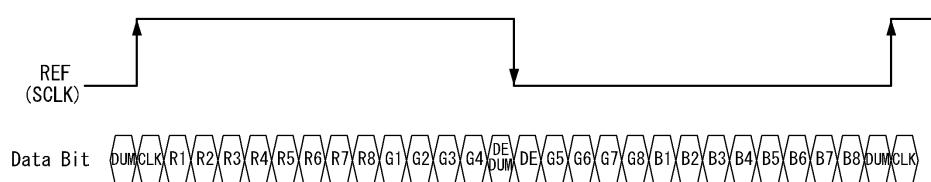

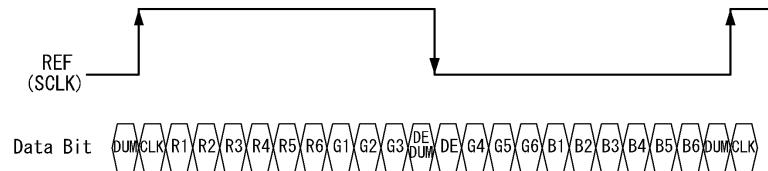

[0072] 도 12 및 도 13은 제3 단계(Phase 3)에서 타이밍 콘트롤러(TCON)로부터 발생되는 신호들을 보여 주는 과정도이다.

[0073] 도 12 및 도 13을 참조하면, 타이밍 콘트롤러(TCON)는 제2 단계(phase 2)의 신호에 이어서 1 수평기간 내에서 제3 단계(Phase 3)의 신호 즉, 액정표시장치의 1 라인에 표시될 다수의 RGB 데이터 패킷들을 데이터 배선쌍(DATA&CLK)을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다.

[0074] 클럭 분리 및 데이터 샘플링부(21)는 RGB 데이터 패킷에서 클럭(CLK)과 데이터 인에이블 클럭(CLK)을 분리하여 기준 클럭을 복원하고 그 기준 클럭과 높은 주파수의 출력 클럭들의 위상을 비교하면서 RGB 디지털 비디오 데이터의 비트 각각을 샘플링하기 위한 직렬 클럭들을 출력한다. 1 RGB 데이터 패킷의 비트 스트림에 각각 10 bits의 RGB 비트들과 4 개의 클럭 비트들이 포함되는 경우에, 그 RGB 데이터 패킷의 헤드 영역에 로우 논리의 더미 클럭 비트(DUM), 하이논리의 클럭 비트(CLK)가 할당되며, 그 헤드 영역 뒤에 RGB 데이터의 전반부에 해당하는 R1~R10 및 G1~G5 비트들이 할당되고 그 뒤에 논리가 서로 반전된 내부 데이터 인에이블 로우논리의 더미 클럭 비트(DE DUM)과 하이논리의 내부 데이터 인에이블 클럭 비트(DE)가 할당된다. 그리고 내부 데이터 인에이블 클럭 비트(DE) 뒤에는 RGB 데이터의 후반부에 해당하는 G6~G10 및 B1~G10 비트들이 할당된다. 클럭 분리 및 데이터 샘플링부(21)는 클럭(CLK)과 내부 데이터 인에이블 클럭(DE)을 검출하여 그 뒤에 직렬로 입력되는 데이터들을 RGB 디지털 비디오 데이터로 판단할 수 있고, 그 데이터들을 샘플링 클럭에 따라 샘플링한다.

[0075] RGB 데이터를 포함하지 않은 상태를 지시하기 위하여, 제1 및 제2 단계(phase 1, phase 2)의 신호에서 더미 데이터 인에이블 클럭과 데이터 인에이블 클럭 위치의 비트값들은 제3 단계(phase 3)의 신호에 할당된 더미 데이터 인에이블 클럭(DE DUM)과 데이터 인에이블 클럭(DE)와 다른 값으로 설정된다.

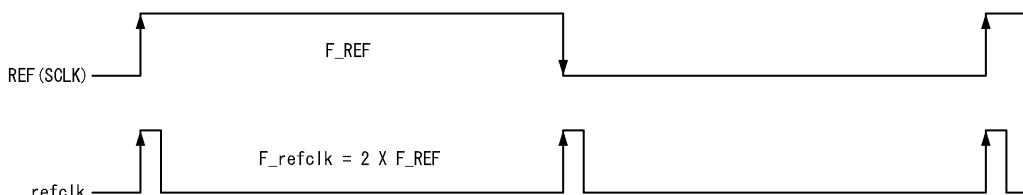

- [0076] 클럭 분리 및 데이터 샘플링부(21)의 클럭 분리부(63)는 클럭(CLK)과 내부 데이터 인에이블 클럭(DE)에 라이징 에지가 동기되는 기준 클럭(refclk)을 발생한다. 이 기준 클럭(refclk)은 내부 데이터 인에이블 클럭(DE)에서 한 번 더 트랜지션되므로 제1 및 제2 단계(phase 1, phase 2)에서 복원되는 기준 클럭(REF)에 비하여 주파수가 2 배 높아진다. 이렇게 클럭 분리 및 데이터 샘플링부(21)의 기준 클럭 주파수가 높아지면 PLL(64)의 VCO 내의 스테이지(stage) 수를 줄일 수 있으므로 PLL(64) 출력이 더 안정화될 수 있다. 이를 상세히 하면, 내부 데이터 인에이블 신호(DE)에서 RGB 데이터 패킷의 중간 지점에서 PLL의 기준 클럭(refclk)을 트랜지션시켜 PLL의 기준 클럭 주파수를 2 배로 증가시키면, PLL(64)내의 VCO 스테이지 수를 1/2로 줄일 수 있다. 내부 데이터 인에이블 클럭(DE)에서 기준 클럭(refclk)을 트랜지션 클럭으로 사용하지 않으면 34 개의 VCO 스테이지가 필요한 반면, 내부 데이터 인에이블 클럭(DE)을 트랜지션 클럭으로 사용하면 17 개의 VCO 스테이지만이 필요하다. PLL(64)에서 VCO 스테이지 수가 많아지면 프로세스, 전압, 온도(PVT) 변동에 대한 효과가 스테이지 수 만큼 곱해져서 나타나므로 이러한 외부 변동에 대해 PLL 락이 풀릴 가능성이 커진다. 따라서, 본 발명은 클럭(CLK) 이외에 내부 데이터 인에이블 클럭(DE)을 트랜지션 클럭으로 사용하여 PLL의 기준 클럭(refclk) 주파수를 높여 PLL 락킹 신뢰성을 향상높일 수 있다.

- [0077] RGB 데이터 패킷과 소스 콘트롤 패킷들(Cf, Cr, Cb, Cl)은 소정의 비트들을 다르게 설정함으로써 구분될 수 있다. 도 14는 도 14는 제2 단계(phase 2)에서 발생되는 소스 콘트롤 패킷들(Cf, Cr, Cb, Cl)과 제3 단계(phase 3)에서 발생되는 RGB 데이터 패킷의 데이터 맵핑 테이블이다. RGB 데이터 패킷과 소스 콘트롤 패킷들의 데이터 테이블은 도 14에 한정되는 것이 아니라 도 14의 데이터 테이블을 기본으로 하여 다양하게 변형될 수 있다.

- [0078] 도 14를 참조하면, RGB 각각의 데이터가 10 bits의 데이터라면 RGB 데이터 패킷은 총 34 bits를 포함한다. RGB 데이터 패킷을 상세히 설명하면, RGB 데이터 패킷은 1 bit의 클럭, 10 bits의 R 데이터[0:9], 5 bits의 G 데이터[0:4], 1 bit의 더미 데이터 인에이블(DE DUM), 1 bit의 데이터 인에이블(DE), 5 bits의 G 데이터[5:9], 10 bits의 B 데이터[0:9]를 포함한다. 소스 콘트롤 패킷들(Cf, Cr, Cb)은 RGB 데이터 패킷과 동일한 데이터 길이 즉, 34 bits를 포함한다. 소스 콘트롤 패킷들(Cf, Cr, Cb)을 상세히 설명하면, 1 bit의 클럭, R 데이터[0:9]와 G 데이터[0:4]에 대신하는 15 bits의 전반부 콘트롤 데이터, 1 bit의 더미 데이터 인에이블(DE DUM), 1 bit의 데이터 인에이블(DE), G 데이터[5:9] 및 B 데이터[0:9]를 대신하는 15 bits의 후반부 콘트롤 데이터를 포함한다. RGB 데이터 패킷과 소스 콘트롤 패킷들(Cf, Cr, Cb)은 더미 데이터 인에이블(DE DUM)과 데이터 인에이블(DE)의 비트값을 다르게 하여 구분될 수 있다.

- [0079] 더미 소스 콘트롤 패킷들(Cf, Cb, Cl)과 리얼 소스 콘트롤 패킷(Cr)은 도 14의 전반부 콘트롤 데이터와 후반부 콘트롤 데이터 내에서 결정되는 소정의 비트들로 구분될 수 있다. 도 15는 소스 콘트롤 패킷들의 데이터 테이블 예로써 이에 한정되는 것이 아니라 도 15의 데이터 테이블을 기본으로 하여 다양하게 변형될 수 있다.

- [0080] 도 15는 소스 콘트롤 패킷들(Cf, Cr, Cb, Cl)의 데이터 맵핑 테이블이다.

- [0081] 도 15를 참조하면, 더미 소스 콘트롤 패킷들(Cf, Cb, Cl)에서 C0~C3의 4 bits에는 하이논리(H), 로우논리(L), 로우논리(L), 로우논리(L)가 할당된다. 이에 비하여, 리얼 소스 콘트롤 패킷(Cr)에서 C0~C3의 4 bits에는 하이논리(H), 하이논리(H), 하이논리(H), 로우논리(L)가 할당된다. 따라서, 더미 소스 콘트롤 패킷들(Cf, Cb, Cl)과 리얼 소스 콘트롤 패킷(Cr)은 C1 및 C2의 bits로 구분될 수 있다.

- [0082] 더미 소스 콘트롤 패킷들(Cf, Cb, Cl) 중에서 RGB 데이터 패킷의 전송을 지시하는 마지막 더미 소스 콘트롤 패킷(Cl)은 C16~C17의 2 bits로 다른 더미 소스 콘트롤 패킷(Cf, Cb)과 구분될 수 있다.

- [0083] 리얼 소스 콘트롤 패킷(Cr)은 도 16과 같은 형태로 극성제어 관련 콘트롤 데이터와, 소스 출력 관련 콘트롤 데이터가 저장될 수 있다. 도 16에서 소스 출력 관련 콘트롤 데이터는 리얼 소스 콘트롤 패킷(Cr)의 C2 bit의 SOE, C4~C11 사이의 SOE\_PRD[3:0]을 포함하고, 극성제어 관련 콘트롤 데이터는 리얼 소스 콘트롤 패킷(Cr)의 C14 bit의 POL을 포함한다.

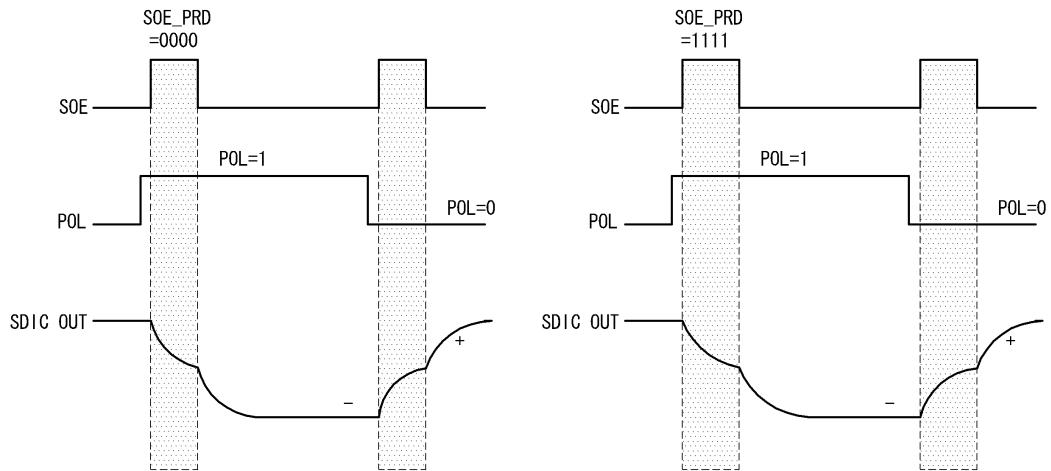

- [0084] 클럭 분리 및 데이터 샘플링부(21)의 SOE&POL 복원부(74)는 도 17과 같이 리얼 소스 콘트롤 패킷(Cr)의 C2 bit를 검출하여 소스 출력 인에이블신호(SOE)를 1 수평주기 단위로 미리 결정된 라이징 타임 시작에 발생하고 리얼 소스 콘트롤 패킷(Cr)의 C5, C7, C9 및 C11에서 SOE\_PRD[3:0]을 검출하여 소스 출력 인에이블신호(SOE)의 폴링 타임을 판단한다. 그리고 클럭 분리 및 데이터 샘플링부(21)의 SOE&POL 복원부(74)는 미리 결정된 라이징 타임과 SOE\_PRD[3:0]로 결정되는 폴링 타임 사이에서 하이논리를 유지하고 그 이외의 시간 동안 로우 논리를 유지하는 소스 출력 인에이블신호(SOE)를 발생한다.

- [0085] 클럭 분리 및 데이터 샘플링부(21)의 SOE&POL 복원부(74)는 도 17과 같이 리얼 소스 콘트롤 패킷(Cr)의 C14 bit

를 검출하여 극성제어신호(POL)를 발생시키고 그 극성제어신호(POL)를 i 수평기간 동안 동일한 논리로 유지한 후에 반전시킨다. 예컨대, 클럭 분리 및 데이터 샘플링부(21)의 SOE&POL 복원부(74)는 리얼 소스 콘트롤 패킷(Cr)의 C14 bit를 검출하여 극성제어신호(POL)를 발생시키고 그 극성제어신호(POL)를 1 수평기간 또는 2 수평기간 동안 하이논리로 유지한 다음 로우논리로 유지하고 1 수평기간 또는 2 수평기간 단위로 논리를 반전시킬 수 있다.

[0086] 도 18은 리얼 소스 콘트롤 패킷(Cr)의 SOE\_PRD[3:0]에 따라 결정되는 소스 출력신호의 폴스폭을 예시한 도면이다.

[0087] 소스 출력 인에이블신호(SOE)의 폴스폭은 도 18과 같이 리얼 소스 콘트롤 패킷(Cr)의 SOE\_PRD[3:0]에 따라 결정되며, SOE\_PRD[3:0]이 "0000(또는 LLLL)"일 때 가장 짧은 폭으로 제어되고 SOE\_PRD[3:0]이 "1111(또는 HHHH)"일 때 가장 긴 폭으로 결정될 수 있다. 소스 출력 인에이블신호(SOE)의 폴스폭은 액정표시장치의 모델마다 최적화값이 다를 수 있다. 이는 액정셀의 최적 데이터 충전양이 해상도 등의 패널 특성과 인버전 방식에 따라 달라질 수 있고 그 이외에도 여러 요인을 판단하여 결정될 수 있기 때문이다. 따라서, 액정표시장치의 제품 검토 시 액정셀의 데이터 충전타임을 조정하기 위하여 소스 출력 인에이블신호(SOE)의 폴스폭을 변경하여야 한다.

[0088] 본 발명은 SOE\_PRD[3:0]에 따라 클럭 분리 및 데이터 샘플링부(21)에서 복원되는 직렬 클럭(SCLK)의 주기를 카운트하여 소스 출력 인에이블신호(SOE)의 폴스폭을 조절할 수 있다. 여기서, 직렬 클럭(SCLK)의 1 주기는 1 콘트롤/RBG 데이터 패킷 타임과 실질적으로 동일하다. FHD(Full High Definition) 120Hz의 프레임 주파수로 구동되는 액정표시장치의 경우에 직렬 클럭(SCLK)의 1 주기는 대략 27.2ns이며, FHD 60Hz의 프레임 주파수로 구동되는 액정표시장치의 경우에 직렬 클럭(SCLK)의 1 주기는 대략 55.2ns이다. 따라서, FHD(Full High Definition) 120Hz의 프레임 주파수로 구동되는 액정표시장치의 경우에 SOE\_PRD<3:0> = 0000이면, 소스 출력 인에이블신호(SOE)의 폴스폭은 도 19와 같이 SCLK×4= 27.2ns×4= 108.8ns 만큼 짧게 제어되며, SOE\_PRD<3:0> = 1111 일 경우에 SCLK×64=27.2ns×64=1740.8ns 만큼 길게 제어된다.

[0089] 도 20은 R 데이터, G 데이터 및 B 데이터 각각이 10 bits의 데이터일 때, 클럭 분리 및 데이터 샘플링부(21)로부터 복원된 클럭(SCLK), 그 클럭(SCLK)에 따라 샘플링된 RGB 데이터 출력률을 보여 주는 과정도이다.

[0090] 본 발명의 실시예에 따른 액정표시장치와 그 구동방법은 도 10 내지 도 15와 같은 콘트롤/RBG 데이터 패킷에 한정되지 않고 도 21a 내지 도 21d와 같이 입력 영상의 비트수에 따라 콘트롤/RBG 데이터 패킷의 길이를 다르게 할 수 있다.

[0091] R 데이터, G 데이터 및 B 데이터 각각이 10 bits의 데이터일 때, 타이밍 콘트롤러(TCON)는 1 콘트롤/RBG 데이터 패킷을 도 21a와 같이 T 시간 동안 DUM, CLK, R1~R10, G1~G5, DE DUM, DE, G6~G10 및 B1~B10을 포함한 비트 스트림으로 발생한다. 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부(21)은 타이밍 콘트롤러(TCON)로부터 입력된 1 콘트롤/RBG 데이터 패킷 내에서 34 개의 에지 클럭들과 34 개의 센터 클럭들을 발생하고 센터 클럭들에 맞추어 콘트롤 데이터/RBG의 데이터 비트들을 샘플링한다.

[0092] R 데이터, G 데이터 및 B 데이터 각각이 8 bits의 데이터일 때, 타이밍 콘트롤러(TCON)는 1 콘트롤/RBG 데이터 패킷을 도 21b와 같이 T×(28/34) 시간 동안 DUM, CLK, R1~R8, G1~G4, DE DUM, DE, G5~G8, 및 B1~B8을 포함한 비트 스트림으로 발생한다. 소스 드라이브 IC들(SDIC#1~SDIC#8)의 클럭 분리 및 데이터 샘플링부(21)은 타이밍 콘트롤러(TCON)로부터 입력된 1 콘트롤/RBG 데이터 패킷 내에서 28 개의 에지 클럭들과 28 개의 센터 클럭들을 발생하고 센터 클럭들에 맞추어 콘트롤 데이터/RBG의 데이터 비트들을 샘플링한다.

[0093] R 데이터, G 데이터 및 B 데이터 각각이 6 bits의 데이터일 때, 타이밍 콘트롤러(TCON)는 1 콘트롤/RBG 데이터 패킷을 도 21c와 같이 T×(22/34) 시간 동안 DUM, CLK, R1~R6, G1~G3, DE DUM, DE, G4~G6 및 B1~B6을 포함한 비트 스트림으로 발생한다. 소스 드라이브 IC들(S-DIS#1~S-DIS#8)의 클럭 분리 및 데이터 샘플링부(21)은 타이밍 콘트롤러(TCON)로부터 입력된 1 콘트롤/RBG 데이터 패킷 내에서 22 개의 에지 클럭들과 22 개의 센터 클럭들을 발생하고 센터 클럭들에 맞추어 콘트롤 데이터/RBG의 데이터 비트들을 샘플링한다.

[0094] R 데이터, G 데이터 및 B 데이터 각각이 12 bits의 데이터일 때, 타이밍 콘트롤러(TCON)는 1 콘트롤/RBG 데이터 패킷을 도 21d와 같이 T×(40/34) 시간 동안 DUM, CLK, R1~R12, G1~G6, DE DUM, DE, G7~G12, 및 B1~B12을 포함한 비트 스트림으로 발생한다. 소스 드라이브 IC들(S-DIS#1~S-DIS#8)의 클럭 분리 및 데이터 샘플링부(21)은 타이밍 콘트롤러(TCON)로부터 입력된 1 콘트롤/RBG 데이터 패킷 내에서 40 개의 에지 클럭들과 40 개의 센터 클럭들을 발생하고 센터 클럭들에 맞추어 RGB의 데이터 비트들을 샘플링한 후에 그 데이터들을 병렬 체계로 변환하여 출력한다.

- [0095] 타이밍 콘트롤러(TCON)는 입력 데이터의 비트 수를 판단하여 도 21a 내지 도 21d와 같이 콘트롤/RGB 데이터 패킷의 길이를 자동 전환할 수 있다.

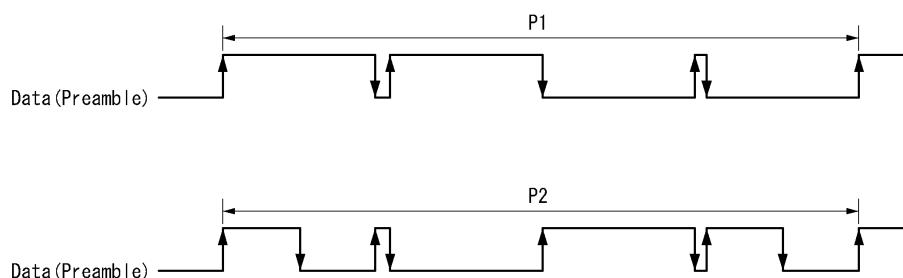

- [0096] 본 발명의 제2 실시예에 따른 액정표시장치는 제1 단계(phase 1)의 신호들을 펄스폭과 주기가 다른 다수의 펄스 그룹들을 포함한 프리앰블(preamble) 신호로 발생하여 클럭 분리 및 데이터 샘플링부(21)의 PLL 출력 클럭의 위상 및 주파수를 더 확실하게 락킹시킬 수 있다.

- [0097] 도 22 및 도 23은 본 발명의 다른 실시예에 따른 제1 단계(phase 1)의 신호를 보여 주는 과정도이다.

- [0098] 도 22 및 도 23을 참조하면, 제1 단계 신호는 phase 1-1 신호와 phase 1-2 신호를 포함한다. phase 1-1 신호는 전술한 프리앰블신호와 동일하게 그 1 주기가 1 콘트롤/RGB 데이터 패킷과 동일한 타임으로 설정되는 신호이다. phase 1-2 신호는 phase 1-1 신호보다 주파수가 높고 phase 1-1 신호의 1/2 이하의 주기로 발생된다. phase 1-2 신호는 위상과 주파수가 다른 두 개의 펄스 그룹(P1, P2)이 반복되는 형태로 발생될 수 있다. 제1 펄스 그룹(P1)은 phase 1-1 신호로 발생되는 펄스열의 주파수보다 2 배 이상 높고, 제2 펄스 그룹(P2)은 제1 펄스 그룹(P1)의 주파수보다 2 배 이상 높다. 클럭 분리 및 데이터 샘플링부(21)의 PLL(64)은 도 22 및 도 23과 같은 phase 1-1보다 주파수가 빠르고 위상이 규칙적으로 변하는 펄스들을 트랙킹하면 도 10과 같은 낮은 주파수의 규칙적인 프리앰블신호에 비하여 더 빠르고 안정되게 출력의 위상과 주파수를 락킹시킬 수 있다.

- [0099] 소스 드라이브 IC들(SDIC#1~SDIC#8)은 LCD 모듈 메이커의 요구가 다양화됨에 따라 LCD 모듈 메이커(소비자)가 세부 동작을 조절할 수 있도록 다양한 옵션을 제공하고 있다. 이를 위하여, 종래 기술에서는 소스 드라이브 IC들(SDIC#1~SDIC#8)에 다수의 옵션핀을 마련하고, LCD 모듈 메이커는 필요에 따라 소스 드라이브 IC들(SDIC#1~SDIC#8)의 옵션핀들에 풀업저항이나 풀다운저항을 연결하고 전원전압(Vcc)이나 기저전압(GND)을 인가하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 옵션 동작을 제어하였다. 그런데, 소스 드라이브 IC들(SDIC#1~SDIC#8)에 옵션핀들을 마련하면 그 만큼 칩 사이즈가 커질뿐 아니라 옵션핀들에 연결되는 풀업/풀다운저항 및 배선들로 인하여 PCB 사이즈가 커질 수 밖에 없었다.

- [0100] 본 발명의 제3 실시예에 따른 액정표시장치는 제2 단계(phase 2)의 일부 구간에 소스 드라이브 IC들(SDIC#1~SDIC#8)의 동작 옵션을 제어하기 위한 신호들을 추가하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 칩 사이즈와 PCB 사이즈를 더 줄일 수 있다. 이를 위하여, 본 발명의 제2 실시예에 따른 액정표시장치는 PWRC1/2, MODE, SOE\_EN, PACK\_EN, CHMODE, CID1/2, H\_2DOT 등의 소스 드라이브 IC들(SDIC#1~SDIC#8)의 다양한 동작을 제어하기 위한 콘트롤 옵션 정보를 별도의 소스 콘트롤 패킷으로 발생하고 그 소스 콘트롤 패킷을 제2 단계(phase 2)의 일부 구간에 데이터 배선쌍(DATA&CLK)을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다.

- [0101] PWRC1/2는 아래의 표 1과 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)의 출력 베피 증폭비를 조정하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 파워용량을 선택할 수 있게 하는 옵션 정보이다.

**표 1**

|                |                      |

|----------------|----------------------|

| PWRC1/2=11(HH) | High Power Mode      |

| PWRC1/2=10(HL) | Normal Power Mode    |

| PWRC1/2=01(LH) | Low Power Mode       |

| PWRC1/2=00(LL) | Ultra Low Power Mode |

- [0103] MODE는 아래의 표 2와 같이 소스 출력 인에이블신호(SOE)의 하이논리 기간 동안 차지쉐어전압 출력을 인에이블 할 것인지 아니면 디스에이블할 것인지 결정하는 옵션이다.

**표 2**

|           |                                                         |

|-----------|---------------------------------------------------------|

| MODE=1(H) | Hi_Z Mode Operation(charge share output disable)        |

| MODE=0(L) | Charge-share mode operation(Charge share output enable) |

- [0105] SOE\_EN은 아래의 표 3과 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)로 하여금 소스 출력 인에이블신호(SOE)를 RGB 디지털 비디오 데이터에 추가된 형태(embedded)로 입력받을 것인지 아니면 외부의 별도 배선을 통해 입력받을 것인 결정하는 옵션이다.

표 3

|             |                  |                  |

|-------------|------------------|------------------|

|             | PACK_EN=0(L)     | PACK_EN=1(H)     |

| SOE_EN=0(L) | Forbidden        | Use internal SOE |

| SOE_EN=1(H) | Use external SOE |                  |

[0107] PACK\_EN은 아래의 표 4와 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)로 하여금 극성제어신호(POL)와 게이트 드라이브 IC들(GDIC#1~GDIC#4)로 중계할 게이트 스타트 펄스(GSP)를 RGB 디지털 비디오 데이터에 추가된 형태(embedded)로 입력받을 것인지 아니면 외부의 별도 배선을 통해 입력받을 것인 결정하는 옵션이다.

표 4

|              |                                                    |

|--------------|----------------------------------------------------|

| PACK_EN=1(H) | Enable control packet                              |

| PACK_EN=0(L) | Disable control packet(Ignore the value of SOE_EN) |

[0109] CHMODE는 아래의 표 5와 같이 액정표시장치의 해상도에 맞게 소스 드라이브 IC들(SDIC#1~SDIC#8)의 출력 채널 수를 선택하는 옵션이다.

표 5

|             |                                      |

|-------------|--------------------------------------|

| CHMODE=1(H) | 690 Ch. Outputs(691~720 Ch. Disable) |

| CHMODE=0(L) | 720 Ch. Outputs                      |

[0111] CID1/2는 아래의 표 6과 같이 소스 드라이브 IC들(SDIC#1~SDIC#8) 별로 고유의 침식별코드(CID)를 부여하여 소스 드라이브 IC들(SDIC#1~SDIC#8)을 독립적으로 제어할 수 있게 하는 옵션이다. 소스 드라이브 IC들(SDIC#1~SDIC#8)의 개수에 따라 CID1/2의 비트수는 조정될 수 있다. 한편, 전술한 실시예와 같이 타이밍 콘트롤러(TCON)와 제어 배선쌍(SCL/SDA)을 통한 I2C 통신을 통해 소스 드라이브 IC들(SDIC#1~SDIC#8)을 개별 제어할 수 있다. LCD 메이커들은 상기 2 가지 방법들 중에서 소스 드라이브 IC들(SDIC#1~SDIC#8)을 독립적으로 제어하는 방법을 선택할 수 있다.

표 6

|               |           |

|---------------|-----------|

| CID1/2=00(LL) | SDIC#1 지정 |

| CID1/2=01(LH) | SDIC#2 지정 |

| CID1/2=10(HL) | SDIC#3 지정 |

| CID1/2=11(HH) | SDIC#4 지정 |

[0113] H\_2DOT는 아래의 표 7과 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)에서 출력되는 정극성/부극성 아날로그 비디오 데이터전압의 수평극성 주기를 제어하는 옵션이다. 예컨대, H\_2DOT=H 이면 소스 드라이브 IC들(SDIC#1~SDIC#8)은 수평 2 도트 인버전 방식(Horizontal 2-Dot inversion)으로 데이터전압의 극성을 제어한다. 수평 2 도트 인버전 방식에서 소스 드라이브 IC들(SDIC#1~SDIC#8)은 이웃하는 2 개의 데이터라인들에 동일 극성의 데이터전압을 출력하고 2 개의 데이터라인들 주기로 데이터전압의 극성을 반전시켜 수평으로 이웃하는 액정셀들에 충전되는 전압의 극성을 "- + + -... + - - + (또는 + - +... - + + -)"로 제어한다. H\_2DOT=L 이면 소스 드라이브 IC들(SDIC#1~SDIC#8)은 수평 1 도트 인버전 방식(Horizontal 1-Dot inversion)으로 데이터전압의 극성을 제어한다. 수평 1 도트 인버전 방식에서 소스 드라이브 IC들(SDIC#1~SDIC#8)은 이웃하는 데이터라인들에 공급되는 전압들의 극성을 반전시켜 수평으로 이웃하는 액정셀들에 충전되는 전압의 극성을 "- + - +... + - + - (또는 + - + -... - + - +)"로 제어한다.

표 7

|             |                                    |

|-------------|------------------------------------|

| H_2DOT=1(H) | Horizontal 2-Dot inversion Enable  |

| H_2DOT=0(L) | Horizontal 2-Dot inversion Disable |

[0115] 한편, 전술한 실시예들에서 타이밍 콘트롤러(TCON)는 마지막 소스 드라이브 IC(SDIC#8)로부터 하이논리의 피드백 락 신호를 입력받아야만 제2 단계(phase 1)이 행한다. 소스 드라이브 IC들(SDIC#1~SDIC#8) 중 어느 하나로도 PLL 락킹이 되지 않으면 타이밍 콘트롤러(TCON)는 제1 단계(phase)의 프리앰블신호만을 반복해서 발생하고 소스 드라이브 IC들(SDIC#1~SDIC#8)은 데이터전압을 출력하지 않는다. 따라서, 타이밍 콘트롤러(TCON)에 피드백 락 신호가 입력되지 않으면 소스 드라이브 IC들(SDIC#1~SDIC#8)의 개별 구동 상태를 확인할 수 없었다. 그런데, 소스 드라이브 IC들(SDIC#1~SDIC#8) 중에 어느 소스 드라이브 IC가 불량 칩인지 그리고 소스 드라이브 IC들(SDIC#1~SDIC#8) 각각의 구동 상태를 확인할 필요가 있다.

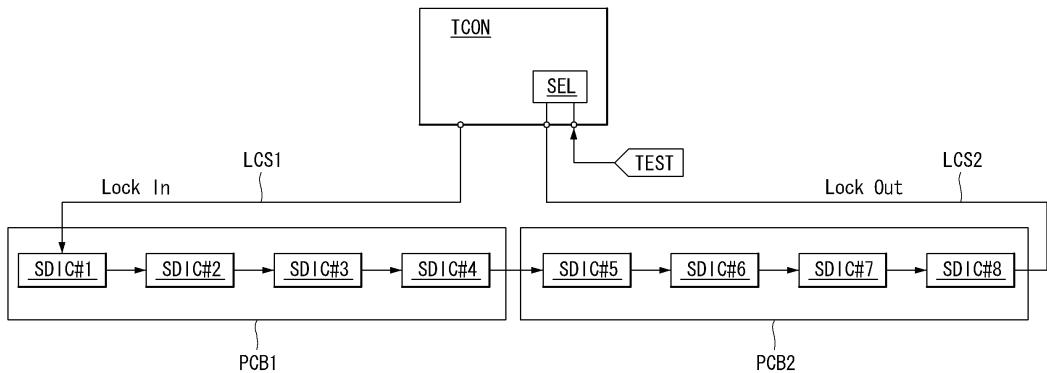

[0116] 본 발명의 제4 실시예에 따른 액정표시장치는 위와 같이 소스 드라이브 IC들(SDIC#1~SDIC#8)의 개별 구동 상태를 확인하기 위하여, 테스트 모드를 마련하고, 그 테스트 모드에서 타이밍 콘트롤러(TCON)에 피드백 락 신호를 입력하여 소스 드라이브 IC들(SDIC#1~SDIC#8)의 데이터전압 출력을 유도한다. 이를 위하여, 본 발명의 제4 실시예에 따른 액정표시장치는 도 24와 같이 타이밍 콘트롤러(TCON)의 내부 또는 외부에 선택부(SEL)를 설치한다.

[0117] 선택부(SEL)의 제1 입력단자는 피드백 락체크 배선(LCS2)에 접속되고, 제2 입력단자는 테스트 모드 인에이블신호(TEST)의 입력단자에 접속된다. 선택부(SEL)는 피드백 락 신호(Lock Out)와 테스트 모드 인에이블신호(TEST) 중 적어도 어느 하나를 출력하는 OR 게이트로 구현될 수 있다. 선택부(SEL)는 하이 논리의 피드백 락 신호(Lock Out)가 입력되지 않더라도 하이논리의 테스트 모드 인에이블신호(TEST)가 입력되면 그 하이논리의 테스트 모드 인에이블신호를 타이밍 콘트롤러(TCON)의 데이터 전송 모듈에 입력한다. 따라서, 타이밍 콘트롤러(TCON)는 테스트 모드에서 리얼 피드백 라신호를 입력받지 못하더라도 도 6에서 S8 단계로 이행하여 제2 단계(phase 2)의 신호들과 제3 단계(phase 3)의 신호들을 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다. 이 때, 타이밍 콘트롤러(TCON)는 테스트 모드에서 내장 메모리로부터 독출한 테스트 데이터를 제3 단계(phase 3)의 RGB 데이터 패킷으로 코딩하여 소스 드라이브 IC들(SDIC#1~SDIC#8)에 전송한다. 운용자는 테스트 모드에서 액정표시패널에 표시되는 테스트 데이터의 이미지를 보고 소스 드라이브 IC들(SDIC#1~SDIC#8)의 개별 구동 상태와 불량 여부를 확인할 수 있다.

[0118] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### 도면의 간단한 설명

[0119] 도 1은 본 발명의 실시예에 따른 액정표시장치를 나타내는 블록도이다.

[0120] 도 2는 도 1에 도시된 타이밍 콘트롤러와 소스 드라이브 IC들 사이의 배선들을 보여주는 도면들이다.

[0121] 도 3 및 도 4는 도 1에 도시된 소스 드라이브 IC의 내부 구성을 보여 주는 블록도이다.

[0122] 도 5는 도 1에 도시된 게이트 드라이브 IC의 내부 구성을 보여 주는 블록도이다.

[0123] 도 6은 도 1에 도시된 타이밍 콘트롤러와 소스 드라이브 IC들 사이의 신호 전송 과정을 단계적으로 보여주는 흐름도이다.

[0124] 도 7은 도 3에 도시된 클럭 분리 및 데이터 샘플링부를 상세히 보여 주는 블록도이다.

[0125] 도 8은 소스 드라이브 IC들의 디버깅을 가능하게 하는 직렬 통신 제어 경로와 칩 식별코드의 예를 보여 주는 도면이다.

[0126] 도 9는 도 7에 도시된 PLL을 상세히 보여 주는 블록도이다.

[0127] 도 10은 타이밍 콘트롤러에서 발생되는 제1 단계 신호를 보여 주는 과정도이다.

[0128] 도 11은 타이밍 콘트롤러에서 발생되는 제2 단계 신호를 보여 주는 과정도이다.

[0129] 도 12 및 도 13은 타이밍 콘트롤러에서 발생되는 제3 단계 신호를 보여 주는 과정도이다.

[0130] 도 14는 소스 콘트롤 패킷과 RGB 데이터 패킷의 데이터 맵핑 테이블 예를 보여 주는 도면이다.

[0131] 도 15는 더미 소스 콘트롤 패킷, 리얼 소스 콘트롤 패킷, 라스트 더미 소스 콘트롤 패킷의 맵핑 테이블 예를 보여 주는 도면이다.

- [0132] 도 16은 리얼 소스 콘트롤 패킷의 비트별 제어 데이터 내용의 예를 보여 주는 도면이다.

- [0133] 도 17은 리얼 소스 콘트롤 패킷의 소스 출력 관련 콘트롤 데이터와 극성제어 관련 콘트롤 데이터에 의해 제어되는 소스 출력 인에이블신호와 극성제어신호를 보여 주는 파형도이다.

- [0134] 도 18은 리얼 소스 콘트롤 패킷의 SOE\_PRD에 따라 결정되는 소스 출력신호의 펄스폭을 예시한 도면이다.

- [0135] 도 19는 도 18과 같은 SOE\_PRD에 따라 변화되는 소스 출력신호의 펄스폭을 예시하는 파형도이다.

- [0136] 도 20은 클럭 분리 및 데이터 샘플링부의 출력을 보여 주는 파형도이다.

- [0137] 도 21a 내지 도 21d는 RGB 데이터 패킷의 비트수가 달라질 때 데이터 패킷의 길이를 보여 주는 단면도이다.

- [0138] 도 22 및 도 23은 본 발명의 다른 실시예에 따른 제1 단계 신호를 보여 주는 파형도이다.

- [0139] 도 24는 본 발명의 실시예들에 따른 액정표시장치에서 테스트 모드를 위해 추가되는 구성을 보여 주는 도면이다.

- [0140] 〈도면의 주요 부분에 대한 부호의 설명〉

- [0141] TCON : 타이밍 콘트롤러 SDIC : 소스 드라이브 IC

- [0142] GDIS : 게이트 드라이브 IC

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

21

## 도면8

## 도면9

## 도면10

## 도면11

## 도면12

## 도면13

## 도면14

|        | Data Bit | CLK | D1~D10                | D11~D15     | DE_DUM | DE          | D16~D20                | D21~D30     |

|--------|----------|-----|-----------------------|-------------|--------|-------------|------------------------|-------------|

| Format | Clock    |     | R_data[0:9]           | G_data[0:4] | DUMMY  | Data Enable | G_data[5:9]            | B_data[0:9] |

|        | Clock    |     | Control Data (C1~C15) |             | DUMMY  | Data Enable | Control Data (C18~C32) |             |

## 도면15

| Items                     | C0  | C1  | C2      | C3 | C12~C11  | C12 | C13~C14  | C15 | C16 | C17 | C18~C32 |

|---------------------------|-----|-----|---------|----|----------|-----|----------|-----|-----|-----|---------|

| Dummy Control signal      | H   | L   | L       | L  | Assigned | L   | Assigned | H   | H   | L   |         |

| Real Control signal       | H   | (H) | (H)     | L  | Assigned | L   | Assigned | H   | H   | L   |         |

| Last Dummy Control signal | H   | L   | L       | L  | Assigned | L   | Assigned | H   | (L) | (H) |         |

| Control signal Mapping    | CLK | SOE | SOE PRD |    |          | POL |          | DE  |     |     |         |

## 도면16

| Position       |         | Items        | Description                  |

|----------------|---------|--------------|------------------------------|

| CLK            | C0      |              | -                            |

| R0             | C1      | DUM_SOE      | Dummy signal for SOE         |

| R1             | C2      | SOE          | Strobe Output Enable         |

| R2             | C3      | Reserved     | -                            |

| R3             | C4      | DUM_SOE_PRD0 | Dummy signal for SOE_PRD0    |

| R4             | C5      | SOE_PRD0     | Control SOE Period           |

| R5             | C6      | DUM_SOE_PRD1 | Dummy signal for SOE_PRD1    |

| R6             | C7      | SOE_PRD1     | Control SOE Period           |

| R7             | C8      | DUM_SOE_PRD2 | Dummy signal for SOE_PRD2    |

| R8             | C9      | SOE_PRD2     | Control SOE Period           |

| R9             | C10     | DUM_SOE_PRD3 | Dummy signal for SOE_PRD3    |

| G0             | C11     | SOE_PRD3     | Control SOE Period           |

| G1             | C12     | Reserved     | -                            |

| G2             | C13     | DUM_POL      | Dummy signal for POL         |

| G3             | C14     | POL          | Strobe polarity control      |

| G4             | C15     | Reserved     | -                            |

| DE_DUM         | C16     | DUM_DE       | -                            |

| DE             | C17     | Data Enable  | Control/RGB Signal Selection |

| G4~G9<br>B0~B9 | C18~C32 | Reserved     | -                            |

## 도면17

## 도면18

| SOE_PRD<3:0> | SOE High Period |

|--------------|-----------------|

| 0000         | SCLK x 4        |

| 0001         | SCLK x 8        |

| 0010         | SCLK x 12       |

| 0011         | SCLK x 16       |

| 0100         | SCLK x 20       |

| 0101         | SCLK x 24       |

| 0110         | SCLK x 28       |

| 0111         | SCLK x 32       |

| 1000         | SCLK x 36       |

| 1001         | SCLK x 40       |

| 1010         | SCLK x 44       |

| 1011         | SCLK x 48       |

| 1100         | SCLK x 52       |

| 1101         | SCLK x 56       |

| 1110         | SCLK x 60       |

| 1111         | SCLK x 64       |

도면19

도면20

도면21a

도면21b

도면21c

도면21d

도면22

도면23

## 도면24

|                |                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                       |         |            |

| 公开(公告)号        | <a href="#">KR1020100068936A</a>                                                            | 公开(公告)日 | 2010-06-24 |

| 申请号            | KR1020080127456                                                                             | 申请日     | 2008-12-15 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                    |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                   |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                   |         |            |

| [标]发明人         | KANG PIL SUNG<br>강필성<br>PARK MAN GYU<br>박만규<br>KOH GEUN WOO<br>고근우<br>HONG JIN CHEOL<br>홍진철 |         |            |

| 发明人            | 강필성<br>박만규<br>고근우<br>홍진철                                                                    |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                 |         |            |

| CPC分类号         | G09G3/3688 G09G3/3611 G09G2310/08 G09G3/006 G09G2300/0426                                   |         |            |

| 其他公开文献         | KR101322119B1                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                   |         |            |

### 摘要(译)

本发明涉及液晶显示器，包括定时控制器，第三步通过数据线对传输RGB数据包，它从第二步通过数据线对传输源控制包，通过锁定检查线传输锁定信号它发送前导信号，其中多个低逻辑的位通过数据布线对继续，多个高逻辑的位在第一步中继续，多个源驱动集成电路输入，反馈锁定信号在时序控制器，如果根据前导信号锁定输出时钟并锁定输出时钟，则使用源控制包生成源控制数据，并根据输出时钟对RGB数据包的RGB数据进行采样，并将RGB数据转换为根据源控制数据和RGB数据输出的直极性/负数据电压。