(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년06월22일

(11) 등록번호 10-1750126

(24) 등록일자 2017년06월16일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G11C 19/28* (2006.01)

(21) 출원번호 10-2012-7018662

(22) 출원일자(국제) 2010년12월20일

심사청구일자 2015년12월08일

(85) 번역문제출일자 2012년07월17일

(65) 공개번호 10-2012-0115521

(43) 공개일자 2012년10월18일

(86) 국제출원번호 PCT/JP2010/073649

(87) 국제공개번호 WO 2011/089832

국제공개일자 2011년07월28일

(30) 우선권주장

JP-P-2010-010419 2010년01월20일 일본(JP)

## (56) 선행기술조사문헌

US20050237294 A1

JP2007522498 A

전체 청구항 수 : 총 14 항

심사관 : 이승민

## (54) 발명의 명칭 표시 장치의 구동 방법 및 액정 표시 장치

**(57) 요약**

정지 화상 표시 모드는, 구동 회로부로부터의 화상 신호의 데이터를 화소에 기입하는 제1 기간; 제1 기간 후에, 구동 회로부를 동작시키기 위한 신호 또는 전압의 구동 회로부로의 공급을 중단하는 제2 기간; 및 제2 기간 후에, 구동 회로부를 동작시키기 위한 신호 또는 전압의 구동 회로부로의 공급을 재개하고, 구동 회로부로부터 화소에 화상 신호를 기입하여, 화소가 정지 화상을 계속 표시하게 하는 제3 기간을 포함한다. 구동 회로부를 동작시키기 위한 신호의 구동 회로부로의 공급의 중단부터 재개까지의 기간의 길이는, 표시 장치의 온도에 따라 설정된다.

**대 표 도 - 도1**

## 명세서

### 청구범위

#### 청구항 1

표시 장치를 구동하는 방법으로서,

구동 회로부로부터 화소 내로 화상 신호의 데이터를 기입하는 단계;

소정의 기간 동안 상기 구동 회로부를 동작시키기 위한 신호의 상기 구동 회로부의 공급을 중단하는 단계; 및

상기 기간 후에, 상기 구동 회로부로부터 상기 화소 내로 상기 화상 신호의 데이터를 기입하기 위해 상기 구동 회로부를 동작시키기 위한 신호의 상기 구동 회로부의 공급을 재개하는 단계;

를 포함하고,

상기 구동 회로부를 동작시키기 위한 신호의 공급을 중단하는 단계부터 상기 구동 회로부를 동작시키기 위한 신호의 공급을 재개하는 단계까지의 상기 기간의 길이는 상기 표시 장치 내의 온도 검출 회로에 의해 검출된 상기 표시 장치의 온도에 따라 설정되고,

상기 표시 장치는 상기 구동 회로부와 상기 화소를 포함하고,

상기 화소는 상기 기간에서 정지 화상을 표시하고,

상기 화소는 상기 화상 신호의 데이터를 기입함으로써 동화상을 표시하는, 표시 장치의 구동 방법.

#### 청구항 2

제1항에 있어서,

상기 구동 회로부를 동작시키기 위한 신호의 공급을 중단하는 단계부터 상기 구동 회로부를 동작시키기 위한 신호의 공급을 재개하는 단계까지의 기간의 길이는, 상기 온도 검출 회로에 의해 검출된 온도의 데이터를 이용하여 생성된 제어 신호에 기초하여 설정되는, 표시 장치의 구동 방법.

#### 청구항 3

삭제

#### 청구항 4

제1항 또는 제2항에 있어서,

스타트 신호, 클록 신호, 및 전원 전압의 상기 구동 회로부의 공급은, 상기 구동 회로부를 동작시키기 위한 신호의 공급의 중단 시에 중단되는, 표시 장치의 구동 방법.

#### 청구항 5

삭제

#### 청구항 6

제1항 또는 제2항에 있어서,

스타트 신호, 클록 신호, 및 전원 전압의 상기 구동 회로부의 공급은, 상기 구동 회로부를 동작시키기 위한 신호의 공급의 재개 시에 재개되는, 표시 장치의 구동 방법.

#### 청구항 7

삭제

#### 청구항 8

제4항에 있어서,

상기 스타트 신호, 상기 클록 신호, 및 상기 전원 전압의 상기 구동 회로부로의 공급은, 상기 구동 회로부를 동작시키기 위한 신호의 공급의 재개 시에 재개되는, 표시 장치의 구동 방법.

### 청구항 9

액정 표시 장치로서,

화상 신호, 제1 제어 신호, 및 제2 제어 신호를 수신하고, 상기 제1 제어 신호 및 상기 제2 제어 신호에 기초하여 순차적으로 스타트 신호의 출력, 클록 신호의 출력, 및 전원 전압의 출력 중 적어도 하나를 선택적으로 개시하거나 중단하는 표시 제어 회로;

상기 화상 신호, 상기 스타트 신호, 상기 클록 신호, 및 상기 전원 전압의 출력을 수신하는 구동 회로부; 및

상기 구동 회로부로부터 상기 화상 신호를 수신하는 화소

를 포함하고,

상기 제1 제어 신호는 상기 화상 신호에 기초하는 신호이고,

상기 제2 제어 신호는 상기 액정 표시 장치의 온도에 기초하는 신호인, 액정 표시 장치.

### 청구항 10

액정 표시 장치로서,

제1 화상 신호의 데이터 및 제2 화상 신호의 데이터를 순차적으로 저장하는 메모리 회로;

상기 제1 화상 신호의 데이터와 상기 제2 화상 신호의 데이터를 비교하여 제1 제어 신호를 생성하는 비교 회로;

상기 제1 제어 신호에 기초하여 제3 화상 신호의 데이터를 판독하여 상기 제3 화상 신호의 데이터를 출력하는 선택 회로;

상기 액정 표시 장치의 온도를 검출하여 제2 제어 신호를 생성하는 보정 회로;

상기 제1 제어 신호, 상기 제2 제어 신호, 및 상기 제3 화상 신호를 수신하고, 상기 제1 제어 신호 및 상기 제2 제어 신호에 기초하여 순차적으로 상기 제3 화상 신호의 출력, 스타트 신호의 출력, 클록 신호의 출력, 및 전원 전압의 출력을 선택적으로 개시하거나 중단하는, 표시 제어 회로;

상기 제3 화상 신호, 상기 스타트 신호, 상기 클록 신호, 및 상기 전원 전압의 출력을 수신하는 구동 회로부; 및

상기 제3 화상 신호에 대응하는 화상을 표시하는 화소

를 포함하고,

상기 제1 화상 신호 및 상기 제2 화상 신호는 연속된 프레임 기간의 화상 신호이며,

상기 제3 화상 신호는 상기 제1 화상 신호 또는 상기 제2 화상 신호인, 액정 표시 장치.

### 청구항 11

제10항에 있어서,

상기 보정 회로는,

상기 액정 표시 장치의 온도를 검출하여 검출된 온도에 따라 제1 계수값을 생성하는 온도 검출 회로;

정지 화상에 대응하는 연속된 프레임 기간의 수를 계수하여 제2 계수값을 생성하는 계수 회로; 및

상기 제1 계수값과 상기 제2 계수값을 비교하고 비교 결과에 기초하여 상기 제2 제어 신호를 생성하는 계수값 비교 회로를 포함하는, 액정 표시 장치.

### 청구항 12

제9항에 있어서,

상기 화소는, 액정 표시 소자와, 상기 화상 신호의 데이터를 상기 액정 표시 소자에 출력할지 여부를 제어하는 트랜지스터를 포함하고,

상기 트랜지스터는, 채널 형성층으로서 기능하고  $1 \times 10^{14} / \text{cm}^2$  미만의 캐리어 농도를 갖는 산화물 반도체층을 포함하는, 액정 표시 장치.

### 청구항 13

삭제

### 청구항 14

제10항 또는 제11항에 있어서,

상기 화소는, 액정 표시 소자와, 상기 제3 화상 신호의 데이터를 상기 액정 표시 소자에 출력할지 여부를 제어하는 트랜지스터를 포함하고,

상기 트랜지스터는, 채널 형성층으로서 기능하고  $1 \times 10^{14} / \text{cm}^2$  미만의 캐리어 농도를 갖는 산화물 반도체층을 포함하는, 액정 표시 장치.

### 청구항 15

표시 장치를 구동하는 방법으로서,

구동 회로로부터 화소 내로 화상 신호의 데이터를 기입하는 단계;

소정의 기간 동안 상기 구동 회로부를 동작시키기 위한 신호의 상기 구동 회로부로의 공급을 중단하는 단계; 및 상기 기간 후에, 상기 구동 회로부를 동작시키기 위한 신호의 상기 구동 회로부로의 공급을 재개하여 상기 구동 회로부로부터 상기 화소 내로 상기 화상 신호의 데이터를 기입하는 단계

를 포함하고,

상기 구동 회로부를 동작시키기 위한 신호의 공급을 중단하는 단계부터 상기 구동 회로부를 동작시키기 위한 신호의 공급을 재개하는 단계까지의 상기 기간의 길이는 상기 표시 장치 내의 온도 검출 회로에 의해 검출된 상기 표시 장치의 온도에 따라 설정되고,

상기 표시 장치는 상기 구동 회로부와 상기 화소를 포함하며,

상기 화소는 상기 기간에서 정지 화상을 표시하는, 표시 장치의 구동 방법.

### 청구항 16

액정 표시 장치로서,

제1 화상 신호의 데이터 및 제2 화상 신호의 데이터를 순차적으로 저장하는 메모리 회로;

상기 제1 화상 신호의 데이터와 상기 제2 화상 신호의 데이터를 비교하여 제1 제어 신호를 생성하는 비교 회로;

상기 제1 화상 신호의 데이터를 판독하여 상기 제1 화상 신호를 출력하는 선택 회로;

상기 액정 표시 장치의 온도를 검출하여 제2 제어 신호를 생성하는 보정 회로;

상기 제1 제어 신호, 상기 제2 제어 신호, 및 상기 제1 화상 신호를 수신하고, 스타트 신호의 출력, 클록 신호의 출력, 및 전원 전압의 출력 중 적어도 하나를 순차적으로 중단하는 표시 제어 회로;

상기 표시 제어 회로가 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력 중 적어도 하나를 중단하는 동안 동작을 중단하는 구동 회로부; 및

상기 표시 제어 회로가 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력 중 적어도 하나를 중단하는 동안 상기 제1 화상 신호에 대응하는 화상을 표시하는 화소

를 포함하고,

상기 제1 화상 신호 및 상기 제2 화상 신호는 연속된 프레임 기간의 화상 신호인, 액정 표시 장치.

### 청구항 17

제16항에 있어서,

상기 표시 제어 회로는 상기 제1 화상 신호의 출력, 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력을 순차적으로 중단하고,

상기 구동 회로부는, 상기 표시 제어 회로가 상기 제1 화상 신호의 출력, 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력을 중단하는 동안 동작을 중단하며,

상기 화소는, 상기 표시 제어 회로가 상기 제1 화상 신호의 출력, 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력을 중단하는 동안 상기 제1 화상 신호에 대응하는 화상을 표시하는, 액정 표시 장치.

### 청구항 18

제9항에 있어서,

상기 표시 제어 회로는, 상기 제1 제어 신호 및 상기 제2 제어 신호에 기초하여 순차적으로 상기 화상 신호의 출력, 상기 스타트 신호의 출력, 상기 클록 신호의 출력, 및 상기 전원 전압의 출력을 선택적으로 개시하거나 중단하는, 액정 표시 장치.

## 발명의 설명

### 기술 분야

[0001]

본 발명의 실시형태는 표시 장치의 구동 방법에 관한 것이다. 본 발명의 또 다른 실시형태는 액정 표시 장치에 관한 것이다.

### 배경 기술

[0002]

액정 표시 장치 등의 표시 장치는 텔레비전 수상기 등의 대형 표시 장치로부터 휴대 전화 등의 소형 표시 장치에 이르기까지 광범위하게 응용되고 있으며, 더욱 높은 부가가치를 갖는 제품이 개발되고 있다. 최근에는, 예를 들어, 모바일 장치의 편리성 향상의 관점에서, 낮은 전력 소비를 갖는 표시 장치의 개발이 주목받고 있다.

[0003]

예를 들어, 특히 문헌 1은, 어떠한 주사선 및 신호선도 선택되지 않은 휴지 기간(break period)에 각 신호선의 전압을 일정하게 유지하기 위하여, 모든 신호선이 신호선 구동 회로로부터 전기적으로 접속해제되어 고 임피던스 상태가 형성되는, 액정 표시 장치의 전력 소비를 저감하는 기술을 개시하고 있다.

[0004]

비특히 문헌 1은, 동화상 표시 때의 리프레쉬 레이트(refresh rate)가 정지 화상 표시 때의 리프레쉬 레이트와 상이한, 액정 표시 장치의 전력 소비의 저감을 위한 구조를 개시하고 있다. 또한, 비특히 문헌 1에서는, 정지 화상 표시 때의 휴지 기간과 주사 기간 사이에서 신호의 스위칭에 의해 액정 소자에 인가되는 전압의 변동에 기인한 플리커의 인지를 방지하기 위하여, 휴지 기간에도 신호선과 공통 전극에 동위상의 교류 신호를 인가하는, 액정 소자에 인가되는 전압의 변동을 방지하는 기술이 개시되어 있다.

### 선행기술문헌

#### 특허문헌

[0005]

(특허문헌 0001) 일본 공개 특허 출원 제2001-312253

#### 비특허문헌

[0006] (비)특허문현 0001) Kazuhiko Tsuda et al., IDW'02, pp. 295-298

### 발명의 내용

- [0007] 그러나, 상기 구동 방법에서는, 액정 표시 장치의 주사선이나 신호선에 신호를 공급하는 구동 회로의 구조 및 동작이 복잡하여, 액정 표시 장치의 전력 소비가 충분히 저감될 수 없다.

- [0008] 또한, 특히 문헌 1에서와 같이, 어떠한 주사선 및 신호선도 선택되지 않는 휴지 기간이 제공되는 경우, 화소로의 기입 동작들 사이의 간격이 길어지고, 이것은 일부 경우에는 트랜지스터의 리크 전류나 기생 용량에 기인하여 액정 소자에 인가되는 전압이 크게 감소되도록 할 수도 있다. 액정 소자에 인가되는 전압의 큰 감소는 표시 품질을 저하시킨다; 예를 들어, 미리결정된 계조의 표시가 실시될 수 없다.

- [0009] 또한, 상기 액정 표시 장치에서, 자신의 온도 변화에 기인하여 휘도가 변하여, 정지 화상을 표시하는 경우에도, 시간이 경과함에 따라 휘도의 변화가 점진적으로 커짐으로써, 표시 품질이 저하된다.

- [0010] 상기 문제에 비추어, 본 발명의 실시형태의 목적은, 표시 장치의 구동 회로에서의 복잡한 동작 없이 전력 소비를 저감하는 것이다. 본 발명의 실시형태의 또 다른 목적은 표시 품질의 저하를 저감하는 것이다.

- [0011] 본 발명의 실시형태에서는, 동화상 표시 모드와 정지 화상 표시 모드가 설정되고, 정지 화상 표시 모드 때, 구동 회로를 동작시키기 위한 신호나 전압을 구동 회로에 공급하는 동작이 중단되더라도, 그 동작의 중단 직전에 기입된 화상이 정지 화상으로서 유지된다. 그 다음, 표시된 화상이 정지 화상으로서 유지되기 위하여 화상 신호의 데이터가 재기입됨으로써, 화소가 정지 화상을 계속 표시한다. 또한, 표시 장치의 온도에 따라 정지 화상의 유지 기간이 설정된다.

- [0012] 또한, 본 발명의 한 실시형태에서는, 비교적 높은 주파수(예를 들어, 60 Hz 이상)에서 동화상이 표시되는 모드 와, 비교적 낮은 주파수(예를 들어, 1 Hz 이하)에서 화상 신호의 데이터가 화소에 기입되는 정지 화상 표시 모드 또는 간이 동화상 재생 모드가 설정된다. 정지 화상 표시 모드 또는 간이 동화상 재생 모드의 화상 신호 데이터의 기입 동작들 간의 간격이 표시 장치의 온도에 따라 설정된다.

- [0013] 본 발명의 실시형태는, 화상 신호가 입력되는 구동 회로부와 구동 회로부로부터의 화상 신호의 데이터의 기입에 의해 표시 상태가 제어되는 화소를 포함하고 동화상 표시 모드와 정지 화상 표시 모드를 갖는, 표시 장치의 구동 방법이다. 정지 화상 표시 모드는, 구동 회로부로부터의 화상 신호의 데이터를 화소에 기입하는 제1 기간; 제1 기간 후에, 구동 회로부를 동작시키기 위한 신호 또는 전압의 구동 회로부로의 공급을 중단하는 제2 기간; 및 제2 기간 후에, 구동 회로부를 동작시키기 위한 신호 또는 전압의 구동 회로부로의 공급을 재개하고, 구동 회로부로부터 화소에 화상 신호를 기입하여, 화소가 정지 화상을 계속 표시하게 하는 제3 기간을 포함한다. 제2 기간과 제3 기간에서 구동 회로부를 동작시키기 위한 신호 또는 전압의 구동 회로부로의 공급의 중단부터 재개까지의 기간의 길이는, 표시 장치의 온도에 따라 설정된다.

- [0014] 본 발명의 또 다른 실시형태는, 화상 신호, 스타트 신호, 클록 신호, 화상 신호에 기초하는 신호인 제1 제어 신호, 액정 표시 장치의 온도에 기초한 신호인 제2 제어 신호, 및 전원 전압이 입력되고, 입력 화상 신호, 스타트 신호, 클록 신호, 및 전원 전압의 출력을 제1 제어 신호 및 제2 제어 신호에 기초하여 선택적으로 개시 또는 중단하는 표시 제어 회로; 표시 제어 회로로부터 순차적으로 입력되는 화상 신호, 스타트 신호, 클록 신호, 및 전원 전압에 의해 동작의 개시 또는 중단이 제어되는 구동 회로부; 및 구동 회로부로부터 기입된 화상 신호의 데이터에 의해 표시 상태가 제어되는 화소를 포함하는 액정 표시 장치이다.

- [0015] 본 발명의 또 다른 실시형태는, 화상 신호가 입력되고 입력된 화상 신호의 상태를 데이터로서 순차적으로 저장하는 메모리 회로; 메모리 회로에 저장된 화상 신호의 데이터 중에서 연속하는 프레임 기간의 화상에 대응하는 화상 신호의 데이터를 비교하고, 비교 결과에 기초하여 제1 제어 신호를 생성하는 비교 회로; 제1 제어 신호에 기초하여 메모리 회로에 저장된 화상 신호의 데이터를 판독하고 판독된 화상 신호의 판독 데이터를 데이터 신호로서 출력하는 선택 회로; 액정 표시 장치의 온도를 검출하고 검출된 온도에 따라 제2 제어 신호를 생성하는 온도 검출 회로; 스타트 신호, 클록 신호, 제1 제어 신호, 제2 제어 신호, 및 전원 전압이 입력되고 선택 회로로부터 화상 신호가 입력되면 입력 화상 신호, 스타트 신호, 클록 신호, 및 전원 전압의 출력을 제1 제어 신호 및 제2 제어 신호에 기초하여 선택적으로 개시 또는 중단하는 표시 제어 회로; 및 구동 회로부로부터 기입된 화상 신호의 데이터에 의해 표시 상태가 제어되는 화소를 포함하는 액정 표시 장치이다.

[0016] 본 발명의 실시형태에 의해, 정지 화상을 표시할 때의 전력 소비가 저감될 수 있다. 또한, 표시 품질의 열화가 저감될 수 있다.

### 도면의 간단한 설명

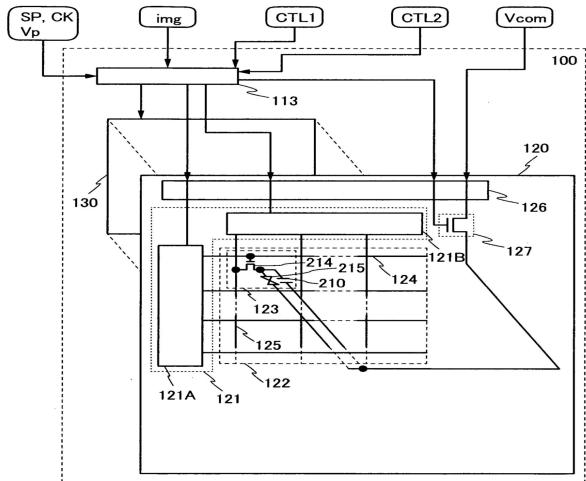

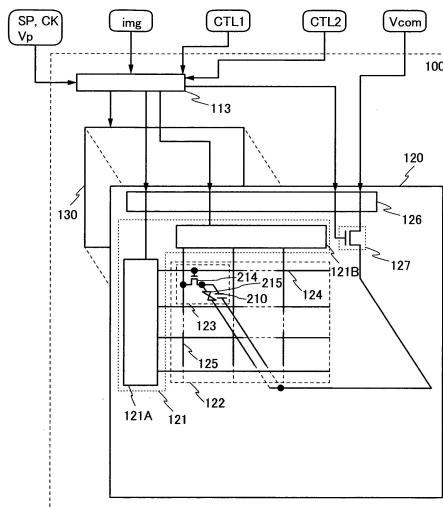

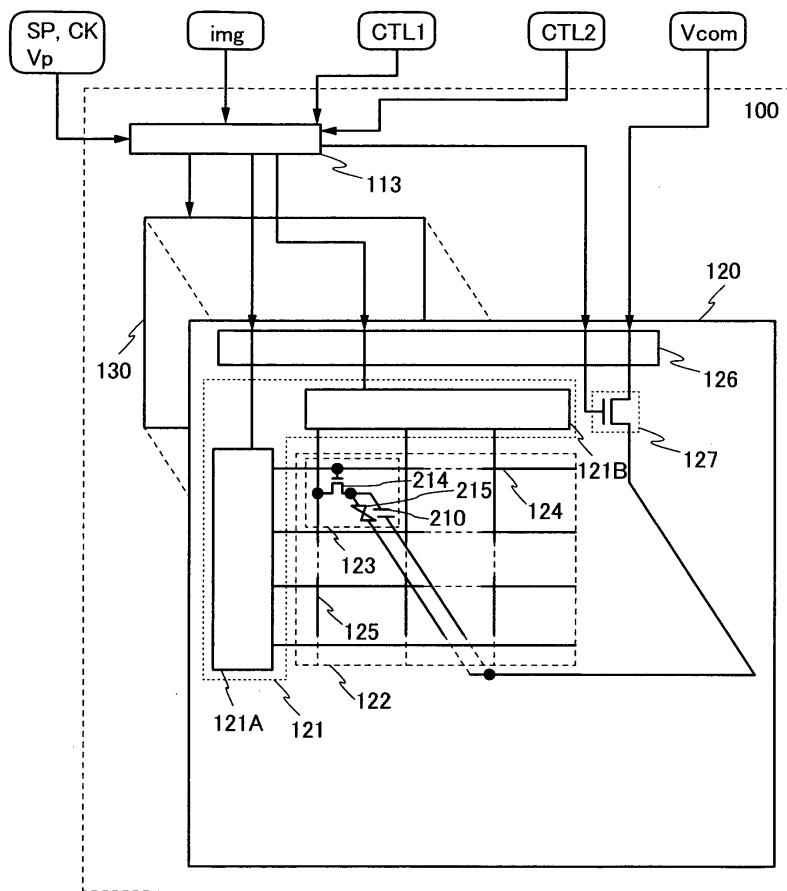

[0017] 도 1은 실시형태 1의 표시 장치의 구조예를 나타낸다;

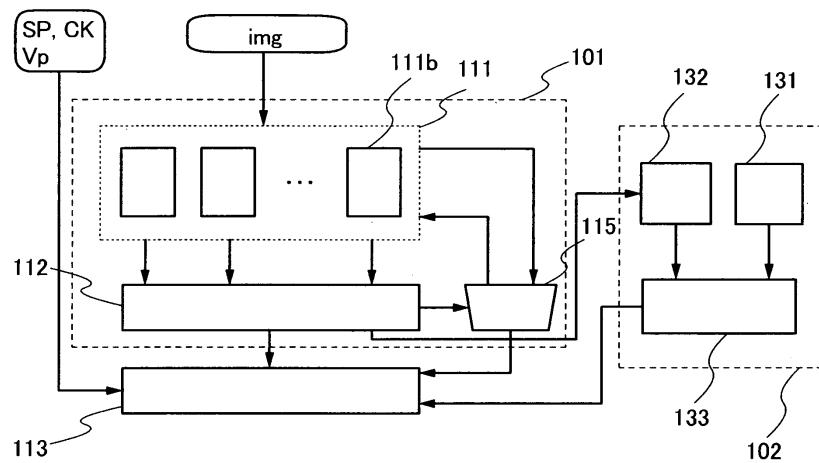

도 2는 화상 처리 회로, 보정 회로, 및 표시 제어 회로의 구조를 나타낸다;

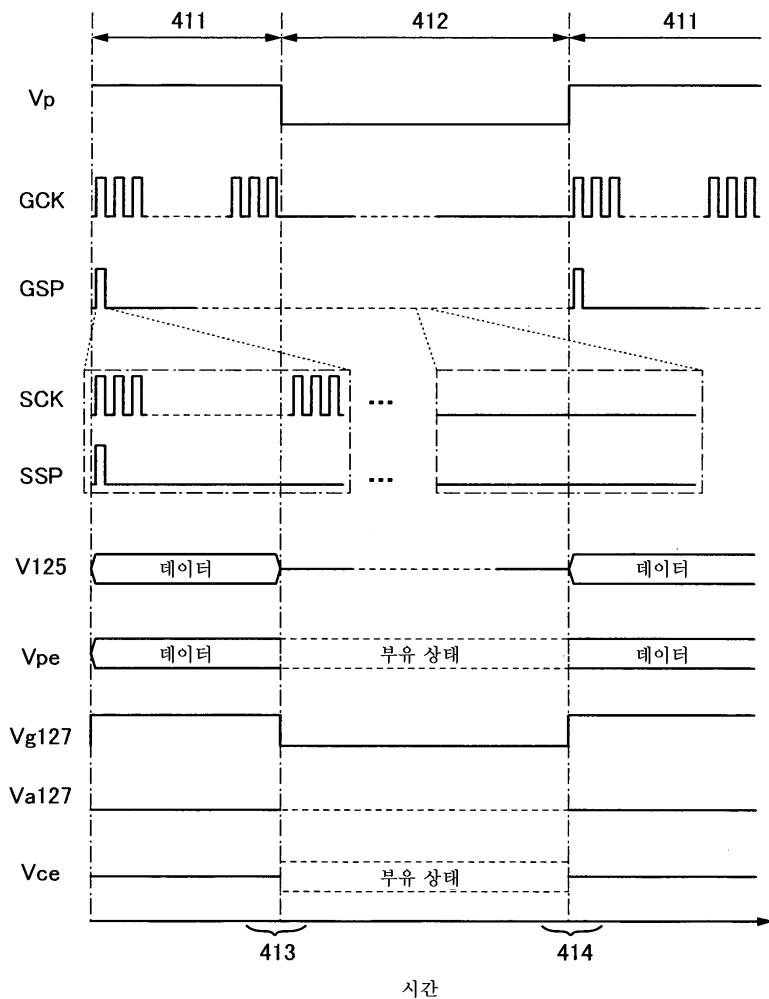

도 3은 도 1에 나타낸 표시 장치의 동작예를 도시하는 타이밍도이다;

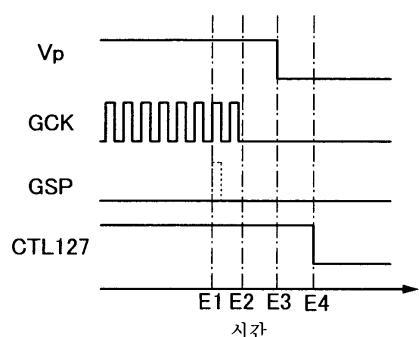

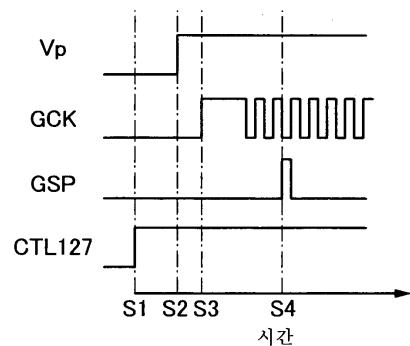

도 4a 및 도 4b는 도 1에 나타낸 표시 장치의 동작예를 도시하는 타이밍도이다;

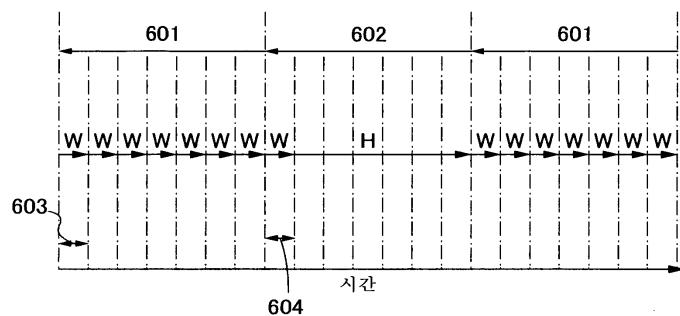

도 5는 도 1에 나타낸 표시 장치의 동작예를 도시하는 타이밍도이다;

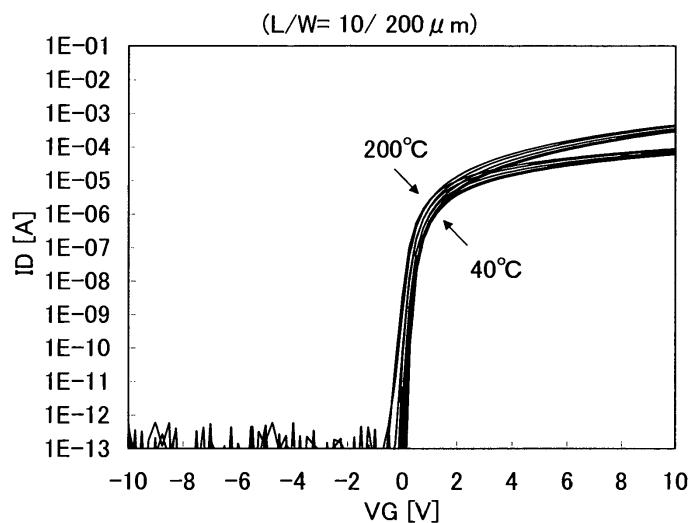

도 6a 및 도 6b는 온도 변화에 따른 트랜지스터의 전기 특성의 변동을 도시한다;

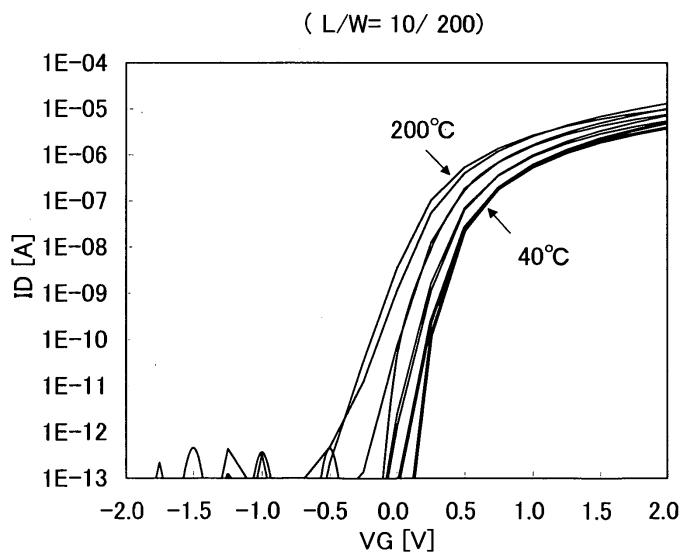

도 7은 온도 변화에 따른 표시 장치의 화소에서의 유지 전압의 변동을 도시한다;

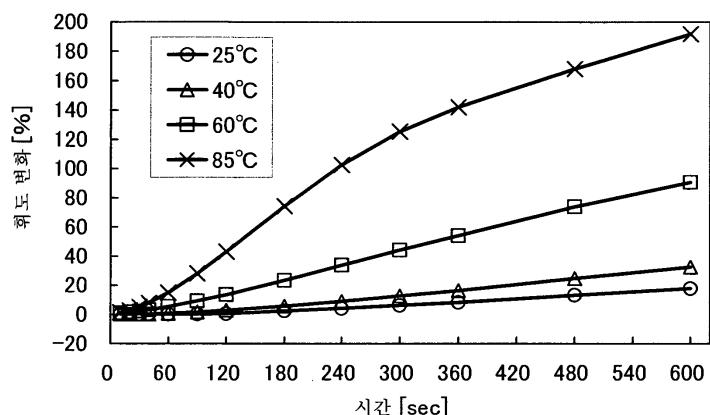

도 8a 내지 도 8c는 실시형태 2의 시프트 레지스터의 구성예를 도시한다;

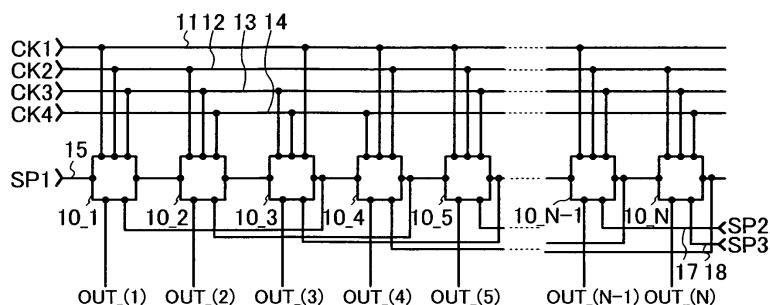

도 9는 실시형태 2의 시프트 레지스터의 동작예를 도시한다;

도 10a 내지 도 10d는 실시형태 3의 트랜지스터의 구조예를 나타낸다;

도 11의 (a) 내지 (e)는 실시형태 3의 트랜지스터의 제조 방법의 예를 나타낸다;

도 12a 내지 도 12c는 실시형태 4의 액정 표시 장치의 구조예를 나타낸다;

도 13a 및 도 13b는 실시형태 5의 액정 표시 장치의 구조예를 나타낸다;

도 14는 실시형태 6의 표시 장치의 구조예를 나타낸다;

도 15a 내지 도 15f는 실시형태 7의 액정 표시 장치의 구조예를 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0018] 이하에서부터, 본 발명의 실시형태들이 도면들을 참조하여 상세히 설명될 것이다. 본 발명은 이하의 설명으로 한정되는 것은 아니며, 당업자라면 본 발명의 사상과 범위로부터 벗어나지 않고 형태 및 세부사항이 다양한 방식으로 수정될 수 있다는 것을 용이하게 이해할 것이라는 점에 유의한다. 따라서, 본 발명은 이하의 실시형태들의 설명으로 한정되는 것으로 해석되어서는 안 된다.

[0019] (실시형태 1)

[0020] 본 실시형태에서는, 주변 온도에 따라 구동 회로의 개시 또는 중단 동작의 타이밍이 제어되는 액정 표시 장치를 표시 장치의 일례로서 설명한다.

[0021] 우선, 도 1을 참조하여 본 실시형태의 액정 표시 장치의 구조예를 설명한다. 도 1은 액정 표시 장치의 구조예를 나타내는 블록도이다.

[0022] 도 1에 나타낸 액정 표시 장치(100)는, 제어 신호(CTL1) 및 제어 신호(CTL2)에 기초하여 신호 또는 전압의 출력이 제어되는 표시 제어 회로(113)와, 표시 제어 회로(113)에 의해 표시 동작이 제어되는 표시 패널(120)을 포함한다.

[0023] 용어 "전압"이란, 일반적으로 두 지점의 전위들 사이의 차(전위차라고도 함)를 의미한다는 점에 유의한다. 그러나, 일부 경우에, 회로도 등에서 전압과 전위 양쪽 모두의 값은 볼트(V)를 이용하여 표시되므로, 이들 간을 구분하는 것은 어렵다. 따라서, 본 명세서에서는, 달리 명시하지 않는 한, 한 지점에서의 전위와 기준 전위 사이의 전위차는 때때로 그 지점에서의 전압이라고 부른다.

[0024] 또한, 표시 패널(120)은 구동 회로부(121), 화소부(122), 주사선(124), 및 화상 신호선(125)을 포함한다. 구동 회로부(121)는 구동 회로(121A)와 구동 회로(121B)를 포함한다. 화소부(122)는 복수의 화소(123)를 포함한다.

[0025] 화상 신호(img)와, 구동 회로부(121)를 동작시키기 위한 신호 또는 전압(예를 들어, 스타트 신호 SP, 클록 신호 CK, 제어 신호 CTL1, 제어 신호 CTL2, 및 전원 전압 Vp)이 표시 제어 회로(113)에 입력(공급)된다. 표시 제어

회로(113)는, 제어 신호(CTL1) 및 제어 신호(CTL2)에 기초하여, 입력 화상 신호(img), 스타트 신호(SP), 클록 신호(CK), 및 전원 전압(Vp)을 선택적으로 출력하는 기능을 가진다. 전원 전압(Vp)은, 예를 들어, 외부 장치로부터 입력된다.

[0026] 예를 들어, 화상 신호는, 예를 들어, 도트 반전 구동, 소스선 반전 구동, 게이트선 반전 구동, 프레임선 구동 등에 의해 프레임 기간마다 특성을 반전시킨 신호일 수 있다. 화상 신호(img)가 아날로그 신호의 경우에는, A/D 컨버터 등에 의해 아날로그 신호가 디지털 신호로 변환되고, 그 디지털 신호가 화상 신호(img)로서 이용될 수도 있다.

[0027] 스타트 신호(SP)의 예로는, 구동 회로(121A)에 출력되는 스타트 신호(GSP), 및 구동 회로(121B)에 출력되는 스타트 신호(SSP)가 있다. 스타트 신호(GSP) 및 스타트 신호(SSP)에 대응하는 스타트 신호들 각각은 복수의 신호일 수도 있다는 점에 유의한다. 스타트 신호(SP)는, 예를 들어, 외부 장치로부터 입력된다.

[0028] 클록 신호(CK)의 예로서는, 구동 회로(121A)에 출력되는 클록 신호(GCK), 및 구동 회로(121B)에 출력되는 클록 신호(SCK)가 있다. 클록 신호(GCK) 및 클록 신호(SCK)에 대응하는 클록 신호들 각각은 복수의 신호일 수도 있다는 점에 유의한다. 클록 신호(CK)는, 예를 들어, 외부 장치로부터 입력된다.

[0029] 제어 신호(CTL1)는 화상 신호(img)에 따라 표시 제어 회로(113)의 동작을 제어하기 위한 신호이다. 제어 신호(CTL1)에 포함되는 데이터의 예로서는, 표시 제어 회로(113)로부터 구동 회로부(121)에 화상 신호(img), 스타트 신호(SP), 클록 신호(CK), 및 전원 전압(Vp)을 출력하는 타이밍 또는 횟수 등을 지정하는 명령이나 정보가 있다. 제어 신호(CTL1)는, 예를 들어, 화상 신호(img)에 따라 적절히 생성된다. 생성된 제어 신호(CTL1)의 데이터는 미리 메모리 회로 등에 저장되고, 메모리 회로로부터 적절히 판독될 수도 있다.

[0030] 제어 신호(CTL2)는 액정 표시 장치(100)의 온도에 따라 표시 제어 회로(113)의 동작을 제어하기 위한 신호이다. 제어 신호(CTL2)에 포함되는 데이터의 예로서는, 액정 표시 장치(100)의 온도에 따라, 표시 제어 회로(113)로부터 구동 회로부(121)에 화상 신호(img), 스타트 신호(SP), 클록 신호(CK), 및 전원 전압(Vp)을 출력하는 최적 타이밍 또는 최적 횟수를 지정하는 명령이나 정보가 있다. 제어 신호(CTL2)는, 예를 들어, 액정 표시 장치의 온도에 따라 적절히 생성된다. 여기서, 온도란, 예를 들어, 액정 표시 장치(100) 내부의 온도, 또는 액정 표시 장치(100)가 놓인 환경의 온도를 의미한다.

[0031] 도 1에 나타낸 액정 표시 장치에 화상 처리 회로가 제공되어 제어 신호(CTL1)를 생성할 수도 있고, 도 1에 나타낸 액정 표시 장치에 보정 회로가 제공되어 제어 신호(CTL2)를 생성할 수도 있다. 화상 처리 회로 및 보정 회로를 제공하는 경우 화상 처리 회로, 보정 회로, 및 표시 제어 회로(113)의 구조를 도 2를 참조하여 설명한다. 도 2는 화상 처리 회로, 보정 회로, 및 표시 제어 회로의 구조예를 나타낸다.

[0032] 도 2에 나타낸 화상 처리 회로(101)는, 화상 신호(img)의 데이터(화상 데이터라고도 함)를 저장하는 메모리 회로(111), 메모리 회로(111)에 저장된 복수의 화상 데이터를 비교하는 비교 회로(112), 메모리 회로(111)로부터의 화상 데이터의 판독이 비교 회로(112)에 의해 제어되는 선택 회로(115)를 포함한다.

[0033] 메모리 회로(111)는, 화상 신호(img)가 입력되고 입력된 화상 신호(img)를 데이터로서 순차적으로 저장하는 기능을 갖는 회로이다. 메모리 회로(111)는, 복수의 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터를 저장하기 위한 복수의 프레임 메모리를 포함한다. 1 프레임 기간의 메모리 영역을 개념적으로 나타내기 위하여도 2에 프레임 메모리(111b)가 도시되어 있다. 메모리 회로(111)의 프레임 메모리의 개수는, 메모리 회로(111)가 복수의 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터를 저장할 수 있는 한, 특별히 제한되지 않는다. 프레임 메모리는, DRAM(dynamic random access memory) 또는 SRAM(static random access memory) 등의 메모리 소자를 이용하여 형성된다는 점에 유의한다.

[0034] 비교 회로(112)는, 연속하는 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터를 메모리 회로(111)로부터 판독하고, 판독된 화상 신호(img)의 데이터를 비교하며, 비교 결과에 기초한 신호인 제어 신호(CTL1)를 생성하고, 생성된 제어 신호(CTL1)를 표시 제어 회로(113) 및 선택 회로(115)에 출력한다. 비교 회로(112)에서의 화상 데이터의 비교에 의해, 연속하는 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터가 동화상을 표시하기 위한 데이터인지 또는 정지 화상을 표시하기 위한 데이터인지가 판단된다.

[0035] 동화상이란, 시분할된 복수의 화상을 고속으로 복수의 프레임 기간으로 스위칭함으로써 인간의 눈에 의해 움직이는 화상으로서 인식되는 화상을 말한다는 점에 유의한다.

[0036] 대조적으로, 정지 화상이란, 동화상 및 부분 동화상과는 달리, 시분할된 복수의 화상이 고속으로 복수의 프레임

기간으로 스위칭되더라도, 연속하는 프레임 기간, 예를 들어, 제n 프레임 기간(n은 자연수)과 제(n+1) 프레임 기간 동안에 변하지 않는 화상으로서 인간의 눈에 의해 인식되는 화상을 말한다.

[0037] 전술된 예에서는, 비교 회로(112)가 연속하는 프레임 기간의 화상에 대응하는 화상 신호의 데이터를 비교함으로써, 비교된 화상이 동화상인지 또는 정지 화상인지가 판단되는 구조를 설명하였다. 그러나, 상기 예로 한정되지 않고, 본 실시형태의 액정 표시 장치는, 미리 동화상인지 또는 정지 화상인지가 결정되어 있는 화상 신호(img)가 외부로부터 입력되는 구조를 가질 수도 있다.

[0038] 선택 회로(115)는, 제어 신호(CTL1)에 기초하여, 메모리 회로(111)에 저장된 화상 신호(img)의 데이터를 판독하고, 판독된 화상 신호(img)의 데이터를 테이터 신호로서 선택적으로 출력하는 기능을 가진다. 선택 회로(115)의 동작은 비교 회로(112)의 검출 기준에 기초하여 설정될 수도 있다는 점에 유의한다.

[0039] 선택 회로(115)는, 예를 들어, 복수의 스위치를 포함한 회로에 의해 구성된다. 스위치로서, 예를 들어, 트랜지스터가 이용될 수 있다.

[0040] 보정 회로(102)는, 온도 검출 회로(131), 계수 회로(132), 및 계수값 비교 회로(133)를 포함한다.

[0041] 온도 검출 회로(131)는 검출된 온도에 따라 온도 데이터 신호(TML)를 생성하고, 나아가, 온도 데이터 신호(TML)를 이용하여 기준 계수값의 데이터 신호(CNT1)를 생성하는 기능을 가진다. 온도 검출 회로(131)는, 예를 들어, 온도 데이터 신호(TML)를 생성하는 온도 센서를 포함한다. 온도 센서로서, 열전대(thermocouple), 저항 온도 센서, 서미스터, IC 온도 센서, 자기 온도 센서, 적외선 온도 센서 등을 이용할 수 있다. 온도 센서로서, 트랜지스터의 온도 특성을 이용한 센서 등을 이용할 수도 있다.

[0042] 계수 회로(132)는 비교 회로(112)에서 정지 화상이라고 판단된 화상에 대응하는 연속하는 프레임 기간의 수를 계수하여, 그 계수값의 데이터 신호(CNT2)를 출력하는 기능을 가진다.

[0043] 계수값 비교 회로(133)는, 계수 회로(132)로부터의 계수값의 데이터 신호(CNT2)를 기준 계수값의 데이터(CNT1)와 비교하고, 비교 결과에 기초하여 제어 신호(CTL2)를 생성하며, 생성된 제어 신호(CTL2)를 표시 제어 회로(113)에 출력하는 기능을 가진다.

[0044] 기준 계수값은 온도 센서에 의해 생성된 온도 데이터(TML)에 기초하여 설정될 수 있다. 예를 들어, 각 온도에 대응하는 계수값이 설정되고, 온도에 대응하는 계수값의 보정 데이터 테이블이 작성된다. 온도 검출 회로(131)는, 온도 센서에 의해 생성된 온도 데이터(TML)에 대응하는 계수값의 데이터를 데이터 테이블로부터 판독하고, 판독된 계수값의 데이터를 기준 계수값의 데이터 신호(CNT1)의 데이터로서 이용한다. 따라서, 구동 회로부(121)를 동작시키기 위한 신호 또는 전압(화상 신호(img), 스타트 신호(SP), 클록 신호(CK), 및 전원 전압(Vp))을 출력하는 타이밍이 온도에 따라 보정될 수 있다. 또한, 본 실시형태의 액정 표시 장치는, 계수값의 보정 데이터 테이블이 별도 메모리 등에 데이터로서 저장되고, 필요하다면 저장된 보정 데이터 테이블이 적절히 판독되어 이용되는 구조를 가질 수도 있다.

[0045] 보정 회로(102)의 구조는, 온도 검출 회로(131)에 의해 온도가 검출될 수 있고 검출된 온도의 데이터를 이용하여 제어 신호(CTL2)가 생성될 수 있는 한, 도 2에 나타낸 구조로 한정되지 않는다.

[0046] 하기에는, 화상 처리 회로(101) 및 보정 회로(102)의 동작의 예가 제시된다.

[0047] 우선, 화상 신호(img)가 메모리 회로(111)에 입력된다.

[0048] 메모리 회로(111)는 입력 화상 신호(img)의 데이터를 순차적으로 저장하고, 저장된 화상 신호(img)의 데이터를 비교 회로(112)에 순차적으로 출력한다.

[0049] 또한, 비교 회로(112)는, 메모리 회로(111)로부터 입력되며 연속하는 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터를 비교하고, 비교된 화상 신호(img)의 데이터 사이에 차이가 있는지를 조사하고, 비교된 화상 신호(img)의 데이터에 대응하는 화상이 동화상인지 또는 정지 화상인지를 판단한다.

[0050] 예를 들어, 연속하는 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터 사이에서 차이가 검출된 경우, 비교 회로(112)는, 비교된 화상 신호(img)의 데이터에 대응하는 화상을 동화상이라고 판단한 다음, 비교 결과에 기초한 제어 신호(CTL1)를 표시 제어 회로(113) 및 선택 회로(115)에 출력한다.

[0051] 반면, 연속하는 프레임 기간의 화상에 대응하는 화상 신호(img)의 데이터 사이에서 차이가 검출되지 않은 경우, 비교 회로(112)는, 비교된 화상 신호(img)의 데이터에 대응하는 화상을 정지 화상이라고 판단한 다음, 비교 결

과에 기초한 제어 신호(CTL1)를 표시 제어 회로(113) 및 선택 회로(115)에 출력한다.

[0052] 비교 회로(112)에 의해 검출된 차이가 소정 값을 초과한 경우 차이가 검출되었다고 판단될 수 있도록, 차이의 검출 기준이 설정될 수도 있다는 점에 유의한다.

[0053] 또한, 선택 회로(115)는, 비교 회로(112)로부터 입력된 제어 신호(CTL1)에 기초하여 메모리 회로(111)로부터 화상 신호(img)의 데이터를 판독하고, 판독된 화상 신호(img)의 데이터를 데이터 신호로서 표시 제어 회로(113)에 출력한다.

[0054] 예를 들어, 비교 회로(112)에서 비교된 화상 신호(img)의 데이터에 대응하는 화상이 동화상이라고 판단된 경우, 선택 회로(115)는, 메모리 회로(111)로부터 화상 신호(img)의 데이터를 판독하고, 판독된 화상 신호(img)의 데이터를 데이터 신호로서 표시 제어 회로(113)에 출력한다.

[0055] 대조적으로, 비교 회로(112)에서 비교된 화상 신호(img)의 데이터에 대응하는 화상이 정지 화상이라고 판단된 경우, 선택 회로(115)는 표시 제어 회로(113)로의 화상 신호(img)의 출력을 중단한다.

[0056] 온도 검출 회로(131)는 액정 표시 장치의 온도를 검출하고, 검출된 온도에 대응하는 온도 데이터 신호(TML)를 생성한다. 또한, 온도 검출 회로(131)는, 온도 검출 회로(131)에 의해 생성된 온도 데이터(TML)에 대응하는 계수값의 데이터를 데이터 테이블로부터 판독하고, 판독된 계수값의 데이터를 기준 계수값의 데이터 신호(CNT1)로서 계수값 비교 회로(133)에 출력한다.

[0057] 계수 회로(132)는, 정지 화상이라고 판단된 화상에 대응하는 프레임 기간의 수를 계수하고, 계수값의 데이터를 계수값의 데이터 신호(CNT2)로서 계수값 비교 회로(133)에 출력한다.

[0058] 계수값 비교 회로(133)는, 계수 회로(132)로부터의 계수값의 데이터 신호(CNT2)의 데이터를 기준 계수값의 데이터 신호(CNT1)와 비교하고, 비교 결과에 기초하여 제어 신호(CTL2)를 생성하며, 생성된 제어 신호(CTL2)를 표시 제어 회로(113)에 출력한다. 또한, 계수 회로(132)의 계수값이 기준 계수값에 도달하면, 화상 신호(img), 스타트 신호(SP), 클록 신호(CK), 및 전원 전압(Vp)이 제어 신호(CTL2)에 따라 표시 제어 회로(113)로부터 구동 회로부(121)에 출력된다. 이것은 화상 처리 회로(101) 및 보정 회로(102)의 동작 예이다.

[0059] 도 1에 나타낸 액정 표시 장치에는, 표시 패널(120)에 광을 공급하는 광원부(130)가 제공된다.

[0060] 광원부(130)는 표시 패널(120)에 광을 공급하는 기능을 가지며, 예를 들어, 광원 제어 회로와 광원을 포함한다. 광원은, 액정 표시 장치의 용도에 따라 선택된 구성요소들의 조합을 포함할 수도 있다. 예를 들어, 폴 컬러의 화상을 표시하는 경우, 삼원색의 광을 방출할 수 있는 광원이 광원으로서 이용될 수 있다. 대안으로서, 예를 들어, 백색광을 방출하는 발광 소자(예를 들어, LED)가 광원으로서 이용될 수 있다. 도 1에 나타낸 바와 같이, 광원부(130)의 점등 상태는 표시 제어 회로(113)에 의해 제어될 수 있다. 광원부(130)는 반드시 표시 제어 회로(113)에 의해 제어될 필요는 없지만, 표시 제어 회로(113)에 의한 광원부(130)의 제어는, 필요에 따라 광원을 소등시킬 수 있다; 따라서, 전력 소비가 저감될 수 있다. 예를 들어, 광원으로서 백라이트 또는 사이드 라이트가 이용될 수 있다.

[0061] 그 다음, 표시 패널(120)의 구조를 이하에 설명한다.

[0062] 구동 회로(121A)는, 화상 신호(img)가 출력되는 화소(123)를 선택하는 주사선(124)을 제어하는 주사선 구동 회로의 기능을 가진다. 단자부(126)를 통해, 전원 전압(Vp), 스타트 신호(GSP), 및 클록 신호(GCK)가 구동 회로(121A)에 선택적으로 입력된다.

[0063] 구동 회로(121B)는, 화소(123)에 화상 신호(img)가 출력되는지를 제어하는 신호선 구동 회로의 기능을 가진다. 단자부(126)를 통해, 화상 신호(img), 전원 전압(Vp), 스타트 신호(SSP), 및 클록 신호(SCK)가 구동 회로(121B)에 선택적으로 입력된다.

[0064] 예를 들어, 구동 회로(121A) 및 구동 회로(121B)는, 예를 들어, 시프트 레지스터를 포함하는 구조를 가질 수 있다; 시프트 레지스터는, 예를 들어, 트랜지스터를 이용하여 형성될 수 있다.

[0065] 복수의 화소(123)가 매트릭스로 제공되고, 주사선(124) 및 화상 신호선(125)에 의해 둘리싸인다. 도 1의 액정 표시 장치에서, 주사선(124)은 구동 회로(121A)로부터 연장되고, 화상 신호선(125)은 구동 회로(121B)로부터 연장된다.

[0066] 또한, 화소(123)의 회로 구조의 예를 이하에서 설명한다.

- [0067] 화소(123)는, 트랜지스터(214), 용량 소자(210), 및 액정 소자(215)를 포함한다.

- [0068] 본 명세서에서, 트랜지스터란, 적어도 소스, 드레인, 및 게이트를 포함하는 전계 효과 트랜지스터를 말한다는 점에 유의한다.

- [0069] 소스란, 소스 전극 및 소스 배선의 전부 또는 그 일부를 의미한다. 일부 경우에는 소스 전극과 소스 배선 간의 구별 없이 소스 전극 및 소스 배선의 양쪽 모두의 기능을 갖는 도전층을 소스라고 말한다.

- [0070] 드레인이란, 드레인 전극 및 드레인 배선의 전부 또는 그 일부를 의미한다. 일부 경우에는 드레인 전극과 드레인 배선 간의 구별 없이 드레인 전극 및 드레인 배선의 양쪽 모두의 기능을 갖는 도전층을 드레인이라고 말한다.

- [0071] 게이트란, 게이트 전극 및 게이트 배선의 전부 또는 그 일부를 의미한다. 일부 경우에는 게이트 전극과 게이트 배선 간의 구별 없이 게이트 전극 및 게이트 배선의 양쪽 모두의 기능을 갖는 도전층을 게이트라고 말한다.

- [0072] 또한, 트랜지스터의 소스 및 드레인은 트랜지스터의 구조, 동작 조건 등에 따라 서로 바뀔 수도 있다; 따라서, 어느 것이 소스인지 또는 드레인인지를 정의하는 것은 어렵다. 따라서, 본 서류(명세서, 특히 청구의 범위 또는 도면 등)에서는, 일부 경우에, 이를 중 하나는 소스 및 드레인 중 하나라고 언급되는 반면, 다른 쪽은 소스 및 드레인 중 다른 하나라고 언급된다.

- [0073] 트랜지스터(214)의 소스 및 드레인 중 하나는 화상 신호선(125)에 전기적으로 접속되고, 트랜지스터(214)의 게이트는 주사선(124)에 전기적으로 접속된다.

- [0074] 액정 소자(215)는 제1 단자와 제2 단자를 가진다. 제1 단자는 트랜지스터(214)의 소스 및 드레인 중 다른 하나에 전기적으로 접속된다. 액정 소자(215)는, 제1 단자의 일부 또는 전부로서 기능하는 화소 전극과, 제2 단자의 일부 또는 전부로서 기능하는 공통 전극과, 화소 전극과 공통 전극 사이에서 전압의 인가에 의해 광의 투과율이 변하는 액정층을 포함할 수 있다.

- [0075] 화소 전극은 가시광을 투과하는 영역과 가시광을 반사하는 영역을 포함하는 구조를 가질 수 있다는 점에 유의한다. 화소 전극에서 가시광을 투과하는 영역은, 광원부(130)로부터 입사된 광을 투과시키고, 화소 전극에서 가시광을 반사하는 영역은 액정층을 통해 입사된 광을 반사한다.

- [0076] 화소 전극은 제1 기판 위에 제공되는 것이 바람직하고, 공통 전극은 제2 기판 위에 제공되는 것이 바람직하다. 여기서, 공통 전극이 제공된 제2 기판은 공통 접속부를 통해 제1 기판에 전기적으로 접속된다. 예를 들어, 공통 접속부는, 절연성 구체(insulating sphere)에 금속막이 피복된 도전 입자를 이용하여 형성될 수 있다. 제1 기판과 제2 기판의 사이에는 복수의 공통 접속부가 제공될 수도 있다.

- [0077] 화소 전극과 공통 전극의 형상은, 다양한 개구 패턴을 포함하는 형상일 수도 있다.

- [0078] 액정층에 이용될 수 있는 액정의 예로서는, 네마틱 액정(nematic liquid crystal), 콜레스테릭 액정(cholesteric liquid crystal), 스멕틱 액정(smectic liquid crystal), 디스크오틱 액정(discotic liquid crystal), 써모트로픽 액정(thermotropic liquid crystal), 리오토로픽 액정(lyotropic liquid crystal), 저분자 액정, 고분자 분산형 액정(PDLC), 강유전 액정, 반강유전 액정, 주쇄형 액정(main-chain liquid crystal), 측쇄형 고분자 액정(side-chain high-molecular liquid crystal), 또는 바나나형 액정(banana-shaped liquid crystal) 등이 있다.

- [0079] 액정층에 이용되는 액정 재료의 저항은,  $1 \times 10^{12} \Omega \cdot \text{cm}$  이상, 바람직하게는  $1 \times 10^{13} \Omega \cdot \text{cm}$  이상, 더욱 바람직하게는  $1 \times 10^{14} \Omega \cdot \text{cm}$  이상이다. 본 명세서에서의 저항은 20°C에서 측정된 것임에 유의한다. 상기 액정 재료를 이용하여 액정 표시 장치가 형성되는 경우, 액정 소자로서 역할하는 부분의 저항은, 배향막 또는 밀봉재 등으로부터 액정층 내로 혼입되는 불순물 때문에, 일부 경우에  $1 \times 10^{11} \Omega \cdot \text{cm}$  이상, 또는 나아가  $1 \times 10^{12} \Omega \cdot \text{cm}$  이상이 될 수도 있다.

- [0080] 액정 재료의 저항이 커짐에 따라, 액정층의 리크 전류가 저감될 수 있고, 표시 기간에서 액정 소자에 인가되는 전압의 경시적 저하가 저감될 수 있다. 그 결과, 화상 데이터의 1회 기입에 대응하는 화소(123)의 표시 기간이 연장될 수 있어서, 화소(123) 내에 화상 데이터를 기입하는 빈도가 감소될 수 있고, 이것은 액정 표시 장치의 전력 소비의 저감으로 이어진다.

- [0081] 액정 소자에 이용될 수 있는 액정 구동 방법의 예로서 다음과 같은 모드들이 있다: TN(twisted nematic) 모드,

STN(super twisted nematic) 모드, OCB(optically compensated birefringence) 모드, ECB(electrically controlled birefringence) 모드, FLC(ferroelectric liquid crystal) 모드, AFLC(antiferroelectric liquid crystal) 모드, PDLC(polymer dispersed liquid crystal) 모드, PNLC(polymer network liquid crystal) 모드, 게스트-호스트 모드 등.

[0082] 용량 소자(210)는 제1 단자와 제2 단자를 가진다. 제1 단자는 트랜지스터(214)의 소스 및 드레인 중 다른 하나에 전기적으로 접속된다. 용량 소자(210)는, 축적 용량 소자의 기능을 가지며, 제1 단자의 일부 또는 전부로서 기능하는 제1 전극과, 제2 단자의 일부 또는 전부로서 기능하는 제2 전극과, 제1 전극과 제2 전극 사이의 전압 인가에 의해 전하가 축적되는 유전체충을 포함할 수 있다. 용량 소자(210)의 용량은 트랜지스터(214)의 오프 전류를 고려하여 설정될 수도 있다. 본 실시형태에서는, 각 화소에서 액정 소자(215)의 용량(액정 용량이라고도 함)의 1/3이하, 바람직하게는 1/5이하의 용량을 갖는 축적 용량 소자가 제공되면 충분하다. 또한, 용량 소자(210)가 반드시 제공될 필요는 없고, 용량 소자(210)가 없는 구조가 이용될 수도 있다. 용량 소자(210)가 없으면, 화소(123)의 개구율(aperture ratio)이 증가될 수 있다.

[0083] 또한, 본 실시형태의 액정 표시 장치는, 도 1에 나타낸 바와 같은 트랜지스터(127)를 포함하는 구조를 가질 수 있다.

[0084] 트랜지스터(127)는 표시 제어 회로(113)의 제어하에 온 또는 오프됨으로써, 공통 전위(Vcom)를 액정 소자(215)의 공통 전극에 공급할 것인지를 제어하는 제어 트랜지스터로서 기능한다. 트랜지스터(127)의 소스 및 드레인 중 하나에는 공통 전위(Vcom)가 입력되고 트랜지스터(127)의 게이트에는 표시 제어 회로(113)로부터 제어 신호가 입력된다. 트랜지스터(127)의 소스 및 드레인 중 다른 하나는 액정 소자(215)의 제2 단자에 전기적으로 접속된다. 트랜지스터(127)는, 구동 회로부(121) 또는 화소부(122)와 동일한 기판 위에, 또는 상이한 기판 위에 형성될 수도 있다는 점에 유의한다. 온 또는 오프됨으로써, 트랜지스터(127)는 공통 전위(Vcom)를 용량 소자(210)의 제2 단자에 출력할지를 제어한다.

[0085] 공통 전위(Vcom)는 화상 신호(img)의 전위에 관하여 설정되는 전위로서, 예를 들어, 접지 전위일 수도 있다. 공통 전위(Vcom)는, 예를 들어, 외부 장치로부터 입력된다.

[0086] 여기서는, 본 실시형태의 액정 표시 장치의 트랜지스터(예를 들어, 표시 패널의 트랜지스터)로서 이용될 수 있는 트랜지스터를 설명한다.

[0087] 본 실시형태의 액정 표시 장치에 이용될 수 있는 트랜지스터로서, 예를 들어, 채널 형성층으로서의 기능을 갖는 산화물 반도체층을 포함한 트랜지스터가 이용될 수 있다. 트랜지스터의 채널 형성층의 기능을 갖는 산화물 반도체층은, n형 불순물인 수소를 제거하고 산화물 반도체의 주성분 이외의 불순물이 가능한 한 내부에 포함하지 않도록 산화물 반도체층을 고순도화함으로써 얻어지는 진성(i형) 또는 실질적으로 진성인 반도체층이다. 즉, 본 실시형태에서 설명된 산화물 반도체층을 포함하는 트랜지스터는, 산화물 반도체층에 불순물을 첨가하는 것이 아니라 수소나 물 등의 불순물을 가능한 한 많이 제거하여 산화물 반도체층을 고순도화함으로써 산화물 반도체층이 i형(진성) 또는 i형에 근접하도록 형성된다는 특징을 가진다.

[0088] 고순도화란 다음과 같은 개념들 중 적어도 하나를 의미한다: 산화물 반도체층으로부터 수소를 가능한 한 많이 제거하는 것; 및 산화물 반도체층에 산소를 공급함으로써 산화물 반도체층 내의 산소 결핍에 의해 야기되는 결함을 저감하는 것.

[0089] 산화물 반도체로서, 예를 들어, 4원계 금속 산화물, 3원계 금속 산화물, 또는 2원계 금속 산화물을 이용할 수 있다. 4원계 금속 산화물로서, 예를 들어, In-Sn-Ga-Zn-O계 금속 산화물 등을 이용할 수 있다. 3원계 금속 산화물로서, 예를 들어, In-Ga-Zn-O계 금속 산화물, In-Sn-Zn-O계 금속 산화물, In-Al-Zn-O계 금속 산화물, Sn-Ga-Zn-O계 금속 산화물, Al-Ga-Zn-O계 금속 산화물, 또는 Sn-Al-Zn-O계 금속 산화물 등을 이용할 수 있다. 2원계 금속 산화물로서, In-Zn-O계 금속 산화물, Sn-Zn-O계 금속 산화물, Al-Zn-O계 금속 산화물, Zn-Mg-O계 금속 산화물, Sn-Mg-O계 금속 산화물, In-Mg-O계 금속 산화물, 또는 In-Sn-O계 금속 산화물을 이용할 수 있다. 또한, 산화물 반도체로서, In-O계 금속 산화물, Sn-O계 금속 산화물, Zn-O계 금속 산화물 등을 이용할 수 있다. 산화물 반도체로서 이용될 수 있는 금속 산화물은  $\text{SiO}_2$ 를 포함할 수도 있다.

[0090] 산화물 반도체로서,  $\text{InMO}_3(\text{ZnO})_m$  ( $m>0$ )로 표기되는 재료를 이용할 수 있다. 여기서, M은, Ga, Al, Mn 및 Co로부터 선택된 하나 이상의 금속 원소를 나타낸다. 예를 들어, Ga, Ga 및 Al, Ga 및 Mn, Ga 및 Co 등이 M으로서 주어질 수 있다. M으로서 Ga가 포함되는  $\text{InMO}_3(\text{ZnO})_m$  ( $m>0$ )로 표기되는 조성식의 산화물 반도체를 In-Ga-Zn-O

산화물 반도체라고 부른다.

[0091] 또한, 산화물 반도체층으로서 이용되는 산화물 반도체의 밴드 갭은 2 eV이상, 바람직하게는 2.5 eV이상, 더욱 바람직하게는 3 eV이상으로서, 이것은 열적 여기에 의해 발생되는 캐리어수를 무시할만한 수준으로 저감한다. 또한, 도너로서 역할하는 수소 등의 불순물의 양이 소정량 이하로 저감되어, 캐리어 농도가  $1 \times 10^{14}/\text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12}/\text{cm}^3$  이하로 된다. 즉, 산화물 반도체층의 캐리어 농도가 제로 또는 실질적 제로로 저감된다.

[0092] 전술된 산화물 반도체층을 포함하는 트랜지스터에서, 채널폭 1  $\mu\text{m}$ 당 오프 전류 밀도는 매우 작을 수 있다; 예를 들어, 오프 전류 밀도는  $10 \text{ aA}/\mu\text{m}$  ( $1 \times 10^{-17} \text{ A}/\mu\text{m}$ ) 이하, 바람직하게는  $1 \text{ aA}/\mu\text{m}$  ( $1 \times 10^{-18} \text{ A}/\mu\text{m}$ ) 이하, 더욱 바람직하게는  $10 \text{ zA}/\mu\text{m}$  ( $1 \times 10^{-20} \text{ A}/\mu\text{m}$ ) 이하, 더욱 더 바람직하게는,  $1 \text{ zA}/\mu\text{m}$  ( $1 \times 10^{-21} \text{ A}/\mu\text{m}$ ) 이하일 수 있다.

[0093] 예를 들어, 전술된 산화물 반도체층을 포함하는 트랜지스터가 트랜지스터(214)로서 이용되는 경우, 화상 데이터의 1회 기입에 대응하는 화상의 표시 기간을 길게 할 수 있다. 따라서, 화상 데이터의 기입 동작들 사이의 간격을 길게 할 수 있다. 예를 들어, 화상 데이터의 기입 간격은, 10초 이상, 바람직하게는 30초 이상, 더욱 바람직하게는 1분 이상으로 증가될 수 있다. 화상 데이터의 기입 동작들 사이의 간격이 길어질수록, 전력 소비가 더욱 저감될 수 있다.

[0094] 그 다음, 도 1에 나타낸 액정 표시 장치의 동작예를 도 3을 참조하여 설명한다. 도 3은 본 실시형태에서의 액정 표시 장치의 동작 예의 타이밍도로서, 전원 전압(V<sub>p</sub>), 클록 신호(GCK), 스타트 신호(GSP), 클록 신호(SCK), 스타트 신호(SSP), 화상 신호선(125)의 전위(V125로 도시), 액정 소자(215)의 화소 전극의 전위(V<sub>pe</sub>로 도시), 트랜지스터(127)의 게이트의 전위(V<sub>g127</sub>로 도시), 트랜지스터(127)의 소스 및 드레인 중 다른 하나의 전위(V<sub>a127</sub>로 도시), 및 액정 소자(215)의 공통 전극의 전위(V<sub>ce</sub>로 도시)의 과정을 도시하고 있다. 도 3의 타이밍도에서, 스타트 신호(GSP)는 수직 동기 주파수에 대응하는 펄스 신호이며, 스타트 신호(SSP)는 1 게이트 선택 기간에 대응하는 펄스 신호이다. 또한, 도 3의 타이밍도에서 클록 신호(GCK) 및 클록 신호(SCK)는, 편의상, 단순한 구형파(rectangular wave)이다.

[0095] 도 1에 나타낸 액정 표시 장치의 동작의 예에서, 기간(411)의 동작 및 기간(412)의 동작을 고려할 수 있다. 기간(411)은 동화상을 표시하기 위한 화상 신호를 기입하는 프레임 기간이고, 기간(412)은 정지 화상을 표시하는 프레임 기간이다. 각 기간의 동작의 예를 이하에서 설명한다. 동화상을 표시하기 위한 모드는 동화상 표시 모드라 하고, 정지 화상을 표시하기 위한 모드는 정지 화상 모드라 한다. 정지 화상 모드는 또한, 동화상의 일부를 정지 화상으로서 표시하는 모드(간이 동화상 재생 모드라고도 함)를 포함한다.

[0096] 기간(411)에서, 화상 신호(img), 전원 전압(V<sub>p</sub>), 스타트 신호(GSP), 스타트 신호(SSP), 클록 신호(GCK), 클록 신호(SCK), 제어 신호(CTL1), 및 제어 신호(CTL2)가 표시 제어 회로(113)에 입력된다. 제어 신호(CTL1) 및 제어 신호(CTL2)에 기초하여, 표시 제어 회로(113)는, 입력 전원 전압(V<sub>p</sub>), 스타트 신호(GSP), 및 클록 신호(GCK)를 구동 회로(121A)에 출력하고, 화상 신호(img), 전원 전압(V<sub>p</sub>), 스타트 신호(SSP), 및 클록 신호(SCK)를 구동 회로(121B)에 출력한다. 또한, 기간(411)에서, 표시 제어 회로(113)는 트랜지스터(127)의 게이트에 트랜지스터(127)를 온으로 하는 제어 신호(CTL127)를 출력한다. 그러면, 트랜지스터(127)가 온으로 되고, 공통 전극의 전위가 공통 전위(V<sub>com</sub>)의 전위와 동등하게 된다.

[0097] 또한, 구동 회로(121A)는 입력 스타트 신호(GSP) 및 클록 신호(GCK)에 응답하여 동작을 개시하고, 주사선(124)에 주사 신호를 출력한다. 구동 회로(121B)는 입력 스타트 신호(SSP) 및 클록 신호(SCK)에 응답하여 동작을 개시하고, 화상 신호선(125)에 화상 신호(img)를 출력한다.

[0098] 또한, 화소(123)에서, 트랜지스터(214)는 주사선(124)의 전위에 따라 온 또는 오프로 된다. 트랜지스터(214)가 온일 때, 화소 전극의 전위는 화상 신호선(125)의 전위와 동등하게 된다. 액정 소자(215)의 광 투과율은 화소 전극과 공통 전극 사이에 인가되는 전압에 따라 설정된다. 따라서, 화상 신호(img)의 데이터가 화소(123)에 기입되고, 화소(123)는 표시 상태가 된다.

[0099] 기간(412)에서, 표시 제어 회로(113)는, 제어 신호(CTL1) 및 제어 신호(CTL2)에 기초하여, 구동 회로(121A)로의 전원 전압(V<sub>p</sub>), 스타트 신호(GSP), 및 클록 신호(GCK)의 출력을 순차적으로 중단하고, 구동 회로(121B)로의 전원 전압(V<sub>p</sub>), 스타트 신호(SSP), 및 클록 신호(SCK)의 출력을 순차적으로 중단한다. 기간(412)에서, 구동 회로(121A)로의 전원 전압(V<sub>p</sub>), 스타트 신호(GSP), 및 클록 신호(GCK)의 출력의 중단이 항상 필요한 것은 아니라는

점에 유의한다. 또한 기간(412)에서, 표시 제어 회로(113)는 트랜지스터(127)의 게이트에 트랜지스터(127)를 오프로 하는 제어 신호(CTL127)를 출력한다. 그러면, 트랜지스터(127)가 오프로 되어, 공통 전극이 부유 상태가 된다.

[0100] 또한, 구동 회로(121B)의 동작이 중단되고 화상 신호(img)가 입력되지 않기 때문에, 화소(123)로의 신호의 출력이 중단된다.

[0101] 또한, 화소(123)에서, 트랜지스터(214)가 주사선(124)의 전위에 따라 오프로 되어, 화소 전극이 부유 상태가 된다. 그러면, 화소(123)는 기간(411)의 표시 상태를 유지하여, 표시된 화상이 정지 화상으로서 유지된다.

[0102] 이런 방식으로, 도 1에 나타낸 액정 표시 장치에서는, 기간(412)에서 액정 소자(215)의 화소 전극 및 공통 전극을 부유 상태로 만들었으므로써, 액정 소자(215)의 화소 전극과 공통 전극 사이에 추가적으로 전압을 인가하지 않고 복수의 연속하는 프레임 기간에서 정지 화상의 표시가 유지될 수 있다.

[0103] 도 1에 나타낸 액정 표시 장치의 트랜지스터로서, 작은 오프 전류를 갖는 트랜지스터가 이용된다; 따라서, 액정 소자의 화소 전극과 공통 전극 사이에 인가되는 전압이 시간의 경과에 따라 감소되는 현상의 발생이 방지될 수 있다. 따라서, 정지 화상을 표시하는 기간에서 구동 회로를 동작시키기 위한 신호 또는 전압의 구동 회로로의 공급이 중단될 수 있음으로써, 전력 소비가 저감될 수 있다.

[0104] 또한, 제1 화상 스위칭 기간(도 3의 기간(413))과 제2 화상 스위칭 기간(도 3의 기간(414))에서의 표시 제어 회로(113)의 동작예를, 도 4a 및 도 4b를 참조하여 설명한다. 도 4a 및 도 4b는, 도 1에 나타낸 액정 표시 장치의 동작 예의 타이밍도로서, 전원 전압(Vp), 스타트 신호(GSP), 클록 신호(GCK), 및 트랜지스터(127)를 제어하기 위한 제어 신호(CTL127)의 파형 예를 도시하고 있다.

[0105] 우선, 기간(413)에서, 표시 제어 회로(113)는 스타트 신호(GSP)의 출력을 중단한다(도 4a의 E1, 제1 스텝). 시프트 레지스터의 최종단으로부터 펄스가 출력된 후, 클록 신호(GCK)의 출력이 중단된다(도 4a의 E2, 제2 스텝). 그 다음, 전원 전압(Vp)의 출력이 중단된다(도 4a의 E3, 제3 스텝). 그 다음, 제어 신호(CTL127)의 전위가 트랜지스터(127)를 오프하도록 설정된다(도 4a의 E4, 제4 스텝).

[0106] 전술된 바와 같이, 구동 회로(121A)의 오동작을 야기하지 않고, 구동 회로(121A)의 동작, 예를 들어, 구동 회로(121A)를 동작시키기 위한 신호 또는 전압의 구동 회로(121A)로의 출력이 중단될 수 있다. 동화상으로부터 정지 화상으로 표시가 스위칭될 때의 오동작은 노이즈를 발생시키며, 노이즈 때문에 화상 신호의 파형이 변동한다. 구동 회로의 오동작을 방지하면, 화상 열화를 적게 하여 정지 화상을 표시할 수 있다.

[0107] 전술된 방법으로 한정되지 않고, 구동 회로(121B)를 동작시키기 위한 신호 또는 전압(전원 전압(Vp), 스타트 신호(SSP), 및 클록 신호(SCK))의 구동 회로(121B)로의 출력이, 구동 회로(121A)의 경우와 마찬가지로 중단될 수 있다.

[0108] 또한, 기간(414)에서, 표시 제어 회로(113)는 제어 신호(CTL127)의 전위를 트랜지스터(127)를 온으로 하는 전위에 설정한다(도 4b의 S1, 제1 스텝). 그 다음, 전원 전압(Vp)의 출력이 재개된다(도 4b의 S2, 제2 스텝). 그 다음, 클록 신호가 입력되는 배선의 전위가 클록 신호(GCK)의 하이 레벨의 전위와 동등한 값으로 설정된 다음, 클록 신호(GCK)의 출력이 재개된다(도 4b의 S3, 제3 스텝). 그 다음, 스타트 신호(GSP)의 출력이 재개된다(도 4b의 S4, 제4 스텝).

[0109] 전술된 바와 같은 방식으로, 오동작을 야기하지 않고, 구동 회로(121A)의 동작, 예를 들어, 구동 회로(121A)를 동작시키기 위한 신호 또는 전압의 구동 회로(121A)로의 출력이 재개될 수 있다.

[0110] 전술된 방법으로 한정되지 않고, 구동 회로(121B)를 동작시키기 위한 신호 또는 전압(전원 전압(Vp), 스타트 신호(SSP), 및 클록 신호(SCK))의 구동 회로(121B)로의 출력이, 구동 회로(121A)의 경우와 마찬가지로 재개될 수 있다.

[0111] 도 5는 동화상을 표시하는 기간(601) 또는 정지 화상을 표시하는 기간(602)에서 프레임 기간마다의 화상 신호의 기입 빈도를 도시한다. 도 5는, 프레임 기간마다의 화상 신호의 기입 빈도를 도시하는 개략도로서, "W"는 화상 신호를 기입하는 기간을 나타내고, "H"는 화상 신호를 유지하는 기간을 나타내며, 기간(603)은 단위 프레임 기간을 나타낸다.

[0112] 본 실시형태의 액정 표시 장치의 구조에서, 기간(602)에서 표시되는 정지 화상의 화상 신호는 기간(604)에서 기입되고, 기간(604)에서 기입된 화상 신호는 기간(602)의 다른 기간에서 유지된다.

- [0113] 또한, 도 1에 나타낸 액정 표시 장치의 온도가 변동하는 경우를 이하에 설명한다.

- [0114] 본 실시형태의 액정 표시 장치에 이용되는 트랜지스터에서, 전기 특성은 온도에 따라 변동한다. 온도에 따른 트랜지스터의 전기 특성의 변동을 이하에 설명한다.

- [0115] 트랜지스터가 형성된 기판의 온도가 40°C, 85°C, 150°C, 및 200°C로 고정되었고, 1 V 및 10 V인 2개의 드레인 전압 조건 하에서 게이트 전위(VG라고도 함)를 -10 V 내지 10 V로 변화시키면서 트랜지스터의 VG-ID 특성을 얻었다. "ID"란, 소스와 드레인 사이에 흐르는 전류를 말한다는 점에 유의한다. 또한, 측정된 트랜지스터는, 10  $\mu\text{m}$ 의 채널 길이(L), 200  $\mu\text{m}$ 의 채널폭, 및 100 nm의 게이트 절연층의 두께를 가진다.

- [0116] 도 6a는 상기 각각의 온도에서 측정된 트랜지스터의 VG-ID 특성을 도시하고, 도 6b는 도 6a에서 -2 V 내지 2 V의 게이트 전위의 범위의 확대도이다. 도면에서 화살표로 표시된 우단의 곡선은 40°C에서 얻어진 곡선이고; 좌단의 곡선은 200°C에서 얻어진 곡선이며; 그 외의 온도에서 얻어진 곡선들은 이들 사이에 위치해 있다. 도 6a 및 도 6b에 도시된 바와 같이, 온도가 증가함에 따라 컷-오프 전류(VG=0 V일 때의 드레인 전류)는 증가한다; 따라서, 트랜지스터가 오프 상태일 때에도 리크 전류의 발생 등의 문제가 발생한다.

- [0117] 도 7은 트랜지스터를 포함하는 액정 표시 장치에 화상 데이터를 기입한 후의 전압 유지 특성을 도시한다. 도 7은 액정 표시 장치의 화소에 화상 신호(img)의 데이터를 기입한 다음 구동 회로의 동작이 중단된 후의 화소의 휘도의 경시 변화를 도시하며, 여기서, 횡축은 유지 기간(예를 들어, 도 5에서 기간(602))을 나타내며, 종축은 기준치에 대한 화소의 휘도 변화의 퍼센트를 나타낸다. 도 7에서는, 휘도가 증가함에 따라, 화상이 백색에 가까워진다.

- [0118] 도 7에 도시된 바와 같이, 온도가 높아지거나 유지 기간이 길어질 때 화소의 휘도 변화가 증가한다는 것을 알 수 있다. 이것은, 온도 상승이, 화상 신호선과 액정 소자의 사이에 제공된 트랜지스터의 리크 전류를 크게 하 고 액정 소자의 화소 전극의 전위를 변화시키기 때문이다.

- [0119] 이에 대한 대책으로서, 본 실시형태의 액정 표시 장치에서는, 구동 회로부(121)를 동작시키기 위한 신호 및 전 압의 구동 회로부(121)로의 공급의 중단부터 재개까지의 기간의 길이가 액정 표시 장치의 온도에 따라 설정된다. 이것은 트랜지스터의 전기 특성이 온도에 따라 변동하는 경우에도 표시 화상에 미치는 악영향을 저감할 수 있다.

- [0120] 예를 들어, 액정 표시 장치의 온도가 증가함에 따라, 구동 회로부(121)를 동작시키기 위한 신호 및 전압의 구동 회로부(121)로의 공급의 중단부터 재개까지의 기간의 길이가 단축된다. 이것은 화소(123)로의 화상 신호(img)의 데이터의 기입 간격이 짧아지게 한다. 예를 들어, 도 7의 결과에서는, 휘도 변화가 20% 이상일 때, 표시되는 화상의 변화가 현저하게 나타난다. 예를 들어, 60°C에서는, 구동 회로부(121)를 동작시키기 위한 신호 또는 전압의 구동 회로부(121)로의 공급의 중단부터 재개까지의 기간의 길이를, 유지 시간이 180초로 되도록 설정하는 것이 바람직하다. 또한, 85°C에서는, 구동 회로부(121)를 동작시키기 위한 신호 또는 전압의 구동 회로부(121)로의 공급의 중단부터 재개까지의 기간의 길이를, 유지 시간이 60초로 되도록 설정하는 것이 바람직하다. 이런 방식으로, 화상의 휘도 변화에 미치는 온도 변화의 악영향이 저감될 수 있다.

- [0121] 본 실시형태의 액정 표시 장치는, 화상 신호의 기입 빈도를 저감할 수 있다. 따라서, 전력 소비가 저감될 수 있다.

- [0122] 동일한 화상을 복수 회 재기입함으로써 정지 화상을 표시하는 경우, 화상의 기시적인 스위칭은 인간 눈의 피로를 야기할 수도 있다. 본 실시형태의 액정 표시 장치에서는 화상 신호의 기입 빈도가 저감되기 때문에, 야기되는 눈의 피로 수준이 낮게 될 수 있다.

- [0123] 특히, 본 실시형태의 액정 표시 장치에서 작은 오프 전류를 갖는 트랜지스터가 각 화소의 트랜지스터로서 이용되면, 액정 소자 또는 축적 용량 소자에서 전압을 유지하는 기간이 늘어날 수 있다. 그 결과, 화상 신호의 기입 빈도가 저감될 수 있어서, 전력 소비가 저감될 수 있다. 또한, 야기되는 눈의 피로 수준이 낮아질 수 있다.

- [0124] (실시형태 2)

- [0125] 본 실시형태에서는, 상기 실시형태에서 설명된 표시 장치의 주사선 구동 회로 및 신호선 구동 회로에 이용될 수 있는 시프트 레지스터의 예를 설명한다.

- [0126] 본 실시형태의 시프트 레지스터의 구조예를 도 8a 내지 도 8c를 참조하여 설명한다. 도 8a 내지 도 8c는 본 실시형태의 시프트 레지스터의 구조의 예를 나타내는 도면이다.

- [0127] 도 8a의 시프트 레지스터는, 제1 내지 제 $N$  펄스 출력 회로(10\_1 내지 10\_N)( $N$ 은 3 이상의 자연수)를 포함한다.

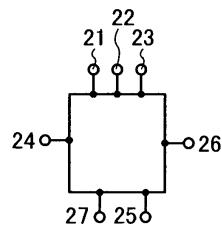

- [0128] 제1 내지 제 $N$  펄스 출력 회로(10\_1 내지 10\_N)의 각각은, 제1 입력 단자(21), 제2 입력 단자(22), 제3 입력 단자(23), 제4 입력 단자(24), 제5 입력 단자(25), 제1 출력 단자(26), 및 제2 출력 단자(27)를 포함한다(도 8b 참조). 펄스 출력 회로들 각각의 제1 입력 단자(21), 제2 입력 단자(22), 및 제3 입력 단자(23)는, 제1 내지 제4 배선(11 내지 14) 중에서 상이한 배선들에 전기적으로 접속되고, 제1 입력 단자(21), 제2 입력 단자(22), 및 제3 입력 단자(23) 각각은 제1 내지 제4 배선(11 내지 14) 중 하나에 전기적으로 접속된다.

- [0129] 도 8a 및 도 8b의 제1 펄스 출력 회로(10\_1)에서, 제1 입력 단자(21)는 제1 배선(11)에 전기적으로 접속되고, 제2 입력 단자(22)는 제2 배선(12)에 전기적으로 접속되며, 제3 입력 단자(23)는 제3 배선(13)에 전기적으로 접속된다.

- [0130] 도 8a 및 도 8b의 제2 펄스 출력 회로(10\_2)에서, 제1 입력 단자(21)는 제2 배선(12)에 전기적으로 접속되고, 제2 입력 단자(22)는 제3 배선(13)에 전기적으로 접속되며, 제3 입력 단자(23)는 제4 배선(14)에 전기적으로 접속된다.

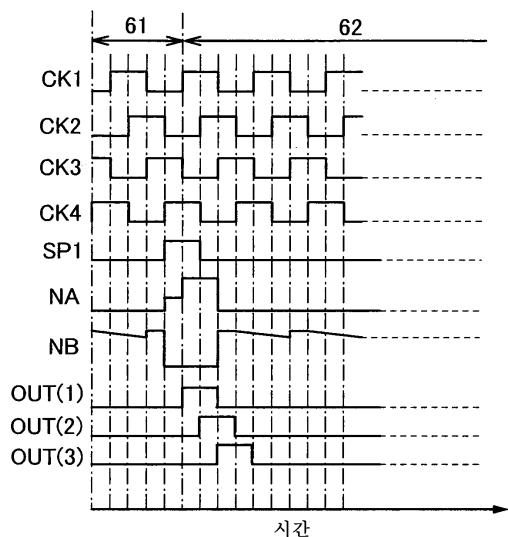

- [0131] 도 8a에 나타낸 시프트 레지스터에서, 제1 클록 신호(CK1)는 제1 배선(11)을 통해 입력되고, 제2 클록 신호(CK2)는 제2 배선(12)을 통해 입력되며, 제3 클록 신호(CK3)는 제3 배선(13)을 통해 입력되고, 제4 클록 신호(CK4)는 제4 배선(14)을 통해 입력된다.

- [0132] 제1 클록 신호(CK1) 내지 제4 클록 신호(CK4) 각각은 하이 레벨과 로우 레벨 사이에서 레벨이 반복적으로 스위칭되는 디지털 신호이다. 제1 내지 제4 클록 신호(CK1 내지 CK4)는 1/4 주기만큼 순차적으로 지연된다. 본 실시형태의 시프트 레지스터에서는, 제1 내지 제4 클록 신호(CK1 내지 CK4)를 이용하여 펄스 출력 회로의 구동이 제어된다.

- [0133] 제1 펄스 출력 회로(10\_1)의 제4 입력 단자(24)는 제5 배선(15)에 전기적으로 접속된다. 본 실시형태의 시프트 레지스터에서는 스타트 신호(SP1)(제1 스타트 펄스)는 제5 배선(15)을 통해 입력된다.

- [0134] 또한, 2단 또는 그 이후 단의 제 $n$  펄스 출력 회로(10\_n)( $n$ 은, 2이상 N이하의 자연수)에는, 전단의 펄스 출력 회로(10\_(n-1))로부터 전단 신호 OUT(n-1)가 입력된다.

- [0135] 또한, 제1 펄스 출력 회로(10\_1)에는, 제1 펄스 출력 회로(10\_1)의 2단 후단인 제3 펄스 출력 회로(10\_3)로부터의 신호가 입력된다; 마찬가지로, 제1 펄스 출력 회로(10\_1)에는, 제1 펄스 출력 회로(10\_1)의 2단 후단인 제(1+2) 펄스 출력 회로(10\_(1+2))로부터 후단 신호 OUT(1+2)(1은 2이상 (N-2)이하의 자연수)가 입력된다.

- [0136] 각 단의 펄스 출력 회로는, 전단 및/또는 후단의 펄스 출력 회로에 제1 출력 신호를 출력하고, 펄스 출력 회로가 전기적으로 접속되어 있는 배선 등에 제2 출력 신호를 출력한다.

- [0137] 예를 들어, 도 8a 및 도 8b의 제1 펄스 출력 회로(10\_1)에서, 제4 입력 단자(24)를 통해 스타트 신호가 입력되고, 제5 입력 단자(25)를 통해 후단 신호(제3 펄스 출력 회로(10\_3)로부터의 제2 출력 신호)가 입력되며, 제1 출력 단자(26)를 통해 제1 출력 신호가 출력되고, 제2 출력 단자(27)를 통해 제2 출력 신호가 출력된다.

- [0138] 제( $N-1$ ) 단의 펄스 출력 회로(10\_(N-1)) 및 제 $N$  단의 펄스 출력 회로(10\_N)에는, 후단 신호 OUT(1+2)가 입력되지 않는다; 따라서, 도 8a에 도시된 시프트 레지스터와 같이, 제6 배선(17)을 통해 제2 스타트 신호(SP2)가 제( $N-1$ ) 단의 펄스 출력 회로(10\_(N-1))에 입력되고, 제7 배선(18)을 통해 제3 스타트 신호(SP3)가 제 $N$  단의 펄스 출력 회로(10\_N)에 입력되는 구조가 이용될 수도 있다. 제2 스타트 신호(SP2) 및 제3 스타트 신호(SP3)로 한정되지 않고, 제2 스타트 신호(SP2) 및 제3 스타트 신호(SP3) 대신에 내부에서 생성된 신호가 이용될 수도 있다. 예를 들어, 화소부의 펄스 출력에 기여하지 않는 제( $N+1$ ) 펄스 출력 회로(10\_(N+1)) 및 제( $N+2$ ) 펄스 출력 회로(10\_(N+2))(더미단의 펄스 출력 회로라고도 함)가 제공되어, 제( $N+1$ ) 펄스 출력 회로(10\_(N+1))로부터의 제1 출력 신호가 제( $N-1$ ) 펄스 출력 회로(10\_(N-1))의 제5 입력 단자(25)에 입력되고, 제( $N+2$ ) 펄스 출력 회로(10\_(N+2))로부터의 제1 출력 신호가 제 $N$  펄스 출력 회로(10\_N)의 제5 입력 단자(25)에 입력될 수도 있다. 대안으로서, 시프트 레지스터에서 발생된 또 다른 신호가 이용되는 구조가 이용될 수 있다.

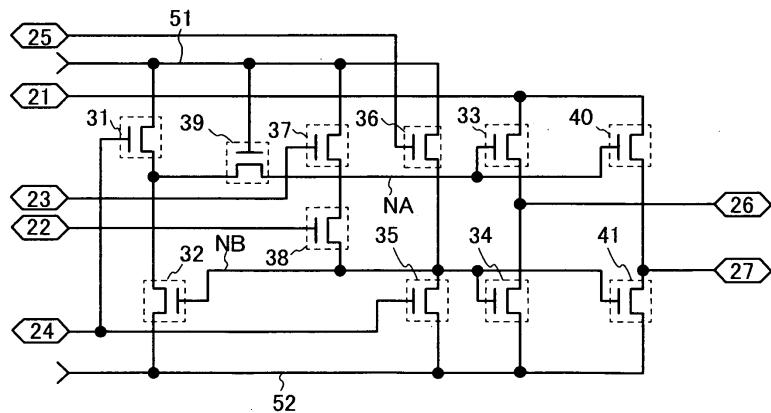

- [0139] 그 다음, 도 8b의 펄스 출력 회로의 회로 구성의 예를 도 8c를 참조하여 설명한다. 도 8c는 도 8b의 펄스 출력 회로의 회로 구성의 예를 도시하는 회로도이다.

- [0140] 도 8c에 도시된 펄스 출력 회로는, 트랜지스터(31), 트랜지스터(32), 트랜지스터(33), 트랜지스터(34), 트랜지스터(35), 트랜지스터(36), 트랜지스터(37), 트랜지스터(38), 트랜지스터(39), 트랜지스터(40), 및 트랜지스터

(41)를 포함한다.

- [0141] 트랜지스터(31)의 소스 및 드레인 중 하나는 전원선(51)에 전기적으로 접속되고, 그 게이트는 제4 입력 단자(24)에 전기적으로 접속된다.

- [0142] 트랜지스터(32)의 소스 및 드레인 중 하나는 전원선(52)에 전기적으로 접속되고, 트랜지스터(32)의 소스 및 드레인 중 다른 하나는 트랜지스터(31)의 소스 및 드레인 중 다른 하나에 전기적으로 접속된다.

- [0143] 트랜지스터(33)의 소스 및 드레인 중 하나는 제1 입력 단자(21)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 제1 출력 단자(26)에 전기적으로 접속된다.

- [0144] 트랜지스터(34)의 소스 및 드레인 중 하나는 전원선(52)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 제1 출력 단자(26)에 전기적으로 접속되며, 그 게이트는 트랜지스터(32)의 게이트에 전기적으로 접속된다.

- [0145] 트랜지스터(35)의 소스 및 드레인 중 하나는 전원선(52)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 트랜지스터(32)의 게이트에 전기적으로 접속되며, 그 게이트는 제4 입력 단자(24)에 전기적으로 접속된다.

- [0146] 트랜지스터(36)의 소스 및 드레인 중 하나는 전원선(51)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 트랜지스터(32)의 게이트에 전기적으로 접속되며, 그 게이트는 제5 입력 단자(25)에 전기적으로 접속된다.

- [0147] 트랜지스터(37)의 소스 및 드레인 중 하나는 전원선(51)에 전기적으로 접속되고, 그 게이트는 제3 입력 단자(23)에 전기적으로 접속된다.

- [0148] 트랜지스터(38)의 소스 및 드레인 중 하나는 트랜지스터(32)의 게이트에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 트랜지스터(37)의 소스 및 드레인 중 다른 하나에 전기적으로 접속되며, 그 게이트는 제2 입력 단자(22)에 전기적으로 접속된다.

- [0149] 트랜지스터(39)의 소스 및 드레인 중 하나는 트랜지스터(31)의 소스 및 드레인 중 다른 하나 및 트랜지스터(32)의 소스 및 드레인 중 다른 하나에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 트랜지스터(33)의 게이트에 전기적으로 접속되며, 그 게이트는 전원선(51)에 전기적으로 접속된다.

- [0150] 트랜지스터(40)의 소스 및 드레인 중 하나는 제1 입력 단자(21)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 제2 출력 단자(27)에 전기적으로 접속되며, 그 게이트는 트랜지스터(39)의 소스 및 드레인 중 다른 하나에 전기적으로 접속된다.

- [0151] 트랜지스터(41)의 소스 및 드레인 중 하나는 전원선(52)에 전기적으로 접속되고, 그 소스 및 드레인 중 다른 하나는 제2 출력 단자(27)에 전기적으로 접속되며, 그 게이트는 트랜지스터(32)의 게이트에 전기적으로 접속된다.

- [0152] 도 8c에서, 트랜지스터(33)의 게이트, 트랜지스터(40)의 게이트, 및 트랜지스터(39)의 소스 및 드레인 중 다른 하나가 서로 접속되어 있는 부분을 노드 NA라 부른다는 점에 유의한다. 또한, 트랜지스터(32)의 게이트, 트랜지스터(34)의 게이트, 트랜지스터(35)의 소스 및 드레인 중 다른 하나, 트랜지스터(36)의 소스 및 드레인 중 다른 하나, 트랜지스터(38)의 소스 및 드레인 중 다른 하나, 및 트랜지스터(41)의 게이트가 서로 접속되어 있는 부분을 노드 NB라 부른다.

- [0153] 예를 들어, 제1 펄스 출력 회로(10\_1)에서, 제1 클록 신호(CK1)는 제1 입력 단자(21)를 통해 입력되고, 제2 클록 신호(CK2)는 제2 입력 단자(22)를 통해 입력되며, 제3 클록 신호(CK3)는 제3 입력 단자(23)를 통해 입력되고, 스타트 신호(SP)는 제4 입력 단자(24)를 통해 입력되며, 제3 펄스 출력 회로(10\_3)의 제1 출력 단자(26)로부터 출력된 신호는 제5 입력 단자(25)를 통해 입력된다. 또한, 제1 펄스 출력 회로(10\_1)는 제1 출력 단자(26)를 통해 제1 출력 신호를 출력하고, 제2 출력 단자(27)를 통해 제2 출력 신호인 신호 OUT(1)을 출력한다.

- [0154] 여기서, 도 8a 내지 도 8c의 시프트 레지스터의 동작예를 도 9를 참조하여 설명한다. 도 9는 도 8a 내지 도 8c의 시프트 레지스터의 동작예를 도시하는 타이밍도이다. 주사선 구동 회로에 이용되는 시프트 레지스터의 경우, 도 9의 기간(61)은 수직 귀선 시간(vertical retrace period)이고, 기간(62)은 게이트 선택 기간이다.

- [0155] 전술된 구조에 의해, 구동 회로부를 항상 동작시키지 않고도 정지 화상이 표시될 수 있다.

- [0156] 본 실시형태는 다른 임의의 실시형태와 적절히 조합되거나 치환될 수 있다.

- [0157] (실시형태 3)

- [0158] 본 실시형태에서는, 상기 실시형태의 표시 장치에서 이용될 수 있는 트랜지스터를 설명한다.

- [0159] 상기 실시형태의 표시 장치에 이용될 수 있는 트랜지스터의 구조로서, 예를 들어, 톱 게이트 구조, 보텀 게이트 구조 등을 들 수 있다. 또한, 보텀 게이트 구조로서는, 예를 들어, 스탠다드 구조나 플래너형 구조가 이용될 수 있다.

- [0160] 상기 실시형태에서 설명된 트랜지스터는, 하나의 채널 형성 영역이 형성되는 구조(싱글 게이트 구조라고도 함), 또는 복수의 채널 형성 영역이 형성되는 구조(멀티 게이트 구조)를 가질 수도 있다. 대안으로서, 상기 실시형태의 표시 장치에 이용될 수 있는 트랜지스터는, 채널 영역의 위와 아래에, 게이트 절연층을 사이에 두고, 2개의 게이트 전극층이 제공된 구조(듀얼 게이트 구조라고도 함)를 가질 수도 있다.

- [0161] 본 실시형태의 트랜지스터의 구조예를 도 10a 내지 도 10d를 참조하여 설명한다. 도 10a 내지 도 10d는 본 실시형태의 트랜지스터의 구조예를 나타내는 단면 개략도이다.

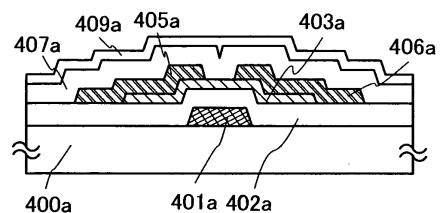

- [0162] 도 10a에 나타낸 트랜지스터는, 보텀 게이트 트랜지스터의 한 타입이며, 또한 역스탠다드 트랜지스터이다.

- [0163] 도 10a에 나타낸 트랜지스터는, 게이트 전극층(401a), 게이트 절연층(402a), 산화물 반도체층(403a), 소스 전극층(405a), 및 드레인 전극층(406a)을 포함한다.

- [0164] 게이트 전극층(401a)은 기판(400a) 위에 제공되고, 게이트 절연층(402a)은 게이트 전극층(401a) 위에 제공되며, 산화물 반도체층(403a)은 게이트 절연층(402a)을 사이에 두고 게이트 전극층(401a) 위에 제공되고, 소스 전극층(405a) 및 드레인 전극층(406a)은 산화물 반도체층(403a) 위에 각각 제공된다.

- [0165] 도 10a에 나타낸 트랜지스터에서, 산화물 반도체층(403a)의 상면의 일부(소스 전극층(405a) 및 드레인 전극층(406a))이 제공되어 있지 않은 상면의 일부)에 접하여 산화물 절연층(407a)이 제공된다. 또한, 산화물 절연층(407a) 위에 보호 절연층(409a)이 제공된다.

- [0166] 도 10b에 나타낸 트랜지스터는, 채널 보호형(채널-스톱형) 트랜지스터라 불리는 보텀 게이트 트랜지스터의 한 타입이며, 또한 역스탠다드 트랜지스터이다.

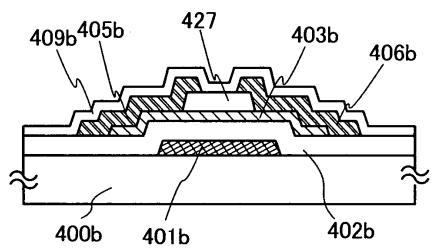

- [0167] 도 10b에 나타낸 트랜지스터는, 게이트 전극층(401b), 게이트 절연층(402b), 산화물 반도체층(403b), 절연층(427), 소스 전극층(405b), 및 드레인 전극층(406b)을 포함한다.

- [0168] 게이트 전극층(401b)은 기판(400b) 위에 제공되고, 게이트 절연층(402b)은 게이트 전극층(401b) 위에 제공되며, 산화물 반도체층(403b)은 게이트 절연층(402b)을 사이에 두고 게이트 전극층(401b) 위에 제공되고, 절연층(427)은 게이트 절연층(402b) 및 산화물 반도체층(403b)을 사이에 두고 게이트 전극층(401b) 위에 제공되며, 소스 전극층(405b) 및 드레인 전극층(406b)은 절연층(427)을 사이에 두고 산화물 반도체층(403b) 위에 제공된다.

- [0169] 또한, 보호 절연층(409b)은 도 10b에 나타낸 트랜지스터의 상부에 접한다.

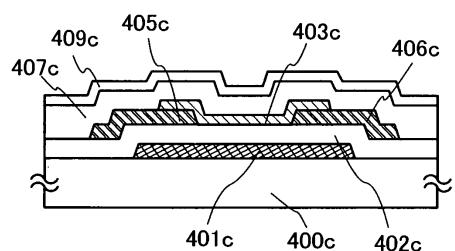

- [0170] 도 10c에 나타낸 트랜지스터는 보텀 게이트 트랜지스터의 한 타입이다.

- [0171] 도 10c에 나타낸 트랜지스터는, 게이트 전극층(401c), 게이트 절연층(402c), 산화물 반도체층(403c), 소스 전극층(405c), 및 드레인 전극층(406c)을 포함한다.

- [0172] 게이트 전극층(401c)은 기판(400c) 위에 제공되고, 게이트 절연층(402c)은 게이트 전극층(401c) 위에 제공되며, 소스 전극층(405c) 및 드레인 전극층(406c)은 게이트 절연층(402c) 위에 제공되고, 산화물 반도체층(403c)은 게이트 절연층(402c), 소스 전극층(405c), 및 드레인 전극층(406c)을 사이에 두고 게이트 전극층(401c) 위에 제공된다.

- [0173] 또한, 도 10c에 나타낸 트랜지스터에서, 산화물 절연층(407c)은 산화물 반도체층(403c)의 상면 및 측면에 접한다. 또한, 산화물 절연층(407c) 위에 보호 절연층(409c)이 제공된다.

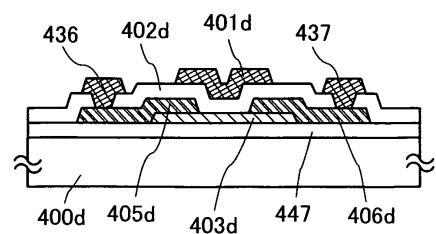

- [0174] 도 10d에 나타낸 트랜지스터는 톱 게이트 트랜지스터의 한 타입이다.

- [0175] 도 10d에 나타낸 트랜지스터는, 게이트 전극층(401d), 게이트 절연층(402d), 산화물 반도체층(403d), 소스 전극층(405d), 및 드레인 전극층(406d)을 포함한다.

- [0176] 산화물 반도체층(403d)은 하지층(base layer, 447)을 사이에 두고 기판(400d) 위에 제공되고, 소스 전극층(405d) 및 드레인 전극층(406d) 각각은 산화물 반도체층(403d)의 일부 위에 제공되며, 게이트 절연층(402d)은, 산화물 반도체층(403d), 소스 전극층(405d), 및 드레인 전극층(406d) 위에 제공되고, 게이트 전극층(401d)은 게

이트 절연층(402d)을 사이에 두고 산화물 반도체층(403d) 위에 제공된다.

[0177] 도 10d에 나타낸 트랜지스터에서, 소스 전극층(405d)은 게이트 절연층(402d)에 제공된 개구부의 배선층(436)에 접하고, 드레인 전극층(406d)은 게이트 절연층(402d)에 제공된 개구부의 배선층(437)에 접한다.

[0178] 기판(400a) 내지 기판(400d)으로서, 예를 들어, 바륨 보로실리케이트 유리, 알루미노보로실리케이트 유리 등의 유리 기판이 이용될 수 있다.

[0179] 대안으로서, 세라믹 기판, 석영 기판, 또는 사파이어 기판 등의 절연체로 형성된 기판이 기판(400a) 내지 기판(400d)으로서 이용될 수 있다. 추가의 대안으로서, 결정화된 유리가 기판(400a) 내지 기판(400d)으로서 이용될 수 있다. 역시 추가의 대안으로서, 플라스틱 기판 등이나 실리콘 등의 반도체 기판이 기판(400a) 내지 기판(400d)으로서 이용될 수 있다.

[0180] 하지층(447)은 기판(400d)으로부터의 불순물 원소의 확산을 방지하는 기능을 가진다. 하지층(447)으로서는, 예를 들어, 질화 실리콘층, 산화 실리콘층, 질화 산화 실리콘층, 산화 질화 실리콘층, 산화 알루미늄층, 또는 산화 질화 알루미늄층이 이용될 수 있다. 하지층(447)은 또한, 하지층(447)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수도 있다.

[0181] 도 10a 내지 도 10c에 나타낸 트랜지스터에서도, 도 10d에 나타낸 트랜지스터에서와 같이 기판과 게이트 전극층 사이에 하지층이 제공될 수도 있다.

[0182] 게이트 전극층(401a 내지 401d)으로서, 예를 들어, 몰리브덴, 티탄, 크롬, 탄탈, 텉스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐 등의 금속 재료, 또는 이들 재료들 중 임의의 것을 주성분으로 포함하는 합금 재료의 층을 이용할 수 있다. 게이트 전극층(401a 내지 401d)은 또한, 게이트 전극층(401a 내지 401d)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0183] 게이트 절연층(402a 내지 402d)으로서, 예를 들어, 산화 실리콘층, 질화 실리콘층, 산화 질화 실리콘층, 질화 산화 실리콘층, 산화 알루미늄층, 질화 알루미늄층, 산화 질화 알루미늄층, 질화 산화 알루미늄층, 또는 산화 하프늄층을 이용할 수 있다. 게이트 절연층(402a 내지 402d)은 또한, 게이트 절연층(402a 내지 402d)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수도 있다. 게이트 절연층(402a 내지 402d)에 적용될 수 있는 재료의 층은, 예를 들어, 플라즈마 CVD법, 스퍼터링법 등에 의해 형성될 수 있다. 예를 들어, 게이트 절연층(402a 내지 402d)은, 플라즈마 CVD법에 의해 질화 실리콘층을 형성하고 플라즈마 CVD법에 의해 질화 실리콘층 위에 산화 실리콘층을 형성하는 방식으로 형성될 수 있다.

[0184] 산화물 반도체층(403a 내지 403d)에 이용될 수 있는 산화물 반도체로서, 예를 들어, 4원계 금속 산화물, 3원계 금속 산화물, 또는 2원계 금속 산화물을 들 수 있다. 4원계 금속 산화물로서, 예를 들어, In-Sn-Ga-Zn-O계 금속 산화물 등을 들 수 있다. 3원계 금속 산화물로서, 예를 들어, In-Ga-Zn-O계 금속 산화물, In-Sn-Zn-O계 금속 산화물, In-Al-Zn-O계 금속 산화물, Sn-Ga-Zn-O계 금속 산화물, Al-Ga-Zn-O계 금속 산화물, Sn-Al-Zn-O계 금속 산화물 등을 들 수 있다. 2원계 금속 산화물로서, In-Zn-O계 금속 산화물, Sn-Zn-O계 금속 산화물, Al-Zn-O계 금속 산화물, Zn-Mg-O계 금속 산화물, Sn-Mg-O계 금속 산화물, In-Mg-O계 금속 산화물, In-Sn-O계 금속 산화물 등을 들 수 있다. 또한, 산화물 반도체로서, In-O계 금속 산화물, Sn-O계 금속 산화물, Zn-O계 금속 산화물 등을 이용할 수 있다. 산화물 반도체로서 이용될 수 있는 금속 산화물은  $\text{SiO}_2$ 를 포함할 수도 있다. 여기서, 예를 들어, In-Ga-Zn-O계 금속 산화물이란, 적어도 In, Ga, 및 Zn을 포함하는 산화물을 의미하며, 원소들의 조성비는 특별히 제한되지 않는다. In-Ga-Zn-O계 금속 산화물은 In, Ga, 및 Zn 이외의 원소를 포함할 수도 있다.

[0185] 또한, 산화물 반도체층(403a 내지 403d)에 이용될 수 있는 산화물 반도체로서, 화학식  $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ )으로 표기되는 금속 산화물을 들 수 있다. 여기서, M은, Ga, Al, Mn 및 Co로부터 선택된 하나 이상의 금속 원소를 나타낸다. 예를 들어, Ga, Ga 및 Al, Ga 및 Mn, Ga 및 Co 등이 M으로서 주어질 수 있다.

[0186] 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)으로서, 예를 들어, 알루미늄, 크롬, 구리, 탄탈, 티타늄, 몰리브덴, 또는 텉스텐 등의 금속 재료, 또는 상기 금속 재료들 중 임의의 것을 주성분으로 포함하는 합금 재료의 층을 이용할 수 있다. 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)은 또한, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0187] 예를 들어, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)은, 알루미늄이나 구리의 금속층과

티타늄, 몰리브덴, 텅스텐 등의 고용접 금속층과의 적층에 의해 형성될 수 있다. 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)은, 복수의 고용접 금속층들 사이에 알루미늄 또는 구리의 금속층이 제공된 구조를 가질 수도 있다. 또한, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)이 힐록(hilllock)이나 휘스커(wisker)의 발생을 방지하는 원소(예를 들어, Si, Nd, 또는 Si)를 첨가한 알루미늄층을 이용하여 형성되면, 내열성이 향상될 수 있다.

[0188] 대안으로서, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)은 도전성 금속 산화물을 포함하는 층을 이용하여 형성될 수 있다. 도전성 금속 산화물로서, 예를 들어, 산화 인듐( $In_2O_3$ ), 산화 주석( $SnO_2$ ), 산화 아연( $ZnO$ ), 산화 인듐 및 산화 주석의 합금( $In_2O_3-SnO_2$ , ITO로 약기함), 산화 인듐 및 산화 아연의 합금( $In_2O_3-ZnO$ ), 또는 산화 실리콘을 포함하는 이러한 금속 산화물 재료를 이용할 수 있다.

[0189] 또한, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)을 형성하는 데 사용되는 재료를 이용하여 또 다른 배선이 형성될 수도 있다.

[0190] 배선층(436 및 437)으로서, 소스 전극층(405a 내지 405d) 및 드레인 전극층(406a 내지 406d)에 적용될 수 있는 재료의 층을 이용할 수 있다. 배선층(436 및 437)은 또한, 배선층(436 및 437)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0191] 절연층(427)으로서, 예를 들어, 하지층(447)에 적용될 수 있는 층을 이용할 수 있다. 절연층(427)은 또한, 절연층(427)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0192] 산화물 절연층(407a 및 407c)으로서, 산화물 절연층을 이용할 수 있으며, 예를 들어, 산화 실리콘층 등을 이용할 수 있다. 산화물 절연층(407a 및 407c)은 또한, 산화물 절연층(407a 및 407c)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0193] 보호 절연층(409a 내지 409c)으로서, 무기 절연층을 이용할 수 있으며, 예를 들어, 질화 실리콘층, 질화 알루미늄층, 질화 산화 실리콘층, 또는 질화 산화 알루미늄층 등을 이용할 수 있다. 보호 절연층(409a 내지 409c)은 또한, 보호 절연층(409a 내지 409c)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수도 있다.

[0194] 상기 실시형태의 표시 장치에서는, 본 실시형태의 트랜지스터에 기인하는 표면 요철을 저감하기 위하여, 트랜지스터 위에(트랜지스터가 산화물 절연층 또는 보호 절연층을 포함하는 경우, 산화물 절연층 또는 보호 절연층을 사이에 두고 트랜지스터 위에) 평탄화 절연층이 제공될 수 있다. 평탄화 절연층으로서, 폴리이미드, 아크릴, 또는 벤조시클로부тен 등의 유기 재료의 층을 이용할 수 있다. 대안으로서, 평탄화 절연층으로서 저유전율 재료(low-k 재료)의 층을 이용할 수 있다. 평탄화 절연층은 또한, 평탄화 절연층에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

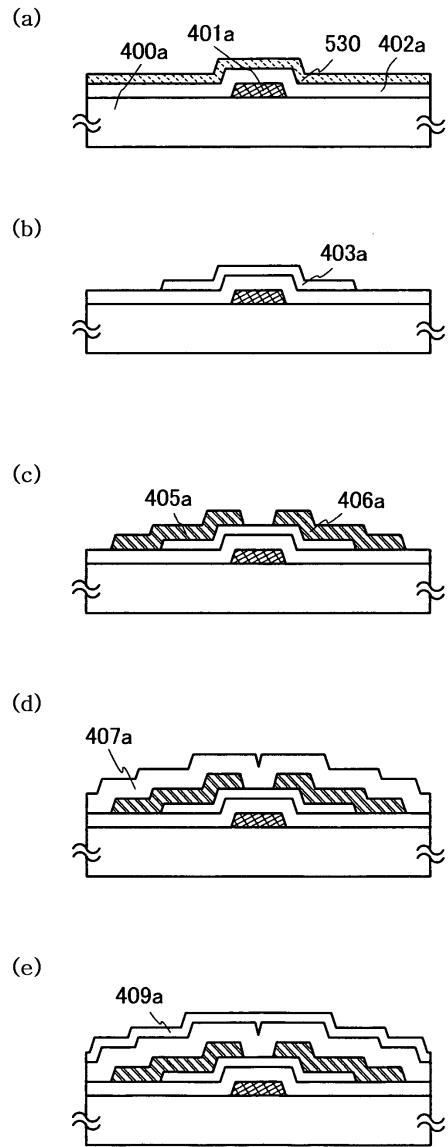

[0195] 그 다음, 본 실시형태의 트랜지스터의 제조 방법의 예로서, 도 10a에 나타낸 트랜지스터의 제조 방법의 예를 도 11의 (a) 내지 (e)를 참조하여 설명한다. 도 11의 (a) 내지 (e)는 도 10a에 나타낸 트랜지스터의 제조 방법의 예를 나타낸다. 도 10a에 나타낸 트랜지스터의 제조 방법의 예를 본 실시형태의 예로서 설명하지만, 본 실시형태의 트랜지스터의 제조 방법은 이것으로 한정되지 않는다는 점에 유의한다. 예를 들어, 도 10b 내지 도 10d의 구성요소들에 관해서는 참조 부호를 제외하고는 도 10a에 나타낸 구성요소들과 동일하므로, 도 10a에 나타낸 트랜지스터의 제조 방법의 예에 대한 설명을 적절히 참조할 수 있다.

[0196] 우선, 기판(400a)이 준비되고, 기판(400a) 위에 제1 도전막이 형성된다.

[0197] 기판(400a)으로서, 유리 기판이 예로서 이용된다.

[0198] 제1 도전막으로서는, 몰리브덴, 티탄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐 등의 금속 재료, 또는 이를 금속 재료들 중 임의의 것을 주성분으로 포함하는 합금 재료의 막을 이용할 수 있다. 제1 도전막은 또한, 제1 도전막에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0199] 그 다음, 제1 포토리소그래피 공정이 실행된다: 제1 도전막 위에 제1 레지스트 마스크가 형성되고, 제1 레지스트 마스크를 이용하여 제1 도전막이 선택적으로 에칭되어 게이트 전극층(401a)을 형성하며, 제1 레지스트 마스크가 제거된다.

[0200] 본 실시형태에서는, 레지스트 마스크는 잉크젯법에 의해 형성될 수도 있다. 잉크젯법에 의한 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않는다; 따라서, 제조 비용이 저감될 수 있다.

- [0201] 포토리소그래피 공정에서 포토마스크의 수 및 단계 수를 줄이기 위하여, 다계조 마스크에 의해 형성된 레지스트 마스크를 이용하여 에칭 단계가 실시될 수도 있다. 다계조 마스크는, 투과된 광이 복수의 강도를 갖게 되는 마스크이다. 다계조 마스크를 이용하여 형성된 레지스트 마스크는 복수의 두께를 가지며, 에칭에 의해 형상이 더욱 변형될 수 있다; 따라서, 이 레지스트 마스크는 상이한 패턴으로 가공하는 복수의 에칭 단계에 이용될 수 있다. 따라서, 하나의 다계조 마스크에 의해 적어도 2종류의 상이한 패턴에 대응하는 레지스트 마스크가 형성될 수 있다. 따라서, 노광 마스크의 수가 저감될 수 있고, 대응하는 포토리소그래피 공정수도 저감될 수 있음으로써, 제조 공정이 간략화될 수 있다.

- [0202] 그 다음, 게이트 전극층(401a) 위에 게이트 절연층(402a)이 형성된다.

- [0203] 본 실시형태의 트랜지스터에 이용되는 산화물 반도체로서, 불순물을 제거함으로써 i형화 또는 실질적으로 i형화된 산화물 반도체를 이용한다. 이러한 고순도화된 산화물 반도체는 계면 준위 및 계면 전하에 극히 민감하다; 따라서, 산화물 반도체층과 게이트 절연층 사이의 계면은 중요하다. 이러한 이유로, 고순도화된 산화물 반도체에 접하는 게이트 절연층은 높은 품질을 가질 필요가 있다. 따라서, 게이트 절연층(402a)은 산화물 반도체와의 낮은 계면 준위 밀도를 가지며 양호한 막 품질 뿐만 아니라 양호한 계면을 형성할 수 있는 절연층인 것이 바람직하다.

- [0204] 예를 들어, 게이트 절연층(402a)은 고밀도 플라즈마 CVD법에 의해 형성될 수 있다. 예를 들어, 마이크로파(예를 들어, 2.45 GHz의 주파수를 갖는 마이크로파)를 이용한 고밀도 플라즈마 CVD법을 이용하는 것이, 절연층이 치밀할 수 있고 높은 내압과 높은 품질을 가질 수 있기 때문에 바람직하다. 이것은, 고순도화된 산화물 반도체층이 고품질 게이트 절연층에 접하면, 계면 준위가 저감될 수 있고 계면 특성이 양호해질 수 있기 때문이다.

- [0205] 게이트 절연층(402a)을 형성하기 위해 스퍼터링법이나 플라즈마 CVD법 등의 또 다른 성막 방법을 이용할 수도 있다. 또한, 게이트 절연층(402a)의 형성 후 열 처리가 실시될 수도 있다. 열 처리는, 게이트 절연층(402a)의 막 품질과, 게이트 절연층(402a)과 산화물 반도체 사이의 계면 특성을 향상시킬 수 있다.

- [0206] 그 다음, 게이트 절연층(402a) 위에, 2 nm이상 200 nm이하, 바람직하게는 5 nm이상 30 nm이하의 두께를 갖는 산화물 반도체막(530)이 형성된다(도 11의 (a) 참조). 예를 들어, 산화물 반도체막(530)은 스퍼터링법에 의해 형성될 수 있다.

- [0207] 산화물 반도체막(530)의 형성 전에, 아르곤 가스를 도입해 플라즈마를 생성하는 역스퍼터링에 의해, 게이트 절연층(402a)의 표면에 부착된 분말 물질(입자 또는 먼지라고도 함)을 제거하는 것이 바람직하다는 점에 유의한다. 역스퍼터링이란, 타겟 측에 전압을 인가하지 않고, RF 전원을 이용하여 아르곤 분위기에서 기판측에 전압을 인가해 플라즈마를 생성하여 기판 표면을 개질(modify)하는 방법을 말한다. 아르곤 대신에, 질소, 헬륨, 산소 등을 이용할 수도 있다는 점에 유의한다.

- [0208] 예를 들어, 산화물 반도체막(530)은, 산화물 반도체층(403a)의 재료로서 이용될 수 있는 산화물 반도체 재료를 이용하여 형성될 수 있다. 본 실시형태에서, 산화물 반도체막(530)은 In-Ga-Zn-O계 산화물 타겟을 이용하여 스퍼터링법에 의해 형성된다. 또한, 산화물 반도체막(530)은, 희가스(대표적으로는, 아르곤) 분위기, 산소 분위기, 또는 희가스 및 산소의 혼합된 분위기에서 스퍼터링법에 의해 형성될 수 있다.

- [0209] 스퍼터링법에 의해 산화물 반도체막(530)을 형성하기 위한 타겟으로서, 예를 들어,  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [몰비]의 조성비를 갖는 산화물 타겟을 이용할 수 있다. 상기 타겟으로 한정되지 않고, 예를 들어,  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [몰비]의 조성비를 갖는 산화물 타겟을 이용할 수도 있다. 산화물 타겟의 총 체적에 관하여 공극(space) 등이 차지하는 영역을 제외한 부분의 체적의 비율(충전율이라고도 함)은, 90%이상 100%이하, 바람직하게는 95%이상 99.9%이하이다. 높은 충전율을 갖는 금속 산화물 타겟을 이용하여 형성된 산화물 반도체막은 높은 밀도를 가진다.

- [0210] 산화물 반도체막(530)의 형성시에 이용되는 스퍼터링 가스로서, 예를 들어, 수소, 물, 수산기, 또는 수소화물 등의 불순물이 제거된 고순도 가스를 이용하는 것이 바람직하다.

- [0211] 산화물 반도체막(530)의 형성 전에, 스퍼터링 장치의 예비가열 챔버에서 게이트 전극층(401a)이 형성된 기판(400a) 또는 게이트 전극층(401a) 및 게이트 절연층(402a)이 형성된 기판(400a)을 예비가열하여, 기판(400a)에 흡착된 수소나 수분 등의 불순물을 이탈시켜 제거하는 것이 바람직하다. 예비가열은, 수소, 수산기, 및 수분이 게이트 절연층(402a) 및 산화물 반도체막(530)에 침입하는 것을 방지할 수 있다. 예비가열 챔버에 제공되는 배기 수단으로서 크라이오펌프(cryopump)가 바람직하다는 점에 유의한다. 예비가열 처리는 생략될 수도 있다.

또한, 예비가열은, 산화물 절연층(407a)의 성막 전에, 소스 전극층(405a) 및 드레인 전극층(406a)까지의 층들이 형성된 기판(400a)에도 마찬가지로 실시될 수도 있다.

[0212] 스퍼터링법에 의해 산화물 반도체막(530)이 형성되는 경우, 감압 상태로 유지된 성막 챔버 내부에 기판(400a)이 유지되고, 기판 온도가 100°C 이상 600°C 이하, 바람직하게는 200°C 이상 400°C 이하로 설정된다. 기판(400a)을 가열함으로써, 산화물 반도체막(530)에 포함되는 불순물의 농도가 저감될 수 있다. 또한, 기판(400a)의 가열은 스퍼터링법에 기인한 손상을 저감할 수 있다. 또한, 성막 챔버 내의 잔류 수분을 제거하면서 수소와 수분이 제거된 스퍼터링 가스가 도입되고, 전술된 타겟이 이용된다; 따라서, 기판(400a) 위에 산화물 반도체막(530)이 형성된다.

[0213] 성막 챔버 내의 잔류 수분을 제거하기 위하여, 크라이오펌프, 이온 펌프, 티타늄 승화 펌프(titanium sublimation pump) 등의 흡착형 진공 펌프(entrapment vacuum pump)를 이용하는 것이 바람직하다. 또한, 배기 수단은 콜드 트랩(cold trap)을 갖춘 터보 펌프(turbo pump)일 수도 있다. 크라이오펌프에 의해 성막 챔버가 배기되는 경우, 수소 원자, 물 등의 수소 원자를 포함한 화합물, 더욱 바람직하게는, 수소 원자 및 탄소 원자를 포함한 화합물 등이 제거된다. 따라서, 크라이오펌프에 의해, 성막 챔버에서 형성된 산화물 반도체막(530)에 포함되는 불순물의 농도가 저감될 수 있다.

[0214] 성막 조건의 한 예로서, 하기의 사항이 이용될 수 있다: 기판(400a)과 타겟 사이의 거리는 100 mm, 압력은 0.6 Pa, 직류 (DC) 전력이 0.5 kW, 분위기는 산소 분위기(산소 유량비는 100 %). 펄스 직류(DC) 전원을 이용한 스퍼터링법이 바람직한데, 이것은, 성막시에 발생되는 분말 물질이 저감될 수 있고 막 두께가 균일해질 수 있기 때문이라는 점에 유의한다.

[0215] 그 다음, 제2 포토리소그래피 공정이 실행된다: 산화물 반도체막(530) 위에 제2 레지스트 마스크가 형성되고, 제2 레지스트 마스크를 이용하여 산화물 반도체막(530)이 선택적으로 에칭되어 산화물 반도체막(530)을 섬 형상의 산화물 반도체층으로 가공하며, 제2 레지스트 마스크가 제거된다.

[0216] 게이트 절연층(402a)에 컨택트 홀을 형성하는 경우, 컨택트 홀은 산화물 반도체막(530)을 섬 형상의 산화물 반도체층으로 가공할 때에 형성될 수 있다.

[0217] 산화물 반도체막(530)의 에칭에 대해, 예를 들어, 건식 에칭, 습식 에칭, 또는 건식 에칭 및 습식 에칭의 양쪽 모두를 이용할 수 있다. 산화물 반도체막(530)의 습식 에칭에 이용되는 에칭액으로서는, 예를 들어, 인산, 아세트산, 및 질산의 혼합 용액 등이 이용될 수 있다. 또한, (KANTO CHEMICAL CO., INC.에 의해 생산되는) ITO07N을 이용할 수도 있다.

[0218] 그 다음, 산화물 반도체층에 제1 열 처리를 실시한다. 제1 열 처리를 통해, 산화물 반도체층이 탈수화 또는 탈수소화될 수 있다. 제1 열 처리의 온도는, 350°C 이상 750°C 이하, 바람직하게는 350°C 이상 기판의 변형점 미만이다. 여기서는, 열 처리 장치의 일종인 전기로에 기판을 두고, 450°C, 1시간 동안 질소 분위기에서 산화물 반도체층에 열 처리를 실시한 다음, 산화물 반도체층이 대기에 노출되지 않도록 하여 산화물 반도체층으로의 물과 수소의 침입을 방지한다. 이러한 방식으로, 산화물 반도체층(403a)이 얻어진다(도 11의 (b) 참조).

[0219] 열 처리 장치는 전기로에 한정되지 않고, 저항 발열체 등의 발열체로부터의 열 전도 또는 열 복사를 이용하여 피처리물(process object)을 가열하는 장치를 갖춘 것일 수도 있다. 예를 들어, GRTA(gas rapid thermal annealing) 장치 또는 LRTA(lamp rapid thermal annealing) 장치 등의 RTA(rapid thermal annealing) 장치가 이용될 수 있다. LRTA 장치는, 할로겐 램프(halogen lamp), 메탈 헬라이드 램프(metal halide lamp), 크세논 아크 램프(xenon arc lamp), 카본 아크 램프(carbon arc lamp), 고압 나트륨 램프(high pressure sodium lamp), 또는 고압 수은 램프(high pressure mercury lamp) 등의 램프로부터 방출되는 광(전자기파)의 복사에 의해 피처리물을 가열하는 장치이다. GRTA 장치는 고온의 가스를 이용한 열 처리를 위한 장치이다. 고온 가스로서는, 아르곤과 같은 희가스나 질소 등의, 열 처리에 의해 피처리물과 반응하지 않는 불활성 가스가 이용된다.

[0220] 예를 들어, 제1 열 처리로서, GRTA는 다음과 같이 실시될 수도 있다. 650 °C 내지 700°C의 고온으로 가열된 불활성 가스 내에 기판을 이송하여 두고, 수 분간 가열한 다음, 기판을 이송하여 고온으로 가열된 불활성 가스로부터 꺼낸다.

[0221] 제1 열 처리시에, 질소, 또는 헬륨, 네온, 또는 아르곤 등의 희가스에, 물, 수소 등이 포함되지 않는 것이 바람직하다는 점에 유의한다. 열 처리 장치 내에 도입되는 질소, 또는 헬륨, 네온, 또는 아르곤 등의 희가스는 6N(99.9999%) 이상, 바람직하게는 7N(99.99999%) 이상의 순도(즉, 불순물 농도가 1 ppm 이하, 바람직하게는

0.1 ppm 이하)를 갖는 것이 바람직하다.

[0222] 제1 열 처리에 의해 산화물 반도체층이 가열된 후, 동일한 노(furnace)에 고순도의 산소 가스, 고순도의 N<sub>2</sub>O 가스, 또는 초건조 공기(이슬점이 -40°C이하, 바람직하게는 -60°C이하)가 도입될 수도 있다. 산소 가스 또는 N<sub>2</sub>O 가스는, 물, 수소 등을 포함하지 않는 것이 바람직하다. 열 처리 장치에 도입되는 산소 가스 또는 N<sub>2</sub>O 가스의 순도는, 바람직하게는 6N(99.9999%) 이상, 더 바람직하게는 7N(99.99999%) 이상(즉, 산소 가스 또는 N<sub>2</sub>O 가스의 불순물 농도는 바람직하게는 1ppm 이하, 더 바람직하게는 0.1 ppm 이하)이다. 산소 가스 또는 N<sub>2</sub>O 가스의 효과에 의해, 탈수화 또는 탈수소화 처리에 의한 불순물의 제거 단계를 통해 감소된 산화물 반도체의 주성분인 산소가 공급된다; 따라서, 산화물 반도체층(403a)이 고순도화된다.

[0223] 섬 형상의 산화물 반도체층으로 가공되기 이전의 산화물 반도체막(530)에 제1 열 처리가 실시될 수도 있다. 이러한 경우, 제1 열 처리 후에 가열 장치로부터 기판을 꺼낸 다음, 산화물 반도체막(530)을 섬 형상의 산화물 반도체층으로 가공한다.

[0224] 전술된 타이밍 외에도, 제1 열 처리는 산화물 반도체층의 형성 후에, 예를 들어, 산화물 반도체층(403a) 위에 소스 전극층(405a) 및 드레인 전극층(406a)을 형성한 후, 또는 소스 전극층(405a) 및 드레인 전극층(406a) 위에 산화물 절연층(407a)을 형성한 후에 실시될 수도 있다.

[0225] 게이트 절연층(402a)에 컨택트 홀을 형성하는 경우, 컨택트 홀은 산화물 반도체막(530)에 제1 열 처리를 실시하기 전에 형성될 수도 있다.

[0226] 산화물 반도체층은, 산화물, 질화물, 금속 등의 기초 부재(base component)의 재료에 관계없이, 결정 영역(단결정 영역), 즉, 막의 표면에 수직으로 배향된 c-축을 갖는 결정 영역을 포함하는 두꺼운 막이 되도록, 2개의 성막 단계를 통해 형성된 산화물 반도체막을 이용하여 형성될 수도 있다. 예를 들어, 3 nm이상 15 nm이하의 두께를 갖는 제1 산화물 반도체막이 성막되고, 질소, 산소, 희가스, 또는 건조 공기의 분위기하에서 450°C이상 850°C이하, 바람직하게는 550°C이상 750°C이하의 온도에서 제1 열 처리되어, 표면을 포함한 영역의 결정 영역(판모양 결정을 포함함)을 포함하는 제1 산화물 반도체막이 형성된다. 그 다음, 제1 산화물 반도체막보다 두꺼운 제2 산화물 반도체막이 형성되고, 450°C이상 850°C이하, 바람직하게는 600°C이상 700°C이하의 온도에서 열 처리되어, 제1 산화물 반도체막을 결정 성장의 씨드(seed)로서 이용하여 윗쪽을 향하여 결정 성장을 진행시켜, 제2 산화물 반도체막의 전체 영역이 결정화된다. 결과적으로 두꺼운 결정 영역을 포함하는 막을 이용하여, 산화물 반도체층이 형성될 수도 있다.

[0227] 그 다음, 게이트 절연층(402a) 및 산화물 반도체층(403a) 위에 제2 도전막이 형성된다.

[0228] 제2 도전막으로서, 예를 들어, 알루미늄, 크롬, 구리, 탄탈, 티타늄, 몰리브덴, 또는 텅스텐 등의 금속 재료, 또는 이러한 금속 재료들 중 임의의 것을 주성분으로 포함하는 합금 재료의 막을 이용할 수 있다. 제2 도전막은 또한, 제2 도전막에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

[0229] 그 다음, 제3 포토리소그래피 공정이 실행된다: 제2 도전막 위에 제3 레지스트 마스크가 형성되고, 제2 도전막이 제3 레지스트 마스크를 이용하여 선택적으로 에칭되어 소스 전극층(405a) 및 드레인 전극층(406a)을 형성하며, 제3 레지스트 마스크가 제거된다(도 11의 (c) 참조).

[0230] 또한, 소스 전극층(405a) 및 드레인 전극층(406a)의 형성시에 제2 도전막으로부터 또 다른 배선이 형성될 수도 있다.

[0231] 제3 레지스트 마스크 형성시의 노광에 있어서, 자외선, KrF 레이저광, 또는 ArF 레이저광을 이용하는 것이 바람직하다. 이후에 완성되는 트랜지스터의 채널 길이(L)는, 산화물 반도체층(403a) 위에서 서로 인접하는 소스 전극층(405a)의 하단과 드레인 전극층(406a)의 하단 사이의 간격의 폭에 의존한다. 채널 길이(L)가 25 nm 미만인 경우, 노광은, 수 nm 내지 수십 nm의 극히 짧은 과장을 갖는 초자외선을 이용한 제3 레지스트 마스크 형성시에 실시되는 것이 바람직하다. 초자외선을 이용한 노광에서는, 해상도가 높고 초점 심도가 크다. 따라서, 이후에 완성되는 트랜지스터의 채널 길이(L)는 10 nm이상 1000 nm이하일 수 있고, 전술된 바와 같은 노광을 통해 형성된 트랜지스터 등의 이용은 회로의 고속 동작을 가능케 한다. 또한, 이 트랜지스터의 오프 전류값은 극히 작기 때문에, 이 트랜지스터를 포함한 전력 소비가 저감될 수 있다.

[0232] 제2 도전막을 에칭하는 경우, 산화물 반도체층(403a)이 에칭에 의해 분단되는 것을 방지하기 위하여 에칭 조건을 최적화하는 것이 바람직하다. 그러나, 제2 도전막만이 에칭될 수 있고 산화물 반도체층(403a)은 에칭되지

않는 조건을 설정하기는 어렵다. 일부 경우에는, 제2 도전막의 에칭시에 산화물 반도체층(403a)의 일부만이 에칭되어, 산화물 반도체층(403a)이 흄부(오목부)를 포함하게 된다.

[0233] 본 실시형태에서는, 제2 도전막의 예로서 티타늄막이 이용되고, 산화물 반도체층(403a)의 예로서 In-Ga-Zn-O계 산화물 반도체가 이용되며, 에칭액으로서 암모니아과수(암모니아, 물, 과산화수소수의 혼합액)를 이용한다.

[0234] 그 다음, 산화물 반도체층(403a), 소스 전극층(405a), 및 드레인 전극층(406a) 위에는, 산화물 절연층(407a)이 형성된다. 여기서, 산화물 절연층(407a)은 산화물 반도체층(403a)의 상면의 일부에 접한다.

[0235] 산화물 절연층(407a)은, 산화물 절연층(407a)에 물과 수소 등의 불순물을 혼입시키지 않는 방법, 예를 들어, 스퍼터링법을 적절히 이용하여 적어도 1 nm 이상의 두께를 갖도록 형성될 수 있다. 산화물 절연층(407a)에 수소가 포함되면, 산화물 반도체층으로의 수소의 침입, 또는 수소에 의한 산화물 반도체층 내의 산소의 추출이 야기됨으로써, 산화물 반도체층의 백채널이 더 낮은 저항을 갖도록(n형 도전형을 갖도록) 하여, 기생 채널이 형성될 수도 있다. 따라서, 가능한 한 수소를 적게 포함하는 산화물 절연층(516)을 형성하기 위하여, 수소가 이용되지 않는 형성 방법을 이용하는 것이 중요하다.

[0236] 본 실시형태에서는, 산화물 절연층(407a)으로서 200 nm의 두께를 갖는 산화 실리콘막이 스퍼터링법에 의해 형성된다. 성막시의 기판 온도는, 실온 이상, 300°C 이하일 수 있다; 본 실시형태에서, 기판 온도는 일례로서 100 °C이다. 스퍼터링법에 의한 산화 실리콘막의 형성은, 희가스(대표적으로는, 아르곤) 분위기, 산소 분위기, 또는 희가스 및 산소의 혼합 분위기에서 실시될 수 있다.

[0237] 또한, 산화물 절연층(407a)을 형성하기 위한 타겟으로서 산화 실리콘 타겟이나 실리콘 타겟이 이용될 수 있다. 예를 들어, 실리콘 타겟을 이용하여, 산소를 포함하는 분위기하에서 스퍼터링법에 의해 산화 실리콘막이 형성될 수 있다.

[0238] 산화물 절연층(407a)의 형성에 이용되는 성막 챔버 내의 잔류 수분을 제거하기 위하여, 크라이오펌프 등의 흡착형 진공 펌프를 이용하는 것이 바람직하다. 크라이오펌프로 성막 챔버 내의 잔류 수분을 제거함으로써, 산화물 절연층(407a)에 포함되는 불순물의 농도가 저감될 수 있다. 산화물 절연층(407a)의 형성에 이용되는 성막 챔버 내의 잔류 수분을 제거하기 위한 배기 수단으로서, 콜드 트랩을 갖춘 터보 펌프가 이용될 수 있다.

[0239] 또한, 산화물 반도체층(407a)의 형성에 이용되는 스퍼터링 가스로서, 수소, 물, 수산기, 또는 수소화물 등의 불순물이 제거된 고순도 가스를 이용하는 것이 바람직하다.

[0240] 산화물 절연층(407a)의 형성 전에, N<sub>2</sub>O, N<sub>2</sub>, 또는 Ar 등의 가스를 이용한 플라즈마 처리를 실시하여 산화물 반도체층(403a)의 노출된 표면에 흡착된 물 등을 제거할 수도 있다. 플라즈마 처리를 실시하는 경우, 산화물 반도체층(403a)의 상면의 일부에 접하는 산화물 절연층(407a)을 대기에 노출시키지 않고 형성하는 것이 바람직하다.

[0241] 그 다음, 불활성 가스 분위기 또는 산소 가스 분위기에서 제2 열 처리(바람직하게는, 200°C 이상 400°C 이하, 예를 들어, 250°C 이상 350°C 이하의 온도에서)를 실시할 수 있다. 예를 들어, 제2 열 처리는 질소 분위기에서 250°C로 1시간 동안 실시된다. 제2 열 처리에 의해, 산화물 반도체층(403a)의 상면의 일부가 산화물 절연층(407a)에 접한 상태로 가열된다.

[0242] 전술된 공정을 통해, 산화물 반도체막에 제1 열 처리가 실시되어, 수소, 수분, 수산기 또는 수소화물(수소 화합물이라고도 함)등의 불순물이 산화물 반도체층으로부터 의도적으로 제거될 수 있고, 추가적으로, 불순물의 제거 단계를 통해 감소된 산화물 반도체의 주성분인 산소가 공급될 수 있다. 따라서, 산화물 반도체층이 고순도화되고 i형(진성) 반도체로 된다.

[0243] 전술된 공정을 통해, 트랜지스터가 형성된다(도 11의 (d) 참조).

[0244] 결함을 많이 갖는 산화 실리콘층이 산화물 절연층으로서 이용되면, 산화 실리콘층의 형성 후의 열 처리는, 산화물 반도체층에 포함된 수소, 수분, 수산기, 또는 수소화물 등의 불순물을 산화물 절연층으로 확산시키는 효과를 가지므로, 산화물 반도체층에 포함된 불순물이 더욱 저감될 수 있다.

[0245] 산화물 절연층(407a) 위에 보호 절연층(409a)이 추가로 형성될 수도 있다. 예를 들어, RF 스퍼터링법에 의해 질화 실리콘막이 형성된다. 높은 양산성을 달성한다는 이유 때문에 보호 절연층의 형성 방법으로서 RF 스퍼터링법이 바람직하다. 보호 절연층으로서, 수분 등의 불순물을 포함하지 않고 이러한 불순물이 외부로부터 침입하는 것을 방지하는, 질화 실리콘막이나 질화 알루미늄막 등의 무기 절연막을 이용할 수 있다. 본 실시형태에서는, 보호 절연층(409a)으로서 질화 실리콘막이 형성된다(도 11의 (e) 참조).

- [0246] 본 실시형태에서는, 산화물 절연층(407a)까지의 층이 형성된 기판(400a)을 100°C 내지 400°C의 온도에서 가열하고, 수소 및 수분이 제거된 고순도 질소를 포함한 스퍼터링 가스와 실리콘 반도체의 타겟을 이용하여 질화 실리콘막을 형성하는 방식으로 보호 절연층(409a)을 형성한다. 이 경우에도, 산화물 절연층(407a)의 경우와 마찬가지로, 처리 챔버 내의 잔류 수분을 제거하면서 보호 절연층(409a)을 형성하는 것이 바람직하다.

- [0247] 또한, 보호 절연층(409a)의 형성 후, 대기하에서 100°C 이상 200°C이하의 온도로 1시간 이상 30시간 이하 동안 열 처리가 추가로 실시될 수도 있다. 이 열 처리는 일정한 가열 온도에서 실시될 수도 있다. 대안으로서, 다음과 같은 가열 온도 변화가 복수회 반복적으로 실시될 수도 있다: 가열 온도가 실온으로부터 100°C 내지 200°C의 온도로 상승된 다음, 실온으로 하강된다.

- [0248] 전술된 바와 같이, 본 실시형태의 트랜ジ스터는 채널 형성층으로서 산화물 반도체층을 포함하는 트랜지스터이다. 본 실시형태의 트랜지스터에 이용되는 산화물 반도체층은 열 처리에 의해 고순도화됨으로써, i형 또는 실질적으로 i형인 산화물 반도체층이 된다.

- [0249] 고순도화된 산화물 반도체층은 극히 적은 캐리어를 포함한다(제로에 가까움). 산화물 반도체층의 캐리어 농도는  $1 \times 10^{14} / \text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12} / \text{cm}^3$  미만, 더욱 바람직하게는  $1 \times 10^{11} / \text{cm}^3$  미만이다. 산화물 반도체층의 캐리어수가 극히 적기 때문에, 본 실시형태의 트랜지스터의 오프 전류가 저감될 수 있다. 오프 전류는 가능한 한 작은 것이 바람직하다. 본 실시형태의 트랜지스터에서는, 채널폭 1  $\mu\text{m}$ 당 오프 전류 밀도는  $10 \text{ aA} (1 \times 10^{-17} \text{ A} / \mu\text{m})$  이하, 바람직하게는  $1 \text{ aA} / \mu\text{m} (1 \times 10^{-18} \text{ A} / \mu\text{m})$  이하, 더욱 바람직하게는  $10 \text{ zA} (1 \times 10^{-20} \text{ A} / \mu\text{m})$  이하, 더욱 더 바람직하게는  $1 \text{ zA} (1 \times 10^{-21} \text{ A} / \mu\text{m})$  이하일 수 있다.

- [0250] 작은 오프 전류를 갖는 트랜지스터가, 예를 들어, 실시형태 1의 액정 표시 장치에서의 화소 트랜지스터로서 이용되면, 정지 화상을 표시할 때의 화상 데이터의 재기입 동작(리프레쉬라고도 함)의 횟수가 저감될 수 있다.

- [0251] 본 실시형태의 트랜지스터는 비교적 높은 전계 효과 이동도를 가지며 고속 구동이 가능하다. 따라서, 예를 들어, 본 실시형태의 트랜지스터가 실시형태 1의 표시 장치에 이용되면, 화상 품질이 향상될 수 있다. 본 실시형태의 트랜지스터를 실시형태 1의 표시 장치에 이용함으로써, 구동 회로부 및 화소부가 동일 기판 위에 제조될 수 있다. 따라서, 표시 장치의 부품수가 저감될 수 있고, 예를 들어, 표시 장치를 구부리는 경우에도 구동 회로부와 화소부 사이의 접속 불량의 발생이 방지될 수 있다.

- [0252] 본 실시형태는 임의의 다른 실시형태와 적절히 조합되거나 치환될 수 있다.

- [0253] (실시형태 4)

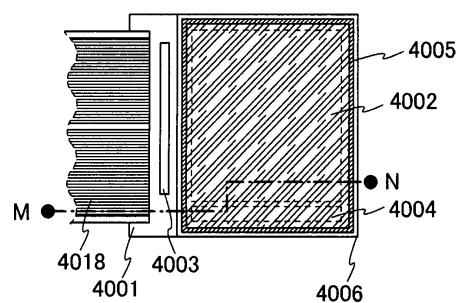

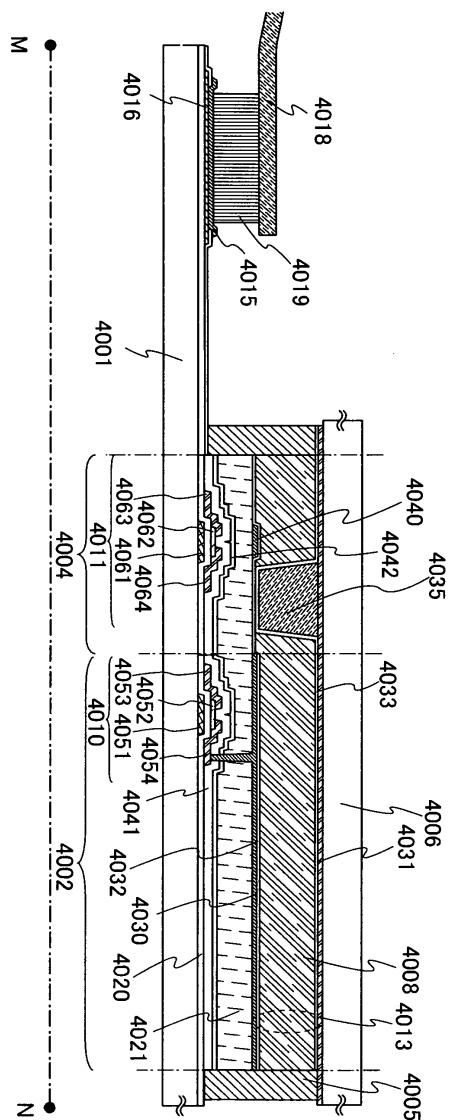

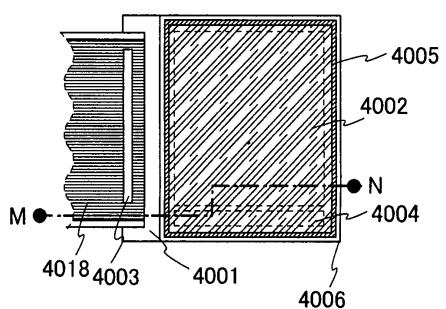

- [0254] 본 실시형태에서는, 상기 실시형태에서 설명된 액정 표시 장치의 예의 외관 및 단면을 도 12a 내지 도 12c를 참조하여 설명한다. 도 12a 내지 도 12c는 본 실시형태의 액정 표시 장치의 예를 나타낸다. 도 12a 및 도 12c는 평면도이고, 도 12b는 도 12a 또는 도 12c의 라인 M-N을 따른 단면도이다.

- [0255] 도 12a 내지 도 12c에 나타낸 액정 표시 장치에서, 제1 기판(4001) 위에 제공된 화소부(4002)와 주사선 구동 회로(4004)를 둘러싸도록 밀봉재(sealant, 4005)가 제공된다. 또한, 화소부(4002)와 주사선 구동 회로(4004) 위에 제2 기판(4006)이 제공된다. 따라서, 화소부(4002)와 주사선 구동 회로(4004)는 액정층(4008)과 함께, 제1 기판(4001)과 제2 기판(4006) 사이에서 밀봉재(4005)에 의해 밀봉된다. 또한, 도 12a 내지 도 12c에 나타낸 액정 표시 장치에서, 또 다른 기판 위에 단결정 반도체막 또는 다결정 반도체막을 이용하여 형성된 신호선 구동 회로(4003)는, 제1 기판(4001) 위의 밀봉재(4005)에 의해 둘러싸인 영역과는 상이한 영역에 탑재된다.

- [0256] 별도 형성된 구동 회로의 접속 방법에는 특별한 제한이 없다; COG 방법, 와이어 본딩 방법, TAB 방법 등이 이용될 수 있다. 도 12a는 COG 방법에 의해 신호선 구동 회로(4003)를 탑재하는 예를 나타내며, 도 12c는 TAB 방법에 의해 신호선 구동 회로(4003)를 탑재하는 예를 나타낸다.

- [0257] 제1 기판(4001) 위에 제공된 화소부(4002)와 주사선 구동 회로(4004) 각각은 복수의 트랜지스터를 포함한다. 도 12b에는, 화소부(4002)에 포함된 트랜지스터(4010)와 신호선 구동 회로(4004)에 포함된 트랜지스터(4011)가 예로서 나타나 있다. 트랜지스터(4010 및 4011) 위에는 절연층(4041, 4042, 및 4021)이 제공된다.

- [0258] 트랜지스터(4010 및 4011)로서, 실시형태 1의 액정 표시 장치와 같이, 채널 형성층으로서 기능하는 산화물 반도체층을 포함하는 트랜지스터가 이용될 수 있다; 예를 들어, 실시형태 3에서 설명된 트랜지스터가 이용될 수 있다.

- [0259] 트랜지스터(4010)는, 게이트 전극층(4051), 게이트 전극층(4051) 위에 제공된 게이트 절연층(4020), 게이트 절연층(4020)을 사이에 두고 게이트 전극층(4051) 위에 제공된 산화물 반도체층(4052), 및 산화물 반도체층(4052) 위에 제공된 소스 전극층(4053) 및 드레인 전극층(4054)을 포함한다.

- [0260] 트랜지스터(4011)는, 게이트 전극층(4061), 게이트 전극층(4061) 위에 제공된 게이트 절연층(4020), 게이트 절연층(4020)을 사이에 두고 게이트 전극층(4061) 위에 제공된 산화물 반도체층(4062), 및 산화물 반도체층(4062) 위에 제공된 소스 전극층(4063) 및 드레인 전극층(4064)을 포함한다.

- [0261] 트랜지스터(4011)의 산화물 반도체층(4062)의 채널 형성 영역과 중첩하도록 절연층(4021) 위에 도전층(4040)이 제공된다. 도전층(4040)을 산화물 반도체층(4062)의 채널 형성 영역과 중첩하도록 제공함으로써, BT시험에서 트랜지스터(4011)의 임계 전압의 변화량을 저감할 수 있다. 도전층(4040)의 전압은 트랜지스터(4011)의 게이트 전극층(4061)과 동일하거나 상이할 수 있으며, 도전층(4040)은 제2 게이트 전극층으로서 기능할 수 있다. 도전층(4040)의 전위는 접지 전위 또는 0 V이거나, 또는 도전층(4040)은 플로팅 상태일 수도 있다. 도전층(4040)은 반드시 제공될 필요는 없다.

- [0262] 화소 전극층(4030)은, 절연층(4041, 4042, 및 4021)의 개구를 통해 트랜지스터(4010)의 소스 전극층(4053) 또는 드레인 전극층(4054)에 전기적으로 접속되도록 제공된다. 대향 전극층(4031)은 제2 기판(4006) 위에 제공된다. 화소 전극층(4030)과 대향 전극층(4031)과 액정층(4008)이 서로 중첩하고 있는 부분이 액정 소자(4013)에 대응한다. 화소 전극층(4030) 및 대향 전극층(4031)에는 각각 배향막으로서 역할하는 절연층(4032) 및 절연층(4033)이 제공되고, 액정층(4008)은 화소 전극층(4030)과 대향 전극층(4031) 사이에 끼워져 있고, 이들 사이에는 절연층(4032 및 4033)이 개재되어 있다.

- [0263] 제1 기판(4001) 및 제2 기판(4006)으로서 투광성 기판이 이용될 수가 있다; 유리, 세라믹, 또는 플라스틱이 이용될 수 있다. 플라스틱으로서, FRP(fiberglass-reinforced plastics) 판, 폴리비닐 플루오라이드(PVF; polyvinyl fluoride) 필름, 폴리에스테르 필름, 또는 아크릴 수지 필름이 이용될 수 있다.

- [0264] 절연층들(4032 및 4033) 사이에는 스페이서(4035)가 제공된다. 스페이서(4035)는 절연막의 선택적 예칭에 의해 얻어지는 격벽이며, 화소 전극층(4030)과 대향 전극층(4031) 사이의 거리(셀 캡)를 제어하기 위해 제공된다. 스페이서(4035)로서 구형 스페이서(spherical spacer)가 이용될 수도 있다.

- [0265] 대향 전극층(4031)은 트랜지스터(4010)와 동일한 기판 위에 제공된 공통 전압선에 전기적으로 접속된다. 공통 전압선과의 접속부(공통 접속부라고도 함)를 이용하여 한 쌍의 기판 사이에 배치되는 도전성 입자를 통해 대향 전극층(4031)이 공통 전압선에 전기적으로 접속될 수 있다.

- [0266] 밀봉재(4005)는 도전성 입자를 포함한다.

- [0267] 본 실시형태의 액정 표시 장치에서, 액정층(4008)의 액정 재료로서 배향막을 요구하지 않는 블루상을 나타내는 액정을 이용할 수도 있다. 블루상은 액정상들 중 하나로서, 콜레스테릭 액정의 온도를 상승시키는 동안 콜레스테릭상이 등방상으로 전이되기 직전에 나타나는 상이다. 블루상은 좁은 온도 범위에서만 나타나기 때문에, 온도 범위를 넓히기 위해 5 중량% 이상의 카이럴제(chiral agent)를 포함하는 액정 조성물이 액정 재료로서 이용된다. 블루상을 나타내는 액정과 카이럴제를 포함하는 액정 조성물은 1 msec 이하의 짧은 응답 시간을 가지며, 광학적 등방성을 가지므로, 배향 처리가 불필요하고, 시야각 의존성이 작다. 또한, 배향막이 제공될 필요가 없고 러빙 처리(rubbing treatment)가 불필요하기 때문에, 러빙 처리에 의해 야기되는 정전 방전 손상이 방지될 수 있고 제조 공정에서 액정 표시 장치의 결함 및 손상이 저감될 수 있다. 따라서, 액정 표시 장치의 생산성이 증가될 수 있다. 특히 산화물 반도체층을 포함하는 트랜지스터는, 트랜지스터의 전기적 특성이 정전기로 인해 현저하게 변동하여 설계 범위를 벗어날 가능성을 가진다. 따라서, 산화물 반도체층을 포함하는 트랜지스터를 포함하는 액정 표시 장치에 대해 블루상을 나타내는 액정 재료를 이용함으로써, 정전기에 기인한 트랜지스터의 전기적 변동이 저감될 수 있다.

- [0268] 본 실시형태의 액정 표시 장치에서는, 기판의 외측(관찰자 측)에 편광판이 제공되고 기판의 내측 면에 착색층과 표시 소자에 이용되는 전극층이 순차적으로 제공될 수도 있다; 대안으로서, 편광판은 기판의 내측 면에 제공될 수도 있다. 편광판과 착색층의 적층 구조는, 편광판 및 착색층의 재료 및 제조 공정의 조건에 따라 적절하게 설정될 수도 있다. 또한, 표시부 이외의 부분에 블랙 매트릭스로서 역할하는 차광층이 제공될 수도 있다.

- [0269] 절연층(4041)은 산화물 반도체층(4052 및 4062)에 접한다. 절연층(4041)으로서, 예를 들어, 산화 실리콘층이 이용될 수 있다.

- [0270] 절연층(4041) 위에 접하여 절연층(4042)이 제공된다. 절연층(4042)으로서, 예를 들어, 절화 실리콘층이 이용될 수 있다.

- [0271] 절연층(4042) 위에는 절연층(4021)이 제공된다. 절연층(4021)은 트랜지스터의 표면의 요철을 저감하기 위한 평탄화 절연층으로서 기능한다. 절연층(4021)에 대해, 폴리이미드(polyimide), 아크릴(acrylic) 수지, 벤조시클로부텐(benzocyclobutene)계 수지, 폴리아미드(polyamide), 또는 에폭시(epoxy) 수지 등의, 내열성을 갖는 유기 재료가 이용될 수 있다. 이러한 유기 재료 외에도, 저유전율 재료(low-k 재료), 실록산계 수지(siloxane-based resin), PSG(phosphosilicate glass), BPSG(borophosphosilicate glass) 등을 이용하는 것도 가능하다. 이러한 재료로 형성된 복수의 절연막을 적층함으로써 절연층(4021)이 형성될 수도 있다.

- [0272] 절연층(4021)의 형성 방법에는 특별한 제한이 없다. 그 재료에 따라, 다음과 같은 방법이 이용될 수 있다: 스퍼터링법, SOG법, 스펀 코팅법, 딥핑법, 스프레이 도포법, 액적 토출법(예를 들어, 잉크젯법, 스크린 인쇄법, 또는 오프셋 인쇄법), 닉터 나이프를 이용한 형성법, 롤 코터를 이용한 형성법, 커텐 코더를 이용한 형성법, 나이프 코터를 이용한 형성법 등.

- [0273] 화소 전극층(4030) 및 대향 전극층(4031)은, 인듐 주석 산화물, 산화 인듐에 산화 아연을 혼합한 금속 산화물(인듐 아연 산화물(IZO)이라고도 함), 산화 인듐에 산화 실리콘( $\text{SiO}_2$ )을 혼합한 도전 재료, 유기 인듐, 유기 주석, 산화 텉스텐을 포함하는 인듐 산화물, 산화 텉스텐을 포함하는 인듐 아연 산화물, 산화 티타늄을 포함하는 인듐 산화물, 산화 티타늄을 포함하는 인듐 주석 산화물 등의 투광성의 도전성 재료의 층을 이용하여 형성될 수 있다. 본 실시형태의 액정 표시 장치가 반사형으로 형성되는 경우, 화소 전극층(4030) 및 대향 전극층(4031)으로서, 텉스텐, 몰리브덴, 지르코늄, 하프늄, 바나듐, 니오브, 탄탈, 크롬, 코발트, 니켈, 티타늄, 백금, 알루미늄, 구리, 또는 은 등의 금속, 또는 이러한 금속의 합금의 층이 이용될 수 있다. 화소 전극층(4030) 및 대향 전극층(4031)은 또한, 화소 전극층(4030) 및 대향 전극층(4031)에 적용될 수 있는 재료의 층들을 적층함으로써 형성될 수 있다.

- [0274] 화소 전극층(4030) 및 대향 전극층(4031)에 대하여, 도전성 고분자(도전성 폴리머라고도 함)를 포함하는 도전성 조성물이 이용될 수 있다. 도전성 조성물을 이용하여 형성된 화소 전극층은 10000 ohms/square 이하의 시트 저항(sheet resistance)과 과장 550 nm에서 70% 이상의 투광율을 갖는 것이 바람직하다. 또한, 도전성 조성물에 포함된 도전성 고분자의 저항율이 0.1  $\Omega \cdot \text{cm}$ 이하인 것이 바람직하다.

- [0275] 도전성 고분자로서, 이른바  $\pi$ -전자 결합( $\pi$ -electron conjugated) 도전성 고분자가 이용될 수 있다. 예를 들어, 폴리아닐린 또는 그 유도체, 폴리피롤 또는 그 유도체, 폴리티오펜 또는 그 유도체, 및 아닐린, 피롤, 및 티오펜 또는 그 유도체의 2개 이상의 공중합체 등을 들 수 있다.

- [0276] 또한, FPC(4018)로부터 다양한 신호 및 전압이, 별도 형성된 신호선 구동 회로(4003), 주사선 구동 회로(4004), 또는 화소부(4002)에 공급된다. FPC(4018)는 접속 단자 전극(4015) 및 이방성 도전막(4019)을 통해 단자 전극(4016)에 전기적으로 접속된다.

- [0277] 접속 단자 전극(4015)은 액정 소자(4013)의 화소 전극층(4030)과 동일한 도전막을 이용하여 형성되고, 단자 전극(4016)은 트랜지스터(4010)의 소스 전극층(4053) 또는 드레인 전극층(4054)과 동일한 도전막을 이용하여 형성된다.

- [0278] 접속 단자 전극(4015)은 이방성 도전막(4019)을 통해 FPC(4018)에 포함된 단자에 전기적으로 접속된다.

- [0279] 도 12a 내지 도 12c는, 신호선 구동 회로(4003)가 별도로 형성되어 제1 기판(4001) 위에 탑재된 예를 나타낸다; 그러나, 본 발명의 한 실시형태는 이 구조로 한정되는 것은 아니다. 주사선 구동 회로가 별도로 형성된 다음 탑재되거나, 신호선 구동 회로의 일부 또는 주사선 구동 회로의 일부만이 별도로 형성된 다음 탑재될 수도 있다.

- [0280] 또한, 도 12a 내지 도 12c에 나타낸 액정 표시 장치에는, 블랙 매트릭스(차광층); 편광 부재; 위상차 부재; 반사 방지 부재 등의 광학 부재(광학 기판) 등이 적절히 제공될 수 있다. 예를 들어, 광학 부재로서는, 편광 기판 및 위상차 기판을 이용함으로써 원형 편광이 얻어질 수도 있다. 또한, 광원으로서 백라이트 등이 이용될 수도 있다.

- [0281] 액티브 매트릭스 액정 표시 장치에서, 매트릭스로 배치된 화소 전극을 구동함으로써, 표시 패턴이 화면에 형성된다. 구체적으로는, 선택된 화소 전극과 그 화소 전극에 대응하는 대향 전극 사이에 전압이 인가되어, 화소 전극과 대향 전극 사이에 배치된 액정층이 광학적으로 변조된다. 이러한 광학적 변조는 관찰자에 의해 표시 패

턴으로서 인식된다.

[0282] 추가의 대안으로서, 액정 표시 장치의 동화상 특성을 개선하기 위하여, 복수의 LED(발광 다이오드) 광원 또는 복수의 EL 광원을 이용하여 백 라이트로서 면광원을 형성하고, 면광원의 각 광원을 1 프레임 기간에서 펄스화된 방식으로 독립적으로 구동하는 구동 기술이 이용될 수도 있다. 면광원으로서, 3 종류 이상의 LED가 이용되거나, 백색광을 방출하는 LED가 이용될 수도 있다. 복수의 LED가 독립적으로 제어될 수 있기 때문에, LED의 발광 타이밍은, 액정층이 광학적으로 변조되는 타이밍과 동기화될 수 있다. 이 구동 기술에서는, LED들 중 일부가 소등될 수 있어서, 한 화면에서 검정색 화상 면적의 비율이 높은 화상을 표시하는 경우에는, 전력 소비가 저감될 수 있다.

[0283] 이러한 구동 기술을 조합함으로써, 상기 실시형태에서 설명된 액정 표시 장치의 표시 특성이 향상될 수 있다.

[0284] 트랜지스터는 정전기 등으로 인해 파손되기 쉽기 때문에, 화소부 및 구동 회로부와 동일한 기판 위에 보호 회로를 제공하는 것이 바람직하다. 보호 회로는 산화물 반도체층을 포함하는 비선형 소자를 이용하여 형성하는 것이 바람직하다. 예를 들어, 보호 회로는 화소부와 주사선 입력 단자 사이에, 및 화소부와 신호선 입력 단자 사이에 제공된다. 본 실시형태에서는, 복수의 보호 회로가 제공되어, 정전기 등으로 인해 주사선, 신호선, 또는 용량 소자 버스 라인에 서지 전압이 인가될 때 화소 내의 트랜지스터 등이 파손되지 않는다. 따라서, 보호 회로는, 보호 회로에 서지 전압이 인가될 때 전하가 공통 배선으로 릴리스되도록 형성된다. 또한, 보호 회로는 주사선에 대해 병렬로 배치된 비선형 소자를 포함한다. 비선형 소자는, 다이오드 등의 2단자 소자, 또는 트랜지스터 등의 3단자 소자를 포함한다. 예를 들어, 비선형 소자는 화소부의 트랜지스터와 동일한 공정을 통해 형성될 수 있다. 예를 들어, 비선형 소자의 드레인 단자에 게이트를 접속함으로써 다이오드와 유사한 특성을 얻을 수 있다.

[0285] 본 실시형태의 액정 표시 장치의 표시 모드로서, 하기의 모드들이 이용될 수 있다: TN(twisted nematic) 모드, IPS(in-plane-switching) 모드, ASM(axially symmetric aligned micro-cell) 모드, OCB(optically compensated birefringence) 모드, FLC(ferroelectric liquid crystal) 모드, AFLC(antiferroelectric liquid crystal) 모드. 표시 모드는 전술된 것들로 한정되지 않으며, FFS(fringe field switching) 모드 등이 이용될 수도 있다.

[0286] 본 실시형태의 액정 표시 장치에 대해, TN 액정, OCB 액정, STN 액정, VA 액정, ECB 액정, GH 액정, 고분자 분산형 액정, 디스크오틱 액정 등을 이용할 수 있다. 본 실시형태의 액정 표시 장치는, 노멀리-블랙 액정 표시 장치, 예를 들어, 수직 배향(VA) 모드를 이용한 투과형 액정 표시 장치인 것이 바람직하다. 수직 배향 모드로서 몇 가지 예를 들 수 있다: 예를 들어, MVA(multi-domain vertical alignment) 모드, PVA(patterned vertical alignment) 모드, ASV 모드 등을 이용할 수 있다.

[0287] 이러한 방식으로, 본 실시형태의 액정 표시 장치를 제조할 수 있다. 본 실시형태에서 설명되는 액정 표시 장치의 구조에 의해, 전력 소비가 저감될 수 있다.

[0288] 본 실시형태는 임의의 다른 실시형태와 적절히 조합되거나 치환될 수 있다.

[0289] (실시형태 5)

[0290] 본 실시형태에서는, 상기 실시형태에서 설명된 액정 표시 장치의 예로서 터치 패널 기능이 부가된 액정 표시 장치를 설명한다.

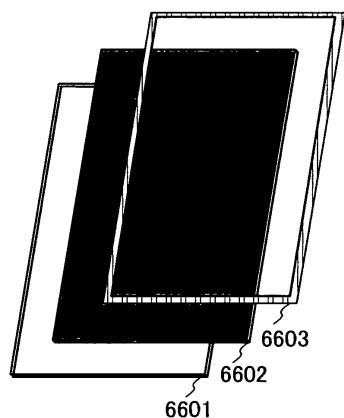

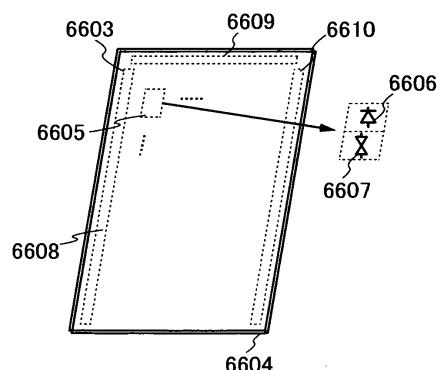

[0291] 본 실시형태의 액정 표시 장치의 구조를 도 13a 및 도 13b를 참조하여 설명한다. 도 13a 및 도 13b는 본 실시 형태의 액정 표시 장치의 구조예를 나타낸다.

[0292] 도 13a에 나타낸 액정 표시 장치는, 액정 표시 유닛(6601), 및 액정 표시 유닛(6601)과 중첩하도록 제공된 터치 패널 유닛(6602)을 포함한다. 액정 표시 유닛(6601)과 터치 패널 유닛(6602)은 하우징(케이스)(6603)에 의해 서로 부착된다.

[0293] 상기 실시형태에서 설명된 액정 표시 장치는 액정 표시 유닛(6601)에 적용될 수 있다.

[0294] 터치 패널 유닛(6602)으로서, 예를 들어, 저항식 터치 패널, 표면 정전용량식 터치 패널, 또는 투영형 정전용량식 터치 패널을 이용할 수 있다.

[0295] 도 13a에 나타낸 바와 같이, 본 실시형태의 액정 표시 장치의 한 예는, 서로 별개로 제조된 액정 표시 유닛과 터치 패널 유닛이 서로 중첩되어 있는 구조를 가진다. 이 구조에 의해, 터치 패널 기능이 부가된 액정 표시 장

치의 제조 비용이 저감될 수 있다.

[0296] 도 13b에 나타낸 액정 표시 장치(6604)는 표시부에 복수의 화소(6605)를 포함하고, 각 화소(6605)는 광센서(6606)와 액정 소자(6607)를 포함한다. 도 13b에 나타낸 액정 표시 장치(6604)는 다음과 같은 방식으로 센싱을 실시한다: 피검지물(예를 들어, 손가락이나 펜)을 이동시켜 화소(6605)의 광센서(6606)에 접촉하거나 근접시키면, 그 물체로부터 반사된 광에 따라 광센서(6606)에 의해 광전류가 발생된다. 도 13b에 나타낸 액정 표시 장치(6604)는, 도 13a에 나타낸 액정 표시 장치와는 달리, 터치 패널 유닛(6602)과 중첩될 필요가 없어서, 액정 표시 장치의 두께가 저감될 수 있다. 또한, 화소부(6605) 외에도, 주사선 구동 회로(6608), 신호선 구동 회로(6609), 및 광센서 구동 회로(6610)가 화소부(6605)와 동일한 기판 위에 형성될 수 있어서, 액정 표시 장치가 소형화될 수 있다. 광센서(6606)는, 아몰퍼스(amorphous) 실리콘 등을 이용하여 형성되며, 산화물 반도체를 포함하는 트랜지스터와 중첩될 수도 있다.

[0297] 본 실시형태의 터치 패널의 기능이 부가된 액정 표시 장치에서는 채널 형성층으로서 기능하는 산화물 반도체층을 포함하는 트랜지스터를 이용함으로써, 표시 장치가 정지 화상을 장시간 표시할 수 있다. 또한, 정지 화상이 표시되는 기간 동안에 구동 회로부의 동작이 중단될 수 있음으로써, 전력 소비가 저감될 수 있다.

[0298] 본 실시형태는 임의의 다른 실시형태와 적절히 조합되거나 치환될 수 있다.

[0299] (실시형태 6)

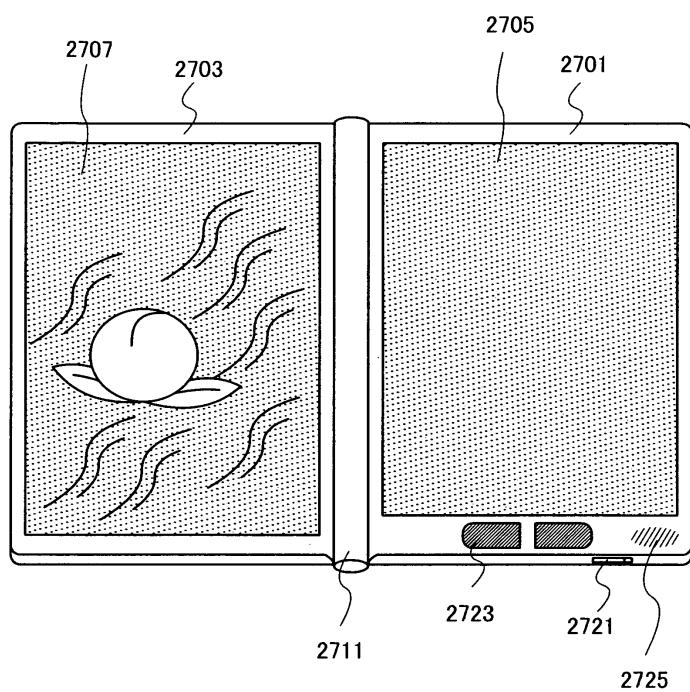

[0300] 본 실시형태에서는, 상기 실시형태에서 설명된 표시 장치의 예로서 전자서적 리더를 설명한다.

[0301] 본 실시형태의 전자서적 리더를 도 14를 참조하여 설명한다. 도 14는 본 실시형태의 전자서적 리더의 예를 나타낸다.

[0302] 도 14에 나타낸 전자서적 리더는, 2개의 하우징, 하우징(2701) 및 하우징(2703)을 포함한다. 하우징(2701) 및 하우징(2703)은 경첩부(2711)에 의해 접속되고, 경첩부(2711)를 축으로 하여 개방되거나 폐쇄될 수 있다. 이러한 구조에 의해, 전자서적 리더가 종이 서적처럼 동작할 수 있다.

[0303] 표시부(2705) 및 표시부(2707)는, 각각 하우징(2701) 및 하우징(2703)에 병합된다. 표시부(2705) 및 표시부(2707)는 상이한 화상들을 표시할 수도 있다. 하나의 화상이 표시부(2705)와 표시부(2707)에 걸쳐 표시될 수도 있다. 상이한 화상들을 표시하는 경우, 예를 들어, 우측의 표시부(도 14에서는 표시부(2705))에는 텍스트가 표시될 수 있고, 좌측의 표시부(도 14에서는 표시부(2707))에는 그래픽이 표시될 수 있다.

[0304] 도 14에 나타낸 전자서적 리더의 예는 하우징(2701)에 조작부 등을 갖추고 있다. 예를 들어, 하우징(2701)에는 전원 스위치(2721), 조작 키(2723), 스피커(2725) 등이 제공되고 있다. 조작 키(2723)에 의해, 페이지를 넘길 수 있다. 또한, 하우징의 표시부와 동일한 면에는, 키보드, 포인팅 장치 등이 제공될 수도 있다. 또한, 하우징의 이면이나 측면에는, 외부 접속용 단자(이어폰 단자, USB 단자, 또는 AC 어댑터 및 USB 케이블 등의 각종 케이블에 접속 가능한 단자 등), 기록 매체 삽입부 등이 제공될 수도 있다. 또한, 도 14에 나타낸 전자서적 리더에는, 전자 사전 기능이 제공될 수도 있다.

[0305] 본 실시형태의 전자서적 리더는 데이터를 무선으로 송신 및 수신할 수도 있다. 무선 통신을 통해, 전자서적 서버로부터 서적 데이터 등을 구입하여 다운로드할 수 있다.

[0306] 본 실시형태의 전자서적 리더는, 태양전지 셀, 태양전지 셀로부터 출력되는 전압을 충전하는 축전 장치, 및 축전 장치에 충전된 전압을 각 회로에 필요한 전압으로 변환하는 DC 변환기를 포함하는 전원 회로를 가질 수도 있다. 따라서, 외부 전원이 불필요하므로, 외부 전원이 없는 장소에서도, 전자서적 리더를 장시간 사용할 수 있어서, 편리성이 향상될 수 있다. 축전 장치로서, 리튬 이온 2차 전지, 리튬 이온 용량 소자, 전기 이중층 용량 소자, 및 레독스(redox) 용량 소자 등 중에서 하나 이상을 이용할 수 있다. 예를 들어, 리튬 이온 2차 전지 및 리튬 이온 용량 소자를 함께 이용함으로써, 고속으로 충전 또는 방전할 수 있고 장시간 전력을 공급할 수 있는 축전 장치가 형성될 수 있다. 축전 장치는 리튬 이온 2차 전지로 한정되는 것은 아니다. 축전 장치로서, 또 다른 알칼리 금속 이온, 알칼리 토류 금속 이온 등을 가동 이온(mobile ion)으로서 이용하는 2차 전지를 이용할 수도 있다. 리튬 이온 용량 소자에 관해서도 제한은 없다. 축전 장치로서, 또 다른 알칼리 금속 이온, 알칼리 토류 금속 이온 등을 가동 이온(mobile ion)으로서 이용하는 용량 소자를 이용할 수도 있다.

[0307] 본 실시형태의 전자서적 리더에서는 채널 형성층으로서 기능하는 산화물 반도체층을 포함하는 트랜지스터를 이용함으로써, 표시 장치가 정지 화상을 장시간 표시할 수 있어서, 전자서적 리더로 소정 정지 화상을 장시간 보는 경우에 특히 효과적이다. 또한, 정지 화상의 표시 기간 동안에 구동 회로부의 동작이 중단될 수

있음으로써, 전력 소비가 저감될 수 있다.

[0308] 본 실시형태는 임의의 다른 실시형태와 적절히 조합되거나 치환될 수 있다는 점에 유의한다.

[0309] (실시형태 7)

[0310] 본 실시형태에서는, 상기 실시형태에서 설명된 액정 표시 장치를 표시부에 갖는 전자 장치를 설명한다.

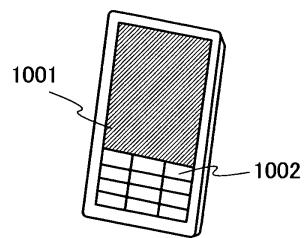

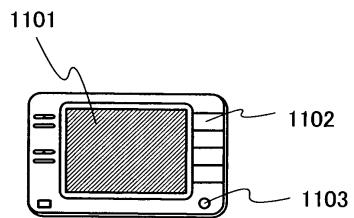

[0311] 상기 실시형태에서 설명된 액정 표시 장치를 다양한 전자 장치의 표시부에 적용함으로써, 전자 장치가 표시 기능 외에도 다양한 기능을 가질 수 있다. 상기 실시형태에 설명된 액정 표시 장치를 표시부에 적용한 전자 장치의 구체적인 예를 도 15a 내지 도 15f를 참조하여 설명한다. 도 15a 내지 도 15f는 각각 본 실시형태의 전자 장치의 구조예를 나타낸다.

[0312] 도 15a는 PDA(personal digital assistant)를 나타낸다. 도 15a에 나타낸 PDA는 적어도 표시부(1001)를 포함한다. 도 15a에 나타낸 PDA는, 예를 들어, 터치 패널 등과 조합될 수 있으며, 다양한 휴대품에 대한 대안으로서 이용될 수 있다. 예를 들어, 표시부(1001)가 조작부(1002)를 갖춤으로써, PDA가 휴대 전화로서 이용될 수 있다. 조작부(1002)는 표시부(1001)에 반드시 제공될 필요는 없고, 추가적인 조작 버튼이 제공될 수도 있다. 또한, PDA는 노트패드로서 이용되거나, 문서 입출력 기능을 이용함으로써 핸디 스캐너로서 이용될 수 있다. 또한, 상기 실시형태에서 설명된 액정 표시 장치는, 1회의 화상 데이터의 기입에 대한 표시 시간이 길기 때문에 기입 동작들 사이의 간격을 길게 할 수 있다. 따라서, 상기 실시형태에서 설명된 액정 표시 장치를 도 15a에 나타낸 PDA에 이용함으로써, 예를 들어, 표시부의 화상을 장시간 시청하는 경우에도, 야기되는 눈의 피로 수준이 낮게 될 수 있다.

[0313] 도 15b는, 예를 들어, 차량 내비게이션 시스템(automotive navigation system)을 포함하는 정보 안내 단말을 나타낸다. 도 15b에 나타낸 정보 안내 단말은 적어도 표시부(1101)를 가지며, 또한, 조작 버튼(1102), 외부 입력 단자(1103) 등을 가질 수 있다. 차량내 온도는 외부-공기 온도에 따라 크게 변동하며, 때때로 50°C를 초과한다. 상기 실시형태에서 설명된 액정 표시 장치의 온도에 기인한 특성 변화는 작기 때문에, 상기 실시형태에서 설명된 액정 표시 장치는 차량 내부 등의 온도가 크게 변동하는 환경 하에서 특히 효과적이다.

[0314] 도 15c는 랩톱 퍼스널 컴퓨터를 나타낸다. 도 15c에 나타낸 랩톱 퍼스널 컴퓨터는, 하우징(1201), 표시부(1202), 스피커(1203), LED 램프(1204), 포인팅 장치(1205), 접속 단자(1206), 및 키보드(1207)를 포함한다. 상기 실시형태에서 설명된 액정 표시 장치는, 1회의 화상 데이터의 기입에 대한 표시 시간이 길기 때문에 기입 동작들 사이의 간격을 길게 할 수 있다. 따라서, 상기 실시형태에서 설명된 액정 표시 장치를 도 15c에 나타낸 랩톱 퍼스널 컴퓨터에 이용함으로써, 예를 들어, 표시부의 화상을 장시간 시청하는 경우에도, 야기되는 눈의 피로 수준이 낮게 될 수 있다.

[0315] 도 15d는 휴대형 게임기를 나타낸다. 도 15d의 휴대형 게임기는, 제1 표시부(1301), 제2 표시부(1302), 스피커(1303), 접속 단자(1304), LED 램프(1305), 마이크로폰(1306), 기록 매체 판독부(1307), 조작 버튼(1308), 및 센서(1309)를 포함한다. 또한, 상기 실시형태에서 설명된 액정 표시 장치는, 1회의 화상 데이터의 기입에 대한 표시 시간이 길기 때문에 기입 동작들 사이의 간격을 길게 할 수 있다. 따라서, 상기 실시형태에서 설명된 액정 표시 장치를 도 15d에 나타낸 휴대형 게임기에 이용함으로써, 예를 들어, 표시부의 화상을 장시간 시청하는 경우에도, 야기되는 눈의 피로 수준이 낮게 될 수 있다. 또한, 제1 표시부(1301)와 제2 표시부(1302)에는 상이한 화상이 표시될 수 있다; 예를 들어, 이들 중 한편에는 동화상이 표시되고, 다른 한편에는 정지 화상이 표시된다. 따라서, 정지 화상을 표시하는 표시부에 대해 구동 회로부로의 신호 또는 전압의 공급이 중단될 수 있음으로써, 전력 소비가 저감될 수 있다.

[0316] 도 15e는 정지형 정보 통신 단말을 나타낸다. 도 15e에 나타낸 정지형 정보 통신 단말은 적어도 표시부(1401)를 포함한다. 표시부(1401)는 또한 평면부(1402)에 제공될 수 있다. 또한, 평면부(1402)에는 조작 버튼 등이 제공될 수 있다. 도 15e에 나타낸 정지형 정보 통신 단말은, 현금 자동 입출금기, 또는 (승차권을 포함한) 티켓 주문용 정보 통신 단말(멀티미디어 스테이션이라고도 함)으로서 이용될 수 있다. 상기 실시형태에서 설명된 액정 표시 장치는, 1회의 화상 데이터의 기입에 대한 표시 시간이 길기 때문에 기입 동작들 사이의 간격을 길게 할 수 있다. 따라서, 상기 실시형태에서 설명된 액정 표시 장치를 도 15e에 나타낸 정지형 정보 통신 단말에 이용함으로써, 예를 들어, 표시부의 화상을 장시간 시청하는 경우에도, 야기되는 눈의 피로 수준이 낮게 될 수 있다.

[0317] 도 15f는 디스플레이를 나타낸다. 도 15f에 나타낸 디스플레이는, 하우징(1501), 표시부(1502), 스피커(1503), LED 램프(1504), 조작 버튼(1505), 접속 단자(1506), 센서(1507), 마이크로폰(1508), 및 지지대(1509)를 포함

한다. 상기 실시형태에서 설명된 액정 표시 장치는, 1회의 화상 데이터의 기입에 대한 표시 시간이 길기 때문에 기입 동작들 사이의 간격을 길게 할 수 있다. 따라서, 상기 실시형태에서 설명된 액정 표시 장치를 도 15f에 나타낸 디스플레이에 이용함으로써, 예를 들어, 표시부의 화상을 장시간 시청하는 경우에도, 야기되는 눈의 피로 수준이 낮게 될 수 있다.

[0318] 상기 실시형태에서 설명된 액정 표시 장치를 전자 장치의 표시부에 적용함으로써, 다기능 전자 장치가 제공될 수 있다.

[0319] 본 실시형태는 임의의 다른 실시형태와 적절히 조합되거나 치환될 수 있다.

[0320] 본 출원은 2010년 1월 20일 일본 특허청에 출원된 출원번호 제2010-010419호에 기초하며, 그 전체 내용을 본 명세서에서 참조용으로 원용한다.

### 부호의 설명

[0321] 10: 펠스 출력 회로, 11: 배선, 12: 배선, 13: 배선, 14: 배선, 15: 배선, 17: 배선, 18: 배선, 21: 입력 단자, 22: 입력 단자, 23: 입력 단자, 24: 입력 단자, 25: 입력 단자, 26: 출력 단자, 27: 출력 단자, 31: 트랜지스터, 32: 트랜지스터, 33: 트랜지스터, 34: 트랜지스터, 35: 트랜지스터, 36: 트랜지스터, 37: 트랜지스터, 38: 트랜지스터, 39: 트랜지스터, 40: 트랜지스터, 41: 트랜지스터, 51: 전원선, 52: 전원선, 61: 기간, 62: 기간, 100: 액정 표시 장치, 101: 화상 처리 회로, 102: 보정 회로, 111: 메모리 회로, 111b: 프레임 메모리, 112: 비교 회로, 113: 표시 제어 회로, 115: 선택 회로, 120: 표시 패널, 121: 구동 회로부, 122: 화소부, 123: 화소, 124: 주사선, 125: 화상 신호선, 126: 단자부, 127: 트랜지스터, 130: 광원부, 131: 온도 검출 회로, 132: 계수 회로, 133: 계수값 비교 회로, 210: 용량 소자, 214: 트랜지스터, 215: 액정 소자, 400a: 기판, 400b: 기판, 400c: 기판, 400d: 기판, 401a: 게이트 전극층, 401b: 게이트 전극층, 401c: 게이트 전극층, 401d: 게이트 전극층, 402a: 게이트 절연층, 402b: 게이트 절연층, 402c: 게이트 절연층, 402d: 게이트 절연층, 403a: 산화물 반도체층, 403b: 산화물 반도체층, 403c: 산화물 반도체층, 403d: 산화물 반도체층, 405a: 소스 전극층, 405b: 소스 전극층, 405c: 소스 전극층, 405d: 소스 전극층, 406a: 드레인 전극층, 406b: 드레인 전극층, 406c: 드레인 전극층, 406d: 드레인 전극층, 407a: 산화물 절연층, 407c: 산화물 절연층, 409a: 보호 절연층, 409b: 보호 절연층, 409c: 보호 절연층, 411: 기간, 412: 기간, 413: 기간, 414: 기간, 427: 절연층, 436: 배선층, 437: 배선층, 447: 하지층, 516: 산화물 절연층, 530: 산화물 반도체막, 601: 기간, 602: 기간, 603: 기간, 604: 기간, 1001: 표시부, 1002: 조작부, 1101: 표시부, 1102: 조작 버튼, 1103: 외부 입력 단자, 1201: 하우징, 1202: 표시부, 1203: 스피커, 1204: LED 램프, 1205: 포인팅 장치, 1206: 접속 단자, 1207: 키보드, 121A: 구동 회로, 121B: 구동 회로, 1301: 표시부, 1302: 표시부, 1303: 스피커, 1304: 접속 단자, 1305: LED 램프, 1306: 마이크로폰, 1307: 기록 매체 판독부, 1308: 조작 버튼, 1309: 센서, 1401: 표시부, 1402: 평면부, 1501: 하우징, 1502: 표시부, 1503: 스피커, 1504: LED 램프, 1505: 조작 버튼, 1506: 접속 단자, 1507: 센서, 1508: 마이크로폰, 1509: 지지대, 2701: 하우징, 2703: 하우징, 2705: 표시부, 2707: 표시부, 2711: 경첩부, 2721: 전원 스위치, 2723: 조작 키, 2725: 스피커, 4001: 기판, 4002: 화소부, 4003: 신호선 구동 회로, 4004: 주사선 구동 회로, 4005: 밀봉재, 4006: 기판, 4008: 액정층, 4010: 트랜지스터, 4011: 트랜지스터, 4013: 액정 소자, 4015: 접속 단자 전극, 4016: 단자 전극, 4018: FPC, 4019: 이방성 도전막, 4020: 게이트 절연층, 4021: 절연층, 4030: 화소 전극층, 4031: 대향 전극층, 4032: 절연층, 4033: 절연층, 4035: 스페이서, 4040: 도전층, 4041: 절연층, 4042: 절연층, 4051: 게이트 전극층, 4052: 산화물 반도체층, 4053: 소스 전극층, 4054: 드레인 전극층, 4061: 게이트 전극층, 4062: 산화물 반도체층, 4063: 소스 전극층, 4064: 드레인 전극층, 6505: 화소, 6601: 액정 표시 유닛, 6602: 터치 패널 유닛, 6603: 하우징, 6604: 액정 표시 장치, 6605: 화소, 6606: 광센서, 6607: 액정 소자, 6608: 주사선 구동 회로, 6609: 신호선 구동 회로, 및 6610: 광센서 구동 회로.

## 도면

## 도면1

## 도면2

도면3

도면4a

도면4b

도면5

도면6a

## 도면6b

## 도면7

## 도면8a

도면8b

도면8c

도면9

도면10a

도면10b

도면10c

도면10d

## 도면11

## 도면12a

### 도면12b

도면12c

도면13a

도면13b

도면14

도면15a

도면15b

도면15c

도면15d

도면15e

도면15f

|                |                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 显示装置驱动方法和液晶显示装置                                                               |         |            |

| 公开(公告)号        | <a href="#">KR101750126B1</a>                                                      | 公开(公告)日 | 2017-06-22 |

| 申请号            | KR1020127018662                                                                    | 申请日     | 2010-12-20 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                       |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                 |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                 |         |            |

| [标]发明人         | HAYAKAWA MASAHIKO<br>하야까와마사히꼬<br>WAKIMOTO KENICHI                                  |         |            |

| 发明人            | 하야까와마사히꼬<br>와끼모도겐이찌                                                                |         |            |

| IPC分类号         | G09G3/36 G11C19/28                                                                 |         |            |

| CPC分类号         | G09G3/36 G09G3/3655 G11C19/28 G09G2320/041 G09G2320/103 G09G2330/021 G09G2340/0435 |         |            |

| 代理人(译)         | Jangsugil<br>Bakchungbeom<br>Yijunghui                                             |         |            |

| 优先权            | 2010010419 2010-01-20 JP                                                           |         |            |

| 其他公开文献         | <a href="#">KR1020120115521A</a>                                                   |         |            |