(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0070563

(43) 공개일자 2008년07월30일

(51) Int. Cl.

G02F 1/136 (2006.01) G02F 1/133 (2006.01)

(21) 출원번호 10-2008-0007710

(22) 출원일자 2008년01월24일

심사청구일자 2008년01월24일

(30) 우선권주장

JP-P-2007-00014660 2007년01월25일 일본(JP)

(71) 출원인

엡슨 이미징 디바이스 가부시키가이샤

일본국 나가노肯 아즈미노시 도요시나 다자와

6925

(72) 발명자

호리구치 마사히로

일본국 나가노肯 아즈미노시 도요시나 다자와

6925 엡슨 이미징디바이스 가부시키가이샤 내

카네코 히데키일본국 나가노肯 아즈미노시 도요시나 다자와

6925 엡슨 이미징디바이스 가부시키가이샤 내

(74) 대리인

특허법인태평양

전체 청구항 수 : 총 8 항

(54) 액정 표시 장치 및 그 제조 방법

**(57) 요약**

본 발명의 액정 표시 장치(10A)의 제조 방법은, 평탄화막(18)의 표면에 서브 화소마다 화소 전극(19a)을 형성하고, 그 다음에 표면 전체에 걸쳐 절연막(20)을 형성하고, 이 절연막(20)의 표면으로부터 드레인 전극 D, 공통 배선(common line)의 접속부(16<sub>1</sub>) 및 화소 전극(19a)이 노출하도록 제1 ~ 제3 컨택트 홀(contact hole)(21a ~ 21c)을 동시에 형성하고, 그 다음에 표면 전체에 걸쳐 투명 도전성 재료로 이루어진 막을 형성한 후, 서브 화소마다 복수의 슬릿(slit)을 갖는 공통 전극(22a)을 형성하고, 제1 컨택트 홀(21a)을 통하여 공통 전극(22)과 접속부(16<sub>1</sub>) 사이, 제2 컨택트 홀(21b), 절연막(20)상 및 제3 컨택트 홀(21c)을 거치는 인터페이스 구조의 도전로(23)를 통하여 화소 전극(19a)과 드레인 전극 D를 각각 접속하는 공정을 구비한다. 이와 같은 구성을 구비하는 것에 의해, 단일 공정으로 복수의 컨택트 홀을 동시에 형성할 수 있는, 평탄화막상에 화소 전극 및 공통 전극을 배치한 FFS(Fringe Field Switching) 모드의 액정 표시 장치 및 그 제조 방법을 제공할 수 있게 된다.

**대표도** - 도1

## 특허청구의 범위

### 청구항 1

액정층을 끼운 한 쌍의 투명 기판을 구비하고, 상기 한 쌍의 투명 기판 중 한쪽의 상기 액정층측에는, 표시 영역에 매트릭스 형상으로 배치된 복수의 주사선 및 신호선과, 복수의 상기 주사선 및 신호선의 교차점 근방에 마련된 스위칭 소자와, 상기 표시 영역의 주연부(周緣部)를 따라서 형성된 공통 배선(common line)과, 적어도 표시 영역의 전체에 걸쳐 형성된 평탄화막과, 상기 평탄화막의 표면에 형성된 제1 전극과, 상기 제1 전극상에 형성된 절연막과, 상기 절연막상에 형성되고, 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 복수의 슬릿(slit)을 갖는 제2 전극이 형성되어 있고, 상기 제2 전극은 상기 절연막 및 평탄화막에 형성된 제1 컨택트 홀을 통하여 상기 공통 배선 또는 스위칭 소자에 전기적으로 접속되어 있고, 상기 제1 전극은 상기 절연막에 형성된 제2 컨택트 홀, 상기 절연막의 표면, 상기 절연막 및 평탄화막에 형성된 제3 컨택트 홀을 거치도록 형성된 상기 제2 전극과 동일한 재료로 형성된 인터페이스 구조의 도전로를 거쳐, 제2 전극과는 다른 상기 스위칭 소자 또는 공통 배선에 전기적으로 접속되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 2

청구항 1에 있어서, 상기 제1 전극은 상기 표시 영역의 평탄화막의 표면에 있어서 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 형성되어 있고, 각각의 상기 제1 전극은 복수의 상기 스위칭 소자의 각각에 전기적으로 접속되어 있고, 상기 제2 전극은 상기 절연막의 적어도 표시 영역의 표면 전체에 걸쳐 형성되어 있는 동시에 상기 공통 배선에 접속되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 3

청구항 2에 있어서, 상기 인터페이스 구조의 도전로는 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 4

청구항 2에 있어서, 상기 제2 전극과 상기 공통 배선의 접속 개소(箇所)는 복수 개 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 5

청구항 1에 있어서, 상기 제1 전극은 상기 표시 영역의 평탄화막의 표면 전체에 걸쳐 형성되어 있는 동시에 상기 공통 배선에 접속되어 있고, 상기 제2 전극은 상기 표시 영역의 절연막의 표면에 있어서 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 형성되어 있고,

각각의 상기 제2 전극은 복수의 상기 스위칭 소자의 각각에 전기적으로 접속되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 6

청구항 5에 있어서,

상기 인터페이스 구조의 도전로는 상기 공통 배선과 상기 표시 영역의 경계부에 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 7

청구항 5에 있어서,

상기 인터페이스 구조의 도전로는 복수 개 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 8

(1) 표시 영역에 매트릭스 형상으로 형성된 복수의 주사선 및 신호선과, 복수의 상기 주사선 및 신호선의 교차 점 근방에 마련된 스위칭 소자와, 상기 표시 영역의 주연부를 따라서 형성된 공통 배선을 구비하는 제1 투명 기판을 준비하는 공정,

(2) 상기 제1 투명 기판의 적어도 표시 영역의 전체에 걸쳐 평탄화막을 형성하는 공정,

(3) 상기 평탄화막의 표면에 제1 전극을 형성하는 공정,

(4) 상기 (3)의 공정을 거친 제1 투명 기판의 표면 전체에 걸쳐 절연막을 형성하는 공정,

(5) 상기 절연막 및 평탄화막에 상기 스위칭 소자 및 공통 배선이 노출하도록 제1 및 제3 컨택트 홀을 형성하는 동시에, 상기 절연막에 상기 제1 전극이 노출하도록 제2 컨택트 홀을 형성하는 공정,

(6) 상기 (5)의 공정에서 얻어진 투명 기판의 표면 전체에 걸쳐 도전성 재료로 이루어진 막을 형성한 후 에칭하는 것에 의해, 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 복수의 슬릿을 갖는 제2 전극을 형성하는 동시에, 상기 제1 컨택트 홀을 통하여 상기 제2 전극과 상기 스위칭 소자 또는 공통 배선을 전기적으로 접속하고, 상기 제2 컨택트 홀, 상기 절연막상 및 상기 제3 컨택트 홀을 거치도록 형성된 인터페이스 구조의 도전로를 거쳐 상기 제1 전극과 상기 공통 배선 또는 스위칭 소자를 전기적으로 접속하는 공정,

(7) 상기 (6)의 공정에서 얻어진 제1 투명 기판의 표면에 제2 투명 기판을 소정 거리 사이를 두고 대향 배치시키고, 상기 제1 및 제2 투명 기판 사이에 액정을 봉입(封入)하는 공정을 갖는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 기술분야

<1> 본 발명은 제조 공정수를 늘리지 않고 제조할 수 있는, 평탄화막상에 화소 전극 및 공통 전극을 배치한 높은 개구율(開口率) 및 높은 표시 화질을 달성할 수 있는 FFS 모드의 액정 표시 장치 및 그 제조 방법에 관한 것이다.

#### 배경기술

<2> 액정 표시 장치는, 표면에 전극 등이 형성된 한 쌍의 투명 기판과, 이 한 쌍의 기판 사이에 끼워진 액정층을 갖고, 양 기판상의 전극에 전압을 인가하는 것에 의해 액정을 재배열시키고 각종 정보를 표시하는 세로 방향 전계 방식인 것이 많이 사용되고 있다. 이와 같은 세로 방향 전계 방식의 액정 표시 장치는 TN(Twisted Nematic) 모드의 것이 일반적이나, 시야각이 좁다고 하는 문제점이 존재하기 때문에, VA(Vertical Alignment) 모드나 MVA(Multidomain Vertical Alignment) 모드 등, 각종 개량된 세로 방향 전계 방식의 액정 표시 장치가 개발되고 있다.

<3> 한편, 상술한 세로 방향 전계 방식의 액정 표시 장치와는 달리, 한쪽 기판에만 화소 전극 및 공통 전극으로 이

루어진 한 쌍의 전극을 구비한 IPS(In-Plane Switching) 모드 내지 FFS 모드의 액정 표시 장치도 알려져 있다.

- <4> 이 중 IPS 모드의 액정 표시 장치는 한 쌍의 전극을 동일 층에 배치하고, 액정에 인가하는 전계의 방향을 기판에 거의 평행한 방향으로 하여 액정 분자를 기판에 평행한 방향으로 재배열하는 것이다. 그렇기 때문에, 이 IPS 모드의 액정 표시 장치는 횡방향 전계 방식의 액정 표시 장치라고도 불리며, 상술한 세로 방향 전계 방식의 액정 표시 장치와 비교하면 매우 광시야각이라고 하는 이점을 가지고 있다. 그렇지만, IPS 모드의 액정 표시 장치는 액정에 전계를 인가하기 위해 한 쌍의 전극이 동일 층에 마련되어 있기 때문에, 화소 전극의 상측에 위치하는 액정 분자는 충분히 구동되지 않아, 투과율 등의 저하를 초래한다고 하는 문제점이 존재하고 있다.

- <5> 이와 같은 IPS 모드의 액정 표시 장치의 문제점을 해결하기 위해, 이른바 경상 전계 방식이라고도 해야 할 FFS 모드의 액정 표시 장치가 개발되고 있다(하기 특허 문현 1 및 2 참조). 이 FFS 모드의 액정 표시 장치는 액정층에 전계를 인가하기 위한 화소 전극과 공통 전극을 각각 절연막을 통하여 다른 층에 배치한 것이다.

- <6> 이 FFS 모드의 액정 표시 장치는 IPS 모드의 액정 표시 장치보다 광시야각에 고(高)컨트라스트이고, 또한 저전압 구동이 가능한 동시에 보다 고투과율이기 때문에 밝은 표시가 가능하게 된다고 하는 특징을 구비하고 있다. 또한, FFS 모드의 액정 표시 장치는 IPS 모드의 액정 표시 장치보다 평면에서 보아 화소 전극과 공통 전극의 중복 면적이 크기 때문에, 보다 큰 유지 용량이 부차적으로 생겨서 별도 보조 용량선을 마련할 필요가 없어진다고 하는 장점도 존재하고 있다.

- <7> [특허 문현 1] 일본 특개 2001-235763호 공보

- <8> [특허 문현 2] 일본 특개 2002-182230호 공보

## 발명의 내용

### 해결 하고자하는 과제

- <9> 그러나, 종래의 FFS 모드의 액정 표시 장치는 스위칭 소자나 공통 배선과 겹치는 화소 전극의 표면에는 단차(段差)가 형성되어 있기 때문에, 그 단차의 부분에서는 액정 분자의 배향이 흐트러져 버린다. 그렇기 때문에, 종래의 FFS 모드의 액정 표시 장치에 있어서, 단차의 부분은 실질적으로 표시에 기여하지 않는 영역이 되므로, 컬러 필터 기판에 있어서 블랙 매트릭스(black matrix)에 의해 차광할 필요가 있기 때문에, 이 단차의 부분만큼 개구율이 저하해 버린다.

- <10> 이와 같은 단차를 없애기 위해서는 상술한 VA 방식 내지 MVA 방식의 액정 표시 장치에서 사용되고 있는 평탄화막을 사용하여, 이 평탄화막상에 화소 전극이나 공통 전극을 배치하는 것도 생각할 수 있다. 그러나, 이와 같은 구성을 채용하면, 스위칭 소자 및 공통 배선은 평탄화막의 하부에 형성되어 있기 때문에, 화소 전극과 스위칭 소자 사이 및 공통 전극과 공통 배선 사이를 전기적으로 접속하기 때문에 컨택트 홀을 2 개소(箇所) 형성할 필요가 생긴다. 이 2 개소의 컨택트 홀은 화소 전극 및 공통 전극이 다른 층에 배치되어 있기 때문에, 통상은 동시에 형성하지 못하여, 각각 별개의 공정으로 형성할 필요가 있다고 하는 문제점이 존재한다.

- <11> 본 발명은, 이상의 점을 감안하여 이루어진 것으로, 평탄화막상에 화소 전극 및 공통 전극을 배치했을 때에, 단일 공정으로 복수의 컨택트 홀을 형성할 수 있고, 고개구율이며 표시 화질이 양호한 FFS 모드의 액정 표시 장치를 제공하는 것을 목적으로 한다.

### 과제 해결수단

- <12> 상기 목적을 달성하기 위해, 본 발명의 액정 표시 장치는, 액정층을 끼운 한 쌍의 투명 기판을 구비하고, 상기 한 쌍의 투명 기판 중 한쪽의 상기 액정층측에는, 표시 영역에 매트릭스 형상으로 배치된 복수의 주사선 및 신호선과; 복수의 상기 주사선 및 신호선의 교차점 근방에 마련된 스위칭 소자와; 상기 표시 영역의 주연부(周緣部)를 따라서 형성된 공통 배선과; 적어도 표시 영역의 전체에 걸쳐 형성된 평탄화막과; 상기 평탄화막의 표면에 형성된 제1 전극과; 상기 제1 전극상에 형성된 절연막과; 상기 절연막상에 형성되고, 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 복수의 슬릿을 갖는 제2 전극이 형성되어 있고, 상기 제2 전극은 상기 절연막 및 평탄화막에 형성된 제1 컨택트 홀을 통하여 상기 공통 배선 또는 스위칭 소자에 전기적으로 접속되어 있고, 상기 제1 전극은 상기 절연막에 형성된 제2 컨택트 홀, 상기 절연막의 표면, 상기 절연막 및 평탄화막에 형성된 제3 컨택트 홀을 거치도록 형성된 상기 제2 전극과 동일한 재료로 형성된 인터페이스 구조의 도전로를 거쳐, 제2 전극과는 다른 상기 스위칭 소자 또는 공통 배선에 전기적으로 접속되어 있는 것을 특징으로

한다.

- <13> 본 발명의 액정 표시 장치에 있어서는, 절연막의 표면에 마련되는 제2 전극은 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다(이하, 「서브 화소 영역마다」라고 함) 복수의 슬릿을 갖는 것이 필요하다. 본 발명의 액정 표시 장치는 이 슬릿을 통하여 서브 화소 영역마다 제1 전극과 제2 전극 사이에 인가되는 전계에 의해 프린지 필드 효과(fringe field effect)를 발휘시킬 수 있다.

- <14> 이 복수의 슬릿은 서로 평행한 방향으로 형성되어 있을 필요가 있으나, 하나의 화소내에서 다른 복수의 방향으로 형성되어 있는 군(群)이 존재하고 있어도 상관없다. 이와 같은 구성으로 하면, 시각에 따른 화질의 변화를 저감하는 것이 가능하게 된다.

- <15> 또, 본 발명에 있어서는 제1 전극 및 제2 전극으로서, ITO(Indium Thin Oxide) 또는 IZO(Indium Zinc Oxide) 등을 사용할 수 있다. 이 경우, 제1 전극과 제2 전극은 동일한 조성의 것이어도 다른 조성의 것이어도 된다.

- <16> 또, 본 발명에 있어서는 스위칭 소자로서 p-Si(폴리 실리콘(poly silicon))형의 박막 트랜지스터(TFT : Tin Film Transistor) 소자, a-Si(아모퍼스 실리콘(amorphous silicon))형의 TFT 소자, 저온 폴리 실리콘(LTPS : Low Temperature Poly Silicon)형의 TFT 소자 등의 3단자형 소자, 또는 박막 다이오드(TFD : Thin Film Diode) 소자 등으로 대표되는 2 단자형 비선행 소자 등을 사용할 수 있다.

- <17> 또, 본 발명에 있어서 평탄화막은 적어도 표면이 평탄성을 갖는 투명한 절연막이면 사용할 수 있고, 예를 들어 아크릴 수지나 폴리이미드 등의 투명 수지를 사용할 수 있다. 또한, 본 발명에 있어서 절연막으로서는 산화 규소나 질화 규소 등의 무기 절연막을 사용할 수 있다.

- <18> 그리고, 본 발명의 액정 표시 장치에 의하면, 컨택트 홀은 3 개소 형성되어 있으나, 이들 컨택트 홀은 모두 제1 전극상의 절연막을 관통하고 있기 때문에, 한 번의 공정으로 3 개소의 컨택트 홀을 동시에 형성할 수 있다. 또한, 본 발명의 액정 표시 장치에 의하면, 인터페이스 구조의 도전로는 제2 전극과 동일한 재료로 형성되어 있기 때문에, 제2 전극의 형성과 동시에 각 컨택트 홀을 통하여 제1 전극과 스위칭 소자 또는 공통 배선과의 사이, 제2 전극과 공통 배선 또는 스위칭 소자 사이의 전기적 도통을 달성할 수 있다. 그렇기 때문에, 본 발명의 액정 표시 장치에 의하면, 특히 제조 공정수를 늘리지 않고 제조할 수 있는 평탄화막상에 제1 전극 및 제2 전극이 형성된 FFS 모드의 액정 표시 장치를 제공할 수 있다.

- <19> 또, 본 발명의 액정 표시 장치에 의하면, 제1 전극과 제2 전극 사이의 절연막은 보조 용량을 형성하는 유전체막으로서 기능한다. 그렇기 때문에, 본 발명의 액정 표시 장치에 의하면, 이 절연막의 두께를 조정하는 것에 의해 보조 용량의 크기를 용이하게 조정할 수 있게 된다. 예를 들어, 각 화소의 면적을 작게 하여 고정밀화된 액정 표시 장치로 하는 경우 등, 단위 면적당의 보조 용량을 크게 할 필요가 있는 경우, 유전체로서 기능하는 절연막의 두께를 얇게 하는 것에 의해 충분한 크기의 보조 용량을 얻을 수 있다.

- <20> 또한, 전계 강도는 제1 전극과 제2 전극 사이에 인가되는 전압이 일정하면 전극간 거리에 반비례하여 커지기 때문에, 절연막의 두께를 얇게 하면 제1 전극과 제2 전극 사이의 전계 강도가 강해진다. 그렇기 때문에, 절연막의 두께를 얇게 하면, 제1 전극과 제2 전극 사이에 인가되는 전압을 낮게 해도 액정 분자를 구동하기 위한 소정의 전계 강도를 얻을 수 있다. 따라서, 본 발명의 액정 표시 장치에 의하면, 표시 품질이 향상되는 동시에, 저전압 구동이 가능하게 되고, 또한 저소비 전력화를 도모할 수 있는 액정 표시 장치를 제공할 수 있다.

- <21> 또한, 본 발명의 액정 표시 장치에 의하면, 스위칭 소자 및 공통 배선의 표면은 평탄화막에 의해 피복되어 있기 때문에, 제2 전극에는 종래예의 FFS 모드의 액정 표시 장치와 같은 단차가 생기지 않는다. 그렇기 때문에, 본 발명의 액정 표시 장치에 의하면, 다른 쪽의 투명 기판과 제2의 전극 사이의 간격, 즉 셀 갭(cell gap)이 균일하게 되고, 또한 표시 영역내에 있어서 블랙 매트릭스로 차광해야 하는 영역의 면적이 감소하기 때문에 개구율이 커진다. 따라서, 본 발명의 액정 표시 장치에 의하면, 밝고 표시 화질이 양호한, 소형화 및 고정밀화된 액정 표시 장치로서 바람직하게 사용할 수 있는 FFS 모드의 액정 표시 장치가 얻어진다.

- <22> 또, 상기 발명의 한 형태에 의하면, 상기 제1 전극은 상기 표시 영역의 평탄화막의 표면에 있어서 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 형성되어 있고, 각각의 상기 제1 전극은 복수의 상기 스위칭 소자의 각각에 전기적으로 접속되어 있고, 상기 제2 전극은 상기 절연막의 표시 영역의 표면 전체에 걸쳐 형성되어 있는 동시에 상기 공통 배선에 접속되어 있는 것을 특징으로 한다.

- <23> 이 형태의 액정 표시 장치에 의하면, 절연막 표면의 제2 전극을 공통 전극으로 하는 동시에, 절연막의 하면의 서브 화소 영역마다 형성된 제1 전극을 스위칭 소자에 접속된 화소 전극으로 한, 상기 본 발명의 효과를 나타내

는 FFS 모드의 액정 표시 장치가 얻어진다.

<24> 또, 상기 발명의 다른 형태에 의하면, 상기 인터페이스 구조의 도전로는 상기 서브 화소 영역마다 형성되어 있는 것을 특징으로 한다.

<25> 이 형태의 액정 표시 장치에 의하면, 화소 전극으로서 기능하는 서브 화소 영역마다의 제1 전극을 절연막의 표면에 있어서 제2 전극과의 사이에 절연 상태를 확보하면서 스위칭 소자에 전기적으로 접속할 수 있다.

<26> 또, 상기 발명의 다른 형태에 의하면, 상기 제2 전극과 상기 공통 배선의 접속 개소는 복수 개 형성되어 있는 것을 특징으로 한다.

<27> 이 형태의 액정 표시 장치에 의하면, 제2 전극과 공통 배선간의 접속 저항을 작게 할 수 있기 때문에, 공통 배선을 거쳐 제2 전극에 인가되는 신호가 배선 저항에 의해 열화하는 정도를 작게 할 수 있기 때문에 표시 화질이 양호한 액정 표시 장치가 얻어진다.

<28> 또, 상기 발명의 다른 형태에 의하면, 상기 제1 전극은 상기 표시 영역의 평탄화막의 표면 전체에 걸쳐 형성되어 있는 동시에 상기 공통 배선에 접속되어 있고, 상기 제2 전극은 상기 표시 영역의 절연막의 표면에 있어서 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 형성되어 있고, 각각의 상기 제2 전극은 복수의 상기 스위칭 소자의 각각에 전기적으로 접속되어 있는 것을 특징으로 한다.

<29> 이 형태의 액정 표시 장치에 의하면, 절연막의 표면의 서브 화소 영역마다 형성된 제2 전극을 스위칭 소자에 접속된 화소 전극으로 하는 동시에, 절연막의 하면의 제1 전극을 공통 배선에 접속된 공통 전극으로 한, 상기 본 발명의 효과를 나타내는 FFS 모드의 액정 표시 장치가 얻어진다.

<30> 또, 상기 발명의 다른 형태에 의하면, 상기 인터페이스 구조의 도전로는 상기 공통 배선과 상기 표시 영역의 경계부에 형성되어 있는 것을 특징으로 한다.

<31> 이 형태의 액정 표시 장치에 의하면, 화소 전극으로서 기능하는 제2 전극은 표시 영역에만 형성되기 때문에, 공통 전극으로서 기능하는 제1 전극을 절연막의 표면에 있어서 제2 전극의 사이에 절연 상태를 확보하면서 공통 배선에 전기적으로 접속할 수 있다.

<32> 또, 상기 발명의 다른 형태에 의하면, 상기 인터페이스 구조의 도전로는 복수 개 형성되어 있는 것을 특징으로 한다.

<33> 이 형태의 액정 표시 장치에 의하면, 제1 전극과 공통 배선 사이의 접속 저항을 작게 할 수 있기 때문에, 공통 배선을 거쳐 제1 전극에 인가되는 신호가 배선 저항에 의해 열화하는 정도를 작게 할 수 있기 때문에, 표시 화질이 양호한 액정 표시 장치가 얻어진다.

<34> 또한, 상기 목적을 달성하기 위해, 본 발명의 액정 표시 장치의 제조 방법은, 이하의 (1) ~ (7)의 공정을 갖는 것을 특징으로 한다.

<35> 이하의 (1) ~ (7)의 공정을 갖는 것을 특징으로 하는 액정 표시 장치의 제조 방법으로서,

<36> (1) 표시 영역에 매트릭스 형상으로 형성된 복수의 주사선 및 신호선과, 복수의 상기 주사선 및 신호선의 교차점 근방에 마련된 스위칭 소자와, 상기 표시 영역의 주연부를 따라서 형성된 공통 배선을 구비하는 제1 투명 기판을 준비하는 공정,

<37> (2) 상기 제1 투명 기판의 표시 영역 전체에 걸쳐 평탄화막을 형성하는 공정,

<38> (3) 상기 평탄화막의 표면에 제1 전극을 형성하는 공정,

<39> (4) 상기 (3)의 공정을 거친 제1 투명 기판의 표면 전체에 걸쳐 절연막을 형성하는 공정,

<40> (5) 상기 절연막 및 평탄화막에 상기 스위칭 소자 및 공통 배선이 노출하도록 제1 및 제3 컨택트 홀을 형성하는 동시에, 상기 절연막에 상기 제1 전극이 노출하도록 제2 컨택트 홀을 형성하는 공정,

<41> (6) 상기 (5)의 공정에서 얻어진 투명 기판의 표면 전체에 걸쳐 도전성 재료로 이루어진 막을 형성한 후 예칭하는 것에 의해, 상기 복수의 주사선 및 신호선으로 구획된 영역에 대응하는 위치마다 복수의 슬릿을 갖는 제2 전극을 형성하는 동시에, 상기 제1 컨택트 홀을 통하여 상기 제2 전극과 상기 스위칭 소자 또는 공통 배선을 전기적으로 접속하고, 상기 제2 컨택트 홀, 상기 절연막상 및 상기 제3 컨택트 홀을 거치도록 형성된 인터페이스 구조의 도전로를 거쳐 상기 제1 전극과 상기 공통 배선 또는 스위칭 소자를 전기적으로 접속하는 공정,

<42> (7) 상기 (6)의 공정에서 얻어진 제1 투명 기판의 표면에 제2 투명 기판을 소정 거리 사이를 두고 대향 배치시키고, 상기 제1 및 제2 투명 기판 사이에 액정을 봉입(封入)하는 공정.

### 효과

<43> 본 발명의 액정 표시 장치의 제조 방법에 의하면, 제1 ~ 제3 컨택트 홀을 동일한 공정으로 제조할 수 있기 때문에, 특히 제조 공정수를 늘리지 않고 상기 발명의 효과를 나타내는 액정 표시 장치를 제조할 수 있다.

### 발명의 실시를 위한 구체적인 내용

<44> 이하, 도면을 참조하여 본 발명의 바람직한 실시 형태를 실시예로서 설명한다. 단, 이하에 나타내는 실시예는 본 발명의 기술 사상을 구체화하기 위한 액정 표시 장치로서 FFS 모드의 액정 표시 장치를 예시하는 것으로서, 본 발명을 이 FFS 모드의 액정 표시 장치에 특정하는 것을 의도하는 것이 아니라, 특히 청구의 범위에 포함되는 그 밖의 실시 형태의 것에도 동일하게 적용할 수 있는 것이다.

<45> [실시예 1]

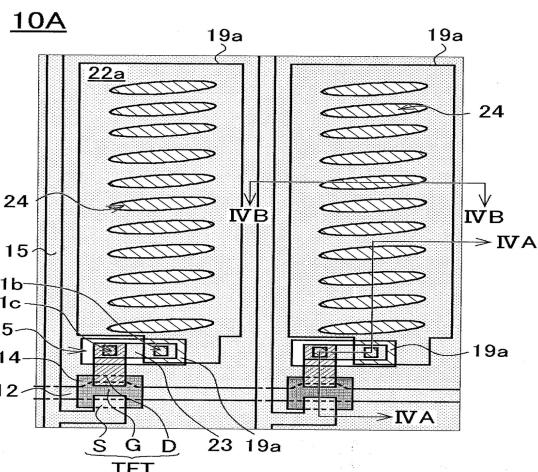

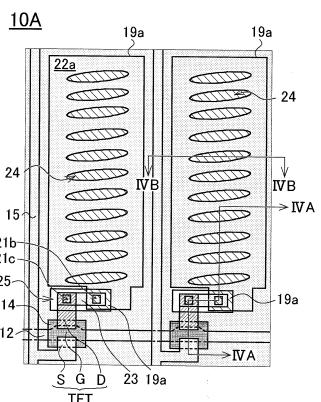

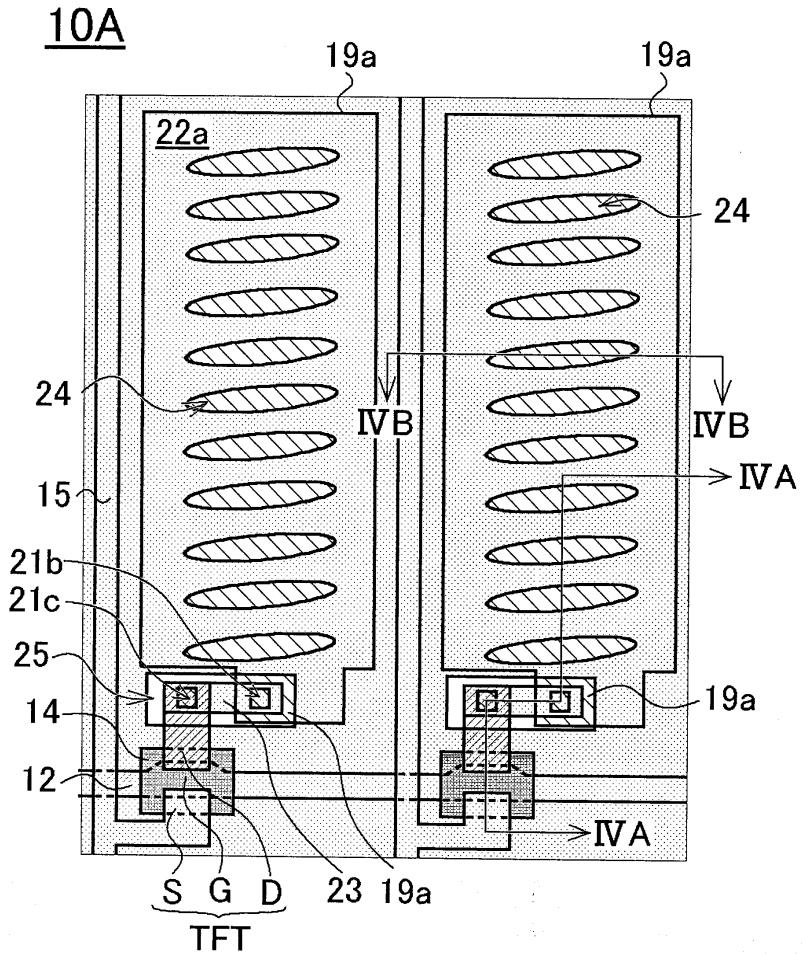

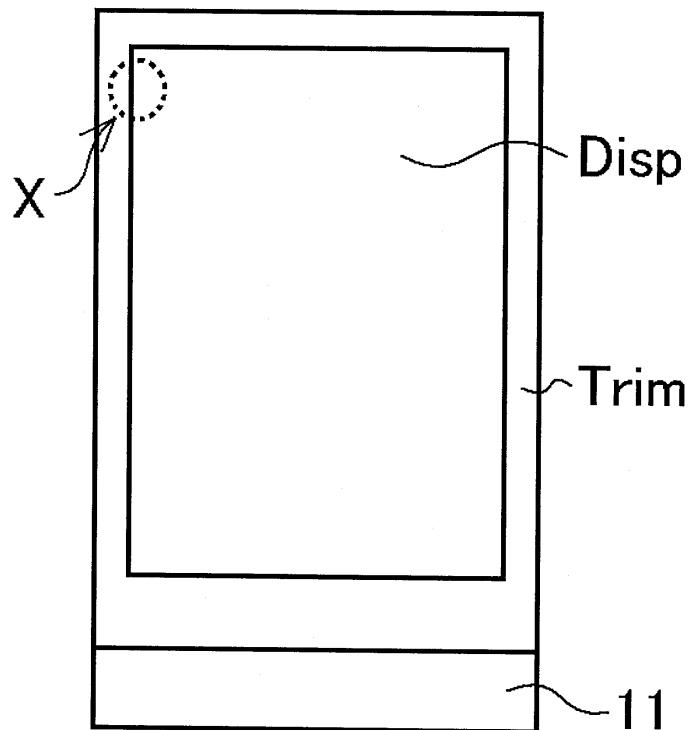

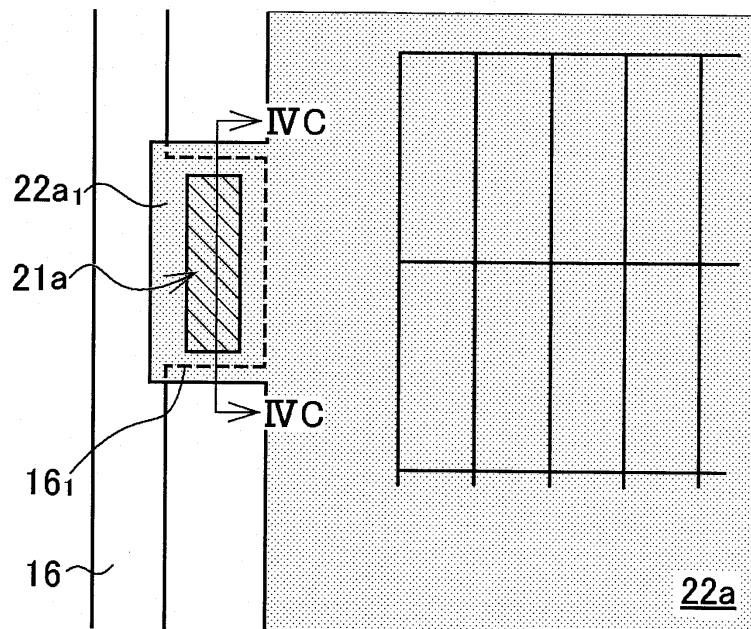

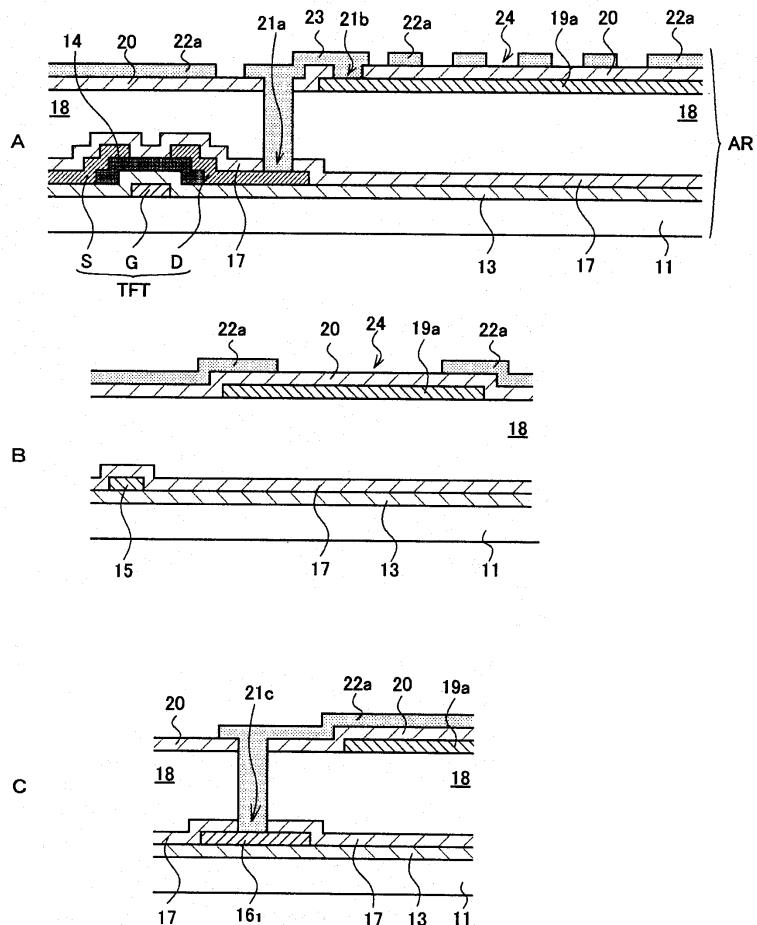

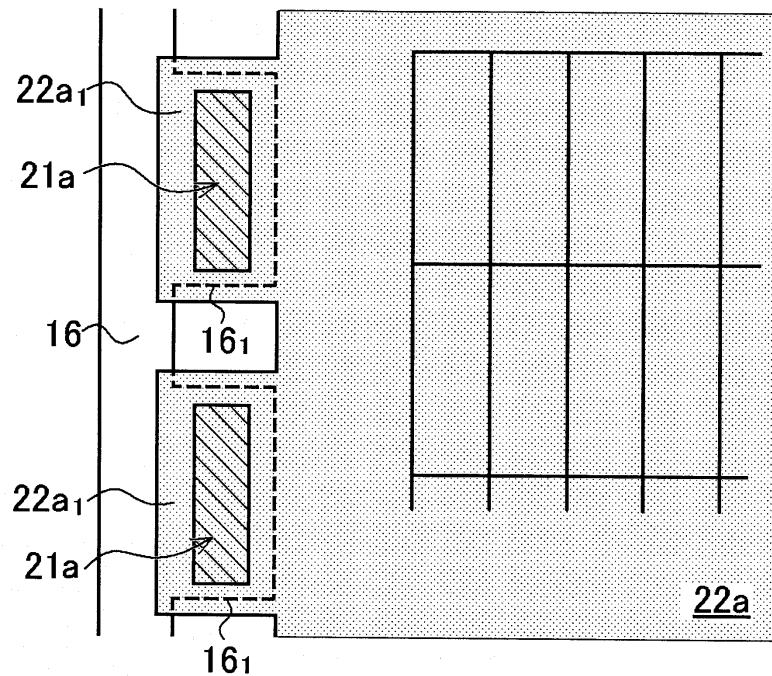

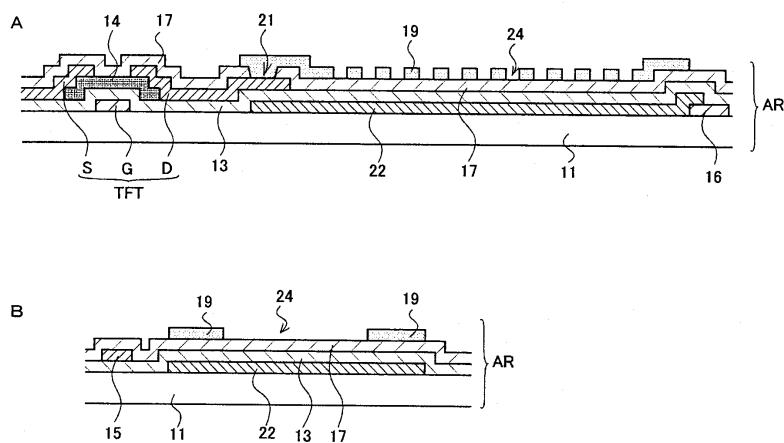

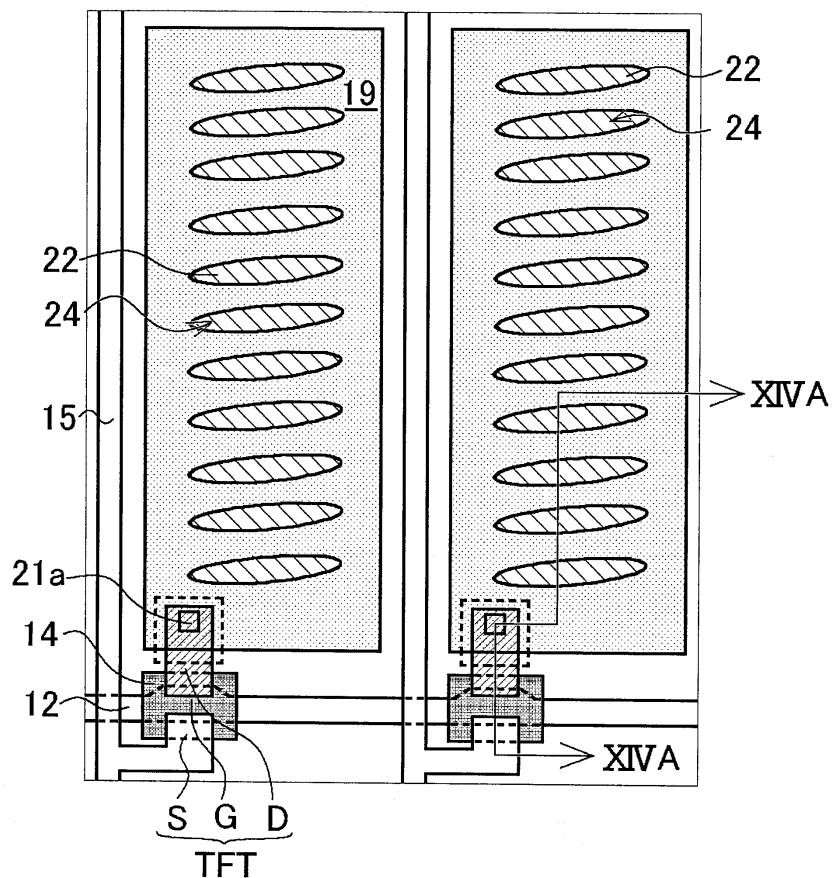

<46> 실시예 1의 FFS 모드의 액정 표시 장치로서, 평탄화막을 갖고, 상전극을 공통 전극으로 하여 공통 배선에 접속한 FFS 모드 액정 표시 장치의 예를 제조 공정순으로 도 1 ~ 도 5를 사용하여 설명한다. 또한, 도 1은 실시예 1의 액정 표시 장치(10A)의 어레이 기판의 2 화소분의 모식 평면도이다. 도 2는 실시예 1의 액정 표시 장치의 공통 배선과 공통 전극의 접속 위치 X를 나타내는 도면이다. 도 3은 실시예 1의 액정 표시 장치(10A)의 X 부분에 있어서 어레이 기판의 확대 평면도이다. 도 4A는 도 1의 IVA-IVA 선을 따른 모식 단면도, 도 4B는 도 1의 IVB-IVB 선을 따른 모식 단면도, 도 4C는 도 3의 IVC-IVC 선을 따른 모식 단면도이다. 또, 도 5는 실시예 1의 액정 표시 장치의 변형예에 있어서 X 부분의 어레이 기판의 확대 평면도이다.

<47> 이 실시예 1의 FFS 모드의 액정 표시 장치(10A)에 있어서 어레이 기판 AR의 제조시에 있어서는 처음에 유리 기판 등의 투명 기판(11)의 표면 전체에 걸쳐 금속막 등의 전도성층을 형성한다. 그 후, 주지된 포토리소그래피(photolithography)법 및 에칭법에 의해, 표시 영역에 복수의 주사선(12)을 서로 평행하게 되도록 형성하는 동시에, 표시 영역의 주위(이하, 「액자 영역」이라고 함)에 게이트 배선(도시하지 않음)을 형성한다. 이 게이트 배선은 반드시 주사선용의 배선으로서 사용되는 것이 아니라, 주사선과 동일한 재질의 배선이기 때문에 「게이트 배선」이라고 불리고 있는 것이고, 적절하게 각종의 배선용으로 사용되는 것이다.

<48> 계속해서, 이 표면 전체에 질화 규소층 내지 산화 규소층으로 이루어진 게이트 절연막(13)을 피복한다. 그 후, CVD법에 의해 예를 들어, 아모페스 실리콘(이하, 「a-Si」라고 함)층을 게이트 절연막(13)의 표면 전체에 걸쳐 피복한 후, 마찬가지로 포토리소그래피법 및 에칭법에 의해 TFT 형성 영역에 a-Si 층으로 이루어진 반도체층(14)을 형성한다. 이 반도체층(14)이 형성되어 있는 위치의 주사선(12)의 영역이 TFT의 게이트 전극 G를 형성한다.

<49> 계속해서, 금속막으로 구성된 도전성층(14)을 형성한 투명 기판(11)의 표면 전체에 걸쳐 피복한다. 또한, 그 금속막으로 구성된 도전성층을 포토리소그래피법 및 에칭법에 의해, 표시 영역(D<sub>isp</sub>)에 있어서 주사선(12)에 직교하도록 소스 전극 S을 포함하는 신호선(15)을 형성하고, TFT 형성 영역에 드레인 전극 D를 형성하고, 또한 액자 영역 T<sub>rim</sub>에 소스 배선(도시하지 않음) 및 공통 배선(16)을 형성한다. 이 공통 배선(16)에는 이하에 나타내는 공통 전극(22a)과의 접속 위치 X(도 2 참조)에 대응하는 위치에 부분적으로 폭이 넓게 된 접속부(16<sub>1</sub>)가 형성되어 있다. 또한, 신호선(15)의 소스 전극 S 부분 및 드레인 전극 D 부분은 모두 반도체층(14)의 표면에 부분적으로 겹쳐져 있다.

<50> 그 후, 상기 공정에서 얻어진 투명 기판(11)의 표면 전체에 패시베이션막(passivation film)(17)을 피복한다. 이 패시베이션막(17)으로서는 질화 규소층 내지 산화 규소층으로 이루어진 것을 사용할 수 있으나, 절연성의 관점에서는 질화 규소층의 쪽이 바람직하다. 또한, 패시베이션막(17)의 표면 전체에, 예를 들어 아크릴 수지 내지 폴리이미드 수지로 이루어진 평탄화막(층간막이라고도 불림)(18) 및 ITO 내지 IZO로 이루어진 투명 도전성층을 순차적으로 적층한다.

<51> 계속해서, 투명 도전성층에 대해, 포토리소그래피법 및 에칭법에 의해, 서브 화소 영역마다 화소 전극(19a)을 형성한다. 실시예 1의 액정 표시 장치(10A)에 있어서는 이 화소 전극(19a)이 본 발명의 제1 전극에 대응한다.

<52> 또한, 화소 전극(19a)이 형성된 기판(11)의 표면 전체에 걸쳐 질화 규소층 내지 산화 규소층으로 이루어진 절연

막(20)을 소정의 두께로 형성한다. 이 절연막(20)은, 화소 전극(19a)과 후의 공정에서 절연막(20)의 표면에 형성되는 투명한 공통 전극 사이에서 보조 용량을 형성하는 유전체막으로서 기능한다. 그렇기 때문에, 이 절연막의 두께를 적절히 조정하는 것에 의해 보조 용량의 크기가 원하는 값이 되도록 조정할 수 있다.

<53> 계속해서, 이 절연막(20)의 표면으로부터 절연막(20), 평탄화막(18) 및 패시베이션막(17)을 관통하여 공통 배선(16)의 접속부(16<sub>1</sub>)의 표면에 도달하는 제1 컨택트 홀(21a), 절연막(20)을 관통하여 화소 전극(19a)의 표면에 도달하는 제2 컨택트 홀(21b), 절연막(20), 평탄화막(18) 및 패시베이션막(17)을 관통하여 드레인 전극 D의 표면에 도달하는 제3 컨택트 홀(21c)을 각각 동시에 형성한다. 이 컨택트 홀(21a ~ 21c)의 형성에는 건식 에칭법의 일종인 플라즈마 에칭법을 채용할 수 있다.

<54> 계속해서, 컨택트 홀(21a ~ 21c)이 형성된 기판(11)의 표면 전체에 걸쳐 ITO내지 IZO로 이루어진 투명 도전성층을 형성한다. 이 때, 투명 도전성층에 의해 컨택트 홀(21a ~ 21c)을 통하여 공통 배선(16), 화소 전극(19a) 및 드레인 전극 D는 서로 전기적으로 접속된 상태가 된다.

<55> 그 후, 포트리소그래피법 및 에칭법에 의해, 상기 투명 도전성층을 에칭하는 것에 의해 표시 영역의 실질적으로 전체를 피복하는 공통 전극(22a)을 형성한다. 이 때 동시에, 공통 전극(22a)에는 서브 화소 영역마다 서로 평행하게 프린지 필드 효과를 발생시키기 위한 복수의 슬릿(24)을 형성하는 동시에, 도전로(23)의 주위에 틀 형상의 절결부(25)를 마련하여 도전로(23)와 공통 전극(22a)을 전기적으로 절연한다. 또, 이 공통 전극(22a)에는 공통 배선(16)과 공통 전극(22a)의 접속 위치 X에 있어서, 평면에서 보아 공통 배선(16)의 부분적으로 폭이 넓게 된 접속부(16<sub>1</sub>)와 중복하도록 접속부(22a<sub>1</sub>)가 형성된다. 또한, 도 3에 있어서는 슬릿(24) 및 틀 형상의 절결부(25)는 도시 생략되어 있다. 실시예 1의 액정 표시 장치(10A)에 있어서는 이 공통 전극(22a)이 본 발명의 제2 전극에 대응한다.

<56> 이와 같이 하여, 공통 전극(22a)은 제1 컨택트 홀(21a)을 통하여 공통 배선(16)과 전기적으로 접속되고, 화소 전극(19a)은 제2 컨택트 홀(21b), 도전로(23) 및 제3 컨택트 홀(21c)을 거쳐 TFT의 드레인 전극 D에 접속된다. 이 후, 공통 전극(22a)측의 표면 전체에 배향막(도시하지 않음)을 마련하는 것에 의해 실시예 1의 액정 표시 장치(10A)의 어레이 기판 AR이 완성된다.

<57> 상기의 어레이 기판 AR에 대향하는 컬러 필터 기판은 도시를 생략하였으나, 종래의 FFS 모드의 액정 표시 패널용의 컬러 필터 기판과 실질적으로 동양(同様)인 것을 사용할 수 있다. 즉, 이 컬러 필터 기판은 각각의 화소 전극에 대향하는 위치에는 각 색의 컬러 필터층이 형성되고, 그리고 컬러 필터층의 표면에는 배향막이 마련되어 있다. 그리고, 컬러 필터층과 투명 기판 사이의 주사선(12) 및 신호선(15)에 대향하는 위치, TFT에 대향하는 위치에는 각각 블랙 매트릭스가 마련되어 있다.

<58> 특히, 실시예 1의 액정 표시 장치(10A)용의 컬러 필터 기판으로 하려면, 상기의 도전로(23) 내지 틀 형상의 절결부(25)에 대향하는 위치에 추가로 블랙 매트릭스를 마련하는 것에 의해, 이 부분으로부터의 누출광을 차광하도록 하면 된다. 계속해서, 상술한 어레이 기판 및 컬러 필터 기판을 각각 대향시켜 내부에 액정을 봉입하는 것에 의해 실시예 1의 액정 표시 장치(10A)가 얻어진다.

<59> 이와 같이 하여 제조된 실시예 1의 액정 표시 장치(10A)에 의하면, 컨택트 홀은 3 개소 형성되어 있으나, 이들 컨택트 홀은 모두 화소 전극(19a)상의 절연막(20)을 관통하고 있기 때문에, 한 번의 공정으로 3 개소의 컨택트 홀을 동시에 형성할 수 있다. 또한, 이 액정 표시 장치(10A)에 의하면, 인터페이스 구조의 도전로(23)는 공통 전극(22a)과 동일한 재료로 형성되어 있기 때문에, 공통 전극(22a)의 형성과 동시에 각 컨택트 홀(21a ~ 2c)을 통하여 각 화소 전극(19a)과 드레인 전극 D 사이, 공통 전극(22a)과 공통 배선(16) 사이의 전기적 도통을 달성을 할 수 있다. 그렇기 때문에, 실시예 1의 액정 표시 장치(10A)에 의하면, 특히 제조 공정수를 늘리지 않고 제조 할 수 있는, 평탄화막(18)상에 화소 전극(19a) 및 공통 전극(22a)이 형성된 FFS 모드의 액정 표시 장치(10A)가 얻어진다.

<60> 또, 실시예 1의 액정 표시 장치(10A)에 의하면, 화소 전극(19a)과 공통 전극(22a) 사이의 절연막(20)은 보조 용량을 형성하는 유전체막으로서 기능한다. 그렇기 때문에, 이 절연막(20)의 두께를 조정하는 것에 의해 보조 용량의 크기를 용이하게 조정할 수 있게 된다. 또한, 전계 강도는 화소 전극(19a)과 공통 전극(22a) 사이에 인가되는 전압이 일정하면, 전극간 거리에 반비례하여 커지기 때문에, 절연막(20)의 두께를 얇게 하면 화소 전극(19a)과 공통 전극(22a) 사이의 전계 강도가 강해진다. 그렇기 때문에, 절연막(20)의 두께를 얇게 하면, 화소 전극(19a)과 공통 전극(22a) 사이에 인가되는 전압을 낮게 해도 액정 분자를 구동하기 위한 소정의 전계 강도를 얻을 수 있다. 따라서, 실시예 1의 액정 표시 장치(10A)에 의하면, 표시 품질이 향상되는 동시에, 저전압 구동

이 가능하게 되고, 또한 저소비 전력화를 도모할 수 있는 액정 표시 장치(10A)가 얻어진다.

<61> 또한, 실시예 1의 액정 표시 장치(10A)에 의하면, TFT 등의 표면은 평탄화막에 의해 피복되어 있기 때문에, 공통 전극(22a)에는 종래예의 FFS 모드의 액정 표시 장치와 같은 단차가 생기지 않는다. 그렇기 때문에, 실시예 1의 액정 표시 장치(10A)에 의하면, 도시하지 않는 컬러 필터 기판과 공통 전극(22a) 사이의 간격, 즉 셀 캡이 균일하게 되며, 또한 표시 영역내에 있어서 블랙 매트릭스로 차광하는 영역의 면적이 감소하기 때문에 개구율이 커진다. 따라서, 실시예 1의 액정 표시 장치(10A)에 의하면, 밝고 표시 화질이 양호하며, 소형화 및 고정밀화된 액정 표시 장치로서 바람직하게 사용할 수 있는 FFS 모드의 액정 표시 장치(10A)가 얻어진다.

<62> [실시예 2]

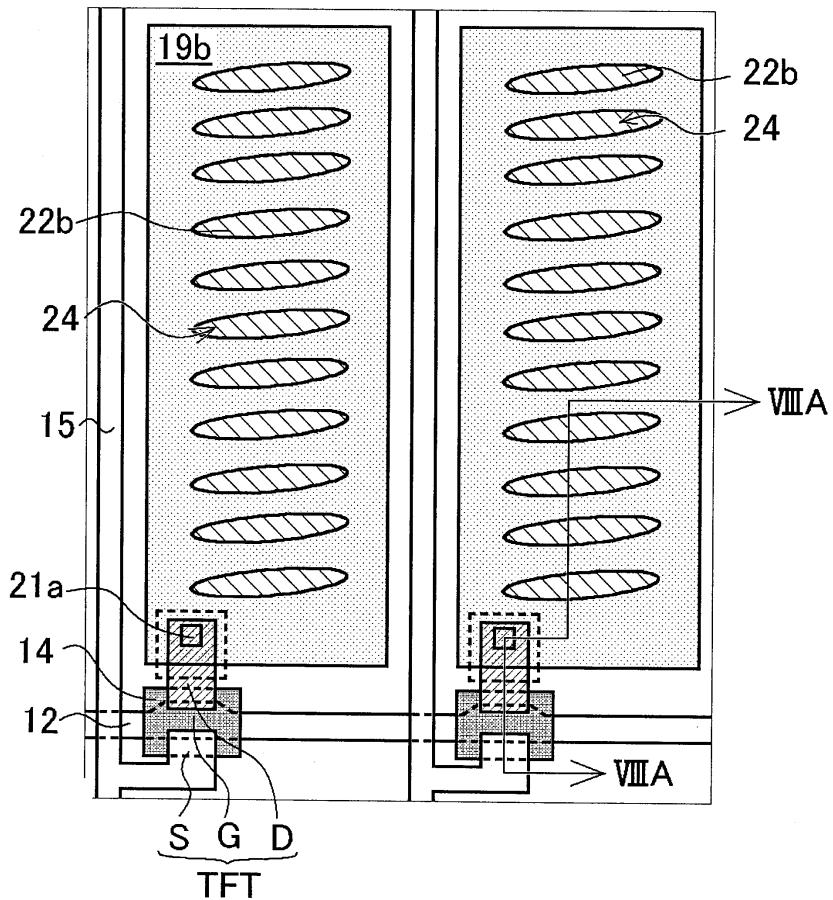

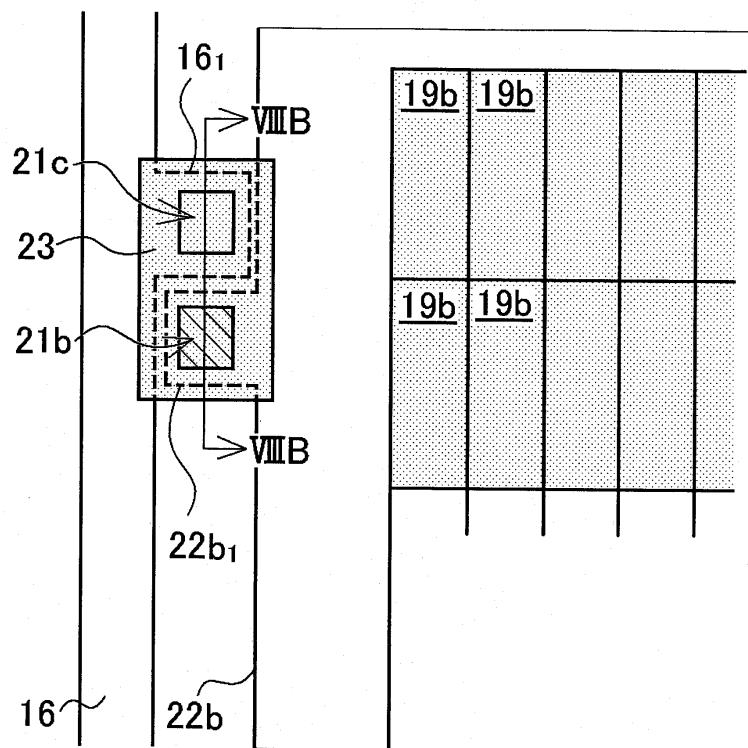

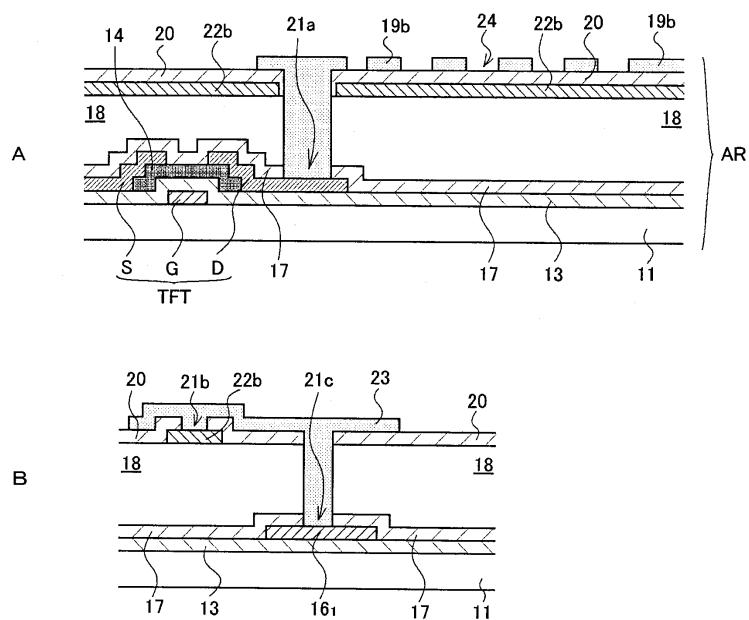

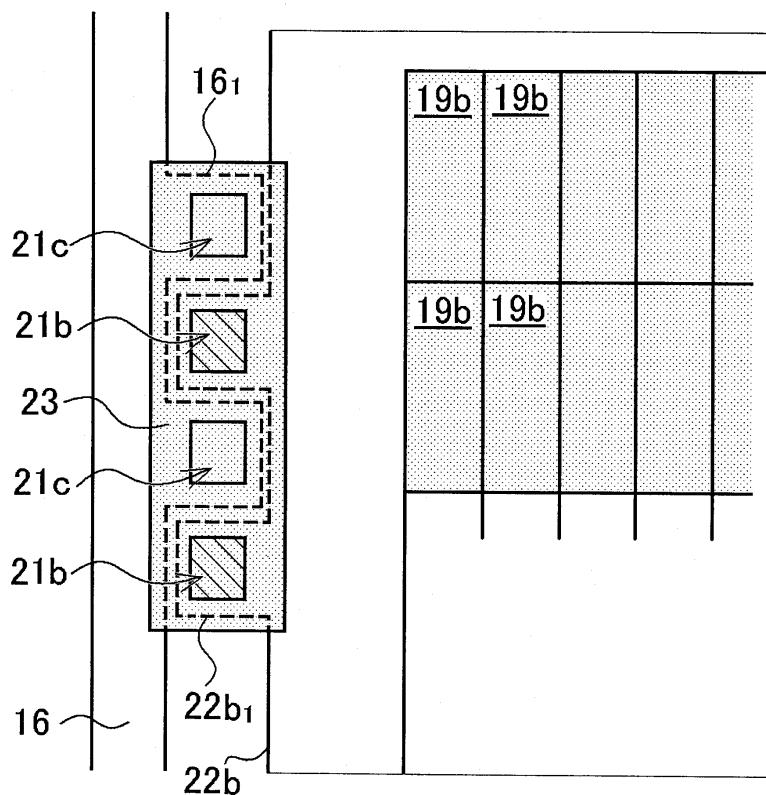

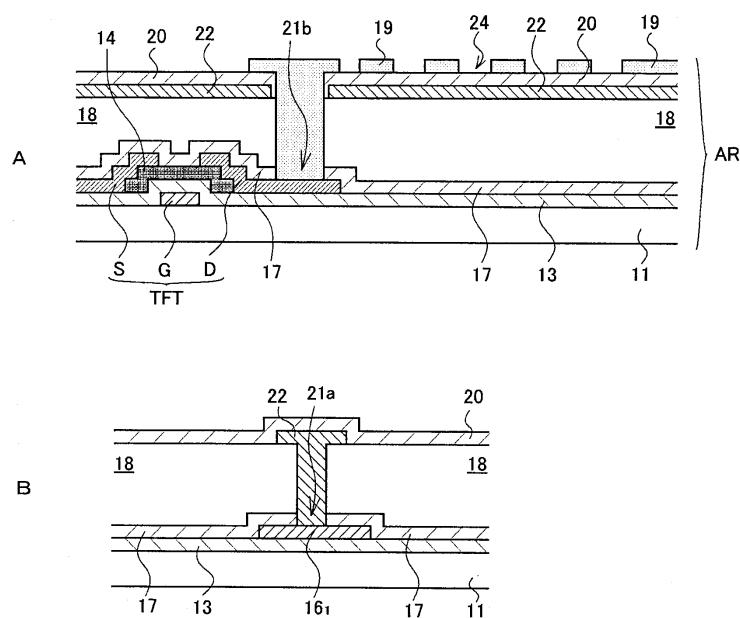

<63> 다음에, 평탄화막을 갖고, 하전극을 공통 전극으로서 공통 배선에 접속한 실시예 2의 FFS 모드의 액정 표시 장치의 예를 제조 공정순으로 도 6 ~ 도 9를 사용하여 설명한다. 또한, 도 6은 실시예 2의 액정 표시 장치의 아래 이 기판의 2 화소분의 모식 평면도이다. 도 7은 실시예 2의 액정 표시 장치의 공통 배선과 공통 전극의 접속 위치에 있어서 어레이 기판의 확대 평면도이다. 도 8A는 도 6의 VIIA-VIIIA 선을 따른 모식 단면도이고, 도 8B는 도 7의 VIIIb-VIIIb 선을 따른 모식 단면도이다. 또, 도 9는 실시예 2의 액정 표시 장치(10B)의 변형예에 있어서 공통 전극과의 접속 위치의 어레이 기판의 확대 평면도이다. 또한, 실시예 2의 액정 표시 장치(10B)에 있어서 공통 배선과 공통 전극의 접속 위치는 도 2에 나타낸 실시예 1의 액정 표시 장치(10A)의 공통 배선과 공통 전극의 접속 위치 X와 동양이므로, 필요에 따라 도 2를 원용하여 설명하는 것으로 한다.

<64> 이 실시예 2의 FFS 모드의 액정 표시 장치(10B)의 어레이 기판 AR은 투명 기판(11)의 표면에 주사선(12), 게이트 절연막(13), 반도체층(14), 소스 전극 S을 포함하는 신호선(15), 드레인 전극 D, 소스 배선, 공통 배선(16) 및 그 접속부(16<sub>1</sub>), 패시베이션막(17) 및 평탄화막(18)의 형성 공정은 실시예 1의 FFS 모드의 액정 표시 장치(10A)의 어레이 기판 AR의 제조 방법과 실질적으로 동일하므로, 그 상세한 설명은 생략한다.

<65> 평탄화막(18)을 형성한 후, 평탄화막(18)의 표면 전체에 걸쳐 ITO 내지 IZO로 이루어진 투명 도전성층을 형성하고, 포트리소그래피법 및 에칭법에 의해 공통 전극(22b)을 소정의 패턴으로 형성한다. 이 공통 전극(22b)에는 공통 배선(16)과 공통 전극(22b)과의 접속 위치 X(도 2 참조)에 있어서, 평면에서 보아 공통 배선(16) 및 그 접속부(16<sub>1</sub>)는 중복되지 않고, 공통 배선(16) 및 그 접속부(16<sub>1</sub>)에 인접한 위치가 되도록 접속부(22b<sub>1</sub>)가 형성된다. 또, 동시에, 공통 전극(22b)의 아래에 기술하는 제1 컨택트 홀(21a)의 형성 위치에는 제1 컨택트 홀(21a)보다 약간 큰 구멍을 형성한다. 실시예 2의 액정 표시 장치(10B)에 있어서는 이 공통 전극(22b)이 본 발명의 제1 전극에 대응한다. 또한, 도 7에 있어서 슬릿(24)은 도시를 생략하고 있다.

<66> 계속해서, 공통 전극(22b)이 형성된 기판(11)의 표면 전체에 걸쳐 질화 규소층 내지 산화 규소층으로 이루어진 절연막(20)을 소정 두께로 형성한다. 이 때, 공통 전극(22b)에 형성한 제1 컨택트 홀(21a)의 크기보다 큰 구멍 안은 절연막(20)으로 메워진다. 계속해서, 이 절연막(20)의 표면으로부터 절연막(20), 평탄화막(18) 및 패시베이션막(17)을 관통하여 드레인 전극 D의 표면에 도달하는 제1 컨택트 홀(21a), 절연막(20)을 관통하여 공통 전극(22b)의 표면에 도달하는 제2 컨택트 홀(21b), 절연막(20), 평탄화막(18) 및 패시베이션막(17)을 관통하여 공통 배선(16)의 접속부(16<sub>1</sub>)의 표면에 도달하는 제3 컨택트 홀(21c)을 각각 동시에 형성한다. 이 때, 공통 전극(22b)은 컨택트 홀(21a)의 주위벽에 노출되지 않는다. 이 컨택트 홀(21a ~ 21c)의 형성에는 전식 에칭법의 일종인 플라즈마 에칭법을 채용할 수 있다.

<67> 계속해서, 컨택트 홀(21a ~ 21c)이 형성된 기판(11)의 표면 전체에 걸쳐 ITO 내지 IZO로 이루어진 투명 도전성층을 형성한다. 이 때, 투명 도전성층에 의해 컨택트 홀(21a ~ 21c)을 통하여 공통 배선(16), 화소 전극(19b) 및 드레인 전극 D는 서로 전기적으로 접속된 상태가 된다.

<68> 그 후, 포트리소그래피법 및 에칭법에 의해 서브 화소 영역마다 화소 전극(19b)을 형성한다. 이 때 동시에, 각 화소 전극(19b)에는 평행하게 프린지 필드 효과를 발생시키기 위한 복수의 슬릿(24)을 형성하는 동시에, 접속 위치 X에 있어서 도전로(23)가 형성되도록, 도전로(23)의 주위의 투명 도전성층을 제거한다. 이와 같은 구성으로 하는 것에 의해, 도전로(23)와 각 화소 전극(19b) 사이의 절연성이 확보된다. 실시예 2의 액정 표시 장치(10B)에 있어서는 이 각 화소 전극(19b)이 본 발명의 제2 전극에 대응된다.

<69> 이와 같이 하여, 각 화소 전극(19b)은 제1 컨택트 홀(21a)을 통하여 드레인 전극 D와 전기적으로 접속되고, 공통 전극(22b)은 제2 컨택트 홀(21b), 도전로(23) 및 제3 컨택트 홀(21c)을 거쳐 공통 배선(16)에 접속된다. 이후, 공통 전극(22b)측의 표면 전체에 배향막(도시하지 않음)을 마련하는 것에 의해 실시예 2의 액정 표시 장치

(10B)의 어레이 기판 AR이 완성된다. 이 이후의 제조 공정은, 실시예 1의 액정 표시 장치(10A)의 제조 공정과 동일하므로, 상세한 설명을 생략한다.

<70> 이와 같이 해서 제조된 실시예 2의 액정 표시 장치(10B)에 의하면, 컨택트 홀은 3 개소 형성되어 있으나, 이들 컨택트 홀은 모두 공통 전극(22b)상의 절연막(20)을 관통하고 있기 때문에, 한 번의 공정으로 3 개소의 컨택트 홀을 동시에 형성할 수 있다. 또한, 이 액정 표시 장치(10B)에 의하면, 인터페이스 구조의 도전로(23)는 화소 전극(19b)과 동일한 재료로 형성되어 있기 때문에, 화소 전극(19b)의 형성과 동시에 각 컨택트 홀(21a ~ 21c)을 통하여 각 화소 전극(19b)과 드레인 전극 D 사이, 공통 전극(22b)과 공통 배선(16) 사이의 전기적 도통을 달성을 할 수 있다. 그렇기 때문에, 실시예 2의 액정 표시 장치(10B)에 의하면, 특히 제조 공정수를 늘리지 않고 제조 할 수 있는, 평탄화막(18)상에 화소 전극(19b) 및 공통 전극(22b)이 형성된 FFS 모드의 액정 표시 장치(10B)가 얻어진다. 또한, 그 외의 실시예 2의 액정 표시 장치(10B)의 작용 · 효과는 실시예 1의 액정 표시 장치의 경우와 동양이므로, 그 상세한 설명은 생략한다.

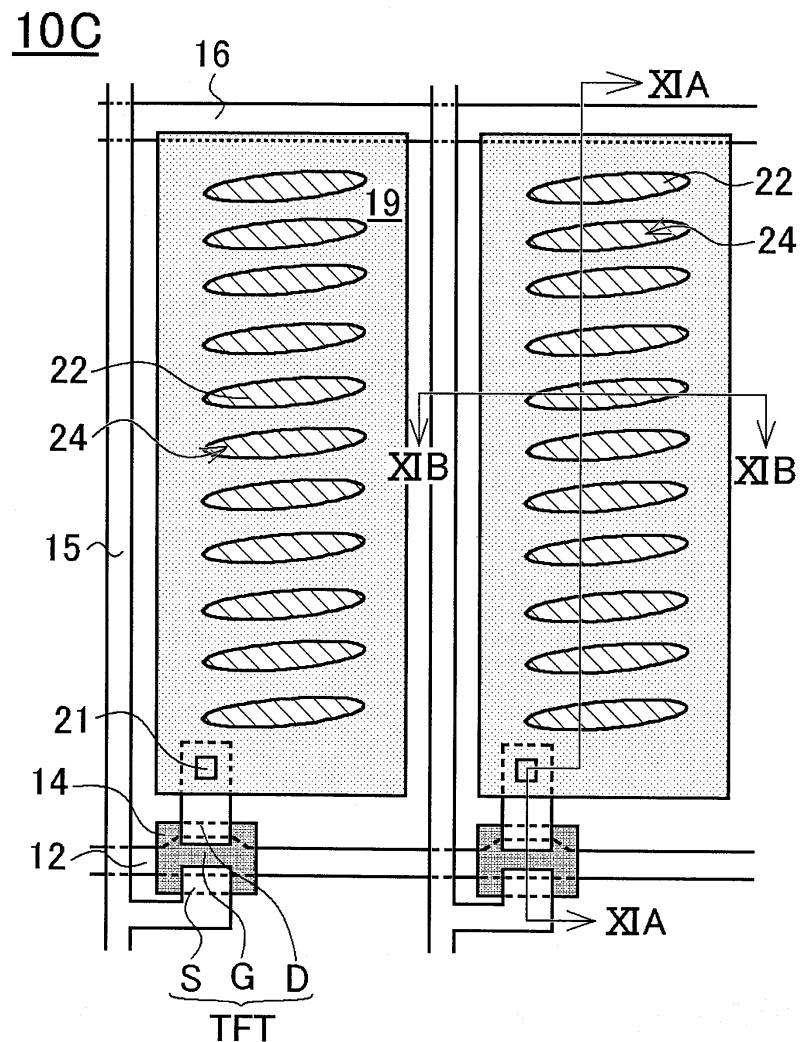

<71> [비]교예 1]

<72> 다음에, 본 발명의 액정 표시 장치의 효과를 확인하기 위해서, 비교예 1의 FFS 모드의 액정 표시 장치로서, 평탄화막을 구비하지 않는 FFS 모드 액정 표시 장치의 예를 제조 공정 순으로 도 10 및 도 11을 사용하여 설명한다. 또한, 도 10은 비교예 1의 FFS 모드의 액정 표시 장치의 어레이 기판의 2 화소분의 개략 평면도이고, 도 11A는 도 10의 XIA-XIA 선을 따른 개략 단면도, 도 11B는 도 10의 XIB-XIB 선을 따른 개략 단면도이다. 또한, 도 10 및 도 11에 있어서는, 도 1 ~ 도 5에 나타낸 실시예 1의 액정 표시 장치와 동일한 구성 부분에는 동일한 참조 부호를 부여하여 설명한다.

<73> 이 비교예 1의 FFS 모드의 액정 표시 장치(10C)의 어레이 기판 AR은 유리 기판 등의 투명 기판(11)의 표면 전체에 걸쳐 하부가 금속막 등의 도전성층을 형성한 후, 포트리소그래피법 및 에칭법에 의해 게이트 부분을 갖는 복수의 주사선(12) 및 복수의 공통 배선(16)을 서로 평행이 되도록 형성한다.

<74> 계속해서, 주사선(12) 및 공통 배선(16)을 형성한 투명 기판(11)의 표면 전체에 걸쳐, 예를 들어 ITO 내지 IZO로 이루어진 투명 도전성층을 피복하고, 마찬가지로 포트리소그래피법 및 에칭법에 의해 공통 전극(22)을 형성한다. 이 공통 전극(22)은 공통 배선(16)과는 전기적으로 접속되어 있으나, 주사선(12) 내지 게이트 전극 G과는 접속되어 있지 않다.

<75> 또한, 이 표면 전체에 질화 규소층 내지 산화 규소층으로 이루어진 게이트 절연막(13)을 피복하고, 그 다음에 CVD법에 의해 예를 들어 a-Si 층을 게이트 절연막(13)의 표면 전체에 걸쳐 피복한 후에, 마찬가지로 포트리소그래피법 및 에칭법에 의해, TFT 형성 영역에 a-Si 층으로 이루어진 반도체층(14)을 형성한다. 이 반도체층(14)이 형성되어 있는 위치의 주사선(12)의 영역이 TFT의 게이트 전극 G를 형성한다.

<76> 계속해서, 금속막 등으로 구성되어 있는 도전성층을 반도체층(14)을 형성한 투명 기판(11)의 표면 전체에 걸쳐 피복하고, 마찬가지로 포트리소그래피법 및 에칭법에 의해, 소스 전극 S를 포함하는 신호선(15) 및 드레인 전극 D를 형성한다. 이 신호선(15)의 소스 전극 S 부분 및 드레인 전극 D 부분은 모두 반도체층(14)의 표면에 부분적으로 겹쳐져 있다. 또한, 이 기판의 표면 전체에 질화 규소층으로 이루어진 패시베이션막(17)을 피복한다.

<77> 그 다음에, 드레인 전극 D에 대응하는 위치의 패시베이션막(17)에 컨택트 홀(21)을 형성하여 드레인 전극 D의 일부를 노출시킨다. 또한, 이 표면 전체에 걸쳐 예를 들어 ITO 내지 IZO로 이루어진 투명 도전성층을 피복한다. 이 때, 드레인 전극 D는 컨택트 홀(21)을 통하여 투명 도전성층과 전기적으로 접속된 상태가 된다. 계속해서, 포트리소그래피법 및 에칭법에 의해, 도 10에 나타낸 패턴이 되도록, 신호선(15)으로 둘러싸인 각각의 영역마다의 패시베이션막(17)상에 서로 평행하게 복수의 슬릿(24)이 형성된 화소 전극(19)을 형성한다. 이 상태에서, 각각의 화소 전극(19)은 컨택트 홀(21)을 통하여 드레인 전극 D와 전기적으로 접속된 상태가 된다.

<78> 이 후, 화소 전극(19)측의 표면 전체에 배향막(도시하지 않음)을 마련하는 것에 의해 비교예 1의 액정 표시 장치(10C)의 어레이 기판 AR이 완성된다. 이 이후의 제조 공정은, 실시예 1의 액정 표시 장치(10A)의 제조 공정과 동일하므로, 상세한 설명을 생략한다.

<79> 이와 같은 구성의 비교예 1의 액정 표시 장치(10C)는 공통 전극(22)과 공통 배선(16)이 직접 접속되어 있기 때문에, 컨택트 홀(21)은 1 개소밖에 필요없으나, 공통 배선(16)의 근방에서 화소 전극(19)의 일부에 단차가 생겨 있고, 또 TFT의 표면이 요철(凹凸) 상태로 되어 있다. 그렇기 때문에, 이 비교예 1의 액정 표시 장치(10C)는, 컬러 필터 기판에는 TFT에 대향하는 부분뿐만 아니라, 단차부에 대향하는 부분에도 블랙 매트릭스를 마련하여

차광할 필요가 있으므로, 적어도 이 단차부의 분만큼 개구율이 저하해 버린다.

<80> 또한, 차광성 재료로 이루어진 공통 배선(16)이 주사선(12) 사이에 평행하게 배치되어 있기 때문에, 이 공통 배선(16)에 의해서도 개구율이 저하해 버린다. 그렇기 때문에, 비교예 1의 액정 표시 장치(10C)는 실시예 1 및 2의 액정 표시 장치(10A, 10B)와 비교하면 개구율은 필연적으로 낮아져 버린다.

<81> [비교예 2]

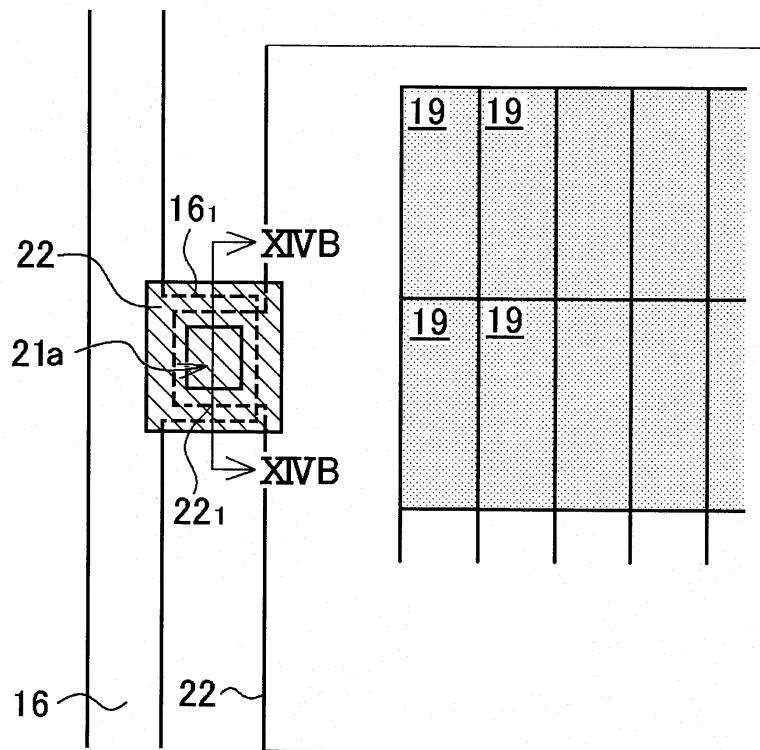

<82> 다음에, 본 발명의 효과를 확인하기 위해서, 비교예 2로서 평탄화막을 구비한 FFS 모드 액정 표시 장치의 예를 제조 공정순으로 도 12 ~ 도 14를 사용해서 설명한다. 또한, 도 12는 비교예 2의 액정 표시 장치의 어레이 기판의 2 화소분의 모식 평면도이다. 도 13은 비교예 2의 액정 표시 장치의 X 부분에 있어서 어레이 기판의 확대 평면도이다. 도 14A는 도 12의 XIVA-XIVA 선을 따른 개략 단면도, 도 14B는 도 13의 XIVB-XIVB 선을 따른 개략 단면도이다. 또한, 도 12 ~ 도 14에 있어서는 도 1 ~ 도 3에 나타낸 실시예 1의 FFS 모드의 액정 표시 장치(10A)와 동일한 구성 부분에 대해서는 동일한 참조 부호를 부여하고 그 상세한 설명은 생략한다. 또, 비교예 2의 액정 표시 장치에 있어서 공통 배선과 공통 전극의 접속 위치는 도 2에 나타낸 실시예 1의 액정 표시 장치(10A)의 공통 배선과 공통 전극의 접속 위치 X와 동양이므로, 필요에 따라서 도 2를 원용하여 설명하기로 한다.

<83> 이 비교예 2의 FFS 모드의 액정 표시 장치(10D)의 어레이 기판 AR의 제조 공정 중에서, 투명 기판(11)의 표면에, 게이트 전극 G를 포함하는 주사선(12), 게이트 절연막(13), 반도체층(14), 소스 전극 S을 포함하는 신호선(15), 드레인 전극 D, 소스 배선, 공통 배선(16) 및 그 접속부(16<sub>1</sub>), 패시베이션막(17) 및 평탄화막(18)의 형성 공정은, 실시예 1의 FFS 모드의 액정 표시 장치(10A)의 어레이 기판 AR의 제조 공정과 실질적으로 동일하므로, 그 상세한 설명은 생략한다.

<84> 평탄화막(18)을 형성한 후, 이하에 기술하는 공통 전극(22)과 공통 배선(16)의 접속 위치 X(도 2 참조)에 있어서, 접속부(16<sub>1</sub>)상의 평탄화막(18) 및 패시베이션막(17)을 관통하도록 제1 컨택트 홀(21a)을 형성하고, 접속부(16<sub>1</sub>)의 표면을 노출시킨다. 계속해서, 이 평탄화막(18)을 형성한 투명 기판(11)의 표면 전체에 걸쳐 ITO 내지 IZO로 이루어진 투명 도전성층을 형성하고, 포트리소그래피법 및 에칭법에 의해 공통 전극(22)을 소정의 패턴으로 형성한다. 이와 동시에, 이하에 나타내는 제2 컨택트 홀(21b)의 형성 위치에, 이 제2 컨택트 홀(21b)의 크기보다 큰 구멍을 형성한다. 이 때, 공통 전극(22)과 공통 배선(16)의 접속부(16<sub>1</sub>)는 제1 컨택트 홀(21a) 내의 투명 도전성층에 의해 전기적으로 접속된 상태가 된다.

<85> 계속해서, 공통 전극(22)이 형성된 기판(11)의 표면 전체에 걸쳐 질화 규소층 내지 산화 규소층으로 이루어진 절연막(20)을 소정 두께로 형성한다. 이 때, 공통 전극(22)에 형성한 제2 컨택트 홀(21b)의 크기보다 큰 구멍은 절연막(20)으로 메워진다. 또한, 이 절연막(20)의 표면으로부터 절연막(20), 평탄화막(18) 및 패시베이션막(17)을 관통하여 드레인 전극 D의 표면에 도달하는 제2 컨택트 홀(21b)을 형성한다. 이 때, 공통 전극(22)은 컨택트 홀(21b)의 주위벽에 노출되지 않는다.

<86> 계속해서, 제2 컨택트 홀(21b)이 형성된 기판(11)의 표면 전체에 걸쳐 ITO 내지 IZO로 이루어진 투명 도전성층을 형성한다. 이 때, 투명 도전성층은 제2 컨택트 홀(21b)을 통하여 드레인 전극 D와 전기적으로 접속된 상태가 된다.

<87> 그 후, 포트리소그래피법 및 에칭법에 의해, 서브 화소 영역마다 소정의 패턴의 화소 전극(19)을 형성한다. 이 때, 동시에 각 화소 전극(19)에는 평행하게 프린지 필드 효과를 발생시키기 위한 복수의 슬릿(24)을 형성한다. 이와 같이 하여, 각 화소 전극(19)은 제2 컨택트 홀(21b)을 통하여 드레인 전극 D와 전기적으로 접속된 상태가 된다.

<88> 이 후, 화소 전극(19)측의 표면 전체에 배향막(도시하지 않음)을 마련하는 것에 의해 비교예 2의 액정 표시 장치(10D)의 어레이 기판 AR이 완성된다. 이 이후의 제조 공정은, 실시예 1의 액정 표시 장치(10A)의 제조 공정과 동일하므로, 상세한 설명을 생략한다.

<89> 이와 같이 하여 제작된 비교예 2의 FFS 모드의 액정 표시 장치(10D)는 실질적으로 실시예 1 및 2의 FFS 모드의 액정 표시 장치(10A, 10B)와 동양인 광학 특성을 구비하고 있다. 그러나, 이 비교예 2의 액정 표시 장치(10D)에는 컨택트 홀은 2 개소 존재하고 있으나, 이 2 개소의 컨택트 홀은 각각 별개 공정으로 형성할 필요가 있다. 그렇기 때문에, 비교예 2의 FFS 모드의 액정 표시 장치(10D)를 제조하려면, 실시예 1 및 2의 액정 표시 장치(10A, 10B)를 제조하는 공정과 비교하면 컨택트 홀의 제조 공정이 한 공정 증가되어 있음을 알 수 있다.

<90> 또한, 실시예 1 및 2에 있어서는 화소 전극(19)에 마련하는 슬릿(24)으로서 길이 방향의 양단이 닫힌 형상으로 한 예를 나타냈으나, 슬릿을 한쪽 단측이 열려 있는 것으로 할 수도 있다. 이 경우, 이 슬릿이 열린 한쪽측의 단부에까지 프린지 필드 효과를 발휘시킬 수 있고, 또한 이 슬릿의 단부가 열려 있는 쪽에서의 액정 분자의 배향의 흐트러짐이 적기 때문에, 슬릿의 양단측이 닫혀 있는 액정 표시 장치와 비교하면 컬러 필터 기판에 마련한 블랙 매트릭스에 의해 차광해야 하는 부분의 면적이 줄어들기 때문에, 표시 개구율이 크고, 밝은 표시의 액정 표시 장치가 얻어진게 된다.

### 도면의 간단한 설명

<91> 도 1은 실시예 1의 액정 표시 장치의 어레이 기판의 2 화소분의 모식 평면도이다.

<92> 도 2는 액정 표시 장치의 공통 배선과 공통 전극의 접속 위치 X를 나타내는 도면이다.

<93> 도 3은 실시예 1의 액정 표시 장치의 X 부분에 있어서 어레이 기판의 확대 평면도이다.

<94> 도 4에서, 도 4A는 도 1의 IVA-IVA 선을 따른 모식 단면도, 도 4B는 도 1의 IVB-IVB 선을 따른 모식 단면도, 도 4C는 도 3의 IVC-IVC 선을 따른 모식 단면도이다.

<95> 도 5는 실시예 1의 액정 표시 장치의 변형예에 있어서 X 부분의 어레이 기판의 확대 평면도이다.

<96> 도 6은 실시예 2의 액정 표시 장치의 어레이 기판의 2 화소분의 모식 평면도이다.

<97> 도 7은 실시예 2의 액정 표시 장치의 X 부분에 있어서 어레이 기판의 확대 평면도이다.

<98> 도 8에서, 도 8A는 도 6의 VIII-A-VIII-A 선을 따른 모식 단면도이고, 도 8B는 도 7의 VIII-B-VIII-B 선을 따른 모식 단면도이다.

<99> 도 9는 실시예 2의 액정 표시 장치의 변형예에 있어서 X 부분에 있어서 어레이 기판의 확대 평면도이다.

<100> 도 10은 비교예 1의 FFS 모드의 액정 표시 장치의 어레이 기판의 2 화소분의 개략 평면도이다.

<101> 도 11에서, 도 11A는 도 10의 XIA-XIA 선을 따른 개략 단면도, 도 11B는 도 10의 XIB-XIB 선을 따른 개략 단면도이다.

<102> 도 12는 비교예 2의 액정 표시 장치의 어레이 기판의 2 화소분의 모식 평면도이다.

<103> 도 13은 비교예 2의 액정 표시 장치의 X 부분에 있어서 어레이 기판의 확대 평면도이다.

<104> 도 14에서, 도 14A는 도 12의 XIVA-XIVA 선을 따른 개략 단면도, 도 14B는 도 13의 XIVB-XIVB 선을 따른 개략 단면도이다.

### <부호의 설명>

<106> 10A ~ 10D : 액정 표시 장치,

<107> 11 : 투명 기판,

<108> 12 : 주사선,

<109> 13 : 게이트 절연막,

<110> 14 : 반도체층,

<111> 15 : 신호선,

<112> 16 : 공통 배선,

<113> 17 : 패시베이션막,

<114> 18 : 평탄화막,

<115> 19, 19a, 19b : 화소 전극,

<116> 20 : 절연막,

<117> 21, 21a ~ 21c : 컨택트 훌,

- <118> 22, 22a, 22b : 공통 전극,

<119> 23 : 도전로,

<120> 24 : 슬릿,

<121> 25 : 틀 형상의 절결부,

<122>  $D_{isp}$  : 표시 영역,

<123>  $T_{rim}$  : 액자 영역.

## 도면

### 도면1

도면2

10A(10B,10D)

도면3

## 도면4

도면5

도면6

10B

도면7

도면8

도면9

도면10

도면11

도면12

10D

도면13

도면14

|                |                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR1020080070563A</a>                                                      | 公开(公告)日 | 2008-07-30 |

| 申请号            | KR1020080007710                                                                       | 申请日     | 2008-01-24 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                          |         |            |

| 申请(专利权)人(译)    | 猎户座森成像装置可否让这个夏                                                                        |         |            |

| 当前申请(专利权)人(译)  | 猎户座森成像装置可否让这个夏                                                                        |         |            |

| [标]发明人         | HORIGUCHI MASAHIRO<br>호리구치마사히로<br>KANEKO HIDEKI<br>카네코 히데키                            |         |            |

| 发明人            | 호리구치마사히로<br>카네코 히데키                                                                   |         |            |

| IPC分类号         | G02F1/136 G02F1/133                                                                   |         |            |

| CPC分类号         | G02F2001/134372 G02F1/134309 G02F1/136227 G02F2201/40 G02F2001/134381 G02F2001/133357 |         |            |

| 优先权            | 2007014660 2007-01-25 JP                                                              |         |            |

| 其他公开文献         | <a href="#">KR100917503B1</a>                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                             |         |            |

### 摘要(译)

本发明的液晶显示器(10A)的制造方法包括从该绝缘层(20)的表面开始的漏电极D，然后在像素电极(19a)的整个表面上形成绝缘层(20)。在子像素的平坦化膜(18)的表面上形成公共线的连接单元(16(SB)1(/SB))以及通过像素电极(19a)连接像素电极(19a)的相应过程接口结构的导电路径(23)同时形成第一～第三接触孔(接触孔)(21a～21c)，使得像素电极(19a)暴露并形成具有多个的公共电极(22a)劈开在形成和穿过第二接触孔(21b)之后，在透明导电材料的整个表面上形成薄膜的子像素，以及绝缘层(20)相和第三接触孔(21c)通过用于公共电极(22)的第一接触孔(21a)和连接单元(16(SB)1(/SB))。和漏电极D.包括这种配置。因此，FFS(边缘场切换)模式的液晶显示器及其制造方法同时可以在单个工艺中形成多个接触孔，将像素电极和公共电极布置在平坦化膜上。提供。