# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

'특허정(KR) (11) 공개번호 10-2016-0092607 |공보(A) (43) 공개일자 2016년08월05일

(51) 국제특허분류(Int. Cl.)

**G09G 3/36** (2006.01)

(52) CPC특허분류

G09G 3/3648 (2013.01)

(21) 출원번호10-2015-0013191

(22) 출원일자 **2015년01월28일**

심사청구일자 **없음**

(71) 출원인

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

## 유재용

서울특별시 은평구 백련산로 38, 203동 1206호 ( 응암동, 백련산 힐스테이트 2차)

#### 최승찬

경경기도 고양시 일산동구 강석로 110, 517동 70 7호 (마두동, 강촌마을5단지아파트) (뒷면에 계속)

(74) 대리인

박영복

전체 청구항 수 : 총 9 항

### (54) 발명의 명칭 쉬프트 레지스터 및 이를 이용한 액정표시장치

### (57) 요 약

본 발명은 표시 장치에 관한 것으로, 특히 라인 별로 LRR(Low Refresh Rate) 구동이 가능하고, LRR(Low Refresh Rate) 구동 시 화질 불량을 개선하며, 베젤 사이즈를 최소화할 수 있는 쉬프트 레지스터 및 이를 이용한 액정표 시장치에 관한 것으로, 각 스테이지가 캐리 펄스 및 스캔 펄스를 독립적으로 출력하는 캐리 펄스 출력부 및 스캔 펄스 출력부를 구비하고, Q노드의 리플을 방지하기 위한 Q노드 리플 제거 패스를 구비하여, 적어도 2개의 캐리 펄스와 적어도 2개의 캐리용 클럭 펄스 및 적어도 2개의 스캔용 클럭 펄스를 이용한 것이다.

## 대 표 도 - 도7

## (72) 발명자

## 이정현

경기도 파주시 월롱면 엘씨디로 201, 105동 330호 (정다운마을 기숙사)

# 김지하

경기도 파주시 동패로 100, 305동 1204호 (동패동, 한울마을 3단지)

## 명세서

## 청구범위

### 청구항 1

복수개의 스테이지를 구비하고,

각 스테이지는,

2개의 전단 스테이지로부터 출력된 2개의 캐리 펄스들(또는 스타트 펄스), 다음단 스테이지로부터 출력된 1개의 캐리 펄스, 및 복수개의 캐리용 클럭펄스들중 3개의 캐리용 클럭펄스들을 수신하여 캐리 펄스를 출력하는 캐리 펄스 출력부와,

2개의 전단 스테이지로부터 출력된 2개의 캐리 펄스들(또는 스타트 펄스), 다음단 스테이지로부터 출력된 1개의 펄스, 및 복수개의 스캔용 클럭펄스들중 3개의 스캔용 클럭펄스들을 수신하여 스캔 펄스를 출력하는 스캔 펄스 출력부를 구비하여 구성되는 쉬프트 레지스터.

### 청구항 2

제 1 항에 있어서,

n번째 스테이지의 상기 캐리 펄스 출력부는,

(n-2)번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 캐리 펄스를 노드(Q)에 충전하는 제 1 스위칭소자와,

n+2번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자와.

상기 복수개의 캐리용 클럭 펄스들 중 어느 하나에 따라 제어되어 (n-1)번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스를 상기 노드(Q)에 충전하는 제 3 스위칭소자와,

리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 4 스위칭소자와,

상기 Q노드의 전압을 부트스트램핑하는 커패시터와,

상기 노드(Q)의 전압에 따라 제어되어 상기 복수개의 캐리용 클럭 펄스들 중 어느 하나를 출력단으로 출력하는 제 5 스위칭소자와,

상기 복수개의 캐리용 클럭 펄스들 중 어느 하나에 따라 제어되어 상기 출력단을 방전시키는 제 6 스위칭소자를 구비하여 구성되는 쉬프트 레지스터.

## 청구항 3

제 1 항에 있어서,

n번째 스테이지의 상기 스캔 펄스 출력부는,

(n-2)번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 캐리 펄스를 노드(Q)에 충전하는 제 1 스위칭소자와,

n+2번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자와,

상기 복수개의 스캔용 클럭 펄스들 중 어느 하나에 따라 제어되어 (n-1)번째 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스를 상기 노드(Q)에 충전하는 제 3 스위칭소자와,

리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 4 스위칭소자와,

상기 0노드의 전압을 부트스트램핑하는 커패시터와,

상기 노드(Q)의 전압에 따라 제어되어 상기 복수개의 스캔용 클럭 펄스들 중 어느 하나를 출력단으로 출력하는 제 5 스위칭소자와,

상기 복수개의 스캔용 클럭 펄스들 중 어느 하나에 따라 제어되어 상기 출력단을 방전시키는 제 6 스위칭소자를 구비하여 구성되는 쉬프트 레지스터.

### 청구항 4

복수개의 스테이지를 구비하고.

각 스테이지는,

2개의 전단 스테이지로부터 출력된 2개의 캐리 펄스들(또는 스타트 펄스), 및 다음단 스테이지로부터 출력된 1 개의 캐리 펄스 및 복수개의 캐리용 클럭펄스들중 어느 하나의 캐리용 클럭펄스(C-CLK\_(n-1)에 따라 Q노드를 제어하는 노드 제어부와,

상기 복수개의 캐리용 클럭펄스들중 2개의 캐리용 클럭펄스들을 수신하여 상기 노드 제어부의 Q노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하는 캐리펄스 출력부와,

복수개의 스캔용 클럭펄스들중 2개의 스캔용 클럭펄스들을 수신하여 상기 노드 제어부의 Q노드의 전압에 따라 스캔 펄스를 출력하는 스캔펄스 출력부를 구비하여 구성되는 쉬프트 레지스터.

#### 청구항 5

복수개의 스테이지를 구비하고,

각 스테이지는,

전단 스테이지로부터 출력된 1개의 캐리 펄스(또는 스타트 펄스), 및 후단 스테이지로부터 출력된 1개의 캐리 펄스 및 복수개의 캐리용 클럭펄스들중 2개의 캐리용 클럭펄스들을 수신하여 캐리 펄스를 출력하는 캐리 펄스 출력부와,

전단 스테이지로부터 출력된 1개의 캐리 펄스(또는 스타트 펄스), 후단 스테이지로부터 출력된 1개의 캐리 펄스, 및 복수개의 스캔용 클럭펄스들중 2개의 스캔용 클럭펄스들을 수신하여 스캔 펄스를 출력하는 스캔 펄스 출력부를 구비하여 구성되는 쉬프트 레지스터.

## 청구항 6

제 5 항에 있어서,

캐리 펄스 출력부는,

전단 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 캐리 펄스를 노드(Q)에 충전하는 제 1 스위칭소자와,

후단 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자와,

리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 3 스위칭소자와,

외부에서 입력되는 방전 신호를 저장하는 제 1 커패시터와,

상기 제 2 커패시터에 저장된 방전 신호에 따라 상기 노드(Q)에서 발생되는 리플을 제거하기 위한 패스를 형성하는 제 4 스위칭소자와,

상기 Q 노드의 전압에 따라 상기 제 1 커패시터에 저장된 방전 신호를 방전시키는 제 5 스위칭소자와,

상기 Q노드의 전압을 부트스트램핑하는 제 2 커패시터와,

상기 노드(Q)의 전압에 따라 제어되어 상기 복수개의 캐리용 클럭 펄스들 중 어느 하나를 출력단으로 출력하는 제 6 스위칭소자와,

상기 복수개의 캐리용 클럭 펄스들 중 다른 어느 하나에 따라 제어되어 상기 출력단을 방전시키는 제 7 스위칭

소자를 구비하여 구성되는 쉬프트 레지스터.

### 청구항 7

제 5 항에 있어서,

상기 스캔 펄스 출력부는.

전단 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 캐리 펄스를 노드(Q)에 충전하는 제 1 스위칭소자와,

후단 스테이지의 캐리 펄스 출력부로부터 출력된 캐리 펄스에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자와,

리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 3 스위칭소자와,

외부에서 입력되는 방전 신호를 저장하는 제 1 커패시터와,

상기 제 1 커패시터에 저장된 방전 신호에 따라 상기 노드(Q)에서 발생되는 리플을 제거하기 위한 패스를 형성하는 제 4 스위칭소자와,

상기 Q 노드의 전압에 따라 상기 제 2 커패시터에 저장된 방전 신호를 방전시키는 제 5 스위칭소자와,

상기 Q노드의 전압을 부트스트램핑하는 제 2 커패시터와,

상기 노드(Q)의 전압에 따라 제어되어 복수개의 스캔용 클럭 펄스들 중 어느 하나를 출력단으로 출력하는 제 6 스위칭소자와.

상기 복수개의 스캔용 클럭 펄스들 중 다른 어느 하나에 따라 제어되어 상기 출력단을 방전시키는 제 7 스위칭 소자를 구비하여 구성되는 쉬프트 레지스터.

#### 청구항 8

복수개의 스테이지를 구비하고,

각 스테이지는,

전단 스테이지로부터 출력된 캐리 펄스(또는 스타트 펄스(Vst)) 및 후단 스테이지로부터 출력된 캐리 펄스에 따라 Q노드를 제어하는 노드 제어부와,

복수개의 캐리용 클럭펄스들 중 2개의 캐리용 클럭펄스들을 수신하여 상기 노드 제어부의 Q노드의 전압에 따라 캐리 펄스를 출력하는 캐리펄스 출력부와,

복수개의 스캔용 클럭펄스들 중 2개의 스캔용 클럭펄스들을 수신하여 상기 노드 제어부의 Q노드의 전압에 따라 스캔 펄스를 출력하는 스캔 펄스 출력부를 구비하여 구성되는 쉬프트 레지스터.

### 청구항 9

복수의 게이트 라인과 상기 각 게이트 라인과 교차되도록 배치되는 복수의 데이터 라인들을 구비한 표시 패널;

상기 청구항 제 1 항, 제 4 항, 제 5 항 또는 제 8 항의 쉬프트 레지스터를 구비하여 상기 복수개의 게이트 라인들을 순차적으로 구동하는 게이트 드라이버;

상기 게이트 드라이버에 복수개의 캐리용 클럭펄스 및 복수개의 스캔용 클럭펄스를 공급하되, 동 영상 화면에 부분적으로 정지 영상이 존재할 경우, 상기 동 영상에 해당되는 게이트 라인들의 구동시에는 상기 복수개의 캐리용 클럭펄스 및 복수개의 스캔용 클럭펄스를 동 영상을 구동하는 주파수로 공급하고, 상기 정지 영상에 해당되는 게이트 라인들의 구동시에는 상기 복수개의 캐리용 클럭펄스를 동 영상을 구동하는 주파수로 공급하고 상기 복수개의 스캔용 클럭펄스를 상기 동 영상을 구동하는 주파수보다 낮은 주파수로 공급하는 타이밍 콘트롤러를 구비하여 구성되는 액정 표시 장치.

## 발명의 설명

## 기술분야

[0001] 본 발명은 표시 장치에 관한 것으로, 특히 라인 별로 LRR(Low Refresh Rate) 구동이 가능하고, LRR(Low Refresh Rate) 구동 시 화질 불량을 개선하며, 베젤 사이즈를 최소화할 수 있는 쉬프트 레지스터 및 이를 이용한 액정표시장치에 관한 것이다.

## 배경기술

- [0002] 통상의 액정표시장치는 전계를 이용하여 액정의 광 투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여 액정표시장치는 화소 영역들이 매트릭스 형태로 배열된 액정패널과, 상기 액정패널을 구동하기 위한 구동회로를 구비한다.

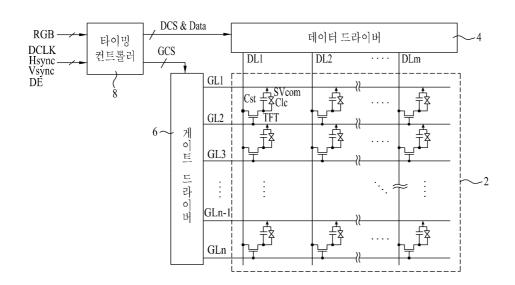

- [0003] 도 1은 일반적인 액정 표시장치의 구동장치를 나타낸 구성 회로도이다.

- [0005] 액정패널(2)은 복수의 게이트 라인(GL1 내지 GLn)과 복수의 데이터 라인들(DL1 내지 DLm)에 의해 정의되는 각화소 영역에 형성된 박막 트랜지스터(TFT; Thin Film Transistor) 및 상기 박막트랜지스터와 접속된 액정 커패시터(Clc)를 구비한다. 액정 커패시터(Clc)는 상기 박막트랜지스터와 접속된 화소전극, 화소전극과 액정을 사이에 두고 배치된 공통전극으로 구성된다. 상기 박막트랜지스터는 각각의 게이트 라인(GL1 내지 GLn)으로부터의 스캔 펄스에 응답하여 각각의 데이터 라인(DL1 내지 DLm)으로부터의 영상신호를 화소 전극에 공급한다.

- [0006] 상기 액정 커패시터(C1c)는 화소 전극에 공급된 영상신호와 공통전극에 인가되는 공통전압(SVcom)과의 차 전압을 충전하고, 그 차 전압에 따라 액정 분자들의 배열을 가변시켜 광 투과율을 조절함으로써 계조를 구현한다. 이때, 스토리지 커패시터(Cst)는 화소전극이 스토리지 라인과 절연막을 사이에 두고 중첩되어 형성될 수 있으며, 박막트랜지스터의 소스 전극과 게이트 라인(GL) 간에는 기생 커패시터(Cgs)가 더 형성되기도 한다.

- [0007] 상기 데이터 드라이버(4)는 타이밍 컨트롤러(8)로부터의 데이터 제어신호(DCS), 예를 들어, 소스 스타트 신호 (SSP; Source Start Pulse), 소스 쉬프트 클럭(SSC; Source Shift Clock), 소스 출력 인에이블(SOE; Source Output Enable) 신호 및 인버젼 신호(Pol Signal) 등을 이용하여 타이밍 컨트롤러(8)로부터 정렬된 데이터 (Data)를 아날로그 전압 즉, 영상신호로 변환한다. 구체적으로, 데이터 드라이버(4)는 SSC에 따라 타이밍 컨트롤러(8)를 통해 정렬된 데이터(Data)를 래치한 후, SOE 신호에 응답하여 각 게이트 라인(GL1 내지 GLn)에 스캔 필스가 공급되는 1수평 주기마다 1수평 라인 분의 영상신호를 각 데이터 라인(DL1 내지 DLm)에 공급한다.

- [0008] 상기 게이트 드라이버(6)는 타이밍 컨트롤러(8)로부터의 게이트 제어신호(GCS)에 따라 각 게이트 라인들(GL1 내지 GLn)을 순차 구동하게 된다. 구체적으로, 게이트 드라이버(4)는 게이트 제어신호(GCS)인 게이트 스타트 신호(GSP; Gate Start Pulse), 게이트 쉬프트 클럭(GSC; Gate Shift Clock), 게이트 출력 인에이블(GOE; Gate Output Enable) 신호 등을 이용하여 각 게이트 라인(GL1 내지 GLn)에 게이트 하이 전압(VGH) 레벨의 스캔 펄스가 순차적으로 공급되도록 구동한다. 그리고 스캔 펄스가 공급되지 않는 나머지 기간에는 게이트 로우 전압 공급되도록 한다.

- [0009] 상기 타이밍 컨트롤러(8)는 외부로부터의 영상 데이터(RGB) 및 복수의 동기신호들(DCLK, Hsync, Vsync, DE)에 따라 데이터 드라이버(4)와 게이트 드라이버(6)를 각각 제어한다. 구체적으로, 타이밍 컨트롤러(8)는 외부로부터 입력되는 영상 데이터(RGB)를 액정패널(2)의 구동에 알맞도록 정렬하여 데이터 드라이버(4)에 공급한다. 그리고 외부로부터 입력되는 동기신호 즉, 도트클럭(DCLK), 데이터 인에이블 신호(DE), 수평 및 수직 동기신호 (Hsync, Vsync) 중 적어도 하나를 이용하여 게이트 제어신호(GCS)와 데이터 제어신호(DCS)를 생성하고, 이를 게이트 드라이버(6)와 데이터 드라이버(4)에 각각 공급한다.

- [0010] 상기 게이트 드라이버(6)는 상술한 바와 같은 스캔 펄스들을 순차적으로 출력할 수 있도록 쉬프트 레지스터를 구비한다.

- [0011] 상기 쉬프트 레지스터는 타이밍 컨트롤러로부터 제공된 복수개의 클럭 펄스들을 근거로 상기 각 게이트 라인 (GL1 내지 GLn)에 스캔 펄스를 순차적으로 출력하는 다수의 스테이지들을 포함한다.

- [0012] 상기 쉬프트 레지스터는 표시패널에 내장될 수 있다. 즉, 표시패널은 화상을 표시하기 위한 표시부와 이 표시부

를 둘러싸는 비표시부를 갖는데, 쉬프트 레지스터(SR)는 비표시부에 내장될 수 있다(GIP).

- [0013] 상기 각 스테이지로부터 발생된 스캔 펼스는 어느 하나의 게이트 라인에 공급될 뿐만 아니라, 후단 스테이지 및 전단 스테이지들 중 적어도 하나로 공급된다.

- [0014] 상기 각 스테이지는 좁은 베젤(narrow bezel)를 구현하기 위하여, 트랜지스터의 수를 줄이고 있지만, 기본적으로 스캔 펄스를 출력하기 위한 풀업 스위칭소자 및 풀다운 스위칭소자를 포함하는 복수개의 트랜지스터와 한개의 부트스트램핑 커패시터를 포함하여 구성된다.

- [0015] 한편, 최근에는 표시하고자 하는 영상에 따라 구동 주파수를 달리하여 구동하므로 소비전력을 최소화하는 LRR(Low Refresh Rate) 구동 방법에 제안되었다.

- [0016] 즉, 전체 화면이 동영상 또는 부분 동영상을 표시할 때는 30Hz 내지 60Hz 프레임 주파수로 구동하고, 전체 화면이 정지 영상을 표시할 때는 1Hz의 프레임 주파수로 구동하는 방법에 제안되었다.

- [0017] 60Hz 프레임 주파수로 구동한다고 하는 것은 1초에 60번씩 각 서브 픽셀의 액정 커패시터(Clc)를 충전한 경우이고, 1Hz의 프레임 주파수로 구동하는 것은 1초에 한번 각 서브 픽셀의 액정 커패시터(Clc)를 충전한 경우이다.

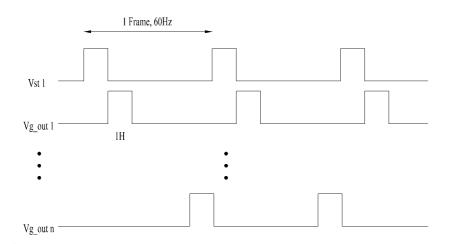

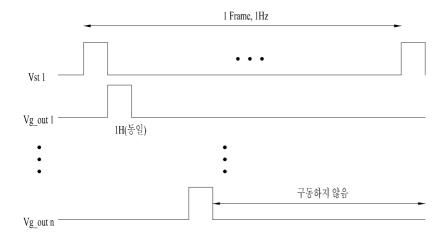

- [0018] 도 2(a)는 60Hz 프레임 주파수로 구동할 때 게이트 스타트 펄스(Vst) 및 스캔 펄스(Vg\_out1....Vg\_outn)를 나타낸 경우이고, 도 2(b)는 1Hz 프레임 주파수로 구동할 때 게이트 스타트 펄스(Vst) 및 스캔 펄스 (Vg\_out1....Vg\_outn)를 나타낸 경우이다.

- [0019] 1Hz 주파수로 구동 시는, 60Hz 주파수로 구동 시와 동일한 1H 타이밍으로 모든 게이트의 스캔 펼스를 출력한 후, 1 프레임의 나머지 시간 동안 구동하지 않고 홀딩(holding)한다. 따라서, 60Hz 주파수 구동 시보다 1Hz 주 파수로 구동 시 소비 전력이 작다.

- [0020] 그러나, 표시 장치의 전체 영역을 동일한 주파수로 구동하기 때문에, 실제로 화면 전체가 변화가 없는 정지 영상을 경우에만 저 주파수(1Hz) 구동이 가능하고, 적은 영역이라도 화면 변화가 이루어지는 경우에는 저 주파수(1Hz) 구동이 불가능하고, 고 주파수(60Hz)로 구동해야 한다. 따라서, 전체 화면에서 정지 영상이 차지하는 영역이 동 영상이 차지하는 영역보다 넓더라고 고 주파수 구동이 이루어지므로 불필요한 전력이 소비되는 문제점이 있었다.

## 발명의 내용

## 해결하려는 과제

[0021] 본 발명은 이와 같은 종래의 문제점을 해결하기 위한 것으로, 표시 패널을 라인별로 구동 주파수를 달리하여 구동할 수 있음은 물론, Q노드의 리플(ripple) 발생을 방지하여 화질을 향상시킬 수 있는 쉬프트 레지스터 및 이를 이용한 액정표시장치를 제공하는데 그 목적이 있다.

### 과제의 해결 수단

- [0022] 상기와 같은 목적을 달성하기 위한 본 발명에 따른 쉬프트 레지스터는, 각 스테이지가 캐리 펄스 및 스캔 펄스를 독립적으로 출력하는 캐리 펄스 출력부 및 스캔 펄스 출력부를 구비하고, Q노드의 리플을 방지하기 위한 Q노드 리플 제거 패스를 구비하여, 적어도 2개의 캐리 펄스와 적어도 2개의 캐리용 클럭 펄스 및 적어도 2개의 스캔용 클럭 펄스를 이용함에 그 특징이 있다.

- [0023] 또한, 각 스테이지의 회로 구성을 최소화하여 좁은 베젤을 구현함에 그 특징이 있다.

## 발명의 효과

- [0024] 성기와 같은 특징을 갖는 본 발명에 따른 쉬프트 레지스터 및 이를 이용한 액정표시장치에 있어서는 다음가 같은 효과가 있다.

- [0025] 즉, 각 스테이지에 Q노드의 리플을 방지하기 위한 Q노드 리플 제거 패스를 구비하므로, 라인 별로 LRR(Low Refresh Rate) 구동이 가능함을 물론, Q 노드의 리플 발생을 방지하므로 화질을 향상시킬 수 있다.

- [0026] 또한, 각 스테이지의 회로 구성을 최소화하므로 좁은 베절을 구현할 수 있다.

## 도면의 간단한 설명

- [0027] 도 1은 일반적인 액정 표시장치의 구동장치를 나타낸 구성 회로도

- 도 2(a) 및 2(b)는 종래의 액정 표시장치의 구동 모드에 따른 게이트 스타트 펄스 및 스캔 펄스 타이밍도

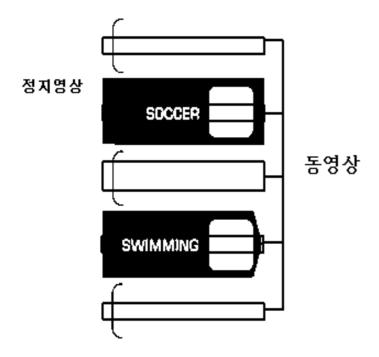

- 도 3은 LRR 구동 방법을 설명하기 위한 화면 구성도

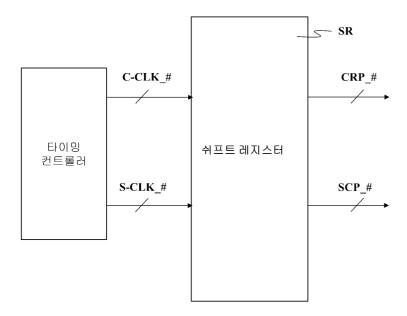

- 도 4는 본 출원인에 의해 기 출원된 표시 장치의 구동 회로도

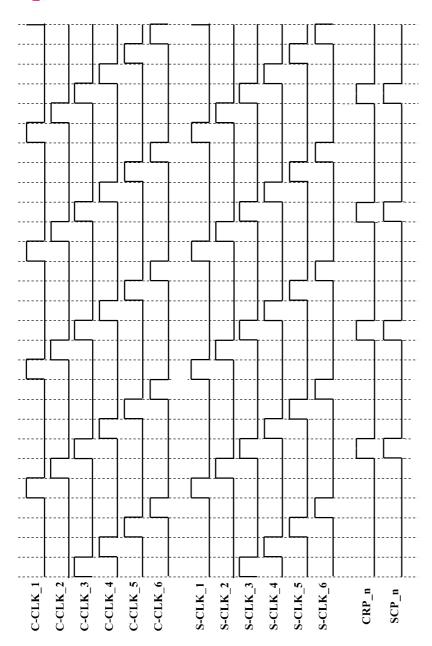

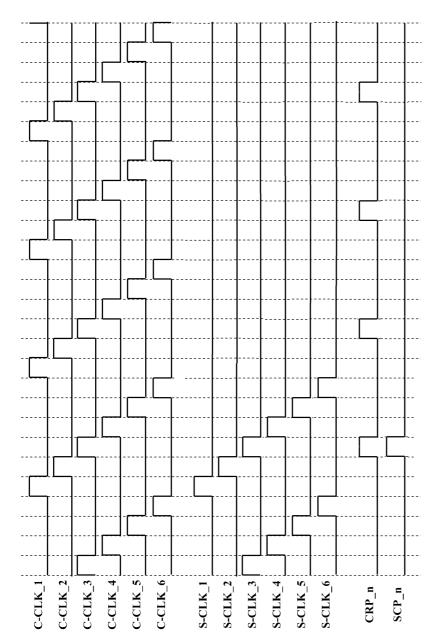

- 도 5는 도 4의 쉬프트 레지스터에서 동영상을 구현할 때 입출력되는 각종 신호 및 출력 신호의 타이밍도

- 도 6은 도 4의 쉬프트 레지스터에서 정지 영상을 구현할 때 입출력되는 각종 신호 및 출력 신호의 타이밍도

- 도 7은 기 출원된 도 4에 도시된 쉬프트 레지스터(SR)에 대한 상세 구성도

- 도 8은 기 출원된 도 7에 도시된 쉬프트 레지스터의 어느 하나의 스테이지의 구성도

- 도 9는 본 발명의 제 1 실시예에 따른 쉬프트 레지스터(SR)에 대한 상세 구성도

- 도 10은 본 발명의 제 1 실시예에 따른 어느 하나의 스테이지의 구성도

- 도 11은 본 발명의 제 2 실시예에 따른 쉬프트 레지스터(SR)에 대한 상세 구성도

- 도 12는 본 발명의 제 2 실시예에 따른 어느 하나의 스테이지의 구성도

## 발명을 실시하기 위한 구체적인 내용

- [0028] 상기와 같은 특징을 갖는 본 발명에 따른 쉬프트 레지스터 및 이를 이용한 액정표시장치를 첨부된 도면을 참조하여 보다 상세히 설명하면 다음과 같다.

- [0029] 먼저, 도 3은 본 발명에 따른 LRR 구동 방법을 설명하기 위한 화면 구성도이다.

- [0030] 본 출원인은, 불필요한 전력을 줄이기 위해, 도 3에서 설명한 바와 같이, 전 화면에 표시되는 영상에서, 부분적으로 동 영상과 정지 영상을 표시하도록 구동하기 위한 게이트 드라이버의 쉬프트 레지스터에 관하여 기 출원한 바 있다(특허출원 번호: 10-2014-0177397, 출원일: 2014년 12월 10일, 발명의 명칭: 표시 장치 및 표시장치의 구동 방법 참조).

- [0031] 도 4는 기 출원된 본 발명의 실시예에 따른 쉬프트 레지스터를 나타낸 도면이고, 도 5는 도 4의 쉬프트 레지스터에서 동영상을 구현할 때 입출력되는 각종 신호 및 출력 신호의 타이밍도를 나타낸 것이고, 도 6은 도 4의 쉬프트 레지스터에서 정지 영상을 구현할 때 입출력되는 각종 신호 및 출력 신호의 타이밍도를 나타낸 것이다.

- [0032] 본 발명의 기 출원된 게이트 드라이버의 쉬프트 레지스터는, 도 4에 도시된 바와 같이, 타이밍 컨트롤러(TC)로 부터 i개의 캐리용 클럭펄스(C-CLK\_#)들과 j개의 스캔용 클럭펄스(S-CLK\_#)들을 제공받는다. 구체적으로, 타이밍 컨트롤러(TC)는 i개(i는 1보다 큰 자연수)의 캐리용 클럭펄스(C-CLK\_#)들을 순차적으로 출력함과 아울러, j개(j는 1보다 큰 자연수)의 스캔용 클럭펄스(S-CLK\_#)들을 순차적으로 출력하고, 이들을 쉬프트 레지스터(SR)로 공급한다. 다시 말하여, 이 타이밍 컨트롤러(TC)는 i상(phase)의 캐리용 클럭펄스들 및 j상의 스캔용 클럭펄스들을 출력한다. 하나의 예로서, 도 5 및 도 6에서는 서로 다른 위상차를 갖는 6상의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)과, 그리고 서로 다른 위상차를 갖는 6상의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)를 출력한다. 그러나, 이에 한정되지 않고, 4상, 8 상 등 다양하게 구성할 수 있다.

- [0033] 도 5 및 6에 도시된 바와 같이, i개의 캐리용 클럭펄스들끼리는 이들의 펄스폭이 서로 중첩하지 않으며, 또한 j 개의 스캔용 클럭펄스들끼리는 이들의 펄스폭이 서로 중첩하지 않는다. 그러나, 다른 실시예로서, 인접한 기간에 출력되는 캐리용 클럭펄스들간의 펄스폭이 서로 중첩되도록 그 i개의 캐리용 클럭펄스들이 출력 타이밍이 조절될 수도 있으며, 마찬가지로 인접한 기간에 출력되는 스캔용 클럭펄스들간의 펄스폭이 서로 중첩되도록 그 i 개의 캐리용 클럭펄스들이 출력 타이밍이 조절될 수도 있다.

- [0034] 쉬프트 레지스터(SR)는, 타이밍 컨트롤러(TC)로부터 제공된 i개의 캐리용 클릭펄스들 및 j개의 스캔용 클릭펄스들을 근거로 다수의 출력들을 순차적으로 발생시키는 바, 이를 위해 이 쉬프트 레지스터(SR)는 그러한 다수의 출력들을 순차적으로 발생시키는 다수의 스테이지들을 포함한다. 각 스테이지로부터 발생된 출력은, 서로 대응되는 한 쌍의 캐리펄스와 스캔펄스로 구성된다. 한 쌍의 캐리펄스와 스캔펄스에서, 그 캐리펄스는 후단 스테이지 및 전단 스테이지들 중 적어도 하나로 공급되는 반면, 그 스캔펄스는 어느 하나의 게이트 라인으로 공급된다.

- [0035] 이 때, 상기 타이밍 콘트롤러(TC)는 표시되는 영상 중 정지 영상에 해당되는 부분의 게이트 라인들과 동 영상에 해당되는 게이트 라인들에 다른 구동 주파수의 스캔 펄스가 출력되도록 스캔용 클럭펄스를 제어한다.

- [0036] 예를들면, 상기 타이밍 콘트롤러(TC)는 표시되는 영상 중 동 영상에 해당되는 부분의 게이트 라인들에 스캔펄스를 출력하는 스테이지들에는, 도 5에 도시한 바와 같이, 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)를 60Hz로 출력한다.

- [0037] 그러나, 상기 타이밍 콘트롤러(TC)는 표시되는 영상 중 정지 영상에 해당되는 부분의 게이트 라인들에 스캔필스를 출력하는 스테이지들에는, 도 6에 도시한 바와 같이, 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)를 1Hz로 출력한다.

- [0038] 보다 더 구체적인 방법은 후술한다.

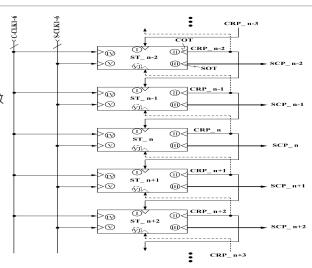

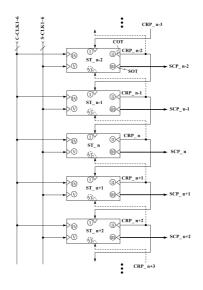

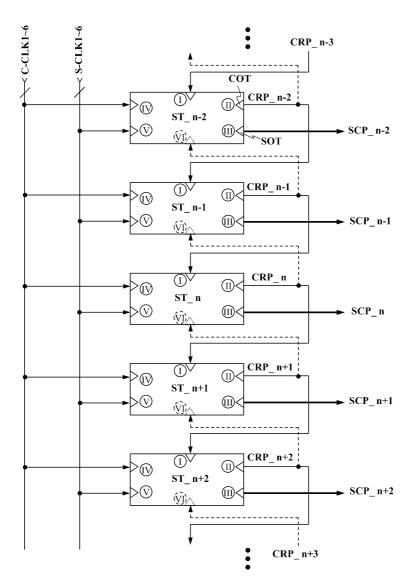

- [0039] 도 7은 기 출원된 도 4에 도시된 쉬프트 레지스터(SR)에 대한 상세 구성도이다.

- [0040] 본 발명의 기출원된 쉬프트 레지스터(SR)는, 도 7에 도시된 바와 같이, 다수의 스테이지들(ST\_n-2 내지 ST\_n+2)을 포함한다. 여기서, 각 스테이지는 총 6개의 단자들(I, II, III, IV, V, VI)을 포함한다.

- [0041] 각 스테이지의 4번 단자(IV)로는 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 어느 하나의 캐리용 클럭펄스가 인가되며, 1번 단자(I)로는 전단 스테이지로부터 출력된 캐리 펄스(또는 스타트 펄스(Vst))가 인가되며, 2번 단자(II; 이하, 캐리펄스 출력단자(COT))를 통해 하나의 캐리펄스(CRPn-2 내지 CRPn+2중 하나)를 출력한다.

- [0042] 또한, 각 스테이지의 5번 단자(V)로는 상기 복수개의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)중 어느 하나의 스캔용 클릭펄스가 인가되며, 6번 단자로는 다음단 스테이지로부터 출력된 캐리 펄스가 인가되며, 3번 단자 (III, 이하, 스캔펄스 출력단자(SOT)를 통해 하나의 스캔 펄스(스캔펄스(SCPn-2 내지 SCPn+2 중 하나)를 출력한 다.

- [0043] 따라서, 각 스테이지의 2번 및 3번 단자에서는 각각, 상술된 바와 같은 캐리펄스 및 스캔펄스가 독립적으로 출력되다.

- [0044] 전술된 도 5 및 도 6에 도시된 바와 같이 6상의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6) 및 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)이 쉬프트 레지스터로 제공된다면, 예를 들어, n-2번째 내지 n+2번째 스테이지들 (ST\_n-2 내지 ST\_n+2)을 포함한 전체 스테이지들 중 6k+1번째(k는 0을 포함한 자연수) 스테이지들은 제 1 캐리용 클럭펄스(C-CLK\_1) 및 제 1 스캔용 클럭펄스(S-CLK\_1)를, 6k+2번째 스테이지들은 제 2 캐리용 클럭펄스(C-CLK\_2) 및 제 2 스캔용 클럭펄스(S-CLK\_2)를, 6k+3번째 스테이지들은 제 3 캐리용 클럭펄스(C-CLK\_3) 및 제 3 스캔용 클럭펄스(S-CLK\_3)를, 6k+4번째 스테이지들은 제 4 캐리용 클럭펄스(C-CLK\_4) 및 제 4 스캔용 클럭펄스(S-CLK\_5)를, 그리고 6k+6번째 스테이지들은 제 6 캐리용 클럭펄스(C-CLK\_6) 및 제 6 스캔용 클럭펄스(S-CLK\_6)를 공급받을 수 있다.

- [0045] 각 스테이지는 캐리펄스를 이용하여 자신의 후단에 위치한 스테이지 및 전단에 위치한 스테이지의 동작을 제어한다. 아울러, 각 스테이지는 스캔펄스를 이용하여 자신에게 접속된 게이트 라인을 구동시킨다. 한편, 도시되지 않았지만, 마지막에 위치한 최종 스테이지의 후단에는 이 최종 스테이지로 캐리펄스를 공급하는 더미 스테이지 가 더 구비될 수 있다. 쉬프트 레지스터(SR)의 구성에 따라, 이 더미 스테이지는 한 개가 아닌 다수가 될 수 있다. 이 더미 스테이지는 게이트 라인에 연결되지 않으므로, 스캔펄스를 출력하지 않는다.

- [0046] 이러한 쉬프트 레지스터(SR)는 표시패널에 내장될 수 있다. 즉, 표시패널은 화상을 표시하기 위한 표시부와 이 표시부를 둘러싸는 비표시부를 갖는데, 쉬프트 레지스터(SR)는 비표시부에 내장될 수 있다 (GIP).

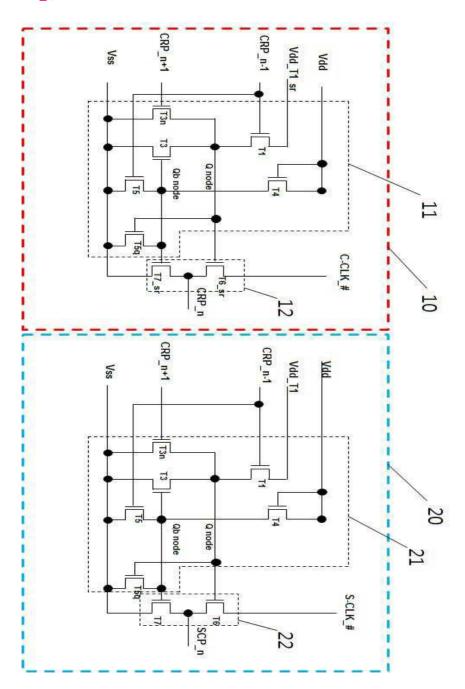

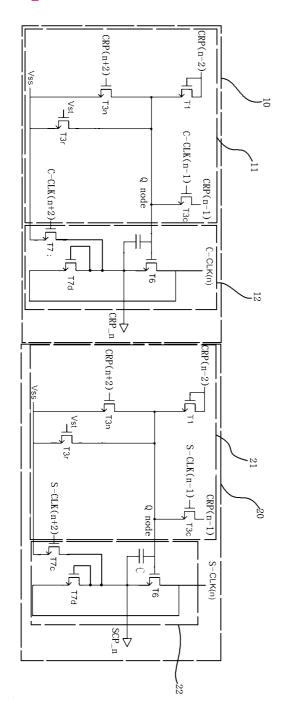

- [0047] 도 8은 기 출원된 본 발명의 따른 어느 하나의 스테이지의 구성을 나타낸 도면이다.

- [0048] 각 스테이지는, 도 8에 도시한 바와 같이, 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)를 별도로 구비한다.

- [0049] 상기 각 스테이지(n번째 스테이지)의 캐리 펄스 출력부(10)는 전단 스테이지로부터 출력된 캐리 펄스(CRP\_n-1) 또는 스타트 펄스(Vst)) 및 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+1)에 따라 Q노드 및 QB 노드를 제어하는 노드 제어부(11)와, 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 어느 하나의 캐리용 클럭 펄스(C-CLK\_#)를 수신하여 상기 노드 제어부(11)의 Q노드 및 QB 노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하

는 캐리펄스 출력부(12)를 구비한다.

- [0050] 또한, 상기 각 스테이지(n번째 스테이지)의 스캔 펄스 출력부(20)는 전단 스테이지로부터 출력된 캐리 펄스 (CRP\_n-1) 또는 스타트 펄스(Vst)) 및 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+1)에 따라 Q노드 및 QB 노드를 제어하는 노드 제어부(21)와, 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 어느 하나의 캐리용 클럭펄스(S-CLK\_#)를 수신하여 상기 노드 제어부(21)의 Q노드 및 QB 노드의 전압에 따라 스캔펄스 (SCP\_n)를 출력하는 스캔 펄스 출력부(22)를 구비한다.

- [0051] 따라서, 정지 영상에 부분적으로 동 영상이 존재할 때, 상기 동 영상에 상응하는 게이트 라인들은 60Hz로 구동하고, 나머지 정지 영상에 상응하는 게이트 라인들은 1Hz로 구동한다.

- [0052] 즉, 상기 동 영상에 상응하는 게이트 라인들은 60Hz로 구동하기 위해서는, 도 5에 도시한 바와 같이, 타이밍 컨트롤러(TC)에서 i상(phase)의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6) 및 j상의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)을 60Hz의 주파수로 게이트 드라이버의 해당 스테이지에 출력한다.

- [0053] 그리고, 정지 영상에 상응하는 게이트 라인들은 1Hz로 구동하기 위하여, 도 6에 도시한 바와 같이, 타이밍 컨트롤러(TC)에서 i상(phase)의 캐리용 클럭펄스들 (C-CLK\_1 내지 C-CLK\_6)은 60Hz의 주파수로 게이트 드라이버의 해당 스테이지에 출력하고, j상의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)은 1Hz의 주파수로 출력한다.

- [0054] 이와 같이, 동 영상 및 정지 영상에 관계 없이, 상기 타이밍 콘트롤러(TC)는 i상(phase)의 캐리용 클릭펄스들 (C-CLK\_1 내지 C-CLK\_6)은 60Hz로 출력하고, 동 영상이 구동되는 구간에서는 상기 j상의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)을 60Hz의 주파수로 출력하고, 정지 영상이 구동되는 구간에서는 상기 j상의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)을 1Hz의 주파수로 출력하므로, 부분적으로 동 영상이 존재할 경우에도 게이트 라인들(블릭)별로 저 주파수 구동이 가능하다.

- [0055] 그러나, 기 출원된 본 발명에서는, 도 8에 도시한 바와 같이, 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)에는, Q노드의 리플(ripple)을 제거하는 패스가 형성되지 않으므로, 리플 발생으로 인한 화질 불량이 발생될 수 있다.

- [0056] 즉, 출력부에 공급되는 캐리용 클럭 펄스(C-CLK(n)) 및 스캔용 클럭 펄스(S-CLK(n)에 의해 Q-노드에 리플이 발생하게 되는데, Q노드의 리플(ripple)을 제거하는 패스가 형성되지 않으므로, 리플 발생으로 인한 화질 불량이 발생될 수 있다.

- [0057] 본 발명은 표시 패널을 라인별로 구동 주파수를 달리하여 구동할 수 있음은 물론, 각 스테이지가 Q노드의 리플 (ripple)을 제거할 수 있는 패스를 형성하여 Q노드의 리플(ripple)발생을 방지하여 화질을 향상시킬 수 있는 쉬프트 레지스터를 제공하는데 그 목적이 있다.

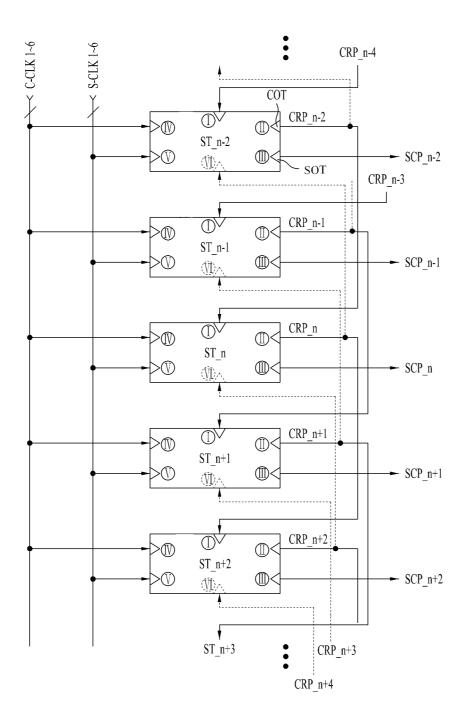

- [0058] 도 9는 본 발명의 제 1 실시예에 따른 쉬프트 레지스터(SR)에 대한 상세 구성도이다.

- [0059] 본 발명의 제 1 실시예에 따른 쉬프트 레지스터(SR)는, 도 9에 도시된 바와 같이, 다수의 스테이지들(ST\_n-2 내지 ST\_n+2)을 포함한다.

- [0060] 각 스테이지에는 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 3개의 캐리용 클럭펄스들과, 전단 및 전전단 스테이지로부터 출력된 캐리 펄스들(또는 스타트 펄스(Vst))과, 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 3개의 스캔용 클럭펄스들과, 다음단 스테이지로부터 출력된 캐리 펄스가 인가된다. 그리고, 캐리펄스 출력단자(COT))를 통해 하나의 캐리펄스를 출력하고, 스캔펄스 출력단자(SOT)를 통해 하나의 스캔 펄스를 출력한다.

- [0061] 6상의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6) 및 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)들은, 상기 도 5 및 도 6에서 설명한 바와 같으나, 하나의 스테이지에 3개의 캐리용 클럭펄스 및 3개의 스캔용 클럭펄스가 인가되고, 전후단에서 출력되는 3개의 캐리 펄스가 인가됨에 차이가 있다.

- [0062] 각 스테이지는 캐리펄스를 이용하여 자신의 후단에 위치한 스테이지 및 전단에 위치한 스테이지의 동작을 제어한다. 아울러, 각 스테이지는 스캔펄스를 이용하여 자신에게 접속된 게이트 라인을 구동시킨다. 한편, 도시되지 않았지만, 마지막에 위치한 최종 스테이지의 후단에는 이 최종 스테이지로 캐리펄스를 공급하는 더미 스테이지 가 더 구비될 수 있다. 쉬프트 레지스터(SR)의 구성에 따라, 이 더미 스테이지는 한 개가 아닌 다수가 될 수 있다. 이 더미 스테이지는 게이트 라인에 연결되지 않으므로, 스캔펄스를 출력하지 않는다.

- [0063] 도 10은 본 발명의 제 1 실시예에 따른 어느 하나의 스테이지의 구성을 나타낸 도면이다.

- [0064] 각 스테이지는, 도 10에 도시한 바와 같이, 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)를 별도로 구비한다.

- [0065] 상기 각 스테이지(n번째 스테이지)의 캐리 펄스 출력부(10)는 전단 스테이지로부터 출력된 캐리 펄스(CRP\_n-1, CRP\_n-2)(또는 스타트 펄스(Vst)), 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2) 및 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 어느 하나의 캐리용 클럭펄스(C-CLK\_(n-1)에 따라 Q노드를 제어하는 노드 제어부(11)와, 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 2개의 캐리용 클럭펄스(C-CLK\_(n), C-CLK\_(n+2)를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하는 캐리펄스 출력부(12)를 구비한다.

- [0066] 또한, 상기 각 스테이지(n번째 스테이지)의 스캔 펄스 출력부(20)는 전단 스테이지로부터 출력된 캐리 펄스들 (CRP\_(n-1), C-CRP\_(n-2))(또는 스타트 펄스(Vst)), 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2) 및 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 어느 하나의 스캔용 클럭펄스(S-CLK\_(n-1)에 따라 Q노드를 제어하는 노드 제어부(21)와, 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 2개의 스캔용 클럭펄스(S-CLK\_(n), S-CLK\_(n+2))를 수신하여 상기 노드 제어부(21)의 Q노드의 전압에 따라 스캔펄스(SCP\_n)를 출력하는 스캔 펄스 출력부(22)를 구비한다.

- [0067] 여기서, 상기 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)의 회로적 구성을 보다 구체적으로 설명하면 다음과 같다.

- [0068] 도 10에 도시한 바와 같이, 상기 캐리 펄스 출력부(10)의 노드 제어부(11)는 (n-2)번째 스테이지(ST\_n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)에 따라 제어되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충전하는 제 1 스위칭소자(T1)와, n+2번째 스테이지(ST\_n+2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n+2)}에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자(T3n)와, 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n-1)}에 따라 제어되어 (n-1)번째 스테이지(ST\_(n-1))의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-1)}를 상기 노드(Q)에 충전하는 제 3 스위칭소자(T3c)와, 리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 4 스위칭소자(T3r)를 구비한다.

- [0069] 상기 캐리 펄스 출력부(10)의 출력부(12)는 상기 Q노드의 전압을 부트스트램핑하는 커패시터(C)와, 상기 노드 (Q)의 전압에 따라 제어되어 상기 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n)}를 출력단으로 출력하는 제 5 스위칭소자(T6)와, 상기 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n+2)}에 따라 제어되어 상기 출력단을 방전시키는 제 6 스위칭소자(T7c) 및 제 7 스위칭소자(T7d)를 구비하여 구성된다.

- [0070] 상기 스캔 펄스 출력부(20)도 상기 캐리 펄스 출력부(10)와 같이 구성되나, 캐리용 클럭 펄스 대신에 스캔용 클럭 펄스가 인가됨에 차이가 있다.

- [0071] 즉, 스캔 펄스 출력부(20)의 노드 제어부(21)는 (n-2)번째 스테이지(ST\_n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)에 따라 제어되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충전하는 제 1 스위칭소자(T1)와, n+2번째 스테이지(ST\_n+2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n+2)}에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자(T3n)와, 서로 다른 위상을 나타내는 다수의 스캔용 클럭 펄스들중 어느 하나{S-CLK(n-1)}에 따라 제어되어 (n-1)번째 스테이지(ST\_(n-1))의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-1)}를 상기 노드(Q)에 충전하는 제 3 스위칭소자(T3c)와, 리셋 신호(Reset) 또는 스타트신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 4 스위칭소자(T3r)를 구비한다.

- [0072] 상기 스캔 펄스 출력부(20)의 출력부(22)는 상기 Q노드의 전압을 부트스트램핑하는 커패시터(C)와, 상기 노드(Q)의 전압에 따라 제어되어 상기 서로 다른 위상을 나타내는 다수의 스캔용 클럭 펄스들 중 어느 하나{S-CLK(n)}를 출력단으로 출력하는 제 5 스위칭소자(T6)와, 상기 서로 다른 위상을 나타내는 다수의 스캔용 클럭 펄스들 중 어느 하나{S-CLK(n+2)}에 따라 제어되어 상기 출력단을 방전시키는 제 6 스위칭소자(T7c) 및 제 7 스위칭소자(T7d)를 구비하여 구성된다.

- [0073] 이와 같이 구성된 본 발명의 제 1 실시예에 따른 n번째 스테이지의 동작을 설명하면 다음과 같다.

- [0074] 먼저, 캐리 펄스 출력부(10)의 동작을 설명하면 다음가 같다.

- [0075] (n-2)번째 스테이지(ST\_(n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)}의 하이 펄스가 제 1 스위칭소자(T1)에 입력되면, 상기 제 1 스위칭소자(T1)는 턴온되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충

전한다. 그리고, 서로 다른 위상을 갖는 복수개의 캐리용 클럭 펄스 중 하나의 캐리용 클럭 펄스 $\{C-CLK(n+2)\}$ 의 하이 펄스가 상기 제 6 스위칭소자 $\{T7c\}$ 에 입력되면 상기 제 6 스위칭소자 $\{T7c\}$ 가 턴온되어 출력단을 방전시킨다.

- [0076] 이와 같은 상태에서, 상기 제 3 스위칭소자(T3c)에 서로 다른 위상을 갖는 복수개의 캐리용 클럭 펄스 중 하나의 클럭 펄스{C-CLK(n-1)}와 n-1번째 스테이지(ST\_(n-1))의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-1)}가 입력되고, 상기 캐리용 클럭 펄스{C-CLK(n-1)}의 하이 구간에 상기 제 3 스위칭소자(T3c)가 턴온되어 상기 노드(Q)에 상기 캐리 펄스{CRT\_(n-1)}를 충전한다. 그러면 상기 상기 노드(Q)는 하이 상태를 유지한다.

- [0077] 상기 노드(Q)가 하이 상태를 유지하면, 제 5 스위칭소자(T6)가 턴온되고 커패시터(C)에 의해 부트스트램핑되며, 상기 제 5 스위칭소자(T6)의 소오스 단자에 입력된 서로 다른 위상을 갖는 복수개의 캐리용 클럭 펄스 중 하나의 캐리용 클럭 펄스(C-CLK(n))가 캐리 펄스(CRP\_n)로서 출력단으로 출력된다.

- [0078] 그리고, 리셋 신호 또는 스타트 신호에 의해 제 4 스위칭소자(T3r)가 턴온되어 상기 노드(Q)를 방전시킴과 동시에, 복수개의 캐리용 클럭 펄스 중 하나의 클럭 펄스{C-CLK(n+2)}가 제 6 스위칭소자(T7c)에 입력되면 상기 제 6 스위칭소자(T7c)도 턴온되어 상기 출력단을 방전시킨다.

- [0079] 상기 스캔 펄스 출력부(20)의 동작도 상기 캐리 펄스 출력부(10)와 동일하게 동작하고, 단, 입력된 클럭 펄스가서로 다른 위상을 갖는 복수개의 스캔용 클럭 펄스(S-CLK\_1 내지 S-CLK\_6)임에 차이가 있으므로, 스캔 펄스 출력부(20)의 동작은 생략한다.

- [0080] 따라서, 상기 도 5 및 도 6에서 설명한 바와 같이, 동 영상 및 정지 영상에 관계 없이, 상기 타이밍 콘트롤러 (TC)는 i상(phase)의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)은 60Hz로 출력하고, 동 영상이 구동되는 구간에서는 상기 j상의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)을 60Hz의 주파수로 출력하고, 정지 영상이 구동되는 구간에서는 상기 j상의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)을 1Hz의 주파수로 출력하므로, 부분적으로 동 영상이 존재할 경우에도 게이트 라인들(블럭)별로 저 주파수 구동이 가능하다.

- [0081] 또한, 제 3 스위칭소자(T3c)에는, 동영상 또는 정지 영상 구동에 관계 없이 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n-1)}와 (n-1)번째 스테이지(ST\_(n-1))의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-1)}가 60Hz로 인가되므로 Q 노드에 발생될 수 있는 리플을 제거하는 패스를 형성하므로, 화질을 향상시킬 수 있는 쉬프트 레지스터를 제공할 수 있다.

- [0082] 상기 도 10에서는 상기 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)가 각각 노드 제어부(11, 21)를 별도로 구비하고 있지만, 이를 공통으로 할 수 있다.

- [0083] 즉, 본 출원인에 의해 기출원된 상기 특허출원(특허출원 번호: 10-2014-0177397)의 도 7에서 설명한 바와 같이, 어느 하나의 스테이지(n번째 스테이지)는, 전단 스테이지로부터 출력된 캐리 펄스(CRP\_n-1, CRP\_n-2)(또는 스타트 펄스(Vst)), 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2) 및 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 어느 하나의 캐리용 클럭펄스(C-CLK\_(n-1)에 따라 Q노드를 제어하는 노드 제어부(11)와, 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 2개의 캐리용 클럭펄스(C-CLK\_(n), C-CLK\_(n+2)를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하는 캐리펄스 출력부(12)와, 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 2개의 스캔용 클럭펄스(S-CLK\_(n), S-CLK\_(n+2))를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 스캔펄스(SCP\_n)를 출력하는 스캔 펄스 출력부(22)를 구비할 수 있다.

- [0084] 상기와 같이 구성하므로, 각 스테이지의 회로 구성을 더 줄일 수 있으므로 좁은 베젤 구현이 가능하다.

- [0085] 상기 도 9 및 도 10에서 설명한 바와 같은 본 발명 제 1 실시예의 쉬프트 레지스터에서는, 제 3 스위칭소자 (T3c)가 Q 노드에 발생될 수 있는 리플을 제거하는 패스를 형성하므로 화질을 향상시킬 수 있는 반면, 상기 제 3 스위칭소자(T3c)의 게이트 전극 및 소오스 전극에 항상 60Hz의 펄스가 인가되므로 상기 제 3 스위칭소자(T3 c)가 열화되어 Q 노드의 리플을 제거하는 패스를 형성하지 못하는 경우가 발생할 수 있다.

- [0086] 따라서, 상기 제 3 스위칭소자(T3c)를 사용하지 않고 별도로 Q 노드에 발생될 수 있는 리플을 제거하는 패스를 형성할 수도 있다.

- [0087] 이와 같이, Q 노드에 발생될 수 있는 리플을 제거하는 패스를 별도로 형성하는 실시예를 설명하면 다음과 같다.

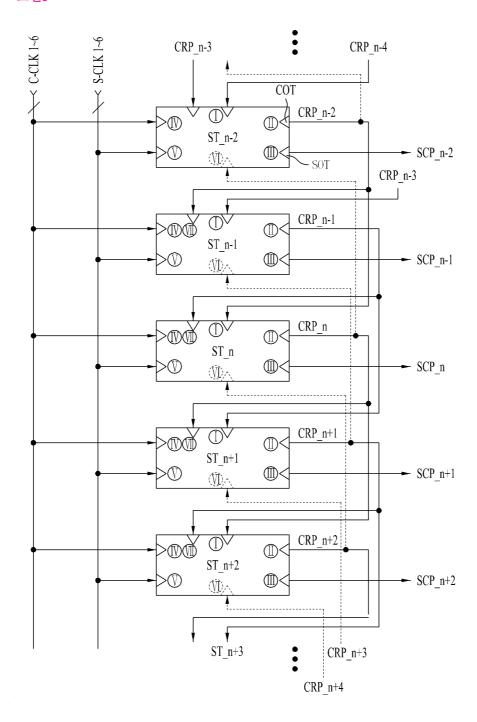

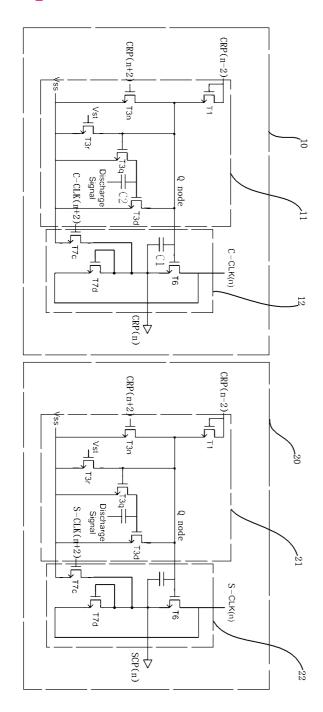

- [0088] 도 11은 본 발명의 제 2 실시예에 따른 쉬프트 레지스터(SR)에 대한 상세 구성도이고, 도 12는 본 발명의 제 2 실시예에 따른 어느 하나의 스테이지의 구성을 나타낸 도면이다.

- [0089] 본 발명의 제 2 실시예에 따른 쉬프트 레지스터(SR)는, 도 11에 도시된 바와 같이, 다수의 스테이지들(ST\_n-2 내지 ST\_n+2)을 포함한다.

- [0090] 각 스테이지에는 상기 복수개의 캐리용 클릭펄스들(C-CLK\_1 내지 C-CLK\_6)중 2개의 캐리용 클릭펄스들과, 전단스테이지로부터 출력된 캐리 펄스(또는 스타트 펄스(Vst))과, 상기 복수개의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)중 2개의 스캔용 클릭펄스들과, 다음단 스테이지로부터 출력된 캐리 펄스가 인가된다. 그리고, 캐리펄스 출력단자(COT))를 통해 하나의 캐리펄스를 출력하고, 스캔펄스 출력단자(SOT)를 통해 하나의 스캔 펄스를 출력하다.

- [0091] 6상의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6) 및 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)들은, 상기 도 5 및 도 6에서 설명한 바와 같으나, 하나의 스테이지에 2개의 캐리용 클럭펄스 및 2개의 스캔용 클럭펄스가 인가되고, 전후단에서 출력되는 2개의 캐리 펄스가 인가됨에 차이가 있다.

- [0092] 각 스테이지는 캐리펄스를 이용하여 자신의 후단에 위치한 스테이지 및 전단에 위치한 스테이지의 동작을 제어한다. 아울러, 각 스테이지는 스캔펄스를 이용하여 자신에게 접속된 게이트 라인을 구동시킨다. 한편, 도시되지 않았지만, 마지막에 위치한 최종 스테이지의 후단에는 이 최종 스테이지로 캐리펄스를 공급하는 더미 스테이지 가 더 구비될 수 있다. 쉬프트 레지스터(SR)의 구성에 따라, 이 더미 스테이지는 한 개가 아닌 다수가 될 수 있다. 이 더미 스테이지는 게이트 라인에 연결되지 않으므로, 스캔펄스를 출력하지 않는다.

- [0093] 본 발명의 제 2 실시예에 따른 각 스테이지는, 도 12에 도시한 바와 같이, 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)를 별도로 구비한다.

- [0094] 상기 각 스테이지(n번째 스테이지)의 캐리 펄스 출력부(10)는 전단 스테이지로부터 출력된 캐리 펄스(CRP\_n-2)(또는 스타트 펄스(Vst)) 및 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2)에 따라 Q노드를 제어하는 노드 제어부(11)와, 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 2개의 캐리용 클럭펄스(C-CLK\_(n), C-CLK\_(n+2)를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하는 캐리펄스 출력부(12)를 구비한다.

- [0095] 또한, 상기 각 스테이지(n번째 스테이지)의 스캔 펄스 출력부(20)는 전단 스테이지로부터 출력된 캐리 펄스(C-CRP\_(n-2))(또는 스타트 펄스(Vst))와 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2)에 따라 Q노드를 제어하는 노드 제어부(21)와, 상기 복수개의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)중 2개의 스캔용 클릭펄스(S-CLK\_(n), S-CLK\_(n+2))를 수신하여 상기 노드 제어부(21)의 Q노드의 전압에 따라 스캔펄스(SCP\_n)를 출력하는 스캔 펄스 출력부(22)를 구비한다.

- [0096] 여기서, 상기 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)의 회로적 구성을 보다 구체적으로 설명하면 다음과 같다.

- [0097] 도 12에 도시한 바와 같이, 상기 캐리 펄스 출력부(10)의 노드 제어부(11)는 (n-2)번째 스테이지(ST\_n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)에 따라 제어되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충전하는 제 1 스위칭소자(T1)와, n+2번째 스테이지(ST\_n+2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n+2)}에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자(T3n)와, 리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 3 스위칭소자(T3r)와, 외부에서 입력되는 방전신호(discharge signal)를 저장하는 커패시터(C2)와, 상기 커패시터(C2)에 저장된 방전 신호에 따라 상기 노드(Q)에서 발생되는 리플을 제거하기 위한 패스를 형성하는 제 4 스위칭소자(T3c)와, 상기 Q 노드의 전압에 따라 상기 커패시터(C2)에 저장된 방전 신호를 방전시키는 제 5 스위칭소자(T3q)를 구비하여 구성된다.

- [0098] 상기 캐리 펄스 출력부(10)의 출력부(12)는 상기 Q노드의 전압을 부트스트램핑하는 커피시터(C1)와, 상기 노드 (Q)의 전압에 따라 제어되어 상기 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n)}를 출력단으로 출력하는 제 6 스위칭소자(T6)와, 상기 서로 다른 위상을 나타내는 다수의 캐리용 클럭 펄스들 중 어느 하나{C-CLK(n+2)}에 따라 제어되어 상기 출력단을 방전시키는 제 7 스위칭소자(T7c) 및 제 8 스위칭소자(T7d)를 구비하여 구성된다.

- [0099] 상기 스캔 펄스 출력부(20)도 상기 캐리 펄스 출력부(10)와 같이 구성되나, 캐리용 클럭 펄스 대신에 스캔용 클럭 펄스가 인가됨에 차이가 있다.

- [0100] 즉, 스캔 펄스 출력부(20)의 노드 제어부(21)는 (n-2)번째 스테이지(ST\_n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)에 따라 제어되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충전하는 제 1 스위칭소자 (T1)와, n+2번째 스테이지(ST\_n+2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n+2)}에 따라 제어되어 상기 노드(Q)를 방전시키는 제 2 스위칭소자(T3n)와, 리셋 신호(Reset) 또는 스타트 신호(Vst)에 따라 제어되어 상기 노드(Q)를 방전시키는 제 3 스위칭소자(T3r)와, 외부에서 입력되는 방전 신호(discharge signal)를 저장하는 커패시터(C2)와, 상기 커패시터(C2)에 저장된 방전 신호에 따라 상기 노드(Q)에서 발생되는 리플을 제거하기 위한 패스를 형성하는 제 4 스위칭소자(T3c)와, 상기 Q 노드의 전압에 따라 상기 커패시터(C2)에 저장된 방전 신호를 방전시키는 제 5 스위칭소자(T3q)를 구비하여 구성된다.

- [0101] 상기 스캔 펄스 출력부(20)의 출력부(22)는 상기 Q노드의 전압을 부트스트램핑하는 커피시터(C1)와, 상기 노드 (Q)의 전압에 따라 제어되어 상기 서로 다른 위상을 나타내는 다수의 스캔용 클럭 펄스들 중 어느 하나{S-CLK(n)}를 출력단으로 출력하는 제 6 스위칭소자(T6)와, 상기 서로 다른 위상을 나타내는 다수의 스캔용 클럭 펄스들 중 어느 하나{S-CLK(n+2)}에 따라 제어되어 상기 출력단을 방전시키는 제 7 스위칭소자(T7c) 및 제 8 스위칭소자(T7d)를 구비하여 구성된다.

- [0102] 마찬가지로, 상기 도 12에서는 상기 캐리 펄스 출력부(10)와 스캔 펄스 출력부(20)가 각각 노드 제어부(11, 2 1)를 별도로 구비하고 있지만, 이를 공통으로 할 수 있다.

- [0103] 즉, 본 출원인에 의해 기출원된 상기 특허출원(특허출원 번호: 10-2014-0177397)의 도 7에서 설명한 바와 같이, 어느 하나의 스테이지(n번째 스테이지)는, 전단 스테이지로부터 출력된 캐리 펄스(CRP\_n-2)(또는 스타트 펄스(Vst)) 및 다음단 스테이지로부터 출력된 캐리 펄스(CRP\_n+2)에 따라 Q노드를 제어하는 노드 제어부(11)와, 상기 복수개의 캐리용 클럭펄스들(C-CLK\_1 내지 C-CLK\_6)중 2개의 캐리용 클럭펄스(C-CLK\_(n), C-CLK\_(n+2)를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 캐리 펄스(CRP\_n)를 출력하는 캐리펄스 출력부(12)와, 상기 복수개의 스캔용 클럭펄스들(S-CLK\_1 내지 S-CLK\_6)중 2개의 스캔용 클럭펄스(S-CLK\_(n), S-CLK\_(n+2))를 수신하여 상기 노드 제어부(11)의 Q노드의 전압에 따라 스캔펄스(SCP\_n)를 출력하는 스캔 펄스 출력부(22)를 구비할 수 있다.

- [0104] 마찬가지로, 상기와 같이 구성하므로, 각 스테이지의 회로 구성을 더 줄일 수 있으므로 좁은 베젤 구현이 가능하다.

- [0105] 이와 같이 구성된 본 발명의 제 2 실시예에 따른 n번째 스테이지의 동작을 설명하면 다음과 같다.

- [0106] 먼저, 캐리 펄스 출력부(10)의 동작을 설명하면 다음가 같다.

- [0107] (n-2)번째 스테이지(ST\_(n-2)의 캐리 펄스 출력부(10)로부터 출력된 캐리 펄스{CRP\_(n-2)}의 하이 펄스가 제 1 스위칭소자(T1)에 입력되면, 상기 제 1 스위칭소자(T1)는 턴온되어 상기 캐리 펄스{CRP\_(n-2)}를 노드(Q)에 충전한다. 그리고, 서로 다른 위상을 갖는 복수개의 캐리용 클럭 펄스 중 하나의 캐리용 클럭 펄스{C-CLK(n+2)}의 하이 펄스가 상기 제 7 스위칭소자(T7c)에 입력되면 상기 제 7 스위칭소자(T7c)가 턴온되어 출력단을 방전시킨다.

- [0108] 이와 같이 상기 노드(Q)가 하이 상태를 유지하면, 제 6 스위칭소자(T6)가 턴온되고 커패시터(C1)에 의해 부트스트램핑되며, 상기 제 6 스위칭소자(T6)의 소오스 단자에 입력된 서로 다른 위상을 갖는 복수개의 캐리용 클릭 펄스 중 하나의 캐리용 클릭 펄스{C-CLK(n)}가 캐리 펄스(CRP\_n)로서 출력단으로 출력된다.

- [0109] 그리고, n+2번째 스테이지(ST\_n+2)의 캐리 펄스 출력부(10)로부터 하이 상태의 캐리 펄스(CRP\_(n+2)를 출력하면 상기 제 2 스위칭소자(T3n)가 턴온되어 상기 노드(Q)를 방전시킴과 동시에, 복수개의 캐리용 클럭 펄스 중 하나의 클럭 펄스{C-CLK(n+2)}가 제 7 스위칭소자(T7c)에 입력되면 상기 제 6 스위칭소자(T7c)도 턴온되어 상기 출력단을 방전시킨다. 또한, 리셋트 신호 또는 스타트 신호에 의해 제 3 스위칭소자(T3r)가 턴온되어 상기 노드(Q)를 방전시킨다.

- [0110] 상기 스캔 펄스 출력부(20)의 동작도 상기 캐리 펄스 출력부(10)와 동일하게 동작하고, 단, 입력된 클릭 펄스가서로 다른 위상을 갖는 복수개의 스캔용 클릭 펄스(S-CLK\_1 내지 S-CLK\_6)임에 차이가 있으므로, 스캔 펄스 출력부(20)의 동작은 생략한다.

- [0111] 따라서, 상기 도 5 및 도 6에서 설명한 바와 같이, 동 영상 및 정지 영상에 관계 없이, 상기 타이밍 콘트롤러 (TC)는 i상(phase)의 캐리용 클릭펄스들(C-CLK\_1 내지 C-CLK\_6)은 60Hz로 출력하고, 동 영상이 구동되는 구간에 서는 상기 j상의 스캔용 클릭펄스들(S-CLK\_1 내지 S-CLK\_6)을 60Hz의 주파수로 출력하고, 정지 영상이 구동되는

구간에서는 상기 j상의 스캔용 클럭필스들(S-CLK\_1 내지 S-CLK\_6)을 1Hz의 주파수로 출력하므로, 부분적으로 동영상이 존재할 경우에도 게이트 라인들(블럭)별로 저 주파수 구동이 가능하다.

- [0112] 이 때, 상기 커패시터(C2)에 외부에서 방전 신호(discharge signal)가 입력되면, 상기 커패시터(C2)가 충전되고, 상기 커패시터(C2)에 충전된 전압에 따라 상기 제 4 스위칭소자(T3c)가 턴온되어 상기 노드(Q)에서 발생되는 리플을 제거하기 위한 패스를 형성한다. 그리고, 상기 Q 노드의 전압에 따라 상기 제 5 스위칭소자(T3q)가 턴온되어 상기 커패시터(C2)에 저장된 방전 신호를 방전시킨다.

- [0113] 따라서, 동 영상 구동 시는 상기 커패시터(C2)에 한번의 방전 신호(discharge signal)를 인가하고, 정지 영상 구동 시에는 상기 커패시터(C2)에 두번의 방전 신호(discharge signal)를 인가한다.

- [0114] 이와 같이, 별도로 Q 노드에 발생될 수 있는 리플을 제거하는 패스를 형성하므로, 스위칭소자의 열화를 방지할 수 있다.

- [0115] 이상에서 설명한 본 발명은 상술한 실시예 및 첨부된 도면에 한정되는 것이 아니고, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것이 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

## 도면

### 도면1

### 도면2a

## 도면2b

# 도면3

- 16 -

| 专利名称(译)        | 移位寄存器和使用它的液晶显示器                                                                           |         |            |  |

|----------------|-------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020160092607A                                                                          | 公开(公告)日 | 2016-08-05 |  |

| 申请号            | KR1020150013191                                                                           | 申请日     | 2015-01-28 |  |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                  |         |            |  |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                 |         |            |  |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                 |         |            |  |

| [标]发明人         | YOU JAE YONG<br>유재용<br>CHOI SEUNG CHAN<br>최승찬<br>LEE JUNG HYUN<br>이정현<br>KIM JI HA<br>김지하 |         |            |  |

| 发明人            | 유재용<br>최승찬<br>이정현<br>김지하                                                                  |         |            |  |

| IPC分类号         | G09G3/36                                                                                  |         |            |  |

| CPC分类号         | G09G3/3648                                                                                |         |            |  |

| 代理人(译)         | Bakyoungbok                                                                               |         |            |  |

| 外部链接           | Espacenet                                                                                 |         |            |  |

|                |                                                                                           |         |            |  |

## 摘要(译)

本发明涉及使用LRR(低刷新率)驱动特别可能作为显示装置的移位寄存器和液晶显示器,尤其是线路,它改善了LRR(低刷新率)驱动中的定义误差。可以最小化边框尺寸,并且包括进位脉冲输出部分和扫描脉冲输出,其中每个级独立地输出进位脉冲和扫描脉冲,并且包括Q节点纹波去除通过以防止Q节点的纹波并且至少包括2个用于进位的时钟脉冲和用于扫描的至少2个时钟脉冲与至少2个进位脉冲一起使用。