(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0139743

(43) 공개일자 2012년12월27일

(51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G02F 1/133* (2006.01)

(21) 출원번호 10-2012-7023942

(22) 출원일자(국제) 2011년02월01일

심사청구일자 없음

(85) 번역문제출일자 2012년09월13일

(86) 국제출원번호 PCT/JP2011/052465

(87) 국제공개번호 WO 2011/102248

국제공개일자 2011년08월25일

(30) 우선권주장

JP-P-2010-034884 2010년02월19일 일본(JP)

(71) 출원인

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

우메자키 아츠시

일본 2430036 가나가와Ken 아쓰기시 하세 398 가부

시키가이샤 한도오따이 에네루기 켄큐쇼 내

미야케 히로유키

일본 2430036 가나가와Ken 아쓰기시 하세 398 가부

시키가이샤 한도오따이 에네루기 켄큐쇼 내

(74) 대리인

박충범, 장수길, 이중희

전체 청구항 수 : 총 22 항

(54) 발명의 명칭 액정 표시 장치 및 전자 장치

### (57) 요약

감소된 재생률로 표시되는 정지 화상의 품질 열화를 억제하기 위한 것이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 화이트 모드(또는 노멀리 블랙 모드) 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급된다. 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색(또는 흰색)을 표현하기 위해 액정에 인가되는 전압의 절대값은, 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색(또는 흰색)을 표현하기 위해 액정에 인가되는 전압의 절대값보다 크다.

**대 표 도** - 도1a

## 특허청구의 범위

### 청구항 1

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 화이트 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급되며,

상기 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 상기 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은, 상기 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 상기 노멀리 화이트 모드 액정에 인가되는 전압의 절대값보다 큰, 액정 표시 장치.

### 청구항 2

제1항에 있어서,

상기 타이밍 제어기는,

상기 화상 신호의 그레이 레벨 수를 판단하는 분석부;

상기 전압들의 절대값들을 스위칭하는 스위치를 포함하는 패널 제어기; 및

상기 분석부로부터의 신호에 따라 상기 스위치의 온/오프를 제어하는 화상 신호 보정 제어부를 포함하는, 액정 표시 장치.

### 청구항 3

제1항에 있어서,

상기 표시부 내의 픽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

### 청구항 4

제1항에 따른 액정 표시 장치를 포함하는, 전자 장치.

### 청구항 5

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 블랙 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급되며,

상기 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 상기 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은, 상기 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 상기 노멀리 블랙 모드 액정에 인가되는 전압의 절대값보다 큰, 액정 표시 장치.

### 청구항 6

제5항에 있어서,

상기 타이밍 제어기는,

상기 화상 신호의 그레이 레벨 수를 판단하는 분석부;

상기 전압들의 절대값들을 스위칭하는 스위치를 포함하는 패널 제어기; 및

상기 분석부로부터의 신호에 따라 상기 스위치의 온/오프를 제어하는 화상 신호 보정 제어부를 포함하는, 액정 표시 장치.

#### 청구항 7

제5항에 있어서,

상기 표시부 내의 퍽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

#### 청구항 8

제5항에 따른 액정 표시 장치를 포함하는, 전자 장치.

#### 청구항 9

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 화이트 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급되며,

상기 표시부에서 상기 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 상기 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은, 상기 화상 신호의 그레이 레벨 수가 작아짐에 따라 증가하는, 액정 표시 장치.

#### 청구항 10

제9항에 있어서,

상기 타이밍 제어기는

상기 화상 신호의 그레이 레벨 수를 판단하는 분석부;

상기 전압의 절대값을 스위칭하는 스위치를 포함하는 패널 제어기; 및

상기 분석부로부터의 신호에 따라 상기 스위치의 온/오프를 제어하는 화상 신호 보정 제어부를 포함하는, 액정 표시 장치.

#### 청구항 11

제9항에 있어서,

상기 표시부 내의 퍽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

#### 청구항 12

제9항에 따른 액정 표시 장치를 포함하는, 전자 장치.

#### 청구항 13

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 블랙 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급되며,

며,

상기 표시부에서 상기 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 상기 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은, 상기 화상 신호의 그레이 레벨 수가 작아짐에 따라 증가하는, 액정 표시 장치.

#### 청구항 14

제13항에 있어서,

상기 타이밍 제어기는

상기 화상 신호의 그레이 레벨 수를 판단하는 분석부;

상기 전압의 절대값을 스위칭하는 스위치를 포함하는 패널 제어기; 및

상기 분석부로부터의 신호에 따라 상기 스위치의 온/오프를 제어하는 화상 신호 보정 제어부를 포함하는, 액정 표시 장치.

#### 청구항 15

제13항에 있어서,

상기 표시부 내의 픽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

#### 청구항 16

제13항에 따른 액정 표시 장치를 포함하는, 전자 장치.

#### 청구항 17

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 화이트 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 정지 화상을 표시하기 위한 제1 그레이 레벨 수를 갖는 제1 화상 신호 및 정지 화상을 표시하기 위한 제2 그레이 레벨 수를 갖는 제2 화상 신호가 공급되며,

상기 타이밍 제어기에 의해, 상기 표시부에서 상기 제1 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 상기 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은, 상기 제1 그레이 레벨 수보다 작은 상기 제2 그레이 레벨 수를 갖는 상기 제2 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 상기 노멀리 화이트 모드 액정에 인가되는 전압의 절대값보다 작게 되는, 액정 표시 장치.

#### 청구항 18

제17항에 있어서,

상기 표시부 내의 픽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

#### 청구항 19

제17항에 따른 액정 표시 장치를 포함하는, 전자 장치.

#### 청구항 20

액정 표시 장치로서,

구동 회로에 의해 제어되며 노멀리 블랙 모드 액정을 포함하는 표시부; 및

상기 구동 회로를 제어하는 타이밍 제어기를 포함하며,

상기 타이밍 제어기에는 정지 화상을 표시하기 위한 제1 그레이 레벨 수를 갖는 제1 화상 신호 및 정지 화상을 표시하기 위한 제2 그레이 레벨 수를 갖는 제2 화상 신호가 공급되며,

상기 타이밍 제어기에 의해, 상기 표시부에서 상기 제1 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 상기 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은, 상기 제1 그레이 레벨 수보다 작은 상기 제2 그레이 레벨 수를 갖는 상기 제2 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 상기 노멀리 블랙 모드 액정에 인가되는 전압의 절대값보다 작게 되는, 액정 표시 장치.

## 청구항 21

제20항에 있어서,

상기 표시부 내의 픽셀들은 각각 화상 신호의 기입을 제어하는 트랜지스터를 포함하며,

상기 트랜지스터의 반도체층은 산화물 반도체를 포함하는, 액정 표시 장치.

## 청구항 22

제20항에 따른 액정 표시 장치를 포함하는, 전자 장치.

## 명세서

### 기술 분야

[0001]

본 발명은 액정 표시 장치, 액정 표시 장치를 구동하는 방법, 및 액정 표시 장치를 포함하는 전자 장치에 관한 것이다.

### 배경 기술

[0002]

액정 표시 장치들은 텔레비전 세트 등의 대형 표시 장치 및 휴대폰 등의 소형 장치들에 널리 사용된다. 고부가 가치의 장치에 대한 수요가 있으며, 그 개발이 진행되고 있다. 최근 전 세계적인 환경에 대한 관심 증가 및 휴대폰의 편리성 개선의 측면에서, 전력 소비가 낮은 액정 표시 장치의 개발이 주목 받고 있다.

[0003]

비특허문헌 1은 액정 표시 장치의 전력 소비를 감소시키기 위해 동화상을 표시할 때의 재생률과 정지 화상을 표시할 때의 재생률이 서로 상이한 구조를 개시하고 있다. 또한, 비특허문헌 1은 정지 화상이 표시되는 경우 정지 기간 및 스캐닝 기간에서의 신호 스위칭으로 인한 드레인 공통 전압의 변화에 따라 플리커(flicker)가 인식되는 것을 방지하기 위해, 동일 위상을 갖는 교류 신호들이 정지 기간에 신호선 및 공통 전극에 인가되고, 이로써 드레인 공통 전압은 변하지 않는다.

### 선행기술문헌

#### 비특허문헌

[0004]

(비특허문헌 0001) Kazuhiko Tsuda 등 "Ultra low power consumption technologies for mobile TFT-LCDs", IDW02, pp. 295-298 (2002)

### 발명의 내용

[0005]

비특허문헌 1에 개시된 바와 같이, 정지 화상을 표시할 때 재생률을 감소해 전력 소비가 줄어들 수 있다. 그러나, 픽셀 전극의 전위가 픽셀 트랜지스터의 오프 전류 및/또는 액정으로부터의 누설 전류에 의해 변할 수 있기 때문에 일부 경우에 픽셀 전극과 공통 전극 사이의 전압은 계속 고정될 수 없다. 결과적으로, 액정에 인가되는 전압이 변하기 때문에 원하는 그레이 레벨(gray level)을 얻을 수 없고 표시 화상의 품질이 열화된다.

[0006]

다중 그레이 레벨 표시가 수행되는 경우 그레이 레벨이 쉽게 변하기 때문에, 그레이 레벨이 변하지 않도록 재생률이 높게 유지될 필요가 있다. 따라서, 액정 표시 장치의 전력 소비는 재생률 감소에 의해 충분히 줄일 수 없다.

[0007]

이에 따라, 본 발명의 일 실시형태의 목적은 감소된 재생률로 정지 화상이 표시되는 경우 그레이 레벨 변화로

인한 화질 열화를 억제하는 것이다.

[0008] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 화이트 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급된다. 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값보다 크다.

[0009] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 블랙 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 동화상을 표시하기 위한 화상 신호 및 정지 화상을 표시하기 위한 화상 신호가 공급된다. 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은, 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값보다 크다.

[0010] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 화이트 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 정지 화상을 표시하기 위한 화상 신호에 공급된다. 표시부에서 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은 화상 신호의 그레이 레벨 수가 작아짐에 따라 타이밍 제어기에 의해 증가한다.

[0011] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 블랙 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 정지 화상을 표시하기 위한 화상 신호가 공급된다. 표시부에서 화상 신호에 대응하는 화상에 흰색을 표현하기 위해, 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은 화상 신호의 그레이 레벨 수가 작아짐에 따라 타이밍 제어기에 의해 증가한다.

[0012] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 화이트 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 정지 화상을 표시하기 위해 제1 그레이 레벨 수를 갖는 제1 화상 신호 및 제2 그레이 레벨 수를 갖는 제2 화상 신호가 제공된다. 타이밍 제어기에 의하면, 표시부에서 제1 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은 제1 그레이 레벨 수보다 작은 제2 그레이 레벨 수를 갖는 제2 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값보다 작아진다.

[0013] 본 발명의 일 실시형태는 다음과 같이 설명되는 액정 표시 장치이다. 액정 표시 장치는 구동 회로에 의해 제어되는 표시부를 포함하고, 노멀리 블랙 모드 액정 및 구동 회로를 제어하기 위한 타이밍 제어기를 포함한다. 타이밍 제어기에는 정지 화상을 표시하기 위해 제1 그레이 레벨 수를 갖는 제1 화상 신호 및 제2 그레이 레벨 수를 갖는 제2 화상 신호가 제공된다. 타이밍 제어기에 의해, 표시부에서 제1 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은 제1 그레이 레벨 수보다 작은 제2 그레이 레벨 수를 갖는 제2 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값보다 작아진다.

[0014] 본 발명의 일 실시형태에 따른 액정 표시 장치에는 동화상을 표시하기 위한 화상 신호가 공급될 수 있다. 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에서 검정색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값은 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 노멀리 화이트 모드 액정에 인가되는 전압의 절대값보다 클 수 있다.

[0015] 본 발명의 일 실시형태에 따른 액정 표시 장치에는 동화상을 표시하기 위한 화상 신호가 공급될 수 있다. 정지 화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값은 동화상을 표시하기 위한 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 노멀리 블랙 모드 액정에 인가되는 전압의 절대값보다 클 수 있다.

[0016] 본 발명의 일 실시형태에 따른 액정 표시 장치에서, 타이밍 제어기는 화상 신호의 그레이 레벨 수를 판단하는 분석부, 전압의 절대값을 스위칭하는 스위치를 포함하는 패널 제어기, 및 분석부로부터의 신호에 따라 스위치의

온/오프를 제어하는 화상 신호 보정 제어부를 포함할 수 있다.

[0017] 본 발명의 일 실시형태에 따른 액정 표시 장치에서, 표시부 내의 픽셀들은 각각 화상 신호의 기입을 제어하기 위한 트랜지스터를 포함할 수 있다. 트랜지스터의 반도체층은 산화물 반도체를 포함할 수 있다.

[0018] 본 발명의 일 실시형태에 따라, 감소된 재생률로 정지 화상이 표시되는 경우 그레이 레벨 변화로 인한 화질 열화를 감소시킬 수 있다. 또한, 정지 화상을 표시할 때 재생률 감소에 의해 전력 소비를 줄일 수 있다.

### 도면의 간단한 설명

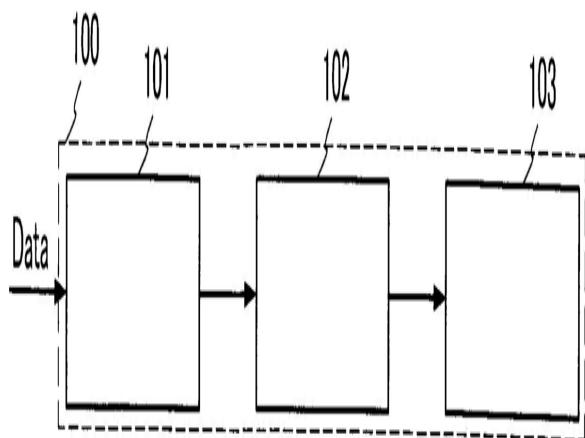

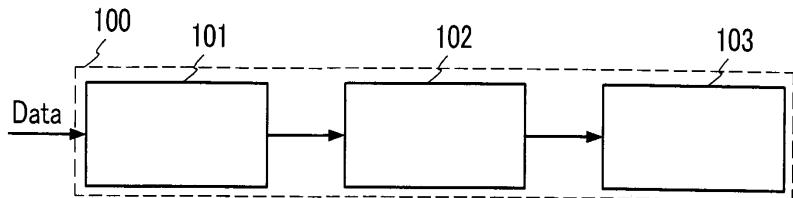

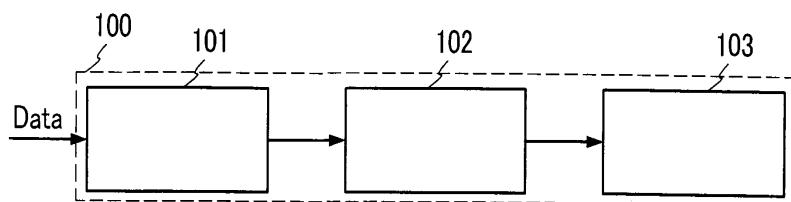

[0019] 도 1a 내지 도 1c는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 2a 및 도 2b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 3a 및 도 3b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 4a 및 도 4b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 5a 및 도 5b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 6은 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 7은 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 8은 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 9a 및 도 9b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 10은 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 11a 내지 도 11d는 각각 본 발명의 일 실시형태에 따른 트랜지스터를 도시한다.

도 12의 (a-1), (a-2), 및 (b)는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 13은 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 14a 및 도 14b는 각각 본 발명의 일 실시형태에 따른 액정 표시 장치를 도시한다.

도 15a 내지 도 15d는 각각 본 발명의 일 실시형태에 따른 전자 장치를 도시한다.

도 16a 내지 도 16d는 각각 본 발명의 일 실시형태에 따른 전자 장치를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0020] 본 발명의 실시형태들은 첨부 도면을 참조하여 이하 설명될 것이다. 본 발명은 여러 상이한 모드로 수행될 수 있으며, 본 발명의 모드 및 상세 설명은 본 발명의 목적 및 범위에서 벗어나지 않고 다양한 방법으로 변형될 수 있다는 점은 당업자에게 쉽게 이해된다는 점에 유의한다. 따라서, 본 발명은 다음의 실시형태들의 설명으로 제한되는 것으로 해석되지 않는다. 이하 설명된 본 발명의 구조에서, 동일한 부분을 표시하는 참조 부호가 상이한 도면에서 공통적으로 사용된다는 점에 유의한다.

[0021] 일부 경우에, 실시형태들의 도면 내의 컴포넌트의 사이즈, 층의 두께, 신호 파형, 또는 영역은 간략화를 위해 과장되어 있다. 따라서, 본 발명의 실시형태들은 이러한 규모로 제한되지 않는다.

[0022] 본 명세서에서 채택된 "제1", "제2", "제3", "제N"(여기서, N은 자연수) 등의 용어는 컴포넌트들 사이의 혼동을 피하기 위해 사용되며 수치상으로 제한을 설정하지 않는다는 점에 유의한다.

[0023] (제1 실시형태)

[0024] 이 실시형태에서, 액정 표시 장치는 개략도, 블록도, 및 액정 소자의 투과율 및 인가 전압 사이의 관계를 나타내는 도면을 참조하여 설명될 것이다.

[0025] 우선, 본 명세서에 관한 액정 표시 장치는 액정 표시 장치의 블록도이고 액정 표시 장치를 설명하는 개략도인 도 1a 내지 도 1c를 참조하여 설명될 것이다.

[0026] 도 1a에 도시된 액정 표시 장치(100)는 (타이밍 제어 회로라고도 지칭되는) 타이밍 제어기(101), 구동 회로

(102), 및 표시부(103)를 포함한다. 타이밍 제어기(101)에는 외부로부터 화상 신호(Data)가 공급된다.

[0027] 도 1a의 타이밍 제어기(101)에는 화상 신호(Data)의 그레이 레벨들의 수(즉, 화상 신호(Data)로 표시되는 화상의 그레이 레벨들의 수)에 따라 액정 소자에 인가되는 전압의 절대값을 변환하는 기능이 있다. 구체적으로, 타이밍 제어기(101)에는 표시부(103)에 화상 신호에 대응하는 화상에 검은색이 표시되는 경우 노멀리 화이트 모드 액정들을 포함하는 액정 소자에 인가되는 전압의 절대값을 증가시키는 기능 또는 표시부(103)에 화상 신호에 대응하는 화상에 흰색이 표시되는 경우 노멀리 블랙 모드 액정들을 포함하는 액정 소자에 인가되는 전압의 절대값을 증가시키는 기능이 있다.

[0028] 도 1a에 도시된 구동 회로(102)는 (스캔선 구동 회로라고도 지칭되는) 게이트선 구동 회로(gate line driver circuit) 및 (신호선 구동 회로라고도 지칭되는) 소스선 구동 회로(source line driver circuit)를 포함한다. 게이트선 구동 회로 및 소스선 구동 회로는 각각 복수의 픽셀을 포함하는 표시부(103)를 구동하기 위한 회로로서, (시프트 레지스터(shift register)라고도 지칭되는) 시프트 레지스터 회로 또는 디코딩 회로를 포함한다. 게이트선 구동 회로 및 소스선 구동 회로는 표시부(103)가 형성된 기판 또는 표시부(103)가 형성된 기판과 상이한 기판 위에 형성될 수 있다는 점에 유의한다.

[0029] 도 1a에 도시된 표시부(103)는 복수의 픽셀, 복수의 픽셀을 스캔하고 선택하는 (스캔선이라고도 지칭되는) 게이트선, 및 복수의 픽셀에 화상 신호를 공급하는 (신호선이라고도 지칭되는) 소스선을 포함한다. 게이트선은 게이트선 구동 회로에 의해 제어된다. 소스선은 소스선 구동 회로에 의해 제어된다. 픽셀은 각각 스위칭 소자로서의 트랜지스터, 용량 소자, 및 액정 소자를 포함한다. 액정 소자는 액정들이 픽셀 전극(제1 전극)과 대향 전극(counter electrode)(제2 전극) 사이에 개재되는 구조이다. 본 명세서에서, 픽셀 전극, 대향 전극, 및 액정들이 액정 소자로 통칭된다.

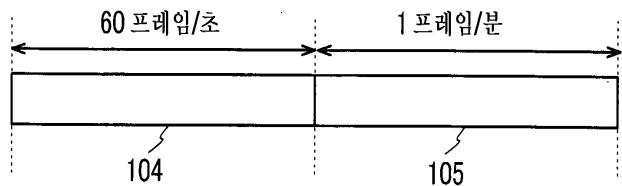

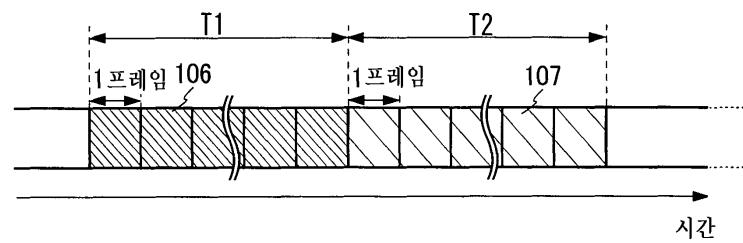

[0030] 이 실시형태에서 설명된 액정 표시 장치(100)는 도 1b에 도시된 바와 같이 동화상 표시 기간(104) 및 정지 화상 기간(105)을 갖는다. 이 실시형태에서, 정지 화상 표시 기간(105) 내의 각각의 프레임 기간 내의 화상 신호 기입 기간 및 유지 기간이 구체적으로 설명된다는 점에 유의한다.

[0031] 바람직하게, 동화상 표시 기간(104)에서 일 프레임 기간의 사이클(또는 프레임 주파수)은 1/60초 이하(60Hz 이상)이라는 점에 유의한다. 높은 프레임 주파수는 관측자가 틀리기를 인식하지 않게 만들 수 있다. 정지 화상 표시 기간(105)에서는 일 프레임 기간의 사이클이, 예를 들어 1분 이상(0.017Hz 이하) 극단적으로 연장되는 것이 바람직하다. 표시가 여러 번 스위칭되어 동일한 화상을 표시하는 경우에 비해, 프레임 주파수를 감소시킴으로써 눈의 피로감을 줄일 수 있다. 프레임 주파수는 재생률을 의미하며, 초당 스크린 표시 사이클의 횟수라는 점에 유의한다.

[0032] 동화상 표시 기간(104) 및 정지 화상 표시 기간(105)은 외부로부터 스위칭 신호를 공급함으로써 스위칭되거나, 동화상 표시 기간(104) 또는 정지 화상 표시 기간(105)이 화상 신호(Data)에 따라 판단될 수 있다는 점에 유의한다. 동화상 표시 기간(104) 및 정지 화상 표시 기간(105)이 화상 신호(Data)를 판단함으로써 스위칭되는 경우, 도 1a의 타이밍 제어기(101)는 표시부(103)의 각 픽셀에 기입된 화상 신호가 이전 기간에 기입된 화상 신호와 상이할 때 화상 신호의 연속 기입에 의해 동화상이 표시되는 동화상 표시 기간과, 표시부(103)의 각 픽셀에 기입된 화상 신호가 이전 기간에 기입된 것과 동일할 때 화상 신호의 기입이 중단되고 각 픽셀에 기입된 화상 신호가 유지되어 정지 화상이 표시되는 정지 화상 표시 기간 사이에서 기간을 스위칭한다. 또한, 재생률 감소는 프레임 기간의 길이의 증가에 대응한다.

[0033] 도 1a의 타이밍 제어기(101)의 동작을 설명하기 위해, 복수의 화상 신호, 여기에서 제1 화상 신호 및 제2 화상 신호가 도 1c에 도시된 개략도를 참조하여 특정 화상 신호(Data)로서 설명될 것이다. 도 1c에 도시된 바와 같이, 제1 화상 신호는 제1 그레이 레벨 수(구체적으로 M개의 그레이 레벨, 여기서 M은 3 이상의 자연수)를 갖는 화상 신호이며, 제1 화상 신호가 있는 표시는 기간(T1)에서 수행되며, 제2 화상 신호는 제2 그레이 레벨 수(구체적으로 N개의 그레이 레벨, 여기서 N은 2 이상의 자연수)를 갖는 화상 신호이고, 제2 화상 신호가 있는 표시는 기간(T2)에서 수행된다. 제1 그레이 레벨 수(M)는 제2 그레이 레벨 수(N)보다 큰 데, 즉 제1 화상 신호는 제2 화상 신호보다 그레이 레벨의 수가 더 많은 화상을 생성한다는 점에 유의한다. 도 1c의 기간(T1)에서의 프레임 기간으로서 기능하는 기간(106)은 제1 화상 신호가 있는 프레임 기간이다. 도 1c의 기간(T2)에서의 프레임 기간으로서 기능하는 기간(107)은 제2 화상 신호가 있는 프레임 기간이다. 이하, 제1 그레이 레벨 수(M)가 제2 그레이 레벨 수(N)보다 크다는 가정(여기서, M > N) 하에서 설명된다는 점에 유의한다.

[0034] 재생률은 기간(T1) 및 기간(T2)에서 변할 수도 있다. 예를 들어, 화상 신호의 그레이 레벨들의 수가 작아짐에

따라, 화상 신호에 대응하는 화상을 표시부에 표시할 때의 재생률이 감소할 수 있다. 재생률이 화상 신호의 그레이 레벨들의 수에 따라 변하는 경우, 시간에 따라 액정 소자에 인가되는 전압이 변하는 경우에도 그레이 레벨 변화를 줄일 수 있다. 특히, 정지 화상이 표시되는 경우에는 그레이 레벨의 개수가 작은 경우 재생률을 극적으로 감소시키는 것이 바람직하다. 정지 화상을 표시할 때 재생률을 줄이는 경우, 화상 신호의 기입 빈도가 감소될 수 있으며, 전력 소비를 줄일 수 있다. 또한, 동일한 화상을 여러 번 재기입함으로써 정지 화상이 표시되는 경우, 화상들의 스위칭이 인식되면 눈의 피로감이 발생할 수 있다. 이러한 이유 때문에, 재생률의 상당한 감소는 눈의 피로감을 감소시킬 수 있다.

[0035] 그레이 레벨들의 수(그레이 레벨 수)는 화상을 생성하는 픽셀이 컬러의 그라데이션(gradation)을 표현하는 색션들의 개수를 지칭하고, 픽셀에 기입된 화상 신호의 전압의 레벨(이하, 전압 레벨이라고 지칭함)에 의해 표현된다는 점에 유의한다. 구체적으로, 그레이 레벨들의 수는 전압 레벨의 구배(gradi ent)를 복수의 레벨들로 분할함으로써 획득되는 전압 레벨들의 전체 개수이며, 구배는 흰색으로부터 검은색으로의 변화를 나타내며, 노멀리 화이트 모드 액정들을 포함하는 액정 소자에 전압을 인가함으로써 표현된다. 또한, 그레이 레벨들의 수는 전압 레벨의 구배를 복수의 레벨들로 분할함으로써 획득되는 전압 레벨들 중에, 프레임 기간 내의 화상을 생성하는 픽셀들에 실제로 공급되는 전압 레벨들의 수를 지칭하며, 구배는 흰색으로부터 검은색으로의 변화를 나타내며, 액정 소자에 전압을 인가함으로써 표현된다. 구체적으로, 그레이 레벨들의 수는 화상을 생성하는 픽셀에 공급되는 전압 레벨들의 수에 의해 표현된다. 복수의 화상 신호들은 상이한 그레이 레벨 수들을 갖는 화상 신호들, 예를 들어 앞서 설명한 제1 화상 신호 및 제2 화상 신호 등의 상이한 그레이 레벨 수들을 갖는 복수의 화상 신호라는 점에 유의한다.

[0036] 이 실시형태에서, 액정 표시 장치에는, 특히 정지 화상 표시 기간 내의 화상 신호로 표시되는 화상의 그레이 레벨들의 수에 따라, 액정 표시 장치에는 노멀리 화이트 모드 액정들이 화상 신호에 대응하는 화상에 검은색을 표현하는 경우 액정 소자에 인가되는 전압의 절대값을 증가시키거나, 노멀리 블랙 모드 액정들이 화상 신호에 대응하는 화상에 흰색을 표현하는 경우 액정 소자에 인가되는 전압의 절대값을 증가시키는 기능이 있다. 다시 말하면, 액정들의 배향(alignment)을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값은 화상의 그레이 레벨들의 수에 따라 변환된다.

[0037] 이 실시형태의 액정 표시 장치에서, 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값은 도 1b에 도시된 동화상 표시 기간(104)보다 정지 화상 표시 기간(105)에서 더 큰 것이 바람직할 수 있다는 점이 유의한다. 예를 들어, 노멀리 화이트 모드 액정들의 경우, 정지 화상 표시 기간(105) 내의 화상 신호에 대응하는 화상에 검은색을 표현하기 위해 액정 소자에 인가되는 전압의 절대값은 동화상 표시 기간(104) 내에서 보다 크게 된다. 마찬가지로, 노멀리 블랙 모드 액정들의 경우, 정지 화상 표시 기간(105) 내의 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 액정 소자에 인가되는 전압의 절대값은 동화상 표시 기간(104) 내에서도 보다 크게 된다. 즉, 액정 표시 장치는 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값이 동화상 표시 기간(104)보다 정지 화상 표시 기간(105)에서 더 크게 되어 있는 구조이다.

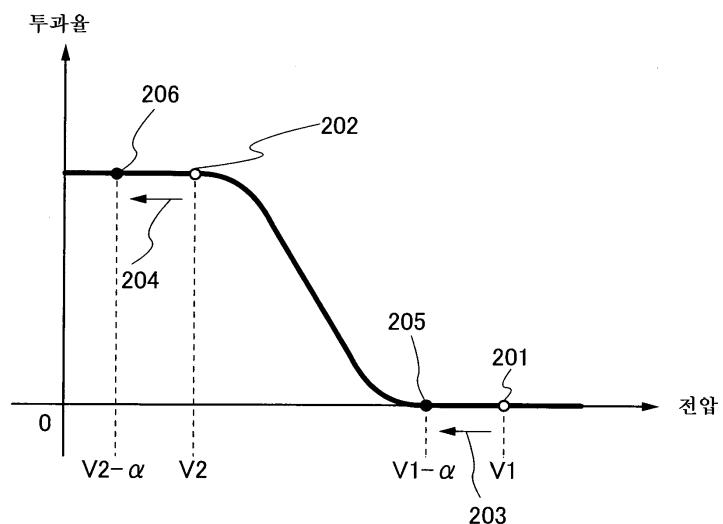

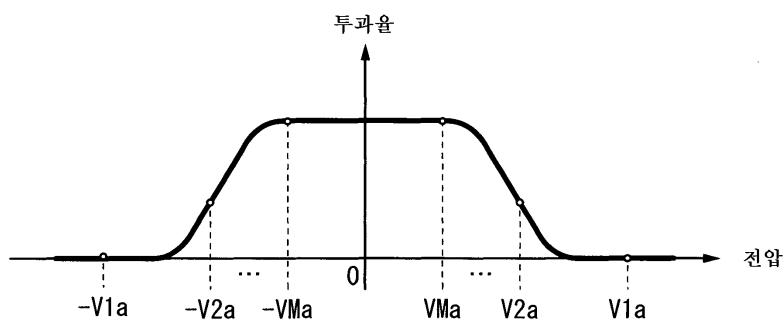

[0038] 다음으로, 이 실시형태에서의 구조의 효과를 설명하기 위해, 도 2a는 2개의 그레이 레벨들을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시하며, 도 2b는 M개의 그레이 레벨들을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시한다. 도 2a 및 도 2b는 0V가 인가되면 높은 투과율을 갖는 노멀리 화이트 모드 액정들의 투과율을 도시한다는 점에 유의한다.

[0039] 도 2a에서, 2개의 그레이 레벨들을 갖는 화상 신호 중에서, 전압(V1)은 제1 그레이 레벨(201)(검은색)에 대응하고, 전압(V2)은 제2 그레이 레벨(202)(흰색)에 대응한다. 도 2a에서 전압(V1) 및 전압(V2)이 인가된 후에, 액정 소자에 인가되는 전압들은 시간에 따라  $a$  ( $a$ 는 양수)만큼 감소되며(도 2a의 화살표(203) 및 화살표(204)를 참조), 이로써 그레이 레벨들은 전압( $V1 - a$ )에 대응하는 그레이 레벨(205) 및 전압( $V2 - a$ )에 대응하는 그레이 레벨(206)이 된다. 도 2a에서, 전압( $V1 - a$ )을 갖는 그레이 레벨(205) 및 전압( $V2 - a$ )을 갖는 그레이 레벨(206)은 각각 제1 그레이 레벨(201)(검은색) 및 제2 그레이 레벨(202)(흰색)과 동일한 투과율을 갖는다. 다시 말해, 전압(V1)은 미리 증가된 전압으로 바람직하게 변환되며, 이로써 시간에 따라 전압이 감소하는 경우에도 투과율의 변화로 인해 화상 품질이 열화되지 않는다.

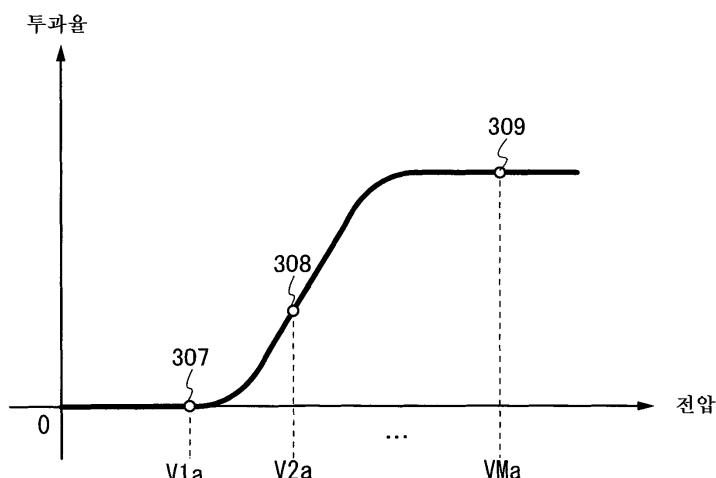

[0040] 도 2b에서, M개의 그레이 레벨들을 갖는 화상 신호 중에서, 전압(V1a)은 제1 그레이 레벨(207)(검은색)에 대응하고, 전압(V2a)은 제2 그레이 레벨(208)(중간 레벨)에 대응하고, 전압(VMa)은 M번째 그레이 레벨(209)(흰색)에 대응한다. 도 2a에 도시된 바와 같이, 도 2b에 있는 전압(V1a)은 미리 증가된 전압으로 바람직하게 변환되며, 이로써 시간에 따라 전압이 감소하는 경우에도 투과율의 변화로 인해 화상 품질이 열화되지 않는다. 도 2b의

예시에서, 중간 레벨인 제2 그레이 레벨(208)의 경우, 전압 변화에 대해 그레이 레벨이 변하지 않는 정도로 증가된 전압이 인가될 수도 있거나, 중간 레벨들에 관한 전압들이 증가되지 않을 수 있다는 점에 유의한다.

[0041] 도 2a에 예시된 2개의 그레이 레벨들을 갖는 화상 신호와 같이, 작은 개수의 그레이 레벨들을 갖는 화상 신호의 경우, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 작다. 이러한 이유로 인해, 많은 개수의 증가된 전압들의 인가에 의해, 시간에 따른 전압 감소로 인한 그레이 레벨 변화를 줄이고, 화질 열화를 줄일 수 있다. 반면에, 도 2b에 예시된 M개의 그레이 레벨들을 갖는 화상 신호와 같이, 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 크다. 이러한 이유로 인해, 많은 개수의 증가된 전압의 인가에 의한 것보다 재생률 증가만큼 화질 열화를 감소시키는 것이 바람직할 수 있다. 도 2b에 예시된 M개의 그레이 레벨들을 갖는 화상 신호와 같이, 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우조차, 시간에 따른 전압 감소로 인한 그레이 레벨 변화를 고려하여 증가된 전압의 인가에 의해 제1 그레이 레벨(검은색)을 표현하는 전압이 유지될 수 있고, 화상들의 명암비(contrast ratio)의 감소가 억제될 수 있다는 점에 유의한다. 전력 소비를 줄이기 위해, 바람직하게 더 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우보다 특히 더 작은 개수의 그레이 레벨들을 갖는 화상 신호의 경우 전압이 증가된다는 점에 유의한다.

[0042] 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값이 동화상 표시 기간(104)보다 정지 화상 표시 기간(105)에서 더 크게 되어 있는 앞서 설명한 구조를 이용하면, 화상들의 명암비의 감소는 억제될 수 있다. 구체적으로, 노멀리 화이트 모드 액정들의 경우, 정지 화상 표시 기간(105) 내의 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 액정 소자에 인가되는 전압의 절대값은 동화상 표시 기간(104) 내에서도 커진다. 정지 화상 표시 기간(105) 내의 재생률이 동화상 표시 기간(104) 내의 재생률보다 낮기 때문에, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 크다. 이러한 이유로, 정지 화상 표시 기간(105) 내의 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값을 증가시킴으로써, 화상들의 명암비 감소가 억제될 수 있다. 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값이 동화상 표시 기간(104) 내에서 증가하는 경우에도, 시간에 따른 전압 감소로 인한 그레이 레벨의 변화는 화상들의 명암비 감소를 억제하는데 영향을 미치지 않는다는 점에 유의한다. 따라서, 전력 소비를 줄일 수 있기 때문에, 액정들의 배열을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값을 감소시키는 것이 더 바람직할 수 있다.

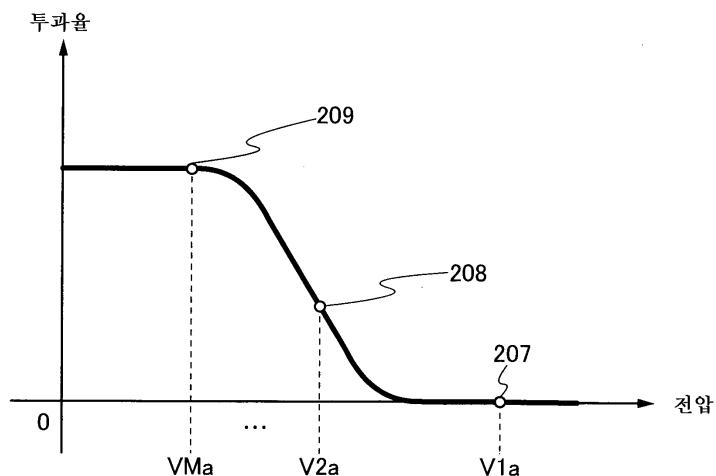

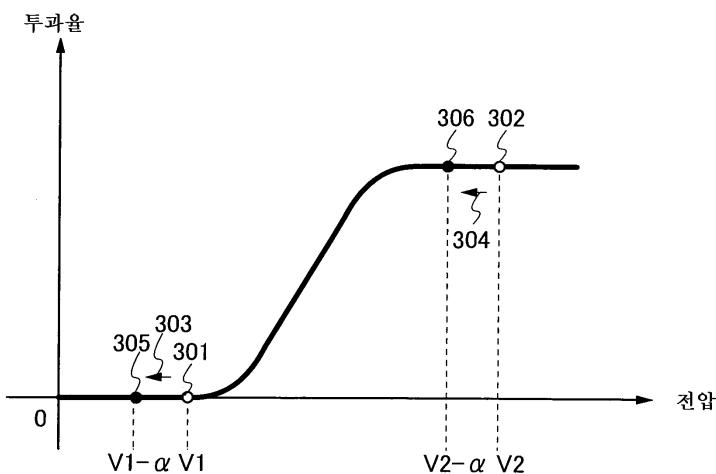

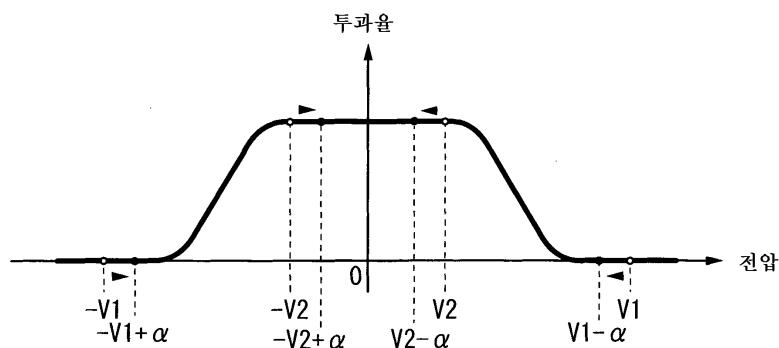

[0043] 도 2a 및 도 2b에서와 같이, 도 3a는 2개의 그레이 레벨을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시하며, 도 3b는 M개의 그레이 레벨들을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시한다. 도 3a 및 도 3b는 OV가 인가되면 낮은 투과율을 갖는 노멀리 블랙 모드 액정들의 투과율을 도시한다는 점에 유의한다.

[0044] 도 3a에서, 2개의 그레이 레벨들을 갖는 화상 신호 중에서, 전압(V1)은 제1 그레이 레벨(301)(검은색)에 대응하고, 전압(V2)은 제2 그레이 레벨(302)(흰색)에 대응한다. 도 3a에서 전압(V1) 및 전압(V2)이 인가된 후에, 액정 소자에 인가되는 전압들은 시간에 따라  $a$  ( $a$ 는 양수)만큼 감소되며(도 3a의 화살표(303) 및 화살표(304)를 참조), 이로써 그레이 레벨들은 전압( $V1 - a$ )에 대응하는 그레이 레벨(305) 및 전압( $V2 - a$ )에 대응하는 그레이 레벨(306)이 된다. 도 3a에서, 전압( $V1 - a$ )을 갖는 그레이 레벨(305) 및 전압( $V2 - a$ )을 갖는 그레이 레벨(306)은 각각 제1 그레이 레벨(301)(검은색) 및 제2 그레이 레벨(302)(흰색)과 동일한 투과율을 갖는다. 다시 말해, 전압(V2)은 미리 증가된 전압으로 바람직하게 변환되며, 이로써 시간에 따라 전압이 감소하는 경우에도 투과율의 변화로 인해 화상 품질이 열화되지 않는다. 시간에 따른 전압 감소량이 작은 경우, 더 많은 개수의 증가된 전압들의 인가는 전력 소비의 증가를 초래하기만 한다. 따라서, 작은 개수의 그레이 레벨들을 갖는 화상 신호의 경우, 바람직하게 이 실시형태에서는 증가된 전압이 인가된다.

[0045] 도 3b에서, M개의 그레이 레벨들을 갖는 화상 신호 중에서, 전압(V1a)은 제1 그레이 레벨(307)(검은색)에 대응하고, 전압(V2a)은 제2 그레이 레벨(308)(중간 레벨)에 대응하고, 전압(VMa)은 M번째 그레이 레벨(309)(흰색)에 대응한다. 도 3a에 도시된 바와 같이, 도 3b에 있는 전압(VMa)은 미리 증가된 전압으로 바람직하게 변환되며, 이로써 시간에 따라 전압이 감소하는 경우에도 투과율의 변화로 인해 화상 품질이 열화되지 않는다. 도 3b의 예시에서, 중간 레벨인 제2 그레이 레벨(308)의 경우, 전압 변화에 대해 그레이 레벨이 변하지 않는 정도로 증가된 전압이 인가될 수도 있거나, 중간 레벨들에 관한 전압들이 증가되지 않을 수 있다는 점에 유의한다.

[0046] 도 3a에 예시된 2개의 그레이 레벨들을 갖는 화상 신호와 같이, 작은 개수의 그레이 레벨들을 갖는 화상 신호의 경우, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 작다. 이러한 이유로 인해, 많은 개수의 증가된 전압들의 인가에 의해, 시간이 지남에 따른 전압 감소로 인한 그레이 레벨 변화가 감소될 수 있으며, 화질 열화가

감소될 수 있다. 한편, 도 3b에 예시된 M개의 그레이 레벨들을 갖는 화상 신호와 같이, 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 크다. 이러한 이유로 인해, 많은 개수의 증가된 전압의 인가에 의한 것보다 재생률 증가에 의해 화질 열화를 감소시키는 것이 바람직할 수 있다. 도 3b에 예시된 M개의 그레이 레벨들을 갖는 화상 신호와 같이, 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우조차, 시간에 따른 전압 감소로 인한 그레이 레벨 변화를 고려하여 증가된 전압의 인가에 의해 M번 째 그레이 레벨(흰색)을 표현하는 전압이 유지될 수 있고, 화상들의 명암비(contrast ratio)의 감소가 억제될 수 있다는 점에 유의한다. 전력 소비를 줄이기 위해, 바람직하게 더 많은 개수의 그레이 레벨들을 갖는 화상 신호의 경우보다 특히 더 작은 개수의 그레이 레벨들을 갖는 화상 신호의 경우 전압이 증가된다는 점에 유의한다.

[0047] 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값이 동화상 표시 기간(104)보다 정지 화상 표시 기간(105)에서 더 크게 되어 있는 앞서 설명한 구조를 이용하면, 화상들의 명암비의 감소는 억제될 수 있다. 구체적으로, 노멀리 블랙 모드 액정들의 경우, 정지 화상 표시 기간(105) 내의 화상 신호에 대응하는 화상에 흰색을 표현하기 위해 액정 소자에 인가되는 전압의 절대값은 동화상 표시 기간(104) 내에서보다 커진다. 정지 화상 표시 기간(105) 내의 재생률이 동화상 표시 기간(104) 내의 재생률보다 낮기 때문에, 시간에 따른 전압 감소로 인한 그레이 레벨 변화가 크다. 이러한 이유로, 정지 화상 표시 기간(105) 내의 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값을 증가시킴으로써, 화상들의 명암비 감소가 억제될 수 있다. 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값이 동화상 표시 기간(104) 내에서 증가하는 경우에도, 시간에 따른 전압 감소로 인한 그레이 레벨의 변화는 화상들의 명암비 감소를 억제하는데 영향을 미치지 않는다는 점에 유의한다. 따라서, 전력 소비를 줄일 수 있기 때문에, 액정들의 배열을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값을 감소시키는 것이 더 바람직할 수 있다.

[0048] 도 2a 및 도 2b, 도 3a 및 도 3b에서와 같이, 도 4a은 2개의 그레이 레벨을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시하며, 도 4b는 M개의 그레이 레벨들을 갖는 화상 신호의 전압과 액정들의 투과율 사이의 관계를 도시한다. 도 4a 및 도 4b는 OV가 인가되면 높은 투과율을 갖는 노멀리 화이트 모드 액정들의 투과율을 도시하며, 반전 구동을 수행할 때 투과율과 전압 사이의 관계를 도시한다. 반전 구동의 경우, 화상 신호의 극성은 도트 반전 구동(dot inversion driving), 소스선 반전 구동, 게이트선 반전 구동, 프레임 반전 구동 등에 따라 적절히 반전되며, 반전된 전압은 액정 소자에 인가된다.

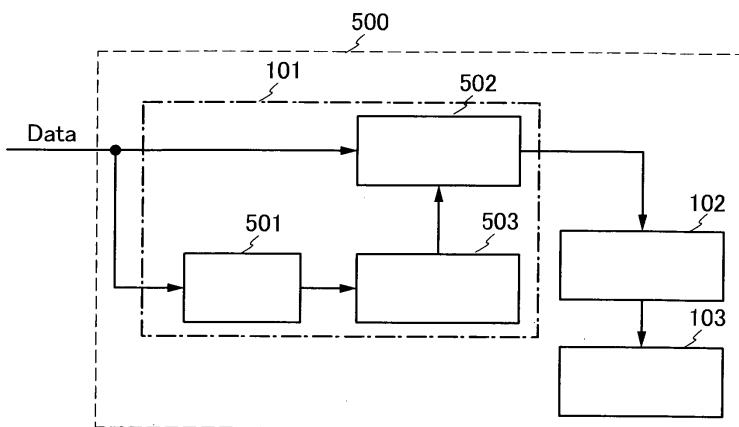

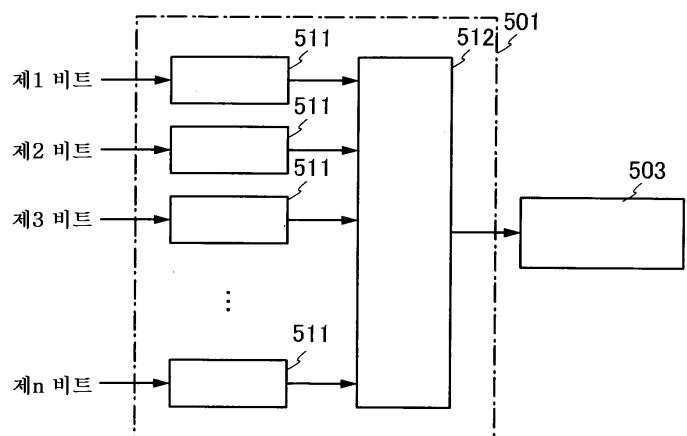

[0049] 도 5a에 도시된 블록도 내의 액정 표시 장치(500)는 도 1a에 도시된 바와 같이 (타이밍 제어 회로라고도 지칭되는) 타이밍 제어기(101), 구동 회로(102), 및 표시부(103)를 포함한다. 이 실시형태의 타이밍 제어기(101)는, 액정들의 배향을 제어하기 위해 인가되는 전압 중에 가장 높은 전압의 절대값을 특히 정지 화상 표시 기간 내의 화상 신호로 표시되는 화상의 그레이 레벨들의 수에 따라 변환한다. 도 5a의 블록도는 상이한 그레이 레벨 수들을 갖는 화상 신호들에 따라 전압이 다양하게 만들 수 있는 타이밍 제어기(101)의 상세 구조를 도시한다.

[0050] 도 5a의 타이밍 제어기(101)는 분석부(501), (표시 제어 회로로도 지칭되는) 패널 제어기(502), 및 화상 신호 보정 제어부(503)를 포함한다. 도 5a에 도시된 분석부(501)는 입력된 화상 신호(Data)의 그레이 레벨을 검출하는 회로일 수 있으며, 픽셀들의 비트 값들을 분석할 수 있다. 화상 신호 보정 제어부(503)는 분석부(501)에 의해 검출된 화상 신호(Data)의 그레이 레벨 또는 픽셀들의 비트 값의 분석 결과에 기초하여, 그레이 레벨 수가 상이한 제1 화상 신호 및 제2 화상 신호의 전압을 변경하기 위해 패널 제어기(502)를 제어한다.

[0051] 도 5b는 분석부(501)의 구조를 도시한다. 도 5b의 분석부(501)는 복수의 카운터 회로(511) 및 판단부(512)를 포함한다. 카운터 회로(511)는 비트마다 제공되는데, 입력된 화상 신호(Data)의 비트 값에 따라 카운트 값을 스위칭함으로써 카운팅을 수행한다. 구체적으로, 예를 들어 복수의 카운터 회로(511) 중 적어도 하나에서 카운트 값이 스위칭되는 경우, 모든 픽셀의 비트 값들이 동일하지 않다는 것을 알 수 있다. 판단부(512)는 카운트 값이 복수의 카운터 회로(511)에서 스위칭되는지 여부를 판단하고, 그 결과를 화상 신호 보정 제어부(503)로 출력한다.

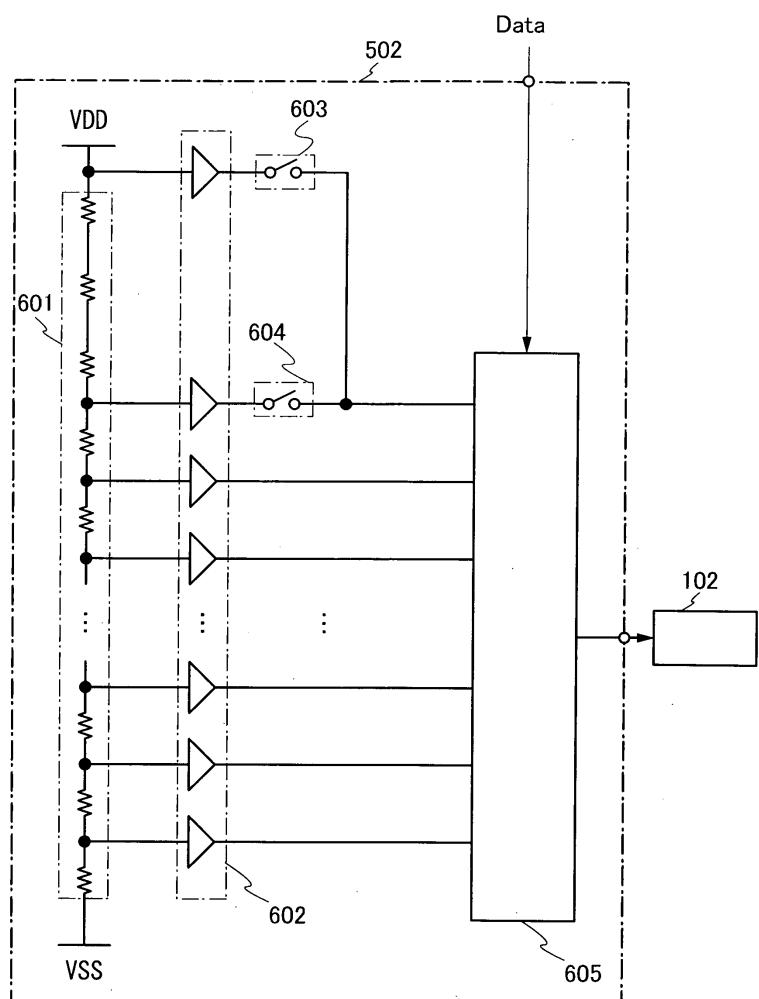

[0052] 도 6에 도시된 바와 같이, 패널 제어기(502)는 복수의 저항 소자(601), 버퍼 회로(602), 제1 스위치(603), 제2 스위치(604), 및 선택 회로(멀티플렉서 회로)(605)를 포함한다. 도 6에 도시된 회로는 직렬로 접속된 복수의 저항 소자(601)에 의해 획득되는 복수의 전압들을 버퍼 회로(602)를 통해 출력하고, 화상 신호의 그레이 레벨에 대응하는 전압으로서 각각의 그레이 레벨에 관한 전압들을 변환한다. 예를 들어, 화상 신호 보정 제어부(503)로부터의 신호에 따라 제1 스위치(603) 및 제2 스위치(604)가 스위칭되어 동작하는 경우, 픽셀들의 비트 값들의 분석 결과 또는 그레이 레벨들의 수에 따라 제1 화상 신호 및 제2 화상 신호의 가장 높은 전압을 변경할 수 있

다.

[0053] 도 6에 도시된 바와 같이, 제1 스위치(603) 및 제2 스위치(604)는 화상 신호 보정 제어부(503)에 의해 스위칭되어 동작한다. 구체적으로, 도 6에서, 예를 들어 화상 신호가 제1 그레이 레벨 수(M)를 갖는 경우 제1 스위치(603)는 오프(비도통)되고, 제2 스위치(604)는 온(도통)되고, 화상 신호가 제2 그레이 레벨 수(N)를 갖는 경우 제1 스위치(603)는 온되고, 제2 스위치(604)는 오프된다. 이에 따라, 투과율이 변하지 않을 정도로 증가된 전압을 인가할 수 있다.

[0054] 선택 회로(605)는 화상 신호에 따라 직렬로 접속된 복수의 저항 소자(601)에 의해 획득된 복수의 전압 중 어느 하나를 선택하고, 선택 전압을 구동 회로(102)로 출력한다.

[0055] 앞서 설명한 바와 같이, 이러한 실시형태의 구조에서 정지 화상을 표시하는 기간에, 그레이 레벨 변화로 인한 화질 열화를 재생률 감소에 의해 사전에 줄일 수 있으며, 특히 명암비 감소를 줄일 수 있다. 또한, 정지 화상을 표시할 때 재생률 감소에 의해 전력 소비를 줄일 수 있다.

[0056] 이 실시형태는 다른 실시형태들에서 설명된 컴포넌트들 중 어느 하나와의 적절한 결합으로 구현될 수 있다.

[0057] (제2 실시형태)

[0058] 이 실시형태에서, 본 발명의 액정 표시 장치 및 전력 소비가 더 낮은 액정 표시 장치의 일 실시형태를 도 7, 도 8, 도 9a 및 도 9b, 및 도 10을 참조하여 설명할 것이다.

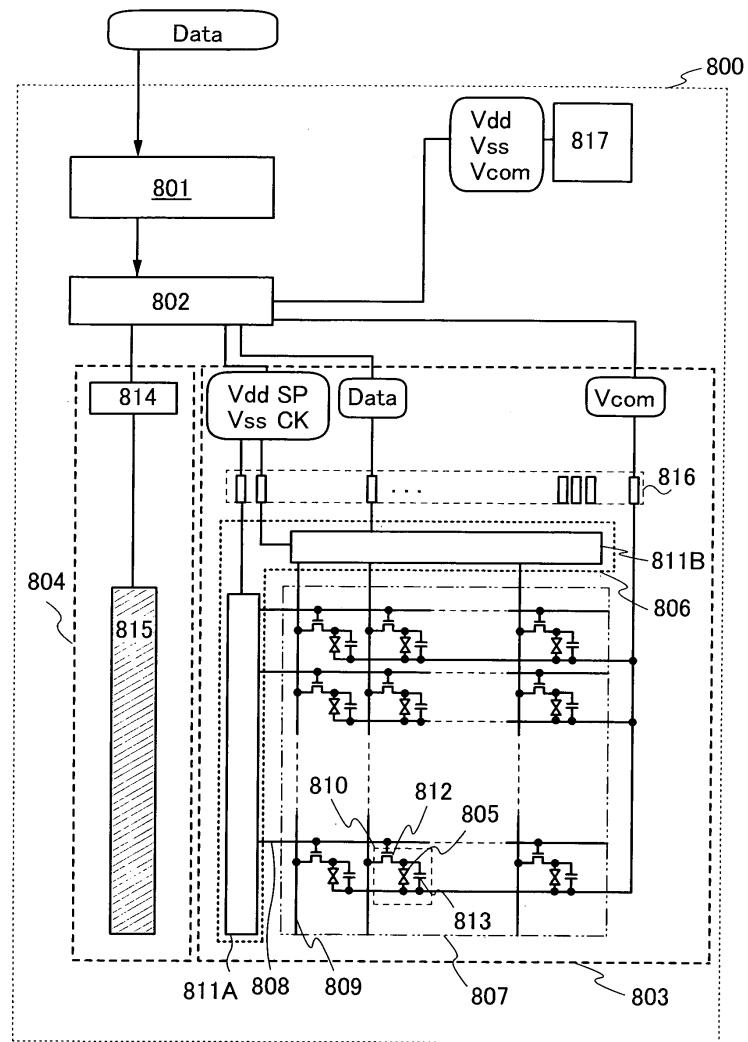

[0059] 도 7의 블록도는 이 실시형태에 설명된 액정 표시 장치(800) 내의 컴포넌트들을 도시한다. 액정 표시 장치(800)는 화상 처리 회로(801), 타이밍 제어기(802), 및 표시 패널(803)을 포함한다. 액정 표시 장치(800)가 투과형(transmissive) 액정 표시 장치 또는 반투과형(transflective) 액정 표시 장치인 경우, 백라이트부(804)는 광원으로서 제공된다.

[0060] 액정 표시 장치(800)에는 그에 접속된 외부 장치로부터 화상 신호(화상 신호(Data))가 공급된다. 액정 표시 장치의 전원(817)이 턴온되어 전원 공급을 시작하면 전원 전위들(높은 전원 전위(Vdd), 낮은 전원 전위(Vss), 및 공통 전위(Vcom))가 공급된다. 제어 신호(시작 펄스(SP) 및 클럭 신호(CK))는 타이밍 제어기(802)에 의해 공급된다.

[0061] 높은 전원 전위(Vdd)는 기준 전위보다 높으며, 낮은 전원 전위(Vss)는 기준 전위와 같거나 낮다는 점에 유의한다. 바람직하게 높은 전원 전위(Vdd) 및 낮은 전원 전위(Vss) 모두 트랜ジ스터가 동작할 수 있는 전위이다. 일부 경우에 높은 전원 전위(Vdd) 및 낮은 전원 전위(Vss)는 전원 전압이라고 통칭된다는 점에 유의한다.

[0062] 공통 전위(Vcom)는 픽셀 전극에 공급되는 화상 신호의 전위에 관해 참조로서 기능하는 고정 전위이기만 하면 임의의 전위일 수 있다. 예를 들어, 공통 전위(Vcom)는 접지 전위일 수 있다.

[0063] 화상 신호(Data)는 도트 반전 구동, 소스선 반전 구동, 게이트선 반전 구동, 프레임 반전 구동 등에 따라 적절히 반전되어 액정 표시 장치(800)에 입력된다. 화상 신호가 아날로그 신호인 경우, 화상 신호는 A/D 변환기 등을 통해 디지털 신호로 변환되어 액정 표시 장치(800)에 공급된다.

[0064] 이 실시형태에서, 액정 소자(805)의 전극 중 하나(대향 전극) 및 용량 소자(813)의 하나의 전극에는 전원(817)으로부터 타이밍 제어기(802)를 통해 고정 전위인 공통 전위(Vcom)가 공급된다.

[0065] 화상 처리 회로(801)는 입력된 화상 신호(Data)를 분석, 연산, 및/또는 처리하며, 제어 신호와 함께 처리된 화상 신호(Data)를 타이밍 제어기(802)로 출력한다.

[0066] 구체적으로, 화상 처리 회로(801)는 입력된 화상 신호(Data)를 분석하고, 신호가 동화상을 위한 것인지 정지 화상을 위한 것인지를 판단하고, 판단 결과를 포함하는 제어 신호를 타이밍 제어기(802)로 출력한다. 또한, 화상 처리 회로(801)는 동화상 또는 정지 화상을 위한 데이터를 포함하는 화상 신호(Data)로부터 하나의 프레임의 정지 화상을 위한 데이터를 추출하여, 데이터가 정지 화상을 위한 것임을 나타내는 제어 신호와 함께 추출된 데이터를 타이밍 제어기(802)로 출력한다. 화상 처리 회로(801)는 앞서 설명한 제어 신호와 함께 입력된 화상 신호(Data)를 타이밍 제어기(802)로 출력한다. 앞서 설명한 기능은 화상 처리 회로(801)의 기능의 예시이며, 표시 장치의 응용 형태에 따라 다양한 화상 처리 기능들이 적용될 수 있다는 점에 유의한다.

[0067] 타이밍 제어기(802)는 제1 실시형태에서 설명된 기능들을 가질 뿐 아니라, 처리된 화상 신호(Data), 제어 신호(구체적으로, 시작 펄스(SP) 및 클럭 신호(CK) 등의 제어 신호의 공급 및 중단 사이의 스위칭을 제어하는 신

호), 전원 전위(높은 전원 전위(Vdd), 낮은 전원 전위(Vss), 및 공통 전위(Vcom))를 표시 패널(803)로 공급하는 회로이다. 화상 처리 회로(801)의 기능의 일부가 타이밍 제어기(802)와 공유되는 경우 타이밍 제어기(802)는 화상 처리 회로(801)의 기능을 가질 수도 있다는 점에 유의한다.

- [0068] 산술 연산(예를 들어, 화상 신호 간의 차 검출)이 디지털 신호로 변환되는 화상 신호에서 쉽게 수행된다는 점에 유의하며, 이에 따라 입력된 화상 신호(화상 신호(Data))가 아날로그 신호인 경우, A/D 변환기 등이 화상 처리 회로(801)에 제공될 수 있다.

- [0069] 표시 패널(803)에서, 액정 소자(805)는 한 쌍의 기판(제1 기판 및 제2 기판) 사이에 배치된다. 제1 기판에는 구동 회로부(806) 및 픽셀부(807)가 제공된다. 제2 기판은 (공통 컨택이라고도 지칭되는) 공통 접속부 및 (대향 전극이라고도 지칭되는) 공통 전극이 제공된다. 공통 접속부는 제1 기판과 제2 기판을 전기적으로 접속시키며, 제1 기판 위에 제공될 수 있다는 점에 유의한다.

- [0070] 픽셀부(807)에서, 복수의 게이트선(스캔선)(808) 및 복수의 소스선(신호선)(809)이 제공되며, 복수의 픽셀들(810)이 게이트선(808) 및 소스선(809)으로 둘러 싸여서 행렬 형태로 배열된다. 이 실시형태에 설명한 표시 패널에서, 게이트선(808)은 게이트선 구동 회로(811A)로부터 연장되며, 소스선(809)은 소스선 구동 회로(811B)로부터 연장된다는 점에 유의한다.

- [0071] 픽셀(810)은 스위칭 소자로서 트랜지스터(812), 트랜지스터(812)에 접속된 용량 소자(813), 및 액정 소자(805)를 포함한다.

- [0072] 액정 소자(805)는 액정의 광학적 변조 작용(optical modulation action)에 의해 광을 전송할지 여부를 제어한다. 액정의 광학적 변조 작용은 액정에 인가되는 전기장에 의해 제어된다. 액정에 인가되는 전기장의 방향은 액정 재료, 구동 방법, 전극 구조에 따라 다양하며, 적절하게 선택될 수 있다. 예를 들어, 전기장이 액정의 두께 방향(소위 수직 방향)에 인가되는 구동 방법이 사용되는 경우, 픽셀 전극 및 공통 전극이 각각 제1 기판 및 제2 기판에 제공되며, 이로써 액정들은 제1 기판 및 제2 기판 사이에 제공된다. 또한, 전기장이 기판의 평면 방향에 인가되는(즉, 소의 수평 방향 전기장이 인가되는) 구동 방법이 사용되는 경우, 픽셀 전극 및 공통 전극이 액정들에 관해 동일 측면에 제공된다. 또한, 픽셀 전극 및 공통 전극은 다양한 개구 패턴들을 가질 수 있다. 이 실시형태에서, 소자가 광학적 변조 작용에 의해 광을 전송할지 여부를 제어하는 한, 액정 재료, 구동 방법, 및 전극 구조에 특별한 제한은 없다.

- [0073] 트랜지스터(812)에 포함된 게이트 전극은 픽셀부(807)에 제공되는 복수의 게이트선(808) 중 하나에 접속된다. 트랜지스터(812)의 소스 전극 및 드레인 전극 중 하나는 복수의 소스선(809) 중 하나에 접속된다. 트랜지스터(812)의 소스 전극 및 드레인 전극 중 다른 하나는 용량 소자(813)의 다른 전극 및 액정 소자(805)의 다른 전극(픽셀 전극)에 접속된다.

- [0074] 바람직하게, 오프 전류가 낮은 트랜지스터가 트랜지스터(812)로서 사용된다. 트랜지스터(812)가 오프된 경우, 오프 전류가 낮은 트랜지스터(812)에 접속된 액정 소자(805)에 축적된 전하 및 용량 소자(813)에 축적된 전하들은 트랜지스터(812)를 통해 거의 누설되지 않으며, 이로써 트랜지스터(812)가 턴오프되기 전에 기입된 데이터는 다음 신호가 기입될 때까지 안정적으로 유지될 수 있다. 따라서, 픽셀(810)은 오프 전류가 낮은 트랜지스터(812)에 접속된 용량 소자(813)를 사용하지 않고 형성될 수 있다.

- [0075] 이러한 구조를 이용하여, 용량 소자(813)는 액정 소자(805)에 인가되는 전압을 유지할 수 있다. 또한, 용량 소자(813)의 전극은 추가적으로 제공되는 용량 소자에 접속될 수 있다.

- [0076] 구동 회로부(806)는 게이트선 구동 회로(811A) 및 소스선 구동 회로(811B)를 포함한다. 게이트선 구동 회로(811A) 및 소스선 구동 회로(811B)는 각각 복수의 픽셀을 포함하는 픽셀부(807)를 구동하기 위한 회로로서, (시프트 레지스터(shift register)라고도 지칭되는) 시프트 레지스터 회로를 포함한다.

- [0077] 게이트선 구동 회로(811A) 및 소스선 구동 회로(811B)는 픽셀부(807)가 형성된 기판 또는 표시부(807)가 형성된 기판과 상이한 기판 위에 형성될 수 있다는 점에 유의한다.

- [0078] 구동 회로부(806)에는 타이밍 제어기(802)에 의해 제어되는 높은 전원 전위(Vdd), 낮은 전원 전위(Vss), 시작 펄스(SP), 클럭 신호(CK), 및 화상 신호(Data)가 공급된다.

- [0079] 단자부(816)는 타이밍 제어기(802)로부터 구동 회로부(806)로 출력되는 소정의 신호들(예를 들어, 높은 전원 전위(Vdd), 낮은 전원 전위(Vss), 시작 펄스(SP), 클럭 신호(CK), 화상 신호(Data), 및 공통 전위(Vcom))을 공급

하기 위한 입력 단자이다.

[0080] 액정 표시 장치는 측광 회로(photometric circuit)를 포함할 수 있다. 측광 회로를 포함하는 액정 표시 장치는 액정 표시 장치가 위치하는 환경의 밝기를 검출할 수 있다. 결과적으로, 측광 회로가 접속된 타이밍 제어기(802)는 측광 회로로부터 입력된 신호에 따라 백라이트 및 사이드라이트(sidelight) 등의 광원의 구동 방법을 제어할 수 있다.

[0081] 백라이트부(804)는 백라이트 제어 회로(814) 및 백라이트(815)를 포함한다. 백라이트(815)는 액정 표시 장치(800)의 응용 형태에 따라 선택되고 결합될 수 있으며, 발광 다이오드(LED) 등이 사용될 수 있다. 백라이트(815)의 경우, 흰색 발광 소자(예를 들어, LED)가 제공될 수 있다. 전원 전위 및 백라이트를 제어하는 백라이트 신호가 타이밍 제어기(802)로부터 백라이트 제어 회로(814)로 공급된다.

[0082] 컬러 표시는 컬러 필터들의 조합으로 수행될 수 있다는 점에 유의한다. 또한, 다른 광학 필름(예를 들어, 편광막, 지연막(retardation film), 또는 반사방지막)이 조합되어 사용될 수 있다. 투과형 액정 표시 장치 또는 반투과형 액정 표시 장치에 사용되는 백라이트 등의 광원은 액정 표시 장치(800)의 응용 형태에 따라 선택되고 결합될 수 있으며, 냉음극 형광 램프, 발광 다이오드(LED) 등이 사용될 수 있다. 또한, 면 광원(surface light source)은 복수의 LED 광원 또는 복수의 전계 발광(EL) 광원을 사용하여 형성될 수 있다. 면 광원으로서, 3가지 종류 이상의 LED들이 사용될 수 있으며, 흰색 광을 방출하는 LED가 사용될 수 있다. 컬러 필터는 RGB 등의 발광 다이오드가 백라이트로서 배열되는 경우에 항상 제공되는 것은 아니며, 컬러 표시가 시분할(time division)에 의해 수행되는 연속 추가 혼색법(successive additive color mixing method)(필드 순차법)이 채택 된다는 점에 유의한다.

[0083] 다음으로, 픽셀에 공급되는 신호들의 상태는 도 7에 도시된 픽셀들의 회로도 및 도 8에 도시된 타이밍도를 사용하여 설명될 것이다.

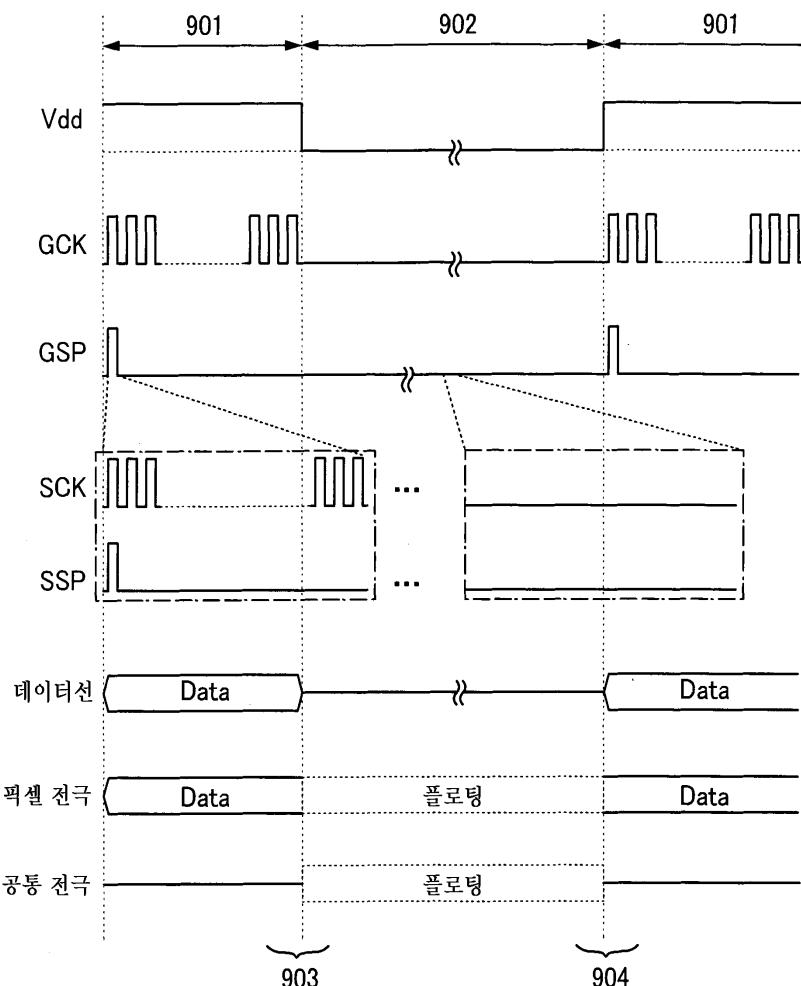

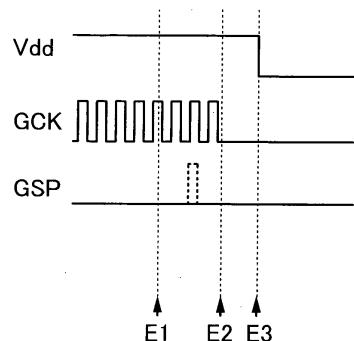

[0084] 도 8은 타이밍 제어기(802)로부터 게이트선 구동 회로(811A)에 공급되는 클럭 신호(GCK) 및 시작 펄스(GSP) 및 타이밍 제어기(802)로부터 소스선 구동 회로(811B)에 공급되는 클럭 신호(SCK) 및 시작 펄스(SSP)를 도시한다. 도 8은 클럭 신호의 출력의 타이밍을 설명하기 위해 클럭 신호의 파형으로서 간단한 구형파를 도시한다는 점에 유의한다.

[0085] 도 8은 소스선(809)(데이터선)의 전위, 픽셀 전극의 전위, 및 공통 전극의 전위를 도시한다.

[0086] 도 8에서, 기간(901)은 동화상을 표시하는 화상 신호가 기입되는 기간에 대응한다. 기간(901)에서, 타이밍 제어기(802)는 화상 신호 및 공통 전위가 픽셀부(807) 내의 픽셀 및 공통 전극에 공급되도록 동작한다.

[0087] 기간(902)은 정지 화상이 표시되는 기간에 대응한다. 기간(902)에서, 픽셀부(807) 내의 픽셀로 화상 신호를 공급하고 공통 전극으로 공통 전위를 공급하는 것이 중단된다. 도 8의 기간(902)에서, 구동 회로부의 동작이 중단되도록 각각의 신호가 공급되는데, 기간(902)의 길이 및 재생률에 따라 정지 화상의 품질 열화를 방지하기 위해 화상 신호들을 주기적으로 기입하는 것이 바람직할 수 있다는 점에 유의한다. 제1 실시형태에서 설명되는 재생률을 사용하면, 그레이 테일 변화로 인한 화질 열화가 줄어들 수 있다.

[0088] 우선, 기간(901)에서의 타이밍도가 설명될 것이다. 기간(901)에서, 클럭 신호가 클럭 신호(GCK)로서 항상 공급되며, 수직 동기화 주파수에 대응하는 펄스가 시작 펄스(GSP)로서 공급된다. 또한 기간(901)에서, 클럭 신호가 클럭 신호(SCK)로서 항상 공급되며, 하나의 게이트 선택 기간에 대응하는 펄스가 시작 펄스(SSP)로서 공급된다.

[0089] 또한, 화상 신호(Data)는 소스선(809)을 통해 각각의 행 내의 픽셀들에 공급되며, 소스선(809)의 전위는 게이트 선(808)의 전위에 따라 픽셀 전극에 공급된다.

[0090] 한편, 기간(902)은 정지 화상이 표시되는 기간이다. 우선, 기간(902)에서의 타이밍도가 설명될 것이다. 기간(902)에서, 클럭 신호(GCK), 시작 펄스(GSP), 클럭 신호(SCK), 및 시작 펄스(SSP)의 공급이 모두 중단된다. 또한, 기간(902)에서 소스선(809)에 화상 신호(Data)가 공급되는 것이 중단된다. 클럭 신호(GCK)와 시작 펄스(GSP) 모두의 공급이 중단된 기간(902)에서, 트랜지스터(812)가 턴오프되고, 픽셀 전극의 전위는 플로팅 상태로 들어 간다.

[0091] 기간(902)에서, 액정 소자(805)의 반대 전극들, 즉 픽셀 전극 및 공통 전극의 전위들을 플로팅 상태로 가져갈 수 있으며, 정지 화상은 다른 전위의 공급 없이 표시될 수 있다.

[0092] 또한, 게이트선 구동 회로(811A) 및 소스선 구동 회로(811B)에 클럭 신호 및 시작 펄스를 공급하는 것을 중단함

으로써 전력 소비를 줄일 수 있다.

[0093] 특히, 오프 전류가 낮은 트랜지스터를 트랜지스터(812)로 사용하는 것은 액정 소자(805)의 반대 전극들에 인가된 전압의 시간에 따른 감소를 억제할 수 있다.

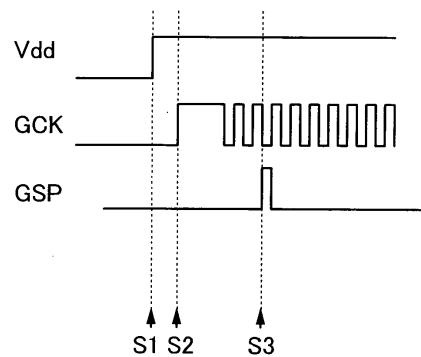

[0094] 그 다음, 표시 화상이 동화상으로부터 정지 화상으로 스위칭되는 기간(도 8의 기간(903)) 및 표시 화상이 정지 화상으로부터 동화상으로 스위칭되는 기간(도 8의 기간(904))에서의 표시 제어 회로의 동작이 도 9a 및 도 9b를 참조하여 설명될 것이다. 도 9a 및 도 9b는 표시 제어 회로로부터 출력되는 시작 펄스(여기서, GSP)의 전위, 클럭 신호(여기서, GCK)의 전위, 및 높은 전원 전위(Vdd)의 전위를 도시한다.

[0095] 도 9a는 표시 화상이 동화상으로부터 정지 화상으로 스위칭되는 기간(903)에서의 표시 제어 회로의 동작을 도시한다. 표시 제어 회로는 시작 펄스(GSP)를 공급하는 것을 중단한다(도 9a에서 E1, 제1 단계). 다음으로, 시작 펄스(GSP)의 공급을 중단한 다음, 표시 제어 회로는 펄스 출력이 시프트 레지스터의 최종 스테이지에 도달한 후 복수의 클럭 신호(GCK)의 공급을 중단한다(도 9a에서 E2, 제2 단계). 그 다음, 전원 전압의 전위는 높은 전원 전위(Vdd)로부터 낮은 전원 전위(Vss)로 변경된다(도 9a에서 E3, 제3 단계).

[0096] 앞서 설명한 단계들을 통해, 구동 회로부(806)의 오작동을 발생시키지 않고 구동 회로부(806)로의 신호 공급이 중단될 수 있다. 표시 화상이 동화상으로부터 정지 화상으로 스위칭될 때 일어나는 오작동은 잡음을 발생시키는데, 이는 정지 화상의 데이터의 일부로서 유지된다. 따라서, 오작동이 거의 없는 표시 제어 회로를 포함하는 액정 표시 장치에서, 그레이 템포 변환으로 인해 품질이 열화되지 않을 정지 화상이 표시될 수 있다.

[0097] 신호의 "중단"은 배선에 대한 소정의 전위 공급이 중단되어, 이 배선이 소정의 고정 전위가 공급되는 배선, 예를 들어 낮은 전원 전위(Vss)가 공급되는 배선에 접속되는 것을 의미한다는 점에 유의한다.

[0098] 다음으로, 도 9b는 표시 화상이 정지 화상으로부터 동화상으로 스위칭되는 기간(904)에서의 표시 제어 회로의 동작을 도시한다. 표시 제어 회로는 낮은 전원 전위(Vss)로부터 높은 전원 전위(Vdd)로 전원 전압의 전위를 변경한다(도 9b에서 S1, 제1 단계). 그 다음, 높은 레벨의 전위가 클럭 신호(GCK)로서 공급된 후 복수의 클럭 신호(GCK)가 공급된다(도 9b에서 S2, 제2 단계). 다음으로, 시작 펄스(GSP)가 공급된다(도 9b에서 S3, 제3 단계).

[0099] 앞서 설명한 단계들을 통해, 구동 회로부(806)로 구동 신호를 공급하는 것은 구동 회로부(806)의 오작동을 발생시키지 않고 재개될 수 있다. 배선의 전위는 동화상을 표시할 때의 전위로 순차적으로 돌아가며, 이로써 구동 회로부가 오작동 없이 구동될 수 있다.

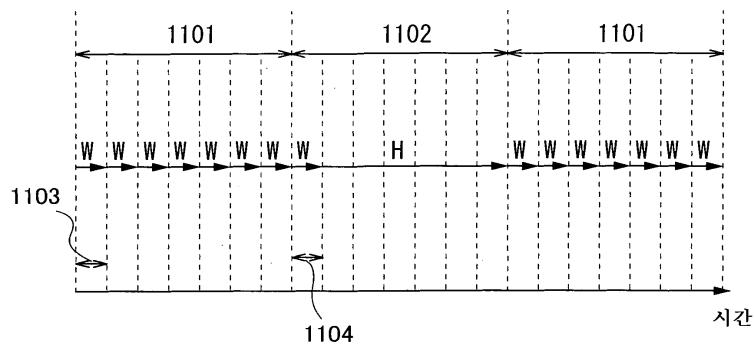

[0100] 도 10은 동화상을 표시하기 위한 기간(1101) 또는 정지 화상을 표시하기 위한 기간(1102)에서 프레임 기간당 화상 신호의 기입 빈도를 개략적으로 도시한다. 도 10에서 "W"는 화상 신호가 기입되는 기간을 지시하며, "H"는 화상 신호가 유지되는 기간을 지시한다. 또한, 기간(1103)은 도 10의 한 프레임 기간을 지시하는데, 기간(1103)은 상이한 기간일 수 있다.

[0101] 앞서 설명한 바와 같이, 이 실시형태의 액정 표시 장치에서, 기간(1102)에 표시된 정지 화상을 위한 화상 신호가 기간(1104)에 기입되며, 기간(1104)에 기입된 화상 신호는 기간(1104) 이외의 기간(1102)의 다른 기간에서 유지된다.

[0102] 이 실시형태에 설명된 액정 표시 장치에서, 화상 신호의 기입 빈도는 정지 화상이 표시되는 기간에서 줄어들 수 있다. 그 결과, 정지 화상을 표시하는 경우의 전력 소비를 줄일 수 있다.

[0103] 동일한 화상을 여러 번 재기입함으로써 정지 화상이 표시되는 경우, 화상들의 스위칭이 인식되면 눈의 피로감이 발생할 수 있다. 이 실시형태에 설명된 액정 표시 장치에서, 화상 신호의 기입 빈도는 줄어들며, 이는 발생할 눈의 피로감의 레벨을 줄이는 데 효과적이다.

[0104] 구체적으로, 오프 전류가 낮은 트랜지스터가 이 실시형태에서의 액정 표시 장치 내의 공통 전극을 위한 스위칭 소자로서 픽셀에 사용되는 경우, 전압이 축적 용량 소자에서 유지될 수 있는 기간(시간)이 더 길어질 수 있다. 결과적으로, 화상 신호의 기입 빈도가 줄어들 수 있으며, 이는 정지 화상을 표시할 때의 전력 소비를 줄이고, 발생할 눈의 피로감의 레벨을 줄이는 데 상당히 효과적이다.

[0105] (제3 실시형태)

[0106] 이 실시형태에서, 이 명세서에 개시된 액정 표시 장치에 인가될 수 있는 트랜지스터의 일례가 설명될 것이다.

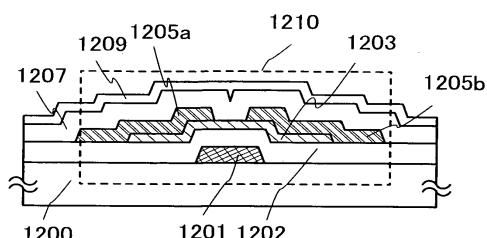

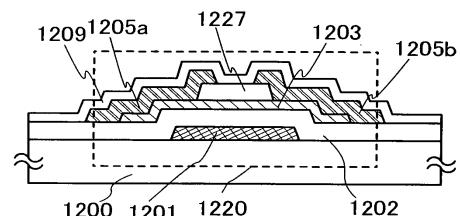

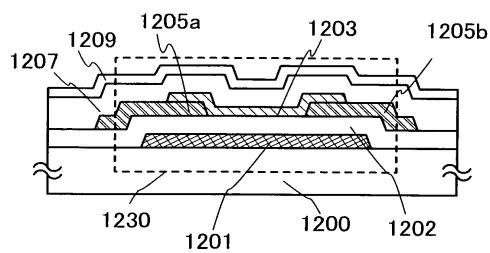

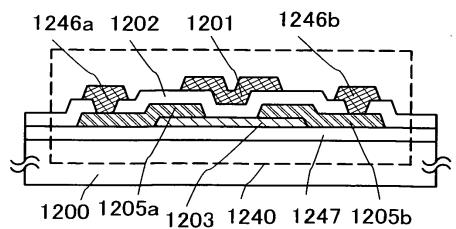

- [0107] 도 11a 내지 도 11d는 각각 트랜지스터의 단면 구조의 일례를 도시한다.

- [0108] 도 11a에 도시된 트랜지스터(1210)는 일종의 하부 게이트 트랜지스터이며, 역스테거형(inverted staggered) 트랜지스터라고도 지칭된다.

- [0109] 트랜지스터(1210)는 절연면을 갖는 기판(1200) 위에 게이트 전극층(1201), 게이트 절연층(1202), 반도체층(1203), 소스 전극층(1205a) 및 드레인 전극층(1205b)을 포함한다. 트랜지스터(1210)를 덮고 반도체층(1203) 위에 적층되기 위해 절연층(1207)이 제공된다. 보호 절연층(1209)이 절연층(1207) 위에 제공된다.

- [0110] 도 11b에 도시된 트랜지스터(1220)는 채널 보호 타입(channel-protective type)(채널 중단 타입(channel-stop type))이라고 지칭되는 일종의 하부 게이트 구조이며, 역스테거형 트랜지스터라고도 지칭된다.

- [0111] 트랜지스터(1220)는 절연면을 갖는 기판(1200) 위에 게이트 전극층(1201), 게이트 절연층(1202), 반도체층(1203), 반도체층(1203) 내의 채널 형성 영역 위에 제공되어 채널 보호층으로 기능하는 절연층(1227), 소스 전극층(1205a) 및 드레인 전극층(1205b)을 포함한다. 트랜지스터(1220)를 덮기 위해 보호 절연층(1209)이 제공된다.

- [0112] 도 11c에 도시된 트랜지스터(1230)는 하부 게이트 트랜지스터로서, 절연면을 갖는 기판(1200) 위에 게이트 전극층(1201), 게이트 절연층(1202), 소스 전극층(1205a), 드레인 전극층(1205b) 및 반도체층(1203)을 포함한다. 트랜지스터(1230)를 덮고 반도체층(1203)과 접촉하기 위해 절연층(1207)이 제공된다. 보호 절연층(1209)이 절연층(1207) 위에 제공된다.

- [0113] 트랜지스터(1230)에서는, 게이트 절연층(1202)은 기판(1200) 및 게이트 전극층(1201)과 접촉하여 제공된다. 소스 전극층(1205a) 및 드레인 전극층(1205b)은 게이트 절연층(1202)과 접촉하여 제공된다. 반도체층(1203)은 게이트 절연층(1202), 소스 전극층(1205a), 및 드레인 전극층(1205b) 위에 제공된다.

- [0114] 도 11d에 도시된 트랜지스터(1240)는 일종의 상부 게이트 트랜지스터이다. 트랜지스터(1240)는 절연면을 갖는 기판(1200) 위에, 절연층(1247), 반도체층(1203), 소스 전극층(1205a) 및 드레인 전극층(1205b), 게이트 절연층(1202) 및 게이트 전극층(1201)을 포함한다. 배선층(1246a) 및 배선층(1246b)이 각각 소스 전극층(1205a) 및 드레인 전극층(1205b)에 접촉하도록 제공되어 소스 전극층(1205a) 및 드레인 전극층(1205b)에 전기적으로 접속된다.

- [0115] 이 실시형태에서, 반도체층(1203)은 산화물 반도체를 포함한다.

- [0116] 산화물 반도체의 예시에는 4원계 금속 산화물인  $In-Sn-Ga-Zn-O$ 계 금속 산화물; 3원계 금속 산화물인  $In-Ga-Zn-O$ 계 금속 산화물,  $In-Sn-Zn-O$ 계 금속 산화물,  $In-Al-Zn-O$ 계 금속 산화물,  $Sn-Ga-Zn-O$ 계 금속 산화물,  $Al-Ga-Zn-O$ 계 금속 산화물, 및  $Sn-Al-Zn-O$ 계 금속 산화물; 2원계 금속 산화물인  $In-Zn-O$ 계 금속 산화물,  $Sn-Zn-O$ 계 금속 산화물,  $Al-Zn-O$ 계 금속 산화물,  $Zn-Mg-O$ 계 금속 산화물,  $Sn-Mg-O$ 계 금속 산화물, 및  $In-Mg-O$ 계 금속 산화물; 및  $In-O$ 계 금속 산화물,  $Sn-O$ 계 금속 산화물, 및  $Zn-O$ 계 금속 산화물이 있다. 또한, 앞서 설명한 금속 산화물 반도체는  $SiO_2$ 를 포함할 수 있다. 여기서, 예를 들어  $In-Ga-Zn-O$ 계 금속 산화물은 적어도  $In$ ,  $Ga$ , 및  $Zn$ 을 포함하는 산화물로서, 이들 원소의 조성비에 특별한 제한은 없다. 또한,  $In-Ga-Zn-O$ 계 금속 산화물은  $In$ ,  $Ga$ , 및  $Zn$  이외의 원소를 포함할 수 있다.

- [0117] 산화물 반도체의 경우, 화학식  $InMO_3(ZnO)_m$ ( $m > 0$ )에 의해 표현되는 박막이 사용될 수 있다. 여기서, M은  $Ga$ ,  $Al$ ,  $Mn$ , 및  $Co$ 로부터 선택된 하나 이상의 금속 원소를 나타낸다. 예를 들어, M은  $Ga$ ,  $Ga$  및  $Al$ ,  $Ga$  및  $Mn$ , 또는  $Ga$  및  $Co$ 일 수 있다.

- [0118] 이 실시형태의 구조에서, 산화물 반도체는 고순도를 위해 산화물 반도체로부터 n형 불순물인 수소를 제거함으로써 획득되어 주요 성분 이외의 불순물을 거의 함유하지 않는 진성(i형) 또는 실질적인 진성 반도체인 점에 유의한다. 다시 말해, 이 실시형태에서의 산화물 반도체는 불순물 원소를 첨가하지 않고 수소와 물 등의 불순물을 가능한 많이 제거함으로써 획득되는 고순도의 i형(진성) 반도체이거나 진성 반도체에 가깝다. 또한, 산화물 반도체의 밴드 갭은 2eV 이상이며, 바람직하게 2.5eV 이상이며, 더 바람직하게 3.0eV 이상이다. 이에 따라, 산화물 반도체층에서, 열적 여기(thermal excitation)로 인한 캐리어의 생성을 억제할 수 있다. 따라서, 채널 형성 영역이 산화물 반도체를 사용하여 형성된 트랜지스터의 동작 온도 증가로 인한 오프 전류의 증가를 억제할 수 있다.

- [0119] 고순도 산화물 반도체 내의 캐리어의 개수는 매우 적으며(0에 가까움), 캐리어 농도는  $1 \times 10^{14} / cm^3$  미만이며, 바

람직하게  $1 \times 10^{12} / \text{cm}^3$  미만이며, 더 바람직하게  $1 \times 10^{11} / \text{cm}^3$  미만이다.

- [0120] 산화물 반도체 내의 캐리어의 개수가 상당히 적기 때문에 트랜지스터의 오프 전류가 감소될 수 있다. 구체적으로, 앞서 설명한 산화물 반도체가 반도체층에 사용된 트랜지스터의  $1 \mu\text{m}$ 의 채널 폭당 오프 전류는  $10\text{aA}/\mu\text{m}$  ( $1 \times 10^{-17} \text{ A}/\mu\text{m}$ ) 이하로 감소되며,  $1\text{aA}/\mu\text{m}$  ( $1 \times 10^{-18} \text{ A}/\mu\text{m}$ ) 이하로 더 감소되며,  $10\text{zA}/\mu\text{m}$  ( $1 \times 10^{-20} \text{ A}/\mu\text{m}$ )로 더 감소될 수 있다. 다시 말해, 회로 설계에서, 트랜지스터가 오프인 경우 산화물 반도체는 절연체로 간주될 수 있다. 또한, 트랜지스터가 온인 경우, 산화물 반도체층의 전류 공급 능력은 비정질 실리콘으로 형성된 반도체층보다 높을 것으로 예상된다.

- [0121] 산화물 반도체가 반도체층(1203)에 사용되는 트랜지스터(1210, 1220, 1230, 및 1240) 각각에서, 오프 상태에서의 전류(오프 전류)가 낮을 수 있다. 이에 따라, 화상 데이터 등의 전기 신호에 관한 유지 시간이 연장될 수 있으며, 배선 사이의 간격이 연장될 수 있다. 그 결과, 재생률을 줄일 수 있으며, 이로써 전력 소비는 더 줄일 수 있다.

- [0122] 또한, 산화물 반도체가 반도체층(1203)에 사용된 트랜지스터(1210, 1220, 1230, 및 1240)는 비정질 반도체를 사용하여 형성된 트랜지스터와 같이 상대적으로 높은 전계 효과 이동도(field-effect mobility)를 가질 수 있으며, 이로써 트랜지스터들은 고속으로 동작할 수 있다. 그 결과, 표시 장치의 고기능성 및 고속 응답이 실현될 수 있다.

- [0123] 절연면을 갖는 기판(1200)으로서 사용될 수 있는 기판에 특별한 제한이 없는 경우라도, 기판은 사후 수행될 열 처리를 견디기 위해 충분히 높은 내열성을 가질 필요가 있다. 바륨 보로실리케이트 유리, 알루미노보로실리케이트 유리 등으로 구성된 유기 기판이 사용될 수 있다.

- [0124] 사후에 수행될 열 처리의 온도가 높은 경우, 바람직하게 변형점(strain point)이  $730^\circ\text{C}$  이상인 유리 기판이 사용된다. 유리 기판의 경우, 예를 들어 알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 또는 바륨 보로실리케이트 유리가 사용된다. 실제 고저항 유리인 봉소 산화물( $\text{B}_2\text{O}_3$ )보다 많은 양의 바륨 산화물( $\text{BaO}$ )을 함유하는 유리 기판이 사용될 수 있다는 점에 유의한다.

- [0125] 세라믹 기판, 석영 기판, 또는 사파이어 기판 등의 절연체로 형성된 기판이 유리 기판 대신에 사용될 수 있다는 점에 유의한다. 또한, 결정화 유리(crystallized glass) 등이 사용될 수 있다. 플라스틱 기판 등이 적절히 사용될 수 있다.

- [0126] 하부 게이트 트랜지스터(1210, 1220, 및 1230)에서, 하지막으로서 역할을 하는 절연막이 기판과 게이트 전극층 사이에 제공될 수 있다. 하지막은 기판으로부터 불순물 원소의 확산을 방지하는 기능을 가지며, 질화 실리콘막, 산화 실리콘막, 질화 산화 실리콘막 및/또는 산화 질화 실리콘막을 포함하는 단층 구조 또는 적층 구조로 형성될 수 있다.

- [0127] 게이트 전극층(1201)은 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 스칸듐 또는 이들 중 임의의 재료를 함유하는 합금 재료 등의 금속 재료를 주요 성분으로 사용하는 단층 구조 또는 적층 구조로 형성될 수 있다.

- [0128] 게이트 전극층(1201)의 2층 구조로서, 바람직하게 다음의 적층 구조 중 어느 하나가 채택될 수 있는데, 예를 들어 몰리브덴층이 알루미늄층 위에 적층된 2층 구조, 몰리브덴층이 구리층 위에 적층된 2층 구조, 질화 티타늄층 또는 질화 탄탈층이 구리층 위에 적층된 2층 구조, 또는 질화 티타늄층 및 몰리브덴층이 적층된 2층 구조가 있다. 게이트 전극층(1201)의 3층 구조로서, 텅스텐층 또는 질화 텅스텐층, 알루미늄 및 실리콘의 합금층 또는 알루미늄 및 티타늄의 합금층, 및 질화 티타늄층 또는 티타늄층의 적층을 채택하는 것이 바람직하다. 게이트 전극층이 투광성 도전막(light-transmitting conductive film)을 사용하여 형성될 수 있다는 점에 유의한다. 투광성 도전막을 위한 재료의 일례는 투광성 도전성 산화물이다.

- [0129] 게이트 절연층(1202)은, 플라즈마 CVD 방법, 스퍼터링법 등에 의해 산화 실리콘층, 질화 실리콘층, 산화 질화 실리콘층, 질화 산화 실리콘층, 산화 알루미늄층, 질화 알루미늄층, 산화 질화 알루미늄층, 질화 산화 알루미늄층, 및 산화 하프늄층 중 어느 하나를 사용하는 단층 구조 또는 적층 구조로 형성될 수 있다.

- [0130] 게이트 절연층(1202)은 질화 실리콘층 및 산화 실리콘층이 게이트 전극층에서부터 적층되는 구조를 가질 수 있다. 예를 들어, 50nm 내지 200nm의 두께를 갖는 질화 실리콘층( $\text{SiN}_y$  ( $y > 0$ ))을 스퍼터링법에 의해 제1 게이트 절연층으로서 형성한 후 5nm 내지 300nm의 두께를 갖는 실리콘 산화층( $\text{SiO}_x$  ( $x > 0$ ))을 제1 게이트 절연층 위에

제2 게이트 절연층으로서 적층하는 방법으로 100nm 두께의 게이트 절연층이 형성된다. 게이트 절연층(1202)의 두께는 트랜지스터에 필요한 특성에 따라 적절히 설정될 수 있으며, 대략 350nm 내지 1200nm일 수 있다.

[0131] 소스 전극층(1205a) 및 드레인 전극층(1205b)에 사용되는 도전막의 경우, 예를 들어 Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 원소, 이들 중 임의의 원소를 함유하는 합금, 또는 이들 중 임의의 원소들의 조합을 함유하는 합금막이 사용될 수 있다. Cr, Ta, Ti, Mo, W 등의 용융점이 높은 금속층이 Al, Cu 등의 금속층의 상면 및 하면 중 적어도 하나에 적층되는 구조가 채택될 수 있다. 알루미늄막에서 힐록(hilllock) 및 위스커(wisker) 생성을 방지하는 Si, Ti, Ta, W, Mo, Cr, Nd, Sc, 또는 Y 등의 원소가 첨가된 알루미늄 재료를 사용함으로써, 내열성을 증가시킬 수 있다.

[0132] 소스 전극층(1205a) 및 드레인 전극층(1205b)에 접속된 배선층(1246a 및 1246b)으로서 기능하는 도전막이 소스 전극층(1205a) 및 드레인 전극층(1205b)과 유사한 재료를 사용하여 형성될 수 있다.

[0133] 소스 전극층(1205a) 및 드레인 전극층(1205b)은 단층 구조 또는 2개 이상의 층이 있는 적층 구조를 가질 수 있다. 예를 들어, 소스 전극층(1205a) 및 드레인 전극층(1205b)이 실리콘을 함유하는 알루미늄막의 단층 구조, 티타늄막이 알루미늄막 위에 적층된 2층 구조, 또는 티타늄막, 알루미늄막, 및 티타늄막이 순서대로 적층되는 3층 구조를 가질 수 있다.

[0134] (소스 전극층 및 드레인 전극층과 동일한 층을 사용하여 형성된 배선층을 포함하는) 소스 전극층(1205a) 및 드레인 전극층(1205b)이 될 도전막이 도전성 금속 산화물을 사용하여 형성될 수 있다. 도전성 금속 산화물로서, 산화 인듐( $In_2O_3$ ), 산화 주석( $SnO_2$ ), 산화 아연( $ZnO$ ), (ITO라고 지칭되는) 산화 인듐과 산화 주석의 합금( $In_2O_3-SnO_2$ ), 산화 인듐 및 산화 아연의 합금( $In_2O_3-ZnO$ ), 또는 실리콘 또는 산화 실리콘을 함유하는 금속 산화물 중 어느 하나가 사용될 수 있다.

[0135] 절연층(1207, 1227, 및 1247) 및 보호 절연층(1209)으로서, 바람직하게 산화 절연막 또는 질화 절연막 등의 무기 절연막(inorganic insulating film)이 사용된다.

[0136] 절연층(1207, 1227, 및 1247)으로서, 산화 실리콘막, 산화 질화 실리콘막, 산화 알루미늄막, 또는 산화 질화 알루미늄막 등의 무기 절연막이 통상적으로 사용될 수 있다.

[0137] 보호 절연층(1209)으로서, 질화 실리콘막, 질화 알루미늄막, 질화 산화 실리콘막, 또는 질화 산화 알루미늄막 등의 무기 절연막이 사용될 수 있다.

[0138] 트랜지스터로 인한 표면 거칠기(surface roughness)를 감소시키기 위해 평탄화 절연막(planarization insulating film)이 보호 절연막(1209) 위에 형성될 수 있다. 평탄화 절연막은 폴리아미드, 아크릴, 벤조사이클로부텐, 폴리아미드, 에폭시 등의 내열성 유기 재료를 사용하여 형성될 수 있다. 이러한 유기 재료 이외에, 저유전상수 재료(low-dielectric constant material)(low-k 재료), 실록산계 수지, PSG(phosphosilicate glass), BPSG(borophosphosilicate glass) 등을 사용할 수 있다. 평탄화 절연막은 이를 재료로부터 형성되는 복수의 절연막을 적층함으로써 형성될 수 있다는 점에 유의한다.

[0139] 이 실시형태에서 산화물 반도체가 반도체층에 사용되는 트랜지스터를 사용함으로써, 소비 전력이 낮은 고기능성의 액정 표시 장치를 제공할 수 있다.

[0140] 이 실시형태는 다른 실시형태들에서 설명된 컴포넌트들 중 어느 하나와의 적절한 조합으로 구현될 수 있다.

[0141] (제4 실시형태)

[0142] 트랜지스터가 핀셀부 및 구동 회로를 위해 제조되어 사용되는 경우, 표시 기능을 갖는 액정 표시 장치가 제조될 수 있다. 또한, 핀셀부가 형성된 기판 위에 트랜지스터를 포함하는 전체 구동 회로의 일부가 형성되는데, 이로써 시스템-온-패널(system-on-panel)이 획득될 수 있다.

[0143] 액정 표시 장치는 카테고리 내에 다음 중 임의의 모듈을 포함하는데, 예를 들어 가요성 인쇄 회로(flexible printed circuit (FPC)), 테이프 자동화 접착(tape automated bonding (TAB)) 테이프, 또는 테이프 캐리어 패키지(tape carrier package (TCP)) 등의 커넥터가 제공되는 모듈, TAB 테이프 또는 TCP의 끝단에 인쇄 배선 기판(printed wiring board)이 제공되는 모듈; 및 접착 회로(IC)가 COG(chip-on-glass) 방법에 의해 표시 소자 위에 직접 실장되는 모듈이 있다는 점에 유의한다.

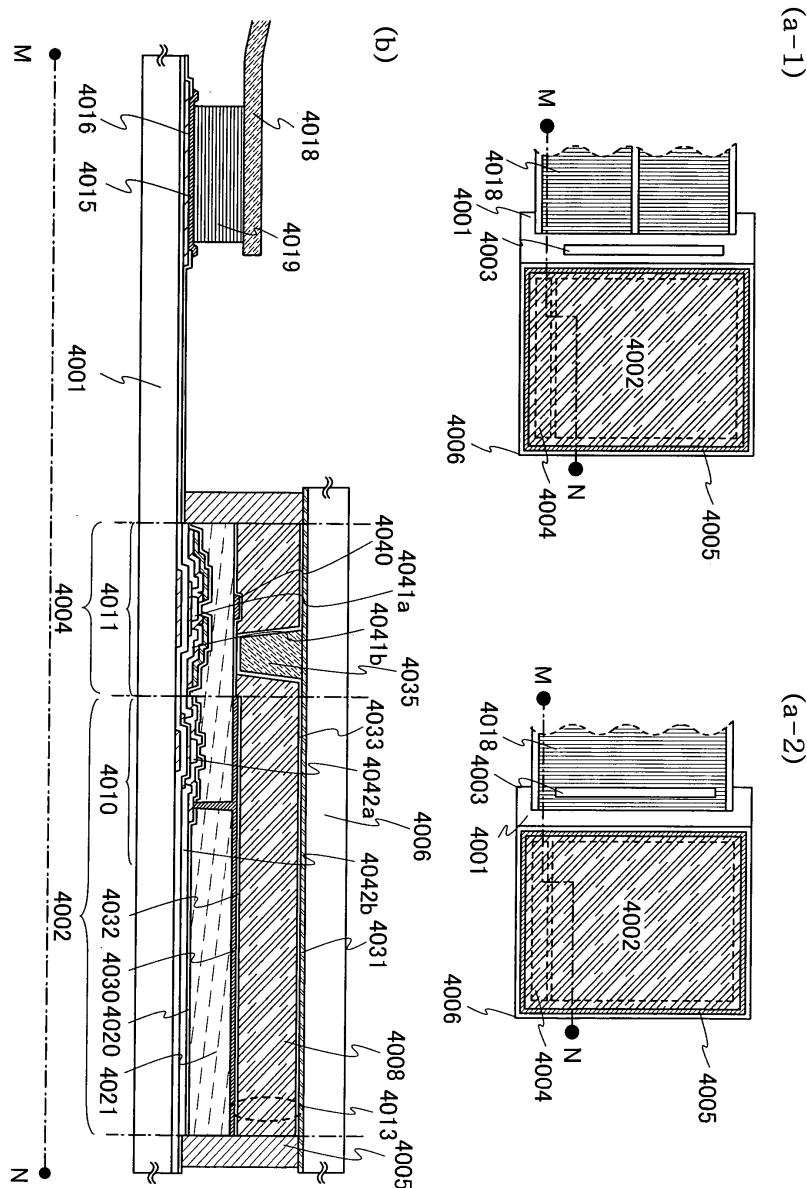

[0144] 액정 표시 정차의 외관 및 단면부가 도 12의 (a-1), (a-2), 및 (b)를 참조하여 설명될 것이다. 도 12의 (a-1)

및 (a-2)는 트랜지스터(4010 및 4011)와 액정 소자(4013)가 제1 기판(4001) 및 제2 기판(4006) 사이에서 밀봉재(sealant)(4005)에 의해 밀봉된 패널들의 평면도이다. 도 12b는 도 12의 (a-1) 및 (a-2)의 M-N을 따른 단면도이다.

[0145] 밀봉재(4005)는 제1 기판(4001) 위에 제공되는 픽셀부(4002) 및 스캔선 구동 회로(4004)를 둘러싸도록 제공된다. 제2 기판(4006)은 픽셀부(4002) 및 스캔선 구동 회로(4004) 위에 제공된다. 따라서, 픽셀부(4002) 및 스캔선 구동 회로(4004)는 제1 기판(4001), 밀봉재(4005), 및 제2 기판(4006)에 의해 액정층(4008)과 함께 밀봉된다. 별도로 마련된 기판 위에 단결정 반도체막 또는 다결정 반도체막을 사용하여 형성된 신호선 구동 회로(4003)는 제1 기판(4001) 위에 밀봉재(4005)에 의해 둘러싸인 영역과는 상이한 영역에 실장된다.

[0146] 별도로 형성된 구동 회로의 접속 방법, COG 방법, 배선 접착 방법, TAB 방법 등에 특별한 제한이 없다는 점에 유의한다. 도 12의 (a-1)은 신호선 구동 회로(4003)가 COG 방법에 의해 실장되는 일례를 도시한다. 도 12의 (a-2)는 신호선 구동 회로(4003)가 TAB 방법에 의해 실장되는 일례를 도시한다.

[0147] 제1 기판(4001) 위에 제공되는 픽셀부(4002) 및 스캔선 구동 회로(4004)는 복수의 트랜지스터를 포함한다. 도 12의 (b)는 픽셀부(4002)에 포함된 트랜지스터(4010) 및 스캔선 구동 회로(4004)에 포함된 트랜지스터(4011)를 도시한다. 절연층(4041a, 4041b, 4042a, 4042b, 4020, 및 4021)은 트랜지스터(4010 및 4011) 위에 제공된다.

[0148] 산화물 반도체가 반도체층에 사용되는 트랜지스터는 트랜지스터(4010 및 4011)로서 사용될 수 있다. 이 실시형태에서, 트랜지스터(4010 및 4011)는 n 채널 트랜지스터이다.

[0149] 도전층(4040)이 절연층(4021)의 일부 위에 제공되는데, 구동 회로를 위한 트랜지스터(4011)에 산화물 반도체를 사용하는 채널 형성 영역과 중첩된다. 도전층(4040)은 산화물 반도체를 사용한 채널 형성 영역과 중첩되는 위치에 제공되는데, 이로써 트랜지스터(4011)의 문턱 전압의 변화량이 바이어스-온도(BT) 시험 전후로 줄어들 수 있다. 도전층(4040)의 전위는 트랜지스터(4011)의 게이트 전극층과 동일하거나 상이할 수 있다. 도전층(4040)은 제2 게이트 전극층으로서 기능할 수도 있다. 도전층(4040)의 전위는 GND 또는 0V이거나, 도전층(4040)은 플로팅 상태에 있을 수도 있다.

[0150] 액정 소자(4013)에 포함된 픽셀 전극층(4030)은 트랜지스터(4010)에 전기적으로 접속된다. 액정 소자(4013)의 대향 전극층(4031)이 제2 기판(4006)에 제공된다. 픽셀 전극층(4030), 대향 전극층(4031), 및 액정층(4008)이 서로 중첩되는 부분이 액정 소자(4013)에 대응한다. 픽셀 전극층(4030) 및 대향 전극층(4031)에는 배향막(alignment film)으로서 기능하는 절연층(4032) 및 절연층(4033)이 각각 제공되며, 액정층(4008)은, 픽셀 전극층(4030) 및 대향 전극층(4031) 사이에 절연층(4032 및 4033)을 개재하여 배치된다는 점에 유의한다.

[0151] 투광성 기판이 제1 기판(4001) 및 제2 기판(4006)으로서 사용될 수 있는데, 유리, 세라믹, 또는 플라스틱이 사용될 수도 있다는 점에 유의한다. 플라스틱으로서, 유리섬유 강화 플라스틱(FRP) 판, 폴리비닐 플루오라이드(polyvinyl fluoride (PVF)) 필름, 폴리에스테르 필름, 또는 아크릴 수지 필름이 사용될 수 있다.

[0152] 스페이서(4035)는 절연막의 선택적 예칭에 의해 획득되는 기둥형 스페이서으로서, 픽셀 전극층(4030) 및 대향 전극층(4031) 사이의 거리(셀 갭(cell gap))를 제어하도록 제공된다. 구형 스페이서가 사용될 수도 있다는 점에 유의한다. 대향 전극층(4031)은 트랜지스터(4010)가 형성된 기판 위에 형성된 공통 전위선에 전기적으로 접속된다. 공통 접속부를 사용하면, 대향 전극층(4031) 및 공통 전위선은 한 쌍의 기판 사이에 배열된 도전성 입자들에 의해 서로 전기적으로 접속될 수 있다. 도전성 입자들은 밀봉재(4005) 내에 포함될 수 있다는 점에 유의한다.

[0153] 또한, 배향막이 필요 없는 블루상(blue phase)을 보이는 액정이 사용될 수도 있다. 블루상은 액정상 중 하나로서, 콜레스테릭 액정(cholesteric liquid crystal)의 온도가 증가하는 동안 콜레스테릭상이 등방상(isotropic phase)으로 전이되기 직전에 생성된다. 블루상은 단지 좁은 범위의 온도 내에서만 생성되기 때문에, 온도 범위를 개선하기 위해 5wt% 이상 키랄체(chiral agent)를 함유하는 액정 조성물이 액정층(4008)에 사용된다. 블루상을 보이는 액정 및 키랄체를 포함하는 액정 조성물은 1msec 이하의 짧은 반응시간을 갖고, 배향 공정(alignment process)이 불필요한 광학적 등방성을 가지며, 시야각 의존성(viewing angle dependence)이 작다.

[0154] 이 실시형태는 투과형 액정 표시뿐 아니라 반투과형 액정 표시 장치에 인가될 수도 있다는 점에 유의한다.

[0155] 이 실시형태는 편광판이 기판 외부(관측자 측면)에 제공되고 표시 소자에 사용되는 착색층(coloring layer) 및 전극층이 순서대로 기판 내부에 제공되는 액정 표시 장치의 예시를 도시하는데, 또한 편광판은 기판 내부에 제공될 수도 있다. 편광판 및 착색층의 적층 구조는 이 실시형태로 제한되지 않으며, 편광판 및 착색층의 재료

또는 제조 공정의 조건들에 따라 적절히 설정될 수도 있다. 또한, 블랙 매트릭스(black matrix)로서 기능하는 차광막(light-blocking film)이 표시부 이외의 부위에 제공될 수도 있다.

[0156] 산화물 반도체를 사용하는 반도체층들의 스택의 (측면을 포함하는) 외부 에지부를 덮는 절연층(4041b) 및 채널 보호층으로서 기능하는 절연층(4041a)이 트랜지스터(4011)에 형성된다. 유사한 방식으로, 산화물 반도체를 사용하는 반도체층들의 스택의 (측면을 포함하는) 외부 에지부를 덮는 절연층(4042b) 및 채널 보호층으로서 기능하는 절연층(4042a)이 트랜지스터(4010)에 형성된다.

[0157] 산화물 반도체를 사용하는 반도체층들의 (측면을 포함하는) 외부 에지부를 덮는 산화 절연층인 절연층(4041b 및 4042b)은 게이트 전극층과 게이트 전극층 위 또는 주변에 형성된 배선층(예를 들어, 소스 배선층 또는 용량 소자 배선층) 사이의 거리를 증가시킬 수 있으며, 이로써 기생 용량(parasitic capacitance)을 줄일 수 있다. 트랜지스터의 표면 거칠기를 감소시키기 위해, 트랜지스터들은 평탄화 절연막으로서 기능하는 절연층(4021)으로 덮인다. 여기에서, 절연층(4041a, 4041b, 4042a, 및 4042b)으로서, 예를 들어 산화 실리콘막이 스퍼터링법에 의해 형성된다.

[0158] 또한, 절연층(4020)은 절연층(4041a, 4041b, 4042a, 및 4042b) 위에 형성된다. 절연층(4020)으로서, 예를 들어 질화 실리콘막이 RF 스퍼터링법에 의해 형성된다.

[0159] 절연층(4021)은 평탄화 절연막으로서 형성된다. 절연층(4021)으로서, 폴리이미드, 아크릴, 벤조사이클로부텐, 폴리아미드, 에폭시 등의 내열성을 갖는 유기 재료가 사용될 수 있다. 이러한 유기 재료 이외에, 저유전상수 재료(low-k 재료), 실록산계 수지, PSG, BPSG 등을 사용할 수도 있다. 절연층(4021)은 이들 재료로부터 형성되는 복수의 절연층을 적층함으로써 형성될 수 있다는 점에 유의한다.

[0160] 이 실시형태에서, 픽셀부에 있는 복수의 트랜지스터들은 질화 절연막에 의해 함께 둘러싸일 수 있다. 도 12의 (a-1), (a-2), 및 (b)에 도시된 바와 같이, 액티브 매트릭스 기판 위에 있는 픽셀부의 적어도 주변을 둘러싸기 위해 질화 절연막을 절연층(4020) 및 게이트 절연층으로서 사용할 수 있으며, 절연층(4020)이 게이트 절연층과 접촉하는 영역을 제공할 수 있다. 이 제조 공정에서, 외부로부터 습기가 들어오는 것을 방지할 수 있다. 또한, 장치가 액정 표시 장치로서 완성된 후에도 오랜 기간 외부로부터 습기가 들어오는 것이 방지될 수 있으며, 장치의 장기간 신뢰성이 개선될 수 있다.

[0161] 실록산계 수지는 실록산계 재료를 출발 재료(starting material)로서 사용하여 형성되는 Si-O-Si 결합을 포함하는 수지에 대응한다는 점에 유의한다. 실록산계 수지는 치환기로서 유기기(organic group)(예를 들어, 알킬기 또는 아릴기) 또는 플루오로기를 포함할 수 있다. 유기기는 플루오로기를 포함할 수 있다.

[0162] 절연층(4021)의 형성 방법에는 특별한 제한이 없으며, 다음의 방법 및 도구 중 어느 하나가, 예를 들어 재료에 따라 선택될 수 있는데, 스퍼터링법, SOG 방법, 스핀 코팅 방법, 디핑법(dipping method), 스프레이 코팅법, 액적 토출 방법(droplet discharge method)(예를 들어, 잉크 제트법, 스크린 프린팅, 및 오프셋 프린팅), 닥터 나이프(doctor knife), 롤 코터(roll coater), 커튼 코터(curtain coater), 및 나이프 코터(knife coater)가 있다. 절연층(4021)의 소성(baking) 단계는 또한 반도체층의 어닐링(annealing)으로서 기능하며, 이로써 액정 표시 장치가 효율적으로 제조될 수 있다.

[0163] 픽셀 전극층(4030) 및 대향 전극층(4031)은 산화 텅스텐을 함유한 인듐 산화물, 산화 텅스텐을 함유한 인듐 아연 산화물, 산화 티타늄을 함유한 인듐 산화물, 산화 티타늄을 함유한 인듐 주석 산화물, (ITO라고 지칭되는) 인듐 주석 산화물, 인듐 아연 산화물, 또는 산화 실리콘이 첨가된 인듐 주석 산화물 등의 투광성 도전성 재료를 사용하여 형성될 수 있다.

[0164] 또한, 픽셀 전극층(4030) 및 대향 전극층(4031)은 (도전성 중합체라고도 지칭되는) 도전성 고분자를 포함하는 도전성 조성물을 사용하여 형성될 수 있다. 바람직하게, 도전성 조성물을 사용하여 형성된 픽셀 전극은 시트 저항이 단위 면적당 10000옴(ohm) 이하이며, 투과율이 550nm 파장에서 70% 이상이다. 또한, 도전성 조성물에 포함된 도전성 고분자의 저항률은 바람직하게 0.1Ω?cm 이하이다.

[0165] 도전성 고분자로서, 소위  $\pi$  전자 공액 도전성 고분자( $\pi$ -electron conjugated conductive high molecule)가 사용될 수 있다. 예시에는 폴리아닐린 및 그 유도체(derivative), 폴리페롤 및 그 유도체, 폴리티오펜 및 그 유도체, 아닐린, 피롤, 및 티오펜 중 2 이상의 공중합체 또는 그 유도체가 있다.

[0166] 다양한 신호 및 전위들이 FPC(4018)로부터 별도로 형성된 신호선 구동 회로(4003), 스캔선 구동 회로(4004), 또는 픽셀부(4002)로 공급된다.

- [0167] 접속 단자 전극(4015)은 액정 소자(4013)에 포함되는 픽셀 전극층(4030)과 동일한 도전막으로부터 형성되며, 단자 전극(4016)은 트랜지스터(4010 및 4011)의 소스 전극층 및 드레인 전극층과 동일한 도전막으로부터 형성된다.

- [0168] 접속 단자 전극(4015)은 이방성 도전막(anisotropic conductive film)(4019)을 통해 FPC(4018)에 포함된 단자에 전기적으로 접속된다.

- [0169] 도 12의 (a-1), (a-2), 및 (b)는 신호선 구동 회로(4003)가 별도로 형성되어 제1 기판(4001) 위에 실장된 예를 도시하는데, 이 실시형태가 이 구조로 제한되는 것은 아니다. 스캔선 구동 회로는 별도로 형성되어 실장되거나, 신호선 구동 회로의 일부 또는 스캔선 구동 회로의 일부가 별도로 형성되어 실장될 수 있다.

- [0170] 도 13은 액정 표시 장치의 구조의 일례를 도시한다.

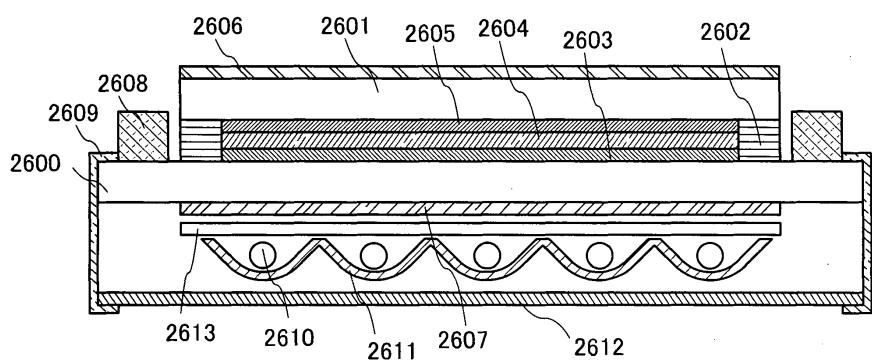

- [0171] 도 13은 액정 표시 장치의 구조의 일례를 도시한다. TFT 기판(2600) 및 대향 기판(2601)이 밀봉재(2602)로 서로 고정된다. TFT 등을 포함하는 픽셀부(2603), 액정층을 포함하는 표시 소자(2604), 및 착색층(2605)이 기판들 사이에 제공되어 표시 영역이 형성된다. 착색층(2605)은 컬러 표시를 수행하는 데 필요하다. RGB 시스템에서, 빨간색, 녹색, 파란색에 대응하는 착색층이 픽셀에 대해 제공된다. 편광판(2606)이 대향 기판(2601)의 외부측에 제공된다. 편광판(2607) 및 확산판(2613)이 TFT 기판(2600)의 외부측에 제공된다. 광원은 냉음극관(2610) 및 반사판(2611)을 포함한다. 회로 기판(2612)은 가요성 배선 기판(2609)에 의해 TFT 기판(2600)의 배선 회로부(2608)에 접속되며, 제어 회로 또는 전원 회로 등의 외부 회로를 포함한다. 편광판 및 액정층은 적층될 수 있으며, 그 사이에 지연판(retardation plate)이 배치될 수 있다.

- [0172] 액정 표시 장치를 구동하기 위한 방법의 경우, TN (twisted nematic) 모드, IPS (in-plane-switching) 모드, FFS (fringe field switching) 모드, MVA (multi-domain vertical alignment) 모드, PVA (patterned vertical alignment) 모드, ASM (axially symmetric aligned micro-cell) 모드, OCB (optically compensated birefringence) 모드, FLC (ferroelectric liquid crystal) 모드, AFLC (antiferroelectric liquid crystal) 모드 등이 사용될 수 있다.

- [0173] 앞서 설명한 공정을 통해, 정지 화상을 표시하는 경우 그레이 레벨 변화로 인한 화질 열화를 감소시킬 수 있는 액정 표시 장치를 제조할 수 있다.

- [0174] 이 실시형태는 다른 실시형태들에서 설명된 컴포넌트들 중 어느 하나와의 적절한 조합으로 구현될 수 있다.

- [0175] (제5 실시형태)

- [0176] 이 실시형태에서, 앞선 실시형태의 액정 표시 장치에 터치 패널 기능을 추가함으로써 획득되는 액정 표시 장치의 구조가 도 14a 및 도 14b를 참조하여 설명할 것이다.

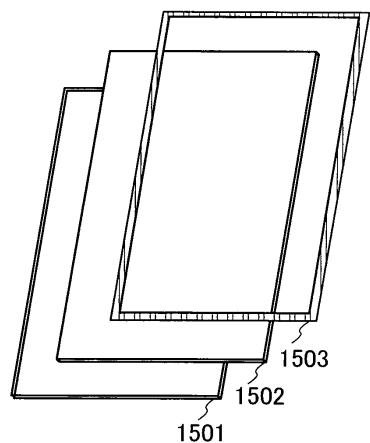

- [0177] 도 14a는 이 실시형태의 액정 표시 장치의 개략도이다. 도 14a는 앞선 실시형태에 따른 액정 표시 장치인 액정 표시 패널(1501)에 터치패널부(1502)가 중첩되어 하우징(케이스)(1503)에 함께 부착된 구조를 도시한다. 터치 패널부(1502)의 경우, 저항방식 터치스크린, 표면 정전용량방식 터치스크린, 투영 정전용량방식 터치스크린 등이 적절히 사용될 수 있다.

- [0178] 도 14a에 도시된 바와 같이, 액정 표시 패널(1501) 및 터치 패널부(1502)가 별도로 제조되어 서로 중첩함으로써, 터치 패널 기능을 갖는 액정 표시 장치의 제조 비용을 감소시킬 수 있다.

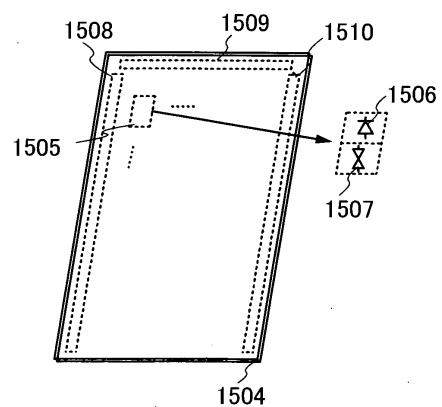

- [0179] 도 14b는 도 14a에 도시된 것과 다른, 터치 패널 기능을 갖는 액정 표시 장치의 구조를 도시한다. 도 14b에 도시된 액정 표시 장치(1504)는 각각 광센서(1506) 및 액정 소자(1507)를 포함하는 복수의 픽셀들(1505)을 포함한다. 따라서, 도 14a와는 달리, 터치 패널부(1502)는 반드시 적층되는 것은 아니며, 이로써 액정 표시 장치의 두께를 줄일 수 있다. 게이트선 구동 회로(1508), 신호선 구동 회로(1509), 및 광센서 구동 회로(1510)가 픽셀들(1505)이 제공되는 기판 위에 형성되는 경우, 액정 표시 기판의 사이즈를 줄일 수 있다. 광센서(1506)는 비정질 실리콘 등을 사용하여 형성되고 산화물 반도체를 포함하는 트랜지스터와 중첩될 수 있다는 점에 유의한다.

- [0180] 산화물 반도체막을 포함하는 트랜지스터가 터치 패널 기능을 갖는 액정 표시 장치에 사용됨으로써, 정지 화상을 표시하는 경우 화상 유지 특성이 개선될 수 있다. 또한, 감소된 재생률로 정지 화상이 표시되는 경우 그레이 레벨 변화로 인한 화질 열화를 감소시킬 수 있다.

- [0181] 이 실시형태는 다른 실시형태들에서 설명된 컴포넌트들 중 어느 하나와의 적절한 조합으로 구현될 수 있다.

[0182] (제6 실시형태)

[0183] 이 실시형태에서는 앞서 설명한 실시형태들 중 어느 하나에 설명된 액정 표시 장치를 포함하는 전자 장치의 일례를 설명할 것이다.

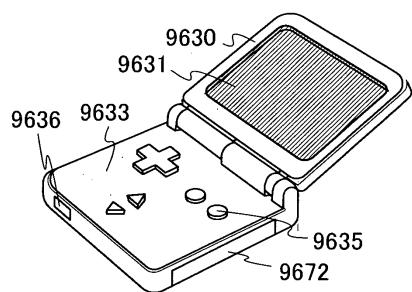

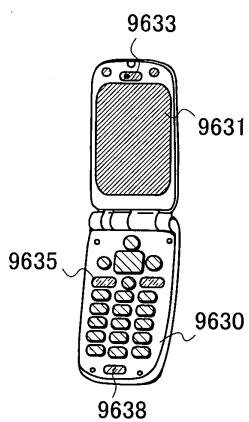

[0184] 도 15a는 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 기록 매체 판독부(9672) 등을 포함할 수 있는 휴대용 게임 기기를 도시한다. 도 15a의 휴대용 게임 기기는 기록 매체에 저장된 프로그램 또는 데이터를 판독하여 표시부에 표시하는 기능 및 무선 통신에 의해 다른 휴대용 게임 기기와 정보를 공유하는 기능을 가질 수 있다. 도 15a의 휴대용 게임 기기의 기능들은 앞서 설명한 것에 제한되지 않으며, 휴대용 게임 기기는 다양한 기능을 가질 수 있다는 점에 유의한다.

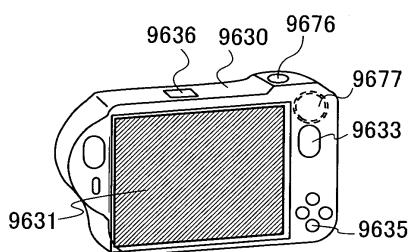

[0185] 도 15b는 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 셔터 버튼(9676), 및 화상 수신부(9677) 등을 포함할 수 있는 디지털 카메라를 도시한다. 도 15b의 디지털 카메라는 정지 화상 및/ 또는 동화상을 촬영하는 기능, 촬영된 화상을 자동 또는 수동으로 보정하는 기능, 안테나로부터 다양한 종류의 정보를 획득하는 기능, 촬영된 화상 또는 안테나로부터 획득된 정보를 저장하는 기능, 촬영된 화상 또는 안테나로부터 획득된 정보를 표시부에 표시하는 기능 등을 가질 수 있다. 도 15b의 디지털 카메라는 앞선 설명으로 제한되지 않고 다양한 기능을 가질 수 있다는 점에 유의한다.

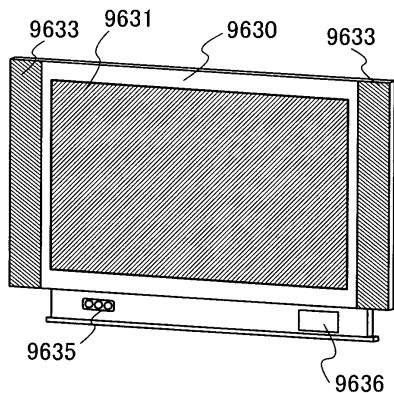

[0186] 도 15c는 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636) 등을 포함할 수 있는 텔레비전 세트를 도시한다. 도 15c의 텔레비전 세트는 텔레비전용 전파를 화상 신호로 변환하는 기능, 화상 신호를 표시에 적합한 신호로 변환하는 기능, 화상 신호의 프레임 주파수를 변환하는 기능 등을 갖는다. 도 15c의 텔레비전 세트는 앞선 설명으로 제한되지 않고 다양한 기능을 가질 수 있다는 점에 유의한다.

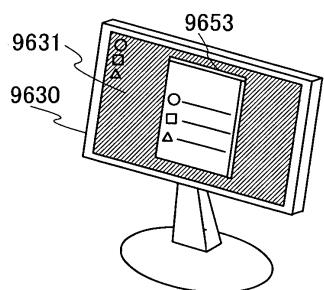

[0187] 도 15d는 하우징(9630), 표시부(9631) 등을 포함할 수 있는 전자 컴퓨터(개인용 컴퓨터)용 (PC 모니터라고도 지칭되는) 모니터를 도시한다. 일례로서, 도 15d의 모니터에서, 윈도우(9653)가 표시부(9631)에 표시된다. 도 15d는 설명을 위해 표시부(9631)에 표시되는 윈도우(9653)를 도시하며, 화상 또는 아이콘과 같은 심볼이 표시될 수 있다는 점에 유의한다. 개인용 컴퓨터를 위한 모니터에서, 여러 경우에 화상 신호가 입력시에만 재기입되는데, 이는 앞서 설명한 실시형태의 액정 표시 장치를 구동하는 방법을 적용하는 데 바람직할 수 있다. 도 15d의 모니터는 앞선 설명으로 제한되지 않고 다양한 기능을 가질 수 있다는 점에 유의한다.

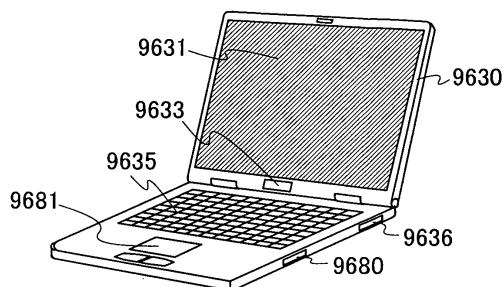

[0188] 도 16a는 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 접속 단자(9636), 포인팅 장치(9681), 외부 접속 포트(9680) 등을 포함할 수 있는 컴퓨터를 도시한다. 도 16a의 컴퓨터는 다양한 정보(예를 들어, 정지 화상, 동화상, 및 텍스트 화상)를 표시부에 표시하는 기능, 다양한 소프트웨어(프로그램)에 의한 프로세싱을 제어하는 기능, 유선 통신 또는 무선 통신 등의 통신 기능, 통신 기능을 이용하여 다양한 통신 네트워크에 접속되는 기능, 통신 기능을 이용하여 다양한 데이터를 송신 또는 수신하는 기능 등을 가질 수 있다. 도 16a의 컴퓨터는 이를 기능을 갖는 것으로 제한되는 것은 아니며, 다양한 기능을 가질 수 있다는 점에 유의한다.

[0189] 도 16b는 하우징(9630), 표시부(9631), 스피커(9633), 조작 키(9635), 마이크(9638) 등을 포함할 수 있는 휴대폰을 도시한다. 도 16b의 휴대폰은 다양한 정보(예를 들어, 정지 화상, 동화상, 및 텍스트 화상)를 표시부에 표시하는 기능, 달력, 날짜, 시간 등을 표시부에 표시하는 기능, 표시부에 표시된 정보를 조작하거나 편집하는 기능, 다양한 종류의 소프트웨어(프로그램)에 의한 처리를 제어하는 기능 등을 가질 수 있다. 도 16b의 휴대폰의 기능들은 앞서 설명한 것에 제한되지 않으며, 휴대폰은 다양한 기능을 가질 수 있다는 점에 유의한다.

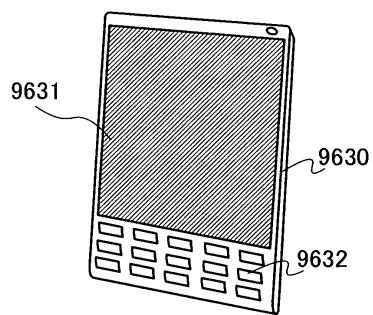

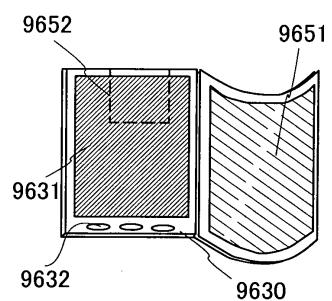

[0190] 도 16c는 하우징(9630), 표시부(9631), 조작 키(9632) 등을 포함할 수 있는 (e북 또는 e-북 리더(e-book reader)라고도 지칭되는) 전자책을 포함하는 전자 장치를 도시한다. 도 16c의 e-북 리더는 다양한 정보(예를 들어, 정지 화상, 동화상, 및 텍스트 화상)를 표시부에 표시하는 기능, 달력, 날짜, 시간 등을 표시부에 표시하는 기능, 표시부에 표시된 정보를 조작하거나 편집하는 기능, 다양한 종류의 소프트웨어(프로그램)에 의한 프로세싱을 제어하는 기능 등을 가질 수 있다. 도 16c의 e-북 리더는 앞선 설명으로 제한되지 않고 다양한 기능을 가질 수 있다는 점에 유의한다. 도 16d는 e-북 리더의 다른 구조를 도시한다. 도 16d의 e-북 리더는 도 16c의 e-북 리더에 태양 전지(9651) 및 전지(9652)를 추가함으로써 획득되는 구조를 갖는다. 반사형 액정 표시 장치가 표시부(9631)로서 사용되는 경우, e-북 리더는 상대적으로 밝은 환경에서 사용될 것으로 예상되는데, 이 경우 태양 전지(9651)가 전력을 효율적으로 생성하고 전지(9652)가 효율적으로 전력을 충전할 수 있기 때문에, 도 16d의 구조가 바람직하다. 리튬 이온 전기가 전지(9652)로서 사용되는 경우 크기 감소 등의 이점이 있을 수 있다는 점에 유의한다.

[0191] 이 실시형태에서 설명된 전자 장치에서, 감소된 재생률로 정지 화상이 표시되는 경우 그레이 레벨 변화로 인한

화질 열화를 감소시킬 수 있다.

[0192] 이 실시형태는 다른 실시형태들에서 설명된 컴포넌트들 중 어느 하나와의 적절한 조합으로 구현될 수 있다.

[0193] 본 출원은 일본 특허청에 2010년 2월 19일에 출원된 일본 특허출원 제2010-034884호에 기초하고 있으며, 그 내용은 참조로서 여기에 원용된다.

### 부호의 설명

[0194] 100: 액정 표시 장치, 101: 타이밍 제어기, 102: 구동 회로, 103: 표시부, 104: 동화상 표시 기간, 105: 정지화상 표시 기간, 106: 기간, 107: 기간, 201: 그레이 레벨, 202: 그레이 레벨, 203: 화살표, 204: 화살표, 205: 그레이 레벨, 206: 그레이 레벨, 207: 그레이 레벨, 208: 그레이 레벨, 209: 그레이 레벨, 301: 그레이 레벨, 302: 그레이 레벨, 303: 화살표, 304: 화살표, 305: 그레이 레벨, 306: 그레이 레벨, 307: 그레이 레벨, 308: 그레이 레벨, 309: 그레이 레벨, 500: 액정 표시 장치, 501: 분석부, 502: 패널 제어기, 503: 화상 신호보정 제어부, 511: 카운터 회로, 512: 판단부, 601: 저항 소자, 602: 버퍼 회로, 603: 스위치, 604: 스위치, 605: 선택 회로, 800: 액정 표시 장치, 801: 화상 처리 회로, 802: 타이밍 제어기, 803: 표시 패널, 804: 백라이트부, 805: 액정 소자, 806: 구동 회로부, 807: 픽셀부, 808: 게이트선, 809: 소스선, 810: 픽셀, 811A: 게이트선 구동 회로, 811B: 소스선 구동 회로, 812: 트랜지스터, 813: 용량 소자, 814: 백라이트 제어 회로, 815: 백라이트, 816: 단자부, 817: 전원, 901: 기간, 902: 기간, 903: 기간, 904: 기간, 1101: 기간, 1102: 기간, 1103: 기간, 1104: 기간, 1200: 기판, 1201: 게이트 전극층, 1202: 게이트 절연층, 1203: 반도체층, 1205a: 소스 전극층, 1205b: 드레인 전극층, 1207: 절연층, 1209: 보호 절연층, 1210: 트랜지스터, 1220: 트랜지스터, 1227: 절연층, 1230: 트랜지스터, 1240: 트랜지스터, 1246a: 배선층, 1246b: 배선층, 1247: 절연층, 1501: 액정 표시 패널, 1502: 터치 패널부, 1503: 하우징, 1504: 액정 표시 장치, 1505: 픽셀, 1506: 광센서, 1507: 액정 소자, 1508: 게이트선 구동 회로, 1509: 신호선 구동 회로, 1510: 광센서 구동 회로, 2600: TFT 기판, 2601: 대향 기판, 2602: 밀봉재, 2603: 픽셀부, 2604: 표시 소자, 2605: 착색층, 2606: 편광판, 2607: 편광판, 2608: 배선 회로부, 2609: 가요성 배선 기판, 2610: 냉음극선판, 2611: 반사판, 2612: 회로 기판, 2613: 확산판, 4001: 기판, 4002: 픽셀부, 4003: 신호선 구동 회로, 4004: 스캔선 구동 회로, 4005: 밀봉재, 4006: 기판, 4008: 액정층, 4010: 트랜지스터, 4011: 트랜지스터, 4013: 액정 소자, 4015: 접속 단자 전극, 4016: 단자 전극, 4018: FPC, 4019: 이방성 도전막, 4020: 절연층, 4021: 절연층, 4030: 픽셀 전극층, 4031: 대향 전극층, 4032: 절연층, 4033: 절연층, 4040: 도전층, 4041a: 절연층, 4041b: 절연층, 4042a: 절연층, 4042b: 절연층, 9630: 하우징, 9631: 표시부, 9632: 조작 키, 9633: 스피커, 9635: 조작 키, 9636: 접속 단자, 9638: 마이크, 9651: 태양 전지, 9652: 전지, 9653: 원도우, 9672: 기록 매체 판독부, 9676: 셋터 버튼, 9677: 화상 수신부, 9680: 외부 접속 포트, 9681: 포인팅 장치

### 도면

#### 도면1a

## 도면1b

## 도면1c

## 도면2a

도면2b

도면3a

도면3b

도면4a

도면4b

도면5a

도면5b

도면6

도면7

## 도면8

## 도면9a

도면9b

도면10

도면11a

도면11b

도면11c

도면11d

## 도면12

도면13

도면14a

도면14b

도면15a

도면15b

도면15c

도면15d

도면16a

도면16b

도면16c

도면16d

|                |                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和电子设备                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">KR1020120139743A</a>                                                                                                                       | 公开(公告)日 | 2012-12-27 |

| 申请号            | KR1020127023942                                                                                                                                        | 申请日     | 2011-02-01 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                     |         |            |

| [标]发明人         | UMEZAKI ATSUSHI<br>우메자카이아츠시<br>MIYAKE HIROYUKI<br>미야케히로유키                                                                                              |         |            |

| 发明人            | 우메자카이아츠시<br>미야케히로유키                                                                                                                                    |         |            |

| IPC分类号         | G09G3/36 G02F1/133                                                                                                                                     |         |            |

| CPC分类号         | G09G3/3607 G09G2320/103 G09G3/3648 G09G3/3655 G09G3/3688 G09G3/3614 G09G2310/0297<br>G09G2310/06 G09G2320/0214 G09G2320/0247 G09G2330/021 G09G2320/043 |         |            |

| 代理人(译)         | Jangsugil<br>Bakchungbeom<br>Yijunghui                                                                                                                 |         |            |

| 优先权            | 2010034884 2010-02-19 JP                                                                                                                               |         |            |

| 其他公开文献         | <a href="#">KR101848684B1</a>                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                              |         |            |

### 摘要(译)

并且抑制以降低的刷新率显示的静止图像的质量的劣化。液晶显示器包括由驱动电路控制的显示器，并包括用于控制常白模式（或常黑模式）液晶的定时控制器和驱动电路。向定时控制器提供用于显示运动图像的图像信号和用于显示静止图像的图像信号。在与用于显示静止图像的图像信号对应的图像中施加到用于表示黑色（或白色）的液晶的电压的绝对值在与用于显示运动图像的图像信号对应的图像中被设置为黑色（或白色）。大于施加到液晶的电压的绝对值。