# (19) 대한민국특허청(KR)

# (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

G09G 3/36 (2006.01) H01L 29/786 (2006.01)

10-2012-7012403 (21) 출원번호

(22) 출원일자(국제) 2010년09월17일 심사청구일자 없음

(85) 번역문제출일자 2012년05월14일

(86) 국제출원번호 PCT/JP2010/066627

(87) 국제공개번호 WO 2011/046010 국제공개일자 2011년04월21일

(30) 우선권주장

JP-P-2009-238869 2009년10월16일 일본(JP) JP-P-2009-279004 2009년12월08일 일본(JP) (11) 공개번호 10-2012-0094927

(43) 공개일자 2012년08월27일

(71) 출원인

가부시키가이샤 한도오따이 에네루기 켄큐쇼 일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자

# 야마자키 순페이

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내

#### 아라사와 료

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내 (뒷면에 계속)

(74) 대리인 장훈

전체 청구항 수 : 총 16 항

## (54) 발명의 명칭 액정 표시 장치 및 액정 표시 장치를 포함한 전자 기기

#### (57) 요 약

표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치에서, 상기 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함하며, 화상 신호가 상기 기록 기간에서 상기 복수 의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트랜지스터는 턴 오프되고 상기 화상 신 호는 상기 유지 기간에서 적어도 30초 동안 유지된다. 상기 화소는 산화물 반도체층을 포함한 반도체층을 포함 하며. 상기 산화물 반도체층은  $1 \times 10^{14}$  /cm 미만의 캐리어 농도를 가진다.

# 대표도

## [도 3a]

# (72) 발명자

# 고야마 준

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내

# 쓰부쿠 마사시

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내

# 노다 고세이

일본 243-0036 가나가와켄 아쓰기시 하세 398 가 부시키가이샤 한도오따이 에네루기 켄큐쇼 내

# 특허청구의 범위

# 청구항 1

표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치를 구동하기 위한 방법에 있어서,

상기 복수의 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함하며,

화상 신호가 상기 기록 기간에서 상기 복수의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트랜지스터는 턴 오프되며 상기 화상 신호는 상기 유지 기간에서 적어도 30초 동안 유지되고,

상기 트랜지스터는 산화물 반도체를 포함한 반도체층을 포함하며,

2차 이온 질량 분석에 의해 측정되는, 상기 산화물 반도체의 수소의 농도는  $5 \times 10^{19}$  /cm 이하인, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 2

제 1 항에 있어서.

상기 화상 신호는 상기 유지 기간에서 1분 이상 및 10분 미만 동안 유지되는, 액정 표시 장치를 구동하기 위한 방법.

# 청구항 3

제 1 항에 있어서,

상기 산화물 반도체는  $1 \times 10^{14}$  /cm 미만의 캐리어 농도를 가진, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 4

제 1 항에 있어서.

상기 트랜지스터의 채널 폭의 마이크로미터 당 오프-상태 전류는  $1\times10^{-17}$  A 이하인, 액정 표시 장치를 구동하기 위한 방법.

## 청구항 5

제 1 항에 있어서.

상기 액정 표시 장치는 전자 기기에 포함되는, 액정 표시 장치를 구동하기 위한 방법.

# 청구항 6

표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치를 구동하기 위한 방법에 있어서,

상기 복수의 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함하며,

화상 신호가 상기 기록 기간에서 상기 복수의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트랜지스터가 턴 오프되며 상기 화상 신호는 상기 유지 기간에서 적어도 30초 동안 유지되는, 액정 표시장치를 구동하기 위한 방법.

# 청구항 7

제 6 항에 있어서,

상기 화상 신호는 상기 유지 기간에서 1분 이상 및 10분 미만 동안 유지되는, 액정 표시 장치를 구동하기 위한 방법.

# 청구항 8

제 6 항에 있어서,

상기 트랜지스터는 산화물 반도체를 포함한 반도체층을 포함하며, 상기 산화물 반도체는  $1\times10^{14}$  /cm 미만의 캐리어 농도를 가진, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 9

제 8 항에 있어서,

상기 트랜지스터의 채널 폭의 마이크로미터 당 오프-상태 전류는  $1\times 10^{-17}$  A 이하인, 액정 표시 장치를 구동하기 위한 방법.

## 청구항 10

제 6 항에 있어서,

상기 액정 표시 장치는 전자 기기에 포함되는, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 11

표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치를 구동하기 위한 방법에 있어서,

상기 복수의 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함하며,

극성이 복수 회 반전되는 전압을 갖는 화상 신호가 상기 기록 기간에서 상기 복수의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트랜지스터는 턴 오프되며, 상기 화상 신호는 상기 유지 기간에서 적어도 30초 동안 유지되는, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 12

제 11 항에 있어서,

상기 유지 기간에서 상기 복수의 화소들의 각각에 유지된 상기 화상 신호의 상기 전압의 극성은 상기 기록 기간의 끝에 공급된 상기 전압의 극성인, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 13

제 11 항에 있어서,

상기 화상 신호는 상기 유지 기간에서 1분 이상 및 10분 미만 동안 유지되는, 액정 표시 장치를 구동하기 위한 방법.

# 청구항 14

제 11 항에 있어서,

상기 트랜지스터는 산화물 반도체를 포함한 반도체층을 포함하며, 상기 산화물 반도체는  $1\times10^{14}$  /cm 미만의 캐리어 농도를 갖는, 액정 표시 장치를 구동하기 위한 방법.

#### 청구항 15

제 14 항에 있어서.

상기 트랜지스터의 채널 폭의 마이크로미터 당 오프-상태 전류는  $1\times10^{-17}$  A 이하인, 액정 표시 장치를 구동하기 위한 방법.

# 청구항 16

제 11 항에 따른 상기 액정 표시 장치를 포함한 전자 기기.

# 명 세 서

### 기술분야

[0001] 본 발명의 일 실시형태는 액정 표시 장치에 관한 것이다. 본 발명의 일 실시형태는 상기 액정 표시 장치를 포함한 전자 기기에 관한 것이다.

# 배경기술

- [0002] 유리 기판과 같은 평판 위에 형성된 박막 트랜지스터들은 대표적으로 액정 표시 장치에 보여지는 바와 같이, 비정질 실리콘 또는 다결정 실리콘을 사용하여 제작되어 왔다. 비정질 실리콘을 사용하여 제작된 박막 트랜지스터들은 낮은 전계 효과 이동도를 가지지만, 큰 유리 기판 위에 형성될 수 있다. 다른 한편으로, 결정 실리콘을 사용하여 제작된 박막 트랜지스터들은 높은 전계 효과 이동도를 가지지만, 레이저 어닐링과 같은 결정화단계로 인해, 이러한 트랜지스터가 큰 유리 기판 위에 형성되기에 반드시 적합한 것은 아니다.

- [0003] 상기를 고려하여, 박막 트랜지스터가 산화물 반도체를 사용하여 제작되는 기술이 관심을 끌고 있으며, 이러한 트랜지스터가 전자 디바이스 또는 광학 디바이스에 적용된다. 예를 들면, 특허 문헌 1은 박막 트랜지스터가 상기 산화물 반도체막으로서 산화 아연 또는 In-Ga-Zn-O-계 산화물 반도체를 사용하여 제작되는 기술을 개시하며, 이러한 트랜지스터는, 예를 들면 액정 표시 장치의 스위칭 소자로서 사용된다.

# 선행기술문헌

#### 특허문헌

[0004] (특허문헌 0001) 일본 공개 특허 출원번호 제2006-165528호

## 발명의 내용

#### 해결하려는 과제

- [0005] 산화물 반도체가 채널 영역을 위해 사용되는 박막 트랜지스터는 비정질 실리콘이 채널 영역을 위해 사용되는 박막 트랜지스터 이상인 전계 효과 이동도를 달성한다. 산화물 반도체를 포함한 이러한 박막 트랜지스터를 포함한 화소는 액정 표시 장치와 같은 표시 장치에 적용되는 것으로 기대된다.

- [0006] 액정 표시 장치에 포함된 각각의 화소는 액정 소자의 배향을 제어하기 위한 전압이 유지되는 저장 용량 소자를 구비한다. 박막 트랜지스터의 오프-상태 전류는 상기 저장 용량의 양을 결정하는 하나의 인자이다. 상기 저장 용량 소자에서의 전압을 유지하기 위한 기간의 연장을 이끄는 오프-상태 전류의 감소는 정지 화상 등이 표시될 때 전력 소비에서의 감소를 위해 중요하다.

- [0007] 본 명세서에서, 오프-상태 전류는 박막 트랜지스터가 오프 상태(또한 비-도전 상태라고 하는)에 있을 때 소스 및 드레인 사이에서 흐르는 전류이다. n-채널 박막 트랜지스터(예를 들면, 약 0V 내지 2V의 임계 전압을 가진)의 경우에, 상기 오프-상태 전류는 음의 전압이 게이트 및 상기 소스 사이에 인가될 때 소스 및 드레인 사이에 흐르는 전류를 의미한다.

- [0008] 또한, 3D 디스플레이 또는 4k2k 디스플레이와 같은, 이상인 값이 부가된 액정 표시 장치와 같이, 화소 당 영역이 작은 것으로 예상되고 개구율이 향상되는 화소를 포함한 액정 표시 장치가 요구된다. 상기 개구율을 향상시키기 위해 유지 용량 소자(holding capacitor)의 면적을 감소시키는 것이 중요하다. 따라서, 박막 트랜지스터의 상기 오프-상태 전류는 감소될 필요가 있다.

- [0009] 상기한 것을 고려할 때, 본 발명의 일 실시형태의 목적은 산화물 반도체를 사용한 박막 트랜지스터의 오프-상 태 전류가 하나의 화소에서 감소될 수 있는 액정 표시 장치를 제공하는 것이다.

# 과제의 해결 수단

[0010] 본 발명의 일 실시형태는 표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치이다. 상기 복수의 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함한다. 화상 신호가 상기 기록 기간에서 상기 복수의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트

랜지스터는 턴 오프되고 상기 화상 신호는 상기 유지 기간에서 적어도 30초 동안 유지된다.

- [0011] 본 발명의 일 실시형태는 표시부에 복수의 화소들을 포함하고 복수의 프레임 기간들에서 표시를 수행하도록 구성된 액정 표시 장치이다. 상기 복수의 프레임 기간들의 각각은 기록 기간 및 유지 기간을 포함한다. 극성이 복수 회 반전되는 전압을 가진 화상 신호가 상기 기록 기간에서 상기 복수의 화소들의 각각에 입력된 후, 상기 복수의 화소들의 각각에 포함된 트랜지스터는 턴 오프되고 상기 화상 신호는 상기 유지 기간에서 적어도 30초 동안 유지된다.

- [0012] 본 발명의 실시형태의 상기 액정 표시 장치에서, 상기 유지 기간에서 상기 복수의 화소들의 각각에 공급된 상기 화상 신호의 전압의 극성은 상기 기록 기간의 끝에서 공급된 상기 전압의 극성일 수 있다.

- [0013] 본 발명의 상기 실시형태의 상기 액정 표시 장치에서, 상기 트랜지스터는 산화물 반도체를 포함한 반도체층을 포함할 수 있으며, 상기 산화물 반도체는  $1\times10^{14}/\mathrm{cm}$  미만의 캐리어 농도를 가질 수 있다.

- [0014] 본 발명의 상기 실시형태의 상기 액정 표시 장치에서, 상기 트랜지스터의 채널 폭의 마이크로미터당 상기 오 프 상태 전류는  $1\times 10^{-17}$  A 이하일 수 있다.

#### 발명의 효과

[0015] 산화물 반도체를 사용한 박막 트랜지스터를 포함한 화소에서, 상기 오프-상태 전류는 감소될 수 있다. 그러므로, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장시키고 정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다. 또한, 개구율이 향상될 수 있어서, 고-화질 표시부를 포함한 액정 표시 장치가 획득될 수 있도록 한다.

## 도면의 간단한 설명

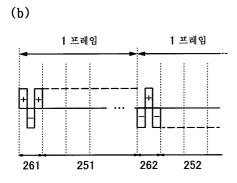

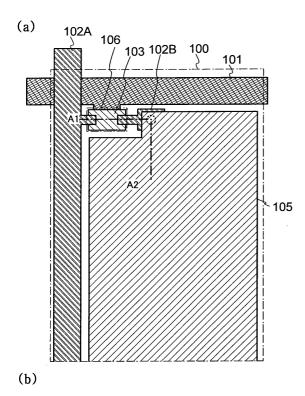

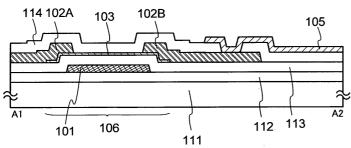

- [0016] 도 1a 내지 도 1c는 액정 표시 장치의 평면도 및 단면도들.

- 도 2는 액정 표시 장치의 블록도.

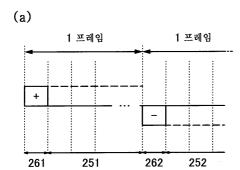

- 도 3a 및 도 3b는 액정 표시 장치의 동작을 도시한 도면.

- 도 4a 및 도 4b는 액정 표시 장치의 평면도 및 단면도.

- 도 5a 및 도 5b는 박막 트랜지스터를 도시한 도면.

- 도 6a 내지 도 6e는 박막 트랜지스터를 제작하는 방법을 도시한 도면.

- 도 7a 및 도 7b는 박막 트랜지스터를 도시한 도면.

- 도 8a 내지 도 8e는 박막 트랜지스터를 도시한 도면.

- 도 9a 및 도 9b는 각각 박막 트랜지스터를 도시한 도면.

- 도 10a 내지 도 10e는 박막 트랜지스터를 도시한 도면.

- 도 11a 내지 도 11e는 박막 트랜지스터를 도시한 도면.

- 도 12a 내지 도 12d는 박막 트랜지스터를 도시한 도면.

- 도 13a 내지 도 13d는 박막 트랜지스터를 도시한 도면.

- 도 14는 박막 트랜지스터를 도시한 도면.

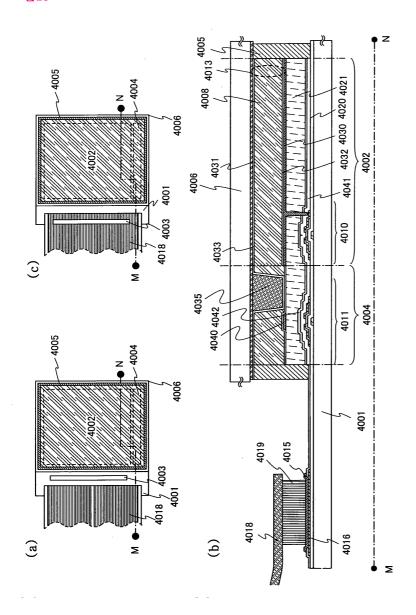

- 도 15a 내지 도 15c는 액정 패널을 도시한 도면.

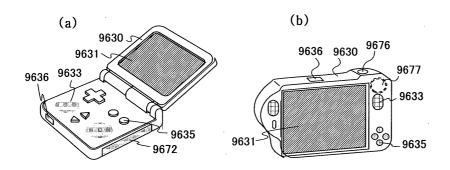

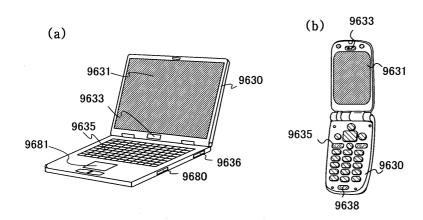

- 도 16a 내지 도 16c는 전자 기기들을 도시한 도면.

- 도 17a 내지 도 17c는 전자 기기들을 도시한 도면.

- 도 18은 실시형태 13을 도시하기 위한 다이어그램.

- 도 19a 및 도 19b는 실시형태 13을 도시하기 위한 다이어그램들.

- 도 20a 및 도 20b는 실시형태 13을 도시하기 위한 다이어그램들.

- 도 21은 실시형태 13을 도시하기 위한 다이어그램.

- 도 22는 실시형태 14를 도시하기 위한 다이어그램.

- 도 23a 및 도 23b는 실시형태 14를 도시하기 위한 다이어그램들.

- 도 24a 및 도 24b는 실시형태 14를 도시하기 위한 다이어그램들.

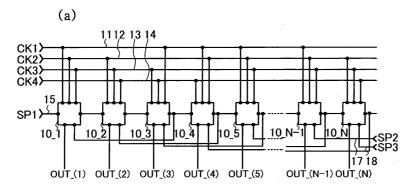

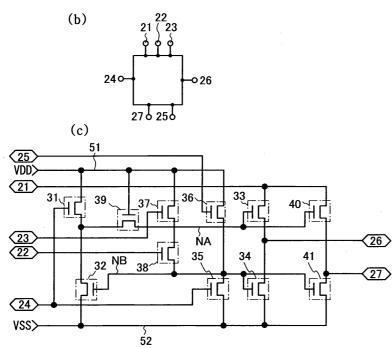

- 도 25a 내지 도 25c는 시프트 레지스터의 구조를 도시한 도면.

- 도 26은 시프트 레지스터의 동작을 도시하기 위한 흐름도.

- 도 27은 시프트 레지스터의 동작을 도시하기 위한 흐름도.

- 도 28은 예 1의 액정 표시 장치를 도시하기 위한 다이어그램.

- 도 29는 예 1의 액정 표시 장치를 도시하기 위한 다이어그램.

- 도 30은 예 1의 액정 표시 장치를 도시하기 위한 다이어그램.

#### 발명을 실시하기 위한 구체적인 내용

- [0017] 본 발명의 실시형태들 및 예들이 상기 도면들을 참조하여 상세히 기술될 것이다. 본 발명은 다음 설명에 제한되지 않으며, 이 기술분야의 숙련자들에 의해 다양한 변경들 및 수정들이 본 발명의 사상 및 범위로부터 벗어나지 않고 이루어질 수 있다는 것이 쉽게 이해될 것이다. 그러므로, 본 발명은 이하의 실시형태들 및 예들의설명에 제한되는 것으로서 해석되어서는 안된다. 이하에 기술된 본 발명의 구조에서, 동일한 부분들 또는 상이한 도면들에서 유사한 기능들을 가진 부분들은 동일한 참조 부호들로서 나타내어지며, 그것들의 반복적인설명은 생략될 것임을 주의하자.

- [0018] 본 명세서에서의 도면들에 도시된 크기, 층의 두께, 또는 각각의 구조의 영역은 몇몇 경우들에서 단순함을 위해 과장된다는 것을 주의하자. 그러므로, 본 발명의 실시형태들 및 예들은 이러한 스케일들에 제한되지 않는다.

- [0019] 본 명세서에 사용된 "제 1", "제 2", 및 "제 3"과 같은 용어들은 단지 구성 요소들의 혼동을 회피하기 위해 사용되며, 상기 구성 요소들의 수에 대한 제한을 의미하지 않는다. 그러므로, 예를 들면 "제 1"이 "제 2" 또는 "제 3"으로 적절하게 교체될 때에도 설명이 이루어질 수 있다.

- [0020] (실시형태 1)

- [0021] 액정 표시 장치의 화소가 박막 트랜지스터를 사용하여 형성되는 일 예가 이하에 설명된다. 이 실시형태에서, 액정 표시 장치의 화소에 포함된 박막 트랜지스터(이하에서, 또한 TFT라고 함) 및 상기 TFT에 접속된 화소 전 극으로서 기능하는 전극(또한 간단하게 화소 전극이라고 하는)이 예들로서 설명된다. 화소는 표시 장치의 각각의 화소에 제공된 소자들을 포함하는 소자 그룹, 예를 들면, 박막 트랜지스터, 화소 전극으로서 기능하는 전극, 또는 배선과 같이, 전기 신호들에 따라 표시를 제어하기 위한 소자를 나타낸다. 화소는 컬러 필터 등을 포함할 수 있으며, 그 밝기가 하나의 화소로 제어될 수 있는 하나의 컬러 성분에 대응할 수 있다. 그러므로, 예를 들면, R, G, 및 B의 컬러 성분들을 포함한 컬러 표시 장치의 경우에, 화상의 최소 단위는 R, G, 및 B의 3개의 화소들을 포함하며, 화상은 복수의 화소들로 획득될 수 있다. 본 발명의 일 실시형태는 컬러 표시 장치에 제한되지 않으며, 단색(monochrome) 표시 장치일 수 있다는 것을 주의하자.

- [0022] "A와 B가 서로 접속된다"는 A와 B가 서로 전기적으로 접속되는 경우 및 A와 B가 서로 직접 접속되는 경우를 포함한다는 것을 주의하자. 여기에서, A와 B의 각각은 대상(예로서, 장치, 소자, 회로, 배선, 전극, 단자, 도전막, 층 등)에 대응한다.

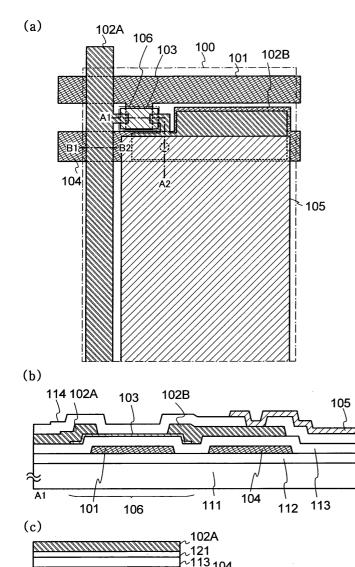

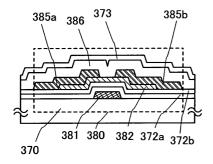

- [0023] 먼저, 화소의 평면도가 도 1a에 도시된다. 도 1a는 TFT의 구조의 일 예로서 보텀-게이트 구조를 도시한다는 것을 주의하자. 도 1a는 TFT의 소스 전극 및 드레인 전극으로서 작용하는 배선충들이 게이트로서 작용하는 배선에 대해 채널 영역으로서 작용하는 산화물 반도체충의 대향 측 상에 제공되는 소위 역 스태거 구조 (inverted staggered structure)를 도시한다는 것을 주의하자.

- [0024] 도 1a에 도시된 화소(100)는 주사선으로서 기능하는 제 1 배선(101), 신호선으로서 기능하는 제 2 배선 (102A), 산화물 반도체층(103), 용량선(104), 및 화소 전극(105)을 포함한다. 게다가, 상기 화소(100)는 상기 산화물 반도체층(103) 및 상기 화소 전극(105)을 서로 전기적으로 접속하기 위한 제 3 배선(102B)을

포함하며, 여기에서 박막 트랜지스터(106)가 형성된다. 상기 제 1 배선(101)은 또한 상기 박막 트랜지스터 (106)의 게이트로서 기능하는 배선이다. 상기 제 2 배선(102A)은 또한 소스 전극 및 드레인 전극 중 하나 및 저장 용량 소자의 하나의 전극으로서 기능하는 배선이다. 상기 제 3 배선(102B)은 또한 상기 소스 전극 및 상기 드레인 전극 중 다른 하나로서 기능하는 배선이다. 상기 용량선(104)은 상기 저장 용량 소자의 다른 하나의 전극으로서 기능하는 배선이다.

- [0025] 프로세스의 단순화를 위해, 상기 제 1 배선(101) 및 상기 용량선(104)이 동일한 층에 제공되며 상기 제 2 배선(102A) 및 상기 제 3 배선(102B)이 동일한 층에 제공되는 것이 바람직하다는 것을 주의하자. 더욱이, 상기 제 3 배선(102B) 및 상기 용량선(104)은 서로 부분적으로 중첩하고 액정 소자를 위한 저장 용량 소자를 형성하도록 제공된다. 상기 박막 트랜지스터(106)에 포함된 상기 산화물 반도체층(103)은 그 사이에 개재된 게이트 절연막(도시되지 않음)을 갖고 상기 제 1 배선(101)으로부터 분기하는 배선 위에 제공된다는 것을 주의하자.

- [0026] 도 1b는 도 1a의 쇄선(A1-A2)을 따라 취해진 단면 구조를 도시한다. 도 1b에 도시된 상기 단면 구조에서, 게이트로서 작용하는 상기 제 1 배선(101) 및 상기 용량선(104)은 그 사이에 개재된 하지막(112)을 갖고 기판(111) 위에 제공된다. 게이트 절연막(113)은 상기 제 1 배선(101) 및 상기 용량선(104)을 커버하도록 제공된다. 상기 산화물 반도체층(103)은 상기 게이트 절연막(113) 위에 제공된다. 상기 제 2 배선(102A) 및 상기 제 3 배선(102B)은 상기 산화물 반도체층(103) 위에 제공된다. 게다가, 패시베이션 막으로서 기능하는 산화물 절연층(114)이 상기 산화물 반도체층(103), 상기 제 2 배선(102A), 및 상기 제 3 배선(102B) 위에 제공된다. 개구부가 상기 산화물 절연층(114)에 형성되며, 상기 개구부에서, 상기 화소 전극(105) 및 상기 제 3 배선(102B)이 서로 접속된다. 더욱이, 용량 소자가 유전체로서 작용하는 상기 제 3 배선(102B), 상기 용량선(104), 및 상기 게이트 절연막(113)에 의해 형성된다.

- [0027] 도 1c는 도 1a의 쇄선(B1-B2)을 따라 취해진 단면도를 도시하며, 절연충(121)이 상기 용량선(104) 및 상기 제 2 배선(102A) 사이에 제공되는 구조를 도시한다.

- [0028] 상기 제 2 배선(102A)이 상기 제 1 배선(101) 및 상기 용량선(104) 위에 제공되는 경우에, 기생 용량은 상기 제이트 절연막(113)의 두께에 의존하여, 상기 제 1 배선(101)과 상기 제 2 배선(102A) 사이 및 상기 용량 소자(104)와 상기 제 2 배선(102A) 사이에 생성될 수 있다. 그러므로, 도 1c에 도시된 바와 같이 상기 절연층 (121)을 제공함으로써, 기생 용량이 감소될 수 있고 오작동과 같은 결함이 감소될 수 있다.

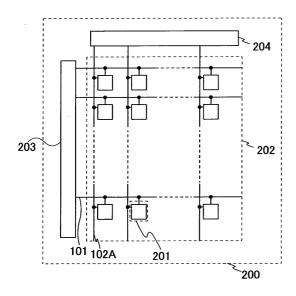

- [0029] 도 1a 내지 도 1c에 도시된 상기 화소는 도 2에 도시된 바와 같이 기판(200) 위에 매트릭스로 배열된 복수의 화소들(201) 중 하나에 대응한다는 것을 주의하자. 도 2는 화소부(202), 주사선 구동기 회로(203), 및 신호선 구동기 회로(204)가 상기 기판(200) 위에 제공되는 구성을 도시한다. 상기 화소들(201)이 선택된 상태인지 또는 비-선택 상태인지 여부는 상기 주사선 구동기 회로(203)에 접속된 상기 제 1 배선(101)으로부터 공급된 주사 신호에 따라 각각의 선에 대해 결정된다. 상기 주사선에 의해 선택된 상기 화소(201)는 상기 신호선 구동기 회로(204)에 접속된 상기 배선(102A)을 통해 비디오 전압(또한, 화상 신호, 영상 신호, 또는 비디오 데이타라고 하는)을 공급받는다.

- [0030] 도 2는 상기 주사선 구동기 회로(203) 및 상기 신호선 구동기 회로(204)가 상기 기판(200) 위에 제공되는 구성을 도시하지만, 상기 주사선 구동기 회로(203) 및 상기 신호선 구동기 회로(204) 중 하나가 상기 기판(200) 위에 제공되고 다른 하나가 또 다른 기판(예로서, 단결정 실리콘 기판) 위에 형성되며, 그 후 TAB 방법 또는 COG 방법과 같은 실장 기술에 의해 상기 화소부(202)에 접속되는 구성이 이용될 수 있다. 대안적으로, 단지 상기 화소부(202)가 상기 기판(200) 위에 제공되고 상기 주사선 구동기 회로(203) 및 상기 신호선 구동기 회로(204)가 또 다른 기판 위에 형성되며 그 후 TAB 방법 또는 COG 방법과 같은 실장 기술에 의해 상기 화소부(202)에 접속되는 구조가 이용될 수 있다.

- [0031] 도 2는 상기 복수의 화소들(201)이 상기 화소부(202)에 매트릭스로(스트라이프로) 배열되는 일 예를 도시한다. 상기 화소들(201)이 반드시 매트릭스로 배열될 필요는 없으며, 예를 들면 델타 패턴(delta pattern) 또는 베이어 패턴(Bayer pattern)으로 배열될 수 있다는 것을 주의하자. 상기 화소부(202)의 표시 방법으로서, 프로그레시브 방법(progressive method) 또는 인터레이스 방법(interlace method) 중 하나가 이용될 수 있다. 컬러 표시를 위해 화소에서 제어된 컬러 성분들은 R, G, 및 B(R, G, 및 B는 각각 빨간색, 녹색, 및 파란색에 대응한다)의 3개의 컬러들에 제한되지 않으며, 3개 이상의 컬러들의 컬러 성분들, 예를 들면, R, G, B, 및 W(W는 흰색에 대응한다), R, G, B, 및 노란색, 청록색, 자홍색 등 중 하나 이상 등이 이용될 수 있다는 것을 주의하자. 표시 영역들의 크기들은 컬러 성분들의 각각의 점들 사이에서 상이할 수 있다는 것

을 주의하자.

- [0032] 도 2에서, 상기 제 1 배선들(101) 및 상기 제 2 배선들(102A)의 수들은 컬럼 방향 및 로우 방향에서의 상기 화소들의 수에 대응한다. 상기 제 1 배선들(101) 및 상기 제 2 배선들(102A)의 수들은 상기 화소들에 포함된 서브-화소들의 수 또는 상기 화소들에서의 상기 트랜지스터들의 수에 의존하여 증가될 수 있다는 것을 주의하자. 대안적으로, 상기 화소(201)는 다른 화소들과 공유되는 상기 제 1 배선(101) 및 상기 제 2 배선(102A)에 의해 구동될 수 있다.

- [0033] 도 1a는 직사각형 형상을 가진 것으로 상기 TFT의 상기 제 2 배선(102A)을 도시하며; 대안적으로, 상기 제 2 배선(102A)은 캐리어들이 이동하는 영역의 면적이 증가될 수 있고 상기 박막 트랜지스터가 턴 온될 때(또한, 온-상태 전류라고 하는) 흐르는 전류의 양이 증가될 수 있도록 상기 제 3 배선(102B)을 둘러싸는 형상(구체적으로, U 형상 또는 C 형상)으로 형성될 수 있다는 것을 주의하자.

- [0034] 본 명세서에서, 온-상태 전류는 박막 트랜지스터가 온 상태(또한 도전 상태라고 하는)에 있을 때 소스 및 드레인 사이에 흐르는 전류임을 주의하자. n-채널 박막 트랜지스터의 경우에, 상기 온-상태 전류는 게이트 및 상기 소스 사이에 인가된 전압이 임계 전압(Vth)보다 높을 때 소스 및 드레인 사이에 흐르는 전류를 의미한다.

- [0035] 개구율은 단위 면적에 대한 투광 면적의 부분의 비를 나타낸다는 것을 주의하자. 광을 투과시키지 않는 부재에 의해 점유된 영역이 커질수록, 상기 개구율은 감소하며, 광을 투과시키는 부재에 의해 점유되는 영역이 커질수록 상기 개구율은 증가한다. 액정 표시 장치에서, 상기 개구율은 화소 전극에 중첩하는 배선 또는 용량선의 면적 및 박막 트랜지스터의 크기를 감소시킴으로써 증가한다.

- [0036] 박막 트랜지스터는 게이트, 드레인, 및 소스의 적어도 3개의 단자들을 갖는 소자임을 주의하자. 상기 박막 트랜지스터는 드레인 영역 및 소스 영역 사이에 채널 영역을 가지며 전류가 상기 드레인 영역, 상기 채널 영역, 및 상기 소스 영역을 통해 흐르도록 허용한다. 여기에서, 상기 박막 트랜지스터의 상기 소스 및 상기 드레인은 상기 박막 트랜지스터의 상기 구조, 상기 동작 조건 등에 의존하여 변할 수 있기 때문에, 어떤 것이 소스 또는 드레인인지를 정의하는 것은 어려운 일이다. 그러므로, 소스 또는 드레인으로서 기능하는 영역은 몇몇 경우들에서 상기 소스 또는 상기 드레인이라고 하지 않는다. 이러한 경우에, 예를 들면, 상기 소스 및 상기 드레인 중 하나는 제 1 단자라고 할 수 있고 다른 하나는 제 2 단자라고 할 수 있다. 대안적으로, 상기 소스 및 상기 드레인 중 하나는 제 1 전극이라고 할 수 있고 다른 하나는 제 2 전극이라고 할 수 있다. 또한 대안적으로, 상기 소스 및 상기 드레인 중 하나는 제 1 영역이라고 할 수 있고, 다른 하나는 제 2 영역이라고 할 수 있다.

- [0037] 다음으로, 상기 산화물 반도체층(103)이 기술될 것이다.

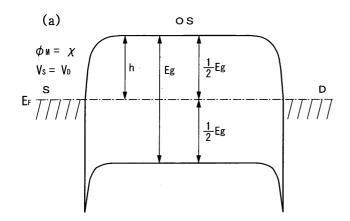

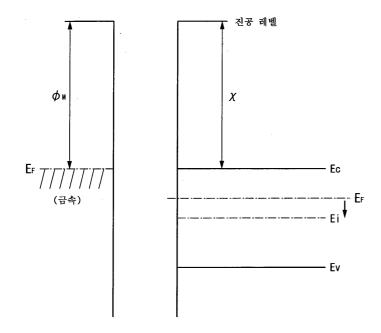

- [0038] 이 실시형태에서, 산화물 반도체로부터, 상기 산화물 반도체에서 수소의 농도가  $5 \times 10^{19}$  /cm 이하, 바람직하게 는  $5 \times 10^{18}$  /cm 이하, 보다 바람직하게는  $5 \times 10^{17}$  /cm 이하가 되도록 수소(OH 결합을 포함하는)가 제거된다. 그 후, 채널 영역이  $1 \times 10^{14}$  /cm 미만, 바람직하게는  $1 \times 10^{12}$  /cm 이하의 캐리어 농도를 가진 산화물 반도체막을 사용하여 형성되는 박막 트랜지스터가 형성된다. 상기 산화물 반도체층에서 수소의 농도는 2차 이온 질량 분석법(secondary ion mass spectrometry; SIMS)에 의한 분석에 의해 측정된다는 것을 주의하자.

- [0039] 산화물 반도체의의 에너지 갭이 2 eV 이상, 바람직하게는 2.5 eV 이상, 보다 바람직하게는 3 eV 이상일 때, 열 여기에 의해 생성된 캐리어들은 그것들이 무시될 수 있도록 적다. 따라서, 도너들을 형성하는 수소와 같은 불순물들은 상기 캐리어 농도가  $1\times10^{14}$  /cm 미만, 바람직하게는  $1\times10^{12}$  /cm 이하가 되도록 가능한 한 많이 감소된다. 달리 말하면, 산화물 반도체층의 상기 캐리어 농도는 가능한 한 0에 가깝게 된다.

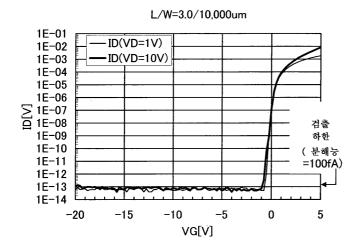

- [0040] 상술된 바와 같이 상기 산화물 반도체로부터 수소를 완전히 제거함으로써 정제되는 산화물 반도체가 박막 트랜지스터의 채널 형성 영역을 위해 사용될 때, 상기 드레인 전류는 상기 채널 폭이 10 mm인 경우에서도 1V 내지 10V의 범위에 있는 드레인 전압 및 -5V 내지 -20V의 범위에 있는 게이트 전압에서  $1 \times 10^{-13}$  A 이하이다.

- [0041] 표시 장치의 회로 등이 이러한 매우 작은 오프-상태 전류를 가진 박막 트랜지스터를 사용하여 제작되는 경우에, 매우 작은 누설이 존재한다. 그러므로, 영상 신호와 같은 전기 신호는 보다 긴 시간 기간 동안 유지될 수있다.

- [0042] 구체적으로, 상기 산화물 반도체층을 포함하고 10 ㎞의 채널 폭을 가진 전술된 트랜지스터의 채널 폭의 마이

크로미터당 상기 오프-상태 전류는  $10 \text{ aA/}\mu\text{m}(1\times10^{-17}\text{ A/}\mu\text{m})$  이하만큼 작을 수 있으며, 뿐만 아니라  $1 \text{ aA/}\mu\text{m}(1\times10^{-18}\text{ A/}\mu\text{m})$  이하만큼 작을 수 있다. 오프 상태에서의 매우 작은 전류(오프-상태 전류)를 가진 트랜지스터가 화소에서 선택 트랜지스터로서 사용될 때, 영상 신호와 같은 전기 신호가 보다 긴 시간 기간 동안 유지될 수 있다. 상기 유지 시간은 연장될 수 있기 때문에, 예를 들면, 영상 신호의 기록 후 유지 기간은 10초 이상, 바람직하게는 30초 이상, 보다 바람직하게는 1분 이상 및 10분 미만으로 설정된다. 상기 유지 기간을 연장함으로써, 기록 간격들은 길게 설정될 수 있고 전력 소비는 보다 효과적으로 감소될 수 있다.

- [0043] 다른 한편, 예를 들면, 저-온 폴리실리콘을 포함한 트랜지스터의 경우에, 설계 등은 상기 오프-상태 전류가 대략  $1 \times 10^{-12}$   $A/\mu$ m이라고 가정하여 수행된다. 그러므로, 저-온 폴리실리콘(대략 0.1 pF)을 포함한 상기 트랜지스터와 동일한 저장 용량을 갖는 산화물 반도체를 포함한 트랜지스터의 경우에, 상기 전압 유지 기간은 저-온 폴리실리콘을 포함한 상기 트랜지스터의 대략  $10^4$ 배일 수 있다. 더욱이, 비정질 실리콘을 포함한 트랜지스터의 경우에, 채널 폭의 마이크로미터당 상기 오프-상태 전류는  $1 \times 10^{-13}$   $A/\mu$ m 이상이다. 그러므로, 고-순도 산화물 반도체를 포함한 트랜지스터의 상기 전압 유지 기간은 이들 트랜지스터들이 서로 동일하거나 또는 실질적으로 동일한 저장 용량(대략 0.1 pF)을 가질 때 비정질 실리콘을 사용한 트랜지스터의  $10^4$  배 이상일 수 있다.

- [0044] 예를 들면, 저-온 폴리실리콘을 포함한 박막 트랜지스터를 가진 활성 매트릭스 표시 장치에서, 상기 박막 트랜지스터의 누설 전류로 인해, 화소에 유지되는 전하들의 손실이 존재하며; 따라서 영상 신호의 재기록이 16 밀리초마다(60프레임들/초) 수행된다. 다른 한편으로, 상기 산화물 반도체층을 포함한 상기 전술한 박막 트랜지스터를 가진 활성 매트릭스 표시 장치에서, 상기 산화물 반도체층을 포함한 상기 박막 트랜지스터의 상기 오프-상태 전류는 저-온 폴리실리콘을 포함한 박막 트랜지스터보다 훨씬 더 작으며; 따라서, 모든 신호 기록을 위한 상기 유지 기간은 10000배 더 길어질 수 있으며, 이것은 대략 160초이다.

- [0045] 상기 유지 기간은 연장될 수 있기 때문에, 신호 기록의 빈도는 특히 정지 화상이 표시될 때 감소될 수 있다. 그러므로, 화소에 대한 신호 기록의 횟수는 감소될 수 있으며, 전력 소비는 감소될 수 있다.

- [0046] 도 1a 내지 도 1c에 도시된 상기 저장 용량 소자는 전극들의 쌍 및 상기 전극들의 쌍 사이에 유전체로서 제공된 절연층에 의해 형성된다. 상기 저장 용량은 전하들이 미리 정해진 기간 동안 유지될 수 있도록 상기 화소부 등에 제공된 박막 트랜지스터의 상기 누설 전류를 고려하여 설정된다. 상기 저장 용량 소자의 크기는 트랜지스터의 오프-상태 전류 등을 고려하여 설정될 수 있다. 이 실시형태에서, 고-순도 산화물 반도체층을 포함한 트랜지스터는 상기 트랜지스터(106)로서 사용되기 때문에, 그것은 각각의 화소에서 액정 용량의 1/3 이하,바람직하게는 1/5 이하인 용량을 가진 저장 용량 소자를 제공하기에 충분하다.

- [0047] 상기 고-순도 산화물 반도체층을 포함한 전술한 트랜지스터의 경우에, 상기 유지 기간이 보다 길게 설정될 수 있다. 그러므로, 신호 기록의 빈도는 특히 정지 화상이 표시될 때 현저하게 감소될 수 있다. 따라서, 표시에서 보다 덜 빈번한 변화들을 수반하는 정지 화상 등을 표시하는 경우에, 화소에 대한 신호 기록의 횟수는 감소될 수 있고, 따라서 전력 소비는 감소될 수 있다.

- [0048] 정지 화상 표시에서, 리프레쉬 동작이 유지 기간 동안 액정 소자에 인가된 전압의 유지율을 고려하여 적절하 게 수행될 수 있다. 예를 들면, 리프레쉬 동작은 신호가 액정 소자의 화소 전국에 기록되는 직후 전압의 값 (초기 값)에 대하여 전압이 미리 정해진 레벨로 감소될 때의 타이밍에서 수행될 수 있다. 상기 미리 정해진 레벨은 바람직하게는 플리커(flicker)가 상기 초기 값에 대해 감지되지 않는 전압으로 설정된다. 구체적으로, 표시 대상이 화상인 경우에, 리프레쉬 동작(재기록)은 바람직하게는 상기 전압이 상기 초기 값보다 1.0%, 바람직하게는 0.3% 낮아질 때마다 수행된다. 표시 대상이 문자인 경우에, 리프레쉬 동작(재기록)은 바람직하게 는 상기 전압이 상기 초기 값보다 10%, 바람직하게는 3% 낮아질 때마다 수행된다.

- [0049] 정지 화상 표시에서의 상기 유지 기간 동안, 대향 전극(또한 공통 전극이라고 하는)이 플로팅 상태에 놓일 수 있다. 구체적으로, 상기 대향 전극에 공통 전위를 공급하기 위해 스위치가 상기 대향 전극 및 전원 사이에 제공될 수 있다. 상기 기록 기간 동안, 상기 스위치는 턴 온될 수 있으며 상기 공통 전위는 상기 대향 전극에 공급될 수 있고; 그 후, 상기 유지 기간 동안, 상기 스위치는 턴 오프될 수 있으며 상기 대향 전극은 플로팅 상태에 놓일 수 있다. 상기 스위치로서, 상기 고-순도 산화물 반도체층을 포함한 상기 전술한 반도체를 사용하는 것이 바람직하다. 상술된 바와 같이 매우 작은 오프-상태 전류를 가진 산화물 반도체를 포함한 TFT를 사용하여, 액정 표시 패널의 상기 대향 전극 및 상기 화소 전극 간의 전위는 거의 변하지 않으며, 상기 정지 화

상 표시는 구동기 회로가 소위 액정의 화상 번-인을 야기하지 않고 중지되는 동안 유지될 수 있다.

- [0050] 액정 재료의 고유 저항은  $1 \times 10^{12} \Omega$ ·cm 이상, 바람직하게는  $1 \times 10^{13} \Omega$ ·cm 이상, 보다 바람직하게는  $1 \times 10^{14}$   $\Omega$ ·cm 이상이다. 본 명세서에서 상기 고유 저항은 20℃에서 측정된다는 것을 주의하자. 액정 표시 장치가 상기 액정 재료를 사용하여 형성되는 경우에, 액정 소자로서 작용하는 부분의 저항률은 불순물이 배향막, 씰재 등으로부터 액정층으로 혼합될 수 있는 가능성이 존재하기 때문에  $1 \times 10^{11} \Omega$ ·cm 이상, 몇몇 경우들에서  $1 \times 10^{12} \Omega$ ·cm 이상일 수 있다

- [0051] 액정 재료의 상기 고유 저항이 더욱 커질수록, 상기 액정 재료를 통해 누설되는 전하들이 보다 많이 감소될 수 있으며, 상기 액정 소자의 동작 상태를 유지하기 위한 전압에서의 시간에 따른 감소가 억제될 수 있다. 그 결과, 상기 유지 기간은 연장될 수 있으며, 그러므로 신호 기록의 빈도는 감소될 수 있고, 표시 장치의 전력소비는 감소될 수 있다.

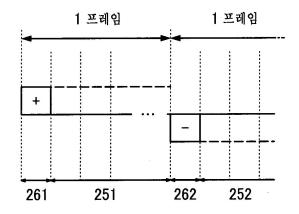

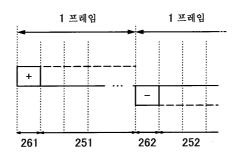

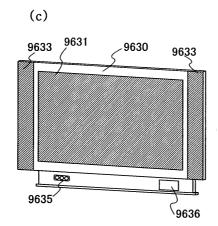

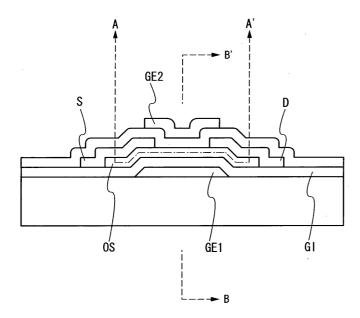

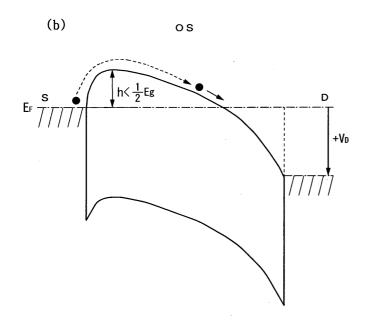

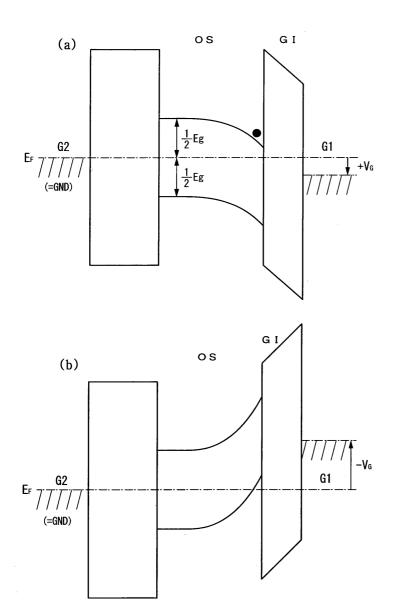

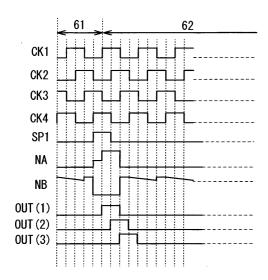

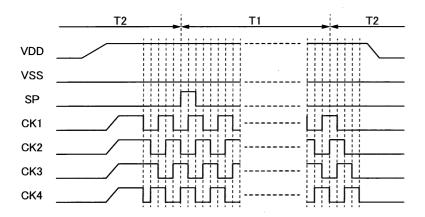

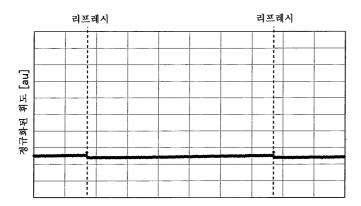

- [0052] 도 3a는 프레임 기간에서 기록 기간 및 유지 기간 간의 관계를 도시한다. 도 3a에서, 기간들(251, 252) 각각은 유지 기간에 대응하며, 기간들(261, 262) 각각은 기록 기간에 대응한다.

- [0053] 도 3a에서, 표시 소자인 액정 소자에 인가된 전압의 극성(도면에서, 극성은 플러스 부호 또는 마이너스 부호로 표시된다)은 모든 프레임 기간에서 반전된다. 따라서, 상기 액정 소자에 인가된 전계는 바이어싱되지 않으며, 상기 액정 소자의 열화도가 감소될 수 있다. 상기 산화물 반도체층을 포함한 전술한 박막 트랜지스터의 경우에, 상기 유지 기간은 보다 길게 설정될 수 있으며, 따라서 화소에 대한 기록의 횟수는 대폭 감소될 수 있다. 그러므로, 표시에서 덜 빈번한 변화들을 수반하는 정지 화상 등을 표시하는 경우에, 전력 소비는 감소될 수 있다.

- [0054] 게다가, 도 3b는 그 극성이 도 3a의 상기 기록 기간들(261, 262)의 각각에서 복수 회 반전되는 전압을 기록하는 경우에서의 관계를 도시한다. 도 3b에 도시된 바와 같이 극성이 상기 기록 기간들(261, 262)의 각각에서 복수 회 반전되는 전압을 기록함으로써, 액정 소자의 열화도가 추가로 감소될 수 있다. 상기 기록 기간들 (261, 262)의 각각의 끝에 인가된 상기 전압의 극성은 상기 유지 기간에서 유지될 극성이라는 것을 주의하자.

- [0055] 도 3a 및 도 3b에서의 액정 소자에 인가된 상기 전압은 도트 반전 구동, 소스선 반전 구동, 게이트선 반전 구동, 프레임 반전 구동 등에 따라 입력될 수 있다는 것을 주의하자.

- [0056] 정지 화상이 표시되지 않고 화소가 산화물 반도체층을 포함한 박막 트랜지스터를 사용하여 형성되는 경우에, 동화상은 저장 용량 소자 없이 표시될 수 있다는 것을 주의하자. 도 4a 및 도 4b는 저장 용량 소자가 형성되지 않는 화소의 구성의 평면도 및 단면도를 도시한다. 도 4a 및 도 4b에 도시된 구성은 도 1a 및 도 1b에서의 용량선이 생략되는 구조에 대응한다. 또한 도 4a의 평면도 및 도 4b의 단면도로부터 보여질 수 있는 바와 같이, 산화물 반도체층을 포함한 박막 트랜지스터를 사용하여, 상기 화소 전극(105)에 의해 점유된 영역, 즉 개구율은 증가될 수 있다. 게다가, 도 4b의 단면도로부터 보여질 수 있는 바와 같이, 산화물 반도체층을 포함한 박막 트랜지스터의 사용으로, 용량선이 제거될 수 있고, 상기 화소 전극(105)에 의해 점유된 영역은 확장될수 있으며, 그러므로 상기 개구율이 증가될 수 있다.

- [0057] 이 실시형태에서 상술된 구성을 가지고, 오프-상태 전류가 산화물 반도체를 포함한 박막 트랜지스터를 가진 화소에서 감소될 수 있다. 따라서, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장하고 정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다. 더욱이, 개구율의 증가에 의해, 고-화질 표시부를 가진 액정 표시 장치가 획득될 수 있다.

- [0058] 이 실시형태는 다른 실시형태들에 기술된 임의의 상기 구성들과 적절하게 결합하여 구현될 수 있다.

- [0059] (실시형태 2)

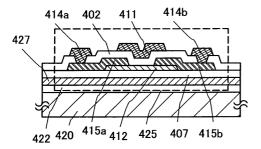

- [0060] 이 실시형태에서, 본 명세서에 기술된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 일 예가 기술될 것이다. 이 실시형태에서 기술된 박막 트랜지스터(410)는 실시형태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

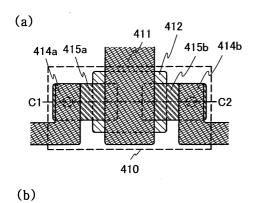

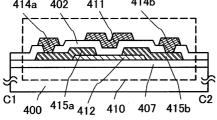

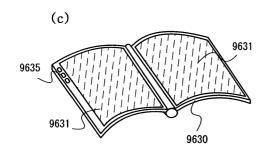

- [0061] 이 실시형태의 박막 트랜지스터 및 상기 박막 트랜지스터를 제작하기 위한 방법의 일 실시형태가 도 5a와 도 5b 및 도 6a 내지 도 6e를 사용하여 기술된다.

- [0062] 도 5a는 상기 박막 트랜지스터의 평면 구조의 일 예를 도시하며, 도 5b는 그 단면 구조의 일 예를 도시한다.

도 5a 및 도 5b에 도시된 상기 박막 트랜지스터(410)는 탑-게이트 박막 트랜지스터이다.

- [0063] 도 5a는 상기 탑-게이트 박막 트랜지스터(410)의 평면도이며, 도 5b는 도 5a에서의 선(C1-C2)에 따른 단면도 이다.

- [0064] 상기 박막 트랜지스터(410)는 절연 표면을 가진 기판(400) 위에, 절연층(407), 산화물 반도체층(412), 소스 및 드레인 전극층(415a, 415b), 게이트 절연층(402), 및 게이트 전극층(411)을 포함한다. 배선층들(414a, 414b)은 각각 그것에 전기적으로 접속될 상기 소스 및 드레인 전극층(415a, 415b)와 접촉하여 제공된다.

- [0065] 상기 박막 트랜지스터(410)는 단일-게이트 박막 트랜지스터로서 기술되며, 복수의 채널 형성 영역들을 포함한 멀티-게이트 박막 트랜지스터가 요구될 때 형성될 수 있다.

- [0066] 상기 기판(400) 위에 상기 박막 트랜지스터(410)를 제작하기 위한 프로세스가 도 6a 내지 도 6e를 참조하여 이하에 설명된다.

- [0067] 절연 표면을 가진 상기 기판(400)으로서 사용될 수 있는 기판에 대한 특별한 제한은 없지만, 상기 기판(400)은 적어도 나중에 수행될 열 처리를 견디기에 충분히 높은 내열성을 가질 필요가 있다.

- [0068] 상기 기판(400)으로서, 변형점이 730℃ 이상인 유리 기판이 나중에 수행될 상기 열 처리의 온도가 높을 때 사용될 수 있다. 상기 유리 기판의 재료로서, 예를 들면, 알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 또는 바륨 보로실리케이트 유리와 같은 유리 재료가 사용된다. 산화 붕소보다 더 많은 양의 산화 바륨 (BaO)을 포함함으로써, 보다 실질적으로 사용하는 내열 유리 기판이 형성될 수 있다는 것을 주의하자. 그러므로, B₂O₃보다 많은 BaO를 포함한 유리 기판이 사용되는 것이 바람직하다.

- [0069] 세라믹 기판, 석영 기판, 또는 사파이어 기판과 같은 절연체를 사용하여 형성된 기판이 상기 기판(400)으로서 상술된 유리 기판 대신에 사용될 수 있다는 것을 주의하자. 대안적으로, 결정화된 유리 기판 등이 사용될 수 있다. 또한 대안적으로, 플라스틱 기판 등이 사용될 수 있다.

- [0070] 먼저, 하지막으로서 기능하는 상기 절연층(407)이 절연 표면을 가진 상기 기판(400) 위에 형성된다. 산화 실리콘층, 산화질화 실리콘층, 산화 알루미늄층, 또는 산화질화 알루미늄층과 같은 산화물 절연층이 상기 산화물 반도체층과 접촉하는 상기 절연층(407)으로서 사용되는 것이 바람직하다. 상기 절연층(407)은 플라즈마CVD 방법, 스퍼터링 방법 등에 의해 형성될 수 있다. 상기 절연층(407)이 많은 양의 수소를 포함하는 것을 방지하기 위해 스퍼터링 방법에 의해 상기 절연층(407)을 형성하는 것이 바람직하다.

- [0071] 이 실시형태에서, 산화 실리콘층이 스퍼터링 방법에 의해 상기 절연층(407)으로서 형성된다. 상기 기판(400)은 처리실로 반송되고, 수소 및 수분이 제거된 고-순도 산소를 포함한 스퍼터링 가스가 상기 처리실로 도입되며, 타겟이 사용되어, 상기 산화 실리콘층이 상기 절연층(407)으로서 상기 기판(400)에 성막되도록 한다. 상기 기판(400)은 실온일 수 있거나 또는 가열될 수 있다.

- [0072] 예를 들면, 산화 실리콘막은 다음과 같이 형성된다: 석영(바람직하게는, 합성 석영)이 상기 타켓으로서 사용되고; 상기 기판 온도는 108℃이고; 상기 타켓과 상기 기판 간의 거리(T-S 거리)는 60 mm이고; 상기 압력은 0.4 Pa이고; 상기 고-주파수 전원은 1.5 kW이고; 상기 분위기는 산소 및 아르곤이며(산소 대 아르곤의 유량비는 25sccm:25sccm = 1:1이다); 및 RF 스퍼터링 방법이 사용된다. 이 실시형태에서 상기 산화 실리콘막의 두께는 100 nm이다. 상기 산화 실리콘막을 형성하기 위해 실리콘 타켓이 상기 석영(바람직하게는, 합성 석영) 대신에 사용될 수 있다. 스퍼터링 가스로서, 산소 또는 산소와 아르곤의 혼합 가스가 이 실시형태에서 사용된다.

- [0073] 상기 경우에, 상기 절연층(407)의 성막에 있어서 상기 처리실에서 잔여 수분을 제거하는 것이 바람직하다. 이 것은 상기 절연층(407)이 수소, 수산기, 또는 수분을 포함하는 것을 방지하기 위한 것이다.

- [0074] 상기 처리실로부터 잔여 수분을 제거하기 위해, 바람직하게는 흡착형 진공 펌프가 사용된다. 예를 들면, 바람 직하게는 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프(titanium sublimation pump)가 사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 크라이오 펌프를 사용하여 배기가 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H<sub>2</sub>0)과 같은 수소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 절연층(407)에 포함된 불순물들의 농도는 감소될 수 있다.

- [0075] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 절연층(407)의 성막을 위한 상기 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0076] 스퍼터링 방법의 예들은 고-주파수 전원이 스퍼터링 전원으로서 사용되는 RF 스퍼터링 방법, DC 스퍼터링 방법, 및 바이어스가 펄스 방식으로 인가되는 펄스 DC 스퍼터링 방법을 포함한다. 상기 RF 스퍼터링 방법은 절연막이 형성되는 경우에서 주로 사용되며 상기 DC 스퍼터링 방법은 금속막이 형성되는 경우에 주로 사용된다.

- [0077] 상이한 재료들로 형성되는 복수의 타켓들이 설정될 수 있는 다원-타켓 스퍼터링 장치가 또한 존재한다. 상기 다원-타켓 스퍼터링 장치를 가지고, 상이한 재료들의 막들이 동일한 처리실에 형성되도록 적충될 수 있거나, 또는 복수의 종류들의 재료들이 상기 동일한 처리실에서 방전에 의해 동시에 성막될 수 있다.

- [0078] 게다가, 상기 처리실 내부에 자석 기구(magnet system)가 제공되고, 마그네트론 스퍼터링 방법을 위해 사용되는 스퍼터링 장치, 또는 글로 방전(glow discharge) 없이 마이크로파들을 사용하여 생성된 플라즈마가 사용되는 ECR 스퍼터링 방법을 위해 사용된 스퍼터링 장치가 또한 존재한다.

- [0079] 또한, 스퍼터링 방법을 사용한 상기 성막 방법으로서, 타켓 물질 및 스퍼터링 가스 성분이 그것의 얇은 화합 막을 형성하기 위해 성막 동안 서로 화학적으로 반응되는 반응성 스퍼터링 방법, 또는 성막 동안 전압이 또한 기판에 인가되는 바이어스 스퍼터링 방법이 존재한다.

- [0080] 상기 절연층(407)은 적층 구조를 가질 수 있으며; 예를 들면, 질화 실리콘층, 질화산화 실리콘층, 질화 알루미늄층, 또는 질화산화 알루미늄층과 같은 질화물 절연층 및 상술된 산화물 절연층이 상기 기판(400) 위에 이러한 순서로 적층되는 적층 구조가 사용될 수 있다.

- [0081] 예를 들면, 수소 및 수분이 제거된 고-순도 질소를 포함한 스퍼터링 가스를 도입하고 실리콘 타켓을 사용함으로써 상기 산화 실리콘층 및 상기 기판(400) 사이에 질화 실리콘층이 형성된다. 상기 경우에, 상기 산화 실리콘층의 성막의 경우에서와 같이 상기 질화 실리콘층의 형성에 있어서 상기 처리실로부터 잔여 수분을 제거하는 것이 바람직하다.

- [0082] 상기 기판은 상기 질화 실리콘층의 성막시 가열될 수 있다.

- [0083] 상기 질화 실리콘층 및 상기 산화 실리콘층이 상기 절연층(407)을 형성하기 위해 적층되는 경우에, 상기 질화 실리콘층 및 상기 산화 실리콘층은 동일한 실리콘 타켓을 갖고 동일한 처리실에서 형성될 수 있다. 예를 들면, 먼저, 질소를 포함한 스퍼터링 가스가 도입되며 상기 처리실 내부에 위치된 실리콘 타켓이 상기 질화 실리콘층을 형성하기 위해 사용되며, 그 후 상기 스퍼터링 가스가 산소를 포함한 스퍼터링 가스로 전환되며, 동일한 실리콘 타켓이 상기 산화 실리콘층을 형성하기 위해 사용된다. 상기 질화 실리콘층 및 상기 산화 실리콘층은 대기에 노출하지 않고 연속적으로 형성될 수 있기 때문에, 수소 또는 수분과 같은 불순물이 상기 질화 실리콘층의 표면상에 흡착되는 것을 방지될 수 있다.

- [0084] 다음으로, 산화물 반도체막이 상기 절연층(407) 위에 형성된다.

- [0085] 상기 산화물 반도체막이 수소, 수산기, 및 수분과 같은 불순물들을 가능한 한 많이 포함하지 않도록 하기 위해, 상기 기판(400) 상에 흡착된 수소 또는 수분과 같은 불순물이 제거되도록 상기 성막 전에 상기 스퍼터링장치의 예열실에서 상기 절연층(407)이 제공된 상기 기판(400)을 예열하고, 배기를 수행하는 것이바람직하다. 상기 예열실에 제공된 배기 수단으로서, 크라이오펌프가 바람직하다. 이러한 예열 단계가 반드시수행되는 것은 아니다.

- [0086] 상기 산화물 반도체막이 스퍼터링 방법에 의해 형성되기 전에, 상기 절연층(407)의 표면상의 먼지가 제거되도록 아르곤 가스가 도입되고 플라즈마가 생성되는 역 스퍼터링을 수행하는 것이 바람직하다는 것을 주의하자. 상기 역 스퍼터링은 타켓 측으로 전압을 인가하지 않고 상기 기판의 부근에 플라즈마를 생성하기 위해 아르곤 분위기에서 고-주파수 전원으로 전압이 기판 측에 인가되어, 표면이 개질되도록 하는 방법이다. 상기 아르곤 분위기 대신에, 질소 분위기, 헬륨 분위기, 산소 분위기 등이 사용될 수 있다.

- [0087] 상기 산화물 반도체막은 상기 스퍼터링 방법에 의해 형성된다. 상기 산화물 반도체막은 In-Ga-Zn-O-계 산화물 반도체막, In-Sn-Zn-O-계 산화물 반도체막, In-Al-Zn-O-계 산화물 반도체막, Sn-Ga-Zn-O-계 산화물 반도체막, Al-Ga-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, In-Zn-O-계 산화물 반도체막, Sn-Zn-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막, 또는 Zn-O-계 산화물 반도체막을 사용하여 형성된다. 이 실시형태에서, 상기 산화물 반도체막은 In-Ga-Zn-O-계 산화물 반도체 타겟을 사용하여 스퍼터링 방법에 의해 형성된다. 구체적으로, In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO = 1:1:1 [분자%] 의 조성비(즉, In:Ga:Zn = 1:1:0.5 [원자%])를 가진 타겟이 사용된다. 대안적으로, In:Ga:Zn = 1:1:1 [원자%] 또는 In:Ga:Zn = 1:1:2 [원자%]의 조성비를 가진 타겟이 사용될 수 있다. 이 실시형태에서, 상기 산화물 반도

체 타겟의 충전율(filling rate)은 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하이다. 높은 충전율을 가진 상기 산화물 반도체 타겟의 사용으로, 상기 성막된 산화물 반도체막은 높은 밀도를 가진다. 상기 스퍼터링을 위한 분위기는 희가스(대표적으로, 아르곤)의 분위기, 산소의 분위기, 또는 희가스와 산소의 혼합 분위기일 수 있다. 상기 타겟은 2 wt% 이상 및 10 wt% 이하의 SiO<sub>9</sub>를 포함할 수 있다.

- [0088] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 산화물 반도체막의 성막을 위한 상기 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0089] 상기 산화물 반도체막은 다음과 같이 상기 기판(400) 위에 형성된다: 상기 기판은 감소된 압력을 갖는 상기 처리실에 유지되고, 상기 처리실에서의 잔여 수분은 제거되고, 수소 및 수분이 제거된 스퍼터링 가스가 도입되며, 상술된 타겟이 사용된다. 상기 처리실에서 상기 잔여 수분을 제거하기 위해, 흡착형 진공 펌프를 사용하는 것이 바람직하다. 예를 들면, 바람직하게는 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프가사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 크라이오펌프를 사용하여 배기가 수행되는 상기 성막실에서, 수소 분자, 물(H<sub>2</sub>O)과 같은 수소 원자를 포함한 화합물, 탄소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 반도체막에 포함된 불순물들의 농도는 감소될 수 있다. 상기 기판은 상기 산화물 반도체막의 성막시 가열될 수 있다.

- [0090] 상기 성막 조건의 일 예로서, 다음 조건이 이용된다: 상기 기판의 온도는 실온이고; 상기 기판과 상기 타켓 간의 거리는 110 mm이고, 상기 압력은 0.4 Pa이고, 상기 직류(DC) 전원은 0.5 kW이며, 상기 분위기는 산소 및 아르곤(산소 대 아르곤의 유량비는 15 sccm:30 sccm이다)이다. 먼지가 감소될 수 있고 막 두께가 균일할 수 있기 때문에 펄스 직류(DC) 전원이 사용되는 것이 바람직하다. 상기 산화물 반도체막은 2 nm 내지 200 nm, 바람직하게는 5 nm 내지 30 nm의 두께를 갖는다. 상기 산화물 반도체막의 적절한 두께는 그것의 재료에 의존하여 변화하며, 그러므로 상기 두께는 상기 재료에 의존하여 적절하게 결정될 수 있다는 것을 주의하자.

- [0091] 다음으로, 상기 산화물 반도체막은 제 1 포토리소그래피 단계에 의해 섬-형상 산화물 반도체층(412)으로 가공된다(도 6a 참조). 상기 섬-형상 산화물 반도체층(412)을 형성하기 위한 레지스트 마스크는 잉크젯 방법을 사용하여 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서 제작 비용이 감소될 수 있다.

- [0092] 상기 산화물 반도체막의 에칭은 드라이 에칭, 웨트 에칭, 또는 드라이 에칭 및 웨트 에칭 둘 모두일 수 있다는 것을 주의하자.

- [0093] 상기 드라이 에칭을 위한 에칭 가스로서, 바람직하게는 염소를 포함한 가스(염소(Cl<sub>2</sub>), 염화 붕소(BCl<sub>3</sub>), 염화 규소(SiCl<sub>4</sub>), 또는 사염화탄소(CCl<sub>4</sub>)와 같은 염소-계 가스)가 사용된다.

- [0094] 대안적으로, 불소를 포함한 가스(사불화 탄소(CF<sub>4</sub>), 불화 유황(SF<sub>6</sub>), 불화 질소(NF<sub>3</sub>), 또는 트리플루오로메탄 (CHF<sub>3</sub>)과 같은 불소-계 가스); 브롬화 수소(HBr); 산소(O<sub>2</sub>); 헬륨(He) 또는 아르곤(Ar)과 같은 희가스가 부가 되는 가스들 중 임의의 것 등이 사용될 수 있다.

- [0095] 상기 드라이 에칭 방법으로서, 평행 평판 RIE(반응성 이온 에칭) 방법 또는 ICP(유도 결합 플라즈마) 에칭 방법이 사용될 수 있다. 상기 층을 원하는 형상으로 에칭하기 위해, 상기 에칭 조건들(코일-형상 전극에 인가된 전력의 양, 기판 측상의 전극에 인가된 전력의 양, 상기 기판측 상에 상기 전극의 온도 등)이 적절하게 조정된다.

- [0096] 웨트 에칭을 위해 사용된 에천트로서, 인산, 아세트산, 및 질산 등의 혼합액, 수산화암모늄/과산화수소 혼합물(31 w% 과산화수소수 : 28 wt% 암모니아수 : 물 = 5:2:2) 등이 사용될 수 있다. 대안적으로, ITO-07N(칸토케미칼 코., 인크.(Kanto Chemical Co., Inc.)에 의해 제작된)이 사용될 수 있다.

- [0097] 상기 웨트 에칭 후, 상기 에천트는 세정에 의해 상기 에칭 오프된 재료와 함께 제거된다. 상기 제거된 재료를 포함한 상기 에천트의 폐액은 정제될 수 있으며, 상기 폐액에 포함된 상기 재료는 재사용될 수 있다. 상기 에칭 후 상기 폐액으로부터 상기 산화물 반도체에 포함된 인듐과 같은 재료를 수집하고 재사용함으로써 상기 리소스들이 효율적으로 사용될 수 있고 비용은 감소될 수 있다.

- [0098] 상기 에칭 조건들(에천트, 에칭 시간, 및 온도와 같은)은 재료가 원하는 형상으로 에칭될 수 있도록 상기 재료에 의존하여 적절하게 조정된다.

- [0099] 이 실시형태에서, 상기 산화물 반도체막은 인산, 아세트산, 및 질산을 혼합함으로써 획득된 용액을 사용하여

웨트 에칭 방법에 의해 상기 섬-형상 산화물 반도체층(412)으로 가공된다.

- [0100] 이 실시형태에서, 제 1 열 처리가 상기 산화물 반도체층(412)에 수행된다. 상기 제 1 열 처리의 온도는 400℃ 이상 또는 750℃ 이하이며, 상기 기판(400)의 변형점이 750℃ 이하일 때 400℃ 이상, 상기 기판(400)의 상기 변형점 미만이다. 이 실시형태에서, 상기 기판은 열 처리 장치의 한 종류인 전기로에 넣어지며, 열 처리는 질소 분위기에서 1시간 동안 450℃로 상기 산화물 반도체층에 수행되며, 대기에 노출하지 않고 그 후 상기 온도는 실온으로 감소되고 물 또는 수소가 상기 산화물 반도체층으로 혼입되는 것이 방지되며, 따라서 산화물 반도체층이 획득된다. 상기 산화물 반도체층(412)은 상기 제 1 열 처리에 의해 탈수화될 수 있거나 또는 탈수소화될 수 있다.

- [0101] 상기 열 처리 장치는 전기로에 제한되지 않고, 저항 가열기 등과 같은 가열기로부터 열 전도 또는 열 복사에 의해 피처리물을 가열하는 장치가 제공될 수 있다. 예를 들면, GRTA(gas rapid thermal annealing) 장치 또는 LRTA(lamp rapid thermal annealing) 장치와 같은 RTA(rapid thermal annealing) 장치가 사용될 수 있다. LRTA 장치는 할로겐 램프, 금속 할라이드 램프, 크세논 아크 램프, 탄소 아크 램프, 고압 나트륨 램프, 또는 고압 수은 램프와 같은 램프로부터 방출된 광(전자기파)의 복사에 의해 피처리물을 가열하기 위한 장치이다. GRTA 장치는 고-온 가스를 사용한 열 처리를 위한 장치이다. 상기 가스로서, 질소 또는 아르곤과 같은 희가스와 같이, 열 처리에 의해 피처리물과 반응하지 않는 불활성 가스가 사용된다.

- [0102] 예를 들면, 상기 제 1 열 처리로서, GRTA가 다음과 같이 수행될 수 있다: 상기 기판은 650℃ 내지 700℃의 고 온으로 가열된 불활성 가스로 이송되어 수 분 동안 가열되고, 이송되어 고온으로 가열된 상기 불활성 가스 밖 으로 꺼내어진다. GRTA는 단시간 동안 고-온 열 처리를 가능하게 한다.

- [0103] 상기 제 1 열 처리에서, 물, 수소 등은 질소 또는 헬륨, 네온, 또는 아르곤 과 같은 희가스에 포함되지 않는 것이 바람직하다. 상기 열 처리 장치로 도입되는 질소 또는 헬륨, 네온, 또는 아르곤과 같은 희가스는 6N(99.9999%) 이상, 보다 바람직하게는, 7N(99.99999%) 이상(즉, 불순물들의 농도가 1ppm 이하, 보다 바람직하게는 0.1ppm 이하이다)의 순도를 갖는 것이 바람직하다.

- [0104] 또한, 상기 제 1 열 처리의 조건들 또는 상기 산화물 반도체층의 재료에 의존하여, 상기 산화물 반도체층 (412)은 미결정 막 또는 다결정 막이 되도록 결정화될 수 있다. 예를 들면, 상기 산화물 반도체층은 결정화율이 90% 이상, 또는 80% 이상인 미결정 산화물 반도체막이 되도록 결정화될 수 있다. 또한, 상기 제 1 열 처리의 조건들 또는 상기 산화물 반도체층의 재료에 의존하여, 상기 산화물 반도체층(412)은 결정 성분들을 포함하지 않는 비정질 산화물 반도체막일 수 있다. 상기 산화물 반도체층은 미결정 부분(1 mm 내지 20 mm, 대표적으로 2 mm 내지 4 mm의 입경을 갖는)이 비정질 산화물 반도체에 혼합되는 산화물 반도체막이 될 수 있다.

- [0105] 상기 산화물 반도체층의 상기 제 1 열 처리는 또한 상기 섬-형상 산화물 반도체층(412)으로 가공되기 전에 상기 산화물 반도체막에 수행될 수 있다. 상기 경우에서, 상기 기판은 상기 제 1 열 처리 후 상기 열 처리 장치로부터 제거되며, 그 후 포토리소그래피 단계가 수행된다.

- [0106] 상기 산화물 반도체층의 탈수화 또는 탈수소화를 위한 상기 열 처리는 상기 산화물 반도체층(412)의 형성 직후 수행되는 상기 예가 상술되었다. 그러나, 탈수화 또는 탈수소화를 위한 상기 열 처리는 그것이 상기 산화물 반도체층의 성막 후 수행되는 한 소스 전극 및 드레인 전극이 상기 산화물 반도체층 에 적층된 후 또는 게이트 절연층이 소스 전극 및 드레인 전극 위에 형성된 후 수행될 수 있다.

- [0107] 다음으로, 도전막이 상기 절연층(407) 및 상기 산화물 반도체층(412) 위에 형성된다. 상기 도전막은 스퍼터링 방법 또는 진공 성막 방법에 의해 형성될 수 있다. 상기 도전막의 재료로서, Al, Cr, Cu, Ta, Ti, Mo, 및 W로 부터 선택된 하나의 원소, 그것의 성분으로서 상기 원소들 중 임의의 것을 포함한 합금, 상기 원소들 중 임의의 것을 결합하여 포함한 합금 막 등이 제공될 수 있다. 또한, 망간, 마그네슘, 지르코늄, 베릴륨, 및 이트륨으로부터 선택된 하나 이상의 재료들이 사용될 수 있다. 또한, 상기 도전막은 단층 구조 또는 두 개 이상의층들의 적층 구조를 가질 수 있다. 예를 들면, 실리콘을 포함한 알루미늄막의 단층 구조, 티타늄 막이 알루미늄막 위에 적층되는 2-층 구조, 티타늄 막, 알루미늄막, 및 티타늄 막이 순서대로 적층되는 3-층 구조 등이제공될 수 있다. 대안적으로, 알루미늄(Al) 및 티타늄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 및 스칸듐(Sc)으로부터 선택된 하나 이상의 원소들을 포함하는 막, 합금 막, 또는 질화막이 사용될 수 있다. 이 실시형태에서, 150 nm의 두께를 가진 티타늄 막이 스퍼터링 방법에 의해 상기 도전막으로서형성된다.

- [0108] 다음으로, 레지스트 마스크가 제 2 포토리소그래피 단계에 의해 상기 도전막 위에 형성된다. 상기 레지스트

마스크는 잉크젯 방법을 사용하여 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토 마스크를 필요로 하지 않으며, 따라서 제작 비용이 감소될 수 있다. 그 후, 선택적 에칭이 수행되며, 따라서 상기 소스 및 드레인 전극층들(415a, 415b)이 형성되고, 그 후 상기 레지스트 마스크가 제거된다(도 6b 참 조). 그 위에 적층된 게이트 절연층을 갖는 커버리지가 향상되기 때문에 상기 소스 및 드레인 전극층들의 각각의 단부는 테이퍼된 형상을 갖는 것이 바람직하다.

- [0109] 각각의 재료 및 에칭 조건들은 상기 산화물 반도체층(412)이 상기 도전막의 에칭에 의해 제거되지 않고 상기 산화물 반도체층(412) 아래의 상기 절연층(407)이 노출되지 않도록 적절히 조정된다는 것을 주의하자.

- [0110] 이 실시형태에서, 상기 Ti 막이 상기 도전막으로서 사용되며 상기 In-Ga-Zn-O-계 산화물 반도체가 상기 산화물 반도체층(412)을 위해 사용되기 때문에, 암모늄 과산화수소수(암모니아, 물, 및 과산화수소수의 혼합액)가 에천트로서 사용된다.

- [0111] 상기 제 2 포토리소그래피 단계에서, 몇몇 경우들에서, 상기 산화물 반도체충(412)의 일부가 에칭되며, 그에 의해 홈(오목한 부분)을 가진 산화물 반도체충이 형성될 수 있다.

- [0112] 상기 제 2 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 노광이 자외선 광, KrF 레이저 광, 또는 ArF 레이저 광을 사용하여 수행될 수 있다. 형성될 박막 트랜지스터의 채널 길이(L)는 상기 산화물 반도체층 (412) 위에서 서로에 인접하는, 상기 소스 전극층의 하단 및 상기 드레인 전극층의 하단 사이의 거리에 의해 결정된다. 노광이 25 nm 미만의 채널 길이(L)에 대해 수행되는 경우에, 상기 제 2 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 상기 노광은 수 나노미터 내지 수십 나노미터의 매우 짧은 파장을 가진 초자 외선 광을 사용하여 수행된다. 초자외선 광에 의한 상기 노광에서, 상기 해상도는 높으며 초점 심도는 크다. 따라서 상기 박막 트랜지스터의 상기 채널 길이(L)는 10 nm 내지 1000 nm가 될 수 있고, 회로의 동작 속도는 증가될 수 있으며, 낮은 전력 소비가 매우 작은 오프-상태 전류에 의해 달성될 수 있다.

- [0113] 다음으로, 상기 게이트 절연층(402)이 상기 절연층(407), 상기 산화물 반도체층(412), 및 상기 소스 및 드레인 전극층들(415a, 415b) 위에 형성된다(도 6c 참조).

- [0114] 상기 게이트 절연층(402)이 플라즈마 CVD 방법, 스퍼터링 방법 등에 의해 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 및 산화 알루미늄층 중 하나 이상을 사용한 단층 구조 또는 적층 구조를 갖고 형성될 수 있다. 상기 게이트 절연층(402)이 많은 양의 수소를 포함하는 것을 방지하기 위해, 스퍼터링 방법에 의해 상기 게이트 절연층(402)을 형성하는 것이 바람직하다. 스퍼터링 방법에 의해 산화 실리콘막을 형성하는 경우에, 실리콘 타켓 또는 석영 타켓이 타켓으로서 사용되며, 산소 또는 산소와 아르곤의 혼합가스가 스퍼터링 가스로서 사용된다. 이 실시형태에서, 100-nm-두께의 산화 실리콘층이 다음과 같이형성된다: 상기 압력은 0.4 Pa이고; 상기 고-주파수 전원은 1.5 kW이고, 상기 분위기는 산소 및 아르곤(산소대 아르곤의 유량비는 25 sccm: 25 sccm = 1:1이다)이며; RF 스퍼터링 방법이 사용된다.

- [0115] 상기 게이트 절연층(402)은 산화 실리콘층 및 질화 실리콘층이 상기 기판 위에 이러한 순서로 적충되는 구조를 가질 수 있다. 70 nm 내지 400 nm, 예를 들면, 100 nm의 두께를 가진 게이트 절연층이 제 1 게이트 절연층으로서 5 nm 내지 300 nm의 두께를 가진 산화 실리콘층(SiO<sub>x</sub>(x>0))이 스퍼터링 방법에 의해 형성되는 방식으로 형성될 수 있으며, 그 후 50 nm 내지 200 nm의 두께를 가진 질화 실리콘층(SiN<sub>y</sub>(y>0))이 상기 제 1 게이트 절연층 위에 제 2 게이트 절연층으로서 적충된다.

- [0116] 다음으로, 레지스트 마스크가 제 3 포토리소그래피 단계에 의해 형성되며, 선택적 에칭이 상기 게이트 절연층 (402)의 일부들을 제거하기 위해 수행되어, 상기 소스 및 드레인 전극층들(415a, 415b)에 도달하는 개구들 (421a, 421b)이 형성되도록 한다(도 6d 참조).

- [0117] 다음으로, 도전막이 상기 게이트 절연층(402) 및 상기 개구들(421a, 421b) 위에 형성된다. 이 실시형태에서, 150 nm의 두께를 가진 티타늄 막이 스퍼터링 방법에 의해 형성된다. 그 후, 레지스트 마스크가 제 4 포토리소 그래피 단계에 의해 도전막 위에 형성되며, 상기 도전막이 상기 레지스트 마스크를 사용하여 선택적으로 에칭되어, 상기 게이트 전극층(411) 및 상기 배선층들(414a, 414b)이 형성되도록 한다. 상기 레지스트 마스크는 잉크젯 방법에 의해 형성될 수 있다는 것을 주의하자. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서 제작 비용이 감소될 수 있다.

- [0118] 상기 게이트 전극충(411) 및 상기 배선충들(414a, 414b)은 각각 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료, 또는 그것의 주요 성분으로서 이들 재료들 중 임의의

것을 포함하는 합금 재료를 사용하여 단층 또는 적층 구조를 갖도록 형성될 수 있다.

- [0119] 예를 들면, 상기 게이트 전극층(411) 및 상기 배선층들(414a, 414b)의 각각의 2-층 구조로서, 다음 구조들 중임의의 것이 바람직하다: 알루미늄층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 질화 티타늄층 또는 질화 탄탈층의 2-층 구조, 및 질화 티타늄층 및 몰리브덴층의 2-층 구조. 3-층 구조로서, 텅스텐층 또는 질화 텅스텐층, 알루미늄 및 실리콘의합금 또는 알루미늄 및 티타늄의합금의 층, 및 질화 티타늄층 또는 티타늄층의 적층이 바람직하다. 상기 게이트 전극층은 투광성 도전막을 사용하여형성될 수 있다. 상기 투광성 도전막의 재료의일 예로서, 투광성도전성 산화물이 제공될 수 있다.

- [0120] 다음으로, 제 2 열 처리(바람직하게는 200℃ 내지 400℃의 온도로, 예를 들면 250℃ 내지 350℃의 온도로)가 불활성 가스 분위기 또는 산소 가스 분위기에서 수행된다. 이 실시형태에서, 상기 제 2 열 처리는 질소 분위기에서 1시간 동안 250℃로 수행된다. 상기 제 2 열 처리는 보호 절연층 또는 평탄화 절연층이 상기 박막 트랜지스터(410) 위에 형성된 후 수행될 수 있다.

- [0121] 더욱이, 열 처리는 대기 중에서 1시간 내지 30시간 동안 100℃ 내지 200℃의 온도로 수행될 수 있다. 이러한 열 처리는 일정한 가열 온도로 수행될 수 있다. 대안적으로, 상기 가열 온도에서의 다음의 변화가 반복적으로 복수 회 행해질 수 있다: 상기 가열 온도는 실온에서 100℃ 내지 200℃의 온도로 증가되며 그 후 실온으로 감소된다. 이러한 열 처리는 상기 산화물 절연층의 형성 전에 감소된 압력 하에서 수행될 수 있다. 상기 감소된 압력 하에서, 상기 열 처리 시간은 단축될 수 있다.

- [0122] 상술된 프로세스를 통해, 수소, 수분, 수소화물 및 수산화물의 농도가 감소되는 상기 산화물 반도체층(412)을 포함한 상기 박막 트랜지스터(410)가 형성될 수 있다(도 6e 참조). 상기 박막 트랜지스터(410)는 실시형태 1에 기술된 상기 박막 트랜지스터(106)로서 사용될 수 있다.

- [0123] 보호 절연층 또는 평탄화를 위한 평탄화 절연층이 상기 박막 트랜지스터(410) 위에 제공될 수 있다. 예를 들면, 상기 보호 절연층은 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 및 산화 알루미늄층 중 하나 이상을 사용한 단층 구조 또는 적층 구조를 갖고 형성될 수 있다.

- [0124] 상기 평탄화 절연층은 폴리이미드, 아크릴, 벤조사이클로부텐, 폴리아미드, 또는 에폭시와 같은 내열성 유기 재료를 사용하여 형성될 수 있다. 이러한 유기 재료들 외에, 저-유전 상수 재료(low-k 재료), 실록산-계수지, PSG(포스포실리케이트 유리), BPSG(보로포스포실리케이트 유리) 등을 사용하는 것이 가능하다. 상기 평탄화 절연층은 이들 재료들을 사용하여 형성된 복수의 절연막들을 적층함으로써 형성될 수 있다.

- [0125] 상기 실록산-계 수지는 출발 재료로서 실록산-계 재료를 사용하여 형성된 Si-0-Si 결합을 포함한 수지에 대응한다는 것을 주의하자. 상기 실록산-계 수지는 치환기로서 유기기(예로서, 알킬기 또는 아릴기) 또는 플루오로기를 포함할 수 있다. 상기 유기기는 플루오로기를 포함할 수 있다.

- [0126] 상기 평탄화 절연층을 형성하기 위한 상기 방법에 대한 특별한 제한은 없다. 상기 평탄화 절연층은 스퍼터링 방법, SOG 방법, 스핀 코팅 방법, 디핑 방법, 스프레이 코팅 방법, 또는 액적 토출 방법(예로서, 잉크-젯 방법, 화면 인쇄 또는 오프셋 인쇄)과 같은 방법에 의해, 또는 닥터 나이프, 롤 코터, 커튼 코터, 또는 나이프 코터와 같은 도구의 사용으로 그것의 재료에 의존하여 형성될 수 있다.

- [0127] 상술된 바와 같이 상기 산화물 반도체막의 성막시 반응성 분위기에서 잔여 수분을 제거함으로써, 상기 산화물 반도체막에서의 수소 및 수소화물의 농도는 감소될 수 있다. 따라서, 상기 산화물 반도체막은 안정화될 수 있 다.

- [0128] 상기 산화물 반도체층을 포함하고 상술된 바와 같이 제작되는 상기 박막 트랜지스터를 사용함으로써, 액정 표시 장치의 표시부의 복수의 화소들의 각각에서, 상기 화소로부터의 누설 전류가 감소될 수 있다. 따라서, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장하고 정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다.

- [0129] 이 실시형태는 다른 실시형태들에 기술된 임의의 상기 구성들과 적절하게 결합하여 구현될 수 있다.

- [0130] (실시형태 3)

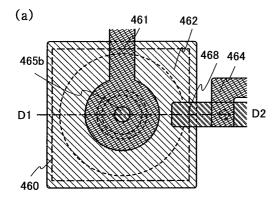

- [0131] 이 실시형태에서, 본 명세서에 개시된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 또 다른 예가 기술될 것이다. 실시형태 2는 실시형태 2와 동일한 부분들 및 그것과 유사한 기능들을 가진 부분들 및 단계들을 위해 참조될 수 있다는 것을 주의하자. 또한, 상기 동일한 부분들에 대한 상세한 설명은 생략된다. 이 실시형

태에서 기술된 박막 트랜지스터(460)는 실시형태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

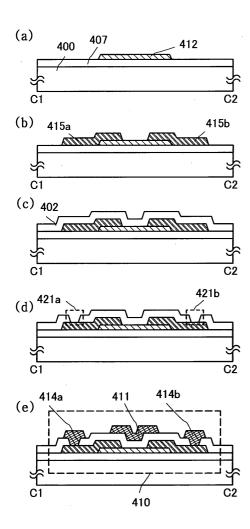

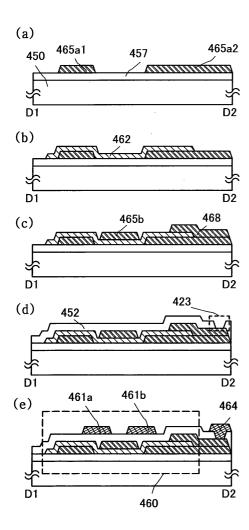

- [0132] 이 실시형태의 박막 트랜지스터 및 상기 박막 트랜지스터를 제작하기 위한 방법의 일 실시형태가 도 7a와 도 7b 및 도 8a 내지 도 8e를 사용하여 기술된다.

- [0133] 도 7a는 상기 박막 트랜지스터의 평면 구조의 일 예를 도시하며, 도 7b는 그것의 단면 구조의 일 예를 도시한다. 도 7a 및 도 7b에 도시된 상기 박막 트랜지스터(460)는 탑-게이트 박막 트랜지스터이다.

- [0134] 도 7a는 상기 탑-게이트 박막 트랜지스터(460)의 평면도이며 도 7b는 도 7a에서의 선(D1-D2)에 따른 단면도이다.

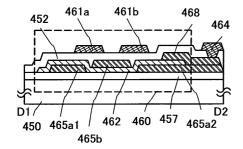

- [0135] 상기 박막 트랜지스터(460)는 절연 표면을 가진 기판(450) 위에, 절연층(457), 소스 또는 드레인 전극층 (465a(465a1, 465a2)), 산화물 반도체층(462), 소스 또는 드레인 전극층(465b), 배선층(468), 게이트 절연층 (452), 및 게이트 전극층(461(461a, 461b))을 포함한다. 상기 소스 또는 드레인 전극층(465a(465a1, 465a2))은 상기 배선층(468)을 통해 배선층(464)에 전기적으로 접속된다. 또한, 비록 도시되지는 않았지만, 상기 소스 또는 드레인 전극층(465b)이 또한 상기 게이트 절연층(452)에 형성된 개구에서 상기 배선층에 전기적으로 접속된다.

- [0136] 상기 기판(450) 위에 상기 박막 트랜지스터(460)를 제작하기 위한 프로세스가 도 8a 내지 도 8e를 참조하여 이하에 기술된다.

- [0137] 먼저, 하지막으로서 기능하는 상기 절연층(457)이 절연 표면을 가진 상기 기판(450) 위에 형성된다.

- [0138] 이 실시형태에서, 산화 실리콘층은 스퍼터링 방법에 의해 상기 절연층(457)으로서 형성된다. 상기 기판(450)은 처리실로 반송되고, 수소 및 수분이 제거된 고-순도 산소를 포함한 스퍼터링 가스가 상기 처리실로 도입되며, 실리콘 타겟 또는 석영(바람직하게는, 합성 석영)이 사용되어, 상기 산화 실리콘층이 상기 절연층(457)으로서 상기 기판(450)에 성막된다. 스퍼터링 가스로서, 산소 또는 산소와 아르곤의 혼합 가스가 이 실시형태에 사용된다.

- [0139] 예를 들면, 산화 실리콘막은 이 실시형태에서 다음과 같이 형성된다: 6N의 순도를 가진 석영(바람직하게는, 합성 석영)이 상기 타켓으로서 사용되고; 상기 기판 온도는 108℃이고; 상기 타켓과 상기 기판 간의 거리(T-S 거리)는 60mm이고; 상기 기압은 0.4 Pa이고; 상기 고-주파수 전원은 1.5 kW이고; 상기 분위기는 산소 및 아르곤(산소 대 아르곤의 유량비는 25 sccm:25 sccm = 1:1이다)이며; RF 스퍼터링 방법이 사용된다. 상기 산화 실리콘막의 두께는 이 실시형태에서 100mm이다. 실리콘 타켓이 상기 산화 실리콘막을 형성하기 위해 상기 석영 (바람직하게는, 합성 석영) 대신에 사용될 수 있다.

- [0140] 상기 경우에, 상기 절연층(457)의 성막에 있어서 상기 처리실에서의 잔여 수분을 제거하는 것이 바람직하다. 이것은 상기 절연층(457)이 수소, 수산기, 또는 수분을 포함하는 것을 방지하기 위한 것이다. 배기가 크라이 오펌프를 사용하여 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H<sub>2</sub>0)과 같은 수소 원자를 포함하는 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 절연층(457)에 포함된 불순물들의 농도는 감소될 수 있다.

- [0141] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 절연층(457)의 성막을 위한 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0142] 상기 절연충(457)은 적충 구조를 가질 수 있으며; 예를 들면, 질화 실리콘충, 질화산화 실리콘충, 질화 알루미늄충, 또는 질화산화 알루미늄충과 같은 질화물 절연충 및 상술된 산화물 절연충이 상기 기판(450) 위에 이러한 순서로 적충되는 적충 구조가 사용될 수 있다.

- [0143] 예를 들면, 질화 실리콘층이 수소 및 수분이 제거된 고-순도 질소를 포함하는 스퍼터링 가스를 도입하고 실리 콘 타겟을 사용함으로써 상기 산화 실리콘층 및 상기 기판(450) 사이에 형성된다. 상기 경우에, 상기 산화 실리콘층의 성막의 경우와 같이 상기 질화 실리콘층의 형성에 있어서 상기 처리실에서 잔여 수분을 제거하는 것이 또한 바람직하다.

- [0144] 다음으로, 도전막이 상기 절연층(457) 위에 형성된다. 상기 도전막의 재료로서, Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 하나의 원소, 그것의 성분으로서 이들 원소들 중 임의의 것을 포함한 합금, 이들 원소들 중 임의의 것을 결합하여 포함한 합금 막 등이 제공될 수 있다. 또한, 망간, 마그네슘, 지르코늄, 베릴륨, 및 이트륨으로부터 선택된 하나 이상의 재료들이 사용될 수 있다. 또한, 상기 도전막은 단층 구조 또는 두 개 이상

의 층들의 적충 구조를 가질 수 있다. 예를 들면, 실리콘을 포함한 알루미늄막의 단충 구조, 티타늄 막이 알루미늄막 위에 적충되는 2-층 구조, 티타늄 막, 알루미늄막, 및 티타늄 막이 순서대로 적충되는 3-층 구조 등이 제공될 수 있다. 대안적으로, 알루미늄(Al) 및 티타늄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 및 스칸듐(Sc)으로부터 선택된 하나 또는 복수의 원소들을 포함하는 막, 합금 막, 또는 질화막이 사용될 수 있다. 이 실시형태에서, 150 mm의 두께를 가진 티타늄 막이 스퍼터링 방법에 의해 상기도전막으로서 형성된다. 다음으로, 레지스트 마스크가 제 1 포토리소그래피 단계에 의해 상기도전막 위에 형성되며, 상기 소스 또는 드레인 전극층들(465a1, 465a2)이 선택적 에칭에 의해 형성되고, 그 후, 상기 레지스트 마스크가 제거된다(도 8a 참조). 단면도에서 절개된 것으로 도시되는, 상기 소스 또는 드레인 전극층들(465a1, 465a2)은 하나의 연속막이다. 상기 소스 또는 드레인 전극층들의 각각의 단부는 그 위에 적충된 게이트 절연층으로 커버리지가 개선되기 때문에 테이퍼된 형성을 갖는 것이 바람직하다.

- [0145] 다음으로, 2nm 내지 200nm의 두께를 갖는 산화물 반도체막이 형성된다. 상기 산화물 반도체막의 적절한 두께는 그것의 재료에 의존하여 변화하며; 그러므로, 상기 두께는 상기 재료에 의존하여 적절하게 결정될 수 있다는 것을 주의하자. 이 실시형태에서, 상기 산화물 반도체막은 In-Ga-Zn-O-계 산화물 반도체 타겟을 사용하여스퍼터링 방법에 의해 형성된다.

- [0146] 상기 산화물 반도체막은 다음과 같이 상기 기판(450) 위에 형성된다: 상기 기판은 감소된 압력을 가진 처리실에 유지되고, 상기 처리실에서의 잔여 수분은 제거되고, 수소 및 수분이 제거된 스퍼터링 가스가 도입되며, 타겟이 사용된다. 상기 처리실에서의 잔여 수분을 제거하기 위해, 흡착형 진공 펌프를 사용하는 것이 바람직하다. 예를 들면, 바람직하게는, 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프가 사용된다. 배기수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 배기가 크라이오펌프를 사용하여 수행되는 상기 성막실에서, 수소 분자, 물(H20)과 같은 수소 원자를 포함한 화합물, 탄소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 반도체막에 포함된 불순물들의 농도는 감소될수 있다. 상기 기판은 상기 산화물 반도체막의 성막시 가열될 수 있다.

- [0147] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 산화물 반도체막의 성막을 위한 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0148] 상기 성막 조건의 일 예로서, 다음의 조건이 이용된다: 상기 기판의 온도는 실온이고; 상기 기판과 상기 타켓 간의 거리는 110 mm이고; 상기 압력은 0.4 Pa이고; 상기 직류(DC) 전원은 0.5 kW이며; 상기 분위기는 산소 및 아르곤(산소 대 아르곤의 유량비는 15 sccm:30 sccm이다)이다.

- [0149] 다음으로, 상기 산화물 반도체막은 제 2 포토리소그래피 단계에 의해 상기 섬-형상 산화물 반도체층(462)으로 가공된다(도 8b 참조). 이 실시형태에서, 상기 산화물 반도체막은 인산, 아세트산, 및 질산을 혼합함으로써 획득된 용액을 사용한 웨트 에칭 방법에 의해 상기 섬-형상 산화물 반도체층(462)으로 가공된다.

- [0150] 이 실시형태에서, 제 1 열 처리는 상기 산화물 반도체층(462)에 수행된다. 상기 제 1 열 처리의 온도는 400℃ 이상 750℃ 이하, 상기 기판(450)의 변형점이 750℃ 이하일 때 400℃ 이상 상기 기판(450)의 상기 변형점 미만이다. 이 실시형태에서, 상기 기판은 열 처리 장치의 한 종류인 전기로에 넣어지며 열 처리는 질소 분위기에서 1시간 동안 450℃에서 상기 산화물 반도체층에 수행되며, 그 후 대기에 노출하지 않고 상기 온도는 실온으로 감소되고 물 또는 수소가 상기 산화물 반도체층에 혼입되는 것이 방지되며, 따라서 산화물 반도체층이획득된다. 상기 산화물 반도체층(462)은 상기 제 1 열 처리에 의해 탈수화되거나 또는 탈수소화될 수 있다.

- [0151] 상기 열 처리 장치는 전기로에 제한되지 않지만 저항 가열기 등과 같은 가열기로부터 열 복사 또는 열 전도에 의해 피처리물을 가열하는 장치가 제공될 수 있다. 예를 들면, GRTA (gas rapid thermal annealing) 장치 또는 LRTA(lamp rapid thermal annealing) 장치와 같은 RTA(rapid thermal annealing) 장치가 사용될 수 있다. 예를 들면, 상기 제 1 열 처리로서, GRTA가 다음과 같이 수행될 수 있다. 상기 기판은 650℃ 내지 700℃의 고 온으로 가열된 불활성 가스로 이송되어 수 분 동안 가열되고, 이송되어 고온으로 가열된 상기 불활성 가스 밖으로 꺼내어진다. GRTA는 단시간 동안 고-온 열 처리를 가능하게 한다.

- [0152] 상기 제 1 열 처리에서, 물, 수소 등은 질소 또는 헬륨, 네온, 또는 아르곤 과 같은 희가스에 포함되지 않는 것이 바람직하다. 상기 열 처리 장치로 도입되는 질소 또는 헬륨, 네온, 또는 아르곤과 같은 희가스는 6N(99.999%) 이상, 보다 바람직하게는, 7N(99.9999%) 이상(즉, 불순물들의 농도가 1ppm 이하, 보다 바람직하게는 0.1ppm 이하이다)의 순도를 갖는 것이 바람직하다.

- [0153] 또한, 상기 제 1 열 처리의 조건들 또는 상기 산화물 반도체층의 재료에 의존하여, 상기 산화물 반도체층

(462)은 미결정 막 또는 다결정 막이 되도록 결정화될 수 있다.

- [0154] 상기 산화물 반도체층의 상기 제 1 열 처리는 또한 상기 섬-형상 산화물 반도체층으로 가공되기 전에 상기 산화물 반도체막에 수행될 수 있다. 상기 경우에서, 상기 기판은 상기 제 1 열 처리 후에 상기 열 처리 장치로 부터 제거되며, 그 후 포토리소그래피 단계가 수행된다.

- [0155] 상기 산화물 반도체층의 탈수화 또는 탈수소화를 위한 제 1 열 처리가 상기 산화물 반도체층(462)의 형성 직후 수행되는 예가 상술되었다. 그러나, 탈수화 또는 탈수소화를 위한 상기 열 처리는 상기 산화물 반도체층의 성막 후에 수행되는 한 상기 소스 또는 드레인 전극(465b)이 상기 산화물 반도체층 상에 적층된 후 또는 상기 게이트 절연층(452)이 상기 소스 또는 드레인 전극(465b) 위에 형성된 후 수행될 수 있다.

- [0156] 다음으로, 도전막은 상기 절연층(457) 및 상기 산화물 반도체층(462) 위에 형성된다. 그 후, 레지스트 마스크 가 제 3 포토리소그래피 단계에 의해 상기 도전 막 위에 형성되고, 상기 도전막은 상기 소스 또는 드레인 전 극층(465b) 및 상기 배선층(468)을 형성하기 위해 선택적으로 에칭되며, 그 후 상기 레지스트 마스크가 제거된다(도 8c 참조). 상기 소스 또는 드레인 전극층(465b) 및 상기 배선층(468)은 상기 소스 또는 드레인 전극층(465a1, 465a2)의 각각의 재료 및 단계와 유사한 재료 및 유사한 단계에 의해 각각 형성될 수 있다.

- [0157] 이 실시형태에서, 150-nm-두께의 티타늄 막이 스퍼터링 방법에 의해 상기 소스 또는 드레인 전극층(465b) 및 상기 배선층(468)의 각각으로서 형성된다. 이 실시형태에서, 상기 소스 또는 드레인 전극층들(465a1, 465a2) 및 상기 소스 또는 드레인 전극층(465b)이 서로 동일한 티타늄 막들이기 때문에, 상기 소스 또는 드레인 전극 층(465b) 및 상기 소스 또는 드레인 전극층들(465a1, 465a2)의 각각 사이의 에칭 선택비는 제공될 수 없다. 그러므로, 상기 소스 또는 드레인 전극층(465b)이 에칭될 때 상기 소스 또는 드레인 전극층들(465a1, 465a2)이 에칭되는 것을 방지하기 위해, 상기 배선층(468)이 상기 산화물 반도체층(462)으로 커버되지 않는 상기 소스 또는 드레인 전극층(465a2)위에 제공된다. 에칭시 높은 선택비를 갖는 상이한 재료들이 상기 소스 또는 드레인 전극층들(465a1, 465a2)및 상기 소스 또는 드레인 전극층(465b)을 형성하기 위해 사용되는 경우에, 상기 소스 또는 드레인 전극층(465a1, 465a2)이 에칭시 보호되는 상기 배선층(468)이 반드시 제공되는 것은 아니다.

- [0158] 상기 산화물 반도체충(462)은 상기 도전막의 에칭에 의해 부분적으로 에칭 오프될 수 있다. 재료들 및 에칭 조건들은 필요 이상으로 상기 산화물 반도체충(462)을 제거하지 않도록 적절하게 제어된다.

- [0159] 이 실시형태에서, 상기 Ti 막이 상기 도전막으로서 사용되고 상기 In-Ga-Zn-O-계 산화물 반도체가 상기 산화물 반도체층(462)으로서 사용되기 때문에, 암모늄 과산화수소수(암모니아, 물, 및 과산화수소수의 혼합액)가 에천트로서 사용된다.

- [0160] 제 2 포토리소그래피 단계에서, 몇몇 경우들에서, 상기 산화물 반도체층(462)의 일부가 에칭되며, 그에 의해 홈(오목한 부분)을 가진 산화물 반도체층이 형성될 수 있다. 상기 소스 또는 드레인 전극층(465b) 및 상기 배선층(468)을 형성하기 위해 사용된 상기 레지스트 마스크는 잉크젯 방법에 의해 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서 제작 비용이 감소될 수 있다.

- [0161] 다음으로, 상기 게이트 절연층(452)이 상기 절연층(457), 상기 산화물 반도체층(462), 상기 소스 또는 드레인 전극층들(465a1, 465a2), 및 상기 소스 또는 드레인 전극층(465b) 위에 형성된다.

- [0162] 상기 게이트 절연층(452)은 플라즈마 CVD 방법, 스퍼터링 방법 등에 의해 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 및 산화 알루미늄층 중 하나 이상을 사용하여 단층 구조 또는 적층 구조로 형성될 수 있다. 상기 게이트 절연층(452)이 많은 양의 수소를 포함하는 것을 방지하기 위해, 스퍼터링 방법에 의해 상기 게이트 절연층(452)을 형성하는 것이 바람직하다. 스퍼터링 방법에 의해 산화 실리콘막을 형성하는 경우에, 실리콘 타겟 또는 석영 타겟이 타겟으로서 사용되며, 산소 또는 산소와 아르곤의 혼합 가스가 스퍼터링 가스로서 사용된다.

- [0163] 상기 게이트 절연층(452)은 산화 실리콘층 및 질화 실리콘층이 상기 소스 또는 드레인 전극층들(465a1, 465a2) 및 상기 소스 또는 드레인 전극층(465b) 위에 이러한 순서로 적충되는 구조를 가질 수 있다. 이 실시 형태에서, 100-nm-두께의 산화 실리콘층이 다음과 같이 형성된다: 상기 압력은 0.4 Pa이고; 상기 고-주파수 전원은 1.5 kW이고, 상기 분위기는 산소 및 아르곤(산소 대 아르곤의 유량비는 25 sccm:25 sccm = 1:1이다)이 며; RF 스퍼터링 방법이 사용된다.

- [0164] 다음으로, 레지스트 마스크가 제 4 포토리소그래피 단계에 의해 형성되며, 에칭은 상기 게이트 절연층(452)의 일부를 제거하기 위해 선택적으로 수행되어, 상기 배선층(468)에 도달하는 개구(423)가 형성된다(도 8d 참

- 조). 상기 소스 또는 드레인 전극층(465b)에 도달하는 개구는 비록 도시되지는 않았지만 상기 개구(423)가 형성될 때 형성될 수 있다. 이 실시형태에서, 상기 소스 또는 드레인 전극층(465b)에 도달하는 상기 개구는 층간 절연층을 적층한 후 형성되며, 전기 접속을 위한 배선층이 상기 개구에 형성된다.

- [0165] 다음으로, 도전막이 상기 게이트 절연층(452) 및 상기 개구(423) 위에 형성된다. 그 후, 제 5 포토리소그래피 단계가 수행되어, 상기 게이트 전극층(461(461a, 461b)) 및 상기 배선층(464)이 형성되도록 한다. 레지스트 마스크가 잉크젯 방법에 의해 형성될 수 있다는 것을 주의하자. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서 제작 비용은 감소될 수 있다.

- [0166] 상기 게이트 전극층(461(461a, 461b)) 및 상기 배선층(464)은 각각 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료, 또는 그것의 주요 성분으로서 이들 재료들 중 임의의 것을 포함하는 합금 재료를 사용한 단층 또는 적층 구조를 갖도록 형성될 수 있다.

- [0167] 이 실시형태에서, 150-nm-두께의 티타늄 막이 스퍼터링 방법에 의해 상기 게이트 전극층(461(461a, 461b)) 및 상기 배선층(464)의 각각으로서 형성된다. 비록 상기 게이트 전극층(461(461a, 461b))은 분할되는 것으로 도 8e에 도시되지만, 상기 게이트 전극층(461(461a, 461b))은 도 7a에 도시된 바와 같이 상기 소스 또는 드레인 전극층들(465a1, 465a2) 및 상기 소스 또는 드레인 전극층(465b)에 의해 형성된 고리형 보이드(torus-shaped void)를 중첩하도록 형성된다.

- [0168] 다음으로, 제 2 열 처리(바람직하게는 200℃ 내지 400℃의 온도로, 예를 들면, 250℃ 내지 350℃의 온도로)가 불활성 가스 분위기 또는 산소 가스 분위기에서 수행된다. 이 실시형태에서, 상기 제 2 열 처리는 질소 분위기에서 1시간 동안 250℃로 수행된다. 상기 제 2 열 처리는 보호 절연층 또는 평탄화 절연층이 상기 박막 트랜지스터(460) 위에 형성된 후 수행될 수 있다.

- [0169] 더욱이, 열 처리는 대기 중에서 1시간 내지 30시간 동안 100℃ 내지 200℃의 온도로 수행될 수 있다. 이러한 열 처리는 일정한 가열 온도로 수행될 수 있다. 대안적으로, 상기 가열 온도에서의 다음의 변화가 복수 회 반복적으로 행해질 수 있다: 상기 가열 온도는 실온에서 100℃ 내지 200℃의 온도로 증가되고 그 후 실온으로 감소된다. 이러한 열 처리는 상기 산화물 절연층의 형성 전에 감소된 압력 하에서 수행될 수 있다. 상기 감소된 압력 하에서, 상기 열 처리 시간은 단축될 수 있다.

- [0170] 상술된 프로세스를 통해, 수소, 수분, 수소화물, 및 수산화물의 농도가 감소되는 상기 산화물 반도체충(462)을 포함하는 상기 박막 트랜지스터(460)가 형성될 수 있다(도 8e 참조). 상기 박막 트랜지스터(460)는 실시형 태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

- [0171] 평탄화를 위한 보호 절연층 또는 평탄화 절연층이 상기 박막 트랜지스터(460) 위에 제공될 수 있다. 비록 도시되지는 않았지만, 이 실시형태에서, 상기 소스 또는 드레인 전극층(465b)에 도달하는 개구가 상기 게이트 절연층(452) 및 상기 보호 절연층 및/또는 상기 평탄화 절연층에 형성되며, 상기 소스 또는 게이트 전극층 (465b)에 전기적으로 접속되는 배선층이 상기 개구에 형성된다.

- [0172] 상술된 바와 같이 상기 산화물 반도체막의 성막시 상기 반응성 분위기에서 잔여 수분을 제거함으로써, 상기 산화물 반도체막에서의 수소 및 수소화물의 농도가 감소될 수 있다. 따라서, 상기 산화물 반도체막이 안정화 될 수 있다.

- [0173] 상기 산화물 반도체층을 사용하여 상기 박막 트랜지스터를 포함한 액정 표시 장치의 표시부의 복수의 화소들에서, 오프-상태 전류가 감소될 수 있다. 따라서, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장하고정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다. 이실시형태에서, 상기 채널의 형상은 원형이며 상기 소스 전극층 및 상기 드레인 전극 층은 상이한 층들을 사용하여 형성되며, 그에 의해 상기 채널 길이는 감소될 수 있고 상기 채널 폭은 증가될 수 있다. 이러한 방식으로, 큰 채널 폭을 가진 박막 트랜지스터가 비교적 작은 면적에서도 형성되어 심지어 큰 전류의 스위칭을 가능하게 할 수 있다. 게다가, 비록 상기 채널 폭이 클지라도, 상기 오프-상태 전류는 정제된 산화물 반도체가 사용되기 때문에 매우 작다.

- [0174] 이 실시형태는 다른 실시형태들에 기술된 임의의 상기 구성들과 적절하게 결합하여 구현될 수 있다.

- [0175] (실시형태 4)

- [0176] 이 실시형태에서, 본 명세서에 개시된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 다른 예들이 설명될 것이다. 실시형태 2는 실시형태 2와 동일한 부분들 및 그것과 유사한 기능을 갖는 부분들 및 단계들을 위

해 참조될 수 있다는 것을 주의하자. 또한, 상기 동일한 부분들에 대한 상세한 설명은 생략된다. 이 실시형태에서 설명된 박막 트랜지스터들(425, 426)은 각각 실시형태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

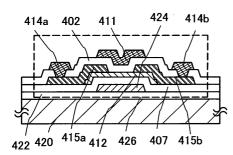

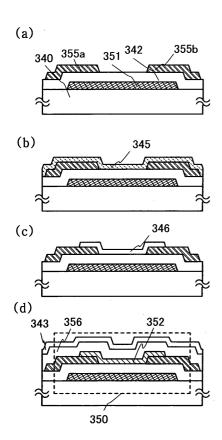

- [0177] 이 실시형태에서 박막 트랜지스터들은 도 9a 및 도 9b를 사용하여 기술된다.

- [0178] 도 9a 및 도 9b는 박막 트랜지스터들의 단면 구조의 예들을 도시한다. 도 9a 및 도 9b에 도시된 상기 박막 트랜지스터들(425, 426)은 각각 산화물 반도체층이 도전층과 게이트 전극층 사이에 개재되는 구조를 갖는 한 종류의 박막 트랜지스터이다.

- [0179] 도 9a 및 도 9b에서, 실리콘 기판(420)이 사용되며, 상기 박막 트랜지스터들(425, 426)의 각각은 상기 실리콘 기판(420) 위에 제공된 절연층(422) 위에 제공된다.

- [0180] 도 9a에서, 도전층(427)은 적어도 산화물 반도체층(412)과 전체적으로 중첩하도록 상기 실리콘 기판(420) 위에 제공된 상기 절연층(422) 및 절연층(407) 사이에 제공된다.

- [0181] 도 9b는 상기 절연층(422) 및 상기 절연층(407) 사이의 도전층이 도전층(424)이 되도록 에칭함으로써 가공되고 적어도 상기 산화물 반도체층(412)의 채널 영역을 포함한 부분에 중첩하는 일 예이다.

- [0182] 상기 도전층들(427, 424)은 각각 나중에 수행되는 열 처리의 온도에 내열성 있는 금속 재료에 의해 형성된다. 티타늄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 및 스칸듐(Sc)으로부터 선택된 하나의 원소, 그것의 주요 성분으로서 상기 원소들 중 임의의 것을 포함한 합금, 이들 원소들 중 임의의 것의 결합을 포함한 합금 막, 그것의 성분으로서 상기 원소들 중 임의의 것을 포함한 질화물 등이 사용될 수 있다. 단층 구조 또는 적층 구조가 사용될 수 있으며; 예를 들면, 텅스텐층의 단층, 질화 텅스텐층 및 텅스텐층의 적층 구조 등이 사용될 수 있다.

- [0183] 상기 도전층들(427, 424)의 각각의 전위는 상기 박막 트랜지스터들(425, 426)의 각각의 상기 게이트 전극층 (411)의 전위와 동일하거나 또는 상이할 수 있으며, 상기 도전층들(427, 424)의 각각은 제 2 게이트 전극층으로서 기능할 수 있다. 상기 도전층들(427, 424)의 전위들은 각각 GND 또는 0V와 같은 고정된 전위일 수 있다.

- [0184] 상기 박막 트랜지스터들(425, 426)의 전기적 특성들은 상기 도전층들(427, 424)에 의해 제어될 수 있다.

- [0185] 이러한 실시형태는 다른 실시형태들 중 임의의 것과 적절하게 결합하여 구현될 수 있다.

- [0186] (실시형태 5)

- [0187] 이 실시형태에서, 본 명세서에 개시된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 일 예가 설명될 것이다.

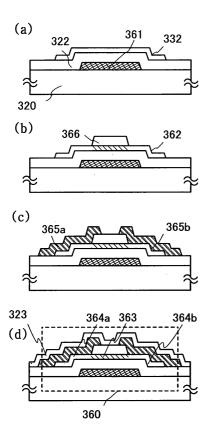

- [0188] 이 실시형태의 박막 트랜지스터 및 상기 박막 트랜지스터를 제작하기 위한 방법의 일 실시형태가 도 10a 내지 도 10e를 사용하여 설명된다.

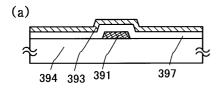

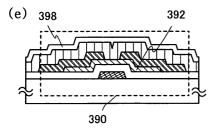

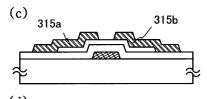

- [0189] 도 10a 내지 도 10e는 박막 트랜지스터의 단면 구조의 일 예를 도시한다. 도 10a 내지 도 10e에 도시된 박막 트랜지스터(390)는 한 종류의 보텀-게이트 구조이며 또한 역 스태거 박막 트랜지스터로서 칭하여진다.

- [0190] 비록 상기 박막 트랜지스터(390)는 단일-게이트 박막 트랜지스터를 사용하여 기술되지만, 복수의 채널 형성 영역들을 포함한 멀티-게이트 박막 트랜지스터가 필요에 따라 형성될 수 있다.

- [0191] 이후, 기판(394) 위에 상기 박막 트랜지스터(390)를 제작하기 위한 프로세스가 도 10a 내지 도 10e를 사용하여 기술된다.

- [0192] 먼저, 도전막은 절연 표면을 가진 상기 기판(394) 위에 형성되며, 그 후 제 1 포토리소그래피 단계가 수행되어, 게이트 전극층(391)이 형성되도록 한다. 상기 게이트 전극층의 단부는 그 위에 적층된 게이트 절연층으로 커버리지가 향상되기 때문에 테이퍼된 형상을 갖는 것이 바람직하다. 레지스트 마스크가 잉크젯 방법에 의해 형성될 수 있다는 것을 주의하자. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로하지 않으며; 따라서 제작 비용은 감소될 수 있다.

- [0193] 비록 절연 표면을 가진 상기 기판(394)으로서 사용될 수 있는 기판에 대한 특별한 제한은 없지만, 상기 기판 (394)은 적어도 나중에 수행될 열 처리를 견디기에 충분히 높은 내열성을 갖는 것이 필요하다.

- [0194] 예를 들면, 유리 기판이 상기 기판(394)으로서 사용되는 경우에, 나중에 수행될 상기 열 처리의 온도가 높다면, 변형점이 730℃ 이상인 유리 기판을 사용하는 것이 바람직하다. 상기 유리 기판의 재료로서, 예를 들면,

알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 또는 바륨 보로실리케이트 유리와 같은 유리 재료가 사용된다. 산화 붕소보다 많은 양의 산화 바륨(BaO)을 포함함으로써, 사용이 보다 실용적인 내열 유리 기판이 형성될 수 있다는 것을 주의하자. 그러므로,  $B_2O_3$ 보다 많은 BaO를 포함한 유리 기판이 사용되는 것이 바람직하다.

- [0195] 세라믹 기판, 석영 기판, 또는 사파이어 기판과 같은 절연체를 사용하여 형성된 기판이 상기 기판(394)으로서, 상술된 유리 기판 대신에 사용될 수 있다는 것을 주의하자. 대안적으로, 결정화된 유리 기판 등이 사용될 수 있다. 또한 대안적으로, 플라스틱 기판 등이 사용될 수 있다.

- [0196] 하지막으로서 기능하는 절연막이 상기 기판(394) 및 상기 게이트 전극층(391) 사이에 제공될 수 있다. 상기 하지막은 상기 기판(394)으로부터 불순물 원소의 확산을 방지하는 기능을 가지며, 질화 실리콘막, 산화 실리콘막, 질화산화 실리콘막, 및 산화질화 실리콘막 중 하나 이상을 사용하여 단층 구조 또는 적층 구조로 형성될 수 있다.

- [0197] 상기 게이트 전극층(391)은 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료, 또는 그것의 주요 성분으로서 이들 재료들 중 임의의 것을 포함한 합금 재료를 사용한 단층 또는 적층 구조를 갖도록 형성될 수 있다.

- [0198] 예를 들면, 상기 게이트 전극층(391)의 2-층 구조로서, 다음 구조들 중 임의의 것이 바람직하다: 알루미늄층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 질화 티타늄층 또는 질화 탄탈층의 2-층 구조, 질화 티타늄층 및 몰리브덴층의 2-층 구조, 및 질화 텅스텐층 및 그 위에 적층된 텅스텐층의 2-층 구조. 3-층 구조로서, 텅스텐층 또는 질화 텅스텐층, 알루미늄 및 실리콘의 합금 또는 알루미늄 및 티타늄의 합금의 층, 및 질화 티타늄층 또는 티타늄층의 적층이 바람직하다. 상기 게이트 전극층은 투광성 도전막을 사용하여 형성될 수 있다. 상기 투광성 도전막의 재료의 일예로서, 투광성 도전성 산화물이 제공될 수 있다.

- [0199] 다음으로, 게이트 절연층(397)이 상기 게이트 전극층(391) 위에 형성된다.

- [0200] 상기 게이트 절연층(397)이 플라즈마 CVD 방법, 스퍼터링 방법 등에 의해 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 및 산화 알루미늄층의 하나 이상을 사용하여 단층 구조 또는 적층 구조로 형성될 수 있다. 상기 게이트 절연층(397)이 많은 양의 수소를 포함하지 않도록 하기 위해, 스퍼터링 방법에 의해 상기 게이트 절연층(397)을 형성하는 것이 바람직하다. 스퍼터링 방법에 의해 산화 실리콘막을 형성하는 경우에, 실리콘 타켓 또는 석영 타켓이 타겟으로서 사용되며, 산소 또는 산소와 아르곤의 혼합 가스가스퍼터링 가스로서 사용된다.

- [0201] 상기 게이트 절연층(397)은 질화 실리콘층 및 산화 실리콘층이 상기 게이트 전극층(391) 위에 이러한 순서로 적충되는 구조를 가질 수 있다. 예를 들면, 100-nm-두께의 게이트 절연층이 50 nm 내지 200 nm의 두께를 가진 질화 실리콘층(SiNy(y>0))이 제 1 게이트 절연층으로서 스퍼터링 방법에 의해 형성되며, 그 후 50 nm 내지 300 nm의 두께를 가진 산화 실리콘층(SiOx(x>0))이 상기 제 1 게이트 절연층 위에 제 2 게이트 절연층으로서 적층되는 방식으로 형성된다.

- [0202] 상기 게이트 절연층(397) 및 산화물 반도체막(393)이 많은 수소, 수산기, 및 수분을 포함하는 것을 가능한 한 방지하기 위해, 상기 기판(394)상에 흡착된 수소 또는 수분과 같은 불순물이 제거되도록 상기 성막 전에 스퍼터링 장치의 예열실에서 상기 게이트 전극층(391)이 제공되는 상기 기판(394) 또는 상기 게이트 전극층(391)및 상기 게이트 절연층(397)이 제공되는 상기 기판(394)을 예열하고, 그 후 배기를 수행하는 것이 바람직하다. 상기 예열 온도는 100℃ 이상 400℃ 이하, 바람직하게는 150℃ 이상 300℃ 이하이다. 상기 예열실에 제공된 배기 수단으로서, 크라이오펌프가 바람직하다. 이러한 예열 단계가 반드시 수행되는 것은 아니다. 이러한 예열 단계는 산화물 절연층(396)이 형성되기 전에 도 10c에 도시된 소스 전극층(395a) 및 드레인 전극층(395b)까지 형성된 상기 기판(394)에 동일한 방식으로 수행될 수 있다.

- [0203] 다음으로, 상기 게이트 절연층(397) 위에, 상기 산화물 반도체막(393)이 스퍼터링 방법에 의해 2 mm 내지 200 mm, 바람직하게는 5 mm 내지 30 mm의 두께로 형성된다(도 10a 참조). 상기 산화물 반도체막의 적절한 두께는 그 재료에 의존하여 변화하며, 그러므로 상기 두께는 상기 재료에 의존하여 적절하게 결정될 수 있다는 것을 주의하자.

- [0204] 상기 산화물 반도체막(393)이 스퍼터링 방법에 의해 형성되기 전에, 상기 게이트 절연층(397)의 표면상의 먼

지가 제거되도록 아르곤 가스가 도입되고 플라즈마가 생성되는 역 스퍼터링을 수행하는 것이 바람직하다는 것을 주의하자. 상기 역 스퍼터링은 타켓 측으로의 전압의 인가 없이 상기 기판의 부근에 플라즈마를 생성하기 위해 아르곤 분위기에서 RF 전원으로 기판 측에 전압이 인가되어, 표면이 개질되도록 하는 방법이다. 상기 아르곤 분위기 대신에, 질소 분위기, 헬륨 분위기, 산소 분위기 등이 사용될 수 있다.

- [0205] 상기 산화물 반도체막(393)은 In-Ga-Zn-O-계 산화물 반도체막, In-Sn-Zn-O-계 산화물 반도체막, In-Al-Zn-O-계 산화물 반도체막, Sn-Ga-Zn-O-계 산화물 반도체막, Sn-Ga-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, In-O-계 산화물 반도체막, In-O-계 산화물 반도체막, In-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막, In-O-계 산화물 반도체막을 사용하여 형성된다. 이 실시형태에서, 상기 산화물 반도체막(393)은 In-Ga-Zn-O-계 산화물 반도체 타겟을 사용하여 스퍼터링 방법에 의해형성된다. 구체적으로, In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO = 1:1:1[분자%](즉, In:Ga:Zn = 1:1:0.5 [원자%])의 조성비를 가진 타겟이 사용된다. 대안적으로, In:Ga:Zn = 1:1:1 [원자%] 또는 In:Ga:Zn = 1:1:2 [원자%]의 조성비를 가진 타겟이 사용될 수 있다. 이 실시형태에서, 상기 산화물 반도체 타겟의 충전율은 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하이다. 높은 충전율을 가진 상기 산화물 반도체 타겟의 사용으로, 상기 성막된 산화물반도체막은 높은 밀도를 가진다. 상기 산화물 반도체막(393)은 희가스(대표적으로, 아르곤)의 분위기, 산소의분위기, 또는 희가스와 산소의 혼합 분위기에서 스퍼터링 방법에 의해 형성될 수 있다. 상기 타겟은 2 wt% 이상 및 10 wt% 이하로 SiO<sub>2</sub>를 포함할 수 있다.

- [0206] 상기 산화물 반도체막(393)은 다음과 같이 상기 기판(394) 위에 형성된다: 상기 기판은 감소된 압력을 가진 상기 처리실에 유지되고, 상기 기판은 실온 또는 400℃ 미만의 온도로 가열되며; 상기 처리실에서의 잔여 수분은 제거되고 수소 및 수분이 제거된 스퍼터링 가스가 도입되며, 상술된 타겟이 사용된다. 상기 처리실로부터 잔여 수분을 제거하기 위해, 바람직하게는 흡착형 진공 펌프가 사용된다. 예를 들면, 바람직하게는 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프가 사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 크라이오펌프를 사용하여 배기가 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H₂0)과 같은 수소 원자를 포함한 화합물, 탄소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 반도체막에 포함된 불순물들의 농도는 감소될 수 있다. 크라이오펌프를 사용하여 상기 처리실에서의 잔여 수분을 제거하면서 스퍼터링에 의한 성막을 수행함으로써, 상기 산화물 반도체막(393)의 형성 동안 상기 기판 온도는 실온 이상 400℃ 미만으로 설정될 수 있다.

- [0207] 상기 성막 조건의 일 예로서, 다음 조건이 이용된다: 상기 기판과 상기 타겟 간의 거리는 100 mm이고; 상기 기압은 0.6 Pa이고; 상기 직류(DC) 전원은 0.5 kW이며; 상기 분위기는 산소(산소 유량비는 100%이다)이다. 먼지가 감소될 수 있고 상기 막 두께가 일정하게 될 수 있기 때문에 펼스 직류(DC) 전원이 사용되는 것이 바람직하다.

- [0208] 스퍼터링 방법의 예들은 고-주파수 전원이 스퍼터링 전원으로서 사용되는 RF 스퍼터링 방법, DC 스퍼터링 방법, 및 바이어스가 펼스 방식으로 인가되는 펼스 DC 스퍼터링 방법을 포함한다. 상기 RF 스퍼터링 방법은 절연막이 형성되는 경우에서 주로 사용되며 상기 DC 스퍼터링 방법은 금속막이 형성되는 경우에 주로 사용된다.

- [0209] 서로 상이한 재료들로 형성되는 복수의 타겟들이 설정될 수 있는 다원-타겟 스퍼터링 장치가 또한 존재한다. 상기 다원-타겟 스퍼터링 장치 내에서, 상이한 재료들의 막들이 동일한 처리실에서 형성되도록 적충될 수 있 거나, 또는 복수의 종류들의 재료들이 상기 동일한 처리실에서 방전에 의해 동시에 성막될 수 있다.

- [0210] 게다가, 상기 처리실 내부에서의 자석 기구가 제공되고 마그네트론 스퍼터링 방법을 위해 사용된 스퍼터링 장치, 또는 글로 방전 없이 마이크로파를 사용하여 생성된 플라즈마가 사용되는 ECR 스퍼터링 방법을 위해 사용된 스퍼터링 장치가 또한 존재한다.

- [0211] 또한, 스퍼터링 방법을 사용한 성막 방법으로서, 타겟 물질 및 스퍼터링 가스 성분이 그것의 얇은 화합막을 형성하도록 성막 동안 서로 화학적으로 반응되는 반응성 스퍼터링 방법, 또는 전압이 또한 성막 동안 기판에 인가되는 바이어스 스퍼터링 방법이 존재한다.

- [0212] 다음으로, 상기 산화물 반도체막이 제 2 포토리소그래피 단계에 의해 섬-형상 반도체 산화물 층(399)으로 가 공된다(도 10b 참조). 상기 섬-형상 산화물 반도체층(399)을 위한 레지스트 마스크가 잉크젯 방법을 사용하여 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서, 제작 비용은 감소될 수 있다.

- [0213] 콘택트 홀이 상기 게이트 절연층(397)에 형성되는 경우에, 그 단계는 상기 산화물 반도체층(399)의 형성시 수

행될 수 있다.

- [0214] 상기 산화물 반도체막(393)의 에칭은 드라이 에칭, 웨트 에칭, 또는 드라이 에칭 및 웨트 에칭 둘 모두일 수 있다는 것을 주의하자.

- [0215] 상기 드라이 에칭을 위한 에칭 가스로서, 바람직하게는 염소를 포함한 가스(염소(Cl<sub>2</sub>), 염화 붕소(BCl<sub>3</sub>), 염화 규소(SiCl<sub>4</sub>), 또는 사염화탄소(CCl<sub>4</sub>)와 같은 염소-계 가스)가 사용된다.

- [0216] 대안적으로, 불소를 포함한 가스(사불화 탄소(CF<sub>4</sub>), 불화 유황(SF<sub>6</sub>), 불화 질소(NF<sub>3</sub>), 또는 트리플루오로메탄 (CHF<sub>3</sub>)과 같은 불소-계 가스); 브롬화 수소(HBr); 산소(O<sub>2</sub>); 헬륨(He) 또는 아르곤(Ar)과 같은 희가스가 부가 되는 이들 가스들 중 임의의 것 등이 사용될 수 있다.

- [0217] 상기 드라이 에칭 방법으로서, 평행 평판 RIE(반응성 이온 에칭) 방법 또는 ICP(유도 결합 플라즈마) 에칭 방법이 사용될 수 있다. 상기 층을 원하는 형상으로 에칭하기 위해, 상기 에칭 조건들(코일-형상 전극에 인가된 전력의 양, 기판 측상의 전극에 인가된 전력의 양, 상기 기판측 상에 상기 전극의 온도 등)이 적절하게 조정된다.

- [0218] 웨트 에칭을 위해 사용된 에천트로서, 인산, 아세트산, 및 질산 등의 혼합액, 수산화암모늄/과산화수소 혼합물(31 w% 과산화수소수 : 28 wt% 암모니아수 : 물 = 5:2:2) 등이 사용될 수 있다. 대안적으로, ITO-07N(칸토케미칼 코., 인크.에 의해 제작된)이 사용될 수 있다.

- [0219] 상기 웨트 에칭 후, 상기 에천트는 세정에 의해 상기 에칭 오프된 재료와 함께 제거된다. 상기 제거된 재료를 포함한 상기 에천트의 폐액은 정제될 수 있으며, 상기 폐액에 포함된 상기 재료는 재사용될 수 있다. 상기 에칭 후 상기 폐액으로부터 상기 산화물 반도체에 포함된 인듐과 같은 재료를 수집하고 재사용함으로써 상기 리소스들이 효율적으로 사용될 수 있고 비용은 감소될 수 있다.

- [0220] 상기 에칭 조건들(에천트, 에칭 시간, 및 온도와 같은)은 재료가 원하는 형상으로 에칭될 수 있도록 상기 재료에 의존하여 적절하게 조정된다.

- [0221] 상기 경우에, 도전막이 다음 단계에서 형성되기 전에, 상기 산화물 반도체충(399) 및 상기 게이트 절연충 (397)의 표면으로부터 레지스트 잔류물 등을 제거하기 위해 역 스퍼터링을 수행하는 것이 바람직하다는 것을 주의하자.

- [0222] 다음으로, 도전막이 상기 게이트 절연층(397) 및 상기 산화물 반도체층(399) 위에 형성된다. 상기 도전막은 스퍼터링 방법 또는 진공 성막 방법에 의해 형성될 수 있다. 상기 도전막의 재료로서, Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 하나의 원소, 성분으로서 상기 원소들 중 임의의 것을 포함한 합금, 상기 원소들 중 임의의 것을 결합하여 포함한 합금 막 등이 제공될 수 있다. 또한, 망간, 마그네슘, 지르코늄, 베릴륨, 및 이트륨으로부터 선택된 하나 이상의 재료들이 사용될 수 있다. 또한, 상기 도전막은 단층 구조 또는 두 개 이상의 층들의 적층 구조를 가질 수 있다. 예를 들면, 실리콘을 포함한 알루미늄막의 단층 구조, 티타늄 막이 알루미늄막 위에 적층되는 2-층 구조, 티타늄 막, 알루미늄막, 및 티타늄 막이 순서대로 적층되는 3-층 구조 등이 제공될 수 있다. 대안적으로, 알루미늄(Al) 및 티타늄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 및 스칸듐(Sc)으로부터 선택된 하나 이상의 원소들을 포함하는 막, 합금 막, 또는 질화막이 사용될 수 있다.

- [0223] 레지스트 마스크는 제 3 포토리소그래피 단계에 의해 상기 도전막 위에 형성되고 상기 소스 전극층(395a) 및 상기 드레인 전극층(395b)이 선택적 에칭에 의해 형성되며, 그 후 상기 레지스트 마스크가 제거된다(도 10c 참조).

- [0224] 상기 제 3 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 노광은 자외선 광, KrF 레이저 광, 또는 ArF 레이저 광을 사용하여 수행될 수 있다. 형성될 박막 트랜지스터의 채널 길이(L)는 상기 산화물 반도체층 (399) 위에서 서로에 인접하는, 상기 소스 전극층의 하단 및 상기 드레인 전극층의 하단 사이의 거리에 의해 결정된다. 노광이 25 nm 미만의 채널 길이(L)에 대해 수행되는 경우에, 상기 제 3 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 상기 노광은 수 나노미터 내지 수십 나노미터의 매우 짧은 파장을 가진 초자외선 광을 사용하여 수행된다. 초자외선 광에 의한 상기 노광에서, 상기 해상도는 높으며 초점 심도는 크다. 따라서 상기 박막 트랜지스터의 상기 채널 길이(L)는 10 nm 내지 1000 nm가 되게 할 수 있고, 회로의 동작 속도는 증가될 수 있으며, 낮은 전력 소비가 매우 작은 오프-상태 전류에 의해 달성될 수 있다.

- [0225] 각각의 재료 및 에칭 조건들이 상기 산화물 반도체층(399)이 상기 도전막의 에칭에 의해 제거되지 않도록 적절하게 조정된다는 것을 주의하자.

- [0226] 이 실시형태에서, Ti 막은 상기 도전막으로서 사용되고 상기 In-Ga-Zn-O-계 산화물 반도체가 상기 산화물 반도체층(399)을 위해 사용되며 암모늄 과산화수소수(암모니아, 물, 및 과산화수소수의 혼합액)가 에천트로서 사용된다.

- [0227] 상기 제 3 포토리소그래피 단계에서, 몇몇 경우들에서, 상기 산화물 반도체층(399)의 일부가 에칭되며, 그에 의해 홈(오목한 부분)을 가진 산화물 반도체층이 형성될 수 있다. 상기 소스 전극층(395a) 및 상기 드레인 전 극층(395b)을 형성하기 위해 사용된 상기 레지스트 마스크가 잉크젯 방법에 의해 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며; 따라서 제작 비용이 감소될 수 있다.

- [0228] 상기 포토리소그래피 단계에서 포토마스크들 및 단계들의 수를 감소시키기 위해, 에칭은 복수의 강도들을 갖도록 광이 투과되는 노광 마스크인 다계조 마스크를 사용하여 형성된 레지스트 마스크를 사용하여 수행될 수 있다. 다계조 마스크를 사용하여 형성된 레지스트 마스크는 복수의 두께들을 갖고 에칭을 수행함으로써 형상이 추가로 변경될 수 있기 때문에, 상기 레지스트 마스크는 상이한 패턴들을 제공하기 위해 복수의 에칭 단계들에 사용될 수 있다. 그러므로, 적어도 두 종류들의 상이한 패턴들에 대응하는 레지스트 마스크는 하나의 다계조 마스크를 사용함으로써 형성될 수 있다. 따라서, 노광 마스크들의 수는 감소될 수 있고 대응하는 포토리소그래피 단계들의 수가 또한 감소될 수 있으며, 그에 의해 상기 제작 프로세스의 단순화가 실현될 수 있다.

- [0229] 상기 레지스트 마스크의 제거 후, N<sub>2</sub>O, N<sub>2</sub>, 또는 Ar과 같은 가스를 사용한 플라즈마 처리가 노출되는 상기 산화물 반도체충(399)의 표면상에 흡착된 물 등을 제거하기 위해 수행될 수 있다. 플라즈마 처리가 산소 및 아르곤의 혼합 가스를 사용하여 수행될 수 있다.

- [0230] 다음으로, 상기 산화물 절연층(396)이 상기 산화물 반도체층의 일부와 접촉하는 보호 절연층으로서 기능하는 산화물 절연층으로서 형성된다(도 10d 참조). 상기 플라즈마 처리가 수행되는 경우에, 상기 산화물 절연층 (396)은 상기 플라즈마 처리 후 연속하여 상기 대기에 상기 산화물 반도체층(399)의 노출 없이 형성될 수 있다. 이 실시형태에서, 상기 산화물 반도체층(399)은 상기 산화물 반도체층(399)이 상기 소스 전극층(395a) 및 상기 드레인 전극층(395b) 어디에도 중첩하지 않는 영역에서 상기 산화물 절연층(396)과 접촉한다.

- [0231] 이 실시형태에서, 상기 산화물 절연층(396)으로서, 결함을 포함한 산화 실리콘층이 다음과 같이 형성된다: 상기 섬-형상 산화물 반도체층(399), 상기 소스 전극층(395a), 및 상기 드레인 전극층(395b)이 형성되는 상기기판(394)이 실온 내지 100℃ 미만의 온도로 가열되고; 수소 및 수분이 제거된 고-순도 산소를 포함한 스퍼터링 가스가 도입되며; 실리콘 반도체 타겟이 사용된다.

- [0232] 예를 들면, 상기 산화 실리콘막은 다음과 같이 형성된다: 붕소(0.01  $\Omega$ ·cm 의 저항도를 가진)로 도핑되고 6N의 순도를 가진 실리콘 타겟이 사용되고; 상기 타겟과 상기 기판 간의 거리(T-S 거리)가 89 mm이고; 상기 압력은 0.4 Pa이고; 상기 직류(DC) 전원은 6 kW이고; 상기 분위기는 산소(산소 유량비는 100%이다)이며; 펄스 DC 스퍼터링 방법이 사용된다. 상기 산화 실리콘막의 두께는 이 실시형태에서 300 nm이다. 석영(바람직하게는, 합성 석영)이 상기 산화 실리콘막을 형성하기 위해 상기 실리콘 타겟 대신에 사용될 수 있다.

- [0233] 상기 경우에, 상기 산화물 절연층(396)의 성막에 있어서 상기 처리실에서의 잔여 수분을 제거하는 것이 바람 직하다. 이것은 상기 산화물 반도체층(399) 및 상기 산화물 절연층(396)이 수소, 수산기, 또는 수분을 포함하는 것을 방지하기 위한 것이다.

- [0234] 상기 처리실로부터 잔여 수분을 제거하기 위해, 바람직하게는, 흡착형 진공 펌프가 사용된다. 예를 들면, 바람직하게는 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프가 사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 크라이오 펌프를 사용하여 배기가 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H₂0)과 같은 수소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 절연층(396)에 포함된 불순물들의 농도는 감소될 수 있다.

- [0235] 상기 산화물 절연층(396)에서, 상기 산화 실리콘층 대신에, 산화질화 실리콘층, 산화 알루미늄층, 산화질화 알루미늄층 등이 사용될 수 있다.

- [0236] 또한, 상기 산화물 절연층(396)의 형성 후, 100℃ 내지 400℃에서의 열 처리가 상기 산화물 절연층(396)이 상기 산화물 반도체층(399)과 접촉하는 상태에서 수행될 수 있다. 이 실시형태에서 상기 산화물 절연층(396)은

많은 결함들을 포함하기 때문에, 상기 산화물 반도체층(399)에 포함된 수소, 수분, 수산기, 또는 수소화물과 같은 불순물은 이러한 열 처리에 의해 상기 산화물 절연층(396)으로 확산되며, 따라서 상기 산화물 반도체층 (399)에 포함된 상기 불순물이 추가로 감소될 수 있다.

- [0237] 상술된 프로세스를 통해, 수소, 수분, 수산기, 또는 수소화물의 농도가 감소되는 산화물 반도체층(392)을 포함한 상기 박막 트랜지스터(390)가 형성될 수 있다(도 10e 참조).

- [0238] 상술된 상기 산화물 반도체막의 성막시 상기 반응 분위기에서의 잔여 수분을 제거함으로써, 상기 산화물 반도 체막에서의 수소 및 수소화물의 농도는 감소될 수 있다. 따라서, 상기 산화물 반도체막이 안정화될 수 있다.

- [0239] 보호 절연층이 상기 산화물 절연층 위에 제공될 수 있다. 이 실시형태에서, 보호 절연층(398)은 상기 산화물 절연층(396) 위에 형성된다. 상기 보호 절연층(398)으로서, 질화 실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 또는 질화산화 알루미늄막 등이 사용될 수 있다.

- [0240] 상기 보호 절연층(398)으로서, 질화 실리콘막이 상기 산화물 절연층(396)까지 및 이를 포함하는 층들이 형성되는 상기 기판(394)을 100℃ 내지 400℃의 온도로 가열하고, 수소 및 수분이 제거된 고-순도 질소를 포함하는 스퍼터링 가스를 도입하며, 실리콘 반도체의 타켓을 사용함으로써 형성된다. 상기 경우에, 상기 산화물 절연층(396)의 경우와 같이 상기 보호 절연층(398)의 형성에 있어서 잔여 수분은 상기 처리실로부터 제거되는 것이 또한 바람직하다.

- [0241] 상기 보호 절연층(398)이 형성되는 경우에, 상기 기판(394)은 상기 보호 절연층(398)의 형성시 100℃ 내지 400℃의 온도로 가열되며, 그에 의해 상기 산화물 반도체층에 포함된 수소 또는 수분이 상기 산화물 절연층으로 확산될 수 있다. 이러한 경우에, 상기 산화물 절연층(396)의 형성 후 열 처리가 반드시 수행되는 것은 아니다.

- [0242] 상기 산화 실리콘층이 상기 산화물 절연층(396)으로서 형성되고 상기 질화 실리콘층이 상기 보호 절연층(398)으로서 적층되는 경우에, 상기 산화 실리콘층 및 상기 질화 실리콘층은 공통 실리콘 타겟을 사용하여 동일한 처리실에 형성될 수 있다. 먼저, 산소를 포함한 스퍼터링 가스가 도입되며 상기 처리실 내부에 위치된 실리콘 타겟이 사용되어, 산화 실리콘층이 형성되도록 하고; 그 후 상기 스퍼터링 가스는 질소를 포함한 스퍼터링 가스로 전환되며 동일한 실리콘 타겟이 사용되어, 질화 실리콘층이 형성되도록 한다. 상기 산화 실리콘층 및 상기 질화 실리콘층은 대기에 노출하지 않고 연속적으로 형성될 수 있고, 수소 또는 수분과 같은 불순물이 상기 산화 실리콘층의 표면상에 흡착되는 것을 방지될 수 있다. 상기 경우에, 상기 산화 실리콘층이 상기 산화물 절연층(396)으로서 형성되고 상기 질화 실리콘층이 상기 보호 절연층(398)으로서 적층된 후, 상기 산화물 반도체층에 포함된 수소 또는 수분을 상기 산화물 절연층으로 확산하기 위한 열 처리(100℃ 내지 400℃의온도로)가 수행될 수 있다.

- [0243] 상기 보호 절연층의 형성 후, 열 처리가 1시간 내지 30시간 동안 대기 중에서 100℃ 내지 200℃의 온도로 수행될 수 있다. 이러한 열 처리는 일정한 가열 온도에서 수행될 수 있다. 대안적으로, 상기 가열 온도에서의 다음의 변화가 복수 회 반복적으로 행해질 수 있다: 상기 가열 온도는 실온에서 100℃ 내지 200℃의 온도로 증가되며 그 후 실온으로 감소된다. 또한, 이러한 열 처리는 상기 산화물 절연층의 형성 전에 감소된 압력 하에서 수행될 수 있다. 상기 감소된 압력 하에서, 상기 열 처리 시간은 단축될 수 있다. 이러한 열 처리로, 노멀리 오프인(n-채널 트랜지스터의 경우에 양의 임계 전압을 갖는) 박막 트랜지스터가 획득될 수 있다. 그러므로, 상기 액정 표시 장치의 신뢰성은 향상될 수 있다.

- [0244] 또한, 상기 게이트 절연층 위에서, 채널 형성 영역이 형성되는 것인 상기 산화물 반도체층의 형성시 상기 반응 분위기에서 잔여 수분을 제거함으로써, 상기 산화물 반도체층에서의 수소 또는 수소화물의 농도는 감소될 수 있다.

- [0245] 상술된 프로세스는 액정 표시 패널, 전계발광 표시 패널, 전자 잉크를 사용한 표시 장치 등의 백플레인(박막트랜지스터가 형성되는 기판)을 제조하기 위해 사용될 수 있다. 상술된 프로세스는 400℃ 이하의 온도로 수행되기 때문에, 프로세스는 1미터보다 긴 변과 1mm 이하의 두께를 가진 유리 기판을 사용하는 제작 프로세스에 적용될 수 있다. 또한, 전체 프로세스가 400℃ 이하의 처리 온도로 수행될 수 있기 때문에, 표시 패널은 너무많은 에너지를 소비하지 않고 제작될 수 있다.

- [0246] 상기 산화물 반도체층을 사용한 상기 박막 트랜지스터를 포함하는 액정 표시 장치의 표시부의 복수의 화소들에서, 오프-상태 전류가 감소될 수 있다. 따라서, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장하고정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다.

- [0247] 이 실시형태는 다른 실시형태들에 기술된 임의의 상기 구성들과 적절하게 결합하여 구현될 수 있다.

- [0248] (실시형태 6)

- [0249] 이 실시형태에서, 본 명세서에 개시된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 또 다른 예가 설명될 것이다. 이 실시형태에서 기술된 박막 트랜지스터(310)는 실시형태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

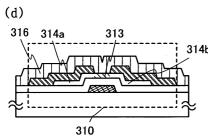

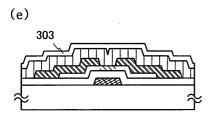

- [0250] 이 실시형태의 박막 트랜지스터 및 상기 박막 트랜지스터를 제작하기 위한 방법의 일 실시형태가 도 11a 내지 도 11e를 사용하여 기술된다.

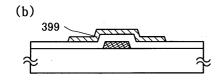

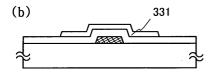

- [0251] 도 11a 내지 도 11e는 박막 트랜지스터의 단면 구조의 일 예를 도시한다. 도 11a 내지 도 11e에 도시된 박막 트랜지스터(310)는 한 종류의 보텀-게이트 구조이며 또한 역 스태거 박막 트랜지스터라고 한다.

- [0252] 상기 박막 트랜지스터(310)는 단일-게이트 박막 트랜지스터를 사용하여 기술되지만, 복수의 채널 형성 영역들을 포함하는 멀티-게이트 박막 트랜지스터가 필요에 따라 형성될 수 있다.

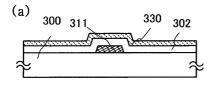

- [0253] 이후, 기판(300) 위에 상기 박막 트랜지스터(310)를 제작하기 위한 프로세스가 도 11a 내지 도 11e를 사용하여 기술된다.

- [0254] 먼저, 도전막이 절연 표면을 가진 상기 기판(300) 위에 형성되며, 그 후 제 1 포토리소그래피 단계가 수행되어, 게이트 전극층(311)이 형성되도록 한다. 레지스트 마스크는 잉크젯 방법에 의해 형성될 수 있다는 것을 주의하자. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며; 따라서 제작 비용은 감소될 수 있다.

- [0255] 절연 표면을 가진 상기 기판(300)으로서 사용될 수 있는 기판에 대한 특별한 제한은 없지만, 상기 기판(300)은 적어도 나중에 수행될 열 처리를 견디기에 충분히 높은 내열성을 갖는 것이 필요하다.

- [0256] 예를 들면, 유리 기판이 상기 기판(300)으로서 사용되는 경우에, 나중에 수행될 상기 열 처리의 온도가 높다면, 변형점이 730℃ 이상인 유리 기판을 사용하는 것이 바람직하다. 상기 유리 기판의 재료로서, 예를 들면, 알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 또는 바륨 보로실리케이트 유리와 같은 유리 재료가사용된다. 산화 붕소보다 더 많은 양의 산화 바륨(BaO)을 포함함으로써, 보다 실질적으로 사용하는 내열 유리기판이 형성될 수 있다. 그러므로, B₂O₃보다 많은 BaO를 포함한 유리 기판이 사용되는 것이 바람직하다.

- [0257] 세라믹 기판, 석영 기판, 또는 사파이어 기판과 같은 절연체를 사용하여 형성된 기판이 상기 기판(300)으로서 상술된 유리 기판 대신에 사용될 수 있다는 것을 주의하자. 대안적으로, 결정화된 유리 기판 등이 사용될 수 있다. 또한 대안적으로, 플라스틱 기판 등이 사용될 수 있다.

- [0258] 하지막으로서 기능하는 절연막은 상기 기판(300) 및 상기 게이트 전극층(311) 사이에 제공될 수 있다. 상기 하지막은 상기 기판(300)으로부터의 불순물 원소의 확산을 방지하는 기능을 가지며, 질화 실리콘막, 산화 실리콘막, 질화산화 실리콘막, 및 산화질화 실리콘막 중 하나 이상을 사용한 단층 구조 또는 적층 구조를 갖고 형성될 수 있다.

- [0259] 상기 게이트 전극층(311)은 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료, 또는 그것의 주요 성분으로 이들 재료들 중 임의의 것을 포함하는 합금 재료를 사용하여단층 또는 적층 구조를 갖도록 형성될 수 있다.

- [0260] 예를 들면, 상기 게이트 전극층(311)의 2-층 구조로서, 다음 구조들 중 임의의 것이 바람직하다: 알루미늄층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 몰리브덴층의 2-층 구조, 구리층 및 그 위에 적층된 질화 티타늄층 또는 질화 탄탈층의 2-층 구조, 질화 티타늄층 및 몰리브덴층의 2-층 구조, 및 질화 텅스텐층 및 그 위에 적층된 텅스텐층의 2-층 구조. 3-층 구조로서, 텅스텐층 또는 질화 텅스텐층, 알루미늄 및 실리콘의 합금 또는 알루미늄 및 티타늄의 합금의 층, 및 질화 티타늄층 또는 티타늄층의 적층이 바람직하다.

- [0261] 다음으로, 게이트 절연층(302)이 상기 게이트 전극층(311) 위에 형성된다.

- [0262] 상기 게이트 절연층(302)은 플라즈마 CVD 방법, 스퍼터링 방법 등에 의해 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 및 산화 알루미늄층의 하나 이상을 사용한 단층 구조 또는 적층 구조를 갖고 형성될 수 있다. 예를 들면, 산화질화 실리콘층은 성막 가스로서 SiH4, 산소, 및 질소를 사용하여 플라

즈마 CVD 방법에 의해 형성될 수 있다. 이 실시형태에서, 상기 게이트 절연층(302)의 두께는 100 nm 이상 500 nm 이하이다. 적층 구조의 경우에, 50 nm 내지 200 nm의 두께를 가진 제 1 게이트 절연층 및 5 nm 내지 300 nm의 두께를 가진 제 2 게이트 절연층이 상기 제 1 게이트 절연층 위에 적층된다.

- [0263] 이 실시형태에서, 100 nm 이하의 두께를 가진 산화질화 실리콘층이 플라즈마 CVD 방법에 의해 상기 게이트 절 연층(302)으로서 형성된다.

- [0264] 다음으로, 상기 게이트 절연층(302) 위에, 2 nm 내지 200 nm, 바람직하게는 5 nm 내지 30 nm의 두께를 가진 산화물 반도체막(330)이 상기 게이트 절연층(302) 위에 형성된다. 상기 산화물 반도체막의 적절한 두께는 그 재료에 의존하여 변화하며; 그러므로 상기 두께는 상기 재료에 의존하여 적절히 결정될 수 있다는 것을 주의하자. 이 단계에서의 단면도는 도 11a이다.

- [0265] 상기 산화물 반도체막(330)이 스퍼터링 방법에 의해 형성되기 전에, 상기 게이트 절연층(302)의 표면상의 먼지가 제거되도록 아르곤 가스가 도입되고 플라즈마가 생성되는 역 스퍼터링을 수행하는 것이 바람직하다는 것을 주의하자. 상기 아르곤 분위기 대신에, 질소 분위기, 헬륨 분위기, 산소 분위기 등이 사용될 수 있다.

- [0266] 상기 산화물 반도체막(330)은 In-Ga-Zn-O-계 산화물 반도체막, In-Sn-Zn-O-계 산화물 반도체막, In-Al-Zn-O-계 산화물 반도체막, Sn-Ga-Zn-O-계 산화물 반도체막, In-Sn-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, Sn-Al-Zn-O-계 산화물 반도체막, In-O-계 산화물 반도체막, In-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막, In-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막, Sn-O-계 산화물 반도체막을 사용하여 형성된다. 이 실시형태에서, 상기 산화물 반도체막(330)은 In-Ga-Zn-O-계 산화물 반도체 타켓을 사용하여 스퍼터링 방법에 의해형성된다. 구체적으로, In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO = 1:1:1 [분자%]의 조성비(즉, In:Ga:Zn = 1:1:0.5 [원자%])를 가진타겠이 사용된다. 대안적으로, In:Ga:Zn = 1:1:1 [원자%] 또는 In:Ga:Zn = 1:1:2 [원자%]의 조성비를 가진 타겠어 사용된다. 이 실시형태에서, 상기 산화물 반도체 타켓의 충전율은 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하이다. 높은 충전율을 가진 상기 산화물 반도체 타켓의 사용으로, 상기 성막된 산화물 반도체막은 높은 밀도를 가진다. 상기 타켓은 2 wt% 이상 및 10 wt% 이하의 SiO<sub>2</sub>를 포함할 수 있다.

- [0267] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 산화물 반도체막(330)의 성막을 위한 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0268] 상기 스퍼터링은 100℃ 내지 600℃, 바람직하게는 200℃ 내지 400℃의 기판 온도로 감소된 압력을 갖는 상기 처리실에 상기 기판을 유지함으로써 수행된다. 성막시 상기 기판을 가열함으로써, 상기 산화물 반도체막에 포함된 불순물들의 농도는 감소될 수 있다. 또한, 상기 스퍼터링에 의한 손상은 억제될 수 있다. 그 후, 상기 처리실에서의 잔여 수분이 제거되고, 수소 및 수분이 제거된 스퍼터링 가스가 도입되며, 상술된 타겟이 사용되어, 상기 산화물 반도체막(330)이 상기 기판(300) 위에 형성되도록 한다. 상기 처리실로부터 잔여 수분을 제거하기 위해, 바람직하게는, 흡착형 진공 펌프가 사용된다. 예를 들면, 바람직하게는, 크라이오펌프, 이온펌프, 또는 티타늄 서블리메이션 펌프가 사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가사용될 수 있다. 배기가 크라이오펌프를 사용하여 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H₂0)과 같은 수소 원자를 포함한 화합물, 탄소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 반도체막에 포함된 불순물들의 농도는 감소될 수 있다.

- [0269] 상기 성막 조건의 일 예로서, 다음 조건이 이용된다: 상기 기판과 상기 타겟 간의 거리는 100 mm이고; 상기 압력은 0.6 Pa이고; 직류(DC) 전원은 0.5 kW이며; 상기 분위기는 산소(산소 유량비는 100%이다)이다. 먼지가 감소될 수 있고 상기 막 두께가 일정해질 수 있기 때문에 펄스 직류(DC) 전원이 사용되는 것이 바람직하다.

- [0270] 다음으로, 상기 산화물 반도체막(330)이 제 2 포토리소그래피 단계에 의해 섬-형상 산화물 반도체층(331)으로 가공된다. 상기 섬-형상 산화물 반도체층을 형성하기 위한 레지스트 마스크가 잉크젯 방법을 사용하여 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며; 따라서, 제작 비용은 감소될 수 있다.

- [0271] 다음으로, 제 1 열 처리가 상기 산화물 반도체층(331)에 수행된다. 상기 산화물 반도체층(331)은 상기 제 1 열 처리에 의해 탈수화 또는 탈수소화될 수 있다. 상기 제 1 열 처리의 온도는 400℃ 이상 750℃ 이하, 바람 직하게는 400℃ 이상 상기 기판의 변형점 미만이다. 이 실시형태에서, 상기 기판은 열 처리 장치의 한 종류인 전기로에 도입되고 열 처리는 질소 분위기에서 1시간 동안 450℃로 상기 산화물 반도체층에 수행되며, 그 후 대기에 노출하지 않고, 물 또는 수소가 상기 산화물 반도체층으로 혼입되는 것이 방지되고, 따라서 상기 산화

물 반도체층(331)이 획득된다(도 11b 참조).

- [0272] 상기 열 처리 장치는 전기로에 제한되지 않지만, 저항 가열기 등과 같은 가열기로부터 열 전도 또는 열 복사에 의해 피처리물을 가열하기 위한 장치가 제공될 수 있다. 예를 들면, GRTA(가스 급속 열 어닐) 장치 또는 LRTA(램프 급속 열 어닐) 장치와 같은 RTA(급속 열 어닐) 장치가 사용될 수 있다. 상기 LRTA 장치는 할로겐 램프, 금속 할라이드 램프, 크세논 아크 램프, 탄소 아크 램프, 고압 나트륨 램프, 또는 고압 수은 램프와 같은 램프로부터 방출된 광(전자기파)의 복사에 의해 피처리물을 가열하기 위한 장치이다. GRTA 장치는 고-온 가스를 사용한 열 처리를 위한 장치이다. 상기 가스로서, 질소 또는 아르곤과 같은 희가스와 같이, 열 처리에 의해 피처리물과 반응하지 않는 불활성 가스가 사용된다.

- [0273] 예를 들면, 상기 제 1 열 처리로서, GRTA가 다음과 같이 수행될 수 있다. 상기 기판은 650℃ 내지 700℃의 고 온으로 가열된 불활성 가스로 이송되어 수 분 동안 가열되고, 이송되어 고온으로 가열된 상기 불활성 가스 밖 으로 꺼내어진다. GRTA는 단시간 동안 고-온 열 처리를 가능하게 한다.

- [0274] 상기 제 1 열 처리에서, 물, 수소 등은 질소 또는 헬륨, 네온, 또는 아르곤 과 같은 희가스에 포함되지 않는 것이 바람직하다. 상기 열 처리 장치로 도입되는 질소 또는 헬륨, 네온, 또는 아르곤과 같은 희가스는 6N(99.9999%) 이상, 보다 바람직하게는. 7N(99.9999%) 이상(즉, 불순물들의 농도가 1 ppm 이하, 보다 바람직하게는 0.1 ppm 이하이다)의 순도를 가지는 것이 바람직하다.

- [0275] 상기 제 1 열 처리에 의해, 상기 산화물 반도체층(331)에 포함된 수소 등이 제거될 수 있지만, 동시에, 산소 결손이 야기되어, 상기 산화물 반도체층(331)이 n-형 반도체(감소된 저항을 갖는 반도체)가 된다. 또한, 상기 산화물 반도체층의 상기 제 1 열 처리의 상기 조건 또는 상기 재료들에 의존하여, 상기 산화물 반도체층(331)은 미결정 막 또는 다결정 막이 되도록 결정화될 수 있다. 예를 들면, 상기 산화물 반도체층은 90% 이상, 또는 80% 이상의 결정화율을 갖는 미결정 반도체막이 되도록 결정화될 수 있다. 또한, 상기 제 1 열 처리의 조건들 또는 상기 산화물 반도체층의 재료에 의존하여, 상기 산화물 반도체층(331)은 결정 성분들을 포함하지 않는 비정질 산화물 반도체막일 수 있다. 상기 산화물 반도체층은 미결정 부분(1 nm 내지 20 nm, 대표적으로 2 nm 내지 4 nm의 입경을 갖는)이 비정질 산화물 반도체에 혼합되는 산화물 반도체막이 될 수 있다.

- [0276] 상기 산화물 반도체층의 상기 제 1 열 처리는 또한 상기 섬-형상 산화물 반도체층으로 가공되기 전에 상기 산화물 반도체막(330)에 수행될 수 있다. 상기 경우에, 상기 기판은 상기 제 1 열 처리 후 상기 열 처리 장치로 부터 제거되며, 그 후 포토리소그래피 단계가 수행된다.

- [0277] 탈수화 또는 탈수소화에 효과적인 상기 열 처리는 상기 산화물 반도체층의 성막 후 수행되는 한 소스 전극 및 드레인 전극이 상기 산화물 반도체층 상에 적충된 후 또는 보호 절연막이 상기 소스 및 상기 드레인 전극 위에 형성된 후 수행될 수 있다.

- [0278] 콘택트 홀이 상기 게이트 절연층(302)에 형성되는 경우에, 그 단계는 상기 탈수화 또는 탈수소화가 상기 산화물 반도체막(330) 또는 상기 산화물 반도체층(331)에 수행되기 전 또는 후에 수행될 수 있다.

- [0279] 상기 산화물 반도체막의 에칭은 웨트 에칭에 제한되지 않으며 드라이 에칭일 수 있다.

- [0280] 상기 에칭 조건들(에천트, 에칭 시간, 또는 온도와 같은)은 재료가 원하는 형상으로 에칭될 수 있도록 상기 재료에 의존하여 적절하게 조정된다.

- [0281] 다음으로, 도전막이 상기 게이트 절연층(302) 및 상기 산화물 반도체층(331) 위에 형성된다. 상기 도전막은 스퍼터링 방법 또는 진공 성막 방법에 의해 형성될 수 있다. 상기 도전막의 재료로서, Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 하나의 원소, 성분으로서 상기 원소들 중 임의의 것을 포함한 합금, 상기 원소들 중 임의의 것을 결합하여 포함한 합금 막 등이 제공될 수 있다. 또한, 망간, 마그네슘, 지르코늄, 베릴륨, 및 이트륨으로부터 선택된 하나 이상의 재료들이 사용될 수 있다. 또한, 상기 도전막은 단층 구조 또는 두 개 이상의 충들의 적층 구조를 가질 수 있다. 예를 들면, 실리콘을 포함한 알루미늄막의 단층 구조, 티타늄 막이 알루미늄막 위에 적층되는 2-층 구조, 티타늄 막, 알루미늄막, 및 티타늄 막이 순서대로 적층되는 3-층 구조 등이 제공될 수 있다. 대안적으로, 알루미늄(Al) 및 티타늄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 및 스칸듐(Sc)으로부터 선택된 하나 이상의 원소들을 포함하는 막, 합금 막, 또는 질화막이 사용될 수 있다.

- [0282] 열 처리가 상기 도전막의 성막 후 수행되는 경우에, 상기 도전막은 상기 열 처리를 견디기에 충분히 높은 내 열성을 갖는 것이 바람직하다.

- [0283] 레지스트 마스크가 제 3 포토리소그래피 단계에 의해 상기 도전 막 위에 형성되며 소스 전극층(315a) 및 드레인 전극층(315b)이 선택적 에칭에 의해 형성되고, 그 후 상기 레지스트 마스크가 제거된다(도 11c 참조).

- [0284] 상기 제 3 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 노광이 자외선 광, KrF 레이저 광, 또는 ArF 레이저 광을 사용하여 수행될 수 있다. 형성될 박막 트랜지스터의 채널 길이(L)는 상기 산화물 반도체층 (331) 위에서 서로에 인접하는, 상기 소스 전극층의 하단 및 상기 드레인 전극층의 하단 사이의 거리에 의해 결정된다. 노광이 25 nm 미만의 채널 길이(L)에 대해 수행되는 경우에, 상기 제 3 포토리소그래피 단계에서 상기 레지스트 마스크의 형성시 상기 노광은 수 나노미터 내지 수십 나노미터의 매우 짧은 파장을 가진 초자 외선 광을 사용하여 수행된다. 초자외선 광에 의한 상기 노광에서, 상기 해상도는 높으며 초점 심도는 크다. 따라서 상기 박막 트랜지스터의 상기 채널 길이(L)는 10 nm 내지 1000 nm가 되게 할 수 있고, 회로의 동작 속도는 증가될 수 있으며, 낮은 전력 소비가 매우 작은 오프-상태 전류에 의해 달성될 수 있다.

- [0285] 각각의 재료 및 에칭 조건들은 상기 산화물 반도체층(331)이 상기 도전막의 에칭에 의해 제거되지 않도록 적절하게 조정된다는 것을 주의하자.

- [0286] 이 실시형태에서, 상기 Ti 막이 상기 도전막으로서 사용되고 상기 In-Ga-Zn-O-계 산화물 반도체가 상기 산화물 반도체층(331)으로서 사용되기 때문에, 암모늄 과산화수소수(암모니아, 물, 및 과산화수소수의 혼합액)가 에천트로서 사용된다.

- [0287] 제 3 포토리소그래피 단계에서, 몇몇 경우들에서, 상기 산화물 반도체층(331)의 일부가 에칭되며, 그에 의해 홈(오목한 부분)을 가진 산화물 반도체층이 형성될 수 있다. 상기 소스 전극층(315a) 및 상기 드레인 전극층 (315b)을 형성하기 위해 사용된 상기 레지스트 마스크는 잉크젯 방법에 의해 형성될 수 있다. 잉크젯 방법에 의한 상기 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며, 따라서 제작 비용이 감소될 수 있다.

- [0288] 또한, 산화물 도전층이 상기 산화물 반도체층과 상기 소스 및 드레인 전극층들 사이에 형성될 수 있다. 상기 산화물 도전층과 상기 소스 및 드레인 전극층들을 형성하기 위해 상기 금속층이 연속하여 형성될 수 있다. 상기 산화물 도전층은 소스 영역 및 드레인 영역으로서 기능할 수 있다.

- [0289] 상기 산화물 반도체층과 상기 소스 및 드레인 전극층들 사이에 상기 소스 영역 및 상기 드레인 영역으로서 상기 산화물 도전층을 제공함으로써, 상기 소스 영역 및 상기 드레인 영역의 저항은 감소될 수 있고 상기 트랜지스터는 고속으로 동작될 수 있다.

- [0290] 상기 포토리소그래피 단계에서 포토마스크들 및 단계들의 수를 감소시키기 위해, 에칭은 복수의 강도들을 갖도록 광이 투과되는 노광 마스크인 다계조 마스크를 사용하여 형성된 레지스트 마스크를 사용하여 수행될 수 있다. 다계조 마스크를 사용하여 형성된 레지스트 마스크는 복수의 두께들을 갖고 에칭을 수행함으로써 형상이 추가로 변경될 수 있기 때문에, 상기 레지스트 마스크는 상이한 패턴들을 제공하기 위해 복수의 에칭 단계들에 사용될 수 있다. 그러므로, 적어도 두 종류들의 상이한 패턴들에 대응하는 레지스트 마스크가 하나의 다계조 마스크를 사용함으로써 형성될 수 있다. 따라서, 노광 마스크들의 수는 감소될 수 있고 대응하는 포토리소그래피 단계들의 수가 또한 감소될 수 있으며, 그에 의해 상기 제작 프로세스의 단순화가 실현될 수 있다.

- [0291] 다음으로, №0, №, 또는 Ar과 같은 가스를 사용한 플라즈마 처리가 수행된다. 이러한 플라즈마 처리에 의해, 노출되는 상기 산화물 반도체층의 표면상에 흡착된 물 등이 제거된다. 플라즈마 처리는 산소 및 아르곤의 혼합 가스를 사용하여 수행될 수 있다.

- [0292] 상기 플라즈마 처리 후, 보호 절연막으로서 기능하고 상기 산화물 반도체층의 일부와 접촉하는 산화물 절연층 (316)이 대기에 노출하지 않고 형성된다.

- [0293] 상기 산화물 절연층(316)은 스퍼터링 방법과 같이, 적절하게, 물 또는 수소와 같은 불순물이 상기 산화물 절연층(316)에 혼입되지 않는 방법에 의해 적어도 1 nm의 두께로 형성될 수 있다. 수소가 상기 산화물 절연층 (316)에 포함될 때, 상기 산화물 반도체층으로의 상기 수소의 혼입, 또는 수소가 상기 산화물 반도체층에서 산소를 추출하여 산소 결손이 발생할 수 있고, 그에 의해 상기 산화물 반도체층의 백채널이 (n-형이 되도록) 낮은 저항을 갖게 하여, 기생 채널이 형성될 수 있도록 한다. 그러므로, 상기 산화물 절연층(316)이 가능한 한 적은 수소를 포함하여 형성되도록 수소가 사용되지 않는 형성 방법이 이용되는 것이 중요하다.

- [0294] 이 실시형태에서, 200-nm-두께의 산화 실리콘막이 스퍼터링 방법에 의해 상기 산화물 절연층(316)으로서 성막된다. 성막시 상기 기판 온도는 실온 이상 300℃ 이하일 수 있으며, 이 실시형태에서는 100℃이다. 상기 산화실리콘막은 희가스(대표적으로, 아르곤) 분위기, 산소 분위기, 또는 희가스 및 산소를 포함한 혼합 분위기에

서 스퍼터링 방법에 의해 형성될 수 있다. 또한, 타겟으로서 산화 실리콘 타겟 또는 실리콘 타겟을 사용할 수 있다. 예를 들면, 실리콘 타겟의 사용으로, 산화 실리콘이 산소 및 질소의 분위기에서 스퍼터링 방법에 의해 성막될 수 있다. 저항이 감소되는 상기 산화물 반도체층과 접촉하여 형성되는 상기 산화물 절연층(316)으로서, 수분, 수소 이온, 또는 OH 와 같은 불순물들을 포함하지 않고 외부로부터 이들 불순물들의 혼입을 차단하는 무기 절연막이 사용된다. 대표적으로, 산화 실리콘막, 산화질화 실리콘막, 산화 알루미늄막, 산화질화 알루미늄막 등이 사용된다.

- [0295] 상기 경우에, 상기 산화물 절연층(316)의 성막에 있어서 상기 처리실에서의 잔여 수분을 제거하는 것이 바람 직하다. 이것은 상기 산화물 반도체층(331) 및 상기 산화물 절연층(316)이 수소, 수산기, 또는 수분을 포함하는 것을 방지하기 위한 것이다.

- [0296] 상기 처리실로부터 잔여 수분을 제거하기 위해, 바람직하게는 흡착형 진공 펌프가 사용된다. 예를 들면, 바람 직하게는 크라이오펌프, 이온 펌프, 또는 티타늄 서블리메이션 펌프가 사용된다. 배기 수단으로서, 콜드 트랩이 부가되는 터보 분자 펌프가 사용될 수 있다. 크라이오 펌프를 사용하여 배기가 수행되는 상기 성막실에서, 예를 들면, 수소 분자, 물(H<sub>2</sub>0)과 같은 수소 원자를 포함한 화합물 등이 배기된다. 따라서, 상기 성막실에서 형성된 상기 산화물 절연층(316)에 포함된 불순물들의 농도는 감소될 수 있다.

- [0297] 수소, 물, 수산기, 또는 수소화물과 같은 불순물이 1 ppm 이하, 바람직하게는 10 ppb 이하로 제거되는 고-순도 가스가 상기 산화물 절연층(316)의 성막을 위한 상기 스퍼터링 가스로서 사용되는 것이 바람직하다.

- [0298] 다음으로, 제 2 열 처리(바람직하게는 200℃ 내지 400℃의 온도로, 예를 들면, 250℃ 내지 350℃의 온도로)가 불활성 가스 분위기 또는 산소 가스 분위기에서 수행된다. 예를 들면, 상기 제 2 열 처리는 질소 분위기에서 1시간 동안 250℃로 수행된다. 상기 제 2 열 처리로 상기 산화물 반도체층의 일부(상기 채널 형성 영역)가 상기 산화물 절연층(316)과 접촉하는 상태에서 가열된다.

- [0299] 상기 프로세스를 통해, 탈수화 또는 탈수소화를 위한 열 처리가 상기 저항을 감소시키기 위해 상기 성막된 산화물 반도체막에 수행되며, 따라서 상기 산화물 반도체막의 일부가 과잉 산소를 선택적으로 포함하게 한다. 그 결과, 상기 게이트 절연층(311)에 중첩하는 채널 형성 영역(313)은 i-형이 되며, 상기 소스 전극층(315a)을 중첩시키고 저-저항 산화물 반도체를 사용하여 형성되는 고-저항 소스 영역(314a) 및 상기 드레인 전극층(315b)을 중첩시키고 상기 저-저항 산화물 반도체를 사용하여 형성되는 고-저항 드레인 영역(314b)이 자기 정합적으로 형성된다. 상기 단계들을 통해, 상기 박막 트랜지스터(310)가 형성된다(도 11d 참조).

- [0300] 더욱이, 열 처리는 1시간 내지 30시간 동안 대기 중에서 100℃ 내지 200℃의 온도로 수행될 수 있다. 이 실시형태에서. 열 처리는 10시간 동안 150℃로 수행된다. 이러한 열 처리는 일정한 가열 온도에서 수행될 수 있다. 대안적으로, 상기 가열 온도에서의 다음의 변화가 복수 회 반복적으로 행해질 수 있다: 상기 가열 온도는 실온에서 100℃ 내지 200℃의 온도로 증가되며 그 후 실온으로 감소된다. 또한, 이러한 열 처리는 상기 산화물 절연막의 형성 전에 감소된 압력 하에서 수행될 수 있다. 상기 감소된 압력 하에서, 상기 열 처리 시간은 단축될 수 있다. 이러한 열 처리로, 수소는 상기 산화물 반도체층에서 상기 산화물 절연층으로 도입되며; 따라서 노멀리-오프 박막 트랜지스터가 획득될 수 있다. 그러므로, 상기 액정 표시 장치의 신뢰성은 향상될 수 있다. 또한, 상기 산화물 절연층으로서 많은 결함들을 포함하는 산화 실리콘층을 사용함으로써, 상기 산화물 반도체층에 포함된 수소, 수분, 수산기, 또는 수소화물과 같은 불순물들은 상기 산화물 반도체층에 포함된 상기 불순물들을 추가로 감소시키기 위해 이러한 열 처리에 의해 상기 산화물 절연층으로 확산된다.

- [0301] 상기 고-저항 드레인 영역(314b)(또는 상기 고-저항 소스 영역(314a))은 상기 드레인 전극층(315b)(또는 상기 소스 전극층(315a))에 중첩하는 상기 산화물 반도체층의 일부에 형성되어, 상기 박막 트랜지스터의 신뢰성이 증가될 수 있도록 한다. 구체적으로, 상기 고-저항 드레인 영역(314b)의 형성에 의해, 상기 도전성은 상기 트랜지스터에서 상기 드레인 전극층(315b)으로부터 상기 고-저항 드레인 영역(314b) 및 상기 채널 형성 영역(313)으로 점차 변화할 수 있다. 그러므로, 상기 박막 트랜지스터가 고 전원 전위(VDD)를 공급하기 위한 배선에 접속된 상기 드레인 전극층(315b)을 사용하여 동작하는 경우에, 상기 게이트 전극층(311) 및 상기 드레인 전극층(315b) 사이에 높은 전계가 인가될지라도 상기 고-저항 드레인 영역이 버퍼로서 작용하여 국소적으로 높은 전계가 인가되지 않으며, 따라서 상기 트랜지스터의 내압은 향상될 수 있다.

- [0302] 상기 고-저항 소스 영역 또는 상기 고-저항 드레인 영역은 상기 산화물 반도체층이 15 nm 이하만큼 얇은 경우에 상기 산화물 반도체층에서의 상기 막 두께 방향으로 전체가 형성될 수 있는 반면, 상기 산화물 반도체층이 30 nm 내지 50 nm만큼 두꺼운 경우에, 상기 산화물 반도체층의 일부, 즉, 상기 소스 또는 드레인 전극층과 접

촉하는 상기 산화물 반도체층의 영역 및 그 근방의 저항은 감소될 수 있어서, 상기 고-저항 소스 영역 또는 상기 고-저항 드레인 영역이 형성되고 상기 게이트 절연층에 가까운 상기 산화물 반도체층의 영역은 i-형이 되게 할 수 있다.

- [0303] 보호 절연층은 상기 산화물 절연층(316) 위에 형성될 수 있다. 예를 들면, 질화 실리콘막은 RF 스퍼터링 방법에 의해 형성된다. RF 스퍼터링 방법은 바람직하게는 그것이 높은 생산성을 갖기 때문에 보호 절연층을 형성하기 위한 하나의 방법으로서 바람직하다. 상기 보호 절연층으로서, 수분, 수소 이온, 또는 OH-과 같은 불순물들을 포함하지 않고 그 외부로부터 이들 불순물들의 혼입을 차단하는 무기 절연막이 사용되고; 질화 실리콘막, 질화 알루미늄막, 질화산화 실리콘막, 질화산화 알루미늄막 등이 사용된다. 이 실시형태에서, 보호 절연층(303)은 상기 보호 절연층으로서 질화 실리콘막을 사용하여 형성된다(도 11e 참조).

- [0304] 이 실시형태에서 상기 보호 절연층(303)으로서, 상기 산화물 절연층(316)까지 및 이를 포함하는 층들이 형성되는 상기 기판(300)을 100℃ 내지 400℃의 온도로 가열하고, 수소 및 수분이 제거된 고-순도 질소를 포함한스퍼터링 가스를 도입하며, 실리콘 반도체의 타켓을 사용함으로써 질화 실리콘막이 형성된다. 상기 경우에, 상기 산화물 절연층(316)의 경우와 같이 상기 보호 절연층(303)의 형성시 잔여 수분이 상기 처리실로부터 제거되는 것이 또한 바람직하다.

- [0305] 평탄화를 위한 평탄화 절연층이 상기 보호 절연층(303) 위에 제공될 수 있다.

- [0306] 상기 산화물 반도체층을 사용한 상기 박막 트랜지스터를 포함한 액정 표시 장치의 표시부의 복수의 화소들에 서, 오프-상태 전류는 감소될 수 있다. 따라서, 저장 용량 소자가 전압을 유지할 수 있는 기간을 연장하고 정지 화상 등을 표시할 때 전력 소비를 감소시킬 수 있는 액정 표시 장치가 획득될 수 있다.

- [0307] 이 실시형태는 다른 실시형태들에 기술된 임의의 상기 구성들과 적절하게 결합하여 구현될 수 있다.

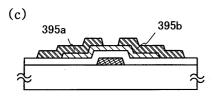

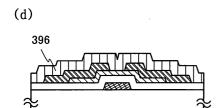

- [0308] (실시형태 7)

- [0309] 이 실시형태에서, 본 명세서에 개시된 액정 표시 장치에 적용될 수 있는 박막 트랜지스터의 또 다른 예가 기술될 것이다. 이 실시형태에서 기술된 박막 트랜지스터(360)는 실시형태 1의 상기 박막 트랜지스터(106)로서 사용될 수 있다.

- [0310] 이 실시형태의 박막 트랜지스터 및 상기 박막 트랜지스터를 제작하기 위한 방법의 일 실시형태가 도 12a 내지 도 12d를 사용하여 기술된다.