(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년08월29일

(11) 등록번호 10-1301312

(24) 등록일자 2013년08월22일

- (51) 국제특허분류(Int. Cl.)

**G09G 3/36** (2006.01) **G09G 3/20** (2006.01)

**G02F 1/133** (2006.01)

- (21) 출원번호 10-2008-0032638

(22) 출원일자 2008년04월08일

심사청구일자 2011년11월02일

(65) 공개번호 10-2009-0107238

(43) 공개일자 2009년10월13일

(56) 선행기술조사문헌

JP08184809 A\*

KR1020060088872 A\*

US20040070581 A1

US5892494 A

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

**엘지디스플레이 주식회사**

서울특별시 영등포구 여의대로 128(여의도동)

- (72) 발명자

**장수혁**

대구광역시 북구 팔거천동로24길 40, 영남2차타운

103동 902호 (동천동)

**이환주**

대구광역시 동구 팔공산로9길 21 (덕곡동)

**차동훈**

경상북도 구미시 인동36길 24-5, B 인의주공아파트

202동 1509호 (진평동)

- (74) 대리인

**특허법인로얄**

전체 청구항 수 : 총 12 항

심사관 : 양성지

(54) 발명의 명칭 액정표시장치와 그 구동방법

**(57) 요약**

본 발명은 액정표시장치와 그 구동방법에 관한 것이다.

이 액정표시장치는 데이터라인들과 게이트라인들이 교차되고 액정셀들이 매트릭스 형태로 배치된 액정표시패널; 디지털 비디오 데이터들과 임계치를 비교하여 그 비교 결과에 근거하여 상기 디지털 비디오 데이터들의 극성이 편향될 때 수평극성 변환신호의 논리를 반전시키는 수평극성 제어부; 상기 디지털 비디오 데이터들을 정극성/부극성 데이터전압들로 변환하고 상기 수평극성 변환신호에 응답하여 상기 데이터전압들의 수평 극성 반전주기를 조정하는 데이터 구동회로; 및 상기 게이트라인들에 스캔신호를 공급하는 게이트 구동회로를 구비한다.

**대 표 도 - 도5**

## 특허청구의 범위

### 청구항 1

데이터라인들과 게이트라인들이 교차되고 액정셀들이 매트릭스 형태로 배치된 액정표시패널;

디지털 비디오 데이터들과 임계치를 비교하여 그 비교 결과에 근거하여 상기 디지털 비디오 데이터들의 극성이 편향될 때 수평극성 변환신호의 논리를 반전시키는 수평극성 제어부;

상기 디지털 비디오 데이터들을 정극성/부극성 데이터전압들로 변환하고 상기 수평극성 변환신호에 응답하여 상기 데이터전압들의 수평 극성 반전주기를 조정하는 데이터 구동회로; 및

상기 게이트라인들에 스캔신호를 공급하는 게이트 구동회로를 구비하며,

상기 임계치는,

상기 디지털 비디오 데이터의 값과 비교되는 제1 임계치;

상기 제1 임계치 이상의 상기 디지털 비디오 데이터들 중에서 정극성 데이터전압으로 표시될 데이터의 개수와 부극성 데이터전압으로 표시될 데이터의 개수의 차이와 비교되는 제2 임계치; 및

한 프레임기간 동안 상기 제2 임계치 이상으로 극성이 편향된 언밸런스 라인들의 총합과 비교되는 제3 임계치를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 논리가 반전된 수평극성 변환신호는 상기 데이터 구동회로를 제어하여 다음 프레임기간 동안 상기 데이터 전압들의 수평극성 반전주기를 제어하는 것을 특징으로 하는 액정표시장치.

### 청구항 3

삭제

### 청구항 4

제 1 항에 있어서,

상기 수평극성 제어부는,

상기 디지털 비디오 데이터들 중에서 상기 제3 임계치 이상의 데이터들을 추출하고 추출된 데이터들 중에서 정극성 데이터의 개수를 카운트하여 정극성 카운트 총합과 부극성 데이터의 개수를 카운트하여 부극성 카운트 총합을 발생하는 극성 카운터;

상기 액정표시패널의 수평 라인마다 상기 정극성 카운트 총합과 상기 부극성 카운트 총합의 차이를 계산하고 그 차이가 상기 제2 임계치 이상인 수평 라인을 상기 언밸런스 라인으로 카운트하여 언밸런스 라인 카운트 값을 발생하는 언밸런스 라인 카운터;

상기 한 프레임기간 동안 누적된 상기 언밸런스 라인 카운트값이 상기 제3 임계치 이상일 때 상기 액정표시패널에 표시될 데이터의 수평 극성 반전주기를 다르게 제어하기 위한 제어신호를 발생하는 언밸런스 총합 판정부; 및

상기 제어신호에 응답하여 상기 수평극성 변환신호의 논리를 반전시키는 수평 극성 변환신호 발생부를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 5

제 1 항에 있어서,

상기 데이터 구동회로는,

상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의

수평극성 반전주기를 넓히는 것을 특징으로 하는 액정표시장치.

#### 청구항 6

제 5 항에 있어서,

상기 데이터 구동회로는,

상기 수평극성 변환신호에 따라 상기 다음 프레임기간에서 상기 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 수평 1 도트 인버전 형태로부터 수평 2 도트 인버전 형태로 넓히는 것을 특징으로 하는 액정표시장치.

#### 청구항 7

제 1 항에 있어서,

상기 데이터 구동회로는,

상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 좁히는 것을 특징으로 하는 액정표시장치.

#### 청구항 8

제 7 항에 있어서,

상기 데이터 구동회로는,

상기 수평극성 변환신호에 따라 상기 다음 프레임기간에서 상기 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 수평 2 도트 인버전 형태로부터 수평 1 도트 인버전 형태로 좁히는 것을 특징으로 하는 액정표시장치.

#### 청구항 9

데이터라인들과 게이트라인들이 교차되고 액정셀들이 매트릭스 형태로 배치된 액정표시패널을 구비하는 액정표시장치의 구동방법에 있어서,

디지털 비디오 데이터들과 임계치를 비교하여 그 비교 결과에 근거하여 상기 디지털 비디오 데이터들의 극성이 편향될 때 수평극성 변환신호의 논리를 반전시키는 단계;

상기 디지털 비디오 데이터들을 정극성/부극성 데이터전압들로 변환하고 상기 수평극성 변환신호에 응답하여 상기 데이터전압들의 수평 극성 반전주기를 조정하는 단계; 및

상기 게이트라인들에 스캔신호를 공급하는 단계를 포함하며,

상기 임계치는,

상기 디지털 비디오 데이터의 값과 비교되는 제1 임계치;

상기 제1 임계치 이상의 상기 디지털 비디오 데이터들 중에서 정극성 데이터전압으로 표시될 데이터의 개수와 부극성 데이터전압으로 표시될 데이터의 개수의 차이와 비교되는 제2 임계치; 및

한 프레임기간 동안 상기 제2 임계치 이상으로 극성이 편향된 언밸런스 라인들의 총합과 비교되는 제3 임계치를 포함하는 것을 특징으로 하는 액정표시장치의 구동방법.

#### 청구항 10

제 9 항에 있어서,

상기 논리가 반전된 수평극성 변환신호는 다음 프레임기간 동안 상기 데이터전압들의 수평극성 반전주기를 제어하는 것을 특징으로 하는 액정표시장치의 구동방법.

#### 청구항 11

삭제

## 청구항 12

제 9 항에 있어서,

상기 수평극성 변환신호의 논리를 반전시키는 단계는,

상기 디지털 비디오 데이터들 중에서 상기 제3 임계치 이상의 데이터들을 추출하고 추출된 데이터들 중에서 정극성 데이터의 개수를 카운트하여 정극성 카운트 총합과 부극성 데이터의 개수를 카운트하여 부극성 카운트 총합을 발생하는 단계;

상기 액정표시패널의 수평 라인마다 상기 정극성 카운트 총합과 상기 부극성 카운트 총합의 차이를 계산하고 그 차이가 상기 제2 임계치 이상인 수평 라인을 상기 언밸런스 라인으로 카운트하여 언밸런스 라인 카운트 값을 발생하는 단계;

상기 한 프레임기간 동안 누적된 상기 언밸런스 라인 카운트값이 상기 제3 임계치 이상일 때 상기 액정표시패널에 표시될 데이터의 수평 극성 반전주기를 다르게 제어하기 위한 제어신호를 발생하는 단계; 및

상기 제어신호에 응답하여 상기 수평극성 변환신호의 논리를 반전시키는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 구동방법.

## 청구항 13

제 9 항에 있어서,

상기 데이터전압들의 수평 극성 반전주기를 조정하는 단계는,

상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 넓히는 것을 특징으로 하는 액정표시장치의 구동방법.

## 청구항 14

제 9 항에 있어서,

상기 데이터전압들의 수평 극성 반전주기를 조정하는 단계는,

상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 좁히는 것을 특징으로 하는 액정표시장치의 구동방법.

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001]

본 발명은 액정표시장치와 그 구동방법에 관한 것이다.

#### 배경 기술

[0002]

액티브 매트릭스(Active Matrix) 구동방식의 액정표시장치는 스위칭 소자로서 박막트랜지스터(Thin Film Transistor : 이하 "TFT"라 함)를 이용하여 동영상을 표시하고 있다. 이 액정표시장치는 음극선관(Cathode Ray Tube, CRT)에 비하여 소형화가 가능하여 휴대용 정보기기, 사무기기, 컴퓨터 등에서 표시기에 응용됨은 물론, 텔레비전에도 응용되어 음극선관을 빠르게 대체하고 있다.

[0003]

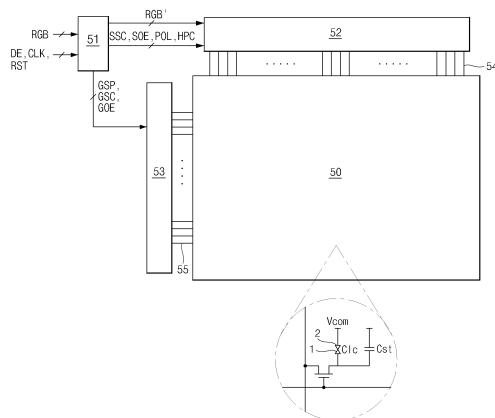

액정표시장치에서 화질을 검사하기 위하여, 도 1과 같은 테스트 패턴이 액정표시장치의 검사공정에서 이용될 수 있다. 검사 공정은 도 1과 같이 화이트 계조전압이 충전되는 픽셀과 블랙 계조전압이 충전되는 픽셀이 교번되는 스트라이프 패턴을 액정표시장치에 인가하여 스트라이프 패턴을 일정시간 동안 표시한 후에, 표시화면의 중간부분의 픽셀들에 인가되는 전압을 화이트 계조와 블랙 계조 사이의 중간계조 전압으로 조정한다. 그 결과, 화면의 위치에 따라 공통전압의 캐리어가 발생하여 크로스 토크(Cross talk)가 발생된다. 이는 액정셀의 화소전극과 공통전극의 커플링에 의해 화소전극에 인가되는 데이터전압의 변화에 따라 공통전극에 인가되는 공통전

압이 쉬프트되기 때문이다.

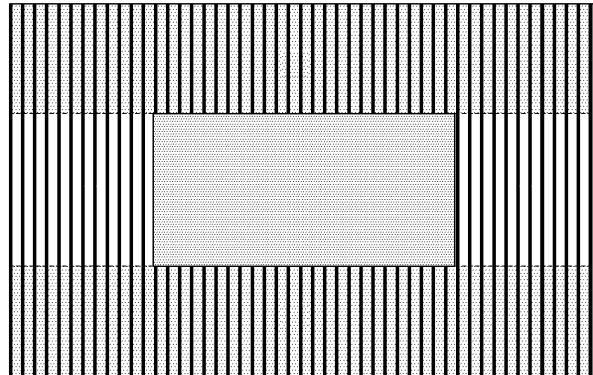

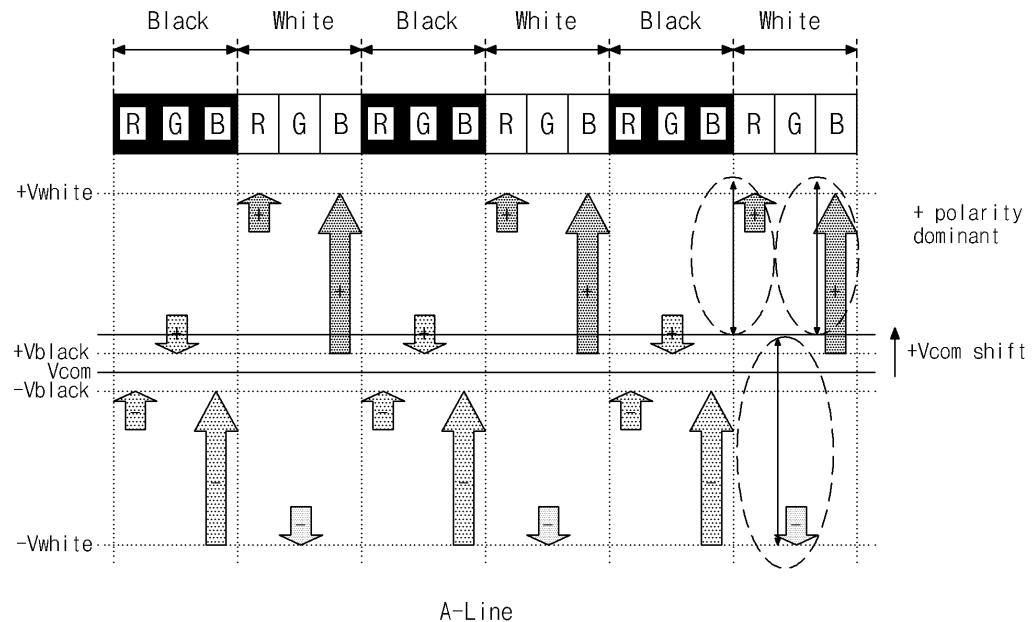

[0004] 액정표시장치에 인가되는 데이터전압은 액정의 직류화를 억제하기 위하여 그 극성이 주기적으로 반전된다. 도 1과 같은 테스트 패턴을 액정표시장치에 표시할 때 데이터전압의 극성은 도 2와 같다. 도 2는 도 1의 테스트 패턴의 일부에 데이터전압의 극성을 표시한 도면이다. 일반적인 영상이 입력될 때와 마찬가지로 테스트 패턴의 데이터 전압은 수평 및 수직 1 도트 인버전 방식으로 반전된다. 수평 및 수직 1 도트 인버전 형태은 수평방향으로 이웃한 액정셀들에 공급되는 데이터전압의 극성이 서로 반대이고, 수직방향으로 이웃한 액정셀들의 극성이 서로 반대이다. 도 1과 같은 테스트 패턴의 데이터들의 극성을 수평 및 수직 1 도트 인버전 형태으로 반전시키면 녹색 셀들이 밝게 보이는 녹색조 현상(greenish)이 나타나고, 이웃한 라인들 사이에 휘도차가 발생된다. 이는 액정표시장치에 충전되는 데이터전압의 극성이 어느 한 극성으로 편향되기 때문이다. 이를 도 3 및 도 4를 결부하여 설명하기로 한다.

[0005] 도 3을 참조하면, A 라인에서 화이트 데이터전압이 인가되는 픽셀들을 보면 R 데이터 전압과 B 데이터전압의 극성이 정극성이고, G 데이터전압의 극성이 부극성이다. 따라서, A 라인에서는 정극성 데이터전압이 부극성 데이터전압에 비하여 우세하다.(+ polarity dominant) 그 결과, A 라인에서 공통전압(Vcom)의 리플(Ripple)이 정극성 쪽으로 증가하여 공통전압(Vcom)이 정극성 쪽으로 쉬프트(shift)된다. 또한, 이전 프레임기간에서 정극성 블랙전압(+Vblack)으로 인가되었던 G 데이터전압이 현재 프레임기간에서 부극성 화이트전압(-Vwhite)으로 변화기 때문에 G 데이터전압의 전압차가 커지므로 A 라인에서 녹색조 현상이 나타난다.

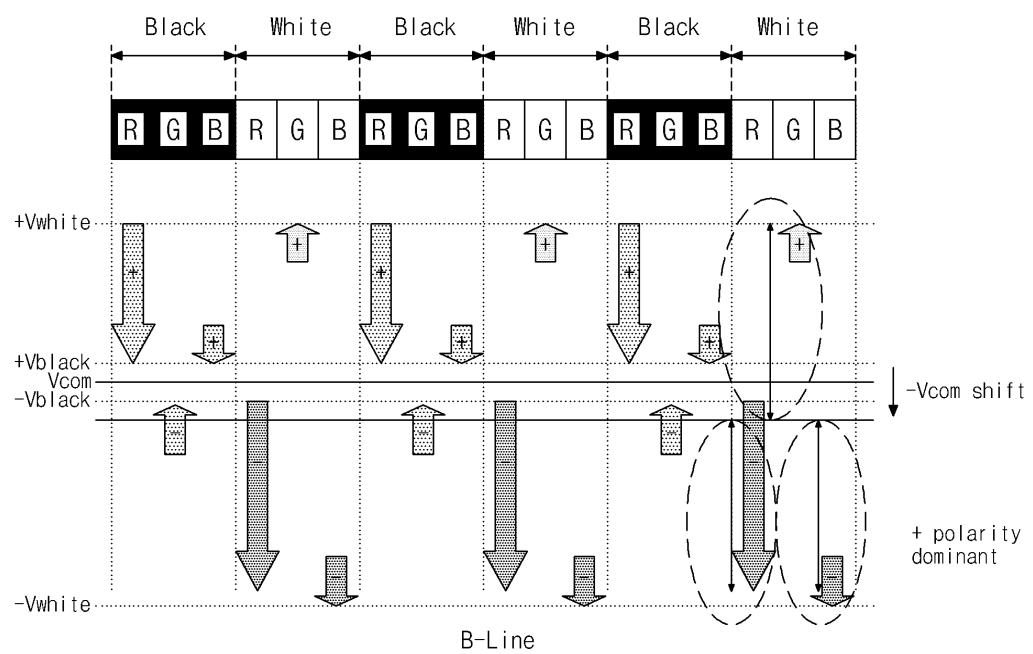

[0006] 도 4를 참조하면, B 라인에서 화이트 데이터전압이 인가되는 픽셀들을 보면 R 데이터 전압과 B 데이터전압의 극성이 부극성이고, G 데이터전압의 극성이 정극성이다. 따라서, B 라인에서는 정극성 데이터전압이 부극성 데이터전압에 비하여 우세하다.(- polarity dominant) 그 결과, B 라인에서 공통전압(Vcom)의 리플이 부극성 쪽으로 증가하여 공통전압(Vcom)이 부극성 쪽으로 쉬프트된다. 또한, 이전 프레임기간에서 부극성 블랙전압(-Vblack)으로 인가되었던 G 데이터전압이 현재 프레임기간에서 정극성 화이트전압(+Vwhite)으로 변화기 때문에 G 데이터전압의 전압차가 커지므로 B 라인에서도 녹색조 현상이 나타난다.

[0007] 따라서, 이웃한 픽셀들에서 데이터전압의 전압차가 화이트 전압과 블랙 전압처럼 커지는 데이터들이 입력될 때 종래의 액정표시장치는 데이터전압의 극성 편향으로 인하여 녹색조 현상, 스메어(smear) 현상 및 크로스토크가 발생된다. 이로 인하여, 종래의 액정표시장치는 일부 취약 패턴의 데이터들에서 표시품질이 떨어진다.

## 발명의 내용

### 해결 하고자하는 과제

[0008] 본 발명의 목적은 상기 종래 기술의 문제점을 해결하고자 안출된 발명으로써 데이터의 극성 편향을 예방하여 표시품질을 높이도록 한 액정표시장치와 그 구동방법을 제공하는데 있다.

### 과제 해결수단

[0009] 상기 목적을 달성하기 위하여, 본 발명의 실시예에 따른 액정표시장치는 데이터라인들과 게이트라인들이 교차되고 액정셀들이 매트릭스 형태로 배치된 액정표시패널; 디지털 비디오 데이터들과 임계치를 비교하여 그 비교 결과에 근거하여 상기 디지털 비디오 데이터들의 극성이 편향될 때 수평극성 변환신호의 논리를 반전시키는 수평극성 제어부; 상기 디지털 비디오 데이터들을 정극성/부극성 데이터전압들로 변환하고 상기 수평극성 변환신호에 응답하여 상기 데이터전압들의 수평 극성 반전주기를 조정하는 데이터 구동회로; 및 상기 게이트라인들에 스캔신호를 공급하는 게이트 구동회로를 구비한다.

[0010] 상기 논리가 반전된 수평극성 변환신호는 상기 데이터 구동회로를 제어하여 다음 프레임기간 동안 상기 데이터 전압들의 수평극성 반전주기를 제어한다.

[0011] 상기 임계치는 상기 디지털 비디오 데이터의 값과 비교되는 제1 임계치; 상기 제1 임계치 이상의 상기 디지털 비디오 데이터들 중에서 정극성 데이터전압으로 표시될 데이터의 개수와 부극성 데이터전압으로 표시될 데이터의 개수의 차이와 비교되는 제2 임계치; 및 한 프레임기간 동안 상기 제2 임계치 이상으로 극성이 편향된 언밸런스 라인들의 총합과 비교되는 제3 임계치를 포함한다.

- [0012] 상기 수평극성 제어부는 상기 디지털 비디오 데이터들 중에서 상기 제3 임계치 이상의 데이터들을 추출하고 추출된 데이터들 중에서 정극성 데이터의 개수를 카운트하여 정극성 카운트 총합과 부극성 데이터의 개수를 카운트하여 부극성 카운트 총합을 발생하는 극성 카운터; 상기 액정표시패널의 수평 라인마다 상기 정극성 카운트 총합과 상기 부극성 카운트 총합의 차이를 계산하고 그 차이가 상기 제2 임계치 이상인 수평 라인을 상기 언밸런스 라인으로 카운트하여 언밸런스 라인 카운트값을 발생하는 언밸런스 라인 카운터; 상기 한 프레임기간 동안 누적된 상기 언밸런스 라인 카운트값이 상기 제3 임계치 이상일 때 상기 액정표시패널에 표시될 데이터의 수평 극성 반전주기를 다르게 제어하기 위한 제어신호를 발생하는 언밸런스 총합 판정부; 및 상기 제어신호에 응답하여 상기 수평극성 변환신호의 논리를 반전시키는 수평 극성 변환신호 발생부를 포함한다.

- [0013] 상기 데이터 구동회로는 상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 넓힌다.

- [0014] 상기 데이터 구동회로는 상기 수평극성 변환신호에 따라 상기 다음 프레임기간에서 상기 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 수평 1 도트 인버전 형태로부터 수평 2 도트 인버전 형태로 넓힌다.

- [0015] 상기 데이터 구동회로는 상기 수평극성 변환신호에 따라 다음 프레임기간에서 상기 액정표시패널의 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 좁힌다.

- [0016] 상기 데이터 구동회로는 상기 수평극성 변환신호에 따라 상기 다음 프레임기간에서 상기 데이터라인들에 공급될 데이터전압의 수평극성 반전주기를 수평 2 도트 인버전 형태로부터 수평 1 도트 인버전 형태로 좁힌다.

- [0017] 본 발명의 실시예에 따른 액정표시장치의 구동방법은 디지털 비디오 데이터들과 임계치를 비교하여 그 비교 결과에 근거하여 상기 디지털 비디오 데이터들의 극성이 편향될 때 수평극성 변환신호의 논리를 반전시키는 단계; 상기 디지털 비디오 데이터들을 정극성/부극성 데이터전압들로 변환하고 상기 수평극성 변환신호에 응답하여 상기 데이터전압들의 수평 극성 반전주기를 조정하는 단계; 및 상기 게이트라인들에 스캔신호를 공급하는 단계를 포함한다.

## 효과

- [0018] 본 발명의 실시예에 따른 액정표시장치와 그 구동방법은 임계치 이상의 데이터들을 추출하고, 그 데이터들의 극성이 어느 일측으로 편향된 언밸런스 라인들이 소정의 수준 이상일 때 데이터의 수평 극성 반전 주기를 다르게 제어하여 극성의 편향을 해소한다. 그 결과, 본 발명의 실시예에 따른 액정표시장치와 그 구동방법은 데이터의 극성 편향을 예방하여 공통전압의 쉬프트 현상과 녹색조 현상 등을 방지하여 표시품질을 높일 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0019] 이하, 도 5 내지 도 13을 참조하여 본 발명의 바람직한 실시예에 대하여 설명하기로 한다.

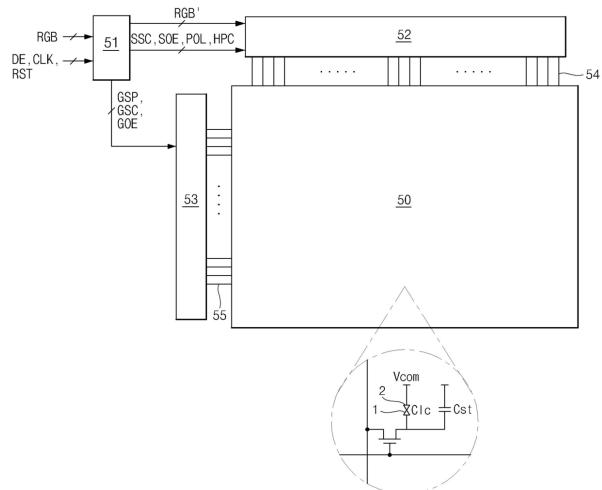

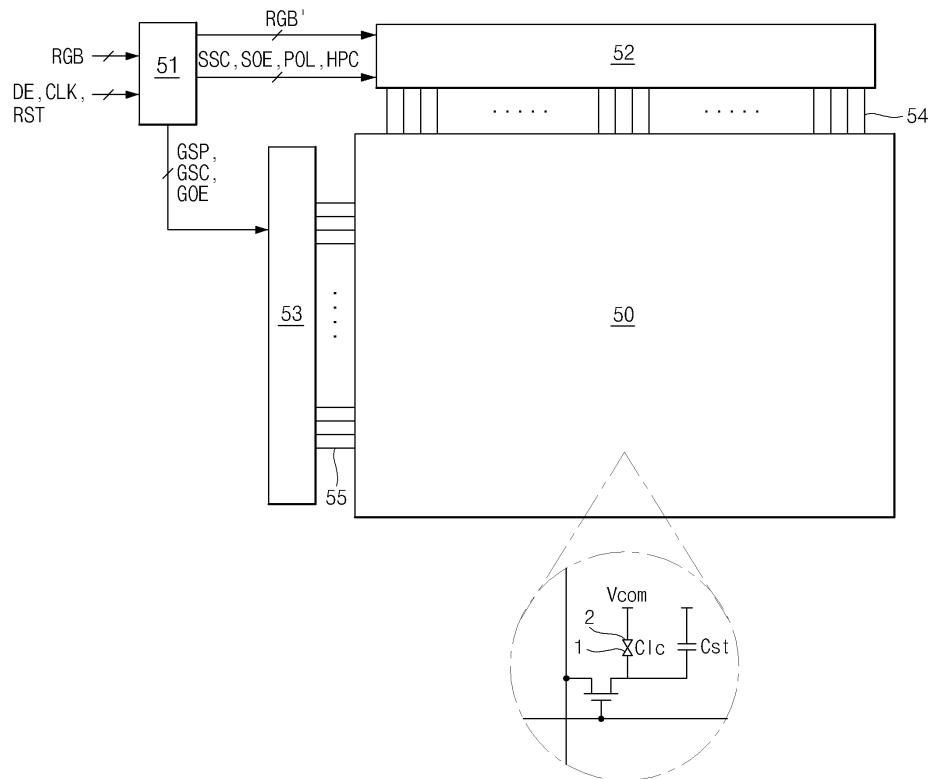

- [0020] 도 5를 참조하면, 본 발명의 실시예에 따른 액정표시장치는 액정표시패널(50), 타이밍 콘트롤러(51), 데이터 구동회로(52), 및 게이트 구동회로(53)를 구비한다. 데이터 구동회로(52)는 다수의 소스 드라이브 IC들을 포함한다. 게이트 구동회로(53)는 다수의 게이트 드라이브 IC들을 포함한다.

- [0021] 액정표시패널(50)은 두 장의 유리기판 사이에 액정층이 형성된다. 이 액정표시패널은 데이터라인들(54)과 게이트라인들(55)의 교차 구조에 의해 매트릭스 형태로 배치된 액정셀들(Cl)을 포함한다.

- [0022] 액정표시패널(50)의 하부 유리기판에는 데이터라인들(54), 게이트라인들(55), TFT들, 및 스토리지 커퍼시터(Cst)가 형성된다. 액정셀들(Cl)은 TFT에 접속되어 화소전극들(1)과 공통전극(2) 사이의 전계에 의해 구동된다. 액정표시패널(50)의 상부 유리기판 상에는 블랙매트릭스, 컬러필터 및 공통전극(2)이 형성된다. 공통전극(2)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직전계 구동방식에서 상부 유리기판 상에 형성되며, IPS(In Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평전계 구동방식에서 화소전극(1)과 함께 하부 유리기판 상에 형성된다. 액정표시패널(50)의 상부 유리기판과 하부 유리기판 각각에는 편광판이 부착되고 액정의 프리틸트각(pre-tilt angle)을 설정하기 위한 배향막이 형성된다.

- [0023] 타이밍 콘트롤러(51)는 데이터 구동회로(52)에 디지털 비디오 데이터(RGB')를 공급한다. 또한, 타이밍 콘트롤러(51)는 데이터 인에이블 신호(Data Enable, DE), 도트 클럭(CLK) 등의 타이밍신호를 입력받아 데이터 구동회

로(52)와 게이트 구동회로(53)의 동작 타이밍을 제어하기 위한 제어신호들을 발생한다. 제어신호들은 게이트 구동회로(53)의 동작 타임을 제어하기 위한 게이트 타이밍 제어신호, 데이터 구동회로(52)의 동작 타이밍과 데이터전압의 수직 극성을 제어하기 위한 데이터 타이밍 제어신호, 및 데이터전압의 수평 극성을 제어하기 위한 수평 극성 변환신호(Horizontal Polarity conversion, HPC)를 포함한다. 타이밍 콘트롤러(51)는 입력 데이터를 미리 저장된 임계치와 비교하여 액정표시패널(50)에 공급될 데이터전압의 극성이 편향될 수 있는 데이터를 판정하고, 그 결과 극성이 편향되는 데이터에서 수평 극성 변환신호(HPC)를 반전시킨다.

[0024] 게이트 타이밍 제어신호는 게이트 스타트 펄스(Gate Start Pulse, GSP), 게이트 쉬프트 클럭(Gate Shift Clock, GSC), 게이트 출력 인에이블신호(Gate Output Enable, GOE1 내지 GOE3) 등을 포함한다. 게이트 스타트 펄스(GSP)는 첫 번째 게이트펄스를 발생하는 게이트 드라이브 IC에 인가되어 첫 번째 게이트펄스가 발생되도록 그 게이트 드라이브 IC를 제어한다. 게이트 쉬프트 클럭(GSC)은 게이트 드라이브 IC들에 공통으로 입력되는 클럭신호로써 게이트 스타트 펄스(GSP)를 쉬프트시키기 위한 클럭신호이다. 게이트 출력 인에이블신호(GOE)는 게이트 드라이브 IC들의 출력을 제어한다.

[0025] 데이터 타이밍 제어신호는 소스 샘플링 클럭(Source Sampling Clock, SSC), 극성제어신호(Polarity : POL), 및 소스 출력 인에이블신호(Source Output Enable, SOE) 등을 포함한다. 소스 샘플링 클럭(SSC)은 라이징 또는 폴링 에지에 기준하여 데이터 구동회로(52) 내에서 데이터의 샘플링 동작을 제어하는 클럭신호이다. 극성제어신호(POL)는 데이터 구동회로(52)로부터 출력되는 데이터전압의 수직 극성을 제어한다. 소스 출력 인에이블신호(SOE)는 데이터 구동회로(52)의 출력을 제어한다.

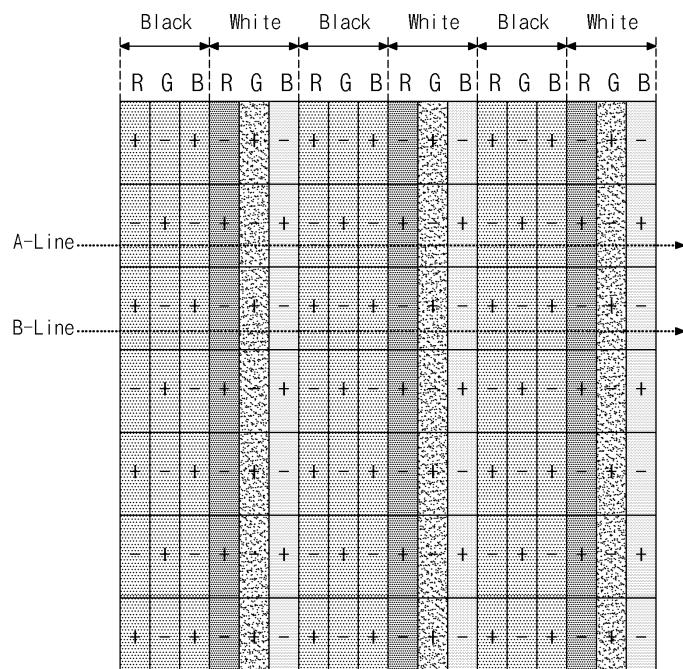

[0026] 수평 극성 변환신호(HPC)는 액정표시패널(50)에 입력되는 데이터전압들의 극성이 어느 일측으로 편향되지 않는 데이터들이 입력될 때 로우 논리로 발생되는 반면, 액정표시패널(50)에 입력되는 데이터전압들의 극성이 어느 일측으로 편향될 수 있는 데이터들이 입력될 때 하이 논리로 발생된다. 수평 극성 변환신호(HPC)가 로우 논리이면, 데이터 구동회로(52)는 이웃한 출력 채널들을 통해 출력되는 데이터전압들의 극성을 수평 1 도트 인버전 형태으로 반전시킨다. 수평 극성 변환신호(HPC)가 하이 논리이면, 데이터 구동회로(52)는 이웃한 출력 채널들을 통해 출력되는 데이터전압들의 극성을 수평 2 도트 인버전 형태으로 반전시킨다. 수평 1 도트 인버전 형태에서 수평으로 이웃하는 데이터전압들은 도 13과 같이 1 도트(또는 1 액정셀) 단위로 극성이 반전된다. 수평 2 도트 인버전 형태에서 수평으로 이웃하는 데이터전압들은 도 14와 같이 2 도트(또는 2 액정셀) 단위로 극성이 반전된다.

[0027] 데이터 구동회로(52)의 데이터 드라이브 IC들 각각은 쉬프트 레지스터, 래치, 디지털-아날로그 변환기, 출력 버퍼 등을 포함한다. 데이터 구동회로(52)는 타이밍 콘트롤러(51)의 제어 하에 디지털 비디오 데이터(RGB')를 래치한다. 그리고 데이터 구동회로(52)는 디지털 비디오 데이터(RGB')를 극성제어신호(POL)에 따라 아날로그 정극성/부극성 감마보상전압으로 변환하여 정극성/부극성 아날로그 데이터전압을 발생하고 그 데이터전압을 데이터라인들(54)에 공급한다. 또한, 데이터 구동회로(52)는 수평 극성 변환신호(HPC)에 응답하여 수평방향으로 이웃하는 데이터전압들의 극성 반전 주기를 제어한다.

[0028] 게이트 구동회로(53)는 게이트 타이밍 제어신호들에 응답하여 게이트펄스를 게이트라인들(55)에 순차적으로 공급한다. 이러한 게이트 드라이브 IC들(631 내지 633)은 도 7과 같이 구성된다.

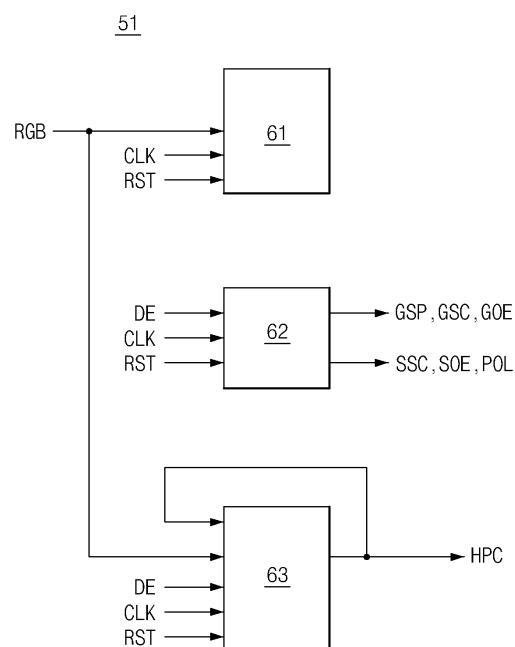

[0029] 도 6은 타이밍 콘트롤러(51)를 상세히 나타낸다.

[0030] 도 6을 참조하면, 타이밍 콘트롤러(51)는 데이터 처리부(61), 게이트/데이터 타이밍 신호 발생부(62), 및 수평 극성 제어부(63)를 구비한다.

[0031] 데이터 처리부(61)는 도트 클럭(CLK)에 따라 입력 디지털 비디오 데이터(RGB)를 샘플링하고 mini LVDS(low-voltage differential signaling) 방식으로 데이터(RGB')와 함께 mini LVDS 클럭을 데이터 구동회로(52)에 전송한다.

[0032] 게이트/데이터 타이밍 신호 발생부(62)는 도트 클럭(CLK)에 따라 데이터 인에이블신호(DE)를 카운트하여 게이트 타이밍 제어신호와 데이터 타이밍 제어신호를 발생한다.

[0033] 수평극성 제어부(63)는 디지털 비디오 데이터(RGB), 피드백된 수평 극성 변환신호(HPC), 데이터 인에이블신호(DE), 도트 클럭(CLK) 등을 입력받아 수평 1 도트 인버전 형태를 기준으로 하여 각 라인에서 미리 저장된 제1 임계치 이상의 디지털 비디오 데이터에 대하여 극성을 판정한다. 수평극성 제어부(63)는 각 라인에서 정극성 총합과 부극성 총합의 차가 미리 저장된 제2 임계치 이상이면 그 라인을 극성이 편향된 언밸런스 라인(Unbalanced line)으로 판정한다. 한 화면에서 언밸런스 라인들의 개수가 제3 임계치 미만이면 수평극성 제어

부(63)는 데이터 구동회로(52)로부터 출력되는 데이터전압의 극성을 수평 1 도트 인버전 형태으로 제어하기 위하여 수평 극성 변환신호(HPC)를 로우 논리로 발생한다. 한 화면에서 언발런스 라인들의 개수가 미리 저장된 제3 임계치 이상이면 수평극성 제어부(63)는 데이터 구동회로(52)로부터 출력되는 데이터전압의 극성을 수평 2 도트 인버전 형태으로 제어하기 위하여 수평 극성 변환신호(HPC)를 하이 논리로 발생한다.

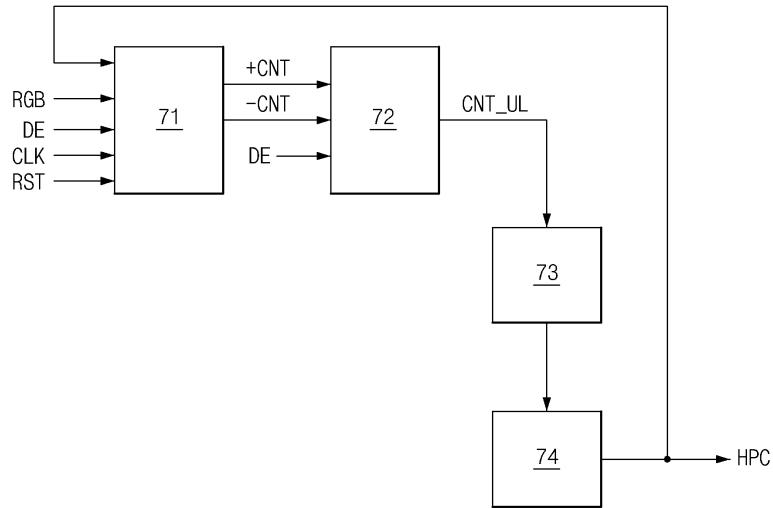

- [0034] 도 7은 수평극성 제어부(63)를 상세히 나타낸다.

- [0035] 도 7을 참조하면, 수평 극성 제어부(63)는 극성 카운터(71), 언발런스 라인 카운터(72), 언발런스 총합 판정부(73), 및 수평 극성 변환신호 발생부(74)를 구비한다.

- [0036] 극성 카운터(71)는 입력 디지털 비디오 데이터들(RGB)를 미리 저장된 제1 임계치와 비교하고, 제1 임계치 이상의 디지털 비디오 데이터들(RGB)을 추출한다. 제1 임계치는 중간 계조 이상의 디지털 비디오 데이터를 추출할 수 있도록 선택될 수 있다. 예컨대, 8 bits의 디지털 비디오 데이터에 의해 액정표시패널(50)이 256 계조로 데이터를 표시할 수 있다면 계조값이 64~255 사이인 디지털 비디오 데이터들의 최상위 2 비트(most significant bit, MSB)는 '01', '10', '11'이다. 이 경우에, 제1 임계치는 '01'로 결정될 수 있다. 이렇게 극성 카운터(71)는 디지털 비디오 데이터(RGB)의 최상위 비트를 제1 임계치와 비교할 수 있지만, 풀 비트 단위로 디지털 비디오 데이터(RGB)와 제1 임계치를 비교할 수 있다. 예컨대, 제1 임계치는 계조 값 '64'와 같은 '01000000'로 결정될 수 있다. 극성 카운터(71)는 제1 임계치와 디지털 비디오 데이터(RGB)를 비교하여, 디지털 비디오 데이터를 추출한다. 그리고 극성 카운터(71)는 수평 1 도트 인버전 형태의 극성 패턴을 기준으로 하여 추출된 디지털 비디오 데이터들 중에서 액정표시패널에 정극성 데이터전압으로 공급될 데이터를 카운트하여 액정표시패널(50)의 각 라인마다 1 라인에 표시될 유효 데이터 구간을 지시하는 1 데이터 인에이블신호(DE)내에서 누적된 정극성 카운트 총합(+CNT)과, 1 데이터 인에이블신호(DE) 내에서 누적된 부극성 카운트 총합(-CNT)을 출력한다. 극성 카운터(71)의 카운트값은 데이터 인에이블신호(DE)의 블랭킹 구간 내에서 리셋된다.

- [0037] 언발런스 라인 카운터(72)는 극성 카운터(71)로부터의 정극성 카운트 총합(+CNT)과 부극성 카운트 총합(-CNT)의 차이값을 산출하고, 그 차이값을 미리 저장된 제2 임계치와 비교한다. 제2 임계값은 1 라인에 포함된 데이터들의 총 개수의 50%에 해당하는 값으로 결정될 수 있다. 예컨대, XGA 해상도에서 1 라인에 포함된 데이터들은 1024(픽셀 수)×3(RGB)=3072이므로 제2 임계값은 XGA 해상도에서 1536으로 결정될 수 있다. 그리고 언발런스 라인 카운터(72)는 정극성 카운트 총합(+CNT)과 부극성 카운트 총합(-CNT)의 차이값과 제2 임계값의 비교를 통해 제2 임계값 이상으로 극성이 편향된 언발런스 라인을 카운트하여 언발런스 라인 카운트 값(CNT\_UL)을 출력한다. 언발런스 라인 카운터(72)의 카운트값은 1 프레임기간 단위로 리셋된다.

- [0038] 언발런스 총합 판정부(73)는 매 프레임기간마다 언발런스 라인 카운트 값(CNT\_UL)을 누적하여 그 누적값을 미리 저장된 제3 임계치와 비교한다. 제3 임계치는 N(N은 액정표시패널(50)의 수평 해상도 라인 수 이하의 양의 정수)로 선택된다. 예컨대, 제3 임계치는 10~50 사이의 정수로 선택될 수 있으나, 이에 한정되지 않고 액정표시패널(50)의 해상도나 화질에 따라 달라질 수 있다. 그리고 언발런스 총합 판정부(73)는 언발런스 라인의 개수에 따라 논리가 반전되는 제어신호를 발생하여 수평 극성 변환신호 발생부(74)의 출력을 제어한다.

- [0039] 수평 극성 변환신호 발생부(74)는 1 프레임기간 내에서 언발런스 라인의 개수가 제3 임계치 이상이면 수평 극성 변환신호(HPC)를 하이 논리로 발생한다. 그리고, 수평 극성 변환신호 발생부(74)는 1 프레임기간 내에서 언발런스 라인의 개수가 제3 임계치 미만이면 수평 극성 변환신호(HPC)를 로우 논리로 발생한다. 데이터 구동회로(52)는 수평 극성 변환신호(HPC)이 로우논리일 때 데이터전압의 극성을 수평 1 도트 인버전 형태로 반전시키고, 수평 극성 변환신호(HPC)이 하이논리일 때 데이터전압의 극성을 수평 2 도트 인버전 형태로 반전시킨다.

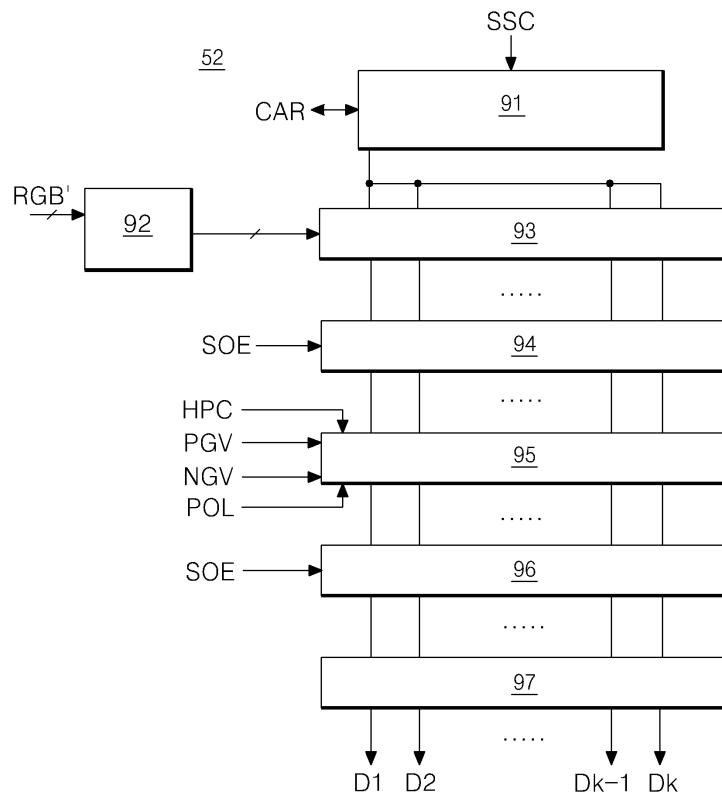

- [0040] 도 8은 데이터 구동회로(52)의 소스 드라이브 IC를 상세히 나타낸다.

- [0041] 도 8을 참조하면, 데이터 구동회로(52)의 소스 드라이브 IC 각각은 k(k는 양의 정수) 개의 데이터라인들(D1 내지 Dk)을 구동한다. 이를 위하여, 소스 드라이브 IC 각각은 쉬프트 레지스터(91), 데이터 레지스터(92), 제1 래치(93), 제2 래치(94), 디지털-아날로그 변환기(이하, "DAC"라 한다)(95), 차지쉐어회로(Charge Share Circuit)(96) 및 출력회로(97)를 포함한다.

- [0042] 쉬프트레지스터(91)는 소스 샘플링 클럭(SSC)에 따라 샘플링신호를 발생한다. 또한, 쉬프트 레지스터(91)는 다음 단의 소스 드라이브 IC에 캐리신호(CAR)를 전달한다. 데이터 레지스터(92)는 타이밍 콘트롤러(51)로부터의 디지털 비디오 데이터(RGB')를 일시 저장하고 그 데이터들을 제1 래치(93)에 공급한다. 제1 래치(93)는 쉬프트 레지스터(91)로부터 순차적으로 입력되는 샘플링신호에 응답하여 데이터 레지스터(92)로부터의 디지털 비디오 데이터들을 샘플링하고, 그 데이터들을 래치한 다음, 그 데이터들을 동시에 출력한다. 제2 래치(94)는 제1 래

치(93)로부터 입력되는 데이터를 래치한 다음, 소스 출력 인에이블신호(SOE)의 로우논리기간 동안 다른 소스 드라이브 IC들의 제2 래치(94)와 동시에 데이터들을 출력한다.

[0043] DAC(95)는 극성제어신호(POL)와 수평 극성 변환신호(HPC)에 응답하여 제2 래치(94)로부터의 디지털 비디오 데이터를 정극성 감마보상전압(PGV) 또는 부극성 감마보상전압(NGV)으로 변환함으로써 아날로그 정극성/부극성 데이터전압을 출력한다.

[0044] 차지쉐어회로(96)는 소스 출력 인에이블신호(SOE)의 하이논리기간 동안 이웃한 데이터 출력채널들을 단락(short)시켜 이웃한 데이터전압들의 평균값을 차지쉐어전압으로 출력하거나, 소스 출력 인에이블신호(SOE)의 하이논리기간 동안 데이터 출력채널들에 공통전압(Vcom)을 공급하여 정극성 데이터전압과 부극성 데이터전압의 급격한 변화를 줄인다.

[0045] 출력회로(97)는 버퍼를 포함하여 데이터라인(D1 내지 Dk)으로 공급되는 아날로그 데이터전압의 신호감쇠를 최소화한다.

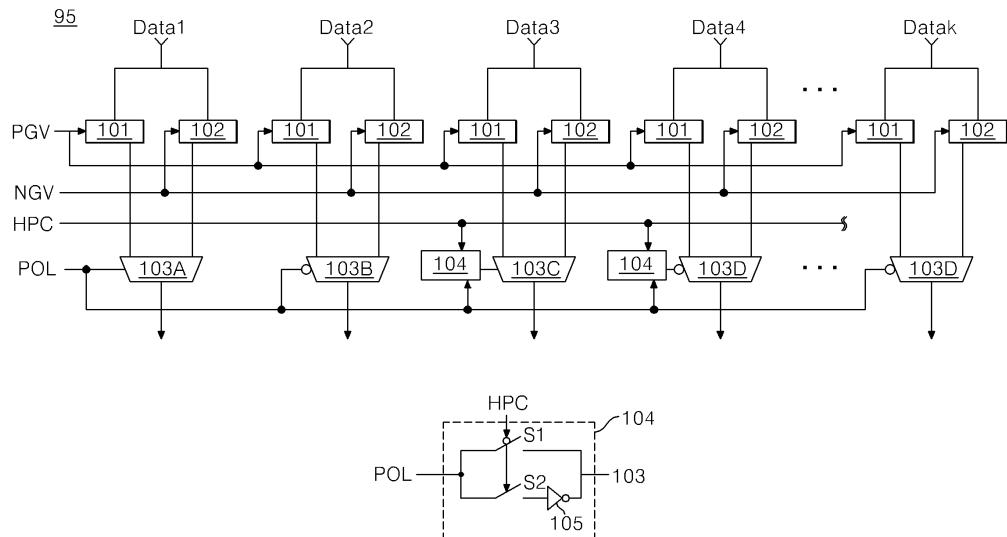

[0046] 도 9는 DAC(95)를 상세히 나타낸다.

[0047] 도 9를 참조하면, DAC(95)는 P-디코더(101), N-디코더(102), 멀티플렉서(103A 내지 103D), 수평출력 반전회로(104)를 구비한다.

[0048] P-디코더(101)는 디지털 비디오 데이터(DATA1 내지 DATAk)를 정극성 감마보상전압(PGV)으로 변환하여 아날로그 정극성 데이터전압을 발생한다. N-디코더(102)는 디지털 비디오 데이터(DATA1 내지 DATAk)를 부극성 감마보상전압(PGV)으로 변환하여 아날로그 부극성 데이터전압을 발생한다.

[0049] 제4i+1(i는 양의 정수) 멀티플렉서(103A)는 자신의 비반전 제어단자에 입력되는 극성제어신호(POL)에 응답하여 1 수평기간 단위로 아날로그 정극성 데이터전압과 아날로그 부극성 데이터전압을 교대로 선택한다. 제4i+2 멀티플렉서(103B)는 자신의 반전 제어단자에 입력되는 극성제어신호(POL)에 응답하여 1 수평기간 단위로 아날로그 정극성 데이터전압과 아날로그 부극성 데이터전압을 교대로 선택한다. 제4i+3 멀티플렉서(103C)는 자신의 비반전 제어단자에 입력되는 수평출력 반전회로(104)의 출력에 응답하여 1 수평기간 단위로 아날로그 정극성 데이터전압과 아날로그 부극성 데이터전압을 교대로 선택한다. 제4i+4 멀티플렉서(103D)는 자신의 반전 제어단자에 입력되는 수평출력 반전회로(104)의 출력에 응답하여 1 수평기간 단위로 아날로그 정극성 데이터전압과 아날로그 부극성 데이터전압을 교대로 선택한다.

[0050] 수평출력 반전회로(104)는 수평 극성 변환신호(HPC)에 응답하여 제4i+3 및 제4i+4 멀티플렉서들(103C, 103D)을 제어하여 수평 극성 변환신호(HPC)에 따라 수평방향에서 데이터전압의 극성반전주기를 제어한다. 수평출력 반전회로(104)는 스위치소자들(S1, S2), 및 인버터(105)를 구비한다. 제1 스위치소자(S1)의 입력단자에는 극성제어신호(POL)가 공급되고 그 출력단자는 제4i+3 또는 제4i+4 멀티플렉서(103C, 103D)의 반전/비반전 제어단자에 접속된다. 제1 스위치소자(S1)의 반전 제어단자에는 수평 극성 변환신호(HPC)가 공급된다. 제2 스위치소자(S2)의 입력단자에는 극성제어신호(POL)가 공급되고 그 출력단자는 인버터(105)에 접속된다. 제2 스위치소자(S2)의 비반전 제어단자에는 수평 극성 변환신호(HPC)가 공급된다. 인버터(105)는 제2 스위치소자(S2)의 출력단자와, 제4i+3 또는 제4i+4 멀티플렉서(103C, 103D)의 반전/비반전 제어단자에 접속되어 수평 극성 변환신호(HPC)에 따라 선택적으로 극성제어신호(POL)를 반전시킨다.

[0051] 수평 극성 변환신호(HPC)가 하이 논리이면, 제2 스위치소자(S2)는 턴-온되고 제1 스위치소자(S1)는 턴-오프된다. 그러면 제4i+3 멀티플렉서(103C)의 비반전 제어단자에는 인버터(105)에 의해 반전된 극성제어신호(POL)가 입력된다. 이와 동시에, 수평 극성 변환신호(HPC)가 하이 논리이면 제4i+4 멀티플렉서(103D)의 반전 제어단자에는 인버터(105)에 의해 반전된 극성제어신호(POL)가 입력된다.

[0052] 수평 극성 변환신호(HPC)가 로우 논리이면, 제1 스위치소자(S1)는 턴-온되고 제2 스위치소자(S2)는 턴-오프된다. 그러면 제4i+3 멀티플렉서(103C)의 비반전 제어단자에는 극성제어신호(POL)가 그대로 입력된다. 이와 동시에 수평 극성 변환신호(HPC)가 로우 논리이면 제4i+4 멀티플렉서(103D)의 반전 제어단자에는 극성제어신호들(POL)가 그대로 입력된다.

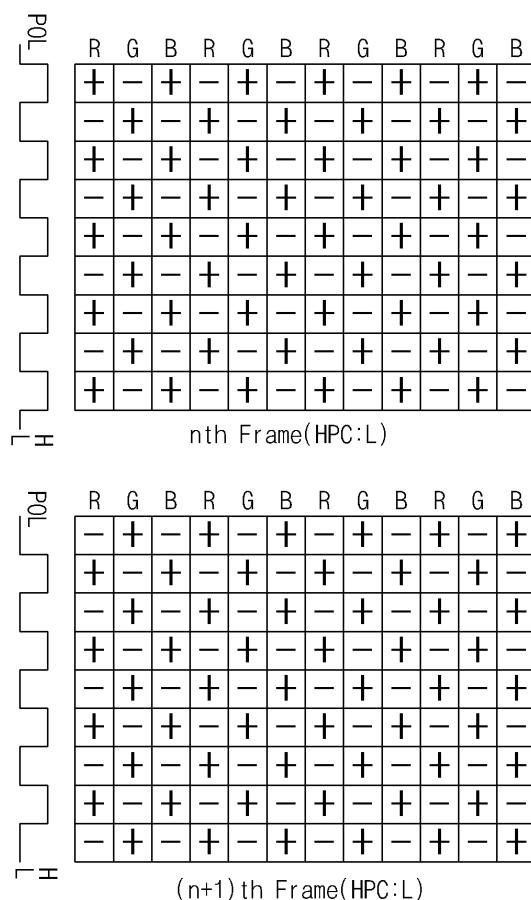

[0053] 따라서, 수평 극성 변환신호(HPC)가 로우 논리(HPC:L)이면 제4i+1 내지 제4i+4 데이터라인들에 공급되는 데이터의 수평 극성패턴은 도 13과 같이 제n(n은 양의 정수) 프레임기간 동안 "+ - + -"로, 제n+1 프레임기간 동안 "- + - +"로 발생된다. 이에 반하여, 수평 극성 변환신호(HPC)가 하이 논리(HPC:H)이면 제4i+1 내지 제4i+4 데이터라인들에 공급되는 데이터의 수평 극성패턴은 도 14와 같이 제n 프레임기간 동안 "+ - - +"로, 제n+1 프레임

기간 동안 "- + + -"로 발생된다.

- [0054] 도 10은 수평 1 도트 인버전 형태을 기준으로 데이터전압의 극성이 변환될 때 제1 임계치 이상의 데이터들에 대한 극성 카운트의 일예를 나타낸다.

- [0055] 디지털 비디오 데이터들(RGB)이 도 10과 같은 데이터 패턴으로 입력되고, 그 데이터들(RGB)의 극성이 수평 1 도트 인버전 형태으로 변환된다고 가정하면, 그 데이터전압의 극성은 정극성으로 편향된다.

- [0056] 이 데이터 패턴에서, 기수 픽셀 데이터들(PXL#1, PXL#3, PXL#5,...PXL#13)은 제1 임계치 이상의 R 데이터와, 제1 임계치 미만의 G 및 B 데이터를 포함한다. 우수 픽셀 데이터들(PXL#2, PXL#4, PXL#6,...PXL#14)은 제1 임계치 이상의 G 데이터와, 제1 임계치 미만의 R 및 B 데이터를 포함한다. 각 픽셀 데이터들(PXL#1 내지 PXL#14)에서 제1 임계치 이상의 데이터 극성은 수평 1 도트 인버전 형태의 극성 패턴에 따라 모두 정극성인데 반하여, 제1 임계치 미만의 데이터 극성은 부극성 또는 부극성이다.

- [0057] 타이밍 콘트롤러(51)는 제1 임계치 미만의 데이터에 대하여 카운트를 하지 않으므로 제1 및 제2 픽셀 데이터들(PXL#1, PXL#2)이 입력될 때 정극성 카운트 총합(+CNT)을 '2' 만큼 증가시키는 반면, 부극성 카운트 총합(-CNT)을 증가시키지 않는다. 제3 및 제4 픽셀 데이터들(PXL#3, PXL#4)이 입력될 때 타이밍 콘트롤러(51)는 정극성 카운트 총합(+CNT)을 '2' 만큼 더 증가시키는 반면, 부극성 카운트 총합(-CNT)을 증가시키지 않는다. 제5 및 제6 픽셀 데이터들(PXL#5, PXL#6)이 입력될 때 타이밍 콘트롤러(51)는 정극성 카운트 총합(+CNT)을 '2' 만큼 더 증가시키는 반면, 부극성 카운트 총합(-CNT)을 증가시키지 않는다. 이와 같은 카운트 동작을 계속한 후, 제14 픽셀 데이터(PXL#14)까지 카운트한 결과는 정극성 카운트 총합(+CNT)은 '14'로 증가된 반면, 부극성 카운트 총합(-CNT)은 '0'이다. 따라서, 타이밍 콘트롤러(51)는 도 10과 같은 데이터 패턴이 입력되고, 그 극성 차이가 제2 임계치 이상이며 한 화면에서 제2 임계치 이상으로 극성이 편향된 언밸런스 라인들의 개수가 제3 임계치 이상이면 현재 프레임기간 동안 입력되는 데이터 패턴을 극성이 일측으로 편향될 수 있는 데이터 패턴으로 판정한다. 이 경우, 타이밍 콘트롤러(51)는 현재 프레임기간 동안 발생되는 수평 극성 변환신호(HPC)를 반전시켜 도 11과 같이 다음 프레임기간 동안 데이터전압의 수평 극성을 수평 2 도트 인버전 형태으로 제어한다.

- [0058] 도 11을 참조하면, 타이밍 콘트롤러(51)는 도 10과 같은 데이터 패턴이 입력될 때 수평 극성 변환신호(HPC)를 하이 논리로 발생한다. 따라서, 제1, 제2, 제5, 제6, 제9, 제10, 제13 및 제14 픽셀 데이터들(PXL#1, PXL#2, PXL#5, PXL#6, PXL#9, PXL#10, PXL#13, PXL#14)은 정극성의 데이터전압으로 변환될 제1 임계치 이상의 R 및 G 데이터를 포함한다. 이에 반하여, 제3, 제4, 제7, 제8, 제11 및 제12 픽셀 데이터들(PXL#3, PXL#4, PXL#7, PXL#8, PXL#11, PXL#12)은 부극성의 데이터전압으로 변환될 제1 임계치 이상의 R 및 G 데이터를 포함한다.

- [0059] 타이밍 콘트롤러(51)는 제1 임계치 미만의 데이터에 대하여 카운트를 하지 않으므로 제1 및 제2 픽셀 데이터들(PXL#1, PXL#2)이 입력될 때 정극성 카운트 총합(+CNT)을 '2' 만큼 증가시키는 반면, 부극성 카운트 총합(-CNT)을 증가시키지 않는다. 제3 및 제4 픽셀 데이터들(PXL#3, PXL#4)이 입력될 때 타이밍 콘트롤러(51)는 정극성 카운트 총합(+CNT)을 증가시키지 않는 반면, 부극성 카운트 총합(-CNT)을 '2' 만큼 증가시킨다. 제5 및 제6 픽셀 데이터들(PXL#5, PXL#6)이 입력될 때 타이밍 콘트롤러(51)는 정극성 카운트 총합(+CNT)을 '2' 만큼 더 증가시키는 반면, 부극성 카운트 총합(-CNT)을 증가시키지 않는다. 제7 및 제8 픽셀 데이터들(PXL#3, PXL#4)이 입력될 때 타이밍 콘트롤러(51)는 정극성 카운트 총합(+CNT)을 증가시키지 않는 반면, 부극성 카운트 총합(-CNT)을 '2' 만큼 더 증가시킨다. 따라서, 이 라인의 디지털 비디오 데이터들이 액정패시페널(50)에 공급될 때 이터전압으로 변환되면 그 극성이 어느 일측으로 과도하게 편향되지 않는다. 따라서, 이 라인에서 공통전압이 쉬프트되지 않고 녹색조 현상이 나타나지 않는다.

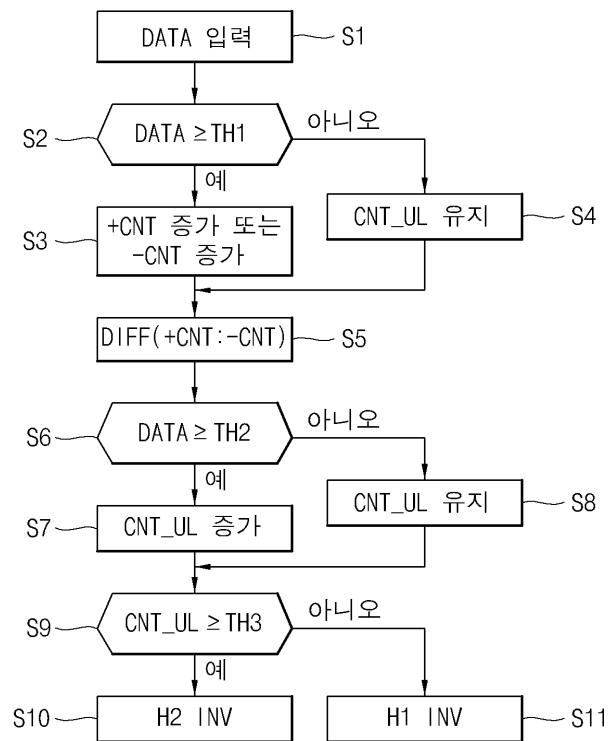

- [0060] 도 12는 본 발명의 실시예에 따른 액정표시장치의 구동방법을 단계적으로 나타낸다.

- [0061] 도 12를 참조하면, 본 발명의 실시예에 따른 액정표시장치의 구동방법은 입력 디지털 비디오 데이터를 제1 임계치(TH1)와 비교한다.(S1, S2)

- [0062] 제1 임계치(TH1) 이상의 디지털 비디오 데이터들에 대하여 수평 1 도트 인버전 형태을 기준으로 하여 극성이 카운트된다.(S3) 제1 임계치(TH1) 미만의 디지털 비디오 데이터들은 극성이 카운트되지 않는다.(S4)

- [0063] 본 발명의 실시예에 따른 액정표시장치의 구동방법은 액정표시패널(50)의 수평 라인마다 정극성 카운트 총합(+CNT)과 부극성 카운트 총합(-CNT)의 차이를 계산하고, 그 극성 차이값(DIFF(+CNT:-CNT))을 제2 임계치(TH2)와 비교한다.(S5, S6) 본 발명의 실시예에 따른 액정표시장치의 구동방법은 극성 차이값(DIFF(+CNT:-CNT))이 제2 임계치(TH2) 이상인 라인들을 언밸런스 라인으로 판정하고, 언밸런스 라인 카운트 값(CNT\_UL)을 증가시킨다.(S7) 극성 차이값(DIFF(+CNT:-CNT))이 제2 임계치(TH2) 미만인 라인에서 언밸런스 라인 카운트 값(CNT\_UL)

은 증가되지 않는다.(S8)

[0064] 본 발명의 실시예에 따른 액정표시장치의 구동방법은 한 프레임기간 동안 누적된 언밸런스 라인 카운트 값(CNT\_UL)을 제3 임계치(TH3)와 비교한다.(S9) 언밸런스 라인 카운트 값(CNT\_UL)이 제3 임계치(TH3) 이상이면 본 발명의 실시예에 따른 액정표시장치의 구동방법은 수평 극성 변환신호(HPC)를 하이 논리로 발생하여 데이터 구동회로(52)로부터 출력되는 데이터전압의 극성을 도 14와 같은 수평 2 도트 인버전 형태으로 제어한다.(S10) 반면에, 언밸런스 라인 카운트 값(CNT\_UL)이 제3 임계치(TH3) 미만이면 본 발명의 실시예에 따른 액정표시장치의 구동방법은 수평 극성 변환신호(HPC)를 로우 논리로 발생하여 데이터 구동회로(52)로부터 출력되는 데이터전압의 극성을 도 13과 같은 수평 1 도트 인버전 형태으로 제어한다.(S11) 데이터 구동회로(52)는 수평극성 변환신호(HPC)에 따라 다음 프레임기간에서 액정표시패널(50)의 데이터라인들(54)에 공급될 데이터전압의 수평극성 반전주기를 수평 1 도트 인버전 형태로로부터 수평 2 도트 인버전 형태로 넓히거나 그 반대로 좁힌다.

[0065] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

## 도면의 간단한 설명

[0066] 도 1은 크로스 토크를 실험하기 위한 테스트 패턴을 보여 주는 도면.

[0067] 도 2는 도 1의 테스트 패턴의 일부를 확대하여 데이터 전압의 극성을 보여 주는 도면.

[0068] 도 3은 도 2에 도시된 A 라인(A-Line)에서 데이터전압의 극성 편향을 보여 주는 도면.

[0069] 도 4는 도 2에 도시된 B 라인(B-Line)에서 데이터전압의 극성 편향을 보여 주는 도면.

[0070] 도 5는 본 발명의 실시예에 따른 액정표시장치를 나타내는 블록도.

[0071] 도 6은 도 5에 도시된 타이밍 콘트롤러를 상세히 나타내는 블록도.

[0072] 도 7은 도 6에 도시된 수평극성 제어부를 상세히 나타내는 블록도.

[0073] 도 8은 도 5에 도시된 데이터 구동회로의 소스 드라이브 IC를 상세히 나타내는 블록도.

[0074] 도 9는 도 8에 도시된 디지털-아날로그 변환기를 상세히 나타내는 회로도.

[0075] 도 10은 수평 1 도트 인버전 형태를 기준으로 데이터전압의 극성이 변환될 때 제1 임계치 이상의 데이터들에 대한 극성 카운트의 일례를 나타내는 도면.

[0076] 도 11은 도 10과 같은 데이터 패턴에서 데이터전압의 극성을 수평 1 도트 인버전 형태으로 변환할 때 제1 임계치 이상의 데이터들에 대한 극성 카운트의 일례를 나타내는 도면.

[0077] 도 12는 본 발명의 실시예에 따른 액정표시장치의 구동방법을 단계적으로 나타내는 흐름도.

[0078] 도 13은 수평 극성 변환신호가 로우 논리일 때 발생되는 수평 1 도트 인버전 형태의 데이터 전압 극성을 보여 주는 도면.

[0079] 도 14는 수평 극성 변환신호가 하이 논리일 때 발생되는 수평 2 도트 인버전 형태의 데이터 전압 극성을 보여 주는 도면.

〈도면의 주요 부분에 대한 부호의 설명〉

|                            |                         |

|----------------------------|-------------------------|

| [0081] 50 : 액정표시패널         | 51 : 타이밍 콘트롤러           |

| [0082] 52 : 데이터 구동회로       | 53 : 게이트 구동회로           |

| [0083] 61 : 데이터 처리부        | 62 : 게이트/데이터 타이밍 신호 발생부 |

| [0084] 63 : 수평 극성 제어부      | 71 : 극성 카운터             |

| [0085] 72 : 언밸런스 라인 카운터    | 73 : 언밸런스 총합 판정부        |

| [0086] 74 : 수평 극성 변환신호 발생부 | 91 : 쉬프트 레지스터           |

| [0087] 92 : 데이터 레지스터       | 93 : 제1 래치              |

- |        |                      |                   |

|--------|----------------------|-------------------|

| [0088] | 94 : 제2 래치           | 95 : 디지털-아날로그 변환기 |

| [0089] | 96 : 차지쉐어회로          | 97 : 출력회로         |

| [0090] | 101 : P-디코더          | 102 : N-디코더       |

| [0091] | 103A 내지 103D : 멀티플렉서 | 104 : 수평출력 반전회로   |

## 도면

### 도면1

### 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

63

## 도면8

도면9

도면10

H1 INV (HPC:L)

## 도면11

H2 INV (HPC:H)

| PXL#1 | PXL#2 | PXL#3 | PXL#4 | PXL#5 | PXL#6 | PXL#7 | PXL#8 | PXL#9 | PXL#10 | PXL#11 | PXL#12 | PXL#13 | PXL#14 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|

| R     | G     | B     | R     | G     | B     | R     | G     | B     | R      | G      | B      | R      | G      |

| +/-   | -/+   | +/-   | -/+   | +/-   | +/-   | +/-   | +/-   | +/-   | +/-    | +/-    | +/-    | +/-    | +/-    |

| +CNT  | 2     | 2 + 0 | 2 + 2 | 4     | 4 + 2 | 6     | 6 + 2 |       |        |        |        |        |        |

| -CNT  | 0     | 2     | 2 + 0 | 2 + 2 | 4     | 4 + 2 | 6     |       |        |        |        |        |        |

## 도면12

## 도면13

## 도면14

nth Frame(HPC:H)

| POL | R | G | B | R | G | B | R | G | B | R | G | B |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|

| -   | + | - | - | + | + | - | - | + | + | - | - | + |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

(n+1)th Frame(HPC:H)

| POL | R | G | B | R | G | B | R | G | B | R | G | B |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

| +   | - | - | + | + | - | - | + | + | - | - | + | - |

| -   | + | + | - | - | + | + | - | - | + | + | - | - |

|                |                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 水平极性可以是水平极性。                                                                                        |         |            |

| 公开(公告)号        | <a href="#">KR101301312B1</a>                                                                       | 公开(公告)日 | 2013-08-29 |

| 申请号            | KR1020080032638                                                                                     | 申请日     | 2008-04-08 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                            |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                           |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                           |         |            |

| [标]发明人         | JANG SU HYUK<br>장수혁<br>LEE HWAN JOO<br>이환주<br>CHA DONG HOON<br>차동훈                                  |         |            |

| 发明人            | 장수혁<br>이환주<br>차동훈                                                                                   |         |            |

| IPC分类号         | G09G3/20 G09G G02F1/133 G02F G09G3/36                                                               |         |            |

| CPC分类号         | G09G3/3614 G09G2320/0242 G09G2320/0276 G09G3/3648 G09G3/3688 G09G3/2092 G09G2310 /027 G09G2320/0204 |         |            |

| 其他公开文献         | KR1020090107238A                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                           |         |            |

## 摘要(译)

本发明涉及液晶显示器及其驱动方法。该液晶显示器是数据线和LCD面板：比较栅极线交叉的数字视频数据和以矩阵和阈值的形式排列的液晶单元。以及用于将扫描信号提供给水平极性控制器的栅极驱动电路：数据驱动电路：将数字视频数据转换为直极/负数据电压，并响应水平极性转换信号调整数据电压的水平极性反转周期。栅极线反转水平极性转换信号的逻辑，包括基于比较结果的数字视频数据的极性被偏转。