(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0105505

(43) 공개일자 2012년09월25일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G02F 1/1345* (2006.01)

*G02F 1/1368* (2006.01)

- (21) 출원번호 10-2012-7017948

- (22) 출원일자(국제) 2010년11월19일

심사청구일자 **없음**

- (85) 번역문제출일자 2012년07월10일

- (86) 국제출원번호 PCT/JP2010/071192

- (87) 국제공개번호 WO 2011/074391

국제공개일자 2011년06월23일

- (30) 우선권주장

JP-P-2009-288312 2009년12월18일 일본(JP)

JP-P-2010-092111 2010년04월13일 일본(JP)

- (71) 출원인

가부시끼가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

- (72) 발명자

야마자키 순페이

일본국 2430036 가나가와Ken 아쓰기시 하세 398

가부시끼가이샤 한도오따이 에네루기 켄큐쇼 내

- (74) 대리인

황의만

전체 청구항 수 : 총 24 항

(54) 발명의 명칭 **액정 표시 장치 및 전자 기기**

### (57) 요 약

본 발명은 액정 표시 장치의 소비 전력을 저감하는 것 및 표시의 열화를 억제하는 것, 또한, 온도 등의 외부 인자에 의한 표시의 열화를 억제하는 것에 관한 것이다.

각 화소에 형성되는 트랜지스터로, 채널 형성 영역이 산화물 반도체층에 의해 구성되는 트랜지스터를 적용한다. 한편, 이 산화물 반도체층을 고순도화함으로써, 이 트랜지스터의 실온에서의 오프 전류값을  $10aA/\mu m$  이하, 또한  $85^{\circ}C$ 에서의 오프 전류값을  $100aA/\mu m$  이하로 하는 것이 가능하다. 이로 인해, 액정 표시 장치의 소비 전력을 저감하는 것 및 표시의 열화를 억제하는 것이 가능하게 된다. 또한, 상기한 바와 같이 이 트랜지스터는,  $85^{\circ}C$ 라는 고온에서도 오프 전류값을  $100aA/\mu m$  이하로 하는 것이 가능하다. 이로 인해, 온도 등의 외부 인자에 의한 액정 표시 장치의 표시의 열화를 억제할 수 있다.

### 대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

액정 표시 장치에 있어서,

매트릭스형으로 배열된 복수의 화소를 포함하고,

각각의 화소는

주사선 구동 회로에 의해 스위칭이 제어되는 트랜지스터와,

한쪽 단자에 신호선 구동 회로에서 상기 트랜지스터를 통하여 화상 신호가 입력되고, 다른 한쪽 단자에 공통 전위가 공급됨으로써, 상기 화상 신호에 따른 전압이 인가되는 액정 소자와,

상기 액정 소자에 인가되는 전압을 유지하는 용량 소자를 구비하고,

상기 주사선 구동 회로 및 상기 신호선 구동 회로의 동작을 제어하고, 상기 화소로의 상기 화상 신호의 입력을 선택하는 제어 회로를 갖고,

상기 트랜지스터는, 채널 형성 영역이 산화물 반도체층에 의해 구성되고,

오프 상태의 상기 트랜지스터를 통한 상기 화상 신호의 리크가, 상기 액정 소자를 통한 상기 화상 신호의 리크 보다 작은, 액정 표시 장치.

### 청구항 2

액정 표시 장치에 있어서,

매트릭스형으로 배열된 복수의 화소를 포함하고,

각각의 화소는

주사선 구동 회로에 의해 스위칭이 제어되는 트랜지스터와,

제 1 전극에 신호선 구동 회로에서 상기 트랜지스터를 통하여 화상 신호가 입력되고, 제 2 전극에 공통 전위가 공급됨으로써, 상기 화상 신호에 따른 전압이 인가되는 액정 소자와,

상기 제 1 전극에 입력되는 화상 신호를 유지하는 용량 소자를 구비하고,

상기 화소부에, 제 1 화상을 형성하기 위한 화상 신호 내지 제 n 화상 (n은 2 이상의 자연수)을 형성하기 위한 화상 신호를 기억하는 기억 회로와,

상기 제 k 화상(k는 n 미만의 자연수)을 형성하기 위한 화상 신호와 상기 제 k+1 화상을 형성하기 위한 화상 신호를 비교하고, 차이를 검출하는 비교 회로와,

상기 차이를 기초로, 상기 화소부로의 상기 제 k+1 화상을 형성하기 위한 화상 신호의 출력을 선택하는 선택 회로와,

상기 차이가 검출된 때에, 상기 주사선 구동 회로 및 상기 신호선 구동 회로로 제어 신호를 공급하고, 상기 차이가 검출되지 않은 때에, 상기 주사선 구동 회로 및 상기 신호선 구동 회로로 상기 제어 신호의 공급을 정지하는 것이 가능한 표시 제어 회로를 갖고,

상기 트랜지스터는, 채널 형성 영역이 산화물 반도체층에 의해 구성되고,

오프 상태의 상기 트랜지스터를 통한 상기 화상 신호의 리크가, 상기 액정 소자를 통한 상기 화상 신호의 리크 보다 작은, 액정 표시 장치.

### 청구항 3

액정 표시 장치에 있어서,

매트릭스형으로 배열된 복수의 화소를 포함하고,

각각의 화소는

트랜지스터와,

상기 트랜지스터를 통하여 화상 신호가 입력되도록 구성되는 단자를 포함하고, 상기 트랜지스터와 전기적으로 접속되는 액정 소자와,

상기 액정 소자에 인가되는 전압을 유지하는 용량 소자를 구비하고,

상기 트랜지스터는, 채널 형성 영역이 산화물 반도체층에 의해 구성되고,

오프 상태의 상기 트랜지스터를 통한 상기 화상 신호의 리크가, 상기 액정 소자를 통한 상기 화상 신호의 리크 보다 작은, 액정 표시 장치.

#### 청구항 4

제 1 항에 있어서,

상기 트랜지스터는, 실질적으로 진성이 되도록 형성된 산화물 반도체층으로 구성된 채널 형성 영역을 포함하는, 액정 표시 장치.

#### 청구항 5

제 2 항에 있어서,

상기 트랜지스터는, 실질적으로 진성이 되도록 형성된 산화물 반도체층으로 구성된 채널 형성 영역을 포함하는, 액정 표시 장치.

#### 청구항 6

제 3 항에 있어서,

상기 트랜지스터는, 실질적으로 진성이 되도록 형성된 산화물 반도체층으로 구성된 채널 형성 영역을 포함하는, 액정 표시 장치.

#### 청구항 7

제 1 항에 있어서,

상기 액정 소자가 갖는 액정 재료의 고유 저항율이,  $1 \times 10^{14} \Omega \cdot \text{cm}$ 를 넘는, 액정 표시 장치.

#### 청구항 8

제 2 항에 있어서,

상기 액정 소자가 갖는 액정 재료의 고유 저항율이,  $1 \times 10^{14} \Omega \cdot \text{cm}$ 를 넘는, 액정 표시 장치.

#### 청구항 9

제 3 항에 있어서,

상기 액정 소자가 갖는 액정 재료의 고유 저항율이,  $1 \times 10^{14} \Omega \cdot \text{cm}$ 를 넘는, 액정 표시 장치.

#### 청구항 10

제 1 항에 있어서,

상기 트랜지스터의 오프 전류가  $10\text{aA}/\mu\text{m}$  이하인, 액정 표시 장치.

#### 청구항 11

제 2 항에 있어서,

상기 트랜지스터의 오프 전류가  $10\text{aA}/\mu\text{m}$  이하인, 액정 표시 장치.

#### 청구항 12

제 3 항에 있어서,

상기 트랜지스터의 오프 전류가  $10\text{aA}/\mu\text{m}$  이하인, 액정 표시 장치.

#### 청구항 13

제 1 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하는, 액정 표시 장치.

#### 청구항 14

제 2 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하는, 액정 표시 장치.

#### 청구항 15

제 3 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하는, 액정 표시 장치.

#### 청구항 16

제 1 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하고,

상기 스위치는 채널 형성 영역이 산화물 반도체층으로 구성된 트랜지스터인, 액정 표시 장치.

#### 청구항 17

제 2 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하고,

상기 스위치는 채널 형성 영역이 산화물 반도체층으로 구성된 트랜지스터인, 액정 표시 장치.

### 청구항 18

제 3 항에 있어서,

상기 액정 소자로의 상기 공통 전위의 공급을 제어하는 스위치를 포함하고,

상기 스위치는 채널 형성 영역이 산화물 반도체층으로 구성된 트랜지스터인, 액정 표시 장치.

### 청구항 19

제 1 항에 있어서,

상기 용량 소자의 용량이, 1pF 이상인, 액정 표시 장치.

### 청구항 20

제 2 항에 있어서,

상기 용량 소자의 용량이, 1pF 이상인, 액정 표시 장치.

### 청구항 21

제 3 항에 있어서,

상기 용량 소자의 용량이, 1pF 이상인, 액정 표시 장치.

### 청구항 22

제 1 항에 기재된 액정 표시 장치를 갖는 전자 기기.

### 청구항 23

제 2 항에 기재된 액정 표시 장치를 갖는 전자 기기.

### 청구항 24

제 3 항에 기재된 액정 표시 장치를 갖는 전자 기기.

## 명세서

### 기술 분야

[0001]

본 발명은, 액정 표시 장치 및 이 액정 표시 장치를 갖는 전자 기기에 관한 것이다.

### 배경 기술

[0002]

액정 표시 장치는, 텔레비전 수상기 등의 대형 표시 장치에서 휴대 전화 등의 소형 표시 장치에 이르기까지

보급되어 있다. 이로 인해, 액정 표시 장치의 개발은, 저비용화 또는 고부가가치화를 목적으로 한 개발이 이루어지고 있다. 특히 근래에는, 지구 환경에의 관심이 높아지고, 저소비 전력형의 액정 표시 장치의 개발이 주목받고 있다.

[0003] 특허문헌 1에서는, 액정 표시 장치에서의 소비 전력을 저감하는 기술이 개시되어 있다. 구체적으로는, 모든 주사선 및 데이터 신호선을 비선택 상태로 하는 휴지 기간에, 모든 데이터 신호선을 전기적으로 데이터 신호 드라이버에서 절리하여 하이 임피던스 상태로 하는 액정 표시 장치가 개시되어 있다.

## 선행기술문헌

### 특허문헌

[0004] (특허문헌 0001) 일본국 특개 2001-312253호 공보

## 발명의 내용

### 해결하려는 과제

[0005] 일반적으로, 액정 표시 장치는, 매트릭스형으로 배열된 복수의 화소가 형성된 화소부를 갖는다. 이 화소는, 화상 신호의 입력을 제어하는 트랜지스터와, 입력되는 화상 신호에 따른 전압이 인가되는 액정 소자와, 이 액정 소자에 인가되는 전압을 유지하는 보조 용량을 갖는다. 한편, 이 액정 소자는 인가되는 전압에 따라 배향이 변화하는 액정 재료를 갖고, 이 액정 재료의 배향을 제어함으로써 각 화소의 표시가 제어된다.

[0006] 특허문헌 1에 개시된 액정 표시 장치에서는, 휴지 기간에서, 화소부에 포함되는 각 화소에 대해 화상 신호가 입력되지 않는다. 즉, 각 화소 내에 화상 신호를 유지한 채로, 화상 신호의 입력을 제어하는 트랜지스터가 오프 상태를 유지하는 기간이 장기화된다. 이로 인해, 이 트랜지스터를 통한 화상 신호의 리크가 각 화소의 표시에 대해 주는 영향이 현재화한다. 구체적으로는, 액정 소자에 인가되는 전압이 저하되고, 이 액정 소자를 갖는 화소의 표시의 열화(변화)가 현재화한다.

[0007] 나아가, 이 트랜지스터를 통한 화상 신호의 리크는, 트랜지스터의 동작 온도에 의해 변동한다. 구체적으로는, 동작 온도의 상승에 따라, 트랜지스터를 통한 화상 신호의 리크가 증가한다. 이로 인해, 특허문헌 1에 개시된 액정 표시 장치는, 환경의 변동이 큰 옥외 등에서 사용하였을 때, 표시 품질을 일정하게 유지하기 어렵다.

[0008] 따라서, 본 발명의 일 양태는, 액정 표시 장치의 소비 전력을 저감하는 것 및 표시의 열화(표시 품질의 저하)를 억제하는 것을 과제의 하나로 한다.

[0009] 또한, 본 발명의 일 양태는, 온도 등의 외부 인자에 대한 표시의 열화(표시 품질의 저하)가 억제된 액정 표시 장치를 제공하는 것을 과제의 하나로 한다.

### 과제의 해결 수단

[0010] 상기한 과제는, 각 화소에 형성되는 트랜지스터로, 채널 형성 영역이 산화물 반도체층에 의해 구성되는 트랜지스터를 적용함으로써 해결할 수 있다. 한편, 이 산화물 반도체층은, 전자 공여체(도너)가 되는 불순물(수소 또는 물 등)을 철저히 제거함으로써 고순도화된 산화물 반도체층이다. 이 트랜지스터로는, 채널 길이 10  $\mu\text{m}$ 인 경우에, 실온에서의 채널 폭 1  $\mu\text{m}$  당 오프 전류값을  $10\text{aA}(1 \times 10^{-17}\text{A})$  이하로 하는 것이 가능하다(이를  $10\text{aA}/\mu\text{m}$ 로 나타낸다).

[0011] 또한, 이 산화물 반도체층은, 2.0eV 이상, 바람직하게는 2.5eV 이상, 더욱 바람직하게는 3.0eV 이상의 밴드갭을 갖는다. 나아가, 이 산화물 반도체층은, 고순도화됨으로써, 도전형이 무한대로 진성형에 가까워진다. 이로 인해, 이 산화물 반도체층에서는, 열여기에 기인하는 캐리어의 발생을 억제할 수 있다. 그 결과, 이 트랜지스터의 동작 온도의 상승에 따른 오프 전류의 증가를 저감할 수 있다. 구체적으로는, 채널 길이 10  $\mu\text{m}$ 인 경

우에, 85°C에서의 채널 폭  $1\mu\text{m}$  당 오프 전류값을  $100\text{aA}(1 \times 10^{-16}\text{A})$  이하로 하는 것이 가능하다(이를  $100\text{aA}/\mu\text{m}$  라 표기한다).

[0012] 구체적으로는, 본 발명의 일 양태는, 주사선 구동 회로에 의해 스위칭이 제어되는 트랜지스터와, 한쪽 단자에 신호선 구동 회로에서 상기 트랜지스터를 통하여 화상 신호가 입력되고, 다른 한쪽 단자에 공통 전위가 공급됨으로써, 상기 화상 신호에 따른 전압이 인가되는 액정 소자와, 상기 액정 소자에 인가되는 전압을 유지하는 용량 소자와, 를 갖는 복수의 화소가 매트릭스형으로 배열된 액정 표시 장치로써, 상기 주사선 구동 회로 및 상기 신호선 구동 회로의 동작을 제어하고, 상기 화소로의 상기 화상 신호의 입력을 선택하는 제어 회로를 갖고, 상기 트랜지스터는, 채널 형성 영역이 산화물 반도체층에 의해 구성되고, 오프 상태의 상기 트랜지스터를 통한 상기 화상 신호의 리크가, 상기 액정 소자를 통한 상기 화상 신호의 리크 보다도 작은 것을 특징으로 하는 액정 표시 장치이다.

### 발명의 효과

[0013] 본 발명의 일 양태의 액정 표시 장치는, 각 화소에 형성되는 트랜지스터로, 채널 형성 영역이 산화물 반도체층에 의해 구성되는 트랜지스터를 적용한다. 한편, 이 산화물 반도체층을 고순도화함으로써, 이 트랜지스터의 실온에서의 오프 전류값을  $10\text{aA}/\mu\text{m}$  이하, 또한 85°C에서의 오프 전류값을  $100\text{aA}/\mu\text{m}$  이하로 하는 것이 가능하다. 이로 인해, 이 트랜지스터를 통한 화상 신호의 리크를 저감할 수 있다. 즉, 이 트랜지스터를 갖는 화소로의 화상 신호의 쓰기 빈도를 저감한 경우에서의 표시의 열화(변화)를 억제할 수 있다. 그 결과, 이 액정 표시 장치의 소비 전력을 저감하는 것 및 표시의 열화(표시 품질의 저하)를 억제할 수 있게 된다.

[0014] 또한, 상기한 바와 같이, 이 트랜지스터는, 85°C라는 고온에서도 오프 전류값을  $100\text{aA}/\mu\text{m}$  이하로 하는 것이 가능하다. 즉, 이 트랜지스터는, 동작 온도의 상승에 따른 오프 전류값의 증가가 현저하게 작은 트랜지스터이다. 이로 인해, 이 트랜지스터를 액정 표시 장치의 각 화소에 형성되는 트랜지스터로 적용함으로써, 온도 등의 외부 인자가 이 화소에서의 화상 신호의 리크에 가하는 영향을 저감할 수 있다. 즉, 이 액정 표시 장치는, 환경의 변동이 큰 옥외 등에서 사용한 경우라도, 표시의 열화(표시 품질의 저하)를 억제하는 것이 가능한 액정 표시 장치이다.

### 도면의 간단한 설명

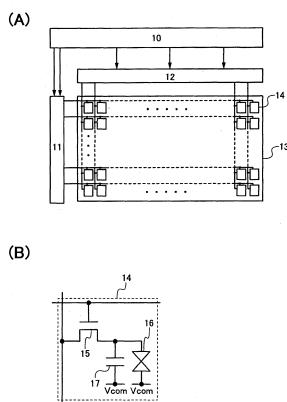

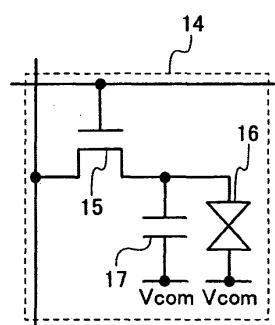

[0015] 도 1(A), (B)는, 실시형태 1에 관한 액정 표시 장치를 설명하는 도면이다.

도 2는, 실시형태 1에 관한 액정 표시 장치를 설명하는 도면이다.

도 3(A)~(C)는, 실시형태 1에 관한 액정 표시 장치를 설명하는 도면이다.

도 4(A)~(D)는, 실시형태 2에 관한 트랜지스터를 설명하는 도면이다.

도 5(A), (B)는, 실시형태 3에 관한 액정 표시 장치를 설명하는 도면이다.

도 6(A)~(F)는, 실시형태 4에 관한 전자 기기를 설명하는 도면이다.

도 7은, 실시예 1에 관한 트랜지스터의 초기 특성을 나타낸 도면이다.

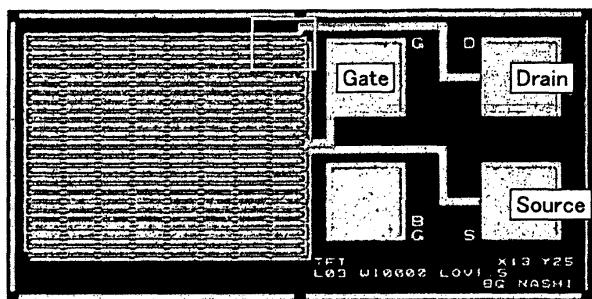

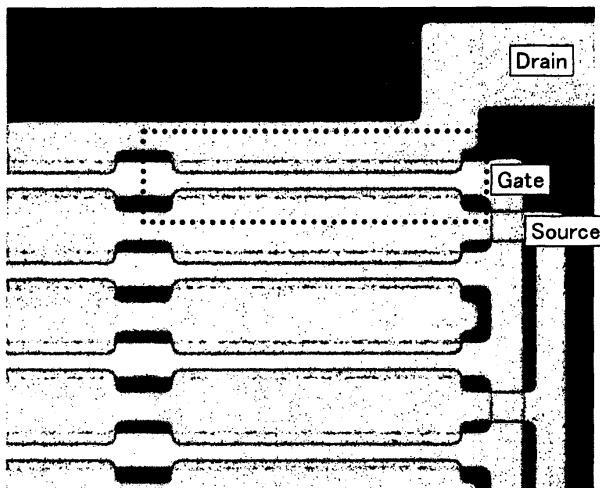

도 8(A), (B)는, 실시예 1에 관한 트랜지스터의 평가용 소자의 상면도이다.

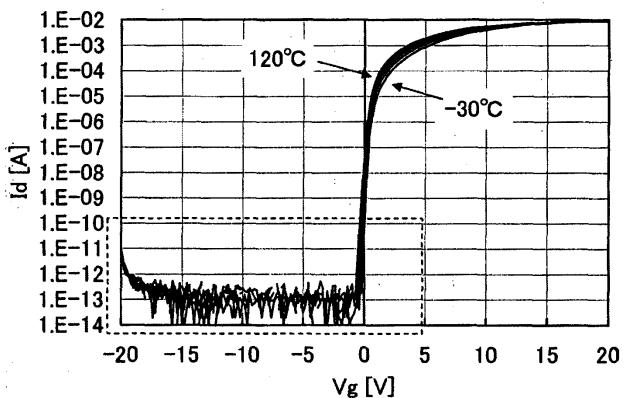

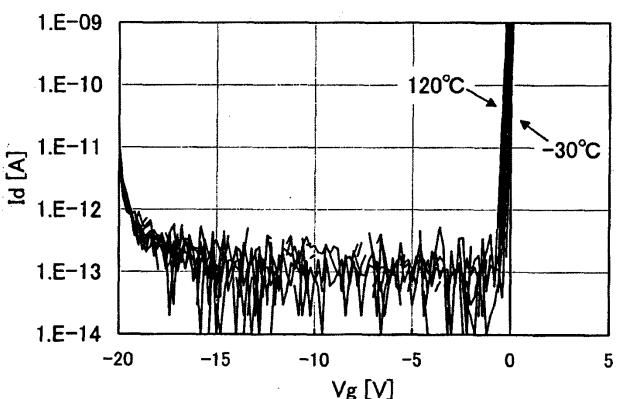

도 9(A), (B)는, 실시예 1에 관한 트랜지스터의 평가용 소자의  $V_{g-Id}$  특성을 나타낸 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0016] 이하에서는, 본 발명의 실시형태에 대해 도면을 이용하여 상세히 설명한다. 단, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어나지 않는 한도 내에서 그 형태 및 상세한 내용을 다양하게 변경할 수 있다는 것은, 당업자라면 용이하게 이해할 수 있다. 따라서, 본 발명은 이하에 나타낸 실시형태의 기재 내용에 한정되어 해석되어서는 안 된다.

[0017] 한편, 트랜지스터의 소스 단자 및 드레인 단자는, 트랜지스터의 구조나 동작 조건 등에 의해 바뀐다. 따라서, 본 서류에서는, 트랜지스터의 소스 및 드레인의 역할을 하는 단자의 한쪽을 제 1 단자, 다른 한쪽을

제 2 단자라 표기하여, 구별하는 것으로 한다.

[0018] 또한, 각 실시형태의 도면 등에서 나타낸 각 구성의, 크기, 층의 두께, 또는 영역은, 명료화를 위해 과장되어 표기되어 있는 경우가 있다. 따라서, 반드시 그 스케일에 한정되지 않는다. 또한, 본 명세서에서 이용되는 '제 1', '제 2', '제 3' 등의 서수는, 구성 요소의 혼동을 피하기 위해 부여한 것으로, 수적으로 한정하는 것이 아님을 밝혀 둔다.

[0019] (실시형태 1)

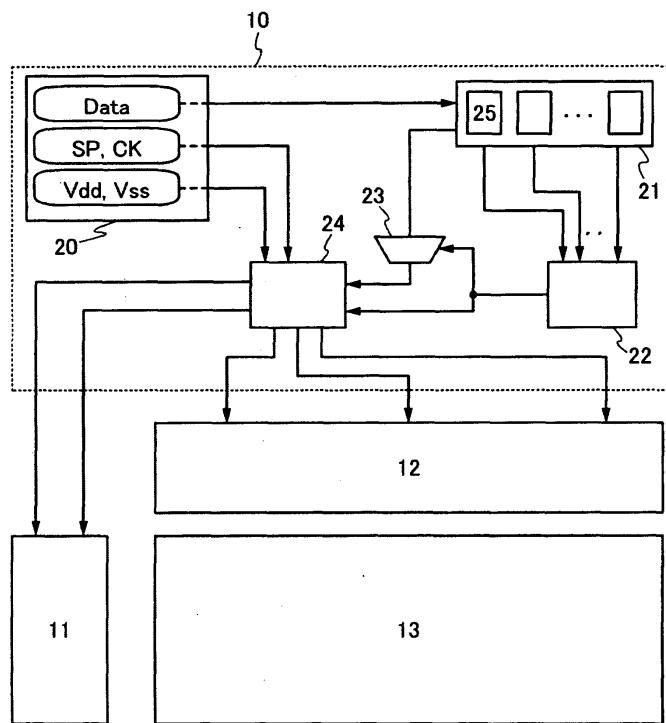

[0020] 본 실시형태에서는, 액티브 매트릭스형의 액정 표시 장치의 일 예에 대해 나타낸다. 구체적으로는, 화소부에 대한 화상 신호의 입력을 선택하는 것이 가능한 액티브 매트릭스형의 액정 표시 장치에 대해 도 1(A) 및 도 1(B), 도 2, 도 3(A) 내지 도 3(C)를 참조하여 설명한다.

[0021] 본 실시형태의 액정 표시 장치의 구성예에 대해 도 1(A) 및 도 1(B)를 참조하여 이하에 설명한다. 도 1(A)는, 액정 표시 장치의 구성예를 나타낸 도면이다. 도 1(A)에 나타낸 액정 표시 장치는, 제어 회로(10)와, 주사선 구동 회로(11)와, 신호선 구동 회로(12)와, 화소부(13)를 갖는다. 또한, 화소부(13)는, 매트릭스형으로 배열된 복수의 화소(14)를 갖는다. 도 1(B)는, 화소(14)의 구성예를 나타낸 도면이다. 도 1(B)에 나타낸 화소(14)는, 게이트 단자가 주사선 구동 회로(11)에 전기적으로 접속되고, 제 1 단자가 신호선 구동 회로(12)에 전기적으로 접속된 트랜지스터(15)와, 한쪽 단자가 트랜지스터(15)의 제 2 단자에 전기적으로 접속되고, 다른 한쪽 단자가 공통 전위(Vcom)를 공급하는 배선에 전기적으로 접속된 액정 소자(16)와, 한쪽 단자가 트랜지스터(15)의 제 2 단자 및 액정 소자(16)의 한쪽 단자에 전기적으로 접속되고, 다른 한쪽 단자가 공통 전위(Vcom)를 공급하는 배선에 전기적으로 접속되는 용량 소자(17)를 갖는다.

[0022] 본 실시형태의 액정 표시 장치는, 주사선 구동 회로(11)에 의해 트랜지스터(15)의 스위칭을 제어하고, 신호선 구동 회로(12)에서 트랜지스터(15)를 통해 액정 소자(16)에 화상 신호가 입력된다. 한편, 액정 소자(16)는, 한쪽 단자 및 다른 한쪽 단자에 협지된 액정층을 갖는다. 이 액정층에는 이 화상 신호와 공통 전위(Vcom)의 전위차의 전압이 인가되고, 이 전압에 의해 이 액정층의 배향 상태가 제어된다. 본 실시형태의 액정 표시 장치에서는, 이 배향을 이용하여 각 화소(14)의 표시를 제어하였다. 한편, 용량 소자(17)는, 액정 소자(16)에 인가되는 전압을 유지하기 위해 형성되어 있다.

[0023] 나아가, 본 실시형태에 나타낸 액정 표시 장치는, 제어 회로(10)에 의해, 주사선 구동 회로(11) 및 신호선 구동 회로(12)의 동작을 제어함으로써, 화소부(13)로의 화상 신호의 입력을 선택하는 것이 가능하다.

[0024] 이어서, 본 실시형태의 액정 표시 장치의 구성 요소의 구체 예에 대해 설명한다.

[0025] <제어 회로(10)>

[0026] 도 2는, 제어 회로(10)의 구성 예를 나타낸 도면이다. 도 2에 나타낸 제어 회로(10)는, 신호 생성 회로(20)와, 기억 회로(21)와, 비교 회로(22)와, 선택 회로(23)와, 표시 제어 회로(24)를 갖는다.

[0027] 신호 생성 회로(20)는, 주사선 구동 회로(11) 및 신호선 구동 회로(12)를 동작시켜, 화소부(13)에 화상을 형성하기 위한 신호를 생성하는 회로이다. 구체적으로는, 화소부(13)에 매트릭스형으로 배열된 복수의 화소에 대해 입력되는 화상 신호(Data), 주사선 구동 회로(11) 또는 신호선 구동 회로(12)의 동작을 제어하는 신호(예를 들어, 스타트 월스 신호(SP), 클럭 신호(CK) 등), 및 전원 전압인 고전원 전위(Vdd) 및 저전원 전위(Vss) 등을 생성하여, 출력하는 회로이다. 한편, 도 2에 나타낸 제어 회로(10)에서는, 신호 생성 회로(20)는, 기억 회로(21)에 대해 화상 신호(Data)를 출력하고, 표시 제어 회로(24)에 대해 주사선 구동 회로(11) 또는 신호선 구동 회로(12)의 동작을 제어하는 신호를 출력한다. 또한, 신호 생성 회로(20)에서 기억 회로(21)에 대해 출력되는 화상 신호(Data)가 아날로그 신호인 경우에는, A/D 컨버터 등을 통하여, 이 화상 신호(Data)를 디지털 신호로 변환할 수도 있다.

[0028] 기억 회로(21)는, 화소부(13)에서, 제 1 화상을 형성하기 위한 화상 신호 내지 제 n 화상(n은, 2 이상의 자연수)을 형성하기 위한 화상 신호를 기억하기 위한 복수의 메모리(25)를 갖는다. 한편, 메모리(25)는, DRAM(Dynamic Random Access Memory), SRAM(Static Random Access Memory) 등의 기억 소자를 이용하여 구성하면 된다. 또한, 메모리(25)는, 화소부(13)에서 형성되는 화상별로 화상 신호를 기억하는 구성이면 되고, 메모리(25)의 수는, 특정 수로 한정되지 않는다. 나아가, 복수의 메모리(25)가 기억하는 화상 신호는, 비교 회로(22) 및 선택 회로(23)에 의해 선택적으로 읽어진다.

- [0029] 비교 회로(22)는, 기억 회로(21)에 기억된 제 k 화상(k는, 1 이상 n 미만의 자연수)을 형성하기 위한 화상 신호 및 제 k+1 화상을 형성하기 위한 화상 신호를 선택적으로 읽어, 이 화상 신호를 비교하고, 차이를 검출하는 회로이다. 한편, 제 k 화상 및 제 k+1 화상은, 화소부(13)에서 연속하여 표시되는 화상이다. 비교 회로(22)에서의 화상 신호의 비교에 의해, 차이가 검출된 경우, 이 화상 신호에 의해 형성되는 2장의 화상은 동화인 것으로 판단된다. 한편, 비교 회로(22)에서의 화상 신호의 비교에 의해, 차이가 검출되지 않은 경우, 이 화상 신호에 의해 형성되는 2장의 화상은 정지화인 것으로 판단된다. 즉, 비교 회로(22)는, 비교 회로(22)에서의 차이의 검출에 의해 연속하여 표시되는 화상을 형성하기 위한 화상 신호가, 동화를 표시하기 위한 화상 신호인지, 정지화를 표시하기 위한 화상 신호인지를 판단하는 회로이다. 한편, 비교 회로(22)는, 이 차이가 일정한 레벨을 넘었을 때에, 차이를 검출한 것으로 판단되도록 설정하여도 좋다.

- [0030] 선택 회로(23)는, 비교 회로(22)에서 검출된 차이를 기초로, 화소부로의 화상 신호의 출력을 선택하는 회로이다. 구체적으로는, 선택 회로(23)는, 비교 회로(22)에서, 차이가 검출된 화상을 형성하기 위한 화상 신호는 출력하고, 차이가 검출되지 않는 화상을 형성하기 위한 화상 신호는 출력하지 않는 회로이다.

- [0031] 표시 제어 회로(24)는, 스타트 펄스 신호(SP), 클럭 신호(CK), 고전원 전위(Vdd), 및 저전원 전위(Vss) 등의 제어 신호의 주사선 구동 회로(11) 및 신호선 구동 회로(12)로의 공급을 제어하는 회로이다. 구체적으로는, 비교 회로(22)에 의해 동화로 판단된 경우(연속하여 표시되는 화상에 차이가 검출된 경우)에는, 선택 회로(23)에서 공급된 화상 신호(Data)를 신호선 구동 회로(12)에 출력함과 동시에, 주사선 구동 회로(11) 및 신호선 구동 회로(12)에 대해, 제어 신호(스타트 펄스 신호(SP), 클럭 신호(CK), 고전원 전위(Vdd), 및 저전원 전위(Vss) 등)을 공급한다. 한편, 비교 회로(22)에 의해 정지화로 판단된 경우(연속하여 표시되는 화상에 차이가 검출되지 않는 경우)에는, 선택 회로(23)에서 화상 신호(Data)가 공급되지 않는 동시에, 주사선 구동 회로(11) 및 신호선 구동 회로(12)에 대해, 제어 신호(스타트 펄스 신호(SP), 클럭 신호(CK), 고전원 전위(Vdd), 및 저전원 전위(Vss) 등)을 공급하지 않는다. 즉, 비교 회로(22)에 의해 정지화로 판단된 경우(연속하여 표시되는 화상에 차이가 검출되지 않는 경우)에는, 주사선 구동 회로(11) 및 신호선 구동 회로(12)의 동작을 완전히 정지시킨다. 단, 정지화로 판단되는 기간이 짧은 경우에는, 고전원 전위(Vdd) 및 저전원 전위(Vss)를 계속 공급하는 구성으로 할 수도 있다. 한편, 고전원 전위(Vdd) 및 저전원 전위(Vss)가 공급되는 것이란, 어느 배선의 전위가 고전원 전위(Vdd) 또는 저전원 전위(Vss)에 고정되는 것이다. 즉, 어느 전위 상태에 있는 이 배선이, 고전원 전위(Vdd) 또는 저전원 전위(Vss)로 변화하게 된다. 당연히, 이 전위의 변화에는 전력 소비가 수반된다. 이로 인해, 빈번하게 고전원 전위(Vdd) 및 저전원 전위(Vss)의 공급 정지 및 재공급을 행함으로써, 결과적으로, 소비 전력이 증대될 가능성이 있다. 이와 같은 경우에는, 고전원 전위(Vdd) 및 저전원 전위(Vss)를 계속 공급하는 구성으로 하는 것이 바람직하다. 한편, 상기한 설명에서, 신호를 '공급하지 않는다'란, 이 신호를 공급하는 배선에서 소정의 전위와는 다른 전위가 공급되는, 또는 이 배선의 전위가 부유 상태가 되는 것을 말하는 것으로 한다.

- [0032] 제어 회로(10)에서, 상기한 바와 같이 주사선 구동 회로(11) 및 신호선 구동 회로(12)의 동작을 제어함으로써 액정 표시 장치의 소비 전력을 저감하는 것이 가능하다.

- [0033] <트랜지스터(15)>

- [0034] 트랜지스터(15)는, 채널 형성 영역이 산화물 반도체층에 의해 구성되는 트랜지스터이다. 이 산화물 반도체층은, 전기적 특성 변동을 억지하기 위해, 변동 요인이 되는 수소, 수분, 수산기 또는 수소화물(수소 화합물이라고도 한다) 등의 불순물을 의도적으로 배제하고, 또한 불순물의 배제 공정에 의해 동시에 감소하게 되는 산화물 반도체를 구성하는 주성분 재료인 산소를 공급함으로써, 고순도화 및 전기적으로 I형(진성)화된 산화물 반도체층이다. 한편, 이 산화물 반도체는, 2eV 이상, 바람직하게는 2.5eV 이상, 더욱 바람직하게는 3.0eV 이상의 밴드갭을 갖는다.

- [0035] 또한, 고순도화된 산화물 반도체 중에는 캐리어가 매우 작고(0에 가까움), 캐리어 밀도는  $1 \times 10^{14} / \text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12} / \text{cm}^3$  이하이다. 즉, 산화물 반도체층의 캐리어 밀도는, 무한대로 0으로 한다. 산화물 반도체층 중에 캐리어가 매우 적으므로, 오프 전류값을 낮게 할 수 있다. 오프 전류값은 낮으면 낮을수록 바람직하다. 이로 인해, 상기한 트랜지스터에서는, 채널 폭(w)이  $1\mu\text{m}$ 당 실온에서의 오프 전류값을  $10\text{aA}/\mu\text{m}$  ( $1 \times 10^{-17} \text{ A}/\mu\text{m}$ ) 이하로 하는 것, 및  $85^\circ\text{C}$ 에서의 오프 전류값을  $100\text{aA}/\mu\text{m}$  ( $1 \times 10^{-16} \text{ A}/\mu\text{m}$ ) 이하로 하는 것이 가능하다. 한편, 일반적으로, 아몰퍼스 실리콘을 구비하는 트랜지스터에서는, 실온에서의 오프 전류값은  $1 \times 10^{-13} \text{ A}/\mu\text{m}$  이상이 된다. 또한, pn 접합이 없고, 핫캐리어 열화가 없으므로, 이들에 트랜지스터의 전기적 특성이 영향을

받지 않는다. 이에 의해, 각 화소(14)의 화상 신호의 유지 기간을 길게 할 수 있다. 즉, 정지화를 표시할 때의 화상 신호의 다시 쓰기의 간격을 길게 할 수 있다. 예를 들어, 화상 신호의 쓰기 간격을 10초 이상, 바람직하게는 30초 이상, 더욱 바람직하게는 1분 이상 10분 미만으로 할 수 있다. 쓰기 간격을 길게 하면, 소비 전력을 억제하는 효과를 높일 수 있다.

[0036] 한편, 트랜지스터의 오프 전류가 흐르기 어려운 정도를 오프 저항율로 나타낼 수 있다. 오프 저항율이란, 트랜지스터가 오프일 때의 채널 형성 영역의 저항율이고, 오프 저항율은 오프 전류에서 산출할 수 있다.

[0037] 구체적으로는, 오프 전류와 드레인 전압의 값을 알면 옴의 법칙으로 트랜지스터가 오프일 때의 저항값(오프 저항( $R$ ))을 산출할 수 있다. 그리고 채널 형성 영역의 단면적( $A$ )과 채널 형성 영역의 길이(소스 드레인 전극 간의 거리에 상당)( $L$ )를 알면  $\rho = RA/L$ 의 식( $R$ 은 오프 저항)에서 오프 저항율( $\rho$ )을 산출할 수 있다.

[0038] 여기서, 단면적( $A$ )은, 채널 형성 영역의 막후를  $d$ 로 하고, 채널 폭을  $W$ 로 할 때,  $A=dW$ 에서 산출할 수 있다. 또한, 채널 형성 영역의 길이( $L$ )는 채널 길이( $L$ )이다. 이상과 같이, 오프 전류에서 오프 저항율을 산출할 수 있다.

[0039] 본 실시형태의 산화물 반도체층을 구비하는 트랜지스터의 오프 저항율은  $1 \times 10^{11} \Omega \cdot \text{cm}$  이상이 바람직하고, 나아가  $1 \times 10^{12} \Omega \cdot \text{cm}$  이상이 더욱 바람직하다.

[0040] 이와 같이 산화물 반도체층에 포함되는 수소를 철저히 제거함으로써 고순도화된 산화물 반도체층을 트랜지스터의 채널 형성 영역으로 이용한 트랜지스터는, 오프 전류값을 매우 낮게 할 수 있다. 즉, 트랜지스터가 오프 상태에 있을 때, 산화물 반도체층을 절연체로 간주하여 회로 설계를 할 수 있다. 한편, 산화물 반도체층을 구비하는 트랜지스터는, 온 상태에서는, 아몰퍼스 실리콘층을 구비하는 트랜지스터보다도 높은 전류 공급 능력을 가질 수 있다.

[0041] 또한, 저온 폴리 실리콘층을 구비하는 트랜지스터에서는, 산화물 반도체층을 구비하는 트랜지스터와 비교하여, 실온에서의 오프 전류값이 10000배 정도 큰 값인 것으로 상정하여 설계 등을 하였다. 이로 인해, 산화물 반도체층을 구비하는 트랜지스터에서는, 저온 폴리 실리콘층을 구비하는 트랜지스터에 비해, 유지 용량이 동등(0.1pF 정도)할 때, 전압의 유지 기간을 10000배 정도로 연장할 수 있다. 일 예로, 동화 표시를 매초 60프레임으로 행하는 경우, 1회의 신호 쓰기에 의한 유지 기간을 10000배인 160초 정도로 할 수 있다. 그리고, 적은 화상 신호의 쓰기 횟수로도, 표시부에서의 정지화의 표시를 행할 수 있다.

[0042] 유지 기간을 길게 함으로써, 화소로의 화상 신호의 공급을 행하는 빈도를 저감할 수 있다. 특히, 상기한 바와 같은, 화상 신호를 선택적으로 화소부에 입력하는 것이 가능한 액정 표시 장치에 대해서는, 상기한 트랜지스터를 적용하는 효과가 크다. 즉, 이 액정 표시 장치에서는, 장기간에 걸쳐 화상 신호가 화소에 입력되지 않을 가능성이 있으나, 상기한 트랜지스터를 화소로의 화상 신호의 입력을 제어하는 트랜지스터로 적용함으로써, 이 화소의 표시의 열화(변화)를 억제할 수 있다.

[0043] 또한, 이 트랜지스터를 화소로의 화상 신호의 입력을 제어하는 스위치로 적용함으로써, 화소에 형성되는 용량 소자의 사이즈를 축소하는 것이 가능해진다. 이에 의해, 이 화소의 개구율을 향상시키는 것 및 이 화소로의 화상 신호의 입력을 고속으로 행하는 것 등이 가능해진다.

[0044] <액정 소자(16) 및 용량 소자(17)>

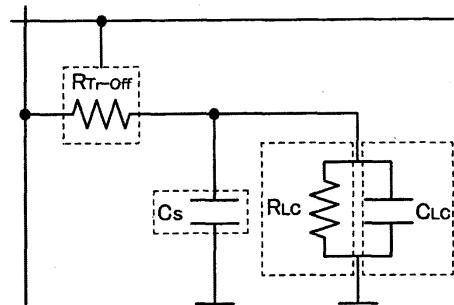

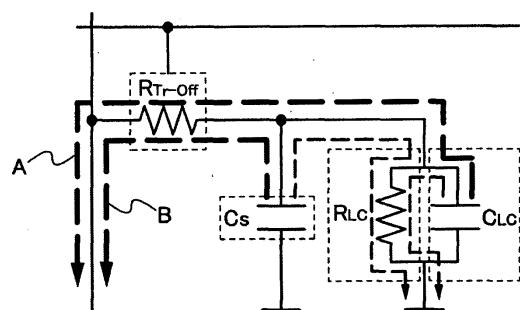

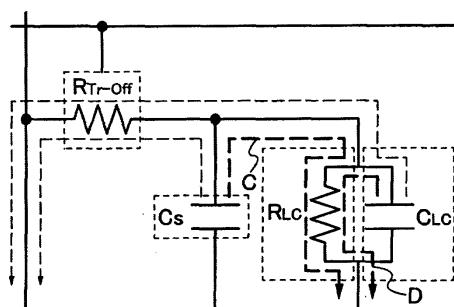

[0045] 화상 신호의 입력을 제어하는 트랜지스터(15)로 상기한 트랜지스터를 적용하는 경우, 액정 소자(16)가 갖는 액정 재료로 고유 저항율이 높은 물질을 적용하는 것이 바람직하다. 여기서, 도 3(A) 내지 도 3(C)를 참조하여 그 이유에 대해 설명한다. 한편, 도 3(A) 내지 도 3(C)는, 아몰퍼스 실리콘층을 구비하는 트랜지스터를 갖는 화소 및 상기 산화물 반도체층을 구비하는 트랜지스터를 갖는 화소에서의 화상 신호의 리크 경로를 나타낸 모식도이다.

[0046] 도 1(B)에 나타낸 바와 같이, 이 화소는, 트랜지스터(15)와, 액정 소자(16)와, 용량 소자(17)에 의해 구성되고, 트랜지스터(15)가 오프 상태에 있는 경우, 도 3(A)에 나타낸 회로와 등가이다. 즉, 트랜지스터(15)를 저항( $R_{\text{tr-off}}$ )에 의해 나타내고, 액정 소자(16)를 저항( $R_{LC}$ ) 및 용량( $C_{LC}$ )에 의해 나타낸 회로와 등가이다. 화상 신호가 이 화소에 입력되면, 이 화상 신호는, 용량 소자(17)의 용량( $C_S$ ) 및 액정 소자(16)의 용량( $C_{LC}$ )에 저장된다. 그 후, 트랜지스터(15)가 오프 상태가 되면, 도 3(B), (C)에 나타낸 바와 같이 트랜지스터(15) 및 액정 소자(16)를 통해, 화상 신호가 리크된다. 한편, 도 3(B)는, 트랜지스터(15)가 아몰퍼스 실리콘층을 구

비하는 트랜지스터인 경우의 화상 신호의 리크를 나타낸 모식도이고, 도 3(C)는, 트랜지스터(15)가 산화물 반도체층을 구비하는 트랜지스터인 경우의 화상 신호의 리크를 나타낸 모식도이다. 아몰퍼스 실리콘층을 구비하는 트랜지스터의 오프 저항값은, 액정 소자의 저항값보다 낮다. 이로 인해, 도 3(B)에 나타낸 바와 같이, 화상 신호의 리크는, 아몰퍼스 실리콘층을 구비하는 트랜지스터를 통한 리크가 주가 된다(도 3(B) 중, 경로(A) 및 경로(B)를 거친 리크가 주가 된다). 한편, 고순도화된 산화물 반도체층을 구비하는 트랜지스터의 오프 저항값은, 액정 소자의 저항값보다 높다. 이로 인해, 도 3(C)에 나타낸 바와 같이, 화상 신호의 리크는, 액정 소자를 통한 리크가 주가 된다(도 3(C), 경로(C) 및 경로(D)를 거친 리크가 주가 된다).

[0047] 즉, 종래에서는, 액정 표시 장치의 각 화소에서의 화상 신호의 유지 특성은, 각 화소에 형성되는 트랜지스터의 특성을 율속점으로 하였으나, 고순도화된 산화물 반도체층을 구비하는 트랜지스터를 각 화소에 형성되는 트랜지스터에 적용함으로써, 액정 소자의 저항값이 율속점이 된다. 이로 인해, 액정 소자(16)가 갖는 액정 재료로 고유 저항율이 높은 물질을 적용하는 것이 바람직하다.

[0048] 구체적으로는, 화소에, 고순도화된 산화물 반도체층을 구비하는 트랜지스터를 갖는 액정 표시 장치에서는, 액정 재료의 고유 저항율은,  $1 \times 10^{12} \Omega \cdot \text{cm}$  이상이고, 바람직하게는  $1 \times 10^{13} \Omega \cdot \text{cm}$ 를 넘는 것이고, 더욱 바람직하게는  $1 \times 10^{14} \Omega \cdot \text{cm}$ 를 넘는 것이 바람직한 요건이 된다. 한편, 이 액정 재료를 이용하여 액정 소자를 구성한 경우의 저항은, 배향막 및 셀재로부터의 불순물이 혼입될 가능성도 있고,  $1 \times 10^{11} \Omega \cdot \text{cm}$  이상이고, 더욱 바람직하게는  $1 \times 10^{12} \Omega \cdot \text{cm}$ 를 넘는 것이 바람직한 요건이 된다. 또한, 본 명세서에서의 고유 저항율의 값은, 20°C에서 측정한 값으로 한다.

[0049] 또한, 정지화 표시에서의 유지 기간에서, 액정 소자(16)의 다른 한쪽 단자로의 공통 전위( $V_{com}$ )의 공급을 하지 않고, 이 단자를 부유 상태로 할 수도 있다. 구체적으로는, 이 단자와, 공통 전위( $V_{com}$ )를 공급하는 전원 사이에 스위치를 구비하고, 쓰기 기간 중에는 스위치를 온으로 하여 전원에서 공통 전위( $V_{com}$ )를 공급한 후, 남은 유지 기간에서는 스위치를 오프로 하여 부유 상태로 하면 된다. 이 스위치에 대해서도, 상기 고순도화된 산화물 반도체층을 구비하는 트랜지스터를 이용하는 것이 바람직하다. 액정 소자(16)의 다른 한쪽 단자를 부유 상태로 함으로써, 부정 펠스 등에 의한, 화소(14)에서의 표시의 열화(변화)를 저감할 수 있다. 왜냐하면, 트랜지스터(15)가 오프 상태에 있는 경우에 트랜지스터(15)의 제 1 단자의 전위가 부정 펠스에 의해 변동하면, 용량 결합에 의해 액정 소자(16)의 한쪽 단자의 전위도 변동한다. 이때, 액정 소자(16)의 다른 한쪽 단자에 공통 전위( $V_{com}$ )가 공급된 상태라면, 이 변동은 액정 소자(16)에 인가되는 전압치의 변화에 직결되는데 반해, 액정 소자의 다른 한쪽 단자가 부유 상태에 있으면, 이 단자의 전위도 용량 결합에 의해 변동한다. 이로 인해, 트랜지스터(15)의 제 1 단자의 전위가 부정 펠스에 의해 변동한 경우라도, 액정 소자(16)에 인가되는 전압치의 변화를 저감할 수 있고, 화소(14)에서의 표시의 열화(변화)를 저감할 수 있다.

[0050] 또한, 용량 소자(17)의 용량( $C_s$ )의 크기는, 각 화소에 형성된 트랜지스터의 오프 전류 등을 고려하여 설정되는 것이다. 단, 상기한 바와 같이, 고순도화된 산화물 반도체층을 구비하는 트랜지스터를 화소가 갖는 트랜지스터에 적용함으로써, 용량 소자(17)의 설계에 요구되는 조건이 크게 변화한다. 이하에 구체적인 수치를 들어 이 내용에 대해 설명한다.

[0051] 일반적으로 화소가 갖는 트랜지스터로 아몰퍼스 실리콘층을 구비하는 트랜지스터를 적용한 경우의 오프 저항값은,  $1 \times 10^{12} \Omega$  정도이고, 액정 소자의 저항값은  $1 \times 10^{15} \Omega$  정도이다. 이로 인해, 화소가 갖는 트랜지스터를 고순도화된 산화물 반도체층을 구비하는 트랜지스터로 함으로써, 이 화소에서의 화상 신호의 리크를  $1/1000$  정도까지 저감하는 것이 가능하다. 즉, 용량 소자(17)의 용량( $C_s$ )의 크기를  $1/1000$  정도까지 저감하는 것, 또는 이 화소에서 정지화를 표시하는 경우의 화상 신호의 다시 쓰기의 빈도를  $1/1000$  정도까지 저감할 수 있다. 예를 들어, 1초 동안 60회의 화상 신호의 쓰기를 하는 경우는, 15초 동안 1회 정도까지 이 쓰기의 빈도를 저감하는 것이 가능하다. 또한, 용량 소자(17)로, 50fF 정도의 용량을 갖는 소자를 적용함으로써, 화소에서 화상 신호를 30초 정도 유지할 수 있다. 일 예로, 각 화소에서 화상 신호를 5초 이상 5분 이하로 유지하기 위해서는, 용량 소자(17)의 용량( $C_s$ )이 0.5pF 이상인 것이 바람직하고, 1pF 이상인 것이 더욱 바람직하다. 한편, 상기한 설명에서의 각종 수치는, 대략 계산한 값인 것을 밝혀둔다.

[0052] 한편, 본 실시형태의 내용 또는 이 내용의 일부는, 다른 실시형태의 내용 또는 이 내용의 일부 또는 실시예의 내용 또는 이 내용의 일부와 자유롭게 조합하는 것이 가능하다.

[0053] (실시형태 2)

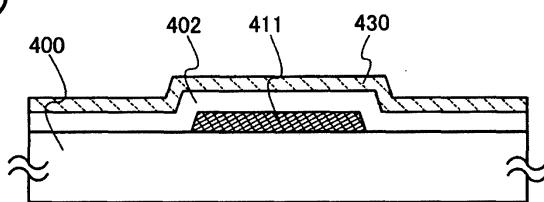

[0054] 본 실시형태에서는, 실시형태 1에 나타낸 트랜지스터의 일 예에 대해 도 4(A)~(D)를 참조하여 설명한다.

[0055] 도 4(A)~(D)는, 실시형태 1에 나타낸 트랜지스터의 구체적인 구성 및 제작 공정의 구체예를 나타낸 도면이다. 한편, 도 4(A)~(D)에 나타낸 박막 트랜지스터(410)는, 채널 에치형이라 불리는 보통 게이트 구조의 하나로, 역스태거형 박막 트랜지스터라고도 한다. 또한, 도 4(A)~(D)에는, 싱글 게이트 구조의 박막 트랜지스터를 나타내나, 필요에 따라, 채널 형성 영역을 복수 갖는 멀티 게이트 구조의 박막 트랜지스터로 할 수 있다.

[0056] 이하, 도 4(A)~(D)를 참조하여, 기판(400) 위에 박막 트랜지스터(410)를 제작하는 공정에 대해 설명한다.

[0057] 우선, 절연 표면을 갖는 기판(400) 위에 도전막을 형성한 후, 제 1 포토리소 그래피 공정에 의해 게이트 전극 층(411)을 형성한다. 한편, 이 공정에서 이용되는 레지스트 마스크는, 잉크젯법에 의해 형성하여도 좋다. 레지스트 마스크를 잉크젯법으로 형성하면 포토 마스크를 사용하지 않으므로, 제조 비용을 저감할 수 있다.

[0058] 절연 표면을 갖는 기판(400)에 사용할 수 있는 기판에 큰 제한은 없으나, 적어도, 후의 가열 처리에 견딜 수 있는 정도의 내열성을 가질 필요가 있다. 예를 들어, 바륨 봉규산 유리나 알루미노 봉규산 유리 등의 유리 기판을 이용할 수 있다. 또한, 유리 기판으로는, 후의 가열 처리의 온도가 높은 경우에는, 변형점이 730°C 이상인 것을 이용하는 것이 좋다.

[0059] 하지막이 되는 절연막을 기판(400)과 게이트 전극층(411) 사이에 형성하여도 좋다. 하지막은, 기판(400)에서의 불순물 원소의 확산을 방지하는 기능이 있고, 질화 실리콘막, 산화 실리콘막, 질화산화 실리콘막, 또는 산화질화 실리콘막에서 선택된 하나 또는 복수의 막에 의한 적층 구조에 의해 형성할 수 있다.

[0060] 또한, 게이트 전극층(411)의 재료는, 몰리브덴, 티탄, 크롬, 탄탈, 텉스텐, 알루미늄, 구리, 네오디뮴, 스칸듐 등의 금속 재료 또는 이를 주성분으로 하는 합금 재료를 이용하여, 단층 또는 적층하여 형성할 수 있다.

[0061] 예를 들어, 게이트 전극층(411)의 2층의 적층 구조로는, 알루미늄층 위에 몰리브덴층을 적층한 2층 구조, 구리층 위에 몰리브덴층을 적층한 2층 구조, 구리층 위에 질화 티탄층 또는 질화 탄탈을 적층한 2층 구조, 질화 티탄층과 몰리브덴층을 적층한 2층 구조로 하는 것이 바람직하다. 3층의 적층 구조로는, 텉스텐층 또는 질화 텉스텐층과, 알루미늄과 실리콘의 합금층 또는 알루미늄과 티탄의 합금층과, 질화 티탄층 또는 티탄층을 적층한 3층 구조로 하는 것이 바람직하다.

[0062] 이어서, 게이트 전극층(411) 위에 게이트 절연층(402)을 형성한다.

[0063] 게이트 절연층(402)은, 플라즈마 CVD법 또는 스퍼터링법 등을 이용하여, 산화 실리콘층, 질화 실리콘층, 산화 질화 실리콘층, 질화산화 실리콘층, 또는 산화 알루미늄층을 단층 또는 적층하여 형성할 수 있다. 예를 들어, 성막 가스로, 실란(SiH<sub>4</sub>), 산소 및 질소를 이용하여 플라즈마 CVD법에 의해 산화질화 실리콘층을 형성하면 된다. 또한, 게이트 절연층으로 산화 하프늄(HfO<sub>x</sub>), 산화탄탈(TaO<sub>x</sub>) 등의 High-k 재료를 이용할 수도 있다. 게이트 절연층(402)의 막후는, 100nm 이상 500nm 이하로 하고, 적층의 경우는, 예를 들어, 막후 50nm 이상 200nm 이하의 제 1 게이트 절연층과, 제 1 게이트 절연층 위에 막후 5nm 이상 300nm 이하의 제 2 게이트 절연층을 적층하여 형성한다.

[0064] 여기서는, 게이트 절연층(402)으로 플라즈마 CVD법에 의해 막후 100nm 이하의 산화질화 실리콘층을 형성한다.

[0065] 또한, 게이트 절연층(402)으로, 고밀도 플라즈마 장치를 이용하여, 산화질화 실리콘막을 형성하여도 좋다. 여기서 고밀도 플라즈마 장치란,  $1 \times 10^{11} / \text{cm}^3$  이상의 플라즈마 밀도를 달성할 수 있는 장치를 말한다. 예를 들어, 3kW~6kW의 마이크로파 전력을 인가하여 플라즈마를 발생시켜, 절연막을 성막한다.

[0066] 챔버에 재료 가스로 실란(SiH<sub>4</sub>), 아산화질소(N<sub>2</sub>O), 및 희가스를 도입하고, 10Pa~30Pa의 압력 하에서 고밀도 플라즈마를 발생시켜 유리 등의 절연 표면을 갖는 기판 위에 절연막을 형성한다. 그 후, 실란(SiH<sub>4</sub>)의 공급을 정지하고, 대기에 노출시키지 않고 아산화질소(N<sub>2</sub>O)와 희가스를 도입하여 절연막 표면에 플라즈마 처리를 하여도 좋다. 적어도 아산화질소(N<sub>2</sub>O)와 희가스를 도입하여 절연막 표면에 이루어지는 플라즈마 처리는, 절연막의 성막보다 나중에 행한다. 상기 프로세스 순서를 거친 절연막은, 막후가 얇고, 예를 들어 100nm 미만이라도 신뢰성을 확보할 수 있는 절연막이다.

- [0067] 게이트 절연층(402)의 형성 시, 챔버에 도입하는 실란(SiH<sub>4</sub>)과 아산화질소(N<sub>2</sub>O)의 유량비는, 1:10에서 1:200의 범위로 한다. 또한, 챔버에 도입하는 희가스로는, 헬륨, 아르곤, 클립톤, 크세논 등을 이용할 수 있으나, 그 중에서도 저렴한 아르곤을 이용하는 것이 바람직하다.

- [0068] 또한, 고밀도 플라즈마 장치에 의해 얻어진 절연막은, 일정한 두께의 막 형성이 가능하므로 단차 피복성이 우수하다. 또한, 고밀도 플라즈마 장치에 의해 얻어진 절연막은, 얇은 막의 두께를 정밀하게 제어할 수 있다.

- [0069] 상기 프로세스 순서를 거친 절연막은, 종래의 평행평판형 PCVD장치에서 얻어지는 절연막과는 크게 다르며, 동일한 에천트를 이용하여 에칭 속도를 비교한 경우에서, 평행평판형 PCVD 장치에서 얻어지는 절연막의 10% 이상 또는 20% 이상 느리며, 고밀도 플라즈마 장치에서 얻어지는 절연막은 치밀한 막이라 할 수 있다.

- [0070] 한편, 후의 공정에서 i형화 또는 실질적으로 i형화된 산화물 반도체층(고순도화된 산화물 반도체층)은 계면 준위, 계면 전하에 대해 매우 민감하므로, 게이트 절연층과의 계면은 중요하다. 이로 인해 고순도화된 산화물 반도체층에 접하는 게이트 절연층은, 고품질화가 요구된다. 따라서  $\mu$ 파(2.45GHz)를 이용한 고밀도 플라즈마 CVD 장치는, 치밀하고 절연 내압이 높은 고품질의 절연막을 형성할 수 있으므로 바람직하다. 고순도화된 산화물 반도체층과 고품질 게이트 절연층이 밀접함으로써, 계면 준위를 저감하여 계면 특성을 양호한 것으로 할 수 있기 때문이다. 게이트 절연층으로써 막질이 양호한 것은 물론, 산화물 반도체층과의 계면 준위 밀도를 저감하고, 양호한 계면을 형성할 수 있는 것이 중요하다.

- [0071] 이어서, 게이트 절연층(402) 위에, 막후 2nm 이상 200nm 이하의 산화물 반도체막(430)을 형성한다. 한편, 산화물 반도체막(430)을 스퍼터링법에 의해 성막하기 전에, 아르곤 가스를 도입하여 플라즈마를 발생시키는 역스퍼터링을 행하고, 게이트 절연층(402)의 표면에 부착되어 있는 가루형 물질(파티클, 먼지라고도 한다)을 제거하는 것이 바람직하다. 역스퍼터링이란, 타겟 측으로 전압을 인가하지 않고, 아르곤 분위기 하에서 기판 측으로 RF 전원을 이용하여 전압을 인가하여 기판에 플라즈마를 형성하여 표면을 개질하는 방법이다. 한편, 아르곤 분위기 대신 질소, 헬륨, 산소 등을 이용하여도 좋다.

- [0072] 산화물 반도체막(430)은, In-Ga-Zn-O계, In-Sn-O계, In-Sn-Zn-O계, In-Al-Zn-O계, Sn-Ga-Zn-O계, Al-Ga-Zn-O계, Sn-Al-Zn-O계, In-Zn-O계, Sn-Zn-O계, Al-Zn-O계, In-O계, Sn-O계, Zn-O계의 산화물 반도체막을 이용한다. 본 실시형태에서는, 산화물 반도체막(430)으로, In-Ga-Zn-O계 금속 산화물 타겟을 이용하여 스퍼터링법에 의해 성막한다. 이 단계에서의 단면도가 도 4(A)에 상당한다. 또한, 산화물 반도체막(430)은, 희가스(대표적으로는 아르곤) 분위기 하, 산소 분위기 하, 또는 희가스(대표적으로는 아르곤) 및 산소의 혼합 분위기 하에서 스퍼터링법에 의해 형성할 수 있다. 또한, 스퍼터링법을 이용하는 경우, SiO<sub>2</sub>를 2중량% 이상 10중량% 이하 포함하는 타겟을 이용하여 성막하고, 산화물 반도체막(430)에 결정화를 저해하는 SiO<sub>x</sub>(X>0)를 포함시켜, 후의 공정에서 행하는 탈수화 또는 탈수소화를 위한 가열 처리 시에 결정화되어 버리는 것을 억제할 수 있다.

- [0073] 여기서는, In, Ga, 및 Zn을 포함하는 금속 산화물 타겟( $In_2O_3:Ga_2O_3:ZnO=1:1:1[mol]$ ,  $In:Ga:Zn=1:1:0.5[atom]$ )을 이용하여, 기판과 타겟 사이의 거리를 100mm, 압력 0.2Pa, 직류(DC) 전원 0.5kW, 아르곤 및 산소(아르곤:산소=30sccm:20sccm, 산소 유량 비율 40%) 분위기 하에서 성막한다. 한편, 펄스 직류(DC) 전원을 이용하면, 성막 시에 발생하는 가루형 물질을 경감할 수 있고, 막후 분포도 균일해지므로 바람직하다. In-Ga-Zn-O계 막의 막후는, 5nm 이상 200nm 이하로 한다. 본 실시형태에서는, 산화물 반도체막으로, In-Ga-Zn-O계 금속 산화물 타겟을 이용하여 스퍼터링법에 의해 막후 20nm의 In-Ga-Zn-O계 막을 성막한다. 또한, In, Ga, 및 Zn을 포함하는 금속 산화물 타겟으로,  $In:Ga:Zn=1:1:1[atom]$ , 또는  $In:Ga:Zn=1:1:2[atom]$ 의 조성비를 갖는 타겟을 이용할 수도 있다.

- [0074] 스퍼터링법에는 스퍼터링용 전원에 고주파 전원을 이용하는 RF 스퍼터링법과 DC 스퍼터링법이 있고, 또한 펄스적으로 바이어스를 가하는 펄스 DC 스퍼터링법도 있다. RF 스퍼터링법은 주로 절연막을 성막하는 경우에 이용되고, DC 스퍼터링법은 주로 금속막을 성막하는 경우에 이용된다.

- [0075] 또한, 재료가 다른 타겟을 복수할 수 있는 다원 스퍼터링 장치도 있다. 다원 스퍼터링 장치는, 동일 챔버에서 다른 재료막을 적층 성막할 수도, 동일 챔버에서 복수 종류의 재료를 동시에 방전시켜 성막할 수도 있다.

- [0076] 또한, 챔버 내부에 자석 기구를 구비한 마그네트론 스퍼터링법을 이용하는 스퍼터링 장치나, 글로 방전을 사용하지 않고 마이크로파를 이용하여 발생시킨 플라즈마를 이용하는 ECR 스퍼터링법을 이용하는 스퍼터링 장치가 있다.

- [0077] 또한, 스퍼터링법을 이용하는 성막 방법으로, 성막 중에 타겟 물질과 스퍼터링 가스 성분을 화학 반응시켜 이

들 화합물 박막을 형성하는 리액티브 스퍼터링법이나, 성막 중에 기판에도 전압을 가하는 바이어스 스퍼터링 법도 있다.

[0078] 이어서, 산화물 반도체막(430)을 제 2 포토리소 그래피 공정에 의해 섬모양의 산화물 반도체층으로 가공한다. 또한, 이 공정에서 이용되는 레지스트 마스크는, 잉크젯법에 의해 형성하여도 좋다. 레지스트 마스크를 잉크젯법으로 형성하면 포토 마스크를 사용하지 않으므로, 제조 비용을 저감할 수 있다.

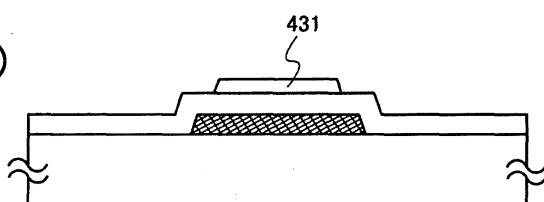

[0079] 이어서, 산화물 반도체층의 탈수화 또는 탈수소화를 행한다. 탈수화 또는 탈수소화를 행하는 제 1 가열 처리의 온도는, 400°C 이상 750°C 이하, 바람직하게는 400°C 이상 기판의 변형 절 미만으로 한다. 여기서는, 가열 처리 장치의 하나인 전기로에 기판을 도입하고, 산화물 반도체층에 대해 질소 분위기 하 450°C에서 1시간의 가열 처리를 한 후, 대기해 접촉시키지 않고, 산화물 반도체층으로의 물이나 수소의 재흡입을 방지하고, 산화물 반도체층(431)을 얻는다(도 4(B) 참조).

[0080] 한편, 가열 처리 장치는 전기로에 한정되지 않고, 저항 발열체 등의 발열체로부터의 열전도 또는 열복사에 의해, 피처리물을 가열하는 장치를 구비하여도 좋다. 예를 들어, GRTA(Gas Rapid Thermal Anneal) 장치, LRTA(Lamp Rapid Thermal Anneal) 장치 등의 RTA(Rapid Thermal Anneal) 장치를 이용할 수 있다. LRTA 장치는, 할로겐 램프, 메탈 할라이드 램프, 크세논아크 램프, 카본아크 램프, 고압 나트륨 램프, 고압 수은 램프 등의 램프에서 발하는 광(전자파)의 복사에 의해, 피처리물을 가열하는 장치이다. GRTA 장치는, 고온의 가스를 이용하여 가열 처리를 행하는 장치이다. 기체에는, 아르곤 등의 희가스, 또는 질소와 같은, 가열 처리에 의해 피처리물과 반응하지 않는 불활성 기체가 이용된다.

[0081] 예를 들어, 제 1 가열 처리로, 650°C~700°C의 고온으로 가열한 불활성 가스 중에 기판을 이동시켜 넣고, 수분간 가열한 후, 기판을 이동시켜 고온으로 가열한 불활성 가스 중에서 꺼내는 GRTA를 행하여도 좋다. GRTA를 이용하면 단시간에 고온 가열 처리가 가능해진다.

[0082] 한편, 제 1 가열 처리에서는, 질소, 또는 헬륨, 네온, 아르곤 등의 희가스에, 물, 수소 등이 포함되지 않는 것이 바람직하다. 또는, 가열 처리 장치에 도입하는 질소, 또는 헬륨, 네온, 아르곤 등의 희가스의 순도를, 6N(99.9999%) 이상, 바람직하게는 7N(99.99999%) 이상, (즉 불순물 농도를 1ppm 이하, 바람직하게는 0.1ppm 이하)로 하는 것이 바람직하다.

[0083] 또한, 제 1 가열 처리는, 섬모양의 산화물 반도체층으로 가공하기 전의 산화물 반도체막(430)에 대해 행할 수도 있다. 이 경우에는, 제 1 가열 처리 후에, 가열 장치에서 기판을 꺼내고, 제 2 포토리소 그래피 공정을 행한다.

[0084] 산화물 반도체층에 대한 탈수화 또는 탈수소화의 가열 처리는, 산화물 반도체층의 형성 후, 산화물 반도체층 위에 소스 전극층 및 드레인 전극층을 적층시킨 후, 소스 전극층 및 드레인 전극층 위에 보호 절연막을 형성한 후, 중 어느 단계에서 행하여도 좋다.

[0085] 또한, 케이트 절연층(402)에 개구부를 형성하는 경우, 그 공정은 산화물 반도체막(430)에 탈수화 또는 탈수소화 처리를 행하기 전이어도, 행한 후에 행하여도 좋다.

[0086] 한편, 여기서의 산화물 반도체막(430)의 에칭은, 습식 에칭에 한정되지 않고 건식 에칭을 이용하여도 좋다.

[0087] 건식 에칭에 이용되는 에칭 가스로는, 염소를 포함하는 가스(염소계 가스, 예를 들어 염소(Cl<sub>2</sub>), 삼염화 봉소(BCl<sub>3</sub>), 사염화 실리콘(SiCl<sub>4</sub>), 사염화 탄소(CCl<sub>4</sub>) 등)가 바람직하다.

[0088] 또한, 불소를 포함하는 가스(불소계 가스, 예를 들어 사불화 탄소(CF<sub>4</sub>), 육불화 유황(SF<sub>6</sub>), 삼불화 질소(NF<sub>3</sub>), 트리플루오로메탄(CHF<sub>3</sub>) 등), 브롬화 수소(HBr), 산소(O<sub>2</sub>), 이들 가스에 헬륨(He)이나 아르곤(Ar) 등의 희가스를 첨가한 가스, 등을 이용할 수 있다.

[0089] 건식 에칭법으로는, 평행평판형 RIE(Reactive Ion Etching)법이나, ICP(Inductively Coupled Plasma: 유도결합형 플라즈마) 에칭법을 이용할 수 있다. 원하는 가공 형상으로 에칭할 수 있도록, 에칭 조건(코일형의 전극에 인가되는 전력량, 기판 측의 전극에 인가되는 전력량, 기판 측의 전극 온도 등)을 적절히 조절한다.

[0090] 습식 에칭에 이용하는 에칭액으로는, 인산과 초산과 질산을 섞은 용액 등을 이용할 수 있다. 또한, IT007N(칸토 카가꾸)을 이용하여도 좋다.

[0091] 또한, 습식 에칭 후의 에칭액은 에칭된 재료와 함께 세척에 의해 제거된다. 이 제거된 재료를 포함하는 에칭

액의 폐액을 정제하여, 포함되는 재료를 재이용하여도 좋다. 이 에칭 후의 폐액에서 산화물 반도체층에 포함되는 인듐 등의 재료를 회수하여 재이용으로써, 자원을 유효하게 활용하여 저비용화 할 수 있다.

[0092] 원하는 가공 형상으로 에칭할 수 있도록, 재료에 맞추어 에칭 조건(에칭액, 에칭 시간, 온도 등)을 적절히 조절한다.

[0093] 이어서, 게이트 절연층(402), 및 산화물 반도체층(431) 위에, 금속 도전막을 형성한다. 금속 도전막을 스퍼터링법이나 진공 증착법으로 형성하면 된다. 금속 도전막의 재료로는, 알루미늄(Al), 크롬(Cr), 구리(Cu), 탄탈(Ta), 티탄(Ti), 몰리브덴(Mo), 텅스텐(W)에서 선택된 원소, 상기한 원소를 성분으로 하는 합금, 또는 상기한 원소를 조합한 합금 등을 들 수 있다. 또한, 망간(Mn), 마그네슘(Mg), 지르코늄(Zr), 베릴륨(Be), 이트륨(Y) 중 어느 하나 또는 복수에서 선택된 재료를 이용하여도 좋다. 또한, 금속 도전막은, 단층 구조이어도, 2층 이상의 적층 구조로 하여도 좋다. 예를 들어, 실리콘을 포함하는 알루미늄막의 단층 구조, 구리 또는 구리를 주성분으로 하는 막의 단층 구조, 알루미늄막 위에 티탄막을 적층하는 2층 구조, 질화 탄탈막 또는 질화 구리막 위에 구리막을 적층하는 2층 구조, 티탄막 위에 알루미늄막을 적층하고, 나아가 알루미늄막 위에 티탄막을 적층하는 3층 구조 등을 들 수 있다. 또한, 알루미늄(Al)에, 티탄(Ti), 탄탈(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 네오디뮴(Nd), 스칸듐(Sc)에서 선택된 원소를 단수, 또는 복수 조합한 막, 합금막, 또는 질화막을 이용하여도 좋다.

[0094] 금속 도전막 후에 가열 처리를 행하는 경우에는, 이 가열 처리에 견딜 수 있는 내열성을 금속 도전막에 갖도록 하는 것이 바람직하다.

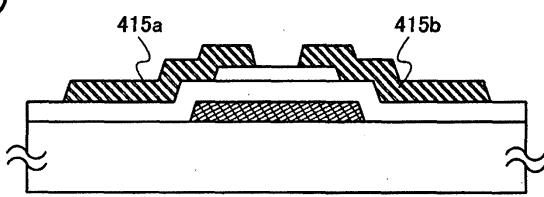

[0095] 제 3 포토리소 그래피 공정에 의해 금속 도전막 위에 레지스트 마스크를 형성하고, 선택적으로 에칭을 하여 소스 전극층(415a), 드레인 전극층(415b)을 형성한 후, 레지스트 마스크를 제거한다(도 4(C) 참조).

[0096] 한편, 금속 도전막의 에칭 시에, 산화물 반도체층(431)은 제거되지 않도록 각각의 재료 및 에칭 조건을 적절히 조절한다.

[0097] 한편, 제 3 포토리소 그래피 공정에서는, 산화물 반도체층(431)은 일부만이 에칭되고, 흄부(요부)를 갖는 산화물 반도체층이 될 수도 있다. 또한, 이 공정에서 이용하는 레지스트 마스크를 잉크젯법으로 형성하여도 좋다. 레지스트 마스크를 잉크젯법으로 형성하면 포토 마스크를 사용하지 않으므로, 제조 비용을 저감할 수 있다.

[0098] 또한, 포토리소 그래피 공정에서 이용하는 포토 마스크 수 및 공정 수를 삭감하기 위해, 투과된 광이 복수의 강도가 되는 노광 마스크인 다계조 마스크에 의해 형성된 레지스트 마스크를 이용하여 에칭 공정을 행하여도 좋다. 다계조 마스크를 이용하여 형성한 레지스트 마스크는 복수의 막후를 갖는 형상이 되고, 애싱을 행함으로써 더욱더 형상을 변형할 수 있으므로, 다른 패턴으로 가공하는 복수의 에칭 공정에 이용할 수 있다. 따라서, 한 장의 다계조 마스크에 의해, 적어도 2종류 이상의 다른 패턴에 대응하는 레지스트 마스크를 형성할 수 있다. 따라서 노광 마스크 수를 삭감할 수 있고, 대응하는 포토리소 그래피 공정도 삭감할 수 있으므로, 공정의 간략화가 가능해진다.

[0099] 이어서, 아산화질소(N<sub>2</sub>O), 질소(N<sub>2</sub>), 또는 아르곤(Ar) 등의 가스를 이용한 플라즈마 처리를 행한다. 이 플라즈마 처리에 의해 노출되어 있는 산화물 반도체층의 표면에 부착한 흡착수 등을 제거한다. 또한, 산소와 아르곤의 혼합 가스를 이용하여 플라즈마 처리를 행하여도 좋다.

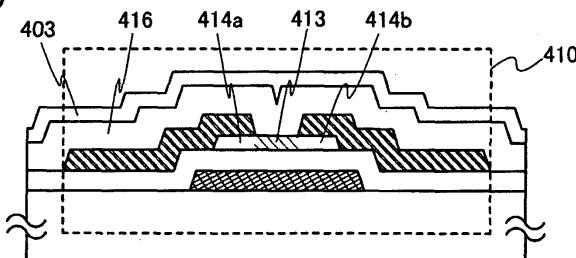

[0100] 플라즈마 처리를 행한 후, 대기에 접촉하지 않고, 산화물 반도체층의 일부에 접하는 보호 절연막이 되는 산화물 절연층(416)을 형성한다.

[0101] 산화물 절연층(416)은, 적어도 1nm 이상의 막후로 하고, 스퍼터링법 등, 산화물 절연층(416)에 물, 수소 등의 불순물을 혼입시키지 않는 방법을 적절히 이용하여 형성할 수 있다. 산화물 절연층(416)에 수소가 포함되면, 이 수소의 산화물 반도체층으로의 혼입이 발생하여 산화물 반도체층(431)의 백채널이 저저항화(N형화)되어, 기생 채널이 형성된다. 따라서, 산화물 절연층(416)은 가능한한 수소를 포함하지 않는 막이 되도록, 성막 방법으로 수소를 이용하지 않는 것이 중요하다.

[0102] 여기서는, 산화물 절연층(416)으로 막후 200nm의 산화 실리콘막을 스퍼터링법을 이용하여 성막한다. 성막 시의 기판 온도는, 실온 이상 300°C 이하로 하면 되고, 본 실시형태에서는 100°C로 한다. 산화 실리콘막의 스퍼터링법에 의한 성막은, 희가스(대표적으로는 아르곤) 분위기 하, 산소 분위기 하, 또는 희가스(대표적으로는 아르곤) 및 산소 분위기 하에서 행할 수 있다. 또한, 타겟으로 산화 실리콘 타겟 또는 실리콘 타겟을 이

용할 수 있다. 예를 들어, 실리콘 타겟을 이용하여, 산소, 및 질소 분위기 하에서 스퍼터링법에 의해 산화 실리콘막을 형성할 수 있다.

[0103] 이어서, 불활성 가스 분위기 하, 또는 산소 가스 분위기 하에서 제 2 가열 처리 (바람직하게는 200°C 이상 400°C 이하, 예를 들어 250°C 이상 350°C 이하)를 행한다. 예를 들어, 질소 분위기 하에서 250°C, 1시간의 제 2 가열 처리를 행한다. 제 2 가열 처리를 하면, 산화물 반도체층의 일부(채널 형성 영역)가 산화물 절연 층(416)과 접한 상태에서 가열된다. 이에 의해, 산화물 반도체층의 일부(채널 형성 영역)에 산소가 공급된다.

[0104] 이상의 공정을 거침으로써, 산화물 반도체층에 대해 탈수화 또는 탈수소화를 위한 가열 처리를 한 후, 산화물 반도체층의 일부(채널 형성 영역)를 선택적으로 산소 파이ning의 상태로 한다. 그 결과, 게이트 전극층(411)과 겹치는 채널 형성 영역(413)은 I형이 되고, 소스 전극층(415a)에 겹치는 소스 영역(414a)과, 드레인 전극층(415b)에 겹치는 드레인 영역(414b)이 자기 정합적으로 형성된다. 이상의 공정으로 박막 트랜지스터(410)가 형성된다.

[0105] 85°C,  $2 \times 10^6 \text{ V/cm}$ , 12시간의 게이트 바이어스?열 스트레스 시험(BT 시험)에서는, 불순물이 산화물 반도체에 첨가되어 있으면, 불순물과 산화물 반도체의 주성분의 결합이, 강전계(B:바이어스)와 고온(T:온도)에 의해 절단되고, 생성된 미결합이 역치 전압(Vth)의 드리프트를 유발하게 된다. 이에 대해, 산화물 반도체의 불순물, 특히 수소나 물 등을 최대한 제거하고, 상기의 고밀도 플라즈마 CVD 장치를 이용하여 치밀하고 절연 내압이 높은 고품질의 절연막으로 하고, 산화물 반도체와의 계면 특성을 양호하게 함으로써, BT 시험에 대해서도 안정적인 트랜지스터를 얻을 수 있다.

[0106] 나아가 대기 중, 100°C 이상 200°C 이하, 1시간 이상 30시간 이하에서 가열 처리를 하여도 좋다. 여기서는 150°C에서 10시간 가열 처리를 한다. 이 가열 처리는 일정한 가열 온도를 유지하여 가열하여도 좋으며, 실온에서 100°C 이상 200°C의 가열 온도로의 승온과, 가열 온도에서 실온까지의 강온을 복수회 반복하여 행하여도 좋다. 또한, 이 가열 처리를, 산화물 절연막 형성 전에, 감압 하에서 행하여도 좋다. 감압 하에서 가열 처리를 하면, 가열 시간을 단축할 수 있다. 이 가열 처리에 의해, 산화물 반도체층에서 산화물 절연층 중에 수소를 포함시킬 수 있다.

[0107] 한편, 드레인 전극층(415b)과 중첩한 산화물 반도체층에서 드레인 영역(414b)을 형성함으로써, 박막 트랜지스터의 신뢰성의 향상을 도모할 수 있다. 구체적으로는, 드레인 영역(414b)을 형성함으로써, 드레인 전극층(415b)에서 드레인 영역(414b), 채널 형성 영역(413)에 걸쳐, 도전성을 단계적으로 변화시킬 수 있도록 한 구조로 할 수 있다.

[0108] 또한, 산화물 반도체층에서의 소스 영역 또는 드레인 영역은, 산화물 반도체층의 막후가 15nm 이하로 얇은 경우는 막후 방향 전체에 걸쳐 형성되나, 산화물 반도체층의 막후가 30nm 이상 50nm 이하로 더욱 얇은 경우는, 산화물 반도체층의 일부, 소스 전극층 또는 드레인 전극층과 접하는 영역 및 그 근방이 저저항화되어 소스 영역 또는 드레인 영역이 형성되고, 산화물 반도체층에서 게이트 절연층에 가까운 영역은 I형으로 할 수도 있다.

[0109] 산화물 절연층(416) 위에 추가로 보호 절연층을 형성하여도 좋다. 예를 들어, RF 스퍼터링법을 이용하여 질화 실리콘막을 형성한다. RF 스퍼터링법은, 양산성이 좋으므로, 보호 절연층의 성막 방법으로 바람직하다. 보호 절연층은, 수분이나, 수소 이온이나,  $\text{OH}^-$  등의 불순물을 포함하지 않고, 이들이 외부에서 침입하는 것을 막는 무기 절연막을 이용하고, 질화 실리콘막, 질화 알루미늄막, 질화산화 실리콘막, 산화질화 알루미늄막 등을 이용한다. 본 실시형태에서는, 보호 절연층으로 보호 절연층(403)을, 질화 실리콘막을 이용하여 형성한다 (도 4(D) 참조).

[0110] 한편, 본 실시형태의 내용 또는 그 내용의 일부는, 다른 실시형태의 내용 또는 그 내용의 일부 또는 실시예의 내용 또는 그 내용의 일부와 자유롭게 조합하는 것이 가능하다.

[0111] (실시형태 3)

[0112] 본 실시형태에서는, 실시형태 1에 나타낸 액정 표시 장치에서, 터치 패널 기능을 부가한 액정 표시 장치의 구성에 대해, 도 5(A), (B)를 이용하여 설명한다.

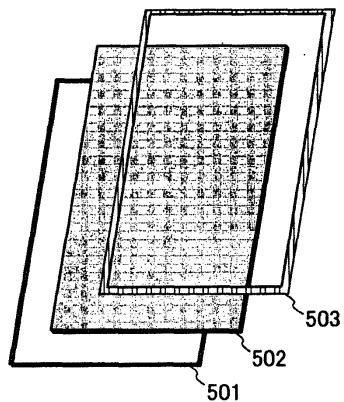

- [0113] 도 5(A)는, 본 실시형태의 액정 표시 장치의 개략도이다. 도 5(A)에는, 실시형태 1의 액정 표시 장치인 액정 표시 패널(501)에 터치 패널 유닛(502)을 중첩하여 형성하고, 하우징(503)으로 합착시키는 구성에 대해 나타낸다. 터치 패널 유닛(502)은, 저항막 방식, 표면형 정전 용량 방식, 투영형 정전 용량 방식 등을 적절히 이용할 수 있다.

- [0114] 도 5(A)에 나타낸 바와 같이, 액정 표시 패널(501)과 터치 패널 유닛(502)을 각각 제작하여 중첩함으로써, 터치 패널 기능을 부가한 액정 표시 장치의 제작에 관한 비용의 삭감을 도모할 수 있다.

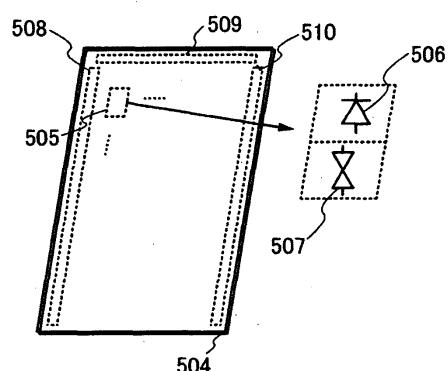

- [0115] 도 5(A)와는 다른 터치 패널 기능을 부가한 액정 표시 장치의 구성에 대해, 도 5(B)에 나타낸다. 도 5(B)에 나타낸 액정 표시 장치(504)는, 복수 형성되는 화소(505)에 광센서(506), 액정 소자(507)를 갖는다. 이로 인해, 도 5(A)와는 다르고, 터치 패널 유닛(502)을 중첩하여 제작할 필요가 없으며, 액정 표시 장치의 박형화를 도모할 수 있다. 한편, 주사선 구동 회로(508), 신호선 구동 회로(509), 광센서용 구동 회로(510)를 화소(505)와 동일한 기판 위에 제작함으로써, 액정 표시 장치의 소형화를 도모할 수 있다. 한편, 광센서(506)는, 아몰퍼스 실리콘 등을 이용하여 형성하고, 산화물 반도체를 이용한 트랜지스터와 중첩하여 형성하는 구성으로 하여도 좋다.

- [0116] 터치 패널의 기능을 부가한 액정 표시 장치에서, 산화물 반도체층을 구비하는 트랜지스터를 이용함으로써, 정지화를 표시할 때의, 화상의 유지 특성을 향상시킬 수 있다. 그리고 그 사이의, 구동 회로부의 동작을 정지함으로써 저소비 전력화를 도모할 수 있다.

- [0117] 한편, 본 실시형태의 내용 또는 그 내용의 일부는, 다른 실시형태의 내용 또는 그 내용의 일부 또는 실시예의 내용 또는 그 내용의 일부와 자유롭게 조합하는 것이 가능하다.

- [0118] (실시형태 4)

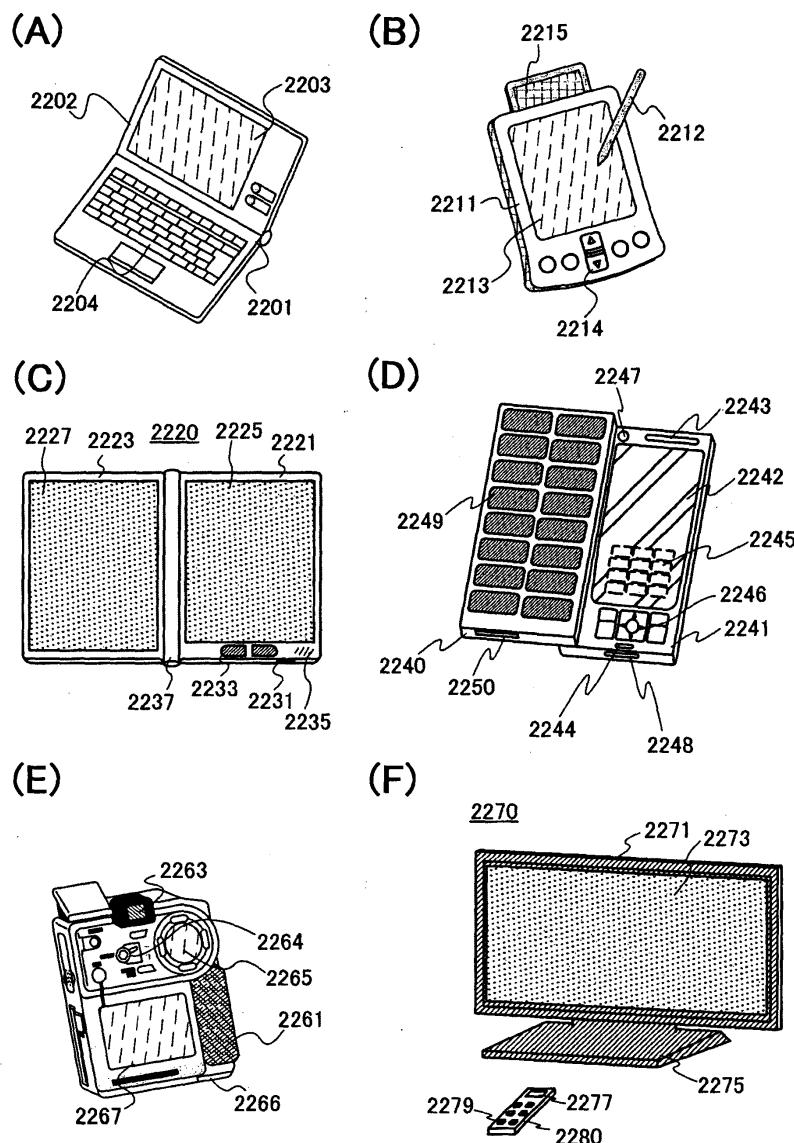

- [0119] 본 실시형태에서는, 실시형태 1에서 얻어지는 액정 표시 장치를 탑재한 전자 기기의 예에 대해 도 6(A) 내지 도 6(F)를 참조하여 설명한다. 한편, 실시형태 1에 관한 액정 표시 장치는, 전자 기기에서 표시부로 이용된다.

- [0120] 도 6(A)는, 노트북형 개인용 컴퓨터를 나타낸 도면으로, 본체(2201), 하우징(2202), 표시부(2203), 키보드(2204) 등에 의해 구성된다. 이 개인용 컴퓨터의 표시부 등으로 실시형태 1에 나타낸 액정 표시 장치를 적용하는 것은, 소비 전력의 저감 뿐만 아니라, 장시간 사용에서의 안정 피로의 저감이라는 의미에서도 효과가 크다. 이하, 그 이유에 대해 서술한다. 개인용 컴퓨터 등은, 주로 사용자의 조작에 의해 표시가 변화한다. 즉, 사용자에 의한 조작 사이에는, 이 개인용 컴퓨터에는 정지화가 표시되게 된다. 또한, 일반적으로 액정 표시 장치에서는, 액정 재료의 열화를 억제하기 위해 반전 구동이 이루어진다. 정지화를 표시하고 있는 기간에 이 반전 구동을 행하면, 사용자가 화상의 눈부심을 시인할 가능성이 있다. 이 눈부심은, 사용자의 안정 피로를 조장하게 된다. 한편, 실시형태 1에 나타낸 액정 표시 장치는, 정지화의 표시 기간에서, 각 화소에서 화상 신호를 장기간에 걸쳐 유지하는 것이 가능하고, 사용자에게 시인되는 눈부심을 경감할 수 있다. 이로 인해, 개인용 컴퓨터 등에서, 실시형태 1에 나타낸 액정 표시 장치를 적용하는 것은, 사용자의 안정 피로를 저감하는 효과가 크다고 할 수 있다.

- [0121] 도 6(B)는, 휴대 정보 단말(PDA)을 나타낸 도면이고, 본체(2211)에는 표시부(2213)와, 외부 인터페이스(2215)와, 조작 버튼(2214) 등이 형성되어 있다. 또한, 조작용 부속품으로 스타일러스(2212)가 있다.

- [0122] 도 6(C)는, 전자 페이퍼의 일 예로, 전자 서적(2220)을 나타낸 도면이다. 전자 서적(2220)은, 하우징(2221) 및 하우징(2223)의 2개의 하우징으로 구성되어 있다. 하우징(2221) 및 하우징(2223)은, 축부(2237)에 의해 일체로 되어 있고, 이 축부(2237)를 축으로 개폐 동작을 행할 수 있다. 이와 같은 구성에 의해, 전자 서적(2220)은, 종이 서적과 동일하게 이용하는 것이 가능하다.

- [0123] 하우징(2221)에는 표시부(2225)가 내장되고, 하우징(2223)에는 표시부(2227)가 내장되어 있다. 표시부(2225) 및 표시부(2227)는, 이어지는 화면을 표시하는 구성으로 하여도 좋으며, 다른 화면을 표시하는 구성으로 하여도 좋다. 다른 화면을 표시하는 구성으로 함으로써, 예를 들어 우측의 표시부(도 6(C)에서는 표시부(2225)에 문장을 표시하고, 좌측의 표시부(도 6(C)에서는 표시부(2227))에 화상을 표시할 수 있다.

- [0124] 또한, 도 6(C)에서는, 하우징(2221)에 조작부 등을 구비한 예를 나타낸다. 예를 들어, 하우징(2221)은, 전원(2231), 조작키(2233), 스피커(2235) 등을 구비한다. 조작키(2233)에 의해, 페이지를 보낼 수 있다. 한편,

하우징의 표시부와 동일면에 키보드나 포인팅 디바이스 등을 구비하는 구성으로 하여도 좋다. 또한, 하우징의 뒷면이나 측면에, 외부 접속용 단자(이어폰 단자, USB 단자, 또는 AC 어댑터 및 USB 케이블 등의 각종 케이블과 접속 가능한 단자 등), 기록 매체 삽입부 등을 구비하는 구성으로 하여도 좋다. 또한, 전자 서적(2220)은, 전자 사전으로서의 기능을 갖게 한 구성으로 하여도 좋다.

[0125] 또한, 전자 서적(2220)은, 무선으로 정보를 송수신할 수 있는 구성으로 하여도 좋다. 무선에 의해, 전자 서적 서버에서, 원하는 서적 데이터 등을 구입하고, 다운로드 하는 구성으로 하는 것도 가능하다.

[0126] 한편, 전자 폐이퍼는, 정보를 표시하는 것이면 어떠한 분야에도 적용하는 것이 가능하다. 예를 들어, 전자 서적 이외에도, 포스터, 전철 등 탈것의 차내 광고, 신용 카드 등의 각종 카드에서의 표시 등에 적용할 수 있다.

[0127] 도 6(D)는, 휴대 전화기를 나타낸 도면이다. 이 휴대 전화기는, 하우징(2240) 및 하우징(2241)의 2개의 하우징으로 구성되어 있다. 하우징(2241)은, 표시 패널(2242), 스피커(2243), 마이크로폰(2244), 포인팅 디바이스(2246), 카메라용 렌즈(2247), 외부 접속 단자(2248) 등을 구비하고 있다. 또한, 하우징(2240)은, 이 휴대 전화기의 충전을 행하는 태양 전지 셀(2249), 외부 메모리 슬롯(2250) 등을 구비하고 있다. 또한, 안테나는 하우징(2241) 내부에 내장되어 있다.

[0128] 표시 패널(2242)은 터치 패널 기능을 구비하고 있으며, 도 6(D)에는 영상 표시되어 있는 복수의 조작키(2245)를 점선으로 나타냈다. 한편, 이 휴대 전화는, 태양 전지 셀(2249)에서 출력되는 전압을 각 회로에 필요한 전압으로 승압하기 위한 승압 회로를 실장하고 있다. 또한, 상기 구성에 더하여, 비접촉 IC칩, 소형 기록 장치 등을 내장한 구성으로 할 수도 있다.

[0129] 표시 패널(2242)은, 사용 형태에 따라 표시 방향이 적절히 변화한다. 또한, 표시 패널(2242)과 동일면 위에 카메라용 렌즈(2247)를 구비하고 있으므로, 영상 통화가 가능하다. 스피커(2243) 및 마이크로폰(2244)은 음성 통화에 한정되지 않고, 영상 통화, 녹음, 재생 등이 가능하다. 또한, 하우징(2240)과 하우징(2241)은 슬라이드되고, 도 6(D)과 같이 전개되어 있는 상태에서 서로 겹쳐진 상태로 할 수 있어, 휴대하기 적합한 소형화가 가능하다.

[0130] 외부 접속 단자(2248)는 AC어댑터나 USB 케이블 등의 각종 케이블과 접속할 수 있고, 충전이나 데이터 통신이 가능하도록 되어 있다. 또한, 외부 메모리 슬롯(2250)에 기록 매체를 삽입하고, 보다 대량의 데이터의 저장 및 이동에 대응할 수 있다. 또한, 상기 기능에 더하여, 적외선 통신 기능, 텔레비전 수신 기능 등을 구비한 것이어도 좋다.

[0131] 도 6(E)는, 디지털 카메라를 나타낸 도면이다. 이 디지털 카메라는, 본체(2261), 표시부(A)(2267), 접안부(2263), 조작 스위치(2264), 표시부(B)(2265), 배터리(2266) 등에 의해 구성되어 있다.

[0132] 도 6(F)는, 텔레비전 장치를 나타낸 도면이다. 텔레비전 장치(2270)에서는, 하우징(2271)에 표시부(2273)가 내장되어 있다. 표시부(2273)에 의해, 영상을 표시하는 것이 가능하다. 한편, 여기서는, 스탠드(2275)에 의해 하우징(2271)을 지지한 구성을 나타냈다.

[0133] 텔레비전 장치(2270)의 조작은, 하우징(2271)이 구비하는 조작 스위치나, 별도의 리모콘 조작기(2280)에 의해 행할 수 있다. 리모콘 조작기(2280)가 구비하는 조작키(2279)에 의해, 채널이나 음량의 조작을 행할 수 있고, 표시부(2273)에 표시되는 영상을 조작할 수 있다. 또한, 리모콘 조작기(2280)에, 이 리모콘 조작기(2280)에서 출력하는 정보를 표시하는 표시부(2277)를 형성하는 구성으로 하여도 좋다.

[0134] 한편, 텔레비전 장치(2270)는, 수신기나 모뎀 등을 구비한 구성으로 하는 것이 적합하다. 수신기에 의해, 일반적인 텔레비전 방송 수신을 할 수 있다. 또한, 모뎀을 통해 유선 또는 무선에 의한 통신 네트워크에 접속함으로써, 한방향(송신자에서 수신자) 또는 쌍방향(송신자와 수신자 간, 또는 수신자끼리 등)의 정보 통신을 하는 것이 가능하다.

[0135] 한편, 본 실시형태의 내용 또는 그 내용의 일부는, 다른 실시형태의 내용 또는 그 내용의 일부 또는 실시예의 내용 또는 그 내용의 일부와 자유롭게 조합하는 것이 가능하다.

[0136] [실시예 1]

[0137] 본 실시예에서는, 평가용 소자(TEG라고도 함)를 이용한 오프 전류의 측정값에 대해 이하에 설명한다.

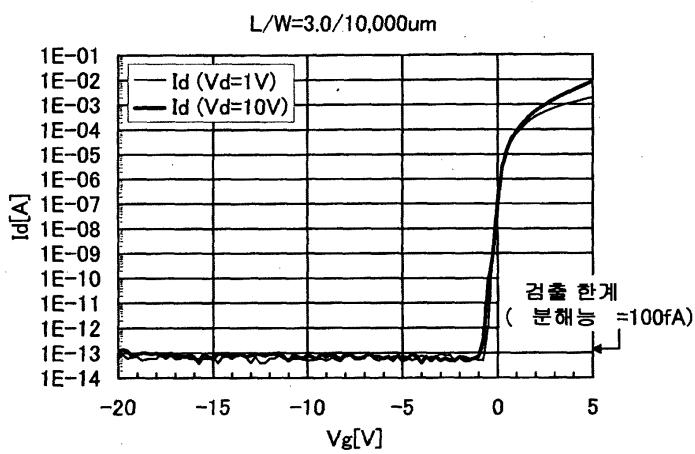

- [0138] 도 7에  $L/W=3\mu\text{m}/50\mu\text{m}$ 의 트랜지스터를 200개 병렬로 접속함으로써 제작한,  $L/W=3\mu\text{m}/10000\mu\text{m}$ 의 트랜지스터의 초기 특성을 나타낸다. 또한, 상면도를 도 8(A)에 나타내고, 그 일부를 확대한 상면도를 도 8(B)에 나타낸다. 도 8(B)의 점선으로 둘러싼 영역이  $L/W=3\mu\text{m}/50\mu\text{m}$ ,  $Lov=1.5\mu\text{m}$ 의 1단의 트랜지스터이다. 한편, 여기서는,  $Lov$ 란 소스 또는 드레인과 산화물 반도체층이 중첩하는 영역의 채널 길이 방향으로의 길이를 나타낸다. 트랜지스터의 초기 특성을 측정하기 위해, 기판 온도를 실온으로 하고, 소스-드레인 간 전압(이하, 드레인 전압 또는  $Vd$ 라 한다)을 10V로 하고, 소스-게이트 간 전압(이하, 게이트 전압 또는  $Vg$ 라 한다)을  $-20V \sim +20V$ 까지 변화시켰을 때의 소스-드레인 전류(이하, 드레인 전류 또는  $Id$ 라 한다)의 변화 특성, 즉  $Vg-Id$  특성을 측정하였다. 한편, 도 7에서는,  $Vg$ 를  $-20V \sim +5V$ 까지의 범위로 나타냈다.

- [0139] 도 7에 나타낸 바와 같이 채널 폭( $W$ )이  $10000\mu\text{m}$ 인 트랜지스터는,  $Vd$ 가 1V 및 10V에서 오프 전류는  $1 \times 10^{-13}[\text{A}]$  이하로 되어 있고, 측정기(반도체 파라메터?아널라이저, Agilent 4156C; Agilent사)의 분해능( $100\text{fA}$ ) 이하로 되어 있다. 즉, 채널 길이가  $3\mu\text{m}$ 인 경우, 이 트랜지스터의 채널 폭  $1\mu\text{m}$  당 오프 전류값은,  $10\text{aA}/\mu\text{m}$  이하인 것으로 예상된다. 한편, 채널 길이가  $3\mu\text{m}$  이상이면, 이 트랜지스터의 오프 전류값은  $10\text{aA}/\mu\text{m}$  이하인 것으로 예상됨을 밝혀둔다.

- [0140] 측정한 트랜지스터의 제작 방법에 대해 설명한다.

- [0141] 우선, 유리 기판 위에 하지층으로, CVD법에 의해 질화 규소층을 형성하고, 질화 규소층 위에 산화질화 규소층을 형성하였다. 산화질화 규소층 위에 게이트 전극층으로 스퍼터링법에 의해 텅스텐층을 형성하였다. 여기서, 텅스텐층을 선택적으로 에칭하여 게이트 전극층을 형성하였다.

- [0142] 다음으로, 게이트 전극층 위에 게이트 절연층으로 CVD법에 의해 두께 100nm의 산화질화 규소층을 형성하였다.

- [0143] 다음으로, 게이트 절연층 위에, 스퍼터링법에 의해 In-Ga-Zn-O계 금속 산화물 타겟(몰수비로,  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO}=1:1:2$ )을 이용하여, 두께 50nm의 산화물 반도체층을 형성하였다. 여기서, 산화물 반도체층을 선택적으로 에칭하고, 섬모양의 산화물 반도체층을 형성하였다.

- [0144] 다음으로, 산화물 반도체층에 대해 클린 오븐에서 질소 분위기 하,  $450^\circ\text{C}$ , 1시간의 제 1 열처리를 하였다.

- [0145] 다음으로, 산화물 반도체층 위에 소스 전극층 및 드레인 전극층으로 티탄층(두께 150nm)을 스퍼터링법에 의해 형성하였다. 여기서, 소스 전극층 및 드레인 전극층을 선택적으로 에칭하고, 1개의 트랜지스터의 채널 길이( $L$ )를  $3\mu\text{m}$ , 채널 폭( $W$ )을  $50\mu\text{m}$ 로 하고, 200개를 병렬로 함으로써,  $L/W=3\mu\text{m}/10000\mu\text{m}$ 가 되도록 하였다.

- [0146] 다음으로, 산화물 반도체층에 접하도록 보호 절연층으로 리액티브 스퍼터링법에 의해 산화 규소층을 막후 300nm로 형성하였다. 여기서, 보호층인 산화 규소층을 선택적으로 에칭하고, 게이트 전극층, 소스 전극층 및 드레인 전극층 위에 개구부를 형성하였다. 그 후, 질소 분위기 하,  $250^\circ\text{C}$ , 1시간의 제 2 열처리를 하였다.

- [0147] 그리고,  $Vg-Id$  특성을 측정하기 전에  $150^\circ\text{C}$ , 10시간 가열하였다.

- [0148] 이상의 공정에 의해, 보통 게이트형의 트랜지스터를 제작하였다.

- [0149] 도 7에 나타낸 바와 같이 트랜지스터의 오프 전류가  $1 \times 10^{-13}[\text{A}]$  정도인 것은, 상기 제작 공정에서 산화물 반도체층 중에서의 수소 농도를 충분히 저감할 수 있었기 때문이다. 산화물 반도체층 중의 수소 농도는,  $1 \times 10^{16} \text{ atoms/cm}^3$  이하로 한다. 한편, 산화물 반도체층 중의 수소 농도 값은, 이차이온 질량분석법(SIMS: Secondary Ion Mass Spectroscopy)으로 얻어진 것이다.

- [0150] 또한, In-Ga-Zn-O계 산화물 반도체를 이용하는 예를 도시하였으나, 특별히 한정되는 것은 아니며, 다른 산화물 반도체 재료, 예를 들어, In-Sn-Zn-O계, Sn-Ga-Zn-O계, Al-Ga-Zn-O계, Sn-Al-Zn-O계, In-Zn-O계, In-Sn-O계, Sn-Zn-O계, Al-Zn-O계, In-O계, Sn-O계, Zn-O계 등을 이용할 수 있다. 또한, 산화물 반도체 재료로,  $\text{AlO}_x$ 를 2.5~10wt% 혼입시킨 In-Al-Zn-O계나,  $\text{SiO}_x$ 를 2.5~10wt% 혼입시킨 In-Zn-O계를 이용할 수도 있다.

- [0151] 또한, 캐리어 측정기로 측정되는 산화물 반도체층의 캐리어 밀도는,  $1 \times 10^{14}/\text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12}/\text{cm}^3$  이하이다. 즉, 산화물 반도체층의 캐리어 밀도는, 무한대로 0에 가깝게 할 수 있다.

- [0152] 또한, 트랜지스터의 채널 길이( $L$ )를 10nm 이상 1000nm 이하로 할 수도 있고, 회로의 동작 속도를 고속화할 수 있으며, 오프 전류값이 매우 작으로, 더욱더 저소비 전력화를 도모할 수도 있다.

- [0153] 또한, 트랜지스터의 오프 상태에서, 산화물 반도체층은 절연체로 간주하여 회로 설계를 행할 수 있다.

- [0154] 이어서, 본 실시예에서 제작한 트랜지스터에 대해 오프 전류의 온도 특성을 평가하였다. 온도 특성은, 트랜지스터가 사용되는 최종 제품의 내환경성이나, 성능의 유지 등을 고려하였을 때 중요하다. 당연한 것이지만, 변화량이 작을수록 바람직하며, 제품 설계의 자유도가 증가한다.

- [0155] 온도 특성은, 항온조를 이용하여, -30, 0, 25, 40, 60, 80, 100, 및 120°C의 각각의 온도에서 트랜지스터를 형성한 기판을 일정 온도로 하고, 드레인 전압을 6V, 게이트 전압을 -20V~+20V까지 변화시켜  $Vg$ - $Id$  특성을 취득한다.

- [0156] 도 9(A)에 나타낸 것은, 상기 각각의 온도에서 측정한  $Vg$ - $Id$  특성을 겹쳐 쓰기한 것으로, 점선으로 둘러싼 오프 전류의 영역을 확대한 것을 도 9(B)에 나타낸다. 도면의 화살표로 나타낸 우단의 곡선이 -30°C, 좌단이 120°C에서 취득한 곡선이고, 그 외 온도에서 취득한 곡선은, 그 사이에 위치한다. 온 전류의 온도 의존성은 거의 보이지 않는다. 한편, 오프 전류는 확대도인 도 9(B)에서도 명확히 알 수 있듯이, 게이트 전압이 -20V 근방을 제외하고, 모든 온도에서 측정기의 분해능 근방인  $1 \times 10^{-12}$  [A] 이하로 되어 있고, 온도 의존성도 보이지 않는다. 즉, 120°C의 고온에서도, 오프 전류가  $1 \times 10^{-12}$  [A] 이하를 유지하고 있고, 채널 폭(W)이  $10000\mu\text{m}$ 인 것을 고려하면, 오프 전류가 매우 작은 것을 알 수 있다. 즉, 채널 길이가  $3\mu\text{m}$ 인 경우, 이 트랜지스터의 채널 폭  $1\mu\text{m}$  당 오프 전류값은,  $100\text{aA}/\mu\text{m}$  이하인 것으로 예상된다. 한편, 채널 길이가  $3\mu\text{m}$  이상이면, 이 트랜지스터의 오프 전류값은  $100\text{aA}/\mu\text{m}$  이하인 것으로 예상할 수 있는 것도 밝혀둔다. 또한, 도 9의 데이터는, 본 실시예에서 제작한 트랜지스터는, -30°C 이상 120°C 이하이면, 오프 전류값이  $100\text{aA}/\mu\text{m}$  이하가 되는 것을 나타낸 것이고, 당연히 85°C에서의 오프 전류값도  $100\text{aA}/\mu\text{m}$ 이 되는 것으로 예상할 수 있는 것을 밝혀둔다. 즉, 도 9의 데이터는, 본 실시예에서 제작한 트랜지스터를 각 화소에 형성되는 트랜지스터로서 적용한 액정 표시 장치에 대해, 85°C의 항온 보존 시험을 행한 경우, 이 화소의 화상 신호의 리크가 저감되고, 표시의 열화(변화)가 억제되는 것을 나타내고 있다고 할 수 있다.

- [0157] 상기와 같이 고순도화된 산화물 반도체(purified OS)를 이용한 트랜지스터는, 오프 전류의 온도 의존성이 거의 나타나지 않는다. 이는, 산화물 반도체가 고순도화됨으로써, 도전형이 무한대로 진성형에 가까워지고, 페르미 준위가 금제대의 중앙에 위치하므로, 온도 의존성을 나타내지 않게 된다고 할 수 있다. 또한, 이는, 산화물 반도체의 밴드갭이 크고, 열여기 캐리어가 매우 적은 것에도 기인한다. 또한, 소스 영역 및 드레인 영역은 축퇴한 상태에 있으므로 역시 온도 의존성이 나타나지 않는 요인이 된다. 트랜지스터의 동작은, 축퇴한 소스 영역에서 산화물 반도체에 주입된 캐리어에 의한 것이 대부분이고, 캐리어 밀도의 온도 의존성이 없다는 점에서 상기 특성(오프 전류의 온도 의존성 없음)을 설명할 수 있다.

- [0158] 이상의 결과는, 캐리어 밀도를  $1 \times 10^{14}/\text{cm}^3$  미만, 바람직하게는  $1 \times 10^{12}/\text{cm}^3$  이하로 한 트랜지스터가, 실온에서의 오프 전류값이  $10\text{aA}/\mu\text{m}$  이하이고 또한 85°C에서의 오프 전류값이  $100\text{aA}/\mu\text{m}$  이하가 되는 것을 나타낸 것이다. 또한, 이 트랜지스터를 액정 표시 장치의 각 화소가 갖는 트랜지스터로 적용함으로써, 이 액정 표시 장치의 소비 전력을 저감하는 것 및 표시의 열화(표시 품질의 저하)를 억제하는 것이 가능한 것을 나타낸 것이다. 나아가, 온도 등의 외부 인자에 기인하는 표시의 열화(변화)가 저감된 액정 표시 장치를 제공하는 것이 가능한 것을 나타낸 것이다.

### 부호의 설명

- |               |               |

|---------------|---------------|

| 10; 제어 회로     | 11; 주사선 구동 회로 |

| 12; 신호선 구동 회로 | 13; 화소부       |

| 14; 화소        | 15; 트랜지스터     |

| 16; 액정 소자     | 17; 용량 소자     |

| 20; 신호 생성 회로  | 21; 기억 회로     |

| 22; 비교 회로     | 23; 선택 회로     |

| 24; 표시 제어 회로  | 25; 메모리       |

|                 |                 |

|-----------------|-----------------|

| 400; 기판         | 402; 게이트 절연층    |

| 403; 보호 절연층     | 410; 박막 트랜지스터   |

| 411; 게이트 전극층    | 413; 채널 형성 영역   |

| 414a; 소스 영역     | 414b; 드레인 영역    |

| 415a; 소스 전극층    | 415b; 드레인 전극층   |

| 416; 산화물 절연층    | 430; 산화물 반도체막   |

| 431; 산화물 반도체층   | 501; 액정 표시 패널   |

| 502; 터치 패널 유닛   | 503; 하우징        |

| 504; 액정 표시 장치   | 505; 화소         |

| 506; 광센서        | 507; 액정 소자      |

| 508; 주사선 구동 회로  | 509; 신호선 구동 회로  |

| 510; 광센서용 구동 회로 | 2201; 본체        |

| 2202; 하우징       | 2203; 표시부       |

| 2204; 키보드       | 2211; 본체        |

| 2212; 스타일러스     | 2213; 표시부       |

| 2214; 조작 버튼     | 2215; 외부 인터페이스  |

| 2220; 전자 서적     | 2221; 하우징       |

| 2223; 하우징       | 2225; 표시부       |

| 2227; 표시부       | 2231; 전원        |

| 2233; 조작키       | 2235; 스피커       |

| 2237; 축부        | 2240; 하우징       |

| 2241; 하우징       | 2242; 표시 패널     |

| 2243; 스피커       | 2244; 마이크로폰     |

| 2245; 조작키       | 2246; 포인팅 디바이스  |

| 2247; 카메라용 렌즈   | 2248; 외부 접속 단자  |

| 2249; 태양 전지 셀   | 2250; 외부 메모리 슬롯 |

| 2261; 본체        | 2263; 접안부       |

| 2264; 조작 스위치    | 2265; 표시부(B)    |

| 2266; 배터리       | 2267; 표시부(A)    |

| 2270; 텔레비전 장치   | 2271; 하우징       |

| 2273; 표시부       | 2275; 스탠드       |

| 2277; 표시부       | 2279; 조작키       |

| 2280; 리모콘 조작기   |                 |

도면

도면1

(A)

(B)

## 도면2

## 도면3

(A)

(B)

(C)

## 도면4

(A)

(B)

(C)

(D)

도면5

(A)

(B)

## 도면6

## 도면7

도면8

(A)

(B)

## 도면9

(A)

$L/W=3.0/10,000\mu m (V_d=6V)$

(B)

$L/W=3.0/10,000\mu m (V_d=6V)$

|                |                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 液晶显示器和电子设备                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR1020120105505A</a>                                                                                                                                                                                                                                         | 公开(公告)日 | 2012-09-25 |

| 申请号            | KR1020127017948                                                                                                                                                                                                                                                          | 申请日     | 2010-11-19 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | YAMAZAKI SHUNPEI<br>아마자키순pei                                                                                                                                                                                                                                             |         |            |

| 发明人            | 야마자키순pei                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G02F1/1345 G02F1/1368                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | H01L29/7869 G09G3/3648 G09G2310/04 G09G2320/0214 G09G2320/103 H01L27/1225 G02F1/1368<br>G06F3/044 H01L29/78609 G02F1/13338 G02F1/136286 G06F3/0412 G06F3/045 G09G3/3677<br>G09G2300/0426 G09G2310/08 G09G2320/0247 G09G2320/043 G09G2330/021 H01L21/02483<br>H01L27/1255 |         |            |

| 代理人(译)         | 黃的.                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 2009288312 2009-12-18 JP<br>2010092111 2010-04-13 JP                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | KR101765849B1                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

本发明降低了液晶显示器的功耗，抑制了显示器的劣化。它还涉及抑制，包括温度等在内的外部因素引起的显示器的劣化。在该氧化物半导体层的每个像素中形成的晶体管构成沟道形成区域的晶体管被施加到该氧化物半导体层中。同时高度纯化。这样就可以做到小于10aA /  $\mu$ m，用85a的关断电流值和100aA /  $\mu$ m这样扼杀液晶显示器的功耗在室温下的关断电流值晶体管由于这种减少，显示器的劣化受到如上所述的抑制，显示器有可能使这个晶体管在高温下的关断电流值称为85°C 100aA /  $\mu$ m这种靶。由此，可以抑制由包括温度等在内的外部因素导致的液晶显示器的显示劣化。