(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0113468

(43) 공개일자 2010년10월21일

(51) Int. Cl.

G02F 1/1345 (2006.01)

(21) 출원번호 10-2010-0091393(분할)

(22) 출원일자 2010년09월17일

심사청구일자 2010년09월17일

(62) 원출원 특허 10-2004-0002533

입출원인 2004년01월14일

(1) 출판일자 2004년01월14일

심사청구일자 2008년12월30일

(30) 우선권

JP-P-2003-007568 2003년01월15일 일본(JP)

JP-P-2003-007697 2003년01월15일 일본(JP)

(71) 출원인

가부시키가이샤 학도오따이 에네루기 켄큐쇼

일본국 가나가와케 아쓰기시 하세 398

(72) 밤면자

글 8시

일본국 가나가와켄 아쓰기시 하세 398 가부시키가이샤

하도우따이 에네루기 케쿄쇼 나이

타카야마 토루

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이야 학도오따이 에네루기 케코쵸 나이

(뒤면에 계소)

(74) 대국왕

전체 청구항 수 : 총 21 항

(54) 액정표시장치 및 액정표시장치를 사용한 전자기기

### (57) 요약

액정표시장치는, 경량화 및 소형화를 저해하지 않고 휴대용 전자기기를 고기능화하기 위해서, 보다 구체적으로는 이 휴대용 전자기기에 설치된 액정표시장치를 기계적 강도가 손상되지 않고 고기능화하기 위해서, 제1 플라스틱 기판과, 제1 플라스틱 기판 위에 배치된 발광소자와, 발광소자를 덮는 수지와, 그 수지에 접한 절연막과, 절연막에 접한 반도체소자와, 반도체소자에 전기적으로 접속된 액정셀과, 제2 플라스틱 기판을 가지며, 반도체소자 및 액정셀은, 제1 플라스틱 기판과 제2 플라스틱 기판 사이에 설치된다.

대표도 - 도1

(72) 발명자

**마루야마 준야**

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이샤 한도오따이 에네루기 켄큐쇼 나이

**고토 유우고**

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이샤 한도오따이 에네루기 켄큐쇼 나이

**오노 유미코**

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이샤 한도오따이 에네루기 켄큐쇼 나이

---

**엔도 아키오**

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이샤 한도오따이 에네루기 켄큐쇼 나이

**아라이 야수유키**

일본국 가나가와켄 아쓰기시 하세 398 가부시키가

이샤 한도오따이 에네루기 켄큐쇼 나이

## 특허청구의 범위

### 청구항 1

제1 플라스틱 기판과,

상기 제1 플라스틱 기판 위에 형성된 발광소자와,

상기 발광소자를 덮은 수지로서, 상기 수지의 굴절율과 다른 굴절율을 갖는 투광성 입자를 포함하는 수지와,

상기 수지 위에 형성된 절연막과,

상기 절연막 위에 형성된 반도체소자와,

상기 반도체소자에 전기적으로 접속된 액정셀과,

제2 플라스틱 기판을 구비하고,

상기 반도체소자 및 상기 액정셀은, 상기 제1 플라스틱 기판과 상기 제2 플라스틱 기판 사이에 형성된 것을 특징으로 하는 액정표시장치.

### 청구항 2

오목부를 갖는 제1 플라스틱 기판과,

상기 제1 플라스틱 기판의 오목부 내에 형성된 발광소자와,

상기 발광소자를 덮도록 상기 오목부 내에 형성된 수지로서, 상기 수지의 굴절율과 다른 굴절율을 갖는 투광성 입자를 포함하는 수지와,

상기 수지 위에 형성된 절연막과,

상기 절연막 위에 형성된 반도체소자와,

상기 반도체소자에 전기적으로 접속된 액정셀과,

제2 플라스틱 기판을 구비하고,

상기 반도체소자 및 상기 액정셀은, 상기 제1 플라스틱 기판과 상기 제2 플라스틱 기판 사이에 형성된 것을 특징으로 하는 액정표시장치.

### 청구항 3

제1 플라스틱 기판과,

상기 제1 플라스틱 기판 위에 형성된 금속 반사막과,

상기 제1 플라스틱 기판 위에 형성되고, 상기 금속 반사막으로부터 전기적으로 분리되어 있는 발광소자와,

상기 발광소자를 덮는 수지로서, 상기 수지의 굴절율과 다른 굴절율을 갖는 투광성 입자를 포함하는 수지와,

상기 수지 위에 형성된 절연막과,

상기 절연막 위에 형성된 반도체소자와,

상기 반도체소자에 전기적으로 접속된 액정셀과,

제2 플라스틱 기판을 구비하고,

상기 반도체소자 및 상기 액정셀은, 상기 제1 플라스틱 기판과 상기 제2 플라스틱 기판 사이에 형성된 것을 특징으로 하는 액정표시장치.

#### 청구항 4

오목부를 갖는 제1 플라스틱 기판과,

상기 오목부 위에 형성된 금속 반사막과,

상기 오목부 내에 형성되고, 상기 금속 반사막으로부터 전기적으로 분리되어 있는 발광소자와,

상기 발광소자를 덮도록 상기 오목부 내에 형성된 수지로서, 상기 수지의 굴절율과 다른 굴절율을 갖는 투광성 입자를 포함하는 수지와,

상기 수지 위에 형성된 절연막과,

상기 절연막 위에 형성된 반도체소자와,

상기 반도체소자에 전기적으로 접속된 액정셀과,

제2 플라스틱 기판을 구비하고,

상기 반도체소자 및 상기 액정셀은, 상기 제1 플라스틱 기판과 상기 제2 플라스틱 기판 사이에 형성된 것을 특징으로 하는 액정표시장치.

#### 청구항 5

제 3 항 및 제 4 항 중 어느 한 항에 있어서,

상기 금속 반사막은 샌드블라스트된 것을 특징으로 하는 액정표시장치.

#### 청구항 6

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 액정셀은 광에 대해 투과형인 것을 특징으로 하는 액정표시장치.

#### 청구항 7

제 1 항에 있어서,

상기 발광소자는 발광다이오드인 것을 특징으로 하는 액정표시장치.

#### 청구항 8

제 7 항에 있어서,

상기 발광다이오드는 FPC에 접속되어, 상기 FPC를 통해 전류가 공급되는 것을 특징으로 하는 액정표시장치.

#### 청구항 9

제 2 항에 있어서,

상기 발광소자는 발광다이오드인 것을 특징으로 하는 액정표시장치.

#### 청구항 10

제 9 항에 있어서,

상기 발광다이오드는 FPC에 접속되어, 상기 FPC를 통해 전류가 공급되는 것을 특징으로 하는 액정표시장치.

#### 청구항 11

제 3 항에 있어서,

상기 발광소자는 발광다이오드인 것을 특징으로 하는 액정표시장치.

#### 청구항 12

제 11 항에 있어서,

상기 발광다이오드는 FPC에 접속되어, 상기 FPC를 통해 전류가 공급되는 것을 특징으로 하는 액정표시장치.

#### 청구항 13

제 4 항에 있어서,

상기 발광소자는 발광다이오드인 것을 특징으로 하는 액정표시장치.

#### 청구항 14

제 13 항에 있어서,

상기 발광다이오드는 FPC에 접속되어, 상기 FPC를 통해 전류가 공급되는 것을 특징으로 하는 액정표시장치.

#### 청구항 15

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 휴대전화.

#### 청구항 16

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 전자서적.

#### 청구항 17

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 손목시계.

#### 청구항 18

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 퍼스널 컴퓨터.

#### 청구항 19

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 자동차 앞유리.

#### 청구항 20

청구항 1 내지 4 중 어느 한 항에 따른 액정표시장치를 구비한 것을 특징으로 하는 전자카드.

## 청구항 21

제1항 내지 제4항 중 어느 한 항에 있어서,

상기 액정셀과 상기 수지 사이에 편광판을 더 구비하는 것을 특징으로 하는 액정표시장치.

## 명세서

### 기술분야

[0001] 본 발명은 액정표시장치에 관한 것으로, 특히, 휴대용 전자기기에 설치된 투과형 액정표시장치에 관한 것이다. 또한, 본 발명은 그 액정표시장치의 제조방법에 관한 것으로, 특히 휴대용 전자기기에 설치된 투과형 액정표시장치의 제조방법에 관한 것이다. 더욱이, 본 발명은 이러한 액정표시장치를 사용한 전자기기에 관한 것이다.

## 배경기술

[0002] 휴대전화나 전자서적 등으로 대표되는 휴대용 전자기기에는, 화상을 표시하기 위한 플랫 패널 디스플레이 이외에, 메일의 송수신, 음성인식, 소형카메라에 의한 영상의 캡처 등의 여러 가지 기능이 요구되고 있는 한편, 소형화, 경량화에 대한 사용자의 요구도 여전히 강하다. 그 때문에, 회로 규모나 메모리 용량이 보다 큰 IC를, 휴대용 전자기기의 한정된 용적 내에 보다 많이 탑재할 필요성이 요구되고 있다.

[0003] IC를 수용하기 위한 공간을 확보하고, 게다가 휴대용 전자기기를 소형화, 경량화하기 위해서는, 어떻게 플랫 패널 디스플레이를 얇고, 가볍게 만들지가 중요한 포인트가 된다. 예를 들면 휴대용 전자기기에 비교적 많이 사용되고 있는 액정표시장치의 경우, 액정이 봉입된 패널에 사용되는 유리기판의 두께를 억제하거나, 광원이나 도광판 등을 불필요하게 할 수 있는 반사형 액정표시장치를 채택함으로써, 어느 정도 박형화 및 경량화를 도모할 수 있다.

[0004] 그러나, 패널의 기계적 강도를 고려하면 유리기판을 너무 얇게 할 수는 없다. 예를 들면 바륨 봉규산 유리, 알루미늄 봉규산 유리 등을 사용한 경우, 3인치 직사각형의 두께는 최대 1~2mm 정도, 중량은 10g정도가 한계이다. 또한, 외광을 이용하는 반사형 액정표시장치는, 어두운 부분에서의 화상 인식이 어려워, 장소를 고르지 않고서 사용할 수 있다고 하는 휴대용 전자기기의 장점을 충분히 살릴 수 없다.

## 발명의 내용

### 해결하려는 과제

[0005] 본 발명의 목적은, 경량화 또는 소형화를 저해하지 않고 휴대용 전자기기를 고기능화하는데 있다. 본 발명의 더욱 구체적인 목적은, 그 휴대용 전자기기에 설치된 액정표시장치를 기계적 강도가 손상되지 않고 고기능화하는데 있다.

## 과제의 해결 수단

[0006] 본 발명의 액정표시장치는, 광원으로서 발광 다이오드(LED: light-emitting diode), 전계발광소자 등의 발광소자를 사용한다. 그리고, 투광성을 갖는 수지로, 가요성을 갖는 플라스틱 기판 상에 설치한 이 발광소자를 덮는 것으로 표면을 평탄화하고, 이 평탄화된 수지 상에 액정셀 및 해당 액정셀을 구동하기 위한 반도체소자를 설치한다. 발광소자를 수지로 덮은 상태의 광원을, 고체상태 광원이라고 부른다.

[0007] 일반적으로, 플라스틱 기판은, 가요성을 갖는 만큼, 진동 및 충격에 대한 기계적 강도가 우수하여, 두께를 감소

하기 쉽다. 그러나, 플라스틱 기판과 수지는, 액정표시장치에 사용된 반도체소자의 제조공정에서의 열처리에 견딜 수 있는 만큼, 내열성이 우수하지 않은 경우가 많다. 이 때문에, 본 발명에서는, 이 열처리에 견딜 수 있는 정도의 내열성을 갖는 기판 상에서 반도체소자를 형성한 후, 고체상태 광원 상에, 이 반도체소자를 옮긴다.

[0008] 그리고, 본 발명의 액정표시장치에는, 발광소자에서 발생된 광을 액정셀 방향으로 반사시키기 위한 수단이 설치되어 있다. 구체적으로는, 기존의 반사판을 플라스틱 기판에 부착하거나, 플라스틱 기판의 표면에 증착법 등으로 금속막(이하, 반사막)을 형성하여, 광을 반사시킬 수 있다. 더구나, 발광소자를 덮고 있는 수지와, 반도체소자 및 액정셀 사이에 편광판을 설치한다.

[0009] 이후, 본 발명에 따른 제1의 액정표시장치의 제조방법을 구체적으로 설명하겠다.

[0010] 반도체소자의 제조공정에서의 열처리에 견딜 수 있도록 내열성을 갖는 제1 기판을 준비한다. 그리고, 이 제1 기판 상에 금속막을 형성하고, 이 금속막의 표면을 산화함으로써 수 nm의 극히 얇은 금속산화막을 형성한다. 다음에, 이 금속산화막 상에 절연막, 반도체막을 순차로 적층하도록 형성한다. 절연막은 단층 또는 복수의 막을 적층한 것이어도 된다. 예를 들면, 질화실리콘, 질화산화실리콘, 산화실리콘 등을 사용할 수 있다. 그리고, 이 반도체막을 사용하여, 액정표시장치에 사용되는 반도체소자를 제조한다.

[0011] 반도체소자를 형성한 후 액정셀을 완성시키기 전에, 이 반도체소자를 덮도록 제2 기판을 접착하여, 제1 기판과 제2 기판의 사이에 반도체소자가 끼워진 상태를 만든다. 액정셀은, 화소전극과, 대향전극과, 상기 화소전극과 대향전극 사이에 설치된 액정을 갖는다. 그리고, 위에 기재된 "액정셀을 완성시키기 전"이란, 반도체소자의 1개인 TFT에 전기적으로 접속된 액정셀의 화소전극과, 이 화소전극을 덮고 있는 배향막을 제조한 후, 대향전극이 형성된 대향기판을 접착하기 전에 해당한다.

[0012] 그리고, 제1 기판의 반도체소자가 형성되어 있는 측과는 반대측에, 제1 기판의 강성을 보강하기 위해 제3 기판을 접착한다. 제2 기판보다도 제1 기판의 강성이 높은 쪽이, 제1 기판을 박리할 때에, 반도체소자에 손상을 주기 어려워 쉽게 벗길 수 있다. 또한, 제3 기판은, 제1 기판을 반도체소자로부터 박리하는데, 제1 기판의 강성이 충분하면, 반드시 접착시킬 필요는 없다.

[0013] 다음에, 가열처리 등을 시행하는 것으로 금속산화막을 결정화하여, 금속산화막의 취성을 높이고, 제1 기판을 반도체소자로부터 박리하기 보다 쉽게 한다. 따라서, 제1 기판을 제3 기판과 함께 반도체소자로부터 박리한다. 또한, 제1 기판을 결정화하기 위한 가열처리는, 제3 기판 또는 제2 기판을 접착하기 전에 실행해도 된다. 이와는 달리, 반도체소자를 형성하는 공정에서 행해지는 열처리는, 이 금속산화막을 결정화하는 열처리로서 기능할 수 있다.

[0014] 그리고, 제1 기판은, 금속막과 금속산화막의 경계면과, 절연막과 금속산화막의 경계면과, 금속산화막 자체가 분리함으로써 제3 기판과 함께 반도체소자로부터 박리되어도 된다. 어쨌든, 반도체소자는 제2 기판에 부착하도록, 제1 기판이 박리된다.

[0015] 한편, 반도체소자를 접착하기 위해, 광원측 플라스틱 기판을 준비한다. 이하, 이 플라스틱 기판을, 후에 사용되는 대향전극측의 플라스틱 기판과 구별하기 위해, 소자기판이라고 부른다. 이 소자기판 상에는 발광소자를 배치하고, 이 발광소자를 덮어 수지를 도포한다. 그리고, 평탄화된 수지 상에 제1 편광판을 접착한다.

[0016] 다음에, 제1 기판이 박리됨으로써, 제2 기판측에 접착된 상태의 반도체소자를, 제1 편광판에 접착제 등으로 접착한다. 그리고, 제2 기판을 박리하여, 반도체소자가 소자기판에 고정된 상태로 된다.

[0017] 다음에, 액정표시장치를 위한 액정셀을 형성한다. 구체적으로는, 대향전극, 제2 편광판 등이 형성된 플라스틱 기판(이하, 대향기판이라고 부른다)을 별도로 준비하고, 이 대향기판을 접착하여 액정을 주입하여, 액정셀을 완성시킨다. 이때, 대향기판에는, 대향전극, 제2 편광판뿐만 아니라, 컬러필터, 배향막, 블랙매트릭스 등을 설치해 두어도 된다.

[0018] 이후, 본 발명에 따른 제2의 액정표시장치의 제조방법을 설명한다.

[0019] 반도체소자의 제조공정에서의 열처리에 견딜 수 있는 내열성을 갖는 제1 기판을 준비한다. 그리고, 이 제1 기판 상에 금속막을 형성하고, 이 금속막의 표면을 산화함으로써 수 nm의 극히 얇은 금속산화막을 형성한다. 다음에, 이 금속산화막 상에 절연막, 반도체막을 순차로 적층하도록 형성한다. 절연막은 단층이거나 복수의 막을 적층한 것이어도 된다. 예를 들면, 질화실리콘, 질화산화실리콘, 산화실리콘 등을 사용할 수 있다. 그리고, 이 반도체막을 사용하여, 액정표시장치에 사용된 반도체소자를 형성한다.

- [0020] 다음에, 액정표시장치를 위한 액정셀을 형성한다. 이러한 액정셀은, 화소전극, 대향전극 및 그 화소전극과 대향전극 사이에 설치된 액정을 구비한다. 구체적으로는, 대향전극, 제2 편광판 등이 형성된 플라스틱 기판(이하, 대향기판이라고 부른다)을 별도로 준비하고, 그 반도체소자 상에 접착하여 액정셀을 완성시킨다. 이때, 대향기판에는, 대향전극과 제2 편광판뿐만 아니라, 컬러필터, 배향막, 블랙매트릭스 등을 설치해 두어도 된다.

- [0021] 반도체소자 및 액정셀을 형성한 후, 그 반도체소자 및 액정셀을 덮도록 제2 기판을 접착한다. 이에 따라서, 제1 기판과 제2 기판 사이에 액정셀이 삽입된다.

- [0022] 그리고 제1 기판의 반도체소자 및 액정셀이 형성되어 있는 측과는 반대측에, 제1 기판의 강성을 보강하기 위해 제3 기판을 접착한다. 제2 기판보다도 제1 기판의 강성이 높은 쪽이, 제1 기판을 박리할 때에, 반도체소자 및 액정셀에 손상이 주어지기 어렵게 쉽게 박리할 수 있다. 또한, 제3 기판은, 후에 제1 기판을 반도체소자로부터 박리할 때에, 제1 기판의 강성이 충분하면, 반드시 접착시킬 필요는 없다.

- [0023] 다음에, 가열처리 등을 시행함으로써 금속산화막을 결정화하고, 금속산화막의 취성을 높여, 제1 기판을 반도체소자로부터 박리하기 쉽게 한다. 그리고 제1 기판을 제3 기판과 함께 반도체소자로부터 박리한다. 또한, 금속산화막을 결정화하기 위한 가열처리는, 제3 기판을 접착하기 전이어도 되고, 제2 기판을 접착하기 전이어도 된다. 이와는 달리, 반도체소자를 형성하는 공정에서 행해지는 열처리가, 이 금속산화막을 결정화하는 열처리의 기능을 할 수 있다.

- [0024] 그리고, 제1 기판은, 금속막과 금속산화막의 경계면과, 절연막과 금속산화막의 경계면과, 또는 금속산화막 자체가 분리함으로써 제3 기판과 함께 반도체소자 및 액정셀로부터 박리하여도 된다. 어쨌든, 반도체소자 및 액정셀은 제2 기판측에 접착하도록, 제1 기판을 박리한다.

- [0025] 반도체소자 및 액정셀을 접착하기 위해 광원측의 플라스틱 기판(소자기판)을 준비한다. 이 소자기판 상에는 발광소자를 배치하고, 그 발광소자를 덮도록 수지를 도포한다. 그리고 평탄화된 수지 상에 제1 편광판을 접착한다.

- [0026] 다음에, 제1 기판이 박리됨으로써, 제2 기판측에 부착된 반도체소자 및 액정셀을, 제1 편광판에 접착제 등으로 접착한다. 그리고, 제2 기판을 박리하여, 반도체소자 및 액정셀이 소자기판에 고정된 상태를 형성하여, 액정표시장치가 완성된다.

- [0027] 1개의 대형기판으로부터 복수의 액정표시장치를 형성하는 경우, 도중에 다이싱을 행하여, 액정표시장치를 서로 분리하도록 한다.

- [0028] 본 발명에서는, 액정표시장치의 두께를 0.6mm 이상 1.5mm 이하로 할 수 있다.

- [0029] 상술한 바와 같이, 소자기판과 대향기판이 가요성을 갖는 만큼, 유리기판과 비교하여 충격에 대한 기계적 강도가 우수하여, 그 액정표시장치의 두께를 쉽게 감소할 수 있다. 또한 소자기판과 대향기판이 가요성을 갖기 때문에, 액정표시장치의 형상의 자유도가 높아진다. 따라서 예를 들면, 일종의 원주형 병 상에 접착가능해지는 만곡된 형상으로 액정표시장치를 형성할 수 있다.

- [0030] 이때, 발광소자를 투광성을 갖는 수지로 덮음으로써, 이 발광소자로부터 발생된 광을 확산시켜, 액정표시장치의 화소부의 밝기를 균일하게 할 수 있다. 액정셀과, 발광소자를 덮고 있는 수지와의 사이에 확산판(dispersion plate)을 설치함으로써 보다 밝기를 균일하게 할 수 있다.

- [0031] 본 발명은, 상기 구성에 의해, 기계적 강도가 손상되지 않고 액정표시장치를 상당히 얇게 할 수 있고, 또한 경량화할 수 있다. 그리고 본 발명의 액정표시장치를 전자기기에 적용함으로써, IC에 사용하는 공간을 보다 넓게 확보할 수 있고, 전자기기의 경량화 또는 소형화를 저해하지 않고 고기능화를 실현할 수 있다. 특히 휴대용 전자기기의 경우, 경량화, 소형화함으로써 사용의 편리함이 상당히 좋아지기 때문에, 본 발명의 액정표시장치를 사용하는 것은 대단히 유용하다. 또한, 본 발명에서는 액정표시장치의 화소부의 사이즈를 크게 해도, 종래의 유리기판을 사용한 액정표시장치와 동일한 정도의 중량으로 할 수 있다.

- [0032] 본 발명의 상기 내용 및 다른 목적, 특징 및 이점을 첨부된 도면에 따라 다음과 같이 상세한 설명을 읽으면 명백해질 것이다.

## 발명의 효과

[0033]

본 발명은, 상기 구성에 의해, 기계적 강도가 손상되지 않고 액정표시장치를 매우 얇게 할 수 있고, 또한 경량화할 수 있다. 그리고 본 발명의 제조방법으로 형성된 액정표시장치를 전자기기에 사용함으로써, IC에 사용하는 공간을 보다 넓게 확보할 수 있다. 따라서 회로규모나 메모리용량이 보다 큰 IC를 보다 많이 탑재할 수 있어, 전자기기의 경량화 또는 소형화를 저해하지 않고 고기능화를 실현할 수 있다. 특히 휴대용 전자기기의 경우, 경량화, 소형화함으로써 사용의 편리함이 매우 좋아지기 때문에, 본 발명의 액정표시장치를 사용하는 것은 매우 유용하다. 또한, 본 발명에서는 액정표시장치의 화소부의 사이즈를 크게 하여, 종래의 소자기판을 사용한 액정표시장치와 동일한 정도의 중량으로 할 수 있다.

### 도면의 간단한 설명

[0034]

도 1은 본 발명의 액정표시장치의 단면도,

도 2는 본 발명의 액정표시장치의 단면도,

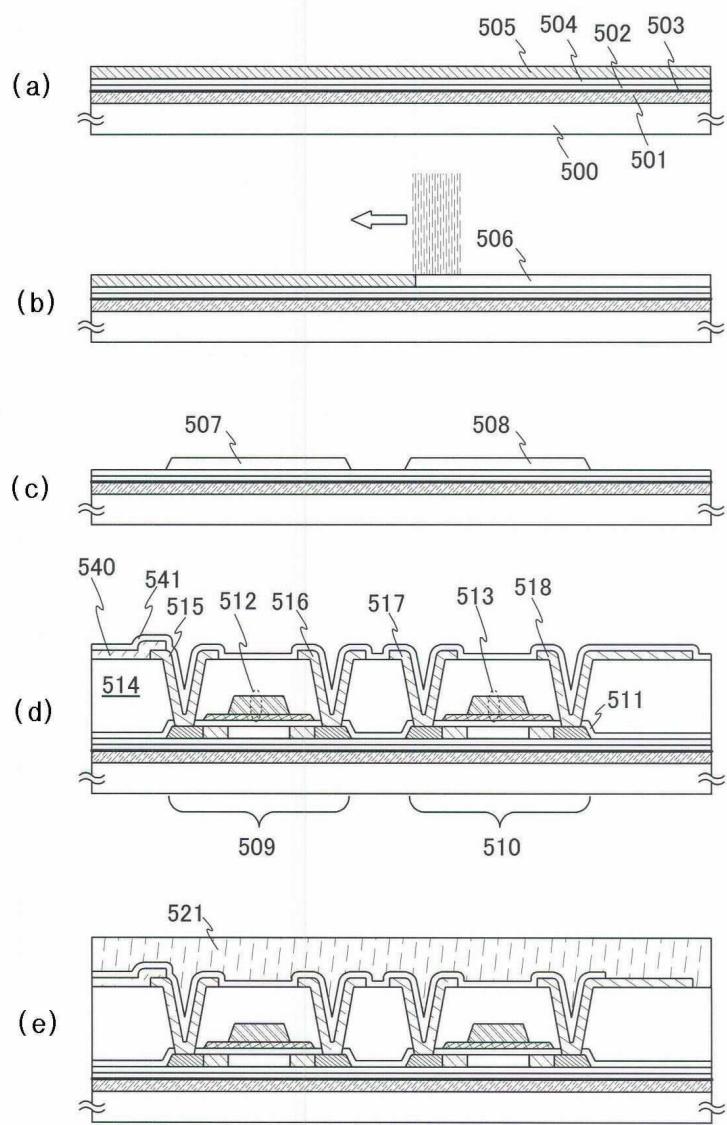

도 3은 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 4는 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 5는 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 6은 본 발명의 액정표시장치의 제조방법을 나타낸 도면,

도 7은 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 8은 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 9는 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 10은 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 11은 본 발명의 액정표시장치의 제조방법을 나타낸 설명도,

도 12는 박막회로 또는 LED 구동용 박막회로의 단면도,

도 13은 본 발명의 액정표시장치를 사용한 전자카드의 단면도,

도 14는 대형 소자기판의 사시도,

도 15는 FPC를 사용한 LED와, 그 LED를 소자기판에 접착한 모양을 나타낸 도면,

도 16은 소자기판의 구조를 나타낸 도면,

도 17은 센서 전자카드의 사시도 및 단면도,

도 18은 본 발명의 액정표시장치를 사용한 전자기기의 도면,

도 19는 박리 전의 금속산화막의 TEM 화상의 단면,

도 20은 박리 후의 절연막의 TEM 화상의 단면,

도 21은 본 발명의 액정표시장치의 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0035]

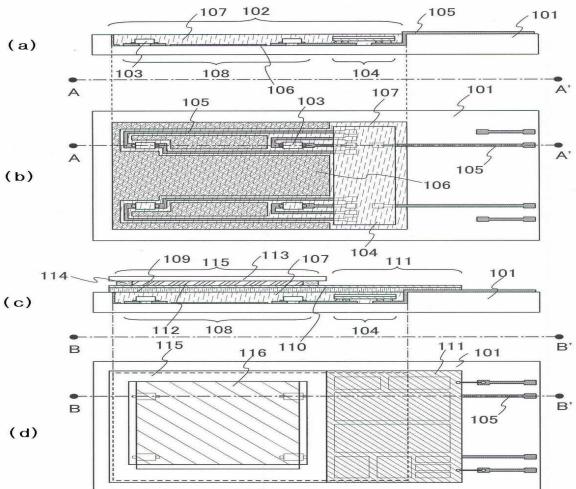

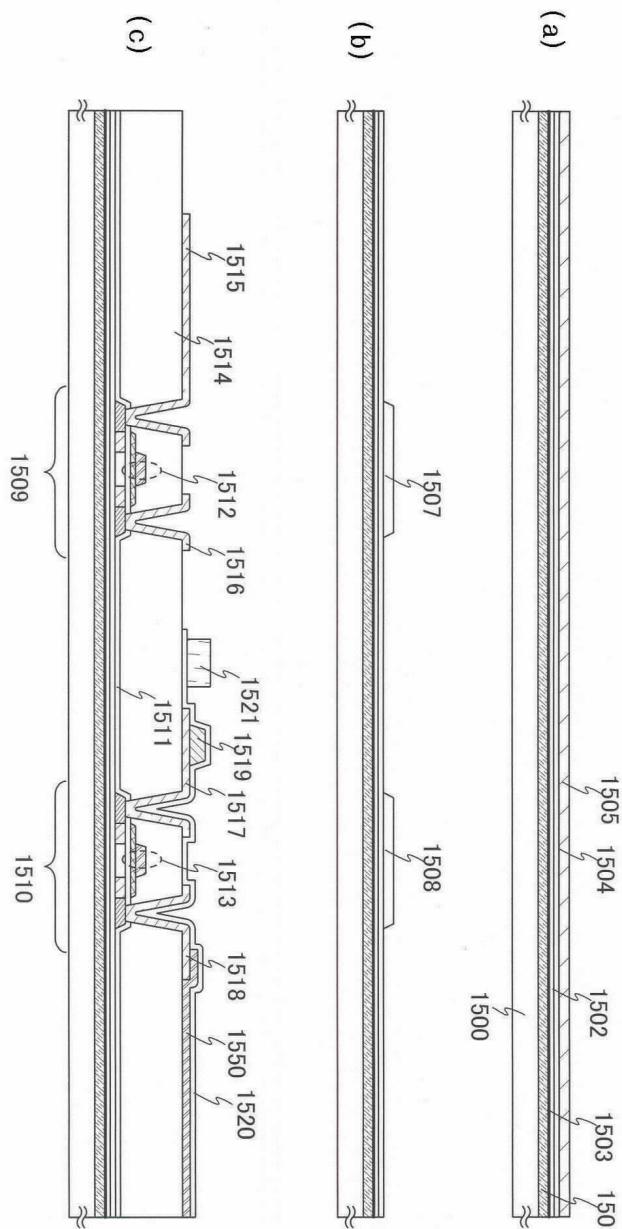

도 1a 내지 도 1d를 참조하여, 본 발명의 액정표시장치의 구성에 관해서 설명한다. 도 1a는 반도체소자를 접착하기 전의 소자기판(101)의 단면도를 나타낸다. 또한, 도 1b는, 도 1a에 나타낸 소자기판의 평면도에 해당하고, 도 1b의 A-A'에서의 단면도가 도 1a에 해당한다.

[0036]

도 1a 및 도 1b에 나타낸 소자기판(101)은, 오목부(102)를 갖고 있고, 이 오목부(102) 내에 LED(103)가 1개 또는 복수개 설치되어 있다. 오목부(102)는 공지의 방법을 사용하여 형성할 수 있으며, 예를 들면 금형을 사용하여 성형할 수 있다. LED(103)의 구동은, LED(103)의 구동용의 박막회로(이하, LED 구동용 박막회로라고 부른다)(104)에 의해 제어된다. LED 구동용 박막회로(104)는 반드시 오목부(102) 내에 설치하지 않아도 되며, 오목부(102) 이외의 부분에 형성해도 된다. LED 구동용 박막회로(104)의 형성의 방식에 관해서는, 후술한다.

- [0037] 도면부호 105는 소자기판(101) 상에 형성된 배선으로, LED(103) 와 LED 구동용 박막회로(104)를 전기적으로 접속하는 것 이외에, LED 구동용 박막회로(104)나, 후에 접착되는 반도체소자와, 액정표시장치의 외부와의 전기적인 접속을 행하기 위해 사용된다. 배선(105)은, 도금법 등 공지의 방법을 사용하여 소자기판(101) 상에 형성할 수 있다.

- [0038] 또한, 도면부호 106은 반사막으로, 증착법 등을 사용하여 오목부(102) 내에 금속을 증착함으로써 형성된다. 반사막(106)은, 배선(105) 또는 LED(103)와 쇼트하지 않도록, 전기적으로 분리하도록 형성한다. 이때, 본 실시예에서는, LED(103)의 광을 액정셀 방향으로 반사시키기 위한 수단으로서, 증착법에 의해 형성한 반사막을 사용하였지만, 별도로 형성된 반사판을 소자기판(101)에 접착하도록 해도 된다. 이 경우, 반사판은, LED(103)의 광을 액정셀측으로 반사시킬 수 있도록 하는 위치에, 접착시키는 것이 바람직하다. 예를 들면, LED(103)에 대향하고 오목부(102)가 설치되지 않은 면에 설치할 수 있다.

- [0039] 또한, LED(103)은 수지(107)로 덮인다. 본 실시예에서는, 오목부(102) 내에 수지(107)가 충전되어 있다. LED 구동용 박막회로(104)가 오목부(102) 내에 형성되어 있는 경우는, 수지(107)로 LED 구동용 박막회로(104)를 덮도록 한다. 수지(107)로서, 예를 들면 아크릴 수지, 에폭시 수지, 우레탄 수지, 폴리카보네이트 수지, 또는 비닐 수지 등의 공지의 수지를 사용할 수 있다. 수지(107)에, 이 수지와는 굴절률이 다른 투광성 입자를 분산시켜도 된다. 예를 들면, 구형 입자는, 폴리메틸메타크릴레이트 수지에 분산될 수 있다. 수지는, 반도체소자의 접착 공정에 따라 적절히 선택하는 것이 바람직하다.

- [0040] 도 1a 및 도 1b에서, LED(103)와 반사막(106)이 설치되어, 수지(107)로 덮인 영역이 광원부(108)에 해당한다.

- [0041] 도 1c는, 반도체소자를 접착하여, 액정셀을 완성한 본 발명의 액정표시장치의 단면도를 나타낸다. 도 1d는, 도 1c에 나타낸 상태의 액정표시장치의 평면도에 해당하고, 도 1d의 B-B'에서의 단면도가 도 1c에 해당한다.

- [0042] 반도체소자(110)는, 접착제(109)에 의해 수지(107) 상에 접착된다. 이때, 도 1c에서는 도시하지 않았지만, 수지(107)와 접착제(109) 사이에는, 제1 편광판이 설치되어 있다. 또한, 본 실시예에서는, 도 1c 및 도 1d에 나타낸 바와 같이, 반도체소자(110)는, 액정표시장치의 화소부에 사용될 뿐만 아니라, 액정표시장치의 구동이나 신호처리를 행하기 위한 박막회로(111)에 사용된다.

- [0043] 도면부호 113은 대향기판으로, 밀봉재(114)에 의해 액정(112)이 봉입되어 있다. 이 대향기판(113)에 의해 액정이 봉입된 영역이 패널(115)에 해당한다. 패널(115)에 설치된 화소부(116)에는, 광원부(108)로부터의 광이 조사된다. 또한, 박막회로(111)는, 와이어 본딩법이나, 플립칩법 등을 사용하여, 배선(105)과 전기적으로 접속된다.

- [0044] 이때, 본 실시예에서는, 배선(105)을 통해 액정표시장치에 신호 또는 전원전압의 공급을 행할 수 있지만, 본 발명은 이것에 한정되지 않고, 예를 들면, 발광소자나 광센서 등을 사용하여 광에 의해 신호나 전원전압의 공급을 행하여도 되고, 안테나코일을 사용하여 전자유도에 의해 신호나 전원전압의 공급을 행해도 된다.

- [0045] 플라스틱 기판으로서는, 극성기를 갖는 노르보넨수지를 함유한 JSR제조 ARTON®를 사용할 수 있다. 또한, 폴리에틸렌테레프탈레이트(PET), 폴리에텔술폰(PES), 폴리에틸렌나프타레이트(PEN), 폴리카보네이트(PC), 나일론, 폴리에테르 에테르 케톤(PEEK), 폴리술폰(PSF), 폴리에테르아미드(PEI), 폴리아릴레이트(PAR), 폴리부틸렌테레프탈레이트(PBT) 또는 폴리아미드 등의 플라스틱기판을 사용할 수 있다.

- [0046] 이때, 본 실시예에서는 소자기판에 오목부를 설치하고, 이 오목부에 LED를 설치한 예에 대하여 설명하였지만, 본 발명은 반드시 이 형태에 한정되지 않는다. 오목부를 설치하고 있지 않은 평탄한 플라스틱 기판을, 소자기판으로서 사용해도 된다.

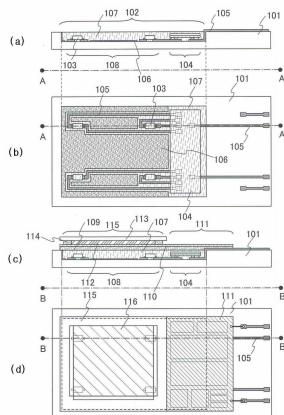

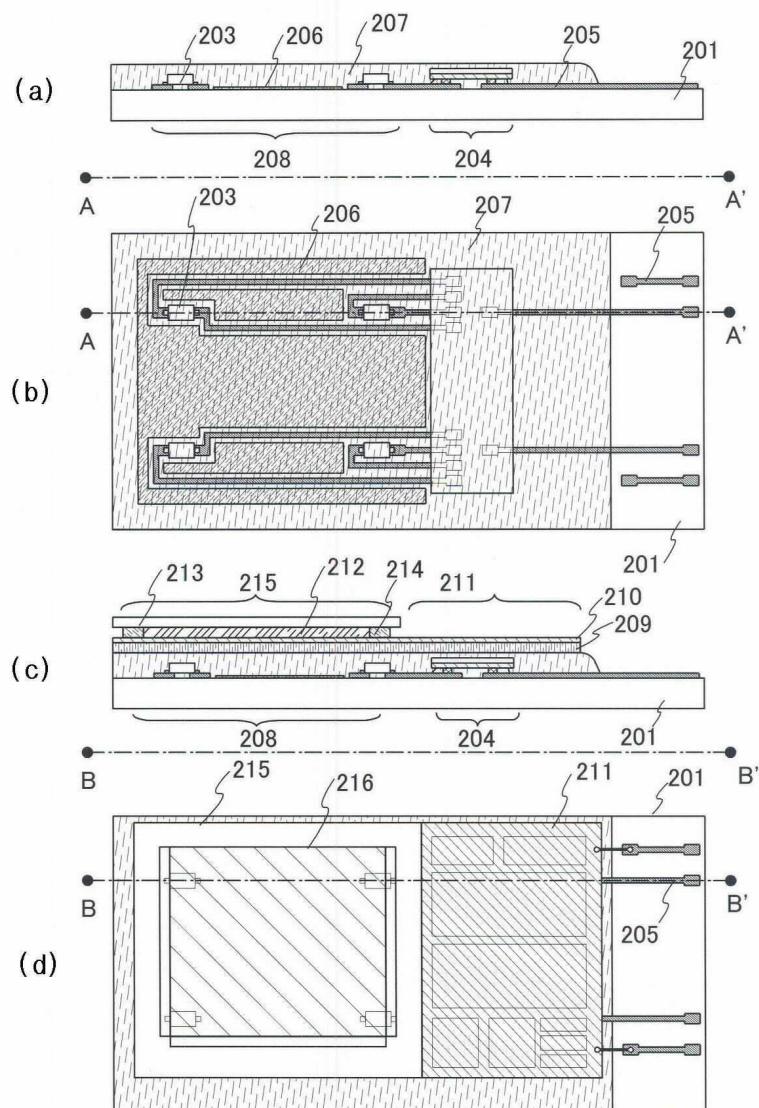

- [0047] 도 2a 내지 도 2d를 참조하여, 평탄한 플라스틱 기판을 소자기판으로서 사용한, 액정표시장치의 구성에 대하여 설명한다. 도 2a는 반도체소자를 접착하기 전의 소자기판(201)의 단면도를 나타낸다. 소자기판(201)에는 오목부가 설치되어 있지 않고, 평탄하다. 또한 도 2b는 도 2a에 나타낸 소자기판(201)의 평면도에 해당하고, 도 2b의 A-A'에서의 단면도가 도 2a에 해당한다.

- [0048] 도 2a 및 도 2b에 나타낸 소자기판(201) 상에는, LED(203)가 1개 또는 복수개 설치되어 있다. 도면부호 204는 LED 구동용 박막회로로, 배선(205)에 의해, LED(203)와 LED 구동용 박막회로(204)가 전기적으로 접속되어 있다. 또한 배선(205)은, LED 구동용 박막회로(204) 또는 후에 형성되는 반도체소자를 액정표시장치의 외부에 전기적으로 접속하기 위해 사용된다. 또한, 반사막(206)은, 배선(205)과 LED(203)와 쇼트하지 않도록 전기적으로 분리되게 형성되어 있다. 이때, 증착법에 의해 형성한 반사막이 아니며, 별도로 형성된 반사막을 사용할 수 있다.

- [0049] 또한, LED(203)는 수지(207)로 덮어져 있다. 본 실시예에서는, 감광성의 수지를 도포한 후, 부분적으로 노광하고, 배선(205)의 일부가 노출하도록, 수지(207)를 막형성한다. LED 구동용 박막회로(204)도 수지(207)에 의해 덮어져 있어도 된다. 도 2a 및 도 2b에서, LED(203)와 반사막(206)이 설치되고, 수지(207)로 덮인 영역이 광원부(208)에 해당한다.

- [0050] 도 2c는 반도체소자를 접착하여, 액정셀을 완성한 본 발명의 액정표시장치의 단면도를 나타낸다. 도 2d는, 도 2c에 나타낸 상태의 액정표시장치의 평면도에 해당하고, 도 2d의 B-B'에서의 단면도가 도 2c에 해당한다.

- [0051] 반도체소자(210)는 접착제(209)에 의해 수지(207) 상에 접착된다. 이때 도 2c에서는 도시하지 않았지만, 수지(207)와 접착제(209) 사이에는, 제1 편광판이 설치된다. 또한, 도면번호 211은, 반도체소자(210)를 사용하여 형성된 박막회로에 해당한다.

- [0052] 도면번호 213은 대향기판으로, 밀봉재(214)에 의해 액정(212)이 봉입되어 있다. 이 대향기판(213)에 의해 액정이 봉입된 영역이 패널(215)에 해당한다. 패널(215)에 설치된 화소부(216)에는, 광원부(208)로부터의 광이 조사된다. 또한 박막회로(211)는, 와이어 본딩법이나, 플립칩법 등을 사용하여, 배선(205)과 전기적으로 접속되어 있다.

- [0053] 소자기판에 오목부를 설치함으로써, 오목부에 수지를 적하하는 것만으로, 용이하게 배선을 노출한 상태로 수지로 LED를 덮을 수 있고, 또한 오목부 내에 반사막을 형성함으로써, LED로부터 발생하는 광을 효율적으로 화소부에 조사할 수 있다. 한편 오목부를 설치하지 않은 경우는, 오목부를 설치한 경우에 비해, 소자기판의 강도를 보다 높일 수 있다.

- [0054] 다음에, 박막회로와 액정표시장치에 사용된 반도체소자의 구체적인 제조방법 및 이 반도체소자의 소자기판에의 접착방법에 대하여 설명한다. 이때 본 실시예에서는, 반도체소자로서 2개의 TFT를 예로 들어 설명하지만, 박막회로와 액정표시장치에 포함되는 반도체소자는 이것에 한정되지 않고, 모든 회로소자를 사용할 수 있다. 예를 들면, TFT 외에, 기억소자, 다이오드, 광전변환소자, 저항소자, 코일, 용량소자, 인덕터 등을 대표적으로 들 수 있다.

- [0055] 도 3a에 나타낸 바와 같이, 스퍼터링법을 사용하여 제1 기판(500) 상에 금속막(501)을 형성한다. 여기서는 금속막(501)에 텅스텐을 사용하고, 막두께를 10nm~200nm, 바람직하게는 50nm~75nm로 한다. 이때 본 실시예에서는 제1 기판(500) 상에 직접 금속막(501)을 형성하지만, 예를 들면 산화실리콘, 질화실리콘, 질화산화실리콘 등의 절연막으로 제1 기판(500)을 덮은 후, 금속막(501)을 형성하도록 해도 된다.

- [0056] 그리고 금속막(501) 형성 후, 대기에 노출하지 않고 산화물막(502)을 적층하도록 형성한다. 여기서는 산화물막(502)으로서 산화실리콘막을 150nm~300nm가 되도록 형성한다. 이때, 스퍼터링법을 사용하여 막형성하는 경우, 제1 기판(500)의 에지 상에도 막이 형성된다. 그 때문에, 후의 공정에서의 박리시에, 산화물막(502)이 제1 기판(500)에 남는 것을 막기 위해, 에지에 막형성된 금속막(501)과 산화물막(502)을 O<sub>2</sub> 애싱 등으로 선택적으로 제거하거나, 제1 기판(500)의 에지를 다이싱 등으로 커트하는 것이 바람직하다.

- [0057] 또한, 산화물막(502) 형성시에, 스퍼터링의 전단층으로서 타깃과 기판의 사이를 셔터로 차단하여 플라즈마를 발생시키는 프리스퍼터(pre-sputter)를 행한다. 프리스퍼터링은 Ar을 10sccm, O<sub>2</sub>를 각각 30sccm의 유량으로 하고, 기판온도를 270°C, 막형성파워를 3kW의 평행상태로 유지하여 행한다. 프리스퍼터링에 의해, 금속막(501)과 산화물막(502) 사이에 매우 얇은 수nm(여기서는 3nm) 정도의 금속산화막(503)이 형성된다. 금속산화막(503)은, 금속막(501)의 표면이 산화함으로써 형성된다. 따라서, 금속산화막(503)은 산화텅스텐으로 형성된다.

- [0058] 이때 본 실시예에서는, 프리스퍼터링에 의해 금속산화막(503)을 형성하고 있지만, 본 발명은 이것에 한정되지 않는다. 예를 들면 산소, 또는 산소에 Ar 등의 불활성가스를 첨가하고, 플라즈마에 의해 의도적으로 금속막(501)의 표면을 산화하여, 금속산화막(503)을 형성하도록 해도 된다.

- [0059] 다음에 산화물막(502)을 형성한 후, 플라즈마 화학기상증착(PCVD)법을 사용하여 하지막(504)을 형성한다. 여기서는 하지막(504)으로서, 산화질화실리콘막을 막두께 100nm 정도가 되도록 막형성한다. 그리고 하지막(504)을 형성한 후, 대기에 노출하지 않고 반도체막(505)을 형성한다. 반도체막(505)의 막두께는 25~100nm, 바람직하게는 30~60nm로 한다. 이때 반도체막(505)은, 비정질 반도체이어도 되고, 다결정 반도체이어도 된다. 또한 반도체는 실리콘만이 아니라 실리콘 게르마늄도 사용할 수 있다. 실리콘 게르마늄을 사용하는 경우, 게르마늄의 농도는 0.01~4.5atomic% 정도인 것이 바람직하다.

- [0060] 다음에 도 3b에 나타낸 바와 같이, 반도체막(505)을 공지의 기술에 의해 결정화한다. 공지의 결정화방법으로서는, 전열로를 사용한 열결정화방법, 레이저광을 사용한 레이저 결정화법, 적외광을 사용한 램프어닐링 결정화법이 있다. 혹은 특개평 7-130652호 공보에서 개시된 기술에 따라, 촉매원소를 사용하는 결정화법을 사용할 수 있다.

- [0061] 또한, 이때 미리 다결정 반도체막인 반도체막(505)을, 스퍼터링법, PCVD법 또는 열 CVD법 등으로 형성하도록 해도 된다.

- [0062] 본 실시예에서는 레이저 결정화에 의해 반도체막(505)을 결정화한다. 연속발진이 가능한 고체레이저를 사용하여, 기본파의 제2 고조파~제4 고조파의 레이저광을 조사함으로써, 대입경의 결정을 얻을 수 있다. 예를 들면, 대표적으로는, Nd:YVO<sub>4</sub> 레이저(기본파 1064nm)의 제2 고조파(532nm) 또는 제3 고조파(355nm)를 사용하는 것이 바람직하다. 구체적으로는, 연속발진의 YVO<sub>4</sub> 레이저로부터 사출된 레이저광을 비선형 광학소자에 의해 고조파로 변환하고, 출력 10W의 레이저광을 얻는다. 또한 비선형 광학소자를 사용하여, 고조파를 사출하는 방법도 있다. 그리고, 바람직하게는 광학계에 의해 조사면에서 구형형상 또는 타원형상의 레이저광으로 성형하여, 반도체막(502)에 조사한다. 이때의 에너지밀도는 0.01~100MW/cm<sup>2</sup> 정도(바람직하게는 0.1~10MW/cm<sup>2</sup>)가 필요하다. 그리고, 주사속도를 10~2000cm/s 정도로 하여 조사한다.

- [0063] 또한, 레이저 결정화는, 연속발진의 기본파의 레이저광과 연속발진의 고조파의 레이저광을 조사하도록 해도 되고, 연속발진의 기본파의 레이저광과 펄스발진의 고조파의 레이저광을 조사하도록 해도 된다.

- [0064] 이때, 희가스나 질소 등의 불활성가스 분위기 중에서 레이저광을 조사하도록 해도 된다. 이에 따라, 레이저광 조사에 의한 반도체표면의 거칠기를 억제할 수 있어, 계면준위 정밀도의 변동에 의해 생기는 임계값의 변동을 억제할 수 있다.

- [0065] 전술한 반도체막 505에의 레이저광의 조사에 의해, 결정성이 보다 높아진 반도체막 506이 형성된다. 다음에, 도 3c에 나타낸 바와 같이 반도체막(506)을 패터닝하고, 섬 형상의 반도체막(507, 508)을 형성하여, 이 섬 형상의 반도체막(507, 508)을 사용하여 TFT로 대표되는 각종의 반도체소자를 형성한다. 이때 본 실시예에서는, 하지막(504)과 섬 형상의 반도체막(507, 508)이 접하고 있지만, 반도체소자에 의해서는, 하지막(504)과 섬 형상의 반도체막(507, 508)과의 사이에, 전극이나 절연막 등이 형성되어도 된다. 예를 들면 반도체소자의 1개인 보텀케이트형 TFT인 경우, 하지막(504)과 섬 형상의 반도체막(507, 508)과의 사이에, 게이트전극과 게이트 절연막이 형성된다.

- [0066] 본 실시예에서는, 섬 형상의 반도체막(507, 508)을 사용하여 톱케이트형 TFT(509, 510)를 형성한다(도 3d). 구체적으로는, 섬 형상의 반도체막(507, 508)을 덮도록 게이트 절연막(511)을 형성한다. 그리고, 게이트 절연막(511) 상에 도전막을 형성하고 패터닝함으로써, 게이트전극(512, 513)을 형성한다. 그리고, 게이트전극(512, 513)이나, 혹은 레지스트를 막형성하고, 패터닝한 것을 마스크로서 사용하여, 섬 형상의 반도체막(507, 508)에 N형을 부여하는 불순물을 첨가하고, 소스영역, 드레인영역, 또한 LDD(Lightly Doped Drain) 영역 등을 형성한다. 이때 여기서는 TFT(509, 510)를 n형으로 하지만, p형 TFT인 경우는, p형을 부여하는 불순물을 첨가한다.

- [0067] 상기 일련의 공정에 의해 TFT(509, 510)를 형성할 수 있다. 이때 TFT의 제조방법은, 전술한 공정에 한정되지 않는다.

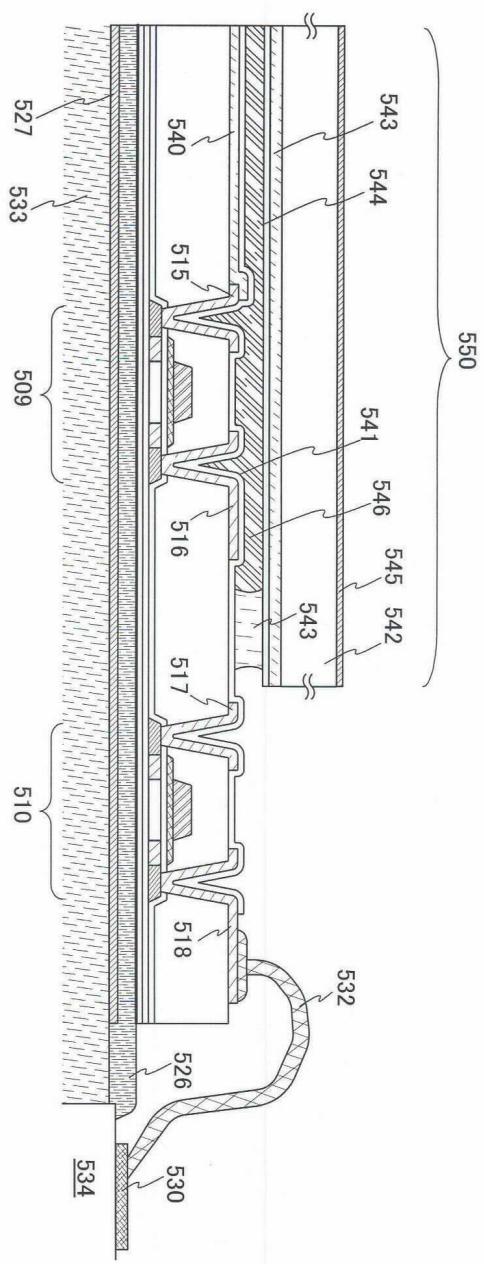

- [0068] 다음에 TFT(509, 510)를 덮어 제1 층간절연막(514)을 형성한다. 그리고, 게이트 절연막(511) 및 제1 층간절연막(514)에 콘택홀을 형성한 후, 콘택홀을 통해 TFT(509, 510)와 접속하는 단자(515~518)를, 제1 층간절연막(514)에 접하도록 형성한다.

- [0069] 그리고 단자(515)에 접하도록, ITO 등의 투명도전막을 사용하고, 액정셀의 화소전극(540)을 형성한다. 그리고, 화소전극(540)을 덮도록 배향막(541)을 형성하고, 배향막(541)에 러빙처리를 시행한다. 이때, 배선(518)의 일부는 배향막(541)으로 덮지 않도록, 예칭 등으로 노출시킨다.

- [0070] 다음에, 배향막(541) 상에 보호층(521)을 형성한다. 보호층(521)은, 후에 제2 기판을 접착하거나 박리하거나 할 때에, TFT(509, 510), 배향막(541) 및 단자(515~518)의 표면을 보호하는 기능을 갖고 있으며, 제2 기판의 박리 후에 제거하는 것이 가능한 재료를 사용한다. 예를 들면, 물 또는 알코올류에 가용인 에폭시계, 아크릴레이트계, 실리콘계의 수지를 전체면에 도포하여, 소성함으로써 보호층(521)을 형성할 수 있다.

- [0071] 본 실시예에서는 스피코트로 수용성수지(TOAGOSEI사 제조:VL-WSHL10)를 막두께  $30\mu\text{m}$ 가 되도록 도포하고, 가경화시키기 위해 2분간의 노광을 행했다고 하면, UV광을 이면으로부터 2.5분, 표면으로부터 10분, 합계 12.5분의 노광을 행하여 본경화시켜, 보호층(521)을 형성한다(도 3e).

- [0072] 본 실시예에서는 배향막(541)을 형성한 후 보호층(521)을 형성한 예를 설명하였지만, 그 배향막(541)은 후의 공정에서 보호층(521)을 제거한 후 형성되어도 된다. 그러나, 복수의 유기수지를 적층하는 경우, 유기수지끼리는 사용하고 있는 용매에 따라 도포 또는 소성시에 일부 용해하거나, 그 밀도가 지나치게 높아질 우려가 있다. 따라서, 배향막(541)을 형성한 후 보호층(521)을 형성하는 경우에, 각각이 모두 같은 용매에 가용인 유기수지를 사용하는 경우, 후의 공정에서 보호층(521)의 제거가 스무스하게 행해지는 바와 같이, 제1 충간절연막(514)을 덮도록, 게다가 제1 충간절연막(514)과 단자(515~518)와의 사이에 끼워지도록, 무기절연막( $\text{SiN}_x$ 막,  $\text{SiN}_x\text{O}_y$ 막,  $\text{AlN}_x$ 막 또는  $\text{AlN}_x\text{O}_y$ 막)을 형성해 두는 것이 바람직하다.

- [0073] 다음에, 후의 박리를 행하기 쉽게 하기 위해, 금속산화막(503)을 결정화시킨다. 결정화에 의해, 금속산화막(503)이 입계에서 깨어지기 쉬워져, 취성을 높일 수 있다. 본 실시예에서는,  $420^\circ\text{C} \sim 550^\circ\text{C}$ , 0.5~5시간 정도 가열처리를 행하고, 결정화를 행하였다.

- [0074] 다음에, 금속산화막(503)과 산화물막(502)의 사이의 밀착성, 또는 금속산화막(503)과 금속막(501)의 사이의 밀착성을 부분적으로 저하시켜, 박리개시의 계기가 되는 부분을 형성하는 처리를 행한다. 구체적으로는, 박리하고자 하는 영역의 주연을 따라 외부에서 국소적으로 압력을 가하여 금속산화막(503)의 층 내 또는 계면 근방의 일부에 손상을 준다. 본 실시예에서는, 다이아몬드 펜 등의 딱딱한 바늘을 금속산화막(503)의 에지 근방에 수직으로 부착하여, 그대로 하중을 건 상태에서 금속산화막(503)을 따라 움직인다. 바람직하게는, 스크라이버 장치를 사용하여, 눌러 들어간 양을  $0.1\text{mm} \sim 2\text{mm}$ 로 하고, 압력을 가하여 움직이게 하면 된다. 이와 같이, 박리를 행하기 전에, 박리가 시작되는 계기가 되는, 밀착성이 저하한 부분을 형성함으로써, 후의 박리공정에서의 불량을 감소시킬 수 있어, 수율 향상으로 이어진다.

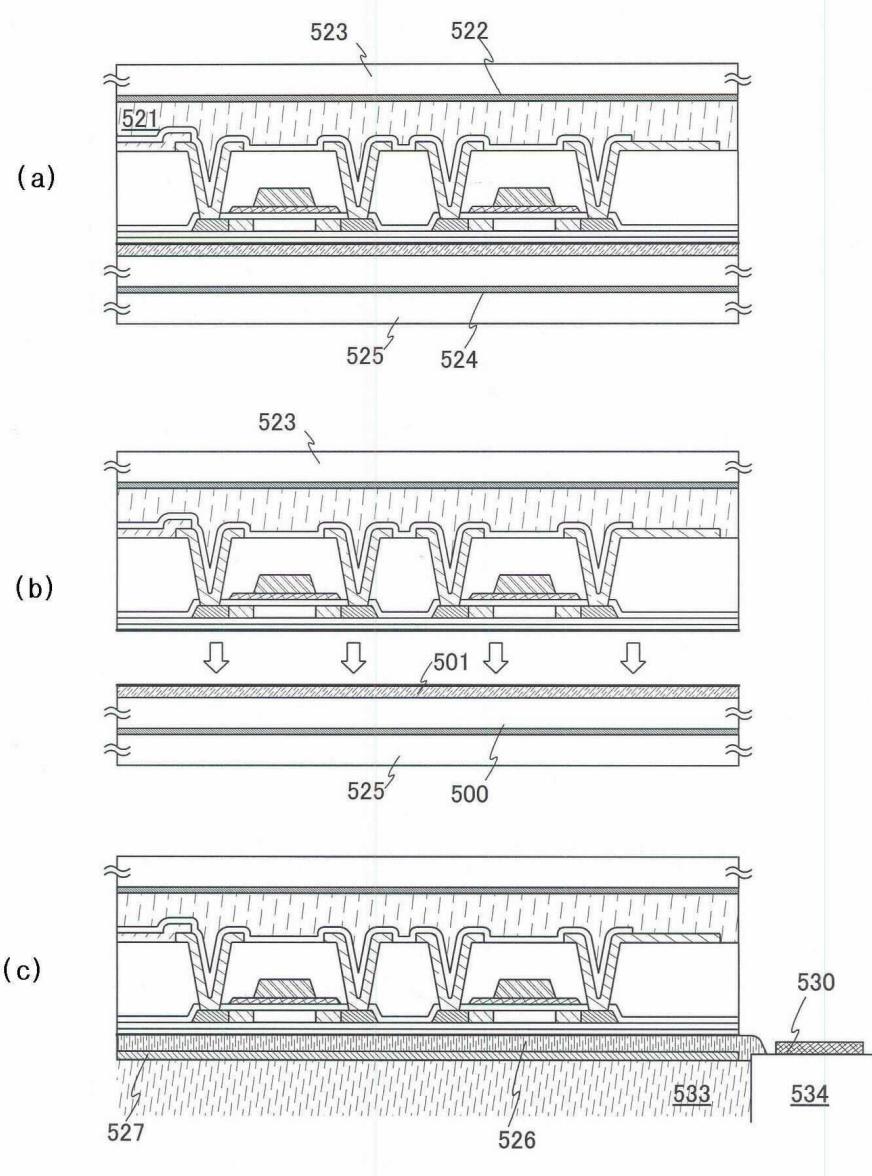

- [0075] 이어서, 양면 테이프(522)를 사용하여, 보호층(521)에 제2 기판(523)을 접착하고, 또한 양면 테이프(524)를 사용하여, 제1 기판(500)에 제3 기판(525)을 접착한다(도 4a). 이때 양면 테이프가 아니라 접착제를 사용해도 된다. 예를 들면 UV선에 의해 박리하는 접착제를 사용함으로써, 제2 기판박리시에 반도체소자의 부담을 경감시킬 수 있다.

- [0076] 제3 기판(525)은, 후의 박리공정으로부터 제1 기판(500)이 파손되는 것을 방지한다. 제2 기판(523) 및 제3 기판(525)으로서는, 제1 기판(500)보다도 강성이 높은 기판, 예를 들면 석영기판 또는 반도체기판을 사용하는 것이 바람직하다.

- [0077] 이어서, 금속막(501)과 산화물막(502)을 물리적수단으로 박리한다. 그 금속막(501)의 박리는, 이전 공정에서, 금속막(501) 또는 산화물막(502)에 대한 밀착성이 부분적으로 저하한 영역에서 시작한다.

- [0078] 금속막(501)과 금속산화막(503)의 사이에서 분리하는 부분과, 산화물막(502)과 금속산화막(503)의 사이에서 분리하는 부분과, 금속산화막(503) 자체가 쌍방으로 분리하는 부분이 생긴다. 그리고 제2 기판(523)측에 반도체소자(여기서는 TFT(509, 510))가, 제3 기판(525)측에 제1 기판(500) 및 금속막(501)이, 각각 접착된 상태로 분리한다. 박리는 비교적 작은 힘(예를 들면, 인간의 손, 노즐로부터 내뿜어지는 가스의 풍압, 초음파 등)으로 행할 수 있다. 박리 후의 상태를 도 4b에 나타낸다.

- [0079] 다음에 접착제(526)로, 수지(533) 상에 설치된 제1 편광판(527)과, 부분적으로 금속산화막(503)이 접착되어 있는 산화물층(502)을 접착한다(도 4c). 이 접착시에, 양면 테이프(522)에 의한 제2 기판(523)과 보호층(521) 사이의 밀착력보다도, 접착제(526)에 의한 산화물층(502)과 제1 편광판(527) 사이의 밀착력 쪽이 높아지도록, 접착제(526)의 재료를 선택하는 것이 중요하다.

- [0080] 이때, 금속산화막(503)이 산화물막(502)의 표면에 잔존하고 있으면, 제1 편광판(527)과의 밀착성이 나빠지는 경우가 있으므로, 완전하게 제거하고 나서 제1 편광판에 접착시켜, 밀착성을 높이도록 해도 된다.

- [0081] 또한, 반도체소자(509, 510)를 박막회로에 사용하는 경우, 반드시 반도체소자(509, 510)를 제1 편광판(527)과 겹치는 위치에 접착하지 않아도 된다.

- [0082] 접착제(526)로서는, 반응경화형 접착제, 열경화형 접착제, 자외선 경화형 접착제 등의 광경화형 접착제, 혼기형 접착제 등의 각종 경화형 접착제를 들 수 있다. 더욱 바람직하게는, 은, 니켈, 알루미늄, 질화알루미늄으로 이

루어지는 분말, 또는 충전재를 포함하게 하고 접착제(526)도 높은 열전도성을 구비하는 것이 바람직하다.

[0083] 또한, 도면부호 530은, 소자기판(534) 상에 형성된 배선으로, 배선(530)은, 예를 들면 구리 땜납, 금 또는 주석을 도금하여 형성된다.

[0084] 다음에 도 5a에 나타낸 바와 같이, 보호층(521)으로부터 양면 테이프(522)와 제2 기판(523)을 순서대로, 또는 동시에 박리한다. 이때, 접착제(526)로서 자외선 경화형 접착제를 사용하고, 양면 테이프(522)에 자외선에 의해 박리하는 테이프 또는 접착제를 사용함으로써, 자외선조사에 의해 양면 테이프(522)의 박리와 접착제(526)의 경화를 동시에 행할 수 있다.

[0085] 그리고 도 5b에 나타낸 바와 같이, 보호층(521)을 제거한다. 여기서는 보호층(521)에 수용성의 수지가 사용되고 있으므로, 물에 용해시켜 제거한다. 보호층(521)이 잔류되어 있으면 불량의 원인이 되는 경우는, 제거 후의 표면에 세정처리나 O<sub>2</sub> 플라즈마처리를 시행하여, 잔류하고 있는 보호층(521)의 일부를 제거하는 것이 바람직하다.

[0086] 이때 본 실시예에서는, 금속막(501)으로서 텅스텐을 사용하고 있지만, 본 발명에서 금속막은 이 재료에 한정되지 않는다. 그 표면에 금속산화막(503)이 형성되고, 이 금속산화막(503)을 결정화함으로써 기판을 박리할 수 있는 금속을 함유하는 재료이어도 된다. 예를 들면, TiN, WN, Mo 등을 사용할 수 있다. 또한 이들 합금을 금속막으로서 사용하는 경우, 그 조성비에 따라 결정화시의 가열처리의 최적 온도가 다르다. 따라서 조성비를 조정함으로써, 반도체소자의 제조공정에서 방해가 되지 않는 온도로 가열처리를 할 수 있어, 반도체소자의 프로세스의 선택범위가 제한되기 어렵다.

[0087] 다음에, 도 6에 나타낸 바와 같이 액정셀을 형성한다.

[0088] 보호층(521)을 형성한 후, 별도로 형성해 둔 대향기판(542)을, 밀봉재(543)를 사용하여 접착한다. 밀봉재에는 충전재가 혼입되어도 된다. 대향기판(542)은, 그 두께가 수백 μm 정도로, 투명도전막으로 이루어진 대향전극(543)과, 러빙처리가 시행된 배향막(544)이 형성되어 있다. 이때 이들에 부가하여, 컬러필터나, 디스크리네이션을 방지하기 위한 블랙 매트릭스(차폐막) 등이 형성되어도 된다. 또한, 제2 편광판(545)을, 대향기판(542)의 대향전극(543)이 형성되어 있는 면과는 반대의 면에, 접착시켜 놓는다.

[0089] 그리고 액정(546)을 주입하고 밀봉하여, 패널(550)을 완성한다. 이때, 액정의 주입은 디스펜서식이거나 딥(dip)식이어도 된다. 또한 셀 캡을 확보하기 위해, 스페이서를 핵소전극(540)과 대향전극(543) 사이에 설치해도 된다. 단자(518)와, 소자기판(534)에 설치된 배선(530)을, 와이어본딩법 등을 사용하여, 전기적으로 접속함으로써, 액정표시장치가 완성된다.

[0090] 다음에, 도 3 내지 도 6에 기재된 것과 다른 본 발명의 액정표시장치의 제조방법을 설명한다. 이때, 본 실시예에서는, 반도체소자로서 TFT를 예로 들어 나타내지만, 박막회로와 패널에 포함되는 반도체소자는 이것에 한정되지 않고, 모든 회로소자를 사용할 수 있다. 예를 들면, TFT 외에, 기억소자, 다이오드, 광전변환소자, 저항소자, 코일, 용량소자, 인덕터 등을 대표적으로 들 수 있다.

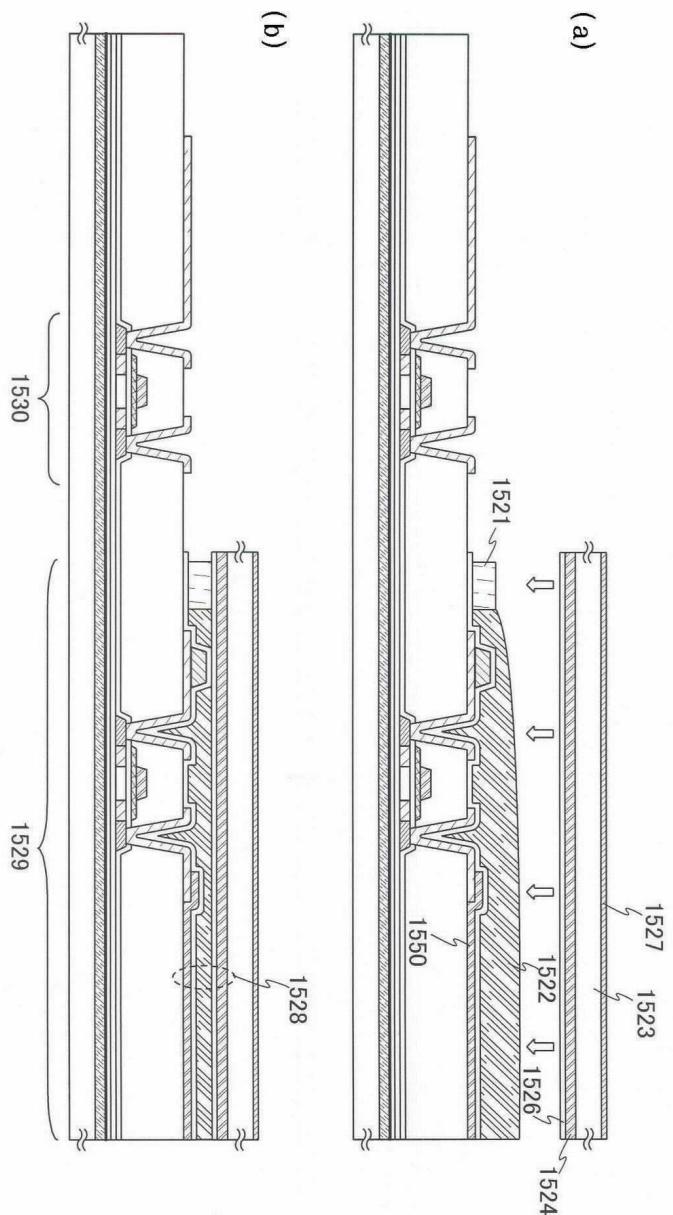

[0091] 도 7a에 나타낸 바와 같이, 스퍼터링법을 사용하여 제1 기판(1500) 상에 금속막(1501)을 형성한다. 여기서는 금속막(1501)에 텅스텐을 사용하고, 막두께를 10nm~200nm, 바람직하게는 50nm~75nm로 한다. 이때 본 실시예에서는 제1 기판(1500) 상에 직접 금속막(1501)을 막형성하지만, 예를 들면 산화실리콘, 질화실리콘 또는 질화산화실리콘 등의 절연막으로 제1 기판(1500)을 덮고 나서, 금속막(1501)을 막형성하도록 해도 된다.

[0092] 그리고 금속막(1501)의 막형성 후, 대기에 노출하지 않고 절연막을 구성하는 산화물막(1502)을, 적층하도록 막형성한다. 여기서는 산화물막(1502)으로서 산화실리콘막을 막두께 150nm~300nm가 되도록 막형성한다. 이때, 스퍼터링법을 사용하는 경우, 제1 기판(1500)의 에지에도 막형성이 시행된다. 그 때문에, 후의 공정에서의 박리시에, 산화물막(1502)이 제1 기판(1500) 측에 남아 버리는 것을 방지하기 위해, 그 금속막(1501)과 산화물막(1502)을 O<sub>2</sub> 애싱 등으로 선택적으로 제거하는 것이 바람직하다.

[0093] 또한 산화물막(1502) 형성시에, 스퍼터링의 전단층으로서 타깃과 기판의 사이를 셔터로 차단하여 플라즈마를 발생시키는 프리스퍼터링을 행한다. 프리스퍼터링은 Ar을 10sccm, O<sub>2</sub>를 각각 30sccm의 유량으로 하고, 제1 기판(1500)의 온도를 270°C, 막형성파워를 3kW의 평행상태로 유지하여 행한다. 프리스퍼터링에 의해, 금속막(1501)과 산화물막(1502)의 사이에 매우 얇은 수 nm(여기서는 3nm) 정도의 금속산화막(1503)이 형성된다. 금속산화막(1503)은, 금속막(1501)의 표면이 산화함으로써 형성된다. 따라서 본 실시예에서는, 금속산화막(1503)은 산화텅

스텐으로 형성된다.

- [0094] 이때 본 실시예에서는, 프리스퍼팅에 의해 금속산화막(1503)을 형성하고 있지만, 본 발명은 이것에 한정되지 않는다. 예를 들면 산소, 또는 산소에 Ar 등의 불활성가스를 첨가하고, 플라즈마에 의해 의도적으로 금속막(1501)의 표면을 산화하여, 금속산화막(1503)을 형성하도록 해도 된다.

- [0095] 다음에 산화물막(1502)을 형성한 후, PCVD법을 사용하여 절연막을 구성하는 하지막(1504)을 막형성한다. 여기서는 하지막(1504)으로서, 산화질화실리콘막을 막두께 100nm 정도가 되도록 막형성한다. 그리고 하지막(1504)을 형성한 후, 대기에 노출하지 않고 반도체막(1505)을 형성한다. 반도체막(1505)의 막두께는 25~100nm, 바람직하게는 30~60nm로 한다. 이때 반도체막(1505)은, 비정질 반도체막이어도 되며, 다결정 반도체막이어도 된다. 또한 반도체는 실리콘뿐만 아니라 실리콘 게르마늄도 사용할 수 있다. 실리콘 게르마늄을 사용하는 경우, 게르마늄의 농도는 0.01~4.5atomic% 정도인 것이 바람직하다.

- [0096] 다음에, 반도체막(1505)을 공지의 기술에 의해 결정화한다. 공지의 결정화방법으로서는, 전열로를 사용한 열결정화방법, 레이저광을 사용한 레이저 결정화법, 적외광을 사용한 램프어닐링 결정화법이 있다. 혹은 미심사된 특개평 7-130652호 공보에서 개시된 기술에 따라, 촉매원소를 사용하는 결정화법을 사용할 수 있다.

- [0097] 본 실시예에서는 레이저 결정화에 의해, 반도체막(1505)을 결정화한다. 레이저 결정화 전에, 반도체막의 레이저에 대한 내성을 높이기 위해, 500°C 1시간의 열어닐링을 이 반도체막에 대하여 행한다. 본 실시예에서는, 이 가열처리에 의해, 금속산화막(1503)의 취성이 높아지고, 후의 제1 기판의 박리가 행하기 쉬워진다. 결정화에 의해, 금속산화막(1503)이 입계에서 깨어지기 쉬워져, 취성을 높일 수 있다. 본 실시예인 경우, 금속산화막(1503)의 결정화는 420°C~550°C, 0.5~5시간 정도의 가열처리가 바람직하다.

- [0098] 그리고 연속발진이 가능한 고체레이저를 사용하여, 기본파의 제2 고조파~제4 고조파의 레이저광을 조사함으로써, 대입경의 결정을 얻을 수 있다. 예를 들면, 대표적으로는, Nd:YVO<sub>4</sub> 레이저(기본파 1064nm)의 제2 고조파(532nm)나 제3 고조파(355nm)를 사용하는 것이 바람직하다. 구체적으로는, 연속발진의 YVO<sub>4</sub> 레이저로부터 사출된 레이저광을 비선형 광학소자에 의해 고조파로 변환하고, 출력 10W의 레이저광을 얻는다. 또한 비선형 광학소자를 사용하여, 고조파를 사출하는 방법도 있다. 그리고, 바람직하게는 광학계에 의해 조사면에서 구형형상 또는 타원형상의 레이저광으로 성형하여, 반도체막(1505)에 조사한다. 이때의 에너지밀도는 0.01~100MW/cm<sup>2</sup> 정도(바람직하게는 0.1~10MW/cm<sup>2</sup>)가 필요하다. 그리고, 주사속도를 10~2000cm/s 정도로 하여 조사한다.

- [0099] 이때 레이저 결정화는, 연속발진의 기본파의 레이저광과 연속발진의 고조파의 레이저광을 조사하도록 해도 되며, 연속발진의 기본파의 레이저광과 펄스발진의 고조파의 레이저광을 조사하도록 해도 된다.

- [0100] 이때, 희가스나 질소 등의 불활성가스 분위기 중에서 레이저광을 조사하도록 해도 된다. 이에 따라, 레이저광조사에 의한 반도체 표면의 거칠함을 억제할 수 있어, 계면준위 정밀도의 변동에 의해 생기는 임계값의 변동을 억제할 수 있다.

- [0101] 전술한 반도체막(1505)에의 레이저광의 조사에 의해, 결정성이 보다 높아진다. 이때, 또 미리 다결정 반도체막인 반도체막(1505)을, 스퍼터링법, PCVD법, 열 CVD법 등으로 형성하도록 해도 된다.

- [0102] 다음에, 도 7b에 나타낸 바와 같이 반도체막(1505)을 패터닝하고, 섬 형상의 반도체막(1507, 1508)을 형성하며, 이 섬 형상의 반도체막(1507, 1508)을 사용하여 TFT로 대표되는 각종의 반도체소자를 형성한다. 이때 본 실시예에서는, 하지막(1504)과 섬 형상의 반도체막(1507, 1508)이 접하고 있지만, 반도체소자에 의해서는, 하지막(1504)과 섬 형상의 반도체막(1507, 1508) 사이에, 전극이나 절연막 등이 형성되어 있어도 된다. 예를 들면 반도체소자의 하나의 보텀 게이트형 TFT인 경우, 하지막(1504)과 섬 형상의 반도체막(1507, 1508) 사이에, 게이트전극과 게이트 절연막이 형성된다.

- [0103] 본 실시예에서는, 섬 형상의 반도체막(1507, 1508)을 사용하여 톱게이트형의 TFT(1509, 1510)를 형성한다(도 7c). 구체적으로는, 섬 형상의 반도체막(1507, 1508)을 덮도록 게이트 절연막(1511)을 형성한다. 그리고, 게이트 절연막(1511) 상에 도전막을 형성하고, 패터닝함으로써, 게이트전극(1512, 1513)을 형성한다. 그리고, 게이트전극(1512, 1513)이나, 혹은 레지스트를 형성하고, 패터닝한 것을 마스크로서 사용하여, 섬 형상의 반도체막(1507, 1508)에 n형을 부여하는 불순물을 첨가하고, 소스영역, 드레인영역 및 LDD 영역을 형성한다. 이때, 여기서는 TFT(1509, 1510)를 모두 n형으로 하지만, p형 TFT일 경우는, p형을 부여하는 불순물을 첨가한다.

- [0104] 상기 일련의 공정에 의해 TFT(1509, 1510)를 형성할 수 있다. 이때, TFT의 제조방법은, 전술한 공정에 한정되지

않는다.

[0105] 다음에, TFT(1509, 1510)를 덮어, 제1 층간절연막(1514)을 막형성한다. 그리고, 게이트 절연막(1511) 및 제1 층간절연막(1514)에 콘택홀을 형성한 후, 콘택홀을 통해 TFT(1509, 1510)와 접속하는 단자(1515~518)를, 제1 층간절연막(1514)에 접하도록 형성한다.

[0106] 액정표시장치의 화소부의 스위칭소자로서 사용되는 TFT(1510)는, 단자(1518)와 전기적으로 접속되어 있다. 다음에, ITO 등의 투명도전막을 사용하여, 단자(1518)에 접하도록 액정셀의 화소전극(1550)을 제조한다. 그리고, 절연막을 사용한 스페이서(1519)를 형성한다. 다음에, 화소전극(1550), 단자(1518) 및 스페이서(1519)를 덮어 배향막(1520)을 형성하여, 러빙처리를 시행한다. 이때, 배향막(1520)은 박막회로와 겹치도록 형성해 두어도 된다.

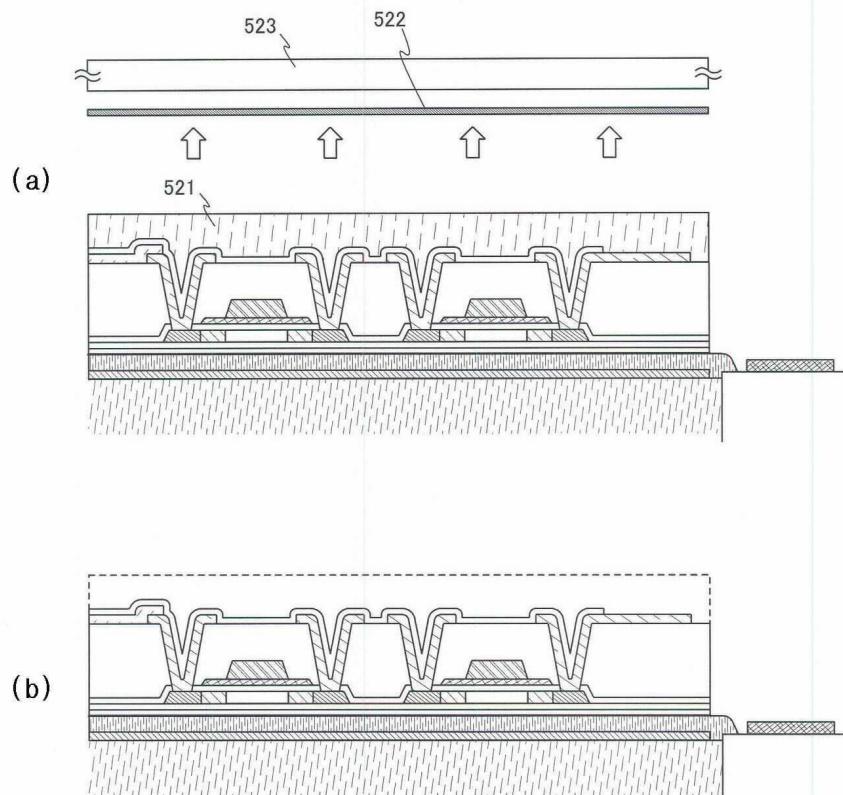

[0107] 다음에, 액정을 밀봉하기 위한 밀봉재(1521)를 형성한다. 그리고, 도 8a에 나타낸 바와 같이, 밀봉재(1521)로 둘러싸인 영역에 액정(1522)을 적하한다. 그리고, 도 8b에 나타낸 바와 같이, 별도로 형성해 둔 대향기판(1523)을, 밀봉재(1521)를 사용하여 접착시킨다. 밀봉재에는 충전재가 혼입되어도 된다. 대향기판(1523)의 두께는 수백  $\mu\text{m}$  정도이며, 투명도전막으로 이루어진 대향전극(1524)과, 러빙처리가 시행된 배향막(1526)이 형성되어 있다. 또, 이들에 덧붙여, 컬러필터나, 디스크리네이션(disclination)을 막기 위한 블랙 매트릭스(차폐막) 등이 형성되어도 된다. 또한, 편광판(1527)을, 대향기판(1523)의 대향전극(1524)이 형성되어 있는 면의 반대면에 접착해둔다.

[0108] 대향전극(1524), 액정(1522) 및 화소전극(1550)이 겹치는 영역이, 액정셀(1528)에 해당한다. 액정셀(1528)이 완성하면, 패널(1529)도 완성된다. 또한, 본 실시예에서는 박막회로(1530)와 대향기판(1523)이 겹쳐 있지 않지만, 감히 대향기판(1523)과 박막회로(1530)를 포개도록 해도 된다. 그 경우, 액정표시장치의 기계적 강도를 높이기 위해, 대향기판과 박막회로의 사이에 절연성을 갖는 수지를 충전시키도록 해도 된다.

[0109] 이때 본 실시예에서는 디스펜서식(적하식)을 사용하여 액정을 봉입하고 있지만, 본 발명은 이것에 한정되지 않는다. 대향기판을 접착하고 나서 모세관 현상을 사용하여 액정을 봉입하는 딥식(퍼 올리기 식)을 사용하여도 된다.

[0110] 다음에, 도 9a에 나타낸 바와 같이, 박막회로(1530) 및 패널(1529)로 덮어 보호층(1531)을 형성한다. 보호층(1531)은, 후에 제2 기판(1533)을 접착하거나 박리하거나 할 때에, 박막회로(1530) 및 패널(1529)을 보호할 수 있고, 게다가 제2 기판(1533)의 박리 후에 제거하는 것이 가능한 재료를 사용한다. 예를 들면, 물 또는 알코올류에 가용인 에폭시계, 아크릴레이트계, 실리콘계의 수지를 전체면에 도포함으로써 보호층(1531)을 형성할 수 있다.

[0111] 본 실시예에서는 스판코트로 수용성수지(TOAGOSEI 제조: VL-WHSL10)를 막두께  $30\mu\text{m}$ 가 되도록 회전도포하여, 가경화시키기 위해 2분간 노광을 한 후, UV 광을 이면으로부터 2.5분, 표면에서 10분, 합계 12.5분의 노광을 하여 본경화시켜, 보호층(1531)을 형성한다.

[0112] 이때, 복수의 유기수지를 적층하는 경우, 유기수지끼리는 사용하고 있는 용매에 의해 도포 또는 소성시에 일부 용해하거나, 밀착성이 지나치게 높아질 우려가 있다. 따라서, 제1 층간절연막(1514)과 보호층(1531)을 함께 같은 용매에 가용인 유기수지를 사용하는 경우, 후의 공정에서 보호층(1531)의 제거가 스무스하게 행하여도록, 제1 층간절연막(1514)을 덮도록, 무기절연막( $\text{SiN}_x$ 막,  $\text{SiN}_x\text{O}_y$ 막,  $\text{AlN}_x$ 막, 또는  $\text{AlN}_x\text{O}_y$ 막)을 형성해 두는 것이 바람직하다.

[0113] 다음에, 금속산화막(1503)과 산화물막(1502) 사이의 밀착성, 또는 금속산화막(1503)과 금속막(1501) 사이의 밀착성을 부분적으로 저하시켜, 박리개시의 계기가 되는 부분을 형성하는 처리를 행한다. 구체적으로, 박리하고자 하는 영역의 주연을 따라 외부로부터 국소적으로 압력을 가하여 금속산화막(1503)의 층 내 또는 계면 균방의 일부에 손상을 준다. 본 실시예에서는, 다이아몬드 펜 등의 딱딱한 바늘을 금속산화막(1503)의 에지 균방에 수직하게 부착하여, 그대로 하중을 건 상태에서 금속산화막(1503)을 따라 움직인다. 바람직하게는, 스크라이버 장치를 사용하고, 가압력을  $0.1\text{mm} \sim 2\text{mm}$ 으로 하여, 압력을 가하여 움직이게 하면 된다. 이와 같이, 박리를 하기 전에, 박리가 시작되는 계기가 되도록 한, 밀착성이 저하된 부분을 형성함으로써, 후의 박리공정에서의 불량을 감소시킬 수 있어, 수율을 향상할 것이다.

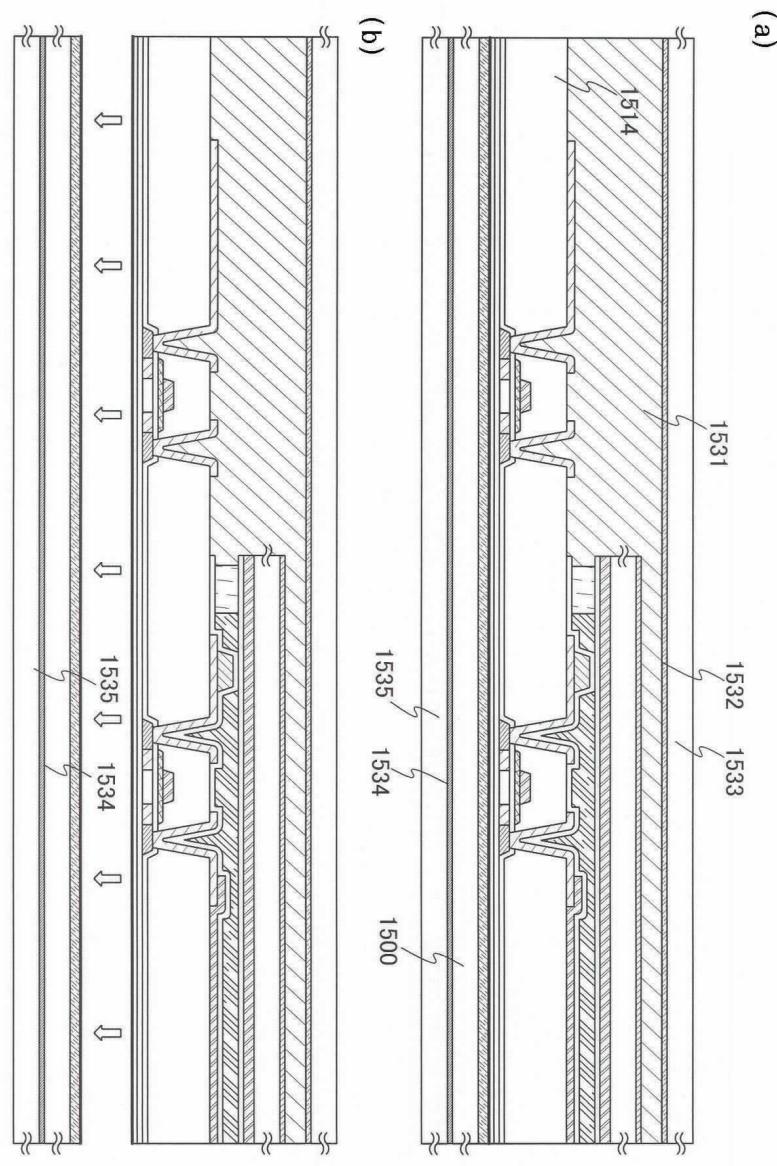

[0114] 이어서, 양면 테이프(1532)를 사용하여, 보호층(1531)에 제2 기판(1533)을 접착하고, 그 위에 양면 테이프(1534)를 사용하여, 제1 기판(1500)에 제3 기판(1535)을 접착한다. 이때, 양면 테이프가 아니라 접착제를 사용해도 된다. 예를 들면, 자외선에 의해 박리하는 접착제를 사용함으로써, 제2 기판 박리시에 반도체소자에 걸리

는 부담을 경감시킬 수 있다. 제3 기판(1535)은, 후의 박리공정에서 제1 기판(1500)이 파손하는 것을 막기 위해 접착한다. 제2 기판(1533) 및 제3 기판(1535)에서는, 제1 기판(1500)보다도 강성이 높은 기판, 예를 들면 석영 기판, 반도체기판을 사용하는 것이 바람직하다.

[0115] 이어서, 금속막(1501)과 산화물막(1502)을 물리적수단으로 박리한다. 박리는, 이전의 공정에서, 금속산화막(1503)의 금속막(1501) 또는 산화물막(1502)에 대한 밀착성이 부분적으로 저하한 영역에서 시작한다.

[0116] 금속막(1501)과 금속산화막(1503)의 사이에서 분리하는 부분과, 산화물막(1502)과 금속산화막(1503) 사이에서 분리하는 부분과, 금속산화막(1503) 자체가 양쪽으로 분리하는 부분이 생긴다. 그리고, 제2 기판(1533)측에 반도체소자(여기서는, TFT(1509, 1510))가, 제3 기판(1535)측에 제1 기판(1500) 및 금속막(1501)이, 각각 접착한 채 분리한다. 박리는, 비교적 작은 힘(예를 들면, 인간의 손, 노즐로부터 내뿜어지는 가스의 풍압, 초음파 등)으로 행할 수 있다. 박리 후의 상태를 도 9b에 나타낸다.

[0117] 다음에, 접착제(1539)로, 소자기판(1540)과, 부분적으로 금속산화막(1503)이 접착되어 있는 산화물층(1502)을 접착한다(도 10). 이때에, 양면 테이프(1532)에 의한 제2 기판(1533)과 보호층(1531) 사이의 밀착력보다도, 접착제(1539)에 의한 산화물층(1502)과 소자기판(1540) 사이의 밀착력 쪽이 높아지도록, 접착제(1539)의 재료를 선택하는 것이 중요하다.

[0118] 접착제(1539)로서는, 반응경화형 접착제, 열경화형 접착제, 자외선 경화형 접착제 등의 광경화형 접착제, 혼기형 접착제 등의 각종 경화형 접착제를 들 수 있다. 더욱 바람직하게는, 은, 니켈, 알루미늄, 질화알루미늄으로 이루어진 분말, 또는 충전재를 포함하게 하고 접착제(1539)도 높은 열전도성을 구비하는 것이 바람직하다.

[0119] 이때, 금속산화막(1503)이 산화물막(1502)의 표면에 잔존하고 있으면, 소자기판(1540)과의 밀착성이 나빠지는 경우가 있으므로, 완전히 에칭 등으로 제거하고 나서 프린트 배선기판에 접착시켜, 밀착성을 높이도록 하여도 된다.

[0120] 다음에, 도 10에 나타낸 바와 같이, 보호층(1531)으로부터 양면 테이프(1532)와 제2 기판(1533)을 순서대로, 또는 동시에 박리한다. 이때, 접착제(1539)로서 자외선 경화형 접착제를 사용하여, 양면 테이프(1532)에 자외선에 의해 박리하는 테이프 또는 접착제를 사용함으로써, 자외선조사에 의해 양면 테이프(1532)의 박리와 접착제(1539)의 경화를 동시에 행할 수 있다.

[0121] 그리고, 도 11a에 나타낸 바와 같이 보호층(1531)을 제거한다. 여기서는, 보호층(1531)에 수용성 수지가 사용되므로, 물에 용해시켜 제거한다. 보호층(1531)이 잔류하고 있으면 불량 원인이 될 경우는, 제거후의 표면에 세정처리나 O<sub>2</sub>플라즈마처리를 시행하여, 잔류하고 있는 보호층(1531)의 일부를 제거하는 것이 바람직하다.

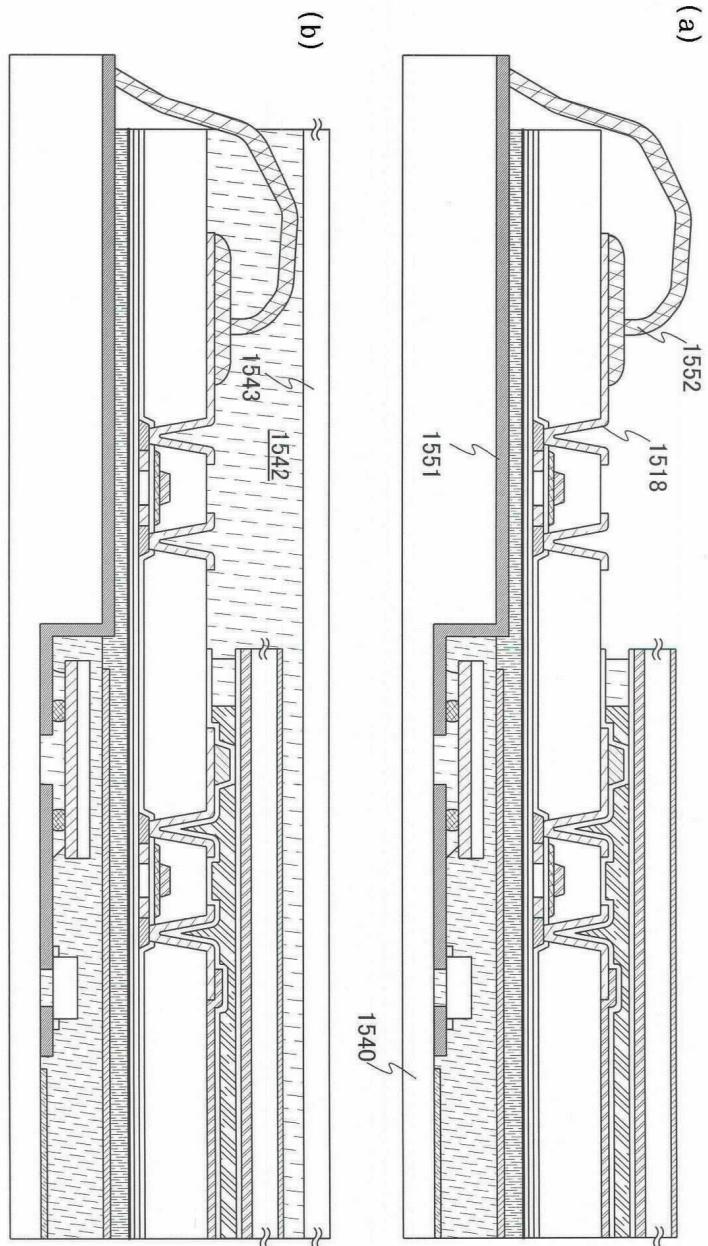

[0122] 다음에, 단자(1518)와, 소자기판(1540)에 설치된 배선 1551을, 와이어본딩법을 사용하여, 배선 1552로 전기적으로 접속함으로써, 액정표시장치가 완성된다. 배선(1551)은, 예를 들면 구리에 금 또는 주석을 도포함으로써 형성할 수 있다. 또 단자(1518)와 배선(1551)을 접속하는 타이밍은 이것에 한정되지 않는다.

[0123] 이 상태로 액정표시장치를 완성하여도 되지만, 본 실시예에서는, 액정표시장치를 밀봉부재로 더 밀봉함으로써, 기계적 강도를 높인다.

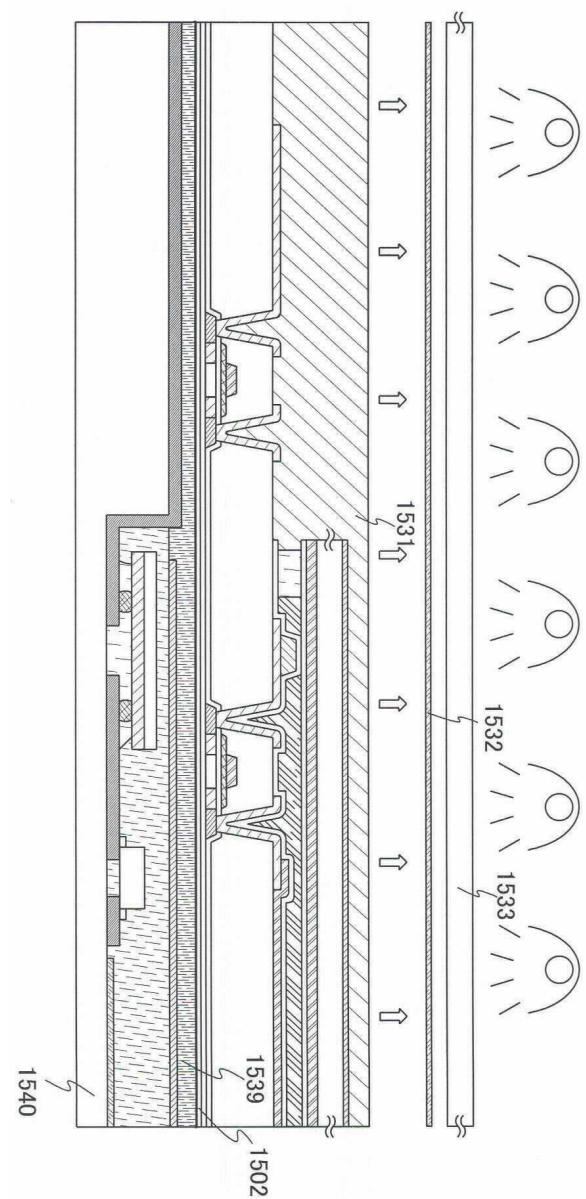

[0124] 도 11b에 나타낸 바와 같이, 박막회로(1530) 및 패널(1529)을 수지(1542)로 덮고, 박막회로(1530) 및 패널(1529)을 보호하기 위한 커버부재(1543)를 설치한다. 또한, 커버부재(1543)는, 반드시 설치할 필요는 없고, 그대로 소자기판(1540)을 밀봉하도록 하여도 된다.

[0125] 액정표시장치의 밀봉에는 일반적으로 사용하고 있는 재료를 사용할 수 있고, 예를 들면 폴리에스테르, 아크릴산, 폴리아세트산 비닐, 프로필렌, 염화비닐, 아크릴로니트릴부타디엔 스티렌 수지, 폴리에틸렌테레프탈레이트 등의 고분자재료를 사용하는 것이 가능하다. 이때, 밀봉시, 액정표시장치의 화소부를 노출시키던가, 화소부로부터의 광이 투과하도록, 수지(1542)나 커버부재(1543)의 재료를 적절히 선택하도록 한다.

[0126] 밀봉부재로 밀봉함으로써, 액정표시장치의 기계적 강도를 높이거나, 액정표시장치로부터 발생한 열을 방열하거나, 액정표시장치의 외부의 인접 회로로부터의 전자노이즈를 차단할 수 있다.

[0127] 이때, 소자기판(1540), 커버부재(1543) 및 대향기판(1523)은, 플라스틱 기판을 사용할 수 있다. 플라스틱 기판으로서는, 극성기가 붙은 노르보르넨수지로 이루어진 JSR 제조의 ARTON®를 사용할 수 있다. 또한, 폴리에틸렌 테레프탈레이트(PET), 폴리에틸슬론(PES), 폴리에틸렌나프타레이트(PEN), 폴리카보네이트(PC), 나일론, 폴리에테르에테르케톤(PEEK), 폴리술론(PSF), 폴리에테르아미드(PEI), 폴리아릴레이트(PAR), 폴리부틸렌테레프탈레이

트(PBT), 폴리이미드 등의 플라스틱 기판을 사용할 수 있다. 소자기판(1540)은 액정표시장치에서 발생한 열을 확산시키기 위해, 2~30W/mK 정도의 높은 열전도율을 갖는 것이 바람직하다.

[0128] 이때, 본 실시예에서는, 금속막(1501)의 재료로서 텅스텐을 사용하고 있지만, 본 발명에서 금속막은 이 재료로 한정되지 않는다. 그 표면에 금속산화막(1503)이 형성되어, 이 금속산화막(1503)을 결정화함으로써 기판을 박리 할 수 있는 금속을 함유한 재료이어도 된다. 예를 들면, TiN, WN, Mo 등을 사용할 수 있다. 또한, 이것들의 합금을 금속막으로서 사용하는 경우, 그 조성비에 따라 결정화시의 가열처리의 최적 온도가 다르다. 따라서, 조성비를 조정함으로써, 반도체소자의 제조공정에서 방해되지 않는 온도로 가열처리를 할 수 있어, 반도체소자의 프로세스의 선택범위가 제한되기 어렵다.

[0129] LED 구동용 박막회로에 사용되는 반도체소자도, 전술한 반도체소자의 제조방법을 참조하여 제조할 수 있다.

[0130] 이때, 발광 다이오드를 덮고 있는 수지의 재료는, 제1 기판, 제2 기판 및 접착제의 경화방법에 따라서 적절히 선택하는 것이 바람직하다.

[0131] 다음에, 소자기판 상에 형성된 배선과, 박막회로 또는 LED 구동용 박막회로를, 와이어본딩법이 아니라 플립칩법을 사용하여 전기적으로 접속한 예에 관해서 설명한다.

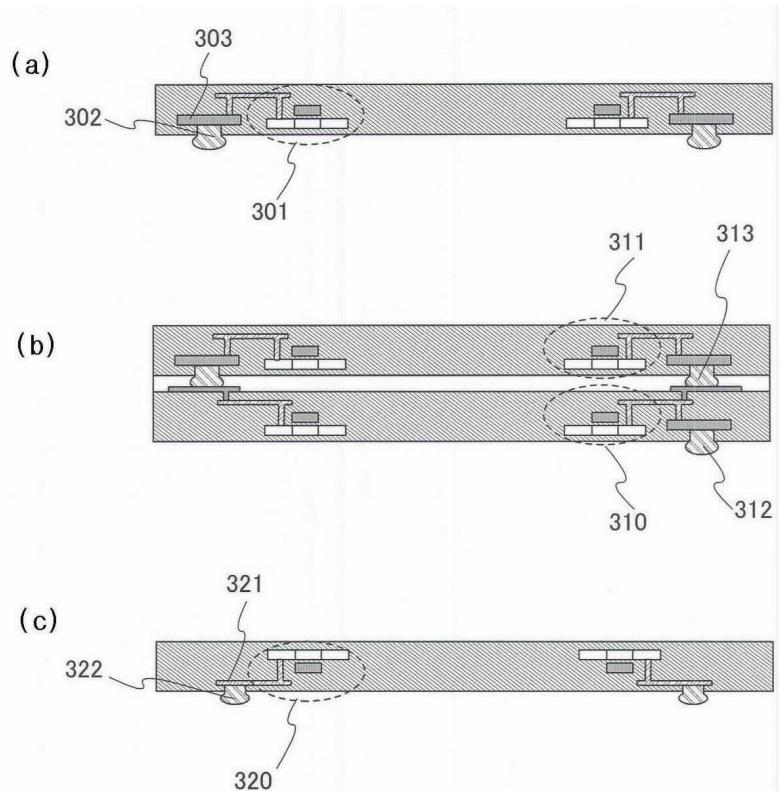

[0132] 도 12a는 솔더볼이 각각 설치되는 박막회로 또는 LED 구동용 박막회로의 단면도를 나타낸다.

[0133] 도 12a에 나타낸 것처럼, 반도체소자(301)와 소자기판 상의 배선을, 솔더볼(302)로 전기적으로 접속한다. 솔더볼(302)은, 반도체소자(301)의 소자기판측에 설치되고, 반도체소자(301)에 전기적으로 접속된 전극(303)에 접속되어 있다. 전극(303)은, 반도체소자(301)가 TFT인 경우, 이 TFT의 게이트전극과 동일한 도전막으로 형성되어 도 된다.

[0134] 다음에, 도 12b는 플립칩법을 사용하여 반도체소자가 적층되어 있다, 박막회로 또는 LED 구동용 박막회로의 단면도를 나타낸다. 도 12b에 나타낸 것처럼, 2개의 층에 형성된 반도체소자(310, 311)가 적층되어 있다. 그리고, 소자기판에 형성된 배선과, 반도체소자 310과의 전기적인 접속은, 솔더볼 312를 사용하여 행해진다. 또한, 반도체소자 311과 반도체소자 310과의 전기적인 접속은, 솔더볼 313을 사용하여 행해진다.

[0135] 다음에, 도 12c는 소자기판 상에 형성된 배선과 솔더볼을 접속한 예를 나타낸다. 도 12c에 나타낸 것처럼, 반도체소자(320)에 직접 접속된 배선(321)에 솔더볼(322)을 접속하도록 형성한다.

[0136] 이때, 플립칩법일 경우, 접속해야 되는 배선 수가 증가해도, 와이어본딩법과 비교하여, 비교적 배선간의 피치를 넓게 확보할 수 있으므로, 박막회로 또는 LED 구동용 박막회로와, 배선과의 접속수가 많은 경우에 효과적이다.

[0137] 솔더볼과, 소자기판 상의 배선의 접속은, 열압착이나, 초음파에 의한 진동을 가한 열압착 등 여러가지 방법을 사용할 수 있다. 이때, 언더필이 압착후된 솔더볼간의 간극을 매립하도록 하여, 접속부분의 기계적 강도나, 박막회로에서 발생한 열 확산 등의 효율을 높이도록 해도 된다. 언더필은, 반드시 사용할 필요는 없지만, 소자기판과 반도체소자의 열팽창 계수의 부정합으로부터 생기는 응력에 의해, 접속불량이 발생하는 것을 방지할 수 있다. 초음파를 가하여 압착하는 경우, 간단히 열압착하는 경우와 비교하여 접속불량을 억제할 수 있다. 특히, 접속하는 범프가 적어도 300정도인 경우에 효과적이다.

[0138] 도 12a~도 12c를 참조하여 나타낸 방식을 조합함으로써, 소자기판에 형성된 배선과, 박막회로 또는 LED 구동용 박막회로를, 여러 가지 형태로 전기적으로 접속할 수 있다. 또한, 플립칩법과, 와이어본딩법을 조합하여 접속하는 것도 가능하다.

[0139] 본 실시예에서는, 액티브 매트릭스형 액정표시장치에 관해서 설명하였지만, 본 발명은 패시브 매트릭스형 액정표시장치이어도 된다.

[0140] 본 발명은 상기 구성에 의해, 기계적 강도가 손상되지 않고 액정표시장치를 비약적으로 얇게 할 수 있고, 또한 경량화할 수 있다. 그리고, 본 발명의 제조방법에 의해 형성된 액정표시장치를 전자기기에 사용함으로써, IC에 사용하는 공간을 보다 넓게 확보할 수 있어, 전자기기의 경량화 또는 소형화를 방해하지 않고 고기능화를 실현 할 수 있다. 특히, 휴대용 전자기기의 경우, 경량화 및 소형화함으로써 편리하게 사용하기가 아주 좋아지기 때문에, 본 발명의 액정표시장치를 사용하는 것은 대단히 유용하다. 또한, 본 발명에서는 액정표시장치의 화소부 사이즈를 보다 크게 해도, 종래의 유리기판을 사용한 액정표시장치와 같은 정도의 중량으로 할 수 있다.

- [0141] [실시예]

- [0142] 이하, 본 발명의 실시예에 관해서 설명한다.

- [0143] (실시예 1)

- [0144] 본 실시예에서는, 전자카드로 대표되는 카드에, 본 발명의 제조방법을 사용하여 형성된 액정표시장치를 사용한 경우에 관해서 설명한다.

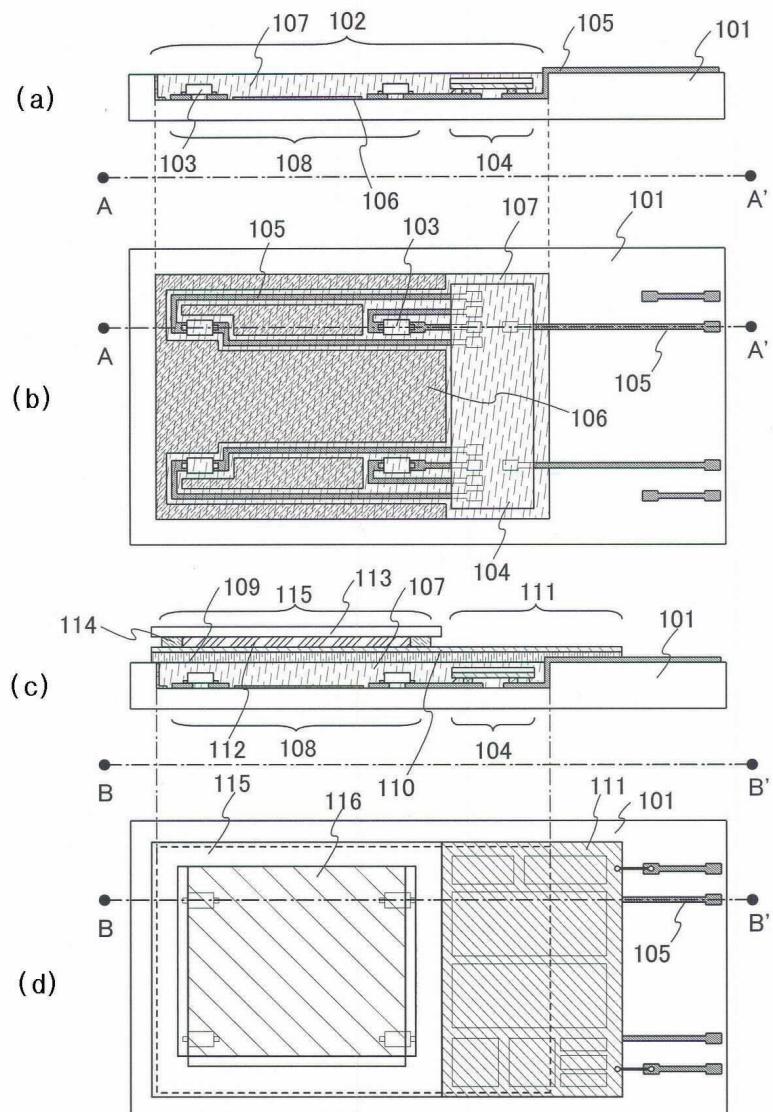

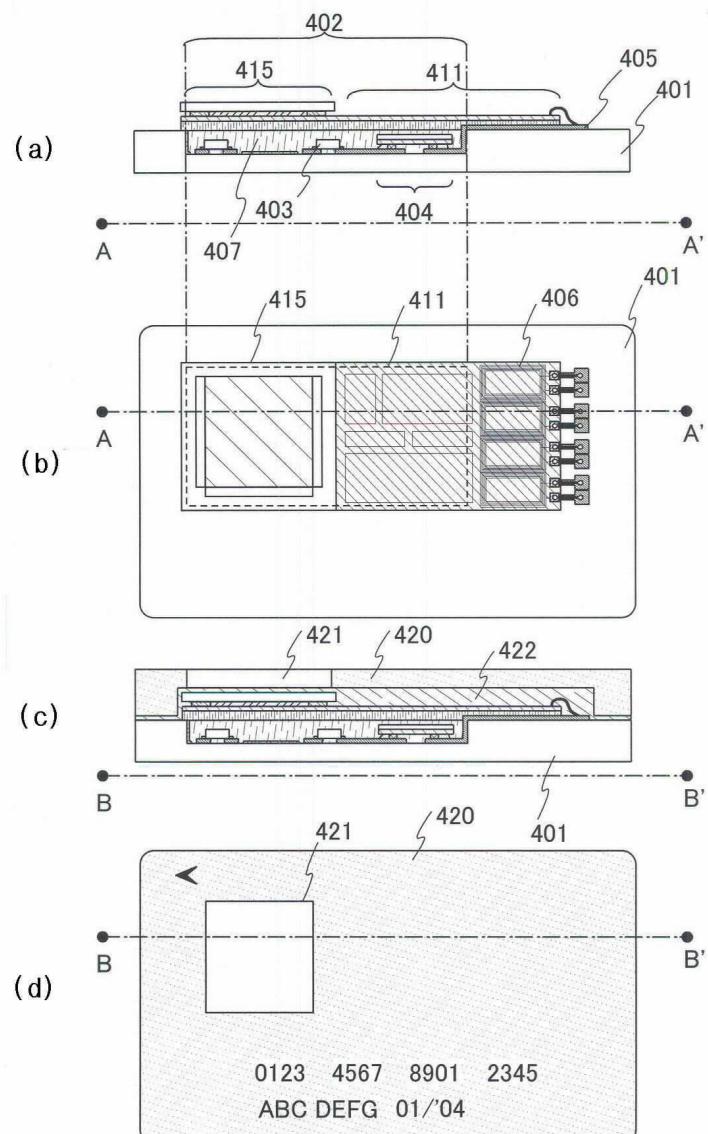

- [0145] 도 13a 내지 도 13d를 참조하여, 본 실시예의 전자카드의 구성에 관해서 설명한다. 도 13a는 패널이 완성한 시점에서의 소자기판(401)의 단면도를 나타낸다. 또한, 도 13b는 도 13a에 나타낸 소자기판의 평면도에 해당하고, 도 13b의 A-A'에서의 단면도가 도 13a에 해당한다.

- [0146] 도 13a 및 도 13b에 나타낸 소자기판(401)은, 오목부(402)를 갖고, 이 오목부(402) 내에 LED(403)가 1개 또는 복수개 설치된다. 또한 오목부(402)에는, LED 구동용 박막회로(404)가 설치되어 있고, LED(403)와 LED 구동용 박막회로(404)가 수지(407)로 덮어져 있다.

- [0147] 도면부호 415는 패널, 도면부호 411은 박막회로로, 모두 별도로 형성되고, 소자기판(401) 상에 접착되어 있다. 박막회로(411)는 안테나코일(406)을 갖고 있다. 그리고, 소자기판(401) 상에 형성된 배선(405)이 안테나코일(406)과 전기적으로 접속되어 있다.

- [0148] 도 13c는 전자카드를 완성한 시점에서의 본 발명의 액정표시장치의 단면도를 나타낸다. 도 13d는 도 13c에 나타낸 상태의 액정표시장치의 평면도에 해당하고, 도 13d의 B-B'에서의 단면도가 도 13c에 해당한다.

- [0149] 도 13c 및 도 13d에 나타낸 전자카드는, 소자기판 상에 형성된 패널(415)과 박막회로(411)가, 수지(422)로 밀봉하도록 커버부재(420)로 덮어져 있다. 그리고 본 실시예에서는, 커버부재(420) 중 패널(415)과 겹치는 부분(421)에서, 패널(415)로부터의 광이 투과하게 되어 있다. 이때 본 발명은 이것에 한정되지 않고, 패널 이외의 부분도 광이 투과하는 재료로, 커버부재를 형성하여도 된다.

- [0150] 본 실시예에서는, 안테나코일을 사용하여 전자유도에 의해 신호 또는 전원전압을 공급할 수 있는 전자카드의 구성에 대하여 설명하였지만, 발광소자 또는 광센서 등을 사용하여 광에 의해 신호 또는 전원전압을 공급하는 전자카드이어도 된다. 또한, 전자카드는 비접촉형 카드로 한정되지 않는다. 전자카드는, 단자를 통해 단말장치에 직접 신호를 전송하는 접촉형 카드이어도 된다.

- [0151] 전자카드는, 현금카드, 신용카드, 프리페이드 카드, 신분증명서 대신이 되는 ID 카드, 정액권 등 여러가지 용도로 사용된다. 본 발명의 제조방법을 사용하여 형성되는 액정표시장치를 탑재함으로써, 전자카드 내의 데이터를 화소부에 표시하는 것이 가능하게 되고, 또한 얼굴 사진을 표시함으로써, 본인 인증의 확실성을 높일 수 있다. 얼굴 사진을 증명사진 대신에 사용하는 것이라면, 적어도 QVGA( $320 \times 240$ ) 정도의 해상도가 필요하다고 생각된다.

- [0152] (실시예 2)

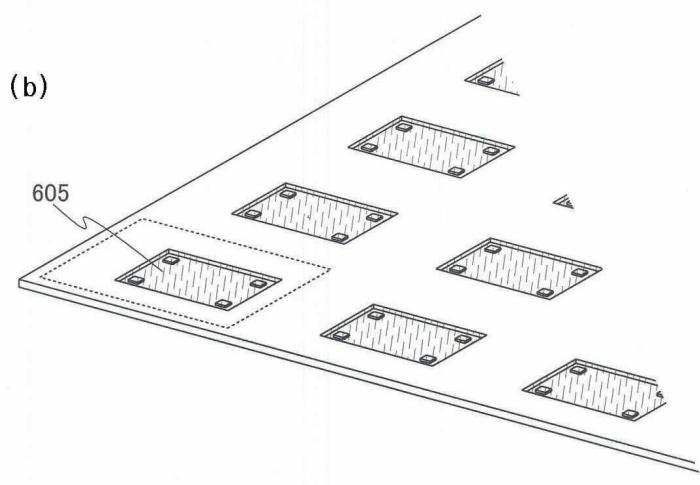

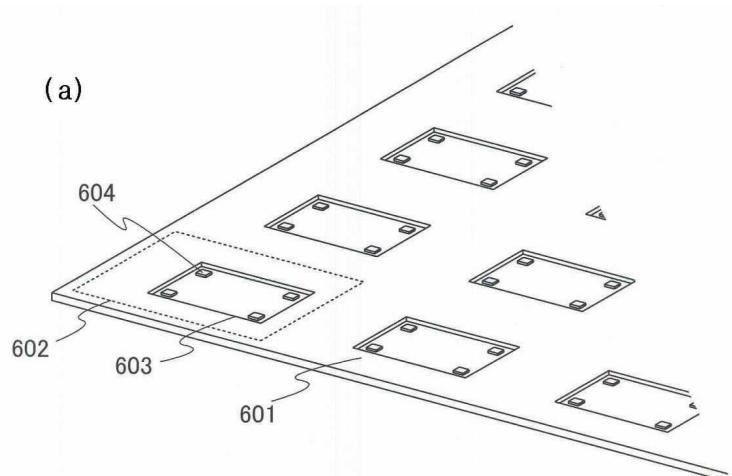

- [0153] 도 14a 및 도 14b는 대형의 소자기판으로부터 복수의 액정표시장치를 제조하는 방법에 대하여 설명한다.

- [0154] 도 14a 및 도 14b에 나타낸 바와 같이, 대형의 소자기판(601)을 사용하는 경우, 각각의 액정표시장치에 대응하는 영역(602)에, 복수의 오목부(603)를 설치한다. 그리고, 각 오목부(603)에 LED(604)를 설치한다. 그리고, LED(604)에 전기적으로 접속된 배선, LED 구동용 박막회로, 반사막 등(모두 도시하지 않음)을 설치한 후, 각 오목부(603)에 도 14b에 나타낸 바와 같이, 수지(605)를 충전한다.

- [0155] 그리고 실시예에서 나타낸 방법에 따라, 패널이나 박막회로를 형성하고, 다이싱함으로써, 복수의 액정표시장치를 1개의 소자기판으로부터 제조할 수 있다. 다이싱은, 패널이나 박막회로를 형성하기 전 또는 후에도, 어느 쪽의 공정에서도 행할 수 있다.

- [0156] (실시예 3)

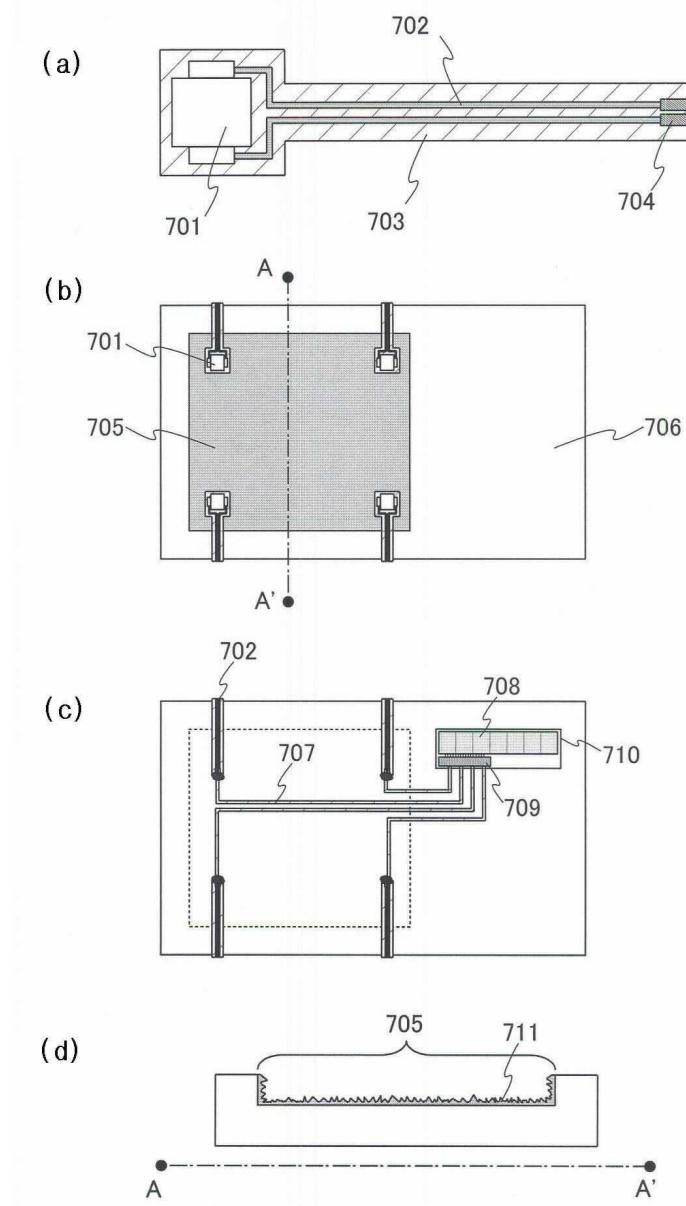

- [0157] 본 실시예에서는, LED를 소자기판 상에 설치한 배선과 직접 접속하는 것은 아니며, LED를 플렉시블 프린트 배선 기판(FPC)에 접속하고, 그 FPC를 소자기판 상의 배선에 접속하는 예에 대하여 설명한다.

- [0158] 도 15a는 LED가 접속된 FPC의 평면도를 나타낸다. LED(701)는 플라스틱필름(703)에 의해 끼워진 리드(702)와 접속되어 있다. 그리고, 리드(702)에 접속되어 있는 단자(704)는, 플라스틱 필름(703)에 덮어지지 않고, 노출되어

있다.

[0159] 도 15b는 소자기판(706)이 갖는 오목부(705)에, 도 15a에 나타낸 LED(701)를 접착한 모양을 나타낸다. 또한 도 15c는 도 15b에 나타낸 소자기판(706)의 이면측을 나타낸다.

[0160] 소자기판(706)에서, 오목부(705)의 이면측에는, 배선(707)이 설치된다. 그리고, 오목부(705)에 설치된 LED(701)와 배선(707)은, 리드(702)에 의해 전기적으로 접속되어 있다.

[0161] 소자기판(706)의 배선(707)이 설치되는 면에는, 오목부(710)가 설치되어 있다. 오목부(705, 710)가 설치되는 영역은, 소자기판(706)의 강도(intensity)를 고려하면, 서로 겹치지 않도록 하는 편이 바람직하다. 그리고 오목부(710)에는 태양전지(708)와, 그 태양전지(708)의 구동을 제어하기 위한 구동회로(709)가 설치되어 있고, 배선(707)은 구동회로(709)와 전기적으로 접속되어 있다.

[0162] 이와 같이, FPC에 의하면, 소자기판의 양쪽 면에 형성된 소자는, 서로 전기적으로 접속된다. 따라서, 소자기판을 낭비 없이 활용할 수 있다.

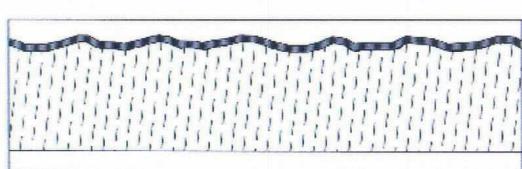

[0163] 도 15d는 오목부(705)의 점선 A-A'에서의 단면도를 나타낸다. 오목부(705)에는, 그 표면에 금속 반사막(711)이 형성되어 있다. 본 실시예에서는, 반사막(711)을 부식시키거나, 금강사를 사용하여 표면을 연마하는 샌드블라스트 가공을 함으로써, 표면에 미세한 요철을 설치하여 광을 난반사시켜, LED로부터의 광을 균일하게 화소부에 조사하기 쉽게 할 수 있다.

[0164] (실시예 4)

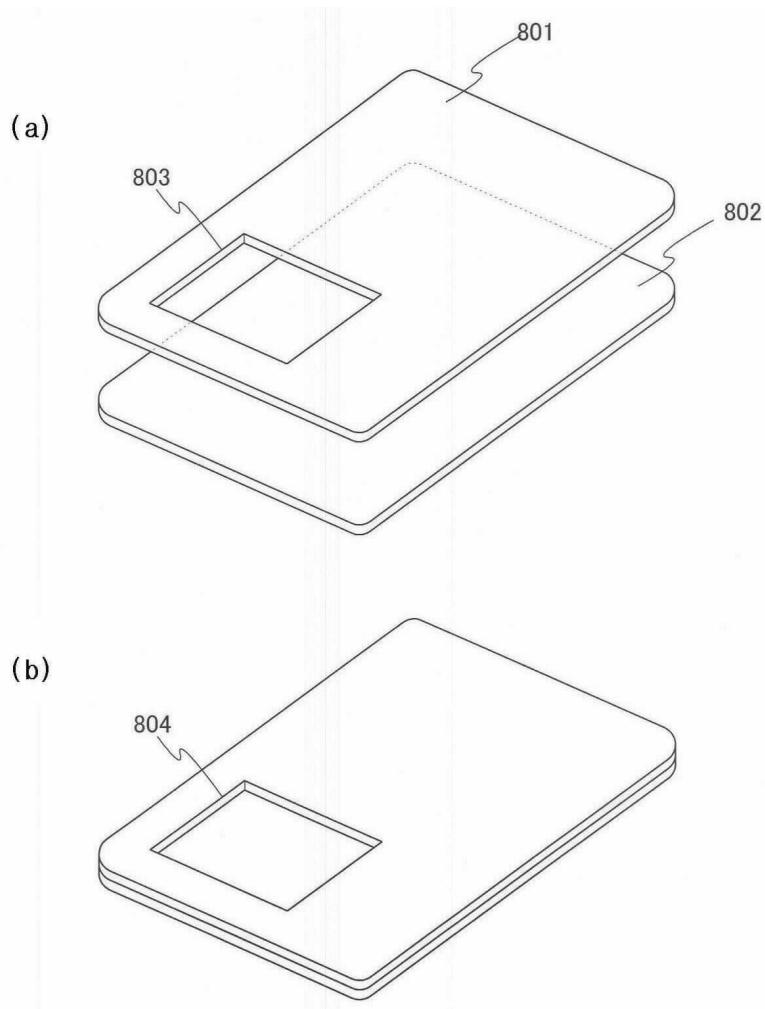

[0165] 본 실시예에서는, 오목부를 갖는 소자기판의 형성 방법에 대하여 설명한다.

[0166] 도 16a는 개구부(803)를 갖는 플라스틱 기판 801과, 평탄한 플라스틱 기판 802를 나타낸다. 이 플라스틱 기판(801, 802)은, 서로 접착된다. 개구부(803)가 평탄한 플라스틱 기판(802)과 겹치는 영역에, 오목부(804)를 갖는 소자기판(805)이 형성된다.

[0167] (실시예 5)

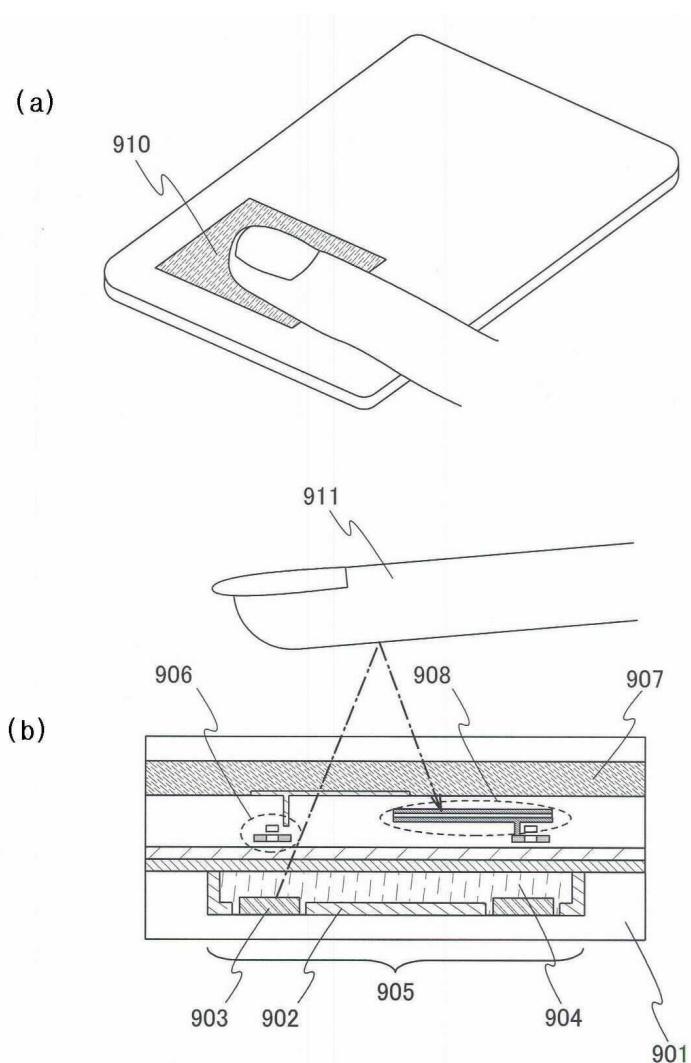

[0168] 본 실시예에서는, 본 발명에 따른 액정표시장치를 사용한 전자카드에 영역센서를 설치한 예에 대하여 나타낸다.

[0169] 도 17a는 화상 표시부뿐만 아니라, 영역센서로서도 기능하는 화소부(910)를, 손가락 끝으로 누르고 있는 도면을 나타낸다. 그리고 도 17b는 도 17a에 나타낸 화소부(910)의, 단면도를 나타낸다.

[0170] 도 17b에 나타낸 바와 같이, 소자기판(901)에는 오목부(905)가 설치되어 있고, 오목부(905)의 표면에는 반사막(902)이 설치되어 있다. 또한, 오목부(905)에는 LED(903)가 설치되어 있고, 이 LED(903)는 수지(904)로 덮여져 있다.

[0171] 또한, 소자기판(901) 상에는, 액정(907)에 전압을 인가하기 위한 TFT(906)와 포토다이오드(908)가 설치되어 있다. TFT(906)와 포토다이오드(908)는, 모두 별도로 다른 기판 상에 형성된 후, 박리되어, 소자기판(901) 상에 접착되어 있다.

[0172] 그리고, LED(903)로부터 발생한 광이 피사체인 손가락(911)에서 반사하고, 포토다이오드(908)에 조사함으로써, 손가락(911)의 화상 데이터를 취득할 수 있다.

[0173] (실시예 6)

[0174] 본 발명에 따른 액정표시장치는 여러가지 전자기기에 사용하는 것이 가능하지만, 특히 휴대용 전자기기의 경우, 경량화 또는 소형화함으로써 사용의 편리함이 매우 좋아지기 때문에, 대단히 유용하다.

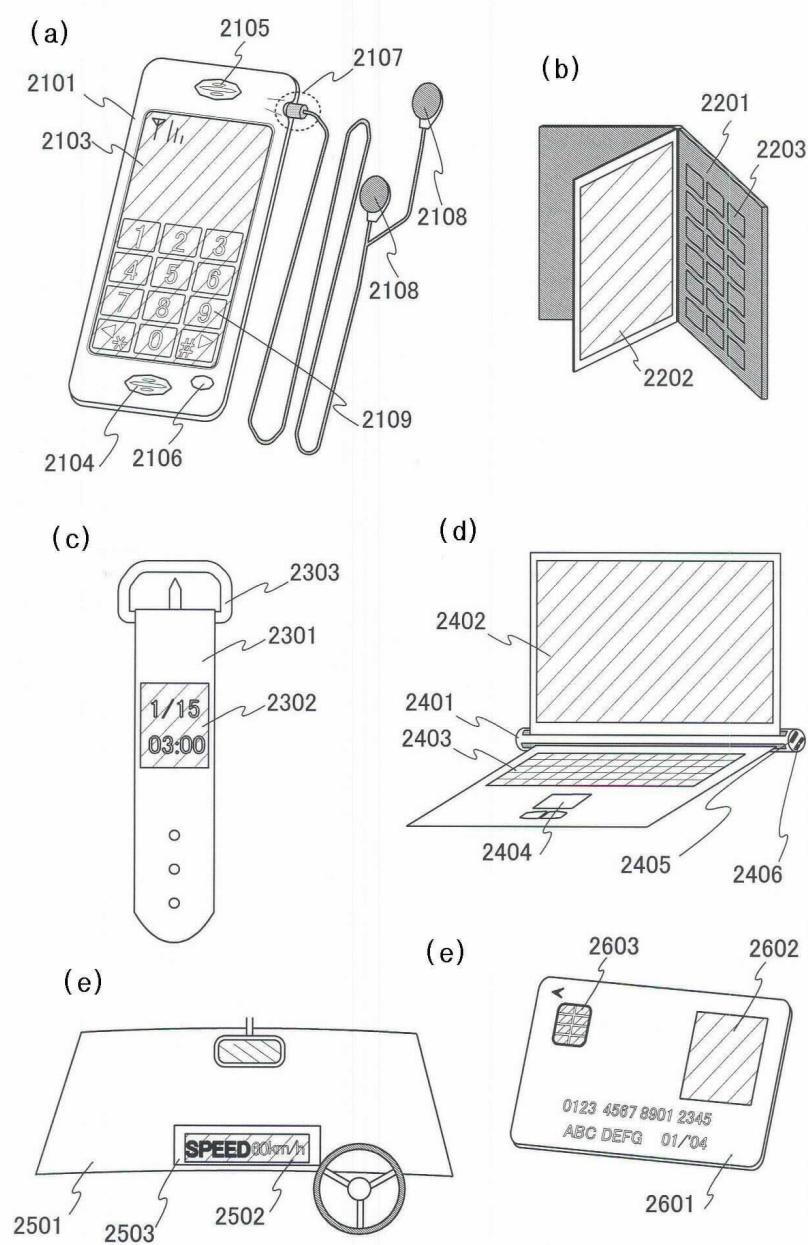

[0175] 도 18a는 시이트형 휴대전화로, 본체(2101), 표시부(2103), 음성입력부(2104), 음성 출력부(2105), 스위치(2106), 외부접속포트(2107) 등을 포함한다. 외부접속포트(2107)를 통해, 별도로 준비한 이어폰(2108)을 접속할 수 있다. 표시부(2103)에는, 본 발명에 따른 센서를 구비한 터치패널식 액정표시장치가 사용되고 있고, 표시부(2103)에 표시된 터치패널식 조작기(2109)에 접촉함으로써, 일련의 조작을 행할 수 있다. 또한, 본 발명의 액정표시장치가 구비된 박막회로는, 본체(2101) 내에 설치된 각종 신호처리회로로서 사용할 수 있다.

[0176] 도 18b는 전자서적으로, 본체(2201), 표시부(2202), 조작기(2203) 등을 포함한다. 또한, 모뎀이 본체(2201)에 내장되어 있어도 된다. 표시부(2202)에는 본 발명에 따른 센서를 갖는 액정표시장치가 사용되고 있다. 또한, 본 발명에 따른 액정표시장치가 구비된 박막회로는, 각종 신호처리회로로서 사용할 수 있다.

- [0177] 도 18c는 손목시계로, 본체(2301), 표시부(2302), 결쇠(2303) 등을 포함한다. 표시부(2302)에는 본 발명에 따른 센서를 갖는 액정표시장치가 사용되고 있다. 또한, 본 발명에 따른 액정표시장치가 구비된 박막회로는, 본체(2301) 내에 설치된 각종 신호처리회로로서 사용할 수 있다.

- [0178] 도 18d는 퍼스널 컴퓨터로, 본체(2401), 표시부(2402), 터치패널식 키보드(2403), 마우스(2404), 외부접속포트(2405), 전원플러그(2406) 등을 포함한다. 표시부(2402)에는, 본 발명에 따른 센서를 갖는 액정표시장치가 사용되고 있다. 또한, 터치패널식 키보드(2403) 및 마우스(2404)에는, 본 발명에 따른 센서를 갖는 터치패널식 액정표시장치가 사용되고 있고, 터치패널식 키보드(2403) 및 마우스(2404)에 접촉함으로써, 일련의 조작을 행할 수 있다. 또한, 본 발명에 따른 액정표시장치의 박막회로는, 각종 신호처리회로로서 사용할 수 있다.

- [0179] 도 18e는 자동차의 차내에서 본 자동차 앞유리에 해당한다. 자동차 앞유리(2501)는, 본 발명에 따른 액정표시장치(2503)와 접착되어 있고, 표시부(2502)에 운전자가 필요로 하는 각종의 정보를 표시할 수 있다. 이때 도 18e에서는, 본 발명에 따른 액정표시장치를 자동차 앞유리에 접착한 예에 대하여 설명하였지만, 운전석의 사이드와 뒤에 배치된 창문유리에 접착될 수 있다. 또한, 액정표시장치는, 자동차의 내부 또는 외부 상에 접착하는 것이 가능하다.

- [0180] 도 18f는 전자카드로, 본체(2601), 표시부(2602), 접속단자(2603) 등을 포함한다. 본 발명에 따른 액정표시장치의 화소부는, 표시부(2602)로서 사용할 수 있다. 또한, 본 발명에 따른 액정표시장치의 박막회로는, 본체(2601) 내에 설치된 각종 신호처리회로로서 사용할 수 있다.

- [0181] 따라서, 본 발명의 적용범위는 매우 넓고, 모든 분야의 전자기기에 사용하는 것이 가능하다. 또한, 본 실시예의 전자기기는, 실시예 1~5에 나타낸 구성의 임의의 구성을 사용할 수 있다.

- [0182] (실시예 7)

- [0183] 본 실시예에서는, 박리 후의 제1 기판측과, 절연막측에서의 단면을, TEM에 의해 관찰한 결과를 나타낸다.

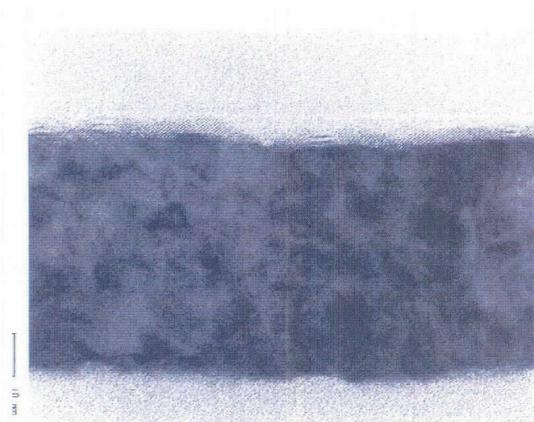

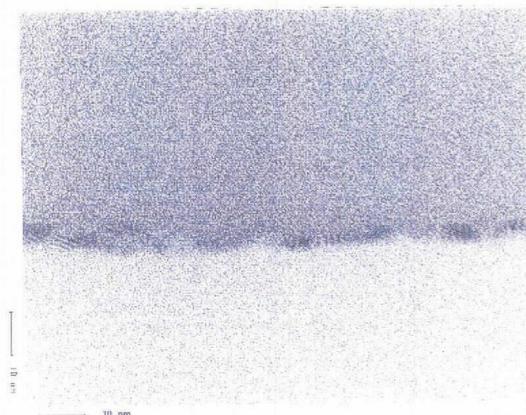

- [0184] 유리기판 상에, 스퍼터링법으로 W막을 50nm, 스퍼터링법으로 산화실리콘막을 200nm, PCVD법으로 산화질화실리콘막을 100nm, 반도체막으로서 플라즈마 CVD법으로 비정질실리콘막을 50nm를 순차로 적층 형성하였다. 그 후, 500°C 1시간과 550°C 4시간의 열처리를 행하여, 폴리테트라플루오로에틸렌레이프 등의 물리적수단에 의해 박리하였다. 이때의 기판측의 W막과 산화물층의 TEM 사진이 도 19이고, 반도체막측의 산화물층과 산화실리콘막의 TEM 사진이 도 20이다.

- [0185] 도 19에서는, 금속막에 접하여 금속산화막이 불균일하게 잔존하고 있다. 마찬가지로, 도 20에서도, 금속막에 접하여 금속산화막이 불균일하게 잔존하고 있다. 양쪽 TEM 사진으로부터, 박리는 금속산화막의 층 내 및 양쪽 계면에서 행해진 것이 실증되고, 또한 금속산화막은 금속막 및 산화실리콘막에 밀착하여 불균일하게 잔존하는 것을 안다.

- [0186] 따라서, 본 발명에 따른 액정표시장치에서, 절연막의 소자기판측에 금속산화막이 다소 부착된다.

- [0187] (실시예 8)

- [0188] 본 실시예에서는, 액정표시장치를 완성하고 나서 제1 기판을 박리하는 경우에 사용된 액정 재료에 대하여 설명한다.

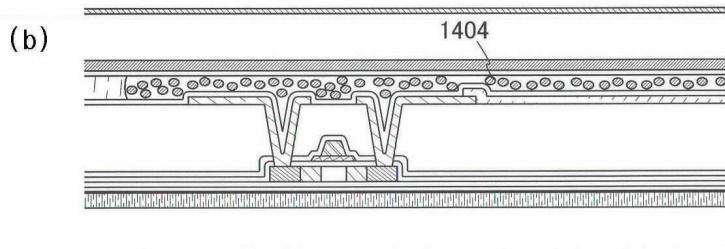

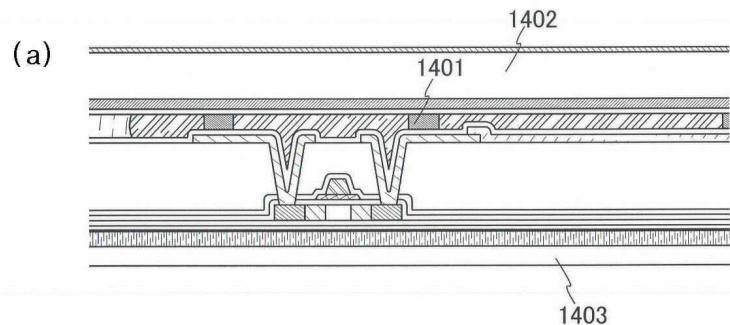

- [0189] 도 21a 및 도 21b는 본 실시예의 액정표시장치의 단면도를 나타낸다. 도 21a에 나타낸 액정표시장치는, 화소에 원주형상의 스페이서(1401)가 설치되어 있어, 대향기판(1402)과 소자측의 편광판(1403) 사이의 밀착성을 높이고 있다. 이에 따라, 제1 기판의 박리시에 밀봉재와 겹치는 영역 이외의 반도체소자가 제1 기판측에 잔류해 버리는 것을 방지할 수 있다.

- [0190] 또한, 도 21b는 네마틱액정, 스메틱액정, 강유전성 액정 혹은 그 액정들이 고분자수지 중에 함유된 PDLC(Polymer dispersed liquid crystal; 폴리머 분산형 액정)를 사용한 액정표시장치의 단면도를 나타낸다. PDLC(1404)를 사용함으로써, 대향기판(1402)과 소자측의 편광판(1403) 사이의 밀착성이 높아지고, 제1 기판의 박리시에 밀봉재와 겹치는 영역 이외의 반도체소자가 제1 기판측에 잔류해 버리는 것을 방지할 수 있다.

- [0191] 본 발명을 첨부도면을 참조하여 실시예들을 설명하였지만, 당업자에게 있어서 여러 가지 변화 및 변경이 명백하다는 것을 알 수 있을 것이다. 따라서, 다른 상기와 같은 변화 및 변경이 이후 설명된 본 발명의 범위를 벗어나지 않는다면, 그 변화 및 변경은 본 발명에 포함된다는 것을 알 수 있을 것이다.

### 부호의 설명

|        |            |                    |

|--------|------------|--------------------|

| [0192] | 101 : 소자기판 | 102 : 오목부          |

|        | 103 : LED  | 104 : LED 구동용 박막회로 |

|        | 105 : 배선   | 106 : 반사막          |

|        | 107 : 수지   | 108 : 광원부          |

|        | 109 : 접착제  | 110 : 반도체소자        |

|        | 111 : 박막회로 | 112 : 액정           |

|        | 113 : 대향기판 | 114 : 밀봉재          |

|        | 115 : 패널   | 116 : 화소부          |

### 도면

#### 도면1

## 도면2

## 도면3

## 도면4

도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

도면12

## 도면13

도면14

## 도면15

도면16

도면17

## 도면18

도면19

(a)

(b)

도면20

(a)

(b)

도면21

|                |                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和使用液晶显示装置的电子装置                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">KR1020100113468A</a>                                                                                                                                                               | 公开(公告)日 | 2010-10-21 |

| 申请号            | KR1020100091393                                                                                                                                                                                | 申请日     | 2010-09-17 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                             |         |            |

| [标]发明人         | YAMAZAKI SHUNPEI<br>아마자키순페이<br>TAKAYAMA TORU<br>타카야마토루<br>MARUYAMA JUNYA<br>마루야마준야<br>GOTO YUUGO<br>고토유우고<br>OHNO YUMIKO<br>오노유미코<br>ENDO AKIO<br>엔도아키오<br>ARAI YASUYUKI<br>아라이야수유키            |         |            |

| 发明人            | 아마자키순페이<br>타카야마토루<br>마루야마준야<br>고토유우고<br>오노유미코<br>엔도아키오<br>아라이야수유키                                                                                                                              |         |            |

| IPC分类号         | G02F1/1345 G02F1/1333 G02F1/13357 G02F1/1362 H01L27/146                                                                                                                                        |         |            |

| CPC分类号         | H01L2221/68359 G02F1/1362 G02F1/133603 H01L27/14678 G02F1/133305 G02F2001/13613<br>H01L2221/68368 H01L2224/48465 H01L2224/73265 H01L2224/8592 B65D88/56 B65G67/04<br>B65G2201/04 B65G2814/0347 |         |            |

| 代理人(译)         | LEE HWA我                                                                                                                                                                                       |         |            |

| 优先权            | 2003007568 2003-01-15 JP<br>2003007697 2003-01-15 JP                                                                                                                                           |         |            |

| 其他公开文献         | KR101072411B1                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                      |         |            |

**摘要(译)**

液晶显示器具有第一塑料基板和发光器件，发光器件布置在第一塑料基板和树脂上，覆盖发光器件和绝缘层，接触树脂和半导体器件，接触绝缘层和液晶单元，电连接到半导体器件和第二塑料基板，它的机械强度很高，不是安装在这种便携式电子仪器上的液晶显示器，重量的减轻和小型化不会受到损害。并且半导体器件和液晶单元安装在第一塑料基板和第二塑料基板之间。