(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0070663

(43) 공개일자 2010년06월28일

(51) Int. Cl.

G09G 3/36 (2006.01) G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

(21) 출원번호 10-2008-0129311

(22) 출원일자 2008년12월18일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

김윤장

경기 수원시 영통구 영통동 신나무실5단지아파트

542동1704호

박경호

충남 천안시 두정동 1214번지 503호

(뒷면에 계속)

(74) 대리인

팬코리아특허법인

전체 청구항 수 : 총 27 항

(54) 액정 표시 장치

**(57) 요 약**

본 발명은 액정 표시 장치에 관한 것이다. 본 발명의 한 실시예에 따른 액정 표시 장치는 제1 기판, 상기 제1 기판 위에 형성되어 있으며 제1 게이트 신호를 전달하는 게이트선, 상기 게이트선과 교차하며, 데이터 전압을 전달하는 데이터선, 상기 제1 기판 위에 형성되어 있으며 제2 게이트 신호를 전달하는 승압 게이트선, 상기 제1 기판 위에 형성되어 있으며 제1 부화소 전극 및 제2 부화소 전극을 포함하는 화소 전극, 상기 게이트선에 연결된 제1 게이트 전극, 상기 데이터선에 연결된 제1 소스 전극, 상기 제1 부화소 전극과 연결된 제1 드레인 전극을 포함하는 제1 스위칭 소자, 상기 게이트선에 연결된 제2 게이트 전극, 상기 데이터선에 연결된 제2 소스 전극, 상기 제2 부화소 전극과 연결된 제2 드레인 전극을 포함하는 제2 스위칭 소자, 상기 제1 부화소 전극과 연결되어 있는 제1 단자를 포함하는 승압 축전기, 상기 게이트선과 연결된 제3 게이트 전극, 제3 소스 전극, 그리고 상기 승압 축전기의 제2 단자와 연결된 제3 드레인 전극을 포함하는 제3 스위칭 소자, 그리고 상기 승압 게이트선에 연결된 제4 게이트 전극, 상기 제2 부화소 전극과 연결된 제4 소스 전극, 그리고 상기 제2 단자 사이와 연결된 제4 드레인 전극을 포함하는 제4 스위칭 소자를 포함한다.

**대 표 도 - 도2**

(72) 발명자

문성재

서울 영등포구 영등포동 649번지 두산위브 아파트

103동1002호

박기범

충남 천안시 두정동 561-7번지 307호

## 특허청구의 범위

### 청구항 1

제1 기판,

상기 제1 기판 위에 형성되어 있으며 제1 게이트 신호를 전달하는 게이트선,

상기 게이트선과 교차하며, 데이터 전압을 전달하는 데이터선,

상기 제1 기판 위에 형성되어 있으며 제2 게이트 신호를 전달하는 승압 게이트선,

상기 제1 기판 위에 형성되어 있으며 제1 부화소 전극 및 제2 부화소 전극을 포함하는 화소 전극,

상기 게이트선에 연결된 제1 게이트 전극, 상기 데이터선에 연결된 제1 소스 전극, 상기 제1 부화소 전극과 연결된 제1 드레인 전극을 포함하는 제1 스위칭 소자,

상기 게이트선에 연결된 제2 게이트 전극, 상기 데이터선에 연결된 제2 소스 전극, 상기 제2 부화소 전극과 연결된 제2 드레인 전극을 포함하는 제2 스위칭 소자,

상기 제1 부화소 전극과 연결되어 있는 제1 단자를 포함하는 승압 축전기,

상기 게이트선과 연결된 제3 게이트 전극, 제3 소스 전극, 그리고 상기 승압 축전기의 제2 단자와 연결된 제3 드레인 전극을 포함하는 제3 스위칭 소자, 그리고

상기 승압 게이트선에 연결된 제4 게이트 전극, 상기 제2 부화소 전극과 연결된 제4 소스 전극, 그리고 상기 제2 단자 사이와 연결된 제4 드레인 전극을 포함하는 제4 스위칭 소자

를 포함하는 액정 표시 장치.

### 청구항 2

제1항에서,

상기 제1 게이트 신호가 게이트 온 전압(Von)일 때 상기 제2 게이트 신호는 게이트 오프 전압(Voff)이고, 상기 제2 게이트 신호가 게이트 온 전압(Von)일 때 상기 제1 게이트 신호는 게이트 오프 전압(Voff)인 액정 표시 장치.

### 청구항 3

제2항에서,

상기 제2 게이트 신호가 게이트 온 전압(Von)일 때 상기 제1 부화소 전극과 상기 제2 부화소 전극의 전압이 달라지는 액정 표시 장치.

### 청구항 4

제1항에서,

상기 기판 위에 형성되어 있는 공통 전압선을 더 포함하고, 상기 제3 소스 전극은 상기 공통 전압선으로부터 공통 전압(Vcom)을 전달받는 액정 표시 장치.

### 청구항 5

제4항에서,

상기 공통 전압선은 상기 게이트선과 상기 승압 게이트선 중 적어도 하나와 동일한 층에 위치하는 액정 표시 장치.

### 청구항 6

제5항에서,

상기 제3 소스 전극은 상기 공통 전압선과 연결 다리를 통해 연결되어 있는 액정 표시 장치.

### 청구항 7

제6항에서,

상기 연결 다리는 상기 제1 및 제2 부화소 전극과 동일한 층에 위치하는 액정 표시 장치.

### 청구항 8

제7항에서,

상기 제1 부화소 전극 및 상기 제1 드레인 전극이 연결되는 제1 접촉부와 상기 제3 소스 전극 및 상기 연결 다리가 연결되는 제2 접촉부는 상기 제1 부화소 전극을 기준으로 대칭인 액정 표시 장치.

### 청구항 9

제4항에서,

상기 공통 전압선은 상기 게이트선과 나란한 출기선, 상기 출기선으로부터 돌출한 세로부를 포함하는 액정 표시 장치.

### 청구항 10

제9항에서,

상기 세로부의 적어도 일부분은 상기 제1 부화소 전극의 둘레와 중첩하는 액정 표시 장치.

### 청구항 11

제9항에서,

상기 제1 부화소 전극의 일부는 상기 승압 게이트선과 중첩하는 액정 표시 장치.

### 청구항 12

제9항에서,

상기 공통 전압선은 상기 세로부와 연결되어 있으며 상기 제1 부화소 전극의 둘레와 중첩하는 가로부를 더 포함하는 액정 표시 장치.

### 청구항 13

제1항에서,

상기 제1 기판 위에 형성되어 있는 색필터를 더 포함하는 액정 표시 장치.

### 청구항 14

제13항에서,

상기 제1 및 제2 부화소 전극 위 및 아래 중 적어도 하나에 형성되어 있는 차광 부재를 더 포함하는 액정 표시 장치.

### 청구항 15

제13항에서,

상기 제1 기판과 마주하는 제2 기판 및 상기 제2 기판 위에 형성되어 있는 차광 부재를 더 포함하는 액정 표시 장치.

### 청구항 16

제13항에서,

상기 색필터 위에 위치하는 보호막을 더 포함하는 액정 표시 장치.

**청구항 17**

제16항에서,

상기 승압 축전기가 위치하는 곳의 상기 보호막은 제거되어 있는 액정 표시 장치.

**청구항 18**

제1항에서,

상기 게이트선, 상기 승압 게이트선, 상기 제1, 제2, 제3 및 제4 스위칭 소자, 그리고 상기 승압 축전기 중 적어도 하나는 상기 제1 부화소 전극과 상기 제2 부화소 전극 사이에 위치하는 액정 표시 장치.

**청구항 19**

제1 게이트 신호를 전달하는 게이트선,

제2 게이트 신호를 전달하는 승압 게이트선,

제1 데이터 전압을 전달하는 제1 데이터선 및 제2 데이터 전압을 전달하는 제2 데이터선, 그리고

상기 제1 및 제2 데이터선 사이에 위치하며 서로 이웃하는 제1 화소 및 제2 화소를 포함하고,

상기 제1 및 제2 화소는 각각

제1 액정 축전기 및 제1 스위칭 소자를 포함하는 제1 부화소,

제2 액정 축전기 및 제2 스위칭 소자를 포함하는 제2 부화소, 그리고

상기 제1 게이트 신호에 의해 제어되는 제3 스위칭 소자, 상기 제3 스위칭 소자와 연결되어 있고 상기 제2 게이트 신호에 의해 제어되는 제4 스위칭 소자, 그리고 상기 제3 스위칭 소자와 상기 제1 액정 축전기 사이에 연결된 승압 축전기를 포함하는 승압부

를 포함하며,

상기 제1 화소의 상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제1 데이터 전압을 상기 제1 화소의 상기 제1 액정 축전기 및 상기 제2 액정 축전기에 각각 전달하고,

상기 제2 화소의 상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제2 데이터 전압을 상기 제2 화소의 상기 제1 액정 축전기 및 상기 제2 액정 축전기에 각각 전달하는

액정 표시 장치.

**청구항 20**

제19항에서,

상기 승압 게이트선은 상기 제1 화소의 상기 제4 스위칭 소자와 연결되어 있는 제1 승압 게이트선, 그리고 상기 제2 화소의 상기 제4 스위칭 소자와 연결되어 있는 제2 승압 게이트선을 포함하는 액정 표시 장치.

**청구항 21**

제20항에서,

상기 제1 화소 및 상기 제2 화소는 상기 게이트선을 기준으로 서로 대칭인 액정 표시 장치.

**청구항 22**

제21항에서,

상기 제1 액정 축전기는 상기 제1 스위칭 소자와 연결된 제1 부화소전극을 포함하고, 상기 제2 액정 축전기는 상기 제2 스위칭 소자와 연결된 제2 부화소 전극을 포함하는 액정 표시 장치.

**청구항 23**

제22항에서,

상기 게이트선, 상기 승압 게이트선, 상기 제1, 제2, 제3 및 제4 스위칭 소자, 그리고 상기 승압 축전기 중 적어도 하나는 상기 제1 화소의 상기 제1 부화소 전극과 상기 제2 화소의 상기 제1 부화소 전극 사이에 위치하는 액정 표시 장치.

#### 청구항 24

제19항에서,

제3 데이터 전압을 전달하는 제3 데이터선 및 제4 데이터 전압을 전달하는 제4 데이터선, 그리고

상기 제3 및 제4 데이터선 사이에 위치하며 서로 이웃하는 제3 화소 및 제4 화소를 더 포함하고,

상기 제3 및 제4 화소는 각각

제3 액정 축전기 및 제5스위칭 소자를 포함하는 제3 부화소,

제4 액정 축전기 및 제6스위칭 소자를 포함하는 제4 부화소, 그리고

상기 제1 게이트 신호에 의해 제어되는 제7 스위칭 소자, 상기 제7 스위칭 소자와 연결되어 있고 상기 제2 게이트 신호에 의해 제어되는 제8 스위칭 소자, 그리고 상기 제7 스위칭 소자와 상기 제3 액정 축전기 사이에 연결된 제1 승압 축전기를 포함하는 제1 승압부

를 포함하며,

상기 제3 화소의 상기 제5 스위칭 소자 및 상기 제6 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제3 데이터 전압을 상기 제3 화소의 상기 제3 액정 축전기 및 상기 제4 액정 축전기에 각각 전달하고,

상기 제4 화소의 상기 제5 스위칭 소자 및 상기 제6 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제4 데이터 전압을 상기 제4 화소의 상기 제3 액정 축전기 및 상기 제4 액정 축전기에 각각 전달하는

액정 표시 장치.

#### 청구항 25

제24항에서,

상기 제1, 제2, 제5 및 제6 스위칭 소자는 각각 제1, 제2, 제3 및 제4 소스 전극을 포함하고,

상기 제1, 제2, 제3 및 제4 소스 전극은 각각 개구부를 포함하며,

상기 제1 및 제2 화소 각각에 있어서 상기 제1 및 제2 소스 전극의 개구부의 방향은 서로 반대이고,

상기 제3 및 제4 화소 각각에 있어서 상기 제3 및 제4 소스 전극의 개구부의 방향은 서로 반대인

액정 표시 장치.

#### 청구항 26

제25항에서,

상기 제1 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제2 화소의 상기 제1 소스 전극의 개구부의 방향은 서로 반대이고,

상기 제3 화소의 상기 제3 소스 전극의 개구부의 방향과 상기 제4 화소의 상기 제3 소스 전극의 개구부의 방향은 서로 반대인

액정 표시 장치.

#### 청구항 27

제26에서,

상기 제1 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제3 화소의 상기 제3 소스 전극의 개구부의 방향

은 서로 반대이고,

상기 제2 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제4 화소의 상기 제3 소스 전극의 개구부의 방향은 서로 반대인

액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001]

본 발명은 액정 표시 장치에 관한 것이다.

#### 배경 기술

[0002]

액정 표시 장치는 현재 가장 널리 사용되고 있는 평판 표시 장치 중 하나로서, 화소 전극과 공통 전극 등 전기장 생성 전극(field generating electrode)이 형성되어 있는 두 장의 표시판과 그 사이에 들어 있는 액정층을 포함한다. 액정 표시 장치는 전기장 생성 전극에 전압을 인가하여 액정층에 전기장을 생성하고 이를 통하여 액정층의 액정 분자들의 방향을 결정하고 입사광의 편광을 제어함으로써 영상을 표시한다.

[0003]

액정 표시 장치 중에서도 전기장이 인가되지 않은 상태에서 액정 분자의 장축을 상하 표시판에 대하여 수직을 이루도록 배열한 수직 배향 방식(vertically aligned mode) 액정 표시 장치가 대비비가 크고 얕은 기준 시야각 구현이 용이하여 각광받고 있다.

[0004]

이러한 수직 배향 모드 액정 표시 장치에서 광시야각을 구현하기 위하여 하나의 화소에 액정의 배향 방향이 다른 복수의 도메인(domain)을 형성할 수 있다.

[0005]

이와 같이 하나의 화소에 복수의 도메인을 형성하는 수단으로 전기장 생성 전극에 미세 슬릿 등의 절개부를 형성하거나 전기장 생성 전극 위에 돌기를 형성하는 등의 방법을 사용한다. 이 방법은 절개부 또는 돌기의 가장자리(edge)와 이와 마주하는 전기장 생성 전극 사이에 형성되는 프린지 필드(fringe field)에 의해 액정이 프린지 필드에 수직하는 방향으로 배향됨으로써 복수의 도메인을 형성할 수 있다.

[0006]

하나의 화소에 복수의 도메인을 형성하는 다른 수단으로 배향막에 광을 조사하여 액정의 배향 방향 및 배향 각도를 제어하는 광 배향 방법이 있다.

[0007]

한편 수직 배향 방식의 액정 표시 장치는 전면 시인성에 비하여 측면 시인성이 떨어질 수 있는데, 이를 해결하기 위하여 하나의 화소를 두 개의 부화소로 분할하고 두 개의 부화소의 전압을 달리하는 방법이 제시되었다.

[0008]

이를 위한 여러 가지 방법 중 하나의 데이터 전압을 두 부화소에 인가한 후 승압 축전기를 통해 한 부화소의 충전 전압을 내리고 다른 부화소의 충전 전압을 올림으로써 데이터선이나 게이트선의 증가로 인한 개구율의 감소 없이 두 부화소의 전압을 달리하여 시인성을 향상할 수 있다. 또한 두 부화소의 용량성 결합으로 인한 휘도 감소의 문제도 없게 된다.

#### 발명의 내용

##### 해결 하고자 하는 과제

[0009]

본 발명이 이루고자 하는 기술적 과제는 휘도 감소나 개구율 감소의 문제 없이 우수한 시인성을 가지며 개구율 및 투과율이 극대화된 액정 표시 장치를 제공하는 것이다.

[0010]

본 발명이 이루고자 하는 또 다른 기술적 과제는 액정 표시 장치의 구동시 충전 마진을 높이는 것이다.

[0011]

본 발명이 이루고자 하는 또 다른 기술적 과제는 게이트선의 수를 줄이며 시야각에 따른 표시 특성의 차이를 없애는 것이다.

[0012]

본 발명이 이루고자 하는 또 다른 기술적 과제는 액정 표시 장치의 박막들의 정렬에 편차가 발생해도 표시 특성의 열화를 방지하는 것이다.

## 과제 해결수단

[0013]

본 발명의 한 실시예에 따른 액정 표시 장치는 제1 기판, 상기 제1 기판 위에 형성되어 있으며 제1 게이트 신호를 전달하는 게이트선, 상기 게이트선과 교차하며, 데이터 전압을 전달하는 데이터선, 상기 제1 기판 위에 형성되어 있으며 제2 게이트 신호를 전달하는 승압 게이트선, 상기 제1 기판 위에 형성되어 있으며 제1 부화소 전극 및 제2 부화소 전극을 포함하는 화소 전극, 상기 게이트선에 연결된 제1 게이트 전극, 상기 데이터선에 연결된 제1 소스 전극, 상기 제1 부화소 전극과 연결된 제1 드레인 전극을 포함하는 제1 스위칭 소자, 상기 게이트선에 연결된 제2 게이트 전극, 상기 데이터선에 연결된 제2 소스 전극, 상기 제2 부화소 전극과 연결된 제2 드레인 전극을 포함하는 제2 스위칭 소자, 상기 제1 부화소 전극과 연결되어 있는 제1 단자를 포함하는 승압 축전기, 상기 게이트선과 연결된 제3 게이트 전극, 제3 소스 전극, 그리고 상기 승압 축전기의 제2 단자와 연결된 제3 드레인 전극을 포함하는 제3 스위칭 소자, 그리고 상기 승압 게이트선에 연결된 제4 게이트 전극, 상기 제2 부화소 전극과 연결된 제4 소스 전극, 그리고 상기 제2 단자 사이와 연결된 제4 드레인 전극을 포함하는 제4 스위칭 소자를 포함한다.

[0014]

상기 제1 게이트 신호가 게이트 온 전압(Von)일 때 상기 제2 게이트 신호는 게이트 오프 전압(Voff)이고, 상기 제2 게이트 신호가 게이트 온 전압(Von)일 때 상기 제1 게이트 신호는 게이트 오프 전압(Voff)일 수 있다.

[0015]

상기 제2 게이트 신호가 게이트 온 전압(Von)일 때 상기 제1 부화소 전극과 상기 제2 부화소 전극의 전압이 달라질 수 있다..

[0016]

상기 기판 위에 형성되어 있는 공통 전압선을 더 포함하고, 상기 제3 소스 전극은 상기 공통 전압선으로부터 공통 전압(Vcom)을 전달받을 수 있다.

[0017]

상기 공통 전압선은 상기 게이트선과 상기 승압 게이트선 중 적어도 하나와 동일한 층에 위치할 수 있다.

[0018]

상기 제3 소스 전극은 상기 공통 전압선과 연결 다리를 통해 연결되어 있을 수 있다.

[0019]

상기 연결 다리는 상기 제1 및 제2 부화소 전극과 동일한 층에 위치할 수 있다.

[0020]

상기 제1 부화소 전극 및 상기 제1 드레인 전극이 연결되는 제1 접촉부와 상기 제3 소스 전극 및 상기 연결 다리가 연결되는 제2 접촉부는 상기 제1 부화소 전극을 기준으로 대칭일 수 있다.

[0021]

상기 공통 전압선은 상기 게이트선과 나란한 줄기선, 상기 줄기선으로부터 돌출한 세로부를 포함할 수 있다.

[0022]

상기 세로부의 적어도 일부분은 상기 제1 부화소 전극의 둘레와 중첩할 수 있다.

[0023]

상기 제1 부화소 전극의 일부는 상기 승압 게이트선과 중첩할 수 있다.

[0024]

상기 공통 전압선은 상기 세로부와 연결되어 있으며 상기 제1 부화소 전극의 둘레와 중첩하는 가로부를 더 포함할 수 있다.

[0025]

상기 제1 기판 위에 형성되어 있는 색필터를 더 포함할 수 있다.

[0026]

상기 제1 및 제2 부화소 전극 위 및 아래 중 적어도 하나에 형성되어 있는 차광 부재를 더 포함할 수 있다.

[0027]

상기 제1 기판과 마주하는 제2 기판 및 상기 제2 기판 위에 형성되어 있는 차광 부재를 더 포함할 수 있다.

[0028]

상기 색필터 위에 위치하는 보호막을 더 포함할 수 있다.

[0029]

상기 승압 축전기가 위치하는 곳의 상기 보호막은 제거되어 있을 수 있다.

[0030]

상기 게이트선, 상기 승압 게이트선, 상기 제1, 제2, 제3 및 제4 스위칭 소자, 그리고 상기 승압 축전기 중 적어도 하나는 상기 제1 부화소 전극과 상기 제2 부화소 전극 사이에 위치할 수 있다.

[0031]

본 발명의 한 실시예에 따른 액정 표시 장치는 제1 게이트 신호를 전달하는 게이트선, 제2 게이트 신호를 전달하는 승압 게이트선, 제1 데이터 전압을 전달하는 제1 데이터선 및 제2 데이터 전압을 전달하는 제2 데이터선, 그리고 상기 제1 및 제2 데이터선 사이에 위치하며 서로 이웃하는 제1 화소 및 제2 화소를 포함하고, 상기 제1 및 제2 화소는 각각 제1 액정 축전기 및 제1 스위칭 소자를 포함하는 제1 부화소, 제2 액정 축전기 및 제2 스위칭 소자를 포함하는 제2 부화소, 그리고 상기 제1 게이트 신호에 의해 제어되는 제3 스위칭 소자, 상기 제3 스위칭 소자와 연결되어 있고 상기 제2 게이트 신호에 의해 제어되는 제4 스위칭 소자, 그리고 상기 제3 스위칭 소자와 상기 제1 액정 축전기 사이에 연결된 승압 축전기를 포함하는 승압부를 포함하며, 상기 제1 화소의 상기

제1 스위칭 소자 및 상기 제2 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제1 데이터 전압을 상기 제1 화소의 상기 제1 액정 축전기 및 상기 제2 액정 축전기에 각각 전달하고, 상기 제2 화소의 상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제2 데이터 전압을 상기 제2 화소의 상기 제1 액정 축전기 및 상기 제2 액정 축전기에 각각 전달한다.

[0032] 상기 승압 게이트선은 상기 제1 화소의 상기 제4 스위칭 소자와 연결되어 있는 제1 승압 게이트선, 그리고 상기 제2 화소의 상기 제4 스위칭 소자와 연결되어 있는 제2 승압 게이트선을 포함할 수 있다.

[0033] 상기 제1 화소 및 상기 제2 화소는 상기 게이트선을 기준으로 서로 대칭일 수 있다.

[0034] 상기 제1 액정 축전기는 상기 제1 스위칭 소자와 연결된 제1 부화소전극을 포함하고, 상기 제2 액정 축전기는 상기 제2 스위칭 소자와 연결된 제2 부화소 전극을 포함할 수 있다.

[0035] 상기 게이트선, 상기 승압 게이트선, 상기 제1, 제2, 제3 및 제4 스위칭 소자, 그리고 상기 승압 축전기 중 적어도 하나는 상기 제1 화소의 상기 제1 부화소 전극과 상기 제2 화소의 상기 제1 부화소 전극 사이에 위치할 수 있다.

[0036] 제3 데이터 전압을 전달하는 제3 데이터선 및 제4 데이터 전압을 전달하는 제4 데이터선, 그리고 상기 제3 및 제4 데이터선 사이에 위치하며 서로 이웃하는 제3 화소 및 제4 화소를 더 포함할 수 있고, 상기 제3 및 제4 화소는 각각 제3 액정 축전기 및 제5 스위칭 소자를 포함하는 제3 부화소, 제4 액정 축전기 및 제6 스위칭 소자를 포함하는 제4 부화소, 그리고 상기 제1 게이트 신호에 의해 제어되는 제7 스위칭 소자, 상기 제7 스위칭 소자와 연결되어 있고 상기 제2 게이트 신호에 의해 제어되는 제8 스위칭 소자, 그리고 상기 제7 스위칭 소자와 상기 제3 액정 축전기 사이에 연결된 제1 승압 축전기를 포함하는 제1 승압부를 포함하며, 상기 제3 화소의 상기 제5 스위칭 소자 및 상기 제6 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제3 데이터 전압을 상기 제3 화소의 상기 제3 액정 축전기 및 상기 제4 액정 축전기에 각각 전달하고, 상기 제4 화소의 상기 제5 스위칭 소자 및 상기 제6 스위칭 소자는 상기 제1 게이트 신호에 응답하여 상기 제4 데이터 전압을 상기 제4 화소의 상기 제3 액정 축전기 및 상기 제4 액정 축전기에 각각 전달할 수 있다.

[0037] 상기 제1, 제2, 제5 및 제6 스위칭 소자는 각각 제1, 제2, 제3 및 제4 소스 전극을 포함하고, 상기 제1, 제2, 제3 및 제4 소스 전극은 각각 개구부를 포함하며, 상기 제1 및 제2 화소 각각에 있어서 상기 제1 및 제2 소스 전극의 개구부의 방향은 서로 반대이고, 상기 제3 및 제4 화소 각각에 있어서 상기 제3 및 제4 소스 전극의 개구부의 방향은 서로 반대일 수 있다.

[0038] 상기 제1 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제2 화소의 상기 제1 소스 전극의 개구부의 방향은 서로 반대이고, 상기 제3 화소의 상기 제3 소스 전극의 개구부의 방향과 상기 제4 화소의 상기 제3 소스 전극의 개구부의 방향은 서로 반대일 수 있다.

[0039] 상기 제1 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제3 화소의 상기 제3 소스 전극의 개구부의 방향은 서로 반대이고, 상기 제2 화소의 상기 제1 소스 전극의 개구부의 방향과 상기 제4 화소의 상기 제3 소스 전극의 개구부의 방향은 서로 반대일 수 있다.

## 효과

[0040] 본 발명의 실시예에 따르면 승압 축전기 등을 사용하여 제1 및 제2 부화소의 충전 전압에 차이가 생기게 하여 측면 시인성 등 표시 특성을 향상할 수 있고, 액정 표시 장치의 투과율을 높일 수 있다.

[0041] 또한 본 발명의 실시예에 따르면 열 방향으로 이웃하는 화소의 게이트선을 공유하여 액정 표시 장치의 고속 구동과 마진을 확보할 수 있고, 시야각에 따른 개구율을 높일 수 있다.

[0042] 또한 각 부화소의 박막 트랜지스터의 방향을 반대로 배치하여 킥백 전압의 편차에 의한 표시 불량을 줄일 수 있다.

## 발명의 실시를 위한 구체적인 내용

[0043] 그러면 첨부한 도면을 참고로 하여 본 발명의 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다.

[0044] 도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유

사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판등의 부분이 다른 부분 "위에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우 뿐만 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

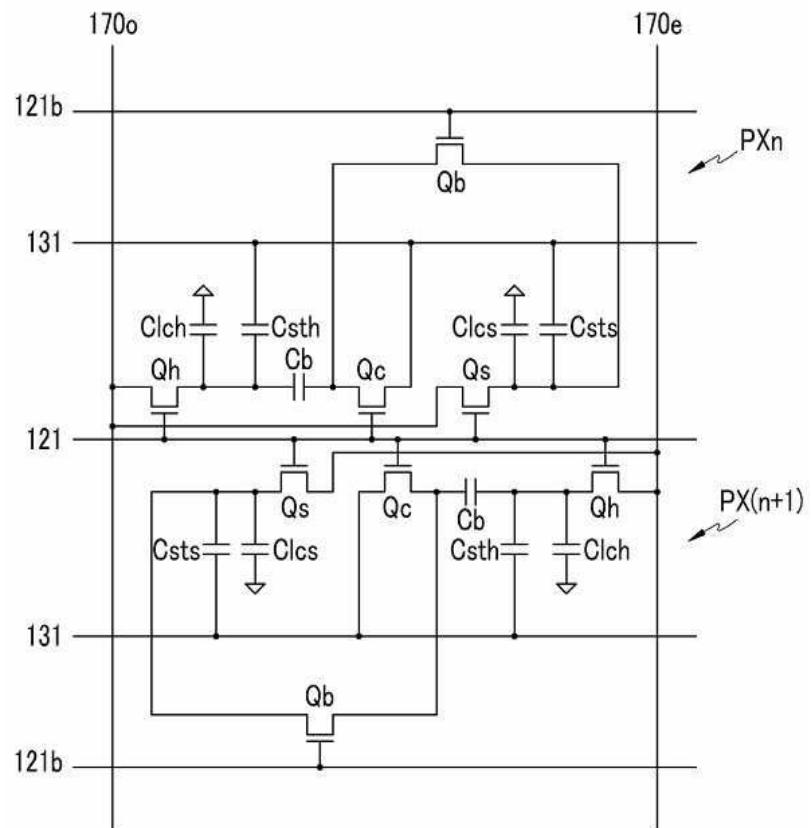

[0045] 그러면 도 1 및 도 2를 참고하여 본 발명에 따른 액정 표시 장치에 대하여 설명한다.

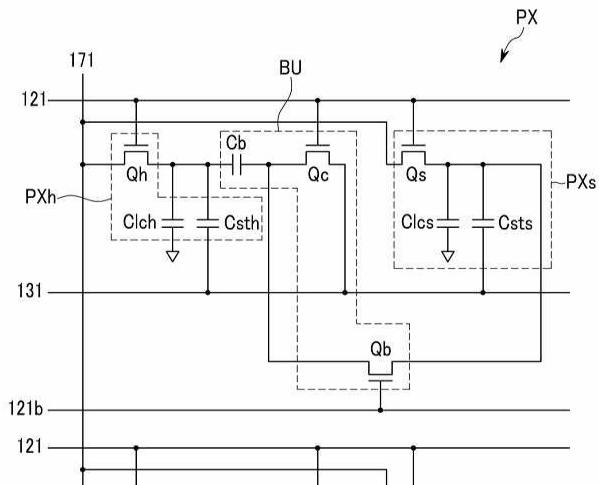

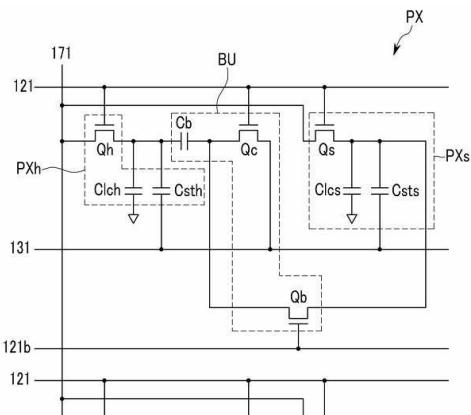

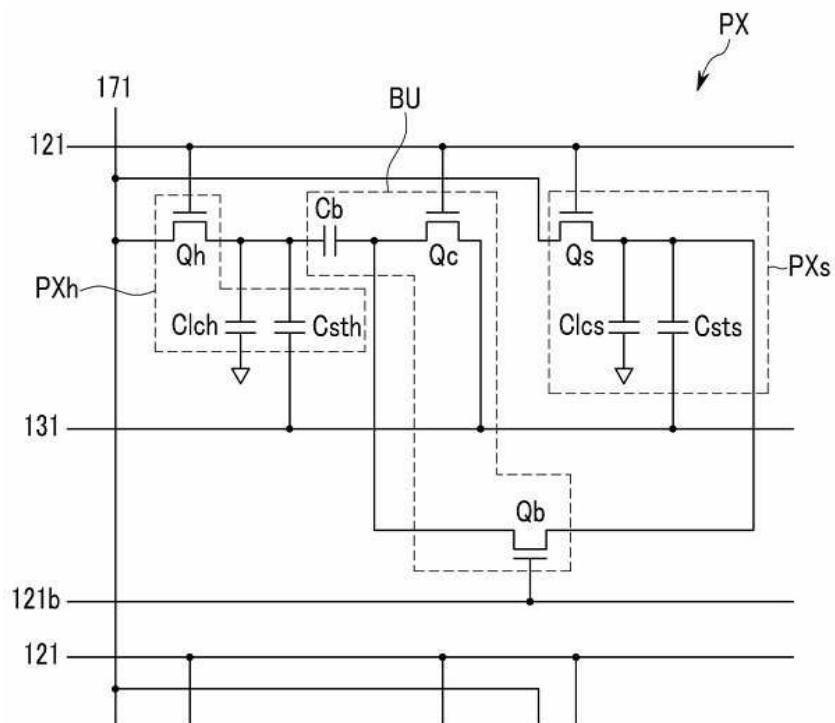

[0046] 도 1은 본 발명의 한 실시예에 따른 액정 표시 장치의 한 화소에 대한 등가 회로도이고, 도 2는 본 발명의 한 실시예에 따른 액정 표시 장치의 한 화소에 대한 등가 회로도이다.

[0047] 도 1 및 도2를 참고하면, 본 실시예에 따른 액정 표시 장치는 복수의 게이트선(121), 복수의 승압 게이트선(121b), 복수의 데이터선(171) 및 복수의 공통 전압선(131)을 포함하는 신호선과 이에 연결된 복수의 화소(PX)를 포함한다. 액정 표시 장치를 구조적으로 보면 서로 마주하는 하부 표시판(100) 및 상부 표시판(200)과 그 사이에 들어 있는 액정층(3)을 포함한다.

[0048] 신호선(121, 121b, 131, 171)은 모두 하부 표시판(100)에 위치한다. 게이트선(121) 및 승압 게이트선(121b)은 게이트 신호를 전달하고, 데이터선(171)은 데이터 신호를 전달하며, 공통 전압선(131)에는 공통 전압(Vcom) 따위의 정해진 전압이 인가된다.

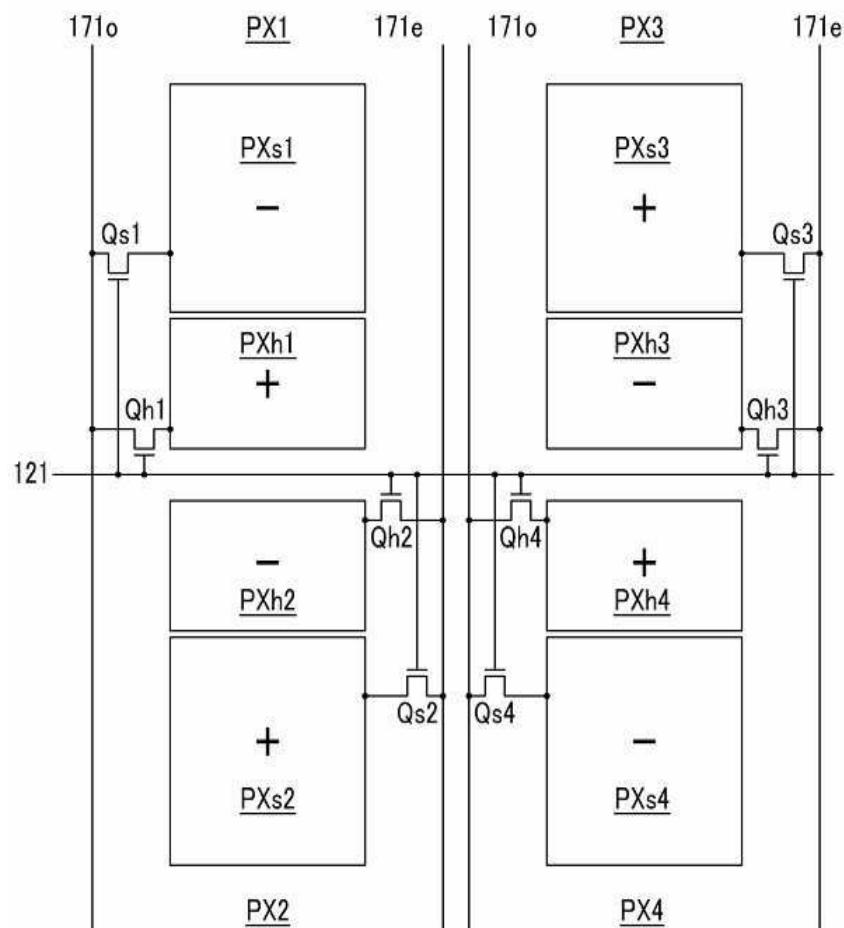

[0049] 도 2를 참고하면, 각 화소(PX)는 제1 및 제2 부화소(PX<sub>h</sub>, PX<sub>s</sub>) 및 승압부(BU)를 포함한다. 제1/제2 부화소(PX<sub>h</sub>/PX<sub>s</sub>)는 제1/제2 스위칭 소자(Q<sub>h</sub>/Q<sub>s</sub>)와 제1/제2 액정 축전기(C1ch/C1cs) 및 제1/제2 유지 축전기(storage capacitor)(Cst<sub>h</sub>/Cst<sub>s</sub>)를 포함하며, 승압부(BU)는 제3 스위칭 소자(Q<sub>c</sub>)와 제4 스위칭 소자(Q<sub>b</sub>) 및 승압 축전기(C<sub>b</sub>)를 포함한다.

[0050] 제1 내지 제4 스위칭 소자(Q<sub>h</sub>, Q<sub>s</sub>, Q<sub>c</sub>, Q<sub>b</sub>)는 하부 표시판(100)에 구비되어 있는 박막 트랜지스터 등의 삼단자 소자이다.

[0051] 제1/제2 스위칭 소자(Q<sub>h</sub>/Q<sub>s</sub>)의 제어 단자는 게이트선(121)과 연결되어 있고, 입력 단자는 데이터선(171)과 연결되어 있으며, 출력 단자는 제1/제2 액정 축전기(C1ch/C1cs) 및 제1/제2 유지 축전기(Cst<sub>h</sub>/Cst<sub>s</sub>)와 연결되어 있다.

[0052] 제3 스위칭 소자(Q<sub>c</sub>)의 제어 단자는 게이트선(121)과 연결되어 있고, 입력 단자는 공통 전압선(131)과 연결되어 있으며, 출력 단자는 제4 스위칭 소자(Q<sub>b</sub>) 및 승압 축전기(C<sub>b</sub>)와 연결되어 있다.

[0053] 제4 스위칭 소자(Q<sub>b</sub>)의 제어 단자는 승압 게이트선(121b)과 연결되어 있고, 입력 단자는 제2 스위칭 소자(Q<sub>s</sub>)의 출력 단자, 제2 액정 축전기(C1cs) 및 제2 유지 축전기(Cst<sub>s</sub>)와 연결되어 있으며, 출력 단자는 제3 스위칭 소자(Q<sub>c</sub>)의 출력 단자 및 승압 축전기(C<sub>b</sub>)와 연결되어 있다.

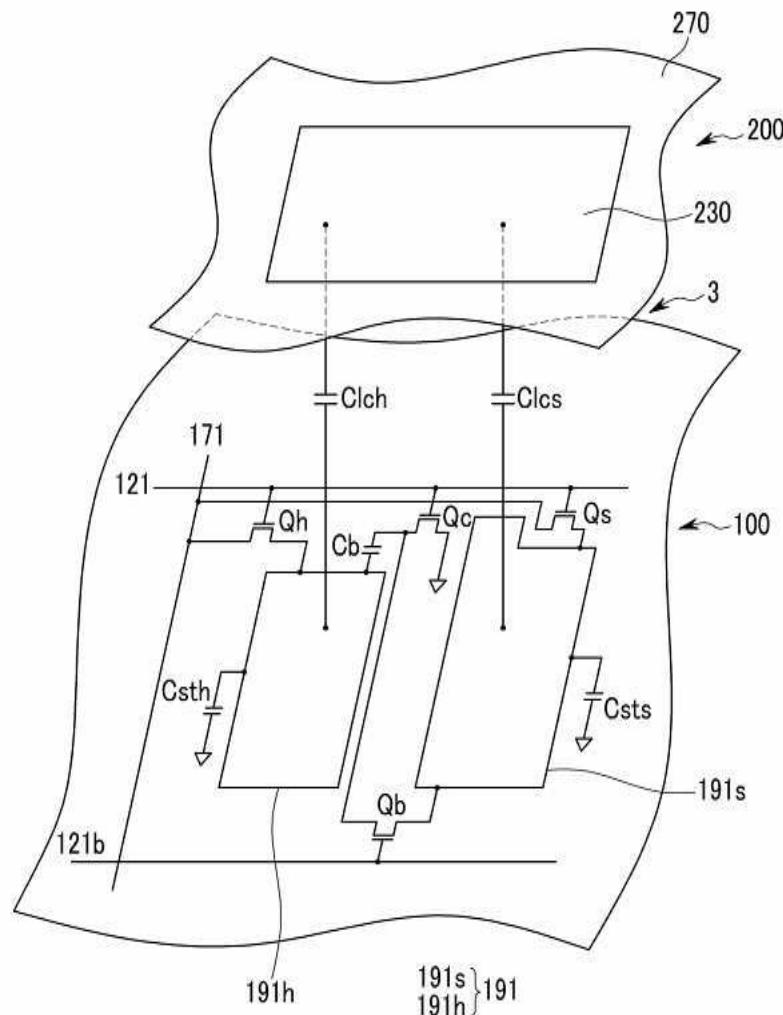

[0054] 도 1을 참고하면, 제1/제2 액정 축전기(C1ch/C1cs)는 하부 표시판(100)의 제1/제2 부화소 전극(191h/191s)과 상부 표시판(200)의 공통 전극(270)을 두 단자로 하고, 두 단자 사이의 액정층(3)은 유전체로서 기능한다. 제1 및 제2 부화소 전극(191h, 191s)은 서로 분리되어 있으며 하나의 화소 전극(191)을 이룬다. 공통 전극(270)은 상부 표시판(200)의 전면에 형성되어 있고 공통 전압(Vcom)을 인가 받는다. 액정층(3)은 음의 유전율 이방성을 가지며, 액정층(3)의 액정 분자는 전기장이 없는 상태에서 그 장축이 두 표시판의 표면에 대하여 수직을 이루도록 배향되어 있을 수 있다. 도 1에서와는 달리 공통 전극(270)이 하부 표시판(100)에 구비되는 경우도 있으며 이때에는 두 전극(191, 270) 중 적어도 하나가 선형 또는 막대형으로 만들어질 수 있다.

[0055] 제1/제2 액정축전기(C1ch/C1cs)의 보조적인 역할을 하는 제1/제2 유지 축전기(Cst<sub>h</sub>/Cst<sub>s</sub>)는 제1/제2 부화소 전극(191h/191s)과 공통 전압선(SL)이 절연체를 사이에 두고 중첩되어 이루어진다. 그러나 제1 및 제2 유지 축전기(Cst<sub>h</sub>, Cst<sub>s</sub>)는 제1 및 제2 부화소 전극(191h, 191s)이 절연체를 매개로 바로 위의 전단 게이트선과 중첩되어 이루어질 수 있다. 유지 축전기(Cst<sub>h</sub>, Cst<sub>s</sub>)는 생략할 수 있다.

[0056] 승압 축전기(C<sub>b</sub>)는 하부 표시판(100)의 제1 부화소 전극(191h)을 한 단자로 하고 제3 스위칭 소자(Q<sub>c</sub>)의 출력 단자 및 제4 스위칭 소자(Q<sub>b</sub>)의 출력 단자를 다른 한 단자로 하여 절연체를 사이에 두고 중첩하여 이루어진다.

[0057] 한편, 색 표시를 구현하기 위해서는 각 화소(PX)가 기본색(primary color) 중 하나를 고유하게 표시하거나(공간 분할) 각 화소가 시간에 따라 번갈아 기본색을 표시하게(시간 분할) 하여 이를 기본색의 공간적, 시간적 합으로 원하는 색상이 인식되도록 한다. 기본색의 예로는 적색, 녹색, 청색 등 삼원색을 들 수 있다. 도 1은 공간 분할의 한 예로서 각 화소(PX)가 상부 표시판(200)의 영역에 기본색 중 하나를 나타내는 색필터(230)를 구비함을 보여주고 있다. 도 1과는 달리 색필터(230)는 하부 표시판(100)의 부화소 전극(191h, 191s) 위 또는 아래에 형

성할 수도 있다.

[0058] 그러면 본 발명의 한 실시예에 따른 액정 표시 장치의 동작에 대하여 도 1 및 도 2를 참고하여 설명한다.

[0059] 우선 데이터선(171)에 공통 전압(Vcom)을 기준으로 극성이 양(+)인 데이터 전압이 인가되는 경우를 예로 하여 설명한다.

[0060] 게이트선(121)에 게이트 온 전압(Von)이 인가되면 이에 연결된 제1, 제2 및 제3 박막 트랜지스터(Qh, Qs, Qc)가 턴 온된다.

[0061] 이에 따라 데이터선(171)의 데이터 전압은 턴 온된 제1 및 제2 박막 트랜지스터(Qh, Qs)를 통하여 제1 및 제2 부화소 전극(191h, 191s)에 인가된다. 그러므로 제1 및 제2 부화소 전극(191h, 191s)의 전압은 서로 동일하다. 제1/제2 액정 축전기(Clch/Clcs)는 공통 전극(270)의 공통 전압(Vcom)과 제1/제2 부화소 전극의 전압 차이만큼 충전되므로 제1 액정 축전기(Clch)의 양단 전압과 제2 액정 축전기(Clcs)의 양단 전압도 서로 동일하다. 또한 제1 및 제2 부화소 전극(191h, 191s)에는 양(+)의 전하가 모인다.

[0062] 한편 공통 전압선(131)의 공통 전압(Vcom)은 제3 박막 트랜지스터(Qc)를 통하여 승압 축전기(Cb)의 제1 단자에 인가되어 제1 부화소 전극(191h)의 전압이 승압 축전기(Cb)의 제2 단자에 인가된다. 그러면 승압 축전기(Cb)는 제1 부화소 전극(191h)의 전압과 공통 전압(Vcom)의 차이만큼 충전되고, 제3 박막 트랜지스터(Qc)와 승압 축전기(Cb)의 접점, 즉 승압 축전기(Cb)의 제2 단자에는 음(-)의 전하가 모인다.

[0063] 그런 후 게이트선(121)에 게이트 오프 전압(Voff)이 인가되고 승압 게이트선(121b)에 게이트 온 전압(Von)이 인가되면, 게이트선(121)에 연결된 제1, 제2 및 제3 박막 트랜지스터(Qh, Qs, Qc)는 턴 오프되고, 승압 게이트선(121b)에 연결된 제4 박막 트랜지스터(Qb)가 턴 온된다.

[0064] 제1, 제2 및 제3 박막 트랜지스터(Qh, Qs, Qc)가 턴 오프됨에 따라 제1 및 제2 부화소 전극(191h, 191s), 그리고 승압 축전기(Cb)의 제2 단자는 고립(floating) 상태가 되고, 제4 박막 트랜지스터(Qb)가 턴 온됨에 따라 제2 부화소 전극(191s)과 승압 축전기(Cb)의 제2 단자는 서로 연결된다. 그러면 제2 부화소 전극(191s)에 모인 양(+)의 전하와 승압 축전기(Cb)의 제2 단자에 모여 있던 음(-)의 전하가 서로 섞이게 된다. 이에 따라 제2 부화소 전극(191s)의 전압은 낮아지고 승압 축전기(Cb)의 제2 단자의 전압이 상승한다. 승압 축전기(Cb)의 제2 단자의 전압이 올라가면 고립 상태에 있는 제1 부화소 전극(191h)의 전압도 동반 상승한다. 따라서 제1 액정 축전기(Clch)의 양단의 전압차가 커지게 된다. 반면 제2 부화소 전극(191s)의 전압은 하강하므로 제2 액정 축전기(Clcs) 양단의 전압도 하강한다.

[0065] 제2 부화소 전극(191s)의 면적이 제1 부화소 전극(191h)의 면적보다 큰 경우 제2 액정 축전기(Clcs)의 정전 용량이 제1 액정 축전기(Clch)의 정전 용량보다 크므로 제2 부화소 전극(191s)의 전압 강하량보다 제1 부화소 전극(191h)의 전압 상승량이 더 크다.

[0066] 이와는 반대로 데이터선(171)에 공통 전압(Vcom)을 기준으로 극성이 음(-)인 데이터 전압이 인가되는 경우는 축전기(Clch, Clcs, Csth, Csts, Cb)의 양단에 모이는 전하의 극성이 앞의 설명과 반대가 된다. 승압 게이트선(121b)에 게이트 온 전압(Von)이 인가되어 제4 박막 트랜지스터(Qb)가 턴 온되면 음(-)인 제2 부화소 전극(191s)의 전압이 상승하여 공통 전압(Vcom)과의 차이가 작아지고 제2 액정 축전기(Clcs)의 충전 전압은 하강하게 된다. 동시에 승압 축전기(Cb)의 제2 단자의 전압이 하강하게 되어 제1 부화소 전극(191h)의 전압도 동반 하강하여 공통 전압(Vcom)과의 차이가 더욱 커지게 된다. 따라서 제1 액정 축전기(Clch)의 충전 전압은 상승한다.

[0067] 이와 같이 본 실시예에 따르면 데이터 전압의 극성에 상관없이 제1 액정 축전기(Clch)의 충전 전압을 제2 액정 축전기(Clcs)의 충전 전압보다 항상 높게 할 수 있다.

[0068] 따라서 전체적인 휘도 및 투과율의 감소 없이 제1 및 제2 액정 축전기(Clch, Clcs)의 충전 전압을 다르게 하여 두 부화소(PXh, PXs)의 휘도를 다르게 할 수 있다. 제1 및 제2 액정 축전기(Clch, Clcs)의 충전 전압을 적절하게 맞추면 측면에서 바라보는 영상이 정면에서 바라보는 영상에 최대한 가깝게 할 수 있다. 즉, 측면 감마 곡선을 정면 감마 곡선에 최대한 가깝게 할 수 있으며, 측면 시인성을 향상할 수 있고 투과율을 높일 수 있다.

[0069] 또한 승압 게이트선(121b)에 게이트 온 전압(Von)이 인가될 때마다 제3 박막 트랜지스터(Qc)에 의해 승압 축전기(Cb)의 제2 단자의 전압이 공통 전압(Vcom)으로 갱신(refresh)되므로 전 프레임(frame)에 의한 잔상을 없앨 수 있다.

- [0070] 또한 제4 스위칭 소자(Qb)를 제어하기 위한 게이트 신호는 게이트선(121)과는 별도로 구동되는 승압 게이트선(121b)을 통해 인가되기 때문에 다음 화소(PX) 행의 액정 축전기(Clch, Clcs)의 선 충전이 가능할 수 있다.

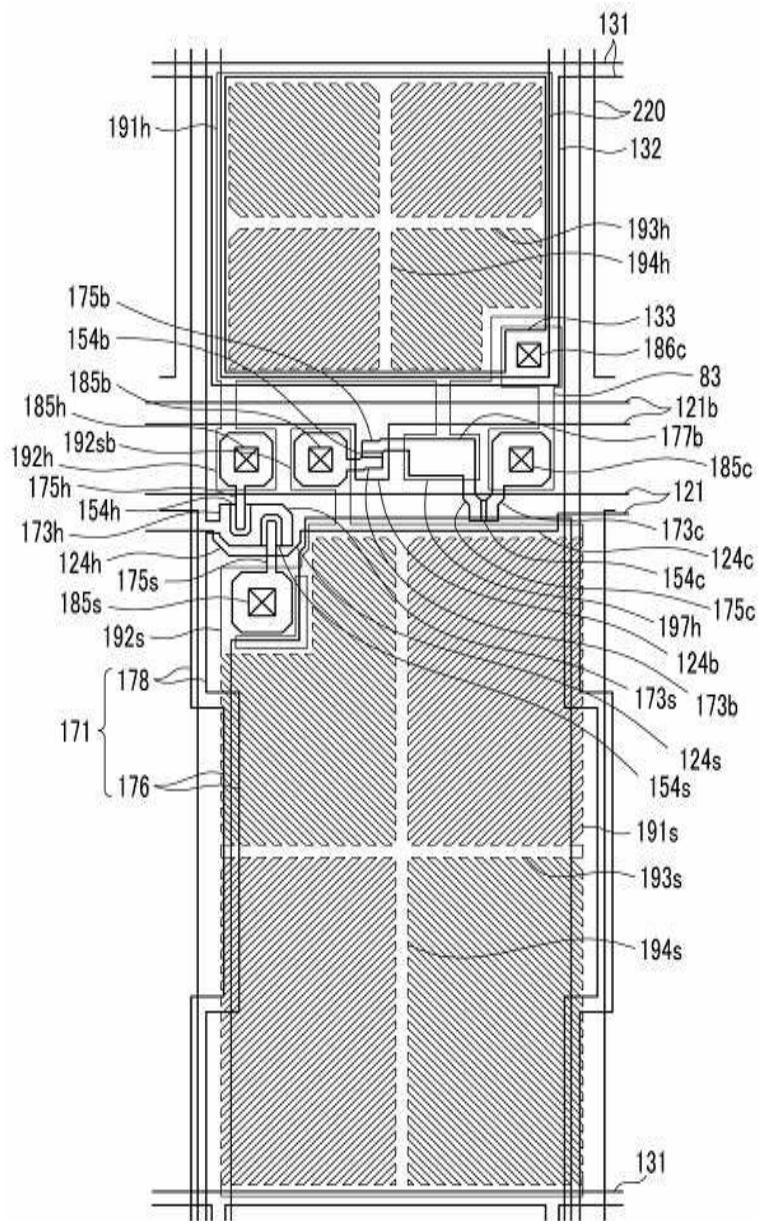

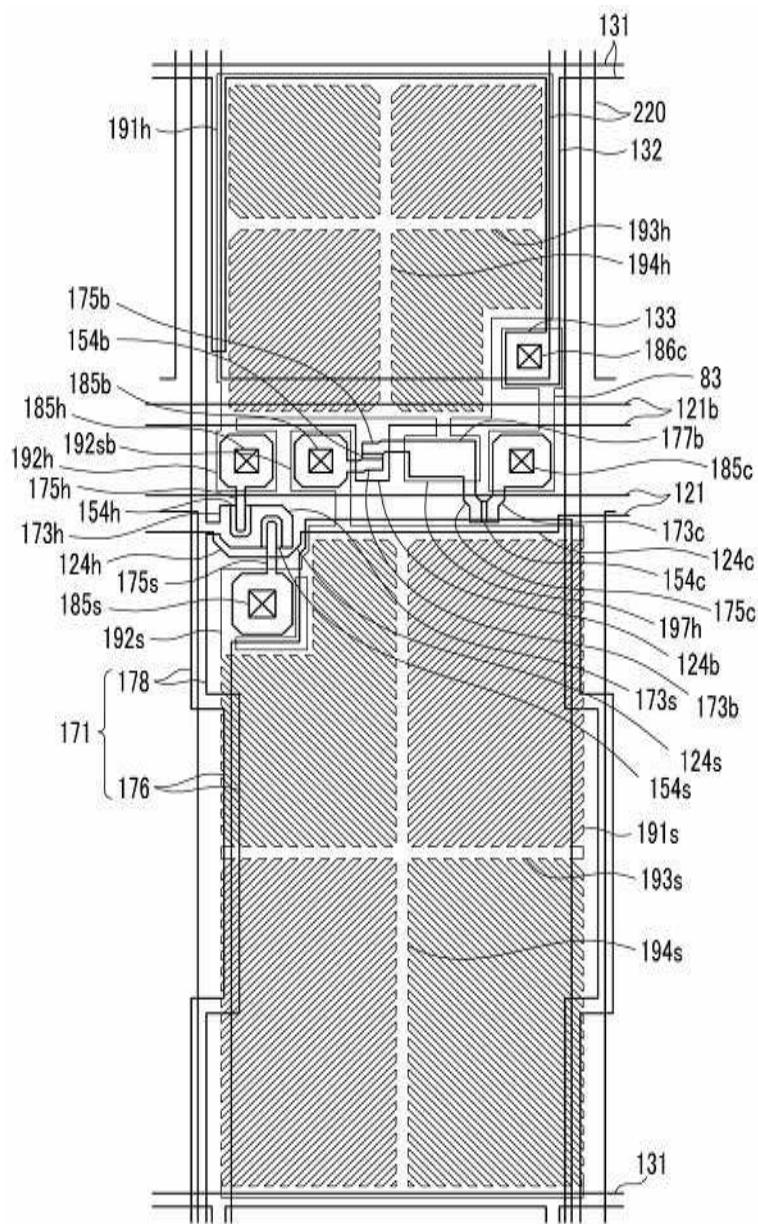

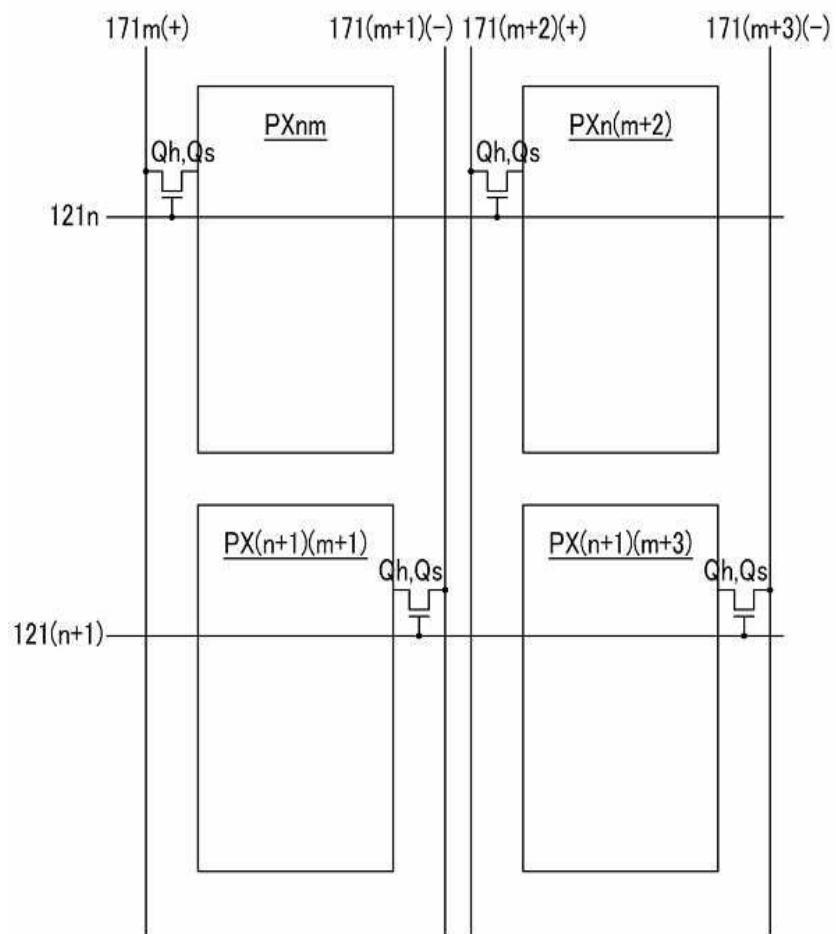

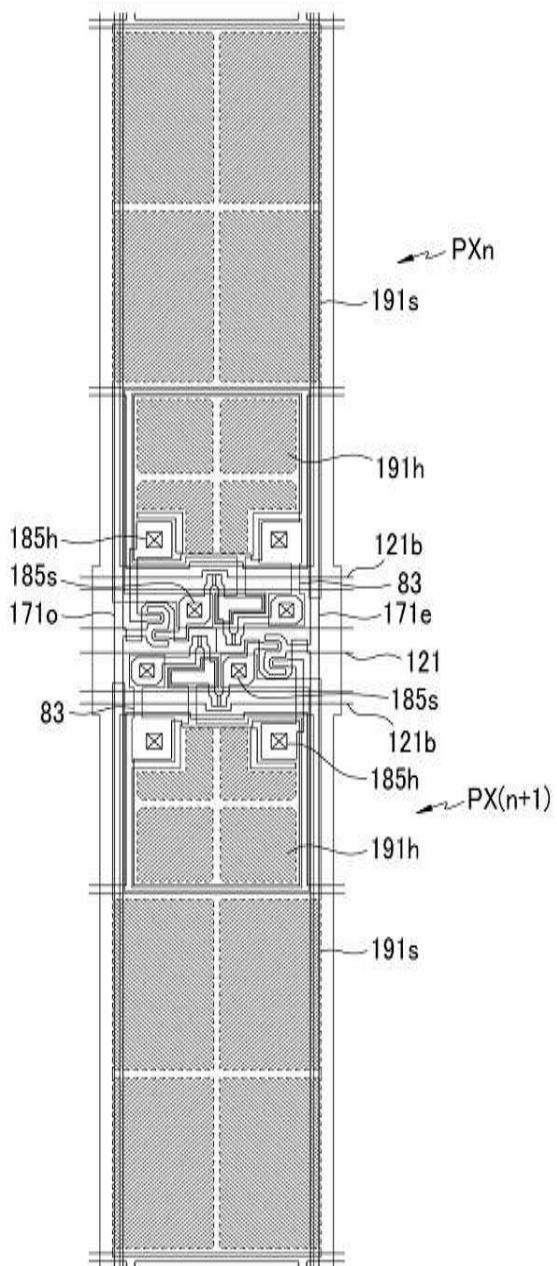

- [0071] 그러면 도 1 및 도 2에 도시한 액정 표시 장치의 신호선 및 화소의 배치에 대해 도 3 및 도 4를 앞에서 설명한 도 1 및 도 2와 함께 참고하여 설명한다.

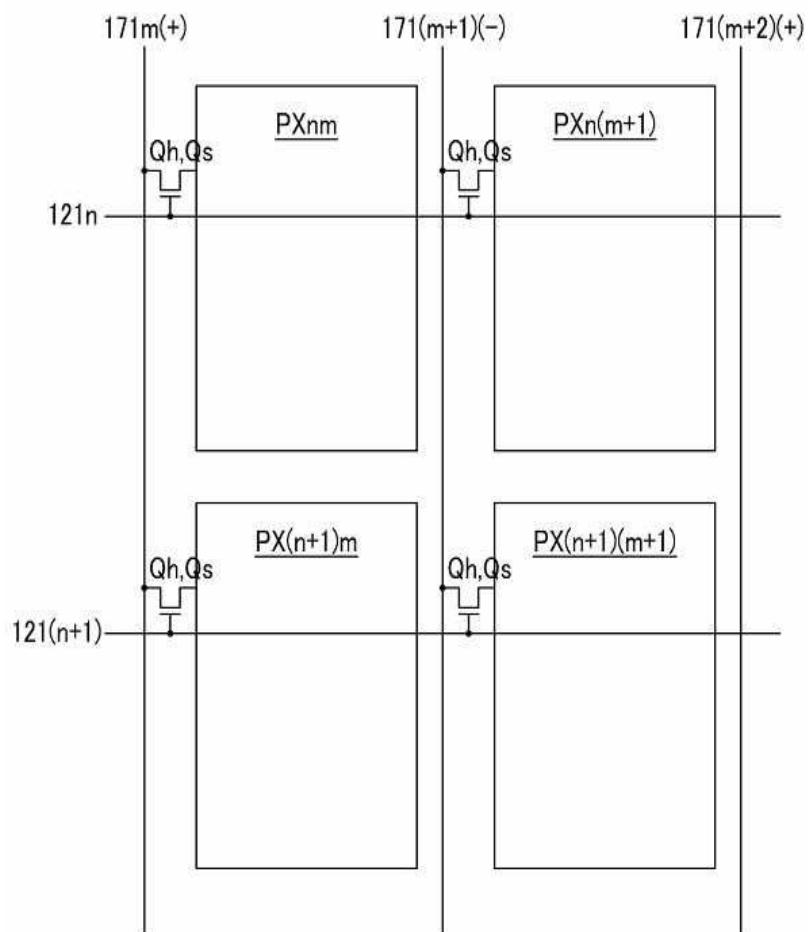

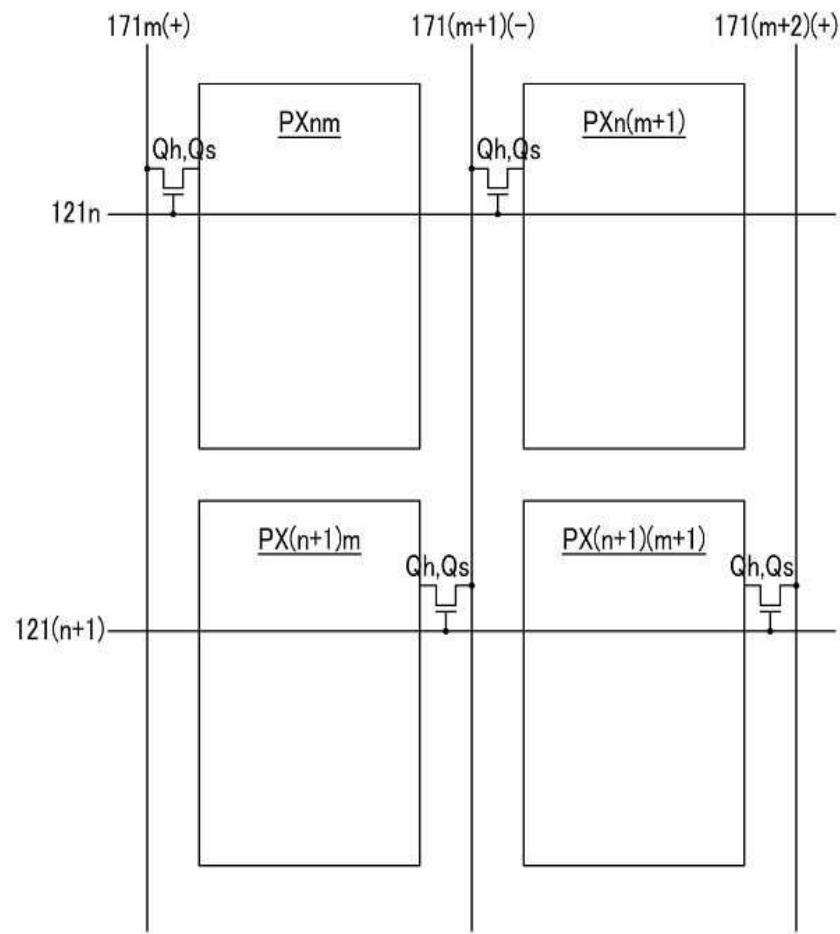

- [0072] 도 3 및 도 4는 각각 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜지스터 및 화소 전극의 간략한 배치도이다.

- [0073] 도 3 및 도 4를 참고하면, 본 실시예에 따른 액정 표시 장치는 복수의 게이트선(121n, 121(n+1)), 복수의 승압 게이트선(도시하지 않음) 및 복수의 데이터선(171m, 171(m+1), 171(m+2))을 포함하는 신호선과 이에 연결된 복수의 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1))를 포함한다. 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1))는 행렬의 형태로 배열되어 있을 수 있다.

- [0074] 도 3의 경우, 모든 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1))는 왼쪽에 위치하는 데이터선(171m, 171(m+1))과 스위칭 소자(Qh, Qs)를 통해 연결되어 있다. 따라서 이웃하는 데이터선(171m, 171(m+1), 171(m+2))에 극성이 반대인 데이터 전압이 인가되는 경우 열 반전 구동이 된다.

- [0075] 도 4의 경우는 행 방향으로 이웃하는 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1))는 스위칭 소자(Qh, Qs)가 연결된 데이터선(171m, 171(m+1), 171(m+2))의 방향이 동일하지만, 열 방향으로 이웃하는 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1))의 스위칭 소자(Qh, Qs)가 연결된 데이터선(171m, 171(m+1), 171(m+2))의 방향은 서로 반대이다. 즉, 왼쪽 데이터선(171m, 171(m+1), 171(m+2))에 연결된 스위칭 소자(Qh, Qs)와 오른쪽 데이터선(171m, 171(m+1), 171(m+2))에 연결된 스위칭 소자(Qh, Qs)가 열 방향으로 교대로 배열되어 있다. 따라서 이웃하는 데이터선(171m, 171(m+1), 171(m+2))에 극성이 반대인 데이터 전압이 인가되는 경우 점 반전 구동이 가능하다.

- [0076] 스위칭 소자(Qh, Qs)를 포함한 화소(PXnm, PXn(m+1), PX(n+1)m, PX(n+1)(m+1)) 및 그 동작에 대한 설명은 앞에서 하였으므로 생략한다.

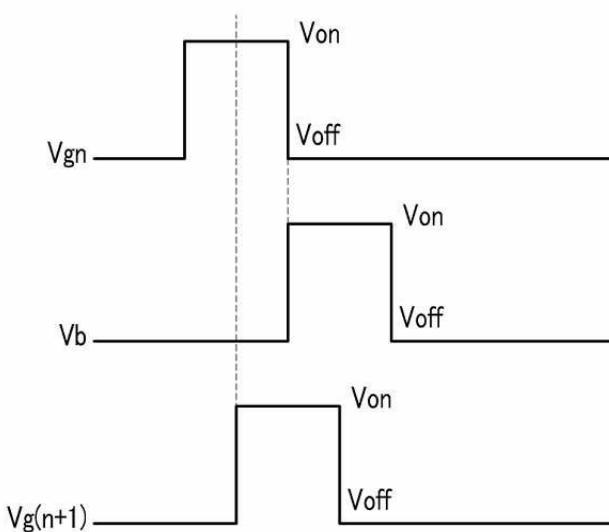

- [0077] 그러면 도 1 내지 도 4에 도시한 액정 표시 장치의 구동 방법의 한 실시예에 대해 도 5를 참고하여 설명한다.

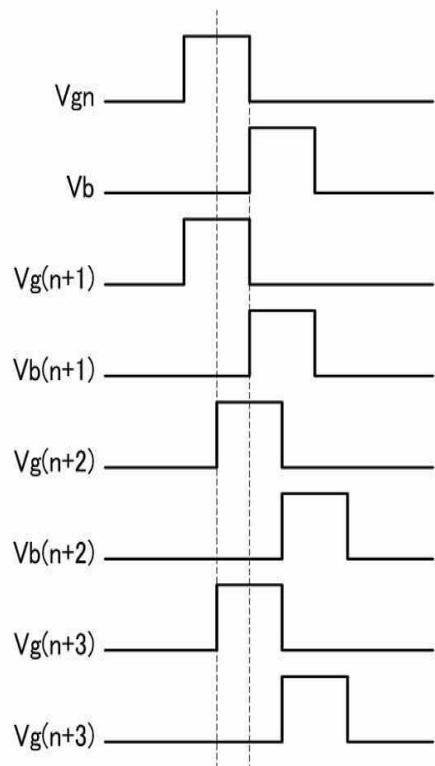

- [0078] 도 5는 본 발명의 한 실시예에 따른 액정 표시 장치의 게이트 신호의 파형도이다.

- [0079] 도 3, 도 4 및 도 5를 참고하면, 게이트 신호(Vgn)는 n번째 게이트선(121n)에 인가되는 신호이고, 게이트 신호(Vb)는 n번째 게이트선(121n)에 연결된 화소(PXnm, PXn(m+1))에 연결된 승압 게이트선(121b)[도 1 및 도 2 참고]에 인가되는 신호이고, 게이트 신호(Vg(n+1))는 (n+1)번째 게이트선(121(n+1))에 인가되는 신호이다.

- [0080] 앞에서 설명한 바와 같이 게이트선(121n)에 게이트 온 전압(Von)이 인가되면 제1 및 제2 스위칭 소자(Qh, Qs)를 통해 제1 및 제2 부화소 전극(191h, 191s)에 데이터 전압이 인가된다. 다음 게이트선(121n)에 게이트 오프 전압(Voff)이 인가됨과 동시에 승압 게이트선(121b)에 게이트 온 전압(Von)이 인가되어 제1 및 제2 부화소 전극(191h, 191s)의 전압이 서로 달라진다. 이때 인접한 게이트선(121(n+1))에 게이트 온 전압(Von)이 인가되는 시간과 이전 게이트선(121n)에 게이트 온 전압(Von)이 인가되는 시간이 중첩할 수 있다.

- [0081] 이와 같이 이웃한 게이트선(121n, 121(n+1))의 게이트 온 전압(Von)의 인가 시간을 중첩시킴으로써 액정 표시 장치의 120Hz 이상의 고속 구동의 경우 액정 축전기(Clch, Clcs)의 선 충전을 통해 구동 마진을 확보할 수 있다.

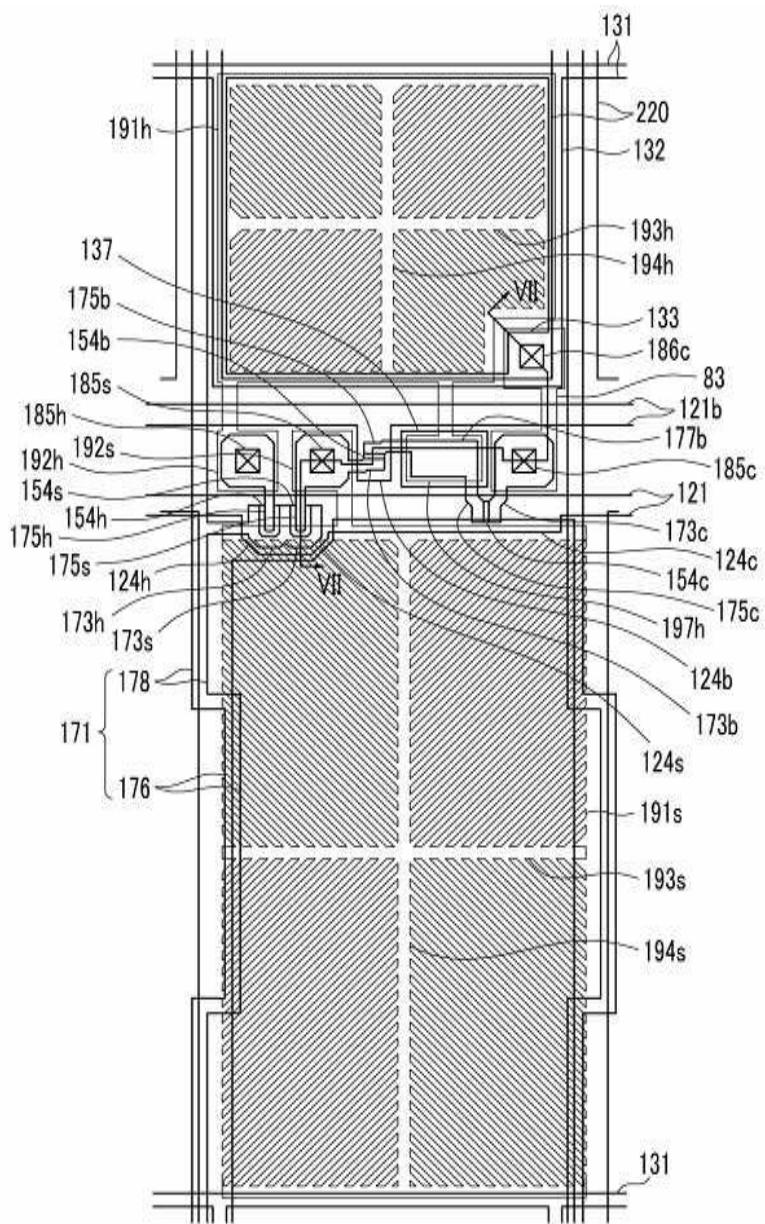

- [0082] 이제 도 6 및 도 7을 참고로 하여 본 발명의 한 실시예에 따른 액정 표시 장치의 상세 구조에 대하여 설명한다.

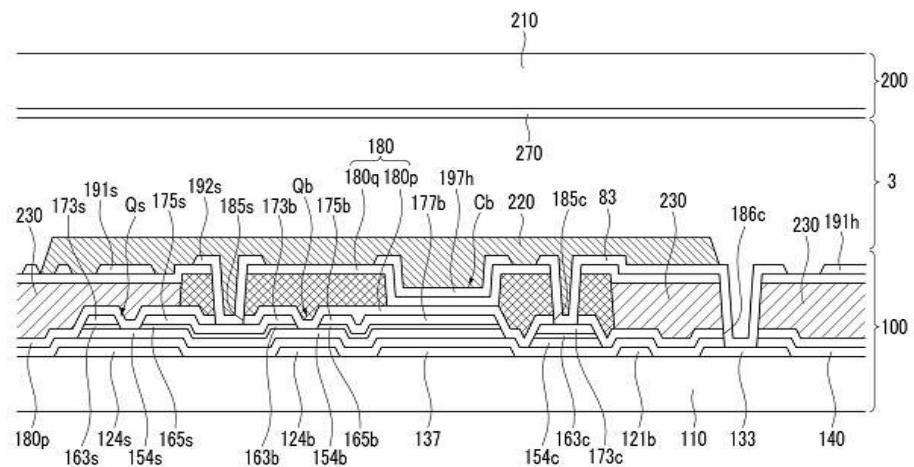

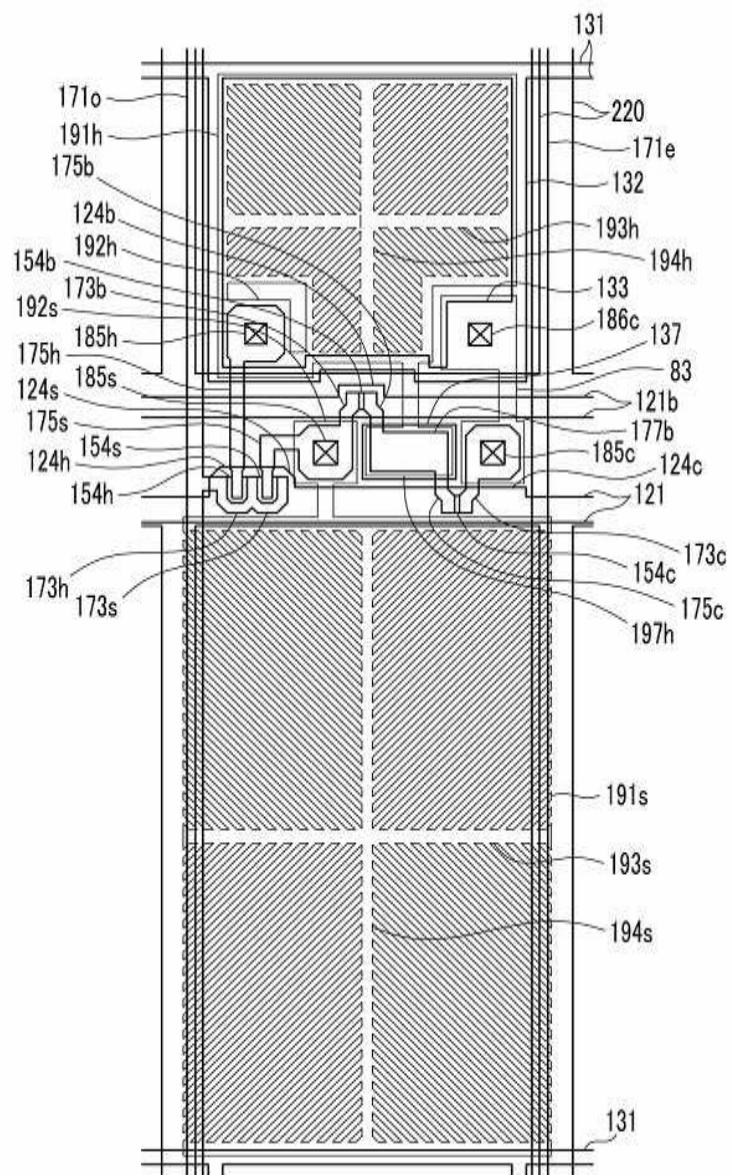

- [0083] 도 6은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고, 도 7은 도 6의 액정 표시 장치를 VII-VII 선을 따라 잘라 도시한 단면도이다.

- [0084] 도 6 및 도 7을 참고하면, 본 발명의 한 실시예에 따른 액정 표시 장치는 서로 마주하는 하부 표시판(100)과 상부 표시판(200) 및 이들 두 표시판(100, 200) 사이에 들어 있는 액정층(3)을 포함한다.

- [0085] 먼저, 하부 표시판(100)에 대하여 설명한다.

- [0086] 절연 기판(110) 위에 복수의 게이트선(gate line)(121), 복수의 승압 게이트선(121b), 복수의 공통 전압선(131) 및 광 차단부(137)를 포함하는 복수의 게이트 도전체가 형성되어 있다.

- [0087] 게이트선(121) 및 승압 게이트선(121b)은 주로 가로 방향으로 뻗어 있으며 게이트 신호를 전달한다. 게이트선(121)은 아래로 돌출한 제1, 제2 및 제3 게이트 전극(gate electrode)(124h, 124s, 124c)을 포함한다. 제1 및 제2 게이트 전극(124h, 124s)는 서로 연결되어 하나의 돌출부를 이룬다. 승압 게이트선(121b)은 아래로 돌출한 제4 게이트 전극(124b)을 포함한다.

- [0088] 각 공통 전압선(131)은 공통 전압(Vcom)을 전달하며 줄기(도시하지 않음) 및 고리부(132)를 포함한다. 줄기선은 게이트선(121) 및 승압 게이트선(121b)에 실질적으로 나란하며 고리부(132)는 줄기선으로부터 아래로 뻗어 사각형의 고리 모양을 이룬다. 고리부(132)는 고리부(132)의 오른쪽 아래모퉁이에서 안쪽으로 돌출한 접촉부(133)를 포함한다.

- [0089] 광 차단부(137)는 직사각형일 수 있으며 게이트선(121) 및 승압 게이트선(121b) 사이에 위치한다. 광 차단부(137)은 생략할 수 있다.

- [0090] 게이트 도전체(121, 121b, 131, 137) 위에는 게이트 절연막(gate insulating layer)(140)이 형성되어 있다.

- [0091] 게이트 절연막(140) 위에는 비정질 또는 결정질 규소 등으로 만들어질 수 있는 복수의 선형 반도체(도시하지 않음)가 형성되어 있다. 선형 반도체는 주로 세로 방향으로 뻗어 있으며 오른쪽으로 굽은 복수의 굽은 부를 포함한다. 각 선형 반도체는 제1 및 제2 게이트 전극(124h, 124s)을 향하여 뻗어 나와 있으며 서로 연결된 제1 및 제2 반도체(154h, 154s), 이와 연결된 제4 반도체(154b), 그리고 제4 반도체(154b)와 연결된 제3 반도체(154c)를 포함한다.

- [0092] 선형 반도체 위에는 복수의 선형 저항성 접촉 부재(ohmic contact)(도시하지 않음) 및 복수의 섬형 저항성 접촉 부재(165h, 165s, 163b, 165b, 163c, 165c)[165h, 165c는 도시되어 있지 않지만 편의상 사용하기로 한다]가 형성되어 있다. 선형 저항성 접촉 부재는 선형 반도체의 제1 및 제2 반도체(154h, 154s)를 따라 뻗은 복수의 돌출부(163h, 163s)[163h는 도시되어 있지 않지만 편의상 사용하기로 한다]를 포함한다. 두 돌출부(163h, 163s)는 서로 연결되어 있다. 두 섬형 저항성 접촉 부재(165s, 163b)는 서로 연결되어 있으며, 두 섬형 저항성 접촉 부재(165b, 165c)도 서로 연결되어 있다.

- [0093] 돌출부(163h)와 섬형 저항성 접촉 부재(165h)는 제1 게이트 전극(124h)을 중심으로 서로 마주하며 쌍을 이루어 제1 반도체(154h) 위에 배치되어 있다. 돌출부(163s)와 섬형 저항성 접촉 부재(165s)는 제2 게이트 전극(124s)을 중심으로 서로 마주하며 쌍을 이루어 제2 반도체(154s)위에 배치되어 있다. 두 섬형 저항성 접촉 부재(163b, 165b)는 제4 게이트 전극(124b)을 중심으로 서로 마주하며 쌍을 이루어 제4 반도체(154b)위에 배치되어 있다. 두 섬형 저항성 접촉 부재(165c, 163c)는 제3 게이트 전극(124c)을 중심으로 서로 마주하며 쌍을 이루어 제3 반도체(154c) 위에 배치되어 있다.

- [0094] 저항성 접촉 부재(163h, 163s, 165h, 165s, 163b, 165b, 163c, 165c)는 인파위의 n형 불순물이 고농도로 도핑되어 있는 n<sup>+</sup> 수소화 비정질 규소 따위의 물질로 만들어지거나 실리사이드(silicide)로 만들어질 수 있다.

- [0095] 저항성 접촉 부재(163h, 163s, 165h, 165s, 163b, 165b, 163c, 165c) 위에는 복수의 데이터선(data line)(171), 복수의 제3 및 제4 소스 전극(source electrode)(173c, 173b), 그리고 복수의 제1, 제2, 제3 및 제4 드레인 전극(drain electrode)(175h, 175s, 175c, 175b)을 포함하는 데이터 도전체가 형성되어 있다.

- [0096] 데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어 게이트선(121) 및 승압 게이트선(121b)과 교차한다. 데이터선(171)은 게이트선(121) 및 승압 게이트선(121b)과 교차하는 직선부(178)와 선형 반도체를 따라 굽은 복수의 굽은 부(176)를 포함한다. 각 데이터선(171)은 제1 및 제2 게이트 전극(124h, 124s)을 향하여 뻗어 함께 'M' 형태를 이루는 제1 및 제2 소스 전극(173h, 173s)을 포함한다.

- [0097] 제2 드레인 전극(175s)과 제4 소스 전극(173b)은 서로 연결되어 있다. 제4 드레인 전극(175b)과 제3 드레인 전극(175c)도 서로 연결되어 있으며, 연결 지점에 면적이 넓은 확장부(177b)가 위치한다. 확장부(177b)는 광 차단막(137)과 중첩한다.

- [0098] 제1/제2 드레인 전극(175h/175s)의 한 쪽 끝은 제1/제2 게이트 전극(124h/124s)을 중심으로 제1/제2 소스 전극(173h/173s)과 마주하며 제1/제2 소스 전극(173h/173s)으로 일부 둘러싸여 있다. 제3/제4 소스 전극(173c/173b) 및 제3/제4 드레인 전극(175c/175b)도 제3/제4 게이트 전극(124c/124b)을 중심으로 서로 마주한다. 제1 및 제2 드레인 전극(175h, 175s)의 다른 한 쪽 끝과 제3 소스 전극(173c)의 한 쪽 끝은 각각 다른 충과의 접속을 위해 면적이 넓다.

- [0099] 제1/제2/제3/제4 게이트 전극(124h/124s/124c/124b), 제1/제2/제3/제4 소스 전극(173h/173s/173c/173b) 및 제

1/제2/제3/제4 드레인 전극(175h/175s/175c/175b)은 제1/제2/제3/제4 반도체(154h/154s/154c/154b)와 함께 제1/제2/제3/제4 박막 트랜지스터(thin film transistor, TFT)(Qh/Qs/Qc/Qb)를 이루며, 제1/제2/제3/제4 박막 트랜지스터(Qh/Qs/Qc/Qb)의 채널(channel)은 제1/제2/제3/제4 소스 전극(173h/173s/173c/173b)과 제1/제2/제3/제4 드레인 전극(175h/175s/175c/175b) 사이의 제1/제2/제3/제4 반도체(154h/154s/154c/154b)에 형성된다.

[0100] 제1, 제2, 제3 및 제4 반도체(154h, 154s, 154c, 154b)를 포함하는 선형 반도체는 소스 전극(173h, 173s, 173c, 173b)과 드레인 전극(175h, 175s, 175c, 175b) 사이의 채널 영역을 제외하고는 데이터 도전체(171, 173c, 173b, 175h, 175s, 175c, 175b) 및 그 하부의 저항성 접촉 부재(163h, 165h, 163s, 165s, 163b, 165b, 163c, 165c)와 실질적으로 동일한 평면 모양을 가진다. 즉, 반도체(154h, 154s, 154c, 154b)에는 소스 전극(173h, 173s, 173c, 173b)과 드레인 전극(175h, 175s, 175c, 175b) 사이를 비롯하여 데이터 도전체(171, 173c, 173b, 175h, 175s, 175c, 175b)에 의해 가리지 않고 노출된 부분이 있다.

[0101] 저항성 접촉 부재(163h, 165h, 163s, 165s, 163b, 165b, 163c, 165c)는 그 아래의 반도체(154h, 154s, 154c, 154b)와 그 위의 데이터 도전체(171, 173c, 173b, 175h, 175s, 175c, 175b) 사이에만 존재하며 이들 사이의 접촉 저항을 낮추어 준다.

[0102] 데이터 도전체(171, 173c, 173b, 175h, 175s, 175c, 175b) 및 노출된 반도체(154h, 154s, 154c, 154b) 부분 위에는 질화규소 또는 산화규소 따위의 무기 절연물로 만들어질 수 있는 보호막(180)이 형성되어 있다. 보호막(180)에는 제1 및 제2 드레인 전극(175h, 175s)을 드러내는 복수의 제1 및 제2 접촉 구멍(185h, 185s), 그리고 제3 소스 전극(173c)을 드러내는 복수의 접촉 구멍(185c)이 형성되어 있다. 보호막(180) 및 게이트 절연막(140)에는 공통 전압선(131)의 접촉부(133)를 드러내는 복수의 접촉 구멍(186c)이 형성되어 있다.

[0103] 보호막(180) 위에는 복수의 제1 및 제2 부화소 전극(pixel electrode)(191h, 191s)과 연결 다리(83)가 형성되어 있다.

[0104] 제1 부화소 전극(191h)의 전체적인 모양은 사각형이며, 가로 줄기부(193h), 세로 줄기부(194h) 및 아래로 돌출한 두 돌출부(192h, 197h)를 포함한다.

[0105] 제1 부화소 전극(191h)은 가로 줄기부(193h)와 세로 줄기부(194h)에 의해 네 개의 부영역으로 나뉘어진다. 각 부영역은 가로 줄기부(193h) 및 세로 줄기부(194h)에서부터 바깥쪽으로 비스듬하게 뻗어 있는 복수의 미세 가지부를 포함한다. 미세 가지부가 게이트선(121) 또는 가로 줄기부(193h)와 이루는 각은 대략 45도 또는 135도일 수 있다. 이웃하는 두 부영역의 미세 가지부는 서로 직교할 수 있다.

[0106] 제1 부화소 전극(191h)은 돌출부(192h)를 통해 제1 드레인 전극(175h)으로부터 데이터 전압을 인가 받는다. 또한 돌출부(197h)는 대략 직사각형이며 제4 드레인 전극(175b) 및 제3 드레인 전극(175c) 사이에 연결되어 있는 확장부(177b)와 보호막(180)을 사이에 두고 중첩하여 승압 측전기(Cb)를 이룬다.

[0107] 제2 부화소 전극(191s)은 가로 줄기부(193s), 세로 줄기부(194s) 및 위로 돌출한 돌출부(192s)를 포함한다. 제2 부화소 전극(191s)의 높이는 제1 부화소 전극(191h)의 높이보다 높으며 대략 1배 내지 3배일 수 있다. 제2 부화소 전극(191s)은 돌출부(192s)를 통해 제2 드레인 전극(175s)으로부터 데이터 전압을 인가 받는다. 제2 부화소 전극(191s)의 가로 줄기부(193s) 및 세로 줄기부(194s)에 대한 설명은 제1 부화소 전극(191h)과 동일하므로 생략한다.

[0108] 한편, 제1 및 제2 부화소 전극(191h, 191s)은 게이트선(121) 및 승압 게이트선(121b)를 사이에 두고 각각 위 및 아래에 위치한다. 제1 부화소 전극(191h)은 게이트선(121) 및 승압 게이트선(121b)과 중첩하지 않을 수 있고, 제2 부화소 전극(191s)의 상단부는 일부분 게이트선(121)과 중첩한다. 이와 같이 제1 및 제2 부화소 전극(191h, 191s)과 게이트선(121) 또는 승압 게이트선(121b)과의 중첩을 없게 하거나 최소화하여 그들 사이의 기생 용량에 의한 킥백 전압을 줄일 수 있다. 그러면 박막 트랜지스터를 구동하기 위한 게이트 구동부(도시하지 않음)가 하부 표시판(100)에 접적되어 있는 경우 게이트 구동부의 크기를 작게 할 수 있다.

[0109] 제1 부화소 전극(191h)의 하단부는 공통 전압선(131)의 고리부(132)와 중첩하여 제1 부화소 전극(191h)의 하단부에서의 빛샘을 가릴 수 있다.

[0110] 연결 다리(83)는 접촉 구멍(185c, 186c)을 통하여 공통 전압선(131)의 접촉부(133)와 제3 소스 전극(173c)을 전기적으로 연결하며, 제3 소스 전극(173c)은 연결 다리(83)를 통해 공통 전압(Vcom)을 인가 받는다.

[0111] 제1 및 제2 부화소 전극(191h, 191s)과 연결 다리(83)는 ITO, IZO 등의 투명한 도전체 따위로 만들어질 수

있다.

[0112] 제1 및 제2 부화소 전극(191h, 191s) 및 연결 다리(83) 위에는 배향막(도시하지 않음)이 형성되어 있을 수 있다.

[0113] 다음 상부 표시판(200)에 대하여 설명한다.

[0114] 절연 기판(210) 위에 공통 전극(common electrode)(270)이 형성되어 있다.

[0115] 공통 전극(270) 위에는 블랙 매트릭스(black matrix)라고도 하는 차광 부재(220)가 형성되어 있다. 차광 부재(220)는 빛샘을 방지하며 데이터선(171)을 따라 형성된 복수의 세로부와 게이트선(121) 및 승압 게이트선(121b)을 따라 형성된 가로부를 포함하며 복수의 개구부를 가진다. 차광 부재(220)의 가로부는 제1 및 제2 부화소 전극(191h, 191s) 사이의 대부분을 가린다.

[0116] 절연 기판(210) 및 차광 부재(220) 위에는 복수의 색필터(230)가 형성되어 있다. 색필터(230)는 차광 부재(220)로 둘러싸인 개구부 내에 대부분 존재한다. 색필터(230)는 제1 및 제2 부화소 전극(191h, 191s)에 대응하는 영역에 섬형으로 존재하거나 제1 및 제2 부화소 전극(191h, 191s) 열을 따라서 길게 형성되어 있을 수도 있다. 각 색필터(230)는 적색, 녹색 및 청색의 삼원색 등 기본색(primary color) 중 하나를 표시할 수 있다.

[0117] 색필터(230) 및 차광 부재(220) 위에는 덮개막(overcoat)(250)이 형성되어 있다. 덮개막(250)은 (유기) 절연물로 만들어질 수 있으며, 색필터(230)가 노출되는 것을 방지하고 평坦면을 제공한다. 덮개막(250)은 생략할 수 있다.

[0118] 덮개막(250) 위에는 공통 전극(270)이 형성되어 있다. 공통 전극(270)은 ITO, IZO 등의 투명한 도전체 따위로 만들어질 수 있다.

[0119] 공통 전극(270) 위에는 배향막(도시하지 않음)이 형성되어 있을 수 있다.

[0120] 표시판(100, 200)의 바깥쪽 면에는 편광자(polarizer)(도시하지 않음)가 구비되어 있을 수 있다.

[0121] 하부 표시판(100)과 상부 표시판(200) 사이에 들어 있는 액정층(3)은 음의 유전율 이방성을 가지는 액정 분자를 포함하며 액정 분자는 전기장이 없는 상태에서 그 장축이 두 표시판(100, 200)의 표면에 대하여 수직을 이루도록 배향되어 있을 수 있다.

[0122] 게이트선(121)에 게이트 신호를 인가하여 데이터 전압이 인가된 제1 및 제2 부화소 전극(191h, 191s)은 공통 전압(Vcom)을 인가 받는 공통 전극(270)과 함께 전기장을 생성한다. 그러면 액정층(3)의 액정 분자들은 전기장에 응답하여 그 장축이 전기장의 방향에 수직을 이루도록 방향을 바꾸고자 한다. 액정 분자가 기울어진 정도에 따라 액정층(3)에 입사된 빛의 편광의 변화 정도가 달라지며 이러한 편광의 변화는 편광자에 의하여 투과율 변화로 나타나며 이를 통하여 액정 표시 장치는 영상을 표시한다.

[0123] 제1/제2 부화소 전극(191h/191s)과 공통 전극(270)은 그 사이의 액정층(3)과 함께 제1/제2 액정 축전기(liquid crystal capacitor)(Clch/Clcs)를 이루어 제1/제2 박막 트랜지스터(Qh/Qs)가 터 오프된 후에도 인가된 전압을 유지한다.

[0124] 제1/제2 부화소 전극(191h/191s)은 게이트 절연막(140)과 보호막(180)을 사이에 두고 고리부(132)를 포함하는 공통 전압선(131)과 중첩하여 유지 축전기(storage capacitor)(Csth/Csts)를 이루어 제1/제2 액정 축전기(Clch/Clcs)의 전압 유지 능력을 강화한다.

[0125] 도 6에 도시한 바와 같이 본 발명의 실시예에 따르면 제1, 제2, 제3 및 제4 박막 트랜지스터(Qh, Qs, Qc, Qb)와 승압 축전기(Cb) 모두 빛이 투과하지 않는 영역, 즉 제1 및 제2 부화소 전극(191h, 191s) 사이에 게이트선(121) 및 승압 게이트선(121b)이 위치하는 곳에 위치한다. 따라서 제1 및 제2 부화소 전극(191h, 191s)이 위치하는 투과 영역의 개구율이 높아지고 투과율도 높아질 수 있다.

[0126] 또한 데이터선(171)이 굽곡되어 있어 데이터선(171)과 제1 및 제2 부화소 전극(191h, 191s) 사이의 기생 용량에 의한 크로스 토크(cross talk)를 줄일 수 있다.

[0127] 다음 도 6에 도시한 액정 표시 장치의 다른 실시예에 따른 여러 단면 구조에 대해 도 6과 도 8, 도 9, 도 10 및 도 11을 참고하여 설명한다.

[0128] 도 8, 도 9, 도 10 및 도 11은 각각 도 6의 액정 표시 장치를 VII-VII 선을 따라 잘라 도시한 단면도이다.

- [0129] 앞선 실시예와 동일한 구성 요소는 동일한 도면 부호를 부여하고, 동일한 설명은 생략한다.

- [0130] 먼저 도 6 및 도 8을 참고하면, 보호막(180)은 질화규소 또는 산화규소 따위의 무기 절연물로 만들어질 수 있는 하부 보호막(180p)과 유기 절연물로 만들어질 수 있는 상부 보호막(180q)을 포함한다. 상부 보호막(180q)의 유기 절연물은 음 또는 양의 감광성(photosensitivity)을 가질 수 있고, 그 유전 상수(dielectric constant)는 약 4.0 이하일 수 있으며, 표면이 평탄할 수 있다. 하부 보호막(180p)은 색필터(230)의 안료가 노출된 반도체(154h, 154s, 154c, 154b) 부분으로 유입되는 것을 방지할 수 있다.

- [0131] 색필터(230)는 상부 표시판(200)이 아닌 하부 표시판(100)에 위치하며 하부 보호막(180p) 및 상부 보호막(180q) 사이에 위치한다. 공통 전압선(131)의 접촉부(133)를 드러내는 복수의 접촉 구멍(186c)은 중첩하는 색필터(230)를 관통할 수 있다.

- [0132] 차광 부재(220) 역시 하부 표시판(100)에 위치하며 제1 및 제2 부화소 전극(191h, 191s), 연결 다리(83) 및 상부 보호막(180q) 위에 위치한다. 이러한 차광 부재(220)는 액정층(3)의 간격을 유지하기 위한 간격재(spacer) (도시하지 않음)와 동일한 층을 이룰 수 있다. 따라서 차광 부재(220)와 간격재를 동시에 형성할 수 있고 액정 표시 장치의 제조 공정 및 시간을 감소시킬 수 있다.

- [0133] 이와 같이 색필터(230) 및 차광 부재(220)가 하부 표시판에 위치하면 액정 표시 장치의 개구율 및 투과율을 높일 수 있다.

- [0134] 다음 도 6 및 도 9를 참고하면, 보호막(180)은 질화규소 또는 산화규소 따위의 무기 절연물로 만들어질 수 있는 하부 보호막(180p) 및 상부 보호막(180q)을 포함한다. 하부 보호막(180p)은 색필터(230)의 안료가 노출된 반도체(154h, 154s, 154c, 154b) 부분으로 유입되는 것을 방지할 수 있다. 상부 보호막(180q)은 유기 절연물을 포함할 수도 있다.

- [0135] 차광 부재(220)는 상부 표시판(200)의 절연 기판(210) 위에 위치하나, 색필터(230)는 하부 표시판(100)의 하부 보호막(180p) 및 상부 보호막(180q) 사이에 위치한다. 접촉 구멍(186c)은 중첩하는 색필터(230)를 관통할 수 있다.

- [0136] 다음 도 6 및 도 10을 참고하면, 본 실시예에 따른 액정 표시 장치는 도 8에 도시한 단면 구조와 거의 동일한 구조를 가지나, 차광 부재(220) 및 보호막(180)의 구조가 다르다.

- [0137] 보호막(180)은 질화규소 또는 산화규소 따위의 무기 절연물로 만들어질 수 있는 하부 보호막(180p) 및 상부 보호막(180q)의 이중막을 포함한다. 상부 보호막(180q)은 유기 절연물을 포함할 수도 있다.

- [0138] 차광 부재(220)는 상부 보호막(180q) 아래에 위치하며 대부분 이웃하는 색필터(230) 사이에 위치한다. 이에 따라 접촉 구멍(185h, 185s, 185c)은 중첩하는 차광 부재(220)를 관통할 수 있다. 또한 승압 축전기(Cb)를 이루는 제1 부화소 전극(191h)의 돌출부(197h)와 확장부(177b) 사이의 차광 부재(220)는 제거되어 승압 축전기(Cb)의 용량을 확보할 수 있다.

- [0139] 먼저 도 6 및 도 11을 참고하면, 보호막(180)은 질화규소 또는 산화규소 따위의 무기 절연물로 만들어질 수 있는 하부 보호막(180p)과 상부 보호막(180q)을 포함한다. 상부 보호막(180q)은 평탄면 및 감광성을 가지는 유기 절연물로 만들어질 수 있다. 상부 보호막(180q)이 유기 절연물로 만들어질 경우 승압 축전기(Cb)를 이루는 제1 부화소 전극(191h)의 돌출부(197h)와 확장부(177b) 사이의 상부 보호막(180q)은 제거되어 승압 축전기(Cb)의 용량을 확보할 수 있다.

- [0140] 하부 보호막(180p) 위에는 격벽(partition)(240)이 형성되어 있다. 격벽(240)은 제1 및 제2 부화소 전극(191h, 191s) 각각 또는 모두의 가장자리 주변을 둑(bank)처럼 둘러싸서 개구부를 정의하며 유기 절연물 또는 무기 절연물로 만들어질 수 있다. 승압 축전기(Cb)를 이루는 제1 부화소 전극(191h)의 돌출부(197h)와 확장부(177b) 사이의 격벽(240)은 제거되어 승압 축전기(Cb)의 용량을 확보할 수 있다.

- [0141] 격벽(240)은 또한 검정색 안료를 포함하는 감광제로 만들어질 수 있는데, 이 경우 격벽(240)은 차광 부재의 역할을 하며 그 형성 공정이 간단하다.

- [0142] 격벽(240) 사이에는 잉크젯 프린팅 방법에 의해 형성될 수 있는 색필터(230)가 위치한다.

- [0143] 차광 부재(220) 역시 하부 표시판(100)에 위치하며 제1 및 제2 부화소 전극(191h, 191s), 연결 다리(83) 및 상부 보호막(180q) 위에 위치한다. 이러한 차광 부재(220)는 액정층(3)의 간격을 유지하기 위한 간격재(spacer) (도시하지 않음)와 동일한 층을 이룰 수 있다. 격벽(240)은 검정색 안료를 포함하는 감광성 물질로 만들어질

수 있는데, 이 경우 격벽(240)은 차광 부재(220)의 역할을 할 수 있으며 차광 부재(220)는 생략할 수 있다.

[0144] 도 8, 도 9, 도 10 및 도 11에 도시한 액정 표시 장치에서 상부 보호막(180q)은 색필터(230)가 들뜨는 것을 방지하고 색필터(230)로부터 유입되는 용제(solvent)와 같은 유기물에 의한 액정층(3)의 오염을 억제하여 구동시 초래할 수 있는 잔상과 같은 불량을 방지할 수 있다.

[0145] 다음 본 발명의 다른 실시예에 따른 액정 표시 장치에 대하여 도 12를 참고하여 상세하게 설명한다.

[0146] 도 12는 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이다.

[0147] 본 실시예에 따른 액정 표시 장치의 층상 구조는 대개 도 6 내지 도 11에 도시한 액정 표시 장치의 층상 구조와 동일하다. 도 6 내지 도 11에 도시한 실시예와 동일한 구성 요소는 동일한 도면 부호를 부여하고, 동일한 설명은 생략한다.

[0148] 도 12를 참고하면, 본 실시예에 따른 액정 표시 장치는 도 6에 도시한 액정 표시 장치와 거의 동일한 구조를 가지고, 제2 소스 전극(173h, 173s), 제2 드레인 전극(175s), 제2 접촉 구멍(185s), 제4 소스 전극(173b) 및 제2 부화소 전극(191s)의 돌출부 등의 구조가 다르다.

[0149] 제1 및 제2 소스 전극(173h, 173s)의 열린 부분의 방향이 서로 반대이며, 제2 소스 전극(173s)의 열린 부분은 아래를 향하고 있다. 제2 드레인 전극(175s)은 제2 소스 전극(173s)의 아래 부분에 위치하여 제2 접촉 구멍(185s)을 통해 제2 부화소 전극(191s)의 돌출부(192s)와 전기적으로 연결되어 있다. 돌출부(192s)는 제2 부화소 전극(191s)의 왼쪽 위 모퉁이에 위치한다.

[0150] 제4 소스 전극(173b)은 제2 드레인 전극(175s)과 분리되어 있다. 제4 소스 전극(173b)은 보호막(180)에 형성된 접촉 구멍(185b)을 통하여 제2 부화소 전극(191s)의 돌출부(192sb)와 전기적으로 연결되어 있다. 따라서 제4 소스 전극(173b)은 제2 드레인 전극(175s)과 따로 제2 부화소 전극(191s)의 전압을 인가받는다.

[0151] 본 실시예에서는 승압 축전기(Cb)를 이루는 제1 부화소 전극(191h)의 돌출부(197h)와 확장부(177b) 아래에 별도의 광 차단막이 존재하지 않는다.

[0152] 다음 본 발명의 다른 실시예에 따른 액정 표시 장치에 대하여 도 13을 참고하여 상세하게 설명한다.

[0153] 도 13은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이다.

[0154] 본 실시예에 따른 액정 표시 장치의 층상 구조는 대개 도 6 내지 도 11에 도시한 액정 표시 장치의 층상 구조와 동일하다. 도 6 내지 도 11에 도시한 실시예와 동일한 구성 요소는 동일한 도면 부호를 부여하고, 동일한 설명은 생략한다.

[0155] 도 13을 참고하면, 본 실시예에 따른 액정 표시 장치는 도 12에 도시한 액정 표시 장치와 거의 동일한 구조를 가지고, 공통 전압선(131)의 고리부(132) 및 제1 부화소 전극(191h)의 하단부 모양이 다르다. 고리부(132)의 아래쪽 가로 부분이 생략되어 있으며, 제1 부화소 전극(191h)의 하단부는 승압 게이트선(121b)까지 확장되어 일부 중첩한다. 이와 같이 하면 개구율을 더욱 높일 수 있고, 승압 게이트선(121b)의 주변의 빛샘을 줄일 수 있다.

[0156] 다음 도 1 및 도 2에 도시한 액정 표시 장치의 본 발명의 다른 실시예에 따른 신호선 및 화소의 배치에 대해 도 14 및 앞에서 설명한 도 1 및 도 2와 함께 참고하여 설명한다.

[0157] 도 14는 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜ジ스터 및 화소 전극의 간략한 배치도이다.

[0158] 도 14를 참고하면, 본 실시예에 따른 액정 표시 장치는 앞에서 설명한 도 4에 도시한 액정 표시 장치와 대부분 동일한 배치 구조를 가지고, 각 화소(PX) 열 사이에 두 개의 데이터선(171m, 171(m+1), 171(m+2), 171(m+3))이 위치한다. 즉, 열 방향으로 이웃한 제1 및 제2 스위칭 소자(Qh, Qs)는 각 화소(PXnm, PXn(m+2), PX(n+1)(m+1), PX(n+1)(m+3))의 양쪽에 위치하는 두 데이터선(171m, 171(m+1), 171(m+2), 171(m+3))에 번갈아 연결되어 있다. 따라서 이웃하는 데이터선(171m, 171(m+1), 171(m+2), 171(m+3))에 극성이 반대인 데이터 전압이 인가되는 경우 점 반전 구동이 될 수 있다.

[0159] 본 실시예에서 게이트선(121n, 121(n+1))은 두 개씩 쌍을 이루어 동일한 게이트 신호를 인가 받을 수 있다.

[0160] 그러면 도 1, 도 2 및 도 14에 도시한 액정 표시 장치의 구동 방법의 한 실시예에 대해 도 15를 참고하여 설명

한다.

[0161] 도 15는 본 발명의 한 실시예에 따른 액정 표시 장치의 게이트 신호의 과정도이다.

[0162] 본 실시예에 따른 구동 방법은 앞에서 설명한 도 5의 구동 방법과 대부분 동일하다. 그러나 도 15에 도시한 바와 같이 이웃한 게이트선(121n, 121(n+1))은 두 개씩 쌍을 이루어 동일한 게이트 신호를 인가 받는다. 즉, n번째 게이트선(121n)의 게이트 신호(Vgn)와 (n+1)번째 게이트선(121(n+1))의 게이트 신호(Vg(n+1))는 서로 동일하며, (n+2)번째 게이트선(도시하지 않음)의 게이트 신호(Vg(n+2))과 (n+3)번째 게이트선(도시하지 않음)의 게이트 신호(Vg(n+3))는 서로 동일하다. 승압 게이트선(121b)[도 1 및 도 2 참고]의 게이트 신호(Vb, Vb(n+1), Vb(n+2), Vb(n+3))도 두 개씩 쌍을 이루어 동일한 게이트 신호를 인가 받는다.

[0163] 이와 같이 각 화소(PX) 열을 두 개의 데이터선(171)과 연결하고, 이웃한 두 화소(PX) 행에 동일한 게이트 신호를 인가하면 게이트 구동부의 구조를 간단하게 할 수 있다.

[0164] 그러면 도 14의 액정 표시 장치의 상세한 구조에 대해 도 16 및 도 17을 앞에서 설명한 도 1, 도 2 및 도 14와 함께 참고하여 상세하게 설명한다.

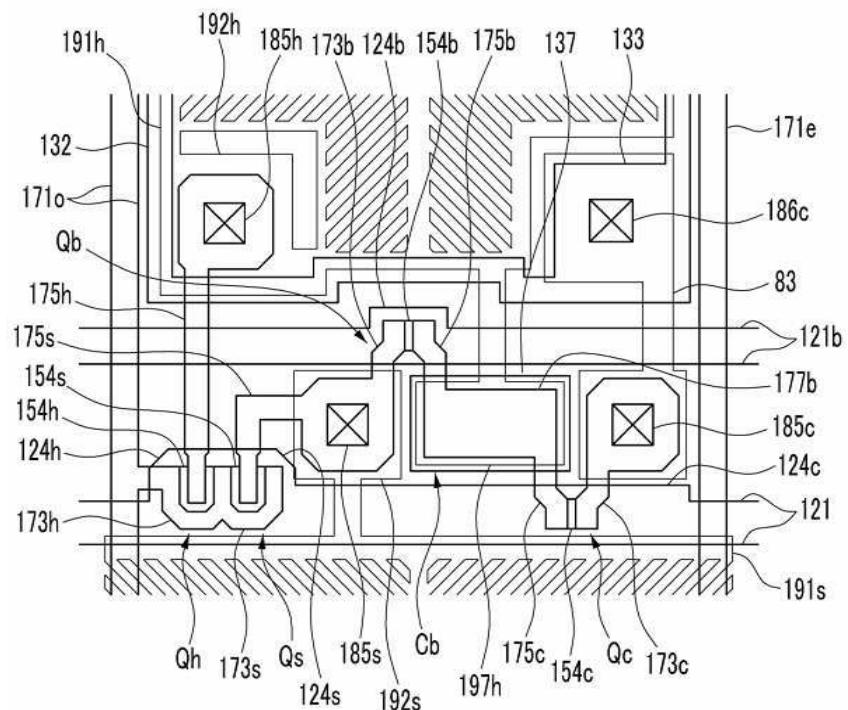

[0165] 도 16은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고, 도 17은 도 16에 도시한 부분의 일부를 확대한 배치도이다.

[0166] 본 실시예에 따른 액정 표시 장치의 층상 구조는 대개 도 6 내지 도 11에 도시한 액정 표시 장치의 층상 구조와 동일하다. 도 6 내지 도 11에 도시한 실시예와 동일한 구성 요소는 동일한 도면 부호를 부여하고, 동일한 설명은 생략한다.

[0167] 도 16 및 도 17을 참고하면, 본 실시예에 따른 액정 표시 장치는 제1 및 제2 부화소 전극(191h, 191s)의 양쪽에 위치하는 제1 및 제2 데이터선(171o, 171e)을 포함한다. 제1 및 제2 데이터선(171o, 171e)은 굽은 부분 없이 열 방향으로 뻗어 있다.

[0168] 도 16에 도시된 제1 및 제2 소스 전극(173h, 173s)은 제1 데이터선(171o)과 연결되어 있고, 도시하지는 않았지만 열 방향으로 이웃한 화소(PX)의 제1 및 제2 소스 전극(173h, 173s)은 제2 데이터선(171e)과 연결되어 있다.

[0169] 제1 부화소 전극(191h)과 제1 드레인 전극(175h)이 연결되는 제1 접촉 구멍(185h)과 제1 부화소 전극(191h)의 돌출부(192h)는 제1 부화소 전극(191h)의 왼쪽 아래 모퉁이에 위치한다. 따라서 제1 접촉 구멍(185h)은 공통 전압선(131)의 접촉부(133)를 드러내는 접촉 구멍(186c)과 대칭을 이루게 되고 시야각에 따른 개구부 모양이 동일할 수 있다.

[0170] 제1, 제2, 제3 및 제4 게이트 전극(124h, 124s, 124c, 124b)은 게이트선(121) 및 승압 게이트선(121b)으로부터 위로 돌출되어 있다. 이에 따라 제1, 제2, 제3 및 제4 박막 트랜지스터(Qh, Qs, Qc, Qb)의 각 구성 요소의 배치 또는 형태는 도 6의 배치 또는 형태와 다르게 약간씩 변형될 수 있다.

[0171] 그러면 도 18을 참고하여 본 발명의 다른 실시예에 따른 액정 표시 장치에 대하여 설명한다.

[0172] 도 18은 본 발명의 한 실시예에 따른 액정 표시 장치의 두 화소에 대한 등가 회로도이다.

[0173] 본 실시예에 따른 액정 표시 장치는 앞에서 설명한 도 2의 액정 표시 장치와 대부분 동일하다. 그러나 열 방향으로 인접한 두 화소(PXn, PX(n+1))는 게이트선(121)을 공유하여 두 화소(PXn, PX(n+1))의 제1, 제2 및 제3 스위칭 소자(Qh, Qs, Qc)는 동일한 게이트 신호를 인가 받는다. 한편, 두 화소(PXn, PX(n+1))의 제1, 제2 및 제3 스위칭 소자(Qh, Qs, Qc)는 서로 다른 데이터선(171o, 171e)에 연결되어 각 화소(PXn, PX(n+1))에 해당하는 데이터 전압을 인가 받는다.

[0174] 도 18에 도시한 액정 표시 장치의 상세한 구조에 대해 도 19 및 도 20을 참고하여 설명한다.

[0175] 도 19는 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고, 도 20은 도 19에 도시한 액정 표시 장치의 일부를 확대한 배치도이다.

[0176] 본 실시예에 따른 액정 표시 장치의 층상 구조는 대부분 도 16 및 도 17에 도시한 액정 표시 장치의 층상 구조와 동일하다. 도 16 및 도 17에 도시한 실시예와 동일한 구성 요소는 동일한 도면 부호를 부여하고, 동일한 설명은 생략한다.

[0177] 도 19 및 도 20을 참고하면, 열 방향으로 이웃한 두 화소(PXn, PX(n+1))는 점대칭을 이루며 게이트선(121)을 공유하고 있다. 이와 같이 열 방향으로 이웃하는 두 화소(PXn, PX(n+1))의 구조를 대칭이 되게 하면 시야각에 따

른 개구부의 차이가 없어질 수 있다. 특히 모든 박막 트랜지스터( $Q_h$ ,  $Q_s$ ,  $Q_c$ ,  $Q_b$ ) 및 승압 축전기( $C_b$ )가 이웃한 화소( $PX_n$ ,  $PX_{(n+1)}$ ) 사이에 위치하며 두 화소( $PX_n$ ,  $PX_{(n+1)}$ )가 게이트선(121)을 공유하므로 개구율 및 액정 표시 장치의 투과율이 증가될 수 있다. 도시하지는 않았지만 행 방향으로 이웃하는 화소( $PX$ )도 Y축 대칭을 이룰 수 있다.

[0178] 각각의 화소( $PX_n$ ,  $PX_{(n+1)}$ )의 구조는 대부분 도 16 및 도 17에 도시한 액정 표시 장치와 동일하다. 그러나, 제1 및 제2 박막 트랜지스터( $Q_h$ ,  $Q_s$ ), 특히 제1 및 제2 소스 전극(173h, 173s)과 제1 및 제2 드레인 전극(175h, 175s)의 형태가 다르다.

[0179] 제1 및 제2 소스 전극(173h, 173s)은 위 아래 방향으로 연결되어 있으며, 제1 및 제2 소스 전극(173h, 173s)의 열린 부분은 서로 반대 방향을 향하고 있으며 왼쪽 또는 오른쪽을 향하고 있다. 이와 같이 제1 및 제2 소스 전극(173h, 173s)의 열린 부분을 서로 반대가 되게 하면, 게이트선(121)의 게이트 온 전압(Von)이 게이트 오프 전압(Voff)으로 바뀔 때 제1 및 제2 박막 트랜지스터( $Q_h$ ,  $Q_s$ )의 게이트 전압(124h, 124s)과 드레인 전극(175h, 175s) 사이의 기생 용량에 의해 발생하는 킥백 전압의 편차에 의한 표시 불량을 줄일 수 있다.

[0180] 이에 대해 도 21, 도 22 및 도 23을 참고하여 상세하게 설명한다.

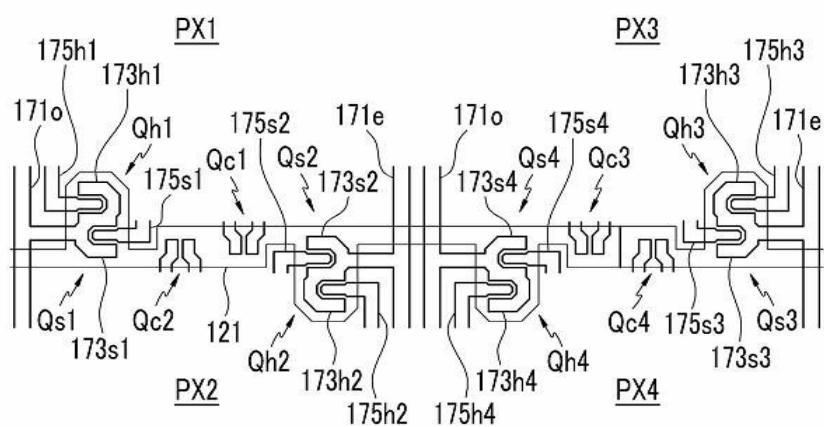

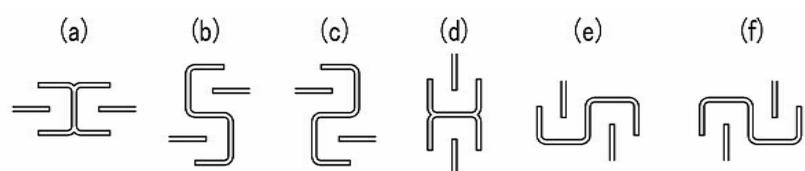

[0181] 도 21은 본 발명의 한 실시예에 따른 액정 표시 장치의 행 및 열 방향으로 이웃한 네 화소( $PX_1$ ,  $PX_2$ ,  $PX_3$ ,  $PX_4$ )의 박막 트랜지스터의 배치도이고, 도 22는 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜지스터 및 화소 전극의 간략한 배치와 킥백 전압의 변화를 보여주는 도면이고, 도 23은 본 발명의 한 실시예에 따른 박막 트랜지스터의 다양한 형태를 보여주는 도면이다.

[0182] 도 21 및 도 22를 참고하면, 화소( $PX_1$ )는 제1 및 제2 박막 트랜지스터( $Q_{h1}$ ,  $Q_{s1}$ )와 연결되어 있고, 화소( $PX_2$ )는 제1 및 제2 박막 트랜지스터( $Q_{h2}$ ,  $Q_{s2}$ )와 연결되어 있으며, 화소( $PX_3$ )는 제1 및 제2 박막 트랜지스터( $Q_{h3}$ ,  $Q_{s3}$ )와 연결되어 있고, 화소( $PX_4$ )는 제1 및 제2 박막 트랜지스터( $Q_{h4}$ ,  $Q_{s4}$ )와 연결되어 있다.

[0183] 열 방향으로 이웃한 화소( $PX_1$ ,  $PX_2$ ,  $PX_3$ ,  $PX_4$ )는 서로 점대칭을 이루므로, 제1 박막 트랜지스터( $Q_{h1}$ ,  $Q_{h2}$ / $Q_{h3}$ ,  $Q_{h4}$ )의 제1 소스 전극(173h1, 173h2/ 173h3, 173h4)의 열린 방향은 서로 반대이고, 제2 박막 트랜지스터( $Q_{s1}$ ,  $Q_{s2}$ /  $Q_{s3}$ ,  $Q_{s4}$ )의 제2 소스 전극(173s1, 173s2/ 173s3, 173s4)의 열린 방향도 서로 반대이다. 또한 행 방향으로 이웃한 화소( $PX_1$ ,  $PX_3$ /  $PX_2$ ,  $PX_4$ )는 Y축 대칭을 이루고 있으므로, 제1 박막 트랜지스터( $Q_{h1}$ ,  $Q_{h3}$ / $Q_{h2}$ ,  $Q_{h4}$ )의 제1 소스 전극(173h1, 173h3/ 173h2, 173h4)의 열린 방향은 서로 반대이고, 행 방향으로 이웃한 화소( $PX_1$ ,  $PX_3$ /  $PX_2$ ,  $PX_4$ )의 제2 박막 트랜지스터( $Q_{s1}$ ,  $Q_{s3}$ /  $Q_{s2}$ ,  $Q_{s4}$ )의 제2 소스 전극(173s1, 173s3/ 173s2, 173s4)의 열린 방향도 서로 반대이다.

[0184] 이와 같이 배치하면 게이트선(121)과 드레인 전극(175h1, 175s1, 175h2, 175s2, 175h3, 175s3, 175h4, 175s4) 사이의 좌우 정렬에 오차가 생겨도 킥백 전압이 서로 상쇄될 수 있다.

[0185] 도 22는 도 21의 게이트선(121)이 상대적으로 왼쪽으로 정렬되었을 경우 각 화소( $PX_1$ ,  $PX_2$ ,  $PX_3$ ,  $PX_4$ )의 킥백 전압의 증감을 나타낸 도면이다.

[0186] 게이트선(121)이 드레인 전극(175h1, 175s1, 175h2, 175s2, 175h3, 175s3, 175h4, 175s4)에 대해 왼쪽으로 정렬되면, 화소( $PX_1$ )의 제1 박막 트랜지스터( $Q_{h1}$ )와 연결된 제1 부화소( $PX_{h1}$ ), 화소( $PX_2$ )의 제2 박막 트랜지스터( $Q_{s2}$ )와 연결된 제2 부화소( $PX_{s2}$ ), 화소( $PX_3$ )의 제2 박막 트랜지스터( $Q_{s3}$ )와 연결된 제2 부화소( $PX_{s3}$ ), 그리고 화소( $PX_4$ )의 제1 박막 트랜지스터( $Q_{h4}$ )와 연결된 제1 부화소( $PX_{h4}$ )의 킥백 전압은 커지게 되나, 나머지 제1 및 제2 부화소( $PX_{s1}$ ,  $PX_{h2}$ ,  $PX_{h3}$ ,  $PX_{s4}$ )의 킥백 전압은 작아진다. 게이트선(121)이 오른쪽으로 치우쳐 정렬되는 경우는 반대가 된다. 따라서 도 24에 도시한 바와 같이 킥백 전압의 증감은 모자이크 형태로 나타나게 되고 서로 상쇄되므로 게이트선(121)과 드레인 전극(175h1, 175s1, 175h2, 175s2, 175h3, 175s3, 175h4, 175s4) 사이의 정렬에 오차가 생겨도 가로줄 얼룩과 같은 표시 불량이 발생하지 않는다.

[0187] 하나의 화소( $PX_1$ ,  $PX_2$ ,  $PX_3$ ,  $PX_4$ )에 대한 한 쌍의 소스 전극(173h1, 173s1/ 173h2, 173s2/ 173h3, 173s3/ 173h4, 173s4) 및 한 쌍의 드레인 전극(175h1, 175s1/ 175h2, 175s2/ 175h3, 175s3/ 175h4, 175s4)의 형태는 본 실시예에 한하지 않고 도 23의 (a), (b), (c), (d), (e) 및 (f)에 도시한 바와 같이 다양한 형태를 할 수 있다.

[0188] 이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

## 도면의 간단한 설명

- [0189] 도 1은 본 발명의 한 실시예에 따른 액정 표시 장치의 두 부화소에 대한 등가 회로도이고,

- [0190] 도 2는 본 발명의 한 실시예에 따른 액정 표시 장치의 한 화소에 대한 등가 회로도이고,

- [0191] 도 3 및 도 4는 각각 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜지스터 및 화소 전극의 간략한 배치도이고,

- [0192] 도 5는 본 발명의 한 실시예에 따른 액정 표시 장치의 게이트 신호의 파형도이고,

- [0193] 도 6은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고,

- [0194] 도 7, 도 8, 도 9, 도 10 및 도 11은 각각 도 6의 액정 표시 장치를 VII-VII 선을 따라 잘라 도시한 단면도이고,

- [0195] 도 12 및 도 13은 각각 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고,

- [0196] 도 15는 도 14에 도시한 부분의 일부를 확대한 배치도이고,

- [0197] 도 14는 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜지스터 및 화소 전극의 간략한 배치도이고,

- [0198] 도 15는 본 발명의 한 실시예에 따른 액정 표시 장치의 게이트 신호의 파형도이고,

- [0199] 도 16은 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고,

- [0200] 도 17은 도 16에 도시한 부분의 일부를 확대한 배치도이고,

- [0201] 도 18은 본 발명의 한 실시예에 따른 액정 표시 장치의 두 화소에 대한 등가 회로도이고,

- [0202] 도 19는 본 발명의 한 실시예에 따른 액정 표시 장치의 배치도이고,

- [0203] 도 20은 도 19에 도시한 액정 표시 장치의 일부를 확대한 배치도이고,

- [0204] 도 21은 본 발명의 한 실시예에 따른 액정 표시 장치의 행 및 열 방향으로 이웃한 네 화소의 박막 트랜지스터의 배치도이고,

- [0205] 도 22는 본 발명의 한 실시예에 따른 액정 표시 장치의 신호선, 박막 트랜지스터 및 화소 전극의 간략한 배치와 킥백 전압의 변화를 보여주는 도면이고,

- [0206] 도 23은 본 발명의 한 실시예에 따른 박막 트랜지스터의 다양한 형태를 보여주는 도면이다.

- [0207] <도면의 주요 부분에 대한 부호의 설명>

- |                                       |              |

|---------------------------------------|--------------|

| [0208] 3: 액정층                         | 100: 하부 표시판  |

| [0209] 110, 210: 절연 기판                | 121: 게이트선    |

| [0210] 121b: 승압 게이트선                  |              |

| [0211] 124h, 124s, 124c, 124b: 게이트 전극 |              |

| [0212] 131: 공통 전압선                    | 140: 게이트 절연막 |

| [0213] 154h, 154s, 154c, 154b: 반도체    |              |

| [0214] 171: 데이터선                      |              |

| [0215] 173h, 173s, 173c, 173b: 소스 전극  |              |

| [0216] 175h, 175s, 175c, 175b: 드레인 전극 |              |

| [0217] 180p: 하부 보호막                   | 180q: 상부 보호막 |

| [0218] 185h 185s, 185c, 185b: 접촉 구멍   |              |

| [0219] 191h, 191s: 화소 전극              | 200: 상부 표시판  |

[0220]

220: 차광 부재

230: 색필터

[0221]

270: 공통 전극

**도면****도면1**

## 도면2

**도면3**

**도면4****도면5**

## 도면6

도면7

도면8

도면9

도면10

도면11

## 도면12

## 도면13

## 도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

|                |                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR1020100070663A</a>                                                                                                                                                   | 公开(公告)日 | 2010-06-28 |

| 申请号            | KR1020080129311                                                                                                                                                                    | 申请日     | 2008-12-18 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                                                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                                                                                                                                          |         |            |

| [标]发明人         | KIM YOON JANG<br>김윤장<br>PARK KYUNG HO<br>박경호<br>MOON SUNG JAE<br>문성재<br>PARK KEE BUM<br>박기범                                                                                        |         |            |

| 发明人            | 김윤장<br>박경호<br>문성재<br>박기범                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/1362 G09G2300/0852 G09G2300/0443 G09G2300/0439 G09G2300/0842 G09G2300/0861 G09G2310/0262 G09G3/3659 G09G2320/028 G02F2201/52 G09G3/3614 G09G3/3648 G09G2300/0426 G02F1/13624 |         |            |

| 其他公开文献         | <a href="#">KR101518325B1</a>                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                          |         |            |

### 摘要(译)

液晶显示装置技术领域本发明涉及液晶显示装置。根据本发明示例性实施例的液晶显示器包括第一基板，形成在第一基板上用于传输第一栅极信号的栅极线，与栅极线交叉的数据线，像素电极，形成于第一基板上且包括第一子像素电极和第二子像素电极，第一栅极连接至栅极线，电极，连接到所述第二栅极电极上的第二源，如权利要求连接到所述第一开关元件，栅极线包括第一源极电极，连接到连接到数据线的第一子像素电极的第一漏电极的数据线像素电极，第二开关元件，包括耦合到第一子像素电极的第一电极，第二开关元件，包括耦合到第二子电极的第一电极电压的电容器，连接到所述栅极线的第三栅极电极，第三源电极，和连接到第三开关元件的第四栅电极，和对于升压用栅极线和连接到该升压电容器的第二端子的第三漏电极第四源电极连接到第二子像素电极，第四漏电极连接在第二端子之间。