(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0030704

(43) 공개일자 2012년03월29일

(51) 국제특허분류(Int. Cl.)

*G02F 1/136* (2006.01)

(21) 출원번호 10-2010-0092385

(22) 출원일자 2010년09월20일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

오금미

서울특별시 서대문구 세무서2가길 47 (홍제동)

이한석

서울특별시 성동구 성수이로 137, 현대아이파크아파트 111동 404호 (성수동2가)

박원근

서울특별시 강동구 구천면로 557, 중앙하이츠아파트 3동 103호 (상일동)

(74) 대리인

특허법인천문

전체 청구항 수 : 총 13 항

(54) 발명의 명칭 터치 스크린이 내장된 액정 표시장치와 이의 제조방법

### (57) 요약

본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 기판의 각 화소 영역에 액티브층, 게이트 전극, 절연층, 데이터 전극(source/drain)을 형성하여 박막 트랜지스터를 구성하는 단계; 상기 박막 트랜지스터 상부에 제1 보호층을 형성하고, 상기 제1 보호층의 일부 영역을 식각하여 상기 데이터 전극을 노출시키는 제1 컨택 홀을 형성하는 단계; 상기 제1 보호층의 상부와 상기 제1 컨택 홀 내부에 공통 전극 및 상기 공통 전극과 접속되는 도전성 라인을 형성하는 단계; 상기 공통 전극 및 도전성 라인 상부에 제2 보호층을 형성하고, 상기 제2 보호층 일부 영역을 식각하여 상기 데이터 전극과 대응되는 영역의 도전성 라인을 노출시키는 제2 컨택 홀을 형성하는 단계; 및 상기 제2 보호층의 상부 및 상기 제2 컨택 홀 내부에 상기 도전성 라인과 전기적으로 접속되는 화소 전극을 형성하는 단계;를 포함하고, 상기 제2 보호층, 상기 제2 컨택 홀 및 상기 화소 전극은 단일 마스크를 이용한 포토리소그래피 공정, 에칭 공정 및 애싱 공정을 통해 형성되는 것을 특징으로 한다.

### 대표도 - 도4

## 특허청구의 범위

### 청구항 1

데이터 라인 및 게이트 라인의 의해 복수의 화소 영역이 정의된 기판;

상기 기판의 각 화소 영역에 형성된 액티브층, 게이트 전극, 절연층, 데이터 전극(source/drain)으로 구성된 박막 트랜지스터;

상기 박막 트랜지스터 상부에 형성되는 제1 보호층;

상기 제1 보호층의 일부 영역이 식각되어 상기 데이터 전극을 노출시키는 제1 컨택 홀;

상기 제1 보호층의 상부 및 상기 제1 컨택 홀 내부에 형성되는 공통 전극;

상기 제1 보호층의 일측 상부 및 상기 제1 컨택 홀 내에서 상기 공통 전극 상부에 형성되는 도전성 라인;

상기 공통 전극 및 상기 도전성 라인 상부에 형성되는 제2 보호층;

상기 제2 보호층 일부 영역이 식각되어 상기 데이터 전극과 대응되는 영역의 도전성 라인을 노출시키는 제2 컨택 홀; 및

상기 제2 보호층의 상부 및 상기 제2 컨택 홀 내에 형성되어 상기 도전성 라인과 전기적으로 접속되는 화소 전극;을 포함하고,

상기 제2 보호층 및 상기 화소 전극은 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치.

### 청구항 2

제 1 항에 있어서, 상기 공통 전극 및 도전성 라인은

하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치.

### 청구항 3

제 1 항에 있어서, 상기 데이터 전극과 화소 전극은

상기 제1 컨택 홀 내부에 형성된 공통 전극 및 도전성 라인을 통해 전기적으로 접속되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치.

### 청구항 4

제 1 항에 있어서, 상기 박막 트랜지스터는

저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 소재로 형성되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치.

### 청구항 5

제 1 항에 있어서, 상기 도전성 라인은

상기 각 화소에 형성된 공통 전극을 연결시키는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치.

### 청구항 6

기판의 각 화소 영역에 액티브층, 게이트 전극, 절연층, 데이터 전극(source/drain)을 형성하여 박막 트랜지스터를 구성하는 단계;

상기 박막 트랜지스터 상부에 제1 보호층을 형성하고, 상기 제1 보호층의 일부 영역을 식각하여 상기 데이터 전극을 노출시키는 제1 컨택 홀을 형성하는 단계;

상기 제1 보호층의 상부와 상기 제1 컨택 홀 내부에 공통 전극 및 상기 공통 전극과 접속되는 도전성 라인을 형성하는 단계;

상기 공통 전극 및 도전성 라인 상부에 제2 보호층을 형성하고, 상기 제2 보호층 일부 영역을 식각하여 상기 데이터 전극과 대응되는 영역의 도전성 라인을 노출시키는 제2 컨택 홀을 형성하는 단계; 및

상기 제2 보호층의 상부 및 상기 제2 컨택 홀 내부에 상기 도전성 라인과 전기적으로 접속되는 화소 전극을 형성하는 단계;를 포함하고,

상기 제2 보호층, 상기 제2 컨택 홀 및 상기 화소 전극은 단일 마스크를 이용한 포토리소그래피 공정, 에칭 공정 및 애싱 공정을 통해 형성되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 7**

제 6 항에 있어서, 상기 공통 전극 및 도전성 라인은

단일 마스크를 이용한 포토리소그래피 공정, 에칭 공정 및 애싱 공정을 통해 형성되는 되는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 8**

제 6 항에 있어서,

상기 제1 컨택 홀 내부에 형성된 공통 전극 및 도전성 라인을 통해 상기 데이터 전극과 상기 화소 전극을 전기적으로 접속시키는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 9**

제 6 항에 있어서,

저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 소재로 상기 박막 트랜지스터를 형성하는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 10**

제 6 항에 있어서, 상기 도전성 라인은

상기 각 화소에 형성된 공통 전극을 연결시키는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 11**

제 6 항에 있어서, 상기 단일 마스크는

광이 투과하지 못하는 비 투과영역, 광의 일부만이 투과하는 반 투과영역 및 광이 모두 투과되는 투과영역을 포함하는 하프 톤 마스크인 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 12**

제 11 항에 있어서,

상기 하프 톤 마스크를 통해 포토레지스트층을 패터닝 하여 서로 다른 폭 및 두께를 가지는 복수의 포토레지스트 패턴을 형성하고, 상기 복수의 포토레지스트 패턴을 마스크로 이용하여 상기 공통 전극 및 도전성 라인을 형성하는 것을 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

#### **청구항 13**

제 11 항에 있어서,

상기 공통 전극 및 상기 공통 전극과 접속되는 도전성 라인을 형성하는 단계에서,

상기 제1 보호층 및 상 제1 컨택 홀 내부에 ITO(Indium Tin Oxide) 레이어와 금속 레이어를 순차적으로 형성하는 단계;

상기 금속 레이어 상에 포토레지스트층을 형성하는 단계;

상기 하프 톤 마스크를 통해 상기 포토레지스트층 패터닝하여 서로 다른 폭 및 두께를 가지를 복수의 포토레지스트 패턴을 상기 금속 레이어 상부에 형성하는 단계;

상기 복수의 포토레지스트 패턴을 마스크로 상기 ITO 레이어와 상기 금속 레이어를 에칭 단계; 및

상기 복수의 포토레지스트 패턴을 애싱하는 단계;를 포함하는 특징으로 하는 터치 스크린이 내장된 액정 표시장치의 제조방법.

## 명세서

### 기술분야

[0001]

본 발명은 평판 표시장치에 관한 것으로, 특히 구동 성능을 향상시킴과 아울러, 제조공정을 단순화시켜 제조비용을 절감시킬 수 있는 터치 스크린이 내장된 액정 표시장치와 이의 제조방법에 관한 것이다.

### 배경기술

[0002]

이동통신 단말기, 노트북 컴퓨터와 같은 각종 휴대용 전자기기가 발전함에 따라 이에 적용할 수 있는 평판 표시장치(Flat Panel Display Device)에 대한 요구가 증대되고 있다.

[0003]

평판 표시장치로는 액정 표시장치(Liquid Crystal Display Device), 플라즈마 디스플레이 패널(Plasma Display Panel), 전계 방출 표시장치(Field Emission Display Device), 발광 다이오드 표시장치(Light Emitting Diode Display Device) 등이 연구되고 있다. 이러한 평판 표시장치 중에서 액정 표시장치는 양산 기술의 발전, 구동수단의 용이성, 저전력 소비, 고화질 및 대화면 구현의 장점으로 적용 분야가 확대되고 있다.

[0004]

평판 표시장치의 입력 장치로서 종래에 적용되었던 마우스나 키보드 등의 입력 장치를 대체하여 사용자가 손가락이나 펜을 이용하여 스크린에 직접 정보를 입력할 수 있는 터치 스크린이 적용되고 있다.

[0005]

터치 스크린은 네비게이션(navigation), 산업용 단말기, 노트북 컴퓨터, 금융 자동화기기, 게임기 등과 같은 모니터; 휴대전화기, MP3, PDA, PMP, PSP, 휴대용 게임기, DMB 수신기, 태블릿 PC 등과 같은 휴대용 단말기; 및 냉장고, 전자 레인지, 세탁기 등과 같은 가전제품 등에 적용되고 있으며, 누구나 쉽게 조작할 수 있는 장점으로 인해 적용이 확대되고 있다.

[0006]

액정 표시장치에 터치 스크린의 적용에 있어서, 슬림(Slim)화를 위해 액정 패널에 터치 스크린이 내장된 형태로 개발이 이루어지고 있으며, 그 중에서 하부기판에 형성된 공통 전극과 같은 기존의 구성을 센싱 전극으로 활용하는 인-셀 터치(in-cell touch) 타입의 액정 표시장치가 개발되고 있다.

[0007]

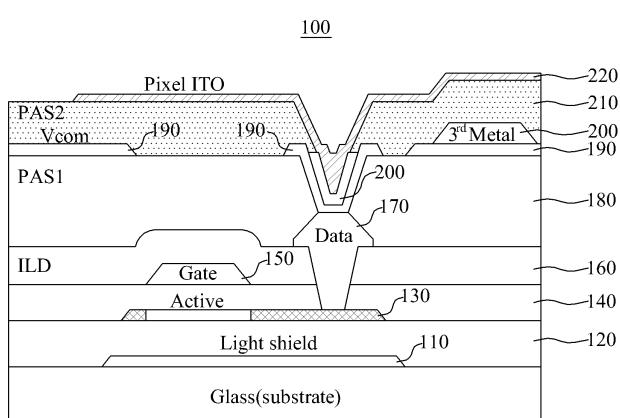

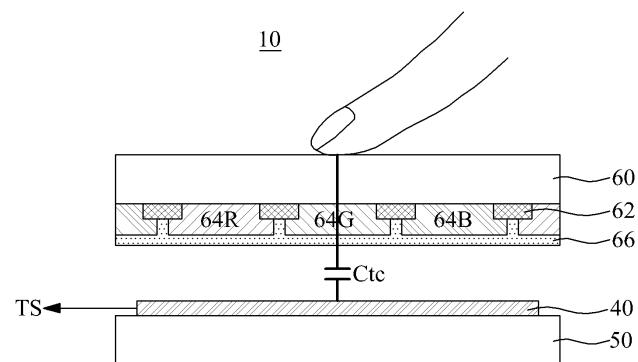

도 1은 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치와 이의 구동방법을 개략적으로 설명하기 위한 도면이다.

[0008]

도 1을 참조하면, 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치는 액정층(미도시)을 사이에 두고 합착된 하부 기판(50) 및 상부 기판(60)을 포함한다.

[0009]

상부 기판(60)은 복수의 화소 각각에 대응되도록 화소 영역을 정의하는 블랙 매트릭스(62); 블랙 매트릭스(62)에 의해 정의된 각 화소 영역에 형성된 적색, 녹색, 및 청색 컬러필터(64R, 64G, 64B); 및 적색, 녹색, 청색 컬러필터(64R, 64G, 64B)와 블랙 매트릭스(62)를 덮도록 형성되어 상부 기판(60)을 평탄화 시키는 오버코트층(66)을 포함한다.

[0010]

하부 기판(50)은 액정층을 구동시킴과 아울러 사용자 손가락의 터치 또는 펜 터치를 검출하기 위한 복수의 화소를 가지는 화소 어레이(40)를 포함하여 구성된다.

[0011]

상기 복수의 화소 각각은 서로 교차하는 데이터 라인과 게이트 라인에 의해 정의되며, 상기 데이터 라인과 상기 게이트 라인이 교차되는 영역에 박막 트랜지스터(TFT: Thin Film Transistor)가 형성된다. 또한, 복수의 화소 각각은 공통 전극 및 화소 전극을 포함한다.

[0012]

도 2는 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 단면도이다. 도 2에서는 FFS(Fringe Field Switch) 모드의 하부 기판 구조를 나타내고 있다.

[0013]

도 2를 참조하면, 상기 하부 기판(50)의 각 화소는 글라스 기판 상에 형성되는 차광층(71, Light shield

layer); 상기 차광층(71) 상에 형성되는 베피층(51); 상기 베피층(51) 상에 형성되는 액티브층(72, 반도체층); 상기 액티브층(72) 상에 형성되는 게이트 절연층(52); 상기 액티브층(72)의 일부와 중첩되도록 게이트 절연층(52) 상에 금속(metal) 물질로 형성되는 게이트 전극(73); 상기 게이트 전극(73) 상에 형성되어 상기 게이트 전극(73)과 데이터 전극(74, Source/Drain)을 절연시키는 하부 절연층(53, ILD: Inter Layer Dielectric); 상기 게이트 절연층(52) 및 상기 하부 절연층(53)이 애칭(식각)되어 형성된 컨택 홀에 의해 일부 영역이 노출된 액티브층(72)과 전기적으로 접속되도록 형성된 데이터 전극(74);을 포함한다.

[0014] 여기서, 상기 데이터 전극(74)은 상기 액티브층(72)의 일부 영역이 노출되도록 형성된 컨택 홀에 금속 물질이 매립되어 형성되고, 후술되는 화소 전극(77, Pixel ITO)과 전기적으로 접속된다.

[0015] 또한, 상기 하부 기판(50)의 각 화소는 상기 하부 절연층(53) 상에 순차적으로 형성되어, 상기 게이트 전극(71) 및 데이터 전극(74)을 덮도록 형성되는 제1 보호층(54, PAS0: passivation layer) 및 제2 보호층(55, PAS1); 상기 제2 보호층(55) 상에 인듐 틴 옥사이드(ITO: Indium Tin Oxide)와 같은 투명 전도성 물질로 형성되는 공통 전극(75, Vcom); 상기 공통 전극(75) 일측의 상부에 형성되어 전기적으로 접속되는 도전성 라인(76, 3<sup>rd</sup> Metal); 상기 공통 전극(75) 및 도전성 라인(76)을 덮도록 형성되는 제3 보호층(56, PAS2); ITO와 같은 투명 전도성 물질로 상기 제3 보호층(56)의 상부 및 상기 데이터 전극(74)과 전기적으로 접속되도록 형성되는 화소 전극(77, Pixel ITO);을 포함한다.

[0016] 여기서, 상기 제1 보호층(54, PAS0) 내지 제3 보호층(56, PAS2)은 그 일부 영역이 식각되어, 상기 데이터 전극(74)의 상부를 노출(open)시키는 컨택 홀이 형성된다.

[0017] 이때, 상기 제1 보호층(54, PAS0) 상에 형성된 제2 보호층(55, PAS1)의 일부 영역이 먼저 식각되고, 이후, 상기 제1 보호층(54, PAS0)과 제3 보호층(56, PAS2)가 동시에 식각되어 상기 게이트 전극(74)의 상부를 노출시키게 된다.

[0018] 상기 화소 전극(77)은 상기 제1 보호층(54, PAS0) 내지 제3 보호층(56, PAS2)의 식각에 의해 형성된 컨택 홀 내부에도 형성되어 상기 데이터 전극(74)과 전기적으로 접속된다.

[0019] 이러한, 종래 기술의 구조에서, 데이터 전극(74)과 화소 전극(77)을 접속시키는 컨택 홀의 오픈 영역은 상기 제2 보호층(55, PAS1)의 식각에 의해 결정되므로, 데이터 전극(74)이 노출되는 영역이 제한적으로 좁아지게 된다. 이로 인해, 데이터 전극(74)과 화소 전극(77)이 접속(contact) 영역이 작게 형성되어 컨택 성능이 저하되는 문제점이 있다.

[0020] 또한, 상기 제2 보호층(55, PAS1)의 식각 이후에 상기 제3 보호층(56, PAS2)를 식각 시키기 위한 포토리쏘그래피 공정 시 얼라인(align) 불량 및 이물 등에 의한 컨택 불량에 취약한 문제점이 있다.

[0021] 상술한 구성을 포함하는 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치는 1 프레임 기간 중 표시 기간에는 상기 하부 기판(50)의 화소 어레이(40)에 인가된 데이터 전압에 따라 각 화소의 액정층을 투과하는 광의 투과율을 조절하여 영상 신호에 따른 화상을 표시한다. 그리고, 비 표시 기간에는 상기 공통 전극(75)을 센싱 전극으로 구동시켜 사용자의 터치에 따른 정전용량(Ctc)의 변화를 감지하고, 이를 통해 터치 위치(TS)를 검출한다.

[0022] 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치는 공통 전극(75)을 화소 각각에 개별적으로 배치하고, 각각의 공통 전극(75)을 도전성 라인(76)을 이용하여 연결하는 구성을 가지게 된다. 따라서, 상기 공통 전극(75)을 형성하는 공정과 상기 도전성 라인(76)을 형성하는 공정을 각각 수행하게 되어 제조공정이 복잡해진다. 이로 인해, 제조비용이 증가되고 생산성이 떨어지는 단점이 있다.

[0023] 아몰퍼스 실리콘(a-Si: amorphous Silicon) TFT의 느린 동작 속도, 미세 선폭 설계 제한 등의 단점을 보완하기 위해, 상기 하부 기판(50)의 구성들(일 예로서, TFT)을 형성하기 위한 소재로 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 이용하고 있다.

[0024] 하부 기판(50)의 구성들의 형성하기 위한 소재로 저온 다결정 실리콘 (LTPS)을 이용하는 경우에는 도 3에 도시된 바와 같이, 제조공정에 10개의 마스크(mask)가 이용되고, 이에 따른 다수의 세부공정(일 예로서 155 steps)을 수행하게 된다. 특히, 공통 전극(75)과 도전성 라인(76)을 형성하는 공정에 각각 별도의 마스크(mask 7: Vcom 형성에 이용, mask 8: 3<sup>rd</sup> Metal 형성에 이용)가 이용되고, 이에 따른 세부공정들이 수행되어야 한다.

[0025] 상술한 바와 같이, 저온 다결정 실리콘(LTPS)은 아몰퍼스 실리콘(a-Si) 대비 고해상도 구현이 용이하고, 탁월한

TFT 동작 특성 등의 장점이 있지만 제조공정에서 마스크 공정 및 세부공정이 아몰퍼스 실리콘(a-Si) 대비 많이 소요되어 가격 경쟁력에서 한계가 있고 제조효율이 떨어지는 단점이 있다.

[0026] 따라서, 터치 스크린이 내장된 액정 표시장치의 소재로 저온 다결정 실리콘(LTPS)을 이용하면서 마스크 공정을 줄이면 저온 다결정 실리콘(LTPS) 소재의 장점을 활용하여 구동성능을 향상시키고, 가격 경쟁력의 확보 및 제조 효율을 높일 수 있다.

## 발명의 내용

### 해결하려는 과제

[0027] 본 발명은 상술한 문제점을 해결하기 위한 것으로서, 하부 기판의 소재로 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 적용하여 구동 성능을 향상시킬 수 있는 터치 스크린이 내장된 액정 표시장치와 이의 제조방법을 제공하는 것을 기술적 과제로 한다.

[0028] 본 발명은 상술한 문제점을 해결하기 위한 것으로서, 하부 기판의 형성 시 마스크 공정을 줄여 제조비용을 절감시킬 수 있는 터치 스크린이 내장된 액정 표시장치와 이의 제조방법을 제공하는 것을 기술적 과제로 한다.

[0029] 본 발명은 상술한 문제점을 해결하기 위한 것으로서, 하부 기판의 제조공정을 단순화시켜 제조효율을 향상시킬 수 있는 터치 스크린이 내장된 액정 표시장치와 이의 제조방법을 제공하는 것을 기술적 과제로 한다.

[0030] 본 발명은 상술한 문제점을 해결하기 위한 것으로서, 하부 기판에 형성된 데이터 전극과 화소 전극의 컨택 성능을 향상시킬 수 있는 터치 스크린이 내장된 액정 표시장치와 이의 제조방법을 제공하는 것을 기술적 과제로 한다.

### 과제의 해결 수단

[0031] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치는 데이터 라인 및 게이트 라인의 의해 복수의 화소 영역이 정의된 기판; 상기 기판의 각 화소 영역에 형성된 액티브층, 게이트 전극, 절연층, 데이터 전극(source/drain)으로 구성된 박막 트랜지스터; 상기 박막 트랜지스터 상부에 형성되는 제1 보호층; 상기 제1 보호층의 일부 영역이 식각되어 상기 데이터 전극을 노출시키는 제1 컨택 홀; 상기 제1 보호층의 상부 및 상기 제1 컨택 홀 내부에 형성되는 공통 전극; 상기 제1 보호층의 일측 상부 및 상기 제1 컨택 홀 내에서 상기 공통 전극 상부에 형성되는 도전성 라인; 상기 공통 전극 및 상기 도전성 라인 상부에 형성되는 제2 보호층; 상기 제2 보호층 일부 영역이 식각되어 상기 데이터 전극과 대응되는 영역의 도전성 라인을 노출시키는 제2 컨택 홀; 및 상기 제2 보호층의 상부 및 상기 제2 컨택 홀 내에 형성되어 상기 도전성 라인과 전기적으로 접속되는 화소 전극;을 포함하고, 상기 제2 보호층 및 상기 화소 전극은 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성되는 것을 특징으로 한다.

[0032] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 상기 공통 전극 및 도전성 라인은 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성되는 것을 특징으로 한다.

[0033] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 상기 데이터 전극과 화소 전극은 상기 제1 컨택 홀 내부에 형성된 공통 전극 및 도전성 라인을 통해 전기적으로 접속되는 것을 특징으로 한다.

[0034] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치에서, 상기 박막 트랜지스터는 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 소재로 형성되는 것을 특징으로 한다.

[0035] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 기판의 각 화소 영역에 액티브층, 게이트 전극, 절연층, 데이터 전극(source/drain)을 형성하여 박막 트랜지스터를 구성하는 단계; 상기 박막 트랜지스터 상부에 제1 보호층을 형성하고, 상기 제1 보호층의 일부 영역을 식각하여 상기 데이터 전극을 노출시키는 제1 컨택 홀을 형성하는 단계; 상기 제1 보호층의 상부와 상기 제1 컨택 홀 내부에 공통 전극 및 상기 공통 전극과 접속되는 도전성 라인을 형성하는 단계; 상기 공통 전극 및 도전성 라인 상부에 제2 보호층을 형성하고, 상기 제2 보호층 일부 영역을 식각하여 상기 데이터 전극과 대응되는 영역의 도전성 라인을 노출시키는 제2 컨택 홀을 형성하는 단계; 및 상기 제2 보호층의 상부 및 상기 제2 컨택 홀 내부에 상기 도전성 라인과 전기적으로 접속되는 화소 전극을 형성하는 단계;를 포함하고, 상기 제2 보호층, 상기 제2 컨택 홀 및 상기 화소 전극은 단일 마스크를 이용한 포토리소그래피 공정, 예칭 공정 및 애칭 공정을 통해 형성되는 것을 특징으로 한다.

[0036] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법에서, 상기 공통 전극 및 도전성 라

인은 단일 마스크를 이용한 포토리소그래피 공정, 예칭 공정 및 애싱 공정을 통해 형성되는 되는 것을 특징으로 한다.

[0037] 본 발명의 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법에서, 상기 단일 마스크는 광이 투과하지 못하는 비 투과영역, 광의 일부만이 투과하는 반 투과영역 및 광이 모두 투과되는 투과영역을 포함하는 하프 톤 마스크인 것을 특징으로 한다.

### 발명의 효과

[0038] 실시 예에 따른 본 발명은 터치 스크린이 내장된 액정 표시장치에서 하부 기판의 PAS2 보호층과 화소 전극(Pixel ITO)을 하나의 마스크를 이용하여 형성시킬 수 있다.

[0039] 실시 예에 따른 본 발명은 터치 스크린이 내장된 액정 표시장치에서 하부 기판의 공통 전극과 도전성 라인을 하나의 마스크를 이용하여 형성시킬 수 있다.

[0040] 실시 예에 따른 본 발명은 하부 기판의 구성들을 형성하는 소재로 저온 다결정 실리콘(LTPS)을 적용하여 터치 스크린이 내장된 액정 표시장치의 구동 성능을 향상시킬 수 있다.

[0041] 실시 예에 따른 본 발명은 하부 기판의 형성 시 마스크 공정을 줄여 터치 스크린이 내장된 액정 표시장치의 제조비용을 절감시킬 수 있다.

[0042] 실시 예에 따른 본 발명은 하부 기판의 제조공정을 단순화시켜 터치 스크린이 내장된 액정 표시장치의 제조효율을 향상시킬 수 있다.

[0043] 실시 예에 따른 본 발명은 하부 기판에 형성된 데이터 전극과 화소 전극의 컨택 구조를 개선하여 컨택 성능을 높일 수 있다. 이를 통해, 터치 스크린이 내장된 액정 표시장치의 구동 성능을 향상시킬 수 있다.

### 도면의 간단한 설명

[0044] 도 1은 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치와 이의 구동방법을 개략적으로 설명하기 위한 도면.

도 2는 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 단면도.

도 3은 종래 기술에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법을 나타내는 도면.

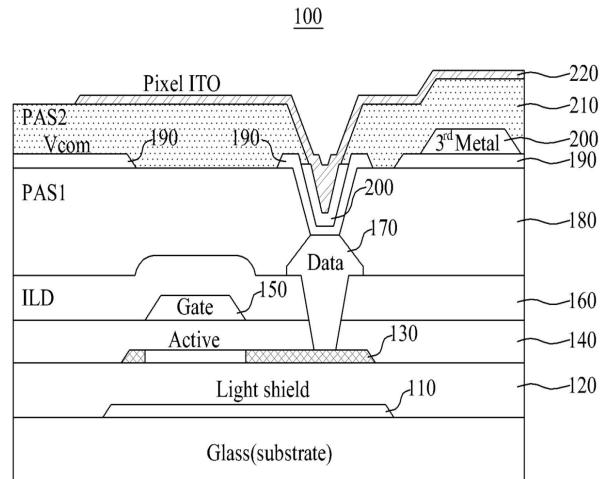

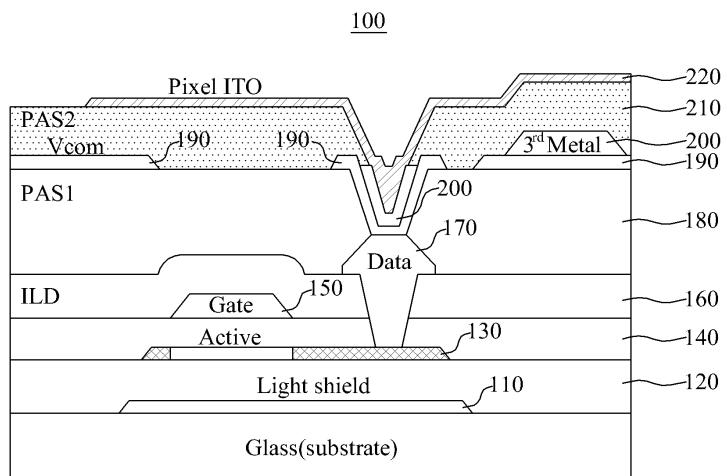

도 4는 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 도면.

도 5 내지 도 9는 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법을 나타내는 도면.

도 10은 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 도면.

도 11 내지 도 16은 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법을 나타내는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0045] 이하, 첨부된 도면을 참조하여 본 발명의 실시 예들에 따른 터치 스크린이 내장된 액정 표시장치와 이의 제조방법에 대하여 설명하기로 한다.

[0046] 본 발명의 실시 예들을 설명함에 있어서 어떤 구조물(전극, 라인, 배선 레이어, 컨택)이 다른 구조물 "상부에", "상에", "아래에" 또는 "하부에" 형성된다고 기재된 경우, 이러한 기재는 이 구조물들이 서로 접촉되어 있는 경우는 물론이고 이들 구조물들 사이에 제3의 구조물이 개재되어 있는 경우까지 포함하는 것으로 해석되어야 한다. 아울러, 상기 "상부에", "상에", "아래에" 또는 "하부에"라는 표현은 도면에 기초하여 본 발명의 구성 및 제조방법을 설명하기 위한 것이다. 따라서, 상기 "상부에", "상에", "아래에" 또는 "하부에"라는 표현은 제조 공정 과정과 제조가 완료된 이후 구성에서 서로 상이할 수 있다.

[0047] 액정 표시장치는 액정층의 배열을 조절하는 방식에 따라 TN(Twisted Nematic) 모드, VA(Vertical Alignment) 모드, IPS(In Plane Switching) 모드, FFS(Fringe Field Switching) 모드 등 다양하게 개발되어 있다.

- [0048] 그 중에서, 상기 IPS 모드와 상기 FFS 모드는 하부 기판 상에 화소 전극과 공통 전극을 배치하여 상기 화소 전극과 공통 전극 사이의 전계에 의해 액정층의 배열을 조절하는 방식이다. 특히, 상기 IPS 모드는 상기 화소 전극과 공통 전극을 평행하게 교대로 배열함으로써 양 전극 사이에서 횡전계를 일으켜 액정층의 배열을 조절하는 방식이다. 이와 같은 IPS 모드는 상기 화소 전극과 상기 공통 전극 상측 부분에서 액정층의 배열이 조절되지 않아 그 영역에서 광의 투과도가 저하되는 단점이 있다.

- [0049] 이와 같은 IPS 모드의 단점을 해결하기 위해 고안된 것이 상기 FFS 모드이다. 상기 FFS 모드는 상기 화소 전극과 상기 공통 전극을 절연층을 사이에 두고 이격되도록 형성시킨다. 이때, 하나의 전극은 판(plate) 형상 또는 패턴으로 구성하고 다른 하나의 전극은 핑거(finger) 형상으로 구성하여 양 전극 사이에서 발생되는 프린지 필드(Fringe Field)를 통해 액정층의 배열을 조절하는 방식이다.

- [0050] 본 발명의 실시 예들에 따른 터치 스크린이 내장된 액정 표시장치는 FFS 모드의 구조를 가지며, 사용자의 터치 위치를 검출하는 터치 스크린이 내장된 인-셀 터치(in-cell touch) 타입의 액정 패널과, 상기 액정 패널에 광을 공급하는 백라이트 유닛(Back Light Unit) 및 구동 회로부를 포함하여 구성된다.

- [0051] 상기 구동 회로부는 타이밍 컨트롤러(T-con), 데이터 드라이버(D-IC), 게이트 드라이버(G-IC), 센싱 드라이버, 백라이트 구동부, 구동 회로들에 구동 전원을 공급하는 전원 공급부를 포함한다.

- [0052] 여기서, 상기 구동 회로부의 전체 또는 일부는 COG(Chip On Glass) 또는 COF(Chip On Flexible Printed Circuit, Chip On Film) 방식으로 액정 패널 상에 형성될 수 있다.

- [0053] 상기 액정 패널은 액정층을 사이에 두고 합착된 상부 기판과 하부 기판을 포함하며, 복수의 화소(Cluster, 액정셀)가 매트릭스 형태로 배열된다.

- [0054] 상기 액정 패널은 데이터 전압에 따라 각 화소의 액정층을 투과하는 광의 투과율을 조절하여 영상 신호에 따른 화상을 표시한다. 또한, 상기 하부 기판에 형성된 공통 전극을 센싱 전극으로 구동시켜 사용자의 터치에 따른 정전용량의 변화를 감지하고, 이를 통해 사용자의 터치 위치를 검출한다.

- [0055] 상기 상부 기판은 복수의 화소 각각에 대응되도록 화소 영역을 정의하는 블랙 매트릭스(BM); 상기 블랙 매트릭스에 의해 정의된 각 화소 영역에 형성된 적색(Red), 녹색(Green), 청색(Blue) 컬러필터; 및 상기 적색, 녹색, 청색 컬러필터와 상기 블랙 매트릭스를 덮도록 형성되어 상부 기판을 평탄화 시키는 오버코트층을 포함한다.

- [0056] 하부 기판은 액정층을 구동시킴과 아울러, 사용자의 터치에 따른 정전용량을 이용하여 터치 위치를 검출하기 위한 복수의 화소를 가지는 화소 어레이를 포함한다.

- [0057] 상기 화소 어레이에는 후술되는 박막 트랜지스터, 공통 전극 및 화소 각각에 형성된 공통 전극을 연결하는 도전성 라인(3<sup>rd</sup> Metal)을 포함하다. 상기 상부 기판과 하부 기판은 실재(sealant)를 통해 합착되며, 액정 패널의 표시 영역(액티브 영역)은 상기 실재에 의해 외부와 차폐된다.

- [0058] 상기 하부기판 상에는 도시하지는 않았지만, 상호 직교하도록 게이트 라인과 데이터 라인이 배열되고, 상기 게이트 라인과 데이터 라인을 통해 복수의 화소가 정의된다.

- [0059] 각각의 화소에는 스위칭 소자로서 박막 트랜지스터(TFT)가 형성되고, 상기 박막 트랜지스터와 전기적으로 연결되는 화소 전극이 상기 복수의 화소 각각에 개별적으로 형성된다.

- [0060] 여기서, 상기 박막 트랜지스터는 게이트 전극, 액티브층(반도체층), 절연층 및 데이터 전극(소스/드레인 전극)을 포함하여 이루어지는데, 게이트 전극이 액티브층 아래에 위치하는 바텀 게이트(bottom gate) 구조로 이루어 질 수도 있고, 게이트 전극이 액티브층 위에 위치하는 탑 게이트(top gate) 구조로 이루어 질 수도 있다.

- [0061] 본 발명의 실시 예들에 따른 터치 스크린이 내장된 액정 표시장치는 하부 기판의 소재로 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 이용할 수 있다.

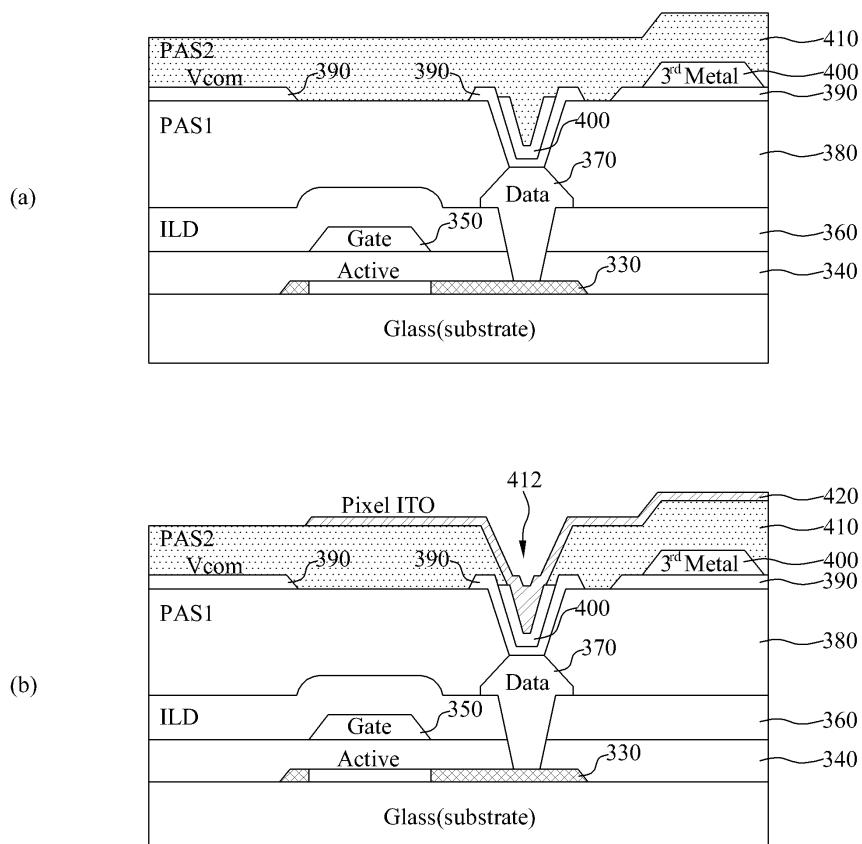

- [0062] 도 4는 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 도면이다.

- [0063] 도 4를 참조하면, 하부 기판(100)에는 복수의 화소가 형성되며, 각 화소는 게이트 전극(150), 데이터 전극(170, Source/Drain), 반도체층(130) 및 절연층으로 이루어진 박막 트랜지스터(TFT); 상기 박막 트랜지스터와 접속되어 화소에 영상 신호에 따른 화소 전압을 공급하는 화소 전극(220, Pixel ITO); 화소에 공통 전압(Vcom)을 공급하는 공통 전극(190); 및 각 화소에 형성된 공통 전극(190)을 연결하는 도전성 라인(200);을 포함한다. 여기서,

상기 도전성 라인(200)은 상기 공통 전극(190)이 사용자의 터치 검출을 위한 센싱 전극으로 구동될 수 있도록 컨택 배선으로 형성된다.

[0064] 구체적으로, 상기 하부 기판(100)의 각 화소는 글라스 기판 상에 형성되는 차광층(110, Light shield layer); 상기 차광층(110) 상에 형성되는 베퍼층(120); 상기 베퍼층(120) 상에 형성되는 액티브층(130, 반도체층); 상기 액티브층(130) 상에 형성되는 게이트 절연층(140, GI: Gate Insulation); 상기 액티브층(130)의 일부와 중첩되도록 게이트 절연층(140) 상에 금속(metal) 물질로 형성되는 게이트 전극(150); 상기 게이트 전극(150) 상에 형성되어 상기 게이트 전극(150)과 데이터 전극(170)을 절연시키는 하부 절연층(160, ILD: Inter Layer Dielectric); 트렌치(trench)에 의해 일부 영역이 노출된 액티브층(130)과 전기적으로 접속되도록 형성된 데이터 전극(170, Source/Drain);을 포함한다.

[0065] 여기서, 상기 데이터 전극(170)은 상기 액티브층(130)의 일부 영역이 노출되도록 상기 게이트 절연층(140) 및 상기 하부 절연층(160)의 일부가 식각되어 형성된 트렌치에 금속 물질이 매립되어 형성되고, 후술되는 공통 전극(190) 및 도전성 라인(200)을 경유하여 화소 전극(220, Pixel ITO)과 전기적으로 접속된다.

[0066] 또한, 상기 하부 기판(100)의 각 화소는 상기 하부 절연층(160) 상에 형성되어, 상기 게이트 전극(150) 및 데이터 전극(170)을 덮도록 형성되는 제1 보호층(180, PAS1: passivation layer); 인듐 틴 옥사이드(ITO: Indium Tin Oxide)와 같은 투명 전도성 물질로 상기 제1 보호층(180)의 상부 및 상기 데이터 전극과 접속되도록 형성되는 공통 전극(190, Vcom); 상기 공통 전극(190) 일측의 상부에 형성되어 상기 공통 전극(190)과 전기적으로 접속되는 도전성 라인(200, 3<sup>rd</sup> Metal);을 포함한다.

[0067] 여기서, 상기 공통 전극(190) 및 상기 도전성 라인(200)은 상기 데이터 전극(170)의 상부가 노출되도록 제1 보호층(180)의 일부가 식각되어 형성된 제1 컨택 홀에 순차적으로 형성된다. 이를 통해, 상기 제1 컨택 홀 영역에서 상기 데이터 전극(170)과 상기 공통 전극(190) 및 도전성 라인(200)은 전기적으로 접속된다.

[0068] 또한, 상기 하부 기판(100)의 각 화소는 상기 공통 전극(190) 및 도전성 라인(200)을 덮도록 형성되는 제2 보호층(210, PAS2); ITO와 같은 투명 전도성 물질로 상기 제2 보호층(210)의 상부 및 상기 데이터 전극(170)과 전기적으로 접속되도록 형성되는 화소 전극(220, Pixel ITO);을 포함한다.

[0069] 여기서, 상기 제2 보호층(210)과 상기 화소 전극(220)은 하나의 하프 톤 마스크(HTM: half tone mask)를 이용한 단일 마스크 공정을 통해 형성된다.

[0070] 상기 화소 전극(220)은 상기 데이터 전극(170)과 접속된 도전성 라인(200)이 노출되도록 제2 보호층(210)의 일부가 식각되어 형성된 제2 컨택 홀에 내부에도 형성되어 상기 도전성 라인(200)과 전기적으로 형성된다. 이를 통해, 상기 화소 전극(220)은 상기 공통 전극(190) 및 도전성 라인(200)을 경유하여 상기 데이터 라인(170)과 전기적으로 접속된다.

[0071] 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치는 1 프레임 기간 중 표시 기간에는 상기 하부 기판(100)의 화소 어레이에 인가된 데이터 전압에 따라 각 화소의 액정층을 투과하는 광의 투과율을 조절하여 영상 신호에 따른 화상을 표시한다.

[0072] 그리고, 비 표시 기간에는 상기 도전성 라인(200)에 의해 접속된 각 화소의 공통 전극(190)을 센싱 라인으로 구동시켜 사용자의 터치에 따른 정전용량(Ctc)의 변화를 감지한다.

[0073] 이를 위해, 상기 공통 전극(190)은 1 프레임 기간 중 표시 기간에는 공통 전압(Vcom)을 화소에 공급하고, 비 표시 기간에는 터치의 검출을 위한 센싱 전극으로 구동된다.

[0074] 사용자의 터치에 따라 각 화소의 상기 상부 기판과 하부 기판의 공통 전극(190) 사이에는 터치 정전용량(Ctc)이 형성된다. 이러한, 터치에 따른 터치 정전용량(Ctc)과 기준 정전용량을 비교하여 터치 위치(TS)를 검출한다.

[0075] 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치는 상기 제1 보호층(180, PAS1)의 상부 및 상기 제1 보호층(180)을 식각하여 형성된 제1 컨택 홀 내부에 공통 전극(190)과 도전성 라인(200)을 순차적으로 형성하여 데이터 전극(170)과 접속시키고, 하프 톤 마스크를 이용한 단일 마스크 공정으로 제2 보호층(210, PAS2) 및 화소 전극(220)을 동시에 형성한다.

[0076] 여기서, 데이터 전극(170)과 컨택 된 도전성 라인(200)과 상기 화소 전극(220)을 컨택 시켜, 상기 공통 전극(190)과 상기 도전성 라인(200)을 경유하여 데이터 전극(170)과 화소 전극(220)이 컨택 되도록 한다.

[0077] 이를 통해, 데이터 전극(170)과 화소 전극(220)의 컨택 면적을 충분히 확보하여 컨택 성능을 향상시킴으로써,

터치 스크린이 내장된 액정 표시장치의 구동 성능을 향상시킬 수 있다.

[0078] 이와 함께, 종래 기술에서 하부 절연층 상에 형성되던 PAS0 보호층을 삭제하고, 하나의 하프 톤 마스크로 제2 보호층(210, PAS2)과 화소 전극(220)을 동시에 형성함으로써, 열라인 마진을 충분히 확보할 수 있는 장점을 있다. 또한, 데이터 전극(170)과 화소 전극(220)의 컨택에 따른 제조공정 중 이물 등에 의한 컨택 불량을 줄일 수 있다.

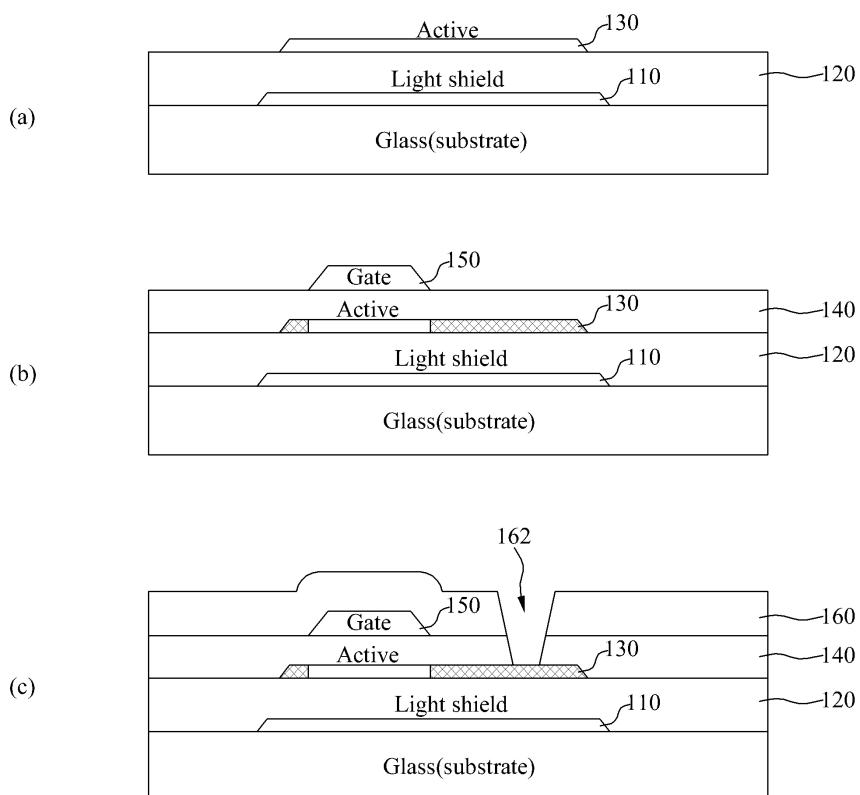

[0079] 이하, 도 5 내지 도 9를 참조하여 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법에 대하여 설명하기로 한다.

[0080] 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 도 5에 도시된 바와 같이, 하부 기판(100)의 제2 보호층(210, PAS2)과 화소 전극(220, Pixel ITO)을 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성할 수 있다. 이를 통해, 종래 기술 대비 제조공정에 소요되는 마스크를 줄이고, 이에 따른 세부공정을 줄일 수 있다. 또한, 종래 기술의 PAS0 보호층을 삭제하여 이에 따른 세부공정도 줄일 수 있다.

[0081] 구체적으로 살펴보면, 도 6(a)에 도시된 바와 같이, 기판(substrate) 상에 금속과 같이 광을 차단하는 물질로 레이어를 형성한 후, 마스크를 이용한 포토리소그래피(photolithography) 및 습식 에칭(etching, 식각) 공정을 통해 패터닝하여 차광층(110, light shield)을 형성한다. 이때, 상기 차광층(110)은 후속 공정에서 형성되는 액티브층(130)과 열라인 되도록 형성된다.

[0082] 여기서, 상기 기판은 투명한 글라스 소재 또는 플라스틱 소재가 적용될 수 있으며, 도 6에서는 기판의 소재로 글라스가 적용된 것을 일 예로 도시하고 있다.

[0083] 이후, 상기 차광층(110)을 덮도록 베퍼층(120)을 형성하고, 상기 베퍼층(120) 상에 비정질 실리콘(a-Si)을 증착하여 반도체 레이어를 형성한 후, 마스크를 이용한 포토리소그래피 및 건식 에칭 공정을 통해 상기 반도체 레이어를 패터닝하여 액티브층(130)을 형성한다. 이때, 상기 액티브층(130)은 상기 기판의 일측에서 상기 차광층(110)과 열라인 되도록 형성된다.

[0084] 이어서, 도 6(b)에 도시된 바와 같이, 상기 기판 전면에 TEOS(Tetra Ethyl Ortho Silicate) 또는 MTO(Middle Temperature Oxide)를 CVD(Chemical Vapor Deposition)로 증착하여 게이트 절연층(140)을 형성한다.

[0085] 이후, 상기 액티브층(130)과 중첩되도록 상기 게이트 절연층(140) 상에 금속(metal) 물질을 증착 한 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 게이트 전극(150)을 형성하고, 상기 게이트 전극(150)을 n-도핑(doping)한다.

[0086] 이때, 상기 게이트 전극(150)의 형성 시, 습식 에칭 공정 및 건식 에칭 공정을 수행하게 되는데, 습식 에칭 공정과 건식 에칭 공정 사이에 상기 액티브층(130)을 n<sup>+</sup> 도핑한다. 상기 액티브층(130) 상에 상기 게이트 전극(150)이 형성되어 있음으로, 상기 액티브층(130)의 전체 영역 중 상기 게이트 전극(150)과 중첩되는 않은 영역이 n<sup>+</sup> 도핑된다.

[0087] 이어서, 도 6(c)에 도시된 바와 같이, 상기 게이트 전극(150) 및 상기 게이트 절연층(140)을 덮도록 상기 기판 상에 절연물질을 증착하여 상기 게이트 전극(150)을 하부 기판의 다른 구성들과 절연시키는 하부 절연층(160, ILD: Inter Layer Dielectric)을 형성한다.

[0088] 이후, 상기 액티브층(130)의 일부와 중첩되는 상기 하부 절연층(160)의 일부 영역 및 게이트 절연층(140)의 일부 영역에 마스크를 이용한 포토리소그래피 및 드라이 에칭 공정을 수행하여, 액티브층(130)의 일부 상면을 노출(open)시키는 트렌치(162)을 형성한다.

[0089] 이어서, 도 7(a)에 도시된 바와 같이, 상기 기판 전면과 상기 트렌치(162) 내부에 금속 물질을 도포(트렌치 내부에 금속 물질 매립)한 후, 마스크를 이용한 포토리소그래피 및 습식 에칭 공정을 수행하여 데이터 전극(170, source/drain)을 형성한다.

[0090] 여기서, 상기 데이터 전극(170)은 상기 트렌치(162) 내에서 상기 액티브층(130)과 전기적으로 접속된다.

[0091] 이어서, 도 7(b)에 도시된 바와 같이, 상기 하부 절연층(160)과 데이터 전극(170)을 덮도록 제1 보호층(180, PAS1)을 형성한 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 상기 데이터 전극(170)을 노출시키는 제1 컨택 홀(182)을 형성한다.

[0092] 이어서, 도 7(c)에 도시된 바와 같이, 상기 제1 보호층(180, PAS1)의 상부와 제1 컨택 홀(182) ITO(Indium Tin

Oxide)와 같은 투명 전도성 물질과 금속 물질을 순차적으로 증착 시킨 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 상기 제1 보호층(180, PAS1) 상의 일부 영역과 상기 제1 컨택 홀(182) 내부에 공통 전극(190)을 형성한다.

[0093] 이어서, 도 8(a)에 도시된 바와 같이, 상기 제1 보호층(180, PAS1) 및 공통 전극(190) 상에 도전성 금속 물질을 도포하여 도전성 레이어를 형성한 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 상기 제1 보호층(180, PAS1)의 상부 일측과 상기 제1 컨택 홀(182) 내부에 도전성 라인(200)을 형성한다.

[0094] 여기서, 상기 공통 전극(190)과 상기 도전성 라인(200)은 전기적으로 접속되고, 상기 제1 보호층(180, PAS1) 상부에 형성된 공통 전극(190)에는 공통전압(Vcom)이 공급된다.

[0095] 한편, 상기 제1 컨택 홀(182) 내부에 형성된 공통 전극(190)은 데이터 전극(170)과 후술되는 화소 전극(220, Pixel ITO)을 전기적으로 접속시키는 컨택 전극의 용도로 형성되므로 공통전압(Vcom)이 공급되지 않는다.

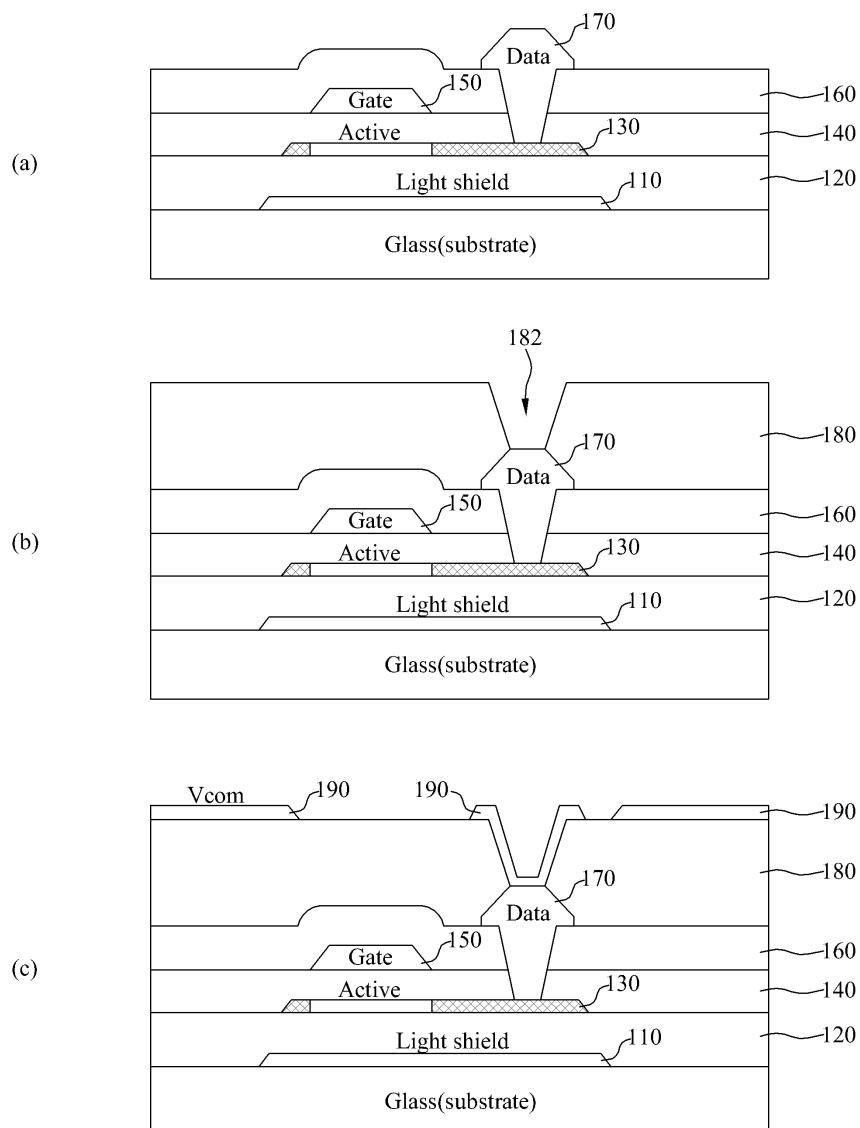

[0096] 이어서, 도 8(b)에 도시된 바와 같이, 상기 공통 전극(190)과 도전성 라인(200)을 덮도록 제2 보호층(210, PAS2)을 형성한 후, 하프 톤 마스크(HTM: half tone mask)를 이용한 포토리소그래피 공정, 에칭 공정 및 애싱(ashing) 공정을 수행하여 제2 보호층(210, PAS2)의 일부 영역에 제2 컨택 홀(212)을 형성한다.

[0097] 여기서, 상기 제2 컨택 홀(212)은 상기 데이터 전극(170)과 대응되는 영역에 형성되며, 상기 데이터 전극(170)과 전기적으로 접속된 도전성 라인(200)을 노출시키도록 형성된다.

[0098] 이후, 상기 제2 보호층(210, PAS2)의 상부 및 제2 컨택 홀(212) 내부에 ITO와 같은 투명 전도성 물질로 화소 전극(220, pixel ITO)을 형성한다. 즉, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해, 상기 제2 보호층(210, PAS2) 및 화소 전극(220)을 동시에 형성할 수 있다.

[0099] 여기서, 상기 화소 전극(220)은 상기 제2 컨택 홀(212) 내에서 상기 도전성 라인(200)과 전기적으로 접속된다. 이를 통해, 상기 데이터 전극(170)은 상기 제1 컨택 홀(182) 내에 형성된 공통 전극(190) 및 도전성 라인(200)을 경유하여 화소 전극(220)과 전기적으로 접속된다.

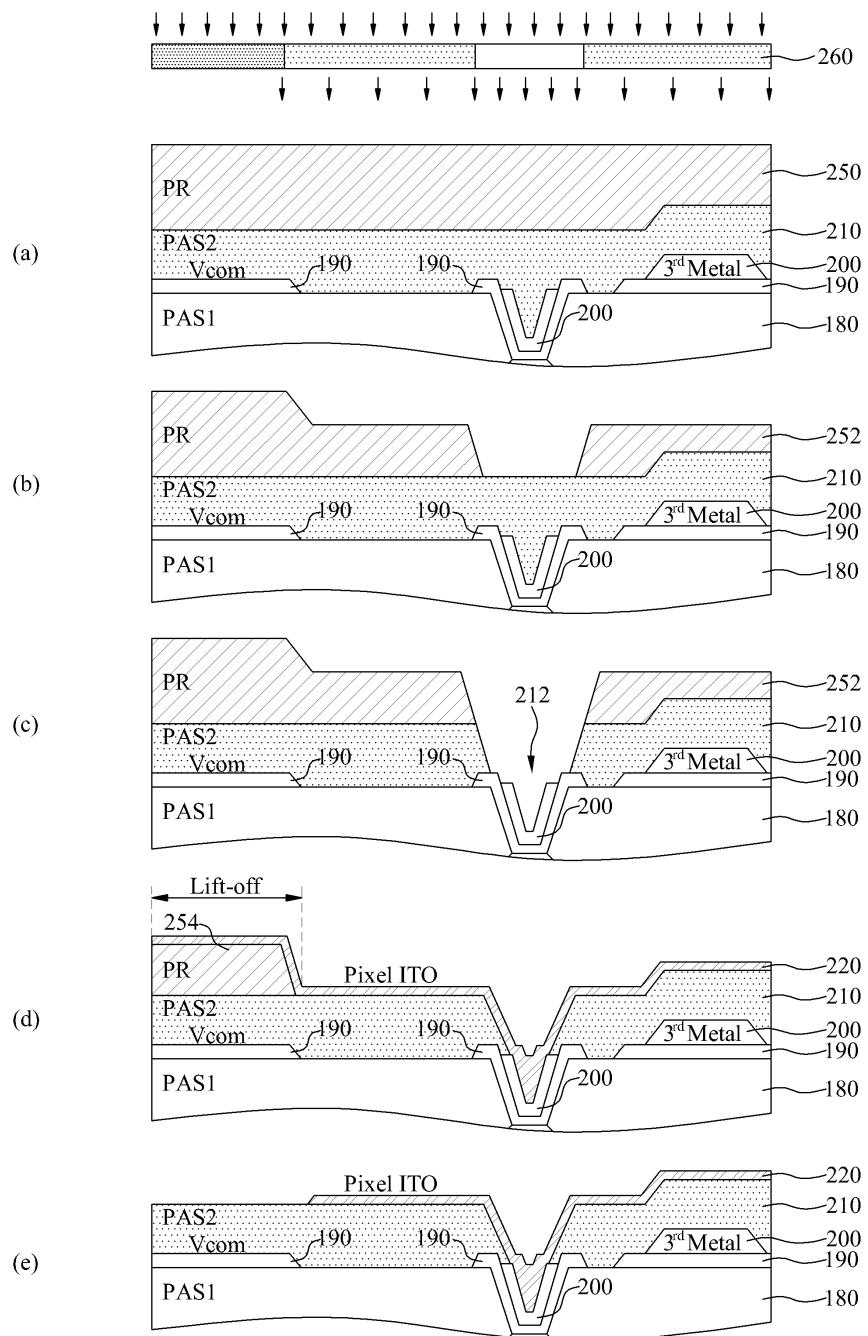

[0100] 이하, 도 9를 결부하여 상기 하프 톤 마스크를 이용한 상기 제2 보호층(210, PAS2) 및 상기 화소 전극(220)의 형성 방법에 대하여 구체적으로 살펴보기로 한다.

[0101] 도 9(a)에 도시된 바와 같이, 상기 공통 전극(190)과 도전성 라인(200)을 덮도록 제2 보호층(210, PAS2)을 형성한다.

[0102] 이후, 상기 제2 보호층(210, PAS2) 상에 포토레지스트(photoresist) 일 예로서, 포토 아크릴(photo acryl) 물질을 도포하여 포토레지스트층(250, 이하 "PR층"이라 함)을 형성한다.

[0103] 이후, 하프 톤 마스크(260, HTM: half tone mask)를 이용한 포토리소그래피 공정 및 에칭(etching) 공정을 수행하여 도 9(b)에 도시된 바와 같이, 요철(凹凸) 형상을 가지는 포토레지스트 패턴(252, 이하 "PR패턴"이라 함)을 형성한다. 즉, 하프 톤 마스크(260)를 이용하여 상기 PR층(250) 상에 광을 조사함으로써, 상기 제2 컨택 홀(212) 및 상기 화소 전극(220)의 형성 시 마스크(mask)로 이용되는 PR패턴(252)을 형성한다.

[0104] 여기서, 상기 하프 톤 마스크(260)는 광이 투과하지 못하는 비 투과영역, 광의 일부만이 투과하는 반 투과영역 및 광이 모두 투과되는 투과영역을 구비한다. 따라서, 상기 하프 톤 마스크(260)를 통해 PR층(250)을 패터닝하여 서로 다른 폭 및 두께를 가지는 복수의 PR패턴(252)을 형성시킬 수 있다.

[0105] 이와 같이, 하프 톤 마스크(260)를 이용하면 비 투과영역에 대응되는 PR층(250)은 그대로 잔존하고, 반 투과영역에 대응되는 PR층(250)은 일부만 잔존하고, 투과영역에 대응되는 PR층(250)은 모두 제거시켜 상기 제2 보호층(210, PAS2)의 일부를 노출시킬 수 있다.

[0106] 이어서, 도 9(c)에 도시된 바와 같이, 상기 PR패턴(252)을 마스크로 이용하여 상기 제2 보호층(210, PAS2)의 노출된 영역을 건식 에칭한다. 이를 통해, 제2 컨택 홀(212)을 형성한다. 이때, 상기 제2 컨택 홀(212)에 의해 상기 제1 컨택 홀(162)에 형성된 도전성 라인(200)이 노출된다.

[0107] 이어서, 도 9(d)에 도시된 바와 같이, 상기 제2 보호층(210, PAS2)의 일측 상에만(게이트 전극의 상부) PR패턴이 잔존하도록 상기 PR패턴(252)을 애싱(ashing)한 후, 상기 제2 보호층(210, PAS2)과 잔존하는 PR패턴(254) 상부에 ITO(Indium Tin Oxide)를 증착하여 화소 전극(220)을 형성한다.

[0108] 이어서, 도 9(e)에 도시된 바와 같이, 게이트 전극(170)의 상부에 잔존하는 PR패턴(254)을 리프트 오프(lift-

off) 시켜 제2 보호층(210, PAS2)과 화소 전극(220)의 형성을 완료한다.

[0109] 도 9을 참조한 설명과 같이, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해, 제2 보호층(210, PAS 2)과 화소 전극(220)을 동시에 형성할 수 있다.

[0110] 상술한 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 하부 기판의 제조 시 종래 기술 대비 1매의 마스크를 줄이고, 이에 따른 세부 공정을 종래 기술 대비 12.2% 줄여(155 steps → 136 steps으로 줄임) 제조비용을 절감시키고, 제조효율을 향상시킬 수 있다.

[0111] 또한, 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 하나의 하프 톤 마스크로 제2 보호층(210, PAS2)과 화소 전극(220)을 동시에 형성함으로써, 제조 공정에서의 얼라인 마진을 확보할 수 있다.

[0112] 또한, 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치 및 제조방법은 하부 기판에 형성된 데이터 전극과 화소 전극의 컨택 성능을 높여 구동 성능을 향상시킬 수 있다.

[0113] 또한, 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치 및 제조방법은 하부 기판의 소재로 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 적용하여 구동 성능을 향상시킬 수 있다.

[0114] 이하, 도 10을 참조하여 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치에 대하여 설명하기로 한다.

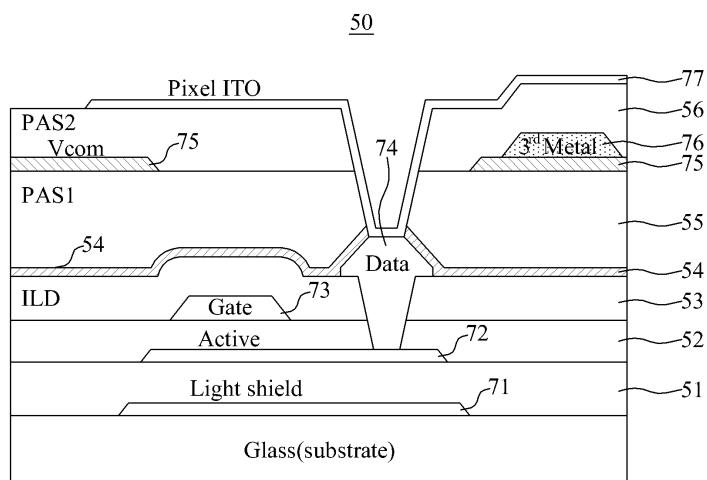

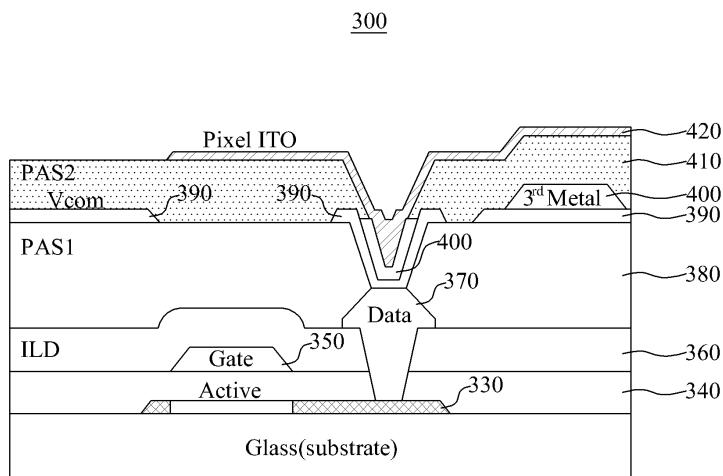

[0115] 도 10은 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판 구조를 나타내는 도면이다. 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판(300)을 설명함에 있어, 도 4에 도시된 본 발명의 제1 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 하부 기판(100)과 동일 또는 유사한 구성에 대한 설명은 생략될 수 있다.

[0116] 도 10을 참조하면, 하부 기판(300)에는 복수의 화소가 형성되며, 각 화소는 게이트 전극(350), 데이터 전극(370, Source/Drain), 액티브층(330, 반도체층) 및 절연층으로 이루어진 박막 트랜지스터(TFT); 상기 박막 트랜지스터와 접속되어 화소에 영상 신호에 따른 화소 전압을 공급하는 화소 전극(420, Pixel ITO); 화소에 공통 전압(Vcom)을 공급하는 공통 전극(390); 및 각 화소에 형성된 공통 전극(390)을 연결하는 도전성 라인(400);을 포함한다. 여기서, 상기 도전성 라인(400)은 상기 공통 전극(390)이 사용자의 터치 검출을 위한 센싱 전극으로 구동될 수 있도록 컨택 배선으로 형성된다.

[0117] 구체적으로, 상기 하부 기판(300)의 각 화소는 글라스 기판 상에 형성되는 액티브층(330, 반도체층); 상기 액티브층(330) 상에 형성되는 게이트 절연층(340, GI: Gate Insulation); 상기 액티브층(330)의 일부와 중첩되도록 게이트 절연층(340) 상에 금속(metal) 물질로 형성되는 게이트 전극(350); 상기 게이트 전극(350) 상에 형성되어 상기 게이트 전극(350)과 데이터 전극(370)을 절연시키는 하부 절연층(360, ILD: Inter Layer Dielectric); 트렌치(trench)에 의해 일부 영역이 노출된 액티브층(330)과 전기적으로 접속되도록 형성된 데이터 전극(370, Source/Drain);을 포함한다.

[0118] 여기서, 상기 데이터 전극(370)은 상기 액티브층(330)의 일부 영역이 노출되도록 상기 게이트 절연층(340) 및 상기 하부 절연층(360)의 일부가 식각되어 형성된 트렌치에 금속 물질이 매립되어 형성되고, 후술되는 공통 전극(390) 및 도전성 라인(400)을 경유하여 화소 전극(420, Pixel ITO)과 전기적으로 접속된다.

[0119] 또한, 상기 하부 기판(300)의 각 화소는 상기 하부 절연층(360) 상에 형성되어, 상기 게이트 전극(350) 및 상기 데이터 전극(370)을 덮도록 형성되는 제1 보호층(380, PAS1: passivation layer); 인듐 틴 옥사이드(ITO: Indium Tin Oxide)와 같은 투명 전도성 물질로 상기 제1 보호층(380)의 상부 및 상기 데이터 전극과 접속되도록 형성되는 공통 전극(390, Vcom); 상기 공통 전극(390) 일측의 상부에 형성되어 상기 공통 전극(390)과 전기적으로 접속되는 도전성 라인(400, 3<sup>rd</sup> Metal);을 포함한다.

[0120] 여기서, 상기 공통 전극(390) 및 상기 도전성 라인(400)은 하나의 하프 톤 마스크(HTM: half tone mask)를 이용한 단일 마스크 공정을 통해 형성된다.

[0121] 상기 공통 전극(390) 및 상기 도전성 라인(400)은 상기 데이터 전극(370)의 상부가 노출되도록 제1 보호층(380)의 일부가 식각되어 형성된 제1 컨택 홀에 순차적으로 형성된다. 이를 통해, 상기 제1 컨택 홀 영역에서 상기 데이터 전극(370)과 상기 공통 전극(390) 및 도전성 라인(400)은 전기적으로 접속된다.

[0122] 또한, 상기 하부 기판(300)의 각 화소는 상기 공통 전극(390) 및 도전성 라인(400)을 덮도록 형성되는 제2 보호

층(410, PAS2); ITO와 같은 투명 전도성 물질로 상기 제2 보호층(410)의 상부 및 상기 데이터 전극(470)과 전기적으로 접속되도록 형성되는 화소 전극(420, Pixel ITO);을 포함한다.

[0123] 여기서, 상기 제2 보호층(410)과 상기 화소 전극(420)은 하나의 하프 톤 마스크(HTM: half tone mask)를 이용한 단일 마스크 공정을 통해 형성된다.

[0124] 상기 화소 전극(420)은 상기 데이터 전극(370)과 접속된 도전성 라인(400)이 노출되도록 제2 보호층(410)의 일부가 식각되어 형성된 제2 컨택 홀에 내부에도 형성되어 상기 도전성 라인(400)과 전기적으로 형성된다. 이를 통해, 상기 화소 전극(420)은 상기 공통 전극(390) 및 도전성 라인(400)을 경유하여 상기 데이터 라인(370)과 전기적으로 접속된다.

[0125] 상기 공통 전극(390)은 1 프레임 기간 중 표시 기간에는 공통 전압(Vcom)을 화소에 공급하고, 비 표시 기간에는 터치의 접촉을 위한 센싱 전극으로 구동된다.

[0126] 상술한 바와 같이, 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치는 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 상기 제1 보호층(380, PAS1)의 상부 및 상기 제1 보호층(380)을 식각하여 형성된 제1 컨택 홀 내부에 공통 전극(390)과 도전성 라인(400)을 동시에 형성한다.

[0127] 이를 통해, 상기 공통 전극(390)과 상기 도전성 라인(400)을 경유하여 데이터 전극(370)과 화소 전극(420)이 컨택 되도록 한다. 따라서, 데이터 전극(370)과 화소 전극(420)의 컨택 면적을 충분히 확보하여 컨택 성능을 향상 시킴으로써, 터치 스크린이 내장된 액정 표시장치의 구동 성능을 향상시킬 수 있다.

[0128] 이와 함께, 종래 기술에서 하부 절연층 상에 형성되던 차광층 및 PAS0 보호층을 삭제하고, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 상기 제2 보호층(410, PAS2)과 화소 전극(420, Pixel ITO)을 동시에 형성함으로써, 열라인 마진을 충분히 확보할 수 있는 장점이 있다. 또한, 데이터 전극(370)과 화소 전극(420)의 컨택에 따른 제조공정 중 이물 등에 의한 컨택 불량을 줄일 수 있다.

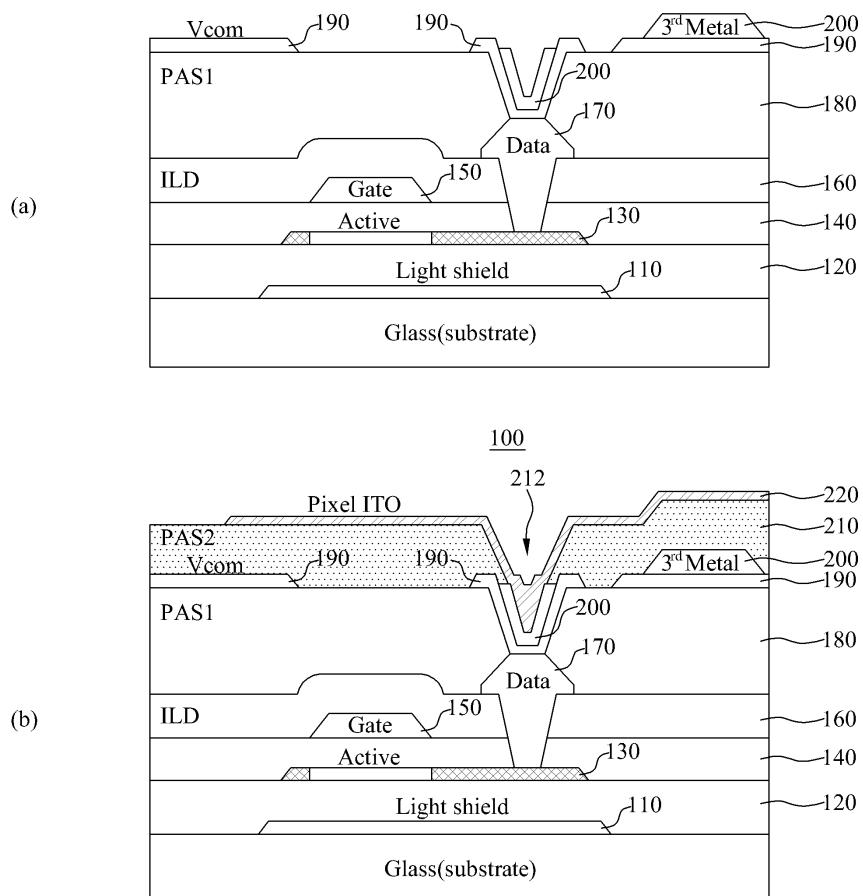

[0129] 이하, 도 11 내지 도 16을 참조하여 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조 방법에 대하여 설명하기로 한다.

[0130] 도 11 내지 도 16은 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법을 나타내는 도면이다.

[0131] 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 도 11에 도시된 바와 같이, 하부 기판(300)의 공통 전극(390)과 도전성 라인(400)을 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성할 수 있다. 또한, 제2 보호층(210, PAS2)과 화소 전극(220, Pixel ITO)을 하프 톤 마스크를 이용한 단일 마스크 공정을 통해 형성할 수 있다.

[0132] 이를 통해, 종래 기술 대비 제조공정에 소요되는 마스크를 줄이고, 이에 따른 세부공정을 줄일 수 있다. 또한, 도 2에 도시된 종래 기술에 따른 터치 스크린을 포함하는 액정 표시장치의 하부 기판에 적용되었던 PAS0 보호층 및 차광층을 삭제하여 이에 따른 세부공정도 줄일 수 있다.

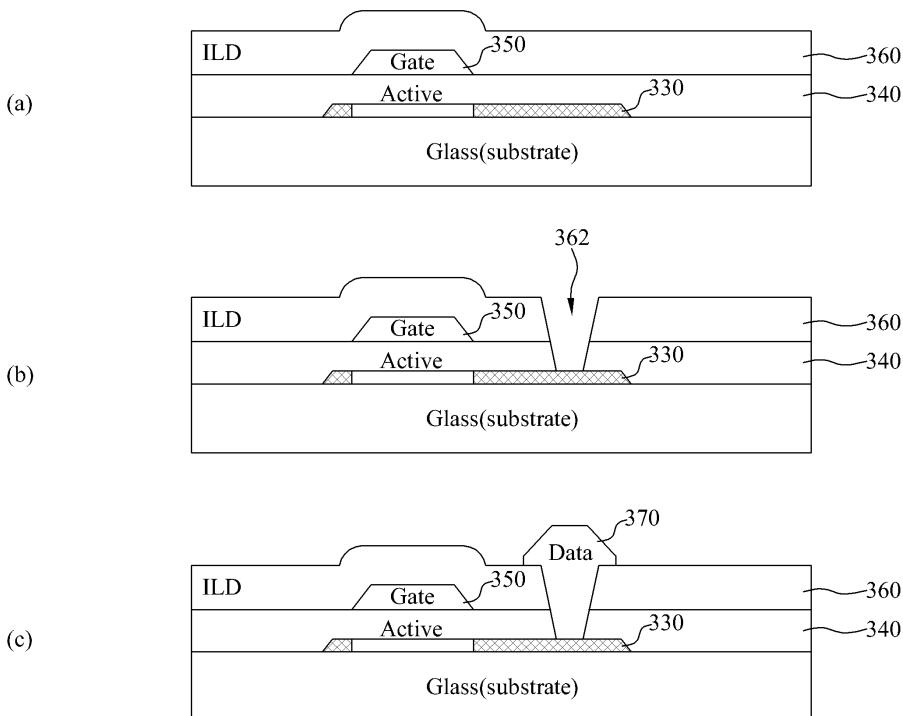

[0133] 구체적으로 살펴보면, 도 12(a)에 도시된 바와 같이, 기판(substrate) 상에 비정질 실리콘(a-Si)을 증착하여 반도체 레이어를 형성한 후, 마스크를 이용한 포토리소그래피 및 전식 에칭 공정을 통해 상기 반도체 레이어를 패터닝하여 액티브층(330)을 형성한다.

[0134] 여기서, 상기 기판은 투명한 글라스 소재 또는 플라스틱 소재가 적용될 수 있으며, 도 12에서는 기판의 소재로 글라스가 적용된 것을 일 예로 도시하고 있다.

[0135] 이후, 상기 기판 전면에 TEOS(Tetra Ethyl Ortho Silicate) 또는 MTO(Middle Temperature Oxide)를 CVD(Chemical Vapor Deposition)로 증착하여 게이트 절연층(340)을 형성한다.

[0136] 이후, 상기 액티브층(330)과 중첩되도록 상기 게이트 절연층(340) 상에 금속(metal) 물질을 증착 한 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 게이트 전극(350)을 형성한다.

[0137] 이후, 상기 게이트 전극(150) 및 상기 게이트 절연층(140)을 덮도록 상기 기판 상에 절연물질을 증착하여 상기 게이트 전극(350)을 하부 기판의 다른 구성들과 절연시키는 하부 절연층(360, ILD: Inter Layer Dielectric)을 형성한다.

[0138] 이어서, 상기 도 12(b)에 도시된 바와 같이, 상기 액티브층(330)의 일부와 중첩되는 상기 하부 절연층(360)의

일부 영역 및 게이트 절연층(340)의 일부 영역에 마스크를 이용한 포토리소그래피 및 드라이 에칭 공정을 수행하여, 액티브층(330)의 일부 상면을 노출(open)시키는 트렌치(362)을 형성한다.

[0139] 이어서, 도 12(c)에 도시된 바와 같이, 상기 기판 전면과 상기 트렌치(162) 내부에 금속 물질을 도포(트렌치 내부에 금속 물질 매립)한 후, 마스크를 이용한 포토리소그래피 및 습식 에칭 공정을 수행하여 데이터 전극(370, source/drain)을 형성한다.

[0140] 여기서, 상기 데이터 전극(370)은 상기 트렌치(362) 내에서 상기 액티브층(330)과 전기적으로 접속된다.

[0141] 이어서, 도 13(a)에 도시된 바와 같이, 상기 하부 절연층(360)과 데이터 전극(370)을 덮도록 제1 보호층(380, PAS1)을 형성한 후, 마스크를 이용한 포토리소그래피 및 에칭 공정을 수행하여 상기 데이터 전극(370)을 노출시키는 제1 컨택 홀(382)을 형성한다.

[0142] 이후, 상기 제1 보호층(380, PAS1)의 상부와 제1 컨택 홀(382) 내부에 ITO(Indium Tin Oxide)와 같은 투명 전도성 물질과 금속 물질을 순차적으로 증착 시킨다.

[0143] 이어서, 도 13(b)에 도시된 바와 같이, 하프 톤 마스크(HTM: half tone mask)를 이용한 포토리소그래피 공정, 에칭 공정 및 애싱(ashing) 공정을 수행하여 상기 제1 보호층(380, PAS1)의 상의 일부 영역과 상기 제1 컨택 홀(382) 내부에 공통 전극(390) 및 도전성 라인(400)을 형성한다. 즉, 하나의 마스크를 이용하여 상기 공통 전극(390) 및 상기 도전성 라인(400)을 동시에 형성한다.

[0144] 여기서, 상기 공통 전극(390)과 상기 도전성 라인(400)은 전기적으로 접속되고, 상기 제1 보호층(380, PAS1) 상부에 형성된 공통 전극(390)에는 공통전압(Vcom)이 공급된다.

[0145] 한편, 상기 제1 컨택 홀(382) 내부에 형성된 공통 전극(390)은 데이터 전극(370)과 후술되는 화소 전극(420, Pixel ITO)을 전기적으로 접속시키는 컨택 전극의 용도로 형성되므로 공통전압(Vcom)이 공급되지 않는다.

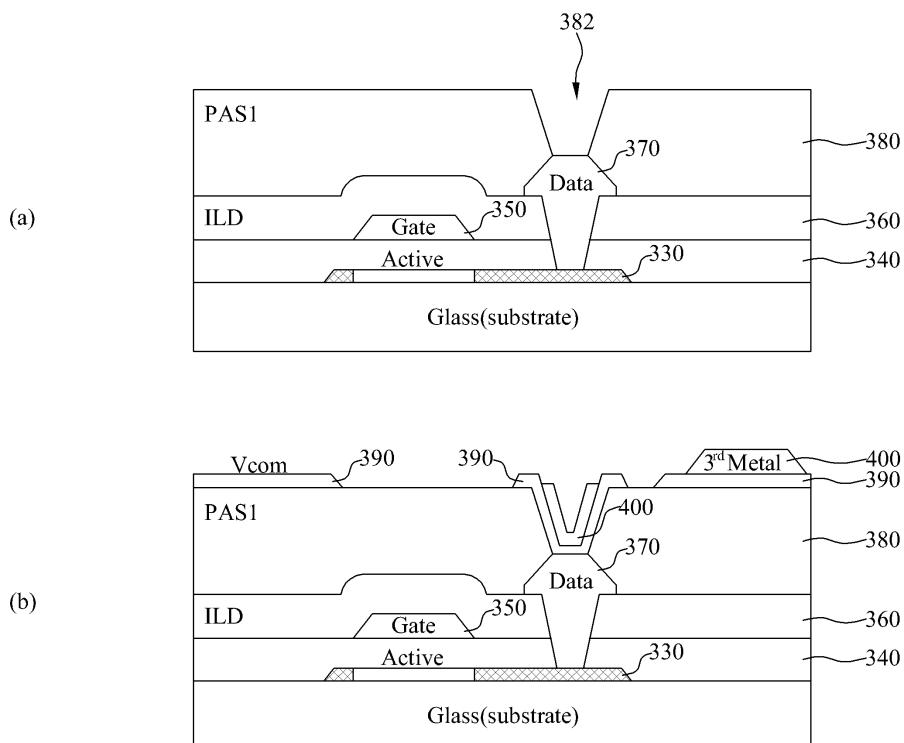

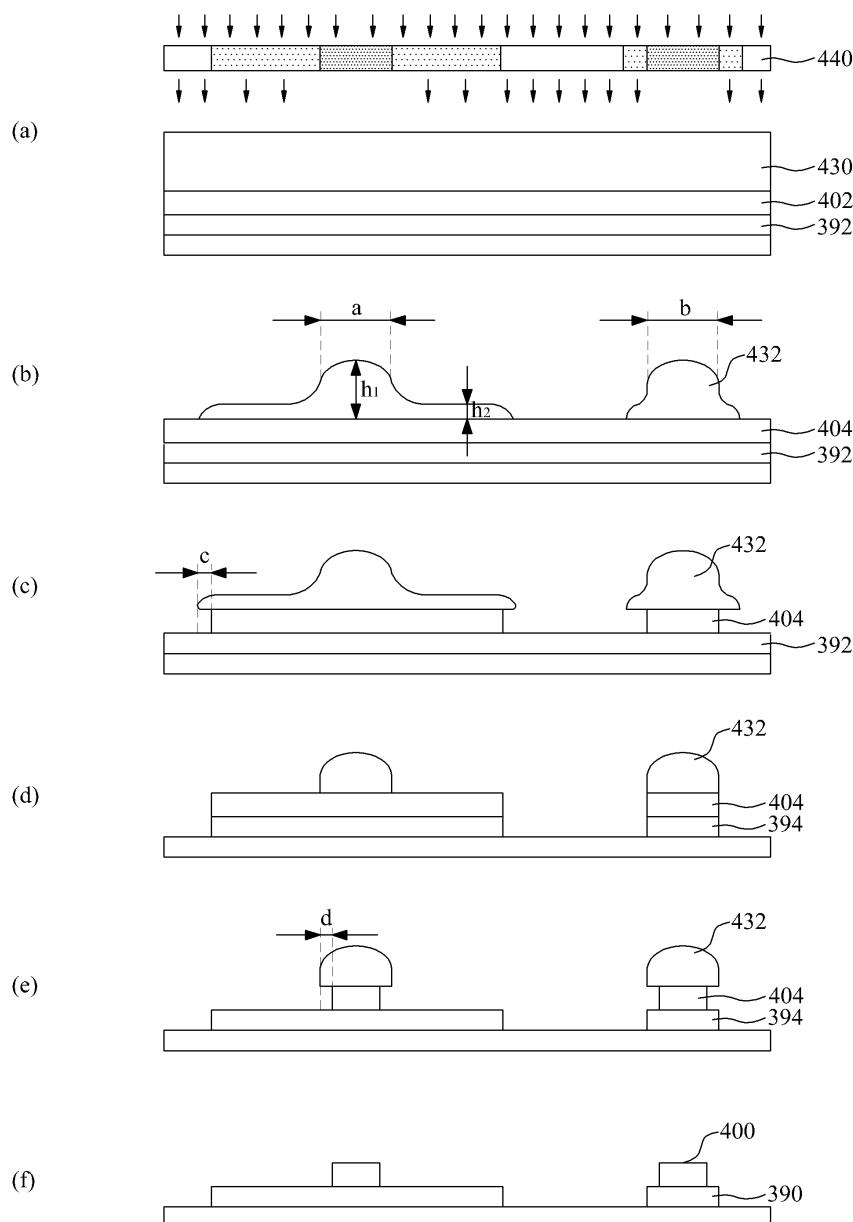

[0146] 이하, 도 14를 결부하여 상기 하프 톤 마스크를 이용한 상기 공통 전극(390) 및 상기 도전성 라인(400)의 형성 방법에 대하여 구체적으로 살펴보기로 한다.

[0147] 도 14(a)에 도시된 바와 같이, 소정 구조(일 예로, 제1 보호층(380, PAS1)) 상에 ITO(Indium Tin Oxide)와 금속 물질을 순차적으로 증착하여 ITO 레이어(392)와 금속 레이어(402)를 순차적으로 형성한다.

[0148] 이후, 상기 금속 레이어(402) 상에 포토레지스트(photoresist) 일 예로서, 포토 아크릴(photo acryl) 물질을 도포하여 포토레지스트층(430, 이하 "PR층"이라 함)을 형성한다.

[0149] 이어서, 하프 톤 마스크(440)를 이용한 포토리소그래피 공정을 수행하여 도 14(b)에 도시된 바와 같이, 상기 금속 레이어(202) 상에 요철(凹凸) 형상을 가지는 포토레지스트 패턴(432, 이하 "PR패턴"이라 함)을 형성한다. 즉, 하프 톤 마스크(440)를 이용하여 상기 PR층(430) 상에 광을 조사함으로써, 상기 공통 전극(390) 및 상기 도전성 라인(400)의 형성 시 마스크(mask)로 이용되는 복수의 PR패턴(432)을 형성한다.

[0150] 여기서, 상기 하프 톤 마스크(440)는 광이 투과하지 못하는 비 투과영역, 광의 일부만이 투과하는 반 투과영역 및 광이 모두 투과되는 투과영역을 구비한다. 따라서, 상기 하프 톤 마스크(440)를 통해 PR층(430)을 패터닝하여 서로 다른 폭 및 두께를 가지는 복수의 PR패턴(432)을 형성시킬 수 있다.

[0151] 이와 같이, 하프 톤 마스크(440)를 이용하면 비 투과영역에 대응되는 PR층(430)은 그대로 잔존하고, 반 투과영역에 대응되는 PR층(250)은 일부만 잔존하고, 투과영역에 대응되는 PR층(430)은 모두 제거된다.

[0152] 일 예로서, 50mJ ~ 100mJ의 노광량으로 PR층(430)에 광을 조사하여 복수의 PR패턴(432)을 형성할 수 있다. 광이 투과하지 않은 PR패턴 영역의 높이 h1은 1.5um ~ 3.0 um, 하프 톤을 통해 광이 일부만이 투과된 PR패턴 영역의 높이 h2는 0.2um ~ 1.0um로 형성될 수 있다.

[0153] 또한, 복수의 PR패턴 중 제1 PR패턴의 폭(a)과 제2 PR패턴의 폭(b)은 2um ~ 5um의 선폭을 가지도록 형성될 수 있으며, 상기 제1 PR패턴의 폭과 제2 PR패턴의 폭(b)은 상이하게 형성할 수 있다. 배선의 직진성 확보를 위해, 제1 PR패턴의 폭(a)은 좁게, 제2 PR패턴의 폭(b)은 넓게 형성할 수 있다.

[0154] 이어서, 도 14(c)에 도시된 바와 같이, 상기 PR패턴(432)을 마스크로 이용하여 상기 금속 레이어(402)를 1차 에칭한다. 이를 통해, 금속 패턴(404)을 형성한다. 이때, 1차 에칭을 통해 형성되는 금속 패턴(404)과 PR패턴(432)의 임계치수 "c"(CD: critical dimension)는 0.5um 이하가 되도록 한다.

[0155] 이어서, 도 14(d)에 도시된 바와 같이, 상기 PR패턴(432)을 애싱(ashing)한 후, 상기 금속 패턴(404)을 마스크

로 이용하여 상기 ITO 레이어(392)를 예칭한다. 이를 통해, ITO 패턴(494)을 형성한다. 이때, 상기 ITO 레이어(392)의 예칭 공정 시, 플라즈마(plasma)에 따른 유기막 손상 즉, 포토 아크릴에 손상이 발생하여 액정 패널이 구동될 때 얼룩이 발생될 수 있다. 따라서, 이를 방지하기 위해 상기 PR패턴(432)의 애싱 공정은 상기 ITO 레이어(392)의 예칭 공정 이전에 수행되도록 한다.

[0156] 이어서, 도 14(e)에 도시된 바와 같이, 상기 PR패턴(432)의 애싱 공정 이후에 잔존하는 PR패턴을 마스크로 이용하여 상기 금속 레이어(402)의 1차 예칭을 통해 형성된 금속 패턴(404)을 2차 예칭한다. 이때, 2차 예칭을 통해 형성되는 금속 패턴(404)과 PR패턴(432)의 임계치수 "d"(CD: critical dimension)는 0.5um 이하가 되도록 한다.

[0157] 이어서, 도 14(f)에 도시된 바와 같이, 기판 상에 잔존하는 PR패턴(432)을 애싱하여 ITO로 상기 공통 전극(390)을 형성하고, 금속 물질로 상기 도전성 라인(400)을 형성한다.

[0158] 여기서, 상기 공통 전극(390)과 도전성 라인(400)은 도 13에 도시된 바와 같이, 상기 제1 보호층(380, PAS1)의 상부 및 상기 데이터 전극(370)을 노출시키는 제1 컨택 홀(382) 내부에 동시에 형성된다.

[0159] 도 14를 참조한 설명과 같이, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해, 공통 전극(390)과 도전성 라인(400)을 동시에 형성할 수 있다.

[0160] 이어서, 도 15(a)에 도시된 바와 같이, 상기 공통 전극(390)과 도전성 라인(400)을 덮도록 상기 제1 보호층(380, PAS1) 상에 제2 보호층(210, PAS2)을 형성한다.

[0161] 이어서, 도 15(b)에 도시된 바와 같이, 하프 톤 마스크(HTM: half tone mask)를 이용한 포토리소그래피 공정, 예칭 공정 및 애싱(ashing) 공정을 수행하여 제2 보호층(410, PAS2)의 일부 영역에 제2 컨택 홀(412)을 형성한다.

[0162] 여기서, 상기 제2 컨택 홀(412)은 상기 데이터 전극(370)과 대응되는 영역에 형성되며, 상기 데이터 전극(370)과 전기적으로 접속된 도전성 라인(400)을 노출시키도록 형성된다.

[0163] 이후, 상기 제2 보호층(410, PAS2)의 상부 및 제2 컨택 홀(412) 내부에 ITO와 같은 투명 전도성 물질로 화소 전극(420, pixel ITO)을 형성한다. 즉, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해, 상기 제2 보호층(410, PAS2) 및 화소 전극(420)을 동시에 형성할 수 있다.

[0164] 여기서, 상기 화소 전극(420)은 상기 제2 컨택 홀(412) 내에서 상기 도전성 라인(400)과 전기적으로 접속된다. 이를 통해, 상기 데이터 전극(370)은 상기 제1 컨택 홀(382) 내에 형성된 공통 전극(390) 및 도전성 라인(400)을 경유하여 화소 전극(420)과 전기적으로 접속된다.

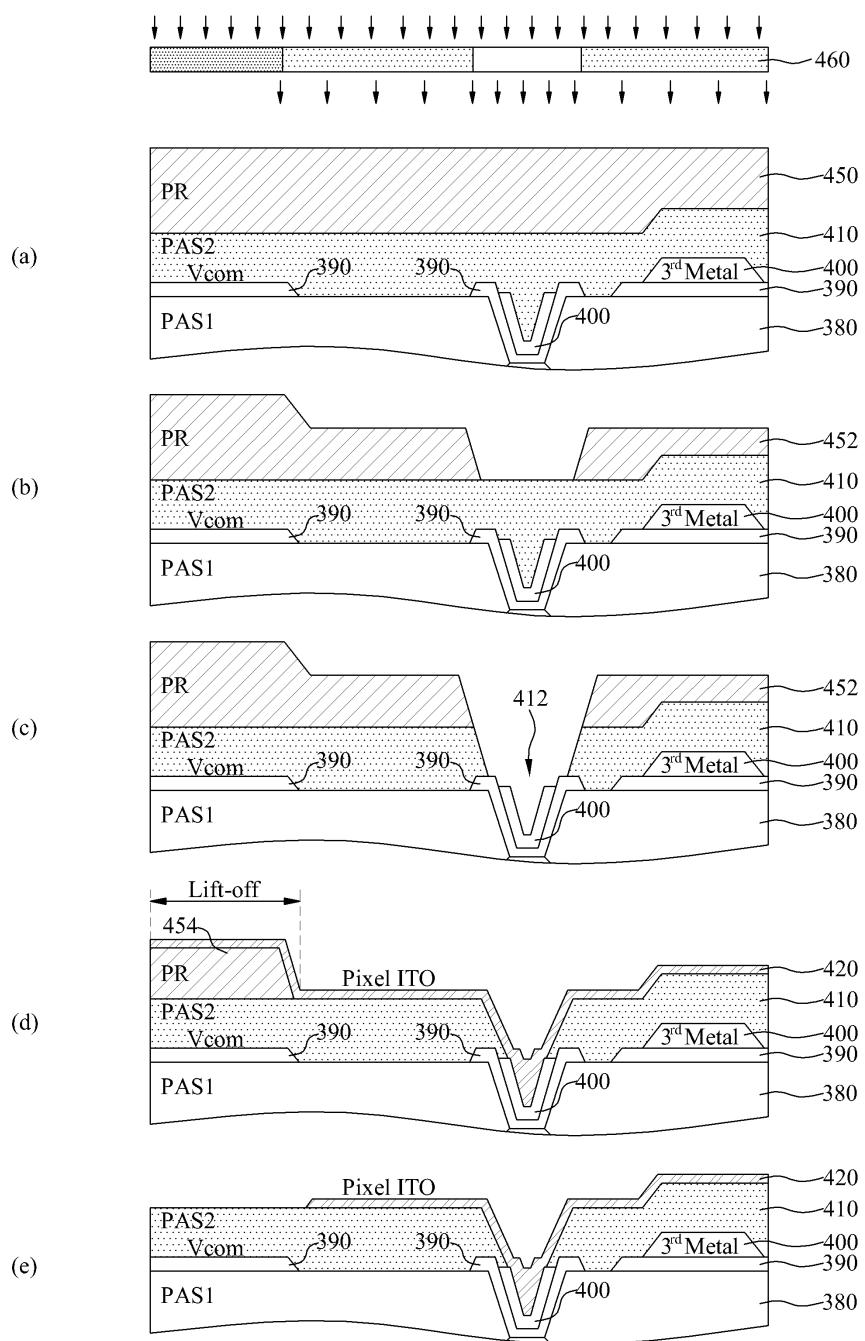

[0165] 이하, 도 16을 결부하여 상기 하프 톤 마스크를 이용한 상기 제2 보호층(410, PAS2) 및 상기 화소 전극(420)의 형성 방법에 대하여 구체적으로 살펴보기로 한다.

[0166] 도 16(a)에 도시된 바와 같이, 상기 공통 전극(390)과 도전성 라인(300)을 덮도록 제2 보호층(410, PAS2)을 형성한다.

[0167] 이후, 상기 제2 보호층(410, PAS2) 상에 포토레지스트(photoresist) 일 예로서, 포토 아크릴(photo acryl) 물질을 도포하여 PR층(450)을 형성한다.

[0168] 이후, 하프 톤 마스크(460, HTM: half tone mask)를 이용한 포토리소그래피 공정 및 예칭(etching) 공정을 수행하여 도 16(b)에 도시된 바와 같이, 요철(凹凸) 형상을 가지는 포토레지스트 PR패턴(452)을 형성한다. 즉, 하프 톤 마스크(460)를 이용하여 상기 PR층(450) 상에 광을 조사함으로써, 상기 제2 컨택 홀(412) 및 상기 화소 전극(420)의 형성 시 마스크(mask)로 이용되는 PR패턴(452)을 형성한다.

[0169] 여기서, 상기 하프 톤 마스크(460)는 광이 투과하지 못하는 비 투과영역, 광의 일부만이 투과하는 반 투과영역 및 광이 모두 투과되는 투과영역을 구비한다. 따라서, 상기 하프 톤 마스크(460)를 통해 PR층(450)을 패터닝하여 서로 다른 폭 및 두께를 가지는 복수의 PR패턴(452)을 형성시킬 수 있다.

[0170] 이와 같이, 하프 톤 마스크(460)를 이용하면 비 투과영역에 대응되는 PR층(450)은 그대로 잔존하고, 반 투과영역에 대응되는 PR층(450)은 일부만 잔존하고, 투과영역에 대응되는 PR층(450)은 모두 제거시켜 상기 제2 보호층(410, PAS2)의 일부를 노출 시킬 수 있다.

[0171] 이어서, 도 16(c)에 도시된 바와 같이, 상기 PR패턴(452)을 마스크로 이용하여 상기 제2 보호층(410, PAS2)의

노출된 영역을 건식 에칭한다. 이를 통해, 제2 컨택 홀(212)을 형성한다. 이때, 상기 제2 컨택 홀(412)에 의해 상기 제1 컨택 홀(362)에 형성된 도전성 라인(400)이 노출된다.

[0172] 이어서, 도 16(d)에 도시된 바와 같이, 상기 제2 보호층(410, PAS2)의 일측 상에만(케이트 전극의 상부) PR패턴이 잔존하도록 상기 PR패턴(452)을 애싱(ashing)한 후, 상기 제2 보호층(410, PAS2)과 잔존하는 PR패턴(454) 상부에 ITO(Indium Tin Oxide)를 증착하여 화소 전극(420)을 형성한다.

[0173] 이어서, 도 16(e)에 도시된 바와 같이, 케이트 전극(370)의 상부에 잔존하는 PR패턴(454)을 리프트 오프(lift-off)시켜 제2 보호층(410, PAS2)과 화소 전극(420)의 형성을 완료한다.

[0174] 도 16을 참조한 설명과 같이, 하나의 하프 톤 마스크를 이용한 단일 마스크 공정을 통해, 제2 보호층(410, PAS2)과 화소 전극(420)을 동시에 형성할 수 있다.

[0175] 또한, 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 하나의 하프 톤 마스크로 제2 보호층(210, PAS2)과 화소 전극(220)을 동시에 형성함으로써, 제조 공정에서의 얼라인 마진을 확보할 수 있다.

[0176] 상술한 설명에서는 상기 액티브층이 n 타입으로 도핑되는 것으로 설명하였으나, 이는 일 예를 나타낸 것이고 본 발명의 다른 실시 예에서는 상기 액티브층이 p 타입으로 도핑될 수 있다.

[0177] 상술한 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 하부 기판의 제조 시 종래 기술 대비 3매의 마스크를 줄이고, 이에 따른 세부 공정을 종래 기술 대비 28%(155 steps → 113 steps으로 줄임) 줄일 수 있다.

[0178] 따라서, 상술한 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법을 이용하면 7 마스크로 하부 기판을 제조할 수 있어, 마스크 공정 및 이에 따른 세부 공정을 줄여 터치 스크린이 내장된 액정 표시장치의 제조비용을 절감시키고, 제조효율을 향상시킬 수 있다.

[0179] 또한, 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치의 제조방법은 하부 기판에 형성된 데 이터 전극과 화소 전극의 컨택 성능을 높여 구동 성능을 향상시킬 수 있다.

[0180] 또한, 본 발명의 제2 실시 예에 따른 터치 스크린이 내장된 액정 표시장치 및 제조방법은 하부 기판의 소재로 저온 다결정 실리콘(LTPS: Low Temperature Poly Silicon)을 적용하여 구동 성능을 향상시킬 수 있다.

[0181] 본 발명이 속하는 기술분야의 당 업자는 상술한 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로, 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로 이해해야만 한다.

[0182] 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

### 부호의 설명

[0183] 100, 300: 하부 기판

110: 차광층

120: 베파층

130, 330: 액티브층

140, 340: 케이트 절연층

150, 350: 케이트 전극

160, 360: 하부 절연층

162, 362: 트렌치

170, 370: 데이터 전극

180, 380: 제1 보호층

182, 382: 제1 컨택홀

190, 390: 공통 전극

200, 400: 도전성 라인

210, 410: 제2 보호층

212, 412: 제2 컨택 홀

220, 420: 화소 전극

250, 450: PR층

252, 452: PR패턴

260, 460: 하프 톤 마스크

**도면****도면1****도면2****도면3**

| Mask | Layer         |

|------|---------------|

| 1    | Light shield  |

| 2    | Active        |

| 3    | Gate          |

| 4    | ILD & contact |

| 5    | Data (S/D)    |

| 6    | PAS0, PAS1    |

| 7    | Vcom          |

| 8    | 3rd Metal     |

| 9    | PAS2          |

| 10   | Pixel ITO     |

**도면4****도면5**

| Mask | Layer            |

|------|------------------|

| 1    | Light shield     |

| 2    | Active           |

| 3    | Gate             |

| 4    | ILD & contact    |

| 5    | Data line(S/D)   |

| 6    | PAS1             |

| 7    | Vcom             |

| 8    | 3rd Metal        |

| 9    | PAS2 & Pixel ITO |

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11

| Mask | Layer            |

|------|------------------|

| 1    | Active           |

| 2    | Gate             |

| 3    | ILD & contact    |

| 4    | Data line(S/D)   |

| 5    | PAS1             |

| 6    | Vcom & 3rd Metal |

| 7    | PAS2 & Pixel ITO |

## 도면12

## 도면13

## 도면14

## 도면15

## 도면16

|                |                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 具有内置触摸屏的液晶显示装置及其制造方法                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR1020120030704A</a>                                                                                                                                                       | 公开(公告)日 | 2012-03-29 |

| 申请号            | KR1020100092385                                                                                                                                                                        | 申请日     | 2010-09-20 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                                                                                              |         |            |

| [标]发明人         | OH KUM MI<br>오금미<br>LEE HAN SEOK<br>이한석<br>PARK WON KEUN<br>박원근                                                                                                                        |         |            |

| 发明人            | 오금미<br>이한석<br>박원근                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/136 G02F1/1333 G02F1/1362 G02F1/1368 G02F1/1343 H01L27/12                                                                                                                        |         |            |

| CPC分类号         | G02F1/13338 G02F1/136227 G02F1/1368 G02F1/136286 G02F1/13439 H01L27/1288 G02F2001/13625 G02F2001/136231 G02F2001/136236 G02F2001/13629 G02F2001/136295 G06F3/0412 G06F3/0443 G06F3/044 |         |            |

| 其他公开文献         | KR101753802B1                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                              |         |            |

**摘要(译)**

目的：提供一种具有嵌入式触摸屏的液晶显示装置及其制造方法，以减少形成下基板时的工艺数量，从而降低制造成本。结构：在第二保护层上形成第二保护层（210）。公共电极和导线。第二接触孔暴露对应于数据电极的区域的导线。像素电极（220）形成在第二保护层上和第二接触孔中。像素电极电连接到导线。第二保护层和像素电极通过单掩模工艺使用半色调掩模形成。COPYRIGHT KIPO 2012