(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년08월22일

(11) 등록번호 10-1298234

(24) 등록일자 2013년08월13일

|                       |                                                          |                                                               |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------|

| (51) 국제특허분류(Int. Cl.) | <b>G02F 1/1345</b> (2006.01) <b>G06F 3/041</b> (2006.01) | (73) 특허권자<br><b>엘지디스플레이 주식회사</b><br>서울특별시 영등포구 여의대로 128(여의도동) |

| (21) 출원번호             | <b>10-2010-0024914</b>                                   | (72) 발명자<br><b>오금미</b>                                        |

| (22) 출원일자             | <b>2010년03월19일</b>                                       | 서울특별시 서대문구 세무서2가길 47 (홍제동)                                    |

|                       | <b>심사청구일자</b> <b>2011년11월04일</b>                         | <b>김진옥</b>                                                    |

| (65) 공개번호             | <b>10-2011-0105652</b>                                   | 경기도 고양시 일산서구 강선로 169, 1507동 801호 (일산동, 후곡마을)                  |

| (43) 공개일자             | <b>2011년09월27일</b>                                       | <b>김성희</b>                                                    |

| (56) 선행기술조사문헌         | KR100790216 B1*<br>KR1020100009472 A*                    | 경기도 파주시 한마음1길 25, 금촌 주공아파트 106동 704호 (금촌동)                    |

| *는 심사관에 의하여 인용된 문헌    |                                                          |                                                               |

전체 청구항 수 : 총 12 항

심사관 : 유창훈

(54) 발명의 명칭 터치인식 횡전계형 액정표시장치 및 이의 제조 방법

(57) 요약

본 발명은, 제 1 기판과 이와 마주하는 제 2 기판 사이에 액정층이 구비되며, 공통전극과 화소전극이 모두 상기 제 1 기판의 내측면 구비되며, 컬러필터층은 상기 제 2 기판의 내측면에 구비된 액정패널과; 상기 액정패널의 상기 제 2 기판의 외측면에 면적항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 가 되도록 유기물질과 탄소나노튜브를 혼합한 물질로 제 1 두께를 가지며 형성된 정전기 방지층을 포함하는 형전계형 액정표시장치를 제공한다.

대표 도 - 도3

## 특허청구의 범위

### 청구항 1

제 1 기판과 이와 마주하는 제 2 기판 사이에 액정층이 구비되며, 공통전극과 화소전극이 모두 상기 제 1 기판의 내측면에 구비되며, 컬러필터층은 상기 제 2 기판의 내측면에 구비된 액정패널과;

상기 액정패널의 상기 제 2 기판의 외측면에 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 가 되도록 유기물질과 탄소나노튜브를 혼합한 물질로 제 1 두께를 가지며 형성된 정전기 방지층

을 포함하며, 상기 제 1 및 제 2 기판에는 다수의 화소영역을 그룹으로 하는 다수의 터치블러를 갖는 표시영역과 상기 표시영역 외측으로 비표시영역이 정의되며, 상기 공통전극은 상기 각 터치블러 별로 이격하여 형성된 것이 특징인 횡전계형 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 유기물질은 PMMA(Polymethyl Methacrylate) 또는 PET(polyethylene terephthalate)인 것이 특징인 횡전계형 액정표시장치.

### 청구항 3

제 1 항에 있어서,

상기 제 1 두께는 300Å 내지 1000Å인 것이 특징인 횡전계형 액정표시장치.

### 청구항 4

제 1 항에 있어서,

상기 제 1 기판 상의 각 화소영역의 경계에 서로 교차하며 형성된 게이트 및 데이터 배선과;

상기 각 화소영역 내에 상기 게이트 및 데이터 배선과 연결되며 형성된 박막트랜지스터와;

상기 박막트랜지스터 위로 전면에 형성된 제 1 보호층과;

상기 제 1 보호층 위로 형성된 상기 공통전극과;

상기 공통전극 위로 상기 게이트 배선과 중첩하도록 형성된 x센싱배선 및 상기 데이터 배선과 중첩하도록 형성된 y센싱배선과;

상기 공통전극과 x센싱배선 및 y센싱배선 위로 전면에 형성되며, 상기 박막트랜지스터의 드레인 전극을 노출시키는 드레인 콘택홀을 가지며 형성된 제 2 보호층과;

상기 제 2 보호층 위로 상기 드레인 콘택홀을 통해 상기 드레인 전극과 접촉하며 각 화소영역 별로 형성되며, 다수의 개구를 갖는 상기 화소전극과;

상기 제 2 기판의 내측면에 상기 각 화소영역 경계에 형성된 블랙매트릭스와;

상기 블랙매트릭스와 중첩되며 상기 각 화소영역에 대응하여 적, 녹, 청색 컬러필터 패턴이 순차 대응되도록 배치된 상기 컬러필터층

을 포함하는 횡전계형 액정표시장치.

### 청구항 5

제 4 항에 있어서,

상기 제 1 기판의 비표시영역에는,

상기 게이트 배선의 연장방향으로 동일한 라인에 배치된 상기 x센싱배선의 끝단에는 x방향 센싱회로가 구비되며,

상기 데이터 배선의 연장방향으로 동일한 라인에 배치된 상기 y센싱배선의 끝단에는 y방향 센싱회로가 구비된 것이 특징인 횡전계형 액정표시장치.

#### 청구항 6

제 1 기판 내측면 상부에 서로 교차하는 게이트 배선 및 데이터 배선과 박막트랜지스터와 공통전극과 상기 박막트랜지스터와 연결된 화소전극을 형성하는 단계와;

제 2 기판의 외측면 전면에 유기물질과 탄소나노튜브가 혼합된 유기용액을 코팅하여 제 1 두께를 가지며 면적항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 인 정전기 방지층을 형성하는 단계와;

상기 정전기 방지층이 형성된 상기 제 2 기판의 내측면에 블랙매트릭스와 컬러필터층을 형성하는 단계와;

상기 화소전극과 상기 컬러필터층이 마주하도록 상기 제 1 및 제 2 기판을 위치시키고 액정층을 개재하여 합착하는 단계

를 포함하는 횡전계형 액정표시장치의 제조 방법.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 두께는  $300\text{\AA}$  내지  $1000\text{\AA}$ 이며, 상기 코팅은 상온의 분위기에서 스피코팅장치 또는 슬릿코팅장치 중 어느 하나를 통해 진행되는 것이 특징인 횡전계형 액정표시장치의 제조 방법.

#### 청구항 8

제 1 기판의 내측면 상부에 서로 교차하는 게이트 배선 및 데이터 배선과 박막트랜지스터와 공통전극과 상기 박막트랜지스터와 연결된 화소전극을 형성하는 단계와;

제 2 기판의 내측면에 블랙매트릭스와 컬러필터층을 형성하는 단계와;

상기 화소전극과 상기 컬러필터층이 마주하도록 상기 제 1 및 제 2 기판을 위치시키고 액정층을 개재하여 합착하여 제 1 두께를 갖는 액정패널을 형성하는 단계와;

상기 액정패널을 화학약액에 노출시켜 상기 제 1 및 제 2 기판의 외측면을 식각하여 상기 제 1 두께보다 얇은 제 2 두께를 갖도록 하는 단계와;

유기물질과 탄소나노튜브가 혼합된 유기용액을 코팅하여 상기 제 2 두께를 갖는 상기 액정패널의 상기 제 2 기판의 외측면 전면에 제 3 두께를 가지며

면적항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 인 정전기 방지층을 형성하는 단계

를 포함하는 횡전계형 액정표시장치의 제조 방법.

#### 청구항 9

제 8 항에 있어서,

상기 제 3 두께는 300Å 내지 1000Å이며, 상기 코팅은 상온의 분위기에서 스픈코팅장치 또는 슬릿코팅장치 중 어느 하나를 통해 진행되는 것이 특징인 횡전계형 액정표시장치의 제조 방법.

### 청구항 10

제 6 항 또는 제 8 항에 있어서,

상기 유기물질은 PMMA(Polymethyl Methacrylate) 또는 PET(polyethylene terephthalate)인 것이 특징인 횡전계형 액정표시장치의 제조 방법.

### 청구항 11

제 6 항 또는 제 8 항에 있어서,

상기 유기용액의 코팅을 실시한 후에는 히팅 수단을 통해 가열함으로써 상기 정전기 방지층을 건조시키는 단계를 포함하는 횡전계형 액정표시장치의 제조 방법.

### 청구항 12

제 6 항 또는 제 8 항에 있어서,

상기 제 1 기판의 내측면에 상기 게이트 배선과 중첩하는 x센싱배선과, 상기 데이터 배선과 중첩하는 y센싱배선을 형성하는 단계와;

상기 제 1 기판 내측면의 비표시영역에 상기 x센싱배선의 끝단과 연결되는 x방향 센싱회로와 상기 y센싱배선의 끝단과 연결되는 y방향 센싱회로를 실장하는 단계

를 포함하는 횡전계형 액정표시장치의 제조 방법.

## 명세서

### 기술분야

[0001] 본 발명은 액정표시장치에 관한 것이며, 특히 제조 공정 중 발생하는 정전기에 의한 불량을 억제하며 터치인식이 가능한 정전기 방지층이 구비된 횡전계형 액정표시장치 및 이의 제조방법에 관한 것이다.

### 배경기술

[0002] 최근에 액정표시장치는 소비전력이 낮고, 휴대성이 양호한 기술 집약적이며, 부가가치가 높은 차세대 첨단 디스플레이(display)소자로 각광받고 있다.

[0003] 일반적으로, 액정표시장치는 액정의 광학적 이방성과 분극성질을 이용하여 구동된다. 상기 액정은 구조가 가늘고 길기 때문에 문자의 배열에 방향성을 가지고 있으며, 인위적으로 액정에 전기장을 인가하여 문자배열의 방향을 제어할 수 있다.

[0004] 따라서, 상기 액정의 문자배열 방향을 임의로 조절하면, 액정의 문자배열이 변하게 되고, 광학적 이방성에 의해 상기 액정의 문자배열 방향으로 빛이 굴절하여 화상정보를 표현할 수 있다.

[0005] 현재에는 박막트랜지스터와 상기 박막트랜지스터에 연결된 화소전극이 행렬방식으로 배열된 능동행렬 액정표시장치(AM-LCD : Active Matrix LCD 이하, 액정표시장치로 약칭함)가 해상도 및 동영상 구현능력이 우수하여 가장 주목받고 있다.

[0006] 상기 액정표시장치는 공통전극이 형성된 컬러필터 기판과 화소전극이 형성된 어레이 기판과, 상기 두 기판 사이에 개재된 액정으로 이루어지는데, 이러한 액정표시장치에서는 공통전극과 화소전극이 상하로 걸리는 전기장에

- 의해 액정을 구동하는 방식으로 투과율과 개구율 등의 특성이 우수하다.

- [0007] 그러나 상하로 결리는 전기장에 의한 액정구동은 시야각 특성이 우수하지 못한 단점을 가지고 있다.

- [0008] 따라서 상기의 단점을 극복하기 위해 시야각 특성이 우수한 횡전계형 액정표시장치가 제안되었다.

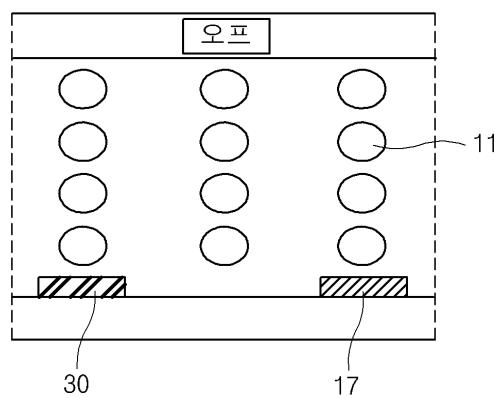

- [0009] 이하, 도 1을 참조하여 일반적인 횡전계형 액정표시장치에 관하여 상세히 설명한다.

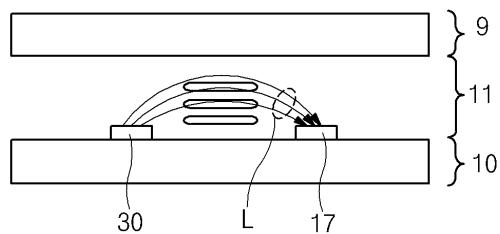

- [0010] 도 1은 일반적인 횡전계형 액정표시장치의 단면을 도시한 도면이다.

- [0011] 도시한 바와 같이, 컬러필터 기판인 상부기판(9)과 어레이 기판인 하부기판(10)이 서로 이격되어 대향하고 있으며, 이 상부 및 하부기판(9, 10)사이에는 액정층(11)이 채워져 있다.

- [0012] 상기 하부기판(10)상에는 공통전극(17)과 화소전극(30)이 동일 평면상에 형성되어 있으며, 이때, 상기 액정층(11)은 상기 공통전극(17)과 화소전극(30)에 의한 수평전계(L)에 의해 작동된다.

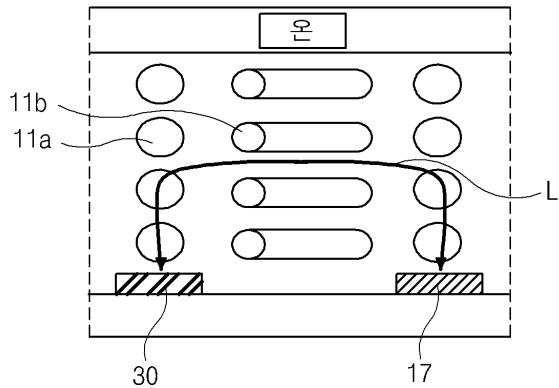

- [0013] 도 2a와 2b는 일반적인 횡전계형 액정표시장치의 온(on), 오프(off) 상태의 동작을 각각 도시한 단면도이다.

- [0014] 우선, 전압이 인가된 온(on)상태에서의 액정의 배열상태를 도시한 도 2a를 참조하면, 상기 공통전극(17) 및 화소전극(30)과 대응하는 위치의 액정(11a)의 상변이는 없지만 공통전극(17)과 화소전극(30)사이 구간에 위치한 액정(11b)은 이 공통전극(17)과 화소전극(30)사이에 전압이 인가됨으로써 형성되는 수평전계(L)에 의하여, 상기 수평전계(L)와 같은 방향으로 배열하게 된다. 즉, 상기 횡전계형 액정표시장치는 액정이 수평전계에 의해 이동하므로, 시야각이 넓어지는 특성을 띠게 된다.

- [0015] 그러므로, 상기 횡전계형 액정표시장치를 정면에서 보았을 때, 상/하/좌/우 방향으로 약 80~85°방향에서도 반전 현상 없이 가시 할 수 있다.

- [0016] 다음, 도 2b를 참조하면, 상기 액정표시장치에 전압이 인가되지 않은 오프(off)상태이므로 상기 공통전극과 화소전극 간에 수평전계가 형성되지 않으므로 액정층(11)의 배열 상태가 변하지 않는다.

- [0017] 한편, 이러한 횡전계형 액정표시장치는 특히 컬러필터 기판에 금속물질로 이루어진 공통전극이 형성되지 않는 구성을 가지므로 제조 공정 특히 모듈공정 진행시 정전기에 의한 문제를 제거하고 정전기로 인한 화질 이상을 방지하기 위해 상기 컬러필터 기판의 배면에 투명 도전성 물질인 인듐-틴-옥사이드(ITO) 또는 인듐-징크-옥사이드(ZnO)로서 배면전극을 형성하고 있다. 이러한 투명도전성 물질로 이루어진 배면전극은 그 두께가 200Å인 경우 면저항이 500Ω/sq정도가 되며, 이러한 면저항 치는 거의 금속물질로 이루어진 금속층 수준이 됨으로써 이러한 배면전극을 통해 제조 공정 중 발생하는 정전기를 외부로 방출시키는 역할을 함으로써 정전기로 인해 발생하는 문제를 방지하고 있다.

- [0018] 전술한 구성을 갖는 횡전계형 액정표시장치는 TV, 프로젝터, 휴대폰, PDA 등 다양한 응용제품에 이용되고 있다.

- [0019] 한편, 근래에 들어서는 개인 휴대가 가능한 휴대폰, PDA 또는 노트북 등에서 터치 센서가 내장되어 화면을 터치하여 동작할 수 있는 기능을 갖는 제품이 출시되어 사용자의 많은 관심을 끌고 있다.

- [0020] 이러한 추세에 편승하여 다양한 응용제품에 표시소자로서 이용되고 있는 횡전계형 액정표시장치에 있어서도 터치 기능을 갖도록 하기 위해 최근 다양한 시도가 진행되고 있다.

- [0021] 하지만, 전술한 바와 같이 컬러필터 기판의 배면에 도전성 물질로 배면전극이 형성된 횡전계형 액정표시장치는 그 내부에 인셀 형식을 정전용량 변화 인식 방식의 터치 센서가 구비된다 하더라도 상기 배면전극에 의해 터치에 의해 발생하는 정전용량 변화를 감지할 수 없게 되어 터치 센서가 작동하지 않는 문제가 발생하고 있다.

- [0022] 즉, 상기 컬러필터 기판의 배면 전면에 투명 도전성 물질로 이루어진 배면전극에 의해 사용자의 손가락이 접촉하는 경우 상기 손가락의 접촉면적에 발생하는 정전용량은 상기 손가락과 상기 배면전극 사이에 발생하게 되며, 이러한 정전용량은 정전기 처리를 위해 형성된 상기 배면전극을 통해 외부로 방전되므로 실질적으로 상기 컬러필터 기판과 어레이 기판 사이에 구현된 인셀 타입 터치센서가 작업자의 터치를 인식하지 못하게 되는 것이다.

- [0023] 이러한 문제를 해결하기 위해 상기 투명 도전성 물질로 이루어진 배면전극을 삭제하게 되면 제조 공정 중 정전기 발생으로 인해 불량률이 상승하며 표시품질이 저하되고 있는 실정이다.

## 발명의 내용

## 해결하려는 과제

[0024] 상기 문제점을 해결하기 위해서, 본 발명은 제조 공정 중에 발생하는 정전기에 따른 불량 및 표시품질 저하를 방지하는 동시에 사용자가 화면을 터치 시 인셀 타입의 터치센서가 정상적으로 동작되어 터치를 인식할 수 있는 터치인식 횡전계형 액정표시장치를 제공하는 것을 그 목적으로 한다.

## 과제의 해결 수단

[0025] 상기 목적을 달성하기 위한 본 발명에 따른 횡전계형 액정표시장치는, 제 1 기판과 이와 마주하는 제 2 기판 사이에 액정층이 구비되며, 공통전극과 화소전극이 모두 상기 제 1 기판의 내측면에 구비되며, 컬러필터층은 상기 제 2 기판의 내측면에 구비된 액정패널과; 상기 액정패널의 상기 제 2 기판의 외측면에 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 가 되도록 유기물질과 탄소나노튜브를 혼합한 물질로 제 1 두께를 가지며 형성된 정전기 방지층을 포함하며, 상기 제 1 및 제 2 기판에는 다수의 화소영역을 그룹으로 하는 다수의 터치블럭을 갖는 표시영역과 상기 표시영역 외측으로 비표시영역이 정의되며, 상기 공통전극은 상기 각 터치블럭 별로 이격하며 형성된 것이 특징이다.

[0026] 이때, 상기 유기물질은 PMMA(Polymethyl Methacrylate) 또는 PET(polyethylene terephthalate)인 것이 특징이며, 상기 제 1 두께는 300Å 내지 1000Å인 것이 특징이다.

[0027] 또한, 상기 제 1 기판 상의 각 화소영역의 경계에 서로 교차하며 형성된 게이트 및 데이터 배선과; 상기 각 화소영역 내에 상기 게이트 및 데이터 배선과 연결되며 형성된 박막트랜지스터와; 상기 박막트랜지스터 위로 전면에 형성된 제 1 보호층과; 상기 제 1 보호층 위로 형성된 상기 공통전극과; 상기 공통전극 위로 상기 게이트 배선과 중첩하도록 형성된 x센싱배선 및 상기 데이터 배선과 중첩하도록 형성된 y센싱배선과; 상기 공통전극과 x센싱배선 및 y센싱배선 위로 전면에 형성되며, 상기 박막트랜지스터의 드레인 전극을 노출시키는 드레인 콘택홀을 가지며 형성된 제 2 보호층과; 상기 제 2 보호층 위로 상기 드레인 콘택홀을 통해 상기 드레인 전극과 접촉하며 각 화소영역 별로 형성되며, 다수의 개구를 갖는 상기 화소전극과; 상기 제 2 기판의 내측면에 상기 각 화소영역 경계에 형성된 블랙매트릭스와; 상기 블랙매트릭스와 중첩되며 상기 각 화소영역에 대응하여 적, 녹, 청색 컬러필터 패턴이 순차 대응되도록 배치된 상기 컬러필터층을 포함한다. 이때, 상기 제 1 기판의 비표시영역에는, 상기 게이트 배선의 연장방향으로 동일한 라인에 배치된 상기 x센싱배선의 끝단에는 x방향 센싱회로가 구비되며, 상기 데이터 배선의 연장방향으로 동일한 라인에 배치된 상기 y센싱배선의 끝단에는 y방향 센싱회로가 구비된 것이 특징이다.

[0028] 본 발명의 일 실시예에 따른 횡전계형 액정표시장치의 제조 방법은, 제 1 기판 내측면 상부에 서로 교차하는 게이트 배선 및 데이터 배선과 박막트랜지스터와 공통전극과 상기 박막트랜지스터와 연결된 화소전극을 형성하는 단계와; 상기 제 2 기판의 외측면 전면에 유기물질과 탄소나노튜브가 혼합된 유기용액을 코팅하여 제 1 두께를 가지며 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 인 정전기 방지층을 형성하는 단계와; 상기 정전기 방지층이 형성된 상기 제 2 기판의 내측면에 블랙매트릭스와 컬러필터층을 형성하는 단계와; 상기 화소전극과 상기 컬러필터층이 마주하도록 상기 제 1 및 제 2 기판을 위치시키고 액정층을 개재하여 합착하여 제 1 두께를 갖는 액정패널을 형성하는 단계와; 상기 액정패널을 화학약액에 노출시켜 상기 제 1 및 제 2 기판의 외측면을 식각하여 상기 제 1 두께보다 얇은 제 2 두께를 갖도록 하는 단계와; 유기물질과 탄소나노튜브가 혼합된 유기용액을 코팅하여 식각되어 상기 제 2 두께를 갖는 상기 액정패널의 상기 제 2 기판의 외측면 전면에 제 3 두께를 가지며 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 인 정전기 방지층을 형성하는 단계를 포함한다.

[0029] 이때, 상기 제 1 두께는 300Å 내지 1000Å이며, 상기 코팅은 상온의 분위기에서 스판코팅장치 또는 슬릿코팅장치 중 어느 하나를 통해 진행되는 것이 특징이다.

[0030] 본 발명의 또 다른 실시예에 따른 횡전계형 액정표시장치의 제조 방법은, 제 1 기판의 내측면 상부에 서로 교차하는 게이트 배선 및 데이터 배선과 박막트랜지스터와 공통전극과 상기 박막트랜지스터와 연결된 화소전극을 형성하는 단계와; 제 2 기판의 내측면에 블랙매트릭스와 컬러필터층을 형성하는 단계와; 상기 화소전극과 상기 컬러필터층이 마주하도록 상기 제 1 및 제 2 기판을 위치시키고 액정층을 개재하여 합착하여 제 1 두께를 갖는 액정패널을 형성하는 단계와; 상기 액정패널을 화학약액에 노출시켜 상기 제 1 및 제 2 기판의 외측면을 식각하여 상기 제 1 두께보다 얇은 제 2 두께를 갖도록 하는 단계와; 유기물질과 탄소나노튜브가 혼합된 유기용액을 코팅하여 식각되어 상기 제 2 두께를 갖는 상기 액정패널의 상기 제 2 기판의 외측면 전면에 제 3 두께를 가지며 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 인 정전기 방지층을 형성하는 단계를 포함한다.

[0031] 이때, 상기 제 3 두께는 300Å 내지 1000Å이며, 상기 코팅은 상온의 분위기에서 스판코팅장치 또는 슬릿코팅장

치 중 어느 하나를 통해 진행되는 것이 특징이다.

[0032] 또한, 상기 유기물질은 PMMA(Polymethyl Methacrylate) 또는 PET(polyethylene terephthalate)인 것이 특징이다.

[0033] 또한, 상기 유기용액의 코팅을 실시한 후에는 히팅 수단을 통해 가열함으로써 상기 정전기 방지층을 건조시키는 단계를 포함하며, 상기 제 1 기판의 내측면에 상기 게이트 배선과 중첩하는 x센싱라인과, 상기 데이터 배선과 중첩하는 y센싱라인을 형성하는 단계와; 상기 제 1 기판 내측면의 비표시영역에 x센싱배선의 끝단과 연결되는 x방향 센싱회로와 상기 y센싱배선의 끝단과 연결되는 y방향 센싱회로를 실장하는 단계를 포함한다.

### 발명의 효과

[0034] 본 발명에 따른 터치인식 횡전계형 액정표시장치는 컬러필터 기판의 외측면에 도전성 특성을 탄소나노튜브를 포함하는 유기물질로서  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 의 면저항을 갖는 정전기 방지층이 형성되어 정전기에 대해서는 도전층으로서의 역할을 함으로써 제조 공정 중 발생하는 정전기를 외부로 방출시켜 정전기 발생에 의한 불량을 방지할 수 있으며, 나아가 상기 정전기 방지층은 사용자가 터치 동작시에는 유전체층으로서의 역할을 하여 표시영역에 대해 사용자가 터치 시 터치된 부분의 정전용량 변화가 발생된 것을 터치센서가 감지하도록 하는데 일조하여 표시영역 터치에 의한 동작 실행이 가능하도록 한 장점을 갖는다.

### 도면의 간단한 설명

[0035] 도 1은 일반적인 횡전계형 액정표시장치의 일부를 개략적으로 도시한 단면도.

도 2a, 2b는 일반적인 횡전계형 액정표시장치의 온(on), 오프(off) 상태의 동작을 각각 도시한 단면도.

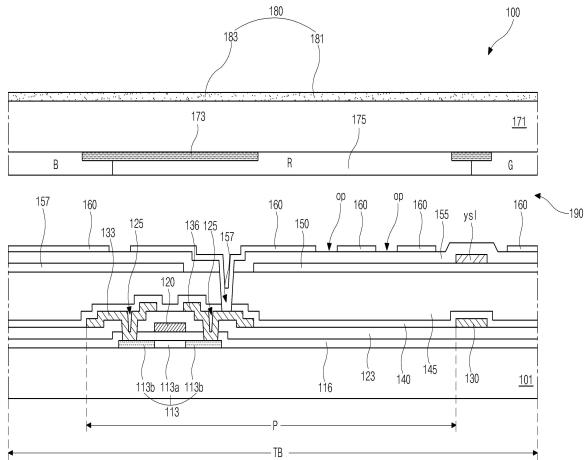

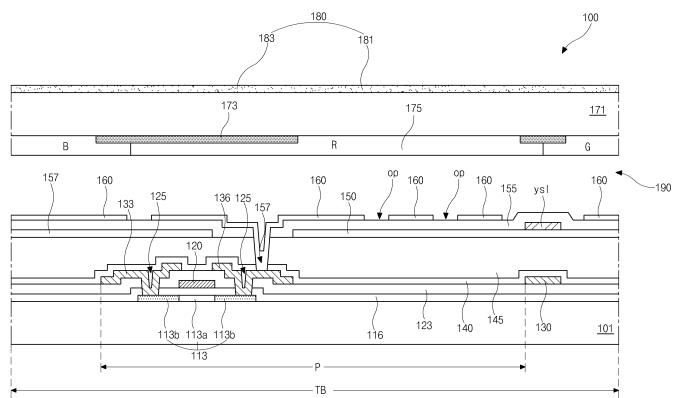

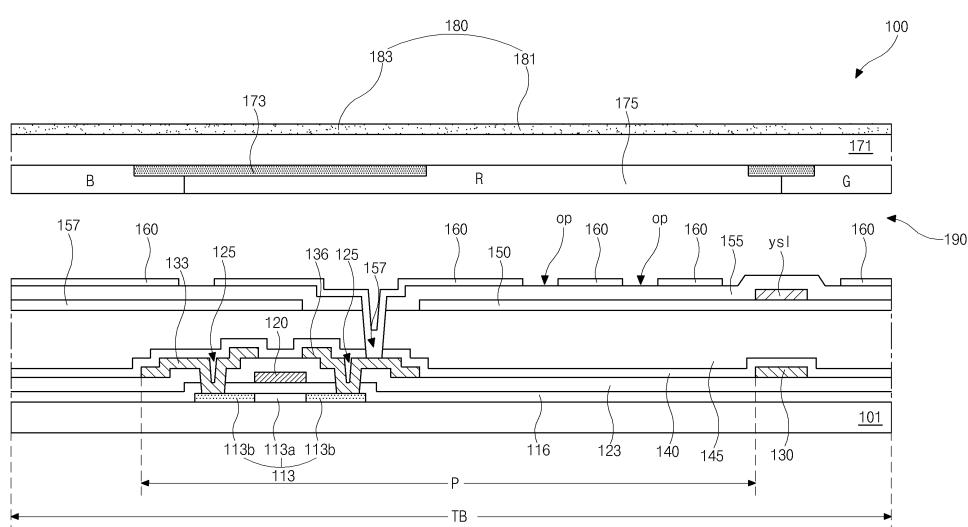

도 3은 본 발명의 실시예에 따른 터치인식 횡전계형 액정표시장치의 표시영역 내의 하나의 화소영역에 대한 단면도.

도 4a 내지 4e는 본 발명의 제 1 실시예에 따른 터치인식 횡전계형 액정표시장치의 제조 단계별 공정 단면도.

도 5a 내지 5f는 본 발명의 제 2 실시예에 따른 터치인식 횡전계형 액정표시장치의 제조 단계별 공정 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0036] 이하, 본 발명에 따른 바람직한 실시예를 도면을 참조하여 설명한다.

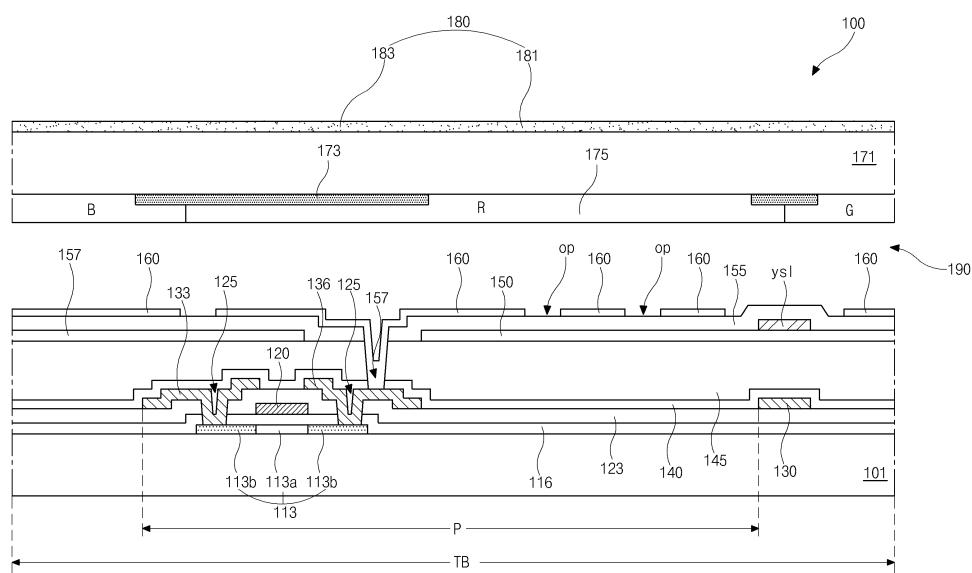

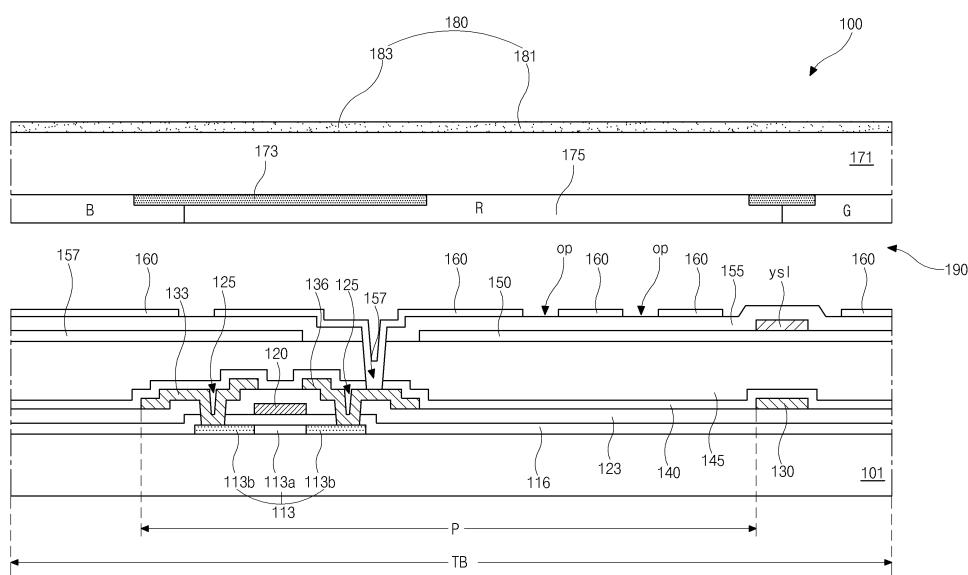

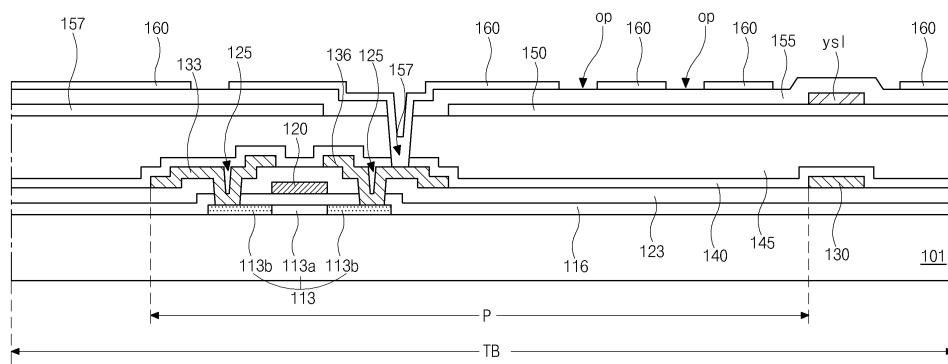

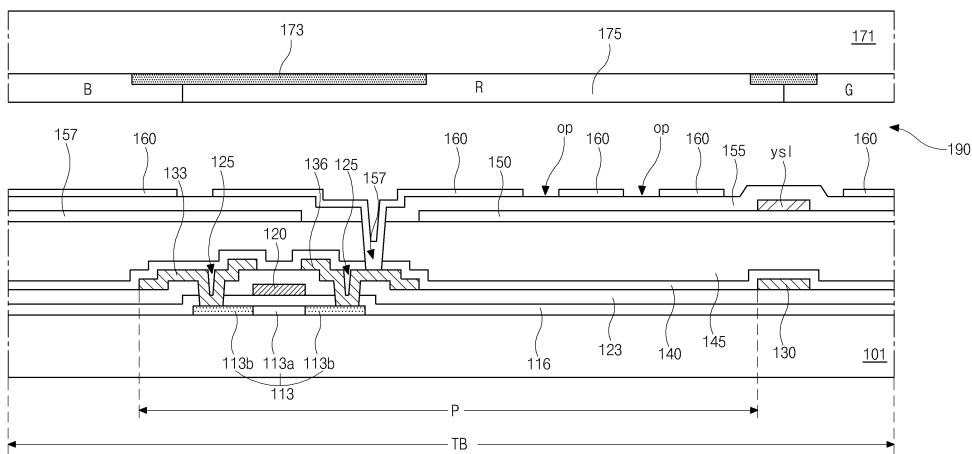

[0037] 도 3은 본 발명의 실시예에 따른 터치인식 횡전계형 액정표시장치의 표시영역 내의 하나의 화소영역에 대한 단면도이다.

[0038] 본 발명의 실시예에 따른 터치인식 횡전계형 액정표시장치(100)는 우선, 투명한 제 1 절연기판(101) 상에 상기 각 화소영역(P)에는 순수 폴리실리콘으로 이루어지며 그 중앙부는 채널을 이루는 제 1 반도체 영역(113a) 그리고 상기 제 1 반도체 영역(113a) 양측면으로 고농도의 불순물이 도핑된 제 2 반도체 영역(113b)으로 구성된 반도체층(113)이 형성되어 있다.

[0039] 또한, 상기 반도체층(113)을 덮으며 전면에 게이트 절연막(116)이 형성되어 있으며, 상기 게이트 절연막(116) 위로는 상기 반도체층(113)의 제 1 반도체 영역(113a)에 대응하여 게이트 전극(120)이 형성되어 있다.

[0040] 또한, 상기 게이트 절연막(116) 위로는 상기 게이트 전극(120)과 연결되며 일방향으로 연장하며 게이트 배선(미도시)이 형성되어 있으며, 상기 게이트 전극(120)과 게이트 배선(미도시) 위로 전면에 무기절연물질 예를들면 산화실리콘( $\text{SiO}_2$ ) 또는 질화실리콘( $\text{SiN}_x$ )으로 이루어진 충간절연막(123)이 형성되어 있다. 이때, 상기 충간절연막(123)과 그 하부에 위치하는 상기 게이트 절연막(116)에는 상기 제 1 반도체영역(113a) 양측에 각각 위치한 상기 제 2 반도체영역(113b) 각각을 노출시키는 반도체층 콘택홀(125)이 구비되고 있다.

[0041] 다음, 상기 반도체층 콘택홀(125)을 구비한 상기 충간절연막(123) 상부에는 상기 게이트 배선(미도시)과 교차하여 화소영역(P)을 정의하는 데이터 배선(130)이 형성되고 있다.

[0042] 또한, 상기 충간절연막(123) 위로 소자영역(TrA)에는 상기 반도체층 콘택홀(125)을 통해 노출된 상기 제 2 반

도체영역(113b)과 각각 접촉하며 서로 이격하는 소스 및 드레인 전극(133, 136)이 형성되어 있다. 이때, 상기 소자영역(TrA)에 순차 적층된 상기 반도체층(113)과 게이트 절연막(116)과 게이트 전극(120)과 충간절연막(123)과 소스 및 드레인 전극(133, 136)은 스위칭 소자인 박막트랜지스터(Tr)를 이룬다. 이때, 상기 박막트랜지스터(Tr)는 상기 게이트 배선(미도시) 및 데이터 배선(130)과 전기적으로 연결되어 있다.

[0043] 한편, 본 발명의 실시예에 있어서는 일례로 폴리실리콘의 반도체층(113)이 구비되어 그 상부에 게이트 전극(120)이 위치한 탑 게이트 타입의 박막트랜지스터(Tr)가 형성되고 있는 것을 보이고 있지만, 이러한 구조를 갖는 박막트랜지스터(Tr)를 대신하여 비정질 실리콘의 액티브층과 이의 상부에서 불순물 비정질 실리콘으로 이루어지며 서로 이격하는 형태의 오믹콘택층으로 이루어진 반도체층을 구비하여 상기 반도체층 하부에 게이트 전극이 위치한 보텀 게이트 타입의 박막트랜지스터가 형성될 수도 있으며, 이를 이외에 다양한 형태로 변형된 박막트랜지스터가 구비될 수도 있음은 자명하다.

[0044] 다음, 상기 데이터 배선(130)과 소스 및 드레인 전극(133, 136)과 상기 제 1 연결패턴(138) 상부에는 무기절연 물질 예를들면 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)로서 제 1 보호층(140)이 형성되고 있다. 이때, 상기 제 1 보호층(140)은 그 상부에 형성된 유기절연물질로 이루어진 제 2 보호층(145)과 상기 금속물질로 이루어진 상기 데이터 배선(130)과 소스 및 드레인 전극(133, 136) 간의 접합특성을 향상시키기 위함이다. 금속물질과 유기 절연물질간의 접합력은 금속물질과 무기절연물질간 및 무기절연물질과 유기절연물질간의 접합력보다 상대적으로 약하므로 이를 개선시키기 위해 무기절연물질로 이루어진 상기 제 1 보호층(140)을 형성하는 것이다. 이러한 접합력 향상의 역할을 하는 상기 제 1 보호층(140)은 생략될 수도 있다.

[0045] 다음, 상기 제 1 보호층(140) 위로는 유기절연물질 예를들면 포토아크릴(photo acryl) 또는 벤조사이클로부텐(BCB)으로서 이루어진 제 2 보호층(145)이 형성되고 있다. 이때, 상기 제 2 보호층(145)은 하부에 위치하는 구성요소간의 단차 등이 극복될 수 있도록 2μm 내지 4μm 정도의 두꺼운 두께를 가져 평탄한 표면 상태를 이루는 것이 특징이다.

[0046] 다음, 상기 제 2 보호층(145) 위에는 투명도전성 물질로서 각 터치블러(TB, 표시영역 내에서 다수의 화소영역을 하나의 단위로 구성한 영역으로써 통상 사용자에 의해 손가락 등으로 터치되는 면적인 1mm<sup>2</sup> 내지 10mm<sup>2</sup>정도의 크기를 갖는 영역) 별로 패터닝 된 형태로 공통전극(150)이 형성되어 있다. 이때, 상기 공통전극(150)은 더욱 정확히는 터치블러(TB) 내부에서 또 다시 제 1, 2 및 3 영역(미도시)별로 분리 형성되고 있는 것이 특징이다.

[0047] 또한, 터치블러(TB) 별로 패터닝되어 형성된 상기 공통전극(150) 위로 일부 게이트 배선(미도시)과 중첩하며 x 센싱배선(미도시)이 형성되고 있으며, 일부 데이터 배선(130)과 중첩하며 y센싱배선(yS1)이 형성되고 있다.

[0048] 한편, 각 터치블러(미도시) 내에서는 그 내부적으로 제 1 및 제 3 영역(미도시)만이 전기적으로 연결되고, 제 2 영역(미도시)은 전기적으로 분리된 형태가 되며, 상기 제 2 영역(미도시)은 데이터 배선(130)의 연장방향으로 이웃한 터치블러(TB) 내의 제 2 영역(미도시)간에만 전기적으로 연결된 구성을 갖는 것이 특징이다. 이러한 각 터치블러(TB) 내의 제 1 영역(미도시)과 제 3 영역(미도시)간의 전기적 연결은 상기 게이트 배선(미도시) 또는 데이터 배선(130)을 형성하는 단계에서 보조배선(미도시)을 더욱 형성한 후 상기 충간절연막(123)을 형성하는 단계 또는 제 2 보호층(145)을 형성하는 단계에서 상기 보조배선(미도시)을 노출시키는 보조콘택홀(미도시)을 형성하고 상기 공통전극(150)을 패터닝하여 형성함으로써 전기적으로 연결되도록 할 수 있다.

[0049] 다음, 상기 공통전극(150)과 x, y센싱배선(xs1, ys1) 상부로 표시영역 전면에 무기절연물질 예를들면 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)으로서 제 3 보호층(155)이 형성되고 있다.

[0050] 이때, 각 소자영역(TrA) 내의 드레인 전극(136)에 대응하는 부분의 상기 제 1, 2, 3 보호층(140, 145, 155)은 각각 패터닝됨으로서 드레인 콘택홀(157)이 구비되고 있으며, 상기 각 터치블러(TB) 내의 제 1 및 제 3 영역(미도시)에 구비된 상기 x센싱배선(xs1)에 대응하는 부분의 제 3 보호층(155)은 패터닝되어 제 4 콘택홀(159)이 구비되고 있다.

[0051] 다음, 상기 제 3 보호층(155) 위로는 각 화소영역(P) 내에 상기 드레인 콘택홀(157)을 통해 상기 드레인 전극(136)과 접촉하는 화소전극(160)이 형성됨으로서 어레이 기판이 완성되고 있다. 이때, 상기 화소전극(160)에는 다수의 바(bar) 형태의 개구(op)가 구비됨으로서 구동전압 인가 시 상기 공통전극(150)과 더불어 프린지 필드를 발생시키게 된다.

[0052] 상기 각 화소영역(P)에 구비된 상기 화소전극(160)과 상기 공통전극(150)은 상기 제 3 보호층(155)을 개재하여 중첩하도록 형성되고 있으며, 중첩하는 상기 공통전극(150)과 제 3 보호층(155)과 화소전극(160)은 스토리지 커

패시터를 이룬다.

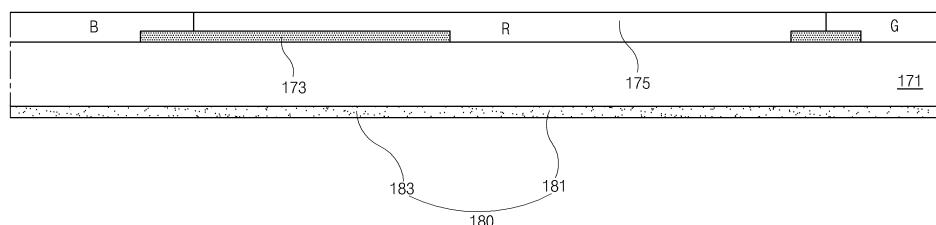

- [0053] 전술한 구성을 갖는 어레이 기판(101)과 마주하며, 투명한 제 2 절연기판(171)이 구비되고 있다.

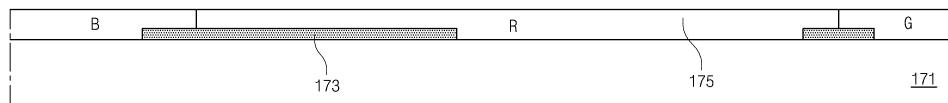

- [0054] 또한, 상기 제 2 절연기판(171)의 내측면에는 각 화소영역(P)의 경계 및 상기 박막트랜지스터(Tr)에 대응하여 블랙매트릭스(173)가 구비되고 있으며, 상기 블랙매트릭스(173)와 중첩하여 상기 블랙매트릭스(173)에 의해 포획된 영역에는 각 화소영역(P)에 순차 대응하는 형태로 적, 녹, 청색 컬러필터 패턴(R, G, B)을 포함하는 컬러필터층(175)이 형성되어 있다.

- [0055] 또한, 본 발명에 있어서 가장 특징적인 것으로 상기 제 2 절연기판(171)의 외측면에는 베이스층(181)은 유기물질로서 이루어지며 그 내부에 도전성 특성을 갖는 탄소나노튜브(Carbon Nano-Tube: CNT)(183)가 포함되어 그 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 이 되는 것을 특징으로 정전기 방지층(180)이 형성되어 있다.

- [0056] 이때, 상기 유기물질은 예를 들면 PMMA(Polymethyl Methacrylate) 또는 PET(polyethylene terephthalate)로서 비저항 값이  $10^{14} \Omega\text{cm}$  내지  $10^{20} \Omega\text{cm}$  정도를 갖는 것이 특징이다.

- [0057] 상기 베이스층(181)을 이루는 유기물질 자체만으로 상기 정전기 방지층(180)을 형성하는 경우 그 비저항 값이 너무 커 전기가 도통되지 않는 절연층이 되어 정전기 방지 수단이 될 수 없다.

- [0058] 즉, 상기 제 2 절연기판(171)의 외측면에 전술한 유기물질만으로 이루어진 물질층을 형성하면 이러한 유기물질은 그 자체의 비저항 값이  $10^{14} \Omega\text{cm}$  내지  $10^{20} \Omega\text{cm}$ 가 되므로, 이러한 비저항 값을 갖는 유기물질을 통해 형성된 상기 물질층은 그 면저항은  $10^{14} \Omega/\text{sq}$  내지  $10^{20} \Omega/\text{sq}$ 되며, 따라서 이러한 큰 면저항을 갖는 유기물질로 이루어진 물질층은 실질적으로 전기가 거의 통하지 않는 절연층을 이루게 된다. 이 경우, 제조 공정 중 특히 모듈 공정 진행 시 정전기기 발생하면 상기 컬러필터층(175)이 구비된 제 2 절연기판(171)의 경우 실질적으로 도전층 또는 금속배선 등이 형성되지 않으므로 상기 정전기를 외부로 배출시키기 위한 구성요소가 없게 되므로 이로 인해 구성요소의 파괴에 의한 불량 및 화질저하가 발생된다.

- [0059] 하지만, 본 발명의 실시예에 따른 터치인식 횡전계형 액정표시장치(100)의 상기 컬러필터층(175)이 구비된 제 2 절연기판(171)의 외측면에는 비저항이  $10^{14} \Omega\text{cm}$  내지  $10^{20} \Omega\text{cm}$ 정도인 유기물질로 이루어진 베이스층(181)과 이의 내부에 도전성 특성을 갖는 다수의 탄소나노튜브(183)로 구비되어 그 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$  정도인 정전기 방지층(180)이 형성됨으로써 제조 공정 중 정전기가 발생된다 하더라도 이를 외부로 방출될 수 있도록 함으로써 정전기 발생에 의한 불량을 억제할 수 있는 것이 특징이다.

- [0060] 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$  정도가 되는 경우,  $10^{14} \Omega/\text{sq}$  내지  $10^{20} \Omega/\text{sq}$ 정도의 면저항을 갖는 물질층 대비 도전성을 갖는다 할 것이다. 따라서 유기물질을 베이스층(181)으로 하여 그 내부에 도전성 특성을 갖는 다수의 탄소나노튜브(183)를 포함하는 것을 특징으로 하는 상기 정전기 방지층(180)은 정전기 발생 시 상기 정전기가 이를 통해 외부로 빠져나갈 수 있는 정전기 방지 수단이 될 수 있는 것이다.

- [0061] 다음, 전술한 구성을 갖는 제 1 절연기판(101)과 제 2 절연기판(171) 사이에는 액정층(170)이 개재되고, 표시영역 외측의 비표시영역에 상기 표시영역을 테두리하는 형태로 셀패턴(미도시)이 됨으로써 본 발명에 따른 터치인식 횡전계형 액정표시장치(100)가 완성되고 있다.

- [0062] 한편, 전술한 바와 같이, 베이스층(181)은 비저항 값이  $10^{14} \Omega\text{cm}$  내지  $10^{20} \Omega\text{cm}$ 정도인 PMMA 또는 PET 등의 유기물질로 이루어지며 그 내부에 도전성의 다수의 탄소나노튜브(183)가 구비되어  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 가지며 상기 컬러필터 기판(171)의 외측면 전면에 형성된 정전기 방지층(180)은 전술한 바와 같이 정전기 방지 수단으로 역할을 하는 동시에 표시영역에 대응하여 사용자가 손가락으로 터치를 실시하였을 경우, 상기 어레이 기판(101) 상에 구비된 x,y센싱배선(미도시, ys1)과 터치블력(TB) 별로 패터닝된 공통전극(150)으로 이루어진 터치감지 센서가 동작하도록 하는 데에는 방해하지 않는 구성요소가 된다.

- [0063] 즉, 상기 정전기 방지층(180)은 상기 사용자의 손가락 터치에 의해 상기 손가락이 터치된 부분에 있어서 상기 손가락과 상기 어레이 기판(101) 상의 공통전극(150) 사이에 구비됨으로써 유전체층으로 역할을 하여 상기 사용자의 손가락과 상기 공통전극(150)을 전극으로 하는 커패시터를 이루도록 하는데 일조하며 따라서 사용자의 손가락과 공통전극에 의해 구성된 커패시터에 의해 터치 동작을 감지할 수 있게 된다.

- [0064] 조금 더 터치에 의한 커패시터 형성에 대해 상세히 설명하면, 이렇게 사용자의 손가락 등에 의해 표시영역의 터치가 발생한 경우, 상기 정전기 방지층(180)은 상기 액정층(190)과 더불어 실질적으로  $10^6 \Omega/\text{sq}$  내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 갖는 절연층으로 작용함으로써 손가락(미도시) 터치에 의해 발생된 손가락과 상기 어레이 기판(101) 상에 구비된 터치블력(TB) 별 공통전극(150) 및 이들 두 구성요소(미도시, 150) 사이에 구성된 상기 액정층(190)과 컬러필터층(175)과 제 2 절연기판(171) 및 상기 정전기 방지층(180)을 유전체층으로 한 커패시터가 형성된다. 그리고 이러한 커패시터에 발생된 정전용량을 기전력으로 하여 상기 공통전극(150)과 연결된 x센싱배선(미도시) 및 y센싱배선(ys1)을 통해 상기 어레이 기판(101)의 비표시영역에 구비된 다수의 X방향센싱회로(미도시) 및 Y방향센싱회로(미도시)로 소정의 전압신호를 인가함으로서 표시영역 내에 터치된 부분의 위치를 파악하게 되며, 터치된 부분에 표시된 동작을 실시하게 되는 것이다.

- [0065] 정전기는 순간적인 정전압이 수천 내지 수만 V가 되며, 정전기기 발생하여 이러한 정전기가 갖는 고전압이 인가되는 상황에서는  $10^6 \Omega/\text{sq}$  내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 갖는 상기 정전기 방지층(180)은 도전체로서의 역할을 하게 되지만, 일반적으로 사람의 손가락에 흐르는 미량의 전류는 그 크기가 수 nA 내지 수  $\mu\text{A}$  정도가 되므로 이러한 크기의 전류에 대해서는 상기  $10^6 \Omega/\text{sq}$  내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 갖는 상기 정전기 방지층(180)은 절연층의 역할을 하게 된다. 따라서 상기 손가락이 터치되는 경우 상기  $10^6 \Omega/\text{sq}$  내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 갖는 정전기 방지층은 커패시터의 유전체층으로서의 역할을 하게 되는 것이다.

- [0066] 그러므로, 본 발명에 따른 터치인식 횡전계형 액정표시장치(100)는 제조 공정 중 발생하는 정전기를 외부로 방출시키는 수단으로서 컬러필터 기판(171)의 외측면에 정전기 방지층(180)이 형성된다 하더라도 이러한 정전기 방지층(180)이 사용자의 터치 시 정전용량을 형성하지 못하도록 하는 방해수단으로 작용하지 않으므로 터치에 의한 동작이 가능한 것이 특징이다.

- [0067] 이후에는 전술한 구성을 갖는 본 발명에 따른 터치인식 횡전계형 액정표시장치의 제조 방법에 대해 간단히 설명한다.

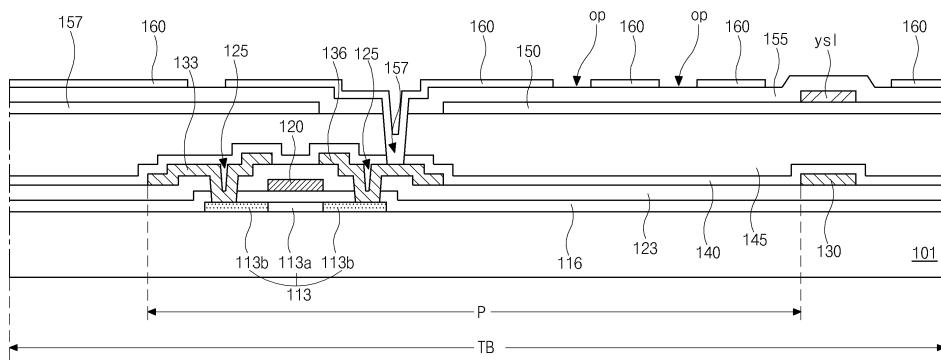

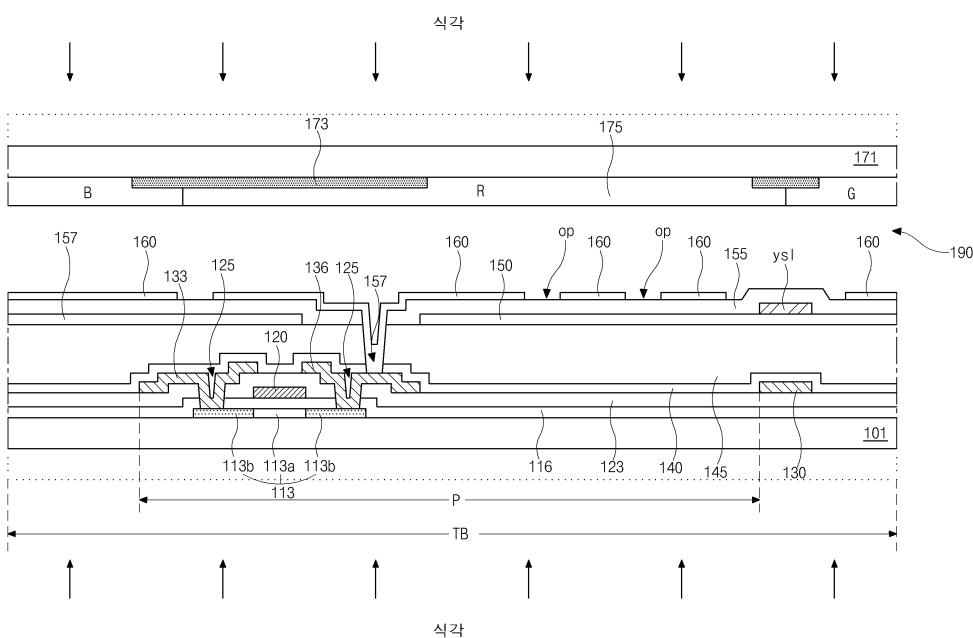

- [0068] 도 4a 내지 4e는 본 발명의 제 1 실시예에 따른 터치인식 횡전계형 액정표시장치의 제조 단계별 공정 단면도이다.

- [0069] 우선, 도 4a에 도시한 바와 같이, 투명한 제 1 절연기판(101) 상에 순수 비정질 실리콘을 증착하여 순수 비정질 실리콘층(미도시)을 형성하고, 이에 대해 레이저 범을 조사하거나 또는 열처리를 실시하여 상기 비정질 실리콘층(미도시)을 폴리실리콘층(미도시)으로 결정화시킨다.

- [0070] 이후, 마스크 공정을 실시하여 상기 폴리실리콘층(미도시)을 패터닝함으로써 상기 각 화소영역(P)에 순수 폴리실리콘 상태의 반도체층(113)을 형성한다.

- [0071] 다음, 상기 순수 폴리실리콘의 반도체층(113) 위로 무기절연물질 예를들면 산화실리콘( $\text{SiO}_2$ ) 또는 질화실리콘( $\text{SiN}_x$ )을 증착하여 게이트 절연막(116)을 형성한다.

- [0072] 다음, 상기 게이트 절연막(116) 위로 금속물질 예를들면 알루미늄(Al), 알루미늄 합금(AlNd), 구리(Cu), 구리합금 및 크롬(Cr) 중 하나를 증착하여 제 1 금속층(미도시)을 형성하고, 이를 패터닝함으로써 상기 각 반도체층(113)의 중앙부에 대응하여 게이트 전극(120)을 각각 형성하고, 동시에 상기 게이트 절연막(116) 위로 상기 화소영역(P)의 경계에 상기 소자영역(TrA)에 형성된 게이트 전극(120)과 연결되며 일 방향으로 연장하는 게이트 배선(미도시)을 형성한다.

- [0073] 다음, 상기 각 게이트 전극(120)을 블록킹 마스크로 이용하여 상기 제 1 절연기판(110) 전면에 불순물을 도핑함으로써 상기 반도체층(113) 중 상기 게이트 전극(120) 외측에 위치한 부분에 상기 불순물이 도핑된 제 2 반도체 영역(113b)을 이루도록 하고, 블록킹됨으로써 상기 불순물의 도핑이 방지된 게이트 전극(120)에 대응하는 부분은 순수 폴리실리콘의 제 1 반도체영역(113a)을 이루도록 한다.

- [0074] 다음, 제 1 및 제 2 반도체영역(113a, 113b)으로 나뉘어진 반도체층(113)이 형성된 제 2 절연기판(110) 전면에 무기절연물질 예를들면 질화실리콘( $\text{SiN}_x$ ) 또는 산화실리콘( $\text{SiO}_2$ )을 증착하여 전면에 층간절연막(123)을 형성 한다.

- [0075] 이후, 상기 층간절연막(123)과 하부의 게이트 절연막(116)을 패터닝함으로써 상기 각 반도체층(113)의 제 2 반

도체영역(113b)을 각각 노출시키는 반도체층 콘택홀(125)을 형성한다.

- [0076] 다음, 상기 반도체층 콘택홀(125)을 갖는 상기 충간절연막(123) 위로 금속물질 예를 들면 알루미늄(A1), 알루미늄 합금(AINd), 구리(Cu), 구리합금, 크롬(Cr) 및 몰리브덴(Mo) 중 하나를 증착하여 제 2 금속층(미도시)을 형성하고, 이를 패터닝함으로써 상기 소자영역(TrA)에 상기 반도체층 콘택홀(125)을 통해 상기 제 2 영역(113b)과 각각 접촉하며 서로 이격하는 소스 및 드레인 전극(133, 136)을 형성 한다.

- [0077] 동시에 상기 충간절연막(123) 위로 상기 화소영역(P)의 경계에 상기 소자영역(TrA)에 형성된 소스 전극(133)과 연결되며 상기 게이트 배선(미도시)과 교차하는 데이터 배선(130)을 형성 한다. 이때, 도면에 나타내지 않았지만, 상기 게이트 배선(미도시) 또는 데이터 배선(130)을 형성하는 단계에서 이들 배선(미도시, 130)과 나란히 배치되는 보조배선(미도시)을 더욱 형성할 수도 있다.

- [0078] 상기 각 화소영역(P)에 구비된 상기 반도체층(113)과 게이트 절연막(116)과 게이트 전극(120)과 충간절연막(123)과 서로 이격하는 소스 및 드레인 전극(133, 136)은 스위칭 소자인 박막트랜지스터(Tr)를 이룬다.

- [0079] 한편, 본 발명의 제 1 실시예에 따른 제조 방법에 있어서는 폴리실리콘의 반도체층(113)이 구비되어 그 상부에 게이트 전극(120)이 위치한 탑 게이트 타입의 박막트랜지스터(Tr)가 형성되고 있는 것을 보이고 있지만, 이의 변형예로서 도면에 나타내지 않았지만, 이러한 탑 게이트 타입의 박막트랜지스터(Tr)를 대신하여 게이트 배선과 게이트 전극을 형성하는 단계와, 게이트 절연막을 형성하는 단계와, 비정질 실리콘의 액티브층과 이의 상부에서 불순물 비정질 실리콘으로 이루어지며 서로 이격하는 형태의 오믹콘택층으로 이루어진 반도체층을 형성하는 단계와, 데이터 배선과 서로 이격하는 소스 및 드레인 전극을 형성하는 단계를 진행함으로써 상기 반도체층 하부에 게이트 전극이 위치한 보텀 게이트 타입의 박막트랜지스터가 형성될 수도 있다.

- [0080] 다음, 상기 박막트랜지스터(Tr)와 데이터 배선(130) 위로 무기절연물질 예를 들면, 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)을 증착하여 제 1 보호층(140)을 형성하고, 연속하여 상기 제 1 보호층(140) 상부로 유기절연물질 예를 들면 포토아크릴(photo acryl) 또는 벤조사이클로부텐(PCB)을 도포하여 그 표면이 평坦한 형태를 갖는 제 2 보호층(145)을 형성 한다. 이때 상기 제 1 보호층(140)은 접합력 향상을 위해 형성한 것으로 생략할 수도 있다.

- [0081] 다음, 상기 제 2 보호층(145) 위로 투명 도전성 물질 예를 들면, 인듐-틴-옥사이드(ITO) 또는 인듐-징크-옥사이드(ZTO)를 전면에 증착하고, 이를 패터닝함으로서 각 터치블럭(TB) 별로 이격하는 형태의 공통전극(150)을 형성 한다. 이때 상기 각 터치블럭(TB) 내부에서 상기 각 공통전극(150)은 x, y센싱배선(미도시, ys1)을 통해 각각 x, y방향센서(미도시)로 터치 시 소정의 전압을 각각 전송시키기 위해 제 1, 2, 3 영역(미도시)으로 분리 되도록 형성하며, 상기 각 터치블럭(TB) 내에서 상기 제 1 영역(미도시)과 제 3 영역(미도시)간의 전기적 연결 및 이웃한 터치블럭(TB) 간의 제 2 영역(미도시)간의 전기적 연결을 위해 상기 게이트 배선(미도시) 또는 데이터 배선(130)을 형성하는 단계에서 보조배선(미도시)을 더욱 형성한 후 상기 충간절연막(123)을 형성하는 단계 또는 제 2 보호층(145)을 형성하는 단계에서 상기 보조배선(미도시)을 노출시키는 보조콘택홀(미도시)을 형성하고 상기 공통전극(150)을 형성함으로써 전기적으로 연결되도록 할 수 있다.

- [0082] 다음, 상기 공통전극(150) 위로 저저항 금속물질 예를 들면 알루미늄(A1), 알루미늄 합금(AINd), 구리(Cu), 구리합금 중 어느 하나를 증착하여 제 3 금속층(미도시)을 형성하고, 이를 패터닝함으로써 일부의 게이트 배선(미도시) 및 데이터 배선(130)과 중첩하는 x센싱배선(미도시) 및 y센싱배선(ys1)을 형성 한다. 이때, 상기 각 터치블럭(TB) 내부에서는 상기 x센싱배선(미도시)과 상기 y센싱배선(ys1) 간에는 셀트되는 형태로 형성될 수 있지만, 각 터치블럭(TB) 간에는 상기 x, y센싱배선(미도시, ys1)은 셀트됨없이 형성하는 것이 특징이다.

- [0083] 다음, 상기 x센싱배선(미도시)과 y센싱배선(ys1) 위로 무기절연물질 예를 들면 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)을 증착하여 제 3 보호층(155)을 형성하고, 상기 제 3 보호층(155)과 제 2 보호층(145) 및 제 1 보호층(140)을 패터닝함으로서 상기 드레인 전극(136)을 노출시키는 드레인 콘택홀(157)을 형성 한다.

- [0084] 다음, 상기 드레인 콘택홀(157)과 상기 제 4 콘택홀(159)을 갖는 상기 제 3 보호층(155) 위로 투명 도전성 물질 예를 들면, 인듐-틴-옥사이드(ITO) 또는 인듐-징크-옥사이드(ZTO)를 증착하고, 이를 패터닝함으로서 각 화소영역(P) 내에 상기 드레인 콘택홀(157)을 통해 상기 드레인 전극(136)과 접촉하는 화소전극(160)을 형성함으로써 터치인식 횡전계형 액정표시장치용 어레이 기판(101)을 완성한다. 이때 상기 화소전극(160)은 그 하부에 위치한 공통전극(150)과 프린지 필드 형태를 위해 각 화소영역(P)내에 일정간격 이격하는 바(bar) 형태의 다수의 개구(op)를 갖도록 형성하는 것이 특징이다.

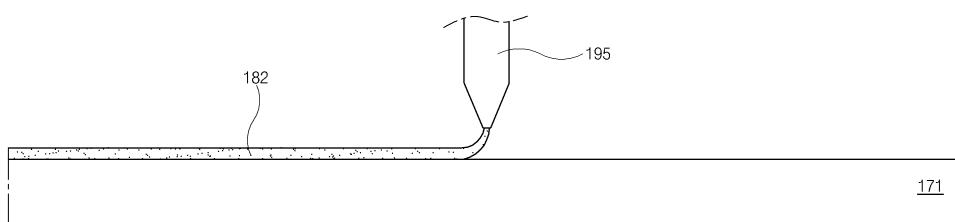

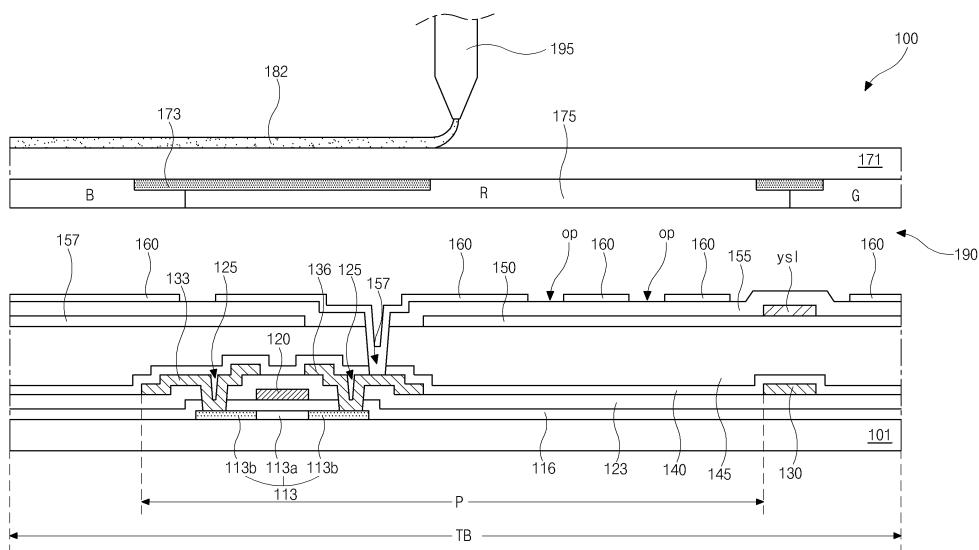

- [0085] 다음, 도 4b에 도시한 바와 같이, 제 2 절연기판(171)의 외측면에 유기 솔벤트를 용매로 하여 유기물질 예를 들면 PMMA 또는 PET이 녹아 있는 용액에 적정량의 탄소나노튜브가 섞인 것을 특징으로 하는 액상의 유기 혼합물을 스픬 코팅장치(미도시) 또는 슬릿 코팅장치(195)를 통해 상온에서 코팅함으로써 유기 용액층(182)을 형성 한다.

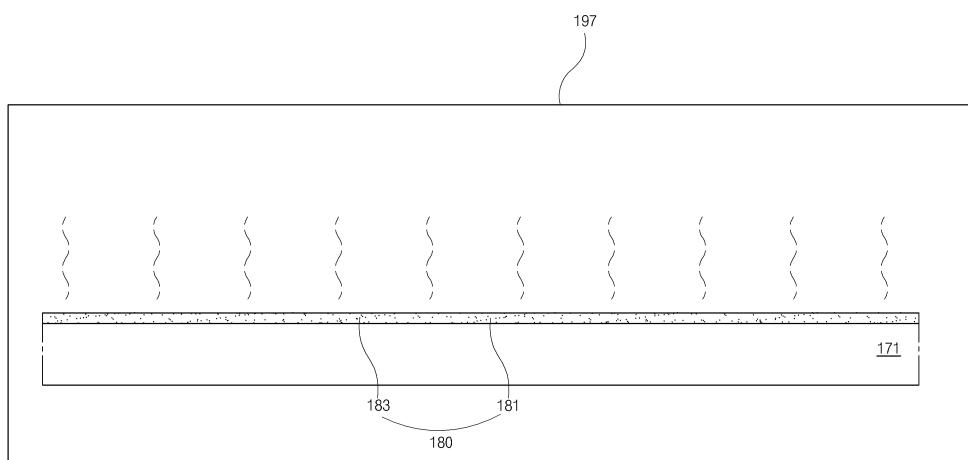

- [0086] 이후, 도 4c에 도시한 바와 같이, 상기 탄소나노튜브를 포함하는 유기 용액층(도 4a의 182)이 이에 대해 퍼니스(furnace) 또는 오븐(oven)(197) 등의 히팅 장치를 이용하여 가열시키는 건조 공정을 진행하여 상기 유기 솔벤트를 휘발하여 제거시킴으로써 유기물질이 베이스층(181)을 이루며 그 내부에 도전성의 다수의 탄소나노튜브(183)를 포함하여 그 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$  정도가 되는 것을 특징으로 하는 정전기 방지층(180)을 형성 한다. 이때, 상기 정전기 방지층(180)은  $300\text{\AA}$  내지  $1000\text{\AA}$ 정도의 두께를 갖도록 형성하는 것이 바람직하다.

- [0087] 상기 유기 혼합물은 상기 유기 솔벤트에 전술한 유기물질을 넣어 용액 상태를 이루도록 한 후, 분말타입의 탄소나노튜브를 상기 유기물질의 중량% 대비 적정 중량% 넣은 후, 교반기를 통해 일정한 비율로 섞이도록 잘 교반해 줌으로써 완성할 수 있다.

- [0088] 이러한 유기 혼합물은 상기 유기물질과 탄소나노튜브(183)의 중량% 비를 조절함으로써 이를 이용하여 박막 또는 층을 이루었을 경우 그 면저항 값을 변화시킬 수 있으며, 따라서 상기 유기 솔벤트에 유기물질과 탄소나노튜브(183)를 적정한 비율로 혼합한 용액을 도포하여  $300\text{\AA}$  내지  $1000\text{\AA}$ 정도의 두께를 갖도록 형성할 경우,  $10^6 \Omega/\text{sq}$  내지  $10^9 \Omega/\text{sq}$  정도의 면저항을 갖는 상기 정전기 방지층(180)을 형성할 수 있다.

- [0089] 다음, 도 4d에 도시한 바와 같이, 외측면에 면저항이  $10^6 \Omega/\text{sq}$ 내지  $10^9 \Omega/\text{sq}$ 정도가 되는  $300\text{\AA}$  내지  $1000\text{\AA}$ 정도의 두께를 갖는 정전기 방지층(180)이 형성된 제 2 절연기판(171)의 내측면에 대해 빛의 투과를 차단하는 물질 예를 들면 블랙레진을 도포하고 이를 마스크 공정을 진행하여 패터닝함으로써 각 화소영역(P)의 경계에 대응하여 블랙매트릭스(173)를 형성 한다.

- [0090] 다음, 상기 블랙매트릭스(173) 위로 적색 레지스트를 도포하고 이를 패터닝함으로서 각 화소영역(P)에 대응하여 적색 컬러필터 패턴(R)을 형성하고, 이후 상기 적색 컬러필터 패턴(R)을 형성한 동일한 방법으로 녹색 및 청색 컬러필터 패턴(G, B)을 형성함으로써 적, 녹, 청색 컬러필터 패턴(R, G, B)을 구비한 컬러필터층(175)을 형성함으로서 컬러필터 기판(171)을 완성한다. 이때, 다음, 상기 컬러필터층(175) 위로 선택적으로 평탄한 표면을 갖는 오버코트층(미도시)을 더욱 형성할 수도 있다.

- [0091] 다음, 도 4e에 도시한 바와 같이, 상기 화소전극(160)과 컬러필터층(175)이 서로 마주하도록 상기 어레이 기판(101)과 상기 컬러필터 기판(171)을 위치시킨 후, 상기 어레이 기판(101) 또는 컬러필터 기판(171) 중 어느 하나의 기판에 대해 표시영역을 테두리하는 형태로 셀패턴(미도시)을 형성 한다.

- [0092] 이후, 상기 셀패턴(미도시) 내측에 대해 액정층(190)을 개재한 상태에서 상기 어레이 기판(101)과 컬러필터 기판(171)을 합착함으로써 액정패널을 완성한다.

- [0093] 한편, 도면에 나타내지 않았지만, 전술한 바와 같이 완성된 액정패널에 대해 모듈공정을 진행함으로써 상기 어레이 기판(101)의 비표시영역에 터치블럭(TB) 라인별로 상기 x센싱배선(미도시)과 y센싱배선(yS1)과 연결되도록 다수의 X방향센싱회로(미도시)와 y방향센싱회로(미도시)를 실장하고, 나아가 상기 게이트 및 데이터 배선(미도시, 130)과 연결되는 구동회로기판(미도시)을 실장함으로써 본 발명의 제 1 실시예의 제조 방법에 따른 터치인식 횡전계형 액정표시장치(100)를 완성한다.

- [0094] 도 5a 내지 도 5f는 본 발명의 제 2 실시예에 따른 터치인식 횡전계형 액정표시장치의 제조 단계별 공정 단면도이다. 이러한 제 2 실시예에 따른 터치인식 횡전계형 액정표시장치의 제조 방법은 컬러필터 기판의 외측면에 정전기 방지층을 형성하는 단계와 상기 컬러필터 기판 및 어레이 기판의 외측면에 대해 식각을 진행하여 그 두께를 얇게 하는 단계만이 차이가 있으며 그 외의 구성요소의 형성은 전술한 제 1 실시예에 따른 제조 방법과 동일하므로 차이가 있는 부분을 위주로 설명한다.

- [0095] 우선, 도 5a에 도시한 바와 같이, 제 1 실시예와 동일하게 진행하여 박막트랜지스터(Tr)와, 서로 교차하는 게이트 및 데이터 배선(미도시, 130)과, x센싱배선(미도시) 및 y센싱배선(yS1)과, 공통전극(150) 및 화소전극(160)을 포함하는 어레이 기판(101)을 완성한다.

- [0096] 다음, 도 5b에 도시한 바와 같이, 제 2 절연기판(171) 상에 유기물질 및 탄소나노튜브로 이루어진 정전기 방지

층 형성없이 빛의 투과를 차단하는 물질 예를 들면 블랙레진을 도포하고 이를 마스크 공정을 진행하여 패터닝함으로써 각 화소영역의 경계에 대응하여 블랙매트릭스(173)를 형성 한다.

- [0097] 이후, 상기 블랙매트릭스(173) 위로 적색 레지스트를 도포하고 이를 패터닝함으로서 각 화소영역에 대응하여 적색 컬러필터 패턴(R)을 형성하고, 이후 상기 적색 컬러필터 패턴(R)을 형성한 동일한 방법으로 녹색 및 청색 컬러필터 패턴(G, B)을 형성함으로써 적, 녹, 청색 컬러필터 패턴(R, G, B)을 구비한 컬러필터층(175)을 형성함으로서 컬러필터 기판(171) 완성한다. 이때, 다음, 상기 컬러필터층(175) 위로 선택적으로 평탄한 표면을 갖는 오버코트층(미도시)을 더욱 형성할 수도 있다.

- [0098] 다음, 도 5c에 도시한 바와 같이, 상기 화소전극(160)과 컬러필터층(175)이 서로 마주하도록 상기 어레이 기판(101)과 상기 컬러필터 기판(171)을 위치시킨 후, 상기 어레이 기판(101) 또는 컬러필터 기판(171) 중 어느 하나의 기판에 대해 표시영역을 테두리하는 형태로 씰패턴(미도시)을 형성 한다. 이후 상기 씰패턴(미도시) 내측에 대해 액정층(190)을 개재한 상태에서 상기 어레이 기판(101)과 컬러필터 기판(171)을 합착함으로써 액정패널을 완성한다.

- [0099] 다음, 도 5d에 도시한 바와 같이, 유리재질로 이루어진 상기 제 1 및 제 2 절연기판(101, 171)의 외측면을 녹일 수 있는 화학약액 예를 들면 불산(HF)용액에 상기 액정패널을 노출시킴으로써 상기 제 1 및 제 2 절연기판(101, 171)의 외측면과 상기 화학약액과 반응하도록 함으로써 유리재질로 이루어진 상기 제 1 및 제 2 절연기판(101, 171)의 두께를 점진적으로 얇게 한다. 이러한 기판의 식각공정은 상기 화학약액이 담긴 수조에 상기 액정패널을 담구는 디핑(dipping)법을 통해 이루어지거나, 또는 상기 액정패널의 상부 및 하부에서 노즐 등을 통해 상기 화학약액을 분무하는 스프레이(spray)법을 통해 이루어진다.

- [0100] 이렇게 액정패널을 화학약액에 노출시켜 그 두께를 얇게하는 것은 경량박형의 액정표시장치를 형성하기 위함이다.

- [0101] 상기 박막트랜지스터(Tr)를 형성하거나 또는 컬러필터층(175)을 형성하기 위한 제조 공정 진행 시 상기 제 1 및 제 2 절연기판(101, 171) 자체를 얇은 두께의 유리기판을 이용할 경우 제조 공정 중 크랙(crack) 또는 깨짐 발생이 빈번하여 불량률이 높아진다.

- [0102] 따라서 제조 공정 중 깨짐 발생이 거의 발생하지 않을 정도의 충분한 두께(통상적으로 0.5mm 내지 0.7mm정도의 두께)를 갖는 유리재질의 기판을 이용하여 액정패널을 완성한 후, 전술한 바와 같은 기판 식각공정을 진행함으로써 상기 제 1 및 제 2 절연기판(101, 171) 자체의 두께를 0.2mm 내지 0.3mm 정도가 되도록 얇게하는 것이다.

- [0103] 다음, 도 5e에 도시한 바와 같이, 상기 기판 식각공정을 진행하여 그 두께를 얇게 한 액정패널의 상기 컬러필터 기판(107)의 외측면에 대해 유기 솔벤트에 유기물질 예를 들면 PMMA 또는 PET과 도전성 특성을 갖는 탄소나노튜브가 적정 중량% 비율로 혼합된 유기용액을 상온의 분위기에서 스판코팅 장치 또는 슬릿코팅 장치(195) 중 어느 하나의 장치를 이용하여 코팅하여 유기 용액층(182)을 형성 한다.

- [0104] 이후, 도 5f에 도시한 바와 같이, 상기 다수의 탄소나노튜브를 포함하는 유기 용액층(도 5e의 182)이 형성된 액정패널에 대해 이에 대해 퍼나스(furnace) 또는 오븐 등의 히팅 장치(미도시)를 통해 가열하는 건조공정을 진행하여 상기 유기 솔벤트를 회발하여 제거시킴으로써 300Å 내지 1000Å정도의 두께를 가지며 그 면적당  $10^6 \Omega /sq$  내지  $10^9 \Omega /sq$  정도가 되는 것을 특징으로 정전기 방지층(180)을 형성 한다. 이때 상기 건조 공정은 100°C 이하 더욱 바람직하게는 50°C 내지 80°C 정도의 온도 분위기에서 진행되는 것이 바람직하다. 이러한 온도 범위에서 상기 건조공정을 진행하는 것은 액정층(190)의 부피 팽창에 의한 액정패널의 셀터짐을 방지하고, 상기 액정층(190)이 100°C 이상의 고온의 분위기에 노출됨으로써 액정 상이 변경되는 표시품질이 저하되는 것을 방지하기 위함이다.

- [0105] 다음, 상기 정전기 방지층(180)이 형성된 액정패널에 대해 모듈공정을 진행하여 상기 어레이 기판의 비표시영역에 터치블럭(TB) 라인별로 상기 x센싱배선(미도시)과 y센싱배선(yS1)과 연결되도록 다수의 X방향센싱회로(미도시)와 y방향센싱회로(미도시)를 실장하고, 나아가 상기 게이트 및 데이터 배선(미도시, 130)과 연결되는 구동회로기판(미도시)을 실장함으로써 본 발명의 제 2 실시예의 제조 방법 따른 경량박형의 터치인식 횡전계형 액정표시장치를 완성한다.

## 부호의 설명

|        |                   |                            |

|--------|-------------------|----------------------------|

| [0106] | 100 : 횡전계형 액정표시장치 | 101 : 제 1 기판               |

|        | 113 : 반도체층        | 113a, 113b : 제 1, 2 반도체 영역 |

|        | 116 : 케이트 절연막     | 123 : 충간절연막                |

|        | 125 : 반도체층 콘택홀    | 130 : 데이터 배선               |

|        | 133 : 소스 전극       | 136 : 드레인 전극               |

|        | 140 : 제 1 보호층     | 145 : 제 2 보호층              |

|        | 150 : 공통전극        | 155 : 제 3 보호층              |

|        | 160 : 화소전극        | 171 : 제 2 기판               |

|        | 173 : 블랙매트릭스      | 175 : 컬러필터층                |

|        | 180 : 정전기 방지층     | 181 : 베이스층                 |

|        | 183 : 탄소나노튜브      | 190 : 액정층                  |

| P :    | 화소영역              | TB : 터치블럭                  |

| Tr :   | 박막트랜지스터           | ysl : y센싱배선                |

## 도면

### 도면1

### 도면2a

## 도면2b

## 도면3

## 도면4a

## 도면4b

## 도면4c

## 도면4d

## 도면4e

## 도면5a

## 도면5b

## 도면5c

## 도면5d

## 도면5e

## 도면5f

|                |                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 触敏横向电场型液晶显示装置及其制造方法                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">KR101298234B1</a>                                                                                                                                                                                                                    | 公开(公告)日 | 2013-08-22 |

| 申请号            | KR1020100024914                                                                                                                                                                                                                                  | 申请日     | 2010-03-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | OH KUM MI<br>오금미<br>KIM JIN WUK<br>김진욱<br>KIM SUNG HEE<br>김성희                                                                                                                                                                                    |         |            |

| 发明人            | 오금미<br>김진욱<br>김성희                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G02F1/1345 G06F3/041                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G02F1/1345 G02F1/13338 G06F3/0412 G06F3/044 G06F2203/04103 G06F3/0445 G06F3/0446 G02F1/133345 G02F1/133512 G02F1/133514 G02F1/134363 G02F1/136204 G02F1/1368 G02F2001/134318 G02F2001/134372 G02F2001/136295 G02F2201/121 G02F2201/123 G06F3/047 |         |            |

| 其他公开文献         | KR1020110105652A                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                        |         |            |

### 摘要(译)

液晶层设置在第一基板和面对第一基板的第二基板之间，公共电极和像素电极均设置在第一基板的内表面上，滤色器层设置在第二基板的内表面上。液晶面板的上表面9并且抗静电层形成在第一基板的外表面上并具有第一厚度并且由有机材料和碳纳米管的混合物形成，以具有 $10\Omega/\text{sq}$ 至 $10\Omega/\text{sq}$ 的薄层电阻。