## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G09G 3/36 (2006.01)

(11) 공개번호 10-2006-0064941

(43) 공개일자 2006년06월14일

(21) 출원번호 10-2004-0103629

(22) 출원일자 2004년12월09일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 안창호

경기 수원시 장안구 율전동 265-47

(74) 대리인 리엔목특허법인

이해영

심사청구 : 있음

(54) 높은 슬루 레이트를 가지는 액정 표시 장치에 포함된 소스드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법

#### 요약

높은 슬루 레이트를 가지는 액정 표시 장치에 포함된 소스 드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법이 제공된다. 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 출력 버퍼는 아날로그 영상 신호를 증폭하는 증폭부와, 증폭부에 의해 증폭된 신호들에 응답하여 소스 라인 구동 신호를 출력하는 출력부와, 소스 라인이 소정의 프리차지 전압으로 프리차지되는 시간인 제1 전하 공유 시간 동안 커패시터부의 커패시턴스를 소스 라인 구동 신호의 주파수 특성이 안정되도록 하는 제1 커패시턴스로 설정하고, 제1 전하 공유 시간 직후 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 커패시터부의 커패시턴스를 제1 커패시턴스 보다 작은 제2 커패시턴스로 설정하고, 제2 전하 공유 시간 직후에 소스 라인 구동 신호의 공급이 유지되는 동안 커패시터부의 커패시턴스를 제1 커패시턴스로 설정하는 슬루 레이트 제어부를 포함한다. 출력 버퍼 및 출력 버퍼의 제어 방법은 소스 라인 구동 신호의 슬루 레이트를 개선시킬 수 있고, 소스 라인에 흐르는 전류를 감소시킬 수 있다.

#### 내용도

도 4

#### 명세서

#### 도면의 간단한 설명

본 발명의 상세한 설명에서 사용되는 도면을 보다 충분히 이해하기 위하여, 각 도면의 간단한 설명이 제공된다.

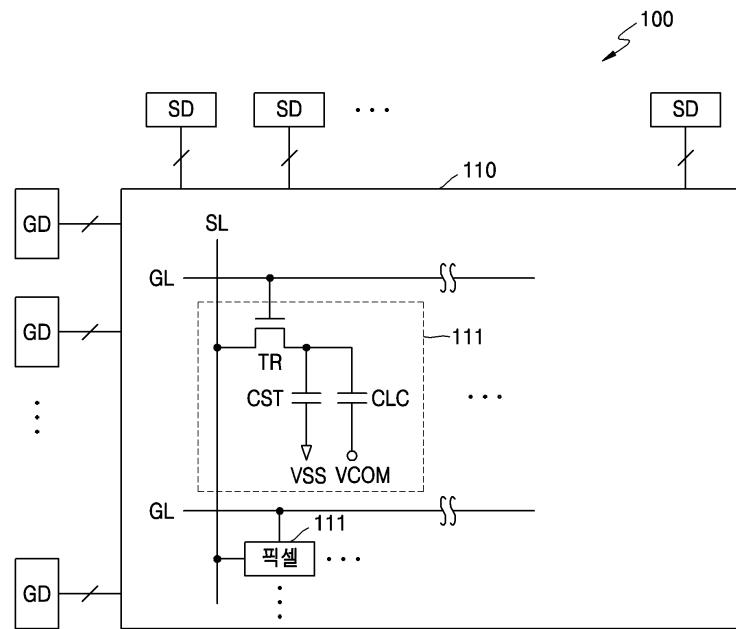

도 1은 일반적인 액정 표시 장치를 나타내는 도면이다.

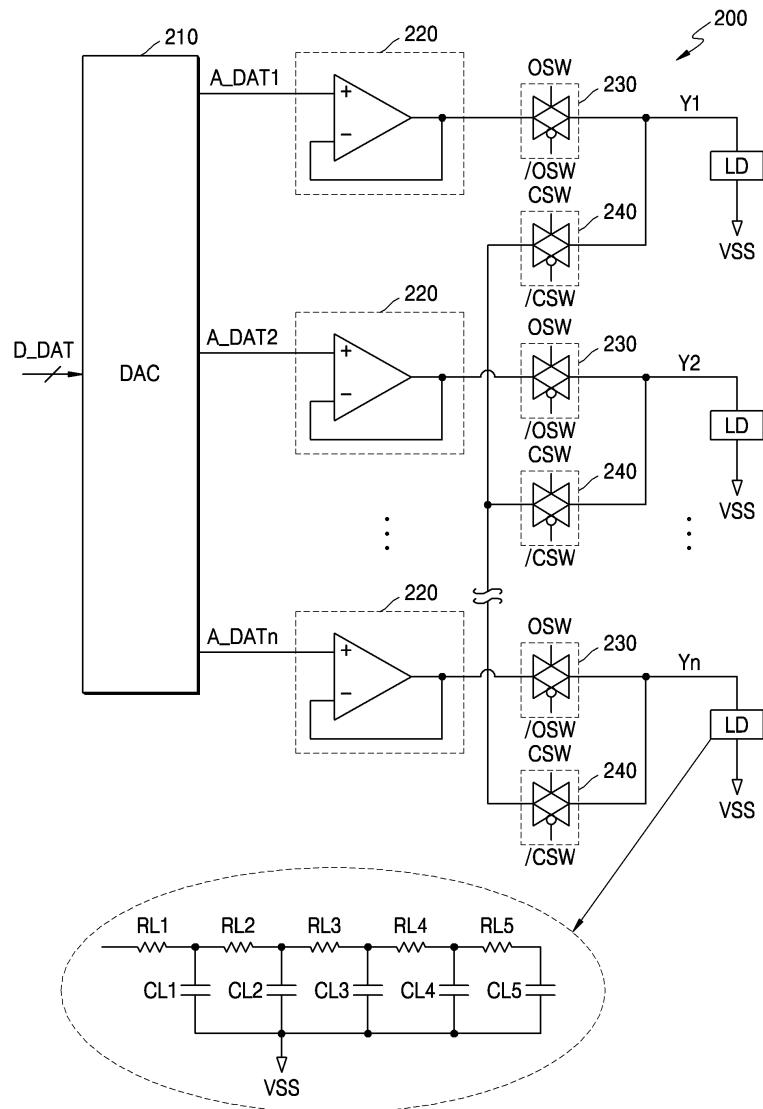

도 2는 도 1의 소스 드라이버를 개략적으로 나타내는 도면이다.

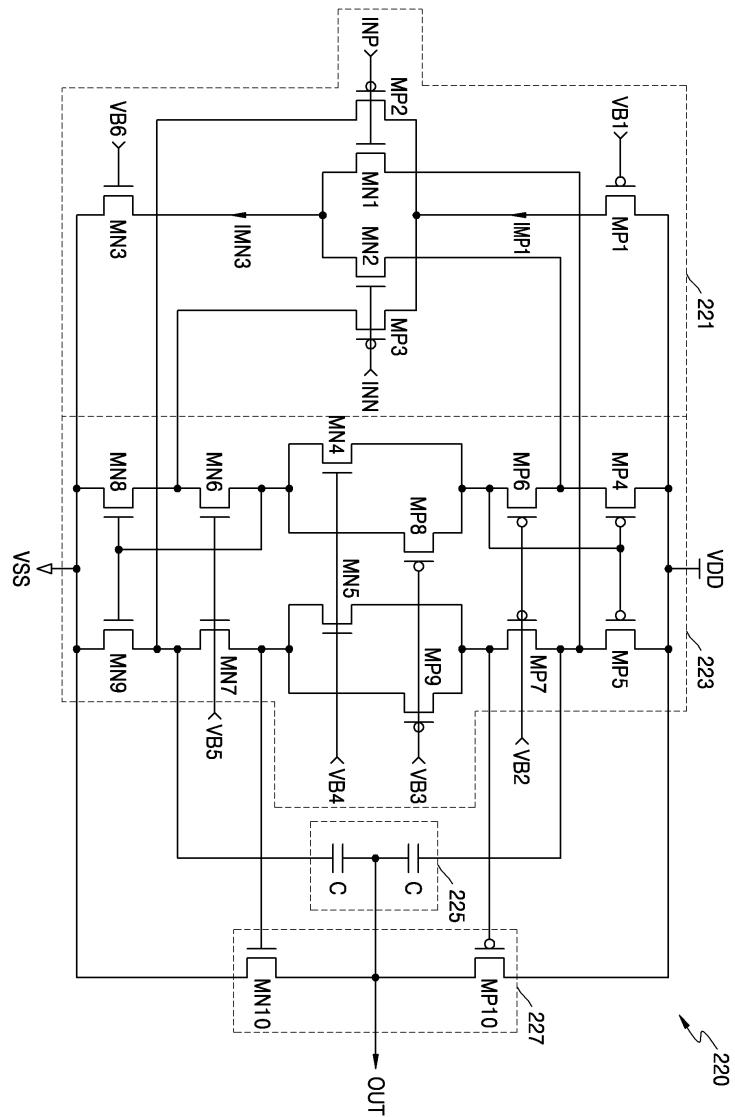

도 3은 도 2에 도시된 종래 기술에 따른 출력 버퍼를 나타내는 회로도이다.

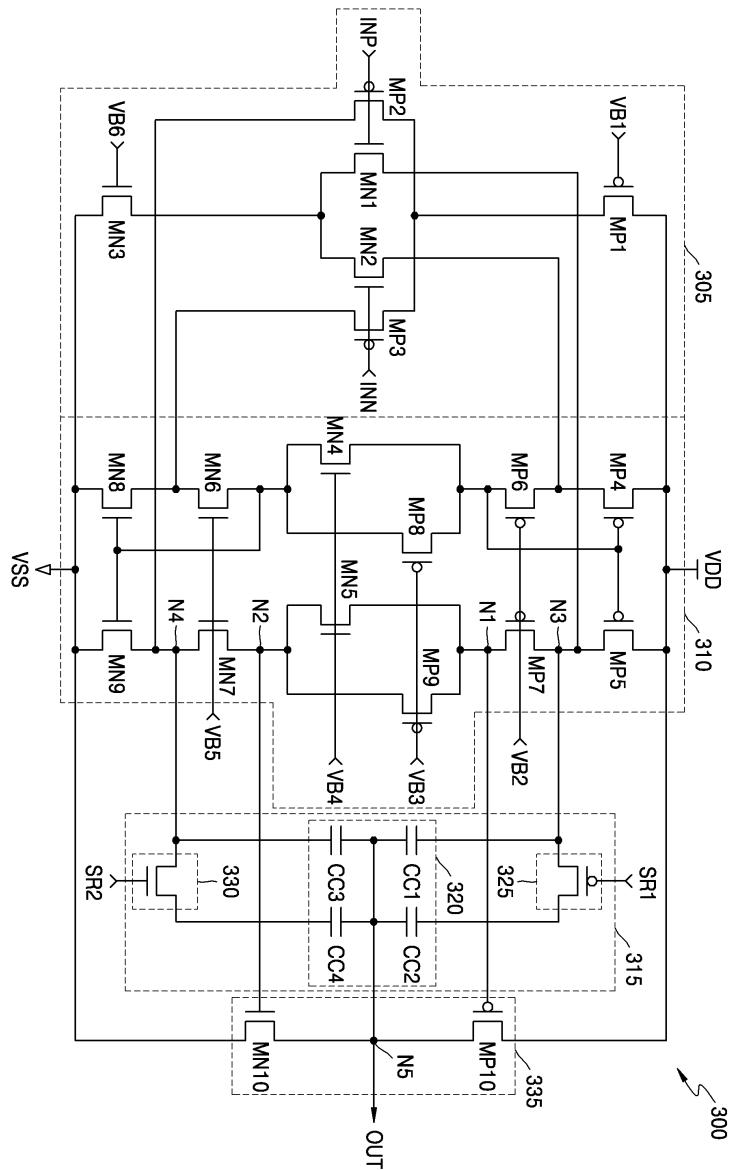

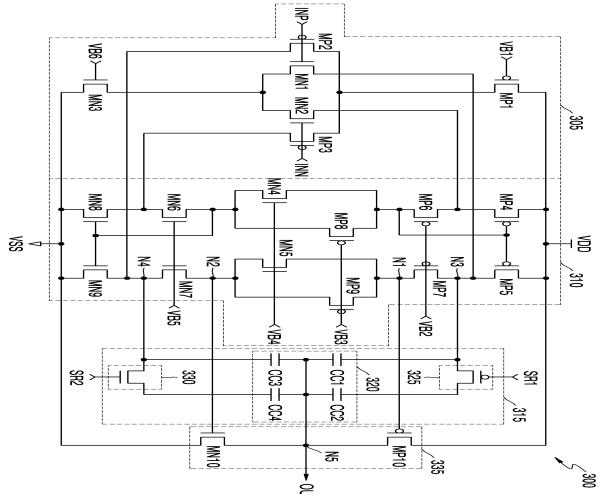

도 4는 본 발명의 실시예에 따른 출력 버퍼를 나타내는 회로도이다.

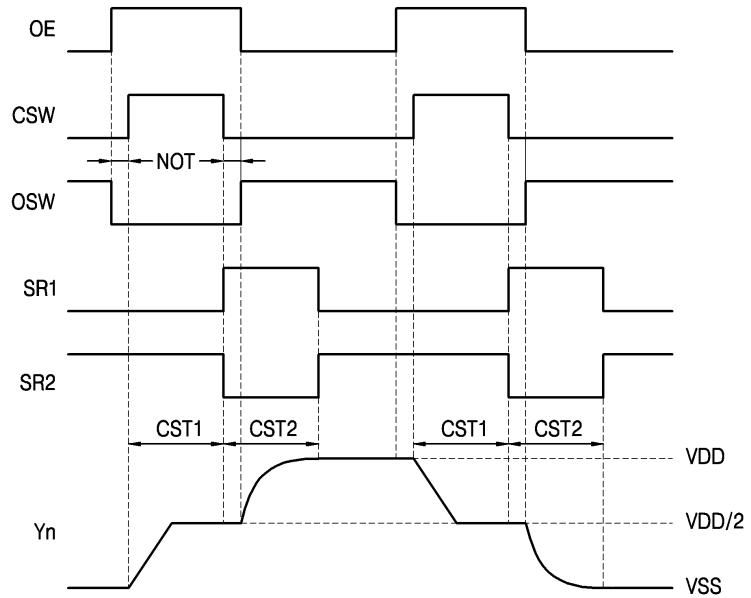

도 5는 도 4의 출력 버퍼가 도 2의 소스 드라이버의 출력 버퍼로 사용될 때의 소스 드라이버의 동작을 나타내는 예시적인 타이밍 다이어그램이다.

도 6은 본 발명의 시뮬레이션 결과(simulation result)와 종래 기술의 시뮬레이션 결과를 비교하는 도표(table)이다.

< 도면의 주요 부분에 대한 부호의 설명 >

305: 입력부 310: 증폭부

315: 슬루 레이트 제어부 335: 출력부

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시 장치에 관한 것으로, 보다 상세하게는, 높은 슬루 레이트를 가지는 액정 표시 장치에 포함된 소스 드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법에 관한 것이다.

액정 표시 장치(Liquid Crystal Display device; LCD)는 소형화, 박형화 및 저전력 소모의 장점들을 가지며, 노트북 컴퓨터 및 LCD TV 등에 이용되고 있다. 특히, 스위치 소자로서 박막 트랜지스터(Thin Film Transistor)를 이용하는 액티브 매트릭스 타입(active matrix type)의 액정 표시 장치는 동영상(moving image)을 표시(display)하기에 적합하다.

도 1은 일반적인 액정 표시 장치를 나타내는 도면이다. 도 1을 참조하면, 액정 표시 장치(100)는 액정 패널(liquid crystal panel)(110), 다수의 소스 라인(source line)(SL)들을 각각 가지는 소스 드라이버(source driver)(SD)들, 및 다수의 게이트 라인(gate line)(GL)들을 각각 가지는 게이트 드라이버(gate driver)(GD)들을 포함한다. 소스 라인은 데이터 라인(data line) 또는 채널(channel)이라고도 한다.

각각의 소스 드라이버(SD)들은 액정 패널(110) 상에 배치되는 소스 라인(SL)들을 구동한다. 각각의 게이트 드라이버(GD)들은 액정 패널(110) 상에 배치되는 게이트 라인(GL)들을 구동한다.

액정 패널(110)은 다수의 픽셀(pixel)(111)들을 포함한다. 각각의 픽셀(111)들은 스위치 트랜지스터(switch transistor) (TR), 액정으로부터의 전류 누설을 감소시키기 위한 저장 커패시터(storage capacitor)(CST), 및 액정 커패시터(liquid crystal capacitor)(CLC)를 포함한다. 스위치 트랜지스터(TR)는 게이트 라인(GL)을 구동하는 신호에 응답하여 턠-온/턴-오프(turn-on/turn-off)되고, 스위치 트랜지스터(TR)의 일 단자는 소스 라인(SL)에 연결된다. 저장 커패시터(CST)는 스위치 트랜지스터(TR)의 타 단자와 접지 전압(VSS) 사이에 연결되고, 액정 커패시터(CL)는 스위치 트랜지스터(TR)의 타 단자와 공통 전압(common voltage)(VCOM) 사이에 연결된다. 예를 들어, 공통 전압(VCOM)은 전원 전압(VDD)/2 일 수 있다.

액정 패널(110)상에 배치되는 픽셀(111)들에 연결된 각각의 소스 라인(SL)들의 부하(load)는 기생 저항들(parasitic resistors) 및 기생 커패시터들(parasitic capacitors)로 모델링(modelling)될 수 있다.

도 2는 도 1의 소스 드라이버를 개략적으로 나타내는 도면이다. 도 2를 참조하면, 소스 드라이버(200)는 디지털-아날로그 변환기(Digital-to-Analog Converter)(DAC, 210), 출력 버퍼(output buffer)(220)들, 출력 스위치(output switch)(230)들, 및 전하 공유 스위치(charge sharing switch)(240)들을 포함한다.

DAC(210)는 디지털 영상 신호들(digital image signals)(D\_DAT)을 아날로그 영상 신호들(analog image signals)(A\_DAT1, A\_DAT2, ..., A\_DATn)로 변환하여 출력한다. 상기 각각의 아날로그 영상 신호들(A\_DAT1, A\_DAT2, ..., A\_DATn)은 계조 레벨 전압(gray level voltage)을 나타낸다.

각각의 출력 버퍼(220)들은 대응되는 아날로그 영상 신호(A\_DAT1, A\_DAT2, ..., A\_DATn 중 하나)를 증폭하여 대응되는 출력 스위치(230)로 전달한다. 출력 스위치(230)는 출력 스위치 제어 신호들(OSW, /OSW)의 활성화에 응답하여 증폭된 아날로그 영상 신호를 소스 라인 구동 신호(Y1, Y2, ..., Yn 중 하나)로서 출력한다. 상기 소스 라인 구동 신호는 소스 라인에 연결된 부하(load)(LD)에 공급된다. 상기 부하(LD)는, 도 2에 도시된 바와 같이, 사다리형(ladder type)으로 연결된 기생 저항들(RL1 ~ RL5)과 기생 커패시터들(CL1 ~ CL5)로 모델링될 수 있다.

전하 공유 스위치(240)는 공유 스위치 제어 신호들(CSW, /CSW)의 활성화에 응답하여 전체 소스 라인들에 연결된 부하들에 저장된 전하들을 공유시켜 소스 라인 구동 신호의 전압을 소정의 프리차지 전압(precharge voltage)으로 프리차징(precharging)한다. 상기 프리차지 전압은, 이웃하는 소스 라인 구동 신호들의 전압 극성(polarity)이 서로 반대일 때(예를 들어, 제1 소스 라인 구동 신호(Y1)의 전압이 VDD과 VDD/2 사이의 정극성(positive polarity)의 전압이고 제2 소스 라인 구동 신호(Y2)의 전압이 VDD/2와 VSS(접지 전압) 사이의 부극성의 전압일 때), VDD/2 일 수 있다. 이러한 전하 공유 방법은 출력 버퍼(220)의 전류 공급 부담을 감소시키기 위하여 대형 액정 패널 구동용 소스 드라이버에서 대부분 사용된다.

전하 공유 스위치(240)는 출력 스위치(230)가 턴-온되기 전 전하 공유 시간(charge sharing time)동안 전체 소스 라인 구동 신호들의 전압이 VDD/2가 되도록 제어한다. 즉, 전체 소스 라인 구동 신호들의 전압이 VDD/2로 프리차지된 후, 턴-온된 출력 스위치(230)는 출력 버퍼(220)에 의해 증폭된 소스 라인 구동 신호를 부하(LD)에 공급한다.

도 3은 도 2에 도시된 종래 기술에 따른 출력 버퍼를 나타내는 회로도이다. 도 3을 참조하면, 종래의 출력 버퍼(220)는 레일-투-레일 연산 증폭기(rail-to-rail operational amplifier)로 구현된다.

종래의 출력 버퍼(220)는 입력부(input portion)(221), 증폭부(amplifier portion)(223), 커패시터부(225), 및 출력부(227)를 포함하며, 출력 신호(OUT)가 입력 신호들(INP, INN)중 반전(inverting) 입력 신호(INN)로 피드백(feedback)되는 전압 팔로워 구조(voltage follower configuration)를 가진다. 제1 입력 신호(INP)는 아날로그 영상 신호이고 제2 입력 신호(INN)는 소스 라인 구동 신호이다.

입력부(221)는 피모스(PMOS) 트랜지스터들(MP1 ~ MP3) 및 엔모스(NMOS) 트랜지스터들(MN1 ~ MN3)을 포함하며, 서로 상보(complementary) 신호 관계인 제1 입력 신호(INP)와 제2 입력 신호(INN)를 수신한다. 제1 피모스 트랜지스터(MP1)의 게이트(gate)에 제1 바이어스(bias) 전압(VB1)이 인가되고, 제3 엔모스 트랜지스터(MN3)의 게이트에 제6 바이어스 전압(VB6)이 인가된다.

증폭부(223)는 폴디드 캐스코드 부분(folded cascode portion)으로서 피모스 트랜지스터들(MP4 ~ MP9) 및 엔모스 트랜지스터들(MN4 ~ MN9)을 포함하며, 입력부(221)의 출력 신호들을 수신하여 입력 신호들(INP, INN)을 증폭한다. 제6 및 제7 피모스 트랜지스터들(MP6, MN7)의 게이트들에 제2 바이어스 전압(VB2)이 인가되고 제8 및 제9 피모스 트랜지스터들(MP8, MP9)의 게이트들에 제3 바이어스 전압(VB3)이 인가되며, 제4 및 제5 엔모스 트랜지스터들(MN4, MN5)의 게이트들에 제4 바이어스 전압(VB4)이 인가되고 제6 및 제7 엔모스 트랜지스터들(MN6, MN7)의 게이트들에 제5 바이어스 전압(VB5)이 인가된다.

커패시터부(225)는 두 개의 커패시터(C)들을 포함하며, 출력 신호(OUT)의 주파수 특성(frequency characteristics)을 안정화시키는 역할을 수행한다. 즉, 커패시터부(225)는 출력 버퍼(220)의 출력 신호(OUT)가 발진(oscillation)하지 않도록 제어한다. 커패시터부(225)는 밀러 보상(Miller compensation) 커패시터부라고도 한다.

출력부(227)는 피모스 트랜지스터(MP10) 및 엔모스 트랜지스터(MN10)를 포함하며, 증폭부(223)의 출력 신호들을 수신하여 출력 버퍼(220)의 출력 신호(OUT)를 발생한다. 상기 출력 신호(OUT)는 소스 라인 구동 신호이다.

종래의 출력 버퍼(220)의 출력 전압의 슬루 레이트(slew rate)(SR)는 다음 같이 주어진다.

[수학식 1]

$$SR = dV_{out}/dt = (IMP1 + IMN3)/2C$$

상기 [수학식 1]에서,  $V_{out}$ 는 출력 버퍼(220)의 출력 전압이고  $IMP1$ 은 제1 피모스 트랜지스터(MP1)를 통해 흐르는 전류량이고  $IMN3$ 는 제3 엔모스 트랜지스터(MN3)를 통해 흐르는 전류량이고  $C$ 는 커패시터부(225)에 포함된 커패시터(C)의 커패시턴스이다.

종래의 출력 버퍼(220)는 고정된 값을 가지는 커패시터(C)를 가지므로, 출력 전압의 슬루 레이트(SR)를 용이하게 개선할 수 없다. 따라서, 종래의 출력 버퍼(220)를 사용하는 소스 드라이버를 큰 부하를 가지는 소스 라인이 배치되는 대형 액정 패널용 소스 드라이버로 사용하는 것은 부적합하다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명이 이루고자 하는 기술적 과제는 커패시터의 값을 조절하는 것에 의해 높은 슬루 레이트를 가지는 액정 표시 장치에 포함된 소스 드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법을 제공하는 데 있다.

### 발명의 구성 및 작용

상기 기술적 과제를 달성하기 위하여 본 발명의 일면에 따른 출력 버퍼는 액정 표시 장치의 소스 드라이버에 포함되고, 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 것에 관한 것이다. 상기 출력 버퍼는, 아날로그 영상 신호를 증폭하는 증폭부; 상기 증폭부에 의해 증폭된 신호들에 응답하여 상기 소스 라인 구동 신호를 출력하는 출력부; 및 상기 소스 라인이 소정의 프리차지 전압으로 프리차지되는 시간인 제1 전하 공유 시간 동안 커패시터부의 커패시턴스를 상기 소스 라인 구동 신호의 주파수 특성이 안정화되도록 하는 제1 커패시턴스로 설정하고, 상기 제1 전하 공유 시간 직후 상기 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스 보다 작은 제2 커패시턴스로 설정하고, 상기 제2 전하 공유 시간 직후에 상기 소스 라인 구동 신호의 공급이 유지되는 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스로 설정하는 슬루 레이트 제어부를 구비하는 것을 특징으로 한다.

바람직한 실시예에 따르면, 상기 제1 전하 공유 시간과 상기 제2 전하 공유 시간은 동일하고, 상기 프리차지 전압은 전원 전압의  $1/2$ 이고, 상기 제2 커패시턴스는 0이다.

바람직한 실시예에 따르면, 상기 출력 버퍼는 상기 아날로그 영상 신호 및 상기 소스 라인 구동 신호가 입력되는 입력부를 더 구비한다.

바람직한 실시예에 따르면, 상기 출력 버퍼는 레일-투-레일 연산 증폭기로 구현되거나 또는 두 개의 단방향 연산 증폭기들로 구현된다.

바람직한 실시예에 따르면, 상기 제1 커패시턴스는 제1 및 제2 슬루 레이트 제어 신호들의 활성화에 의해 설정되고 상기 제2 커패시턴스는 상기 제1 및 제2 슬루 레이트 제어 신호들의 비활성화에 의해 설정되며, 상기 제1 슬루 레이트 제어 신호는 상기 소스 라인이 상기 프리차지 전압으로 프리차지되도록 제어하는 공유 스위치 제어 신호를 지연한 신호이고, 상기 제2 슬루 레이트 제어 신호는 상기 제1 슬루 레이트 제어 신호의 반전 신호이다.

바람직한 실시예에 따르면, 상기 제1 슬루 레이트 제어 신호는 상기 공유 스위치 제어 신호를 D 플립-플립을 통해 상기 제1 전하 공유 시간만큼 지연한 신호이다.

바람직한 실시예에 따르면, 상기 슬루 레이트 제어부는, 상기 제1 및 제2 슬루 레이트 제어 신호들에 각각 응답하여, 상기 커패시터부의 커패시턴스가 상기 제1 커패시턴스로부터 상기 제2 커패시턴스로 또는 상기 제2 커패시턴스로부터 상기 제1 커패시턴스로 변환되도록 제어하는 제1 및 제2 스위치들을 더 구비한다.

바람직한 실시예에 따르면, 상기 제1 스위치는 피모스 트랜지스터이고, 상기 제2 스위치는 엔모스 트랜지스터이다.

상기 기술적 과제를 달성하기 위하여 본 발명의 다른 일면에 따른 출력 버퍼는 액정 표시 장치의 소스 드라이버에 포함되고, 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 것에 관한 것이다. 상기 출력 버퍼는, 아날로그 영상 신호를 증폭하는 증폭부; 상기 증폭부에 의해 증폭된 신호들에 응답하여 상기 소스 라인 구동 신호를 출력 노드를 통해 출력하는 출력부; 및 상기 소스 라인 구동 신호의 주파수 특성을 안정화시키고 상기 소스 라인 구동 신호의 전압에 대한 슬루 레이트를 개선하는 슬루 레이트 제어부를 구비하며, 상기 슬루 레이트 제어부는, 상기 증폭부에 포함된 제1 전류 미러 회로의 출력

노드와 상기 출력 노드 사이에 연결되는 제1 커패시터; 상기 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작될 때 상기 제1 커패시터와의 병렬 연결이 분리되는 제2 커패시터; 상기 증폭부에 포함된 제2 전류 미러 회로의 출력 노드와 상기 출력 노드 사이에 연결되는 제3 커패시터; 및 상기 소스 라인 구동 신호의 공급이 시작될 때 상기 제3 커패시터와의 병렬 연결이 분리되는 제4 커패시터를 구비하는 것을 특징으로 한다.

바람직한 실시예에 따르면, 상기 제1 및 제3 커패시터들의 커패시턴스들은 서로 동일하고, 상기 제2 및 제4 커패시터들의 커패시턴스들은 서로 동일하다.

바람직한 실시예에 따르면, 상기 제1 및 제3 커패시터들의 커패시턴스들은 각각 0이다.

상기 기술적 과제를 달성하기 위하여 본 발명에 따른 출력 버퍼의 제어 방법은 액정 표시 장치의 소스 드라이버에 포함되고 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 출력 버퍼를 제어하는 방법에 관한 것이다. 상기 제어 방법은, (a) 상기 소스 라인이 소정의 끌리차지 전압으로 끌리차지되는 시간인 제1 전하 공유 시간 동안 상기 출력 버퍼에 포함된 커패시터부의 커패시턴스를 상기 소스 라인 구동 신호의 주파수 특성이 안정되도록 하는 제1 커패시턴스로 설정하는 단계; (b) 상기 제1 전하 공유 시간 직후의 시간으로서 상기 소스 라인에 대한 상기 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스 보다 작은 제2 커패시턴스로 설정하는 단계; 및 (c) 상기 제2 전하 공유 시간 직후에 상기 소스 라인 구동 신호의 공급이 유지되는 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스로 설정하는 단계를 구비하는 것을 특징으로 한다.

이러한 본 발명에 따른 액정 표시 장치에 포함된 소스 드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법은 소스 라인 구동 신호의 슬루 레이트를 개선시킬 수 있고, 소스 라인에 흐르는 전류를 감소시킬 수 있다.

본 발명과 본 발명의 동작상의 이점 및 본 발명의 실시에 의하여 달성되는 목적을 충분히 이해하기 위해서는 본 발명의 바람직한 실시예를 예시하는 첨부 도면 및 첨부 도면에 기재된 내용을 참조하여야만 한다.

이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명함으로써, 본 발명을 상세히 설명한다. 각 도면에 제시된 동일한 참조부호는 동일한 부재를 나타낸다.

도 4는 본 발명의 실시예에 따른 출력 버퍼를 나타내는 회로도이다. 도 4를 참조하면, 본 발명에 따른 출력 버퍼(300)는 레일-투-레일 연산 증폭기로 구현될 수 있으며, 도 2에 도시된 소스 드라이버(200)의 출력 버퍼(220) 대신 사용된다.

본 발명의 실시예에 따른 출력 버퍼(300)는 입력부(305), 증폭부(310), 슬루 레이트 제어부(315), 및 출력부(335)를 구비하며, 출력 신호(OUT)가 입력 신호들(INP, INN) 중 반전 입력 신호(INN)로 피드백되는 전압 팔로워 구조를 가진다. 제1 입력 신호(INP)는 아날로그 영상 신호이고 제2 입력 신호(INN)는 소스 라인 구동 신호이다.

입력부(305)는 피모스 트랜지스터들(MP1 ~ MP3) 및 엔모스 트랜지스터들(MN1 ~ MN3)을 포함하며, 서로 상보 신호 관계인 제1 입력 신호(INP)와 제2 입력 신호(INN)를 수신한다. 제1 피모스 트랜지스터(MP1)의 게이트에 제1 바이어스 전압(VB1)이 인가되고, 제3 엔모스 트랜지스터(MN3)의 게이트에 제6 바이어스 전압(VB6)이 인가된다.

증폭부(310)는 폴디드 캐스코드 부분으로서 피모스 트랜지스터들(MP4 ~ MP9) 및 엔모스 트랜지스터들(MN4 ~ MN9)을 포함하며, 입력부(305)의 출력 신호들을 수신하여 입력 신호들(INP, INN)을 증폭한다. 제6 및 제7 피모스 트랜지스터들(MP6, MN7)의 게이트들에 제2 바이어스 전압(VB2)이 인가되고 제8 및 제9 피모스 트랜지스터들(MP8, MP9)의 게이트들에 제3 바이어스 전압(VB3)이 인가되며, 제4 및 제5 엔모스 트랜지스터들(MN4, MN5)의 게이트들에 제4 바이어스 전압(VB4)이 인가되고 제6 및 제7 엔모스 트랜지스터들(MN6, MN7)의 게이트들에 제5 바이어스 전압(VB5)이 인가된다.

제4 내지 제7 피모스 트랜지스터들(MP4 ~ MP7)은 제1 전류 미러 회로(current mirror circuit)를 구성하고, 제6 내지 제9 엔모스 트랜지스터들(MN6 ~ MN9)은 제2 전류 미러 회로를 구성한다. 제8 및 제9 피모스 트랜지스터들(MP8, MP9)과 제4 및 제5 엔모스 트랜지스터들(MN4, MN5)은 출력부(335)의 제10 피모스 트랜지스터(MP10)를 통해 흐르는 전류량 및 / 또는 출력부(335)의 제10 엔모스 트랜지스터(MN10)를 통해 흐르는 전류량을 제어한다.

출력부(335)는 피모스 트랜지스터(MP10) 및 엔모스 트랜지스터(MN10)를 포함하며, 증폭부(320)의 출력 노드(output node)(N1, N2)의 신호들을 수신하여 출력 노드(N5)를 통해 출력 버퍼(300)의 출력 신호(OUT)를 발생한다. 상기 출력 신호(OUT)는 도 2에 도시된 소스 라인을 구동하는 소스 라인 구동 신호이다.

슬루 레이트 제어부(315)는 밀리 보상 커패시터부인 커패시터부(320), 제1 스위치(325), 및 제2 스위치(330)를 구비한다. 커패시터부(320)는 제1 내지 제4 커패시터들(CC1, CC2, CC3, CC4)을 포함한다. 제1 커패시터(CC1)는 증폭부(310)에 포함된 제1 전류 미러 회로의 출력 노드(N3)와 출력부(335)의 출력 노드(N5) 사이에 연결되고, 제2 커패시터(CC2)는 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작될 때 제1 커패시터(CC1)와의 병렬 연결이 분리된다. 제3 커패시터(CC3)는 증폭부(310)에 포함된 제2 전류 미러 회로의 출력 노드(N4)와 출력부(335)의 출력 노드(N5) 사이에 연결되고, 제4 커패시터(CC4)는 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작될 때 제3 커패시터(CC3)와의 병렬 연결이 분리된다.

제1 및 제3 커패시터들(CC1, CC3)의 커패시턴스들은 서로 동일하고, 제2 및 제4 커패시터들(CC2, CC4)의 커패시턴스들은 서로 동일한 것이 바람직하다. 그리고, 제1 커패시터(CC1)의 커패시턴스는 최소값이 0이고 최대값이 제1 커패시터(CC1)의 커패시턴스일 수 있다. 한편, 제1 커패시터(CC1)와 제2 커패시터(CC2)의 병렬 커패시턴스(parallel capacitance)는 도 3에 도시된 커패시터(C)의 커패시턴스와 같다.

제1 스위치(325)는 피모스 트랜지스터이고 제2 스위치(330)는 엔모스 트랜지스터인 것이 바람직하다. 제1 스위치(325)는 제1 슬루 레이트 제어 신호(SR1)에 응답하여 제1 커패시터(CC1)와 제2 커패시터(CC2)를 연결 또는 분리한다. 제2 스위치(330)는 제2 슬루 레이트 제어 신호(SR2)에 응답하여 제3 커패시터(CC3)와 제4 커패시터(CC4)를 연결 또는 분리한다. 제1 슬루 레이트 제어 신호(SR1)는 소스 라인에 소정의 프리차지 전압으로 프리차지되도록 제어하는 공유 스위치 제어 신호(도 2의 CSW)를 지연한 신호이고, 제2 슬루 레이트 제어 신호(SR2)는 제1 슬루 레이트 제어 신호(SR1)의 반전(inversion) 신호이다. 상기 프리차지 전압은 전원 전압의 1/2이고, 제1 슬루 레이트 제어 신호(SR1)는 상기 공유 스위치 제어 신호를 D 플립-플롭(flip-flop)을 통해 소스 라인에 상기 프리차지 전압으로 프리차지되는 시간인 제1 전하 공유 시간만큼 지연한 신호인 것이 바람직하다.

슬루 레이트 제어부(315)는 상기 제1 전하 공유 시간 동안 커패시터부(320)의 커패시턴스를 소스 라인 구동 신호의 주파수 특성이 안정되도록 하는 제1 커패시턴스(즉, CC1과 CC2와의 병렬 연결 및 CC3과 CC4와의 병렬 연결로 구성되는 커패시턴스)로 설정(setting)한다. 그리고, 슬루 레이트 제어부(315)는 상기 제1 전하 공유 시간 직후의 시간으로서 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 커패시터부(320)의 커패시턴스를 상기 제1 커패시턴스 보다 작은 제2 커패시턴스(즉, CC1과 CC3로 구성되는 커패시턴스)로 설정하고, 상기 제2 전하 공유 시간 직후에 상기 소스 라인 구동 신호의 공급이 유지되는 동안 커패시터부(320)의 커패시턴스를 상기 제1 커패시턴스로 설정한다. 상기 제1 커패시턴스는 제1 및 제2 슬루 레이트 제어 신호들(SR1, SR2)의 활성화에 의해 설정되고 상기 제2 커패시턴스는 제1 및 제2 슬루 레이트 제어 신호들(SR1, SR2)의 비활성화에 의해 설정된다. 상기 제1 전하 공유 시간과 상기 제2 전하 공유 시간은 동일한 것이 바람직하다.

요약하면, 슬루 레이트 제어부(315)는 제1 및 제2 슬루 레이트 제어 신호들(SR1, SR2)에 각각 응답하여, 커패시터부(320)의 커패시턴스가 상기 제1 커패시턴스로부터 상기 제2 커패시턴스로 또는 상기 제2 커패시턴스로부터 상기 제1 커패시턴스로 변환되도록 제어한다. 따라서, 슬루 레이트 제어부(315)는 소스 라인 구동 신호(OUT)의 주파수 특성을 안정화시키고 소스 라인 구동 신호(OUT)의 전압에 대한 슬루 레이트를 개선한다.

따라서, 본 발명의 실시예에 따른 출력 버퍼(300)는 [수학식 1]에 기재된 커패시터부(320)의 커패시턴스를 조절하는 것에 의해 높은 슬루 레이트를 가지는 소스 라인 구동 신호(OUT)를 출력할 수 있다.

한편, 본 발명의 실시예에 따른 출력 버퍼(300)는 레일-투-레일 연산 증폭기로 구현되었지만, 본 발명에 따른 슬루 레이트 제어부(315)는 레일-투-레일 연산 증폭기의 입력부와 다른 구조를 가지는 입력부를 각각 포함하는 두 개의 단방향 연산 증폭기들(single operational amplifiers)에도 적용될 수 있다.

도 5는 도 4의 출력 버퍼가 도 2의 소스 드라이버의 출력 버퍼로 사용될 때의 소스 드라이버의 동작을 나타내는 예시적 인 타이밍 다이어그램이다.

도 5를 참조하면, 공유 스위치 제어 신호(CSW) 및 출력 스위치 제어 신호(OSW)는 출력 인에이블 신호(OE)로부터 발생된다. 출력 인에이블 신호(OE)는 소스 드라이버(200)를 제어하는 타이밍 컨트롤러(timing controller)로부터 발생된다.

공유 스위치 제어 신호(CSW)가 하이 레벨(high level) 상태(활성화 상태(activation state))를 유지하는 동안(즉, 제1 전하 공유 시간(CST1) 동안), 소스 라인 구동 신호(Y<sub>n</sub>, n은 자연수 중 하나)는 접지 전압(VSS)으로부터 프리차지 전압(VDD/2)으로 상승한다. 제1 전하 공유 시간(CST1)은, 예를 들어, 0.5(μs) 내지 1.0(μs)일 수 있다. 제1 전하 공유 시간(CST1) 동

안, 제1 슬루 레이트 제어 신호(SR1)는 로우 레벨(low level)로 활성화되고 제2 슬루 레이트 제어 신호(SR2)는 하이 레벨로 활성화되므로, 커패시터부(도 4의 320)의 커패시턴스는 제1 커패시턴스(즉, CC1과 CC2와의 병렬 연결 및 CC3과 CC4와의 병렬 연결로 구성되는 커패시턴스)로 설정된다.

제1 전하 공유 시간(CST1) 직후의 시간으로서 제1 전하 공유 시간과 동일한 시간인 제2 전하 공유 시간(CST2) 동안, 출력 스위치 제어 신호(OSW)가 넌-오버래핑 시간(non-overlapping time)(NOT) 후에 하이 레벨을 유지하므로 소스 라인에 소스 라인 구동 신호 중 정극성의 전압(예를 들어, 전원 전압(VDD))이 공급되기 시작한다. 상기 넌-오버래핑 시간(NOT)은 소스 라인에 과도한 전류가 흐르는 것을 방지하기 위해 필요한 시간으로서, 예를 들어, 5(ns)일 수 있다. 제2 전하 공유 시간(CST2) 동안, 제1 슬루 레이트 제어 신호(SR1)는 하이 레벨로 비활성화되고 제2 슬루 레이트 제어 신호(SR2)는 로우 레벨로 비활성화되므로, 커패시터부(도 4의 320)의 커패시턴스는 제2 커패시턴스(즉, CC1과 CC3로 구성되는 커패시턴스)로 설정된다. 그 결과, 소스 라인 구동 신호(Yn)가 VDD를 향해 급격히 상승한다. 즉, 제2 전하 공유 시간(CST2)은 높은 슬루 레이트 구간(time interval)을 나타낸다.

제2 전하 공유 시간(CST2) 직후에 제1 슬루 레이트 제어 신호(SR1)는 로우 레벨로 다시 활성화되고 제2 슬루 레이트 제어 신호(SR2)는 하이 레벨로 다시 활성화되므로, 커패시터부(도 4의 320)의 커패시턴스는 상기 제1 커패시턴스로 다시 설정된다. 그 결과, 소스 라인 구동 신호(Yn)의 주파수 특성이 안정화된다. 이 때, 출력 스위치 제어 신호(OSW)는 하이 레벨을 유지하므로 소스 라인 구동 신호(Yn)는 VDD 레벨을 유지한다.

한편, 소스 라인 구동 신호(Yn)의 전압이 부극성의 전압(예를 들어, VSS)인 경우도 전술한 정극성의 전압인 소스 라인 구동 신호(Yn)에 대한 설명과 유사하므로, 그것에 대한 설명은 생략된다.

도 6은 본 발명의 시뮬레이션 결과(simulation result)와 종래 기술의 시뮬레이션 결과를 비교하는 도표(table)이다.

도 6의 도표에는 VDD가 13.5(Volt)일 때의 안정화 시간(settling time) 및 소스 라인에 흐르는 동작 전류(operating current)(IDD)가 기재되어 있다. 상기 안정화 시간은 상승 시간(rising time) 및 하강 시간(falling time)으로 분류된다. 그리고, 상승 시간은 제1 상승 시간( $Tr_1$ ) 및 제2 상승 시간( $Tr_2$ )으로 분류되고, 하강 시간은 제1 하강 시간( $Tf_1$ ) 및 제2 하강 시간( $Tf_2$ )으로 분류된다. 제1 상승 시간( $Tr_1$ )은 소스 라인 구동 신호가 타겟 전압(target voltage)의 10%에서 타겟 전압의 90%까지 도달하는 데 소비되는 시간이고 제2 상승 시간( $Tr_2$ )은 소스 라인 구동 신호가 타겟 전압의 10%에서 타겟 전압의 99.5%까지 도달하는 데 소비되는 시간이며, 제1 하강 시간( $Tf_1$ )은 소스 라인 구동 신호가 타겟 전압의 90%에서 타겟 전압의 10%까지 도달하는 데 소비되는 시간이고 제2 하강 시간( $Tf_2$ )은 소스 라인 구동 신호가 타겟 전압의 99.5%에서 타겟 전압의 10%까지 도달하는 데 소비되는 시간이다.

도 6의 도표에 기재된 수치를 참조하면, 본 발명에 따른 출력 버퍼는 종래 기술에 따른 출력 버퍼와 비교할 때 소스 라인 구동 신호의 상승 시간 및 하강 시간을 감소시키고(즉, 소스 라인 구동 신호의 슬루 레이트를 개선시키고), 1 채널(channel)(또는 소스 라인)에 흐르는 전류를 감소시킨다.

이상에서와 같이 도면과 명세서에서 최적의 실시예들이 개시되었다. 여기서, 특정한 용어들이 사용되었으나, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 발명의 효과

본 발명에 따른 액정 표시 장치에 포함된 소스 드라이버의 출력 버퍼 및 출력 버퍼의 제어 방법은 소스 라인 구동 신호의 슬루 레이트를 개선시킬 수 있고, 소스 라인에 흐르는 전류를 감소시킬 수 있다.

### (57) 청구의 범위

#### 청구항 1.

액정 표시 장치의 소스 드라이버에 포함되고, 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 출력 버퍼에 있어서,

아날로그 영상 신호를 증폭하는 증폭부;

상기 증폭부에 의해 증폭된 신호들에 응답하여 상기 소스 라인 구동 신호를 출력하는 출력부; 및

상기 소스 라인이 소정의 프리차지 전압으로 프리차지되는 시간인 제1 전하 공유 시간 동안 커패시터부의 커패시턴스를 상기 소스 라인 구동 신호의 주파수 특성이 안정되도록 하는 제1 커패시턴스로 설정하고, 상기 제1 전하 공유 시간 직후 상기 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스 보다 작은 제2 커패시턴스로 설정하고, 상기 제2 전하 공유 시간 직후에 상기 소스 라인 구동 신호의 공급이 유지되는 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스로 설정하는 슬루 레이트 제어부를 구비하는 것을 특징으로 하는 출력 버퍼.

## 청구항 2.

제1항에 있어서,

상기 제1 전하 공유 시간과 상기 제2 전하 공유 시간은 동일한 것을 특징으로 하는 출력 버퍼.

## 청구항 3.

제1항에 있어서,

상기 프리차지 전압은 전원 전압의 1/2인 것을 특징으로 하는 출력 버퍼.

## 청구항 4.

제1항에 있어서,

상기 제2 커패시턴스는 0 인 것을 특징으로 하는 출력 버퍼.

## 청구항 5.

제1항에 있어서, 상기 출력 버퍼는

상기 아날로그 영상 신호 및 상기 소스 라인 구동 신호가 입력되는 입력부를 더 구비하는 것을 특징으로 하는 출력 버퍼.

## 청구항 6.

제5항에 있어서,

상기 출력 버퍼는 레일-투-레일 연산 증폭기로 구현되는 것을 특징으로 하는 출력 버퍼.

## 청구항 7.

제5항에 있어서,

상기 출력 버퍼는 두 개의 단방향 연산 증폭기들로 구현되는 것을 특징으로 하는 출력 버퍼.

## 청구항 8.

제5항에 있어서,

상기 제1 커패시턴스는 제1 및 제2 슬루 레이트 제어 신호들의 활성화에 의해 설정되고 상기 제2 커패시턴스는 상기 제1 및 제2 슬루 레이트 제어 신호들의 비활성화에 의해 설정되며,

상기 제1 슬루 레이트 제어 신호는 상기 소스 라인이 상기 프리차지 전압으로 프리차지되도록 제어하는 공유 스위치 제어 신호를 지연한 신호이고, 상기 제2 슬루 레이트 제어 신호는 상기 제1 슬루 레이트 제어 신호의 반전 신호인 것을 특징으로 하는 출력 버퍼.

## 청구항 9.

제8항에 있어서,

상기 제1 슬루 레이트 제어 신호는 상기 공유 스위치 제어 신호를 D 플립-플립을 통해 상기 제1 전하 공유 시간만큼 지연한 신호인 것을 특징으로 하는 출력 버퍼.

## 청구항 10.

제8항에 있어서, 상기 슬루 레이트 제어부는

상기 제1 및 제2 슬루 레이트 제어 신호들에 각각 응답하여, 상기 커패시터부의 커패시턴스가 상기 제1 커패시턴스로부터 상기 제2 커패시턴스로 또는 상기 제2 커패시턴스로부터 상기 제1 커패시턴스로 변환되도록 제어하는 제1 및 제2 스위치들을 더 구비하는 것을 특징으로 하는 출력 버퍼.

## 청구항 11.

제10항에 있어서,

상기 제1 스위치는 피모스 트랜지스터인 것을 특징으로 하는 출력 버퍼.

## 청구항 12.

제10항에 있어서,

상기 제2 스위치는 엔모스 트랜지스터인 것을 특징으로 하는 출력 버퍼.

## 청구항 13.

액정 표시 장치의 소스 드라이버에 포함되고, 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 출력 버퍼에 있어서,

아날로그 영상 신호를 증폭하는 증폭부;

상기 증폭부에 의해 증폭된 신호들에 응답하여 상기 소스 라인 구동 신호를 출력 노드를 통해 출력하는 출력부; 및

상기 소스 라인 구동 신호의 주파수 특성을 안정화시키고 상기 소스 라인 구동 신호의 전압에 대한 슬루 레이트를 개선하는 슬루 레이트 제어부를 구비하며,

상기 슬루 레이트 제어부는

상기 증폭부에 포함된 제1 전류 미러 회로의 출력 노드와 상기 출력 노드 사이에 연결되는 제1 커패시터;

상기 소스 라인에 대한 소스 라인 구동 신호의 공급이 시작될 때 상기 제1 커패시터와의 병렬 연결이 분리되는 제2 커패시터;

상기 증폭부에 포함된 제2 전류 미러 회로의 출력 노드와 상기 출력 노드 사이에 연결되는 제3 커패시터; 및

상기 소스 라인 구동 신호의 공급이 시작될 때 상기 제3 커패시터와의 병렬 연결이 분리되는 제4 커패시터를 구비하는 것을 특징으로 하는 출력 버퍼.

#### 청구항 14.

제13항에 있어서, 상기 슬루 레이트 제어부는

제1 슬루 레이트 제어 신호에 응답하여 상기 제1 커패시터와 상기 제2 커패시터를 연결 또는 분리하는 제1 스위치; 및

제2 슬루 레이트 제어 신호에 응답하여 상기 제3 커패시터와 상기 제4 커패시터를 연결 또는 분리하는 제2 스위치를 더 구비하는 것을 특징으로 하는 출력 버퍼.

#### 청구항 15.

제14항에 있어서,

상기 제1 스위치는 피모스 트랜지스터인 것을 특징으로 하는 출력 버퍼.

#### 청구항 16.

제14항에 있어서,

상기 제2 스위치는 엔모스 트랜지스터인 것을 특징으로 하는 출력 버퍼.

#### 청구항 17.

제13항에 있어서,

상기 제1 및 제3 커패시터들의 커패시턴스들은 서로 동일하고, 상기 제2 및 제4 커패시터들의 커패시턴스들은 서로 동일한 것을 특징으로 하는 출력 버퍼.

#### 청구항 18.

제17항에 있어서,

상기 제1 및 제3 커패시터들의 커패시턴스들은 각각 0 인 것을 특징으로 하는 출력 버퍼.

### 청구항 19.

제14항에 있어서, 상기 출력 버퍼는

상기 아날로그 영상 신호 및 상기 소스 라인 구동 신호가 입력되는 입력부를 더 구비하는 것을 특징으로 하는 출력 버퍼.

### 청구항 20.

제19항에 있어서,

상기 출력 버퍼는 레일-투-레일 연산 증폭기로 구현되는 것을 특징으로 하는 출력 버퍼.

### 청구항 21.

제19항에 있어서,

상기 출력 버퍼는 두 개의 단방향 연산 증폭기들로 구현되는 것을 특징으로 하는 출력 버퍼.

### 청구항 22.

제14항에 있어서,

상기 제1 슬루 레이트 제어 신호는 상기 소스 라인이 소정의 프리차지 전압으로 프리차지되도록 제어하는 공유 스위치 제어 신호를 지연한 신호이고, 상기 제2 슬루 레이트 제어 신호는 상기 제1 슬루 레이트 제어 신호의 반전 신호인 것을 특징으로 하는 출력 버퍼.

### 청구항 23.

제22항에 있어서,

상기 프리차지 전압은 전원 전압의 1/2인 것을 특징으로 하는 출력 버퍼.

### 청구항 24.

제22항에 있어서,

상기 제1 슬루 레이트 제어 신호는 상기 공유 스위치 제어 신호를 D 플립-플롭을 통해 상기 소스 라인이 상기 프리차지 전압으로 프리차지되는 시간인 전하 공유 시간만큼 지연한 신호인 것을 특징으로 하는 출력 버퍼.

### 청구항 25.

액정 표시 장치의 소스 드라이버에 포함되고 소스 라인을 구동하는 소스 라인 구동 신호를 출력하는 출력 버퍼를 제어하는 방법에 있어서,

- (a) 상기 소스 라인이 소정의 프리차지 전압으로 프리차지되는 시간인 제1 전하 공유 시간 동안 상기 출력 버퍼에 포함된 커패시터부의 커패시턴스를 상기 소스 라인 구동 신호의 주파수 특성이 안정되도록 하는 제1 커패시턴스로 설정하는 단계;

- (b) 상기 제1 전하 공유 시간 직후의 시간으로서 상기 소스 라인에 대한 상기 소스 라인 구동 신호의 공급이 시작되는 시간인 제2 전하 공유 시간 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스 보다 작은 제2 커패시턴스로 설정하는 단계; 및

- (c) 상기 제2 전하 공유 시간 직후에 상기 소스 라인 구동 신호의 공급이 유지되는 동안 상기 커패시터부의 커패시턴스를 상기 제1 커패시턴스로 설정하는 단계를 구비하는 것을 특징으로 하는 출력 버퍼의 제어 방법.

### 청구항 26.

제25항에 있어서,

상기 제1 전하 공유 시간과 상기 제2 전하 공유 시간은 동일한 것을 특징으로 하는 출력 버퍼의 제어 방법.

### 청구항 27.

제25항에 있어서,

상기 프리차지 전압은 전원 전압의 1/2인 것을 특징으로 하는 출력 버퍼의 제어 방법.

### 청구항 28.

제25항에 있어서, 상기 제2 커패시턴스는 0인 것을 특징으로 하는 출력 버퍼의 제어 방법.

### 청구항 29.

제25항에 있어서,

상기 제1 커패시턴스는 제1 및 제2 슬루 레이트 제어 신호들의 활성화에 의해 설정되고 상기 제2 커패시턴스는 상기 제1 및 제2 슬루 레이트 제어 신호들의 비활성화에 의해 설정되며,

상기 제1 슬루 레이트 제어 신호는 상기 소스 라인이 상기 프리차지 전압으로 프리차지되도록 제어하는 공유 스위치 제어 신호를 지연한 신호이고, 상기 제2 슬루 레이트 제어 신호는 상기 제1 슬루 레이트 제어 신호의 반전 신호인 것을 특징으로 하는 출력 버퍼의 제어 방법.

### 청구항 30.

제29항에 있어서,

상기 제1 슬루 레이트 제어 신호는 상기 공유 스위치 제어 신호를 D 플립-플롭을 통해 상기 제1 전하 공유 시간만큼 지연한 신호인 것을 특징으로 하는 출력 버퍼의 제어 방법.

도면

도면1

## 도면2

도면3

도면4

## 도면5

## 도면6

| 인장회 시간          |                 |                 |                 |                 |                 |                 |                 |                 |                 | IDD   |       |       |    |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------|-------|-------|----|

| VDD<br>[V]      | 종래 기술           |                 |                 |                 | 본 발명            |                 |                 |                 | 종래 기술           | 본 발명  |       |       |    |

|                 | Tr              | Tf              | Tr              | Tf              | Tr              | Tf              | Tr              | Tf              |                 | mA    | mA    | mA    | mA |

| 상승 시간[ $\mu$ s] | 하강 시간[ $\mu$ s] | 상승 시간[ $\mu$ s] | 하강 시간[ $\mu$ s] | 상승 시간[ $\mu$ s] | 하강 시간[ $\mu$ s] | 상승 시간[ $\mu$ s] | 하강 시간[ $\mu$ s] | 상승 시간[ $\mu$ s] | 하강 시간[ $\mu$ s] | mA    | mA    | mA    | mA |

| 13.5            | 1.486           | 8.385           | 1.305           | 9.130           | 0.899           | 8.059           | 0.813           | 8.021           | 61.64           | 23.67 | 61.19 | 23.49 |    |

|                |                                           |         |            |

|----------------|-------------------------------------------|---------|------------|

| 专利名称(译)        | 包括在具有高压摆率的液晶显示装置中的源极驱动器的输出缓冲器和输出缓冲器的输出缓冲器 |         |            |

| 公开(公告)号        | <a href="#">KR1020060064941A</a>          | 公开(公告)日 | 2006-06-14 |

| 申请号            | KR1020040103629                           | 申请日     | 2004-12-09 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                  |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                  |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                  |         |            |

| [标]发明人         | AN CHANGHO                                |         |            |

| 发明人            | AN,CHANGHO                                |         |            |

| IPC分类号         | G09G3/36                                  |         |            |

| CPC分类号         | G09G2310/027 G09G2320/0252 G09G3/3688     |         |            |

| 代理人(译)         | 李, 杨HAE                                   |         |            |

| 其他公开文献         | <a href="#">KR100699829B1</a>             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                 |         |            |

### 摘要(译)

(320) 从第一电容转换为第二电容或从第二电容转换为第一电容。因此，转换速率控制单元315稳定源极线驱动信号OUT的频率特性，并改善相对于源极线驱动信号OUT的电压的转换速率。因此，根据本发明实施例的输出缓冲器300可以通过调整等式(1)中描述的电容器单元320的电容来输出具有高压摆率的源极线驱动信号OUT。那里。在另一方面，根据本发明的实施例的输出缓冲器300包括轨-已经在轨运算放大器实现，压摆率控制单元315是根据本发明的导轨-轨道运算放大器到的到输入单元和其他结构它还可以应用于两个单独的运算放大器，每个都包括一个输入。图5是说明当图4的输出缓冲器用作图4的源极驱动器的输出缓冲器时源极驱动器的操作的示例性时序图。参考图5，从输出使能信号OE生成共享开关控制信号CSW和输出开关控制信号OSW。输出使能信号(OE)从控制源驱动器(200)的定时控制器生成。当共享开关控制信号CSW保持高电平(激活状态)时(即，在第一电荷共享时间CST1期间)，源极线驱动信号Yn，n为其中一个自然数)从地电压VSS

上升到预充电电压VDD/2。第一电荷共享时间CST1可以是例如0.5(μs)至1.0(μs)。在第一电荷共享时间CST1期间，第一转换速率控制信号SR1被激活为低电平，第二转换速率控制信号SR2被激活为高电平，设置为第一电容(即，通过与CC1和CC2并联连接形成的电容以及与CC3和CC4的并联连接)。一时间作为第一同时所述第二电荷共享期间(CST2)和电荷共享时间之后立即输出开关控制信号(OSW)是不重叠的时间(不重叠的时间)的第一电荷共享期间(CST1)(源极线驱动信号的(例如，电源电压VDD)开始被提供给源极线。非重叠时间(NOT)是防止过量电流流到源极线所需的时间，例如5(ns)。在第二电荷共享时间CST2期间，第一转换速率控制信号SR1被去激活到高电平，第二转换速率控制信号SR2被去激活到低电平，电容设定为第二电容(即，由CC1和CC3组成的电容)。结果，源极线驱动信号Yn急剧上升到VDD。也就是说，第二电荷共享时间CST2表示高转换速率时间间隔。由于电荷共享期间(CST2)后，立即在第一斜率控制信号(SR1)的第二被再次激活到低电平，并且该第二斜率控制信号(SR2)再次被激活到高电平，电容器单元(图1的320.4)回到第一个电容。结果，源极线驱动信号Yn的频率特性稳定。此时，由于输出开关控制信号OSW保持高电平，所以源极线驱动信号Yn保持VDD电平。在另一方面，源极线驱动信号(YN)的负电压的电压时，(例如，VSS)也是如此类似于源极线驱动信号(YN)城堡上述正电压的描述，它的描述是省略。图6是用于将本发明的模拟结果与现有技术的模拟结果进行比较的表。图6中的表描述了当VDD为13.5(伏特)时的建立时间和流过源极线的工作电流(IDD)。稳定时间分为上升时间和下降时间。上升时间为第一上升时间Tr1和第二上升时间Tr2，下降时间为第一下降时间Tf1和第二下降时间Tf2。第一上升时间(TR1)是时间，和第二上升时间(TR2)，它需要将源极线驱动信号到目标电压的

90%达到目标电压（目标电压）的10%是一个源极线第一下降时间Tf1是源极线驱动信号从目标电压的90%达到目标电压Vdd所需的时间，并且第二下降时间Tf2是从目标电压的99.5%到目标电压的10%到达源极线驱动信号所消耗的时间。参照图6的图表中描述的数时，输出缓冲器的转换速率是上升时间和（即，源极线驱动源极线驱动信号的信号相比于输出缓冲器根据在根据本发明与现有技术并减少在一个通道（或源线）中流动的电流。