**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) 。 Int. Cl.<sup>7</sup>

G02F 1/1339

(45) 공고일자 2005년07월01일

(11) 등록번호 10-0498625

(24) 등록일자 2005년06월22일

(21) 출원번호 10-2001-0040337

(22) 출원일자 2001년07월06일

(65) 공개번호 10-2002-0007164

(43) 공개일자 2002년01월26일

(30) 우선권주장 JP-P-2000-00213753 2000년07월14일 일본(JP)

(73) 특허권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

(72) 발명자 이마바야시마키코

일본국치바켄모바라시하야노3550

하세가와신지

일본국치바켄모바라시사루부쿠로아자하라704-11

이와카베야스시

일본국치바켄산부군오오아미시라사토마치미즈호다이1-36-20

(74) 대리인 특허법인 원전

**심사관 : 장경태**

**(54) 액정표시장치**

**요약**

상온, 고온에 한정하지 않고, 각 투명기판의 갭을 균일하게 유지한다.

액정을 통하여 대향배치된 각 투명기판과, 한쪽의 투명기판측에 고정되어 형성되며 다른 쪽의 투명기판을 지지하는 복수의 스페이서를 구비하고,

상기 각 스페이서는 제1의 스페이서와 제2의 스페이서로 이루어지며, 제1의 스페이서는 제2의 스페이서에 대하여 탄성이 높은 재료로 형성되어 있음과 동시에, 또, 높이가 높게 형성되어 있다.

**대표도**

도 1

**색인어**

투명기판, 스페이서, 탄성, 단자 높이

**명세서**

**도면의 간단한 설명**

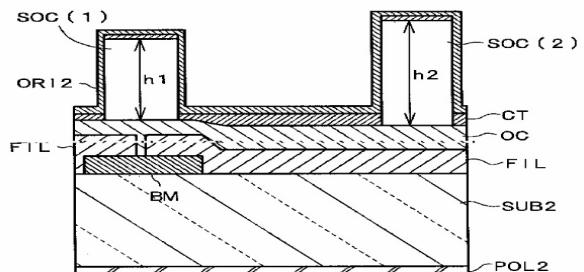

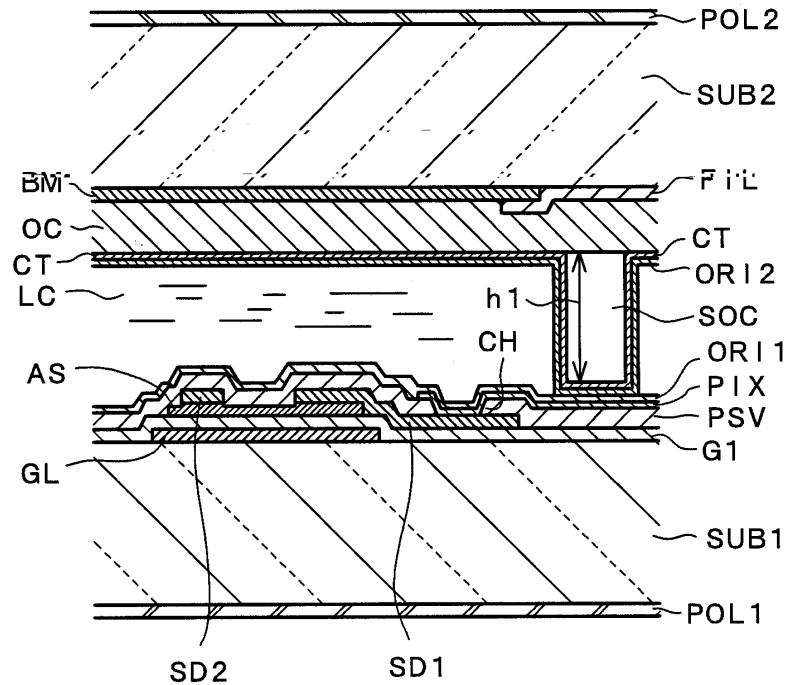

도 1은 본 발명에 의한 액정표시장치의 일실시예를 나타내는 요부단면도,

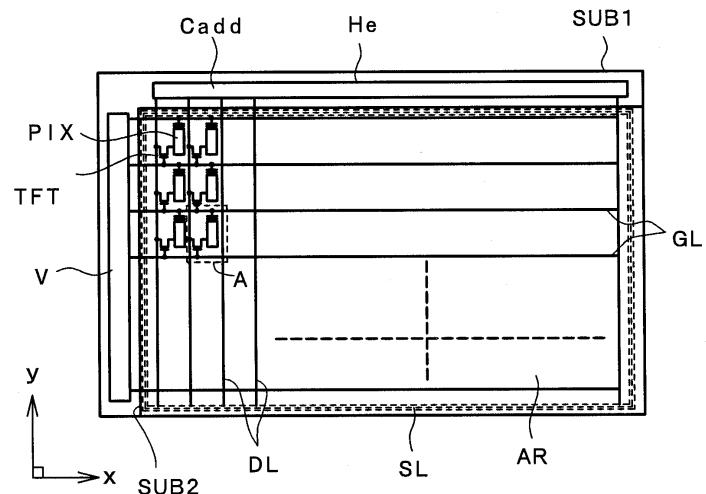

도 2는 본 발명에 의한 액정표시장치의 일실시예를 나타내는 등가회로도,

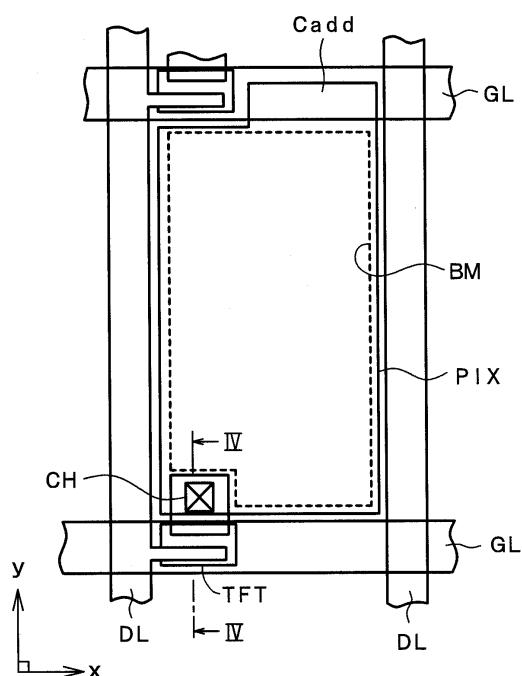

도 3은 본 발명에 의한 액정표시장치 화소의 일실시예를 나타내는 평면도,

도 4는 도 3의 IV-IV선에서의 단면도,

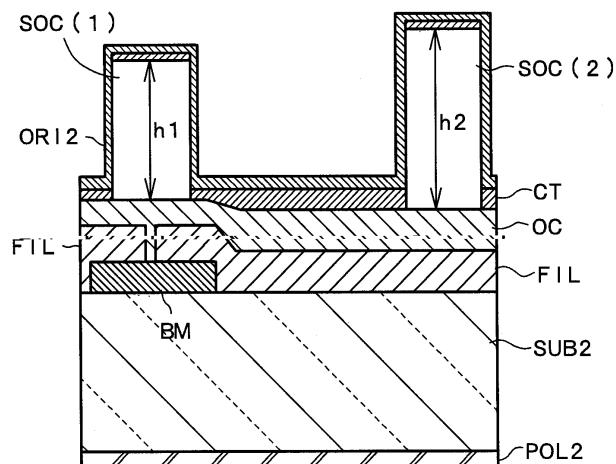

도 5는 본 발명에 의한 액정표시장치의 다른 일실시예를 나타내는 요부단면도,

도 6은 본 발명에 의한 액정표시장치의 다른 실시예를 나타내는 요부단면도,

도 7은 본 발명에 의한 액정표시장치의 다른 실시예를 나타내는 요부단면도이다.

(부호의 설명)

SUB 투명기판

LC 액정

SOC 스페이서

BM 블랙 매트릭스

FIL 컬러필터

ORI 배향막

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정표시장치에 관한 것이다.

액정표시장치는, 액정을 통하여 대향배치되는 각 투명기판을 외위기(外圍器)(vessel)로 하고, 상기 액정의 확장 방향(펴지는 방향)에 다수의 화소로 이루어지는 표시부를 갖추어 구성되어 있다.

한쪽의 투명기판에 대한 다른 쪽 투명기판의 고정은, 상기 액정을 밀봉하는 기능을 겸하는 실(seal)재에 의해 행해지고, 또, 각 투명기판의 표시부에서의 갭(gap)의 유지는 상기 액정 중에 산재되는 스페이서에 의해 행해져 있다.

그리고, 이 스페이서로서는, 근래, 한쪽의 투명기판측에 형성된 수지층을 포토리소그라피(photolithography) 기술에 의한 선택에칭에 의해 기동 모양으로 형성한 것이 알려져 왔다.

이와 같이 형성되는 각 스페이서는, 표시부 내 소정의 위치에 정밀도 좋게 형성할 수 있음과 동시에, 각각의 높이를 균일하게 할 수 있는 효과가 있다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 이러한 액정표시장치는, 예를 들면 백라이트(back light) 등에서의 열에 의해 고온이 되면, 액정이 열팽창하고, 한쪽의 투명기판에 형성되어 있는 스페이서에 대하여 다른 쪽 투명기판의 간격이 벌어져버리는 것이 확인되었다. 액정의 열팽창에 대하여 스페이서의 열팽창을 추종할 수 없기 때문이다.

이 때문에, 각 투명기판의 갭, 즉, 액정의 충두께를 균일하게 유지할 수 없게 되어, 적어도 한쪽의 투명기판에 휘어짐이 발생해 버린다.

이 투명기판의 휘어짐은, 상온이 되어도 용이하게 원래대로 되돌아가지 않고, 표시얼룩을 발생시키는 문제를 초래한다.

본 발명은, 이러한 사정에 의거하여 이루어진 것으로, 그 목적은, 상온, 고온에 한정하지 않고, 각 투명기판의 갭을 균일하게 유지할 수 있는 액정표시장치를 제공하는데 있다.

#### 발명의 구성 및 작용

본원에서 개시되는 발명 중, 대표적인 것의 개요를 간단하게 설명하면 이하와 같다.

즉, 본 발명에 의한 액정표시장치는, 예를 들면, 액정을 통하여 대향배치된 각 투명기판과, 한쪽의 투명기판측에 고정되어 형성되며, 다른 쪽의 투명기판을 지지하는 복수의 스페이서를 구비하고, 상기 각 스페이서는 제1의 스페이서와 제2의 스페이서로 이루어지며, 제1의 스페이서는 제2의 스페이서에 대하여 탄성이 높은 재료로 형성되어 있음과 동시에, 또, 높이가 높게 형성되어 있는 것을 특징으로 하는 것이다.

이와 같이 구성된 액정표시장치는, 각 투명기판은, 온도가 높아지기 전에 제2의 스페이서 높이에 따라 캡이 유지되게 되어 있다. 이 경우, 제1의 스페이서는 그 탄성에 의해 축소된 상태로 되어 있다.

온도가 높아지고, 액정이 열팽창한 경우, 각 투명기판은 그 한 쪽에서 제2의 스페이서에서 멀어지지만, 제1의 스페이서에서는 멀어지지 않게 된다. 제1의 스페이서는 그 탄성에 의해 팽창된 상태가 되기 때문이다.

그리고, 상온으로 되돌아간 경우에는, 제1의 스페이서는 그 탄성에 의해 축소된 상태가 되고, 제2의 스페이서의 높이에 따라 캡이 유지되게 된다.

이것으로부터, 각 투명기판에는 휘어짐이 발생하는 일은 없어지고, 고온, 상온에 한정하지 않고, 각 투명기판의 캡을 균일하게 유지할 수 있게 된다.

#### (발명의 실시형태)

이하, 본 발명에 의한 액정표시장치의 실시예를 도면을 이용하여 설명한다.

#### <실시예 1>

##### 《등가회로》

도 2는 본 발명에 의한 액정표시장치의 일실시예를 나타내는 등가회로도이다. 동도는 회로도이지만, 실제의 기하학적 배치에 대응하여 그려져 있다.

동도에서, 투명기판(SUB1)이 있고, 이 투명기판(SUB1)은 액정을 통하여 다른 투명기판(SUB2)과 대향하여 배치되어 있다.

상기 투명기판(SUB1)의 액정측의 면에는, 도면 중 x방향으로 연장하여 y방향으로 병설되는 게이트 신호선(GL)과, 이 게이트 신호선(GL)과 절연되어 y방향으로 연장하여 x방향으로 병설되는 드레인 신호선(DL)이 형성되며, 이를 각 신호선으로 둘러쌓인 구(矩)형상의 영역이 화소영역이 되고, 이를 각 화소영역의 집합에 의해 표시부(AR)를 구성하도록 되어 있다.

각 화소영역에는, 한 쪽의 게이트 신호선(GL)에서의 주사신호(전압)의 공급에 의해 구동되는 박막 트랜지스터 TFT와, 이 박막 트랜지스터 TFT를 통하여 한 쪽의 드레인 신호선(DL)에서의 영상신호(전압)가 공급되는 화소전극(PIX)이 형성되어 있다.

또한, 화소전극(PIX)과 상기 한 쪽의 게이트 신호선(GL)과 인접하는 다른 쪽의 게이트 신호선(GL)과의 사이에는 용량소자(Cadd)가 형성되고, 이 용량소자(Cadd)에 의해, 상기 박막 트랜지스터 TFT가 OFF했을 때에, 화소전극(PIX)에 공급된 영상신호를 길게 축적시키도록 되어 있다.

각 화소영역에서의 화소전극(PIX)은, 액정을 통하여 대향배치되는 다른 쪽 투명기판(SUB2)의 액정측의 면에서 각 화소영역에 공통으로 형성된 대향전극(CT)(도시하지 않음)과의 사이에 전계를 발생시키도록 되어 있고, 이것에 의해 각 전극 사이의 액정의 광투과율을 제어하게 되어 있다.

각 게이트 신호선(GL)의 일단(一端)은 투명기판의 한 변측(도면 중 좌측)으로 연장되고, 그 연장부는 상기 투명기판(SUB1)에 탑재되는 반도체 집적회로로 이루어지는 수직주사회로(V)와 접속되게 되어 있으며, 또, 각 드레인 신호선(DL)의 일단(一端)도 투명기판(SUB1)의 한 변측(도면 중 상측)으로 연장되고, 그 연장부는 상기 투명기판(SUB1)에 탑재되는 반도체 집적회로로 이루어지는 영상신호 구동회로(He)와 접속되게 되어 있다.

상기 투명기판(SUB2)은, 수직주사회로(V) 및 영상신호 구동회로(He)를 구성하는 반도체 회로가 탑재되는 영역을 회피하도록 하여 투명기판(SUB1)과 대향배치되며, 상기 투명기판(SUB1) 보다도 작은 면적으로 되어 있다.

그리고, 투명기판(SUB1)에 대한 투명기판(SUB2)의 고정은, 상기 투명기판(SUB2)의 주변에 형성된 실(seal)재(SL)에 의해 행해지고, 이 실재(SL)는 투명기판(SUB1, SUB2) 사이의 액정을 밀봉하는 기능도 겸하고 있다.

##### 《화소의 구성》

도 3은 투명기판(SUB1)의 한 화소영역의 구성을 나타내는 평면도이며, 도 2의 점선 프레임(A)으로 나타내는 부분에 상당하는 도면이다.

또한, 도 4는 도 3의 IV-IV선에서의 단면도를 나타내고, 투명기판(SUB2)의 단면도도 나타내고 있다.

각 도면에서, 우선, 투명기판(SUB1) 액정측의 면에 도면 중 x방향으로 연장하여 y방향으로 병설되는 게이트 신호선(GL)이 형성되어 있다.

그리고, 이 게이트 신호선(GL)도 덮어 투명기판(SUB1)의 면에 예를 들면 SiN으로 이루어지는 절연막(GI)이 형성되어 있다.

이 절연막(GI)은, 후술의 드레인 신호선(DL)에 대해서는 게이트 신호선(GL)과의 충간 절연막으로서의 기능, 후술의 박막 트랜지스터 TFT에 대해서는 그 게이트 절연막으로서의 기능, 후술의 용량소자(Cadd)에 대해서는 그 유전체막으로서의 기능을 갖게 되어 있다.

화소영역의 좌측 하부에서 게이트 신호선(GL)과 중첩하는 부분에서, 예를 들면 a-Si로 이루어지는 i형(신세이(眞性) : 도전형 결정 분순물이 도프되어 있지 않음)의 반도체층(AS)이 형성되어 있다.

이 반도체층(AS)은, 그 상면에 소스전극 및 드레인 전극을 형성함으로써, 상기 게이트 신호선의 일부를 게이트 전극으로 하는 MIS형의 박막 트랜지스터 TFT의 반도체층으로 이루어지는 것이다.

이 박막 트랜지스터 TFT의 소스전극(SD1) 및 드레인 전극(SD2)은, 상기 절연막(GI)상에 형성되는 드레인 신호선(DL)과 동시에 형성되게 되어 있다.

즉, 도면 중 y방향으로 연장되어 x방향으로 병설되는 드레인 신호선(DL)이 형성되고, 이 드레인 신호선(DL)의 일부를 상기 반도체층(AS)의 상면에까지 연장시켜 형성함으로써, 그 연장부는 박막 트랜지스터 TFT의 드레인 전극(SD2)으로 형성된다.

또한, 이 때, 상기 드레인 전극(SD2)과 이간시켜 형성된 전극이 소스전극(SD1)이 된다. 이 소스전극(SD1)은 후술의 화소전극(PIX)과 접속되는 것으로, 그 접속부를 확보하기 위해, 화소영역의 중앙측으로 약간 연장시킨 연장부를 갖는 패턴으로 되어 있다.

또한, 드레인 전극(SD2), 소스전극(SD1)의 반도체층(AS)과의 계면에는 불순물이 도프된 반도체층이 형성되고, 이 반도체층은 콘택트층으로서 기능하도록 되어 있다.

상기 반도체층(AS)을 형성한 후, 그 표면에 불순물이 도프된 막두께가 얇은 반도체층을 형성하고, 드레인 전극(SD2) 및 소스전극(SD1)을 형성한 후에, 상기 각 전극을 마스크로 하여, 그것에서 노출된 불순물이 도프된 반도체층을 에칭함으로써, 상술한 구성으로 할 수 있다.

그리고, 이와 같이 드레인 신호선(DL)(드레인 전극(SD2), 소스전극(SD1))이 형성된 투명기판(SUB1)의 표면에는, 상기 드레인 신호선(DL) 등도 덮어, 예를 들면 SiN으로 이루어지는 보호막(PSV)이 형성되어 있다.

이 보호막(PSV)은 박막 트랜지스터 TFT의 액정파의 직접 접촉을 회피하기 위해 설치되는 것이며, 상기 박막 트랜지스터 TFT의 소스전극(SD1) 연장부의 일부를 노출시키기 위한 콘택트홀(CH)이 형성되어 있다.

또한, 이 보호막(PSV)의 상면에는 화소영역의 대부분을 덮어 예를 들면, ITO(Indium-Tin-Oxide)막으로 이루어지는 투명의 화소전극(PIX)이 형성되어 있다.

이 화소전극(PIX)은, 보호막(PSV)의 상기 콘택트홀(CH)도 덮도록 하여 형성되며, 이것에 의해 박막 트랜지스터 TFT의 소스전극(SD1)과 접속되게 되어 있다.

또한, 이와 같이 화소전극(PIX)이 형성된 투명기판(SUB1)의 표면에는, 상기 화소전극(PIX)도 덮어 배향막(ORI1)이 형성되어 있다. 이 배향막(ORI1)은 예를 들면 수지로 이루어지고, 그 표면에는 일정 방향으로 러빙처리가 행해져 있다. 이 배향막(ORI1)은 액정(LC)과 접촉하게 되어 있고, 이 배향막(ORI1)에 의해 상기 액정(LC)의 초기 배향방향을 결정하도록 되어 있다.

그리고, 투명기판(SUB1)의 액정(LC)과 반대측의 면에는, 편광판(POL1)이 피착되어 있다.

한편, 투명기판(SUB2) 액정측의 면에는, 각 화소영역을 구획하도록 하여 블랙 매트릭스(BM)가 형성되어 있다.

이 블랙매트릭스(BM)는 외래(外來)의 광이 박막 트랜지스터 TFT에 조사하는 것을 회피시키기 위해, 표시의 콘트리스트를 양호하게 하기 위해 설치되어 있다.

또한, 블랙 매트릭스(BM)의 개구부(광이 투과하는 영역이 되고, 실질적인 화소영역이 된다)에는 각 화소영역에 대응한 색을 갖는 컬러필터(FIL)가 형성되어 있다.

이 컬러필터(FIL)는, 예를 들면 y방향에 병설되는 각 화소영역에서 동색(同色)의 필터가 이용되고, x방향의 각 화소영역마다 예를 들면 적(R), 녹(G), 청(B)의 필터가 순서대로 반복되어 배열되어 있다.

이와 같이 블랙 매트릭스(BM) 및 컬러필터(FIL)가 형성된 투명기판(SUB2)의 표면에는 상기 블랙 매트릭스(BM) 등을 덮어 예를 들면 도포 등에 의해 형성된 수지로 이루어지는 평탄화막(OC)이 형성되고, 그 표면에 상기 블랙 매트릭스(BM) 및 컬러필터(FIL)에 의한 단차가 현재(顯在)되지 않게 되도록 되어 있다.

평탄화막(OC)의 표면에는, 스페이서(SOC)가 형성되어 있다. 이 스페이서(SOC)는 표시부(AR)에 산재하게 하여 형성되며(도 4에서는, 1개의 스페이서를 나타내고 있다), 투명기판(SUB2)에 대한 투명기판(SUB1)의 캡을 균일하게 유지시키는 것이다.

이 스페이서(SOC)는, 투명기판(SUB2)에 고정된 기둥 모양의 예를 들면 수지체로 이루어지고, 상기 투명기판(SUB2)측의 면에 수지를 도포에 의해 형성하여 수지막을 형성하고, 포토리소그라피 기술에 의한 선택에칭에 의해 형성하도록 되어 있다.

이것으로부터, 이 스페이서(SOC)는 화소영역 중 광이 투과하는 영역 혹은 투과하지 않는 영역에 임의로 형성할 수 있도록 되어 있다.

이 스페이서(SOC)에 대해서는 후에 더 상세하게 기술하겠지만, 도 4에 나타낸 액정표시장치는 상온상태로 되어 있고, 스페이서(SOC)(도면에 나타나 있지 않은 다른 스페이서(SOC)도 포함한다)의 높이는  $h_1$ 으로 되어 있다.

그리고, 상기 평탄화막(OC)의 표면은 스페이서(SOC)의 표면도 덮어 각 화소영역에 공통으로 예를 들면 ITO로 이루어지는 대향전극(CT)이 형성되어 있다.

이 대향전극(CT)은 각 화소영역에서의 화소전극(PIX)과의 사이에 영상신호(전압)에 대응한 전계를 발생시키고, 이들 각 전극과의 사이의 액정(LC)의 광투과율을 제어하게 되어 있다.

또한, 이와 같이 대향전극(CT)이 형성된 투명기판(SUB2)의 표면에는, 상기 대향전극(CT)도 덮어 배향막(ORI2)이 형성되어 있다. 이 배향막(ORI2)은 예를 들면 수지로 이루어지고, 그 표면에는 일정 방향으로 러빙처리가 행해져 있다. 이 배향막(ORI2)은 액정과 접촉하도록 되어 있고, 이 배향막(ORI2)에 의해 상기 액정(LC)의 초기 배향방향을 결정하도록 되어 있다.

그리고, 투명기판(SUB1)의 액정(LC)과 반대측의 면에는, 편광판(POL2)이 피착되어 있다.

### 《스페이서》

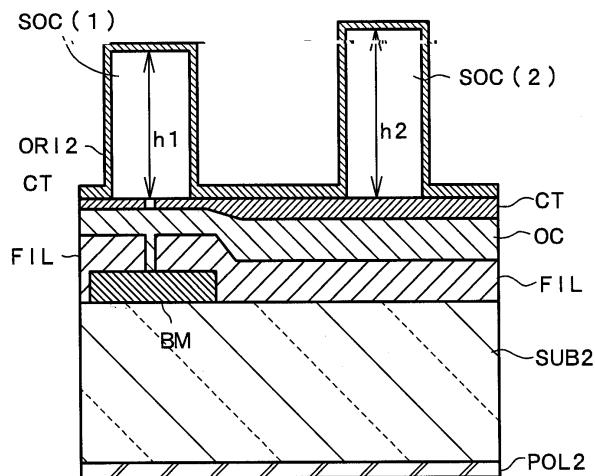

도 1은, 상기 스페이서(SOC)가 형성되어 있는 투명기판(SUB2)만을 나타낸 도면으로, 다시 말하면, 투명기판(SUB1)이 아직 대향하여 배치되어 있지 않은 상태를 나타낸 도면이다.

또한, 도 4의 경우 투명기판(2)과는 상하가 역으로 나타나 있다.

투명기판(SUB2)측에 형성되는 각 스페이서(SOC)는, 2종류의 다른 스페이서로 구성되고, 그 중 한 쪽의 스페이서(SOC(1))는 그 높이가  $h_1$ 으로, 비교적 탄성이 적은 재료로 형성되며, 다른 쪽의 스페이서(SOC(2))는 그 높이가  $h_2$ ( $>h_1$ )로 비교적 탄성이 큰 재료로 형성되어 있다.

각종 스페이서(SOC(1), SOC(2))는 각각 다른 공정으로 형성되게 되어 있다. 즉, 평탄화막(OC)의 상면에 수지(탄성율을  $E_1$ 로 함)를 도포하여 막두께가  $h_1$ 의 수지막을 형성하고, 그것을 포토리소그라피 기술에 의한 선택에칭에 의해 패턴화 함으로써, 한쪽의 스페이서(SOC(1))를 형성한다. 그리고, 평탄화막(OC)의 상면에 다른 수지(탄성율을  $E_2$ ( $>E_1$ )로 함)를 도포하여 막두께가  $h_2$ 의 수지막을 형성하고, 그것을 포토리소그라피 기술에 의한 선택에칭에 의해 패턴화함으로써, 다른 쪽의 스페이서(SOC(2))를 형성한다.

이러한 스페이서를 갖는 투명기판(SUB2)에 대하여 투명기판(SUB1)을 대향배치(액정셀의 형성)시킨 경우, 각 투명기판(SUB1, SUB2)의 캡은, 도 4에 나타낸 바와 같이, 한쪽의 스페이서(SOC(1)) 높이  $h_1$ 에 의해 결정되게 된다.

이 경우, 각 투명기판(SUB1, SUB2)측에서의 압력에 의해, 다른 쪽의 스페이서(SOC(2))는 그 탄성이 크므로 축소되고, 그 높이가  $h_1$  상태로 각 투명기판의 사이에 개재되며, 각 투명기판은 그 표시부(AR)의 전역에 걸쳐 거의  $h_1$ 의 캡이 유지되게 된다.

그리고, 상온에서 고온이 되어 액정이 열팽창함으로써, 각 투명기판의 캡은  $h_1$  이상이 되고, 한쪽의 스페이서(SOC(1))의 두부(頭部)가 투명기판(SUB1)에서 벌어져 버리지만, 다른 쪽의 스페이서(SOC(2))가 그 탄성에 의해 팽창 투명기판(SUB1)에 밀착된 상태가 된다.

이 경우, 각 투명기판의 캡은 변화하게 되지만, 표시부의 각 위치에 걸쳐 캡이 변동될 리가 없으므로(즉, 투명기판에 휘어짐이 발생하지 않으므로), 표시의 얼룩은 발생하지 않게 된다.

이것은, 고온에서 상온으로 되돌아갈 때에도 동일하며, 여전히 표시의 얼룩은 발생하지 않게 된다.

이 때문에, 상온, 고온에 한정하지 않고, 각 투명기판의 캡을 균일하게 유지할 수 있게 된다.

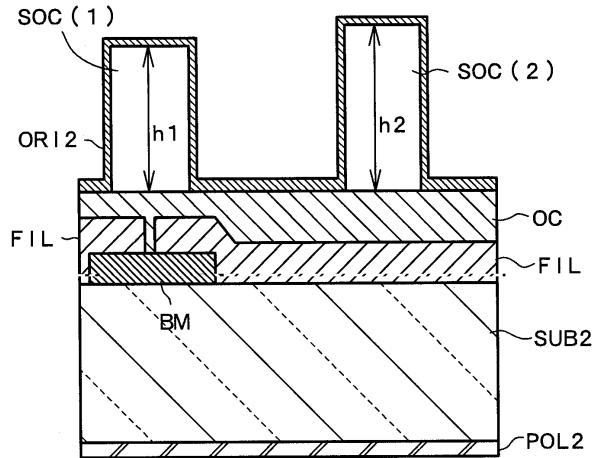

도 5는 다른 실시예를 나타낸 구성도이며 도 1과 대응한 도면으로 되어 있다. 도 5에서, 평탄화막(OC)의 상면에 대향전극(CT)이 형성되고, 이 대향전극(CT)의 면에 스페이서(SOC)가 형성된 부분이 도 1과 다르다.

상술한 실시예는, 그 화소구성으로서, 한쪽의 투명기판(SUB1)측에 화소전극이, 다른 쪽의 투명기판(SUB2)측에 대향전극이 형성되고, 그들 사이의 액정에 전계를 인가하는(이것에 의해 전계의 방향은 기판에 대하여 수직이 된다) 구성에 대하여 나타낸 것이다.

그러나, 한쪽의 투명기판측에 화소전극 및 대향전극이 형성되고, 그들 사이의 액정에 전계를 인가하는(이것에 의해 기판과 거의 평행한 전계성분에 의해 액정을 구동한다) 구성에 있어서도 적용할 수 있는 것이다.

화소의 구성이 어떤 것이라도, 표시영역의 각 개소에서의 각 투명기판의 캡 즉 액정의 층두께의 변동을 없애는 요청은 모두 동일하기 때문이다.

도 6은, 후자의 화소구성에서의 도 1과 대응하는 도면이다. 투명기판(SUB2)측에는 대향전극(CT)이 형성되어 있지 않다는 점을 제외하면, 도 1과 동일한 구성으로 되어 있다.

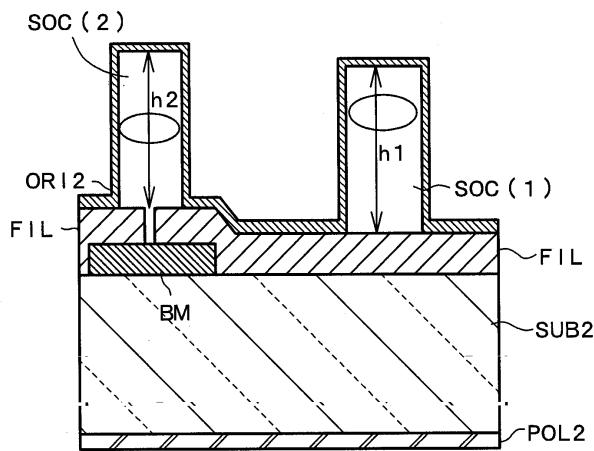

#### <실시예 2>

상술한 실시예의 경우, 각종 스페이서에서 재료가 다른 것을 이용하고 있으므로, 그 제조에서 포토리소그라파 기술에 의한 선택에칭을 2회 행하지 않으면 안된다.

그러나, 스페이서를 형성하는 베이스가 되는 층에 단차가 형성되어 있고, 또한, 스페이서의 평면형상(중심축을 획단하는 단면형상)을 다르게 함으로써 스페이서 자체의 탄성을 바꿀 수 있으므로, 1회의 포토리소그라파 기술에 의한 선택에칭에 의해 동일한 효과를 얻을 수 있다.

도 7은, 이와 같이 하여 형성한 구성도이며, 도 6과 대응한 도면으로 되어 있다. 도 7에서, 평탄화막(OC)은 형성되어 있지 않고, 이것에 의해, 블랙 매트릭스(BM)에 기인하는 단차를 적극적으로 형성하고 있다.

그리고, 단차가 낮은 부분에 스페이서(SOC(1))를 형성하고, 이 스페이서(SOC(1))의 면적(중심축을 획단하는 면적)을  $S_1$ 로 한다. 또한, 단차가 높은 부분에 스페이서(SOC(2))를 형성하고, 이 스페이서(SOC(2))의 면적을  $S_2(< S_1)$ 로 한다.

이와 같이 형성함으로써, 각 스페이서(SOC)의 재료가 동일하다고 해도, 스페이서(SOC(2))는 외관상의 높이를 높게 할 수 있고, 더욱이 스페이서(SOC(2)) 자체의 탄성을 크게 할 수 있게 된다.

동일한 취지로, 실시예 1의 구성에서, 한쪽의 스페이서의 배치개소를 다른 쪽의 스페이서 보다도 단차가 높은 부분에 형성함으로써, 그들 각 스페이서의 높이를 동일하게 형성해도 되는 것은 물론이다.

이상, 각 실시예에 의한 액정표시장치에 의하면, 상온, 고온에 한정하지 않고, 각 투명기판의 캡을 균일하게 유지할 수 있게 된다.

#### 발명의 효과

이상 설명한 것으로부터 밝혀진 바와 같이, 본 발명에 의한 액정표시장치에 의하면, 상온, 고온에 한정하지 않고, 각 투명기판의 캡을 균일하게 유지할 수 있게 된다.

#### (57) 청구의 범위

##### 청구항 1. 삭제

##### 청구항 2. 삭제

##### 청구항 3.

실(seal)재에 의해 서로 대향하여 고정된 한쌍의 투명기판으로 이루어진 외위기(外圍器),

상기 외위기의 상기 투명기판 사이에 밀봉된 액정층,

상기 외위기내에서 상기 액정층의 확장방향(펴지는 방향)을 따라서 배치된 다수의 화소영역으로 이루어진 표시부,

상기 표시부에서 상기 투명기판의 한쪽으로 고정해서 형성된 복수의 스페이서를 구비하며,

상기 복수의 스페이서는 제1의 스페이서와 제2의 스페이서를 포함하며,

상기 투명기판상에 있어서, 상기 스페이서를 형성하는 하지(下地)로 되는 층에는 단차가 형성되고,

상기 제 1의 스페이서가 상기 단차가 높은 위치에 배치되고,

상기 제 2의 스페이서가 상기 단차가 낮은 위치에 배치되며,

상기 제 1의 스페이서는, 상기 제2의 스페이서보다 상기 하지층에 접촉하는 면적이 작은, 액정표시장치.

#### 청구항 4.

제 3항에 있어서,

상기 제 1의 스페이서는 상기 제2의 스페이서와 같은 재료로 형성되어 있는 것을 특징으로 하는, 액정표시장치.

#### 청구항 5. 삭제

#### 청구항 6. 삭제

#### 청구항 7.

제 3항에 있어서,

상기 한 쪽의 투명기판은, 상기 표시부의 상기 다수의 화소영역에 대응한 개구를 가지는 블랙 매트릭스를 가지고, 상기 블랙 매트릭스의 존재에 의해 상기 단차가 형성되어 있는, 액정표시장치.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7

|                |                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                    |         |            |

| 公开(公告)号        | <a href="#">KR100498625B1</a>                                                            | 公开(公告)日 | 2005-07-01 |

| 申请号            | KR1020010040337                                                                          | 申请日     | 2001-07-06 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA                                                                  |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                |         |            |

| [标]发明人         | IMABAYASHI MAKIKO<br>이마바야시마키코<br>HASEGAWA SHINJI<br>하세가와신지<br>IWAKABE YASUSHI<br>이와카베야스시 |         |            |

| 发明人            | 이마바야시마키코<br>하세가와신지<br>이와카베야스시                                                            |         |            |

| IPC分类号         | G02F1/1339                                                                               |         |            |

| CPC分类号         | G02F1/13394                                                                              |         |            |

| 优先权            | 2000213753 2000-07-14 JP                                                                 |         |            |

| 其他公开文献         | KR1020020007164A                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                |         |            |

### 摘要(译)

每个透明基板的间隙均匀地保持，不限于常温和高温。 以及多个间隔物，其固定到一个透明基板上并支撑另一个透明基板， 角度间隔物由第一间隔物和第二间隔物构成，第一间隔物由相对于第二间隔物具有高弹性的材料形成，并且形成为具有高的高度。 1 指数方面 透明基板，垫片，弹性，台阶高