(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년11월02일

(11) 등록번호 10-0991111

(24) 등록일자 2010년10월26일

(51) Int. Cl.

GO2F 1/133 (2006.01)

(21) 출원번호 10-2003-0061153

(22) 출원일자 2003년09월02일

심사청구일자 2008년09월02일

(65) 공개번호 10-2004-0020845

(43) 공개일자 2004년03월09일

(30) 우선권주장

JP-P-2002-00257209 2002년09월02일 일본(JP)

(56) 선행기술조사문헌

KR1020020013713 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

샤프 가부시키가이샤

일본 오사카후 오사카시 아베노구 나가이케조 22

방 22고

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 별명자

코야마준

일본, 가나가와Ken 243-0036, 아쓰기시, 하세, 398, 가부

시키가이샤 한도오따이 에네루기 켄큐쇼내

키무라하지메

일본, 가나가와Ken 243-0036, 아쓰기시, 하세, 398, 가부

시키가이샤 한도오따이 에네루기 켄큐쇼내

(뒷면에 계속)

(74) 대리인

이병호, 장훈

심사관 : 이강하

전체 청구항 수 : 총 10 항

(54) 액정 디스플레이 디바이스 및 액정 디스플레이 디바이스구동 방법

### (57) 요약

아날로그 버퍼 회로들을 갖고, 루미넌스 변동이 감소된 액정 디스플레이 디바이스가 제공된다. 소스 신호 라인 구동 회로는 복수의 아날로그 버퍼 회로들을 갖는다. 아날로그 버퍼 회로들에 연결된 소스 신호 라인들은 새로운 기간이 시작될 때마다, 그들의 연결들을 다른 아날로그 버퍼 회로들로 스위치한다. 따라서, 아날로그 버퍼 회로들 중의 출력 변동은 평균화되고 균일한 이미지가 스크린 상에 디스플레이될 수 있다.

### 대 표 도

(72) 발명자

시오노이리유타카

일본, 가나가와켄243-0036, 아쓰기시, 하세, 398, 가부

시키가이사한도오따이에네루기켄큐쇼내

히라야마야수히로

일본, 오사카545-0013, 오사카시, 아베노쿠, 나가이케

초, 22-22, 샤프가부시키가이샤내

---

이부열

일본, 오사카545-0013, 오사카시, 아베노쿠, 나가이케

초, 22-22, 샤프가부시키가이샤내

## 특허청구의 범위

### 청구항 1

삭제

### 청구항 2

삭제

### 청구항 3

절연 기판 상에 복수의 팩셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스로서, 상기 소스 신호 라인 구동 회로는 상기 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 갖는, 상기 액정 디스플레이 디바이스에 있어서,

스위칭 회로들이 상기 아날로그 버퍼 회로들과 상기 소스 신호 라인들 사이에 제공되고,

$n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 주기적으로 반복되고,

$r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서, 상기 스위칭 회로는  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m \leq n$ 을 만족시키는 자연수)을 ( $m+r-1$ )번째 아날로그 버퍼 회로로 연결하는, 액정 디스플레이 디바이스.

### 청구항 4

절연 기판 상에 복수의 팩셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스로서, 상기 소스 신호 라인 구동 회로는 상기 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 갖는, 상기 액정 디스플레이 디바이스에 있어서,

스위칭 회로들이 상기 아날로그 버퍼 회로들과 상기 소스 신호 라인들 사이에 제공되고,

$n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 시간적으로 랜덤하게 반복되고,

$r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서, 상기 스위칭 회로는  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m \leq n$ 을 만족시키는 자연수)을 ( $m+r-1$ )번째 아날로그 버퍼 회로로 연결하는, 액정 디스플레이 디바이스.

### 청구항 5

삭제

### 청구항 6

삭제

### 청구항 7

절연 기판 상에 복수의 팩셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스 구동 방법으로서, 상기 소스 신호 라인 구동 회로는 상기 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 갖는, 상기 액정 디스플레이 디바이스 구동 방법에 있어서,

$n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 주기적으로 반복되고,

$r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m \leq n$ 을 만족시키는 자연수)은 ( $m+r-1$ )번째 아날로그 버퍼 회로에 의해 구동되는, 액정 디스플레이 디바이스 구동 방법.

### 청구항 8

절연 기판 상에 복수의 팩셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스 구동 방법으로서, 상기 소스 신호 라인 구동 회로는 상기 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 갖는, 상기 액정 디스플레이 디바이스 구동 방법에 있어

서,

$n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 시간적으로 랜덤하게 반복되고,

$r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m \leq n$ 을 만족시키는 자연수)은  $(m+r-1)$ 번째 아날로그 버퍼 회로에 의해 구동되는, 액정 디스플레이 디바이스 구동 방법.

### 청구항 9

제 3 항 또는 제 4 항에 있어서, 상기 아날로그 버퍼 회로들은 소스 팔로어 회로들(source follower circuit)을 포함하는, 액정 디스플레이 디바이스.

### 청구항 10

제 3 항 또는 제 4 항에 있어서, 상기 아날로그 버퍼 회로들은 전압 팔로어 회로들을 포함하는, 액정 디스플레이 디바이스.

### 청구항 11

제 3 항 또는 제 4 항에 있어서, 상기 스위칭 회로들은 아날로그 스위칭 회로들을 포함하는, 액정 디스플레이 디바이스.

### 청구항 12

제 3 항 또는 제 4 항의 상기 액정 디스플레이 디바이스를 포함하는 전자 장치.

### 청구항 13

제 7 항 또는 제 8 항에 있어서, 상기 아날로그 버퍼 회로들은 소스 팔로어 회로들을 포함하는, 액정 디스플레이 디바이스 구동 방법.

### 청구항 14

제 7 항 또는 제 8 항에 있어서, 상기 아날로그 버퍼 회로들은 전압 팔로어 회로들을 포함하는, 액정 디스플레이 디바이스 구동 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

##### [0023] 1. 발명의 분야

본 발명은 액정 디스플레이 디바이스에 관한 것으로, 특히 유리, 플라스틱 등으로 만들어진 투명 기판 상에 형성된 박막 트랜지스터들(TFT들)을 사용하는 액정 디스플레이 디바이스 및 그 구동 방법에 관한 것이다. 또한, 본 발명은 액정 디스플레이 디바이스를 사용하는 전자 장치에 관한 것이다.

##### [0025] 2. 관련 분야의 설명

최근, 이동 전화들이 통신 기술의 발전에 따라 널리 퍼지게 되었다. 미래에, 동화상 전송 및 보다 많은 양의 정보 전송이 또한 기대된다. 개인용 컴퓨터에 대해서는, 그 중량의 감소 덕분에 이동 애플리케이션들용 제품들이 제조된다. 전자 수첩들로 시작된 PDA들로 불리는 다수의 정보 단말들이 또한 제조되어 널리 보급되고 있다. 또한, 디스플레이 디바이스들 등의 발전과 함께, 대부분의 휴대용 정보 디바이스들은 평판 디스플레이를 구비하고 있다.

[0027] 최근의 기술들에 따르면, 액티브 매트릭스 디스플레이 디바이스(active matrix display device)가 그것에 사용된 디스플레이 디바이스로서 사용되는 경향이 있다. 액티브 매트릭스 디스플레이 디바이스에서, TFT가 각 픽셀

에서 배열되고 스크린은 TFT들에 의해 제어된다. 패시브 매트릭스 디스플레이 디바이스(passive matrix display device)와 비교하면, 액티브 매트릭스 디스플레이 디바이스는 고성능 및 고화질을 달성하고 동화상들을 다룰 수 있다는 장점들을 갖는다. 따라서, 액정 디스플레이 디바이스들의 주류가 패시브 매트릭스형들에서 액티브 매트릭스형들로 또한 변화될 것이라고 고려된다.

[0028] 또한, 최근, 액티브 매트릭스 디스플레이 디바이스들에서 저온 폴리실리콘을 사용하는 디스플레이 디바이스의 상업화가 진행되고 있다. 저온 폴리실리콘으로, 픽셀들 뿐만 아니라 구동 회로를 픽셀부의 주위에 일체로 형성할 수 있고, 디스플레이 디바이스의 소형화 및 고선명화가 가능하기 때문에, 저온 폴리실리콘을 사용하는 디스플레이 디바이스는 보다 널리 사용될 것이라 기대된다.

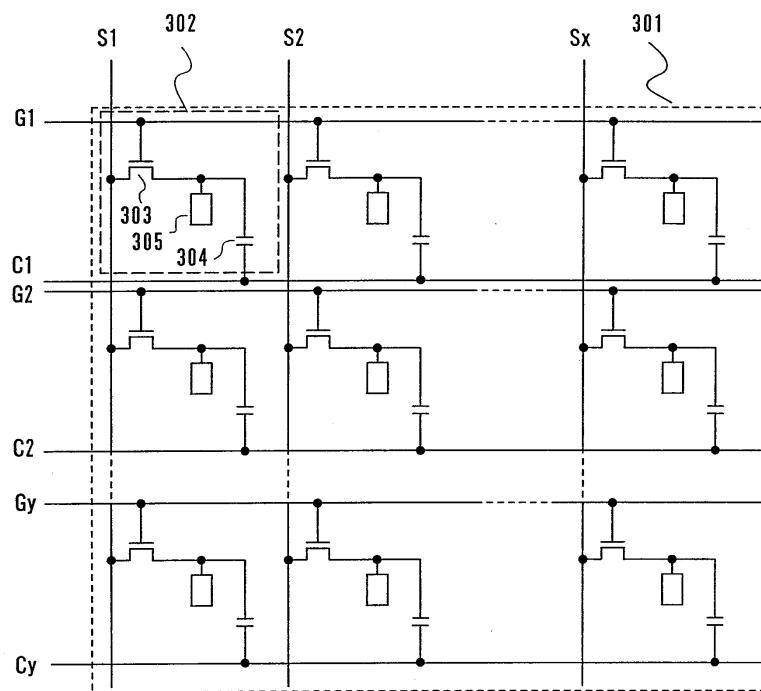

[0029] 액티브 매트릭스 액정 디스플레이 디바이스의 픽셀부의 동작에 대한 설명이 이하에서 주어진다. 도 3은 액티브 매트릭스 액정 디스플레이 디바이스의 구조의 예를 도시한다. 하나의 픽셀(302)은 소스 신호 라인(S1), 게이트 신호 라인(G1), 캐패시턴스 라인(C1), 픽셀 TFT(303), 및 저장 캐패시터(304)로 구성된다. 캐패시턴스 라인은 다른 배선이 캐패시턴스 라인으로서 배가 될 수 있다면 항상 필요하지는 않다. 픽셀 TFT(303)의 게이트 전극은 게이트 신호 라인(G1)에 연결된다. 픽셀 TFT(303)의 드레인 영역 및 소스 영역 중 하나가 소스 신호 라인(S1)에 연결되며 다른 것은 저장 캐패시터(304)와 픽셀 전극(305)에 연결된다.

[0030] 게이트 신호 라인들은 라인 사이클에 따라 순차적으로 선택된다. 픽셀 TFT가 n채널 TFT이면, 게이트 신호 라인을 Hi로 설정하는 것은 라인을 활성화시키고, 픽셀 TFT를 턴온(turn ON)시킨다. 픽셀 TFT가 턴온됨에 따라, 소스 신호 라인의 전위가 저장 캐패시터와 액정에 기록된다. 다음 라인 기간에서, 인접 게이트 신호 라인이 활성화되고 소스 신호 라인의 전위가 유사한 방법으로 저장 캐패시터와 액정에 기록된다.

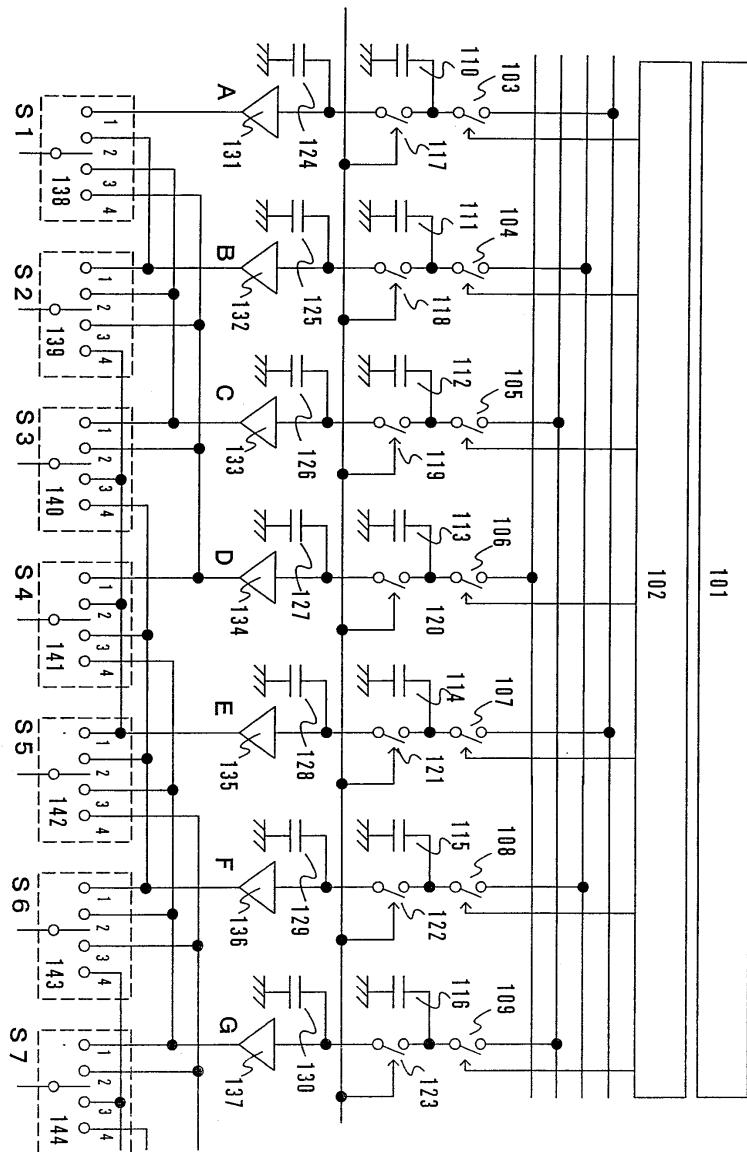

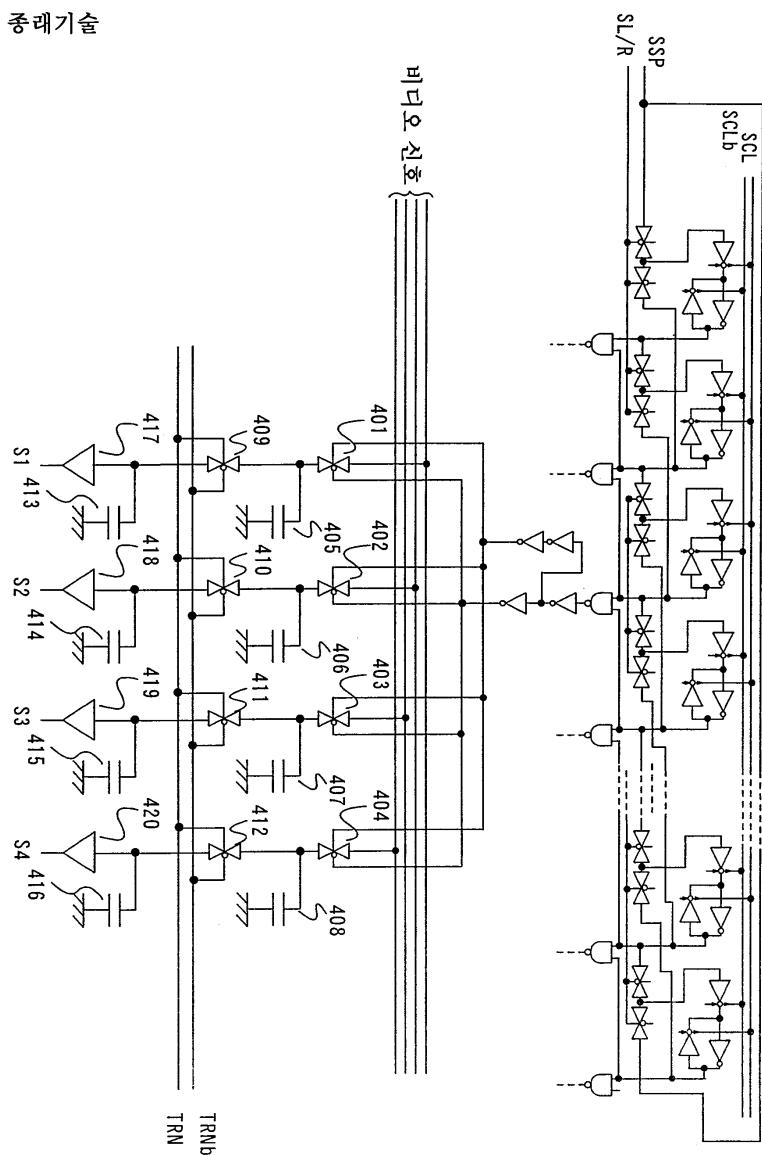

[0031] 다음 설명은 소스 라인 구동 회로의 동작이다. 도 2는 종래의 소스 신호 라인 구동 회로의 예를 도시한다. 도 2의 소스 신호 라인 구동 회로는 아날로그형 도트 순차 구동(analog type dot sequential driving)을 위한 것이다. 이러한 예에서, 소스 신호 라인 구동 회로는 시프트 레지스터(201), NAND 회로(207), 버퍼 회로(208), 및 아날로그 스위치(209)로 구성된다. 먼저, 소스 시작 펄스(sourcr start pulse; SSP)가 스위치(206)를 통해 시프트 레지스터의 제 1 단으로 입력된다. 스위치(206)는 시프트 레지스터의 주사 방향을 결정한다. 주사는 SL/R이 Lo이면 도 2에서 좌측에서 우측으로 행해지고 SL/R이 Hi이면 우측에서 좌측으로 행해진다. DFF(202)는 시프트 레지스터의 각 단을 구성한다. DFF(202)는 클럭된 인버터들(203 및 204)과 인버터(205)로 구성되며, 클럭 펄스들(CL 및 CLb)이 입력될 때마다 펄스들을 시프트한다.

[0032] 시프트 레지스터의 출력은 NAND 회로(207)를 통해 버퍼 회로(208)로 입력된다. 버퍼 회로의 출력은 소스 신호 라인들(S1 내지 S4)로 향하는 비디오 신호들의 샘플링을 위해 아날로그 스위치들(209 내지 212)을 턴온시킨다.

[0033] 중간 또는 작은 크기의 액정 패널은 위에서 설명된 도트 순차 구동에 의해 동작될 수 있다. 그러나, 큰 크기의 액정 패널에서, 도트 순차 구동은 소스 신호 라인들의 배선 캐패시턴스가 약 100pF이고 소스 신호 라인들 자체의 지연 시간이 너무 크기 때문에 소스 신호 라인들의 기록을 위한 충분한 시간을 제공할 수 없다. 따라서, 기록을 수행하는 것이 불가능해진다. 그러므로, 큰 크기의 패널은 데이터가 소스 신호 라인 구동 회로 내의 메모리에 임시로 저장되고 그 후 다음의 하나의 라인 기간동안 소스 신호 라인에 기록되는 선형 순차 구동이 필요하다.

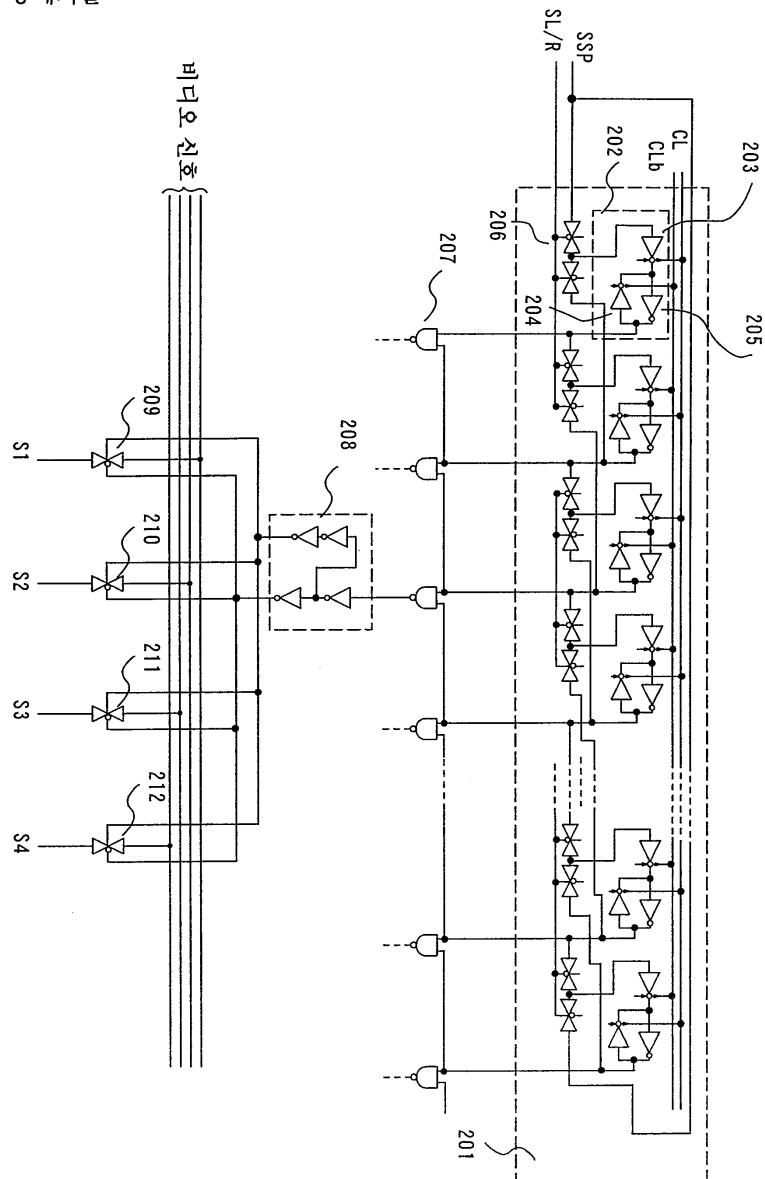

[0034] 이러한 선형 순차 구동은 메모리의 다운스트림에 위치되는 아날로그 버퍼 회로들을 필요로 한다. 선형 순차 구동에 적응가능한 소스 신호 라인 구동 회로의 예가 도 4에 도시된다. 아날로그 스위치들(401 내지 404)은 도 2에 도시된 도트 순차 소스 신호 라인 구동 회로에서 아날로그 스위치들이 동작하는 것과 동일한 방법으로 동작한다. 아날로그 스위치들이 소스 신호 라인들을 구동하는 도 2와 달리, 아날로그 스위치들(401 내지 404)은 아날로그 메모리들로서 동작하는 캐패시터들(405 내지 408)을 구동한다. 데이터의 한 라인이 아날로그 메모리들에 순차적으로 저장되면, TRN 및 TRNb 신호들은 다음 귀선(retrace) 기간에서 아날로그 스위치들(409 내지 412)을 턴온시키기 위해 활성화된다. 이는 아날로그 메모리들(405 내지 408)의 데이터의 아날로그 메모리 캐패시터들(413 내지 416)로의 전송을 시작한다.

[0035] 이후, 아날로그 스위치들(409 내지 412)은 다음 샘플링을 위하여 아날로그 스위치들(401 내지 404)이 턴온되기 전에 턴오프된다. 아날로그 메모리들(413 내지 416)의 데이터는 아날로그 버퍼 회로들(417 내지 420)을 통해 소스 신호 라인들(S1 내지 S4)로 출력된다. 아날로그 메모리들(413 내지 416)의 데이터는 하나의 라인 기간동안 유지되고 따라서 아날로그 버퍼 회로들(417 내지 420)은 소스 라인들을 충전하기 위하여 하나의 라인 기간을 축 하도록 허용된다. 이러한 방법으로, 큰 크기의 패널에서의 선형 순차 구동이 아날로그 메모리들 및 아날로그 버

퍼 회로들에 의해 실현되는 것이 가능하다.

[0036] 그러나, 큰 크기의 패널의 아날로그 버퍼 회로들이 TFT들로 구성될 때, 아날로그 버퍼 회로들 중의 변동 (fluctuation)이 문제가 된다. 동일한 그레이스케일(gray scale)의 비디오 신호들이 입력되더라도, 아날로그 버퍼 회로들 중의 변동은 출력 변동을 야기한다. 그 결과, 수직의 줄무늬들(vertical streaks)이 스크린 상에 나타나고 화질이 상당히 하락한다.

[0037] 저온 다결정 실리콘의 액정 디스플레이 디바이스를 제조하는데 사용되면, 구동 회로가 일체로 형성된다. 그러나, 이러한 구동 회로의 트랜지스터들은 단일 결정 실리콘으로 형성되는 구동 회로의 트랜지스터들보다 많이 변동된다. 이것은 추측컨대 프로세스 중의 정전기에 의한 손상 및 불균일한 결정화 때문이다. 구동 회로가 이러한 변동을 고려하여 형성되면, 변동은 논리부(logic portion)에서보다는 아날로그 동작을 수행하는 구성 요소, 특히, 아날로그 버퍼 회로들에서 더욱 명백해진다.

[0038] 도 4에 도시된 종래의 소스 신호 라인 구동 회로에서, 각 아날로그 버퍼 회로의 출력 전압과 복수의 아날로그 버퍼 회로들의 출력의 평균 사이의 전압차가 얻어진다. 평균 출력값과 아날로그 버퍼 회로 출력(A)사이의 전압 차는  $\Delta VA$ 로서 주어진다. 유사하게, 평균 출력값과 아날로그 버퍼 회로 출력들(B,C, 및 D)사이의 전압차들은  $\Delta VB$ ,  $\Delta VC$ , 및  $\Delta VD$ 로 각각 주어진다.  $\Delta VA$ 가  $+100mV$ ,  $\Delta VB$ 가  $-100mV$ ,  $\Delta VC$ 가  $-50mV$ 이고,  $\Delta VD$ 가  $+30mV$ 이면, 소스 신호 라인(S2)과 소스 신호 라인(S3) 사이의 차이는  $50mV$ 이고, 소스 신호 라인(S1)과 소스 신호 라인(S2) 사이의 차이는  $200mV$ 이며, 이는 사람의 눈이 그레이 스케일의 차이를 인식하기에 충분히 크다.

### 발명이 이루고자 하는 기술적 과제

#### 발명의 요약

[0040] 본 발명은 위의 문제들을 해결하기 위해 만들어졌으며, 따라서 본 발명의 목적은 출력들을 스위치시키기 위해 아날로그 버퍼 회로들과 소스 신호 라인들 사이에 스위치들을 삽입시키는 것에 의해 루미넌스 변동이 감소되는 액정 디스플레이 디바이스를 제공하는 것이다. 이는 아날로그 버퍼 회로들 중의 출력 변동을 시간적으로 평균화하고, 따라서 디스플레이 비평탄성이 눈에 띄지 않게 된다.

[0041] 본 발명의 구조는 다음과 같이 도시된다.

[0042] 본 발명에 따라, 절연 기판 상에 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 복수의 픽셀들과, 소스 신호 라인들을 구동하기 위한 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스가 제공되며, 이 액정 디스플레이 디바이스는 소스 신호 라인 구동 회로가 복수의 아날로그 버퍼 회로들을 갖고, 아날로그 버퍼 회로들에 연결된 소스 신호 라인들은 스위칭 회로들에 의해 그들의 연결들이 다른 아날로그 버퍼 회로들로 주기적으로 스위칭되는 것을 특징으로 한다.

[0043] 본 발명에 따라, 절연 기판 상에 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 복수의 픽셀들과, 소스 신호 라인들을 구동하기 위한 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스가 제공되며, 이 액정 디스플레이 디바이스는 소스 신호 라인 구동 회로는 복수의 아날로그 버퍼 회로들을 갖고, 소스 신호 라인들은 스위칭 회로들에 의해 그들의 연결들이 다른 아날로그 버퍼 회로들로 시간적으로 랜덤하게 스위칭되는 것을 특징으로 한다.

[0044] 본 발명에 따라, 절연 기판 상에 복수의 픽셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스가 제공되고, 소스 신호 라인 구동 회로는 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 가지며, 이 액정 디스플레이 디바이스는  $n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 주기적으로 반복되고,  $r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m$ 을 만족시키는 자연수)은  $(m+r-1)$ 번째 아날로그 버퍼 회로로 연결되는 것을 특징으로 한다.

[0045] 본 발명에 따라, 절연 기판 상에 복수의 픽셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스가 제공되고, 소스 신호 라인 구동 회로는 소스 신호 라인들을 구동하기 위한 아날로그 버퍼 회로들을 가지며, 이 액정 디스플레이 디바이스는  $n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 시간적으로 랜덤하게 반복되고,  $r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m$ 을 만족시키는 자연수)은  $(m+r-1)$ 번째 아날로그 버퍼 회로로 연결되는 것을 특징으로 한다.

- [0046] 상술된 본 발명의 구조에서, 아날로그 베퍼 회로들은 소스 팔로어 회로들 또는 전압 팔로어 회로들인 것을 특징으로 한다.

- [0047] 본 발명에 따라, 절연 기판 상에 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 복수의 픽셀들과, 소스 신호 라인들을 구동하기 위한 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스를 구동하는 방법이 제공되며, 이 액정 디스플레이 디바이스 구동 방법은 소스 신호 라인 구동 회로는 복수의 아날로그 베퍼 회로들을 갖고, 소스 신호 라인들은 다른 아날로그 베퍼 회로들에 의해 주기적으로 구동되는 것을 특징으로 한다.

- [0048] 본 발명에 따라, 절연 기판 상에 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 복수의 픽셀들과, 소스 신호 라인들을 구동하기 위한 소스 신호 라인 구동 회로를 갖는 액정 디스플레이 디바이스를 구동하는 방법이 제공되며, 이 액정 디스플레이 디바이스 구동 방법은 소스 신호 라인 구동 회로는 복수의 아날로그 베퍼 회로들을 갖고, 소스 신호 라인들은 다른 아날로그 베퍼 회로들에 의해 시간적으로 랜덤하게 구동되는 것을 특징으로 한다.

- [0049] 본 발명에 따라, 절연 기판 상에 복수의 픽셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스 구동 방법이 제공되며, 소스 신호 라인 구동 회로는 소스 신호 라인들을 구동하기 위한 아날로그 베퍼 회로들을 갖고, 이 액정 디스플레이 디바이스 구동 방법은  $n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 주기적으로 반복되고,  $r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m$ 을 만족시키는 자연수)은  $(m+r-1)$ 번째 아날로그 베퍼 회로에 의해 구동되는 것을 특징으로 한다.

- [0050] 본 발명에 따라, 절연 기판 상에 복수의 픽셀들과, 복수의 소스 신호 라인들과, 복수의 게이트 신호 라인들과, 소스 신호 라인 구동 회로를 포함하는 액정 디스플레이 디바이스 구동 방법이 제공되며, 소스 신호 라인 구동 회로는 소스 신호 라인들을 구동하기 위한 아날로그 베퍼 회로들을 갖고, 이 액정 디스플레이 디바이스 구동 방법은  $n$ ( $n$ 은  $2 \leq n$ 을 만족시키는 자연수)개의 기간들의 세트가 시간적으로 랜덤하게 반복되고,  $r$ 번째 기간( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)에서,  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m$ 을 만족시키는 자연수)은  $(m+r-1)$ 번째 아날로그 베퍼 회로에 의해 구동되는 것을 특징으로 한다.

- [0051] 상술된 본 발명의 액정 디스플레이 디바이스 구동 방법에서 아날로그 베퍼 회로들은 소스 팔로어 회로들 또는 전압 팔로어 회로들인 것을 특징으로 한다.

- [0052] 위의 구조 및 방법을 통해, 절연 기판 상에 형성된 아날로그 베퍼 회로들이 출력에서 변동된다고 하더라도 수직의 줄무늬들이 스크린 상에 디스플레이되는 것이 방지된다.

### 발명의 구성 및 작용

- [0053] 바람직한 실시예들의 상세한 설명

- [0054] 실시예 모드

- [0055] 본 발명의 실시예 모드가 도면들을 참조하여 이하로 상세히 설명될 것이다.

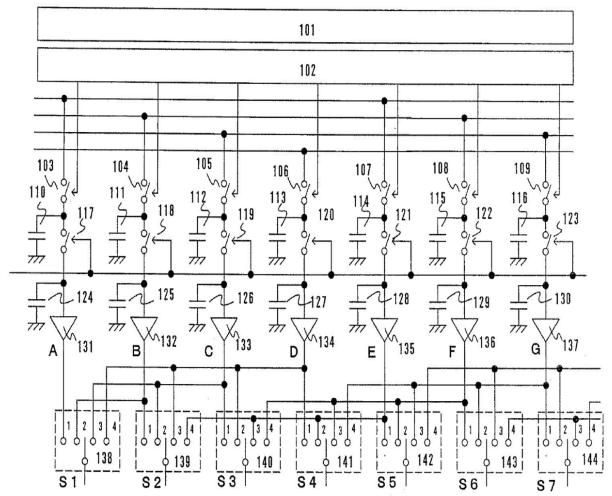

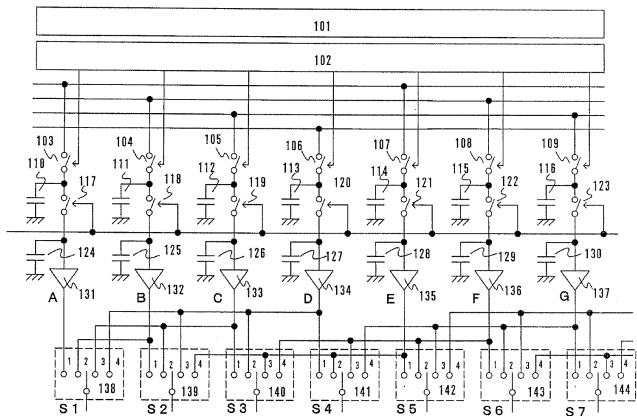

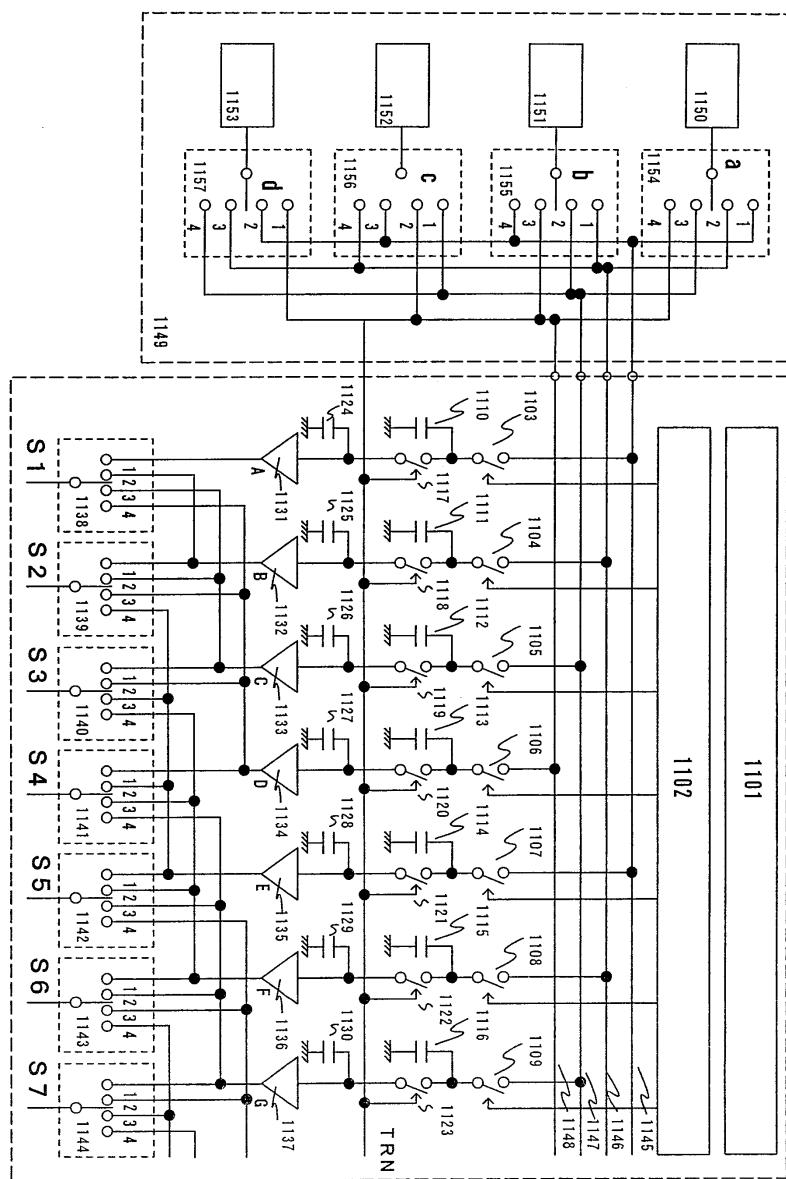

- [0056] 도 1은 본 발명의 액정 디스플레이 디바이스를 도시한다. 그의 시프트 레지스터 및 다른 구성요소들은 종래 기술에서 설명된 것과 유사하다. 본 발명과 종래 기술과의 차이는 도 1의 디바이스가 아날로그 베퍼 회로들(131 내지 137)과 소스 신호 라인들(S1 내지 S7)사이에 스위치들(138 내지 144)을 가진다는 것이다. 이제, 본 실시예 모드의 디바이스의 동작이 설명된다. 이러한 설명은 스위치들(138 내지 144)에 대한 4-접촉 포인트 스위치들을 사용하는 경우를 예로 든다. 그러나, 본 발명은 4-접촉 포인트 스위치들로 제한되지 않으며 접촉 포인트들의 개수는 본 발명을 수행하는데 문제가 되지 않는다.

- [0057] 본 발명에서, 스위치들(138 내지 144)의 연결들은 하나에서 다른 하나로 스위칭된다. 여기서, 스위칭 사이클은 하나의 프레임이지만 본 발명은 이에 제한되지 않는다. 어떻게 스위칭이 행해지는가가 이하로 설명된다. 제 1 프레임에서, 스위치들(138 내지 144)은 아날로그 베퍼 회로(131)의 출력(A)이 소스 신호 라인(S1)에 연결되고 아날로그 베퍼 회로들(132 내지 137)의 출력들(B,C,D,E,F 및 G)이 각각 소스 신호 라인들(S2, S3, S4, S5, S6, 및 S7)에 연결되는 "1"연결 상태에 있다.

- [0058] 다음, 제 2 프레임에서, 스위치들(138 내지 144)은 아날로그 버퍼 회로(132)의 출력(B)이 소스 신호 라인(S1)에 연결되고 아날로그 버퍼 회로들(133 내지 137)의 출력들(C,D,E,F 및 G)이 각각 소스 신호 라인들(S2,S3,S4,S5 및 S6)에 연결되는 "2"연결 상태에 있다. 제 3 프레임에서, 스위치들(138 내지 144)은 아날로그 버퍼 회로(133)의 출력(C)이 소스 신호 라인(S1)에 연결되고 아날로그 버퍼 회로들(134 내지 137)의 출력들(D,E,F 및 G)이 각각 소스 신호 라인들(S2,S3,S4 및 S5)에 연결되는 "3"연결 상태에 있다.

- [0059] 다음, 제 4 프레임에서, 스위치들(138 내지 144)은 아날로그 버퍼 회로(134)의 출력(D)이 소스 신호 라인(S1)에 연결되고 아날로그 버퍼 회로들(135 내지 137)의 출력들(E,F 및 G)이 각각 소스 신호 라인들(S2,S3 및 S4)에 연결되는 "4"연결 상태에 있다.

- [0060] 다음, 제 5 프레임에서, 스위치들(138 내지 144)은 아날로그 버퍼 회로(131)의 출력(A)이 소스 신호 라인(S1)에 연결되고 아날로그 버퍼 회로들(132 내지 137)의 출력들(B,C,D,E,F 및 G)이 각각 소스 신호 라인들(S2,S3,S4,S5,S6 및 S7)에 연결되는 "1"연결 상태에 다시 있다. 이러한 방법으로, 스위치들(138 내지 144)은 4개의 프레임들의 기간으로 연결 변화를 반복한다.

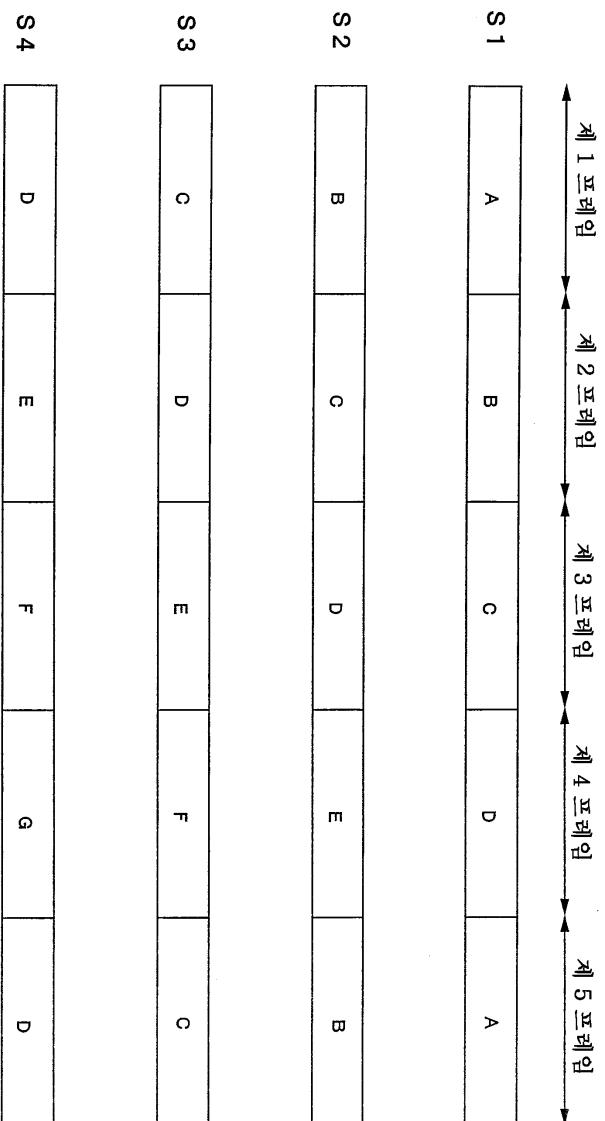

- [0061] 스위칭은 4-접촉 포인트 스위치들이 사용되기 때문에 4-프레임 사이클에서 행해진다. 사이클은 위에서 설명된 바와 같은 접촉 포인트들의 개수를 변화시킴으로써 변화될 수 있다. 프레임 기반 사이클을 고집하는 것이 또한 필요하지 않다. 변동이 명백하게 평균화될 수 있는 한 임의의 사이클이 행해질 것이다. 도 10은 각각이 소스 신호 라인에 연결된 아날로그 버퍼 회로들의 출력을 도시한다.

- [0062] 종래 기술에서와 같이, 각 아날로그 버퍼 회로의 출력 전압과 복수의 아날로그 버퍼 회로들의 출력의 평균 사이의 전압차가 얻어진다. 평균 출력값과 아날로그 버퍼 회로 출력(A) 사이의 전압차가  $\Delta VA$ 로 주어진다. 유사하게, 평균 출력값과 아날로그 버퍼 회로 출력들(B,C 및 D) 사이의 전압차들은 각각  $\Delta VB$ ,  $\Delta VC$ , 및  $\Delta VD$ 로 주어진다. 이후, 전압차들은 사람의 눈에 평균화된 것처럼 보인다. 따라서, 소스 신호 라인들(S1, S2, S3 및 S4)의 각각에는  $(\Delta VA + \Delta VB + \Delta VC + \Delta VD) / 4$ 의 출력 전위차가 주어지고 그들 사이의 차이는 0이 된다.

- [0063] 종래 기술에서와 같이  $\Delta VA$ 가  $+100mV$ ,  $\Delta VB$ 가  $-100mV$ ,  $\Delta VC$ 가  $-50mV$ ,  $\Delta VD$ 가  $+30mV$ 일 때, 소스 신호 라인들(S1 내지 S4)의 전압들은 평균화되고 각각은  $-5mV$ 로 설정된다. 따라서, 선명한 수직의 줄무늬들을 생성하도록 근접한 라인들 사이에  $200mV$  정도의 큰 전위차가 존재하는 종래 기술의 문제가 회피될 수 있다.

- [0064] 위의 실시예 모드에서, 스위치들 각각은 4개의 접촉 포인트들을 갖고, 반복 사이클은 4개의 기간들을 포함한다. 그러나, 기간들의 수는 4로 제한되지 않는다. 객관적인 효과는  $n$ ( $n$ 은 자연수이며 2와 같거나 그보다 크다)개의 기간들을 설정하고,  $r$ 번째 기간에서  $m$ 번째 소스 신호 라인( $m$ 은  $1 \leq m \leq n$ 을 만족시키는 자연수)을  $(m+r-1)$ 번째 아날로그 버퍼( $r$ 은  $1 \leq r \leq n$ 을 만족시키는 자연수)로 연결시킴으로써 얻어질 수 있다. 또한, 객관적인 효과는  $(m+r-1)$ 번째 아날로그 버퍼를 갖는  $m$ 번째 소스 신호 라인을 구동시킴으로써 얻어질 수 있다.

- [0065] [실시예 1]

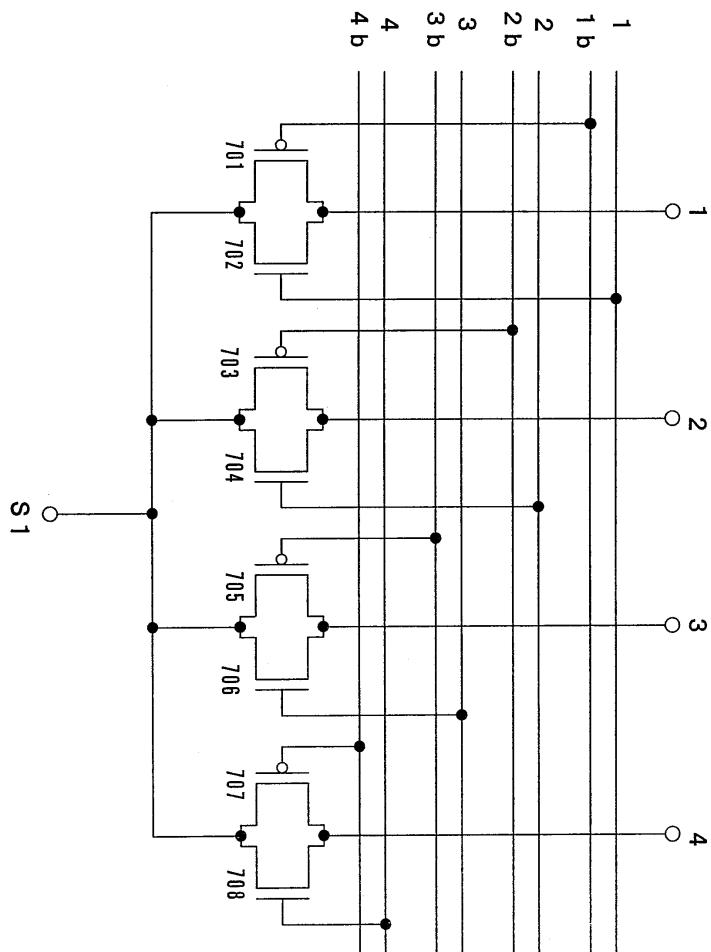

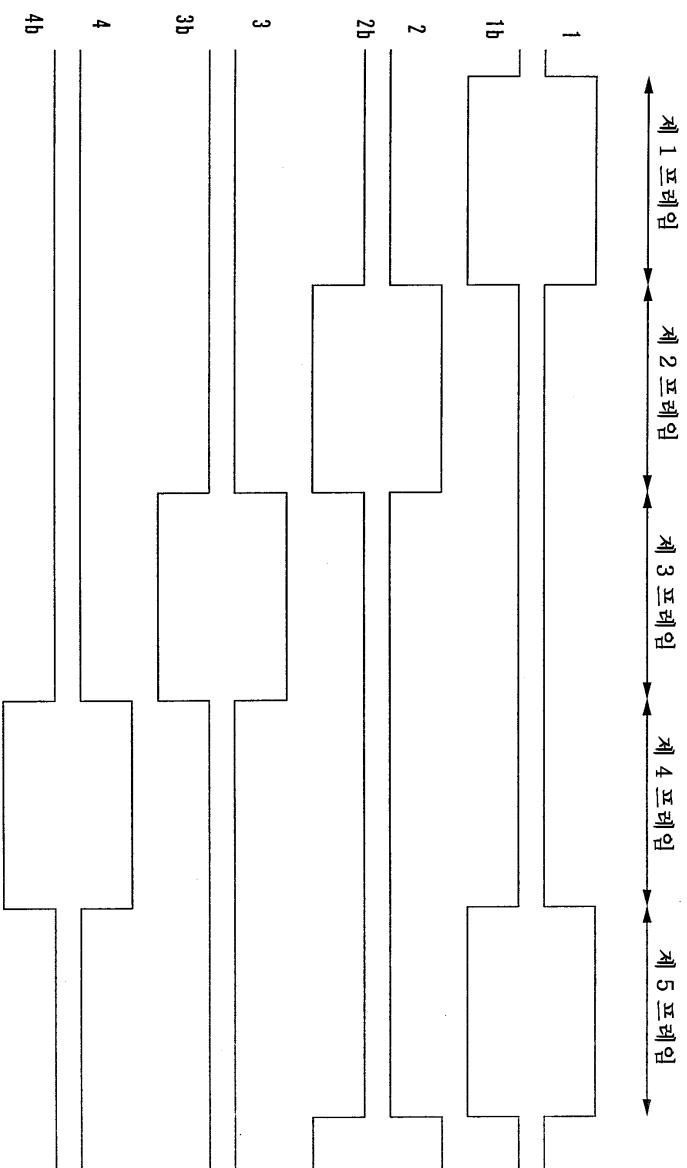

- [0066] 도 7은 실시예 1을 도시하며, 도 1에 도시된 스위치(123)의 특정 회로의 예이다. 본 실시예에서, 아날로그 스위칭 회로가 스위치로서 사용된다. 스위치는 TFT들(701 내지 708)로 구성되고 이는 제어 라인들(1, 1b, 2, 2b, ..., 및 4b)에 의해 제어되며 TFT들(701 내지 708)의 게이트 단자들로 개별적으로 연결된다. 도 8은 제어 라인들(1 내지 4b)의 타이밍도이다. 도 8에 도시된 제어 신호는 제 1 내지 제 4 프레임 동안 소스 신호 라인들(S1 내지 S4)로 도 1에 도시된 D를 연결한다. 도 7에 도시된 회로도는 CMOS 구조를 갖지만, NMOS 또는 PMOS 구조를 대신 가질 수도 있다. 이러한 경우에, 제어 라인들의 수는 반으로 줄어든다.

- [0067] [실시예 2]

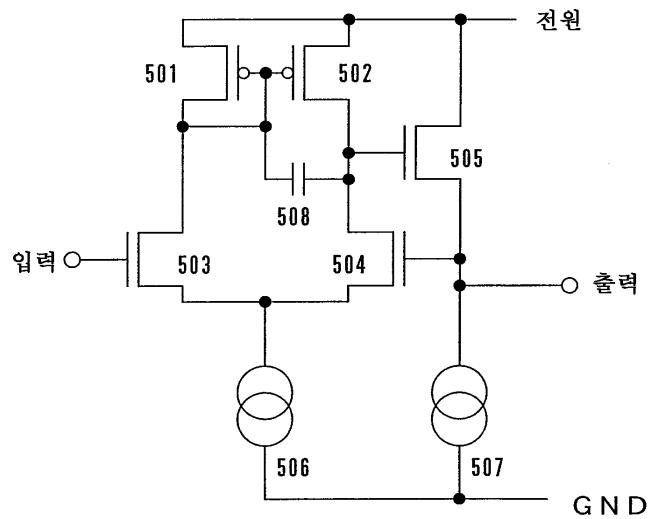

- [0068] 도 5는 아날로그 버퍼 회로의 예로서 연산 증폭기 회로를 도시한다. 아날로그 버퍼 회로의 이러한 유형의 출력 전압 변동은 차분 회로를 구성하는 TFT(503)와 TFT(504) 사이의 특징의 변동과, 전류 미러 회로(current mirror circuit)를 구성하는 TFT(501)과 TFT(502) 사이의 변동에 의존한다. 한 쌍의 인접한 TFT들간의 변동이 작으면, 패널의 전체 변동은 문제를 일으키지 않으면서 클 수 있다. 이러한 이유로, 연산 증폭기형 아날로그 버퍼 회로들이 종종 접촉 회로들에 사용된다.

- [0069] 이러한 예에서, 차분 회로는 n-채널 TFT들로 구성되고 전류 미러 회로는 p-채널 TFT들로 구성된다. 그러나, 본 발명은 이에 제한되지 않으며 이러한 회로들의 극성들은 역전될 수 있다. 또한, 본 발명은 본 예에 도시된 회로 연결에 제한되지 않으며 연산 증폭기의 기능을 제공하는 한 임의의 회로 연결이 사용될 수 있다.

[0070] [실시예 3]

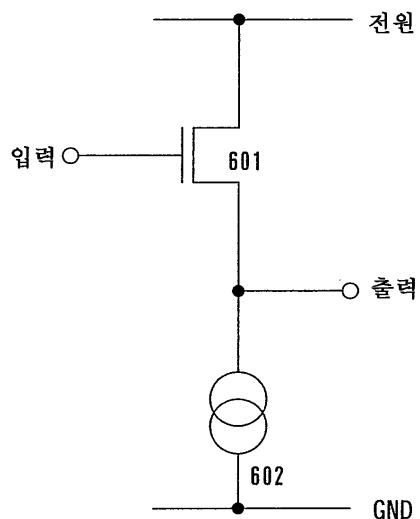

도 6은 아날로그 버퍼 회로의 예로서 소스 팔로어 회로를 도시한다. 소스 팔로어 회로는 버퍼 TFT(601)와 일정한 전류 소스(602)로 구성된다. 이러한 예에서, 버퍼 TFT는 n-채널 TFT이지만 p-채널 TFT가 대신될 수도 있다. n-채널 TFT가 사용되면, 소스 팔로어 회로의 출력 전위는 TFT의 V<sub>gs</sub>에 의해 입력 전위보다 낮다. 한편, p-채널 TFT가 사용되면, 소스 팔로어 회로의 출력 전위는 TFT의 V<sub>gs</sub>에 의해 입력 전위보다 높다. 소스 팔로어 회로가 이러한 문제를 가짐에도 불구하고, CMOS보다 단순한 구조를 가진다는 장점을 또한 갖는다. 단극 프로세스가 TFT 제조 공정들의 수를 감소시키기 위해 사용되는 경우에, 연산 증폭기형 아날로그 버퍼 회로를 생성하는 것이 어려워지며, 따라서 소스 팔로어형이 선택된다.

[0072] [실시예 4]

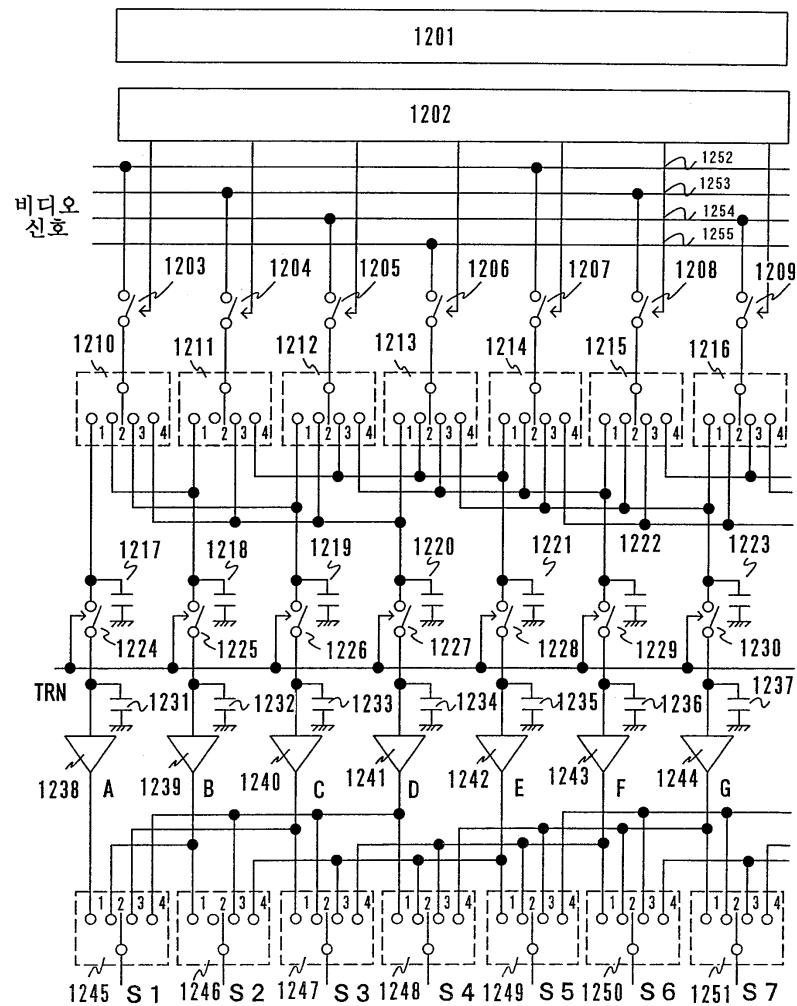

도 11은 소스 신호 라인 구동 회로로 입력되는 비디오 신호들을 스위칭하기 위한 회로가 본 발명의 회로를 사용하기 위해 소스 신호 라인 구동 회로의 외부에 위치되는 예를 도시한다. 단지 아날로그 스위치들과 소스 신호 라인들 사이에서 소스 신호 라인들의 스위칭이 본 발명에 따라 행해지면, 출력 변동은 감소되지만 아날로그 버퍼 출력은 4 개의 소스 신호 라인들로 보내져 일반적인 이미지를 얻는 것을 불가능하게 만든다. 따라서, 아날로그 버퍼 회로들로 입력되기 전에 신호들이 스위칭되고 아날로그 버퍼 회로들의 다운스트림으로 위치되는 스위치들에 의해 다시 스위칭된다. 이러한 방법에서, 일반적인 이미지가 형성된다.

본 발명의 실시예 모드로서, 스위칭이 새로운 프레임이 시작될 때마다 행해지는 경우가 고려된다. 제 1 프레임에서, 비디오 회로(1150)의 출력은 스위치(1154)를 "1"로 연결하는 것에 의해 비디오 신호 라인(1145)으로 연결된다. 비디오 신호 라인(1145)의 신호는 스위치들(1103 및 1117)을 통해 아날로그 버퍼 회로(1131)로 입력된다. 스위치(1138)가 제 1 프레임에서 "1"로 연결되면 따라서 아날로그 버퍼 회로(1131)의 출력이 소스 신호 라인(S1)에 연결된다. 유사하게, 비디오 회로들(1151, 1152, 및 1153)의 출력들은 소스 신호 라인들(S2, S3, 및 S4)로 각각 연결된다.

제 2 프레임에서, 비디오 회로(1150)의 출력은 스위치(1154)를 "2"로 연결하는 것에 의해 비디오 신호 라인(1146)으로 연결된다. 비디오 신호 라인(1146)의 신호는 스위치들(1104 및 1118)을 통해 아날로그 버퍼 회로(1132)로 입력된다. 스위치(1138)가 제 2 프레임에서 "2"로 연결되면 따라서 아날로그 버퍼 회로(1132)의 출력이 소스 신호 라인(S1)에 연결된다. 유사하게, 비디오 회로들(1151, 1152, 및 1153)의 출력들은 소스 신호 라인들(S2, S3, 및 S4)로 각각 연결된다.

제 3 프레임에서, 비디오 회로(1150)의 출력은 스위치(1154)를 "3"으로 연결하는 것에 의해 비디오 신호 라인(1147)으로 연결된다. 비디오 신호 라인(1147)의 신호는 스위치들(1105 및 1119)을 통해 아날로그 버퍼 회로(1133)로 입력된다. 스위치(1138)가 제 3 프레임에서 "3"으로 연결되면 따라서 아날로그 버퍼 회로(1133)의 출력이 소스 신호 라인(S1)에 연결된다. 유사하게, 비디오 회로들(1151, 1152, 및 1153)의 출력들은 소스 신호 라인들(S2, S3, 및 S4)로 각각 연결된다.

제 4 프레임에서, 비디오 회로(1150)의 출력은 스위치(1154)를 "4"로 연결하는 것에 의해 비디오 신호 라인(1148)으로 연결된다. 비디오 신호 라인(1148)의 신호는 스위치들(1106 및 1120)을 통해 아날로그 버퍼 회로(1134)로 입력된다. 스위치(1138)가 제 4 프레임에서 "4"로 연결되면 따라서 아날로그 버퍼 회로(1134)의 출력이 소스 신호 라인(S1)에 연결된다. 유사하게, 비디오 회로들(1151, 1152, 및 1153)의 출력들은 소스 신호 라인들(S2, S3, 및 S4)로 각각 연결된다.

이러한 방법으로, 비디오 회로(1150)의 출력은 각 프레임에서 소스 신호 라인(S1)으로 연결된다. 이는 일반적인 이미지를 얻으면서 새로운 프레임이 시작될 때마다 하나에서 다른 하나로 아날로그 버퍼 회로들을 스위치하는 것을 가능하게 한다. 유사하게, 임의의 프레임에서, 비디오 회로들(1151, 1152, 및 1153)의 출력들은 각각 소스 신호 라인들(S2, S3, 및 S4)로 연결된다.

이러한 회로는 기판(인쇄된 기판 또는 가변 기판)을 TFT 기판의 외측에 위치시킴으로써, 또는 TFT 기판의 최상 표면에 LSI 칩을 접합시킴으로써, 또는 동일한 기판 상에 비디오 스위칭 회로와 픽셀부를 형성하도록 TFT들을 사용함으로써 얻어질 수 있다.

[0080] [실시예 5]

본 실시예는 소스 신호 라인 구동 회로에 스위칭 회로를 통합시킨 예를 설명한다. 이러한 실시예에서, 스위칭 회로는 도 12에 도시된 바와 같이 아날로그 버퍼 회로들과 비디오 신호 라인들 사이에 위치된다.

- [0082] 본 발명의 실시예 모드로서, 스위칭이 새로운 프레임이 생성될 때마다 행해지는 경우가 고려된다. 제 1 프레임에서, 비디오 신호 라인(1252)의 출력은 스위치(1203)를 통해 통과하고 스위치(1210)를 "1"로 연결하는 것에 의해 아날로그 메모리(1217) 및 스위치(1224)로 연결된다. 비디오 신호 라인(1252)의 신호는 스위치(1224)를 통해 아날로그 메모리(1231)와 아날로그 버퍼 회로(1238)로 입력된다. 스위치(1245)는 제 1 프레임에서 "1"로 연결되며 따라서 아날로그 버퍼 회로(1238)의 출력은 소스 신호 라인(S1)으로 연결된다. 유사하게, 비디오 신호 라인들(1253, 1254, 및 1255)의 출력들은 각각 소스 신호 라인들(S2, S3 및 S4)로 연결된다.

- [0083] 다음, 제 2 프레임에서, 비디오 신호 라인(1152)의 출력은 스위치(1203)를 통해 통과하고 스위치(1210)를 "2"로 연결하는 것에 의해 아날로그 메모리(1218) 및 스위치(1225)로 연결된다. 비디오 신호 라인(1252)의 신호는 스위치(1225)를 통해 아날로그 메모리(1232)와 아날로그 버퍼 회로(1239)로 입력된다. 스위치(1245)는 제 2 프레임에서 "2"로 연결되며 따라서 아날로그 버퍼 회로(1239)의 출력은 소스 신호 라인(S1)으로 연결된다. 유사하게, 비디오 신호 라인들(1253, 1254, 및 1255)의 출력들은 각각 소스 신호 라인들(S2, S3 및 S4)로 연결된다.

- [0084] 이후, 제 3 프레임에서, 비디오 신호 라인(1252)의 출력은 스위치(1203)를 통해 통과하고 스위치(1210)를 "3"으로 연결하는 것에 의해 아날로그 메모리(1219) 및 스위치(1226)로 연결된다. 비디오 신호 라인(1252)의 신호는 스위치(1226)를 통해 아날로그 메모리(1233)와 아날로그 버퍼 회로(1240)로 입력된다. 스위치(1245)는 제 3 프레임에서 "3"으로 연결되며 따라서 아날로그 버퍼 회로(1240)의 출력은 소스 신호 라인(S1)으로 연결된다. 유사하게, 비디오 신호 라인들(1253, 1254, 및 1255)의 출력들은 각각 소스 신호 라인들(S2, S3 및 S4)로 연결된다.

- [0085] 이후, 제 4 프레임에서, 비디오 신호 라인(1252)의 출력은 스위치(1203)를 통해 통과하고 스위치(1210)를 "4"로 연결하는 것에 의해 아날로그 메모리(1220) 및 스위치(1227)로 연결된다. 비디오 신호 라인(1252)의 신호는 스위치(1227)를 통해 아날로그 메모리(1234)와 아날로그 버퍼 회로(1241)로 입력된다. 스위치(1245)는 제 4 프레임에서 "4"로 연결되며 따라서 아날로그 버퍼 회로(1241)의 출력은 소스 신호 라인(S1)으로 연결된다. 유사하게, 비디오 신호 라인들(1253, 1254, 및 1255)의 출력들은 각각 소스 신호 라인들(S2, S3 및 S4)로 연결된다.

- [0086] 이러한 방법으로, 비디오 신호 라인(1252)의 출력은 각 프레임에서 소스 신호 라인(S1)으로 연결된다. 이는 일반적인 이미지를 얻으면서 새로운 프레임이 시작될 때마다 하나에서 다른 하나로 아날로그 버퍼 회로들이 스위치하는 것을 가능하게 한다. 유사하게, 임의의 프레임에서, 비디오 신호 라인들(1253, 1254, 및 1255)의 출력들은 각각 소스 신호 라인들(S2, S3, 및 S4)로 연결된다.

- [0087] [실시예 6]

- [0088] 본 발명의 실시예 모드와 실시예들 1,4 및 5에서, 스위칭은 미리 정해진 순서로 주기적으로 행해진다. 그러나, 스위칭이 항상 고정된 순서로 행해져야 하는 것은 아니다. 예를 들어, 소스 신호 라인(S1)이 이를 주기적으로 반복하기 위하여 첫번째 4개의 프레임들에서 아날로그 버퍼 출력들(A,B,C, 및 D)에, 다음 4개의 프레임들에서 A,B,C, 및 D에 순차적으로 연결되는 실시예 모드는, S1이 첫번째 4개의 프레임들에서 A,B,C 및 D에, 다음 4개의 프레임들에서 C,B,D, 및 A에 순차적으로 연결되고 이로써 시간적으로 랜덤한 순서로 셋업되도록 변경될 수 있다. 이러한 경우에, 실시예들 1 내지 5에 도시된 회로들은 본 실시예와 자유롭게 조합될 수 있다.

- [0089] 본 발명의 디스플레이 디바이스는 본 실시예의 소스 신호 라인 구동 회로 구조에 제한되지 않으며 임의의 알려진 소스 신호 라인 구동 회로 구조를 사용할 수 있다.

- [0090] [실시예 7]

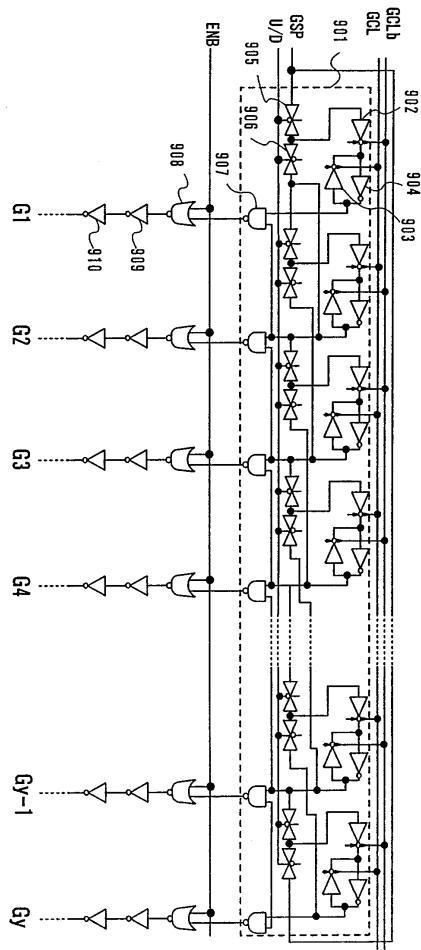

- [0091] 본 실시예는 본 발명의 디스플레이 디바이스의 게이트 신호 라인 구동 회로의 구조의 예를 도 9를 참조하여 설명한다.

- [0092] 게이트 신호 라인 구동 회로는 시프트 레지스터, 주사 방향 스위칭 회로 및 다른 구성요소들로 구성된다. 도면에는 도시되지 않았지만, 레벨 시프터(level shifter), 버퍼 등이 필요에 따라 추가될 수 있다.

- [0093] 시프트 레지스터는 시작 펄스(GSP), 클럭 펄스(GCL), 및 다른 것들을 수신하고 게이트 신호 라인 선택 신호를 출력한다.

- [0094] 901로 표시된 시프트 레지스터는, 클럭된 인버터들(902 및 903), 인버터(904), 및 NAND(907)로 구성된다. 시작

펄스(GSP)는 시프트 레지스터(901)로 입력되고, 클럭 펄스(GCL) 및 GCL의 극성을 변환하는 것에 의해 얻어지는 변환된 클럭 펄스(GSPb)는 클럭된 인버터들(902 및 903)을 도전적으로 및 비도전적으로 변환시킨다. 샘플링 펄스들이 따라서 NAND(907)로부터 순차적으로 출력된다.

[0095] 주사 방향 스위칭 회로는 스위치들(905 및 906)로 구성되고, 시프트 레지스터의 동작 방향을 도면에서 좌우측으로 스위치시킨다. 주사 방향 스위칭 신호(U/D)가 Lo신호일 때, 시프트 레지스터는 샘플링 펄스들을 도 9의 좌측에서 우측으로 순차적으로 출력한다. 이와 달리, 주사 방향 스위칭 신호(U/D)가 Hi 신호이면, 시프트 레지스터는 샘플링 펄스들을 도면의 우측에서 좌측으로 순차적으로 출력한다.

[0096] 시프트 레지스터로부터 출력된 샘플링 펄스들은 NOR(908)로 입력되고 인에이블 신호들(enable signal; ENB)과 계산된다. 이러한 계산의 목적은 둔해진 샘플링 펄스들에 의해 동시에 야기되는 근접 게이트 신호 라인들을 선택하는 에러를 회피하기 위한 것이다. NOR(908)로부터 출력된 신호들은 버퍼들(909 및 910)을 통해 게이트 신호 라인들(G1 내지 Gy)로 출력된다.

[0097] 시프트 레지스터들이 수신하는 시작 펄스(GSP), 클럭 펄스(GCL) 및 다른 것들이 외부 타이밍 제어기로부터 입력된다.

[0098] 본 발명의 디스플레이 디바이스는 본 실시예의 게이트 신호 라인 구동 회로 구조에 한정되지 않으며 임의의 알려진 게이트 신호 라인 구동 회로 구조를 자유롭게 사용할 수 있다. 본 실시예는 본 발명의 다른 실시예들과 조합될 수 있다.

[0099] [실시예 8]

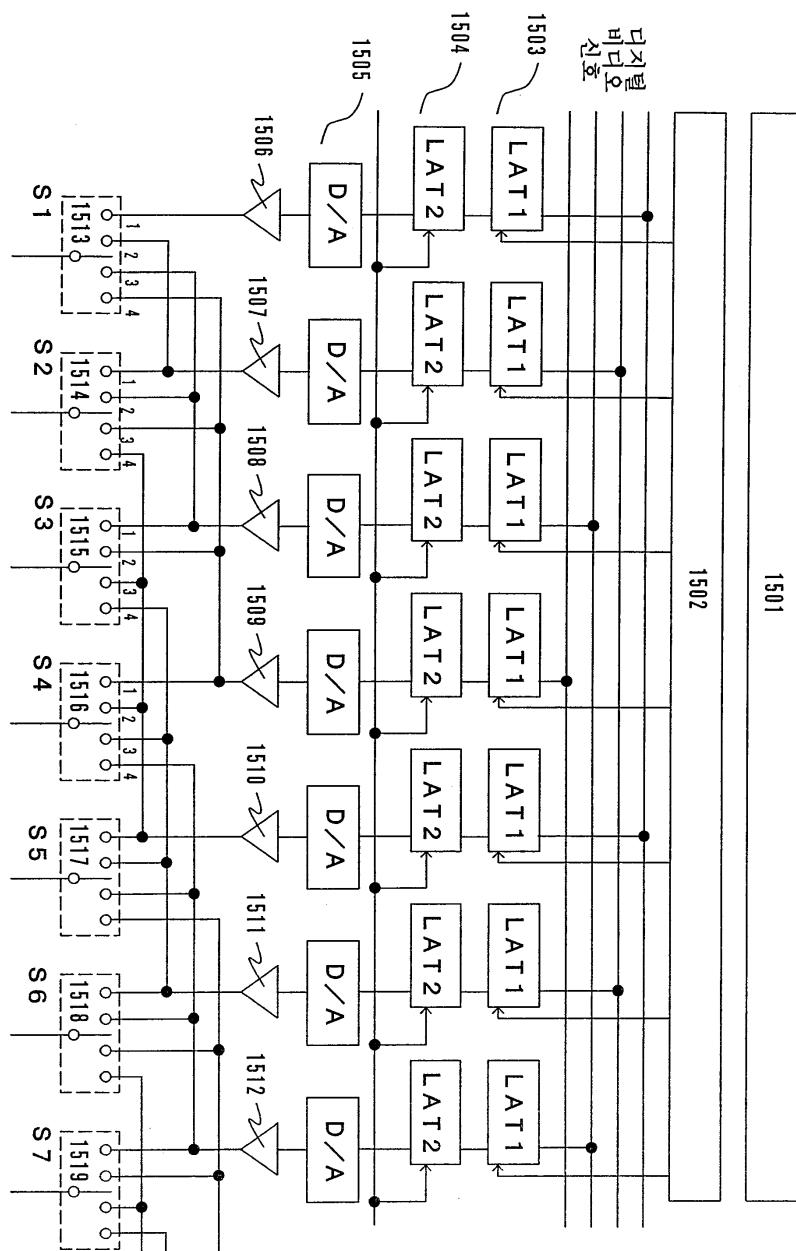

[0100] 도 15는 디지털 입력 소스 신호 라인 구동 회로의 예를 도시한다. 시프트 레지스터(1501)의 출력은 버퍼 회로(1502)를 통해 래치(latch) 회로(1503)로 입력된다. 래치 회로는 버퍼 회로의 출력이 활성화될 때 디지털 비디오 신호를 취하고 저장하는 기능을 갖는다. 하나의 라인 기간동안, 시프트 레지스터는 필요가 발생함에 따라 디지털 비디오 신호들을 취하고 디지털 데이터의 하나의 라인이 저장된다. 데이터의 하나의 라인 저장이 끝난 후에, 래치 펄스들은 귀선 기간에 입력되고 래치 회로(1503)의 데이터는 래치 회로(1504)로 보내진다.

[0101] 래치 회로(1504)의 데이터는 다음 귀선 기간까지 유지된다. 래치 회로(1504)에서 보관되는 동안, 데이터는 D/A 인버터(1505)에 의한 아날로그 변환을 수신한다. D/A 인버터의 출력은 아날로그 버퍼 회로(1506)와 스위치(1513)를 통해 소스 신호 라인들을 구동시키기 위해 사용된다.

[0102] 스위치 회로(1513)는 실시예 모드에서 스위치가 행하는 바와 동일한 방법으로 동작하며, 소스 신호 라인(S1)을 제 1 프레임에 아날로그 버퍼 회로(1506)와, 제 2 프레임에 아날로그 버퍼 회로(1507)와, 제 3 프레임에 아날로그 버퍼 회로(1508)와, 제 4 프레임에 아날로그 버퍼 회로(1509)로 연결한다. 이러한 방법으로, 아날로그 버퍼 회로들의 출력 변동은 실시예 모드에서와 같이 평균화된다. 따라서 디스플레이 비평탄성이 감소되고 화질이 개선된다. 이러한 실시예는 다른 실시예들과 조합될 수 있다.

[0103] [실시예 9]

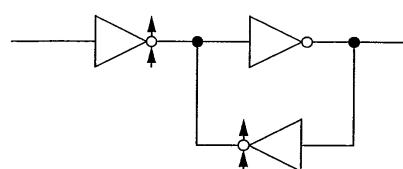

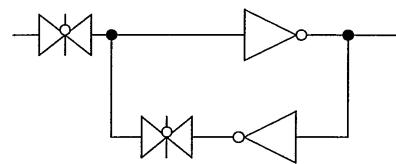

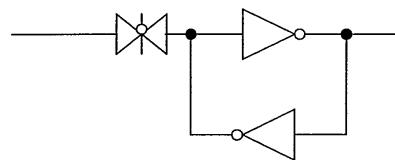

[0104] 도 16a 내지 16c는 실시예 8에 나타낸 래치 회로들의 특정한 예들을 도시한다. 도 16a의 래치 회로는 클럭된 인버터를 사용하고 이는 또한 위에서 설명된 신호 라인 구동 회로의 시프트 레지스터에 사용된다. 도 16b의 래치 회로는 인버터들과 아날로그 스위치들의 조합이다. 도 16c의 래치 회로는 도 16b로부터 하나의 아날로그 스위치를 제거함으로써 얻어진다. 도 16c의 두개의 인버터 회로들 중 출력이 아날로그 스위치에 연결된 하나는 아날로그 스위치보다 구동 성능이 낫도록 설계되고, 따라서 메모리 상태는 아날로그 스위치를 동작시키는 것에 의해 변화될 수 있다. 이러한 래치 회로들 중 임의의 것이 사용될 수 있다. 또한, 본원에 도시된 것들과 다른 회로들이 사용될 수도 있다. 이러한 실시예는 본 발명의 다른 실시예들과 조합될 수 있다.

[0105] [실시예 10]

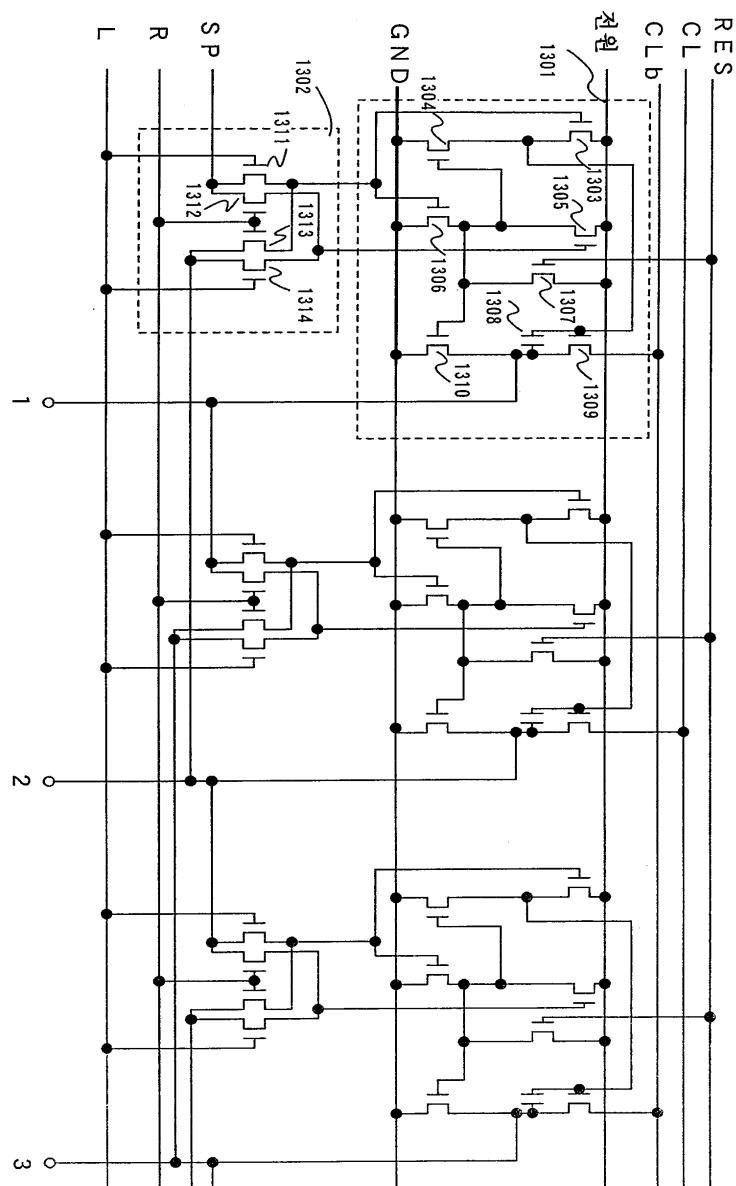

[0106] 도 13은 시프트 레지스터를 생성하기 위해 단극 TFT들을 사용하는 예를 도시한다. 도 13에 도시된 예는 n-채널 TFT들을 사용한다. 대신, 사용된 모든 TFT들은 p-채널 TFT들일 수 있다. 단극 프로세스의 사용은 마스크들의 개수를 감소시키는 것을 가능하게 한다.

[0107] 도 13에서, 시작 펄스가 주사 방향 스위칭 스위치(1302)로 입력되고, 스위칭 TFT(1311)를 통해 시프트 레지스터(1301)로 입력된다. 시프트 레지스터(1301)는 부트 스트랩(boot strap)을 사용하는 세트 리셋형 시프트 레지스

터이다. 시프트 레지스터(1301)의 동작이 이하에 설명될 것이다.

[0108] 시작 필스가 TFT(1303)의 게이트와 TFT(1306)의 게이트로 입력된다. TFT(1306)가 턴온되면, TFT(1304)의 게이트가 TFT(1304)를 턴오프하도록 Lo로 설정된다. TFT(1310)의 게이트가 또한 TFT(1310)를 턴오프하도록 Lo로 설정된다. TFT(1303)의 게이트의 전위는 전원 전위의 레벨로 상승된다. 따라서, TFT(1309)의 게이트의 전위가 전원 전위(-Vgs)의 레벨로 먼저 상승된다. 출력 1의 초기 전위가 Lo이므로, TFT(1309)는 출력 1 및 캐패시터(1308)가 변화하는 동안 소스 전위를 상승시킨다. TFT(1309)의 게이트가 전원 전위 -Vgs에 도달하면, TFT(1309)는 출력(1)이 전위에서 계속 상승하도록 여전히 온이다. TFT(1309)의 게이트는 전기 방전 경로를 갖지 않으며 따라서 전원 전위를 지나 그 소스를 따라 전위에서 계속 상승한다.

[0109] TFT(1309)의 드레인과 그의 소스가 동일한 전위에 도달함에 따라, 출력으로의 전류 흐름은 TFT(1309)의 전위에서의 상승을 정지시키기 위해 정지된다. 출력(1)은 따라서 전원 전위와 동일한 Hi 전위를 출력할 수 있다. 이 시점에서, CLb의 전위가 Hi로 설정된다. CLb가 Lo로 하강하면, 캐패시터(1308)의 전하들은 출력(1)을 Lo로 하강시키기 위해 TFT(1309)를 통해 CLb로 보내진다. 출력(1)의 필스들은 다음 단의 시프트 레지스터로 전송된다. 위는 실시예 10의 회로의 동작이다. 이러한 실시예는 본 발명의 다른 실시예들과 조합될 수 있다.

[0110] [실시예 11]

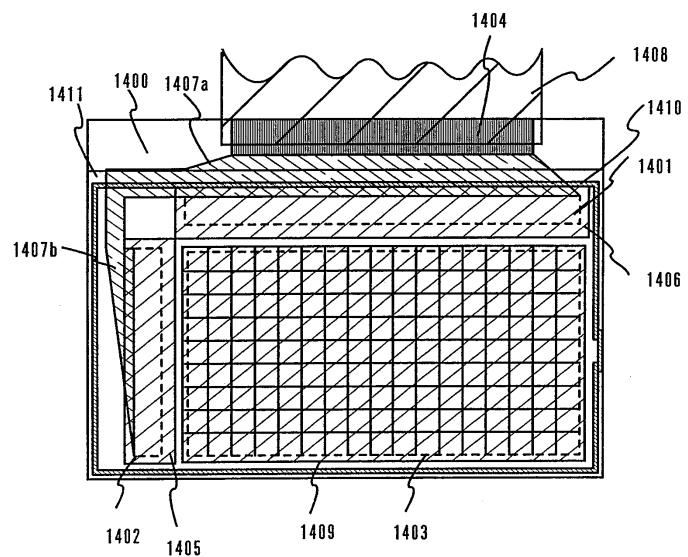

[0111] 도 14는 본 발명의 액정 디스플레이 디바이스의 평면도이다. 도 14에서, 액티브 매트릭스 기판은 픽셀부(1403), 소스 신호 라인 구동 회로(1401), 게이트 신호 라인 구동 회로(1402), FPC 단자(1408)가 접합되는 외부 입력 단자(1404), 외부 입력 단자를 각 회로의 입력부로 연결시키기 위한 배선들(1407a 및 1407b) 등을 갖는다. 액티브 매트릭스 기판은 컬러 필터 및 다른 구성요소들을 갖는, 두 기판들 사이에 삽입된 밀봉 부재(1410)를 갖는 반대 기판(1411)에 접합된다.

[0112] 광차폐층(1405)은 반대편 기판 측에 제공되어 소스 신호 라인 구동 회로(1401)를 오버랩한다. 광차폐층(1406)은 반대편 기판 쪽에 형성되어 게이트 신호 라인 구동 회로(1402)를 오버랩한다. 컬러 필터(1409)는 픽셀부(1403) 위의 반대편 기판 측 상에 제공되고, 광차폐층과 픽셀들의 컬러들에 적합하게 적색(R), 녹색(G), 및 청색(G)의 3개의 컬러들로 착색된 층들로 구성된다. 실제 디스플레이에서, 적색(R)으로 착색된 층, 녹색(G)으로 착색된 층, 및 청색(B)으로 착색된 층은 풀 컬러 이미지(full color image)를 형성한다. 3가지 컬러들로 착색된 층들은 임의로(arbitrarily) 배열될 수 있다.

[0113] 컬러 필터(1409)가 컬러 이미지를 얻기 위하여 여기서는 반대편 기판 상에 위치되지만, 특별한 제한은 없다. 컬러 필터는 액티브 매트릭스 기판의 제조동안 액티브 매트릭스 기판상에 형성될 수 있다.

[0114] 컬러 필터에서, 광차폐층은 광에 대하여 디스플레이 영역 이외의 부분들을 차폐하기 위하여 인접 픽셀들 사이에 제공된다. 구동 회로들을 덮는 영역들의 광차폐층들(1405 및 1406)은 생략될 수 있는데, 이는 액정 디스플레이 디바이스가 전자 장치에 디스플레이 유닛으로서 설치될 때 구동 회로들을 덮는 영역들이 덮여지기 때문이다. 대안적으로, 액티브 매트릭스 기판이 액티브 매트릭스 기판의 제조동안 광차폐층에 제공될 수 있다.

[0115] 상기 광차폐층들을 사용하지 않고 광에 대하여 디스플레이 영역(픽셀 전극들 사이의 캡들)과 구동 회로들 이외의 부분들을 차폐하는 것이 또한 가능하다. 이러한 경우에, 컬러 필터를 구성하는 복수의 착색된 층들이 적층되고 반대편 기판과 반대편 전극 사이에 적절히 배열되어 광에 대하여 이러한 영역들을 차폐한다.

[0116] 따라서 액정 디스플레이 디바이스가 완성된다. 이러한 실시예는 전달형 액티브 매트릭스 액정 디스플레이 디바이스의 제조 방법을 나타내지만 반사형 액티브 매트릭스 액정 디스플레이 디바이스가 유사한 방법으로 제조될 수 있다. 이러한 실시예는 본 발명의 다른 실시예들과 조합될 수 있다.

[0117] [실시예 12]

[0118] 위와 같이 제조된 액정 디스플레이 디바이스는 액정 모듈을 구성할 수 있고 다양한 전자 장치의 디스플레이 유닛으로서 사용될 수 있다. 이하에서 주어지는 것은 본 발명에 따라 제조된 액정 디스플레이 디바이스가 디스플레이 매체로서 통합되는 전자 장치에 대한 설명이다.

[0119] 이러한 전자 장치의 예들로는, 비디오 카메라들, 디지털 카메라들, 고글형 디스플레이들(헤드 장착형 디스플레이들), 네비게이션 시스템들, 오디오 재생 디바이스들(자동차 오디오들, 오디오 컴포넌트들, 등), 노트북형 개인용 컴퓨터들, 게임기들, 휴대 정보 단말들(이동 컴퓨터들, 이동 전화들, 이동형 게임기들, 및 전자책들, 등), 기록 매체를 갖는 이미지 재생 디바이스들(특히, 디지털 다기능 디스크(DVD) 등과 같은 기록 매체를 재생할 수 있고 이들의 이미지를 디스플레이할 수 있는 디스플레이 디바이스를 갖는 디바이스들), 등이 주어질 수 있다.

이들 전자 장치의 예들이 도 17에 도시된다.

[0120] 도 17a는 프레임(2001), 지지 기반(2002), 디스플레이부(2003), 스피커부(2004), 비디오 입력 단말(2005), 등으로 구성되는 디스플레이 디바이스이다. 본 발명에 따라 제조된 발광 디바이스는 디스플레이 디바이스의 제조에 디스플레이부(2003)로 사용된다. 발광 소자를 갖는 발광 디바이스가 자체-발광형(self-luminous type)이면 백라이트가 필요 없고, 이에 의해 액정 디스플레이 디바이스의 것보다 얇은 디스플레이부를 얻는 것이 가능하다. 디스플레이 디바이스라는 용어는 이를테면, 개인용 컴퓨터들을 위한, TV 방송 수신을 위한, 광고를 위한 정보를 디스플레이 하기 위한 모든 디스플레이 디바이스들을 포함한다는 것에 유의한다.

[0121] 도 17b는 본체(2101), 디스플레이부(2102), 이미지 수신부(2103), 조작 키들(2104), 외부 접속 포트(2105), 셔터(2106), 등으로 구성되는 디지털 스틸 카메라이다. 본 발명에 따라 제조된 발광 디바이스는 디지털 스틸 카메라의 제조에 디스플레이부(2102)로 사용된다.

[0122] 도 17c는 본체(2201), 프레임(2202), 디스플레이부(2203), 키보드(2204), 외부 접속 포트(2205), 포인팅 마우스(2206) 등으로 구성되는 노트북형 개인 컴퓨터이다. 본 발명에 따라 제조된 발광 디바이스는 노트북형 개인용 컴퓨터의 제조에 디스플레이부(2203)로 사용된다.

[0123] 도 17d는 본체(2301), 디스플레이부(2302), 스위치(2303), 조작키들(2304), 적외선 포트(2305), 등으로 구성되는 이동 컴퓨터이다. 본 발명에 따라 제조된 발광 디바이스는 이동 컴퓨터의 제조에 디스플레이부(2302)로 사용된다.

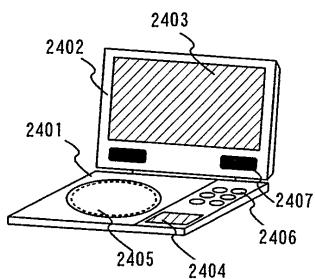

[0124] 도 17e는 본체(2401), 프레임(2402), 디스플레이부 A(2403), 디스플레이부 B(2404), 기록매체(DVD와 같은) 판독부(2405), 조작 키들(2406), 스피커부(2407) 등으로 구성되는 기록 매체(특히, DVD 재생 디바이스)가 제공된 휴대 이미지 재생 디바이스이다. 디스플레이부 A(2403)는 주로 이미지 정보를 디스플레이하고, 디스플레이부 B(2404)는 주로 문자 정보를 디스플레이하며, 본 발명에 따라 제조된 발광 디바이스는 휴대 이미지 재생 디바이스의 제조에 디스플레이부 A(2303) 및 디스플레이부 B(2404)로 사용될 수 있다. 기록 매체가 제공된 이미지 재생 디바이스들은 가정용의 게임기들 등을 포함한다는 것에 유의한다.

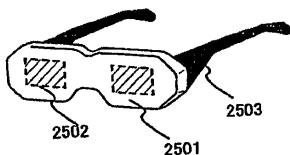

[0125] 도 17f는 본체(2501), 디스플레이부(2502), 암(arm; 2503) 등으로 구성되는 고글형 디스플레이(헤드 장착형 디스플레이)이다. 본 발명에 따라 제조된 발광 디바이스는 고글형 디스플레이의 제조에 디스플레이부(2502)로 사용된다.

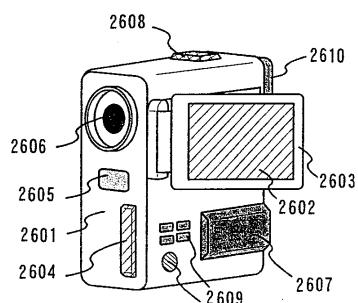

[0126] 도 17g는 본체(2601), 디스플레이부(2602), 프레임(2603), 외부 접속 포트(2604), 원격 제어 수신부(2605), 이미지 수신부(2606), 뒷데리(2607), 오디오 입력부(2608), 조작키들(2609), 접안렌즈부(2610), 등으로 구성되는 비디오 카메라이다. 본 발명에 따라 제조된 발광 디바이스는 비디오 카메라의 제조에 디스플레이부(2602)로 사용된다.

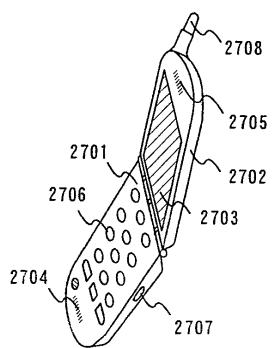

[0127] 도 17h는 본체(2701), 프레임(2702), 디스플레이부(2703), 오디오 입력부(2704), 오디오 출력부(2705), 조작키들(2706), 외부 접속 포트(2707), 안테나(2708) 등으로 구성되는 이동 전화이다. 본 발명에 따라 제조된 발광 디바이스는 이동 전화의 제조에 디스플레이부(2703)로 사용된다. 흑색의 배경 상에 백색의 문자들을 디스플레이 함으로써, 디스플레이부(2703)는 이동 전화의 전력 소비를 억제할 수 있음에 유의한다.

[0128] 위에서 설명된 바와 같이, 본 발명의 제조 방법에 따라 제조된 발광 디바이스의 응용 범위는 매우 넓어서 본 발명의 발광 디바이스는 전자 장치의 임의의 분야에서 사용될 수 있다. 또한 본 실시예의 전자 장치는 실시예들 1 내지 4를 조합하는 것에 의해 형성된 임의의 조합으로 이루어질 수 있다.

[0129] 출력들을 위해 아날로그 베퍼 회로들을 사용하는 종래의 액정 디스플레이 디바이스들은 아날로그 베퍼 회로들의 변동으로 인한 수직의 줄무늬들과 이미지 품질이 보다 낮다는 문제점을 가진다.

[0130] 본 발명에 따라, 아날로그 베퍼 회로들의 출력들은 출력 전압 변동을 평균화 시키기 위하여 하나에서 다른 하나로 주기적으로 스위칭되고 출력에서의 변동이 따라서 감소된다.

### 발명의 효과

[0131] 절연 기판 상에 형성된 아날로그 베퍼 회로들이 출력에서 변화되어도 수직의 줄무늬들이 스크린 상에 디스플레이되는 것으로부터 방지된다.

## 도면의 간단한 설명

- [0001] 도 1은 본 발명의 액정 디스플레이 디바이스의 소스 신호 라인 구동 회로의 블럭도.

- [0002] 도 2는 종래의 액정 디스플레이 디바이스의 소스 신호 라인 구동 회로의 블럭도.

- [0003] 도 3은 액정 디스플레이 디바이스의 팩셀부의 구조를 도시하는 도면.

- [0004] 도 4는 종래의 액정 디스플레이 디바이스의 소스 신호 라인 구동 회로의 블럭도.

- [0005] 도 5는 연산 증폭기형 아날로그 버퍼의 회로도.

- [0006] 도 6은 소스 팔로어형 아날로그 버퍼(source follower type analog buffer)의 회로도.

- [0007] 도 7은 본 발명의 스위치의 회로도.

- [0008] 도 8은 본 발명의 스위치의 타이밍도.

- [0009] 도 9는 본 발명의 게이트 신호 라인 구동 회로의 회로도.

- [0010] 도 10은 소스 신호 라인과 각각 연결된 아날로그 버퍼 회로들의 출력을 도시하는 도면.

- [0011] 도 11은 본 발명의 액정 디스플레이 디바이스의 비디오 신호 스위칭을 도시하는 도면.

- [0012] 도 12는 본 발명의 액정 디스플레이 디바이스의 비디오 신호 스위칭을 도시하는 도면.

- [0013] 도 13은 단극 트랜지스터들을 사용하는 시프트 레지스터(shift register)의 회로도.

- [0014] 도 14는 본 발명의 액정 디스플레이 디바이스의 외부 도면.

- [0015] 도 15는 본 발명이 적용되는 디지털 소스 신호 라인 구동 회로의 블럭도.

- [0016] 도 16a 내지 16c는 디지털 소스 신호 라인 구동 회로의 래치 회로들(latch circuits)의 회로도들.

- [0017] 도 17a 내지 17h는 본 발명의 액정 디스플레이 디바이스를 사용하는 전자 장치의 도면들.

- [0018] \*도면의 주요 부분에 대한 부호의 설명\*

- |                       |                 |

|-----------------------|-----------------|

| [0019] 123:스위치        | 601:버퍼 TFT      |

| [0020] 602:전류 소스      | 1131:아날로그 버퍼 회로 |

| [0021] 1150:비디오 회로    | 1138:스위치        |

| [0022] 1145:비디오 신호 라인 |                 |

도면

도면1

## 도면2

종래기술

## 도면3

## 도면4

종래기술

도면5

도면6

도면7

도면8

### 도면9

## 도면10

## 도면11

## 도면12

도면13

도면14

도면15

도면16a

도면16b

도면16c

도면17a

도면17b

도면17c

도면17d

도면17e

도면17f

도면17g

도면17h

|                |                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和液晶显示装置的驱动方法                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">KR100991111B1</a>                                                                                                        | 公开(公告)日 | 2010-11-02 |

| 申请号            | KR1020030061153                                                                                                                      | 申请日     | 2003-09-02 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所<br>夏普株式会社                                                                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦<br>夏普株式会社                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦<br>夏普株式会社                                                                                                         |         |            |

| [标]发明人         | KOYAMA JUN<br>코야마준<br>KIMURA HAJIME<br>키무라하지메<br>SHIONOIRI YUTAKA<br>시오노 이리유타카<br>HIRAYAMA YASUHIRO<br>히라야마야수히로<br>LEE BUYEOL<br>이부열 |         |            |

| 发明人            | 코야마준<br>키무라하지메<br>시오노 이리유타카<br>히라야마야수히로<br>이부열                                                                                       |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F G02F1/133                                                                                                     |         |            |

| CPC分类号         | G09G3/3677 G09G2310/027 G09G3/2011 G09G2320/0233 G09G2310/0297 G09G3/3688 G09G2310/0283                                              |         |            |

| 代理人(译)         | 李 , 何炳<br>李昌勋                                                                                                                        |         |            |

| 优先权            | 2002257209 2002-09-02 JP                                                                                                             |         |            |

| 其他公开文献         | KR1020040020845A                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                            |         |            |

**摘要(译)**

提供一种具有模拟缓冲电路并具有降低的亮度变化的液晶显示装置。源信号线驱动电路具有多个模拟缓冲电路。源信号耦合到模拟缓冲电路每次新的周期开始时，这些线路都会将它们的连接切换到其他模拟缓冲电路。因此，模拟缓冲电路中的输出变化被平均，并且可以在屏幕上显示均匀的图像有。