## (19) 대한민국특허청(KR)

## (12) 공개특허공보(A)

(51) Int. Cl.<sup>7</sup>G09G 3/36

(11) 공개번호 특2001-0015252

(43) 공개일자 2001년02월26일

(21) 출원번호 10-2000-0039126

(22) 출원일자 2000년07월08일

(30) 우선권주장 1999-196212 1999년07월09일 일본(JP)

(71) 출원인 가부시키가이샤 히타치세이사쿠쇼 가나이 쓰토무

일본 도쿄도 치요다구 간다스루가다이 4쪽에 6반지히타치 디바이스엔지니어링 가부시키가이샤 나시모토 류오조

일본국 치바켄 모바라시 하야노 3681

(72) 발명자 이또우시게루

일본지바肯모바라시시모나가요시460

가따오까노보루

일본지바肯산부궁오오아미시라사또마찌미즈호다이3쪽에29반지39

오구라아끼라

일본지바肯쵸세이궁나가라마찌하리가야1179

(74) 대리인 장수길, 구영창

**심사청구 : 있음****(54) 액정 표시 장치****요약**

액정 표시 소자에 표시되는 표시 화면의 표시 품질을 향상시킴과 동시에, 고속 동작을 가능하게 하고, 액정 표시 소자의 대화면화를 가능하게 하는 액정 표시 장치를 제공한다.

액정 표시 소자와, 적어도 1개의 반도체 집적 회로 장치로 구성되며, 상기 액정 표시 소자의 각 영상 신호선에 표시 데이터에 대응하는 계조 전압을 공급하는 영상 신호선 구동 수단을 포함하는 액정 표시 장치로서, 상기 반도체 집적 회로 장치는, 복수의 계조 전압 중에서 입력되는 표시 데이터에 대응하는 계조 전압을 선택하는 복수의 계조 전압 선택 수단과, 상기 각 계조 전압 선택 수단에서 선택된 계조 전압을 증폭하여 각 영상 신호선으로 출력하는 복수의 앰프 회로와, 상기 각 계조 전압 선택 수단과 상기 각 앰프 회로 사이에 설치되는 프리차지 컨트롤 회로를 포함한다.

**대표도****도7****색인어**

액정 표시 소자, 계조 전압, 프라자아지, 대화면화, 영상 신호

**영세서****도면의 간단한 설명**

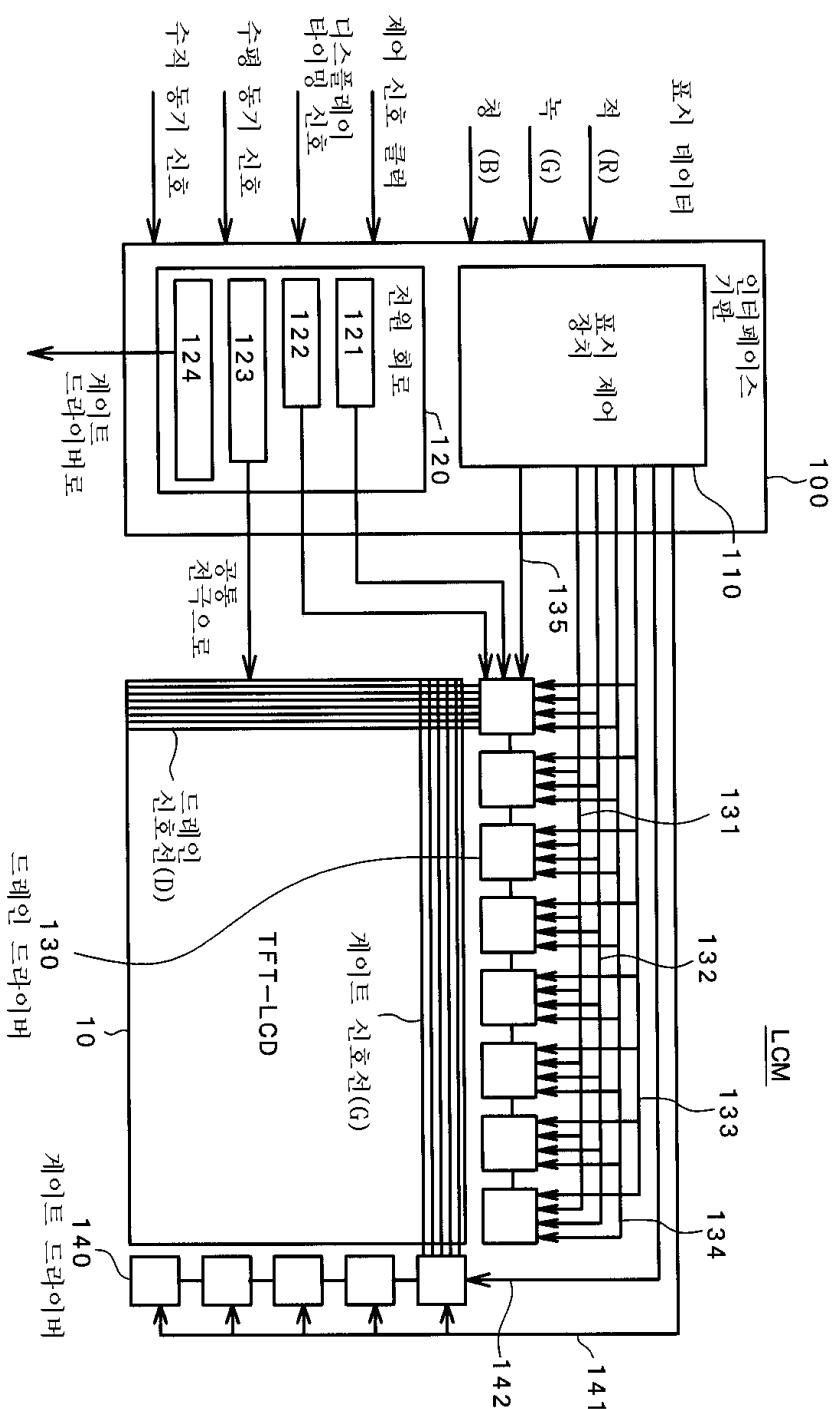

도 1은 본 발명이 적용되는 TFT 방식의 액정 표시 장치의 개략 구성을 나타내는 블록도.

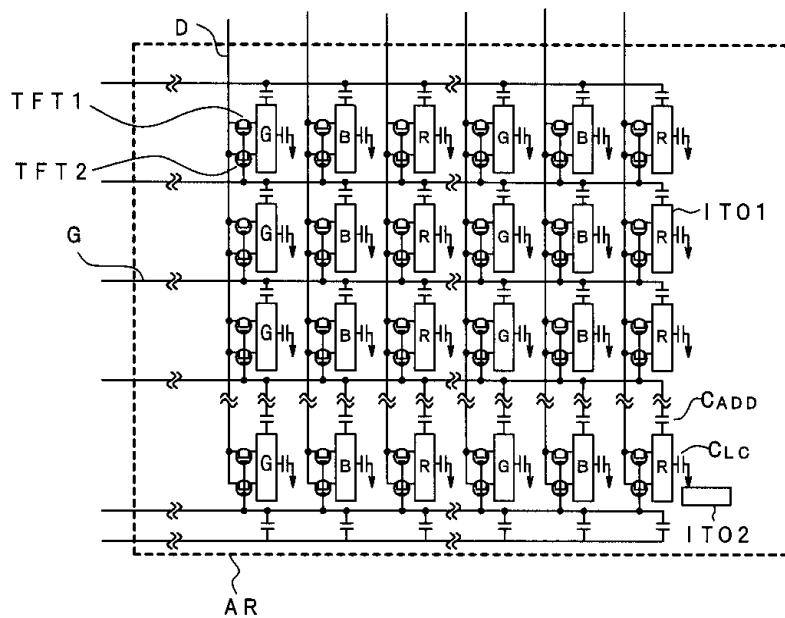

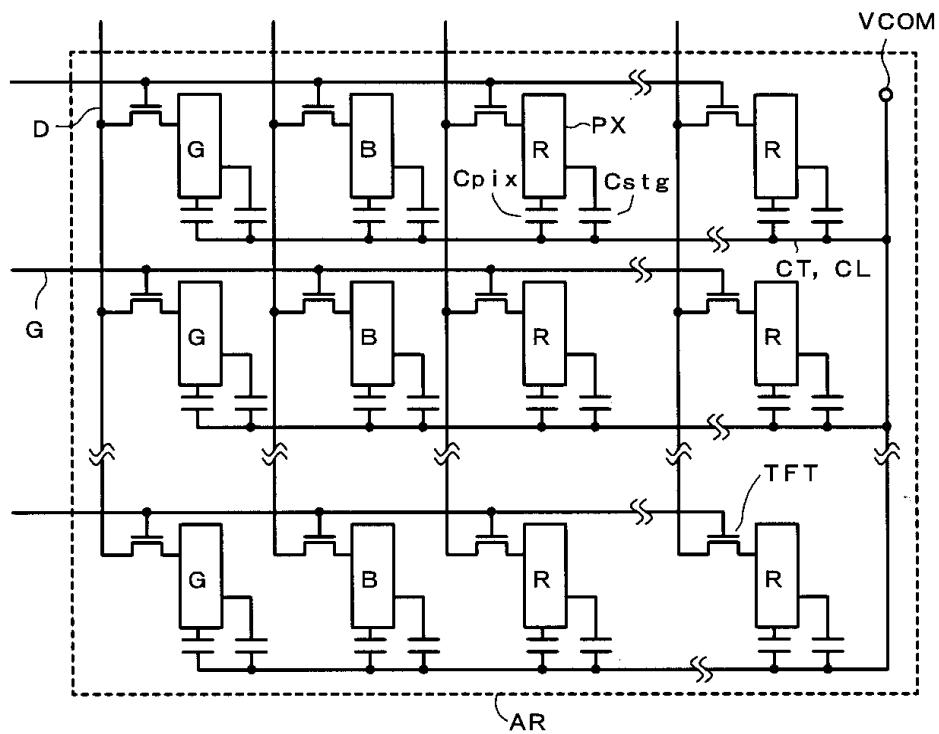

도 2는 도 1에 도시한 액정 표시 패널의 일례의 등가 회로를 나타내는 도면.

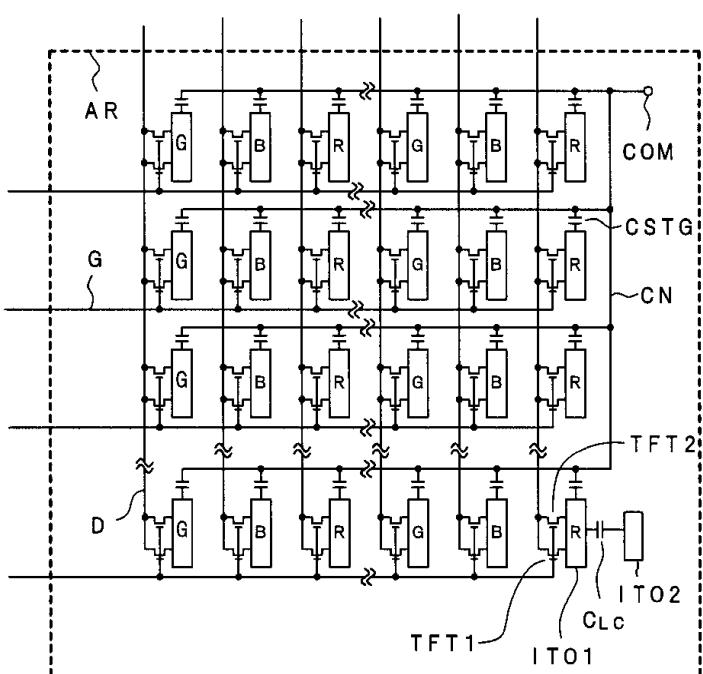

도 3은 도 1에 도시한 액정 표시 패널의 다른 예의 등가 회로를 나타내는 도면.

도 4는 액정 표시 장치의 구동 방법으로서, 도트 반전법을 사용한 경우에 드레인 드라이버로부터 드레인 신호선(D)으로 출력되는 액정 구동 전압의 극성을 설명하기 위한 도면.

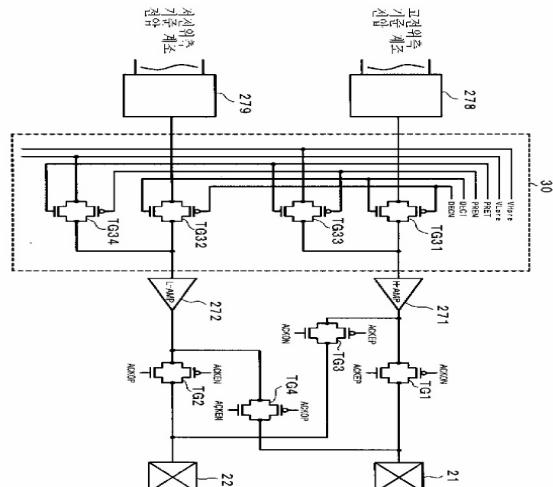

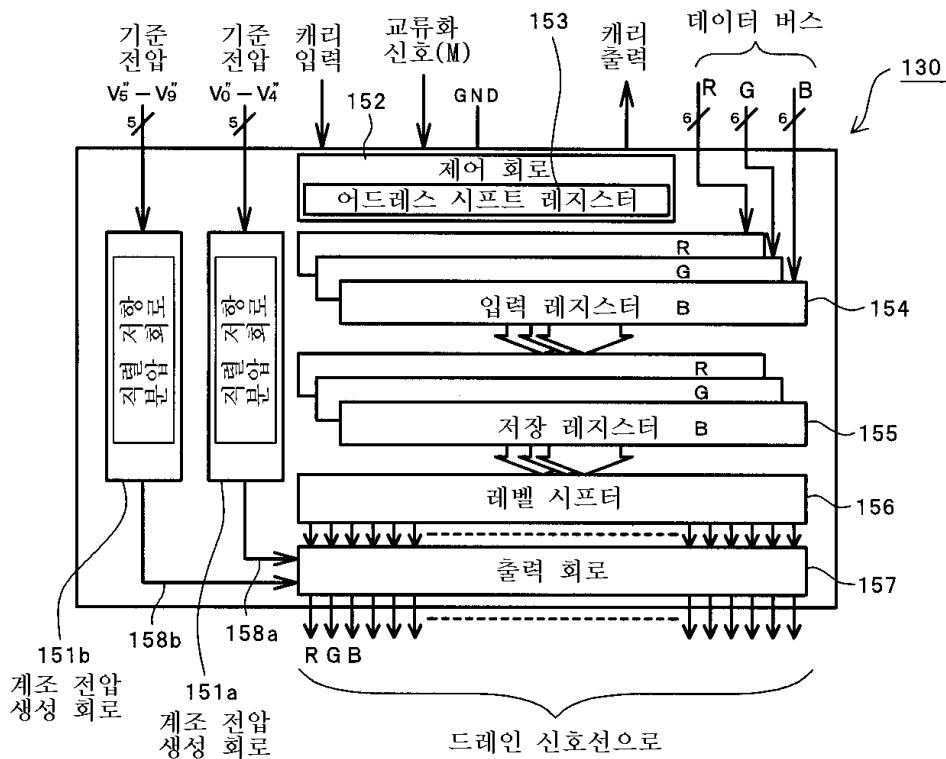

도 5는 도 1에 도시한 드레인 드라이버의 일례의 개략 구성을 나타내는 블록도.

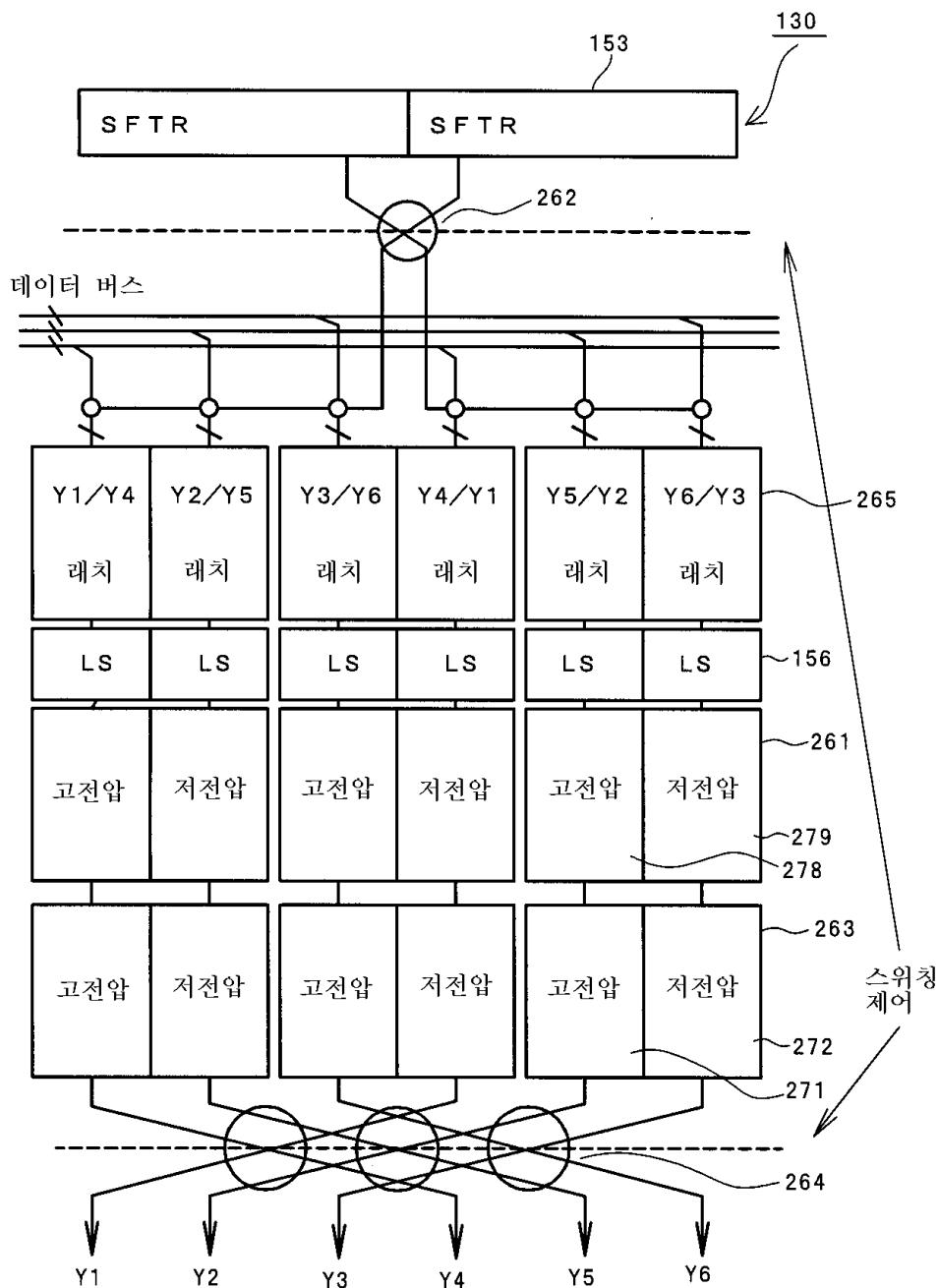

도 6은 출력 회로의 구성을 중심으로 도 5에 도시한 드레인 드라이버의 구성을 설명하기 위한 블록도.

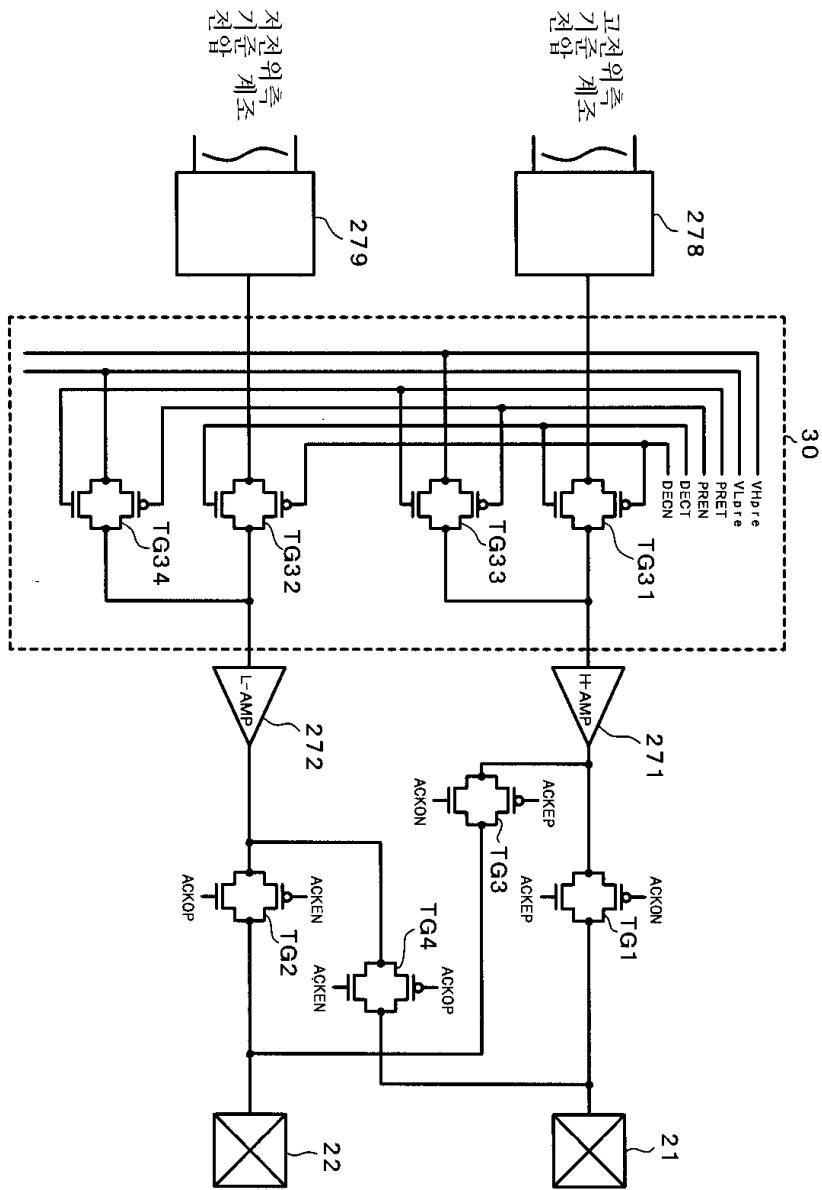

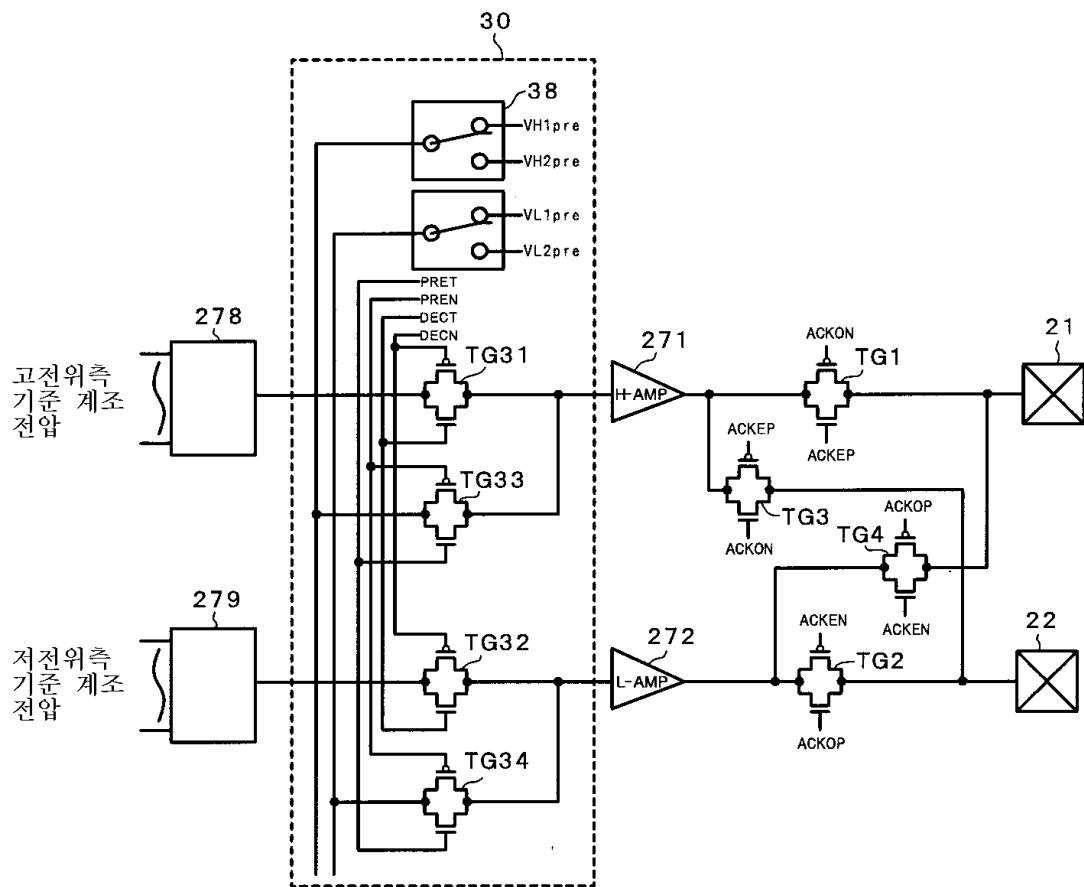

도 7은 본 실시예의 액정 표시 장치의 드레인 드라이버의 개략 구성을 나타내는 도면.

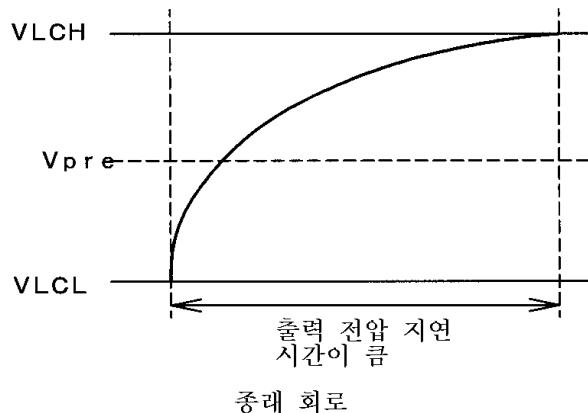

도 8은 도 1에 도시한 액정 표시 장치의 드레인 드라이버의 출력 지연 시간(tDD) 특성을 설명하기 위한 도면.

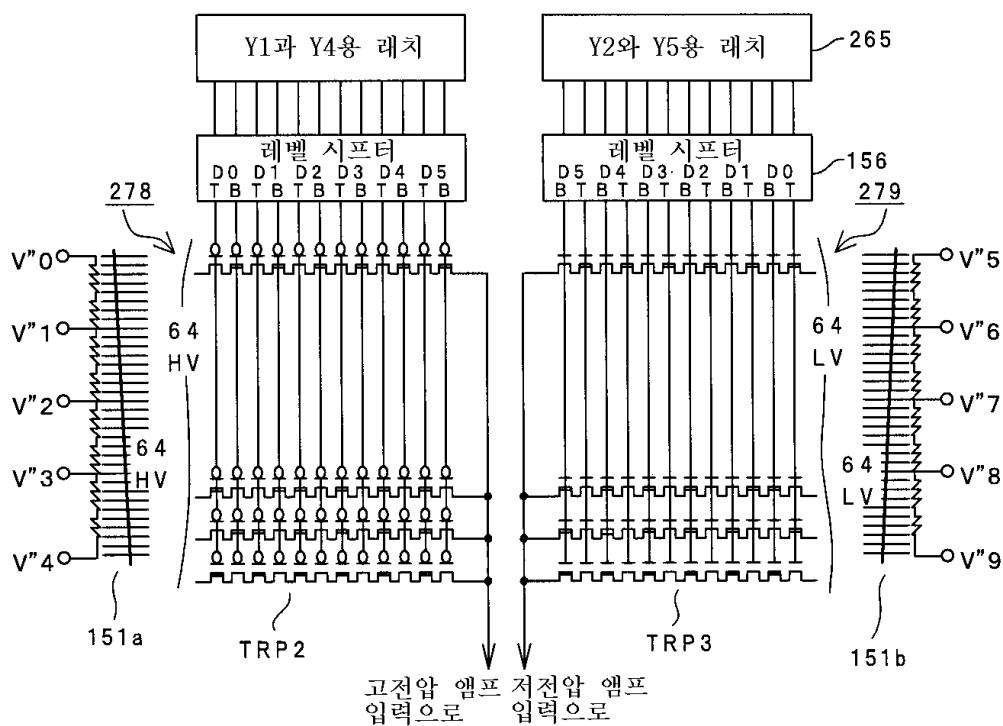

도 9는 도 6에 도시한 고전압용 디코더 회로 및 저전압용 디코더 회로의 일례의 개략 구성을 나타내는 도면.

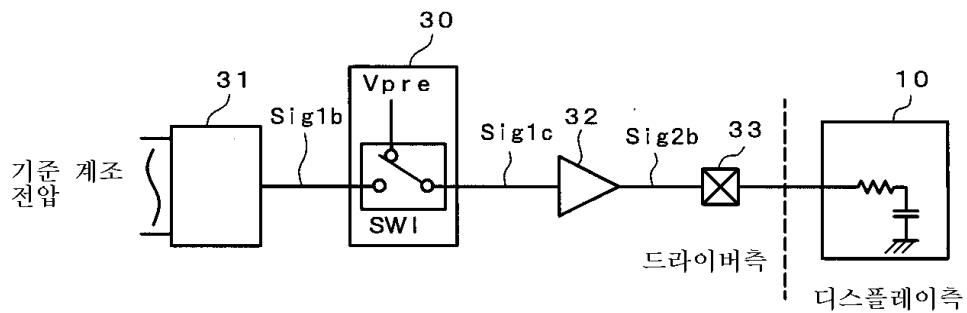

도 10은 본 발명의 실시예의 액정 표시 장치의 드레인 드라이버의 출력 지연 시간( $t_{DD}$ ) 특성을 설명하기 위한 도면.

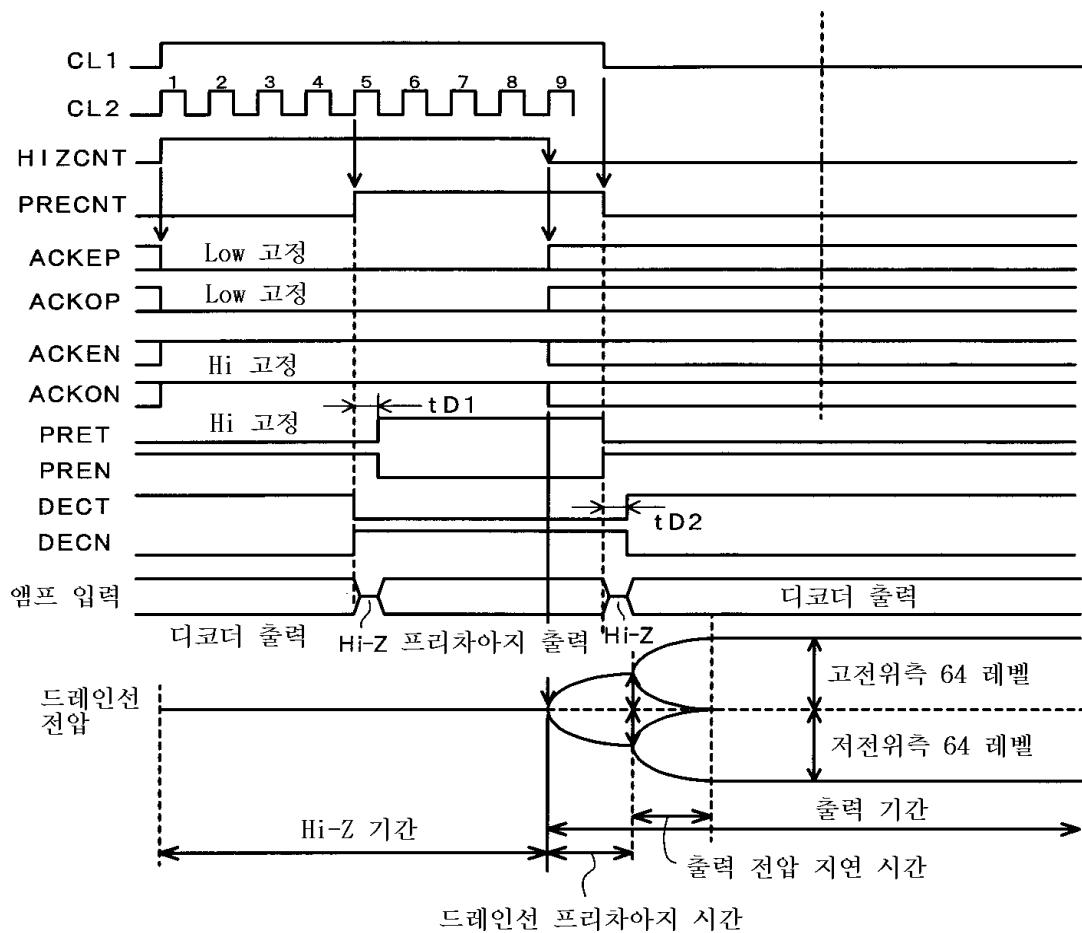

도 11은 도 7에 도시한 프리차아지 회로의 동작을 설명하기 위한 타이밍차트의 일례.

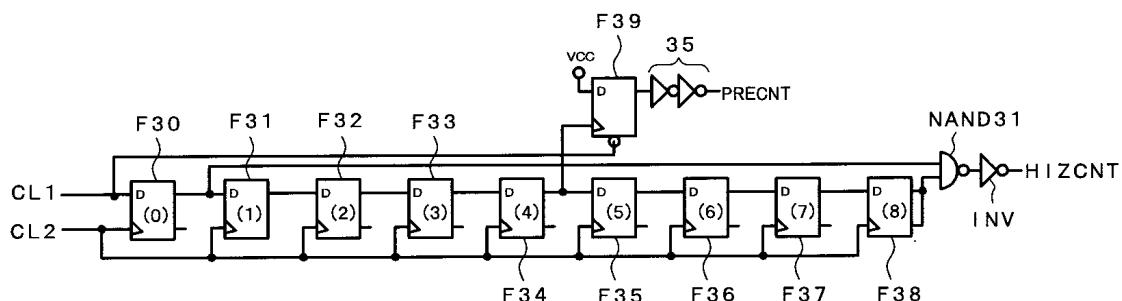

도 12는 도 11에 도시한 제어 신호(HIZCNT) 및 제어 신호(PRECNT)를 생성하기 위한 회로 구성의 일례를 나타내는 도면.

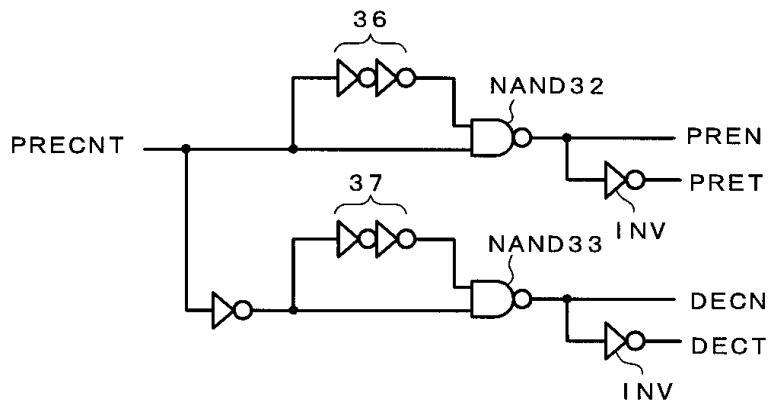

도 13은 도 11에 도시한 제어 신호(PRET, PREN, DECT, DECN)을 생성하기 위한 회로 구성의 일례를 나타내는 도면.

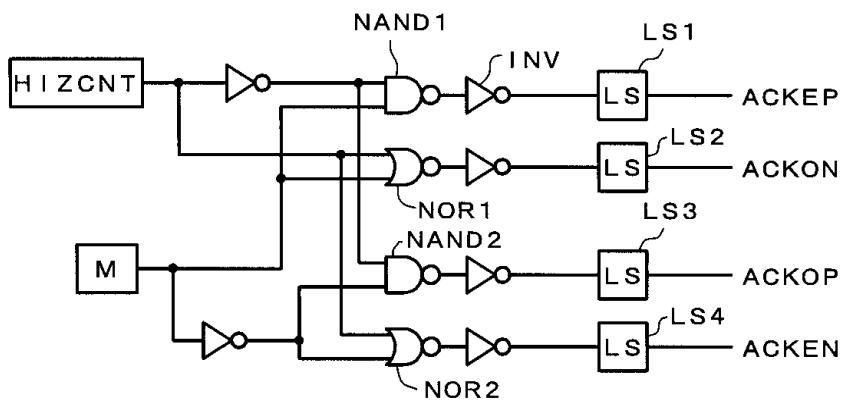

도 14는 도 11에 도시한 제어 신호(ACKEP, ACKOP, ACKEN, ACKON)를 생성하기 위한 회로 구성의 일례를 나타내는 도면.

도 15는 본 발명의 실시예의 액정 표시 장치의 다른 예의 개략 구성을 나타내는 도면.

도 16은 한개의 드레인 신호선(D)에 있어서, 드레인 드라이버의 근접 부분과 드레인 드라이버로부터 가장 먼 원격 부분에서의 프리차아지 기간 내의 전위 변동을 설명하기 위한 그래프.

도 17은 도 6에 도시한 고전압용 앰프 회로, 및 저전압용 앰프 회로로서 사용되는 전압 풀로워 회로를 나타내는 회로도.

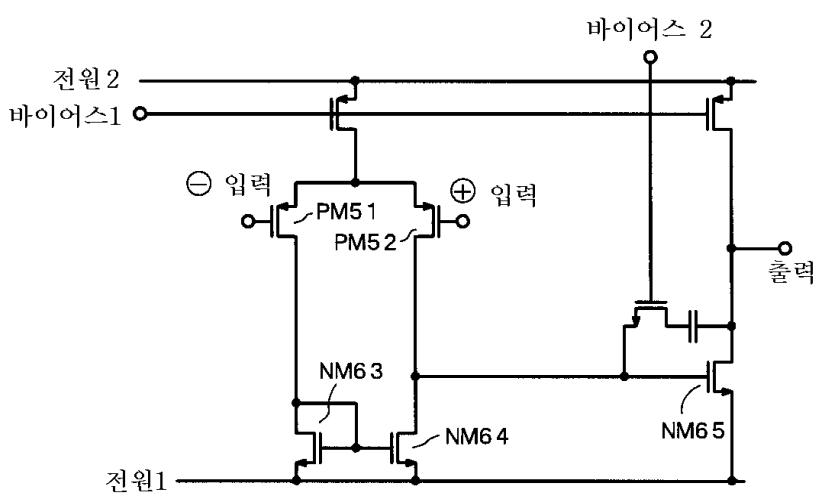

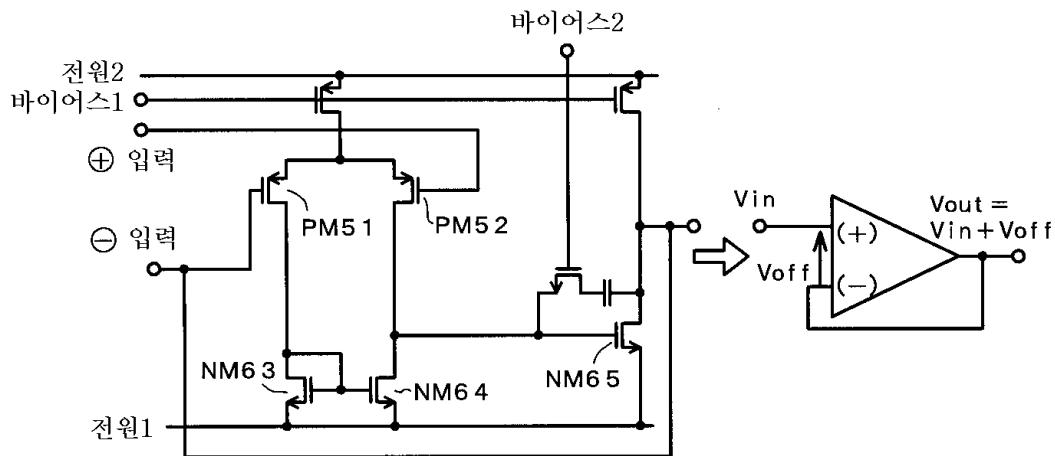

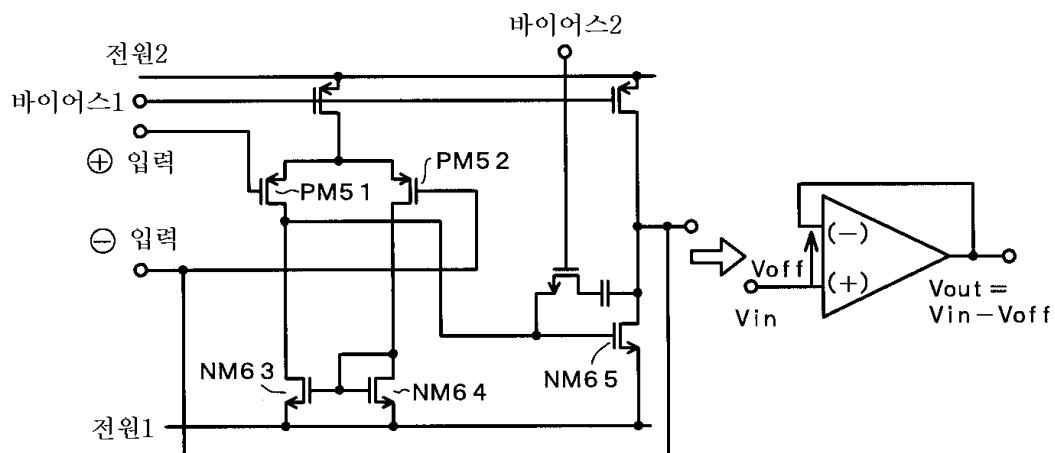

도 18은 도 6에 도시한 저전압용 앰프 회로에 사용되는 연산 증폭기를 구성하는 차동 증폭 회로의 일례를 나타내는 회로도.

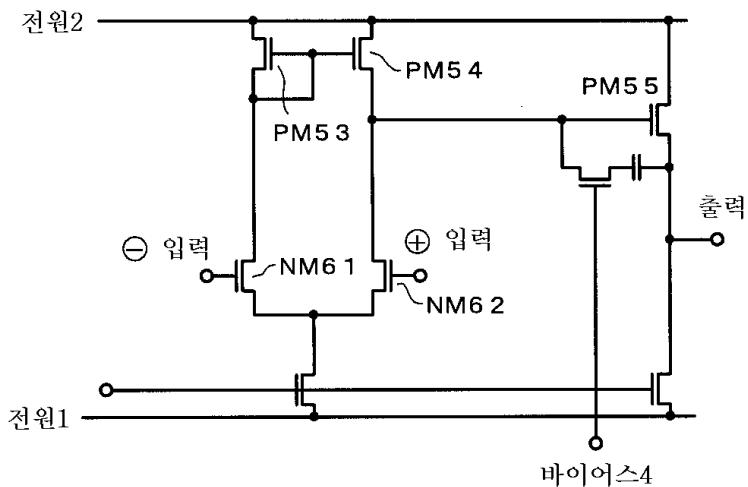

도 19는 도 6에 도시한 고전압용 앰프 회로에 사용되는 연산 증폭기를 구성하는 차동 증폭 회로의 일례를 나타내는 회로도.

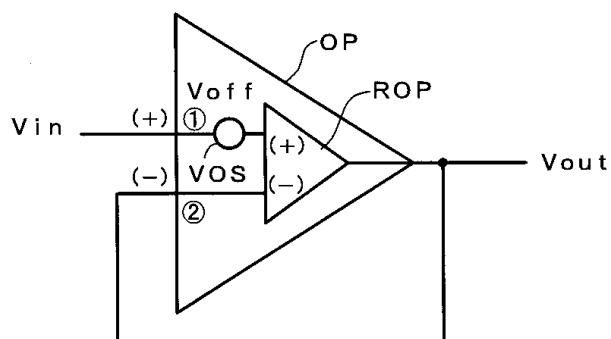

도 20은 오프셋 전압( $V_{off}$ )을 고려한 연산 증폭기의 등가 회로를 나타내는 도면.

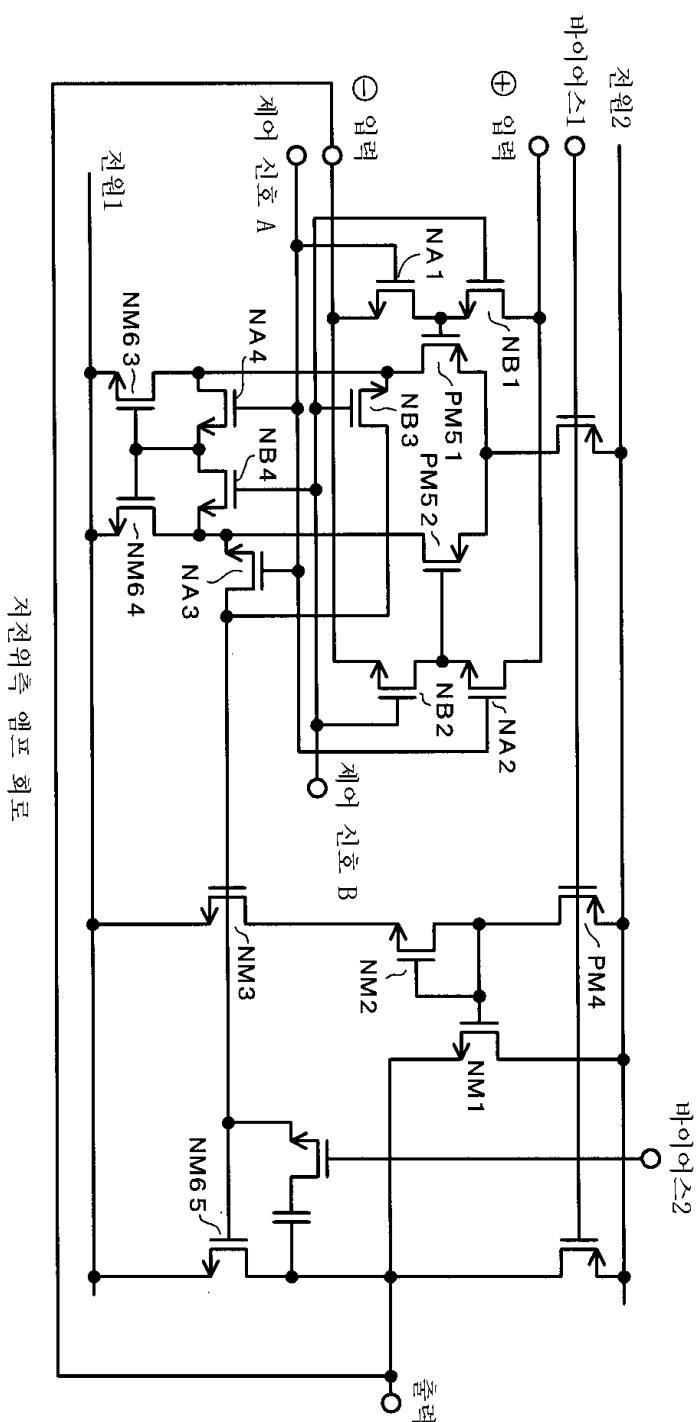

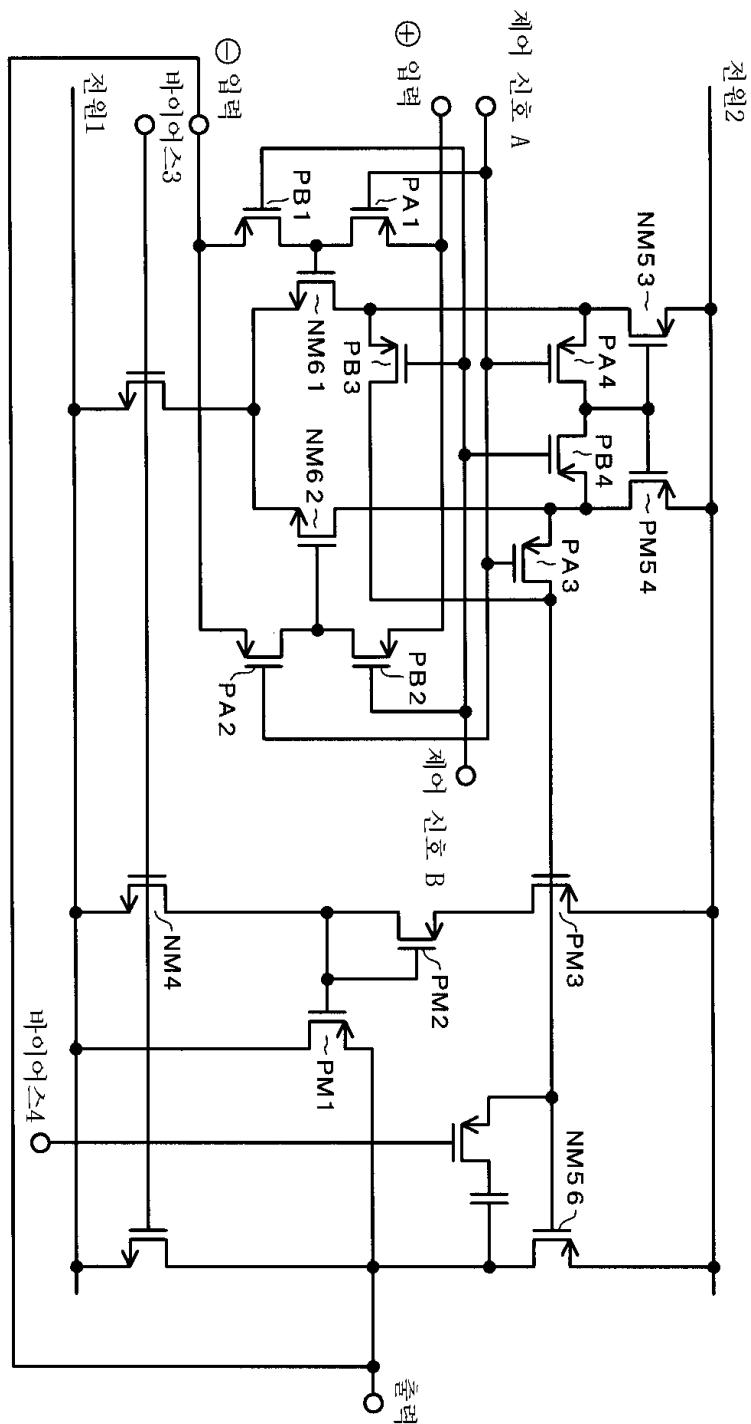

도 21은 본 실시예 1의 저전압용 앰프 회로의 회로 구성을 나타내는 회로도.

도 22는 본 실시예 1의 고전압용 앰프 회로의 회로 구성을 나타내는 회로도.

도 23은 본 실시예 1의 저전압용 앰프 회로에 있어서, 제어 신호(A)가 H 레벨인 경우의 회로 구성을 나타내는 회로도.

도 24는 본 실시예 1의 저전압용 앰프 회로에 있어서, 제어 신호(B)가 H 레벨인 경우의 회로 구성을 나타내는 회로도.

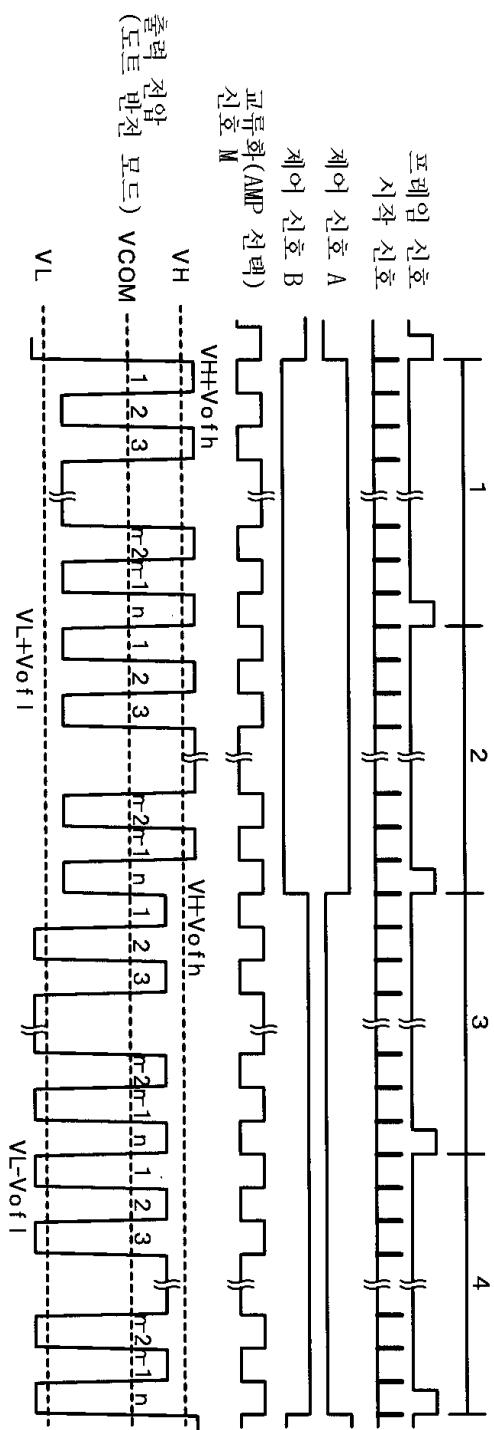

도 25는 본 실시예 1의 드레인 드라이버의 동작을 설명하기 위한 타이밍차트.

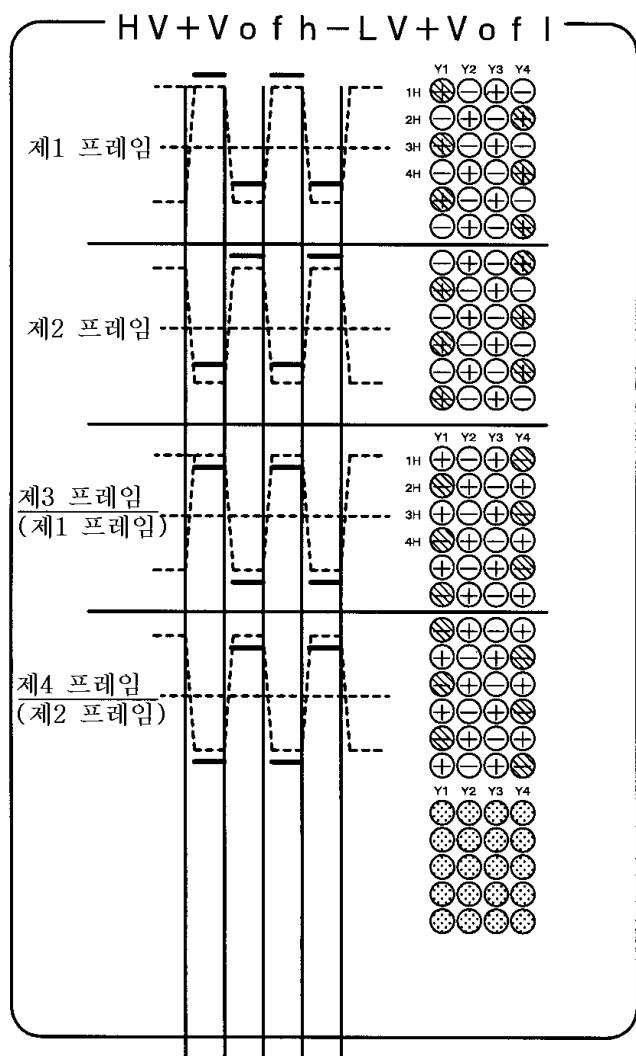

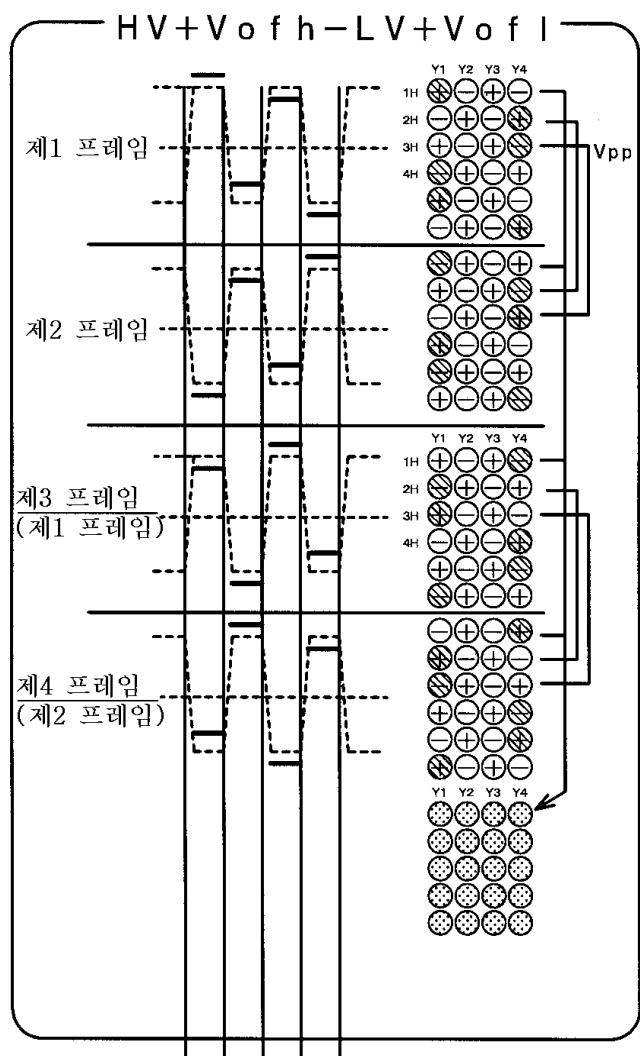

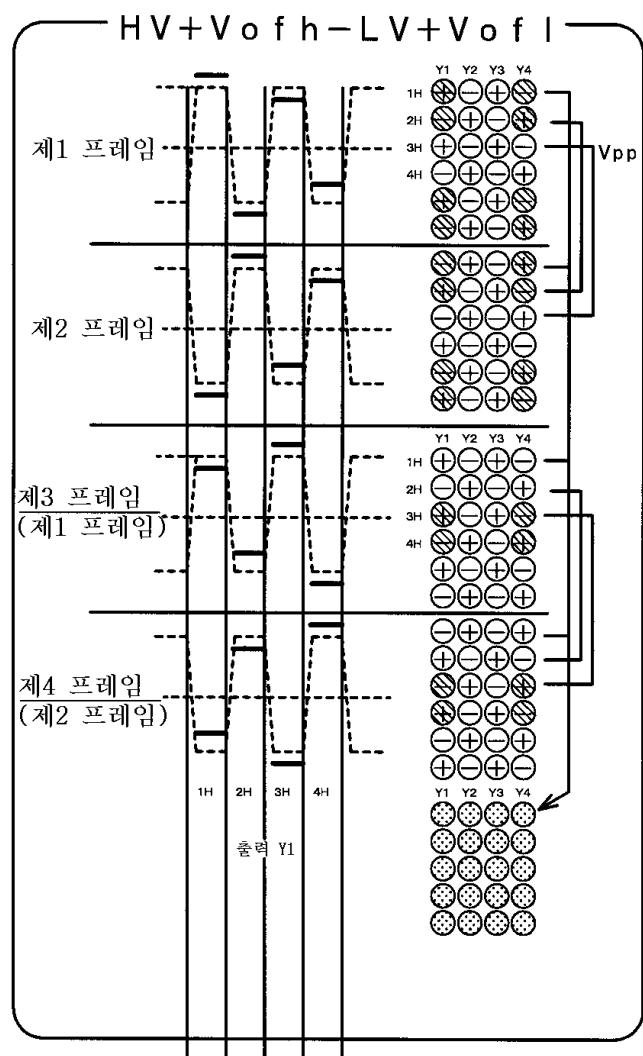

도 26은 본 실시예 1에 있어서, 오프셋 전압 ( $V_{off}$ )에 의해 액정 표시 패널에 생기는 세로 줄무늬가 눈에 띠지 않게 되는 이유를 설명하기 위한 도면.

도 27은 본 실시예 1에 있어서, 오프셋 전압( $V_{off}$ )에 의해 액정 표시 패널에 생기는 세로 줄무늬가 눈에 띠지 않게 되는 이유를 설명하기 위한 도면.

도 28은 본 실시예 1에 있어서, 오프셋 전압( $V_{off}$ )에 의해 액정 표시 패널에 생기는 세로 줄무늬가 눈에 띠지 않게 되는 이유를 설명하기 위한 도면.

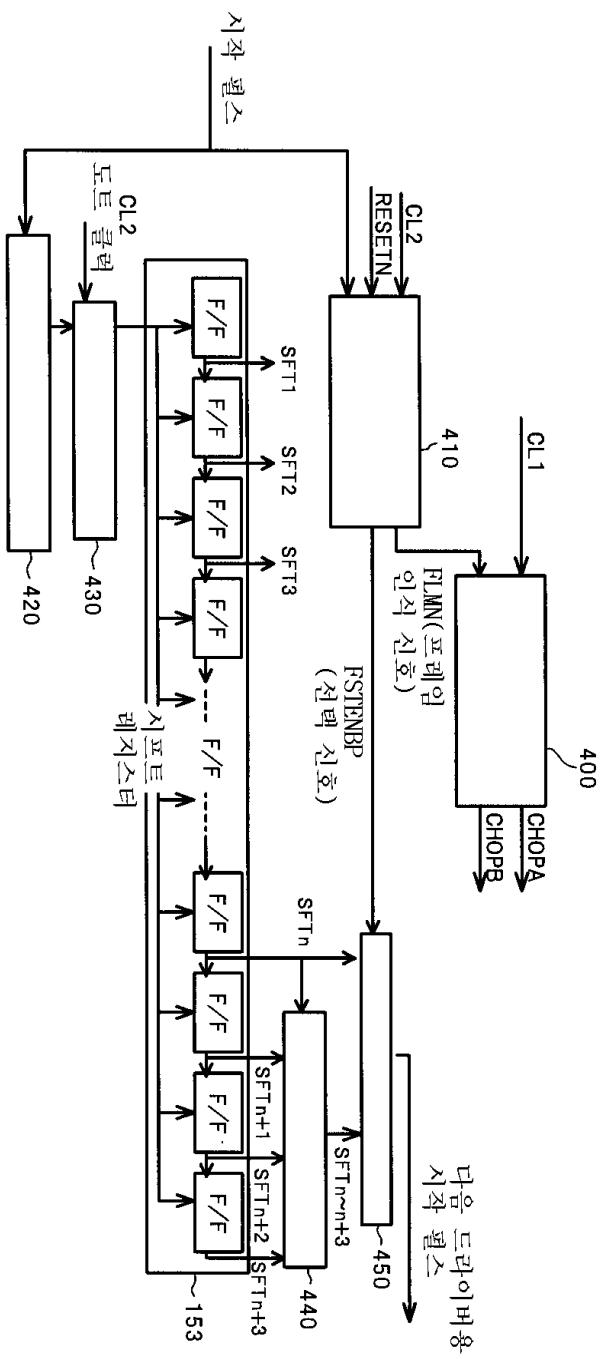

도 29는 본 실시예 1의 드레인 드라이버 내의 제어 회로의 주요부 회로 구성을 나타내는 블록도.

도 30은 도 29에 도시한 제어 신호 생성 회로의 회로 구성을 나타내는 회로도.

도 31은 도 30에 도시한 제어 신호 생성 회로의 동작을 설명하기 위한 타이밍차트.

도 32는 도 29에 도시한 프레임 인식 신호 생성 회로의 회로 구성을 나타내는 회로도.

도 33은 도 32에 도시한 프레임 인식 신호 생성 회로의 동작을 설명하기 위한 타이밍차트.

도 34는 본 실시예 1의 제어 회로의 동작을 설명하기 위한 타이밍차트.

도 35는 도 29에 도시한 클럭 생성 회로의 일례를 나타내는 회로도.

도 36은 본 발명의 실시예의 앤프 회로의 변형예를 나타내는 회로도.

도 37은 본 발명의 실시예의 앤프 회로의 변형예를 나타내는 회로도.

도 38은 횡전계 방식의 액정 표시 패널의 등가 회로를 나타내는 도면.

〈도면의 주요 부분에 대한 부호의 설명〉

10 : 액정 표시 패널(TFT-LCD)

21, 22, 33 : 출력 패드

30 : 프리차아지 컨트롤 회로

31, 278, 279 : 디코더 회로

32 : 앤프 회로

35, 36, 37, 403 : 인버터 회로군

38 : 프리차아지 전압 선택 스위치

100 : 인터페이스부

110 : 표시 제어 장치

120 : 전원 회로

121, 122 : 전압 생성 회로

123 : 공통 전극 전압 생성 회로

124 : 게이트 전극 전압 생성 회로

130 : 드레인 드라이버

131, 132, 134, 135, 141, 142 : 신호선

133 : 표시 데이터 버스 라인

140 : 게이트 드라이버

151a, 151b : 계조 전압 생성 회로

152 : 제어 회로

153 : 시프트 레지스터 회로

154 : 입력 레지스터 회로

155 : 저장 레지스터 회로

156 : 레벨 시프트 회로

157 : 출력 회로

158a, 158b : 전압 버스 라인

261 : 디코더부

262, 264 : 스위치부

263 : 앰프 회로쌍

265 : 데이터 래치부

271 : 고전압용 앰프 회로

272 : 저전압용 앰프 회로

400 : 제어 신호 생성 회로

401 : PORN 신호 생성 회로

402 : 분압 회로

410 : 프레임 인식 신호 생성 회로

420 : 시프트 클럭 인에이블 신호 생성 회로

430 : 시프트용 클럭 생성 회로

440 : 펄스 생성 회로

450: 펄스 선택 회로

D : 드레인 신호선(영상 신호선 또는 수직 신호선)

G : 게이트 신호선(주사 신호선 또는 수평 신호선)

IT01, CX : 화소 전극

IT02 : 공통 전극

CT : 대향 전극

CL : 대향 전극 신호선

TFT : 박막 트랜지스터

CLC, Cp1x : 액정 용량

CSTG : 보유 용량

CADD : 부가 용량

Cstg : 축적 용량

PM, PA, PB : PMOS 트랜지스터

NM, NA, NB : NMOS 트랜지스터

TG : 트랜스퍼 게이트 회로

LS : 레벨 시프트 회로

TRP : 트랜지스터 열

NAND : NAND 회로

AND : AND 회로

NOR : NOR 회로

INV : 인버터

OP : 연산 증폭기

F : 플립플롭 회로

EXOR : 배타적 논리합 회로

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시 장치에 관한 것으로, 특히, 다계조 표시가 가능한 액정 표시 장치의 영상 신호선 구동 수단(드레인 드라이버)에 적용하기에 유익한 기술에 관한 것이다.

화소마다 능동 소자(예를 들면, 박막 트랜지스터)를 가지고, 이 능동 소자를 스위칭 구동하는 액티브 매트릭스형 액정 표시 장치는, 노트북 컴퓨터 등의 표시 장치로서 널리 사용되고 있다.

이 액티브 매트릭스형 액정 표시 장치는 능동 소자를 통해 화소 전극에 영상 신호 전압(표시 데이터에 대응하는 계조 전압; 이하, 계조 전압이라 칭한다)을 인가하기 때문에, 각 화소 사이의 크로스토크가 없고, 단순 매트릭스형 액정 표시 장치와 같이 크로스토크를 방지하기 위한 특수한 구동 방법을 이용할 필요가 없이, 다계조 표시가 가능하다.

이 액티브 매트릭스형 액정 표시 장치의 하나로, TFT(Thin Film Transistor, 박막 트랜지스터)방식의 액정 표시 패널(TFT-LCD)과, 액정 표시 패널의 상측에 배치되는 드레인 드라이버와, 액정 표시 패널의 측면에 배치되는 게이트 드라이버 및 인터페이스부를 구비하는 TFT 방식의 액정 표시 장치가 알려져 있다.

이 TFT 방식의 액정 표시 장치에서는, 드레인 드라이버 내에 계조 전압 생성 회로와, 이 계조 전압 생성 회로에서 생성된 복수의 계조 전압 중에서 표시 데이터에 대응하는 1개의 계조 전압을 선택하는 계조 전압 선택 회로(디코더 회로)와, 계조 전압 선택 회로에서 선택된 1개의 계조 전압이 입력되는 앰프 회로를 포함하고 있다.

또, 이러한 기술은, 예를 들면, 특원평8-86668호에 기재되어 있다.

#### 발명이 이루고자 하는 기술적 과제

최근, TFT 방식의 액정 표시 모듈 등의 액정 표시 장치에 있어서는, 액정 표시 패널의 대화면화의 요구에 따라, 액정 표시 패널의 해상도로서, XGA 표시 모드의  $1024 \times 768$  화소, SXGA 표시 모드의  $1280 \times 1024$  화소, UXGA 표시 모드의  $1600 \times 1200$  화소와 한층 더 고해상도화가 요구되고 있다.

이 때문에, 1 수직 주사 기간 내의 수평 주사수가 증가하고, 그에 따라 1수평 주사당의 기록 시간은 점점 짧게 되어, 드레인 드라이버의 출력 지연 시간( $t_{DD}$ )이 큰 문제로 되고 있다.

예를 들면, XGA 표시 모드에서는, 1수평 주사당 기록 시간이  $20\mu s$  정도이지만, 드레인 드라이버의 출력 지연 시간( $t_{DD}$ )이  $10 \sim 20\mu s$ 에 도달하는 경우도 있다.

이러한 경우에는, 화소 기입 전압이 부족하고, 액정 표시 패널에 표시되는 표시 화면의 표시 품질이 현저히 열화된다.

한편, 액정 표시 장치에 있어서는, 액정 표시 패널의 대형화, 고해상도화(다화소화)하는 경향이고, 또한, 쓸모 없는 스페이스를 없애고 표시 장치로서의 미관을 좋게 하기 위해, 액정 표시 장치의 표시 영역 이외의 영역, 즉 테두리 부분을 조금이라도 작게 하는(협액면화: 狹額緣化) 것이 요망되고 있다.

그 때문에, 드레인 드라이버를 구성하는 반도체 칩의 칩 사이즈를 보다 축소할 필요가 있고, 그에 따라, 상기 계조 전압 선택 회로는 최소 사이즈의 전계 효과형 트랜지스터(MOS 트랜지스터)로 구성되도록 되어 있다.

그 결과, 상기 계조 전압 선택 회로의 전류 구동 능력이 낮게 되어, 상기 계조 전압 선택 회로에서 표시 데이터에 대응하는 계조 전압이 확정되기까지의 시간(출력 지연 시간)이 길어지고, 이것이 상기한 드레인 드라이버의 출력 지연 시간( $t_{DD}$ )의 큰 요인으로 되고 있다.

또한, 액정 표시 장치에 있어서는, 64계조 표시에서 256계조 표시로 보다 다계조 표시가 계속 진척되고, 상기 계조 전압 생성 회로에서 생성되는 복수의 계조 전압의 1계조당 전압폭(즉, 인접하는 계조 전압 사이의 전위차)이 작아지고 있다.

한편, 앰프 회로는 앰프 회로를 구성하는 능동 소자의 특성의 변동에 의해 오프셋 전압이 생기지만, 상기 앰프 회로에 오프셋 전압이 생기면, 상기 앰프 회로의 출력 전압에 오차가 생겨 상기 앰프 회로의 출력 전압은 목표

치(정규의 계조 전압)와 다른 전압으로 된다.

이에 따라, 액정 표시 패널에 표시되는 표시 화면 중에 흑 또는 백의 세로 줄무늬가 발생하여 표시 품질을 현저히 손상시킨다는 문제점이 있었다.

본 발명은 상기 종래 기술의 문제점을 해결하기 위해 이루어진 것으로, 본 발명의 목적은 액정 표시 장치에서 액정 표시 소자에 표시되는 표시 화면의 표시 품질을 향상시키는 것을 가능케하는 기술을 제공하는 것이다.

본 발명의 다른 목적은 액정 표시 장치에서 고속 동작을 가능케 하여 액정 표시 소자의 대화면화를 가능케하는 기술을 제공하는 것이다.

본 발명의 상기 목적과 신규 특징은 본 명세서의 개시내용 및 첨부 도면에 의해 명백하게 될 것이다.

본원에서 개시되는 발명 중 대표적인 것의 개요를 간단히 설명하면 이하와 같다.

즉, 본 발명은 매트릭스형으로 설치되는 복수의 화소와 상기 복수의 화소 중의 열(또는 행) 방향의 각 화소에 표시 데이터에 대응하는 계조 전압을 인가하는 복수의 영상 신호선을 갖는 액정 표시 소자와, 적어도 1개의 반도체 집적 회로 장치로 구성되고 상기 각 영상 신호선에 표시 데이터에 대응하는 계조 전압을 공급하는 영상 신호선 구동 수단을 포함하는 액정 표시 장치로서, 상기 반도체 집적 회로 장치는, 복수의 계조 전압 중에서 입력되는 표시 데이터에 대응하는 계조 전압을 선택함과 함께 상기 반도체 집적 회로 장치 중 최소 사이즈의 트랜지스터로 구성되는 복수의 계조 전압 선택 수단과; 상기 각 계조 전압 선택 수단에서 선택된 계조 전압을 증폭하여 각 영상 신호선으로 출력하는 복수의 앰프 회로와; 상기 각 계조 전압 선택 수단과 상기 각 앰프 회로와의 사이에 설치되는 제1 스위칭 수단과; 소정의 충전 전압이 공급되는 전원선과 상기 각 앰프 회로와의 사이에 설치되는 제2 스위칭 수단과; 1 수평 주사 기간의 처음의 소정 기간 내에 상기 제1 스위칭 수단을 오프로 하고, 또한 상기 제2 스위칭 수단을 온으로 하는 스위칭 제어 수단;을 갖는 것을 특징으로 한다.

또한, 본 발명은, 매트릭스형으로 설치되는 복수의 화소와 상기 복수의 화소 중 열(또는 행) 방향의 각 화소에 표시 데이터에 대응하는 계조 전압을 인가하는 복수의 영상 신호선을 갖는 액정 표시 소자와, 적어도 1개의 반도체 집적 회로 장치로 구성되고 상기 각 영상 신호선에 표시 데이터에 대응하는 계조 전압을 공급하는 영상 신호선 구동 수단을 포함하는 액정 표시 장치로서, 상기 반도체 집적 회로 장치는, 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택함과 함께 상기 반도체 집적 회로 장치 중에서 최소 사이즈의 트랜지스터로 구성되는 복수의 계조 전압 선택 수단과; 상기 각 계조 전압 선택 수단에서 선택된 계조 전압을 증폭하여 각 영상 신호선으로 출력하는 복수의 앰프 회로로서, 상기 각 앰프 회로가 한쌍의 입력 단자 중 한쪽을 반전 입력 단자 혹은 비반전 입력 단자에, 한쌍의 입력 단자 중의 다른쪽을 비반전 입력 단자 혹은 반전 입력 단자로 절환하는 절환 수단을 갖는 복수의 앰프 회로와; 상기 각 계조 전압 선택 수단과 상기 각 앰프 회로와의 사이에 설치되는 제1 스위칭 수단과; 소정의 충전 전압이 공급되는 전원선과 상기 각 앰프 회로와의 사이에 설치되는 제2 스위칭 수단과; 1 수평 주사 기간의 처음의 소정 기간 내에 상기 제1 스위칭 수단을 오프로 하고, 또한 상기 제2 스위칭 수단을 온으로 하는 스위칭 제어 수단과; 상기 앰프 회로의 한쌍의 입력 단자 중 한쪽을 반전 입력 단자로, 다른쪽을 비반전 입력 단자로, 또는 상기 앰프 회로의 한쌍의 입력 단자 중 한쪽을 비반전 입력 단자로, 다른쪽을 반전 입력 단자로 절환하게 하는 절환 제어 신호를 소정의 주기마다 상기 앰프 회로의 절환 수단에 대해 출력하는 절환 지시 수단;을 포함하는 것을 특징으로 한다.

또한, 본 발명은, 상기 스위칭 제어 수단이 상기 제2 스위칭 수단을 온으로 하기 전에 상기 제1 스위칭 수단을 오프로 하고, 또한 상기 제2 스위칭 수단을 오프로 한 후에 상기 제1 스위칭 수단을 온으로 하는 것을 특징으로 한다.

또한, 본 발명은, 상기 스위칭 제어 수단이 출력 타이밍 제어용 클럭 및 표시 데이터 래치용 클럭에 기초하여 상기 제1 및 제2 스위칭 수단을 제어하는 것을 특징으로 한다.

또한, 본 발명은, 상기 소정의 충전 전압이 상기 복수의 계조 전압 중 어느 하나의 전압인 것을 특징으로 한다.

또한, 본 발명은, 상기 반도체 집적 회로 장치는 외부로부터 공급되는 복수의 계조 기준 전압에 기초하여 복수의 계조 전압을 생성하고, 상기 각 계조 전압 선택 수단에 공급하는 계조 전압 생성 수단을 가지고, 상기 소정의 충전 전압이 상기 외부로부터 공급되는 복수의 계조 기준 전압 중 어느 하나의 전압인 것을 특징으로 한다.

또한, 본 발명은, 상기 복수의 화소의 액정층의 한쪽에 인가되는 상기 복수의 계조 전압 중에서 상기 복수의 화소의 액정층의 다른쪽에 인가되는 대향 전압에 대해 가장 전위차가 큰 계조 전압을 최대 계조 전압, 상기 대향 전압에 대해 가장 전위차가 작은 계조 전압을 최소 계조 전압으로 할 때, 상기 소정의 충전 전압은 상기 최대 계조 전압과 최소 계조 전압과의 사이의 중간 전압보다도 상기 최대 계조 전압쪽에 가까운 전압인 것을 특징으로 한다.

또한, 본 발명은, 상기 복수의 앰프 회로가 한쌍이 정극성의 계조 전압을 출력하는 제1 앰프 회로와 부극성의 계조 전압을 출력하는 제2 앰프 회로로 구성되는 여러쌍의 앰프 회로쌍으로 구성되며, 상기 각 앰프 회로쌍의 제1 앰프 회로와 접속되는 계조 전압 선택 수단은 정극성의 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하고, 또한, 상기 각 앰프 회로쌍의 제2 앰프 회로와 접속되는 계조 전압 선택 수단은 부극성의 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하고, 또한, 상기 각 앰프 회로쌍의 제1 앰프 회로와 접속되는 계조 전압 선택 수단 및 상기 각 앰프 회로쌍의 제2 앰프 회로와 접속되는 계조 전압 선택 수단에 입력될 임의의 한쌍의 표시 데이터를 교대로 절환하는 표시 데이터 절환 수단과, 상기 각 앰프 회로쌍으로부터 출력되는 한쌍의 계조 전압을 상기 표시 데이터 절환 수단에서의 절환에 따라 교대로 절환하여 임의의 한쌍의 영상 신호선으로 출력하는 영상 신호선 절환 수단을 포함하는 것을 특징으로 한다.

### 발명의 구성 및 작용

이하, 본 발명 실시예를 도면을 참조하여 설명한다.

또, 발명의 실시예를 설명하기 위한 전 도면에 있어서, 동일 기능을 갖는 것에는 동일 부호를 붙이고, 그 반복

설명은 생략한다.

### [실시예 1]

#### <본 발명이 적용되는 표시 장치의 기본 구성>

도 1은, 본 발명이 적용되는 TFT 방식의 액정 표시 장치(액정 표시 모듈)의 개략 구성을 나타내는 블록도이다.

도 1에 도시한 액정 표시 장치(LCM)는, 액정 표시 패널(TFT-LCD: 10)의 상측에 드레인 드라이버(130)가 배치되고, 또한, 액정 표시 패널(10)의 측면에 게이트 드라이버(140), 인터페이스부(100)가 배치된다.

인터페이스부(100)는 인터페이스 기판에 실장되고, 또한, 드레인 드라이버(130), 게이트 드라이버(140)도 각각 전용의 TCP(Tape Carrier Package) 또는 직접 액정 표시 패널에 실장된다.

#### <도 1에 도시한 액정 표시 패널(10)의 구성>

도 2는 도 1에 도시한 액정 표시 패널(10)의 일례의 등가 회로를 나타내는 도면이다.

이 도 2에 도시한 바와 같이, 액정 표시 패널(10)은 매트릭스형으로 형성되는 복수의 화소를 갖는다.

각 화소는 인접하는 2개의 신호선[드레인 신호선(D) 또는 게이트 신호선(G)]과, 인접하는 2개의 신호선[게이트 신호선 (G) 또는 드레인 신호선(D)]과의 교차 영역 내에 배치된다.

각 화소는 박막 트랜지스터[TFT(1), TFT(2)]를 가지고, 각 화소의 박막 트랜지스터[TFT(1), TFT(2)]의 소스 전극은 화소 전극[ITO(1)]에 접속된다.

또한, 화소 전극[ITO(1)]과 공통 전극[ITO(2)] 사이에 액정층이 설치되므로, 화소 전극[ITO(1)]과 공통 전극[ITO(2)] 사이에는 액정 용량(CLC)이 등가적으로 접속된다.

또한, 박막 트랜지스터[TFT(1), TFT(2)]의 소스 전극과 전단의 게이트 신호선(G) 사이에는 부가 용량(CAD D)이 접속된다.

도 3은 도 1에 도시한 액정 표시 패널(10)의 다른 예의 등가 회로를 나타내는 도면이다.

도 2에 도시한 예에서는, 전단의 게이트 신호선 (G)와 소스 전극 사이에 부가 용량(CADD)이 형성되어 있지만, 도 3에 도시한 예의 등가 회로에서는, 공통 신호선(COM)과 소스 전극 사이에 보유 용량(CSTG)이 형성되어 있는 점이 다르다.

본 발명은 어느 쪽에도 적용 가능하지만, 전자의 방식에서는, 전단의 게이트 신호선(G) 펄스가 부가 용량(CADD)을 통해 화소 전극(ITO1)으로 들어가는데 반하여, 후자의 방식에서는, 펄스가 들어가는 일이 없기 때문에, 보다 양호한 표시가 가능해진다.

또한, 도 2, 도 3은 종전계 방식의 액정 표시 패널의 등가 회로를 나타내고 있고, 도 2, 도 3에 있어서, AR은 표시 영역이다.

또한, 도 2, 도 3은 회로도이지만, 실제의 기하학적 배치에 대응하여 그려져 있다.

도 2, 도 3에 도시한 액정 표시 패널(10)에 있어서, 열 방향으로 배치된 각 화소의 박막 트랜지스터(TFT)의 드레인 전극은 각각 드레인 신호선(D)에 접속되고, 각 드레인 신호선(D)은 열 방향의 각 화소의 액정에 계조 전압을 인가하는 드레인 드라이버(130)에 접속된다.

또한, 행 방향으로 배치된 각 화소에 있어서의 박막 트랜지스터(TFT)의 게이트 전극은 각각 게이트 신호선(G)에 접속되고, 각 게이트 신호선(G)은 1 수평 주사 시간 행 방향의 각 화소의 박막 트랜지스터(TFT)의 게이트 전극에 주사 구동 전압(정극성의 바이어스 전압 혹은 부극성의 바이어스 전압)을 공급하는 게이트 드라이버(140)에 접속된다.

#### <도 1에 도시한 인터페이스부(100)의 구성과 동작 개요>

도 1에 도시한 인터페이스부(100)는 표시 제어 장치(110)와 전원 회로(120)로 구성된다.

표시 제어 장치(110)는 1개의 반도체 집적 회로(LSI)로 구성되며, 컴퓨터 본체측으로부터 송신되어 오는 클럭 신호, 디스플레이 타이밍 신호, 수평 동기 신호, 수직 동기 신호의 각 표시 제어 신호 및 표시용 데이터(R·G·B)를 기초로, 드레인 드라이버(130) 및 게이트 드라이버(140)를 제어·구동하는 표시 제어 장치(110)는 디스플레이 타이밍 신호가 입력되면 이것을 표시 개시 위치라고 판단하고, 시작 펄스(표시 데이터 취득 개시 신호)를 신호선(135)을 통해 제1번짜의 드레인 드라이버(130)로 출력하고, 또한, 수신한 단순 1열의 표시 데이터를 표시 데이터의 버스 라인(133)을 통해 드레인 드라이버(130)로 출력한다.

그 때, 표시 제어 장치(110)는, 각 드레인 드라이버(130)의 데이터 래치 회로에 표시 데이터를 래치하기 위한 표시 제어 신호인 표시 데이터 래치용 클럭(CL2)[이하, 단순히, 클럭(CL2)이라 칭한다]을 신호선(131)을 통해 출력한다.

본체 컴퓨터측으로부터의 표시 데이터는 6비트이고, 1화소 단위, 즉, 적(R), 녹(G), 청(B)의 각 데이터를 1개의 조로 하여 단위 시간마다 전송된다.

또한, 제1번짜의 드레인 드라이버(130)에 입력된 시작 펄스에 의해 제1번짜의 드레인 드라이버(130)에 있어서의 데이터 래치 회로의 래치 동작이 제어된다.

이 제1번짜의 드레인 드라이버(130)에 있어서의 데이터 래치 회로의 래치 동작이 종료하면, 제1번짜의 드레인 드라이버(130)로부터 시작 펄스가 제2번짜의 드레인 드라이버(130)에 입력되고, 제2번짜의 드레인 드라이버(130)에 있어서의 데이터 래치 회로의 래치 동작이 제어된다.

이하, 마찬가지로 하여, 각 드레인 드라이버(130)에 있어서의 데이터 래치 회로의 래치 동작이 제어되고, 잘

못된 표시 데이터가 데이터 래치 회로에 기입되는 것을 방지하고 있다.

표시 제어 장치(110)는, 디스플레이 타이밍 신호의 입력이 종료하거나, 또는, 디스플레이 타이밍 신호가 입력되고 나서 소정의 일정 시간이 지나면, 1 수평분의 표시 데이터가 종료한 것으로 간주하여, 각 드레인 드라이버(130)에 있어서의 데이터 래치 회로에 저장되어 있던 표시 데이터를 액정 표시 패널(10)의 드레인 신호선(D)으로 출력하기 위한 표시 제어 신호인 출력 타이밍 제어용 클럭(CL1) [이하, 단순히 클럭(CL1)이라 칭한다]을 신호선(132)을 통해 각 드레인 드라이버(130)로 출력한다.

또한, 표시 제어 장치(110)는, 수직 동기 신호 입력 후에 제1번째의 디스플레이 타이밍 신호가 입력되면, 이것을 제1번째의 표시 라인이라고 판단하여 신호선(142)을 통해 게이트 드라이버(140)에 프레임 개시 지시 신호를 출력한다.

또한, 표시 제어 장치(110)는, 수평 동기 신호에 기초하여 1수평 주사 시간마다 순차 액정 표시 패널(10)의 각 게이트 신호선(G)에 정의 바이어스 전압을 인가하도록 신호선(141)을 통해 게이트 드라이버(140)로 1수평 주사 시간 주기의 시프트 클럭(CL3)을 출력한다.

이에 따라, 액정 표시 패널(10)의 각 게이트 신호선 (G)에 접속된 복수의 박막 트랜지스터(TFT)가 1수평 주사 시간 동안 동안 동작한다.

이상의 동작에 의해, 액정 표시 패널(10)에 화상이 표시된다.

#### <도 1에 도시한 전원 회로(120)의 구성>

도 1에 도시한 전원 회로(120)는, 정전압 생성 회로(121), 부전압 생성 회로(122), 공통 전극(대향 전극) 전압 생성회로(123), 게이트 전극 전압 생성 회로(124)로 구성된다.

정전압 생성 회로(121), 부전압 생성 회로(122)는 각각 직렬 저항 분압 회로로 구성되며, 정전압 생성 회로(121)는 정극성의 5치의 계조 기준 전압(V'0~V'4)을, 부전압 생성 회로(122)는 부극성의 5치의 계조 기준 전압(V'5~V'9)을 출력한다.

이 정극성의 계조 기준 전압(V'0~V'4) 및 부극성의 계조 기준 전압(V'5~V'9)은 각 드레인 드라이버(130)로 공급된다.

또한, 각 드레인 드라이버(130)에는 표시 제어 장치(110)로부터의 교류화 신호(교류화 타이밍 신호: M)도 신호선(134)을 통해 공급된다.

공통 전극 전압 생성 회로(123)는 공통 전극[ITO(2)]에 인가하는 구동 전압을, 게이트 전극 전압 생성 회로(124)는 박막 트랜지스터(TFT)의 게이트 전극에 인가하는 구동 전압(정의 바이어스 전압 및 부의 바이어스 전압)을 생성한다.

#### <도 1에 도시한 액정 표시 장치의 교류화 구동 방법>

일반적으로, 액정층은 장시간 동일 전압(직류 전압)이 인가되어 있으면 액정층의 기울기가 고정화되고, 결과로서 잔상 현상을 야기하여 액정층의 수명을 단축하게 된다.

이것을 방지하기 위해, 액정 표시 장치에 있어서는, 액정층에 인가하는 전압을 어떤 일정 시간마다 교류화, 즉, 공통 전극에 인가하는 전압을 기준으로 하여 화소 전극에 인가하는 전압을 일정시간마다 정전압/부전압 측으로 변화하도록 하고 있다.

이 액정층에 교류 전압을 인가하는 구동 방법으로서, 공통 대칭법과 공통 반전법의 2가지 방법이 알려져 있다.

공통 반전법은, 공통 전극에 인가되는 전압과 화소 전극에 인가하는 전압을 교대로 플러스, 마이너스로 반전시키는 방법이다.

또한, 공통 대칭법이란, 공통 전극에 인가되는 전압을 일정하게 하고, 화소 전극에 인가하는 전압을 공통 전극에 인가되는 전압을 기준으로 하여 교대로 플러스, 마이너스로 반전시키는 방법이다.

공통 대칭법은, 화소 전극[ITO(1)]에 인가되는 전압의 진폭이 공통 반전법의 경우에 비교하여 2배가 되고, 임계치 전압이 낮은 액정이 개발되지 않는 한 저내압의 드라이버를 사용할 수 없다고 하는 결점이 있지만, 저소비 전력과 표시 품질의 점에서 우수한 도트 반전법 혹은 N 라인 반전법이 사용 가능하다.

도 1에 도시한 액정 표시 장치에서는, 그 구동 방법으로서, 상기 도트 반전법을 사용하고 있다.

도 4는, 액정 표시 장치의 구동 방법으로서, 도트 반전법을 사용한 경우에 있어서, 드레인 드라이버(130)로부터 드레인 신호선(D)으로 출력되는 액정 구동 전압(즉, 화소 전극[ITO(1)]에 인가되는 계조 전압)의 극성을 설명하기 위한 도면이다.

액정 표시 장치의 구동 방법으로서, 도트 반전법을 사용하는 경우에, 도 4에 도시한 바와 같이, 예를 들면, 흘수 프레임의 흘수 라인에서는, 드레인 드라이버(130)로부터 흘수번째의 드레인 신호선(D)에, 공통 전극[ITO(2)]에 인가되는 액정 구동 전압(VCOM)에 대해 부극성인 액정 구동 전압(도 4에서는 ●로 나타냄)이, 또한, 짹수번째의 드레인 신호선(D)에, 공통 전극[ITO(2)]에 인가되는 액정 구동 전압(VCOM)에 대해 정극성인 액정 구동 전압(도 4에서는 ○로 나타냄)이 인가된다.

또한, 흘수 프레임의 짹수 라인에서는, 드레인 드라이버(130)로부터 흘수번째의 드레인 신호선(D)에 정극성의 액정 구동 전압이, 또한, 짹수번째의 드레인 신호선(D)에 부극성의 액정 구동 전압이 인가된다.

또한, 각 라인마다의 극성은 프레임마다 반전되고, 즉, 도 4에 도시한 바와 같이, 짹수 프레임의 흘수 라인에서는 드레인 드라이버(130)로부터 흘수번째의 드레인 신호선(D)에 정극성의 액정 구동 전압이, 또한, 짹수번째의 드레인 신호선(D)에 부극성의 액정 구동 전압이 인가된다.

또한, 짹수 프레임의 짹수 라인에서는, 드레인 드라이버(130)로부터 흘수번째의 드레인 신호선(D)에 부극성의

액정 구동 전압이, 또한, 짹수번째의 드레인 신호선(D)에 정극성의 액정 구동 전압이 인가된다.

이 도트 반전법을 사용함으로써, 인접하는 드레인 신호선(D)에 인가되는 전압이 반대 극성이 되기 때문에, 공통 전극[ITO(2)]이나 박막 트랜지스터(TFT)의 게이트 전극에 흐르는 전류가 이웃끼리 상쇄하여 소비 전력을 저감시킬 수가 있다.

또한, 공통 전극[ITO(2)]에 흐르는 전류가 적어 전압 강하가 크지 않기 때문에, 공통 전극[ITO(2)]의 전압 레벨이 안정되고 표시 품질의 저하를 최소한으로 억제할 수 있다.

#### <도 1에 도시한 드레인 드라이버 130의 구성>

도 5는, 도 1에 도시한 드레인 드라이버(130)의 일례의 개략 구성은 나타내는 블록도이다.

또, 드레인 드라이버(130)는 1개의 반도체 집적 회로(LSI)로 구성된다.

상기 도면에 있어서, 정극성 계조 전압 생성 회로(151a)는 정전압 생성 회로(121)로부터 입력되는 정극성의 5치의 계조 기준 전압(V'0~V'4)에 기초하여 정극성의 64계조의 계조 전압을 생성하고, 전압 버스 라인(158a)을 통해 출력 회로(157)로 출력한다.

부극성 계조 전압 생성 회로(151b)는 부전압 생성 회로(122)로부터 입력되는 부극성의 5치의 계조 기준 전압(V'5~V'9)에 기초하여 부극성의 64계조의 계조 전압을 생성하고, 전압 버스 라인(158b)을 통해 출력 회로(157)로 출력한다.

또한, 드레인 드라이버(130)의 제어 회로(152) 내의 시프트 레지스터 회로(153)는, 표시 제어 장치(110)로부터 입력되는 클럭(CL2)에 기초하여, 입력 레지스터 회로(154)의 데이터 수신용 신호를 생성하고, 입력 레지스터 회로(154)로 출력한다.

입력 레지스터 회로(154)는, 시프트 레지스터 회로(153)로부터 출력되는 데이터 수신용 신호에 기초하여, 표시 제어 장치(110)로부터 입력되는 클럭(CL2)에 동기하여, 각 색마다 6비트의 표시 데이터를 출력 라인수만큼 래치한다.

저장 레지스터 회로(155)는, 표시 제어 장치(110)로부터 입력되는 클럭(CL1)에 따라 입력 레지스터 회로(154) 내의 표시 데이터를 래치한다.

이 저장 레지스터 회로(155)에 래치된 표시 데이터는 레벨 시프트 회로(156)를 통해 출력 회로(157)에 입력된다.

출력 회로(157)는, 정극성의 64계조의 계조 전압, 혹은 부극성의 64계조의 계조 전압에 기초하여, 표시 데이터에 대응한 1개의 계조 전압(64계조 중의 1개의 계조 전압)을 선택하여, 각 드레인 신호선(D)으로 출력한다.

도 6은, 출력 회로(157)의 구성을 중심으로, 도 5에 도시한 드레인 드라이버(130)의 구성을 설명하기 위한 블록도이다.

상기 도면에 있어서, 참조 번호 153은 도 5에 도시한 제어 회로(152) 내의 시프트 레지스터 회로, 156은 도 5에 도시한 레벨 시프트 회로이며, 또한, 데이터 래치부(265)는, 도 5에 도시한 입력 레지스터 회로(154)와 저장 레지스터 회로(155)를 나타내고, 또한, 디코더부(계조 전압 선택 회로: 261), 앰프 회로쌍(263), 앰프 회로쌍(263)의 출력을 절환하는 스위치부(2)264가, 도 5에 도시한 출력 회로(157)를 구성한다.

여기서, 스위치부(1)262 및 스위치부(2)264는, 교류화 신호(M)에 기초하여 제어된다.

또한, Y1, Y2, Y3, Y4, Y5, Y6은, 각각 제1번째, 제2번째, 제3번째, 제4번째, 제5번째, 제6번째의 드레인 신호선(D)을 나타내고 있다.

도 6에 도시한 드레인 드라이버(130)에 있어서는, 스위치부(1)262에 의해 데이터 래치부(265)[보다 상세하게는, 도 5에 도시한 입력 레지스터(154)]에 입력되는 데이터 수신용 신호를 절환하여, 각 색마다의 표시 데이터를 각 색마다의 인접하는 데이터 래치부(265)에 입력한다.

디코더부(261)는, 계조 전압 생성 회로(151a)로부터 전압 버스 라인(158a)을 통해 출력되는 정극성의 64계조의 계조 전압 중에서 각 데이터 래치부(265)[보다 상세하게는, 도 5에 도시한 저장 레지스터(155)]로부터 출력되는 표시용 데이터에 대응하는 정극성의 계조 전압을 선택하는 고전압용 디코더 회로(278)와, 계조 전압 생성 회로(151b)로부터 전압 버스 라인(158b)을 통해 출력되는 부극성의 64계조의 계조 전압 중에서 각 데이터 래치부(265)로부터 출력되는 표시용 데이터에 대응하는 부극성의 계조 전압을 선택하는 저전압용 디코더 회로(279)로 구성된다.

이 고전압용 디코더 회로(278)와 저전압용 디코더 회로(279)는 인접하는 데이터 래치부(265)마다 설치된다.

앰프 회로쌍(263)은, 고전압용 앰프 회로(271)와 저전압용 앰프 회로(272)로 구성된다.

고전압용 앰프 회로(271)에는 고전압용 디코더 회로(278)로 생성된 정극성의 계조 전압이 입력되고, 고전압용 앰프 회로(271)는 정극성의 계조 전압을 출력한다.

저전압용 앰프 회로(272)에는 저전압용 디코더 회로(279)로 생성된 부극성의 계조 전압이 입력되고, 저전압용 앰프 회로(272)는 부극성의 계조 전압을 출력한다.

도트 반전법에서는, 인접하는 각 색의 계조 전압은 상호 반대 극성으로 되고, 또한, 앰프 회로쌍(263)의 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)의 배열은, 고전압용 앰프 회로(271)→저전압용 앰프 회로(272)→고전압용 앰프 회로(271)→저전압용 앰프 회로(272)로 되기 때문에, 스위치부(1)262에 의해 데이터 래치부(165)에 입력되는 데이터 수신용 신호를 절환하여, 각 색마다의 표시 데이터를 각 색마다의 인접하는 데이터 래치부(265)에 입력하고, 그것에 맞춰, 고전압용 앰프 회로(271) 혹은 저전압용 앰프 회로(272)로부터 출력되는 출력 전압을 스위치부(2)264에 의해 절환하고, 각 색마다의 계조 전압이 출력되는 드레인 신호선(D), 예를 들면, 제1번째의 드레인 신호선(Y1)과 제4번째의 드레인 신호선(Y4)으로 출력함으로써, 각 드레인

신호선(D)에 정극성 혹은 부극성의 계조 전압을 출력하는 것이 가능해진다.

#### <본 실시예의 액정 표시 장치의 특징적 구성>

도 7은, 본 실시예의 액정 표시 장치의 드레인 드라이버(130)의 개략 구성을 나타내는 도면이다.

또, 이 도 7에서는, 고전압용 디코더 회로(278), 저전압용 디코더 회로(279), 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)만, 또한, 각 색마다의 인접하는 드레인 신호(D), 예를 들면, 제1번재의 드레인 신호선(Y1)과 제4번재의 드레인 신호선(Y4)으로 출력되는 출력 계통만을 나타내고 있다.

이 도 7에 있어서, 트랜스퍼 게이트 회로(TG1~TG4)는, 도 6에 도시한 스위치부(2)264의 1 스위치 회로를 구성한다.

또한, 출력 PAD(21, 22)는, 예를 들면, 제1번재의 드레인 신호선(Y1)과 제4번재의 드레인 신호선(Y4)으로 출력되는 반도체 칩(드레인 드라이버)의 출력 패드를 나타낸다.

상기 도면에 도시한 바와 같이, 본 실시예의 액정 표시 장치는, 고전압용 디코더 회로(278)와 고전압용 앰프 회로(271) 사이, 및 저전압용 디코더 회로(279)와 저전압용 앰프 회로(272) 사이에, 프리차아지 컨트롤 회로(이하, 단순히, 프리차아지 회로라 칭한다: 30)를 설치한 것을 특징으로 한다.

이 프리차아지 회로(30)는, 고전압용 디코더 회로(278)와 고전압용 앰프 회로(271) 사이에 접속되는 트랜스퍼 게이트 회로(TG31)와, 저전압용 디코더 회로(279)와 저전압용 앰프 회로(272) 사이에 접속되는 트랜스퍼 게이트 회로(TG32)를 갖는다.

이 트랜스퍼 게이트 회로(TG31, TG32)는 (DECT, DEON)의 제어 신호에 의해 제어되고, 프리차아지 기간 내에 고전압용 디코더 회로(278)와 저전압용 디코더 회로(279)를 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)로부터 분리한다.

또한, 프리차아지 회로(30)는, 트랜스퍼 게이트 회로(TG33)와 트랜스퍼 게이트 회로(TG34)를 갖는다.

이 트랜스퍼 게이트 회로(TG33, TG34)는, (PRET, PREN)의 제어 신호에 의해 제어되고, 프리차아지 기간 내에, 고전압용 앰프 회로(271)에 고전압용 프리차아지 전압(예를 들면, 임의의 계조 기준 전압, 임의의 정극성의 계조 전압) ( $V_{Hpre}$ )을, 또한, 저전압용 앰프 회로(272)에 저전압용 프리차아지 전압(예를 들면, 임의의 계조 기준 전압, 임의의 부극성의 계조 전압) ( $V_{Lpre}$ )을 공급한다.

#### <본 실시예의 드레인 드라이버(130)의 출력 지연 시간( $t_{DD}$ ) 특성>

도 8은, 도 1에 도시한 액정 표시 장치의 드레인 드라이버(130)의 출력 지연 시간( $t_{DD}$ ) 특성을 설명하기 위한 도면이다.

또, 이 도 8a에서는 1계통의 출력 계통만 도시하고, 또한, 도 6에 도시한 스위치부(2)264는 생략하고 있다.

즉, 도 8a에 있어서, 디코더 회로(31)는 도 6에 도시한 고전압용 디코더 회로(278) 또는 저전압용 디코더 회로(279)를, 앰프 회로(32)는 도 6에 도시한 고전압용 앰프 회로(271) 또는 저전압용 앰프 회로(272)를, 또한, 출력 패드(33)는 도 7에 도시한 출력 PAD(20) 또는 출력 PAD(21)를 나타내고 있다.

도 9는, 도 6에 도시한 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 일례의 개략 구성을 나타내는 도면이다.

도 9에 도시한 바와 같이, 도 6에 도시한 고전압용 디코더 회로(278) 또는 저전압용 디코더 회로(279)는, 증가형 MOS 트랜지스터 및 공핍형 MOS 트랜지스터가 직렬 접속된 트랜지스터 열(TRP2, TRP3)로 구성된다.

상기한 바와 같이, 표시 장치 이외의 테두리 부분을 줄이기 위해, 드레인 드라이버(130)를 구성하는 반도체 칩의 칩 사이즈는 보다 축소되고, 그에 따라, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)는 드레인 드라이버(130)를 구성하는 반도체 칩의 최소 사이즈의 MOS 트랜지스터로 구성되어 있다.

그 결과로서, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 전류 구동 능력이 낮아진다.

또한, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 출력에는 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)가 접속되어 있지만, 이 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)는 입력 임피던스가 크다.

그 때문에, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 출력이 확정하기까지의 동안(이하, 단순히, 디코더의 출력 지연 시간이라 칭한다)이 크게 되어, 이 디코더의 출력 지연 시간이 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)에서 더욱 증대된다.

그 결과로서, 도 8b에 도시한 바와 같이, 드레인 신호선(D)에 표시 데이터에 대응한 계조 전압(VLCH)이 출력되기까지의 시간(이하, 단순히, 드레인 드라이버의 출력 지연 시간( $t_{DD}$ )이라 한다)이 커진다.

도 10은, 본 실시예의 액정 표시 장치의 드레인 드라이버(130)의 출력 지연 시간( $t_{DD}$ ) 특성을 설명하기 위한 도면이다.

또, 이 도 10a에서도, 1계통의 출력 계통만 도시하고, 또한, 도 6에 도시한 스위치부(2)264는 생략하고 있다.

즉, 도 10a에 있어서, 디코더 회로(31)는 도 7에 도시한 고전압용 디코더 회로(278) 또는 저전압용 디코더 회로(279)를, 앰프 회로(32)는 도 7에 도시한 고전압용 앰프 회로(271) 또는 저전압용 앰프 회로(272)를, 또한 출력 패드(33)는 도 7에 도시한 출력 PAD(20) 또는 출력 PAD(21)를 나타내고 있다.

본 실시예의 액정 표시 장치에서는, 프리차아지 기간 내에 고전압용 디코더 회로(278)와 저전압용 디코더 회로(279)가 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)로부터 분리되고, 고전압용 디코더 회로(278)와 저전압용 디코더 회로(279)의 출력에는 트랜스퍼 게이트 회로(TG31)와 트랜스퍼 게이트 회로(TG32)가 접

속된다.

이 트랜스퍼 게이트 회로(TG31, TG32)의 오프 시의 입력 임피던스는 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)의 입력 임피던스보다 훨씬 작다.

따라서, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 출력은 도 8에 도시한 경우보다도 빠른 시간으로 확정하고, 결과로서, 디코더의 출력 지연 시간을 작게 할 수가 있다.

또한, 프리차아지 기간 내에 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)에는 고전압용 프리차아지 전압(VHpre) 및 저전압용 프리차아지 전압(VLpre)이 공급되기 때문에, 드레인 신호선(D)은 미리 고전압용 프리차아지 전압(VHpre) 및 저전압용 프리차아지 전압(VLpre)으로 충전된다.

이 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)로부터 드레인 신호선(D)에 대한 프리차아지는, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)와 병렬적으로 행해진다.

그리고, 프리차아지 기간 종료 후에, 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)는, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 출력에 추종하여, 드레인 신호선(D)에, 표시 데이터에 대응한 계조 전압(VLCH)을 출력한다.

그 결과로서, 도 10b에 도시한 바와 같이, 본 실시예에서는, 드레인 드라이버의 출력 지연 시간(tDD)을 도 8에 도시한 경우보다도 작게 할 수가 있다.

도트 반전법에서는, 각 화소의 액정층에 인가되는 계조 전압의 극성은 1프레임마다 반전한다.

따라서, 본 실시예와 같이, 프리차아지 기간 내에 드레인 신호선(D)을 고전압용 프리차아지 전압(VHpre) 혹은 저전압용 프리차아지 전압(VLpre)으로 충전함으로써, 프리차아지 기간 종료 후에, 드레인 신호선(D)의 전위는 표시 데이터에 빠르게 대응한 계조 전압(VLCH)에 추종할 수가 있다.

또, 본 실시예에서는, 도 10b에 도시한 바와 같이, 드레인 신호선(D)에, 표시 데이터에 대응한 계조 전압(VLCL)으로도 드레인 드라이버의 출력 지연 시간(tDD)을 도 8에 도시한 경우보다도 작게 할 수가 있다.

또, 앰프 회로의 전단에 프리차아지 회로를 설치한 액정 표시 장치는, 특개평6-337400호 공보, 특개평10-187100호 공보에 기재되어 있다.

그러나, 상기 공보에 기재되어 있는 것은, 샘플링 용량으로의 충방전 시간이 부족한 것을 방지하기 위해 프리차아지 회로를 설치함으로써, 본원 발명과 같이, 표시 장치 이외의 테두리를 줄이기 위해, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)를 최소 사이즈의 MOS 트랜지스터로 구성할 필요가 있고, 그 결과로서, 고전압용 디코더 회로(278) 및 저전압용 디코더 회로(279)의 전류 구동 능력이 낮게 되어, 드레인 드라이버의 출력 지연 시간(tDD)이 커지는 것을 방지하는 것은 아니다.

또한, 상기 공보에는, 상기한 과제에 대해서는 아무것도 언급되어 있지 않다.

<본 실시예의 프리차아지 회로(30)의 동작 개요>

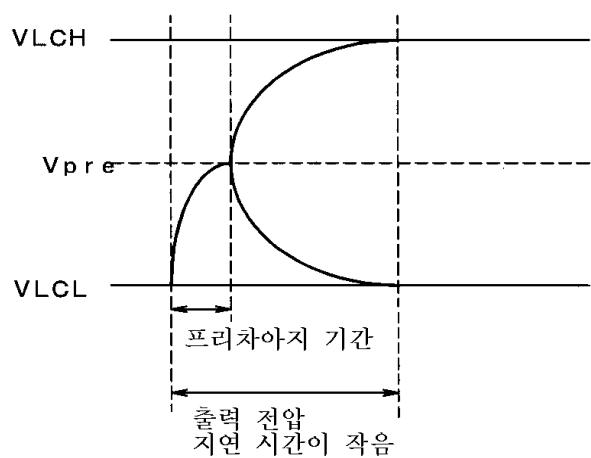

도 11은, 도 7에 도시한 프리차아지 회로(30)의 동작을 설명하기 위한 타이밍 차트의 일례이다.

도 11에 도시한 제어 신호(HIZCNT)는 각 트랜스퍼 게이트 회로(TG1~TG4)의 게이트 전극에 인가되는 제어 신호(ACKEP, ACKOP, ACKEN, ACKON)를 생성하기 위한 제어 신호이며, 이 제어 신호(HIZCNT)는 클럭(CL1)의 High 레벨(이하, 단순히, H 레벨이라고 한다) 기간 내에서 클럭(CL2)의 8주기분의 동안 H 레벨로 되는 신호이다.

주사 라인의 절환 시에는, 고전압용 앰프 회로(271)와 저전압용 앰프 회로(272) 모두 불안정의 상태에 있다.

이 제어 신호(HIZCNT)는 주사 라인의 절환 기간 내에 각 앰프 회로(271, 272)의 출력이 각 드레인 신호선(D)으로 출력되는 것을 방지하기 위해 설치되어 있다.

이 제어 신호(HIZCNT)가 H 레벨의 동안, 제어 신호(ACKEP, ACKOP)는 Low 레벨(이하, 단순히, L 레벨이라고 한다)로 되고, 또한, 제어 신호(ACKEN, ACKON)는 H 레벨로 된다.

이에 따라, 각 트랜스퍼 게이트 회로(TG1~TG4)는 전부 오프가 된다.

도 11에 도시한 제어 신호(PRECNT)는 각 트랜스퍼 게이트 회로(TG31~TG34)의 게이트 전극에 인가되는 제어 신호(PRET, PREN, DECT, DECN)를 생성하기 위한 제어 신호이며, 이 제어 신호(PRECNT)는 제어 신호(HIZCNT)의 상승 시부터 클럭(CL2)의 4주기 후에 H 레벨로 되고, 클럭(CL1)의 하강 시에 L 레벨로 되는 신호이다.

제어 신호(DECT)는 제어 신호(PREN) 전에 H 레벨로부터 L 레벨로 변화하고, 또한, 제어 신호(DECN)는 제어 신호(PRET) 전에 L 레벨로부터 H 레벨로 변화한다.

이에 따라, 우선 트랜스퍼 게이트 회로(TG31, TG32)가 오프로 되고, 그 후, (tD1) 시간 지연되어, 트랜스퍼 게이트 회로(TG33, TG34)가 온으로 된다.

또한, 제어 신호(PREN)는 제어 신호(DECT) 전에 L 레벨로부터 H 레벨로, 또한, 제어 신호(PRET)는 제어 신호(DECN) 전에 H 레벨로부터 L 레벨로 변화한다.

이에 따라, 우선 트랜스퍼 게이트 회로(TG33, TG34)가 오프가 되고, 그 후, (tD2) 시간 지연되어, 트랜스퍼 게이트 회로(TG31, TG24)가 온으로 된다.

도 12는, 도 11에 도시한 제어 신호(HIZCNT) 및 제어 신호(PRECNT)를 생성하기 위한 회로 구성의 일례를 나타내는 도면이다.

도 12에 도시한 회로에서는, D형 플립플롭 회로(F30)에 의해 클럭(CL2)에 동기하여 클럭(CL1)을 받아들이고,

이 D형 플립플롭 회로(F30)의 정상 출력을 클럭(CL2)에 동기하여 각 D형 플립플롭 회로(F31~F38)에서 순차 받아들인다.

이 D형 플립플롭 회로(F38)의 정상 출력은, NAND 회로(NAND31)의 한쪽의 입력 단자에 입력되고, 또한, NAND 회로(NAND31)의 다른쪽의 입력 단자에는, D형 플립플롭 회로(F30)의 정상 출력이 입력되어 있다.

따라서, NAND 회로(NAND31)로부터, 클럭(CL1)의 H 레벨 기간 내에서, 클럭(CL2)의 8주기분의 동안, L 레벨로 되는 출력이 얻어진다.

이 NAND 회로(NAND31)의 출력을 인버터 회로(INV)로 반전함으로써, 도 11에 도시한 제어 신호(HIZCNT)가 얻어진다.

또한, D형 플립플롭 회로(F34)의 출력은 D형 플립플롭 회로(F39)의 클럭 입력 단자에 입력되기 때문에, D형 플립플롭 회로(F39)는 D형 플립플롭 회로(F34)의 정상 출력에 동기하여 H 레벨로 된다.

또한, D형 플립플롭 회로(F39)의 리세트 단자에는 클럭(CL1)이 입력되기 때문에, D형 플립플롭 회로(F39)는 클럭(CL1)이 하강에 동기하여 L 레벨로 된다.

이에 따라, D형 플립플롭 회로(F39)로부터, 제어 신호(HIZCNT)의 상승 시간부터 클럭(CL2)의 4주기 후에 H 레벨로 되고, 클럭(CL1)의 하강 시에 L 레벨이 되는 신호가 얻어진다.

이 신호를 인버터 회로군(35)에 의해 소정 시간 지연하여, 도 11에 도시한 제어 신호(PRECNT)가 얻어진다.

도 13은, 도 11에 도시한 제어 신호(PRET, PREN, DECT, DECN)를 생성하기 위한 회로 구성의 일례를 나타내는 도면이다.

도 13에 도시한 회로에서는, 제어 신호(PRECNT)와, 인버터 회로군(36)에 의해 (tD1)시간만큼 지연된 제어 신호(PRECNT)를 NAND 회로(NAND32)에 입력함으로써 제어 신호(PRET)가 생성되고, 또한, 이 제어 신호(PRET)를 인버터 회로(INV)로 반전함으로써 제어 신호(PREN)가 얻어진다.

또한, 인버터 회로(INV)로 반전된 제어 신호(/PRECNT)와, 인버터 회로군(37)에 의해 tD2 시간만큼 지연된 제어 신호(/PRECNT)를 NAND 회로(NAND33)에 입력함으로써 제어 신호(DECN)가 생성되고, 또한, 이 제어 신호(DECN)를 인버터 회로(INV)로 반전함으로써 제어 신호(DECT)가 얻어진다.

도 14는, 도 11에 도시한 제어 신호(ACKEP, ACKOP, ACKEN, ACKON)를 생성하기 위한 회로 구성의 일례를 나타내는 도면이다.

또, 도 14에 있어서, LS1~LS4는 레벨 시프트 회로이다.

도 14에 도시한 회로에서, NAND 회로(NAND1)와 NOR회로(NOR1)에는 교류화 신호(M)가, NAND 회로(NAND2) 및 NOR회로(NOR2)에는 인버터(INV)로 반전된 교류화 신호(M)가 입력된다.

또한, NAND 회로(NAND1, NAND2)에는 제어 신호(HIZCNT)가, NOR회로(NOR1, NOR2)에는 인버터(INV)로 반전된 제어 신호(HIZCNT)가 입력된다.

표 1에, NAND 회로(NAND1, NAND2)와 NOR 회로(NOR1, NOR2)의 진리값표와, 그 시의 각 트랜스퍼 게이트 회로(TG1~TG4)의 온·오프 상태를 나타낸다.

[표 1]

| HIZCNTT | M | NOR1 | NAND2 | NAND1 | NOR2 | TG1 | TG2 | TG3 | TG4 |

|---------|---|------|-------|-------|------|-----|-----|-----|-----|

| H       | * | L    | H     | H     | L    | OFF | OFF | OFF | OFF |

| L       | H | L    | H     | L     | H    | OFF | OFF | ON  | ON  |

|         | L | H    | L     | H     | L    | ON  | ON  | OFF | OFF |

표 1에서 알 수 있는 바와 같이, 제어 신호(HIZCNT)가 H 레벨일 때에, NAND 회로(NAND1, NAND2)는 H 레벨, NOR 회로(NOR1, NOR2)는 L 레벨로 되고, 각 트랜스퍼 게이트 회로(TG1~TG4)는 오프 상태가 된다.

또한, 표 1로부터 알 수 있는 바와 같이, 제어 신호(HIZCNT)가 L 레벨일 때에는, 교류화 신호(M)의 H 레벨 혹은 L 레벨에 따라 각 NAND 회로(NAND1, NAND2)가 H 레벨 혹은 L 레벨, 각 NOR 회로(NOR1, NOR2)가 H 레벨 혹은 L 레벨로 된다.

이에 따라, 트랜스퍼 게이트 회로(TG1) 및 트랜스퍼 게이트 회로(TG2)가 오프 혹은 온, 트랜스퍼 게이트 회로(TG3) 및 트랜스퍼 게이트 회로(TG4)가 온 혹은 오프로 된다.

본 실시예의 액정 표시 장치(LCM)에서는, 각 화소의 액정층에 인가되는 계조 전압의 전압 범위는, 부극성측에서 0~5V, 정극성측에서 5~10V이며, 따라서, 저전압용 앰프 회로(272)로부터는 0~5V의 부극성의 계조 전압이 출력되고, 고전압용 앰프 회로(271)로부터는 5~10V의 정극성의 계조 전압이 출력된다.

이 경우에, 예를 들면, 트랜스퍼 게이트 회로(TG1)가 오프이고 트랜스퍼 게이트 회로(TG4)가 온인 경우에, 트랜스퍼 게이트 회로(TG1)를 구성하는 MOS 트랜지스터의 소스·드레인 사이에는 최대 10V의 전압이 인가된다.

그 때문에, 각 트랜스퍼 게이트 회로(TG1~TG4)를 구성하는 MOS 트랜지스터는 소스·드레인간 내압이 10V인 고내압 MOS 트랜지스터가 사용된다.

<본 실시예의 액정 표시 장치의 변형예>

도 15는 본 발명의 실시예의 액정 표시 장치의 다른 예의 개략 구성을 나타내는 도면이다.

또, 이 도 15에서도, 고전압용 디코더 회로(278), 저전압용 디코더 회로(279), 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)만, 또한, 각 색마다의 인접하는 드레인 신호(D), 예를 들면, 제1번재의 드레인 신호선(Y1)과 제4번재의 드레인 신호선(Y4)으로 출력되는 출력 계통만을 도시하고 있다.

도 15에 도시한 액정 표시 장치는, 프리차아지 전압 선택 스위치(38)를 설치하고, 이 프리차아지 전압 선택 스위치(38)에 의해 제1 고전압용 프리차아지 전압(VH1pre), 또는 제2 고전압용 프리차아지 전압(VH2pre)을 선택하고, 상기 선택한 전압을 고전압용 프리차아지 전압으로서 프리차아지 기간 내에 고전압용 앰프 회로(271)에 인가하도록 한 것이다.

마찬가지로 저전압용 앰프 회로(272)에 있어서도, 프리차아지 전압 선택 스위치(38)에 의해, 제1 저전압용 프리차아지 전압(VL1pre) 또는 제2 저전압용 프리차아지 전압(VL2pre)을 선택하고, 상기 선택한 전압을 저전압용 프리차아지 전압으로서 프리차아지 기간 내에 저전압용 앰프 회로(272)에 인가한다.

#### <본 실시예의 프리차아지 전압의 전압치>

본 실시예에 있어서, 고전압용 앰프 회로(271)에 공급하는 고전압용 프리차아지 전압(VHpre)은 정극성의 64계조의 계조 전압 중 어느 것이라도 좋고, 저전압용 앰프 회로(272)에 공급하는 저전압용 프리차아지 전압(VLpre)은 부극성의 64계조의 계조 전압 중 어느 것이라도 좋다.

또한, 본 실시예에 있어서, 고전압용 앰프 회로(271)에 공급하는 고전압용 프리차아지 전압(VHpre)은 도 1에 도시한 정전압 생성 회로(121)로부터 공급되는 정극성의 5치의 계조 기준 전압(V'0~V'4) 중 어느 것이라도 좋고, 저전압용 앰프 회로(272)에 공급하는 저전압용 프리차아지 전압(VLpre)은 도 1에 도시한 부전압 생성 회로(122)로부터 공급되는 부극성의 5치의 계조 기준 전압(V'5~V'9) 중 어느 것이라도 좋다.

그러나, 고전압용 앰프 회로(271)에 공급하는 고전압용 프리차아지 전압(VHpre)은, 정극성의 64계조의 계조 전압 중에서 공통 전극에 인가하는 구동 전압(대향 전압)에 대해 전위차가 가장 큰 최대 계조 전압과, 공통 전극에 인가하는 구동 전압에 대해 가장 전위차가 작은 최소 계조 전압과의 중간 전압(이하, 정극성의 중간 전압이라 칭한다)보다 최대 계조 전압쪽에 가까운 전압이 가장 바람직하며, 저전압용 앰프 회로(272)에 공급하는 저전압용 프리차아지 전압(VLpre)은, 부극성의 64계조의 계조 전압 중에서 공통 전극에 인가하는 구동 전압에 대해 가장 전위차가 큰 최대 계조 전압과, 공통 전극에 인가하는 구동 전압에 대해 가장 전위차가 작은 최소 계조 전압과의 중간 전압(이하, 부극성의 중간 전압이라 칭한다)보다 최대 계조 전압쪽에 가까운 전압이 가장 바람직하다.

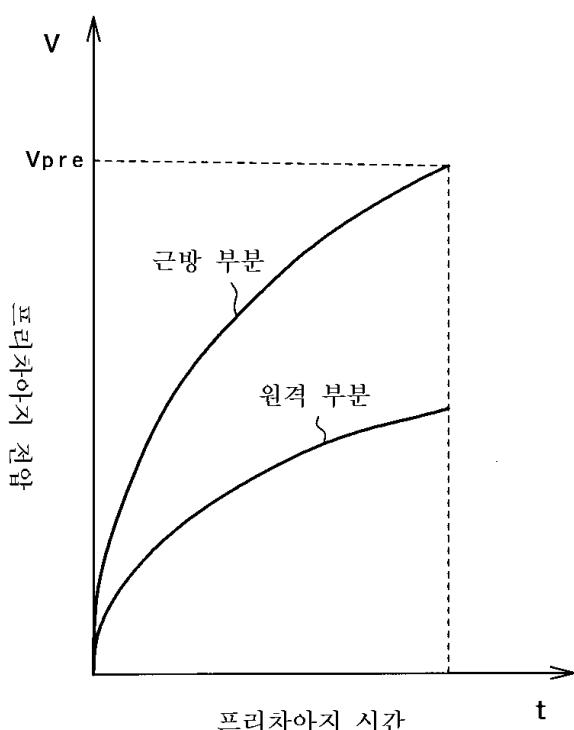

도 16a는, 하나의 드레인 신호선(D)에 있어서, 드레인 드라이버(130)에 근방 부분과, 드레인 드라이버(130)로부터 가장 먼 원격 부분에서의 프리차아지 기간 내의 전위 변동을 설명하기 위한 그래프이다.

이 도 16a로부터 알 수 있는 바와 같이, 프리차아지 기간 내에 하나의 드레인 신호선(D)에 프리차아지 전압(예를 들면, 고전압용 프리차아지 전압(VHpre), 혹은 저전압용 프리차아지 전압(VLpre))을 인가하더라도, 그 전위 변동은 드레인 드라이버(130)의 근방 부분과, 드레인 드라이버(130)로부터 가장 먼 원격 부분과 상위하다.

일반적으로, 고전압용 프리차아지 전압(VHpre)으로서는 정극성의 중간 전압이 바람직하다.

그러나, 고전압용 프리차아지 전압(VHpre)으로서 정극성의 중간 전압을 선택한 경우, 도 16a에 도시한 바와 같이, 상기 드레인 드라이버(130)로부터 가장 먼 원격 부분에서는 정극성의 중간 전압으로는 되지 않는다.

따라서, 도 16b에 도시한 바와 같이, 고전압용 프리차아지 전압(VHpre)으로서는 정극성의 중간 전압보다 최대 계조 전압쪽에 가까운 전압에서, 드레인 드라이버(130)의 근방 부분의 프리차아지 전압과 정극성의 중간 전압과의 전위차(Vs1)와, 드레인 드라이버(130)로부터 가장 먼 원격 부분의 프리차아지 전압과 정극성의 중간 전압과의 전위차(Vs2)와의 절대치가 같게 되는 전압(Vs1= Vs2)이 가장 바람직하다.

마찬가지로, 저전압용 프리차아지 전압(VLpre)으로서는, 부극성의 중간 전압보다 최대 계조 전압쪽에 가까운 전압이 가장 바람직하다.

#### <본 실시예의 앰프 회로의 특징적 구성>

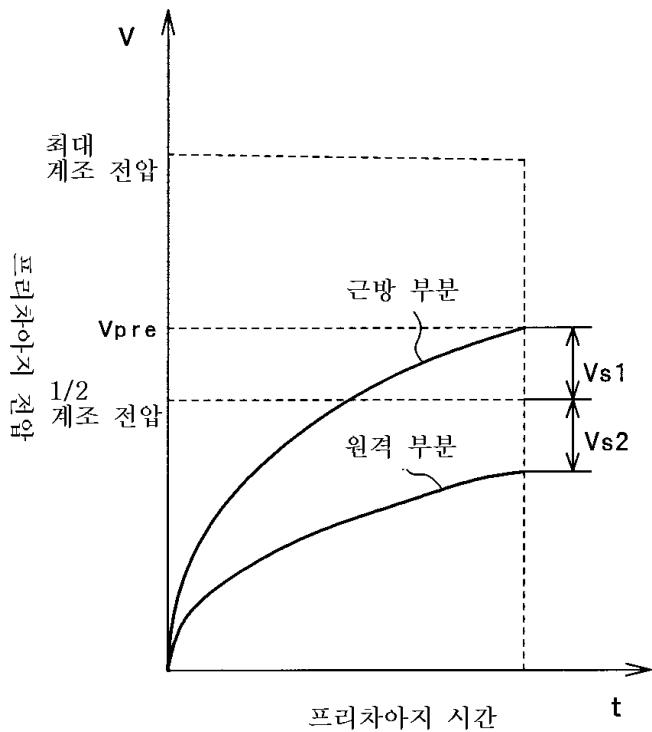

종래, 도 6에 도시한 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)로서는, 예를 들면, 도 17에 도시한 바와 같은, 연산 증폭기(OP)의 반전 입력 단자(-)와 출력 단자가 직결되고, 그 비반전 입력 단자(+)가 입력 단자로 되는 전압 폴로워 회로로 구성된다.

또한, 저전압용 앰프 회로(272)에 사용되는 연산 증폭기(OP)는, 예를 들면, 도 18에 도시한 바와 같은 차동 증폭 회로로 구성되며, 또한, 고전압용 앰프 회로(271)에 사용되는 연산 증폭기(OP)는, 예를 들면, 도 19에 도시한 바와 같은 차동 증폭 회로로 구성된다.

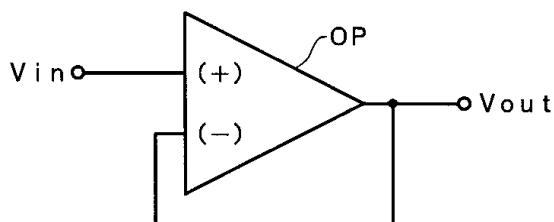

그러나, 일반적으로, 상기 연산 증폭기(OP)는 오프셋 전압(Voff)을 갖고 있다.

상기 연산 증폭기(OP)의 기본 증폭 회로가, 예를 들면, 도 18 또는 도 19에 도시한 차동 증폭 회로에 의해 구성되는 것인 경우에는, 상기 오프셋 전압(Voff)은, 도 18 또는 도 19에 도시한 차동 증폭 회로에서의, 입력단의 PMOS 트랜지스터(PM51, PM52) 또는 NMOS 트랜지스터(NM61, NM62), 혹은 능동 부하 회로를 구성하는 NMOS 트랜지스터(NM63, NM64) 또는 PMOS 트랜지스터(PM53, PM54)의 대칭성의 미묘한 불균형이 원인으로 발생한다.

상기 대칭성의 미묘한 불균형은 제조 공정에서의 이온 주입/이온 주입 공정, 또는 포토리소그래피 공정의 변동에 의해, MOS 트랜지스터의 임계지 전압(Vth), 또는 MOS 트랜지스터의 게이트 폭/게이트 길이(W/L) 등이 변화하게 되는 것에 기인하고 있지만, 공정 관리를 엄격히 하더라도 상기 오프셋 전압(Voff)을 0으로 하는 것은 불가능하다.

그리고, 도 20에 도시한 바와 같이, 상기 연산 증폭기(OP)가 오프셋 전압(Voff)을 갖고 있지 않은 이상적인 연산 증폭기라면, 입력 전압(Vin)과 출력 전압(Vout)이 같게 되는 것(Vin= Vout)에 반하여, 상기 연산 증폭

기(OP)가 오프셋 전압( $V_{off}$ )을 갖고 있는 경우에는, 입력 전압( $V_{in}$ )과 출력 전압( $V_{out}$ )과는 같게 되지 않고, 출력 전압( $V_{out}$ )은 입력 전압( $V_{in}$ )에 오프셋 전압( $V_{off}$ )이 가산( $V_{out}=V_{in}+V_{off}$ )된 것으로 된다.

또, 도 20은, 오프셋 전압( $V_{off}$ )을 고려한 연산 증폭기의 등가 회로를 도시한 도면이고, 도 20에 있어서, ROP는 오프셋 전압( $V_{off}$ )을 갖고 있지 않은 이상적인 연산 증폭기, VOS는 그 전압값이 오프셋 전압( $V_{off}$ )과 같은 전압원이다.

따라서, 드레인 드라이버의 출력 회로(도 5에 도시한 157)의 고전압용 앰프 회로(도 6에 도시한 271) 및 저전압용 앰프 회로(도 6에 도시한 272)로서, 상기 도 17에 도시한 전압 풀로워 회로를 사용하는 종래의 액정 표시 장치에서는, 전압 풀로워 회로의 입력 전압과 출력 전압이 일치하지 않고, 전압 풀로워 회로로부터 드레인 신호선(D)으로 출력되는 액정 구동 전압은 전압 풀로워 회로에 입력되는 계조 전압에 연산 증폭기의 오프셋 전압이 가산된 것으로 된다.

이에 따라, 종래의 액정 표시 장치에서는, 액정 표시 패널에 표시되는 표시 화면 중에 흑 또는 백의 세로 줄무늬가 발생하고, 표시 품질을 현저히 손상시킨다고 하는 문제점이 있었다.

도 21은 본 실시예의 드레인 드라이버(130)에 있어서의 저전압용 앰프 회로(272)의 기본 회로 구성을 나타내는 회로도, 도 22는 본 실시예의 드레인 드라이버(130)에 있어서의 고전압용 앰프 회로(271)의 기본 회로 구성을 나타내는 회로도이다.

도 21에 도시한 본 실시예의 저전압용 앰프 회로(272)는 하기의 점에서 도 18에 도시한 차동 증폭 회로와 상위하다.

(1) 도 18에 도시한 차동 증폭 회로에, 입력단의 PMOS 트랜지스터(PM51)의 게이트 전극(제어 전극)을 (+) 입력 단자 혹은 (-) 입력 단자에 접속하는 스위칭 트랜지스터(NA1, NB1)과, 입력단의 PMOS 트랜지스터(PM52)의 게이트 전극을 (+) 입력 단자 혹은 (-) 입력 단자에 접속하는 스위칭 트랜지스터(NA2, NB2)와, 출력단의 NMOS 트랜지스터(NM65)의 게이트 전극을 입력단의 PMOS 트랜지스터(PM51)의 드레인 전극(제2 전극) 혹은 입력단의 PMOS 트랜지스터(PM52)의 드레인 전극에 접속하는 스위칭 트랜지스터(NA3, NB3)와, 능동 부하 회로를 구성하는 NMOS 트랜지스터(NM63, NM64)의 게이트 전극을 입력단의 PMOS 트랜지스터(PM51)의 드레인 전극 혹은 입력단의 PMOS 트랜지스터(PM52)의 드레인 전극에 접속하는 스위칭 트랜지스터(NA4, NB4)가 부가되어 있다.

(2) 출력 단자와 전원(2) 사이에 접속되는 NMOS 트랜지스터(NM1)와 이 NMOS 트랜지스터(NM1)의 게이트 전극을 제어하는, PMOS 트랜지스터(PM4), NMOS 트랜지스터(NM2) 및 NMOS 트랜지스터(NM3)의 직렬 회로가 접속되어 있다.

이, NMOS 트랜지스터(NM1)는, 출력 단자의 전압(드레인 신호선(D)의 전압)이 차동 증폭 회로의 (+) 입력 단자에 인가되는 전압보다도 낮은 경우에 온으로 되고, 드레인 신호선(D)에 전류를 흘려 드레인 신호선(D)의 전압을 상승시킨다(소위, 오프 버퍼 기능을 실현한다).

도 22에 도시한 본 실시예의 고전압용 앰프 회로(271)는, 하기의 점에서, 도 19에 도시한 차동 증폭 회로와 상위하다.

(1) 도 21에 도시한 저전압용 앰프 회로(272)와 마찬가지로, 도 19에 도시한 차동 증폭 회로에 스위칭 트랜지스터(PA1~PA4, PB1~PB4)가 부가되어 있다.

(2) 출력 단자와 전원(1) 사이에 접속되는 PMOS 트랜지스터(PM1)와 이 PMOS 트랜지스터(PM1)의 게이트 전극을 제어하는, PMOS 트랜지스터(PM3), PMOS 트랜지스터(PM2) 및 NMOS 트랜지스터(NM4)의 직렬 회로가 접속되어 있다.

이, NMOS 트랜지스터(NM4)는, 출력 단자의 전압(드레인 신호선(D)의 전압)이 차동 증폭 회로의 (+) 입력 단자에 인가되는 전압보다도 높은 경우에 온으로 되어, 드레인 신호선(D)로부터 전류를 방출하고, 드레인 신호선(D)의 전압을 저감시킨다(소위, 오프 버퍼 기능을 실현한다).

여기서, 스위칭 트랜지스터(NA1~NA4, PA1~PA4)의 게이트 전극에는 제어 신호(A)가 인가되고, 또한, 스위칭 트랜지스터(NB1~NB4, PB1~PB4)의 게이트 전극에는 제어 신호(B)가 인가된다.

도 21에 도시한 본 실시예의 저전압용 앰프 회로(272)에 있어서, 제어 신호(A)가 H 레벨, 제어 신호(B)가 L 레벨인 경우의 회로 구성을 도 23에, 또한, 제어 신호(A)가 L 레벨, 제어 신호(B)가 H 레벨인 경우의 회로 구성을 도 24에 도시한다.

또, 도 23, 도 24에는, 도 23, 도 24에 도시한 앰프 회로를 일반의 연산 증폭기 기호를 사용하여 표현한 경우의 회로 구성도 함께 도시하고 있다.

또한, 도 23, 도 24에서는, 오프 버퍼 기능을 실현하는, NMOS 트랜지스터(NM1)와 이 NMOS 트랜지스터(NM1)의 게이트 전극을 제어하는, PMOS 트랜지스터(PM1), NMOS 트랜지스터(NM2) 및 NMOS 트랜지스터(NM3)의 직렬 회로는 생략하고 있다.

이 도 23, 도 24로부터 알 수 있는 바와 같이, 본 실시예의 저전압용 앰프 회로(272)에서는, 입력 전압( $V_{in}$ )이 인가되는 입력단의 MOS 트랜지스터와, 출력 전압( $V_{out}$ )이 피드백되는 입력단의 MOS 트랜지스터를 교대로 절환하도록 한 것이다.

그에 따라, 도 23의 회로 구성에서는, 하기의 수학식 1에 나타낸 바와 같이, 출력 전압( $V_{out}$ )은 입력 전압( $V_{in}$ )에 오프셋 전압( $V_{off}$ )이 가산되게 된다.

$$V_{out} = V_{in} + V_{off}$$

또한, 도 24의 회로 구성에서는, 하기 수학식 2에 나타낸 바와 같이, 출력 전압( $V_{out}$ )은 입력 전압( $V_{in}$ )으로부터 오프셋 전압( $V_{off}$ )이 감산된 것으로 된다.

$$V_{out} = V_{in} - V_{off}$$

도 25는 본 실시예의 드레인 드라이버(130)의 동작을 설명하기 위한 타이밍차트이다.

도 25에 도시한 출력 전압은,  $V_{ofh}$ 의 오프셋 전압을 갖는 고전압용 앰프 회로(271)와  $V_{ofl}$ 의 오프셋 전압을 갖는 저전압용 앰프 회로(272)에 접속되는 드레인 신호선(D)에 대해, 상기 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)로부터 출력되는 출력 전압을 나타낸 것이다.

이 출력 전압에 있어서,  $V_H$ 는 고전압용 앰프 회로(271)가 오프셋 전압을 갖지 않을 때에 고전압용 앰프 회로(271)로부터 출력되는 정규의 계조 전압,  $V_L$ 은 저전압용 앰프 회로(272)가 오프셋 전압을 갖지 않을 때에 저전압용 앰프 회로(272)로부터 출력되는 정규의 계조 전압이다.

또한, 도 25의 타이밍차트로 도시한 바와 같이, 제어 신호(A) 및 제어 신호(B)는 2프레임마다 그 위상이 반전된다.

따라서, 도 25에 도시한 바와 같이,  $V_{ofh}$ 의 오프셋 전압을 갖는 고전압용 앰프 회로(271)와  $V_{ofl}$ 의 오프셋 전압을 갖는 저전압용 앰프 회로(272)에 접속되는 드레인 신호선(D)에는, 첫번째 프레임의 첫번째 라인에 고전압용 앰프 회로(271)로부터 ( $V_H + V_{ofh}$ )의 전압이 출력되지만, 3번째 프레임의 첫번째 라인에 고전압용 앰프 회로(271)로부터 ( $V_H - V_{ofh}$ )의 전압이 출력되기 때문에, 대응하는 화소에 있어서, 고전압용 앰프 회로(271)의 오프셋 전압( $V_{ofh}$ )에 의해 생기는 휘도의 상승 및 감소는 상쇄된다.

또한, 두번째 프레임의 첫번째 라인에 저전압용 앰프 회로(272)로부터 ( $V_L + V_{ofl}$ )의 전압이 출력되지만, 4번째 프레임의 첫번째 라인에 저전압용 앰프 회로(272)로부터 ( $V_L - V_{ofl}$ )의 전압이 출력되기 때문에, 대응하는 화소에 있어서, 저전압용 앰프 회로(272)의 오프셋 전압( $V_{ofl}$ )에 의해 생기는 휘도의 상승 및 감소는 상쇄된다.

이에 따라, 도 26에 도시한 바와 같이, 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)의 오프셋 전압( $V_{ofh}, V_{ofl}$ )에 의해 생기는 휘도의 상승 및 감소는 연속하는 4프레임마다 상쇄되기 때문에, 도 25에 도시한 출력 전압이 인가되는 화소의 휘도는 계조 전압에 대응하는 통상의 휘도가 된다.

또, 상기 도 25에 도시한 타이밍차트에서는, 제어 신호(A) 및 제어 신호(B)의 위상을 2프레임마다 반전하도록 하였지만, 제어 신호(A) 및 제어 신호(B)의 위상을 각 프레임 내에서 2라인마다, 또한 2프레임마다 반전시키는 바와 같이 하여도 좋다. 이 경우의 화소의 휘도를 도 27, 도 28에 도시한다.

도 27은, 제어 신호(A)가 H 레벨일 때에, 고전압용 앰프 회로(271)가 (+)의 오프셋 전압( $V_{ofh}$ )을, 저전압용 앰프 회로(272)가 (-)의 오프셋 전압( $V_{ofl}$ )을 갖는 경우이다.

또한, 도 28은, 제어 신호(A)가 H 레벨일 때에, 고전압용 앰프 회로(271)가 (+)의 오프셋 전압( $V_{ofh}$ )을, 저전압용 앰프 회로(272)가 (+)의 오프셋 전압( $V_{ofl}$ )을 갖는 경우이다.

어느 경우에 있어서도, 고전압용 앰프 회로(271) 및 저전압용 앰프 회로(272)의 오프셋 전압( $V_{ofh}, V_{ofl}$ )에 의해 생기는 휘도의 상승 및 감소는 연속하는 4프레임마다 상쇄되기 때문에, 화소의 휘도는 계조 전압에 대응하는 통상의 휘도가 된다.

그러나, 제어 신호(A) 및 제어 신호(B)의 위상을 각 프레임 내에서 2 라인마다 반전시킴으로써, 도 27, 도 28에 도시한 바와 같이, 열 방향의 화소의 휘도는 2 라인마다, 흑→백(또는 백→흑)으로 변화하기 때문에, 보다 액정 표시 패널(10)에 표시되는 표시 화면 중에 세로 줄무늬가 눈에 띄지 않게 된다.

또, 도 27 또는 도 28에서는, 1 프레임 내에서 2 라인마다 제어 신호(A) 및 제어 신호(B)의 위상을 반전시켜 열 방향의 화소의 휘도를 변화시키고, 그에 따라 세로 줄무늬를 눈에 띄지 않게 하고 있지만, 2 라인마다가 아니어도 되는 것은 물론이다.

또한, 이 제어 신호(A) 및 제어 신호(B)의 절환 타이밍을 상기한 프리차아지 기간 내에 행함으로써, 불안정한 상태에 있는 각 앰프 회로(271, 272)의 출력이 각 드레인 신호선(D)으로 출력되지 않게 되므로 바람직하다.

<본 실시예에 있어서의 제어 신호(A)와 제어 신호(B)의 생성 방법>

이하, 본 실시예에 있어서, 제어 신호(A) 및 제어 신호(B)를 생성하는 방법을 설명한다.

도 29는, 본 실시예의 드레인 드라이버(130) 내의 제어 회로(152) 내의 주요부 회로 구성을 나타내는 블록도이다.

상기 도면에 도시한 바와 같이, 본 실시예의 드레인 드라이버(130) 내의 제어 회로(152) 내에는, 시프트 레지스터(153), 제어 신호 생성 회로(400), 프레임 인식 신호 생성 회로(410), 시프트 클럭 인에이블 신호 생성 회로(420), 시프트용 클럭 생성 회로(430), 펄스 생성 회로(440), 및 펄스 선택 회로(450)가 설치된다.

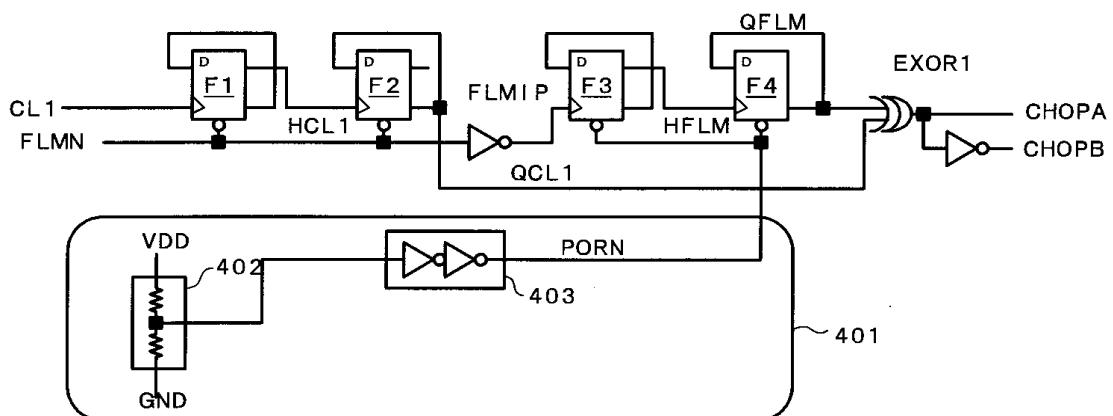

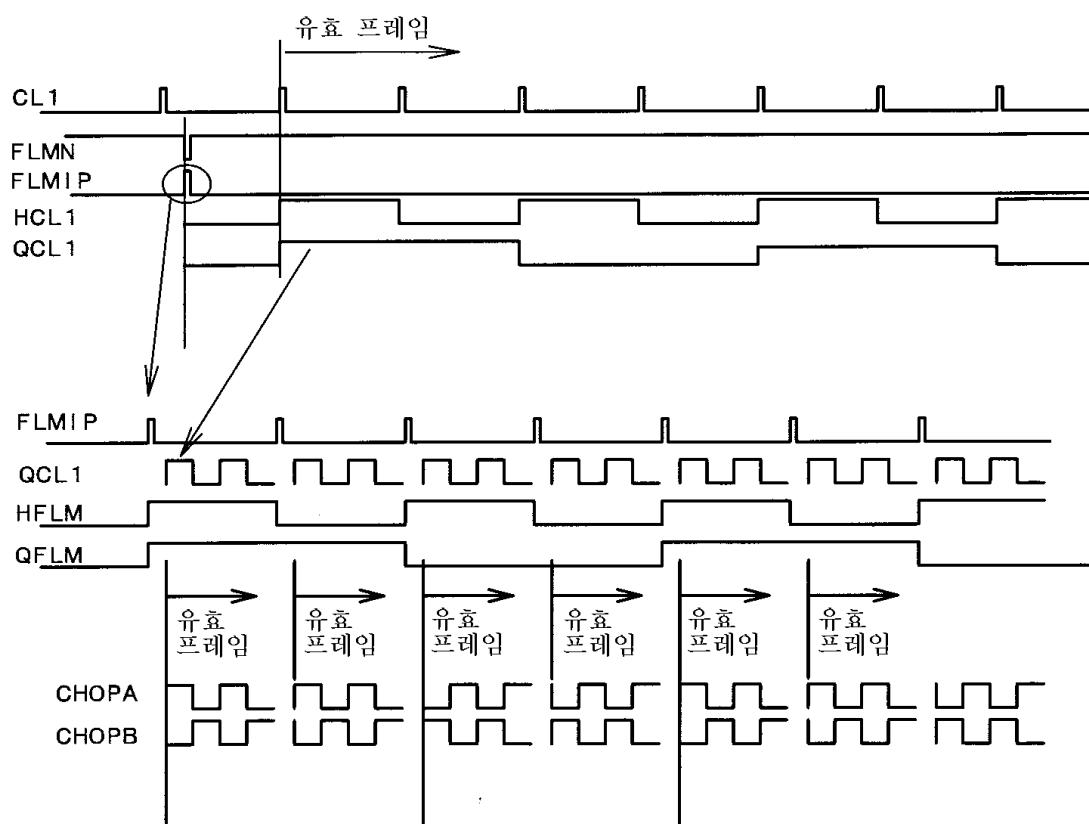

도 30은, 도 29에 도시한 제어 신호 생성 회로(400)의 회로 구성을 나타내는 회로도이며, 도 31은, 도 30에 도시한 제어 신호 생성 회로(400)의 동작을 설명하기 위한 타이밍차트이다.

제어 신호 생성 회로(400)에는 클럭(CL1)이 입력되고, 이 클럭(CL1)은, 도 31에 도시한 바와 같이, D형 플립플롭 회로(F1)에서 2분주되어 클럭(HCL1)으로 되고, 또한, 이 클럭(HCL1)은 D형 플립플롭 회로(F2)에서 2분주되어, 클럭(CL1)이 4분주된 클럭(QCL1)으로 된다.

또한, 이 제어 신호 생성 회로(400)에는, 각 프레임을 인식하기 위한 프레임 인식 신호(FLMN)가 입력된다.

또, 이 프레임 인식 신호(FLMN)의 생성 방법에 대해서는 후술한다.

프레임 인식 신호(FLMN)는 인버터(INV)로 반전되어 신호(FLMIP)로 된다.

이 신호(FLMIP)는, 도 31에 도시한 바와 같이, D형 플립플롭 회로(F3)에서 2분주되어 신호(HCL1)로 되고, 또한, 이 신호(HCL1)는 D형 플립플롭 회로(F4)에서 2분주되어, 프레임 인식 신호(FLMN)가 4분주된 신호(QFLM)로 된다.

그리고, 클럭(QCL1)과 신호(QFLM)는, 배타적 논리합 회로(EXOR1)에 입력되고, 배타적 논리합 회로(EXOR1)로부터 신호(CHOPA)가 출력되고, 이 신호(CHOPA)를 인버터(INV)로 반전함으로써 신호(CHOPB)가 생성된다.

이 신호(CHOPA, CHOPB)는 레벨 시프트 회로에서 레벨 시프트되어 제어 신호(A) 및 제어 신호(B)가 된다.

이에 따라, 제어 신호(A) 및 제어 신호(B)의 위상을 각 프레임 내에서 2라인마다 또한 2프레임마다 반전시킬 수 있다.

또, 제어 신호(A) 및 제어 신호(B)의 위상을 2프레임마다 반전시키는 경우에는, 프레임 인식 신호(FLMN)를 4분주한 신호(QFLM)를 신호(CHOPA)로 하고, 또한, 이 신호(CHOPA)를 인버터(INV)로 반전하여 신호(CHOPB)로 하면 된다.

이 경우에는, 도 30에 도시한 제어 신호 생성 회로(400)에 있어서, D형 플립플롭 회로(F1, F2) 및 배타적 논리합 회로(EXOR1)는 필요로 하지 않는다.

또한, 이 제어 신호 생성 회로(400)에서는, D형 플립플롭 회로(F1, F2)는 프레임 인식 신호(FLMN)로 초기화된다.

한편, D형 플립플롭 회로(F3, F4)는 PORN 신호 생성 회로(401)로부터의 신호(PORN)로 초기화된다.

이 PORN 신호 생성 회로(401)는 고전압의 전원 전압(VDD)을 분압하는 분압 회로(402)와 이 분압 회로(402)의 출력이 입력되는 인버터 회로군(403)으로 구성된다.

이 전원 전압(VDD)은 도 1에 도시한 전원 회로(120) 내의 DC/DC 컨버터(도시하지 않음)로 생성되는 전압이며, 이 전원 전압(VDD)은 액정 표시 장치에 전원이 투입된 시점부터 잠시 후에 상승한다.

따라서, 액정 표시 장치의 전원 투입 후, 이 PORN 신호 생성 회로(401)의 신호(PORN)는 잠시동안 L 레벨로 되기 때문에, D형 플립플롭 회로(F3, F4)는 액정 표시 장치의 전원 투입 시에 확실하게 초기화되게 된다.

#### <본 실시예에 있어서의 프레임 인식 신호의 생성 방법>

다음에, 본 실시예에 있어서, 프레임 인식 신호(FLMN)를 생성하는 방법을 설명한다.

상기 프레임 인식 신호(FLMN)를 생성하기 위해서는, 프레임의 절환을 인식하기 위한 신호가 필요하다.

그리고, 상기 게이트 드라이버(140)에는 표시 제어 장치(110)로부터 프레임 개시 지시 신호가 출력되기 때문에, 이 프레임 개시 지시 신호를 드레인 드라이버(130)에도 입력하도록 하면 프레임 인식 신호(FLMN)를 용이하게 생성하는 것이 가능해진다.

그러나, 이 방법에서는, 드레인 드라이버(130)를 구성하는 반도체 집적 회로(반도체 침)의 입력 핀수를 증가시킬 필요가 있고, 이에 따라, 프린트 배선 기판의 배선 패턴을 변경할 필요가 있다.

그리고, 프린트 배선 기판의 배선 패턴의 변경에 따라, 액정 표시 장치가 발하는 고주파 노이즈 특성이 변화하여 EMI(electro magnetic interference) 레벨 저하 등이 염려된다.

또한, 반도체 집적 회로의 입력 핀수를 증가시키는 것은 입력 핀의 호환성이 없어지게 한다.

그 때문에, 본 실시예에서는, 표시 제어 장치(110)로부터 드레인 드라이버(130)로 출력하는 시작 펄스의 폴스폭을, 각 프레임마다, 프레임 내에서 최초의 시작 펄스(이하, 프레임용 시작 펄스라 칭한다)와, 그 이외의 시작 펄스(이하, 프레임내 시작 펄스라 칭한다)와 다르게 하고, 그에 따라, 각 프레임의 절환을 인식하여 프레임 인식 신호(FLMN)를 생성하도록 하고 있다.

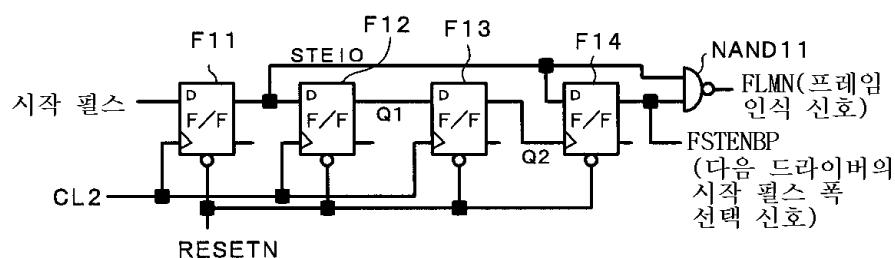

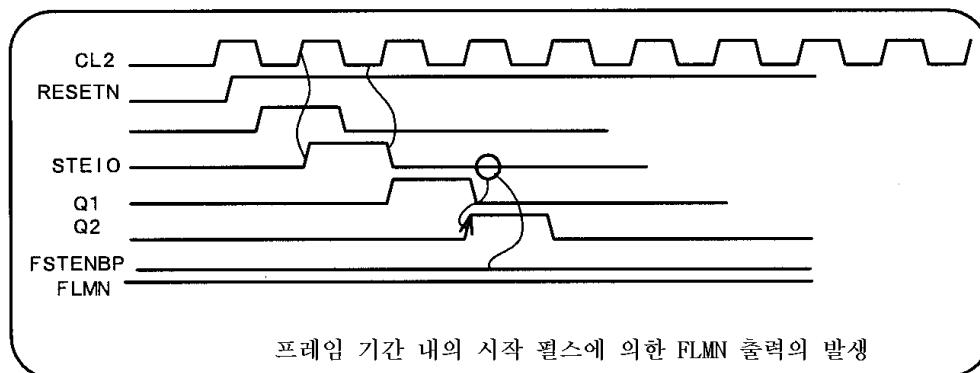

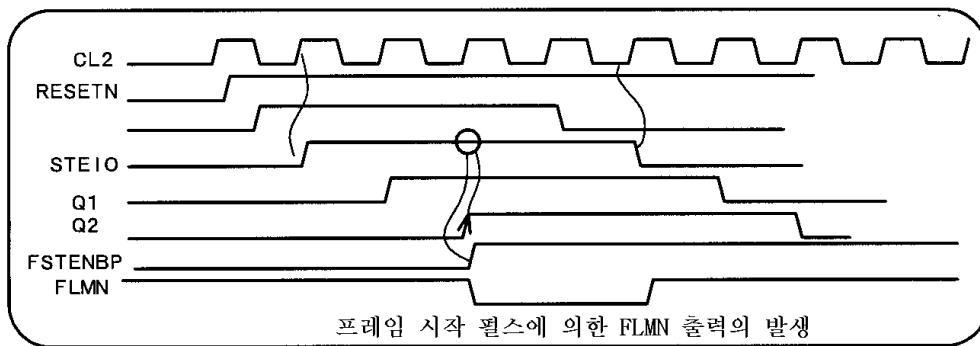

도 32는 도 29에 도시한 프레임 인식 신호 생성 회로(410)의 회로 구성을 나타내는 회로도이며, 도 33은 도 32에 도시한 프레임 인식 신호 생성 회로(410)의 동작을 설명하기 위한 타이밍차트이다.

본 실시예에서는, 프레임용 시작 펄스는 클럭 신호(CL2)의 4주기분의 폴스 폭, 프레임 내 시작 펄스는 클럭 신호(CL2)의 1주기분의 폴스 폭을 갖도록 한다.

도 32에 있어서, D형 플립플롭 회로(F11~F13)는 클럭 신호 입력 단자에 클럭(CL2)이 입력된다.

따라서, 시작 펄스는 클럭(CL2)에 동기하여 D형 플립플롭 회로(F11)에 래치되고, 신호(STE10)로 된다.

이 신호(STE10)는 클럭(CL2)에 동기하여 D형 플립플롭 회로(F12)에 래치되어, 신호(Q1)로 되고, 또한, 이 신호(Q1)는 클럭(CL2)에 동기하여 D형 플립플롭 회로(F13)에 래치되고, 신호(Q2)가 된다.

이 신호(Q2)는 D형 플립플롭 회로(F14)의 클럭 신호 입력 단자에 입력되고, 또한, D형 플립플롭 회로(F14)의 데이터 입력 단자(D)에는 신호(STE10)가 입력된다.

따라서, 시작 펄스가 클럭 신호(CL2)의 4주기분의 폴스 폭을 갖는 프레임용 시작 펄스이면, 이 D형 플립플롭 회로(F14)의 Q 출력은 H 레벨로 된다.

여기서, D형 플립플롭 회로(F14)의 Q 출력이 그 다음 드레인 드라이버용의 시작 펄스 선택 신호(FSTENBP)로 되기 때문에, 시작 펄스 선택 신호(FSTENBP)는 H 레벨로 된다.

또한, D형 플립플롭 회로(F14)의 Q 출력과 신호(STE10)는, NAND 회로(NAND11)에 입력되고, 이 NAND 회로(NAND11)의 출력이 프레임 인식 신호(FLMN)로 되기 때문에, 프레임 인식 신호(FLMN)는 클럭(CL2)의 2주기분 만큼 L 레벨로 된다.

한편, 시작 펄스가 클럭 신호(CL2)의 1주기분의 펄스 폭을 갖는 프레임 내 시작 펄스이면, 이 D형 플립플롭 회로(F14)의 Q 출력은 L 레벨로 된다.

이에 따라, 시작 펄스 선택 신호(FSTENBP)는 L 레벨로 되고, 또한, 프레임 인식 신호(FLMN)는 H 레벨을 유지한다.

또, 각 D형 플립플롭 회로(F11~F14)는 신호(RESETN)에 의해 초기화된다.

본 실시예에 있어서는, 이 신호(RESETN)로서 클럭(CL1)의 반전 신호를 사용하고 있다.

또한, 본 실시예에서는, 프레임용 시작 펄스는 클럭 신호(CL2)의 4 주기분의 펄스 폭을 갖는 경우에 대해 설명하였지만, 이것에 한정되는 것이 아니라, 프레임용 시작 펄스가 입력되었을 때에만 소정 기간 L 레벨로 되는 프레임 인식 신호(FLMN)가 생성 가능하면, 프레임용 시작 펄스의 펄스 폭은 임의로 설정 가능하다.

본 실시예에 있어서, 제1번째의 드레인 드라이버(130)에는, 표시 제어 장치(110)로부터 프레임용 시작 펄스 및 프레임내 시작 펄스가 입력되고, 상기한 동작이 행해진다.

그러나, 제2번째 이후의 드레인 드라이버(130)에는, 표시 제어 장치(110)로부터 프레임용 시작 펄스 및 프레임내 시작 펄스가 입력되지 않기 때문에, 제2번째 이후의 드레인 드라이버(130)에 있어서도, 상기한 동작을 행하게 하기 위해서는, 입력되는 시작 펄스와 동일 펄스 폭을 갖는 펄스를 시작 펄스로서, 그 다음의 드레인 드라이버(130)로 출력할 필요가 있다.

그 때문에, 본 실시예에서는, 도 29에 도시한 펄스 생성 회로(440)에서 클럭 신호(CL2)의 4 주기분의 펄스 폭을 갖는 프레임용 시작 펄스를 생성하고, 입력되는 시작 펄스가 프레임용 시작 펄스인 경우에, 상기 펄스 생성 회로(440)에서 생성된 프레임용 시작 펄스를 그 다음 드레인 드라이버(130)로 송출하도록 하고 있다.

#### <본 실시예에 있어서의 프레임용 시작 펄스의 생성 방법>

이하, 드레인 드라이버(130) 내에서, 프레임용 시작 펄스 및 프레임내 시작 펄스를 생성하는 방법에 대해 설명한다.

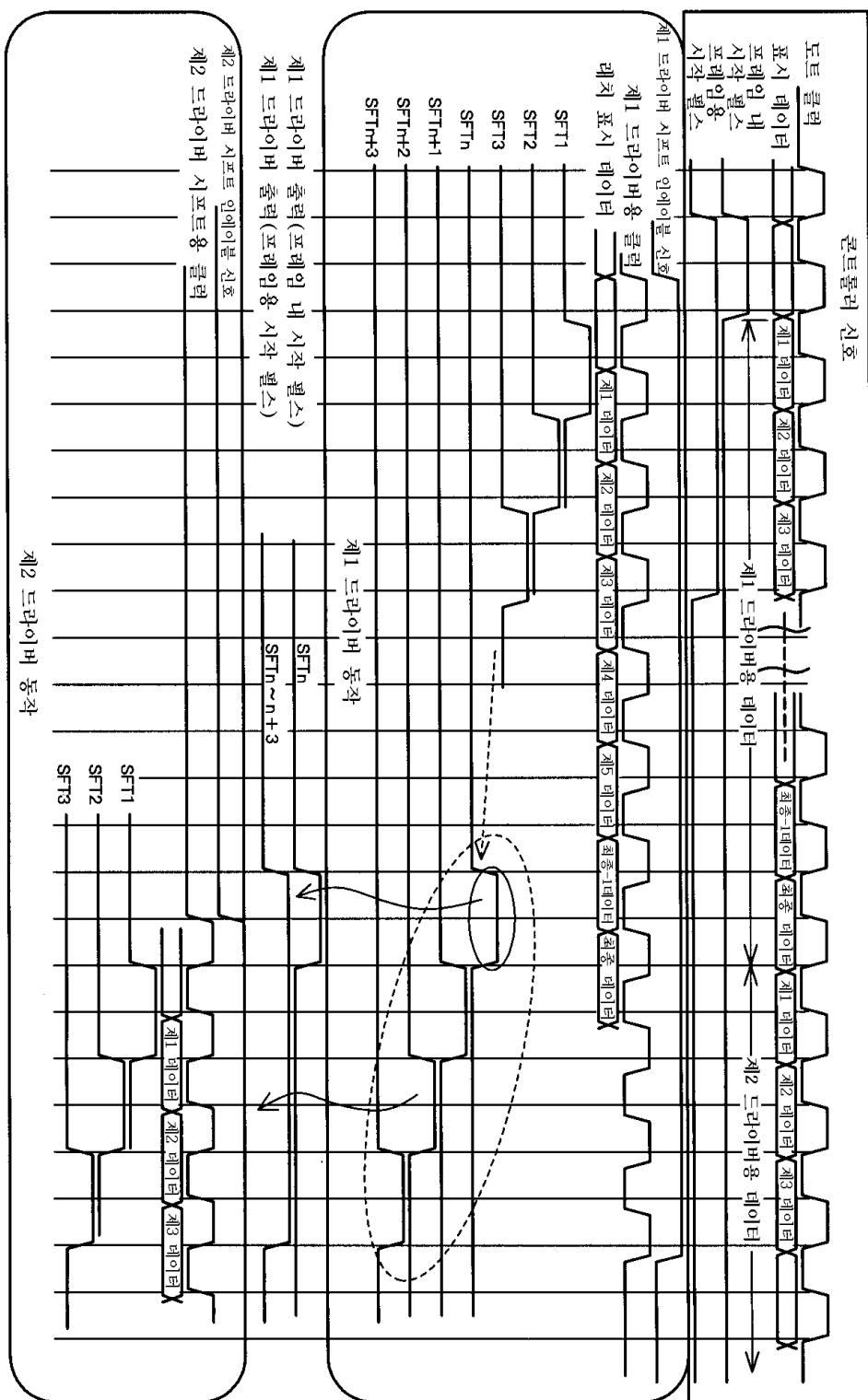

도 34는, 도 29에 도시한 본 실시예의 드레인 드라이버(130) 내의 제어 회로(152)의 동작을 설명하기 위한 타이밍차트이다.

도 34에 도시한 바와 같이, 시프트 클럭 인에이블 신호 생성 회로(420)는, 시작 펄스가 입력되면, H 레벨의 인에이블 신호(EENB)를 시프트용 클럭 생성 회로(430)로 출력한다.

이에 따라, 시프트용 클럭 생성 회로(430)는, 클럭(CL2)에 동기한 시프트용 클럭을 생성하고, 시프트 레지스터 회로(153)로 출력한다.

시프트 레지스터 회로(153)의 각 플립플롭 회로는, 데이터 수신용 신호(SFT1~SFTn+3)를 순차 출력하여, 이에 따라, 입력 레지스터(154)에 표시 데이터가 래치된다.

또한, SFTn의 데이터 수신용 신호는, 클럭(CL2)의 1주기분의 펄스 폭을 갖는 다음단의 드레인 드라이버(130)의 프레임내 시작 펄스로 된다.

여기서, SFT1~SFTn의 데이터 수신용 신호는 입력 레지스터(154)에 1번재~n번재의 표시 데이터를 래치하기 위해 사용되지만, SFTn+1~SFTn+3의 데이터 수신용 신호는 입력 레지스터(154)에 표시 데이터를 래치하기 위해서는 사용되지 않는다.

이 SFTn+1~SFTn+3의 데이터 수신용 신호는 다음단의 드레인 드라이버(130)의 프레임용 시작 펄스를 생성하기 위해 사용된다.

즉, 도 34에 도시한 바와 같이, 클럭 생성 회로(450)에서, SFTn~SFTn+3의 데이터 수신용 신호에 기초하여, 클럭(CL2)의 4주기분의 펄스 폭을 갖는 프레임용 시작 펄스를 생성한다.

상기한 바와 같이, 시작 펄스가 프레임내 시작 펄스이면, 시작 펄스 선택 신호(FSTENBP)는 L 레벨로 되기 때문에, 펄스 선택 회로(450)는 프레임 내 시작 펄스(즉, SFTn의 데이터 수신용 신호)를 선택하고, 그 다음 드레인 드라이버(130)로 출력한다.

한편, 시작 펄스가 프레임용 시작 펄스이면, 시작 펄스 선택 신호(FSTENBP)는 H 레벨이기 때문에, 펄스 선택 회로(450)는 프레임용 시작 펄스를 선택하여 그 다음 드레인 드라이버(130)로 출력한다.

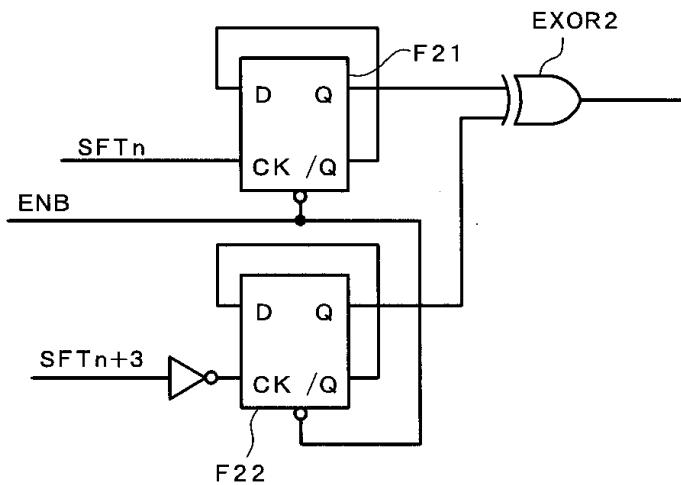

여기서, 클럭 생성 회로(450)에서는, 예를 들면, 도 35에 도시한 바와 같은것이 사용 가능하다.

이 도 35에 도시한 클럭 생성 회로(450)는, SFTn의 데이터 수신용 신호에 기초하여, D형 플립플롭 회로(F21)의 Q 출력을 반전시키고, 또한, 인버터(INV)로 반전된 SFTn+3의 데이터 수신용 신호에 기초하여, D형 플립플롭 회로(F22)의 Q출력을 반전시킨다.

또한, D형 플립플롭 회로(F21)와 D형 플립플롭 회로(F22)의 Q출력을 배타적논리합 회로(EXOR2)에 입력하고, 이 배타적 논리합 회로(EXOR2)로부터 클럭(CL2)의 4 주기분의 펄스 폭을 갖는 프레임용 시작 펄스를 생성하도록 한 것이다.

이와 같이, 본 실시예에서는, 각 드레인 드라이버(130) 내에서, 프레임용 시작 펄스와, 프레임내 시작 펄스를 생성하도록 하였기 때문에, 이에 따라, 드레인 드라이버(130)를 구성하는 반도체 집적 회로의 입력 핀수를 증가시키지 않고, 입력 핀의 호환성을 유지한 상태 그대로, 각 드레인 드라이버(130)에 있어서, 각 프레임의 절환을 인식하는 것이 가능해진다.

#### <본 실시예의 앰프 회로의 변형예>

예를 들면, 도 21에 도시한 저전압용 앰프 회로(272)에서는, 그 특성상, 출력 단자의 전압을 전원(1)의 전압

으로 하는 것은 곤란하다.

마찬가지로, 도 22에 도시한 고전압용 앰프 회로(271)에서는, 출력 단자의 전압을 전원(2)의 전압으로 하는 것은 곤란하다.

따라서, 이 전원(1)의 전압, 혹은 전원(2)의 전압이 64계조의 계조 전압 중 하나이면, 이 계조 전압을 드레인 신호선(D)으로 출력하는 것은 곤란해진다.

도 36은, 본 발명의 실시예의 앰프 회로의 변형예를 나타낸 회로도이다.

또, 이 도 36에서는, 1계통의 출력만 나타내고, 또한, 도 7에 도시한 프리차아지 회로(30) 및 도 6에 도시한 스위치부(2)264는 생략하고 있다.

즉, 도 36에 있어서, 디코더 회로(31)는 도 6에 도시한 고전압용 디코더 회로(278) 또는 저전압용 디코더 회로(279)를, 앰프 회로(32)는 도 6에 도시한 고전압용 앰프 회로(271) 또는 저전압용 앰프 회로(272)를 나타내고 있다.

일반적으로, 전원(1)의 전압 혹은 전원(2)의 전압의 계조 전압은, 표시 데이터의 비트값이 전부「0」, 혹은 전부「1」의 경우에 상당한다.

그래서, 도 36에 도시한 앰프 회로에서는 표시 데이터의 비트값이 전부「1」인 경우를 NAND 회로(NAND41)로 검출하고, 이에 따라, 드레인 신호선(D)에 전원(2)의 전압을 출력하도록 한 것이다.

즉, 표시 데이터의 비트값이 전부「1」인 경우, NAND 회로(NAND41)의 출력이 L 레벨로 되고, 이 L 레벨이 인버터(INV31)로 반전되어 H 레벨로 되어, PMOS 트랜지스터(PM31)의 소스 전극에 인가되고, PMOS 트랜지스터(PM31)가 온으로 되고, 드레인 신호선(D)에 전원(2)의 전압이 공급된다.

마찬가지로, 표시 데이터의 비트값이 전부「0」인 경우, NOR 회로(NOR41)의 출력이 H 레벨로 되고, 이 H 레벨이 인버터(INV32)로 반전되어 L 레벨로 되어, NMOS 트랜지스터(NM31)의 소스 전극에 인가되고, NMOS 트랜지스터(NM31)가 온으로 되고, 드레인 신호선(D)에 전원(1)의 전압이 공급된다.

또, 인버터(INV31, INV32)의 전원 전압은 전원(1)의 전압 및 전원(2)의 전압인 것은 물론이다.

또한, 인버터(INV31, INV32)의 전원 전압을 바꿈으로써, 표시 데이터의 비트값이 전부「0」, 및「1」인 경우에 드레인 신호선(D)에 공급하는 구동 전압을 바꾸는 것도 가능하다.

또한, 표시 데이터의 비트값이 전부「1」인 경우를 AND 회로(AND41)에서, 또한, 표시 데이터의 비트값이 전부「0」인 경우를 NOR 회로(NOR42)에서 검출하고, 이 AND 회로(AND41)와 NOR회로(NOR42)의 출력을 OR 회로(OR41)를 통해 트랜스퍼 게이트 회로(TG41)에 입력함으로써, 앰프 회로(32)를 드레인 신호선(D)으로부터 분리하도록 하고 있다.

이와 같이, 도 36에 도시한 앰프 회로에서는, 64계조의 계조 전압 중의, 예를 들면, 표시 데이터의 비트값이 전부「1」인 경우의 최상위 계조 전압, 및, 예를 들면, 표시 데이터의 비트값이 전부「0」인 경우의 최하위 계조 전압이 전원 전압인 경우에, 이 계조 전압을 드레인 신호선(D)으로 확실하게 출력할 수가 있다.

이 도 36에 도시한 앰프 회로에서는, 표시 데이터의 비트값이 전부「1」 및 전부「0」인 경우에 트랜스퍼 게이트 회로(TG41)가 오프로 되기 때문에, 이 기간에 앰프 회로(32)의 동작을 정지시킴으로써 소비 전력을 저감시키는 것도 가능하다.

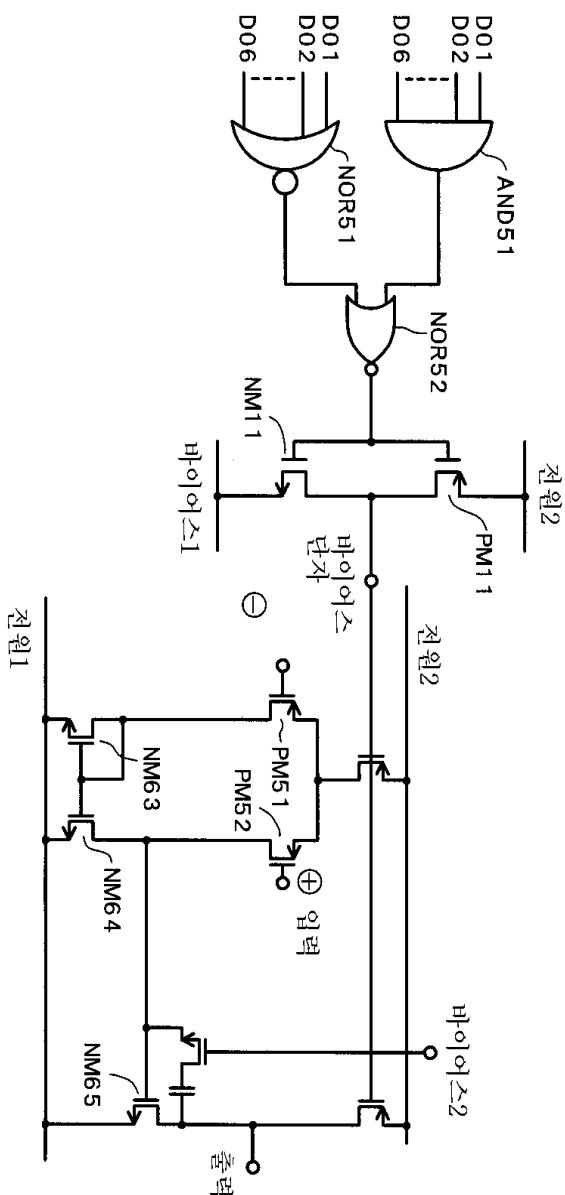

이것은, 예를 들면, 앰프 회로(232)가 도 18에 도시한 회로 구성의 앰프 회로인 경우에는, 도 37에 도시한 회로 구성으로 가능해진다.

이 도 37에 도시한 회로에서는, 표시 데이터의 비트값이 전부「1」인 경우를 AND 회로(AND51)에서, 또한, 표시 데이터의 비트값이 전부「0」인 경우를 NOR회로(NOR51)에서 검출하고, 이 AND 회로(AND51)와 NOR회로(NOR51)의 출력을 NOR 회로(NOR52)를 통해 PMOS 트랜지스터(PM11)의 게이트 전극 및 NMOS 트랜지스터(MM11)의 게이트 전극에 인가하도록 한 것이다.

따라서, 도 37에 도시한 회로에서는, 표시 데이터의 비트값이 전부「1」 및 전부「0」인 경우에 NOR 회로(NOR52)가「0」으로 되기 때문에, 이 경우에는, PMOS 트랜지스터(PM11)가 온으로 되어 앰프 회로(32)의 바이어스 단자에 전원(2)이 인가되기 때문에, 앰프 회로(32)의 동작이 정지한다.

또한, 표시 데이터의 비트값이 전부「1」 및 전부「0」인 경우 이외에는, NOR회로(NOR52)가「1」로 되기 때문에, 이 경우에는, NMOS 트랜지스터(NM11)가 온으로 되어 앰프 회로(32)의 바이어스 단자에 바이어스(1)가 인가되기 때문에, 앰프 회로(32)는 통상의 동작을 행한다.

또, 상기 설명에서는, 종전계 방식의 액정 표시 패널에 본 발명을 적용한 실시예에 대해 설명하였지만, 이것에 한정되지 않고, 본 발명은, 횡전계 방식의 액정 표시 패널에도 적용 가능하다.

도 38은, 횡전계 방식의 액정 표시 패널의 등가 회로를 나타내는 도면이다.

도 2 또는 도 3에 도시한 종전계 방식의 액정 표시 패널에서는, 컬러 필터 기판에 공통 전극[IT0(2)]이 설치되어하는데 반하여, 횡전계 방식의 액정 표시 패널에서는 TFT 기판에 대향 전극(CT), 및 대향 전극(CT)에 구동 전압(VCOM)을 인가하기 위한 대향 전극 신호선(CL)이 설치된다.

그 때문에, 액정 용량(Cpix)은 화소 전극(PX)과 대향 전극(CT) 사이에 등가적으로 접속된다. 또한, 화소 전극(PX)과 대향 전극(CT) 사이에는 축적 용량(Cstg)도 형성된다.

또한, 상기 각 실시예에서는, 구동 방법으로서 도트 반전 방식이 적용되는 실시예에 대해 설명하였지만, 이것에 한정되지 않고, 본 발명은, 1라인마다 혹은 1프레임마다, 화소 전극[IT0(1)] 및 공통 전극[IT0(2)]에 인가하는 구동 전압을 반전하는 공통 반전법에도 적용 가능하다.

이상, 본 발명자에 의해 이루어진 발명을 상기 발명의 실시예에 기초하여 구체적으로 설명하였지만, 본 발명은, 상기 발명의 실시예에 한정되는 것이 아니라, 그 요지를 일탈하지 않은 범위에서 여러 가지로 변경 가능한 것은 물론이다.

### **발명의 효과**

본원에 있어서 개시되는 발명 중 대표적인 것에 의해서 얻어지는 효과를 간단히 설명하면, 이하와 같다.

- (1) 본 발명에 따르면, 영상 신호선 구동 수단을 구성하는 반도체 집적 회로 장치의 출력 지연 시간(tDD)을 적게 할 수 있기 때문에, 액정 표시 소자에 표시되는 표시 화면의 표시 품질을 향상시키는 것이 가능해진다.

- (2) 본 발명에 따르면, 영상 신호선 구동 수단을 구성하는 반도체 집적 회로 장치의 출력 지연 시간(tDD)을 적게 할 수 있기 때문에, 고속 동작이 가능해져서, 액정 표시 소자의 대화면화가 가능해진다.

- (3) 본 발명에 따르면, 영상 신호선 구동 수단을 구성하는 반도체 집적 회로 장치 내의 앰프 회로의 오프셋 전압에 의해, 액정 표시 소자의 표시 화면 중에 흑색 또는 백색의 세로 줄무늬가 생기는 것을 방지하여, 액정 표시 소자에 표시되는 표시 화면의 표시 품질을 향상시키는 것이 가능해진다.

### **(57) 청구의 범위**

#### **청구항 1**

복수의 화소와, 상기 복수의 화소에 표시 데이터에 대응하는 계조 전압을 인가하는 복수의 영상 신호선을 갖는 액정 표시 소자와,

적어도 1개의 반도체 집적 회로 장치로 구성되고, 상기 각 영상 신호선에 표시 데이터에 대응하는 계조 전압을 공급하는 영상 신호선 구동 수단을 포함하는 액정 표시 장치에 있어서,

상기 반도체 집적 회로 장치는,

상기 반도체 집적 회로 장치 중의 최소 사이즈의 트랜지스터로 구성되고, 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하는 복수의 계조 전압 선택 수단과;

상기 각 계조 전압 선택 수단에서 선택된 계조 전압을 증폭하여 각 영상 신호선에 출력하는 복수의 앰프 회로와;

상기 각 계조 전압 선택 수단과 상기 각 앰프 회로 사이에 설치되는 제1 스위칭 수단과;

소정의 충전 전압이 공급되는 전원선과, 상기 각 앰프 회로 사이에 설치되는 제2 스위칭 수단과;

1 수평 주사 기간의 처음의 소정 기간 내에 상기 제1 스위칭 수단을 오프로 하고, 또한, 상기 제2 스위칭 수단을 온으로 하는 스위칭 제어 수단

을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 2**

복수의 화소와, 상기 복수의 화소에 표시 데이터에 대응하는 계조 전압을 인가하는 복수의 영상 신호선을 포함하는 액정 표시 소자와,

적어도 1개의 반도체 집적 회로 장치로 구성되고, 상기 각 영상 신호선에 표시 데이터에 대응하는 계조 전압을 공급하는 영상 신호선 구동 수단을 포함하는 액정 표시 장치에 있어서,

상기 반도체 집적 회로 장치는,

상기 반도체 집적 회로 장치 중에서 최소 사이즈의 트랜지스터로 구성되고, 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하는 복수의 계조 전압 선택 수단과;

상기 각 계조 전압 선택 수단에서 선택된 계조 전압을 증폭하여 각 영상 신호선으로 출력하는 복수의 앰프 회로로서, 상기 각 앰프 회로가 한쌍의 입력 단자 중의 한쪽을 반전 입력 단자 혹은 비반전 입력 단자로, 한쌍의 입력 단자 중의 다른쪽을 비반전 입력 단자 혹은 반전 입력 단자로 절환하는 절환 수단을 포함하는 복수의 앰프 회로와;

상기 각 계조 전압 선택 수단과 상기 각 앰프 회로 사이에 설치되는 제1 스위칭 수단과;

소정의 충전 전압이 공급되는 전원선과, 상기 각 앰프 회로 사이에 설치되는 제2 스위칭 수단과;

1 수평 주사 기간의 처음의 소정 기간 내에 상기 제1 스위칭 수단을 오프로 하고, 또한, 상기 제2 스위칭 수단을 온으로 하는 스위칭 제어 수단과;

상기 앰프 회로의 한쌍의 입력 단자의 한쪽을 반전 입력 단자, 다른쪽을 비반전 입력 단자로, 혹은 상기 앰프 회로의 한쌍의 입력 단자의 한쪽을 비반전 입력 단자, 다른쪽을 반전 입력 단자로 절환하게 하는 절환 제어 신호를 소정의 주기마다 상기 앰프 회로의 절환 수단에 대해 출력하는 절환 지시 수단

을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 3**

제1항에 있어서,

상기 스위칭 제어 수단은 상기 제2 스위칭 수단을 온으로 하기 전에 상기 제1 스위칭 수단을 오프로 하고, 또한, 상기 제2 스위칭 수단을 오프로 한 후에 상기 제1 스위칭 수단을 온으로 하는 것을 특징으로 하는 액정

표시 장치.

#### **청구항 4**

제1항에 있어서,

상기 스위칭 제어 수단은 출력 타이밍 제어용 클럭 및 표시 데이터 래치용 클럭에 기초하여, 상기 제1 및 제2 스위칭 수단을 제어하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 5**

제1항에 있어서,

상기 소정의 충전 전압은 상기 복수의 계조 전압 중 어느 하나의 전압인 것을 특징으로 하는 액정 표시 장치.

#### **청구항 6**

제1항에 있어서,

상기 반도체 집적 회로 장치는 외부로부터 공급되는 복수의 계조 기준 전압에 기초하여 복수의 계조 전압을 생성하여 상기 각 계조 전압 선택 수단에 공급하는 계조 전압 생성 수단을 포함하고,

상기소정의 충전 전압은 상기 외부로부터 공급되는 복수의 계조 기준 전압 중 어느 하나의 전압인 것을 특징으로 하는 액정 표시 장치.

#### **청구항 7**

제1항에 있어서,

상기 복수의 화소의 액정층의 한쪽에 인가되는 상기 복수의 계조 전압 중에서, 상기 복수의 화소의 액정층의 다른쪽에 인가되는 대향 전압에 대해 가장 전위차가 큰 계조 전압을 최대 계조 전압, 상기 대향 전압에 대해 가장 전위차가 작은 계조 전압을 최소 계조 전압으로 할 때,

상기 소정의 충전 전압은 상기 최대 계조 전압과 최소 계조 전압 사이의 중간 전압보다도 상기 최대 계조 전압 쪽에 가까운 전압인 것을 특징으로 하는 액정 표시 장치.

#### **청구항 8**

제1항에 있어서,

상기 복수의 앰프 회로는 한쌍이 정극성의 계조 전압을 출력하는 제1 앰프 회로와 부극성의 계조 전압을 출력하는 제2 앰프 회로로 구성되는 여러쌍의 앰프 회로쌍으로 구성되며,

상기 각 앰프 회로쌍의 제1 앰프 회로와 접속되는 계조 전압 선택 수단은 정극성의 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하고,

또한, 상기 각 앰프 회로쌍의 제2 앰프 회로와 접속되는 계조 전압 선택 수단은 부극성의 복수의 계조 전압 중에서 입력될 표시 데이터에 대응하는 계조 전압을 선택하며,

또한, 상기 각 앰프 회로쌍의 제1 앰프 회로와 접속되는 계조 전압 선택 수단 및 상기 각 앰프 회로쌍의 제2 앰프 회로와 접속되는 계조 전압 선택 수단에 입력되는 임의의 한쌍의 표시 데이터를 교대로 절환하는 표시 데이터 절환 수단과,

상기 각 앰프 회로쌍으로부터 출력되는 한쌍의 계조 전압을 상기 표시 데이터 절환 수단에서의 절환에 따라 교대로 절환하여 임의의 한쌍의 영상 신호선으로 출력하는 영상 신호선 절환 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 9**

제8항에 있어서,

상기 제1 앰프 회로는, 상기 제1 앰프 회로에 접속되는 영상 신호선의 전압이 상기 제1 앰프 회로에 입력되는 정극성의 계조 전압보다 고전압인 경우에, 상기 제1 앰프 회로에 접속되는 영상 신호선으로부터 전류를 유입시키는 전류 유입 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 10**

제8항에 있어서,

상기 제2 앰프 회로는, 상기 제2 앰프 회로에 접속되는 영상 신호선의 전압이 상기 제2 앰프 회로에 입력되는 부극성의 계조 전압보다 저전압인 경우에, 상기 제2 앰프 회로에 접속되는 영상 신호선에 전류를 공급하는 전류 공급 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### **청구항 11**

제2항에 있어서,

상기 각 앰프 회로는 차동 증폭 회로로 구성되며,

상기 절환 수단은,

입력단의 한쌍의 트랜지스터 중 한쪽의 트랜지스터의 제어 전극을 상기 한쌍의 입력 단자 중의 한쪽에 접속하는 제1 스위칭 소자와;

상기 입력단의 한쌍의 트랜지스터 중 한쪽의 트랜지스터의 제어 전극을 상기 한쌍의 입력 단자 중의 다른쪽에 접속하는 제2 스위칭 소자와;

상기 입력단의 한쌍의 트랜지스터 중 다른쪽의 트랜지스터의 제어 전극을 상기 한쌍의 입력 단자 중의 다른쪽에 접속하는 제3 스위칭 소자와;

상기 입력단의 한쌍의 트랜지스터 중 다른쪽의 트랜지스터의 제어 전극을 상기 한쌍의 입력 단자 중의 한쪽에 접속하는 제4 스위칭 소자와;

출력단의 트랜지스터의 제어 전극을 상기 입력단의 한쌍의 트랜지스터 중 다른쪽의 트랜지스터의 제2 전극에 접속하는 제5 스위칭 소자와;

출력단의 트랜지스터의 제어 전극을 상기 입력단의 한쌍의 트랜지스터 중 한쪽의 트랜지스터의 제2 전극에 접속하는 제6 스위칭 소자와;

능동 부하 회로를 구성하는 한쌍의 트랜지스터의 제어 전극을 상기 입력단의 한쌍의 트랜지스터 중 한쪽의 트랜지스터의 제2 전극에 접속하는 제7 스위칭 소자와;

능동 부하 회로를 구성하는 한쌍의 트랜지스터의 제어 전극을 상기 입력단의 한쌍의 트랜지스터 중 다른쪽의 트랜지스터의 제2 전극에 접속하는 제8 스위칭 소자;

를 포함하고,

상기 제1 스위칭 소자, 제3 스위칭 소자, 제5 스위칭 소자, 및 제7 스위칭 소자와, 상기 제2 스위칭 소자, 제4 스위칭 소자, 제6 스위칭 소자, 및 제8 스위칭 소자는, 상기 절환 지시 수단으로부터 소정의 주기마다 출력되는 절환 제어 신호에 의해, 교대로 온 혹은 오프로 되는 것을 특징으로 하는 액정 표시 장치.

### **청구항 12**

제2항에 있어서,

상기 절환 지시 수단은, 상기 각 앰프 회로의 절환 수단에 대해, n 프레임마다 상기 절환 제어 신호를 출력하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 13**

제12항에 있어서,

상기 반도체 집적 회로 장치는, 입력되는 표시 데이터 수신 개시 신호의 하이 레벨 기간 혹은 로우 레벨 기간의 차이에 의해 각 프레임의 절환을 검출하여 프레임 절환 신호를 출력하는 프레임 절환 검출 수단을 가지고,

상기 절환 지시 수단은 상기 프레임 절환 검출 수단으로부터의 프레임 절환 신호에 기초하여 상기 각 앰프 회로의 절환 수단에 대해 상기 절환 제어 신호를 출력하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 14**

제2항에 있어서,

상기 절환 지시 수단은, 상기 각 앰프 회로의 절환 수단에 대해, 각 프레임 내에서 n라인마다, 또한 n프레임마다 상기 절환 제어 신호를 출력하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 15**

제14항에 있어서,

상기 반도체 집적 회로 장치는, 입력되는 표시 데이터 수신 개시 신호의 하이 레벨 기간 혹은 로우 레벨 기간의 차이에 의해, 각 프레임의 절환을 검출하여 프레임 절환 신호를 출력하는 프레임 절환 검출 수단을 포함하며,

상기 절환 지시 수단은, 상기 프레임 절환 검출 수단으로부터의 프레임 절환 신호 및 출력 타이밍 제어용의 클럭에 기초하여, 상기 각 앰프 회로의 절환 수단에 대해, 상기 절환 제어 신호를 출력하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 16**

제13항에 있어서,

상기 반도체 집적 회로 장치는, 입력되는 표시 데이터 수신 개시 신호에 기초하여, 하이 레벨 기간 혹은 로우 레벨 기간이 상위한 표시 데이터 수신 개시 신호를 생성·출력하는 표시 데이터 수신 개시 신호 생성 수단을 더 포함하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 17**

제2항에 있어서,

상기 절환 지시 수단은, 상기 1 수평 주사 기간의 처음의 소정 기간 내에 상기 절환 제어 신호를 상기 각 앰프 회로의 절환 수단에 대해 출력하는 것을 특징으로 하는 액정 표시 장치.

### **청구항 18**

제7항에 있어서,

상기 각 앰프 회로는 전압 플로워 회로로 구성되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 19

제1항에 있어서,

상기 표시 데이터의 각 비트값이 전부 「1」 혹은 전부 「0」 인 경우에, 상기 표시 데이터에 대응하는 계조 전압을 출력하고, 각 앰프 회로에 접속되는 영상 신호선에 공급하는 특정 계조 전압 생성 수단;

상기 각 앰프 회로와 상기 각 영상 신호선 사이에 설치되고, 상기 표시 데이터의 각 비트값이 전부 「1」 혹은 전부 「0」 인 경우에, 상기 각 앰프 회로를 상기 각 영상 신호선으로부터 분리하는 제3 스위칭 수단

을 포함하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 20

제19항에 있어서,

상기 특정 계조 전압 생성 수단은 상기 표시 데이터의 각 비트값이 전부 「1」 혹은 전부 「0」 인 경우의 계조 전압을 전원 전압으로 하고,

상기 표시 데이터의 각 비트값이 전부 「1」 혹은 전부 「0」 인 경우에, H 레벨 혹은 L 레벨의 신호를 출력하는 논리 회로로 구성되는 것을 특징으로 하는 액정 표시 장치.

## 도면

도면1

도면2

도면3

도면4

홀수 프레임

짝수 프레임

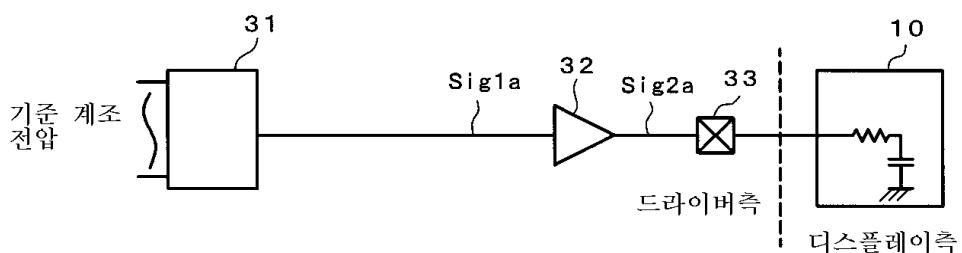

## 도면5

도면6

도연7

도면8a

도면8b

도면9

N 채널 MOS

P 채널 MOS

N 채널 MOS

P 채널 MOS

도면 10a

도면 10b

본 발명

도면11

도면12

도면13

도면14

도면15

도면16a

도면 16b

도면 17

도면 18

도면 19

도면20

$V_{out} = V_{in}$  (옵셋 전압이 없는 경우)

$$V_{out} = V_{in} + V_{off} \quad (\text{옵셋 전압이 있는 경우})$$

도면21

도면22

고전위측 앰프 회로

도면23

도면24

도면25

## 도면26

도면27

## 도면28

도면29

도면30

도면31

도면32

## 도면33

도면34

도면35

도면36

도면37

도면38

|                |                                                                              |         |            |

|----------------|------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                        |         |            |

| 公开(公告)号        | KR1020010015252A                                                             | 公开(公告)日 | 2001-02-26 |

| 申请号            | KR1020000039126                                                              | 申请日     | 2000-07-08 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA<br>日立器件工程株式会社                                        |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>히타치디바이스엔지니어링가부시키가이샤                                             |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>히타치디바이스엔지니어링가부시키가이샤                                             |         |            |

| [标]发明人         | ITO SHIGERU<br>이또우 시게루<br>KATAOKA NOBORU<br>가따오까노보루<br>OGURA AKIRA<br>오구라아끼라 |         |            |

| 发明人            | 이또우 시게루<br>가따오까노보루<br>오구라아끼라                                                 |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G G09G3/20 G02F                                        |         |            |

| CPC分类号         | G09G2320/0233 G09G3/3688                                                     |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                               |         |            |

| 优先权            | 1999196212 1999-07-09 JP                                                     |         |            |

| 其他公开文献         | KR100343922B1                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                    |         |            |

## 摘要(译)

提高在液晶显示元件和锡金同时显示的显示画面，能够进行高速动作的显示质量，并提供了一个液晶显示设备，其能够在大屏幕的液晶显示元件的。的液晶显示元件中，在一个半导体集成电路装置配置的至少，集成在包括视频信号线驱动器的液晶显示装置的半导体装置，用于提供对应于数据显示到所述液晶显示元件的各视频信号线的灰阶电压，电路装置，放大从所述多个灰度电压选择装置选择的灰阶电压，每个灰度电压选择的装置，用于选择对应于显示从所述多个多个输出，每个视频信号线的灰阶电压的输入数据的灰度级电压放大器电路和预充电控制电路设置在每个灰度电压选择装置和每个放大器电路之间。 7 指数方面 液晶显示装置，灰度电压，prascia，大屏幕，视频信号