**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

*G09G 3/36* (2006.01)*G09G 3/20* (2006.01)*G02F 1/133* (2006.01)

(45) 공고일자

2006년12월06일

(11) 등록번호

10-0653754

(24) 등록일자

2006년11월28일

(21) 출원번호

10-2006-0068388(분할)

(65) 공개번호

10-2006-0088873

(22) 출원일자

2006년07월21일

(43) 공개일자

2006년08월07일

심사청구일자

2006년07월21일

(62) 원출원

특허10-1999-0046288

원출원일자 : 1999년10월25일

심사청구일자

2004년01월05일

(30) 우선권주장

JP-P-1998-00304923

1998년10월27일

일본(JP)

JP-P-1998-00355875

1998년12월15일

일본(JP)

JP-P-1999-00217333

1999년07월30일

일본(JP)

(73) 특허권자

샤프 가부시키가이샤

일본 오사카후 오사카시 아베노구 나가이께 쪽 22방 22고

(72) 발명자

히라끼 가쓰요시

일본국 가나가와肯 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

이또 다까에

일본국 가나가와肯 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

스즈끼 도시아끼

일본국 가나가와肯 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

하야시모또 세이지

일본국 가나가와肯 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

미야하라 마사끼

일본국 가나가와肯 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

미네무라 도시미쓰

일본국 가나가와Ken 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

가파가와 고이찌

일본국 가나가와Ken 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

세끼도 사또시

일본국 가나가와켄 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

후루꼬시 야스따께

일본국 가나가와켄 가와사키시 나가하라구 가미고다나카 4-1-1후지쓰

가부시키가이샤 내

(74) 대리인

문두현

문기상

심사관 : 이병우

전체 청구항 수 : 총 2 항

#### (54) 표시 패널의 구동 회로 및 액정 표시 장치

##### (57) 요약

비교적 간단한 회로 구성으로 플리커의 발생을 저감 또는 방지할 수 있는 표시 패널의 구동 방법, 구동 회로 및 액정 표시 장치를 제공한다.

극성 패턴 제어부(32)내의 ROM에 극성 패턴(극성 패턴 신호(POL))을 기억해 둔다. 그리고, 액정 표시 패널의 용도에 따라 극성 패턴을 변경한다. 극성 패턴은 ROM에 기억하고 있으므로, 하드웨어를 변경하는 일이 없이 극성 패턴을 변경할 수 있다. 또, ROM에 2조 이상의 극성 패턴을 기억해 두고, 용도에 따라 어느 한쪽의 극성 패턴을 출력한다. 또한, ROM으로부터 출력된 극성 패턴 신호(POL)와 화상 신호(RGB)를 비교하고, 그 결과에 따라 ROM으로부터 판독하는 극성 패턴을 전환한다.

##### 대표도

도 5

#### 특허청구의 범위

##### 청구항 1.

화상 신호, 수평 동기 신호 및 수직 동기 신호, 또는 인에이블 신호를 입력하여, 표시 패널의 각 데이터 버스 라인에 상기 화상 신호로부터 생성한 정극성 및 부극성으로 변화하는 데이터 신호를 공급하는 표시 패널의 구동 회로에 있어서,

다른 복수의 극성 패턴을 발생시키는 극성 패턴 발생부와,

상기 극성 패턴 발생부로부터 출력하는 극성 패턴을 결정하기 위한 선택 신호를 발생하는 선택 신호 발생부와,

상기 극성 패턴 발생부로부터 출력된 극성 패턴의 각 비트의 논리값을 1수평 동기 기간마다 및 1수직 동기 기간마다 반전 시켜서 극성 신호로서 출력하는 극성 신호 반전부와,

상기 화상 신호를 입력하여, 상기 극성 신호에 따른 극성에 의해 상기 데이터 신호를 출력하는 데이터 신호 출력부를 갖는 것을 특징으로 하는 표시 패널의 구동 회로.

##### 청구항 2.

(i) 액정 표시 패널과,

(ii) 다른 복수의 극성 패턴을 발생시키는 극성 패턴 발생부와, 상기 극성 패턴 발생부로부터 출력하는 극성 패턴을 결정하기 위한 선택 신호를 발생하는 선택 신호 발생부와, 상기 극성 패턴 발생부로부터 출력된 극성 패턴의 각 비트의 논리값을 1수평 동기 기간마다 및 1수직 동기 기간마다 반전시켜 극성 신호로서 출력하는 극성 신호 반전부와, 화상 신호를 입력하여 상기 극성 신호에 따른 극성에 의해 상기 액정 표시 패널에 데이터 신호를 출력하는 데이터 신호 출력부에 의해 구성되는 데이터 구동 회로와,

(iii) 상기 액정 표시 패널의 게이트 버스 라인에 수평 동기 신호 및 수직 동기 신호에 동기한 타이밍으로 주사 신호를 공급하는 게이트 구동 회로를 갖는 것을 특징으로 하는 액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 표시 패널의 개개의 화소(picture element) 전극에 인가하는 데이터 신호의 극성을 일정한 시간마다 반전시키는, 즉 교류 구동을 하는 표시 패널의 구동 방법, 표시 패널의 구동 회로 및 액정 표시 장치에 관한 것이며, 주로 액티브 매트릭스형 액정 표시 패널의 구동 방법, 액정 표시 패널의 구동 회로 및 액정 표시 장치에 관한 것이다.

근년, 노트형 컴퓨터(휴대용 PC) 등의 OA기기를 비롯하여, 디지털 비디오 카메라나 전화기 등의 다양한 기기의 디스플레이로서 액정 표시 장치가 급격하게 보급되고 있다. 액정 표시 장치는 대화면화 및 표시 품질(화질), 가격 등의 면에서, CRT(cathode ray tube) 등의 표시 장치에는 아직 뒤떨어지지만, 저소비 전력, 경량, 공간 절약 등의 뛰어난 특징이 주목되고 있다.

액티브 매트릭스형 액정 표시 패널은 2장의 글래스 기판 사이에 액정을 봉입한 구조를 가지고 있다. 한쪽의 글래스 기판 상에는 수평 방향 및 수직 방향으로 배열한 복수의 화소 전극과, 각 화소 전극에 인가하는 전압을 ON-OFF하기 위한 복수의 스위칭 소자가 형성되어 있다. 스위칭 소자로서는 박막 트랜ジ스터(Thin Film Transistor: 이하, TFT라 한다)가 사용되는 일이 많다.

또, 다른 쪽의 글래스 기판 상에는 컬러 필터 및 대향 전극이 형성되어 있다. 이들 2장의 글래스 기판은 화소 전극이 형성된 면과 대향 전극이 형성된 면을 대향시켜 배치된다. 컬러 필터에는 적(R), 녹(G), 청(B)의 3색이 있고, 각 화소 전극에 대응하여 R·G·B의 컬러 필터가 일정한 차례로 배치된다. 이하, TFT를 갖는 기판을 TFT기판, 대향 전극을 갖는 기판을 대향 기판이라고 한다.

또, 액정을 봉입한 TFT기판 및 대향 기판을 끼워서, 1쌍의 편광판(polarizing plate)이 배치되어 있다. 이 1쌍의 편광판은 일반적으로 편광축을 직교시켜 배치된다.

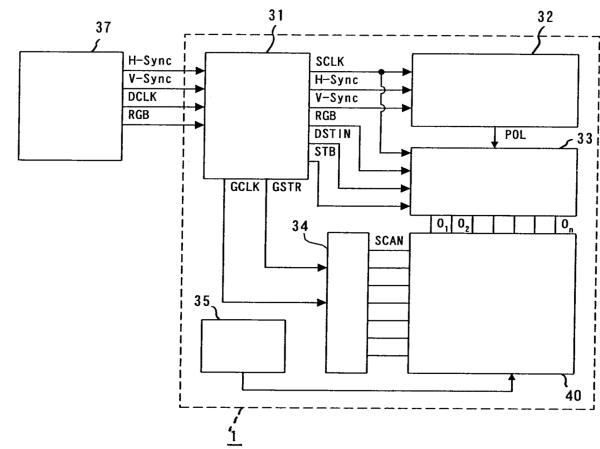

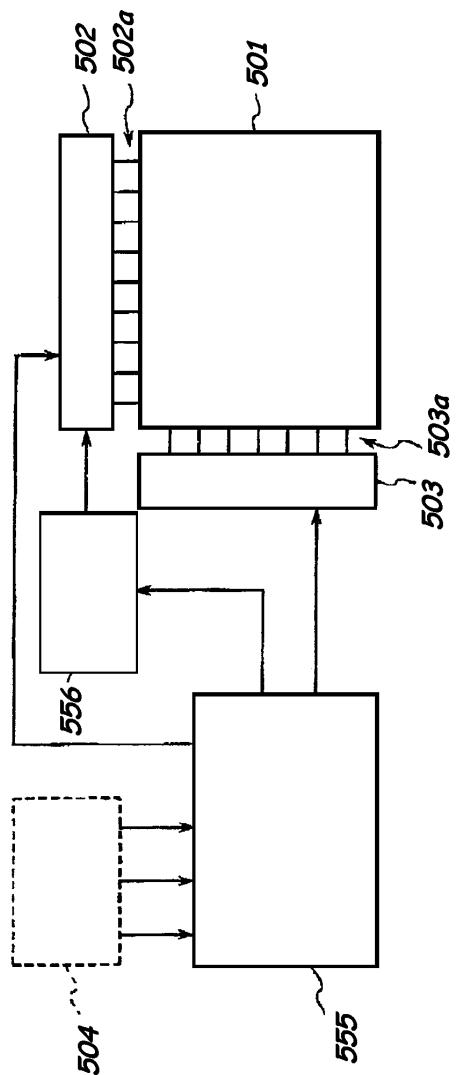

도 1은 종래의 액정 표시 장치의 일례를 나타내는 블럭도이다.

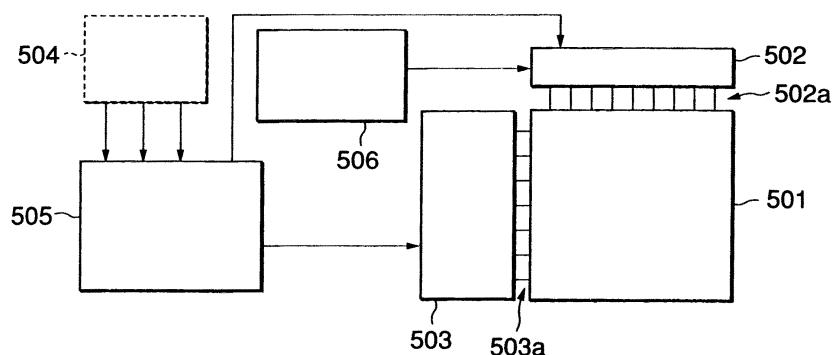

액정 표시 장치는 도 1에 나타낸 바와 같이, 액정 표시 패널(501), 데이터 드라이버(502), 게이트 드라이버(503), 입력 제어부(505), 기준 전원(506)으로 구성되어 있다.

액정 표시 패널(501)에는 매트릭스상으로 배치된 복수의 화소(도시하지 않음)와, 복수개의 데이터 버스 라인(502a) 및 복수개의 게이트 버스 라인(503a)과, 각 화소와 데이터 버스 라인(502a) 및 게이트 버스 라인(503a)에 각각 접속되는 복수의 TFT(도시하지 않음)가 설치되어 있다. 데이터 드라이버(502)는 데이터 버스 라인(502a)에 데이터 신호(표시 데이터)를 출력하고, 게이트 드라이버(503)는 수평 동기 신호에 동기한 타이밍으로 게이트 버스 라인(503b)에 차례로 소정의 주사 신호를 출력한다. TFT는 게이트 버스 라인(503a)에 소정의 주사 신호가 공급되면 ON이 되어, 데이터 버스 라인(502a)에 공급된 데이터 신호를 화소 전극에 전달한다.

입력 제어부(505)는 퍼스널 컴퓨터 등의 표시 제어 정보원(이하, 퍼스널 컴퓨터라고 한다)(504)으로부터 화상 신호, 동기 신호 및 동작 클럭 등의 신호를 입력하여, 데이터 드라이버(502)에 소정의 타이밍으로 화상 신호를 출력하거나, 게이트 드라이버(503)에 클럭 신호를 공급한다. 기준 전원(506)은 화소에 인가하는 기준 전압을 데이터 드라이버(502)에 공급한다.

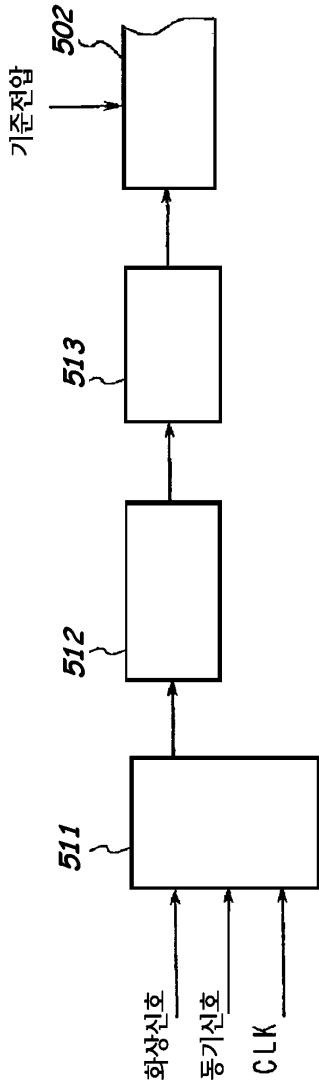

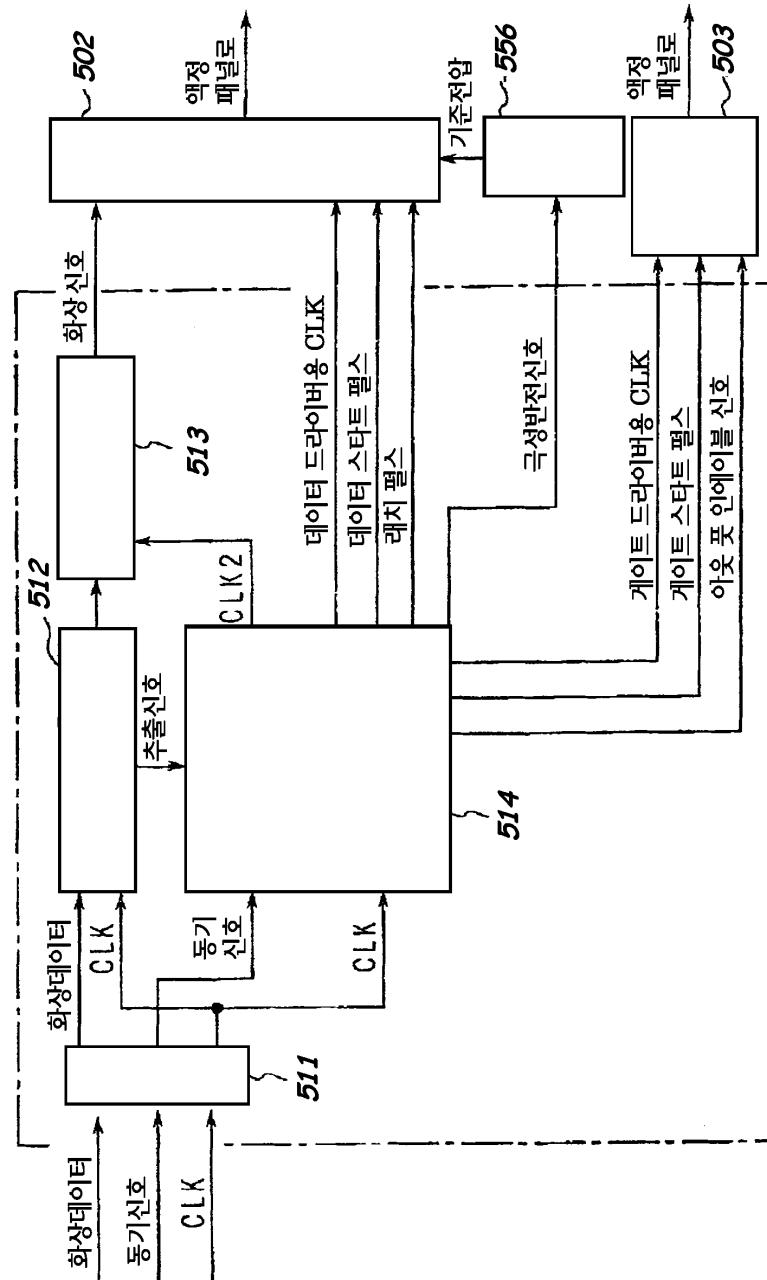

도 2는 입력 제어부(505)의 구성을 나타내는 블럭도이다.

입력 제어부(505)는 입력 인터페이스(I/F)부(511), 입력 데이터 래치 회로(512), 데이터 출력 회로(513)로 구성되어 있다. 입력I/F부(511)는 퍼스널 컴퓨터(504)로부터의 표시 제어 정보(화상 신호, 수평 동기 신호, 동작 제어 신호 등)를 입력하여, 후단의 입력 데이터 래치 회로(512), 데이터 출력 회로(513) 등에 소정의 신호를 전달한다. 입력 데이터 래치 회로(512)는 화상 신호(R,G,B)를 일시 보관 유지한다. 또, 데이터 출력 회로(513)는 화상 신호의 타이밍 조정 및 과형 정형 등을 수행하여, 데이터 드라이버(502)에 출력한다.

이러한 구성에 있어서, 입력I/F부(511)를 통하여 도입된 화상 데이터는 입력 데이터 래치 회로(512) 및 데이터 출력 회로(513)를 통하여, 소정의 타이밍으로 데이터 드라이버(502)에 출력된다. 데이터 드라이버(502)에서는 기준 전원(506)으로부터 공급되는 기준 전압의 반전 주기에 의거하여, 화소에 인가되는 데이터 신호의 극성을 일정한 주기로 반전한다.

여기서, 기준 전압의 반전 주기란, 액정 표시 패널의 화소 전극과 대향 전극에 인가되는 기준 전압이 공통 전압에 대해 정극성 및 부극성의 전압 상태를 교호로 반복하는 반전 주기를 말하고, 통상 일정한 반전 주기로 설정되어 있다.

상술한 바와 같이, 액티브 매트릭스형 액정 표시 패널은 교류 전압으로 구동한다. 예를 들면, 대향 전극에 인가하는 전압을 기준 전압(OV)으로 하여, 화소 전극에는 일정 시간마다 정극성(+) 및 부극성(−)으로 변화하는 전압을 공급한다. 액정에 인가되는 전압은 정의 전압 과형과 부의 전압 과형이 대칭형인 것이 바람직하다. 그러나, 화소 전극에 정의 전압 과형과 부의 전압 과형이 대칭인 교류 전압을 인가하여도, 실제로 액정에 인가되는 정의 전압 과형과 부의 전압 과형은 대칭형인 되지 않는다. 이 때문에, 정의 전압을 인가하였을 때의 광투과율과 부의 전압을 인가하였을 때의 광투과율이 다르다. 따라서, 화소 전극에 인가하는 교류 전압의 주기로 휘도가 변동하여 깜박거림이 발생된다. 이 현상을 플리커(flicker)라고 한다.

종래, 플리커를 억제하는 방법으로서, 대향 전극의 전압을 변화시키는 방법, 횡방향 또는 종방향으로 인접하는 화소 전극에 인가하는 전압의 극성이 다르도록 하는 방법, 및 극성 반전의 주파수를 높게 하는 방법이 알려져 있다. 이들 기술은 예를 들면, 일본 특개평62-113129호 공보, 특개평2-34818호 공보, 특개평6-149174호 공보, 특개평7-175448호 공보, 특개평9-204159호 공보에 개시되어 있다.

인접하는 화소 전극에 극성이 다른 전압을 인가하는 경우, (i) 수직 방향으로 나란한 각 화소 전극에 동일 극성의 전압을 인가하고, 수평 방향으로 인접하는 화소 전극에 역극성의 전압을 인가하는 방법, (ii) 수평 방향으로 나란한 각 화소 전극에 동일 극성의 전압을 인가하고, 수직 방향으로 인접하는 화소 전극에 역극성의 전압을 인가하는 방법, (iii) 수직 방향 및 수평 방향으로 인접하는 화소 전극에 서로 다른 극성의 전압을 인가하는 방법 등이 있다. 액정 표시 패널의 각 화소 전극에 인가하는 전압의 극성을 나타내는 패턴을 극성 패턴이라고 한다.

### 발명이 이루고자 하는 기술적 과제

본 발명자들은 상술한 종래의 기술에는 이하에 나타낸 문제점이 있다고 생각한다. 즉, 상술한 (i)의 극성 패턴에서는 세로 줄무늬의 모양(표시 패턴)을 표시하였을 때에, (ii)의 극성 패턴에서는 가로 줄무늬의 모양을 표시하였을 때에, (iii)의 극성 패턴에서는 모자이크상의 모양(체크 패턴)을 표시하였을 때에 플리커가 현저해진다. 이들의 모양(표시 패턴)은 컴퓨터의 표시에서는 비교적 잘 사용된다.

또, 대향 전극의 전압을 변화시키는 방법에서는 제어가 복잡해지고, 회로 규모가 증대한다. 또한, 반전 주파수를 높게 하는 방법에서는 회로 구성이 복잡해진다.

본 발명의 목적은 비교적 간단한 회로 구성으로 플리커의 발생을 저감 또는 방지할 수 있는 표시 패널의 구동 방법, 구동 회로 및 액정 표시 장치를 제공하는 것이다.

### 발명의 구성

상기한 과제는 도 16에 예시한 바와 같이, 복수개의 데이터 버스 라인(502a) 및 게이트 버스 라인(503a)의 각 교점에 매트릭스상으로 배치된 화소를 갖는 액정 표시 패널(501)과, 상기 화소 단위의 화상 데이터를 상기 데이터 버스 라인(502a)에 공급하는 데이터 드라이버(502)와, 수평 동기 신호에 동기하여 상기 게이트 버스 라인(503a)을 통하여 차례로 각 화소를 동작 상태로 하는 게이트 드라이버(503)와, 적어도 상기 화상 데이터 및 상기 수평 동기 신호를 포함하는 표시 제어 신호를 상기 데이터 드라이버(502) 및 상기 게이트 드라이버(503)에 공급하여, 상기 액정 표시 패널(501)에 표시되는 화상 데이터를 제어하는 입력 제어부(555)와, 상기 화상 데이터에 의거하여 상기 액정 표시 패널(501)의 소정의 극성의 화소에 인가하는 기준 전압을 생성하는 기준 전원 생성부(556)를 갖는 액정 표시 장치에 있어서, 상기 입력 제어부(555)는 상기 화상 데이터의 표시 패턴의 변화 주기와, 상기 기준 전압의 극성 반전 주기와의 상관 관계를 감시하여, 상기 변화 주기 및 상기 극성 반전 주기가 동기하는 상태를 판정하였을 때, 상기 극성 반전 주기를 임의로 전환 설정하는 것을 특징으로 하는 액정 표시 장치에 의해 해결한다.

이 경우에, 도 17, 도 18에 예시한 바와 같이, 상기 입력 제어부(555)는 상기 화상 데이터를 차례로 추출하는 화상 데이터 추출부(512a)와, 추출된 상기 화상 데이터의 변화량을 계수하고, 소정의 규정치와 비교하여 특정의 표시 패턴을 판정하는 패턴 판정부(514a)와, 다른 극성 반전 주기를 갖는 기준 전압을 생성하는 반전 주기 제어부(514b)를 가지며, 상기 반전 주기 제어부(514b)는 상기 패턴 판정부(514a)에 의한 판정 결과에 의거하여, 상기 극성 반전 주기를 임의로 전환 설정하고, 상기 기준 전원 생성부(556)는 전환 설정된 상기 극성 반전 주기를 갖는 기준 전압을 생성하여, 상기 데이터 드라이버(502)에 공급한다.

본 발명에 있어서는 화상 데이터 추출부(512a) 및 패턴 판정부(514a)에 의해, 인접하여 표시되는 화상 데이터가 차례로 추출, 감시되고, 플리커, 혹은 소비 전력의 증대를 일으키는 특정의 표시 패턴이 판정되면, 반전 주기 제어부(514b)에 의해, 미리 준비된 다른 극성 반전 주기로 기준 전압이 공급된다.

따라서, 본 발명의 액정 표시 장치에 의하면, 초기 상태로서 설정된 극성 반전 주기에 의거하여, 화소에 인가되는 화상 데이터의 극성 반전을 행하고 있는 경우에, 표시 화면에 플리커, 혹은 소비 전력의 증대를 일으키는 특정의 패턴을 표시하는 화상 데이터가 입력된 경우에는 다른 극성 반전 주기로 전환할 수 있다. 이에 따라, 화상 데이터의 극성 반전 주기와, 표시 패턴과의 동기를 회피하고, 액정 표시 장치의 플리커, 혹은 소비 전력의 증대를 억제할 수 있다.

상기한 과제는 도 3~도 5, 도 8에 예시한 바와 같이, 화상 신호(RGB), 수평 동기 신호(H-Sync) 및 수직 동기 신호(V-Sync), 또는 인에이블(enable)신호를 입력하여, 액정 표시 패널(30)의 각 데이터 버스 라인(13)에 상기 화상 신호(RGB)로부터 생성한 정극성 및 부극성으로 변화하는 데이터 신호( $O_1 \sim O_n$ )를 공급하는 표시 패널의 구동 방법에 있어서, 극성 패턴을 극성 패턴 기억부(ROM32b)에 기억해 두고, 상기 극성 패턴 기억부(ROM32b)로부터 판독한 극성 패턴을 따라 상기 각 데이터 버스 라인(13)에 공급하는 데이터 신호( $O_1 \sim O_n$ )의 극성을 결정하는 것을 특징으로 하는 표시 패널의 구동 방법에 의해 해결한다.

상기와 같이, 극성 패턴을 극성 패턴 기억부(ROM32b)에 기억해 둠으로써, 하드웨어를 변경하지 않고, 표시 패널(30)에 표시하는 표시 패턴에 따라 극성 패턴을 용이하게 변경할 수 있다. 또, 회로 구성도 비교적 간단하다. 또한, 인에이블 신호는 화상 신호가 유효(표시)할 때 "H"가 되는 신호로서, 수평 동기 신호, 수직 동기 신호의 대신이 되는 신호이다.

이 경우, 상기 극성 패턴 기억부에 복수의 극성 패턴을 기억해 두고, 화상 신호(RGB)에 따라 어느 1개의 극성 패턴만을 상기 극성 패턴 기억부에서 출력시켜, 상기 각 데이터 버스 라인(13)에 공급하는 데이터 신호( $O_1 \sim O_n$ )의 극성을 결정하는 것이 바람직하다.

또, 도 24에 예시한 바와 같이, 복수의 극성 패턴을 기억한 극성 패턴 기억부(ROM62)로부터 어느 1개의 극성 패턴을 출력시켜, 상기 극성 패턴 기억부(ROM62)로부터 출력된 극성 패턴과 화상 신호(RGB)와의 유사를 판정하고, 유사로 판정하였을 때는 상기 극성 패턴 기억부(ROM62)로부터 출력하는 극성 패턴을 전환하여도 좋다.

이에 따라, 플리커가 발생하는 화상(표시 패턴)을 표시할 때에, 극성 패턴 기억부(ROM62)로부터 출력되는 극성 패턴이 자동적으로 전환되어, 플리커의 발생을 방지할 수 있다.

극성 패턴과 화상 신호(RGB)와의 유사 여부의 판정은 예를 들면 단위 시간내 또는 일정한 데이터수마다 화상 신호(RGB)의 값과 극성 패턴의 값이 일치한 수를 계수하고, 그 계수값과 일정한 값을 비교함으로써 실현할 수 있다.

또, 상기 과제는 도 3~도 5, 도 8, 도 9에 예시한 바와 같이, 화상 신호(RGB), 수평 동기 신호(H-Sync) 및 수직 동기 신호(V-Sync), 또는 인에이블 신호를 입력하여, 표시 패널(40)의 각 데이터 버스 라인(13)에 상기 화상 신호(RGB)로부터 생성한 정극성 및 부극성으로 변화하는 데이터 신호( $O_1 \sim O_n$ )를 공급하는 표시 패널의 구동 회로에 있어서, 극성 패턴을 기억한 극성 패턴 기억부(ROM32b)와, 상기 극성 패턴 기억부(ROM32b)로부터 출력되는 상기 극성 패턴을 기억하여, 극성 신호로서 출력하는 일시 기억부(시프트 레지스터(41))와, 상기 화상 신호(RGB)를 입력하여, 상기 일시 기억부(시프트 레지스터(41))로부터 출력되는 극성 신호( $P_1 \sim P_n$ )에 따른 극성으로 상기 데이터 신호( $O_1 \sim O_n$ )를 출력하는 데이터 신호 출력부(시프트 레지스터(42), 데이터 레지스터 회로부(43), 래치 회로부(44), 레벨 시프트 회로부(45), D/A변환 회로부(46) 및 볼티지팔로우어부(47))를 갖는 것을 특징으로 하는 표시 패널의 구동 회로에 의해 해결한다.

본 발명에 있어서는 상기와 같이, 극성 패턴 기억부(ROM32b)에 극성 패턴을 기억해 둠으로, 하드웨어를 변경하는 일없이, 표시 패턴에 따라 극성 패턴을 변경할 수 있다.

상기 극성 패턴 기억부(ROM32b)는 홀수번째의 프레임용의 데이터와, 상기 홀수번째의 프레임용 데이터의 논리값을 반전한 짝수번째의 프레임용의 데이터의 2프레임분의 비트수의 데이터를 1조의 극성 패턴으로서 기억하여도 좋다. 액정 표시 패널에서는 화소 전극에 공급하는 데이터 신호의 극성을 일정한 시간마다 반전시킬 필요가 있다. 상기와 같이 짝수번째의 프레임의 데이터를 홀수번째의 프레임의 데이터의 논리값을 반전한 데이터로 함으로써, 1프레임마다 데이터 신호의 극성이 반전한다.

또한, 표시 패널의 구동 회로에 있어서, 상기 극성 패턴 기억부는 복수 조의 극성 패턴을 기억하는 것이어도 좋다.

도 24에 예시한 바와 같이, 극성 패턴 기억부(ROM62)로부터 출력된 극성 패턴과 화상 신호(RGB)간의 유사 여부를 판정하여 극성 패턴 기억부(ROM62)로부터 출력하는 극성 패턴을 전환하는 패턴 전환부(제어 회로(61), 비교기(63), 계수 회로(64), 비교기(65) 및 임계값 설정부(66))를 설치하여도 좋다. 이에 따라, 표시 패턴에 따라 극성 패턴을 자동적으로 전환할 수 있다.

도 26, 도 27에 예시한 바와 같이, 극성 패턴 기억부(ROM72)로부터 출력되는 1수평 동기 기간분의 극성 패턴을 기억하여 극성 신호( $A_1 \sim A_n$ )로서 출력하는 일시 기억부(시프트 레지스터 회로부(77))와, 상기 극성 신호( $A_1 \sim A_n$ )의 극성을 수평 동기 신호(H-Sync)에 동기하여 반전시키는 극성 신호 반전부(배타적 논리화 회로부(78))를 설치하여도 좋다.

이 경우는 극성 패턴 기억부(ROM72)에 1수평 동기 기간분의 극성 패턴을 기억하면 되고, 극성 패턴 기억부(ROM72)의 기억 용량을 삭감할 수 있다.

이 경우에, 극성 패턴 기억부에는 1수평 동기 기간분의 비트수의 데이터를 1조로 하여, 복수 조의 극성 패턴을 기억하고 있는 것이 바람직하다.

상기한 과제는 청구항 1에 나타내고, 도 31, 도 32에 예시한 바와 같이, 다른 복수의 극성 패턴을 발생 가능한 극성 패턴 발생부(논리 회로(85))와, 상기 극성 패턴 발생부로부터 출력하는 극성 패턴을 결정하기 위한 선택 신호(SEL)를 출력하는 선택 신호 발생부(극성 패턴 제어부(80))와, 상기 극성 패턴 발생부(논리 회로(85))로부터 출력된 극성 패턴의 각 비트의 논리값을 1수평 동기 기간마다 및 1수직 동기 기간마다 반전시켜 극성 신호( $P_1 \sim P_n$ )로서 출력하는 극성 신호 반전부(배타적 논리화 회로부(86))를 갖는 표시 패널의 구동 회로에 의해 해결한다.

이 표시 패널의 구동 회로에 있어서도, 극성 패턴 발생부로부터 표시 패턴에 따른 극성 패턴을 출력시킴으로써, 플리커의 발생을 방지할 수 있다.

상기한 과제는 도 5, 도 8, 도 9에 나타낸 바와 같이, (i) 액정 표시 패널(40)과, (ii) 극성 패턴을 기억한 극성 패턴 기억부(ROM32b)와, 상기 극성 패턴 기억부(ROM32b)로부터 출력되는 상기 극성 패턴을 기억하여 극성 신호( $P_1 \sim P_n$ )로서 출력하는 일시 기억부(시프트 레지스터 회로부(41))와, 화상 신호(RGB)를 입력하여, 상기 일시 기억부(시프트 레지스터 회로부(41))로부터 출력되는 극성 신호( $P_1 \sim P_n$ )에 따른 극성으로 상기 액정 표시 패널(40)의 데이터 버스 라인에 데이터 신호를 출력하는 데이터 신호 출력부(시프트 레지스터(42), 데이터 레지스터 회로부(43), 래치 회로부(44), 레벨 시프트 회로부(45), D/A변환 회로부(46) 및 볼티지팔로우어부(47))로 구성되는 데이터 구동 회로(극성 패턴 제어부(32) 및 데이터 드라

이버(33))와, (iii) 상기 액정 표시 패널(40)의 게이트 버스 라인에 수평 동기 신호(H-Sync) 및 수직 동기 신호(V-Sync)에 동기한 타이밍으로 주사 신호(SCAN)를 공급하는 게이트 구동 회로(게이트 드라이버(34))를 갖는 것을 특징으로 하는 액정 표시 장치에 의해 해결한다.

상기와 같이, 극성 패턴을 극성 패턴 기억부(ROM32b)에 기억하고 있으므로, 하드웨어를 변경하지 않고, 표시 패턴에 따른 극성 패턴으로 변경할 수 있다. 이에 따라, 간단한 구성으로 플리커의 발생을 억제할 수 있다.

또, 청구항 2에 기재한 바와 같이, 상기 데이터 구동 회로에 대신하여, 도 31, 도 32에 예시한 바와 같이, 다른 복수의 극성 패턴을 발생 가능한 극성 패턴 발생부(논리 회로(85))와, 상기 극성 패턴 발생부(논리 회로(85))로부터 출력하는 극성 패턴을 결정하기 위한 선택 신호(SEL)를 발생하는 선택 신호 발생부(극성 패턴 제어부(80))와, 상기 극성 패턴 발생부(논리 회로(85))로부터 출력된 극성 패턴의 각 비트의 논리값을 1수평 동기 기간마다 및 1수직 동기 기간마다 반전시켜 극성 신호( $P_1 \sim P_n$ )로서 출력하는 극성 신호 반전부(배타적 논리화 회로(86))와, 화상 신호를 입력하여 상기 극성 신호에 따른 극성에 의해 데이터 신호를 출력하는 데이터 신호 출력부로 구성되는 데이터 구동 회로(시프트 레지스터(42), 데이터 레지스터 회로부(43), 래치 회로부(44), 레벨 시프트 회로부(45), D/A변환 회로부(46) 및 볼티지팔로우어부(47))로 구성되는 데이터 구동 회로를 사용할 수도 있다.

또, 상기한 과제는 도 3~도 5, 도 35~도 37에 나타낸 바와 같이, 화상 신호(RGB), 수평 동기 신호(H-Sync) 및 수직 동기 신호(V-Sync), 또는 인에이블 신호를 입력하여, 화상 표시 패널(40)의 각 데이터 버스 라인(13)에 상기 화상 신호(RGB)로부터 생성한 정극성 및 부극성으로 변화하는 데이터 신호( $O_1 \sim O_n$ )를 공급하는 표시 패널의 구동 방법에 있어서, 표시 화면을 복수의 블럭으로 분할하고, 그 중의 적어도 1개의 블럭내에 포함되는 플리커 패턴의 비율을 산출하여, 일정한 값을 넘을 때에 상기 데이터 버스 라인(13)에 공급하는 데이터 신호(01-On)의 극성을 결정하는 극성 패턴을 제1 극성 패턴으로부터 제2 극성 패턴으로 변화시키는 것을 특징으로 하는 표시 패널의 구동 방법에 의해 해결한다.

이 경우, 예를 들면, 상기 복수의 블럭 중 상기 플리커 패턴의 비율이 상기 일정한 값을 넘는 블럭의 수가 소정의 값 이상이 되었을 때에, 상기 제2 극성 패턴으로 변화시킨다.

또, 상기 제1 극성 패턴으로부터 상기 제2 극성 패턴으로 변화시킨 후, 소정의 프레임 기간에 걸쳐 상기 블럭내에 포함되는 플리커 패턴의 비율이 상기 일정한 값을 이하일 때에, 상기 제1 극성 패턴으로 되돌리는 것이 바람직하다.

블럭의 갈림길에 존재하는 플리커 패턴을 검출하기 위하여, 상기 블럭의 분할 위치를 프레임마다 변화시키는 것이 바람직하다.

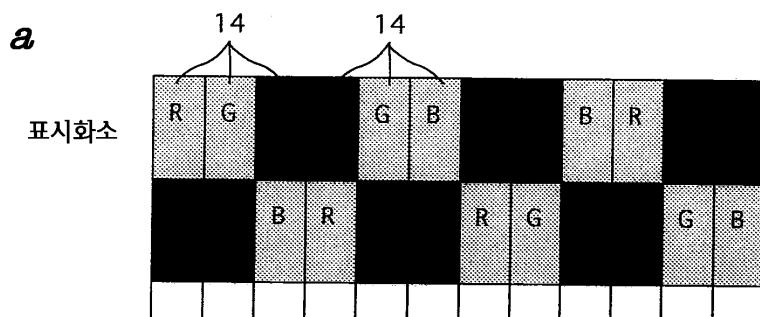

상기 플리커 패턴의 검출은 예를 들면 횡방향으로 인접하는 일정수의 픽셀분의 화상 신호마다 실시한다. 일례를 들면, 횡방향으로 인접하는 2픽셀분의 적(R), 녹(G), 청(B)의 6화소 중의 녹 화소에 대하여, 한쪽의 픽셀의 녹 화소가 점등하고, 다른 쪽의 픽셀의 녹 화소가 비점등일 때에 플리커 패턴으로 한다. 또, 횡방향으로 인접하는 2픽셀분의 적(R), 녹(G), 청(B)의 6화소 중의 적 및 청 화소에 대하여, 한쪽의 픽셀의 적 화소 및 청 화소의 적어도 한쪽의 화소가 점등하고, 다른 쪽의 픽셀의 적 화소 및 청 화소가 모두 비점등일 때에 플리커 패턴으로 한다. 상기의 예는 2픽셀을 1개의 에어리어로 하여 플리커 패턴을 판정하는 방법이지만, 일반적으로 말하면, 인접하는 2픽셀 이상을 1에어리어로 하고, 1에어리어내의 R·G·B의 1색의 화소에 대하여 정극과 부극이 있는 극성의 한쪽의 극성 데이터를 기입하는 화소가 점등하고, 다른 쪽의 극성을 기입 화소의 전부가 비점등일 때에 플리커 패턴으로 판정한다.

또한, 표시 패널의 구동 방법에 있어서, 상기 플리커 패턴의 검출은 횡방향으로 인접하는 2픽셀분의 적(R), 녹(G), 청(B)의 6화소 중의 1색의 화소에 대하여, 한쪽의 픽셀의 화소가 점등하고, 다른 쪽의 픽셀의 화소가 비점등일 때에 플리커 패턴으로 판정해도 좋다.

또, 표시 패널의 구동 방법에 있어서, 상기 플리커 패턴의 검출은 횡방향으로 인접하는 2픽셀분의 적(R), 녹(G), 청(B)의 6화소 중의 2색의 화소에 대하여, 한쪽의 픽셀에서는 상기 2색의 화소의 적어도 한쪽의 화소가 점등하고, 다른 쪽의 픽셀에서는 상기 2색의 화소가 모두 비점등일 때에 플리커 패턴으로 판정하여도 좋다.

또한, 표시 패널의 구동 방법에 있어서, 횡방향으로 나란한 적(R), 녹(G), 청(B)의 화소 중의 1색의 화소에 대하여 점등 화소 및 비점등 화소의 수를 각각 계수하여, N(N은 정수)행째의 점등 화소 및 비점등 화소의 수와 N+1행째의 점등 화소 및 비점등 화소의 수를 비교하고, 그 결과에 의거하여 상기 플리커 패턴으로부터 제외하는 패턴을 검출하여도 좋다.

또한, 표시 패널의 구동 방법에 있어서, 횡방향으로 나란한 적(R), 녹(G), 청(B)의 화소 중의 복수색의 화소에 대하여 점등 화소 및 비점등 화소의 수를 각각 계수하여, N(N은 정수)행째의 점등 화소 및 비점등 화소의 수와 N+1행째의 점등 화소 및 비점등 화소의 수를 비교하고, 그 결과에 의거하여 상기 플리커 패턴으로부터 제외하는 패턴을 검출하여도 좋다.

또한, 표시 패널의 구동 방법에 있어서, 상기 화상 신호 판정부, 상기 플리커 판정부, 상기 동작 범위 지정부, 상기 플리커 정보량 판정부 및 상기 구동 모드 선택부가 모두 논리 회로로 구성되는 것이 바람직하다.

또, 상기한 과제는 도 3~도 5, 도 37에 나타낸 바와 같이, 화상 신호(RGB), 수평 동기 신호(H-Sync) 및 수직 동기 신호(V-Sync), 또는 인에이블 신호를 입력하여, 표시 패널(40)의 각 데이터 버스 라인(13)에 상기 화상 신호(RGB)로부터 생성한 정극성 및 부극성으로 변화하는 데이터 신호( $O_1 \sim O_n$ )를 개별적으로 공급하는 표시 패널의 구동 회로에 있어서, 상기 화상 신호(RGB)를 입력하여 점등 화소 및 비점등 화소를 판정하는 화상 신호 판정부(103)와, 상기 화상 신호 판정부(103)의 판정 결과를 기초로 플리커 패턴인지의 여부를 판정하는 플리커 판정부(104)와, 동작 범위를 지정하는 동작 범위 지정부(105)와, 상기 동작 범위 지정부(105)에서 지정된 동작 범위내에 상기 플리커 판정부(104)에서 플리커 패턴으로 판정된 패턴이 포함되는 비율을 산출하는 플리커 정보량 판정부(106)와, 상기 플리커 정보량 판정부(106)의 판정 결과에 따라 상기 데이터 신호( $O_1 \sim O_n$ )의 극성 패턴을 결정하는 신호를 출력하는 구동 모드 선택부(108)와, 상기 구동 모드 선택부(108)의 출력에 따라 상기 데이터 버스 라인(13)에 공급하는 데이터 신호( $O_1 \sim O_n$ )의 극성을 결정하는 극성 패턴을, 제1 극성 패턴으로부터 제2 극성 패턴으로 변화시키는 극성 패턴 변경부(109)를 갖는 것을 특징으로 하는 표시 패널의 구동 회로에 의해 해결한다.

이 경우, 도 38~도 43, 도 54~도 59에 나타낸 바와 같이, 상기 화상 신호 판정부(103), 상기 플리커 판정부(104), 상기 동작 범위 지정부(105), 상기 플리커 정보량 판정부(107) 및 상기 구동 모드 선택부(108)는 모두 논리 회로로 구성할 수 있다.

## 실시 형태

이하, 본 발명 실시 형태에 대하여, 첨부의 도면을 참조하여 설명한다.

### (제1 실시 형태)

#### (1) 액정 표시 패널의 구조

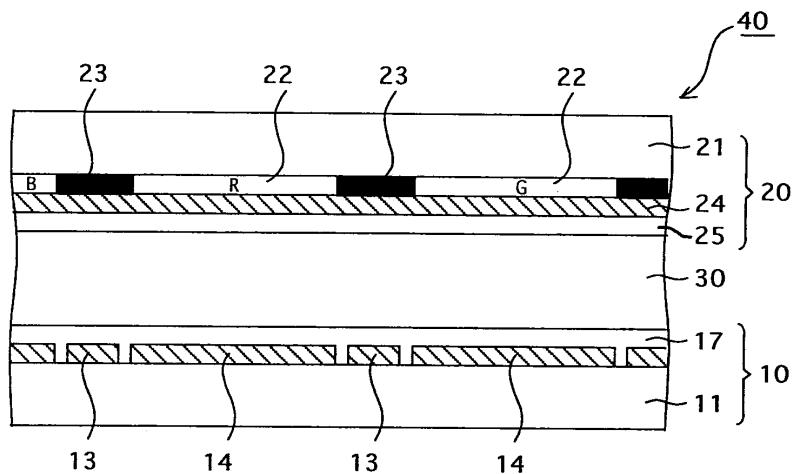

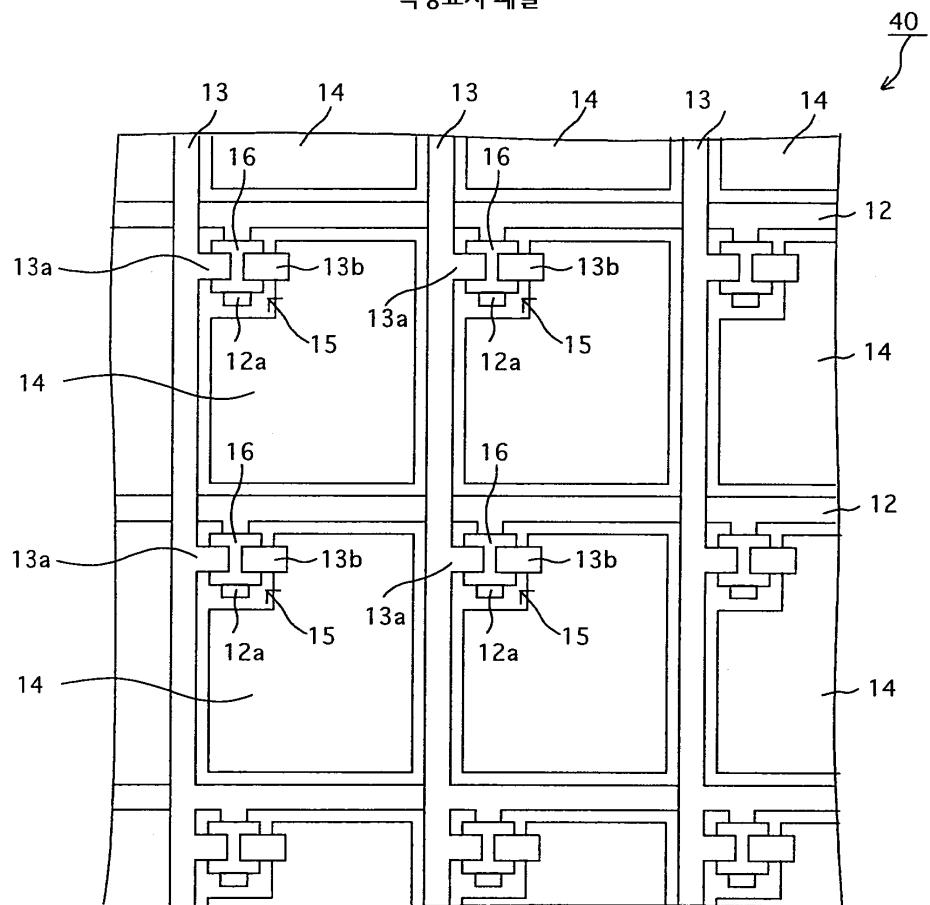

도 3은 제1 실시 형태의 구동 회로에서 구동되는 액정 표시 패널의 구조를 나타내는 단면도, 도 4는 그 TFT기판의 평면도이다.

액정 표시 패널(40)은 대향하여 배치된 TFT기판(10) 및 대향 기판(20)과, 이들 TFT기판(10)과 대향 기판(20) 사이에 봉입된 액정(30)으로 구성되어 있다.

TFT기판(10)은 클래스 기판(11)과, 클래스 기판(11)상에 형성된 게이트 버스 라인(12), 데이터 버스 라인(13), 화소 전극(14) 및 TFT(15) 등으로 구성된다. 게이트 버스 라인(12) 및 데이터 버스 라인(13)은 직각으로 교차하고 있고, 양자간에 형성된 절연막(도시하지 않음)에 의해 전기적으로 절연되어 있다. 이들 게이트 버스 라인(12) 및 데이터 버스 라인(13)은 알루미늄 등의 금속으로 형성되어 있다.

게이트 버스 라인(12)과 데이터 버스 라인(13)으로 구성된 각 직사각형 영역이 화소이다. 각 화소에는 각각 인듐산화주석(indium-tin oxide: 이하, ITO라고 한다)으로 된 투명한 화소 전극(14)이 형성되어 있다. 또, TFT(15)는 게이트 버스 라인(12)과 접속되는 게이트 전극(12a)과, 게이트 전극(12a)의 위쪽에 게이트 절연막(도시하지 않음)을 통하여 형성된 실리콘막(16)과, 실리콘막(16)의 위쪽에 형성된 드레인 전극(13a) 및 소스 전극(13b)으로 된다. 드레인 전극(13a)은 데이터 버스 라인(13)과 접속되어 있고, 소스 전극(13b)은 화소 전극(14)에 접속되어 있다. 또, 화소 전극(14)의 일부에 오버랩하여, 도시하지 않는 축적 용량 전극이 형성되어 있다.

이들 화소 전극(14) 상에는 예를 들면 폴리이미드로 된 배향막(17)이 형성되어 있다. 이 배향막(17)의 표면에는 전압을 인가하지 않을 때의 액정 분자의 배향 방향을 결정하기 위하여, 배향 처리가 실시된다. 배향 처리의 대표적인 방법으로서는 천으로 만든 롤러에 의해 배향막의 표면을 한 방향으로 문지르는 방법이 알려져 있다.

한편, 대향 기판(20)은 클래스 기판(21)과, 클래스 기판(21)의 아래쪽 면측에 형성된 컬러 필터(22), 블랙 매트릭스(23), 대향 전극(24) 및 배향막(25) 등으로 구성되어 있다. 컬러 필터(22)에는 적(R), 녹(G) 및 청(B)의 3종류가 있고, 1개의 화소 전극(14)에 1개의 컬러 필터(22)가 대향하고 있다. 본 실시 형태에서는 컬러 필터(22)는 수평 방향으로 R·G·B의 차례로 나란히 되어 있다. 이들 컬러 필터(22)사이에는 블랙 매트릭스(23)가 형성되어 있다. 이 블랙 매트릭스(23)는 예를 들면 크롬(Cr)과 같이 빛이 투과되지 않는 금속 박막으로 된다.

컬러 필터(22) 및 블랙 매트릭스(23) 밑에는 ITO로 된 투명한 대향 전극(24)이 형성되어 있다. 이 대향 전극(24) 밑에는 배향막(25)이 형성되어 있다. 이 배향막(25)의 표면에도 배향 처리가 되어 있다.

TFT기판(10)과 대향 기판(20) 사이에는 구형의 스페이서(도시하지 않음)가 배치되고, 이에 따라 TFT기판(10)과 대향 기판(20)의 간격이 일정하게 유지된다. 또, TFT기판(10)의 아래 및 대향 기판(20) 위에는 각각 편광판(도시하지 않음)이 배치된다. 이들 편광판은 편광축이 서로 직교하도록 배치된다.

데이터 버스 라인(13)에 데이터 신호를 공급하고, 케이트 버스 라인(12)에 주사 신호를 공급하면, TFT(15)가 ON이 되어 화소 전극(14)에 데이터 신호가 공급된다. 이에 따라, 화소 전극(14)과 대향 전극(24) 사이에 전계가 발생한다. 이 전계에 의해 액정(30) 중의 액정 분자의 방향이 변화하여, 화소의 광투과율이 변화한다. 각 화소마다 화소 전극(14)에 인가하는 전압을 제어함으로써, 액정 표시 패널(40)에 원하는 화상을 표시할 수 있다.

## (2) 구동 회로의 구성

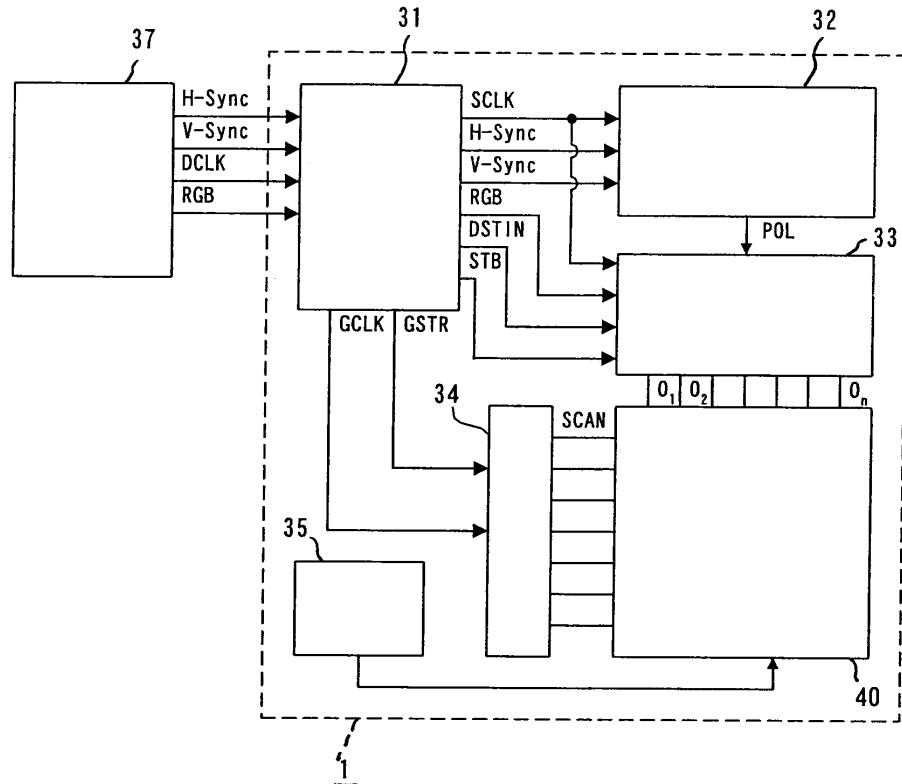

도 5는 제1 실시 형태의 액정 표시 장치를 나타내는 블럭도이다. 이 액정 표시 장치는 도 3, 도 4에 나타낸 구조의 액정 표시 패널(40)과, 타이밍 컨트롤러(31), 극성 패턴 제어부(32), 데이터 드라이버(33) 및 케이트 드라이버(34)와, 기준 전압 발생 회로(35)를 가지고 있다.

타이밍 컨트롤러(31)는 퍼스널 컴퓨터 또는 기타의 화상 신호(RGB)를 출력하는 장치(이하, 단순히, 퍼스널 컴퓨터라고 한다)(37)에 접속되고, 퍼스널 컴퓨터(37)로부터 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync), 데이터 클럭(DCLK) 및 화상 신호(RGB)를 입력한다.

화상 신호(RGB)는 적색의 휘도를 나타내는 R신호, 녹색의 휘도를 나타내는 G신호 및 청색의 휘도를 나타내는 B신호의 3개의 디지털 신호(이하, R·G·B신호라고 한다)로 된다. 통상, R·G·B신호의 각 비트수를 모두 8비트로 하는 것이 많지만, 여기서는 설명을 간단하게 하기 위하여, R·G·B신호는 모두 3비트의 신호로 한다. 이들 R·G·B신호는 데이터 클럭(DCLK)에 동기한 신호이다.

타이밍 컨트롤러(31)는 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync) 및 데이터 클럭(DCLK)을 입력하여, 이들 신호로부터 시프트 클럭(SCLK), 데이터 스타트 신호(DSTIN), 스트로브 신호(STB), 케이트 스타트 신호(GSTR) 및 케이트 클럭(GCLK)을 생성한다.

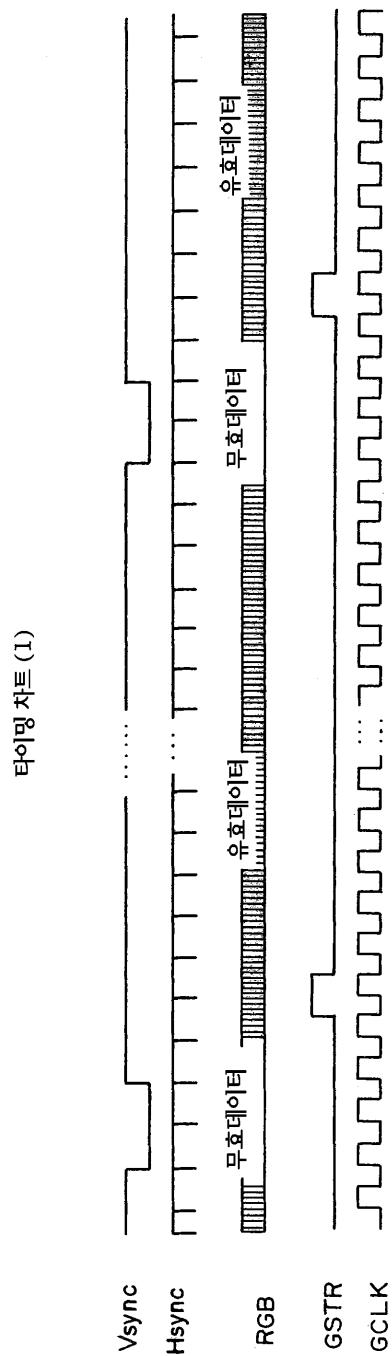

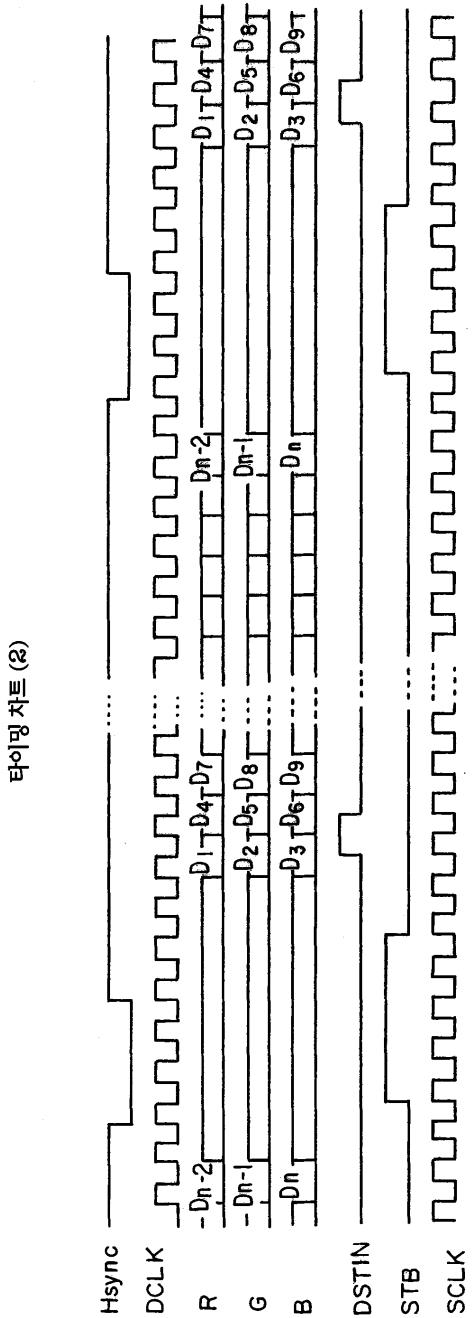

도 6은 수직 동기 신호(V-Sync), 수평 동기 신호(H-Sync), 화상 신호(RGB), 케이트 스타트 신호(GSTR) 및 케이트 클럭(GCLK)의 타이밍을 나타내는 타이밍 차트, 도 7은 수평 동기 신호(H-Sync), 데이터 클럭(DCLK), R신호, G신호, B신호, 데이터 스타트 신호(DSTIN), 스트로브 신호(STB) 및 시프트 클럭(SCLK)의 타이밍을 나타내는 타이밍 차트이다.

이들 도 6, 도 7에 나타낸 바와 같이, 케이트 스타트 신호(GSTR)는 수직 동기 신호(V-Sync)의 상승에 동기한 신호이고, 케이트 클럭(GCLK)은 수평 동기 신호(H-Sync)에 동기한 신호이다. 또, 데이터 스타트 신호(DSTIN)는 화상 신호(RGB)의 송신 개시의 타이밍을 나타내는 신호이다. 화상 신호(RGB)는 수직 동기 신호(V-Sync)가 "0"에서 "1"로 변한 뒤의 최초의 수평 동기 신호(H-Sync)의 상승에 동기하여 송신이 개시된다. 또, 화상 신호(RGB)는 1수평 동기 기간내에 액정 표시 패널(40)의 수평 방향의 화소수(n개)분의 데이터가 데이터 클럭(DCLK)에 동기하여 보내진다. 따라서, 1수평 동기 기간분의 데이터의 송신이 완료되고 나서 다음 수평 동기 기간분의 데이터의 송신을 개시할 때까지 사이와, 1프레임분의 데이터의 송신이 완료되고 나서 다음 프레임의 데이터의 송신을 개시할 때까지 사이의 화상 신호(RGB)의 값은 무효이다.

스트로브 신호(STB)는 수평 동기 신호(H-Sync)에 동기한 신호이다. 시프트 클럭(SCLK)은 데이터 클럭(DCLK)에 동기한 신호이다.

극성 패턴 제어부(32)는 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync) 및 시프트 클럭(SCLK)을 입력하여, 극성 패턴 신호(POL)를 출력한다. 데이터 드라이버(33)는 타이밍 컨트롤러(31)로부터 입력한 화상 신호(RGB), 시프트 클럭(SCLK), 데이터 스타트 신호(DSTIN) 및 스트로브 신호(STB)를 입력하고, 극성 패턴 제어부(32)로부터 극성 패턴 신호(POL)를 입력하여, 액정 표시 패널(40)의 각 데이터 버스 라인(13)에 데이터 신호( $O_1 \sim O_n$ )를 출력한다. 이들 데이터 신호( $O_1 \sim O_n$ )는 일정한 주기로 극성이 반전되는 신호이다.

또, 게이트 드라이버(34)는 타이밍 컨트롤러(31)로부터 게이트 스타트 신호(GSTR) 및 게이트 클럭(GCLK)을 입력하고, 액정 표시 패널(40)의 각 게이트 버스 라인(11)에 차례로 주사 신호(SCAN)를 공급한다.

TFT형 액정 표시 패널의 구동 회로의 경우, 데이터 드라이버(33) 및 게이트 드라이버(34)는 액정 표시 패널(40)의 TFT기판 상에 형성하는 것도 가능하다.

기준 전압 발생 회로(35)는 액정 표시 패널(40)의 대향 전극(24)에 인가하는 기준 전압을 발생한다. 이 기준 전압은 데이터 신호( $O_1 \sim O_n$ )의 중심 전압과, 화소의 용량 성분에 의한 전압 시프트량에 따라 설정한다. 또, 기준 전압 발생 회로(35)는 타이밍 컨트롤러(31), 극성 패턴 제어부(32), 데이터 드라이버(33) 및 게이트 드라이버(34)의 동작에 필요한 소정의 전압을 발생하고, 이들 전압을 도시하지 않는 배선을 통하여 각 회로에 공급한다.

또한, 상기의 예에서는 구동 회로를 컴퓨터(37)에 접속하는 경우에 대하여 설명했지만, 본 발명의 액정 표시 패널의 구동 회로는 TV 투너 등과 같이 비디오 신호를 출력하는 장치에 접속하는 것도 가능하다. 그 경우, 비디오 신호로부터 R·G·B신호, 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync)를 생성하는 회로가 필요하지만, 이들 회로는 공지된 것을 사용할 수 있다.

### (3) 극성 패턴 제어 회로

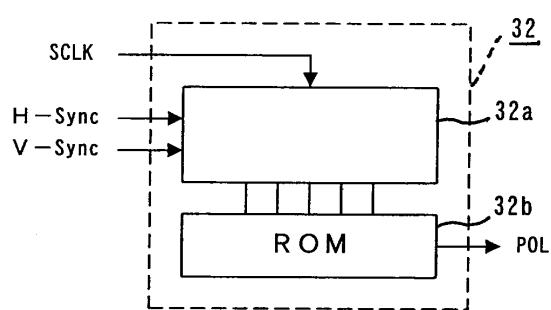

도 8은 극성 패턴 제어부(32)의 구성을 나타내는 블럭도이다.

극성 패턴 제어부(32)는 제어 회로(32a)와, 극성 패턴을 기억한 ROM(32b)으로 구성되어 있다.

ROM(32b)에 기억되어 있는 극성 패턴은 "0"과 "1"의 조합에 의해 구성되고, 예를 들면 "0"일 때는 화소 전극(14)에 정극성(+)의 전압을 인가하고, "1"일 때는 화소 전극(14)에 부극성(-)의 전압을 인가하는 것을 나타낸다. 본 실시 형태에 있어서는 1프레임마다 액정 표시 패널(40)에 공급하는 데이터 신호( $O_1 \sim O_n$ )의 극성을 반전시킨다. 이 때문에, 홀수번째의 프레임에 출력되는 극성 패턴과, 짝수번째의 프레임에 출력되는 극성 패턴은 "0"과 "1"이 정확히 역인 것이 필요하다. ROM(32b)은 2프레임분의 극성 패턴, 즉 액정 표시 패널(40)의 화소수의 2배의 비트수의 극성 패턴을 1조의 데이터로서 기억하고 있다.

제어 회로(32a)는 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync) 및 시프트 클럭(SCLK)을 입력하고, ROM(32b)의 어드레스를 설정한다. 즉, 제어 회로(32a)는 홀수번째의 수직 동기 신호(V-Sync)의 상승에 동기하여 ROM(32b)의 어드레스의 초기값을 설정하고, 그 후, 시프트 클럭(SCLK)에 동기하여 어드레스를 인크리먼트한다. 이에 따라, ROM(32b)으로부터는 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL)가 1비트씩 출력된다. 단, 제어 회로(32a)는 수평 동기 신호(H-Sync)의 1주기간에 표시 패널(40)의 수평 방향의 화소수(n개)와 같은 수만 ROM(32b)의 어드레스를 인크리먼트하면 동작을 일단 정지해, 다음의 수평 동기 신호(H-Sync)의 상승에 인크리먼트를 재개한다.

### (4) 데이터 드라이버의 구성

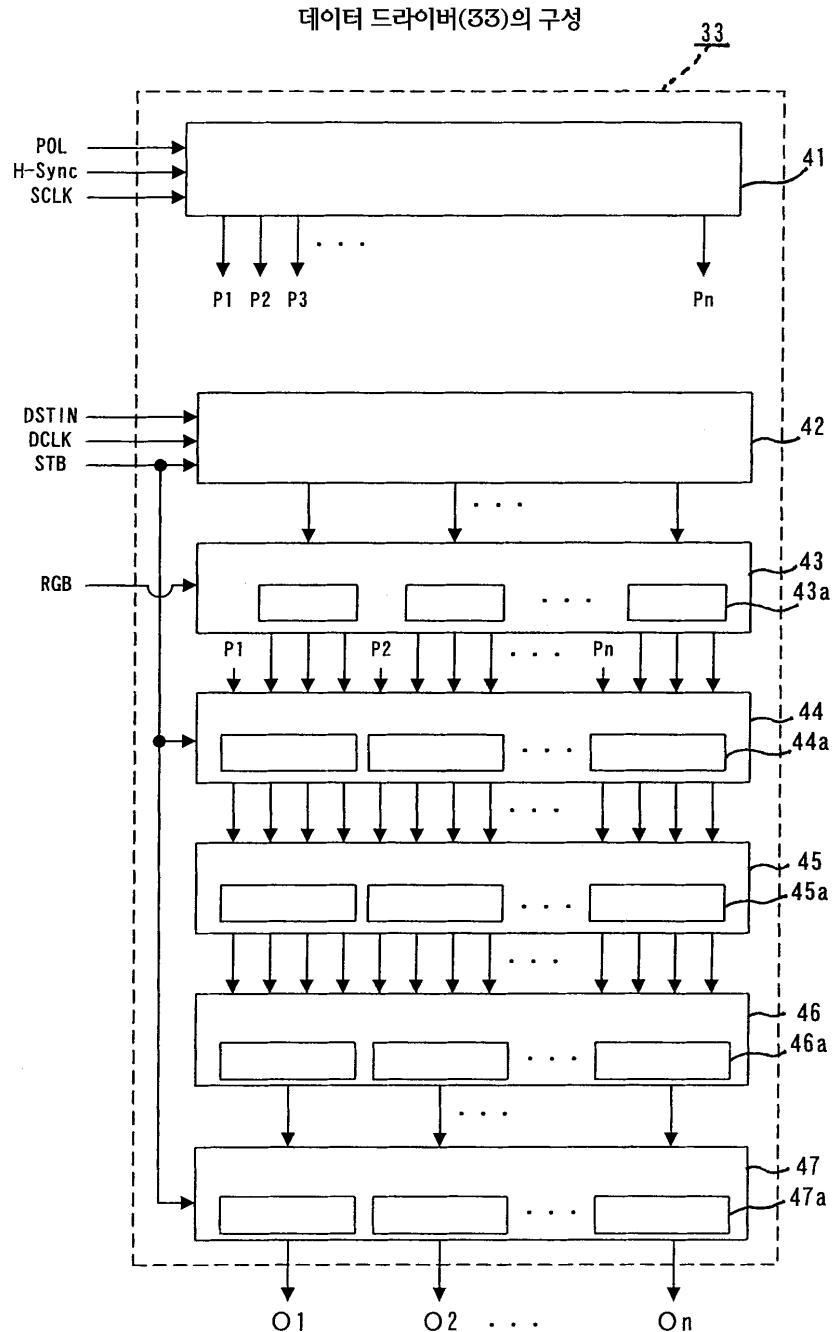

도 9는 데이터 드라이버(33)의 구성을 나타내는 블럭도이다.

데이터 드라이버(33)는 시프트 레지스터 회로부(41,42), 데이터 레지스터 회로부(43), 래치 회로부(44), 레벨 시프트 회로부(45), D/A변환 회로부(46), 볼티지팔로우어부(47)로 구성되어 있다.

시프트 레지스터 회로부(41)는 극성 패턴 제어부(32)로부터 입력한 극성 패턴 신호(POL)를 수평 동기 신호(H-Sync)에 동기하여 판독을 개시한다. 그리고, 반전 패턴 신호(POL)을 시프트 클럭(SCLK)에 동기하여 시프트하고, n비트분의 극성 패턴 신호(POL)를 평행하게 출력한다. 이하, 시프트 레지스터 회로(41)로부터 평행하게 출력되는 신호를 극성 신호( $P_1 \sim P_n$ )라고 한다.

데이터 레지스터 회로부(43)는 n개의 레지스터(43a)로 구성되어 있다. 시프트 레지스터 회로부(42)는 데이터 스타트 신호(DSTIN), 데이터 클럭(DCLK) 및 스트로브 신호(STB)를 입력하여, 데이터 레지스터 회로부(43)의 레지스터(43a)의 어드레스를 설정한다. 즉, 데이터 레지스터 회로부(43)는 데이터 스타트 신호(DSTIN)를 입력하면 레지스터(43a)의 선두 어드레스를 설정하고, 데이터 클럭(DCLK)에 동기하여 어드레스를 인크리먼트한다. 데이터 레지스터 회로부(43)는 화상 신호(RGB)를 입력하고, 시프트 레지스터 회로부(42)에 의해 지정된 어드레스의 레지스터(43a)에 R신호, G신호 또는 B신호를 기억한다.

래치 회로부(44)는 n개의 래치 회로(44a)로 구성되어 있다. 각 래치 회로부(44a)는 스트로브 신호(STB)에 동기하여 데이터 레지스터 회로부(43)의 출력 및 시프트 레지스터 회로부(41)의 출력을 래치한다. 이 때, 각 래치 회로(44a)는 3비트의 R신호, G신호 또는 B신호의 최상위 비트에 극성 신호( $P_1 \sim P_n$ )를 더하여, 4비트의 신호로 한다.

레벨 시프트 회로부(45)는 래치 회로부(44)로부터 출력되는 신호의 레벨을 변환한다. 본 실시 형태에 있어서, 레벨 시프트 회로부(45)는 래치 회로부(44)로부터 출력되는 최고치가 3.3V의 신호를, 최고치가 12V의 신호로 변환해 D/A변환 회로부(46)에 출력한다.

D/A변환 회로부(46)는 n개의 D/A변환기(46a)로 구성되어 있다. 이들 D/A변환기(46a)는 극성 신호( $P_1 \sim P_n$ )가 부가된 4비트의 R신호, G신호 및 B신호를 입력하여, 정극성(+) 또는 부극성(-)의 아날로그의 데이터 신호( $O_1 \sim O_n$ )를 출력한다. 볼티지팔로우어부(47)는 n개의 볼티지팔로우어(47a)로 구성되어 있다. 이들 볼티지팔로우어(47a)는 D/A변환 회로부(46)로부터 출력된 데이터 신호( $O_1 \sim O_n$ )를 스트로브 신호(STB)에 동기하여 액정 표시 패널(40)의 각 데이터 버스 라인(13)에 공급한다.

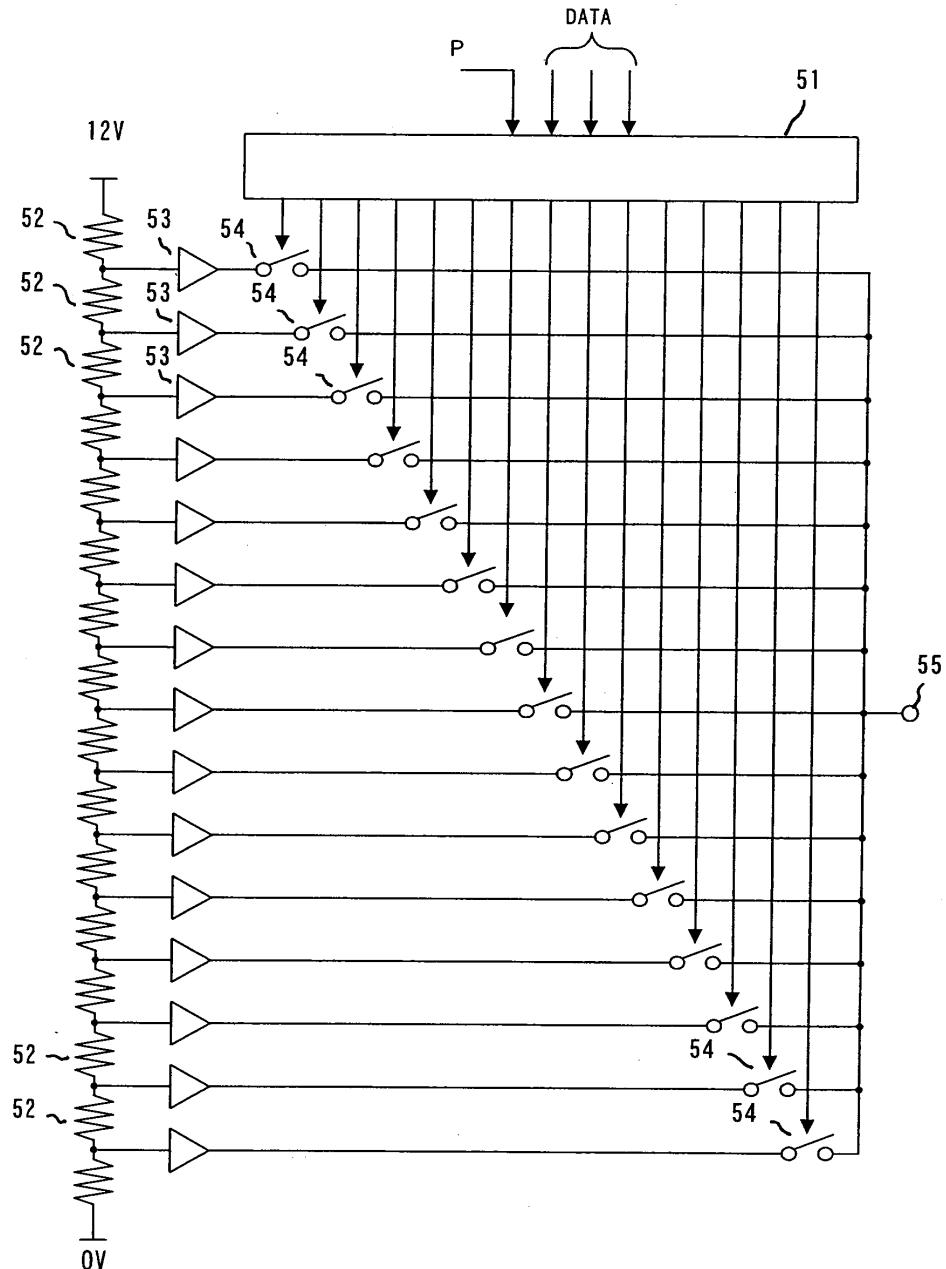

도 10은 D/A변환 회로부(46)내의 D/A변환기(46a)의 구성을 나타내는 회로도이다.

D/A변환기(46a)는 디코더(51), 17개의 저항 소자(52), 16개의 볼티지팔로우어(53), 16개의 스위치 소자(54)로 구성되어 있다. 저항 소자(52)는 고전위측 전원선(+ 12V)과 저전위측 전원선(0V) 사이에 직렬 접속되어 있다. 각 저항 소자(52)의 접속점(노드)에는 각각 볼티지팔로우어(53)의 입력이 접속되어 있다. 이들 볼티지팔로우어(53)의 출력은 각 스위치 소자(54)의 하나의 말단측에 각각 접속되어 있다. 각 스위치 소자(54)의 다른 말단측은 모두 출력 단자(55)에 접속되어 있다.

각 스위치 소자(54)는 디코더(51)로부터 "1"이 주어지면 ON이 되고, "0"이 주어지면 OFF가 된다. 디코더(51)는 3비트의 R신호, G신호 또는 B신호에 1비트의 극성 신호(P)를 더한 4비트의 신호를 입력하고, 16비트의 신호를 출력한다.

도 11은 디코더(51)의 입력과 출력과의 관계를 나타내는 도면이다. 이 도 11에 나타낸 바와 같이, 디코더(51)로부터 출력되는 16비트의 신호는 어느 1비트가 "1"이고 다른 비트가 "0"이다. 또, 입력 신호가 "0000"일 때의 전압이 중심 전압(V0)이고, 이 중심 전압(V0)에 따른 전압을 기준 전압으로서 대향 전극(24)에 인가한다.

출력 단자(55)로부터 출력되는 신호(데이터 신호( $O_1 \sim O_n$ ))의 전압이 기준 전압보다도 높은 경우(V1~V7)는 데이터 신호는 정극성(+)이고, 기준 전압보다도 낮은 경우(V1~V7)는 부극성(-)이다. 즉, 디코더(51)에 입력되는 최상위 비트(극성 신호)가 "0"일 때는 볼티지팔로우어부(47)로부터 출력되는 데이터 신호( $O_1 \sim O_n$ )는 정극성이 되고, 최상위 비트가 "1"일 때는 부극성이 된다.

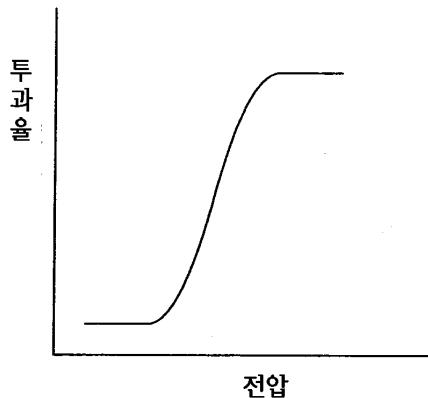

#### (5) 인가 전압과 투과율과의 관계 및 극성 패턴

도 12는 횡축에 화소 전극(14)과 대향 전극(24) 사이에 인가하는 전압을 취하고, 종축에 빛의 투과율을 취해 양자의 관계(전압-투과율 특성)를 나타내는 도면이다. 이 도 12에 나타낸 바와 같이, 인가 전압이 낮은 경우 및 인가 전압이 높은 경우는 전압이 약간 변화되어도 투과율의 변동은 작다. 그러나, 인가 전압이 중간 정도인 경우는 인가 전압의 약간의 변동에 의

해 투과율이 크게 변화한다. 상술한 바와 같이, 화소 전극에는 교류 전압을 인가한다. 따라서, 중간 계조(하프톤)의 표시일 때에, 정극성시의 인가 전압과 부극성시의 인가 전압이 대칭이 아니면, 교류 전압의 주기로 휘도가 변동하여 플리커가 발생한다.

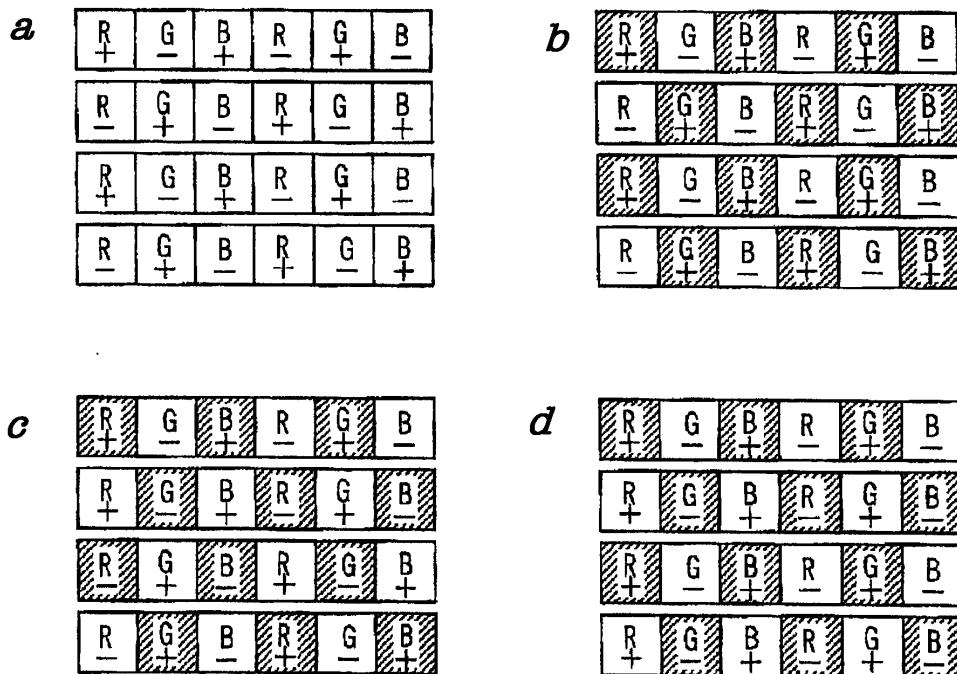

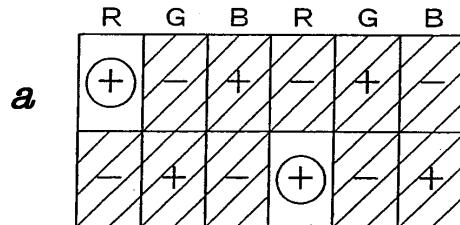

도 13a에서는 액정 표시 패널(40)의 모든 화소 전극(14)의 극성을 동일하게 하고, 1프레임마다 극성을 반전시키는 극성 패턴으로 되어 있다. 이 경우, 예를 들면 회색을 표시하였을 때에 플리커가 현저해진다.

또, 도 13b에서는 홀수행째의 각 화소 전극(14)의 극성을 동일하게 하고, 짝수행째의 각 화소 전극(14)의 극성을 역극성으로 하여, 1프레임마다 극성을 반전시키는 극성 패턴으로 하고 있다. 이 경우, 예를 들면 회색과 흑의 가로 줄무늬를 표시하였을 때에 플리커가 현저해진다.

도 13c에서는 홀수열째의 각 화소 전극(14)의 극성을 동일하게 하고, 짝수열째의 각 화소 전극(14)의 극성을 역극성으로 하여, 1프레임마다 극성을 반전시키는 극성 패턴으로 하고 있다. 이 경우, 예를 들면 중간 계조(암)의 녹과 흑의 세로 줄무늬를 표시하였을 때에 플리커가 현저해진다.

도 13d에서는 수평 방향 및 수직 방향으로 인접하는 화소 전극(14)의 극성을 다르게 하고, 1프레임마다 극성을 반전시키는 극성 패턴으로 하고 있다. 이 경우는 중간 계조(암)의 녹과 흑의 도트마다 모자이크 표시에서 플리커가 현저해진다.

종래, 일반적으로 행해지고 있는 상술한 3종류의 극성 패턴(도 13b~d)에서는 극성 패턴을 어떻게 바꾸어도, 플리커가 현저해지는 표시 패널이 반드시 존재한다. 상술의 표시 패턴, 즉 가로 줄무늬, 세로 줄무늬 또는 모자이크 표시는 통상의 퍼스널 컴퓨터의 표시에서는 빈번하게 사용된다. 이와 같이 빈번하게 사용되는 표시 패턴에서는 플리커가 현저해지는 것은 바람직하지 않다.

본 실시 형태에 있어서는 극성 패턴을 통상 잘 사용되는 표시 패턴에 대하여 플리커의 발생이 지극히 적은 극성 패턴으로 한다. 예를 들면, 도 14에 나타낸 바와 같이, 수평 방향으로 나란한 화소 전극(14)의 극성을 2비트마다 반전시키고, 수직 방향으로 나란한 화소 전극(14)의 극성을 1비트마다 반전시킨다. 또, 이들 화소 전극(14)의 극성을 1프레임마다 반전시킨다. 이 경우, 플리커가 현저하게 나타나는 것은 도 15a와 같이, 중간 휘도 표시의 화소와, 저 휘도 표시의 화소가 2비트씩 교대로 나란히 되었을 때이고, 예를 들면, 도 15b에 나타낸 바와 같은 암황색, 암 물색, 암청, 암적으로 구성되는 모자이크 패턴을 표시할 때이다. 퍼스널 컴퓨터에서는 이러한 모자이크 패턴을 표시하는 확률은 적기 때문에, 도 14에 나타낸 바와 같이 극성 패턴을 설정함으로써, 통상의 사용에서는 플리커가 현저하게 나타나는 일은 없다.

## (6) 동작

이하, 본 실시 형태의 액정 표시 패널의 구동 회로의 동작에 대하여 설명한다.

도 5에 나타낸 바와 같이, 타이밍 컨트롤러(31)는 퍼스널 컴퓨터(37)로부터 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync), 데이터 클럭(DCLK), 화상 신호(RGB)를 입력하고, 이들 신호로부터 시프트 클럭(SCLK), 데이터 스타트 신호(DSTIN), 스트로브 신호(STB), 게이트 스타트 신호(GSTR) 및 게이트 클럭(GCLK)을 생성한다.

도 8에 나타낸 극성 패턴 제어부(32)의 제어 회로(32a)는 수직 동기 신호(V-Sync) 및 수평 동기 신호(H-Sync)에 동기하여 ROM(32b)으로부터 극성 패턴의 판독을 개시한다. 즉, 제어 회로(32a)는 수직 동기 신호(V-Sync)가 "0"에서 "1"로 변화한 뒤, 수평 동기 신호(H-Sync)의 최초의 상승에서 ROM(32b)의 선두 어드레스를 지정하고, 그 후, 시프트 클럭(SCLK)에 동기하여 어드레스를 인크리먼트한다. 이에 따라, ROM(32b)으로부터 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL)가 1비트씩 출력된다. 제어 회로(32a)는 ROM(32b)으로부터 수평 방향의 화소수(n개)분만큼의 극성 패턴 신호(POL)가 출력되면, 다음의 수평 동기 신호(H-Sync)의 상승까지 극성 패턴 신호(POL)의 판독을 일단 정지한다.

본 실시 형태에서는 1프레임마다 화소 전극의 극성을 반전시킨다. 이 때문에, ROM(32b)은 2프레임분의 비트수의 극성 패턴을 기억하고 있고, 홀수번째의 프레임용 극성 패턴과 짝수번째의 프레임용 극성 패턴은 "1"과 "0"이 정확히 역으로 되어 있다. 그리고, 제어 회로(32a)는 2수직 동기 기간마다 ROM(32b)의 판독한 곳을 선두 어드레스로 돌린다. 또, ROM(32b)에 1프레임분의 극성 패턴 신호(POL)를 기억해 두고, 1프레임마다 ROM(32b)의 출력을 반전시켜도 좋다. 이 경우는 ROM(32b)의 출력처를 1수직 동기 기간마다 전환 스위치와, ROM(32b)으로부터 출력된 신호를 반전시키기 위한 인버터가 필요해진다.

도 9에 나타낸 데이터 드라이버(33)의 시프트 레지스터 회로부(41)는 수평 동기 신호(H-Sync)에 동기하여 극성 패턴 신호(POL)의 판독을 개시하고, 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL)를 1비트씩 시프트한다. 그리고, 수평 방향의 화소수(n개)분만큼 극성 패턴 신호(POL)를 시프트하면, 시프트 동작을 정지하고, 극성 신호( $P_1 \sim P_n$ )를 출력한다.

한편, 시프트 레지스터 회로부(42)는 타이밍 컨트롤러(31)로부터 데이터 스타트 신호(DSTIN), 데이터 클럭(DCLK) 및 스트로브 신호(STB)를 입력하고, 데이터 레지스터 회로부(43)의 어드레스 설정을 개시한다. 즉, 시프트 레지스터 회로부(42)는 데이터 스타트 신호(DSTIN)가 "0"에서 "1"로 변화하면, 데이터 레지스터 회로부(43)의 초기 어드레스를 설정한다. 그리고, 데이터 클럭(DCLK)에 동기하여 어드레스를 인크리먼트한다. 이에 따라, 데이터 레지스터 회로부(43)의 각 레지스터(43a)에 R신호, G신호 또는 B신호가 차례로 기입된다. 즉, 1번째의 데이터 클럭(DCLK)에서 1번째의 R신호(D1), G신호(D2) 및 B신호(D3)가 데이터 레지스터 회로부(43)의 1~3번째의 레지스터(43a)에 기입되며, 또 2번째의 데이터 클럭(DCLK)에서 2번째의 R신호(D4), G신호(D5) 및 B신호(D6)가 4~6번째의 레지스터에 기입된다. 이와 같이 하여, 1수평 동기 기간분의 R신호, G신호 및 B신호가 데이터 레지스터 회로부(43)에 기입된다.

래치 회로부(44)의 각 래치 회로(44a)는 데이터 레지스터 회로부(43)로부터 출력되는 각 3비트의 R·G·B신호에 시프트 레지스터 회로부(41)로부터 출력되는 각 1비트의 극성 신호( $P_1 \sim P_n$ )를 더해 각 4비트의 데이터로 하고, 스트로브 신호(STB)에 동기하여 레벨 시프트 회로부(45)에 출력한다. 레벨 시프트 회로부(45)는 이들 각 4비트의 신호의 전압 레벨을 변환해 출력한다.

D/A변환 회로부(46)는 레벨 시프트 회로부(45)로부터 출력된 각 4비트의 신호를 D/A변환하여, 아날로그의 데이터 신호( $O_1 \sim O_n$ )를 출력한다. 이 경우, 도 11에 따라, 디코더 입력의 최상위 비트가 "0"일 때는 정극성의 신호, "1"일 때는 부극성의 신호를 출력한다. 볼티지팔로우어부(47)는 스트로브 신호(STB)에 동기한 타이밍으로 데이터 신호( $O_1 \sim O_n$ )를 액정 표시 패널(40)의 각 데이터 버스 라인(13)에 출력한다.

한편, 게이트 드라이버(34)는 타이밍 컨트롤러(31)로부터 게이트 스타트 신호(GSTR)가 입력되면, 게이트 클럭(GCLK)에 동기하여 최상위의 게이트 버스 라인(12)으로부터 최하위의 게이트 버스 라인(12)까지 1개씩 차례로 주사 신호(SCAN)를 공급한다. 이에 따라, 주사 신호(SCAN)가 주어지고 있는 게이트 버스 라인(12)에 접속한 TFT(15)가 ON이 되고, 데이터 드라이버(33)로부터 출력된 데이터 신호( $O_1 \sim O_n$ )가 화소 전극(14)에 공급된다. 그리고, 화소 전극(14)과 대향 전극(24) 사이에 전계가 발생되고, 액정 문자가 전계에 의해 그 배열이 바뀌기 때문에, 각 화소의 광투과율이 인가 전압에 따라 변화한다. 이 경우, 각 화소 전극(14)에 인가되는 신호의 극성은 ROM(32b)에 기억되어 있는 극성 패턴에 의해 결정되고, 1프레임마다 극성이 반전된다.

#### (7) 제1 실시 형태의 효과

제1 실시 형태에 있어서는 ROM(32b)에 기억한 극성 패턴에 의해 각 화소 전극에 공급하는 신호의 극성을 결정하므로, 화상 신호의 복잡한 처리 등을 하지 않고 간단한 회로 구성으로 플리커의 발생이 어려운 극성 패턴으로 할 수 있다. 예를 들면, 컴퓨터용 액정 표시 패널의 구동 회로에 적용하는 경우, 도 14에 나타낸 바와 같이 극성 패턴을 설정함으로써, 통상의 사용에서는 플리커를 대폭적으로 저감할 수 있다. 또, 본 실시 형태에 있어서는 드라이버 회로(데이터 드라이버(33) 및 게이트 드라이버(34))를 액정 표시 패널(40)의 한편 측에만 배치하는 소위 편측 구동의 액정 표시 장치에 적용하는 것이 가능하다.

#### (제2 실시 형태)

도 16은 본 발명의 제2 실시 형태의 액정 표시 장치의 기본 구성을 나타내는 블럭도이다. 또한, 도 16에 있어서, 도 1과 동일물에는 동일한 부호를 부여하고 있다.

도 16에 나타낸 바와 같이, 본 실시 형태의 액정 표시 장치는 액정 표시 패널(501), 데이터 드라이버(502), 게이트 드라이버(503), 입력 제어부(555), 기준 전원 생성부(556)로 구성되어 있다.

액정 표시 패널(501)에는 매트릭스상에 배치된 복수의 화소(도 4 참조)와, 복수개의 데이터 버스 라인(502a) 및 복수개의 게이트 버스 라인(503a)과, 데이터 버스 라인(502a) 및 게이트 버스 라인(503a)과 각 화소 사이에 각각 접속되는 복수의 TFT(도 4 참조)가 설치되어 있다. 데이터 드라이버(502)는 데이터 버스 라인(502a)에 데이터 신호를 출력하고, 게이트 드

라이버(503)는 수평 동기 신호에 동기한 타이밍으로 게이트 버스 라인(503a)에 차례로 소정의 주사 신호를 출력한다. TFT는 게이트 버스 라인(503a)에 소정의 주사 신호가 공급되면 ON이 되어, 데이터 버스 라인(502a)에 공급된 데이터 신호를 화소 전극에 전달한다.

입력 제어부(555)는 컴퓨터(504)로부터 화상 신호, 동기 신호 및 동작 클럭 등의 신호를 입력하고, 데이터 드라이버(502) 및 게이트 드라이버(503)에 소정의 신호를 출력한다. 또, 입력 제어부(555)는 표시 패턴의 변화 주기와 기준 전압의 극성 반전 주기와의 상관 관계를 상시 감시하고, 양자의 동기가 겹쳐되어, 미리 설정된 특정의 표시 패턴으로 판정되면, 본래의 기준 전압의 극성 반전 주기와는 다른 극성 반전 주기를 기준 전원 생성부(556)에 출력하여, 임의의 반전 주기로 기준 전압을 데이터 드라이버(502)에 공급한다.

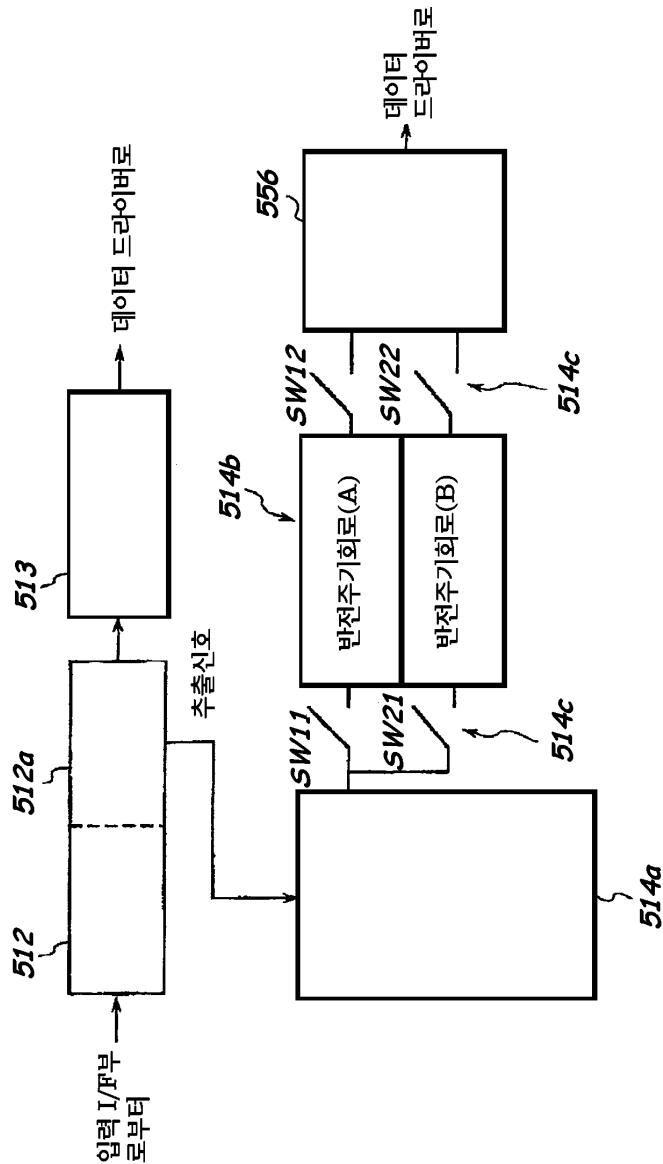

도 17은 입력 제어부(555)의 구성을 나타내는 블럭도이다. 입력 제어부(555)는 입력 I/F부(511), 입력 데이터 래치 회로(512), 데이터 출력 회로(513), 타이밍 제어 회로(514)로 구성되어 있다. 타이밍 제어 회로(514)는 입력 I/F부(511)를 통하여 입력되는 동기 신호 및 동작 클럭(CLK)과, 입력 데이터 래치 회로(512)에 의해 추출되는 화상 데이터 추출 신호에 의거하여, 데이터 출력 회로(513)의 동작 클럭(CLK2)이나, 데이터 드라이버(502)의 동작 클럭, 데이터 스트트 펄스 및 래치 펄스 및 게이트 드라이버(503)의 동작 클럭, 게이트 스트트 펄스 및 아웃풋 인에이블 신호, 또한 기준 전원 생성부(556)로부터 공급되는 기준 전압의 극성 반전 주기를 제어하는 극성 반전 신호를 출력한다. 데이터 출력 회로(513)는 동작 클럭(CLK2)에 의해서, 데이터 드라이버(502)에 출력되는 화상 신호의 출력 타이밍을 설정한다.

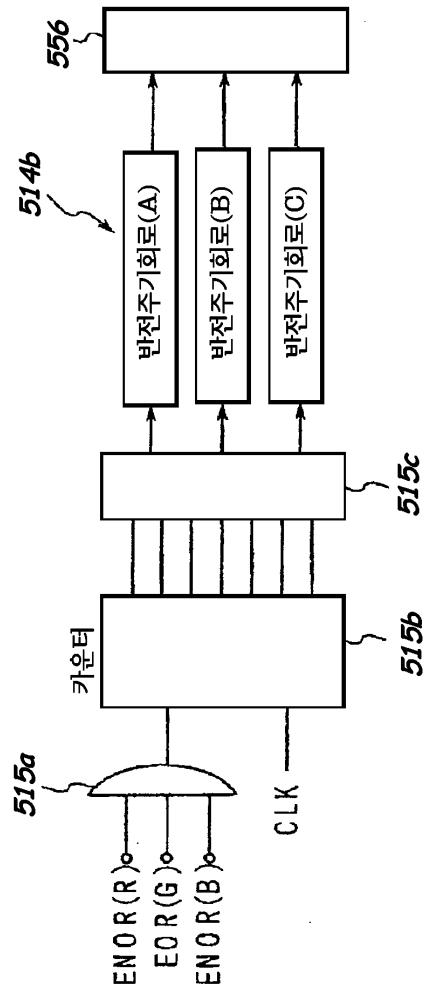

도 18은 타이밍 제어 회로(514)의 구성을 나타내는 블럭도이다.

타이밍 제어 회로(514)는 도 18에 나타낸 바와 같이, 화상 데이터 추출부를 구성하는 입력 데이터 추출부(512a)와, 표시 패턴 판정부를 구성하는 표시 패턴 판정부(514a), 반전 주기 제어부를 구성하는 반전 주기 회로군(514b) 및 스위치군(514c)으로 구성되어 있다.

입력 데이터 추출부(512a)는 입력 데이터 래치 회로(512)내에 설치하고, 연속하는 화상 신호로부터 인접하는 2개의 화소에 공급되는 화상 신호를 차례로 추출하여 추출 신호로서 출력한다.

표시 패턴 판정부(514a)는 추출된 2개의 화상 신호(추출 신호)의 상호 변화, 예를 들면 백으로부터 흑으로의 변화량 및 변화의 회수를 계수하고, 특정의 표시 패턴을 판정한다. 여기서, 특정의 표시 패턴이란, 초기 상태에 있는 기준 전압의 극성 반전 주기에 대해 표시 플리커, 혹은 소비 전력의 증대가 현저해지는 패턴이며, 체크무늬(체크 패턴)이나 녹색의 배경에 수평 라인을 표시하는 등의 패턴을 말한다.

반전 주기 회로군(514b) 및 스위치군(514c)은 표시 패턴 판정부(514a)로부터의 판정 결과에 의거하며, 특정의 표시 패턴이 검출된 경우에, 기준 전원 생성부(556)에 출력되는 극성 반전 신호(극성 반전 주기)를 전환하는 것이며, 도 18에 나타낸 바와 같이, 예를 들면 2개의 다른 극성 반전 주기를 갖는 반전 주기 회로(A,B)를 갖추고, 통상은 한쪽의 반전 주기 회로(A)의 극성 반전 주기에 의거하여 표시 동작을 행하고, 특정의 표시 패턴이 검출되면, 스위치군(514c)을 전환 제어하고, 다른 쪽의 반전 주기 회로(B)를 선택하여 다른 극성 반전 주기에 의해 표시 동작을 한다.

그리고, 기준 전원 생성부(556)는 반전 주기 회로(B)가 갖는 반전 주기에 의거하여 데이터 드라이버(502)에 극성 반전 신호를 공급한다.

또한, 반전 주기 제어부의 구성으로서, 표시 패턴 판정부(514a)에 의한 판정 결과에 의거하여 복수의 반전 주기 회로(A,B) 중, 어느 것인가를 선택하도록, 1개의 스위치(SW11, SW12, SW21, SW22)를 전환 제어하는 것을 나타냈지만, 기준 전원 생성부(556)에 대해 극성 반전 주기를 임의로 변경해 출력할 수 있는 것이면, 이에 한정되는 것은 아니다.

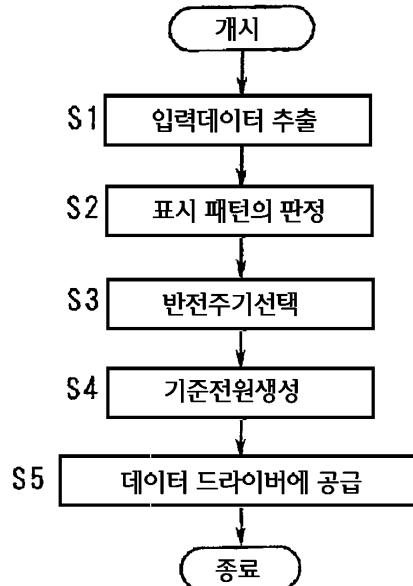

### (1) 동작

다음에, 상술한 타이밍 제어 회로의 반전 주기 제어 동작에 대하여, 도 19의 플로차트를 참조하여 설명한다.

여기서, 도 18에 나타낸 타이밍 제어 회로에 있어서, 초기 상태에서는 반전 주기 회로군(514b)을 선택하는 스위치군(514c)은 SW11과 SW12가 다 같이 ON상태에 있어서, 반전 주기 회로(A)가 갖는 극성 반전 주기가 기준 전원 생성부(556)에 출력되고 있는 것으로 한다.

먼저, 입력 데이터 추출부(512a)는 입력I/F부(511)를 통하여 입력 데이터 래치 회로(512)에 입력되어 보관 유지되는 화상 신호를 상시 감시하고, 인접하는 2개의 화소에 공급되는 화상 신호를 R, G, B의 각 데이터마다 추출한다(S1).

이어서, 표시 패턴 판정부(514a)는 입력 데이터 추출부(512a)에 의해 추출된 화상 데이터의 변화량 및 변화의 회수를 계수 하여, 초기 상태로서 설정되어 있는 반전 주기 회로(A)의 극성 반전 주기에 대하여 표시 화면의 플리커가 현저하게 되거나, 혹은 소비 전력의 증대를 초래하는 표시 패턴을 검출, 판정한다(S2).

이어서, 특정의 표시 패턴이 검출되면, 현재 선택되고 있는 반전 주기 회로(A)와는 다른 반전 주기를 갖는 다른 쪽의 반전 주기 회로(B)를 선택하도록, 스위치 SW11 및 SW12를 OFF상태로 하고, 스위치 SW21 및 SW22를 ON상태로 한다(S3).

이어서, 새로 선택된 반전 주기 회로(B)가 갖는 극성 반전 주기를 극성 반전 신호로서 기준 전원 생성부(556)에 출력하여, 초기 상태와는 다른 극성 반전 주기로 기준 전압을 생성하여, 데이터 드라이버(502)에 공급한다(S4,S5).

한편, 입력 데이터 추출부(512a)에 의해 추출된 화상 데이터가, 표시 패턴 판정부(514a)에 미리 설정된 특정의 표시 패턴으로 판정되지 않을 때, 또 전환된 반전 주기 회로(B)가 갖는 극성 반전 주기에 대하여 표시 화면의 플리커가 현저하게 되거나, 혹은 소비 전력의 증대를 부르는 표시 패턴을 검출한 경우에는, 초기 상태에서 선택되어 있던 반전 주기 회로(A)로 전환하도록 스위치군(514c)을 제어한다.

이러한 반전 주기의 전환 방법에 의하면, 액정 표시 패널의 화소 중, 정극성 또는 부극성의 어느 것인가의 극성 전위의 화소만이 점등(ON) 상태로 되는 표시 패턴의 화상 데이터가 입력된 경우에는, 화소에 인가되는 기준 전압의 극성 반전 주기를 변경함으로써, 정극성과 부극성의 화소의 열을 변경할 수 있다. 여기서, 변경된 화소의 열은 동일한 표시 패턴이라도, 화소 전체의 반수가 ON상태로 되어 있은 것이 바람직하다.

구체적으로는 도 20에 나타낸 바와 같이, 통상의 동작 상태에 있어서는 초기 상태로서 반전 주기 회로(A)가 선택되고, 도 20a에 나타내는 것 같은 [RGBRGB...]의 화소의 열에 대하여 정극성「+」, 부극성「-」의 데이터 전압이 [+ - + - + - ...] 같이 교대로 인가되는 상태에 있는 것으로 한다.

이러한 상태에서, 도 20b에 나타낸 바와 같이, 한쪽의 극성의 화소, 예를 들면 정극성「+」의 화소만이 점등(ON)하는 것 같은 표시 패턴의 경우, 극성 반전의 주기와 표시 패턴의 변화가 동기되어 플리커가 발생된다.

상술한 바와 같이, 표시 화면에 표시되는 패턴은 입력 데이터 추출부(512a) 및 표시 패턴 판정부(514a)에 의해 상시 감시되고, 플리커가 현저하게 되는 표시 패턴이 검출되면, 표시 패턴 판정부(514a)로부터의 판정 결과에 의거하여 반전 주기 회로군(514b)을 전환하도록 스위치군(514c)이 제어된다.

이에 따라, 다른 쪽의 반전 주기 회로(B)가 선택되고, 예를 들면 도 20c에 나타낸 바와 같이 수평 라인 단위로 랜덤하게 극성 반전이 행해지는 주기나, 도 20d에 나타낸 바와 같이 1수평 라인마다 교대로 극성 반전이 행해지는 주기가 극성 반전 신호로서 기준 전원 생성부(556)에 출력된다.

따라서, 표시 화면에 플리커나 소비 전력의 증대를 부르는 표시 패턴이 되는 일련의 화상 데이터가 입력된 경우에는 즉시 화소에 인가되는 기준 전압의 극성 반전 주기를 전환할 수 있기 때문에, 표시 품질의 향상 및 소비 전력의 저감을 도모할 수 있다.

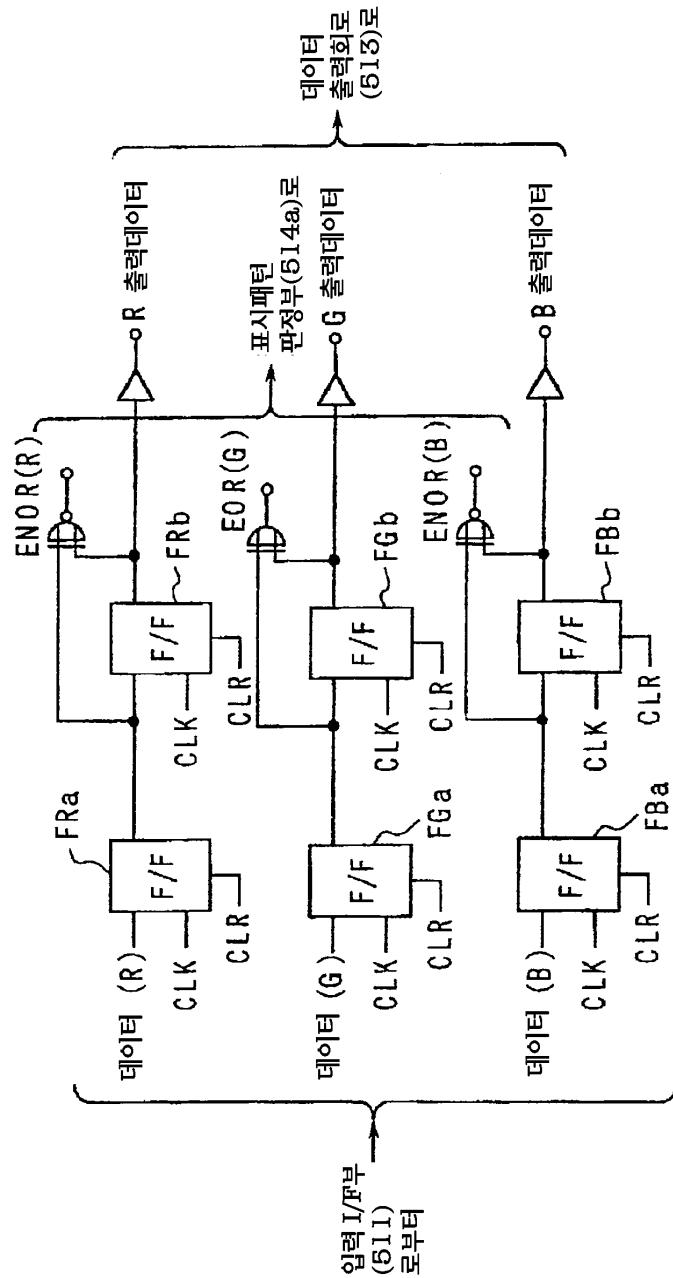

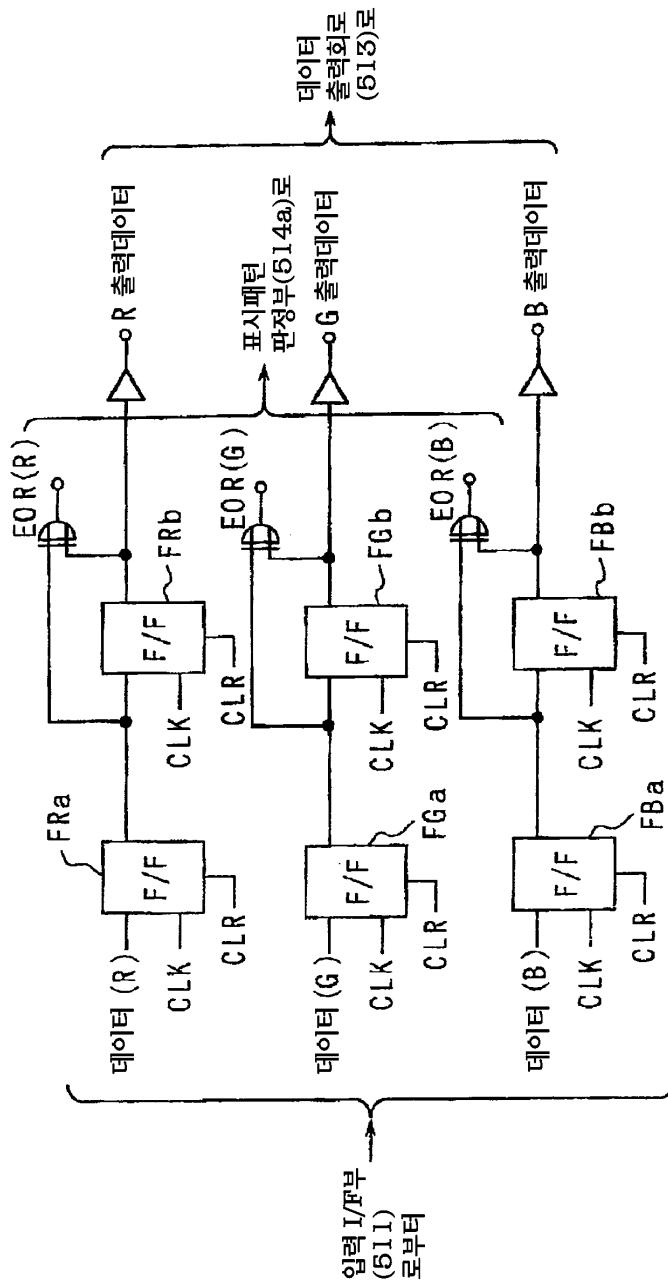

## (2) 입력 데이터 추출부(512a)의 구성

도 21은 입력 데이터 추출부(512a)의 일례를 나타내는 회로도, 도 22는 입력 데이터 추출부(512a)의 다른 예를 나타내는 회로도이다.

도 21 및 도 22에 나타낸 바와 같이, 입력 데이터 추출부(512a)는 R, G, B 각 데이터마다 복수 단의 플립 플롭(flip flop) (F/F)(FRa, FGa, FBa, FRb, FGb, FBb)이 설치된 입력 데이터 래치 회로에 있어서, 후단의 플립 플롭(FRb, FGb, FBb)의 입력 데이터 및 출력 데이터를 입력으로 하고, 소정의 논리 출력을 추출 데이터로서, 표시 패턴 판정부(514a)에 출력하는 논리 게이트를 가지고 있다.

여기서, 논리 게이트는 예를 들면 표시 플리커가 현저하게 발생하는 체크무늬 등의 표시 패턴을 추출하는 경우에는 도 21에 나타낸 바와 같이, R 데이터 및 B 데이터에 대해서는 배타적 NOR(ENOR) 게이트가 설치되고, G 데이터에 대해서는 배타적 OR(EOR) 게이트가 설치된다.

이와 같이, 입력 데이터 래치 회로(512)의 플립 플롭(FRb, FGb, FBb)의 입력 데이터 및 출력 데이터를 입력으로 하는 소정의 논리 출력에 의해서, 연속하여 인접하는 화상 데이터 상호의 변화의 상태를 R, G, B 각 데이터마다 상시 추출할 수 있다.

또, 액정 표시 장치의 소비 전력이 증대되며, 예를 들면 체크무늬의 흑백색이 교체하는 표시 패턴을 추출하는 경우에는 도 22에 나타낸 바와 같이, R, G, B 모든 데이터에 대하여, 플립 플롭(FRb, FGb, FBb)의 입력 데이터 및 출력 데이터를 입력으로 하는 배타적 OR(EOR) 게이트를 설치함으로써, R, G, B 모든 화상 데이터가 동기되는 반전 주기로 변동하는 상태를 상시 추출할 수 있다.

다음에, 본 발명에 관한 액정 표시 장치에 적용되는 표시 패턴 판정부의 일례에 대하여, 도 23을 참조하여 설명한다.

도 23에 나타낸 바와 같이, 표시 패턴 판정부(514a)는 입력 데이터 추출부(512a)에 의해 추출된 R, G, B의 각 논리 출력을 입력으로 하는 논리적(AND) 게이트(515a), 이 논리 출력을 입력으로 하고 카운트값을 비트 출력하는 카운터(515b), 카운터(515b)로부터의 비트 출력과 미리 설정된 규정치(기준치)를 비교하는 비교 회로(515c), 비교 결과에 의거하여 도시를 생략한 스위치에 의해 전환 설정되고, 또한, 서로 다른 극성 반전 주기를 갖는 복수의 반전 주기 회로(514b)로 구성되어 있다.

여기서, 반전 주기 회로(514b)는 후단의 기준 전원 생성부(556)에 소정의 극성 반전 신호를 출력하는 것이며, 예를 들면 초기 상태에 있어서는 반전 주기 회로(A)가 선택되고, 표시 화면의 플리커를 일으키는 특정의 표시 패턴이 검출된 경우에는 다른 반전 주기 회로(B,C)로 전환 설정되는 것이면 되며, 도 18에 나타낸 바와 같이, 적어도 2개의 반전 주기 회로를 가지고 있으면 된다.

또, 도 23에 나타낸 바와 같이, 3개 이상의 반전 주기 회로를 갖춘 구성에 있어서는 도 20b로부터 (C)에 나타낸 다른 극성 반전 상태를 반전 주기 회로(A,B,C) 각각에 미리 설정함으로써, 통상은 반전 주기 회로(A)를 선택하고, 특정의 표시 패턴이 검출된 경우에는 다른 반전 주기 회로(B,C) 중에서 무작위(랜덤)로 1개의 반전 주기 회로를 선택함으로써, 화소에 인가되는 기준 전압의 극성 반전 주기와 표시 패턴의 변화와의 동기를 회피할 수 있다.

이와 같이, 입력 데이터 추출부(512a) 및 표시 패턴 판정부(514a)에 의해서, 연속하여 인접하는 화상 데이터를 추출하고, 그 변화량 및 변화 회수를 카운트하여, 소정의 규정치를 비교함으로써, 특정의 표시 패턴을 감지, 판정할 수 있고, 액정 표시 패널(501)에 표시되는 표시 패턴의 주기와 화소에 인가되는 기준 전압의 극성 반전 주기와의 동기를 회피하여, 화면의 플리커나 소비 전력의 증대를 억제할 수 있다.

또, 이러한 구동 제어 방법에 의하면, 화소에 인가되는 기준 전압의 극성 반전 방식이, 예를 들면 1도트 단위, 2도트 단위 혹은 수평 라인, 수직 라인 단위의 반전 방식이라도, 표시 패턴의 주기와의 동기 상태를 회피하도록 극성 반전의 주기를 적절히 설정할 수 있다.

### (제3 실시 형태)

이하, 본 발명의 제3 실시 형태의 액정 표시 패널의 구동 회로에 대하여 설명한다. 본 실시 형태가 제1 실시 형태와 다른 점은 극성 패턴 제어부의 구성이 다르고, 기타의 구성은 제1 실시 형태와 같으므로, 중복하는 부분의 설명은 생략한다.

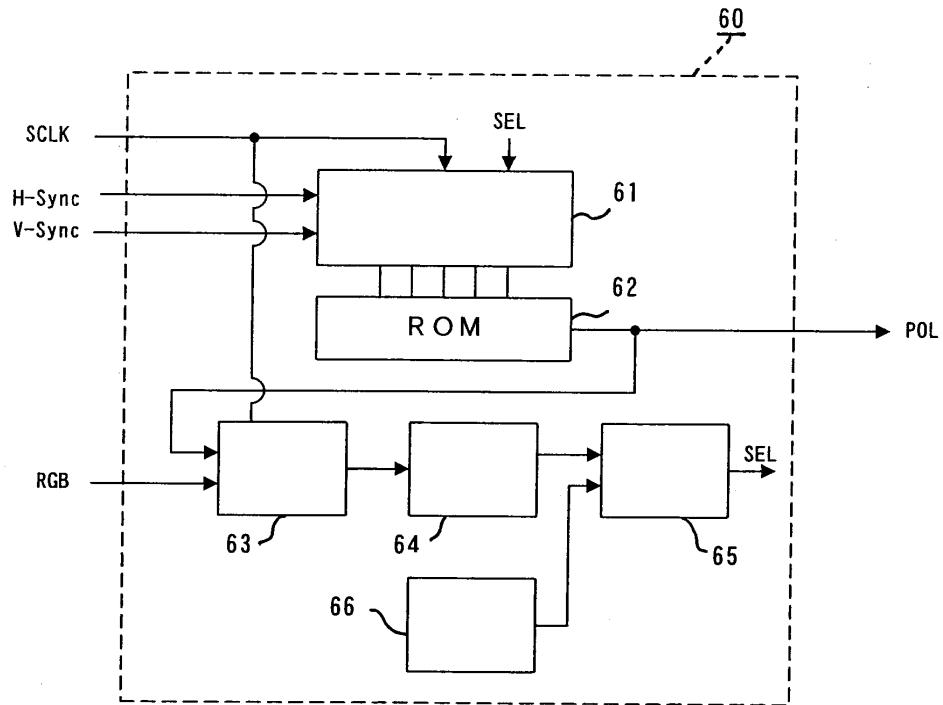

도 24는 본 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부(60)의 구성을 나타내는 블럭도이다. 극성 패턴 제어부(60)는 제어 회로(61), ROM(62), 비교기(63,65), 계수 회로(64), 임계값 설정부(66)로 구성되어 있다.

ROM(62)에는 2조분의 극성 패턴이 기억되어 있다. 각 극성 패턴은 모두 2프레임분의 비트수를 가지며, 1프레임마다 극성이 반전되도록 설정되어 있다. 제어 회로(61)는 어느 한쪽 조의 극성 패턴을 선택하고, ROM(62)의 초기 어드레스를 설정하고, 시프트 클럭(SCLK)에 동기하여 어드레스를 인크리먼트한다. 이에 따라, ROM(62)으로부터 한쪽 조의 극성 패턴이 1비트씩 판독되어, 극성 패턴 신호(POL)로서 출력된다.

비교기(63)는 ROM(62)으로부터 판독된 극성 패턴 신호(POL)와 타이밍 컨트롤러(31)로부터 출력되는 화상 신호(RGB)를 비교한다. 그리고, 예를 들면 화상 신호(RGB)의 최상위 비트와 극성 패턴 신호(POL)가 일치하는 경우는 "1", 다른 경우는 "0"을 시프트 클럭(SCLK)에 동기하여 출력한다. 계수 회로(64)는 비교기(63)의 출력을 감시하여, 단위 시간내에 또는 일정한 데이터수마다(단위 데이터수마다), 비교기(63)의 출력이 "1"이 되는 회수를 계수한다. 비교기(65)는 계수 회로(64)로부터 출력되는 계수값이 임계값 설정부(66)에 설정된 값을 넘는 경우는 선택 신호(SEL)를 "1"로 하고, 넘지 않는 경우는 "0"으로 한다.

제어 회로(61)는 선택 신호(SEL)가 "0"일 때는 현재 판독하고 있는 극성 패턴이 판독을 계속하고, 선택 신호(SEL)가 "1"일 때는 ROM(62)의 어드레스에 오프셋트를 더해, 다른 극성 패턴이 판독을 개시한다.

제1 극성 패턴으로서, 예를 들면 도 14에 나타낸 바와 같이 2비트씩 극성이 다른 패턴을 기억하고, 제2 극성 패턴으로서, 연속하는 3비트의 데이터 중 연속하는 2비트를 동일한 논리값, 다른 1비트를 역의 논리값으로 되는 극성 패턴, 예를 들면 도 25a에 나타낸 바와 같이, 수평 방향으로 연속하는 6개의 화소 전극(14)을 1조와 하고, 각조의 화소 전극(14)이 + + - - - -로 되는 극성 패턴을 ROM(62)에 기억해 둔다. 이 경우 ROM(62)으로부터 시프트 클럭(SCLK)에 동기하여 도 25b에 나타낸 극성 패턴 신호(POL)가 출력된다.

본 실시 형태에 있어서는 상술한 바와 같이, ROM(62)에 2조분의 극성 패턴을 기억해 두고, 비교기(63), 계수 회로(64), 비교기(65) 및 임계값 설정부(66)에 의해, ROM(62)으로부터 출력된 극성 패턴 신호(POL)와 화상 신호(RGB)가 유사한지의 여부를 판정하고 있다. 그리고, 양자가 유사하다고 판정하였을 때는 플리커가 발생할 우려가 있으므로, ROM(62)으로부터 판독하는 극성 패턴을 전환한다. 이에 따라, 표시하는 화상에 따라 극성 패턴이 자동적으로 전환되고, 플리커의 발생을 보다 확실하게 방지할 수 있다. 또, 본 실시 형태에 있어서는 간단한 회로 구성으로 화상 신호에 따라 극성 패턴을 전환하는 액정 표시 장치가 실현된다.

#### (제4 실시 형태)

이하, 본 발명의 제4 실시 형태의 액정 표시 패널의 구동 회로에 대하여 설명한다. 본 실시 형태가 제1 실시 형태와 다른 점은 극성 패턴 제어부 및 데이터 드라이버의 구성이 다르고, 기타의 구성은 제1 실시 형태와 같으므로, 중복하는 부분의 도시는 생략한다.

##### (1) 극성 패턴 제어부의 구성

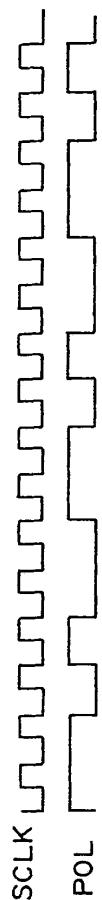

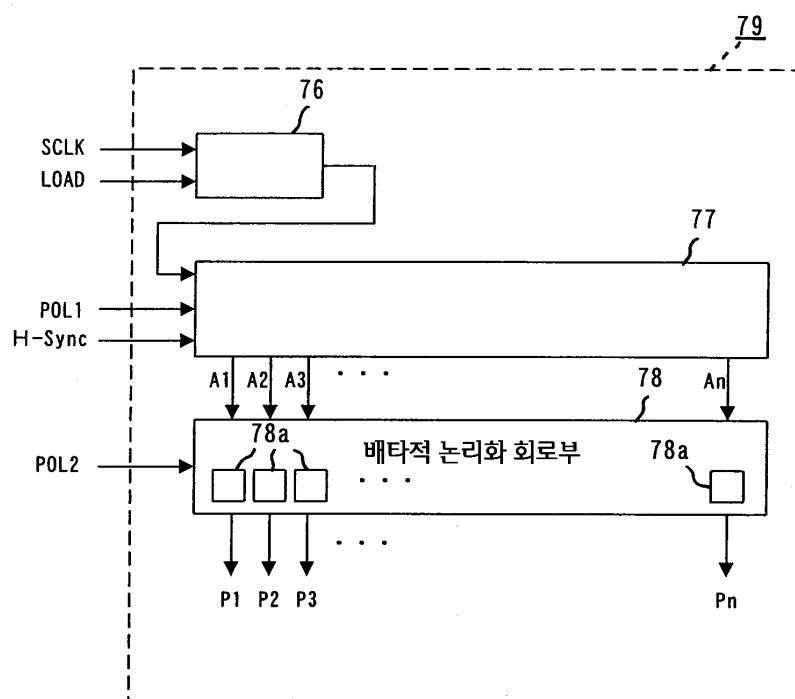

도 26은 본 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부(70)의 구성을 나타내는 블럭도이다.

극성 패턴 제어부(70)는 제어 회로(71), ROM(72), D-플립 플롭 회로(73,74) 및 배타적 논리화 회로(XOR)(75)로 구성되어 있다. ROM(72)에는 액정 표시 패널(40)의 수평 방향의 화소수(n개)분의 데이터를 1조로 한 극성 패턴이 기억되어 있다.

제어 회로(71)는 수평 동기 신호(H-Sync), 수직 동기 신호(V-Sync) 및 시프트 클럭(SCLK)을 입력하고, ROM(72)의 어드레스를 설정하는 것과 동시에, 전원을 ON으로 한 후 최초의 수평 동기 기간만 "1"로 되고, 그 후 "0"으로 되는 기입 신호(LOAD)를 발생한다. ROM(72)으로부터는 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL1)가 1비트씩 출력된다.

D-플립 플롭(73)은 수평 동기 신호(H-Sync)를 클럭 단자(CLK)에 입력하고, 반전 출력 단자(/Q, /)은 반전 신호를 나타낸다. 이하, 동일함)의 출력은 입력 단자(D)에 귀환한다. 또, D-플립 플롭 회로(74)의 클럭 단자(CLK)에는 수직 동기 신호(V-Sync)가 입력된다. 이 D-플립 플롭 회로(74)의 반전 출력 단자(/Q)의 출력은 입력 단자(D)에 귀환한다. D-플립 플롭 회로(73,74)의 각 반전 출력 단자(/Q)로부터 출력된 신호는 배타적 논리화 회로(75)에 입력되고, 이 배타적 논리화 회로(75)는 2개의 입력 신호의 배타적 논리화를 반전 신호(POL2)로서 출력한다.

배타적 논리화 회로(75)로부터 출력되는 반전 신호(POL2)는 수평 동기 신호(H-Sync)의 1주기마다 반전하고, 또한 수직 동기 신호(V-Sync)의 1주기마다 반전한다.

##### (2) 데이터 드라이버의 구성

도 27은 본 실시 형태의 액정 표시 패널의 구동 회로의 데이터 드라이버의 구성을 나타내는 블럭도이다. 단, 본 실시 형태의 액정 표시 패널의 구동 회로의 데이터 드라이버(79)가 도 9에 나타낸 데이터 드라이버와 다른 점은 극성 신호( $P_1 \sim P_n$ )를 출력하는 회로가 다르고, 시프트 레지스터 회로부(42)로부터 볼티지팔로우어부(47)까지의 구성은 같으므로, 도 27에 있어서도 9와 중복되는 부분의 도시를 생략한다.

AND회로(76)는 기입 신호(LOAD)가 "1"의 기간만, 시프트 클럭(SCLK)을 시프트 레지스터 회로부(77)에 전달한다. 시프트 레지스터 회로부(77)는 극성 패턴 제어부(70)로부터 입력한 극성 패턴 신호(POL1)를 시프트 클럭(SCLK)에 동기하여 시프트하고, 1수평 동기 기간분의 극성 패턴 신호(POL1)를 평행하게 출력한다. 이하, 시프트 레지스터 회로부(77)로부터 평행하게 출력되는 신호를 극성 신호( $A_1 \sim A_n$ )라 한다.

배타적 논리화 회로부(78)는 n개의 배타적 논리화 회로(78a)로 구성되어 있다. 그리고, 각 배타적 논리화 회로(78a)는 극성 신호( $A_1 \sim A_n$ )와 반전 신호(POL2)의 배타적 논리화를 극성 신호( $P_1 \sim P_n$ )로서 출력한다. 즉, 배타적 논리화 회로(78a)는 반전 신호(POL2)가 "1"일 때는 시프트 레지스터 회로부(77)로부터 출력된 극성 신호( $A_1 \sim A_n$ )를 극성 신호( $P_1 \sim P_n$ )로서 출력하고, 반전 신호(POL2)가 "0"일 때는 극성 신호( $A_1 \sim A_n$ )를 반전한 신호를 극성신호( $P_1 \sim P_n$ )로서 출력한다.

### (3) 동작

이하, 본 실시 형태의 액정 표시 패널 구동 회로의 동작에 대하여 설명한다.

도 26에 나타낸 극성 패턴 제어부(70)의 제어 회로(71)는 전원을 ON으로 한 후 최초의 수평 동기 신호(H-Sync)의 상승에 동기하여 기입 신호(LOAD)를 "1"로 한다. 또, 제어 회로(71)는 수평 동기 신호(H-Sync)에 동기하여 ROM(72)의 초기 어드레스를 설정하고, 시프트 클럭(SCLK)에 동기하여 어드레스를 인크리먼트한다. 이에 따라, ROM(72)으로부터 극성 패턴 신호(POL1)가 시프트 클럭(SCLK)에 동기하여 1비트씩 출력된다.

한편, 배타적 논리화 회로(75)는 1수평 동기 기간마다 및 1수직 동기 기간마다 논리값이 반전되는 반전 신호(POL2)를 출력한다.

도 27에 나타낸 데이터 드라이버(79)의 AND회로(76)는 기입 신호(LOAD)가 "1"의 기간은 시프트 클럭(SCLK)을 시프트 레지스터 회로부(77)에 전달한다. 시프트 레지스터 회로부(77)는 수평 동기 신호(H-Sync)가 "0"에서 "1"로 변화한 후, AND회로(76)로부터 입력되는 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL1)를 시프트하고, n비트분의 극성 패턴 신호(POL1)를 시프트하면, 이들 n비트분의 신호를 극성 신호( $A_1 \sim A_n$ )로서 평행하게 출력한다. 배타적 논리화 회로부(78)의 각 배타적 논리화 회로(78a)는 반전 신호(POL2)가 "1"인 기간은 극성 신호( $A_1 \sim A_n$ )를 극성 신호( $P_1 \sim P_n$ )로서 출력하고, 반전 신호(POL2)가 "0"인 기간은 극성 신호( $A_1 \sim A_n$ )를 반전한 신호를 극성 신호( $P_1 \sim P_n$ )로서 출력한다.

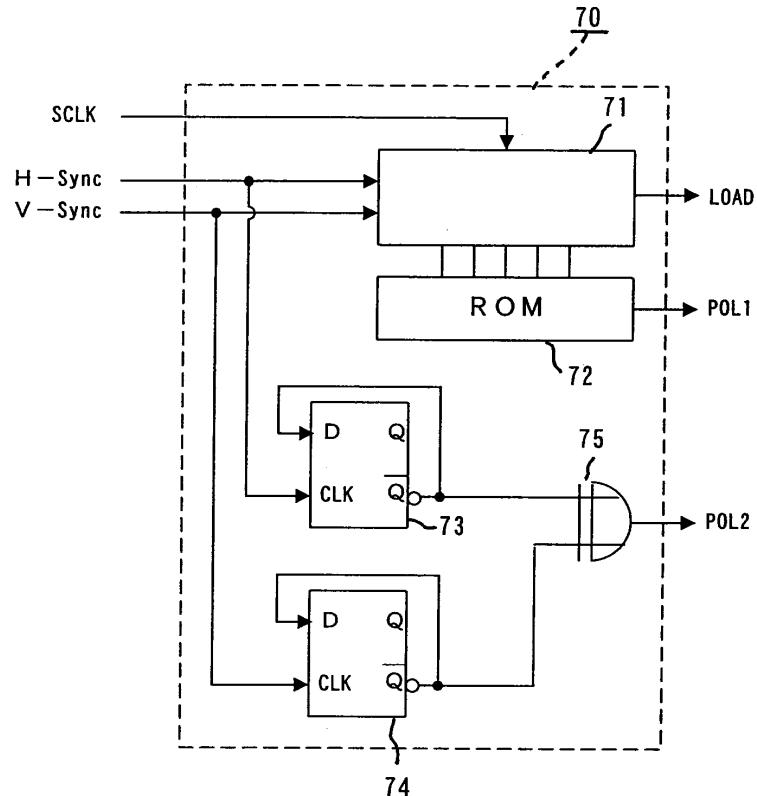

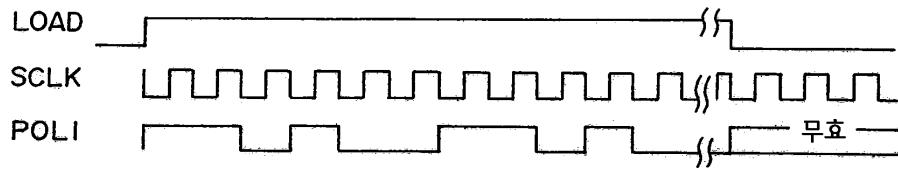

도 28은 기입 신호(LOAD), 시프트 클럭(SCLK) 및 극성 패턴 신호(POL1)의 타이밍을 나타내는 타이밍 차트를 나타내는 도면, 도 29는 반전 신호(POL2)와 극성 패턴과의 관계를 나타내는 도면, 도 30은 액정 표시 패널의 각 화소 전극에 인가되는 전압(극성)을 나타내는 도면이다.

이들 도 28~도 30에 나타낸 바와 같이, 기입 신호(LOAD)가 "1"인 기간은 시프트 클럭(SCLK)에 동기하여 극성 패턴 신호(POL1)가 시프트 레지스터 회로부(77)에 입력된다. 이에 따라, 시프트 레지스터 회로부(77)에는 n비트분의 극성 패턴 신호(POL1)가 기억된다. 그 후, 최초의 1수평 동기 기간이 종료되면 기입 신호(LOAD)가 "0"이 되고, 시프트 클럭(SCLK)이 시프트 레지스터 회로부(77)에 입력되지 않게 된다. 이 때문에, 시프트 레지스터 회로부(77)는 최초의 1수평 동기 기간에 입력된 극성 패턴 신호(POL1)를 그 후에도 보관 유지한다.

한편, 배타적 논리화 회로(75)로부터 출력되는 반전 신호(POL2)는 1수평 동기 기간마다 반전한다. 이 때문에, 도 29에 나타낸 바와 같이, 배타적 논리화 회로부(78)로부터 출력되는 극성 신호( $P_1 \sim P_n$ )(도 29에서는 P01에서 P12까지를 나타낸다)는 1수평 동기 기간마다 반전한다. 따라서, 도 30에 나타낸 바와 같이, 수직 방향으로 인접하는 각 화소 전극의 극성은 서로 다르다.

또한, 배타적 논리화 회로(75)로부터 출력되는 반전 신호(POL2)는 1수직 동기 기간마다 반전한다. 이에 따라, 각 화소 전극의 극성은 1프레임마다 반전한다.

#### (4) 제4 실시 형태의 효과

본 실시 형태에 있어서는 1수평 동기 기간분만큼의 극성 패턴을 ROM(72)에 기억해 두면 좋기 때문에, ROM(72)의 기억 용량이 적어진다.

또한, 본 실시 형태에 있어서도, 제3 실시 형태와 같이, ROM(72)에 복수 조의 극성 패턴을 기억해 두고, 데이터 신호 (DATA)와 극성 패턴 신호(POL1)를 비교기로 비교하여 양자의 유사를 평가하고, 플리커가 발생하는 있을 때에는 ROM (72)으로부터 판독하는 극성 패턴 신호를 전환하여도 좋다.

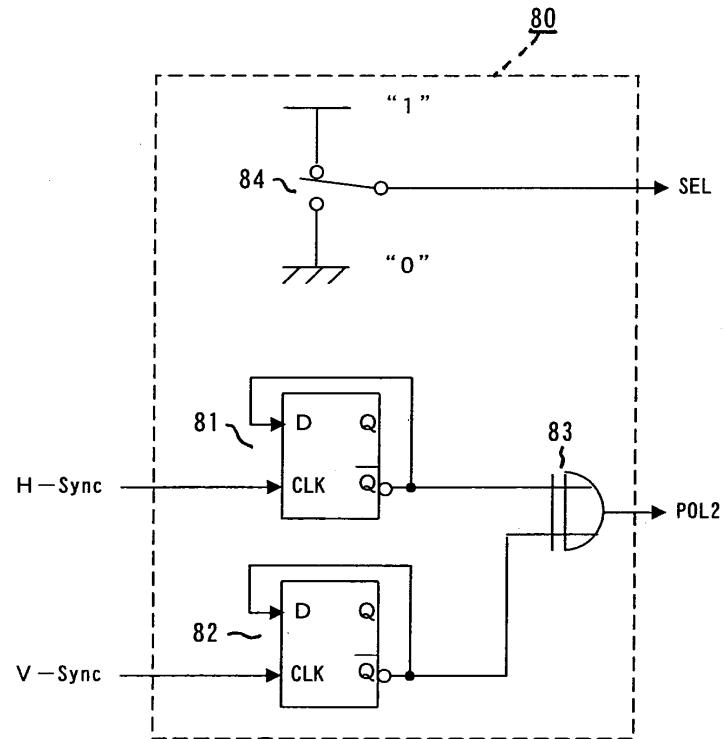

#### (제5 실시 형태)

이하, 본 발명의 제5 실시 형태의 액정 표시 패널의 구동 회로에 대하여 설명한다. 본 실시 형태가 제1 실시 형태와 다른 점은 극성 패턴 제어부 및 데이터 드라이버의 구성이 다르고, 기타의 구성은 제1 실시 형태와 같으므로, 중복하는 부분의 도시는 생략한다.

##### (1) 극성 패턴 제어부의 구성

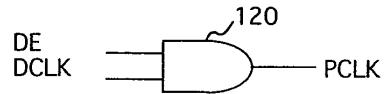

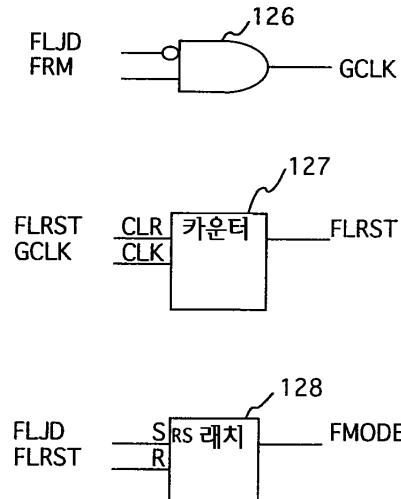

도 31은 본 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부의 구성을 나타내는 블럭도이다. 극성 패턴 제어부 (80)는 D-플립 플롭 회로(81,82), 배타적 논리화 회로(83) 및 전환 스위치(84)로 구성되어 있다. D-플립 플롭(81)은 수평 동기 신호(H-Sync)를 클럭 단자(CLK)에 입력하고, 반전 출력 단자(/Q)의 출력은 입력 단자(D)에 귀환한다. 또, D-플립 플롭 회로(82)의 클럭 단자(CLK)에는 수직 동기 신호(V-Sync)가 입력된다. 이 D-플립 플롭 회로(82)의 반전 출력 단자(/Q)의 출력은 입력 단자(D)에 귀환한다. D-플립 플롭 회로(81,82)의 각 반전 출력 단자(/Q)로부터 출력된 신호는 배타적 논리화 회로(83)에 입력된다. 이 배타적 논리화 회로(83)는 2개의 입력 신호의 배타적 논리화를 반전 신호(POL2)로서 출력한다. 이 배타적 논리화 회로(83)로부터 출력되는 반전 신호(POL2)는 수평 동기 신호(H-Sync)의 1주기마다 반전하고, 또한 수직 동기 신호(V-Sync)의 1주기마다 반전한다. 전환 스위치(84)는 고전위측 배선 또는 저전위측 배선의 어느 한쪽에 접속되고, "1" 또는 "0"을 출력한다.

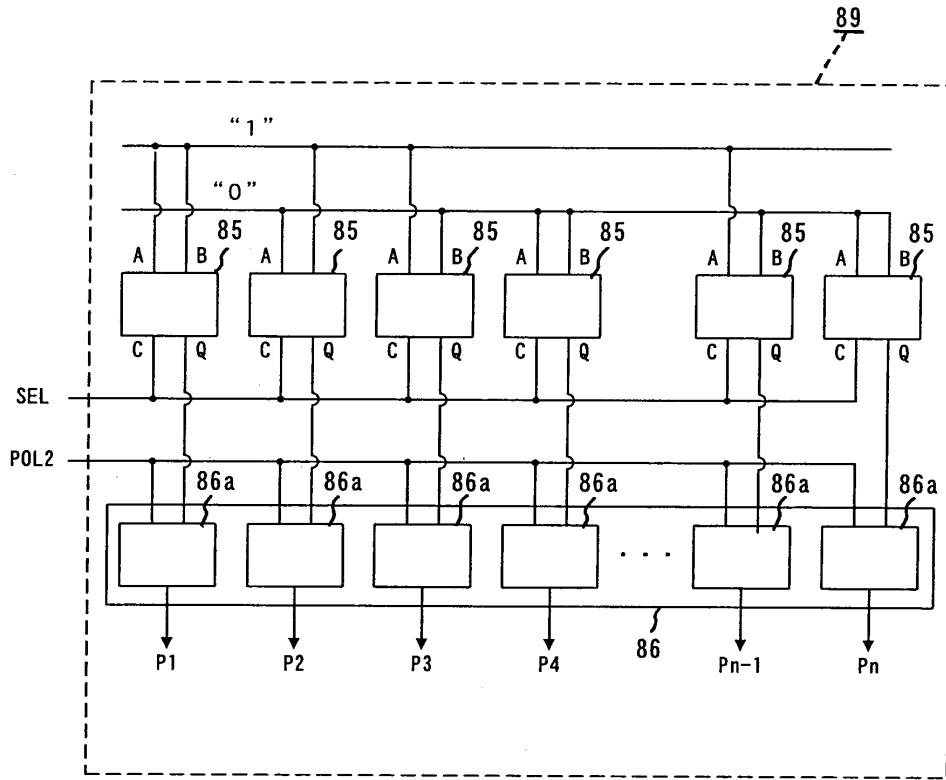

##### (2) 데이터 드라이버의 구성

도 32는 본 실시 형태의 액정 표시 패널의 데이터 드라이버의 구성을 나타내는 블럭도이다. 단, 본 실시 형태의 액정 표시 패널의 구동 회로의 데이터 드라이버(89)가 도 9에 나타내는 데이터 드라이버와 다른 점은 극성 신호( $P_1 \sim P_n$ )를 출력하는 회로가 다르고, 시프트 레지스터 회로부(42)로부터 볼티지팔로우어부(47)까지의 구성은 같으므로, 도 32에 있어서도 9와 중복하는 부분의 도시를 생략한다.

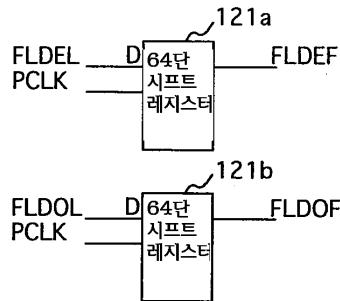

데이터 드라이버(89)는  $n$ 개의 논리 회로(85)와 배타적 논리화 회로부(86)를 가지고 있다. 각 논리 회로(85)는 도 33에 나타낸 바와 같이, 입력 단자(C)에 입력되는 선택 신호(SEL)가 "0"일 때는 입력 단자(A)의 입력이 출력 단자(Q)에 출력되고, 선택 신호(SEL)가 "1"일 때는 입력 단자(B)의 입력이 출력 단자(Q)에 출력된다.

본 실시 형태에 있어서는 도 32에 나타낸 바와 같이,  $4m-3$ (단,  $m=1, 2, \dots$ )번째의 논리 회로(85)는 입력 단자(A,B)가 모두 "1"의 라인에 접속되어 있다. 또,  $4m-2$ 번째의 논리 회로(85)는 단자(A)가 "0"의 라인, 단자(B)가 "1"의 라인에 접속되어 있다.  $4m-1$ 번째의 논리 회로(85)는 단자(A)가 "1"의 라인에 접속되고, 단자(B)가 "0"의 라인에 접속되어 있다.  $4m$ 번째의 논리 회로(85)는 단자(A,B)가 모두 "0"의 라인에 접속되어 있다.

또, 배타적 논리화 회로부(86)는  $n$ 개의 배타적 논리화 회로(86a)로 구성되어 있다. 각 배타적 논리화 회로(86a)의 한쪽의 입력 단자에는 반전 신호(POL2)가 입력되고, 다른 쪽의 입력 단자는 논리 회로(85)의 출력 단자(Q)에 접속되어 있다.

도 34a는 선택 신호(SEL)가 "0"일 때의 극성 패턴을 나타내는 도면, 도 34b는 선택 신호(SEL)가 "1"일 때의 극성 패턴의 극성을 나타내는 도면이다. 선택 신호(SEL)가 "0"일 때는 수평 방향 및 수직 방향으로 인접하는 화소 전극(14)의 극성은 모두 역이 된다. 또, 선택 신호(SEL)가 "1"일 때는 수평 방향으로 나란한 화소 전극(14)은 2화소씩 극성이 반전되고, 수직 방향으로 나란한 화소 전극은 1화소마다 극성이 반전된다.

### (3) 동작

예를 들면, 전환 스위치(84)를 전환하여 선택 신호(SEL)를 "0"으로 한다. 그렇다면, 논리 회로(85)로부터 배타적 논리화 회로부(86)에, 도 34a에 나타내는 반전 신호가 평행하게 입력된다. 배타적 논리화 회로부(86)는 논리 회로(85)로부터 입력된 신호와 반전 신호(POL2)의 논리화를, 극성 신호( $P_1 \sim P_n$ )로서 출력한다. 반전 신호(POL2)는 1수평 동기 기간마다 반전 하므로, 액정 표시 패널(40)의 각 화소 전극의 극성은 도 34a에 나타내게 된다. 또, 반전 신호(POL2)는 1수평 동기 기간마다 반전 하므로, 각 화소 전극의 극성은 1프레임마다 반전한다.

전환 스위치(84)를 전환하여 선택 신호(SEL)를 "1"로 함으로써, 배타적 논리화 회로(86)에 입력되는 극성 패턴이 변화되고, 액정 표시 패널(40)의 각 화소 전극의 극성은 도 34b에 나타낸 바와 같이 된다.

### (4) 제5 실시 형태의 효과

본 실시 형태에 있어서는 선택 신호(SEL)에 의해서, 극성 패턴을 변화시킬 수 있다. 또, 본 실시 형태에 있어서는 제1 내지 제3 실시 형태와 다르고, 극성 패턴을 기억해 두기 위한 ROM이 불필요하게 된다.

### (제6 실시 형태)

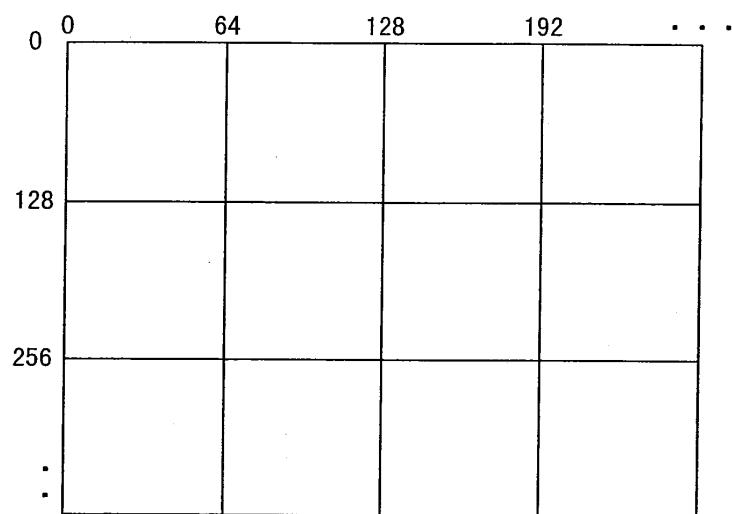

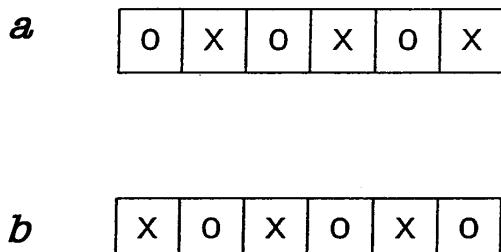

도 35는 제6 실시 형태의 개요를 나타내는 도면이다. 본 실시 형태에서는 표시 범위를 횡  $64 \times 3(R \cdot G \cdot B)$ 화소, 종 128화소의 직사각형의 블럭으로 분할하고, 1개의 블럭내에 플리커가 발생하는 패턴(이하, 플리커 패턴이라 한다)이 어느 정도 포함될지를 최소 전송 단위마다 판정하고, 1블럭내에 플리커 패턴이 일정수(본 예에서는 1블럭내의 25%) 이상 포함될 때에 극성 패턴을 바꾸는 것이다. 또한, 이하의 예에서는 수평 방향으로 나란한 R·G·B의 3개의 화소를 1개의 표시 단위로서 있고, 이 표시 단위를 꾹셀로 표기한다. 또, 상기 최소 전송 단위는 2꼭셀분(6화소분)의 데이터로 한다.

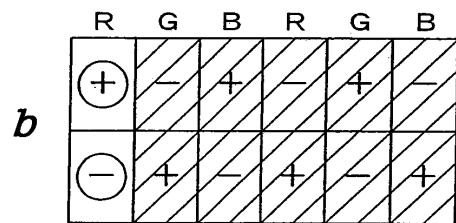

본 실시 형태에서는 초기 상태에 있어서도 36a에 나타낸 바와 같이, 종방향 및 횡방향으로 정극성과 부극성이 교대로 교대하는 극성 패턴(제1 극성 패턴이라 한다)으로 표시하고, 제1 극성 패턴에서는 플리커가 발생한다고 판정하였을 때에 도 36b에서는 나타낸 바와 같이, 횡방향으로 1화소마다, 종방향으로 2화소마다 극성이 교대되는 극성 패턴(제2 극성 패턴이라 한다)으로 변화시키는 동작을 실현하는 것이다.

### (1) 구동 회로의 구성

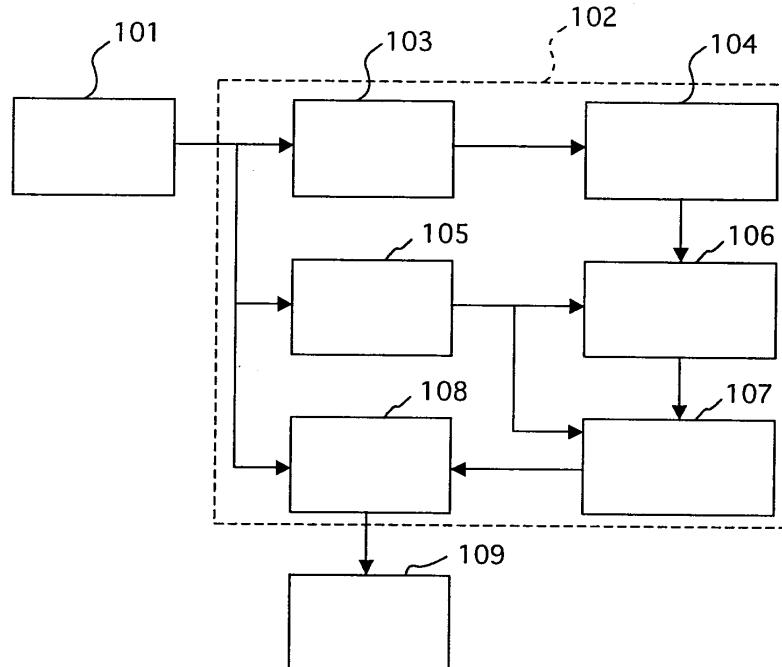

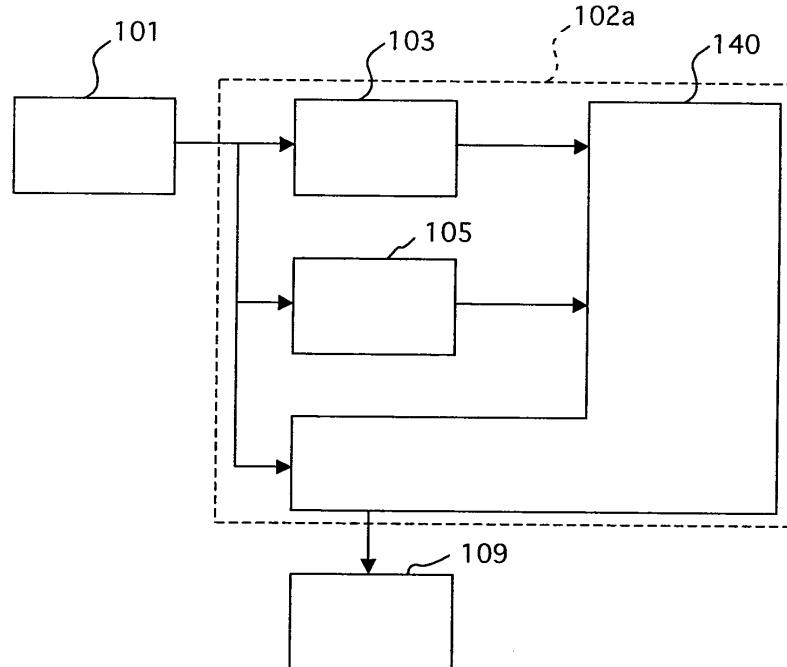

도 37은 본 발명의 제6 실시 형태의 액정 표시 패널의 구동 회로의 구성을 나타내는 블럭도이다.

본 실시 형태의 액정 표시 패널의 구동 회로는 타이밍 컨트롤러(101), 구동 모드 결정부(102), 데이터 드라이버(109), 게이트 드라이버(도시하지 않음) 및 기준 전압 발생 회로(도시하지 않음)로 구성되어 있다. 또, 구동 모드 결정부(102)는 표시 데이터 변환부(103), 플리커 판정부(104), 동작 범위 지정부(105), 플리커 정보 저장부(106), 플리커 정보량 판정부(107) 및 구동 모드 선택부(108)로 구성되어 있다. 타이밍 컨트롤러(101), 게이트 드라이버 및 기준 전압 발생 회로의 구성은 기본적으로 제1 실시 형태와 같으므로, 여기서는 설명을 생략한다. 또, 이하의 설명에서는 타이밍 컨트롤러(101)로부터 출력되는 R·G·B신호는 모두 6비트의 신호로 한다.

### (2) 구동 모드 결정부의 회로

도 38~도 43은 구동 모드 결정부(102)를 구성하는 표시 데이터 변환부(103), 플리커 판정부(104), 동작 범위 지정부(105), 플리커 정보 저장부(106), 플리커 정보량 판정부(107) 및 구동 모드 선택부(108)의 회로도이다.

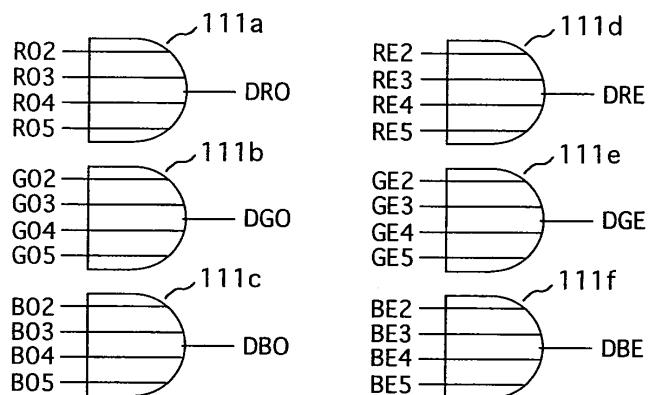

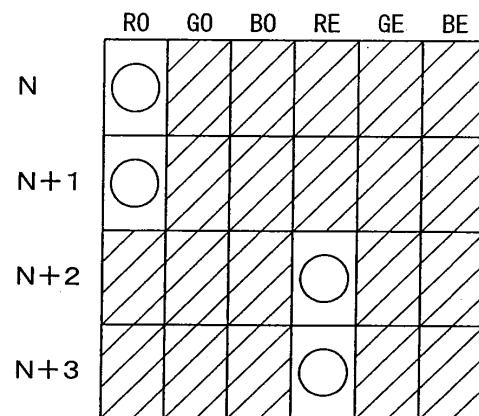

표시 데이터 변환부(103)는 도 38에 나타낸 바와 같이, 6개의 4입력 OR게이트(111a~111f)로 구성되어 있다. OR게이트(111a~111c)는 각각 홀수번째의 핀의 R·G·B신호를 입력하고, OR게이트(111d~111f)는 짝수번째의 핀의 R·G·B신호를 입력하여, 입력 신호를 2진화한 신호를 출력한다.

즉, OR게이트(111a)에는 홀수번째의 핀의 R신호의 상위 4비트(R02~R05)가 입력되고, 이들 비트(R02~R05) 중 적어도 1개의 비트가 "1"이면 출력 신호(DR0)를 "1"로 하고, 비트(R02~R05)가 모두 "0"일 때는 출력 신호(DR0)를 "0"으로 한다. 신호(DR0)가 "1"일 때는 화소가 점등되어 있는 것을 나타내고, "0"일 때는 화소가 비점등인 것을 나타내고 있다. OR게이트(111b, 111c)의 동작도 이에 준하고, 홀수번째의 핀의 G신호 또는 B신호의 상위 4비트(G02~G05, B02~B05)가 입력되고, 이들 4비트의 적어도 1개의 비트가 "1"이면 출력 신호(DG0, DB0)를 "1"로 하고, 입력된 4비트가 모두 "0"이면 출력 신호(DG0, DB0)를 "0"으로 한다.

이와 마찬가지로, OR게이트(111d, 111e, 111f)는 짝수번째의 핀의 R·G·B데이터의 상위 4비트를 각각 입력하고, 입력된 4비트(RE2~RE5, GE2~GE5, BE2~BE5) 중 적어도 1개의 비트가 "1"이면 출력 신호(DRE, DGE, DBE)를 "1"로 하고, 입력된 4비트가 모두 "0"이면 출력 신호(DRE, DGE, DBE)를 "0"으로 한다.

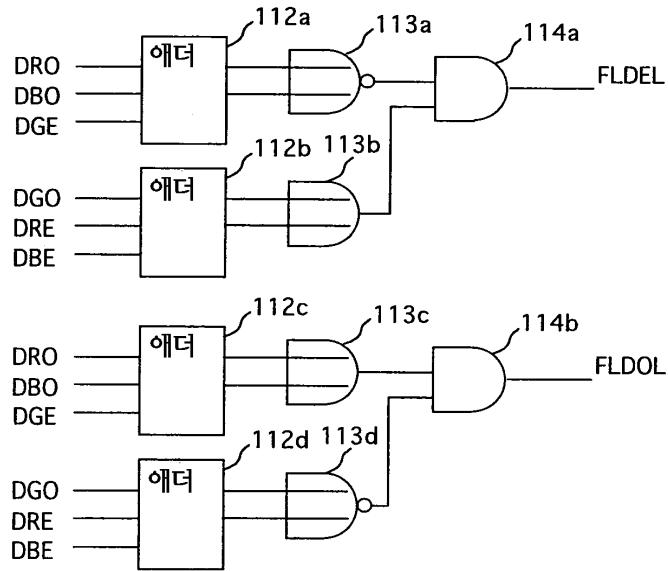

플리커 판정부(104)는 도 39에 나타낸 바와 같이, 4개의 가산기(애더)(112a~112d), 2개의 NOR게이트(113a, 113d), 2개의 OR게이트(113b, 113c), 2개의 AND게이트(114a, 114b)로 구성되어 있다. 이 플리커 판정부(104)는 수평 방향으로 인접하는 2핀(6화소)분의 데이터에 대하여, 플리커 패턴인지의 여부를 판정한다.

즉, 가산기(112a)는 표시 데이터 변환부(103)로부터 출력되는 신호(DR0, DB0, DGE)를 입력하고, 이들을 가산한 신호(2비트의 신호)를 출력한다. 또, 가산기(112b)는 표시 데이터 변환부(103)로부터 출력되는 신호(DG0, DRE, DBE)를 입력하고, 이들을 가산한 신호(2비트의 신호)를 출력한다. NOR게이트(113a)는 가산기(112a)로부터 출력되는 2비트의 신호의 적어도 한쪽의 비트가 "1"일 때 "0"을 출력하고, 모두 "0"일 때에 "1"을 출력한다. OR게이트(113b)는 가산기(112b)로부터 출력되는 2비트의 신호의 적어도 한쪽이 "1"일 때에 "1"을 출력하고, 모두 "0"일 때에는 "0"을 출력한다. AND게이트(114a)는 NOR게이트(113a) 및 OR게이트(113b)의 출력이 모두 "1"일 때에 출력 신호(FLDEL)를 "1"로 하고, 적어도 한쪽이 "0"일 때에 출력 신호(FLDEL)를 "0"으로 한다. 이 AND게이트(114a)의 출력 신호(FLDEL)가 "1"일 때는 도 44a에 나타낸 바와 같은 데이터 배열이 되고, 짝수번째의 화소에 플리커가 발생하는 짝수 플리커 패턴인 것을 나타내고 있다. 또한, 도 44에 있어서, 도면 중 X로 나타낸 화소 중 적어도 1개의 화소는 "1"이다.

가산기(112c)는 표시 데이터 변환부(103)로부터 출력되는 신호(DR0, DB0, DGE)를 입력하고, 이들을 가산한 신호(2비트의 신호)를 출력한다. 또, 가산기(112d)는 표시 데이터 변환부(103)로부터 출력되는 신호(DG0, DRE, DBE)를 입력하고, 이들을 가산한 신호(2비트의 신호)를 출력한다. OR게이트(113c)는 가산기(112c)로부터 출력되는 2비트의 신호의 적어도 한쪽이 "1"일 때에 "1"을 출력하고, 모두 "0"일 때에 "0"을 출력한다. 또, NOR게이트(113d)는 가산기(112d)로부터 출력되는 2비트의 신호의 적어도 한쪽의 비트가 "1"일 때에 "0"을 출력하고, 모두 "0"일 때에는 "1"을 출력한다. AND게이트(114b)는 OR게이트(113c) 및 NOR게이트(113d)의 출력이 모두 "1"일 때에 출력 신호(FLDOL)를 "1"로 하고, 적어도 한쪽이 "0"일 때에 출력 신호(FLDOL)를 "0"으로 한다. AND게이트(114b)의 출력 신호(FLDOL)가 "1"일 때는 도 44b에 나타낸 바와 같은 데이터 배열이 되고, 홀수번째의 화소에 플리커가 발생하는 홀수 플리커 패턴인 것을 나타내고 있다.

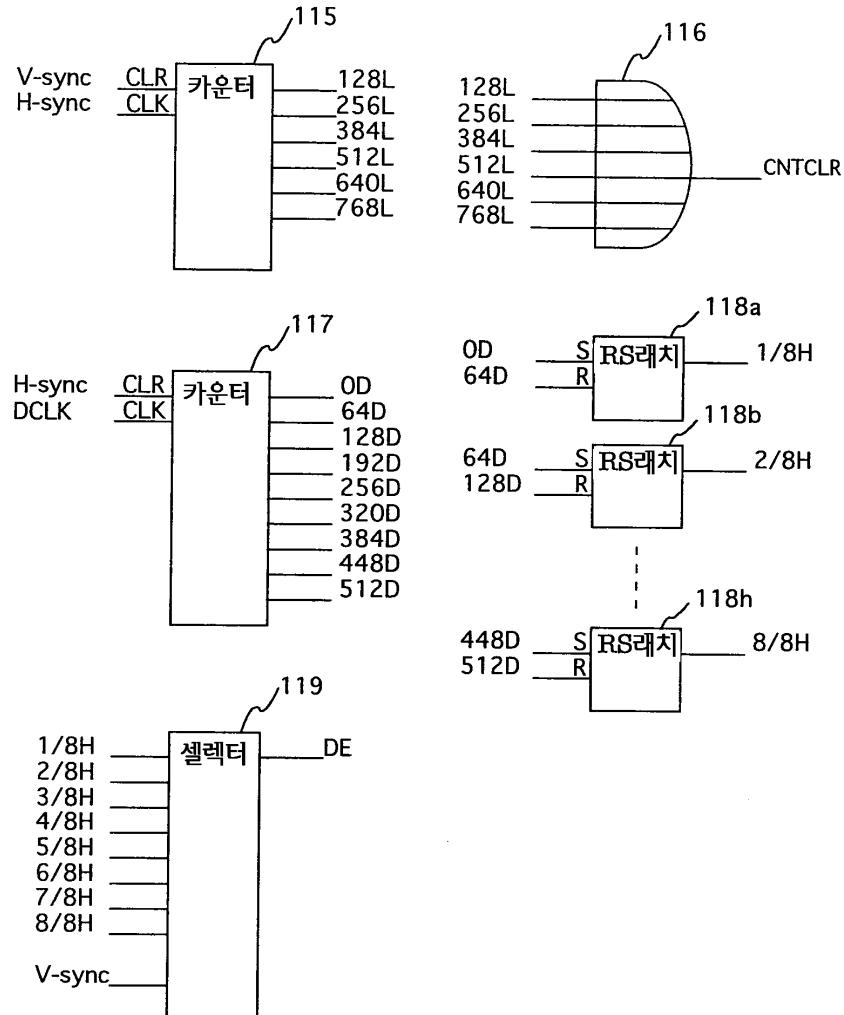

동작 범위 지정부(105)는 도 40에 나타낸 바와 같이, 카운터(115), OR게이트(116), 카운터(117), RS래치 회로(118a~118h)(단, RS래치 회로(118c~118g)의 도시는 생략하고 있다), 셀렉터(119)로 구성되어 있다. 이 동작 범위 지정부(105)는 플리커 패턴의 발생 비율을 조사하는 블럭(동작 범위라고도 한다)을 규정하는 부분이다(도 35 참조).

카운터(115)는 수평 동기 신호(H-Sync)의 펄스를 카운트하고, 수직 동기 신호(V-Sync)에 의해 클리어된다. 그리고, 카운트값이 128, 256, 384, 512, 640 또는 768이 되면, 그것에 따른 출력 신호(128L, 256L, …, 768L)중 어느 1개를 "H"로 한다. OR게이트(116)는 카운터(115)의 출력 신호(128L, 256L, …, 768L)중 어느 1개가 "H"로 되면, 출력 신호(CONTCLR)를 "H"로 한다. 이에 따라, 128라인마다 "H"로 되는 신호(CONTCLR)가 얻어진다.

또, 카운터(117)는 수평 동기 신호(H-Sync)에 의해 클리어되고, 그 후 데이터 클럭(DCLK)을 카운트한다. 그리고, 카운트값이 0일 때(카운터(117)가 클리어되었을 때), 또는 64, 128, 192, 320, 384, 448, 512번째의 데이터 클럭(DCLK)이 카운트되면, 그것에 따른 출력 신호(0D, 64D, …, 512D)가 "H"로 된다.

래치 회로(118a)는 카운터(117)의 출력 신호(OD)에 의해 세트되고, 신호(64D)에 의해 리세트된다. 래치 회로(118a)가 세트되고 있는 동안은 출력 신호(1/8H)가 "H"로 된다. 래치 회로(118b)는 카운터(117)의 출력 신호(64D)에 의해 세트되고, 신호(128D)에 의해 리세트된다. 래치 회로(118b)가 세트되어 있는 동안은 출력 신호(218H)가 "H"로 된다. 기타의 래치 회로(118c~118h)의 동작도 이에 준한다.

셀렉터(119)는 수직 동기 신호(V-Sync)가 입력될 때마다, 래치 회로(118a~118h)로부터 출력된 신호의 어느 1개를 차례로 선택하고, 동작 범위를 규정하는 신호(DE)를 출력한다. 이와 같이 하여, 셀렉터(119)로부터는 소정의 블럭이 선택되어 있는 동안만 "H"로 되는 신호(DE)가 출력된다.

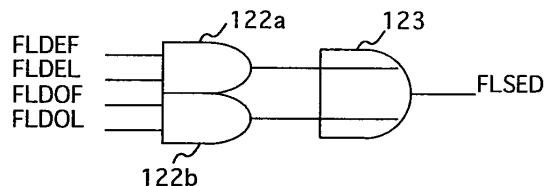

플리커 정보 저장부(106)는 도 41에 나타낸 바와 같이, AND게이트(120), 2개의 64단 시프트 레지스터(121a, 121b), AND게이트(122a, 122b), OR게이트(123)로 구성되어 있다. 이 플리커 정보 저장부(106)는 종방향으로 존재하는 플리커 패턴을 검출한다.

즉, AND게이트(120)는 데이터 클럭(DCLK)을 입력하고, 동작 범위를 규정하는 신호(DE)가 "H"인 기간만 클럭(PCLK)으로서 출력한다. 64단 시프트 레지스터(121a)는 플리커 판정부(104)로부터 출력되는 짹수 플리커 패턴 신호(FLDEL)를 클럭(PCLK)에 동기한 타이밍으로 입력하여 차례로 시프트한다. 그리고, 최종 단의 레지스터의 값이 신호(FLDEF)로서 출력된다. 또, 64단 시프트 레지스터(121b)는 플리커 판정부(104)로부터 출력되는 홀수 플리커 패턴 신호(FLDOL)를 클럭(PCLK)에 동기한 타이밍으로 입력해 차례로 시프트한다. 그리고, 최종 단의 레지스터의 값이 신호(FLDOF)로서 출력된다.

AND게이트(122a)는 짹수 플리커 패턴(FLDEF) 및 시프트 레지스터(121a)의 출력 신호(FLDEL)가 모두 "H"일 때에 "H"를 출력한다. 또, AND게이트(122b)는 홀수 플리커 패턴 신호(FLDOF) 및 시프트 레지스터(121b)의 출력 신호(FLDOF)가 모두 "H"일 때에 "H"를 출력한다. OR게이트(123)는 AND게이트(122a) 및 AND게이트(122b) 중 적어도 한쪽의 출력이 "H"일 때에 출력 신호(FLSED)를 "H"로 한다. 즉, 플리커 정보 저장부(106)는 종방향으로 나란한 화소가 플리커 패턴일 때에 출력 신호(FLSED)를 "H"로 한다.

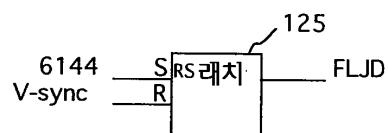

플리커 정보량 판정부(107)는 도 42에 나타낸 바와 같이, 카운터(124)와 RS래치 회로(125)로 구성되어 있다. 그리고, 동작 범위 지정부(105)에 의해 규정된 범위내에 플리커 패턴이 어느 정도의 비율로 존재하는 것인지를 판정한다.

즉, 카운터(124)는 동작 범위 지정부(105)의 OR게이트(116)의 출력 신호(CONTCLR)가 "H"로 되면 클리어되고, 플리커 정보 저장부(106)의 AND게이트(120)로부터 출력되는 클럭(PCLK)에 동기한 타이밍으로, 플리커 정보 저장부(106)의 OR게이트(123)의 출력 신호(FLSED)의 값을 도입하여 카운트수를 늘려 간다. 그리고, 카운트수가 6144이상이 되면, 카운터(124)의 출력이 "H"로 된다. 카운터(124)는 수직 방향의 동작 범위를 넘으면, 동작 범위 지정부(105)의 OR게이트(116)의 출력(CONTCLR)에 의해 클리어된다. RS래치 회로(125)는 카운터(124)의 출력에 의해 세트되고, 수직 동기 신호(V-Sync)에 의해 리세트된다. RS래치 회로(125)의 출력 신호(FLJD)가 "H"일 때는 동작 범위(64×3×128화소)에 6144개의 플리커 패턴이 있는 것을 나타낸다.

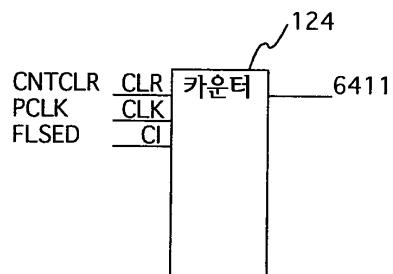

구동 모드 선택부(108)는 도 43에 나타낸 바와 같이, AND게이트(126), 카운터(127), RS래치 회로(128)로 구성된다. 이 구동 모드 선택부(108)는 플리커 정보량 판정부(107)가 일정수를 넘는 플리커 패턴을 검출하였을 때에 출력 신호(FLPT)를 "H"로 한다. 그리고, 플리커 패턴이 상기 일정수 이하의 프레임이 일정 기간에 걸쳐 계속되었을 때에, 출력 신호(FLPT)를 "L"로 되돌리는 기능을 가진다.

즉, AND게이트(126)는 플리커 정보량 판정부(105)의 래치 회로(125)의 출력(FLJD)의 반전 신호와 신호(FRM)를 입력한다. 신호(FRM)는 수직 동기 신호(V-Sync)에 동기한 신호이고, V-Sync의 펄스보다도 앞으로 또한 화상 데이터가 공백이 되는 기간에 "H"로 되는 펄스를 갖는 신호이다. AND게이트(126)는 RS래치 회로(125)의 출력 신호(FLJD)가 "L"이고, 또한 신호(FRM)가 "H"일 때에 "H"로 되는 신호(GCLK)를 출력한다.

카운터(127)는 AND게이트(126)의 출력 신호(GCLK)를 카운트하고, 카운트값이 일정한 값이 되면 출력 신호(FLRST)를 "H"로 하여 카운트값을 클리어한다. 즉, 카운터(127)는 플리커가 없는 프레임을 카운트하고 있고, 플리커가 있는 프레임이 일정한 기간(예를 들면 15~30프레임 기간) 계속되면, 출력 신호(FLRST)를 "H"로 한다.

RS래치 회로(128)는 도 42의 RS래치 회로(125)의 출력 신호(FLJD)가 "H"로 되면 세트되고, 카운터(127)의 출력 신호(FLRDT)로 리세트된다. RS래치 회로(128)의 출력 신호(FM0DE)가 "L"일 때는 제1 극성 패턴이 선택되고, "H"일 때는 제2 극성 패턴이 선택되는 것을 나타낸다.

### (3) 데이터 드라이버의 구성

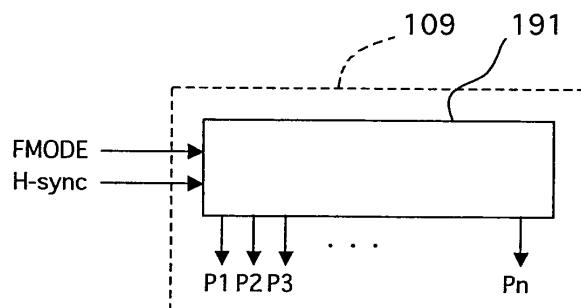

도 45는 데이터 드라이버(109)를 나타내는 블럭도이다. 단, 이 데이터 드라이버(109)가 도 9에 나타낸 데이터 드라이버와 다른 점은 시프트 레지스터 회로부(41)로 바뀌어 극성 패턴 결정부(191)를 갖는 것이고, 기타의 구성은 기본적으로 동일하므로, 중복하는 부분의 도시 및 설명을 생략한다.

극성 패턴 결정부(191)는 래치 회로(128)의 출력 신호(FM0DE)가 "L"인 기간은 1수평 동기 기간마다 극성 신호( $P_1, P_2, \dots, P_n$ )의 극성을 변화시키고, 래치 회로(128)의 출력 신호(FLPT)가 "H"인 기간은 2수평 동기 기간마다 극성 신호( $P_1, P_2, \dots, P_n$ )의 극성을 변화시킨다. 이 극성 신호( $P_1, P_2, \dots, P_n$ )에 의해서, 데이터 드라이버로부터 출력되는 데이터 신호( $O_1 \sim O_n$ )의 극성이 결정된다(도 36 참조).

### (4) 제6 실시 형태의 효과

본 실시 형태에서는 논리 회로로 형성된 회로에 의해 플리커 패턴의 유무를 검출하여, 플리커가 현저히 될 때는 극성 패턴을 제1 극성 패턴에서 제2 극성 패턴으로 자동적으로 변화시킴으로, 플리커에 의해 화면이 보기 어려워지는 것을 방지할 수 있다. 또, 본 실시 형태에서는 구동 모드 결정부(102)를 논리 회로만으로 형성하고, ROM을 사용하지 않으므로, 제조 코스트가砍감되는 이점도 있다.

### (5) 변형 예

상기 제6 실시 형태에서는 화면을 복수의 블럭으로 분할하고, 적어도 1개의 블럭에 일정수 이상의 플리커 패턴이 검출되었을 때에 극성 패턴을 변화시키는 경우에 대하여 설명했지만, 전 블럭수에 대해 플리커 패턴이 일정수(예를 들면 25%) 이상 검출된 블럭의 비율을 구하여, 그 비율이 미리 설정된 값(예를 들면, 전 블럭수의 20%)를 넘은 경우에, 극성 패턴을 변화시키도록 하여도 좋다.

또, 분할한 블럭의 경계선에서의 플리커의 발생을 검출하기 위하여, 예를 들면 1프레임마다 블럭 범위를 반만 상하 방향 또는 좌우 방향으로 시프트시켜도 좋다. 이 경우, 1프레임마다 동작 범위 지정부(105)내의 카운터(115, 117)에 오프셋값을 설정하도록 하면 좋다.

### (제7 실시 형태)

이하, 본 발명의 제7 실시 형태에 대하여 설명한다. 본 실시 형태에서는 제6 실시 형태에 비해 플리커 패턴을 더욱 상세하게 설정한다.

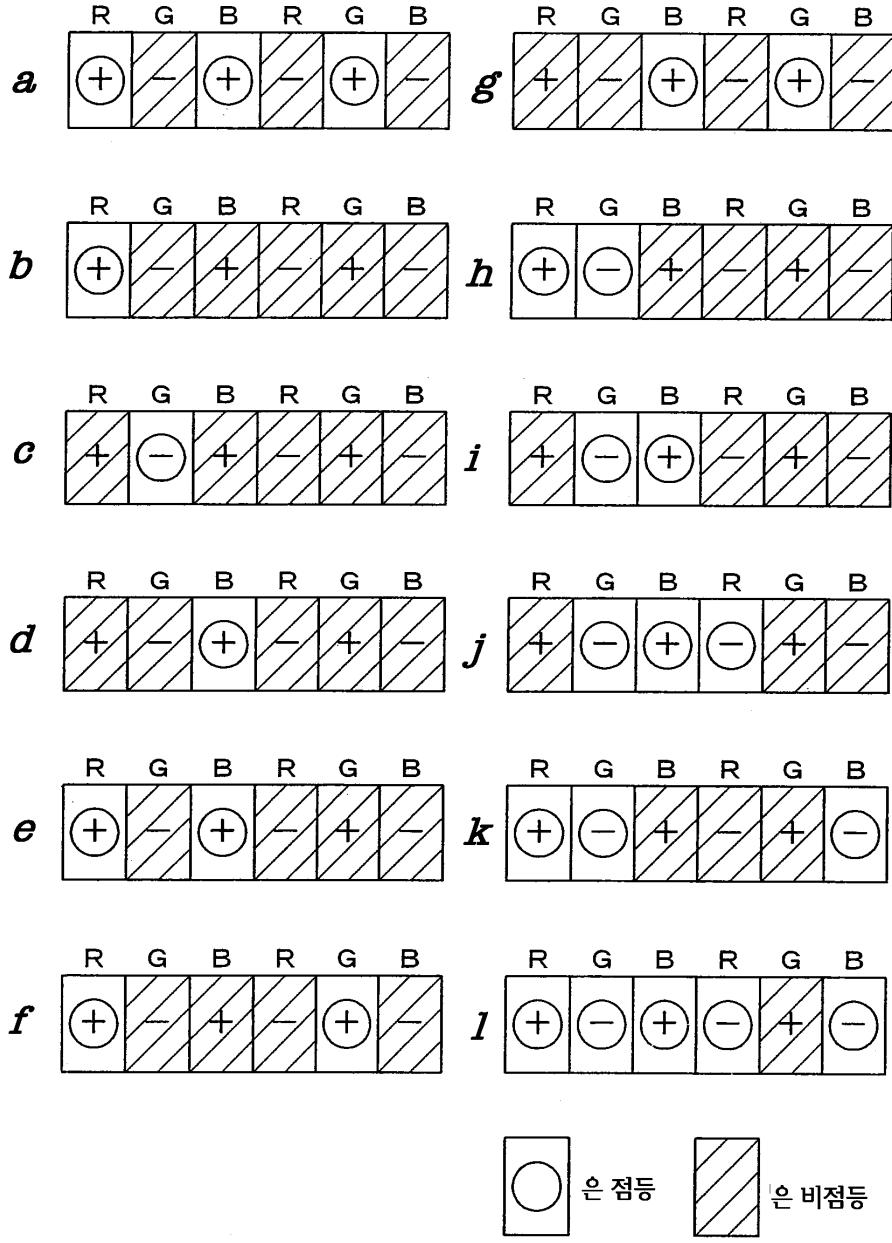

도 46~도 52는 본 실시 형태의 개요를 설명하는 도면이다. 본 실시 형태에 있어서는 도 46에 나타낸 바와 같은 패턴이 검출된 경우를 플리커 패턴으로 한다. 이하, 이들을 플리커 패턴으로 하는 이유를 설명한다.

R·G·B별로 점등 화소의 극성에 편향이 있었던 경우에 플리커가 발생한다. 이 때문에, 수평 방향으로 인접하는 2개의 픽셀의 R·G·B의 1색에 대하여, 한쪽의 화소가 점등되고, 다른 쪽의 화소가 비점등인 패턴을 세고, 일정량이면 플리커 패턴으로 한다. 도 46의 (B), (C), (D)가 이에 해당한다.

그런데, 액정 표시 패널의 화소를 투과하는 빛의 양은 투과량과 컬러 필터의 보정값의 곱에 관계한다. R·G·B의 각 컬러 필터의 보정값은 균일하지 않고, G가 70%, R이 20%, B가 10%정도이다. 따라서, 수평 방향으로 나란한 2개의 픽셀의 G화소의 한쪽만이 점등하고 다른 쪽이 비점등의 경우는 플리커가 현저하게 된다. 그런데, 본 실시 형태에 있어서는 수평 방향으로 인접하는 2개의 픽셀 중 한쪽의 픽셀의 G화소가 점등, 다른 쪽의 픽셀의 G화소가 비점등의 경우, R화소 및 B화소가 점등되어 있는지의 여부에 관계없이, 플리커 패턴으로 한다. 도 46의 (A), (F)~(L)이 이에 해당한다. 또, 본 실시 형태에서는

수평 방향으로 인접하는 2개의 핵셀의 G화소가 모두 비점등이고, 또한, 한쪽의 핵셀의 R화소 또는 B화소의 어느 쪽 또는 양쪽이 점등되고, 다른 쪽의 핵셀의 R화소 및 B화소가 비점등인 경우도 플리커 패턴으로 한다. 도 46의 (B), (D), (E)가 이에 해당한다.

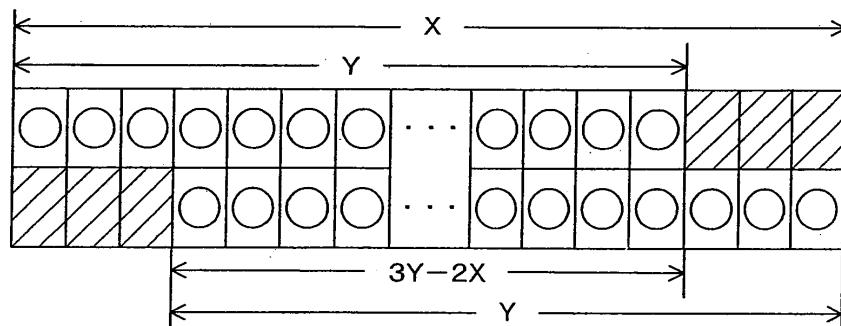

상기의 방법으로는 수평 방향만으로 플리커 패턴을 검출하기 때문에, 도 47b에 나타낸 바와 같은 세로 줄무늬 패턴 등의 플리커가 발생하지 않는 패턴도 플리커 패턴으로서 판정한다. 그런데, 수평 방향으로 나란한 화소 중 R·G·B의 어느 1색에 대하여 주목하고, 점등하고 있는 화소의 수를 홀수열의 화소와 짝수열의 화소로 나누어 카운트하는 회로를 설치하고, 카운트수가 소정의 값 이상이면 플래그를 세운다. 그리고, 홀수번째 또는 짝수번째의 화소에 대하여, N(N은 정수)행째와 N+1 행째에서 플래그를 비교하여, 한쪽의 행에만 플래그가 서 있는 경우는 도 47a와 같은 상태라고 판단한다. 또, N행째 및 N+1행째에 모두 플래그가 서 있으면, 도 47b에 나타낸 바와 같은 상태가 되어 있고, 이러한 상태가 일정 행 있으면 화면에 세로 줄무늬를 표시하고 있다고 판단한다. 도 48을 참조하여 또한 상세하게 설명한다. 도 48에 있어서, 수평 방향의 홀수번째 또는 짝수번째의 화소의 총수를 X로 하고, 그 중 점등하고 있는 화소의 수를 Y로 한다. 여기서, N행째 및 N+1행째에서는 상기 일정한 카운트수 이상 점등하고 있으면, 반드시 3Y-2Y 이상의 화소가 세로로 연속하여 점등하고 있는 것이다. 이러한 원리로 세로 줄무늬를 검출할 수 있다.

또, 상기의 원리를 응용해 도 49에 나타낸 바와 같은 종방향으로 2화소 연속하는 체크무늬(체크 패턴: 이하, 2도트 바둑판 무늬 패턴이라 한다) 등의 특수 패턴을 검출할 수 있다. 예를 들면, 있는 색의 홀수번째의 화소에 대하여, N행째, N+1행째는 점등 화소의 수가 소정의 수 이상인 것을 나타내는 플래그가 서 있고, N+2행째, N+3행째는 점등 화소의 수가 소정의 수 이하인 것을 나타내는 플래그가 서 있다고 한다. 또, 동시에, 동일 색의 짝수번째의 화소에 대하여, N행째, N+1행째는 점등 화소의 수가 소정의 수 이하인 것을 나타내는 플래그가 서 있고, N+2행째, N+3행째는 점등 화소의 수가 소정의 수 이상인 것을 나타내는 플래그가 서 있다고 한다. 이러한 패턴을 추출함으로써, 2도트 바둑판무늬 패턴을 검출할 수 있다.

또한, 플리커는 정극성일 때의 휘도와 부극성일 때의 휘도와의 차에 의해 발생하므로, 휘도가 낮은 부분에서는 플리커가 인식하기 어렵게 된다. 또, 휘도가 높은 부분에서도, 인가 전압에 대한 투과율의 변화가 작기 때문에, 플리커가 인식하기 어렵게 된다. 또한, 백 라이트의 휘도에 의해서도 플리커의 외관은 바뀌게 된다. 이 때문에, 화소의 점등 또는 비점등은 상기의 조건에 맞추어 적절히 설정하면 좋다.

도 50과 같은 패턴을 플리커 패턴으로부터 제외하기 위하여, 있는 일정한 조건에서는 비점등의 화소를 점등 화소와 판정하도록 하여도 좋다. 도 50에 나타낸 패턴의 경우, 전체적으로는 정극성과 부극성이 혼재하기 때문에 플리커는 발생하지 않지만, N+1행째의 RO화소와 N+2행째의 RO화소가 모두 비점등이기 때문에, 세로 줄무늬 또는 2도트 바둑판무늬 패턴의 검출도 행해지지 않는다. 따라서, N행째 및 N+2행째의 홀수번째 또는 짝수번째의 화소가 점등되고, 또한, N+1행째 및 N+2행째의 홀수번째 또는 짝수번째의 화소가 비점등일 때는 N+1행째 및 N+2행째의 화소도 점등하고 있다고 한다. 이에 따라, 도 50과 같은 패턴을 플리커 패턴으로부터 제외할 수 있다.

상술한 플리커 패턴의 판정 방법 및 제외 패턴의 판정 방법을 적절히 편성함으로써, 극성 패턴에 부합한 최적의 플리커 패턴 검출을 실현할 수 있다. 예를 들면, 극성 패턴이 도 36a에 나타낸 바와 같은 도트 반전 패턴의 경우, 수평 방향으로 인접하는 2개의 핵셀의 점등 화소를 조사함으로써 플리커 패턴을 추출한다. 그 후, 세로 줄무늬 패턴인지의 여부의 판정 및 세로 2도트 바둑판무늬 패턴인지의 여부를 판정하고, 세로 줄무늬 패턴 또는 세로 2도트 바둑판무늬 패턴의 경우는 플리커 패턴으로부터 제외한다. 그리고, 최종적으로 플리커 패턴을 표시하고 있다고 판정하였을 때는 극성 패턴을 예를 들면 도 36b에 나타낸 바와 같은 횡 2라인 중 1라인 반전 패턴으로 전환한다.

또, 극성 패턴이 도 51에 나타낸 바와 같은 세로선 반전 극성 패턴의 경우, 있는 색의 짝수번째의 열이 세로 줄무늬이고, 홀수번째의 열이 세로 줄무늬가 아닐 때에 플리커 패턴으로서 극성 패턴을 전환한다.

또한, 극성 패턴이 도 52에 나타낸 바와 같은 가로선 반전 극성 패턴의 경우, 수평 방향으로 나란한 화소 중 점등하고 있는 화소의 수를 카운트하고, 소정의 수 이상인 것을 나타내는 플래그 또는 소정의 수 이하인 것을 나타내는 플래그를 세우고, N라인과 N+1라인에서 비교를 행한다. 예를 들면 N라인의 점등 화소의 수가 소정의 수 이상이고, N+1라인의 비점등 화소의 수가 소정의 수 이상의 패턴이 플리커 패턴이 되기 때문에, 이러한 패턴이 일정수 이상이면 극성 패턴을 전환한다.

### (1) 제7 실시 형태의 구성

도 53은 본 실시 형태의 액정 표시 패널의 구동 회로의 구성을 나타내는 블럭도이다. 단, 도 53에 있어서, 제6 실시 형태의 도 37과 동일물에는 동일 부호를 부여하고 그 자세한 설명은 생략한다.

본 실시 형태의 액정 표시 패널의 구동 방법은 타이밍 컨트롤러(101), 구동 모드 결정부(102a), 데이터 드라이버(109)로 구성된다. 또, 구동 모드 결정부(102a)는 표시 데이터 변환부(103), 동작 범위 지정부(105), 플리커 판정/구동 모드 선택부(140)로 구성된다.

## (2) 플리커 판정/구동 모드 선택부의 회로

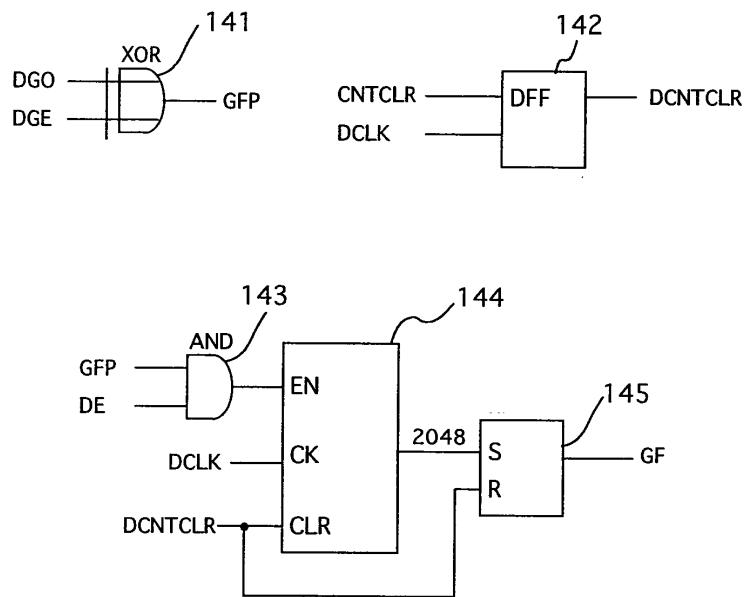

도 54~도 59는 플리커 판정/구동 모드 선택부의 회로도이다. 도 54에 나타낸 회로에 있어서, 표시 데이터 변환부(103)에서 2진화된 R·G·B신호(DR, DRE, DG0, DGE, DB0, DBE)중, 신호(DG0, DGE)는 XOR게이트(141)에 입력된다. XOR게이트(141)는 신호 DG0 또는 DGE의 어느 한쪽만이 "H"일 때에 출력 신호(GFP)를 "H"로 하고, 기타일 때는 출력 신호(GFP)를 "L"로 한다. 한편, D-플립 플롭(142)은 동작 범위 지정부(105)로부터 출력되는 신호(CNTCLR)와 데이터 클럭(DCLK)을 입력하고, 신호(CNTCLR)로부터 1클럭분 지연한 신호(DCNTCLR)를 출력한다.

AND게이트(143)는 동작 범위 지정부(105)로부터 출력되는 동작 범위를 규정하는 신호(DE)와, XOR게이트(141)로부터 출력되는 신호(GFP)가 모두 "H"일 때에 "H"로 되고, 그 이외일 때는 "L"로 되는 신호를 출력한다. 카운터(144)는 AND게이트(143)의 출력을 클럭(DCLK)에 동기한 타이밍으로 카운트한다. 그리고, 카운트값이 2048(블럭내의 G화소의 1/4)로 되면, 출력을 "H"로 한다. 또, 카운터(144)는 D-플립 플롭(142)으로부터 출력되는 신호(DCNTCLR)에 의해 클리어된다. RS래치 회로(145)는 카운터(144)의 출력에 의해 세트되고, 신호(DCNTCLR)에 의해 리세트된다.

이 도 54에 나타낸 회로는 G화소에 대하여 플리커 패턴인지의 여부를 판정하는 것이다. 즉, 수평 방향으로 나란한 2픽셀(6화소)중, 한쪽의 G화소가 점등되고, 다른 쪽의 G화소가 비점등의 경우를 플리커 패턴으로 하고 있다. 그리고, RS래치 회로(145)는 동작 범위 지정부(105)에서 규정된 동작 범위에 G화소에 의한 플리커 패턴이 2048이상 있을 때에, 출력 신호(GF)를 "H"로 한다.

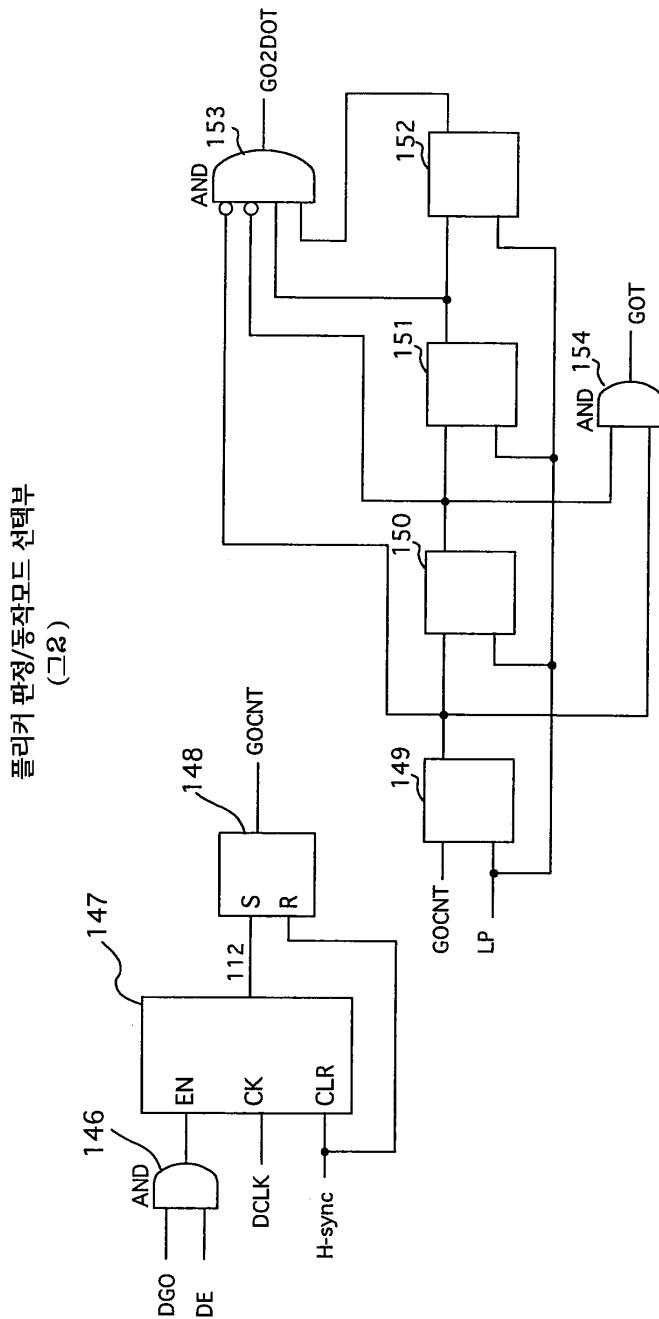

도 55에 나타낸 회로에 있어서, AND게이트(146)는 표시 데이터 변환부(103)로부터 출력되는 신호(DG0)와 동작 범위 지정부(105)로부터 출력되는 동작 범위를 규정하는 신호(DE)를 입력하고, 이들 신호가 모두 "H"일 때만 "H"를 출력한다. 카운터(147)는 AND게이트(146)의 출력을 데이터 클럭(DCLK)에 동기한 타이밍으로 카운트하고, 카운트값이 112가 되면 "H"를 출력한다. 이 카운터(147)는 수평 동기 신호(H-Sync)에 의해 클리어된다. RS래치 회로(148)는 카운터(147)의 출력이 "H"로 되면 세트되어 출력 신호(GOCNT)를 "H"로 하고, 수평 동기 신호(H-Sync)에 의해 리세트된다.

시프트 레지스터(149~152)는 초단의 시프트 레지스터(149)에 RS래치 회로(148)의 출력 신호(GOCNT)가 입력되고, 신호(LP)에 의해 데이터를 시프트한다. 또한, 신호(LP)는 수평 동기 신호(H-Sync)의 유효 데이터 범위 후에 "H"로 되는 신호이다. AND게이트(153)는 시프트 레지스터(149, 150)의 출력과, 시프트 레지스터(151, 152)의 반전 출력을 입력하고, 이들이 모두 "H"일 때에 "H"로 되는 신호(GO2DOT)를 출력한다. 또, AND게이트(154)는 시프트 레지스터(149, 150)의 출력을 입력하고, 이들이 모두 "H"일 때에 "H"로 되는 신호(GOT)를 출력한다.

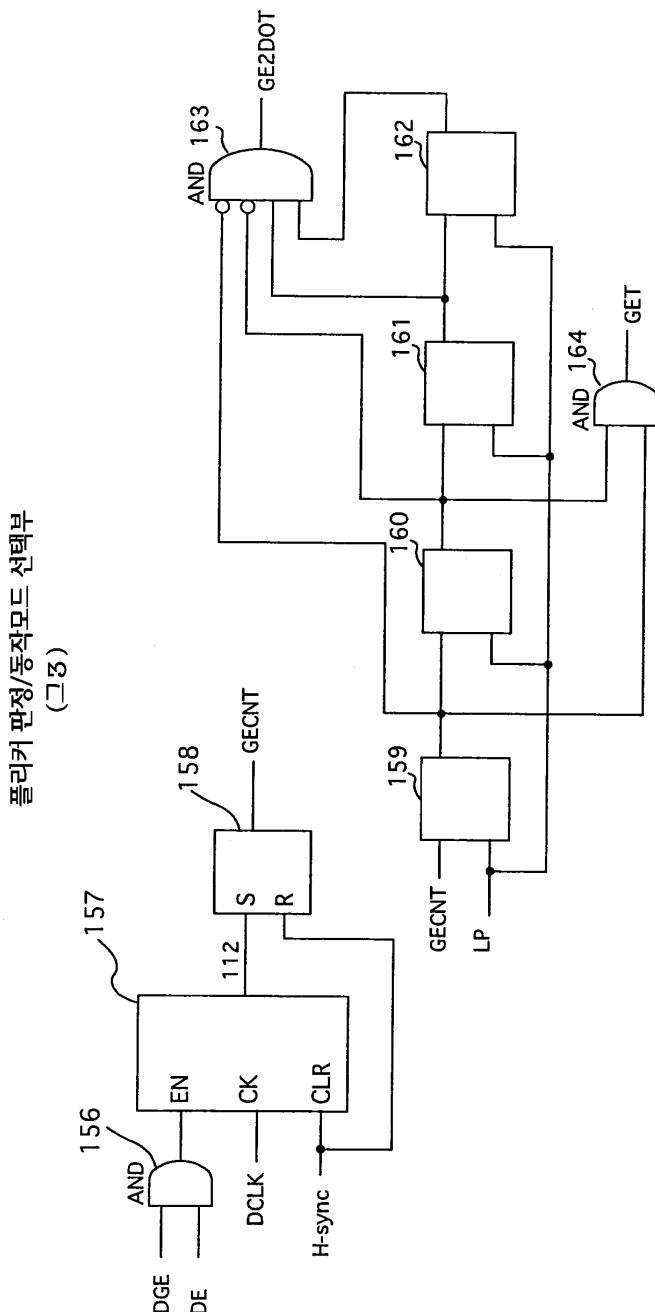

도 56에 나타낸 회로에 있어서도, 도 55의 회로와 같이, AND게이트(155)는 표시 데이터 변환부(103)로부터 출력되는 신호(DGE)와 동작 범위 지정부(105)로부터 출력되는 동작 범위를 규정하는 신호(DE)가 모두 "H"일 때에 "H"로 되는 신호를 출력한다. 카운터(157)는 AND게이트(156)의 출력을 데이터 클럭(DCLK)에 동기한 타이밍으로 카운트한다. 그리고, 카운트값이 112가 되면 출력을 "H"로 한다. 이 카운터(157)는 수평 동기 신호(H-Sync)에 의해 클리어된다. RS래치 회로(158)는 카운터(157)의 출력에 의해 세트되어 신호(GECNT)를 출력하고, 수평 동기 신호(H-Sync)에 의해 리세트된다.

시프트 레지스터(159~162)는 초단의 시프트 레지스터(159)에 RS래치 회로(158)의 출력 신호(GECNT)가 입력되고, 신호(LP)에 의해 데이터를 시프트한다. AND게이트(163)는 시프트 레지스터(159, 160)의 출력과, 시프트 레지스터(161, 162)의 반전 출력을 입력하고, 이들이 모두 "H"일 때에 "H"로 되는 신호(GE2DOT)를 출력한다. 또, AND게이트(164)는 시프트 레지스터(159, 160)의 출력을 입력하고, 이들이 모두 "H"일 때에 "H"로 되는 신호(GET)를 출력한다.

상기의 도 55, 56에 나타낸 회로는 플리커 패턴으로부터 제외하는 패턴을 검출하는 회로이다. 예를 들면, 수평 방향으로 인접하는 2개의 픽셀 중의 한쪽의 G화소가 점등되고, 다른 쪽의 G화소가 비점등의 경우, XOR게이트(141)에서는 플리커 패턴으로 판정한다. 그러나, 도 47a에 나타낸 바와 같은 경우는 플리커가 현저하게 나타나지만, 도 47b에 나타낸 바와 같이 종방향으로 점등 화소가 나란한 경우는 플리커가 현저하지 않게 된다. 그런데, 본 실시 형태에 있어서는 종방향으로 보아 홀수 및 짝수 라인별로 점등하고 있는 화소의 수를 카운터(147, 157)로 카운트하고, 카운트값이 112이상이면, RS래치 회로(148, 158)의 출력 신호(GOCNT, GECNT)를 "H"로 한다. N행째의 신호(GOCNT, GECNT)와 N+ 1행째의 카운트값을 AND게이트(154, 164)에서 비교하고, 모두 "H"일 때는 도 47b에 나타낸 바와 같이 종방향으로 점등 화소가 나란히 되

어 있다고 판단한다. 이 때, AND게이트(154, 164)의 출력 신호(GOT, GET)가 "H"로 된다. 또, AND게이트(153, 163)의 출력이 "H"일 때는 도 49에 나타낸 바와 같이, 2도트 바둑판무늬 패턴이라고 판단한다. 이 때, AND게이트(153, 163)의 출력 신호(G02DOT, GE2DOT)가 "H"로 된다.

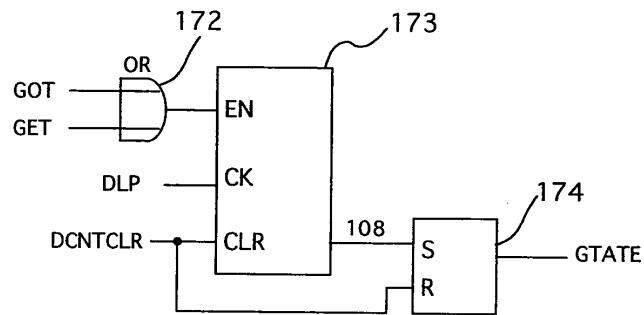

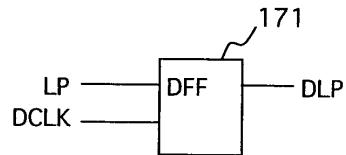

도 57에 나타낸 회로에 있어서, D-플립 플롭(171)은 신호(LP)를 1클럭분 지연한 신호(DLP)를 출력한다. OR게이트(172)는 도 55, 도 56에 나타낸 AND게이트(154, 164)로부터 출력되는 신호(GOT, GET)를 입력하고, 적어도 한쪽이 "H"일 때에 "H"로 되는 신호를 출력한다. 카운터(173)는 OR게이트(172)의 출력을, D-플립 플롭(171)의 출력 신호(DLP)에 동기화 타이밍으로 카운트한다. 그리고, 카운트값이 108이 되면 "H"로 되는 신호를 출력한다. 이 카운터(173)는 도 54에 나타낸 D-플립 플롭(142)의 출력 신호(DCNTCLR)에 의해 클리어된다. RS래치 회로(174)는 카운터(173)의 출력이 "H"로 되면 세트되고, 도 54의 D-플립 플롭(142)으로부터 출력되는 신호(DCNTCLR)가 "H"로 되면 리세트된다.

이 도 57에 나타낸 회로는 선택된 블럭내의 홀수번째의 핵셀의 선화소 또는 짝수번째의 핵셀의 선화소가 종방향으로 나란히 되어 있는 수를 카운트하고, 카운트값이 108이 되면, RS래치 회로(174)의 출력 신호(GTATE)를 "H"로 한다.

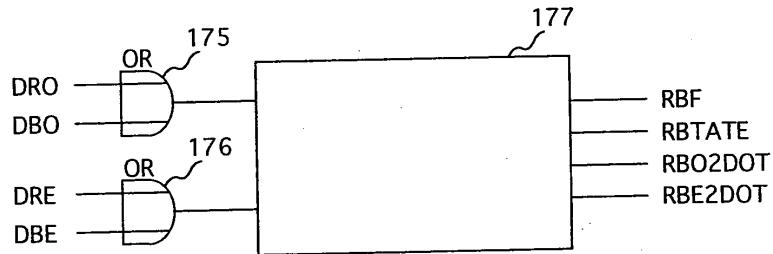

도 58에 나타낸 회로에 있어서, OR게이트(175)는 표시 데이터 변환부(103)로부터 출력되는 신호(DR0, DB0)를 입력하고, 이들 신호(DR0, DB0)의 적어도 한쪽이 "H"일 때에 "H"로 되는 신호를 출력한다. 또, OR게이트(176)는 표시 데이터 변환부(103)로부터 출력되는 신호(DRE, DBE)를 입력하고, 이들 신호(DRE, DBE)의 적어도 한쪽이 "H"일 때에 "H"로 되는 신호를 출력한다. 그리고, 도 54~도 57에 나타낸 회로와 같은 회로(177)에 의해서, 신호(RBF, RBTATE, RBO2DOT, RBE2DOT)를 생성해 출력한다. 또한, 신호(RBF)는 1블럭내에 R화소 또는 B화소의 플리커 패턴이 2048이상 존재하는지의 여부를 나타내는 신호, 신호(RBTATE)는 적(R) 또는 청(B)의 세로 줄무늬 패턴인지의 여부를 나타내는 신호, 신호(RBO2DOT)는 R화소 또는 B화소에 대하여 홀수열 중 2도트 패턴인지의 여부를 나타내는 신호, 신호(RBE2DOT)는 R화소 또는 B화소에 대하여 짝수열 중 2도트 패턴인지의 여부를 나타내는 신호이다.

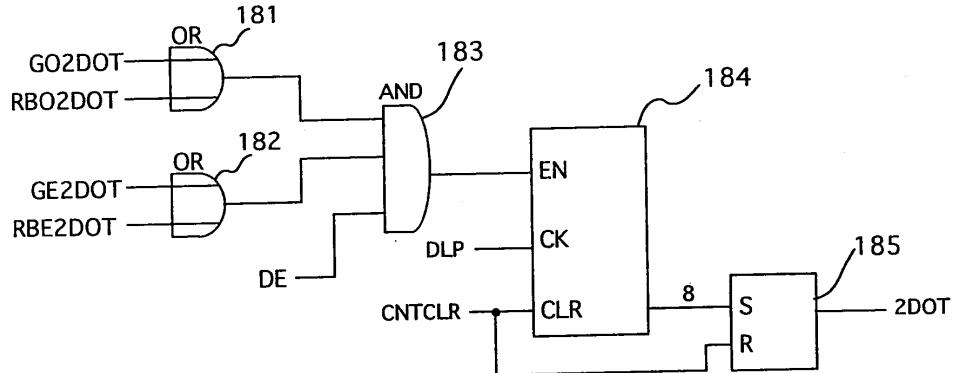

도 59에 나타낸 회로에 있어서, OR게이트(181)는 G화소의 홀수열의 세로 2도트 바둑판무늬 패턴을 나타내는 신호(GO2DOT)와 R화소 및 B화소의 홀수열의 2도트 바둑판무늬 패턴을 나타내는 신호(RBO2DOT)를 입력하고, 적어도 한쪽이 "H"일 때는 "H"를 출력한다. 또, OR회로(182)는 G화소의 짝수열의 2도트 바둑판무늬 패턴을 나타내는 신호(GE2DOT)와 R화소 및 B화소의 짝수열의 2도트 바둑판무늬 패턴을 나타내는 신호(RBE2DOT)를 입력하고, 적어도 한쪽이 "H"일 때는 "H"를 출력한다. AND게이트(183)는 AND게이트(181, 182)의 출력과, 동작 범위를 규정하는 신호(DE)를 입력하고, 이들이 모두 "H"일 때에만 "H"를 출력한다.

카운터(184)는 AND게이트(183)의 출력을 도 57에 나타낸 D-플립 플롭(171)으로부터 출력되는 신호(DLP)의 타이밍으로 카운트하고, 카운트값이 8로 되면 "H"를 출력한다. 이 카운터(184)는 동작 범위 지정부(105)로부터 출력되는 신호(CNTCLR)에 의해 클리어된다. RS래치 회로(185)는 카운터(184)의 출력에 의해 세트되고, 동작 범위 지정부(105)로부터 출력되는 신호(CNTCLR)에 의해 세트된다. 이에 따라, RS래치 회로(185)의 출력 신호(2DOT)는 세로 줄무늬 패턴을 8이상 검출하였을 때에 "H"로 된다.

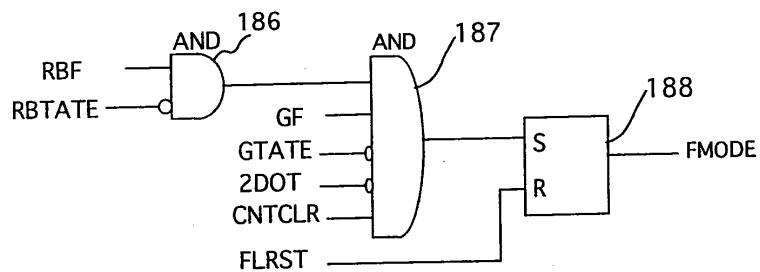

AND게이트(186)의 출력은 도 58에 나타낸 회로로부터 출력되는 신호(RBF)와 신호(RBTATE)의 반전 신호가 모두 "H"일 때만 "H"로 된다. AND게이트(187)는 AND게이트(186)의 출력 신호, 도 54에 나타낸 RS래치 회로(145)의 출력 신호(GF), 도 57에 나타낸 RS래치 회로(174)의 출력 신호(GTATE)의 반전 신호, 도 49의 RS래치 회로(185)의 출력 신호(2DOT)의 반전 신호, 동작 범위 지정부(105)로부터 출력되는 신호(CNTCLR)가 모두 "H"일 때만 "H"를 출력한다. RS래치 회로(188)는 AND게이트(187)의 출력에 의해 세트되고, 동작 모드 선택부의 카운터(127)(도 43 참조)로부터 출력되는 신호(FLRST)에 의해 세트된다. 이 RD래치 회로(188)로부터 출력되는 신호(FMODE)에 의해 제5 실시 형태와 같이 극성 패턴을 바꾼다.

### (3) 제7 실시 형태의 효과

본 실시 형태에 있어서는, 제5 실시 형태와 같은 효과가 얻어짐과 함께, 플리커 패턴이나 플리커 제외 패턴을 적절히 설정함으로써, 보다 세밀한 조정이 가능하다는 이점이 있다.

또한, 상기한 제1~제6 실시 형태에 있어서는 모두 타이밍 컨트롤러(31)는 퍼스널 컴퓨터에 접속되는 것으로 했지만, 본 발명은 이에 한정되는 것이 아니다. 타이밍 컨트롤러에 접속되는 기기로서는 TV튜너나 기타의 영상 기기가 있다.

또, 상술한 제1~제7 실시 형태는 모두 본 발명의 일례이고, 본 발명은 상술한 실시 형태의 범위에 한정되는 것이 아니다.

## 발명의 효과

이상 설명한 바와 같이, 본 발명에 의하면 극성 패턴을 ROM 등의 극성 패턴 기억부에 기억하고 있으므로, 회로 구성이 간단하여, 하드웨어를 변경하지 않고 극성 패턴을 변경할 수 있다. 이에 따라, 표시 패널의 표시 패턴에 따른 극성 패턴으로 설정할 수 있어, 예를 들면 2도트마다 극성이 반전하는 극성 패턴이나, 연속하는 3도트 중 연속하는 2도트가 같은 극성, 다른 1비트가 역의 극성이 되는 극성 패턴으로 함으로써, 플리커의 발생을 저감할 수 있다.

또, 본 발명에 의하면, 복수 종류의 극성 패턴을 극성 패턴 기억부에 기억해 두고, 상기 극성 패턴 기억부로부터 출력된 극성 패턴과 화상 신호를 비교하고, 그 결과에 따라 극성 패턴 기억부로부터 출력하는 극성 패턴을 전환하므로, 표시하는 화상에 따라 극성 패턴이 자동적으로 전환된다. 이에 따라, 플리커의 발생을 보다 확실하게 방지할 수 있다.

또한, 본 발명에 의하면, 복수의 극성 패턴을 발생 가능한 극성 패턴 발생부를 예를 들면 논리 회로로 구성하고, 선택 신호 발생부로부터 출력되는 선택 신호에 따라 어느 1개의 극성 패턴을 극성 패턴 발생부로부터 출력시킨다. 이에 따라, 하드웨어를 변경하지 않고 극성 패턴을 변경할 수 있다.

또한, 본 발명에 의하면, 표시 화면을 복수의 블럭으로 분할하고, 적어도 1개의 블럭에 포함되는 플리커 패턴의 비율을 산출하고, 그 결과에 따라 극성 패턴을 변화시키므로, 플리커의 발생을 저감할 수 있다. 이 경우, 플리커 패턴을 검출하는 회로를 논리 회로만으로 형성할 수 있어서, ROM 등의 메모리 등을 사용하는 경우에 비해 제품 코스트를 저감할 수 있다.

## 도면의 간단한 설명

도 1은 종래의 액정 표시 장치의 개략 구성을 나타내는 블럭도.

도 2는 마찬가지로 종래의 액정 표시 장치의 입력 제어부의 구성을 나타내는 블럭도.

도 3은 액정 표시 패널의 구조를 나타내는 단면도.

도 4는 마찬가지로 액정 표시 패널의 TFT기판의 평면도.

도 5는 본 발명의 제1 실시 형태의 액정 표시 패널의 구동 회로를 나타내는 블럭도.

도 6은 수직 동기 신호(V-Sync), 수평 동기 신호(H-Sync), 화상 신호(RGB), 게이트 스타트 신호(GSTR) 및 게이트 클럭(GCLK)의 타이밍을 나타내는 타이밍 차트.

도 7은 수평 동기 신호(H-Sync), 데이터 클럭(DCLK), R신호, G신호, B신호, 데이터 스타트 신호(DSTIN), 스트로브 신호(STB) 및 시프트 클럭(SCLK)의 타이밍을 나타내는 타이밍 차트.

도 8은 극성 패턴 제어부의 구성을 나타내는 블럭도.

도 9는 데이터 드라이버의 구성을 나타내는 블럭도.

도 10은 D/A변환기의 구성을 나타내는 회로도.

도 11은 마찬가지로 그 D/A변환기의 디코더의 입력과 출력과의 관계를 나타내는 도면.

도 12는 화소 전극에 인가하는 전압과 빛의 투과율과의 관계를 나타내는 도면.

도 13a~d는 어느 것이나 극성 패턴의 예를 나타내는 모식도.

도 14는 극성 패턴의 다른 예를 나타내는 모식도.

도 15a는 도 14의 극성 패턴을 사용하였을 때에 플리커가 현저해지는 표시 패턴을 나타내는 모식도, 도 15b는 마찬가지로 그 표시 패턴으로 표시되는 색을 나타내는 도면.

도 16은 본 발명의 제2 실시 형태의 액정 표시 장치의 개략 구성을 나타내는 블럭도.

도 17은 마찬가지로 그 액정 표시 장치의 입력 제어부의 구성을 나타내는 블럭도.

도 18은 마찬가지로 그 액정 표시 장치의 타이밍 제어 회로의 구성을 나타내는 블럭도.

도 19는 반전 주기 제어 동작을 나타내는 플로차트.

도 20은 화소의 동작 상태와 극성 반전 주기와의 관계를 나타내는 도면.

도 21은 제2 실시 형태에 적용되는 입력 데이터 추출부의 일 실시예.

도 22는 제2 실시 형태에 적용되는 입력 데이터 추출부의 다른 실시예.

도 23은 제2 실시 형태에 적용되는 표시 패턴 판정부의 일 실시예.

도 24는 제3 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부의 구성을 나타내는 블럭도.

도 25a는 극성 패턴의 예를 나타내는 도면, 도 25b는 시프트 클럭 및 극성 패턴 신호의 타이밍을 나타내는 타이밍 차트.

도 26은 제4 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부의 구성을 나타내는 블럭도.

도 27은 제4 실시 형태의 액정 표시 패널의 구동 회로의 데이터 드라이버의 구성을 나타내는 블럭도.

도 28은 기입신호(LOAD), 시프트 클럭(SCLK) 및 극성 패턴 신호(POL1)의 타이밍을 나타내는 타이밍 차트를 나타내는 도면.

도 29는 반전 신호(POL2)와 극성 패턴과의 관계를 나타내는 도면.

도 30은 액정 표시 패널의 각 화소 전극의 극성을 나타내는 도면.

도 31은 제5 실시 형태의 액정 표시 패널의 구동 회로의 극성 패턴 제어부의 구성을 나타내는 블럭도.

도 32는 제5 실시 형태의 액정 표시 패널의 데이터 드라이버의 구성을 나타내는 블럭도.

도 33은 데이터 드라이버내의 논리 회로의 입력과 출력과의 관계를 나타내는 도면.

도 34a는 선택 신호(SEL)가 "0"일 때의 극성 패턴을 나타내는 도면, 34b는 선택 신호(SEL)가 "1"일 때의 극성 패턴을 나타내는 도면.

도 35는 제6 실시 형태의 개요를 나타내는 도면.

도 36a는 제6 실시 형태의 제1 극성 패턴을 나타내는 도면, 도 36b는 제2 극성 패턴을 나타내는 도면.

도 37은 본 발명의 제6 실시 형태의 액정 표시 패널의 구동 회로의 구성을 나타내는 블럭도.

도 38은 제6 실시 형태의 구동 회로의 표시 데이터 변환부의 회로도.

도 39는 제6 실시 형태의 구동 회로의 플리커 판정부의 회로도.

도 40은 제6 실시 형태의 구동 회로의 동작 범위 지정부의 회로도.

도 41은 제6 실시 형태의 구동 회로의 플리커 정보 저장부의 회로도.

도 42는 제6 실시 형태의 구동 회로의 플리커 정보량 판정부의 회로도.

도 43은 제6 실시 형태의 구동 회로의 동작 모드 선택부의 회로도.

도 44a, 44b는 어느 것이나 플리커 패턴의 예를 나타내는 모식도.

도 45는 제6 실시 형태의 데이터 드라이버의 구성을 나타내는 도면.

도 46a~46l은 제7 실시 형태의 플리커 패턴의 예를 나타내는 모식도.

도 47a는 플리커 패턴의 예를 나타내는 모식도, 도 47b는 플리커 패턴에서 제외하는 패턴의 예를 나타내는 모식도.

도 48은 세로 줄무늬 패턴의 판정 방법을 설명하는 도면.

도 49는 2도트 바둑판무늬 패턴을 나타내는 도면.

도 50은 특수 패턴의 예를 나타내는 도면.

도 51은 세로선 반전 극성 패턴을 나타내는 도면.

도 52는 가로선 반전 극성 패턴을 나타내는 도면.

도 53은 제7 실시 형태의 액정 표시 패널 구동 회로를 나타내는 블럭도.

도 54는 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 1).

도 55는 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 2).

도 56은 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 3).

도 57은 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 4).

도 58은 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 5).

도 59는 제7 실시 형태의 플리커 판정/동작 모드 선택부의 회로도(그 6).

### 부호의 설명

10 TFT기판 11,21 글래스 기판

12,503a 게이트 버스 라인 13,502a 데이터 버스 라인

14 화소 전극 15 TFT

20 대향 기판 22 컬러 필터

24 대향 전극 31,101 타이밍 컨트롤러

32,60,70,80 극성 패턴 제어부 32a,61,71 제어 회로

32b,62,72 ROM 33,79,109,502 데이터 드라이버

34,503 게이트 드라이버 35 기준 전압 발생 회로

37 퍼스널 컴퓨터 40,501 액정 표시 패널

41,42,77 시프트 레지스터 회로부 43 데이터 레지스터 회로부

44 래치 회로부 45 레벨 시프트 회로부

46 D/A변환 회로부 47 볼터지팔로우어부

79,86 배타적 논리화 회로부 102,102a 동작 모드 결정부

103 표시 데이터 변환부 104 플리커 판정부

105 동작 범위 지정부 106 플리커 정보 저장부

107 플리커 정보 판정부 108 구동 모드 선택부

140 플리커 판정/구동 모드 선택부 555 입력 제어부

506 기준 전원

### 도면

도면1

도면2

도면3

액정표시 패널의 단면

## 도면4

액정표시 패널

## 도면5

액정표시장치의 구성

## 도면6

도면7

도면8

극성 패턴 제어부(32)의 구성

## 도면9

도면10

## D/A 변환기(46a)의 구성

## 도면11

## 디코더(51)의 입출력

| 디코더입력   | 디코더 출력                          | D/A변환기 출력 |

|---------|---------------------------------|-----------|

| 0 1 1 1 | 1 0 0 0                         | + V7      |

| 0 1 1 0 | 0 1 0 0                         | + V6      |

| 0 1 0 1 | 0 0 1 0                         | + V5      |

| 0 1 0 0 | 0 0 0 1                         | + V4      |

| 0 0 1 1 | 0 0 0 0 1                       | + V3      |

| 0 0 1 0 | 0 0 0 0 0 1                     | + V2      |

| 0 0 0 1 | 0 0 0 0 0 0 1                   | + V1      |

| 0 0 0 0 | 0 0 0 0 0 0 0 1                 | + V0      |

| 1 0 0 0 | 0 0 0 0 0 0 0 0 1               | - V0      |

| 1 0 0 1 | 0 0 0 0 0 0 0 0 0 1             | - V1      |

| 1 0 1 0 | 0 0 0 0 0 0 0 0 0 0 1           | - V2      |

| 1 0 1 1 | 0 0 0 0 0 0 0 0 0 0 0 1         | - V3      |

| 1 1 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 1       | - V4      |

| 1 1 0 1 | 0 0 0 0 0 0 0 0 0 0 0 0 0 1     | - V5      |

| 1 1 1 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1   | - V6      |

| 1 1 1 1 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 | - V7      |

## 도면12

## 전압-트과율 특성

## 도면13

극성 패턴의 예 (1)

**a 표시화소**

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | + | + | + | + | + | + | + | + | + | + | + |

**b 표시화소**

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | + | + | + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - | - | - | - |

**c 표시화소**

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | - | + | - | + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - | + | - | + | - |

**d 표시화소**

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | - | + | - | + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + | - | + | - | + |

## 도면14

극성 패턴의 예(2)

표시화소

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | + | - | - | + | + | - | - | + | + | - | - |

| R | G | B | R | G | B | R | G | B | R | G | B |

| - | - | + | + | - | - | + | + | - | - | + | + |

홀수 프레임의 경우

표시화소

|   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R | G | B | R | G | B | R | G | B | R | G | B |

| - | - | + | + | - | - | + | + | - | - | + | + |

| R | G | B | R | G | B | R | G | B | R | G | B |

| + | + | - | - | + | + | - | - | + | + | - | - |

짝수 프레임의 경우

## 도면15

표시패턴

**b**

| 암황색 | 암물색 | 암청  | 암적  |

|-----|-----|-----|-----|

| 암청  | 암적  | 암황색 | 암물색 |

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

## 도면24

극성패턴 제어부 (제3실시형태)

도면25

극성 패턴의 예 (3)

a

| 출력 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 010 | 011 | 012 | 013 | 014 | 015 | 016 |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| 극성 | +  | +  | -  | +  | -  | -  | -  | +  | -  | +   | -   | -   | -   | +   | -   | +   |

극성 패턴 신호 (POL)

b

도면26

## 극성 패턴 제어부 (제4실시형태)

도면27

## 데이터 드라이버 (제4실시형태)

도면28

## 타이밍 차트 (3)

도면29

## 극성 패턴의 예

| 출력 |      | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 010 | 011 | 012 |

|----|------|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| 극성 | POL2 | 0  | +  | +  | -  | +  | -  | -  | +  | +  | -   | +   | -   |

|    | I    | -  | -  | +  | -  | +  | +  | -  | -  | +  | -   | +   | +   |

도면30

## 화소에 인가되는 전압

| I4   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|------|---|---|---|---|---|---|---|---|---|---|---|---|--|

| 표시화소 | R | G | B | R | G | B | R | G | B | R | G | B |  |

|      | + | + | - | + | - | - | + | + | - | + | - | - |  |

|      | R | G | B | R | G | B | R | G | B | R | G | B |  |

| 표시화소 | - | - | + | - | + | + | - | - | + | - | + | + |  |

도면31

## 극성 패턴 제어부의 구성

## 도면32

데이터 드라이버의 구성 (제5실시형태)

85: 논리회로

86: 배타적 논리회로

## 도면33

논리회로의 입력과 출력

| A | B | C | Q |

|---|---|---|---|

| 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 |

| A | B | C | Q |

|---|---|---|---|

| 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 |

도면34

**a**SEL=0 일때의 극성반전

|      |   |   |   |   |   |   |   |   |   |   |   |   |

|------|---|---|---|---|---|---|---|---|---|---|---|---|

| 표시화소 | R | G | B | R | G | B | R | G | B | R | G | B |

| +    | - | + | - | - | + | - | + | - | + | - | + | - |

| R    | G | B | R | G | B | R | G | B | R | G | B |   |

| -    | + | - | + | - | + | - | + | - | + | - | + | - |

**b**SEL=1 일때의 극성반전

|      |   |   |   |   |   |   |   |   |   |   |   |   |

|------|---|---|---|---|---|---|---|---|---|---|---|---|

| 표시화소 | R | G | B | R | G | B | R | G | B | R | G | B |

| +    | + | - | - | + | + | + | - | - | + | + | - | - |

| R    | G | B | R | G | B | R | G | B | R | G | B |   |

| -    | - | + | + | - | - | + | + | - | - | + | + | - |

도면35

## 화면의 블럭 분할

## 도면36

**a**

제1극성패턴

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

**b**

제2극성패턴

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

도면37

액정표시패널 구동회로 (제6실시형태)

도면38

표시 데이터 변환부

도면39

## 플리커 판정부

도면40

## 동작 범위 지정부

도면41

## 플리커 정보 저장부

도면42

## 플리커 정보량 판정부

## 도면43

## 동작 모드 선택부

## 도면44

## 플리커 패턴 판정

## 도면45

## 데이터 드라이버 (제6실시형태)

## 도면46

플리커 패턴 (제7실시형태)

도면47

## 플리커 패턴 및 제외 패턴의 예

도면48

## 세로 줄무늬 패턴 판정

도면49

## 2도트 바둑판 무늬 패턴

도면50

## 특수 패턴의 예

|     | R0  | G0 | B0 | RE | GE | BE |

|-----|-----|----|----|----|----|----|

| N   | (+) | -  | +  | -  | +  | -  |

| N+1 | -   | +  | -  | +  | -  | +  |

| N+2 | +   | -  | +  | -  | +  | -  |

| N+3 | (-) | +  | -  | +  | -  | +  |

도면51

## 세로선 반전 극성 패턴

|     |   |   |   |   |   |   |

|-----|---|---|---|---|---|---|

| N   | + | - | + | - | + | - |

| N+1 | + | - | + | - | + | - |

| N+2 | + | - | + | - | + | - |

| N+3 | + | - | + | - | + | - |

도면52

## 가로선 반전 극성 패턴

|     |   |   |   |   |   |   |

|-----|---|---|---|---|---|---|

| N   | + | + | + | + | + | + |

| N+1 | - | - | - | - | - | - |

| N+2 | + | + | + | + | + | + |

| N+3 | - | - | - | - | - | - |

도면53

액정표시 패널 구동회로 (제7실시형태)

도면54

플리커 판정/동작모드 선택부

(그 1)

도면55

도면56

도면57

플리커 판정/동작모드 선택부

(그 4)

도면58

플리커 판정/동작모드 선택부

(그 5)

도면59

플리커 판정/동작모드 선택부

(그 6)

|                |                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种显示面板的驱动电路和液晶显示器                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR100653754B1</a>                                                                                                                                                                                                                                                  | 公开(公告)日 | 2006-12-06 |

| 申请号            | KR1020060068388                                                                                                                                                                                                                                                                | 申请日     | 2006-07-21 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | HIRAKI KATSUYOSHI<br>히라끼가쓰요시<br>ITO TAKAE<br>이또다까에<br>SUZUKI TOSHIAKI<br>스즈끼도시아끼<br>HAYASHIMOTO SEIJI<br>하야시모도세이지<br>MIYAHARA MASAKI<br>미야하라마사끼<br>MINEMURA TOSHIMITSU<br>미네무라도시미쓰<br>KATAGAWA KOICHI<br>가타가와고이찌<br>SEKIDO SATOSHI<br>세끼도사또시<br>FURUKOSHI YASUTAKE<br>후루꼬시야스따께 |         |            |

| 发明人            | 히라끼가쓰요시<br>이또다까에<br>스즈끼도시아끼<br>하야시모도세이지<br>미야하라마사끼<br>미네무라도시미쓰<br>가타가와고이찌<br>세끼도사또시<br>후루꼬시야스따께                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G09F9/35 G09G3/18 G09G5/00                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G09G2320/0247 G09G2360/16 G09G3/3688 G09G2310/027 G09G3/2011 G09G2310/0289 G09G3/3614 G09G3/3648                                                                                                                                                                               |         |            |

| 代理人(译)         | MOON , KI桑                                                                                                                                                                                                                                                                     |         |            |

| 优先权            | 1998304923 1998-10-27 JP<br>1998355875 1998-12-15 JP<br>1999217333 1999-07-30 JP                                                                                                                                                                                               |         |            |

| 其他公开文献         | KR1020060088873A                                                                                                                                                                                                                                                               |         |            |