(19)

(12)(KR)

(A)(51) 。 Int. Cl. <sup>7</sup>

G02F 1/133(11)

(43)2002 - 0080243

2002 10 23(21) 10 - 2002 - 0015731

(22) 2002 03 22

(30) JP - P - 2001 - 00096101 2001 03 29 (JP)

(71) 가 가

가 가 가 가 가 4 1 - 1(72) 가 가 가 가 4 - 1 - 1

가 가 가 가 4 - 1 - 1

가

가 가 가 가 4 - 1 - 1

가

가 가 가 가 4 - 1 - 1

가

가 가 가 가 4 - 1 - 1

가

가

(74)

:

(54)

,

(12)가

,

가

3

1

2

3 (12)

4

5

6

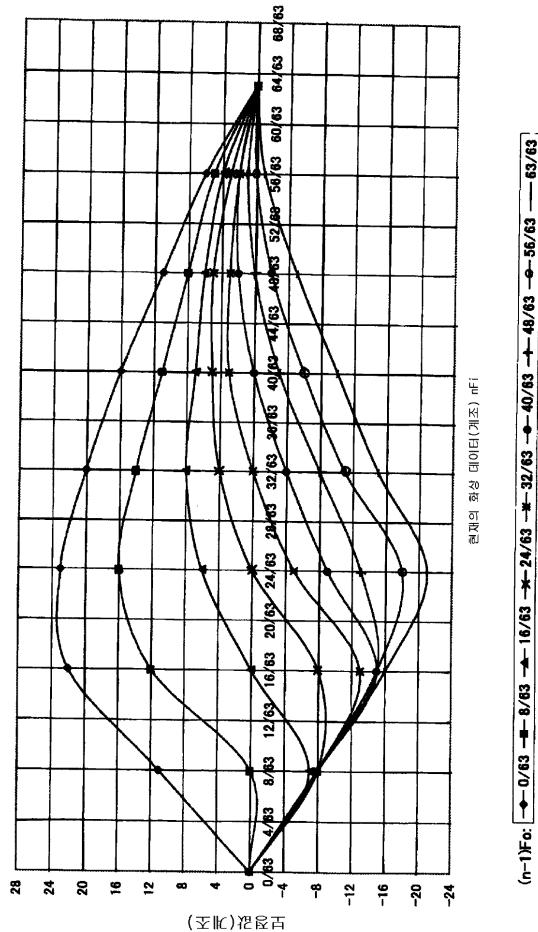

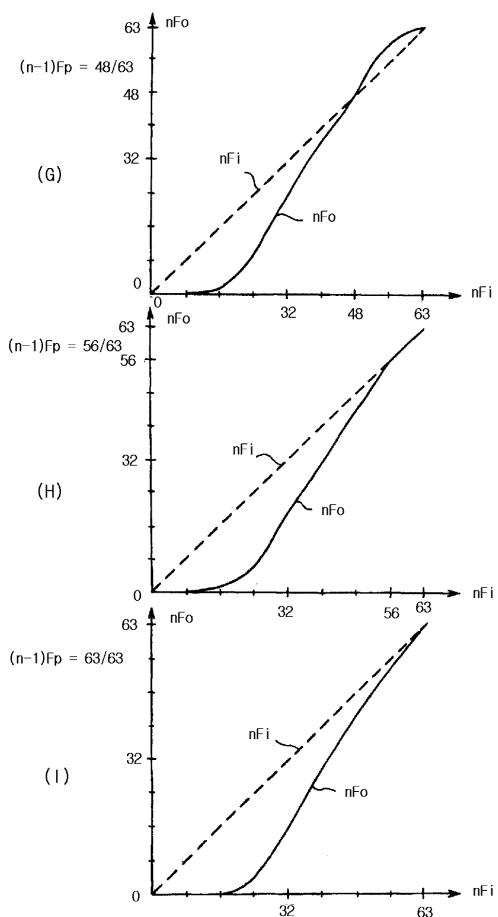

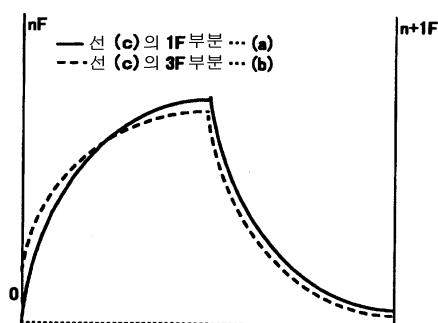

7 6 (現) nFi 가 nFo

8 6 nFi 가 nFo

9 6 nFi 가 nFo

10 (30)

11 (30)

12 CR

13

14 (擬似)

15

16

\*

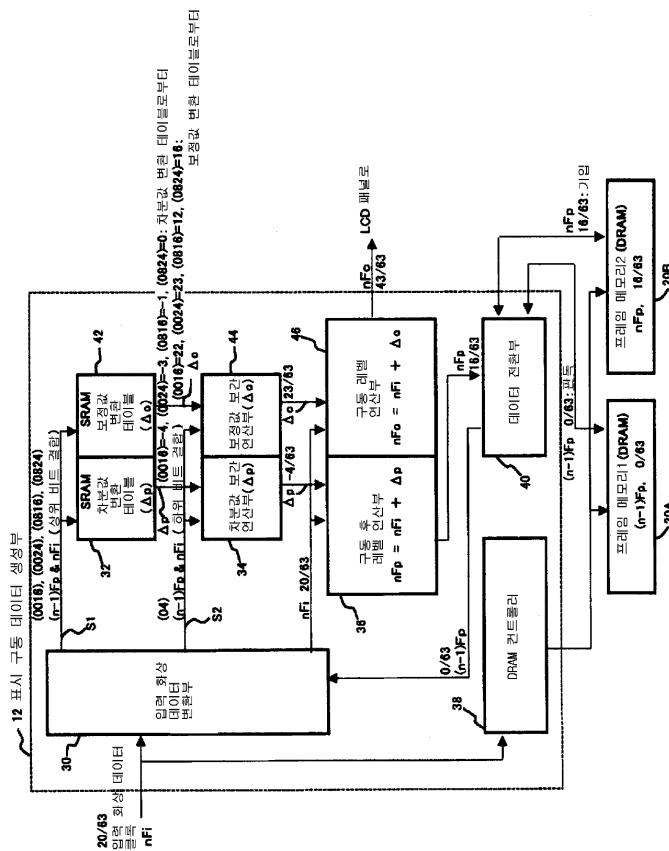

10 :

12 :

20 :

42 : 1 ,

44 : 2 (補間) ,

32 : 2 ,

34 : 1

가

가

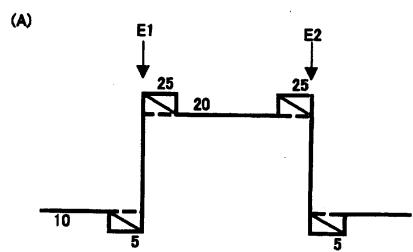

, 16ms 1 가 , 1 가 . 1

, 1 가 . , (zero) 25%

, 가 , 1

· ,

25%

， 1 가 ， (前)

,

50% ,

50%

, 1

, 가

, 가 ,

, 가 가 SRAM

, 가

, 1 , ,

, 가

, 가

가

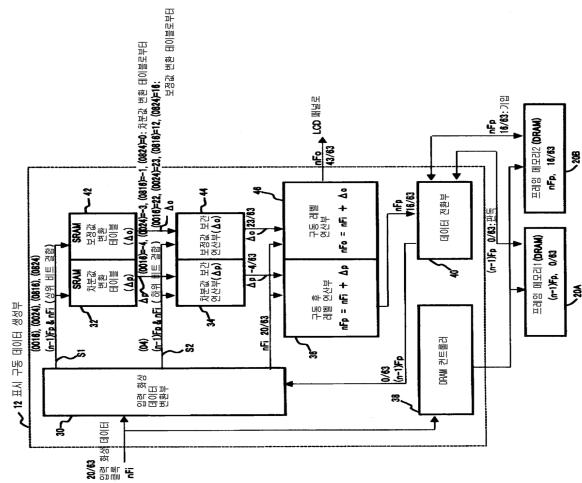

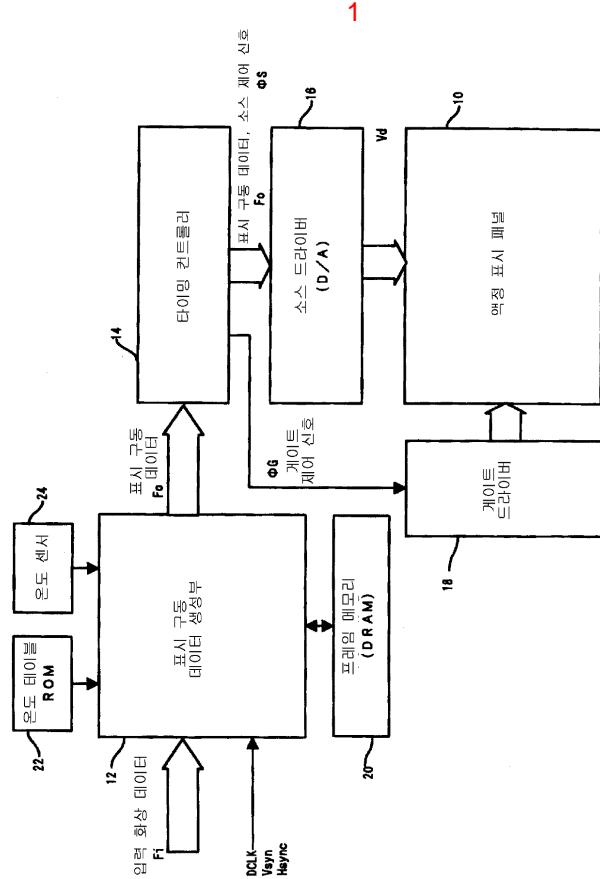

[ 1 ]

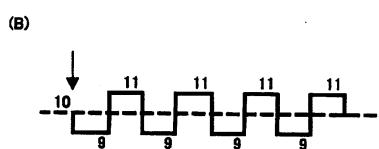

1 , . , TFT (10)

Vd (18) , (16) , Fi 가

DCLK , (12) 가 Fi

, Fo (14) , Fo , 1

Fo 가 (16) , 가

, (16) , 가 , Fo

, Vd ,

, (12) 가 (20)

ROM(22) , (24) ,

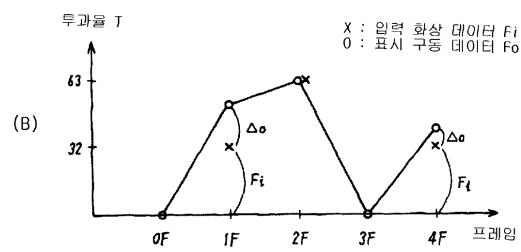

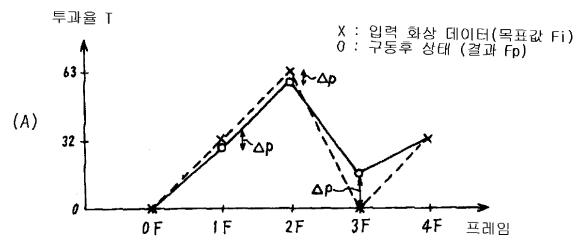

2 T(64 ) , , x 2a ,

, 2b , , Fi(64 ) ,

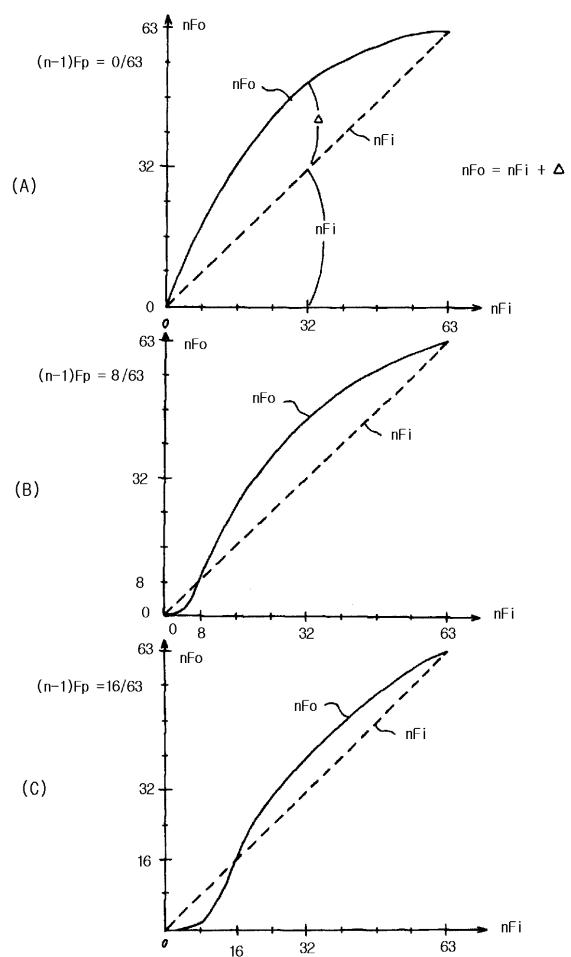

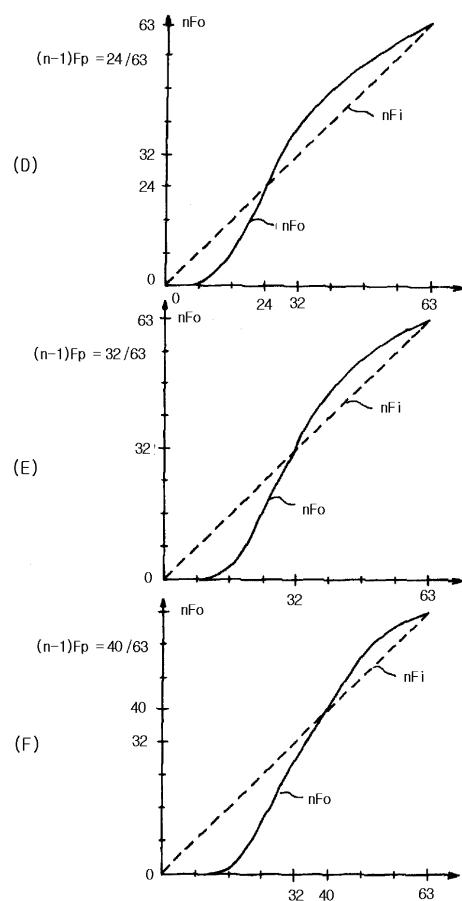

2 , , Fi =0, 0F =0, 1F =32, 2F

=63, 3F Fi =0, 4F =32 , 1F =0

Fi o 가 , o 가 , o 가

T=32 , 1F 가 , 가 ,

Fi =32 , 1F , 1F , 1F

2F , , Fi=63 2a , , 1F , , Fo

, 「63」 , , p , T , , T 2F

, , 3F , , Fi=0 =0 3F

Fo , , 가 , , , p

, , 4F , , Fi=32 1F , , Fo

Fi , , o , , , 4F 1F , , T=16 ( T=32

T=0) , , T=32 , , o

가 , , 4F , , o

Fi , , Fi , , Fi 가 , , o 가

Fi , , Fi , , Fi , , Fi

$$\begin{array}{ccccccccc}

& (44, 34) & & o & & p & & nFi & \text{가} \\

(46), & & (36) & . & & (46) & & & \\

& nFo & , & & & , & & & (36) \\

20B) & . & & nFp & , & (n+1) & , & (40) & ( \\

& , & & nFp & , & (n+1) & , & (n+1) & \\

& & (30) & & & & & &

\end{array}$$

(20B) nFp

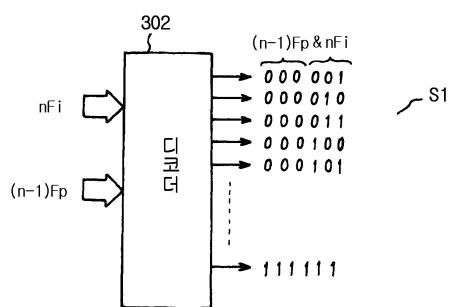

(32, 42) S1 , (34, 44)

S2 , , (34, 44) nFi

$$nF_i \text{ 가 } 20/63 \quad , \quad (n-1)F \quad \text{가} \quad T=0/63 \quad (12) \quad 1F$$

, 1 (20A) 6 (n - 1)Fp=0/63

, 6 nFi=20/63 DRAM (38) 1 (20A)

(n - 1)Fp=0/63 , (40)

(30) , nFi

(n - 1)Fp (32, 42) S1

, nFi=20/63 (n - 1)Fp=0/63 , , 4

가 , nFi=20/63 (n - 1)Fp=0/63 , (30) ,

S1 , , (n - 1)Fp & nFi=(00,16), (00,24), (08,16), (08,24)

64 , 3 (8 )

$$0 \quad p\gamma \quad . \quad , \quad S1 \quad (42) \quad (32)$$

$$o: (00,16)=22, (00,24)=23, (08,16)=12, (08,24)=16$$

$$p: (00,16) = -4, (00,24) = -3, (08,16) = -1, (08,24) = 0$$

, (44, 34) , 4 . , nFi=20/63 (n-1)Fp=0/63 (30) , nFi=20/63 (n-1)Fp=0/63 S2 , (n-1)Fp& nFi=(0,4) . , (44) ,

$$o = [(22 \times (8 - 4) + 23 \times 4/8) \times (8 - 0) + (12 \times (8 - 4) + 16 \times 4/8) \times 0] \div 8 = 22.5 \quad 23$$

$$p = [ [ (-4) \times (8 - 4) + (-3) \times 4/8 ] \times (8 - 0) + [ (-1) \times (8 - 4) + 0 \times 4/8 ] \times 0 ] \div 8 = -3.5 \quad -4$$

$$nFo = 43/63 \quad . \quad , \quad nFi = 20/63 \quad 가 \quad , \quad nFo = 20/63 \quad 가 \quad , \quad (14) \quad , \quad (16) \quad , \quad (20B) \quad , \quad (36) \quad , \quad p = -4/63 \quad , \quad (n-1)Fp = 16/63 \quad . \quad , \quad nFo = 23/63 \quad , \quad (46) \quad , \quad nFi = 20/63 \quad 가 \quad ,$$

$$, \quad , \quad (44) \quad , \quad (42)$$

, (42) 가 ,

0 . , 4 가

. , SRAM ,

(42) ( ) 가 )

. (46) (42)

, SRAM

$$\begin{array}{lll} \text{가} & . & \text{가} \\ . & , & . \\ (32) & , & (34) \\ , & , & . \\ nFp & , & (32) \\ & , & (36) \end{array}$$

The diagram illustrates the connection between three main components: SRAM, ASIC, and SDRAM. The SRAM module is connected to both the ASIC and SDRAM modules. The ASIC module is also connected to the SDRAM module.

$$302) \text{가} \quad , \quad (302) \quad , \quad nF_i \quad . \quad (n-1)F_p \quad (42)$$

$$11 \quad (30) \quad nF_i \quad 6 \quad (n-1)F_p \quad 8 \quad (256 \quad ) \quad , \quad (304) \text{가} \quad 6 \\ S1 - 0 \quad S1 - 255 \quad 0 \quad p \quad , \quad 256 \\ (306) \quad . \quad , \quad \text{가} \quad , \quad \text{가}$$

[ 2 ]

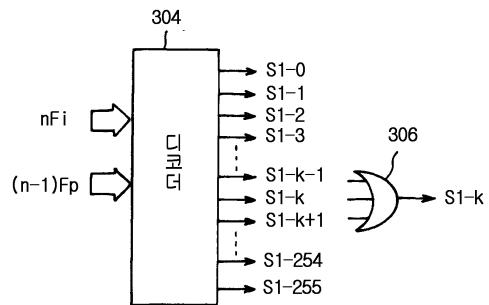

set), , , , , CR 가 , . CR(Charge and Re(zero)

, 가 50%, CR 가 . 16ms . 8ms 가 .

2 , CR 가 20ms (中速) , C

R . ,

, CR , 1 가

, 12c, , ( )

), . , 1F , 가 「3」 「4」

. , ( C1). ,

가 ( C2), 3F

( C4) , 4F , 가 「3」 ,

5).

. , ( C

2 , CR , 3 (12)

(12) , CR , (42), (44), (46)

1 . 2 , (32) 가 가 가

가 . , (34) Fp .

$$, \quad 2 \quad , \quad (36) \quad , \quad (34) \\ ( \quad ) 가 \quad (20A, 20B) \quad ,$$

12 , CR , 「 3 」

, 1F 3F 가 , . 13 .

6 1E 3E . 12

$$14 \quad . \quad 14a \quad 4 \quad 3 \\ 6 \quad 13 \quad , \quad 6 \quad 13 \quad (b) \\ . \quad , \quad 2$$

15 . . . . . 15a , 15b

15c . . . . , 16

. 15 16

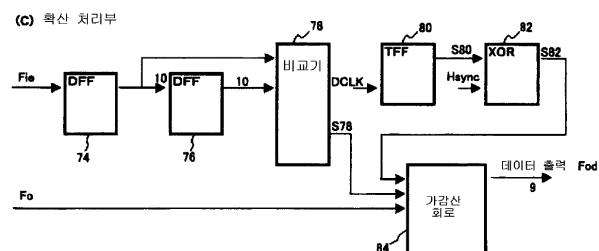

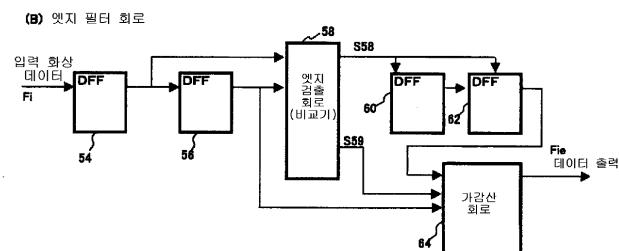

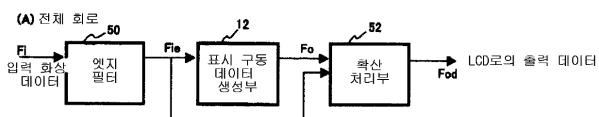

(50) (12) , Fi

, , (52) (12)

, , Fo Fi

, , Fo ㅏ .

$$(-2) \quad 1 \quad , \quad ,$$

$$(-5) \quad 3 \quad , \quad 1 \quad ,$$

( - 6) 1 3 , , 1 / 2

,

,

,

( - 7) 1 3 ,

( 8)

가 ,

가 CR(Charge and Reset)

1

가 ,

1

( 9)

가 CR

가 ,

1

2

가 , 1

, 2

가

( 10)

8 9 , ,

가

( 11)

8 9 , ,

가

가

( 12)

8 9 , , 1 ,

,

( 13)

8 9 , , 1 / 2

,

( 14)

8 9 , ,

,

( 15)

1, 3, 8 9 , ,

,

(57)

1.

1

2.

1 가 ,

2

2

1 가

3.

2

1

4.

가

가 CR (Charge and Reset)

1 가 ,

1

5.

가 ,

가 CR ,

1 ,

2 가

1

2 가

6.

7.

8.

1, 2, 4                    5                    ,

2

4

|         | $nF_1$ | $0/63$ | $8/63$ | $16/63$ | $24/63$ | $32/63$ | $40/63$ | $48/63$ | $56/63$ | $63/63$ |

|---------|--------|--------|--------|---------|---------|---------|---------|---------|---------|---------|

| $0/63$  | -      | 0      | -4     | -3      | -1      | 0       | 0       | -7      |         |         |

| $8/63$  | 0      | -      | -1     | 0       | 0       | 0       | 0       | -3      |         |         |

| $16/63$ | 0      | 0      | -      | 0       | 0       | 0       | 0       | -2      |         |         |

| $24/63$ | 2      | 0      | 0      | -       | 0       | 0       | 0       | -1      |         |         |

| $32/63$ | 4      | 0      | 0      | 0       | -       | 0       | 0       | -1      |         |         |

| $40/63$ | 8      | 0      | 0      | 0       | 0       | -       | 0       | 0       |         |         |

| $48/63$ | 11     | 4      | 0      | 0       | 0       | 0       | -       | 0       |         |         |

| $56/63$ | 14     | 6      | 0      | 0       | 0       | 0       | -       | 0       |         |         |

| $63/63$ | 16     | 8      | 0      | 0       | 0       | 0       | 0       | -       |         |         |

|         |        |        |        |         |         |         |         |         |         |         |

보정값 변환 테이블(표시 구동 테이터  $nF_1$  < 입력 회상 테이터  $nF_1$  + 보정값  $\Delta n$ )

5

|         | $nF_1$ | $0/63$ | $8/63$ | $16/63$ | $24/63$ | $32/63$ | $40/63$ | $48/63$ | $56/63$ | $63/63$ |

|---------|--------|--------|--------|---------|---------|---------|---------|---------|---------|---------|

| $0/63$  | -      | 0      | -4     | -3      | -1      | 0       | 0       | -7      |         |         |

| $8/63$  | 0      | -      | -1     | 0       | 0       | 0       | 0       | -3      |         |         |

| $16/63$ | 0      | 0      | -      | 0       | 0       | 0       | 0       | -2      |         |         |

| $24/63$ | 2      | 0      | 0      | -       | 0       | 0       | 0       | -1      |         |         |

| $32/63$ | 4      | 0      | 0      | 0       | -       | 0       | 0       | -1      |         |         |

| $40/63$ | 8      | 0      | 0      | 0       | 0       | -       | 0       | 0       |         |         |

| $48/63$ | 11     | 4      | 0      | 0       | 0       | 0       | -       | 0       |         |         |

| $56/63$ | 14     | 6      | 0      | 0       | 0       | 0       | -       | 0       |         |         |

| $63/63$ | 16     | 8      | 0      | 0       | 0       | 0       | 0       | -       |         |         |

|         |        |        |        |         |         |         |         |         |         |         |

차분값 변환 테이블(구동 후 테이터  $nF_1$  < 입력 회상 테이터  $nF_1$  + 차분값  $\Delta n$ )

7

9

10

11

12

13

14

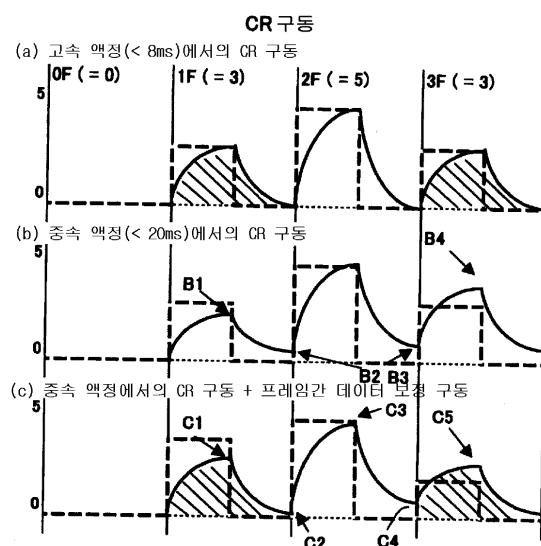

## 화소 처리

(A) 미처리

|   |   |   |

|---|---|---|

| a | a | a |

| a | a | a |

| b | b | b |

| b | b | b |

(B) 확산 처리

|   |   |   |

|---|---|---|

| a | b | a |

| b | a | b |

| a | b | a |

| b | a | b |

15

16

|                |                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种液晶显示装置的控制电路，其执行高速驱动补偿                                                                                                                              |         |            |

| 公开(公告)号        | KR1020020080243A                                                                                                                                     | 公开(公告)日 | 2002-10-23 |

| 申请号            | KR1020020015731                                                                                                                                      | 申请日     | 2002-03-22 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                                                                                               |         |            |

| [标]发明人         | SUZUKI TOSHIAKI<br>스즈키도시아키<br>YONEMURA KOSYU<br>요네무라고슈<br>HIRAKI KATSUYOSHI<br>히라키가쓰요시<br>YAMAZAKI HIROSHI<br>야마자키히로시<br>TANAKA KATSUNORI<br>다나카가쓰노리 |         |            |

| 发明人            | 스즈키도시아키<br>요네무라고슈<br>히라키가쓰요시<br>야마자키히로시<br>다나카가쓰노리                                                                                                   |         |            |

| IPC分类号         | G09G3/36 G09G5/00 G09G3/20 G02F1/133                                                                                                                 |         |            |

| CPC分类号         | G09G2340/16 G09G2320/0252 G09G2320/041 G09G3/3611 G09G2320/0285                                                                                      |         |            |

| 代理人(译)         | MOON , KI桑                                                                                                                                           |         |            |

| 优先权            | 2001096101 2001-03-29 JP                                                                                                                             |         |            |

| 其他公开文献         | KR100707774B1                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                            |         |            |

### 摘要(译)

本发明的目的是通过简化的控制电路改善液晶显示装置的响应特性并改善运动图像显示中的图像质量。在液晶显示装置的控制电路中，显示驱动数据生成部分(12)具有转换表，用于根据当前帧的图像数据和前一帧驱动之后的状态数据参考当前帧的显示驱动数据。该转换表存储显示驱动数据或对应于当前帧图像数据的高位和前一帧图像数据的高位的组合的校正值。因此，高速存储电路的容量可以做小。由于随着转换表的容量变小，显示驱动数据的精度或其校正值降低，因此提供了内插电路，产生用于显示的驱动数据或由酸改善精度的校正值，并相应地校正输入图像数据以获得显示驱动数据。3指针方面液晶显示器，控制电路，内插电路，转换表，高速存储电路