# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl. *G02F 1/1368* (2006.01)

(11) 공개번호

10-2006-0080616

(43) 공개일자

2006년07월10일

(21) 출원번호10-2005-0000891(22) 출원일자2005년01월05일

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 우에모토쯔토모

서울특별시 강남구 대치3동 974 대치현대아파트 101-1001

(74) 대리인 정상빈

김동진

심사청구: 없음

#### (54) 박막 트랜지스터 액정 표시 장치의 제조 방법

#### 요약

연속 측면 고화 방법에 의하여 형성된 결정질 실리콘막을 패턴 식각하여 활성층을 형성하는 박막 트랜지스터 액정 표시 장치의 제조 방법을 제공한다. 박막 트랜지스터 액정 표시 장치의 제조 방법은 기판 상에 비정질 실리콘막을 구비하는 단계, 비정질 실리콘막을 결정립이 생기도록 결정화하여 결정질 실리콘막을 형성하는 단계, 결정질 실리콘막 형성 단계에서 발생한 돌출 패턴이 박막 트랜지스터 별로 동일하게 할당되도록 박막 트랜지스터 배치 정보에 근거하여 돌출 패턴을 정렬하는 단계 및 결정질 실리콘막을 식각하여 활성층을 형성하는 단계를 포함하는 박막 트랜지스터 액정 표시 장치의 제조 방법을 포함한다.

#### 대표도

도 8

#### 색인어

SLS, 결정립 경계, 얼라인 패턴

#### 명세서

#### 도면의 간단한 설명

도 1은 본 발명의 일 실시예에 따라 제조된 박막 트랜지스터 액정 표시 장치의 개념도이다.

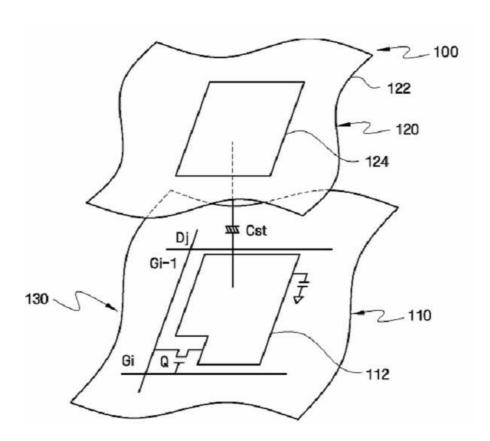

도 2는 도 1에 도시된 박막 트랜지스터 액정 표시 장치의 한 화소에 대한 등가 회로도이다.

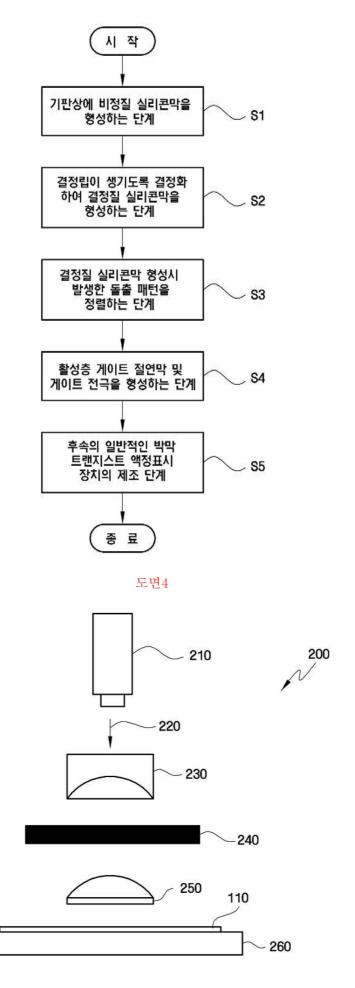

도 3은 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 제조 공정 흐름도이다.

도 4는 연속 측면 고화 방법에 이용되는 장치를 도시한 것이다.

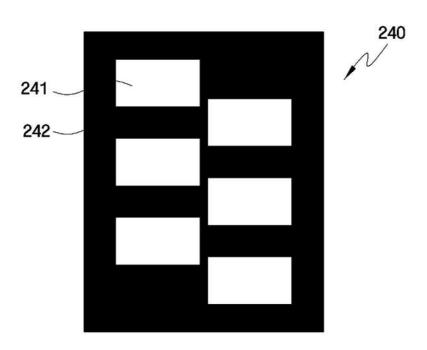

도 5는 도 4의 측면 고화 방법에 이용되는 장치에 포함되는 마스크를 도시한 것이다.

도 6a 내지 도 6d는 도 4의 장치를 이용하여 SLS 방법에 의해 비정질 실리콘막을 결정화하는 과정을 도시한 것이다.

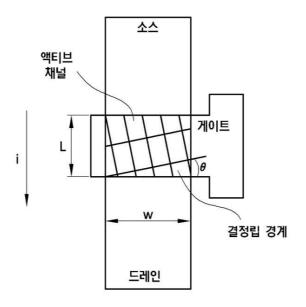

도 7a는 동일한 결정립 크기 및 액티브 채널 차원(L $\times$ W)에 대하여 제 1 차 결정립 경계의 수가 2인 TFT의 개략적인 단면을 도시한 것이고, 도 7b는 제 1 차 결정립 경계의 수가 3인 TFT의 개략적인 단면을 도시한 도면이다.

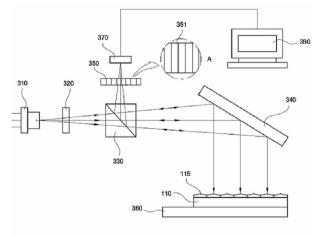

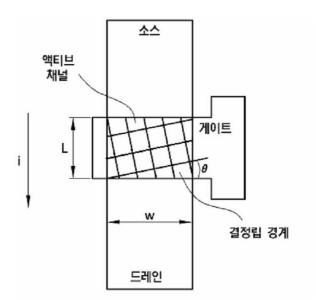

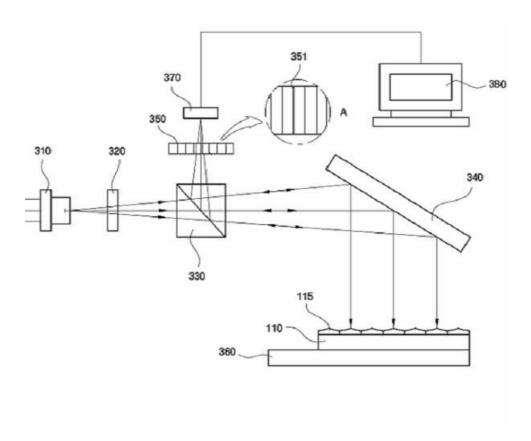

도 8은 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 제조에 사용되는 간섭계를 도시한 것이다.

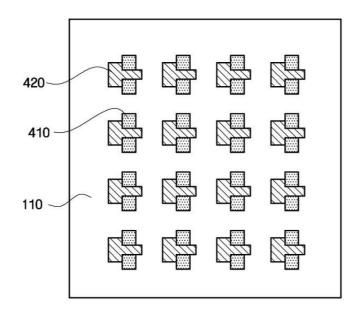

도 9는 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 박막 트랜지스터에 대해 도시한 것이다.

<도면의 주요부분에 대한 부호의 설명>

100: 액정 표시 기판 110: 상부 기판

112: 화소 전극 113: 비정질 실리콘막

114: 계면 115: 돌출 패턴

120: 하부 기판 122: 기준 전극

124: 컬러 필터 130: 액정층

140: 게이트 구동부 150: 데이터 구동부

160: 신호 제어부 170: 구동 전압 생성부

180: 계조 전압 생성부 200: SLS 장치

210: 레이저빔 발생 장치 220: 레이저빔

230: 집속 렌즈 240: 마스크

250: 축소 렌즈 260: 스테이지

241: 투과 영역 242: 차단 영역

300: 간섭계 310: 광원

320: 그레이팅 330: 빔스프리터

340: 반사 미러 350: 얼라인 패턴

360: 스테이지 370: 광 수득 수단

380: 광 처리 수단 410: 활성층

420: 게이트 전극

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막 트랜지스터 액정 표시 장치의 제조 방법에 관한 것으로, 보다 상세하게는 연속 측면 고화(Sequential Lateral Solidification; SLS) 방법에 의하여 형성된 결정질 실리콘막을 패턴 식각하여 활성층을 형성하는 박막 트랜지스터 액정 표시 장치의 제조 방법에 관한 것이다.

일반적으로 실리콘은 결정 상태에 따라 비정질 실리콘(amorphous silicon)과 결정질 실리콘(crystalline silicon)으로 나눌 수 있다.

비정질 실리콘은 낮은 온도에서 증착하여 박막(thin film)을 형성하는 것이 가능하여, 주로 낮은 용융점을 가지는 유리를 기판으로 사용하는 액정 패널(liquid crystal panel)의 스위칭 소자에 많이 사용한다. 그러나, 비정질 실리콘막은 낮은 전계 효과 이동도 등의 문제점으로 액정 표시 장치의 대면적화에 어려움이 있다.

그래서, 높은 전계 효과 이동도(30㎡/VS)와 고주파 동작 특성 및 낮은 누설 전류(leakage current)의 전기적 특성을 가진 다결정 실리콘(poly crystalline silicon)의 응용이 요구되고 있다.

특히, 다결정 실리콘막의 전기적 특성은 결정립의 크기에 큰 영향을 받는다. 즉, 결정립의 크기가 증가함에 따라 전계 효과 이동도도 함께 증가한다.

따라서, 이러한 점을 고려하여 실리콘의 결정립을 크게 하기 위한 방법이 큰 이슈로 떠오르고 있다. 최근 들어 에너지원을 레이저로 하여 실리콘 결정의 측면 성장을 유도하여 거대한 결정립의 실리콘을 제조하는 연속 측면 고화 (Sequential Lateral Solidification; SLS) 방법이 제안되었다.

이러한 SLS 방법은 실리콘 결정립이 액상 실리콘과 고상 실리콘의 경계면에서 그 경계면에 대하여 수직 방향으로 성장한다는 사실을 이용한 것이다. 즉, 레이저 에너지의 크기와 레이저빔(laser beam)의 조사 범위의 이동을 적절하게 조절하여실리콘 결정립을 소정의 길이만큼 측면 성장시킴으로서 비정질 실리콘막을 결정화시키는 것이다. 이러한 실리콘 결정립의유한한 크기로 인하여 실리콘 결정립 사이에는 경계가 발생한다.

박막 트랜지스터의 제작 시에 활성층의 온전류가 이동하는 방향이 SLS 방법에 의하여 성장된 실리콘 결정립 방향에 대하여 평행한 경우 전하 캐리어 방향에 대한 실리콘 결정립계의 배리어(barrier) 효과가 최소가 되므로 단결정 실리콘에 버금 가는 박막 트랜지스터의 특성을 얻을 수 있다고 알려져 있다. 그러나, 활성층의 온전류가 이동하는 방향과 실리콘 결정립의 성장 방향이 90°인 경우에는 박막 트랜지스터의 특성이 전하 캐리어의 트랩(trap)으로 작용하는 실리콘 결정립 경계가 많이 존재하게 되어, 박막 트랜지스터의 특성이 크게 저하된다.

또한, 활성층의 온전류가 이동하는 방향과 실리콘 결정립 성장 방향이 평행한 경우에도 유한한 실리콘 결정립 크기로 인하여 활성층 내에 1차 결정립 경계(primary grain boundary)의 수와 위치에 따라 달라지게 되며, 이로 인해 박막 트랜지스터간의 예측할 수 없는 불균일성이 발생할 수 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명이 이루고자 하는 기술적 과제는 SLS 방법에 의해 형성된 다결정 실리콘막을 사용하여 박막 트랜지스터의 활성충을 형성하는 경우에 있어서, 기판 전체에 걸쳐 형성되는 박막 트랜지스터의 물리적 특정을 균일하게 할 수 있도록 한 박막트랜지스터 액정 표시 장치의 제조 방법을 제공하고자 한다.

본 발명이 이루고자 하는 기술적 과제들은 이상에서 언급한 기술적 과제로 제한되지 않으며, 언급되지 않은 또 다른 기술 적 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 발명의 구성 및 작용

상기 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 제조 방법은 기판 상에 비정질 실리콘막을 구비하는 단계, 상기 비정질 실리콘막을 결정립이 생기도록 결정화하여 결정질 실리콘막을 형성하는

단계, 상기 결정질 실리콘막 형성 단계에서 발생한 돌출 패턴이 박막 트랜지스터 별로 동일하게 할당되도록 상기 박막 트랜지스터 배치 정보에 근거하여 상기 돌출 패턴을 정렬하는 단계 및 상기 결정질 실리콘막을 식각하여 활성층을 형성하는 단계를 포함한다.

기타 실시예의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예를 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예는 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

이하, 도 1 내지 도 9를 참조하여 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 제조 방법을 상세히 설명한다.

도 1은 본 발명의 일 실시예에 따라 제조된 박막 트랜지스터 액정 표시 장치의 개념도 이고, 도 2는 도 1에 도시된 박막 트랜지스터 액정 표시 장치의 한 화소에 대한 등가 회로도이다.

도 1에 도시한 바와 같이, 본 발명의 일 실시예에 따라 제조된 박막 트랜지스터 액정 표시 장치는 액정 표시 기판(liquid crystal panel; 100) 및 액정 표시 기판(100)에 연결된 게이트 구동부(gate driver; 140)와 데이터 구동부(data driver; 150), 게이트 구동부(140)에 연결된 구동 전압 생성부(driving voltage generator; 170), 데이터 구동부(150)에 연결된 계조 전압 생성부(gray voltage generator; 180), 그리고 이들을 제어하는 신호 제어부(signal controller; 160)를 포함한다.

액정 표시 기판(100)은 등가 회로로 볼 때 복수의 게이트 라인 및 데이터 라인(G1-Gn, D1-Dm)에 의해 정의되는 영역에 복수의 화소(pixel)를 포함하며, 각 화소는 게이트 라인 및 데이터 라인(G1-Gn, D1-Dm)에 연결된 박막 트랜지스터(Q)와이에 연결된 액정 캐패시터(Cp) 및 스토리지 캐패시터(storage capacitor; Cst)를 포함한다.

게이트 라인과 데이터 라인(G1-Gn, D1-Dm)은 게이트 신호(gate signal)를 전달하며 행방향으로 뻗어 있는 복수의 게이트 라인(G1-Gn)과 데이터 신호(data signal)를 전달하며 열방향으로 뻗어 있는 데이터 라인(D1-Dm)을 포함한다.

박막 트랜지스터(Q)는 삼단자 소자로서, 그 제어 단자는 게이트 라인(G1-Gn)에 연결되어 있고 입력 단자는 데이터 라인(D1-Dm)에 연결되며, 출력 단자는 액정 캐패시터(Cp) 및 스토리지 캐패시터(Cst)의 한 단자에 연결되어 있다.

이와 달리 스토리지 캐패시터(Cst)의 다른 단자는 바로 위의 게이트 라인(이하, 전단 게이트 라인(previous gate line)이라함)에 연결되어 있을 수 있다. 전자의 연결 방식을 독립 배선 방식(separate wire type)이라고 하며, 후자의 연결 방식을 전단 게이트 방식(previous gate type)이라고 한다.

한편, 액정 표시 기판(100)을 구조적으로 보면 도 2에서와 같이 개략적으로 나타낼 수 있다. 편의상 도 2에는 하나의 화소만을 나타내었다.

도 2에 도시한 것처럼, 액정 표시 기판(100)은 서로 마주 보는 하부 기판(110)과 상부 기판(120) 및 둘 사이의 액정층 (130)을 포함한다. 하부 기판(110)에는 게이트 라인(Gi-1, Gi) 및 데이터 라인(Dj)과 박막 트랜지스터(Q) 및 스토리지 캐패시터(Cst)가 구비되어 있다. 액정 캐패시터(Cp)는 하부 기판(110)의 화소 전극(112)과 상부 기판(120)의 기준 전극 (122)을 두 단자로 하며 두 전극(112, 122) 사이의 액정층(130)은 유전체로서 기능한다.

화소 전극(112)은 박막 트랜지스터(Q)에 연결되며 기준 전극(122)은 상부 기판(120)의 전면(全面)에 형성되어 있고 공통 전압(Vcom)에 연결된다.

여기에서 액정 분자들은 화소 전극(112)과 기준 전극(122)이 생성하는 전기장의 변화에 따라 그 배열을 바꾸고 이에 따라 액정층(130)을 통과하는 광의 편광이 변화한다. 이러한 편광의 변화는 상·하부 기판(120, 11)에 부착된 편광자(미도시)에 의하여 광의 투과율 변화로 나타난다.

화소 전극(112)은 또한 기준 전압을 인가 받는 별개의 배선이 하부 기판(110)에 구비되어 화소 전극(112)과 중첩됨으로써 스토리지 캐패시터(Cst)를 이룬다. 전단 게이트 방식의 경우 화소 전극(112)은 절연체를 매개로 전단 게이트 라인(Gi-1)과 함께 스토리지 캐패시터(Cst)의 두 단자를 이룬다.

도 2에서와는 달리 기준 전극(122)이 하부 기판(110)에 구비되는 경우도 있으며 이때에는 두 전극(112, 122)이 모두 선형으로 만들어진다.

한편, 색 표시를 구현하기 위해서는 각 화소가 색상을 표시할 수 있도록 하여야 하는데, 이는 화소 전극(112)에 대응하는 영역에 적색, 녹색, 또는 청색의 컬러 필터(color filter; 124)를 구비함으로써 가능하다. 컬러 필터(124)는 도 2에서처럼 주로 상부 기판(120)의 해당 영역에 형성되지만 하부 기판(110)의 화소 전극(112) 위 또는 아래에 형성할 수도 있다.

다시 도 1을 참고하면, 구동 전압 생성부(170)는 박막 트랜지스터(Q)를 턴온(turn on)시키는 게이트 온 전압(Von)과 박막 트랜지스터(Q)를 턴오프(turn off)시키는 게이트 오프 전압(Voff) 등을 생성한다.

계조 전압 생성부(180)는 액정 표시 장치의 휘도와 관련된 복수의 계조 전압(gray voltage)을 생성한다.

게이트 구동부(140)는 스캔 구동부(scan driver)라고도 하며, 액정 표시 기판(100)의 게이트 라인(G1-Gn)에 연결되어 구동 전압 생성부(170)로부터의 게이트 온 전압(Von)과 게이트 오프 전압(Voff)의 조합으로 이루어진 게이트 신호를 게이트 라인(G1-Gn)에 인가한다.

또한 데이터 구동부(150)는 소오스 구동부(source driver)라고도 하며, 액정 표시 기판(100)의 데이터 라인(D1-Dm)에 연결되어 계조 전압 생성부(180)로부터의 계조 전압을 선택하여 데이터 신호로서 데이터 라인(D1-Dm)에 인가한다.

신호 제어부(160)는 게이트 구동부(140), 데이터 구동부(150) 및 구동 전압 생성부(170) 등의 동작을 제어하는 제어 신호를 생성하여, 각 해당하는 제어 신호를 게이트 구동부(140), 데이터 구동부(150) 및 구동 전압 생성부(170)에 공급한다.

상기한 바와 같은 박막 트랜지스터 액정 표시 장치의 제조 방법에 대해 도 3 내지 도 9를 참조하여 설명한다.

도 3은 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치의 제조 공정 흐름도 이다.

도 3을 참조하면, 먼저 기판 상에 비정질 실리콘막을 형성한다 (S1).

비정질 실리콘막은 CVD(Chemical Vapor Deposition), SACVD(Sub-Atmospheric CVD), LPCVD(Low Pressure CVD) 또는 PECVD(Plasma Enhanced CVD) 등의 방법을 통해 형성할 수 있다.

계속해서, 비정질 실리콘막에 함유되어 있는 수소는 향후 결정화 공정에 있어서 결함의 원인이 되므로 비정질 실리콘막에 선택적으로 탈수소화 공정을 행할 수 있다. 이때, 비정질 실리콘막은 화학적으로 약한 결합을 하고 있어 열처리에 의해 비정질 실리콘막 내에 함유되어 있는 수소 성분을 제거할 수 있다. 따라서, 탈수소화 공정은 질소(N2) 분위기 하에서 400 내지 500℃의 온도에서 2시간 정도 열처리를 하여 비정질 실리콘막 내의 수소 성분들이 기체 상태로 날아가도록 할 수 있다.

또한, 비정질 실리콘막을 형성하기 전에 기판 상에 버퍼충을 형성할 수도 있다. 버퍼층은 기판의 불순물 성분이 비정질 실리콘막으로 확산되는 것을 방지하기 위한 것으로서 질화 실리콘이나 산화 실리콘 등을 이용하여 형성할 수 있다.

이어서, 결정립이 생기도록 결정화하여 결정질 실리콘막을 형성한다(S2).

상기한 바와 같이 비정질 실리콘막이 형성된 기판을 SLS 장비 내에 위치시켜 비정질 실리콘막을 결정화한다.

도 4는 SLS 방법에 이용되는 장치를 도시한 것이다. 도 4를 참조하여 SLS 장치(200)를 설명하면, SLS 장치(200)는 레이저빔을 발생시키는 레이저 발생 장치(210)와, 레이저 발생 장치(210)를 통해 방출된 레이저빔(220)을 집속시키는 집속 렌즈(230)와 비정질 실리콘막이 형성된 기판(110)에 레이저빔(220)을 투과 또는 차단시키는 마스크(240)와 마스크(240) 하부에 위치하여 마스크(240)를 통과한 레이저빔(220)을 일정한 비율로 축소하는 축소 렌즈(250)로 구성된다.

레이저빔 발생 장치(210)는 광원에서 레이저빔(220)을 방출시킨다. 방출된 레이저빔(220)은 감쇄기(미도시)를 통과하면서 레이저빔(220)이 소정의 에너지 크기를 갖도록 조절되고, 집속 렌즈(230)를 통과하게 된다.

마스크(240)에 대응되는 위치에는 비정질 실리콘이 증착된 기판(110)이 X-Y방향으로 움직이는 스테이지(260) 위에 위치한다.

이때, 비정질 실리콘막이 형성된 기판(110)의 모든 영역을 결정화하기 위해서는 스테이지(260)를 미소하게 움직임으로써 결정 영역을 확대해 간다. 이때 스테이지(260)가 X 또는 Y 방향의 어느 한 방향으로 움직이도록 하고, 마스크(240)가 스테이지(260)와 직교하는 방향으로 움직이며 결정화 할 수도 있다.

전술한 구성에 있어서, 마스크에 대해 도 5를 참조하여 간단히 설명한다.

마스크(240)는 레이저빔을 통과시키는 투과 영역(241)인 다수의 슬릿과 레이저빔을 차단하는 슬릿 사이의 영역인 차단 영역(242)으로 구분된다. 슬릿과 슬릿의 간격은 실리콘 결정립의 측면 성장 길이를 결정한다.

도 6a 내지 도 6d에는 도 4의 장치를 이용하여 SLS 방법에 의해 비정질 실리콘막을 결정화하는 과정을 도시하였다.

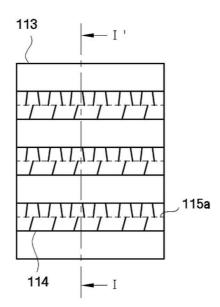

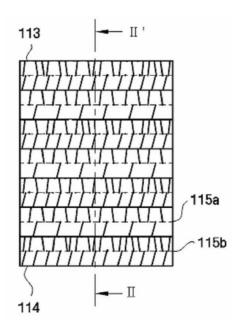

도 6a는 레이저빔을 1차 조사하였을 경우, 비정질 실리콘막이 결정질 실리콘막으로 결정화된 단계를 도시한 도면이다.

먼저, 비정질 실리콘막(113)의 상부에 위치한 마스크(미도시)를 통해 레이저빔을 1차 조사한다. 이때, 조사된 레이저빔은 마스크에 구성된 다수의 슬릿(도 5의 241, 242 참조)에 의해 나누어져 부분적으로 비정질 실리콘막(113)을 녹여 액상화한다. 이와 같은 경우, 상기 레이저 에너지의 정도는 비정질 실리콘막(113)이 완전히 녹을 정도의 고에너지 영역대 (complete melting regime)를 사용한다.

완전히 녹아 액상화된 비정질 실리콘은 레이저빔의 조사가 끝나면 비정질 실리콘 영역과 액상화된 실리콘 영역의 계면 (114)에서 실리콘 결정립의 측면 성장이 진행된다. 실리콘 결정립의 측면 성장은 계면(114)에 대해 수직으로 일어난다.

결과적으로, 마스크에 구성한 슬릿(도 5의 241 참조)의 수만큼 한 블록 내에 부분적으로 결정화된 영역이 발생한다.

도 6b는 도 6a에 있어서 I-I' 선을 따라 잘라 도시한 단면도이다. 도 6b를 참조하면, 양쪽 계면(114)에 대한 수직으로 성장하기 시작한 결정립은 중앙에서 서로 충돌을 일으키게 되어 돌출부(115a)가 형성된다.

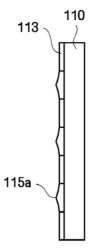

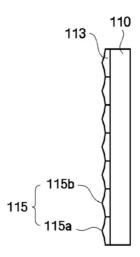

다음으로, 도 6c는 레이저빔을 2차 조사하여, 실리콘 결정립이 성장한 모양을 도시한 도면이다.

1 차 레이저빔 조사 후에, X-Y 스테이지(도 4의 260 참조) 또는 마스크(도 4의 240 참조)를 결정립의 측면 성장 길이와 같거나 작게 수  $\mu$  이동한 후, 다시 2차 레이저빔 조사를 실시한다. 2 차 조사된 레이저빔에 닿은 실리콘 부분은 액상화된 후다시 결정화된다.

이때, 1 차 조사 결과로 형성된 다결정 실리콘 영역의 실리콘 결정립이 씨드로 작용하여 실리콘 용융 영역으로 결정립의 측면 성장이 이루어진다.

2 차 조사가 끝난 후의 실리콘 결정은 1 차 조사에 의해 성장한 결정립에 연속하여 더욱 측면 성장한다.

이와 같은 방법으로 레이저빔 조사를 반복하여 비정질 실리콘막 전체를 주사(scanning)함으로써, 결정립의 크기가 큰 결정질 실리콘막을 제조할 수 있다.

도 6d는 도 6b에 있어서 II-II' 선을 따라 잘라 도시한 단면도이다. 도 6d를 참조하면, 양쪽 계면(114)에 대한 수직으로 성장하기 시작한 결정립은 중앙에서 서로 충돌을 일으키게 되어 돌출부(115b)가 형성된다.

상기한 바와 같이, 비정질 실리콘막이 결정질 실리콘막으로 결정화되는 과정에서 결정립들의 충돌에 의해 돌출부(115a, 115b)가 발생하게 되고, 전체 결정질 실리콘막에 돌출 패턴(115)이형성된다.

계속해서, 결정질 실리콘막 형성시 발생한 돌출 패턴을 정렬한다(S3).

결정질 실리콘막 상의 결정립의 크기, 크기의 균일성, 수와 위치, 방향 등은 문턱 전압(Vth), 문턱치 경사(subthreshold slope), 전하 수송 이동도(charge carrier mobility), 누설 전류(leakage current) 및 디바이스 안정성(device stability) 등과 같은 박막 트랜지스터의 특성에 직접 또는 간접적으로 영향을 줄 수 있다. 또한, 박막 트랜지스터 액정 표시 장치의 기판 제작시 결정립의 위치에 따라서 박막 트랜지스터의 균일성에도 중대한 영향을 줄 수 있다.

이때, 박막 트랜지스터 액정 표시 장치의 전체 기판 위에 형성되는 박막 트랜지스터의 액티브 채널 영역 내의 1차 결정립 경계의 수는 결정립의 크기, 기울어짐 각도(θ), 액티브 채널의 차원(dimension, 길이; L, 폭; W)과 기판 상의 각 박막 트랜 지스터의 위치에 따라 같거나 달라질 수 있다(도 7a 및 도 7b).

도 7a 및 도 7b에서와 같이, 결정립 크기, 액티브 채널 차원(L ×W), 기울어짐 각도(Θ)에 대하여 액티브 채널 영역에 포함될 수 있는 1차 결정립 경계의 수는, 최대 결정립 경계의 수를 Nmax라 할 때, 즉 박막 트랜지스터의 기판 또는 액정 표시장치의 위치에 따라 액티브 채널 영역 내에 포함되는 1차 결정립 경계의 수는 Nmax(도 7a의 경우 2개) 또는 Nmax-1(도 7b의 경우 2개)개가 될 것이다. 이때, 모든 박막 트랜지스터에 대하여 Nmax의 1차 결정립 경계의 수가 액티브 채널 영역 내에 포함될 때 가장 우수한 박막 트랜지스터의 특성의 균일성이 확보될 수 있다. 즉, 각각의 박막 트랜지스터가 동일한 수의 결정립 경계를 갖는 것이 많을수록 균일성이 우수한 박막 트랜지스터 액정 표시 장치를 얻을 수 있다.

상기한 바와 같이 각각의 박막 트랜지스터에 동일한 수의 결정립 경계를 포함하도록 하기 위해서, 결정질 실리콘막상에 발생된 돌출 패턴(115)(이하, 돌출 패턴)을 이용할 수 있다. 즉, 돌출 패턴(115)이 박막 트랜지스터 별로 동일하게 할당되도록 돌출 패턴(115)을 정렬함으로써, 결국 박막 트랜지스터에 동일한 수의 결정립 경계를 포함하도록 할 수 있다. 이러한 돌출 패턴(115)을 정렬하기 위하여 도 8에 도시한 바와 같은 간섭계를 이용할 수 있다.

도 8을 참조하면, 간섭계(300)는 광을 생성하여 출사하는 광원(310), 그레이팅(320), 빔스프리터(330), 반사 미러(340), 얼라인 패턴(350), 스테이지(360), 광 획득 수단(370) 및 광 처리 수단(380)을 포함한다.

그레이팅(320)은 광원(310)과 돌출 패턴(115)이 형성되어 있는 기판(110)이 위치하고 이동 가능한 스테이지(360) 사이의 광경로 상에 배치되어 광원(310)으로부터 입사되는 입사광을 회절 투과시킨다.

빔스프리터(330)는 그레이팅(320)과 스테이지(360) 사이의 광경로상에 배치되어 입사광의 진행 경로를 변환한다.

반사 미러(340)는 빔스프리터(330)를 통과한 광을 기판(110)으로 반사하거나 기판(110)으로부터 반사되어 나오는 광을 다시 빔스프리터(330)로 반사한다.

얼라인 패턴(350)은 기판(110) 상의 돌출 패턴(115)을 박막 트랜지스터 배열과 정렬시키기 위한 것으로, 도 8의 A에 도시한 바와 같이 박막 트랜지스터의 배열 정보에 근거하여 일정 간격으로 이격되어 있는 패턴들(351)을 포함한다.

광 획득 수단(370)은 기판 상의 결정질 실리콘막의 돌출 패턴(115)으로부터 반사되어 빔스프리터(330)를 경유한 광과 얼라인 패턴(350)을 경유한 광을 수광하고, 광 처리 수단(380)은 광 획득 수단(370)에 의해 얻어진 데이터를 처리한다.

이러한 간섭계(300)의 작동은 다음과 같이 이루어진다.

먼저 광원(310)에서 출사된 광은 그레이팅(320)을 통과하면서 0차 광 또는  $\pm 1$ 차 광으로 회절된다. 이와 같이 회절된 0차 광 또는  $\pm 1$ 차 광은 빔스프리터(330)와 반사 미러(340)를 경유하여 기판 상의 돌출 패턴(115)에 조사된다. 그리고 이 0차 광 또는  $\pm 1$ 차 광은 기판(110) 상의 돌출 패턴(115)으로부터 반사된 후, 다시 역방향으로 진행되어 빔스프리터(330)와 얼라인 패턴(350)을 경유하여 광 획득 수단(370)에 의해 수득된다. 이러한 광 획득 수단(370)에 의해 수득된 데이터는 광 처리 수단(380)에 의해 처리된다.

광 획득 수단(370)으로부터 수득된 데이터를 광 처리 수단(380)에 의해 처리한 결과 돌출 패턴(115)과 얼라인 패턴(350)의 정렬 상태가 서로 어긋나는 경우에는 간섭 패턴이 발생하게 된다. 이 경우에는 돌출 패턴(115)과 얼라인 패턴(350)의 불일치에 의한 간섭 패턴이 발생하지 않을 때까지 돌출 패턴(115)이 형성되어 있는 기판(110)이 안착되어 있는 스테이지 (360)를 이동하여 돌출 패턴(115)을 얼라인 패턴(350)을 정렬시킨다.

계속해서, 활성층, 게이트 절연막 및 게이트 전극을 형성한다(S4).

도 9를 참조하면 상기한 바와 같이 얼라인 패턴(350)에 의해 돌출 패턴(115)이 정렬된 결정질 실리콘막이 형성된 기판 상에 포토레지스트(photoresist)를 형성하고 노광, 현상하여 포토레지스트 패턴을 형성한다.

이어서, 포토레지스트 패턴을 마스크로 이용하여 결정질 실리콘막을 건식 또는 습식 식각하여 활성층(410)을 형성한다. 활성층(410)은 박막 트랜지스터의 액티브 채널 영역으로 작용한다.

계속해서, 활성충(410)이 형성된 기판(110) 상에 게이트 절연막을 증착한다. 그리고, 게이트 절연막 상에 게이트 전극 물질을 증착하고, 패터닝하여 게이트 전극(420)을 형성한다.

이어서, 도면에는 도시되지 않았으나 후속의 일반적인 박막 트랜지스터 액정 표시 장치의 제조 공정을 진행하여 박막 트랜지스터 액정 표시 장치를 제조하면, 결정질 실리콘막으로 이루어진 활성층(410)을 가지는 박막 트랜지스터 액정 표시 장치를 제조할 수 있다(S5).

상기한 바와 같이 제조된 박막 트랜지스터 액정 표시 장치는 기판 상의 돌출 패턴을 박막 트랜지스터 배치 정보에 근거한 얼라인 패턴과 정렬시킴으로서 결국 박막 트랜지스터의 액티브 채널 영역에 동일한 수의 결정립 경계를 갖게 함으로서 균 일성이 우수한 박막 트랜지스터액정 표시 장치를 얻을 수 있다.

이상 첨부된 도면을 참조하여 본 발명의 일 실시예에 따른 박막 트랜지스터 액정 표시 장치에 대해 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예는 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

#### 발명의 효과

상기한 바와 같이 본 발명 따라 제조된 박막 트랜지스터 액정 표시 장치는 기판 상의 돌출 패턴을 박막 트랜지스터 배치 정보에 근거한 얼라인 패턴과 정렬시킴으로서 결국 박막 트랜지스터의 액티브 채널 영역은 동일한 수의 결정립 경계를 갖게된다. 따라서, 기판 전체에 걸쳐 형성되는 박막 트랜지스터는 균일한 물리적 특성을 가질 수 있다.

#### (57) 청구의 범위

#### 청구항 1.

기판 상에 비정질 실리콘막을 구비하는 단계;

상기 비정질 실리콘막을 결정립이 생기도록 결정화하여 결정질 실리콘막을 형성하는 단계;

상기 결정질 실리콘막 형성 단계에서 발생한 돌출 패턴이 박막 트랜지스터 별로 동일하게 할당되도록 상기 박막 트랜지스터 배치 정보에 근거하여 상기 돌출 패턴을 정렬하는 단계; 및

상기 결정질 실리콘막을 식각하여 활성층을 형성하는 단계를 포함하는 박막 트랜지스터 액정 표시 장치의 제조 방법.

#### 청구항 2.

제 1 항에 있어서.

상기 비정질 실리콘막을 결정화하는 단계에서 상기 비정질 실리콘막은 SLS 방법에 의해 결정화하는 박막 트랜지스터 액정 표시 장치의 제조 방법.

#### 청구항 3.

제 1 항에 있어서,

상기 돌출 패턴을 정렬하는 단계에서 상기 돌출 패턴은 박막 트랜지스터 배치 정보에 근거한 얼라인 패턴을 포함하는 간섭계에 의해 정렬되는 박막 트랜지스터 액정 표시 장치의 제조 방법.

#### 청구항 4.

제 1 항에 있어서,

상기 결정질 실리콘막에 형성된 결정립의 1차 결정립 경계는 상기 박막 트랜지스터의 상기 활성층 영역 내에 동일한 개수가 존재하도록 배열되는 박막 트랜지스터 액정 표시 장치의 제조 방법.

#### 도면

#### 도면1 150 180 R - 160 G В RVS 신호 계조전압 DE 데이터 구동부 R',G',B 생성부 Hsync 제어부 Vsync D2 D3 · · · Dm CLK G1 OF RVS 게 \_100 G2 0 Voff E Von 구동전압 생성부 구 Vcom Gn-1 동 辞 羟 140 Gn 170

### 도면6a

## 도면6b

## 도면6c

## 도면6d

### 도면7a

### 도면7b

# 도면9

| 专利名称(译)        | 薄膜晶体管液晶显示装置的制造方法 |         |            |

|----------------|------------------|---------|------------|

| 公开(公告)号        | KR1020060080616A | 公开(公告)日 | 2006-07-10 |

| 申请号            | KR1020050000891  | 申请日     | 2005-01-05 |

| [标]申请(专利权)人(译) | 三星电子株式会社         |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司         |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司         |         |            |

| [标]发明人         | UEMOTO TSUTOMU   |         |            |

| 发明人            | UEMOTO,TSUTOMU   |         |            |

| IPC分类号         | G02F1/1368       |         |            |

| CPC分类号         | H04R1/10         |         |            |

| 代理人(译)         | JEONG , SANG BIN |         |            |

| 外部链接           | <u>Espacenet</u> |         |            |

#### 摘要(译)

本发明提供了一种薄膜晶体管液晶显示器的制造方法,该薄膜晶体管液晶显示器形成有源层,该晶体多晶硅由于连续横向固化而形成,该方法被图案蚀刻。薄膜晶体管液晶显示器的制造方法包括在基板上包括非晶硅膜的步骤,以及作为包括形成步骤的薄膜晶体管液晶显示器的制造方法的非晶硅膜的晶粒。结晶多晶硅为了产生而结晶,并且在结晶多晶硅形成步骤中产生的突起图案是薄膜晶体管,基于薄膜晶体管位置信息排列突起图案的步骤特别相同通过蚀刻结晶多晶硅来分配和形成有源层的步骤。SLS,晶界和对齐图案。