**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

**(51) Int. Cl.<sup>7</sup>**

G02F 1/133

**(11) 공개번호** 특2001-0015402

**(43) 공개일자** 2001년02월26일

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>(21) 출원번호</b>  | 10-2000-0042011                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>(22) 출원일자</b>  | 2000년07월21일                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>(30) 우선권주장</b> | 99-206468 1999년07월21일 일본(JP)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>(71) 출원인</b>   | 가부시키가이샤 히타치세이사쿠쇼 가나이 쓰토무<br>일본 도쿄도 치요다구 간다스루가다이 4조메 6반치 가부시키가이샤 히타치초<br>엘에스아이시스템즈 스즈키 진이치로<br>일본국 도쿄도 고다이라시 죠스이촌쵸5-22-1히타치 디바이스엔지니어링 가부<br>시키가이샤 나시모토 류오조<br>일본국 치바켄 모바라시 하야노 3681                                                                                                                                                                                                                                                                                |

| <b>(72) 발명자</b>   | 아키야마켄이치<br>일본국 도쿄도 치요다구 마루노우치 1쵸메 5-1뉴 마루빌딩 가부시키가이샤 히타치 세<br>이사쿠쇼 쇼유肯 혼부나이<br>야마시타유지<br>일본국 도쿄도 치요다구 마루노우치 1쵸메 5-1뉴 마루빌딩 가부시키가이샤 히타치 세<br>이사쿠쇼 쇼유肯 혼부나이<br>이사미히로노부<br>일본국 도쿄도 치요다구 마루노우치 1쵸메 5-1뉴 마루빌딩 가부시키가이샤 히타치 세<br>이사쿠쇼 쇼유肯 혼부나이<br>고토미츠루<br>일본국 도쿄도 치요다구 마루노우치 1쵸메 5-1뉴 마루빌딩 가부시키가이샤 히타치 세<br>이사쿠쇼 쇼유肯 혼부나이<br>야스카와신지<br>일본국 치바켄 모바라시 하야노 3681 히타치 디바이스엔지니어링 가부시키가이샤<br>코테라코이치<br>일본국 도쿄도 코다이라시 조우스이촌쵸 5-22-1 히타치초 엘에스아이시스템즈 가부<br>시키가이샤<br>(74) 대리인<br>이종일 |

**심사청구 : 있음****(54) 액정표시장치****요약**

본 발명은 액정표시장치에 관한 것으로서, 복수의 화소를 가지는 액정패널과, P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고, 상기 영상신호선 구동회로는, Q개의 서로 다른 계조전압을 공급하는 전원회로와, 상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 선택된 하나의 계조전압값을 가지는 2개의 계조전압, 또는 상기 Q개의 서로 다른 계조전압 중에서 선택된 서로 다른 값의 2개의 계조전압을 선택하여 출력하는, 상기 영상신호선의 각각에 대응하여 설치된 복수의 선택회로와, 상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압 중 어느 하나, 또는 상기 서로 다른 값의 2개의 계조전압으로부터 생성된 상기 서로 다른 값의 2개의 계조전압의 중간값의 계조전압을 바탕으로, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압을 출력하는 복수의 앤프회로로 이루어지는 액정표시장치를 제공함으로써, 침크기가 증가하지 않으면서 다계조화를 실현할 수 있으며, 액정패널의 고화질화, 액정표시장치의 프레임 협소화를 달성할 수 있으며, 또한, 디코더회로의 온저항의 증대를 억제할 수 있고, 다계조화한 액정패널의 부하를 줄여 고화질화를 달성할 수 있는 기술이 제시된다.

**내포도****도1****영세서**

## 도면의 간단한 설명

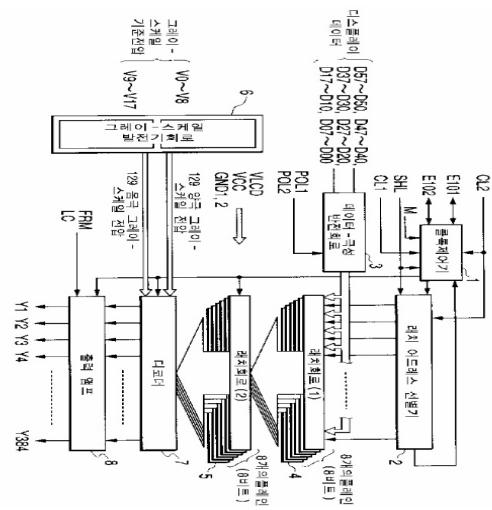

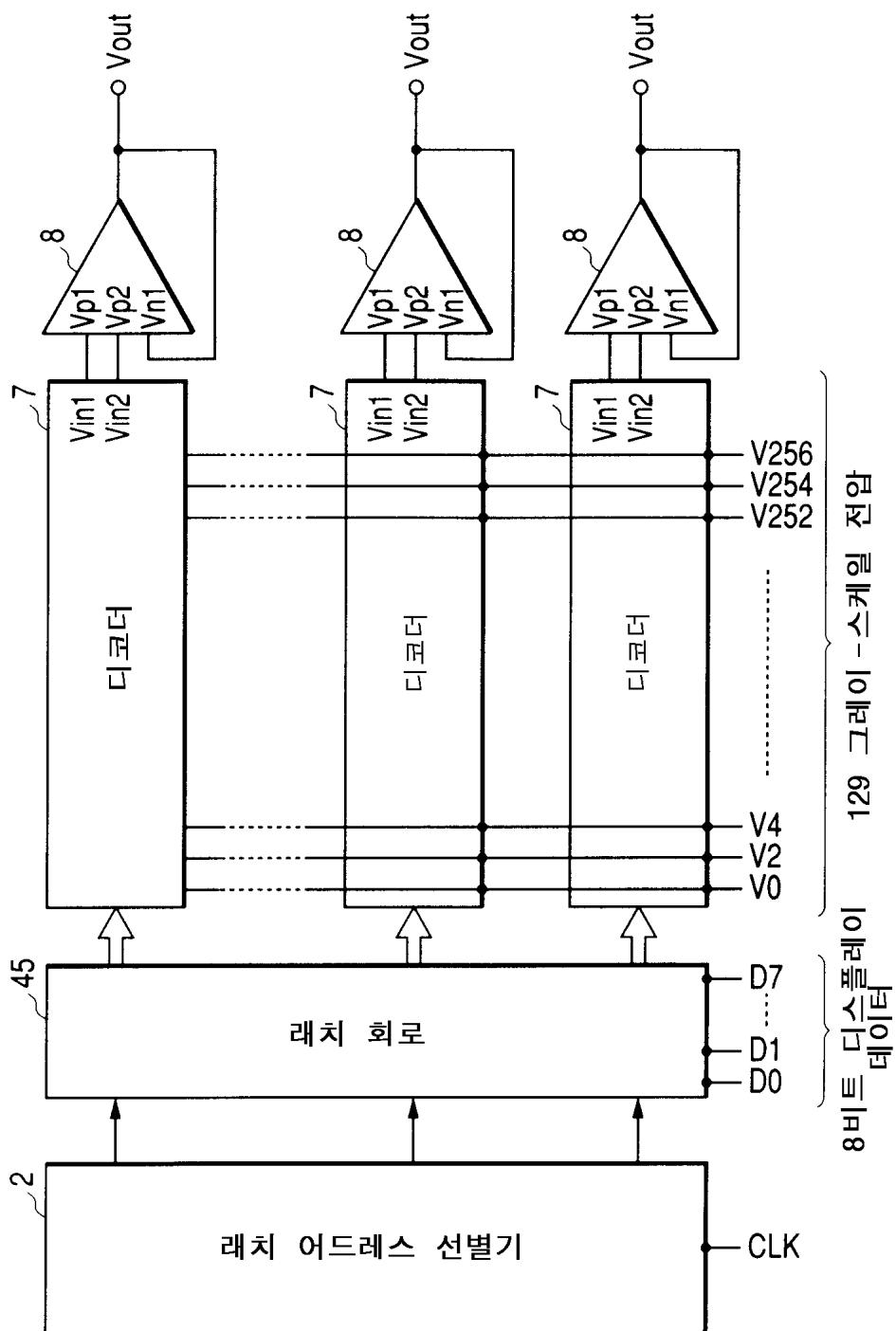

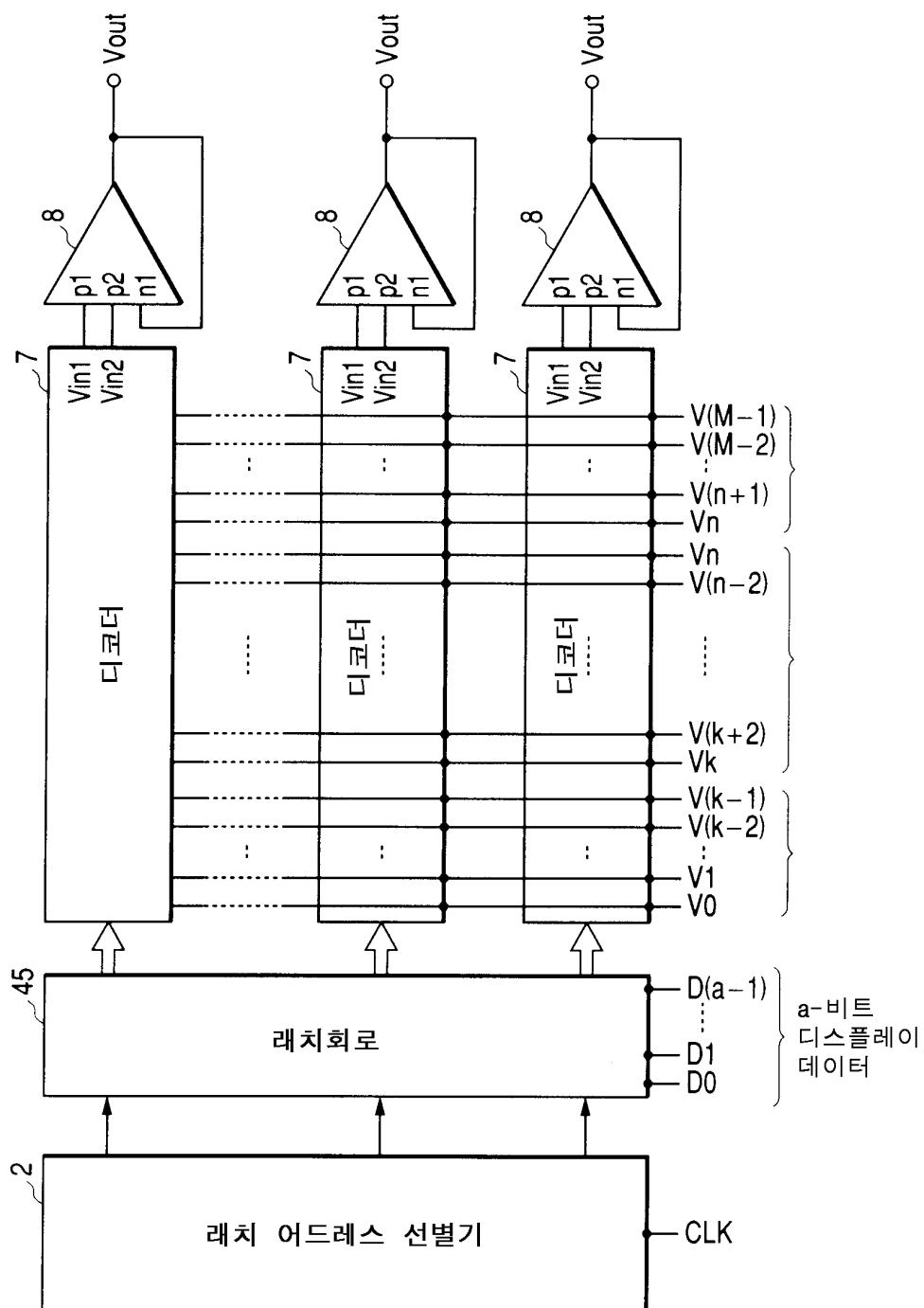

- 도 1은 본 발명의 제 1 실시예에 따른 TFT 액티브 매트릭스형 액정표시장치의 드레인 여진기의 구성을 도시하는 블록도이다.

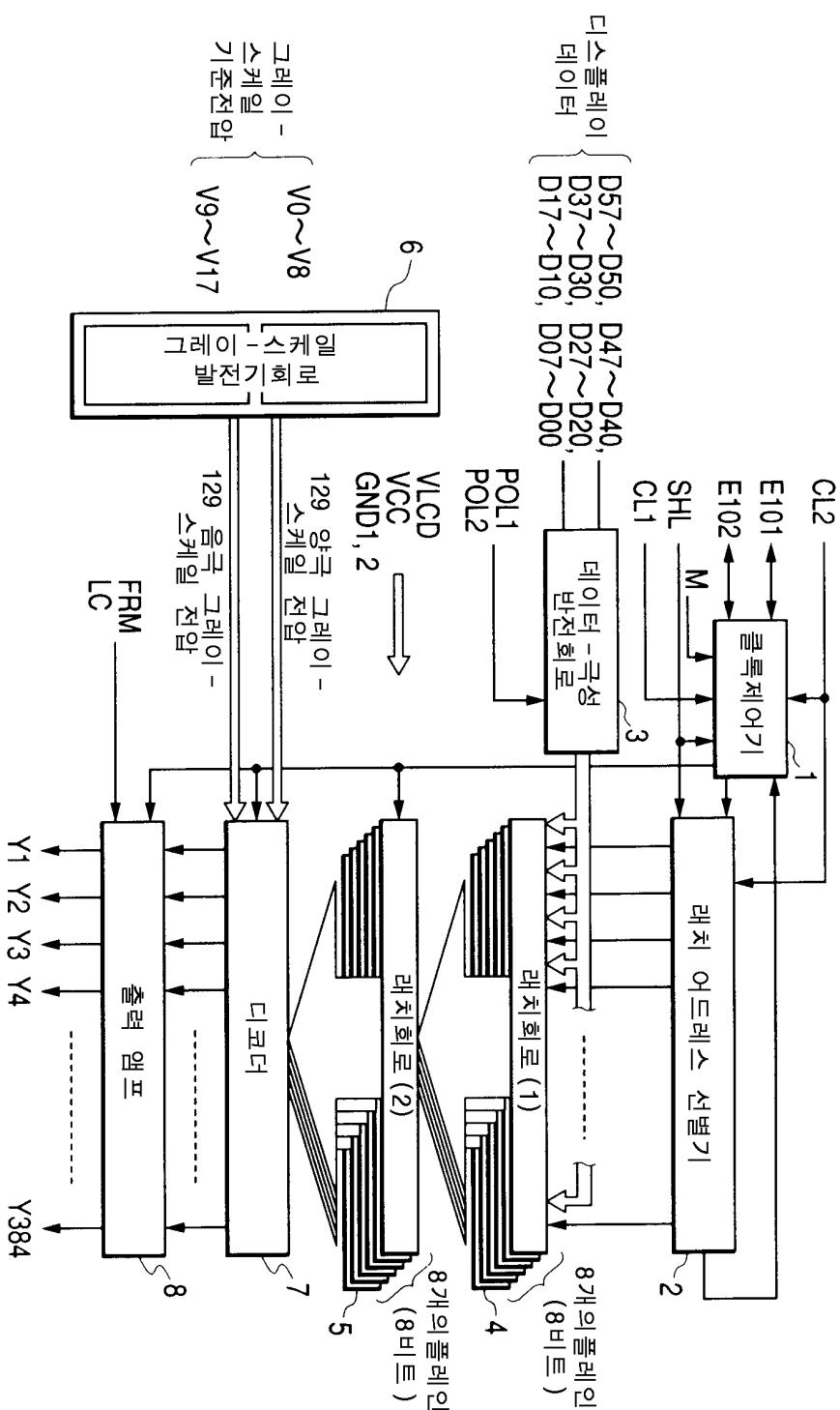

- 도 2는 본 발명의 제 1 실시예에 따른 드레인 여진기 내부회로의 한 예를 나타내는 도이다.

- 도 3은 본 발명의 제 1 실시예에 따른 드레인 여진기 내부회로의 다른 예를 나타내는 도이다.

- 도 4는 도 2 및 3의 드레인 여진기의 작동을 설명하기 위한 블록도이다.

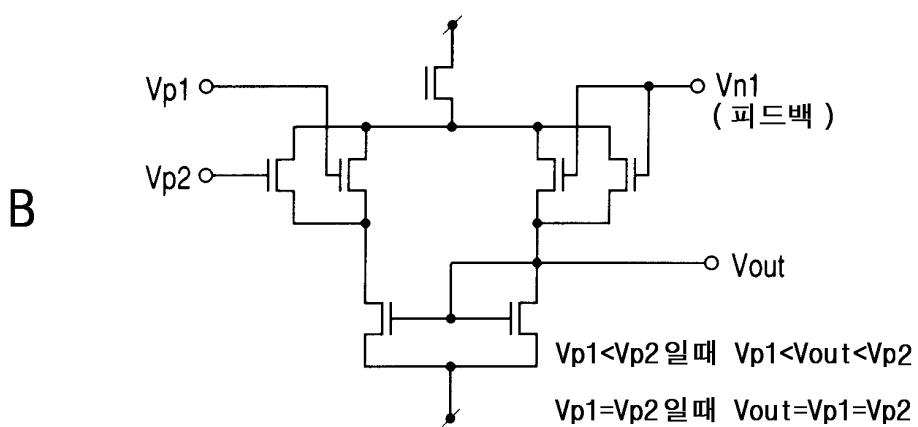

- 도 5A는 드레인 여진기를 위한 종래의 출력증폭기의 회로를 나타내고, 도 5B는 본 발명의 제 1 실시예에 따른 드레인 여진기의 출력증폭기의 구체적인 회로를 나타내는 도이다.

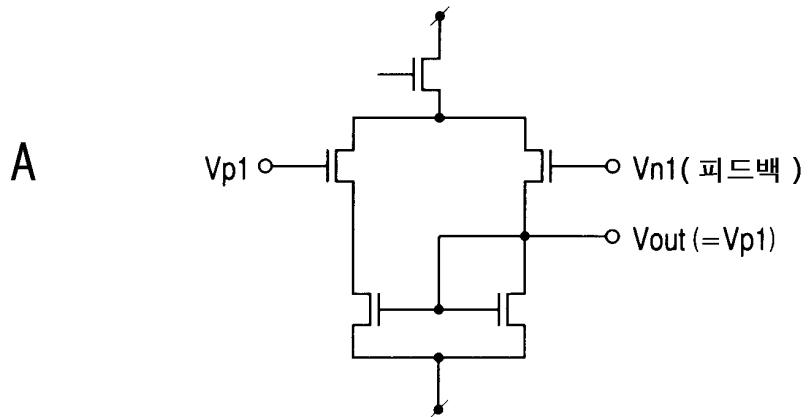

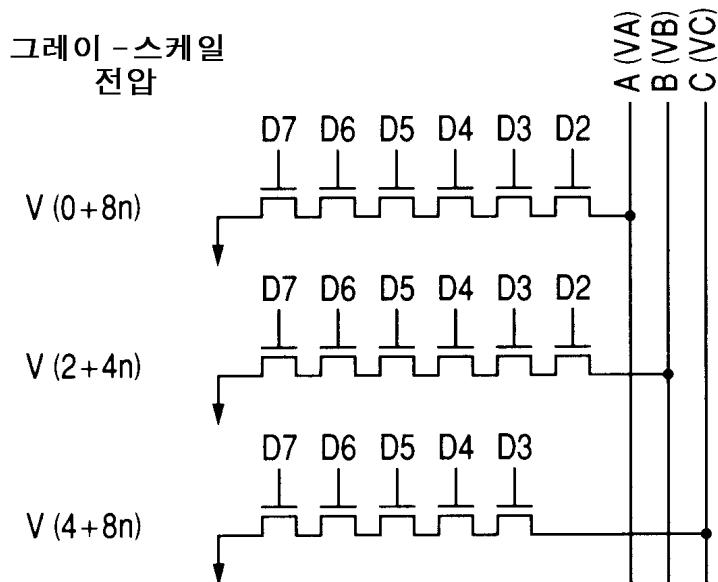

- 도 6은 본 발명의 제 1 실시예에 따른 그레이-스케일 전압선별기 회로의 내부 구성을 설명하기 위한 블록도이다.

- 도 7은 도 6의 그레이-스케일 전압선별기 회로의 구체적인 회로를 나타내는 도이다.

- 도 8은 종래의 토너먼트형 디코더가 사용되는 경우의 출력경로를 나타내는 도이다.

- 도 9는 본 발명의 디코더에서의 출력경로를 나타내는 도이다.

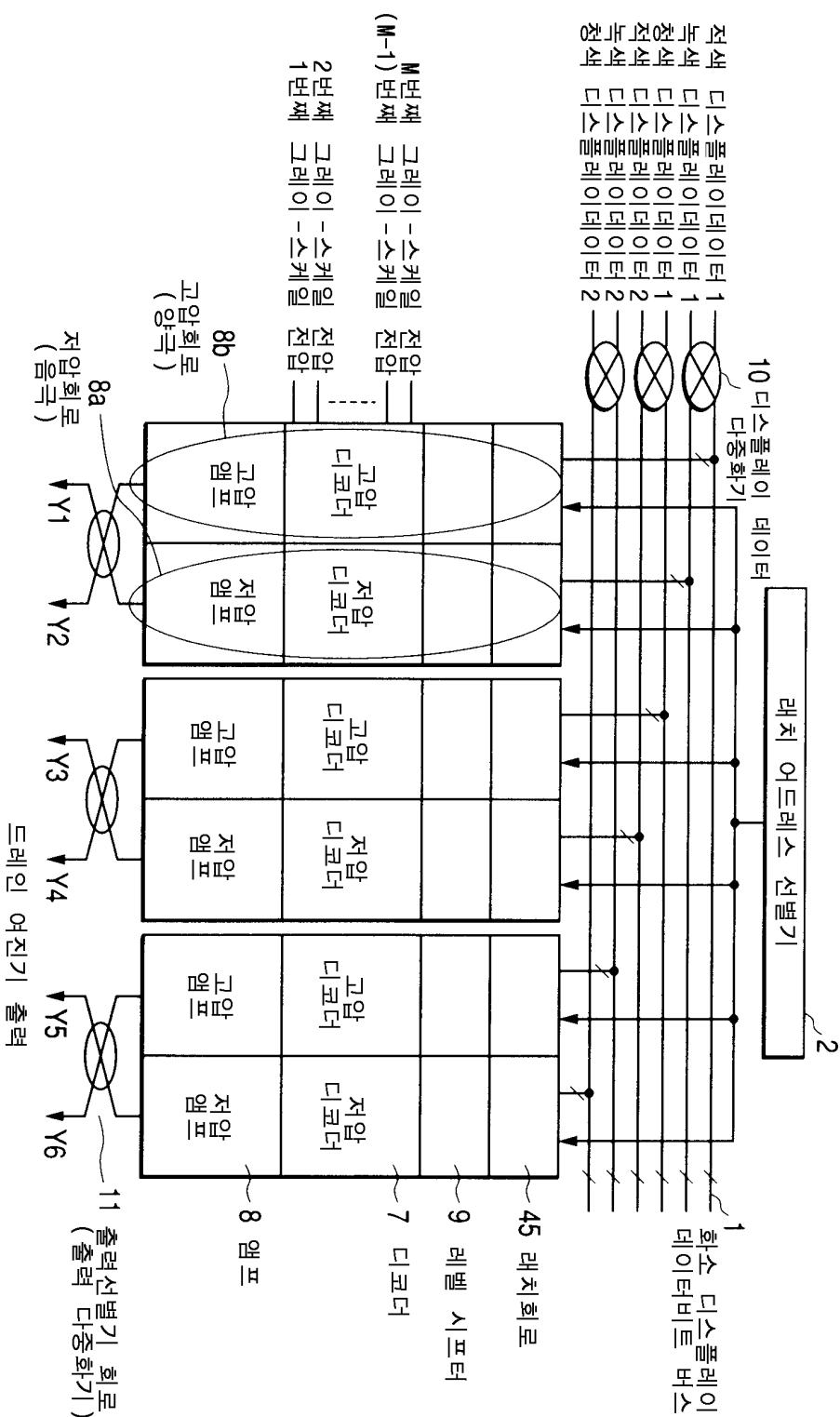

- 도 10은 본 발명의 제 2 실시예에 따른 드레인 여진기의 구성을 도시하는 개략도이다.

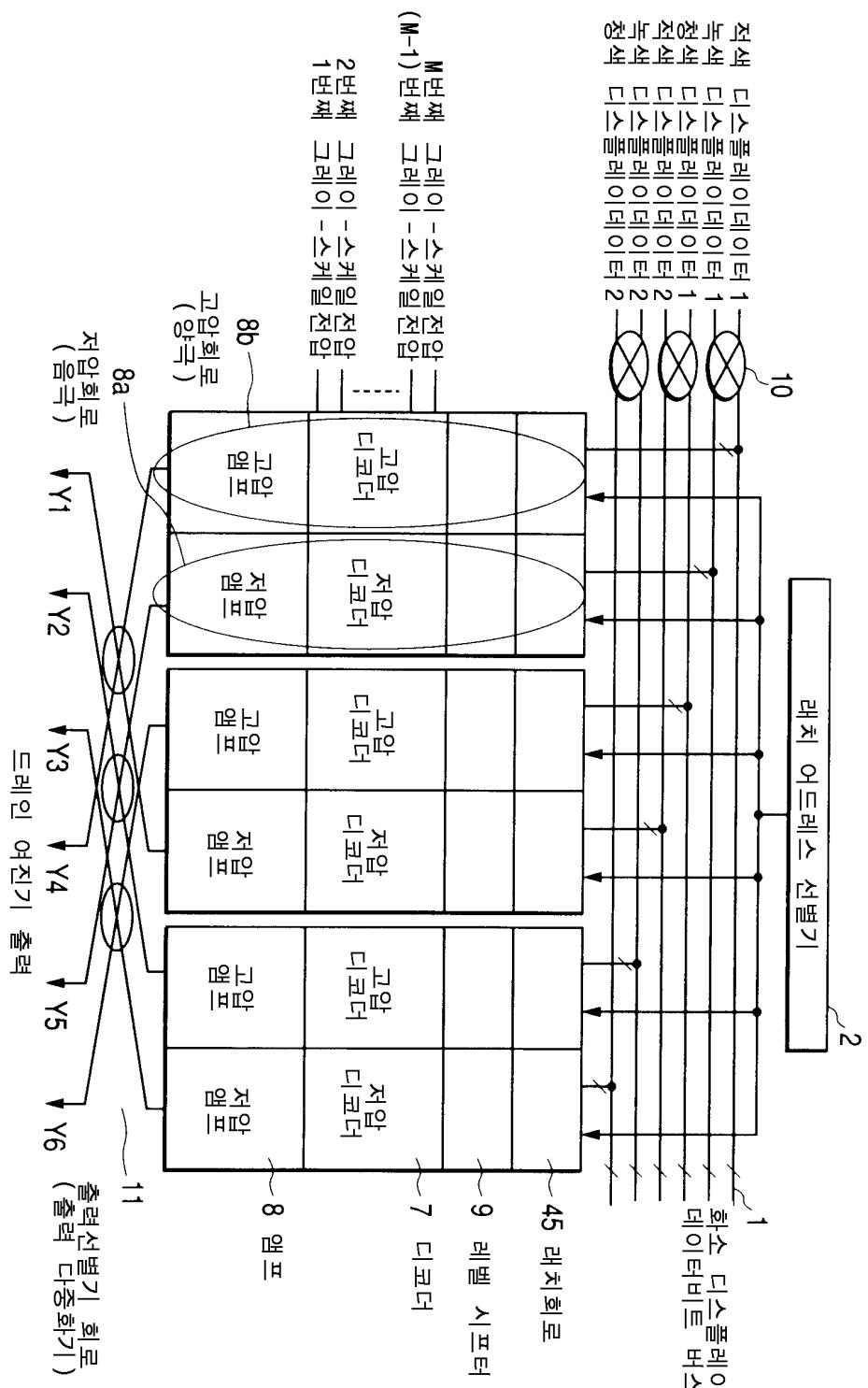

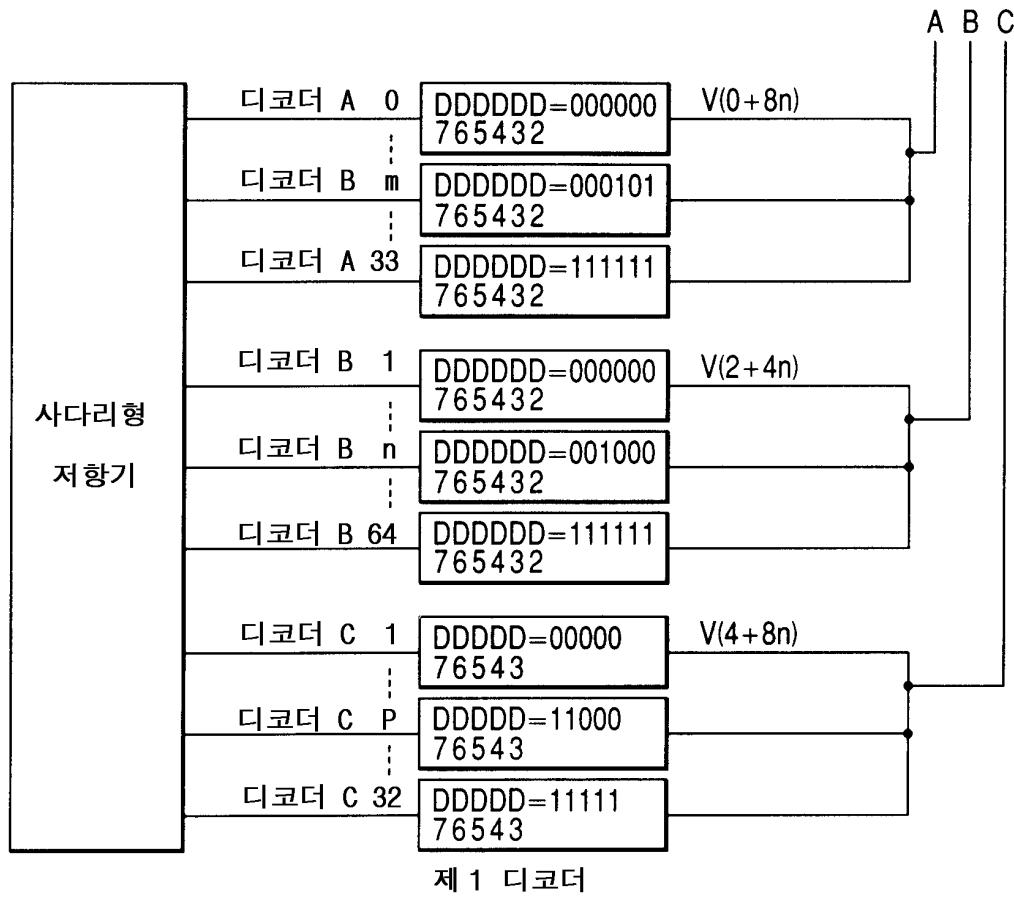

- 도 11은 본 발명의 제 2 실시예에 따른 제1 디코더를 더 설명하기 위한 전체구성도이다.

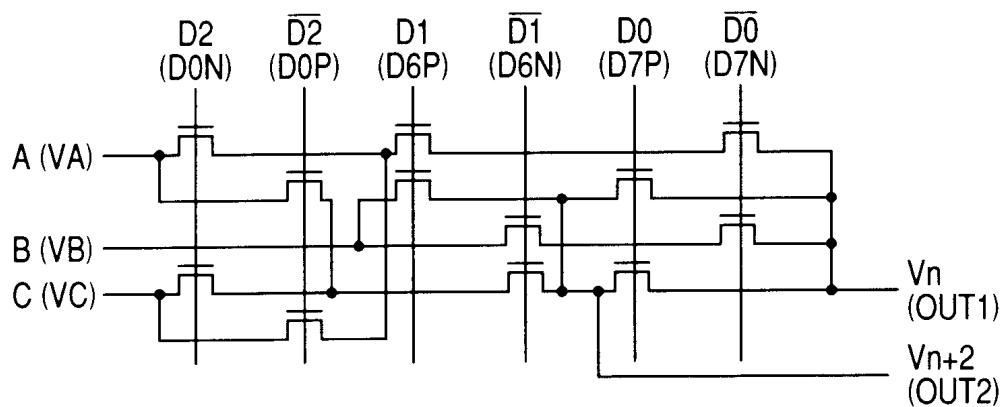

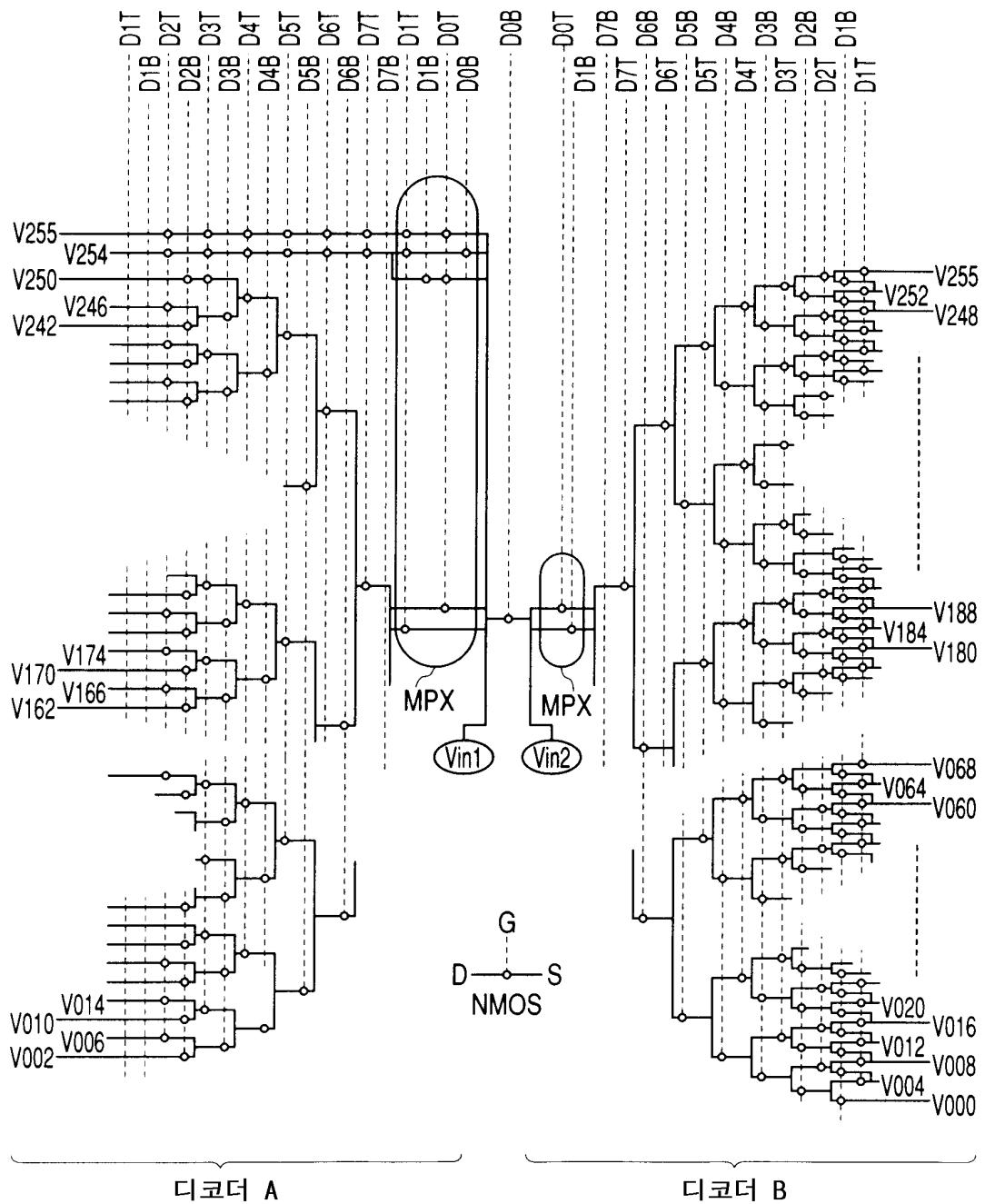

- 도 12는 도 11의 제 1 디코더의 MOS 구성을 도시하는 개략도이다.

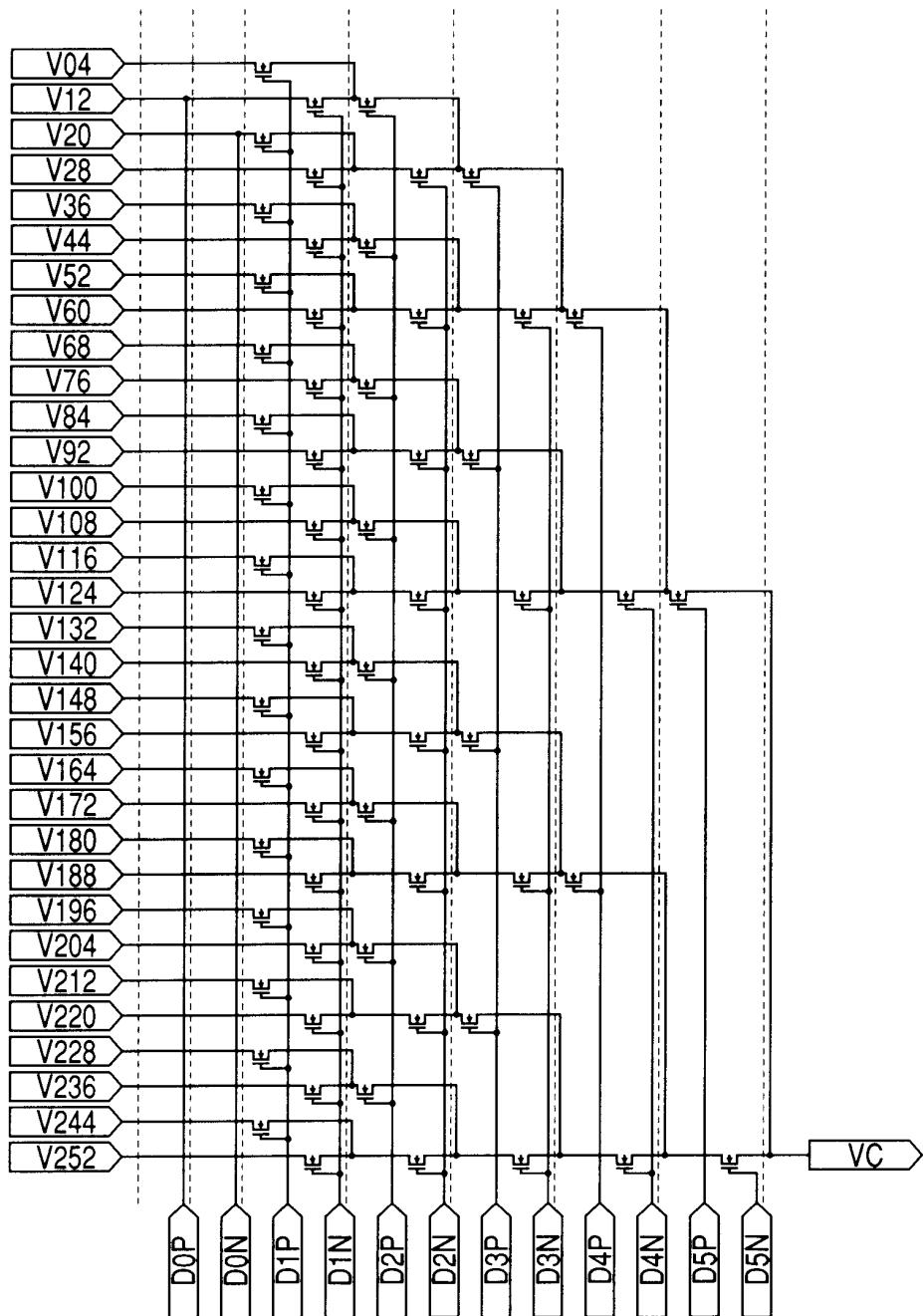

- 도 13은 도 10의 제 2 디코더의 MOS 구성을 도시하는 개략도이다.

- 도 14는 도 10의 토너먼트(1)의 구체적인 회로를 나타내는 도이다.

- 도 15는 도 10의 토너먼트(3)의 구체적인 회로를 나타내는 도이다.

- 도 16은 본 발명의 제 3 실시예에 따른 TFT 액티브 활성매트릭스형 액정표시장치의 드레인 여진기 구성을 도시하는 블록도이다.

- 도 17은 도 16의 디코더를 상세히 설명하기 위한 블록도이다.

- 도 18은 도 17의 디코더의 작동을 설명하기 위한 도면이다.

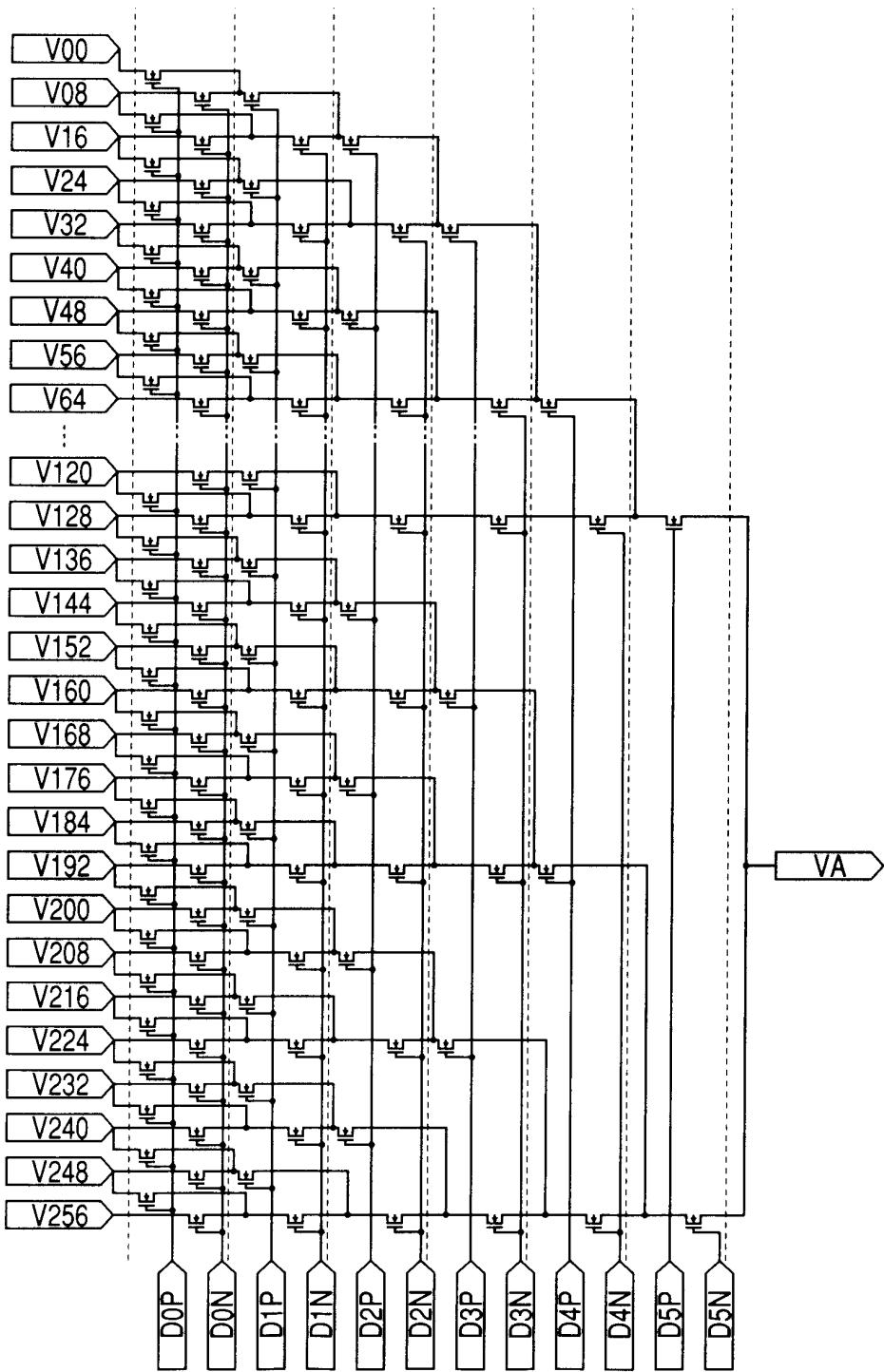

- 도 19는 도 17의 디코더를 구현하는 실제 회로구성을 나타내는 도이다.

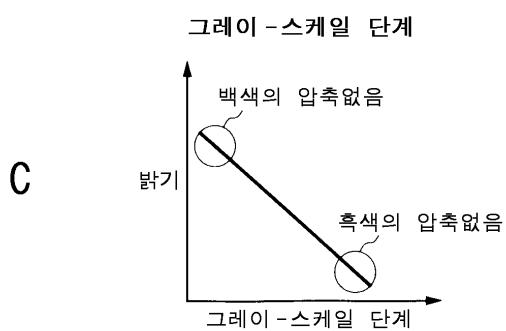

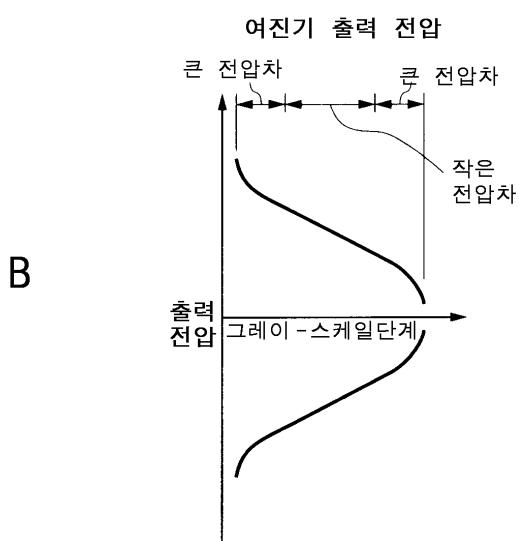

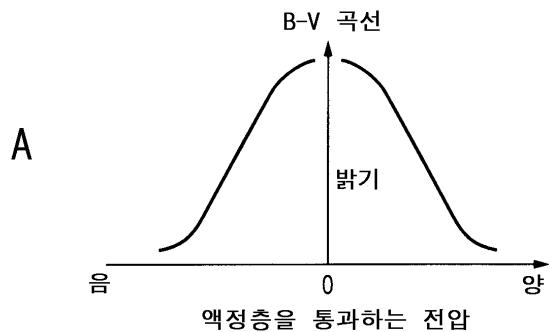

- 도 20A는 액정층을 가로질러 적용되는 전압 및 밝기 사이의 관계를 도시하는 그래프이고, 도 20B는 그레이-스케일 단계 및 드레인 여진기 출력전압 사이의 관계를 도시하는 그래프이고, 도 20C는 밝기 및 그레이-스케일 단계 사이의 관계를 도시하는 그래프이다.

- 도 21은 본 발명의 제 4 실시예에 따른 TFT 액티브 매트릭스형 액정표시장치의 드레인 여진기 구성을 도시하는 블록도이다.

- 도 22는 도 21의 디코더를 상세히 설명하기 위한 블록도이다.

- 도 23은 도 22의 디코더를 구현하는 실제 회로구성을 나타내는 도이다.

- 도 24는 본 발명이 적용된 액정표시장치의 개략적인 구성을 나타내는 도이다.

- 도 25는 종래의 토너먼트형 디코더 시스템을 사용하는 드레인 여진기의 저압회로부분의 회로를 나타내는 도이다.

- 도 26은 토너먼트형 디코더의 전체구성을 도시하는 개략도이다.

- 도 27은 그레이-스케일 전압 및 기록시간 사이의 관계를 도시하는 그래프이다.

- <도면 주요 부분에 대한 부호의 설명>

- |                  |                 |

|------------------|-----------------|

| 1 : 클록제어회로       | 2 : 래치 어드레스 셀렉터 |

| 3 : 데이터 반전회로     | 4, 5, 45 : 래치회로 |

| 6 : 계조전압 생성회로    | 7 : 디코더         |

| 8 : 출력앰프회로       | 8a : 저전압 전용회로   |

| 8b : 고전압 전용회로    | 9 : 레벨시프터회로     |

| 10 : 표시데이터 멀티플렉서 | 11 : 출력선택회로     |

| 281 : 액정패널       | 282 : 드레인 드라이버  |

| 283 : 게이트 드라이버   | 284 : 인터페이스 커넥터 |

| 285 : 표시제어장치     | 286 : 내부전압회로    |

| TFT : 박막 트랜지스터   |                 |

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은, 액정표시장치에 관한 것으로서, 특히 퍼스널 컴퓨터, 워크스테이션 등의 표시수단에 이용하는 다계조표시가 가능한 액정표시장치에 관한 것이다.

PC등의 OA기기의 표시디바이스로서 액정표시장치가 폭넓게 이용되고 있다. 액정표시장치는, 교차시킨 스트라이프모양의 전극의 교점으로 화소를 구성하는 단순매트릭스형과, 각 화소마다 박막 트랜지스터(TFT) 등의 능동소자를 갖추고, 상기 능동소자를 온/오프시키는 액티브 매트릭스형으로 대별된다.

액티브 매트릭스형 액정표시장치는, TFT방식의 액정패널과, 상기 액정패널에 설치한 주사신호선(게이트선)에 주사전압을 공급하는 주사신호선 구동회로(이하, 게이트 드라이버라고도 한다), 마찬가지로 액정패널에 설치한 영상신호선(드레인선)에 영상신호전압을 공급하는 영상신호선 구동수단(이하, 드레인 드라이버라고도 한다), 및 PC 등의 호스트 측으로부터 출력되는 각종 제어신호나 표시데이터를 상기 게이트 드라이버와 드레인 드라이버에 표시용 신호로서 공급하기 위한 표시제어장치나 내부전원회로를 구비하고 있다.

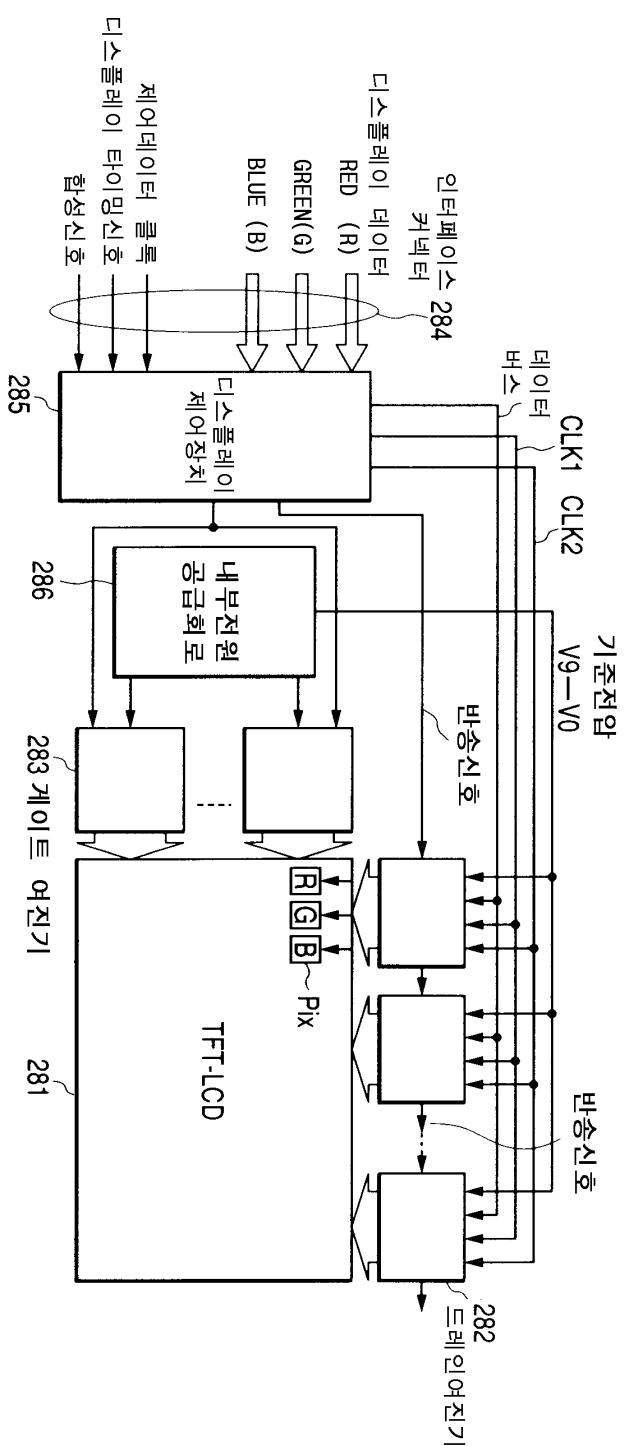

도 24는 본 발명을 적용하는 액정표시장치의 개략구성을 설명하는 블럭도이다. 상기 액정표시장치를 구성하는 액정패널(281)은 박막 트랜지스터형 액티브 매트릭스형 액정패널(TFT-LCD)이며, 그 상변에 복수의 드레인 드라이버(282)와 복수의 게이트 드라이버(283)가 배치되어 있다.

액정패널(281)은, 3색의 서브픽셀(sub-pixel) 적(R), 빨(G), 청(B)을 1화소로 하는, 예를들어  $1024 \times 768$ 의 화소로 구성된다.

PC 등의 호스트(호스트 컴퓨터) 측으로부터 출력되는 적(R), 빨(G), 청(B)의 3색의 표시데이터(영상신호)와, 클록신호, 표시타이밍 신호 및 동기신호로 이루어지는 제어신호는 인터페이스 커넥터(284)를 매개로 하여 표시제어장치(285)에 입력한다.

표시제어장치(285)는 제어신호를 바탕으로 액정패널에 표시시키는 형식의 표시데이터를 생성하고, 이를 데이터버스를 배개로 드레인 드라이버(282)에 공급한다. 또한, 동시에, 표시개시 타이밍클록, 라인클록, 화소클럭 등의 타이밍 신호(캐리 입력, CL1, CL2)를 드레인 드라이버(282)에 공급한다.

또한, 내부전원회로(286)는 표시계조를 작성하기 위한 기준전압(V9~V0)을 생성하여 드레인 드라이버(282)에 공급함과 동시에, 게이트 드라이버(283)에 주사전압(게이트 전압)을 공급한다.

또한, 각 드레인 드라이버(282)는, 소정수의 영상신호선(드레인선)마다 할당되어, 당해 소정수의 카운트 후에 다음 드레인 드라이버에 순서대로 캐리출력을 부여하도록 되어 있다.

드레인 드라이버(282)의 각각은, 표시데이터를 바탕으로 계조전압을 생성하는 계조생성회로와, 생성된 계조전압을 증폭시켜 표시데이터에 대응하는 영상신호전압을 드레인 드라이버(282)에 대응하는 드레인선에 출력하는 증폭회로를 갖추고 있다.

또한, TFT방식의 액정표시장치에 있어서는, 액정측의 잔상(sticking)을 방지하기 위하여 화소전극에 대향 배치되는 대향전극에 인가되는 전압(이하, VCOM)에 대하여, 드레인선에 인가되는 영상신호전압의 극성을 프레임마다 반전시킬 필요가 있다. 이를 실현하는 방법으로서, 화소전극전압의 극성 뿐만 아니라, 대향전극전압의 극성도 변화시키는 VCOM 교류구동과, 대향전극은 고정전위인 채로 화소전극에 인가되는 전압을 크게 변화시키는 도트반전구동이 있다.

또한, 이러한 종류의 액정표시장치에 관한 종래기술을 개시한 것으로는, 예를들어 일본 특허공개 평9-281930호 공보를 들 수 있다.

#### 발명이 이루고자 하는 기술적 과제

최근의 TFT방식의 액티브 매트릭스형 액정표시장치는, 액정패널의 대형화, 고해상도화, 고화질화, 저소비 전력화 되어가는 경향에 있다. 더구나, 필요없는 공간을 없애고, 표시장치로서의 미관을 유지하기 위하여 프레임 부분을 조금이라도 작게 할것이 요구되고 있다.

또한, 시장이 성숙되어 감에 따라, 액정표시장치를 보다 저렴화할 필요가 있게 되었고, 상기한 프레임 부분의 축소를 포함해 드레인 드라이버의 칩면적을 보다 작게 할 것이 요구되고 있다.

또한, 브라운관을 대신하는 큰화면 크기의 표시디바이스로서의 모니터용 액정패널의 보급에 따라, 보다 고해상도이면서 다계조의 표시장치가 요구되고 있다. 종래, 특히 노트형 PC용 액정패널에서는 64계조였던 것이 모니터용 액정패널에서는 256계조가 필수화되어 있다.

해상도에 있어서도, 모니터용 액정패널은 XGA(exended video graphics array)규격에서 SXGA(super XGA) 규격, UXGA(ultra XGA)규격으로 계속 옮겨가며, 액정패널의 전기적 부하는 증가하는 경향에 있다. 한편, 1화소의 표시속도는 일정하기 때문에, 액정패널 1라인분의 계조전압 기록시간은 보다 짧아진다. 또한, 현재 상황에서는 종래와 동등한 휙도를 얻기 위하여 대형화 및 고해상도로 될 수록 고전압의 계조전압을 인가할 필요가 있다.

상기와 같은 상황에서는, 고해상도화, 다계조화, 고전압화는 IC칩 크기의 증대로 이어지므로 비용상승을 초래하게 된다.

이와 같은 상황에서는, 종래의 소위 토너먼트형 디코더방식에서는, 계조수와 동일한 수의 디코드회로가

필요하며, 다계조화에 따른 침크기 증대의 커다란 요인으로 되어 있어, 프레임의 축소가 어렵다고 하는 문제가 있었다. 토너먼트형이라는 용어는 많은 그레이-스케일 전압 중 하나를 선택하는 방식과 많은 경쟁자가 일련의 예선 시합을 거쳐서 우승을 위해 다투는 토너먼트 방식의 중간 정도에 있는 것을 말한다.

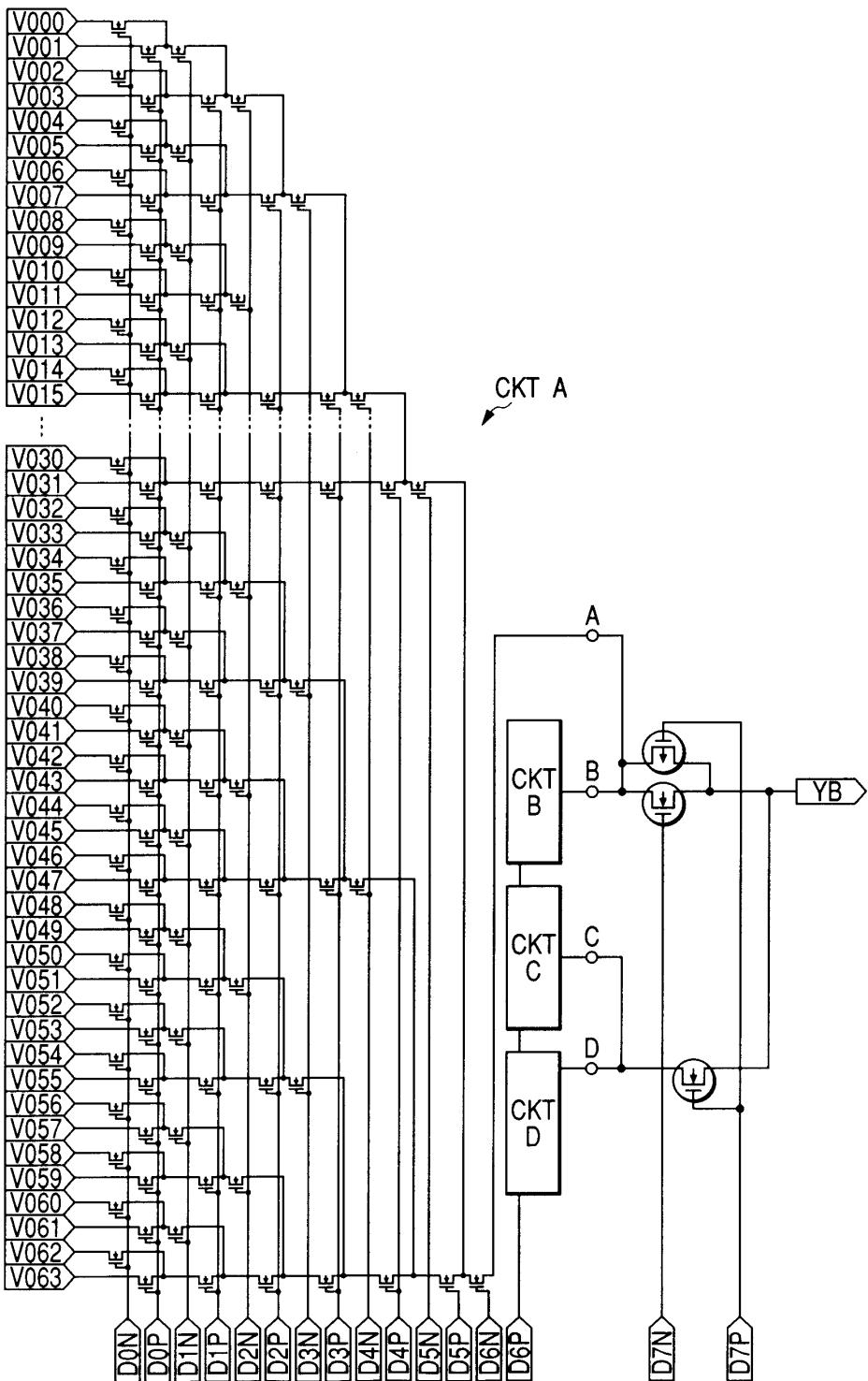

도 25는 종래의 토너먼트형 디코더방식을 이용한 드레인 드라이버의 구성예를 설명하는 저전압회로부의 회로이다. 또한, 도트반전구동에서는, 상기의 저전압회로부와 쌍이 되는 고전압회로부를 필요로 한다. 고전압회로부는, 스위칭소자인 MOS 트랜지스터를, 도 25의 NMOS 트랜지스터 대신에 PMOS 트랜지스터를 이용하여 구성되는 점을 제외하고는, 저전압회로부와 동일한 구성이기 때문에 설명은 생략하기로 한다.

상기 드레인 드라이버의 저전압회로부는, 도 25의 A단자에 접속되는 도시한 회로 CKTA와 동일한 구성의 회로 CKTB, CKTC, CKTD가 각각 B단자, C단자, D단자에 접속되어, 회로 CKTA, CKTB, CKTC, CKTD 각각에 계조전압 V000~V063, V064~V127, V128~V191, V192~V255가 입력되도록 되어 있다.

A단자~D단자에 접속하는 토너먼트형 디코더 CKTA, CKTB, CKTC, CKTD는 동일하기 때문에, 여기서는 A단자에 접속하는 계조전압 V000~V063에 대응하는 토너먼트형 디코더 CKTA만을 설명하기로 한다.

A단자에 접속하는 토너먼트형 디코더 CKTA의 입력단자 D0N, D0P, D1N, D1P, …, D6N, D6P에는 표시데이터가 입력되고, V00, V01, ……V63에는 64개의 계조전압이 입력된다. 또한, NMOS 트랜지스터의 백게이트는 접지(GND)에 접속된다.

그리고, 출력단자(YB)는 음극성측(저전압측)의 드레인선 구동전압을 출력한다.

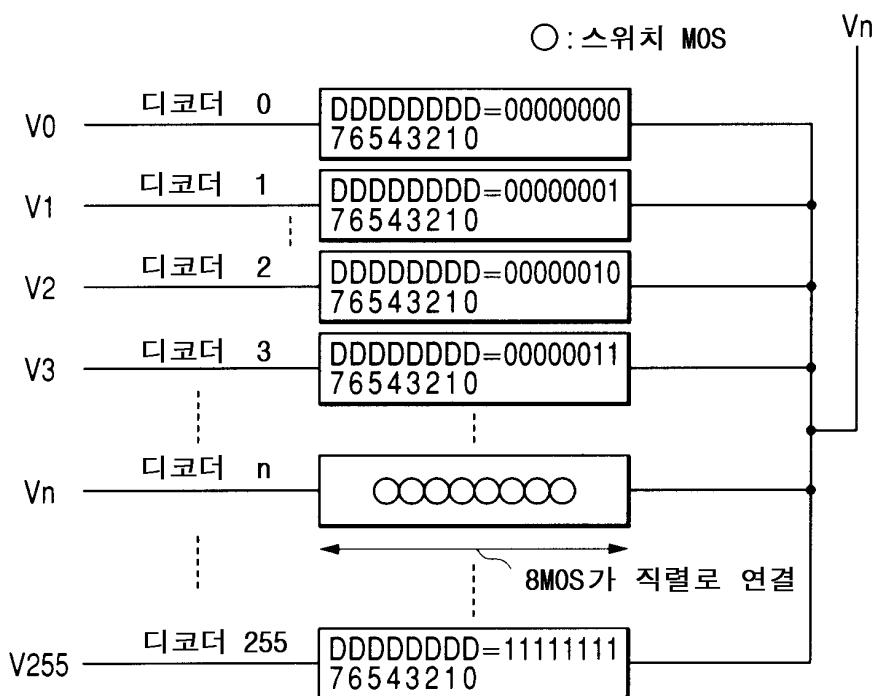

도 26은 토너먼트형 디코더의 전체구성을 설명하는 개략도이다. 도에서,  $V_0 \sim V_{255}$ 는 계조전압, 디코더( $0 \sim 255$ )는 스위칭소자인 MOS 트랜지스터(도에서 ○로 나타낸다) 8개로 구성된다.  $V_n$ 은 출력을 나타낸다.

이와 같은 구성에서는, 8개의 직렬접속 MOS 트랜지스터로 이루어지는 디코드회로가 256개 필요하며, 이들 256개의 디코더회로로는 계조전압 생성회로의 분압회로(러더 저향회로)로부터 256개의 배선(계조전압배선)에서 계조전압을 입력할 필요가 있다.

또한, 액정패널의 고해상도화, 대형화에 따른 액정패널의 부하증대는, 계조전압의 기록부족의 원인으로 되어 고화질화를 저해하는 요인이 된다.

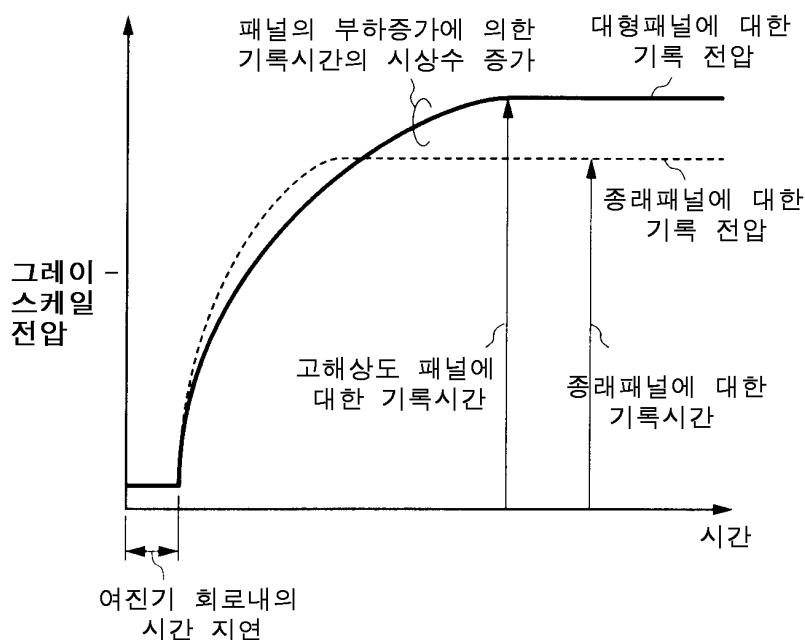

도 27은 계조전압과 기록시간의 관계를 설명하는 설명도이며, 횡축은 기록시간을, 종축은 계조전압을 나타낸다. 도에서, 파선은 종래의 예를들어 공칭 14인치 정도의 SVGA, 64계조표시 액정패널에서의 계조전압과 기록시간의 관계를 나타내고, 굵은 선은 선은 고해상도화, 대형화한 예를들어 공칭 18인치 정도 이상의 XGA, SXGA, 256계조표시 액정패널에서의 계조전압과 기록시간의 관계를 나타낸다.

액정패널을 고해상도화하면 액정패널의 전기적 부하가 증대하고, 기록전압의 시정수가 증대된다. 또한, 화소수가 증가하여도 1프레임의 주기가 변하지 않기 때문에, 계조전압 기록에 사용할 수 있는 시간은 상대적으로 단축된다. 또한, 다계조화에 의하여 표시데이터의 비트수가 늘어나면, 디코더회로의 저항이 증가하고 기록전압의 시정수가 증가한다. 그 결과, 계조전압의 기록부족으로 된다.

본 발명의 목적은, 디코드회로수, 배선수를 줄감하여 칩 크기의 증대를 억제하고, 고해상도이면서 다계조 학과 동시에 표시영역 주위의 프레임을 쉽게 하는 액정표시장치를 제공하는 것에 있다.

본 발명의 다른 목적은, 디코드회로의 온저항의 증대를 억제하여 액정패널의 고화질화를 가능하게 한 액정표시장치를 제공하는 것에 있다.

상기 목적은, 출력앰프회로(이하, 간단히 앰프라고도 한다)만으로 2계조의 전압출력을 생성함으로써 달성된다. 또한, 다계조화에 의한 디코드회로의 온저항의 증가를 억제하고, 칩 내부의 계조전압의 내부지연을 삼각형으로써 달성된다. 상기 물점을 달성하기 위한 본 발명의 대표적인 구성은 기술하면 이하와 같다.

(1) 복수의 화소를 가지는 액정패널과, P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고, 상기 영상신호선 구동회로는, Q개의 서로 다른 계조전압을 공급하는 전원회로와, 상기 표시데이터를 바탕으로 상기 Q개의 서로 다른 계조전압 중에서 선택된 하나의 계조전압값을 가지는 2개의 계조전압, 또는 상기 Q개의 서로 다른 계조전압 중에서 선택된 서로 다른 값의 2개의 계조전압을 선택하여 출력하는, 상기 영상신호선의 각각에 대응하여 설치된 복수의 선택회로와, 상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압 중 어느 하나, 또는 상기 서로 다른 값의 2개의 계조전압으로부터 생성된 상기 서로 다른 값의 2개의 계조전압의 중간값의 계조전압을 바탕으로, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압을 출력하는 복수의 앰프회로로 이루어지는 액정표시장치.

(2) 복수의 화소를 가지는 액정패널과, P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고, 상기 영상신호선 구동회로는, Q개의 서로 다른 계조전압을 공급하는 전원회로와, 상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 복수의 계조전압을 선택하여 출력하는, 각 영상신호선에 대응하여 설치된 복수의 선택회로와, 상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 복수의 계조전압 중 하나의 계조전압, 또는 상기 공급된 복수의 계조전압으로부터 생성된 상기 복수의 계조전압과는 서로 다른 값의 계조전압을 바탕으로, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압을 출력하는 복수의 앰프회로로 이루어지는 액정표시장치.

(3) 복수의 화소를 가지는 액정패널과, P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고, 상기 영상신호선 구동회로는, Q개의 서로 다른 계조전압을 공급하는 전원회로와, 상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 선택된 하나의 계조전압값을 가지는 2개의 계조전압, 또는 상기 Q개의 서로 다른 계조전압 중에서 선택된 서로 다른 값의 2개의 계조전압을 선택하여 출력하는, 상기 영상 신호선의 각각에 대응하여 설치된 복수의 선택회로와, 상기 표시데이터를 바탕으로 상기 복수의 선택회로

로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압이 동일한 값일 때에는 그 계조전압을 전류증폭하고, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압이 서로 다른 값의 2개의 계조전압일 때는 상기 서로 다른 값의 2개의 계조전압으로부터 생성된 상기 서로 다른 값의 2개의 계조전압의 중간값 계조전압을 전류증폭하여, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압으로서 출력하는 복수의 앰프회로로 이루어지는 액정표시장치.

상기와 같은 구성으로 함으로써,  $(M+1)/2$ (총 계조수 M이 홀수인 경우) 또는  $M/2+1$ (총 계조수 M이 짝수인 경우)의 입력전압으로부터 M계조의 출력전압을 생성할 수 있기 때문에, 드레인 드라이버의 회로규모를 줄일 수 있으며, 칩 면적의 축소가 가능하게 되어 액정의 γ특성에 맞는 출력전압을 얻을 수 있으며, TFT액정패널의 저비용화, 액정표시장치의 프레임 협소화를 실현할 수 있다.

또한, 본 발명은 상기의 구성 및 후술하는 실시예의 구성에 한정되는 것이 아니라, 본 발명의 기술적 사상을 벗어나지 않는다면 다양하게 변경할 수 있다.

### 발명의 구성 및 작용

이하, 본 발명의 실시예에 대하여, 실시예의 도면을 참조하여 상세하게 설명하기로 한다.

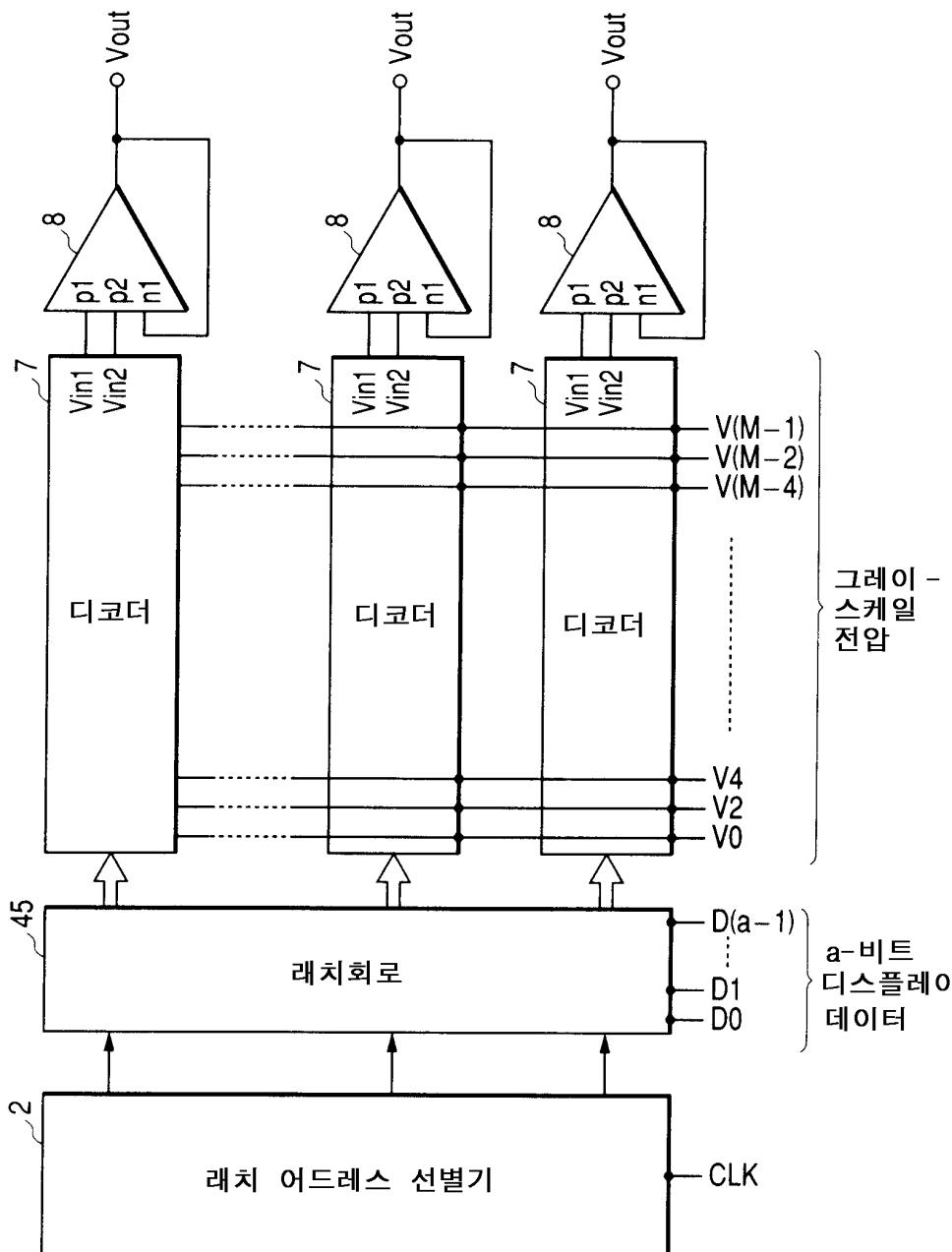

도 1은 본 발명의 제 1 실시예에 관한 TFT방식 액티브 매트릭스형 액정표시장치(이하, 간단하게 TFT 액정표시장치라 부른다)의 드레인 드라이버의 구성을 나타내는 블럭도이다. 여기서는, 예로서 8비트(a=8) 표시데이터에 의한 256계조(M=256), 384출력의 드레인 드라이버로서 설명한다.

상기 드레인 드라이버는, 클록제어회로(1), 래치어드레스 셀렉터(2), 데이터 반전회로(3), 래치회로(1)(4), 래치회로(2)(5), 계조전압 생성회로(6), 디코더(계조전압 선택회로)(7), 및 출력앰프회로(8)로 구성된다. 또한, 클록 및 제어신호로서, 회선 클록(CL1), 화소 클록(CL2), 프레임 인식신호(FRM), 내부회선 계수회로를 위한 제어신호(LC), 이네이블 스타트 펄스(EI01, EI02), AC 구동을 위한 제어신호(M), 방향전환 제어를 위한 신호(SHL), 데이터 극성 역전압을 위한 제어신호(POL1, POL2)가 있고, 동작전압에는 고압회로를 위한 공급전압(VLCD), 저압회로를 위한 공급전압(VCC), 고압 및 저압회로를 위한 접지(GND1, GND2)가 각각 있다.

래치회로(1)(4)와 래치회로(2)(5)는, 8비트(256계조) × 384개로 구성되며, 디코더(7)는 384개의 디코드 데이터를 출력하고, 또한 출력앰프회로(8)는 384개의 표시데이터(Y1~Y384)를 출력한다.

본 실시예에서는, 계조기준전압(V0~V8, V9~V17)을 바탕으로 계조전압 생성회로(6)에 의하여 계조전압으로서 양극성 측 129계조, 음극성 측 129계조를 침내부에서 각각 독립적으로 생성하고, 이를 디코더(7)에 공급하는 양극성 비대칭 전압구동방식(positive-negative polarity asymmetric voltage drive system)을 도입하고 있다. 또한, 계조전압으로서 양극성 측 129(=128+1) 계조, 음극성 측 129(=128+1) 계조를 생성시키는 이유는, 출력앰프회로의 전압합성에 의하여 당해 앰프회로만으로 2계조를 생성하기 때문에, 최종계조는 전압합성에 의하여 생성하게 된다. 이는 이를 합성하기 위한 계조전압을 하나 추가하여(256계조/2)+1=129계조의 전압을 필요로 하기 때문이다.

입력표시데이터(D57~D50, D47~D40, D37~D30, D27~D20, D17~D10, D07~D00)는 데이터 반전회로(3)를 통해 래치회로(1)(4)에 입력되고, 화소클록(CL2)에 의해 제어되는 래치 어드레스 셀렉터(2)에 의해 래치(보지)된다.

래치회로(1)(4)에 보지된 표시데이터는, 액정패널의 1주사선에 동기한 라인클록(CL1)에 의해 래치회로(2)(5)로부터 디코더(7)에 입력한다. 또한, 이하에서는, 디코더는 디코더회로라고도 칭한다.

상기 디코더(7)는, 입력한 표시데이터에 대응하여 계조전압 생성회로(6)에서 생성된 계조전압을 선택하고, 출력앰프회로(8)에 계조전압을 입력한다. 출력앰프회로(8)는 입력된 계조전압을 전류증폭하여 액정패널의 영상신호선(드레인선)에 입력하는 드레인 드라이버 출력 Y1~Y384를 생성하고, 상기 출력으로 화소에 전압을 기록한다.

도 2 및 도 3은, 본 실시예의 드레인 드라이버의 내부회로의 설명도이고, 도 1과 동일한 기능부분에는 동일한 부호를 붙이고 있다. 도에서, 참조번호 45는 도 1에 있어서의 래치회로(4)와 5, 8a는 저전압 전용회로, 8b는 고전압 전용회로, 9는 레벨시프터회로, 10은 표시데이터 멀티플렉서, 11은 출력선택회로(출력멀티플렉서)를 나타낸다.

여기서, 도트반전 구동방식의 경우, 도 2와 도 3에 나타낸 바와 같이, 인접출력단자간에서 음극성 측(저전압측), 양극성 측(고전압측)을 교대로 출력하는 것을 이용하여, 저전압 전용회로(8a)와 고전압 전용회로(8b)의 각각을 출력단자의 수만큼 갖출 뿐 아니라, 저전압 전용회로(8a)와 고전압 전용회로(8b)의 각각을 출력단자의 수의 1/2만큼 가짐으로써 침크기의 축소를 꾀할 수 있다.

또한, 도트반전구동으로 하기 위하여, 저전압 전용회로(8a)와 고전압 전용회로(8b)에 표시데이터를 바꾸는 표시데이터 멀티플렉서(MPX)(10)와 출력멀티플렉서(11)를 저전압 전용회로(8a)와 고전압 전용회로(8b)의 전후로 가지고 있다.

래치회로(45)와 레벨시프터회로(9)는, 저전압 전용회로와 고전압 전용회로 모두 동일한 회로를 이용할 수 있다. 또한, 디코더회로(7)는 침크기의 축소를 위하여 저전압 전용회로(8a)와 고전압 전용회로(8b)에서 전용회로를 이용하고 있다. 상기 회로는, 도 1의 계조전압 생성회로(6)로부터 공급되는 258개의 계조전압 중에서 동일한 계조의 경우를 포함하는 2개의 계조전압을 선택할 수 있는 회로로 하고 있는 점이 특징이다.

도 4는 도 2 및 도 3에 나타낸 본 실시예의 드레인 드라이버의 동작을 설명하는 블럭도이다. 디코더회로(7)에는 표시데이터(8비트면 256계조, 6비트면 64계조→여기서는 8비트면 256계조로 설명) 중 하나 걸러의 계조의 전압값이 입력된다.

여기서, 총 계조수 M이 홀수인 경우에는, 단순히 하나 걸러로 하는 것이 좋지만, 짝수인 경우(통상적으로

는 짹수)에는 최종계조를 추가로 입력할 필요가 있다. 따라서, 입력계조는, 총 계조수 M이 홀수일 때에는 V0, V2, V4, …, V(M-3), V(M-1)의 (M+1)/2개 ; 총 계조수 M이 짹수일 때, V0, V2, V4, …, V(M-4), V(M-2), V(M-1)의 M/2+1개로 된다.

디코더(7)는 2개의 출력(Vin1, Vin2)을 가지고, 이 출력을 출력앰프회로(8)의 양입력(Vp1, Vp2)에 입력한다. 출력앰프회로(8)는 상기 입력에 따라 Vout를 출력한다.

도 5A 및 도 5B는 출력앰프회로의 구체예를 설명하는 설명도이고, 도 5A는 종래의 출력앰프회로, 도 5B는 본 실시예에서 사용하는 출력앰프회로이다. 도 5A의 출력앰프회로에서는, 입력(Vp1)을 전류증폭하여 출력(Vout)을 생성한다. 즉, 하나의 입력에 대하여 하나의 출력을 가진다.

이에 대해, 도 5B에 나타낸 바와 같이 본 실시예의 출력앰프회로는, 입력측의 MOS 트랜지스터를 2분할하여 2개의 입력(Vp1, Vp2)에 대하여 출력(Vout)을 얻도록 하고 있다. 출력(Vout)은, 입력(Vp1)과 입력(Vp2)이 모두 동일한 계조전압(예를들어 V2)인 경우에는, 출력(Vout)은 V2로 되고, 입력(Vp2)과 입력(Vp2)이 인접한 계조전압(예를들어, V0와 V2)이면, 출력(Vout)은 상기 2개의 전압을 합성한 중간의 전압 V10이 된다.

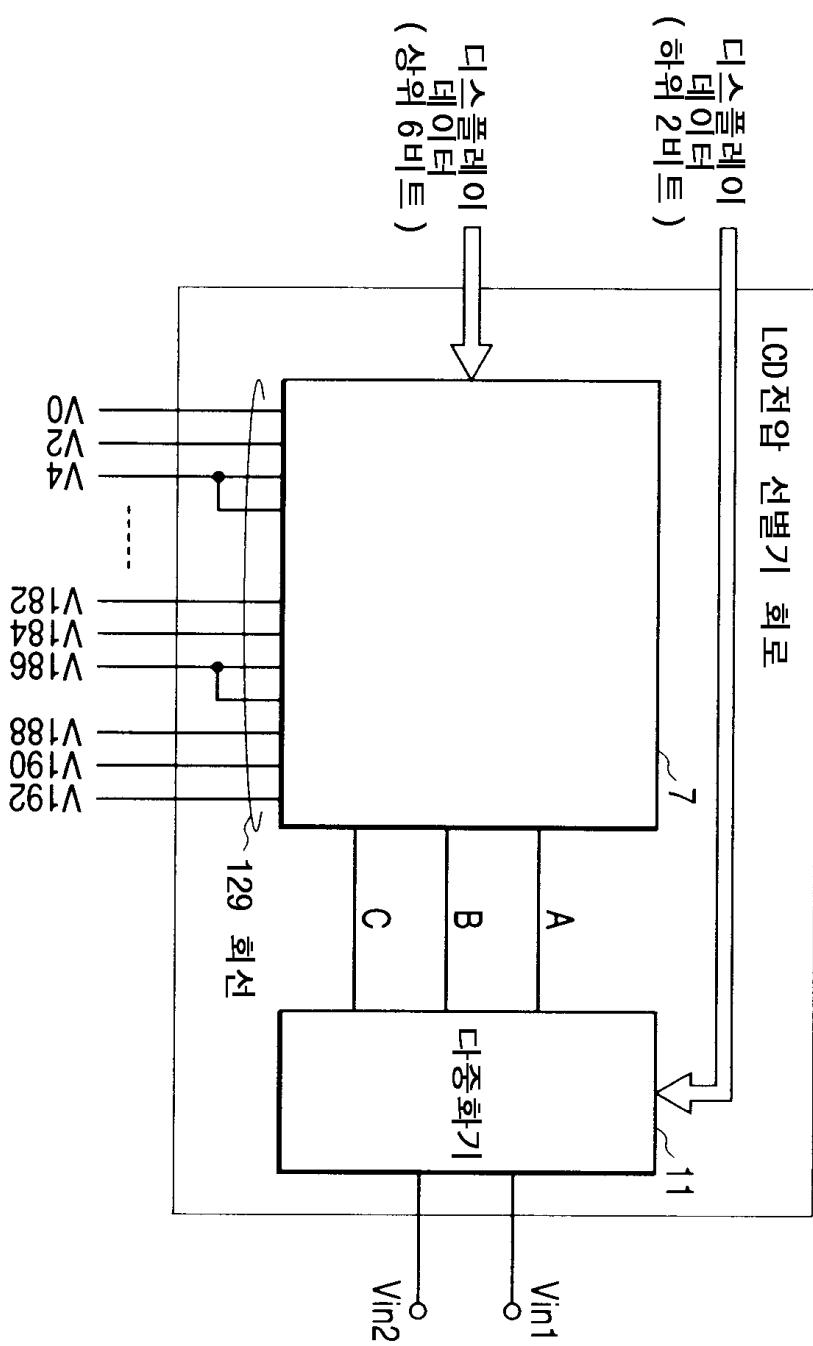

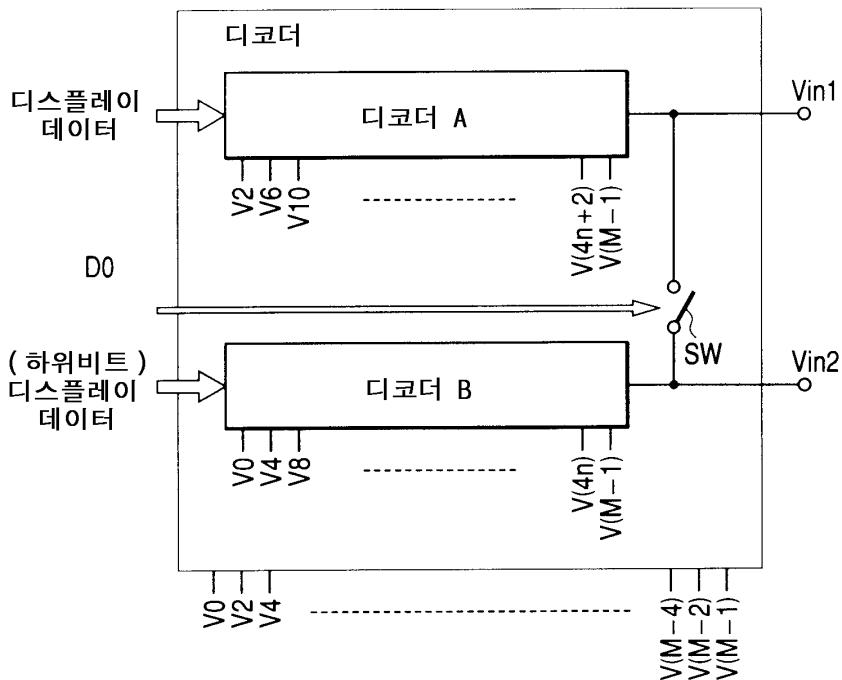

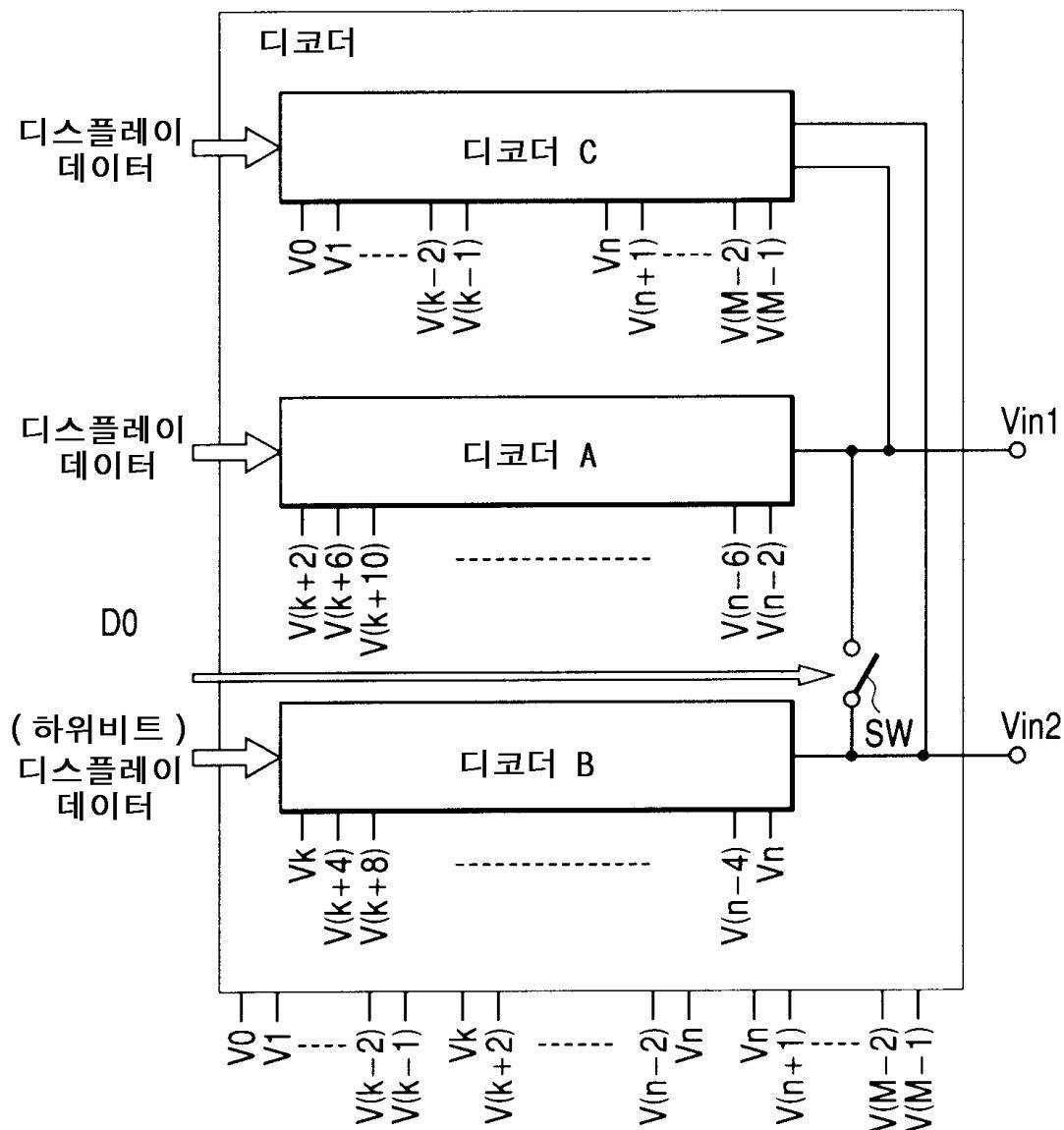

도 6은 본 실시예에 있어서의 계조전압 선택회로의 내부구성을 설명하는 블럭도이고, 계조전압 선택회로는 디코더(7)와 멀티플렉서(11)로 구성된다. 디코더(7)에서는 표시데이터의 상위 6비트에 의하여, 입력된 129 계조 중에서 인접하는 3계조분의 계조전압 A, B, C를 선택하고, 이를 멀티플렉서(11)에 공급한다. 멀티플렉서(11)는 표시데이터의 하위 2비트에 의하고, A, B, C의 계조전압으로부터 1개 혹은 2개의 계조전압을 선택하여 Vin1, Vin2를 출력한다.

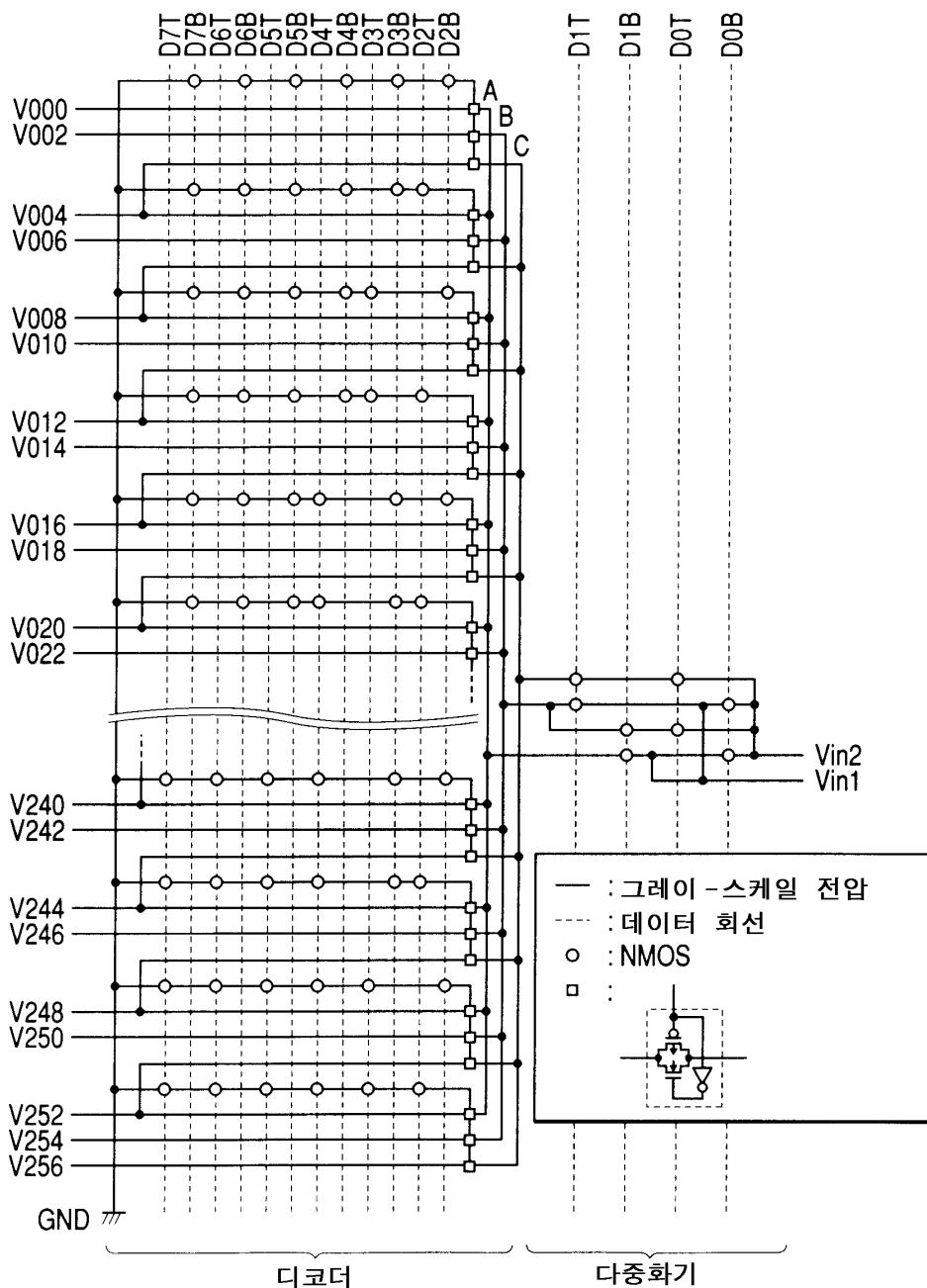

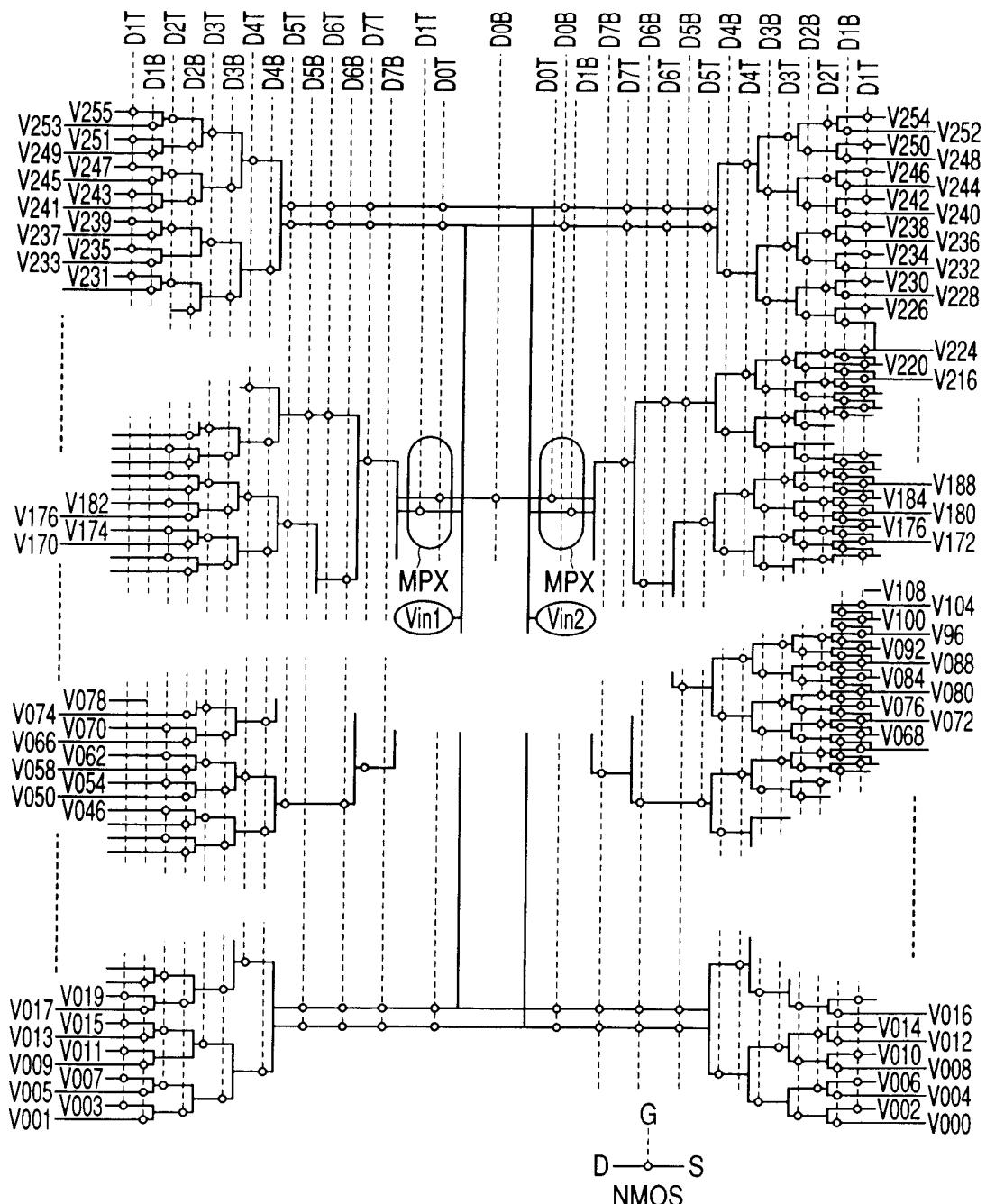

도 7은 도 6에 나타낸 계조전압 선택회로의 구체예를 설명하는 회로도이다. 상기 계조전압 선택회로는 저전압측(음극성측)의 액정전압 선택회로이며, NMOS 트랜지스터만으로 구성되어 있다. 도에서, ○표시로 나타낸 것이 NMOS 트랜지스터를 나타낸다.

또한, 고전압측(양극성측)의 액정전압 선택회로는, 도 7의 입력표시데이터(D2B, D2T, …, D7B, D7T)의 'B'와 'T'를 바꾸어, NMOS 트랜지스터를 모두 PMOS 트랜지스터로 하고, 디코더 블럭의 MOS 트랜지스터의 소스전위를 Vss로 한 것으로 된다(도시는 생략한다).

도 7의 회로동작을 표 1에 나타내었다. 또한, 표 1~표 4는 명세서의 마지막 부분에 정리하여 기재되어 있다.

표 1에서, '계조전압'은 표시데이터에 대응한 계조전압, '디코더입력'은 본 실시예에서 디코더에 입력되는 계조전압, '디지털 입력비트'는 드레인 드라이버에 입력되는 표시데이터(8비트, 256계조), '멀티플렉서 입력전압'은 '디지털 입력비트'의 상위 6비트에 의하여 결정하는 3개의 인접하는 계조전압(각각이 도 6, 도 7에 나타낸 A, B, C의 배선으로 나뉘어진다), '멀티플렉서 선택전압'은 '디지털 입력비트'의 하위 2비트에 의해 상기 (Vin1, Vin2)에 인접되는 계조전압이다.

본 실시예에 의하여, (M+1)/2(총 계조수 M이 홀수), 또는 M/2+1(총 계조수 M이 짹수)의 입력전압으로부터 M계조의 출력전압을 생성할 수 있으며, 칩 면적의 축소가 가능하게 되고, 또한 칩 면적을 증가시키지 않고도 액정의 γ특성(도 20에서 후술)에 맞는 출력전압을 얻을 수 있기 때문에, 액정패널의 저비용화와 액정표시장치의 프레임 협소화를 실현할 수 있다.

따라서, 도 25에서 설명한 토너먼트형 디코더를 이용한 경우와 비교하여, 회로규모를 대폭 줄일 수 있음과 동시에, 계조전압 배선수도 256개에서 192개로 줄일 수 있다.

도 8은 종래의 토너먼트형 디코더를 이용한 경우의 출력경로의 설명도이고, 도 9는 본 실시예의 디코더에 있어서의 출력경로의 설명도이다. 도 8에 나타낸 종래의 디코더에서는, 선택된 계조전원은 8개의 직렬 MOS 트랜지스터를 통하여 출력앰프(도에서 버퍼앰프)에 출력한다.

이에 대해, 도 9에 나타낸 본 실시예의 디코더회로에서는, 3개의 직렬접속된 MOS 트랜지스터를 통해 출력앰프에 입력된다. 이로 인해, 디코더를 구성하는 MOS 트랜지스터의 모든 온저항(총 온저항)은 도 8에 비해 크게 줄어들고, 상기 도 27에서 설명한 드라이버 내부의 지연시간이 줄어든다. 즉, 계조전압의 기록부족을 억제할 수 있다.

다음으로, 다계조화, 고전압화에 따른 표시데이터의 디코드회로의 증가를 억제하고, 칩 크기의 증대를 억제하여 보다 저렴한 다계조 드레인 드라이버를 실현하고, 액정표시장치의 프레임 협소화와 저가격화를 가능하게 한 제 2 실시예에 대하여 설명하기로 한다.

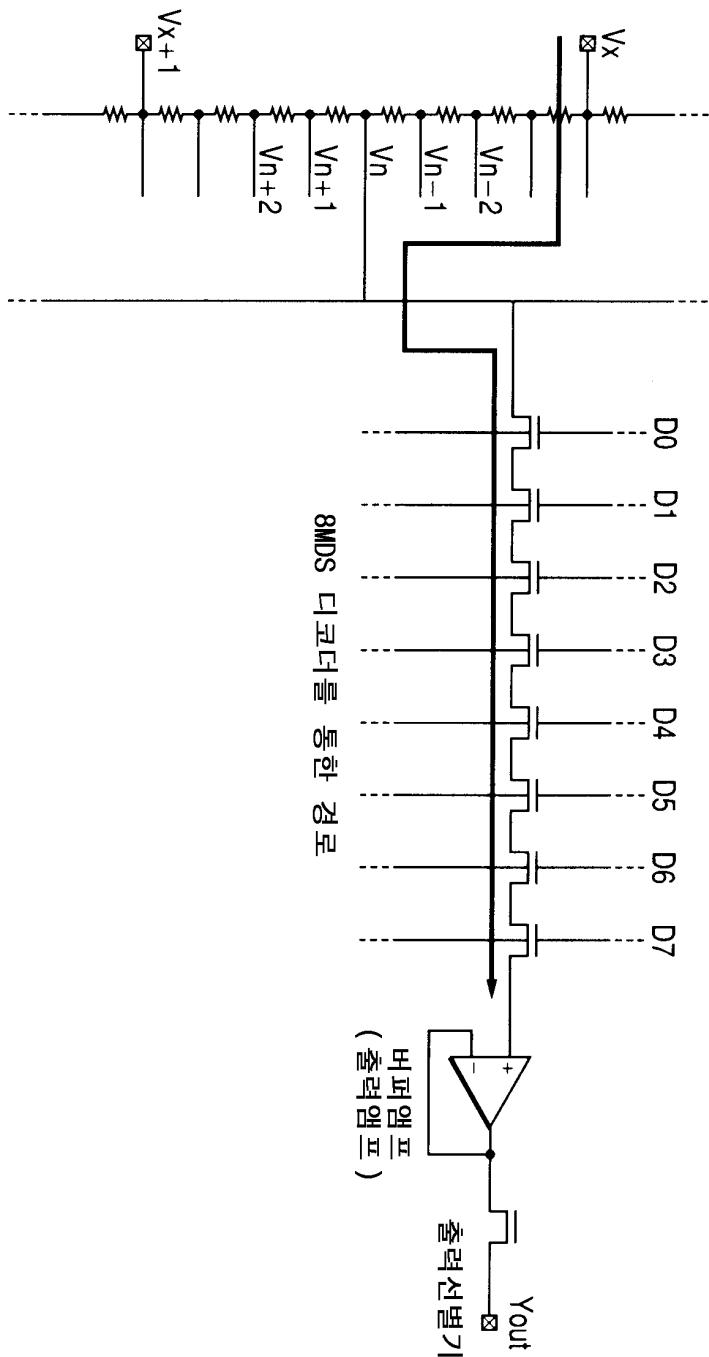

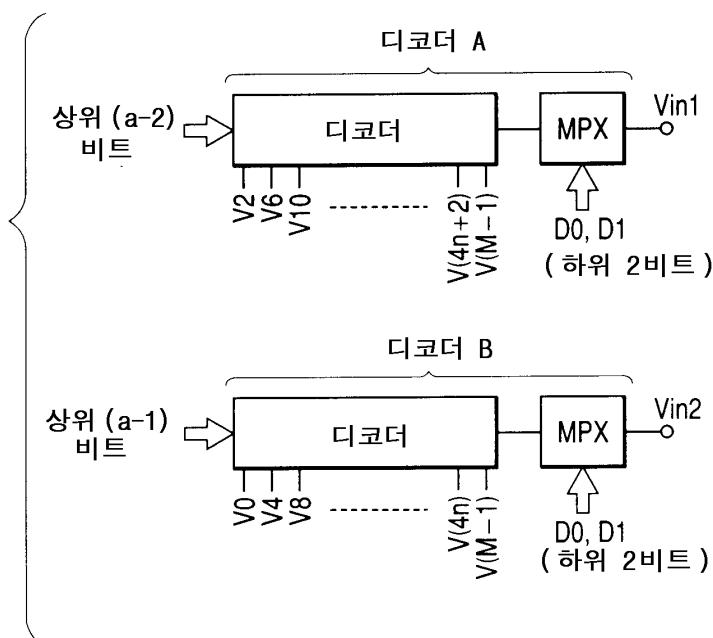

도 10은 디코드회로에서 다계조화를 실현하는 드레인 드라이버의 구성을 설명하는 개략도이다. 본 실시예는, 상기한 2입력의 출력앰프회로를 사용하는 것을 전제로 하고, 입력 8비트를 6비트와 2비트로 분할하여, 6비트의 디코드에 토너먼트방식의 디코더(도에서는 토너먼트로 표기)를 이용하였다.

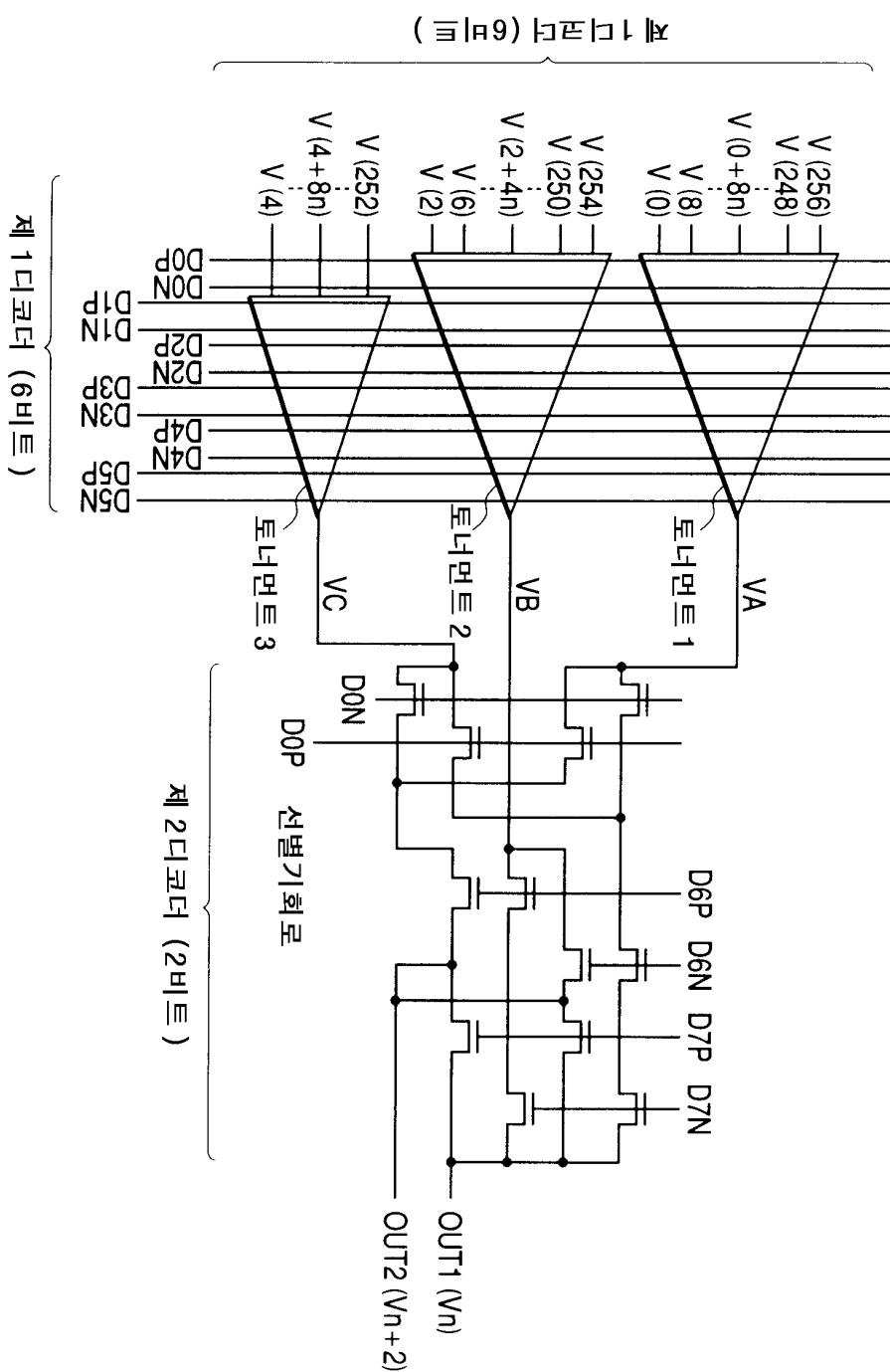

도 10에 있어서, 8비트의 표시데이터에 대하여, 6비트(D0P, D0N, D1P, D1N, D2P, D2N, D3P, D3N, D4P, D4N, D5P, D5N)에 의한 입력계조를 다음 3개의 블럭(A, B, C)으로 분할한다. 즉, 0, 8, …+8n, …, 248, 256계조를 토너먼트 1(A디코더)로 디코드하고, 2, 6, 2+4n, …+250, 254계조를 토너먼트 2(B디코더)로 디코드하고, 4, 4+8n, …+252계조를 토너먼트 3(C디코더)으로 디코드한다. 토너먼트 1, 토너먼트 2 및 토너먼트 3으로 제 1 디코더(첫번째 디코더)를 구성한다.

제 1 디코더의 출력 VA, VB, VC은 D0N, D0P를 절환신호로 하는 선택회로를 통하여 2비트(D6P, D6N, D7P, D7N)의 제 2 디코더(두번째 디코더)에 입력되어, 2개의 출력 OUT1(Vn), OUT2(Vn+2)을 얻는다. 선택회로는 3개의 블럭의 출력 VA, VB, VC의 각각으로부터 하나의 출력을 선택하여 제 2 디코더에 입력하고, 2개의 출력 OUT1(Vn), OUT2(Vn+2)을 얻는다. 상기 2개의 출력 OUT1(Vn), OUT2(Vn+2)은 상기 제 1 실시예에서 설명한 2입력의 출력앰프회로(8)에 입력된다.

도 11은 본 실시예(도 10)에 있어서의 제 1 디코드회로를 더 설명하는 전체구성도이다. 제 1 디코더는, 상기 A디코더, B디코더, C디코더에 저항분할회로(러더저항)로부터의 계조전압을 입력한다. A디코더와 B디

코더는 6비트의 동일한 구성이며, 각각 계조전압 0~m~33, 1~n~64가 입력된다. C디코더는 A디코더와 B디코더의 절반규모(5비트)이며, 러더저항으로부터 계조전압 1~32가 입력된다.

A디코더로부터는  $V(0+8n)$ ( $n=0, 1, 2, 3, \dots$ )의 계조전압이 출력 A(VA)로서 출력되고, B디코더로부터는  $V(2+4n)$ ( $n=0, 1, 2, 3, \dots$ )의 계조전압이 출력 B(VB)로서 출력되고, C디코더로부터는  $V(4+8n)$ ( $n=0, 1, 2, 3, \dots$ )의 계조전압이 출력C(VC)로서 출력된다.

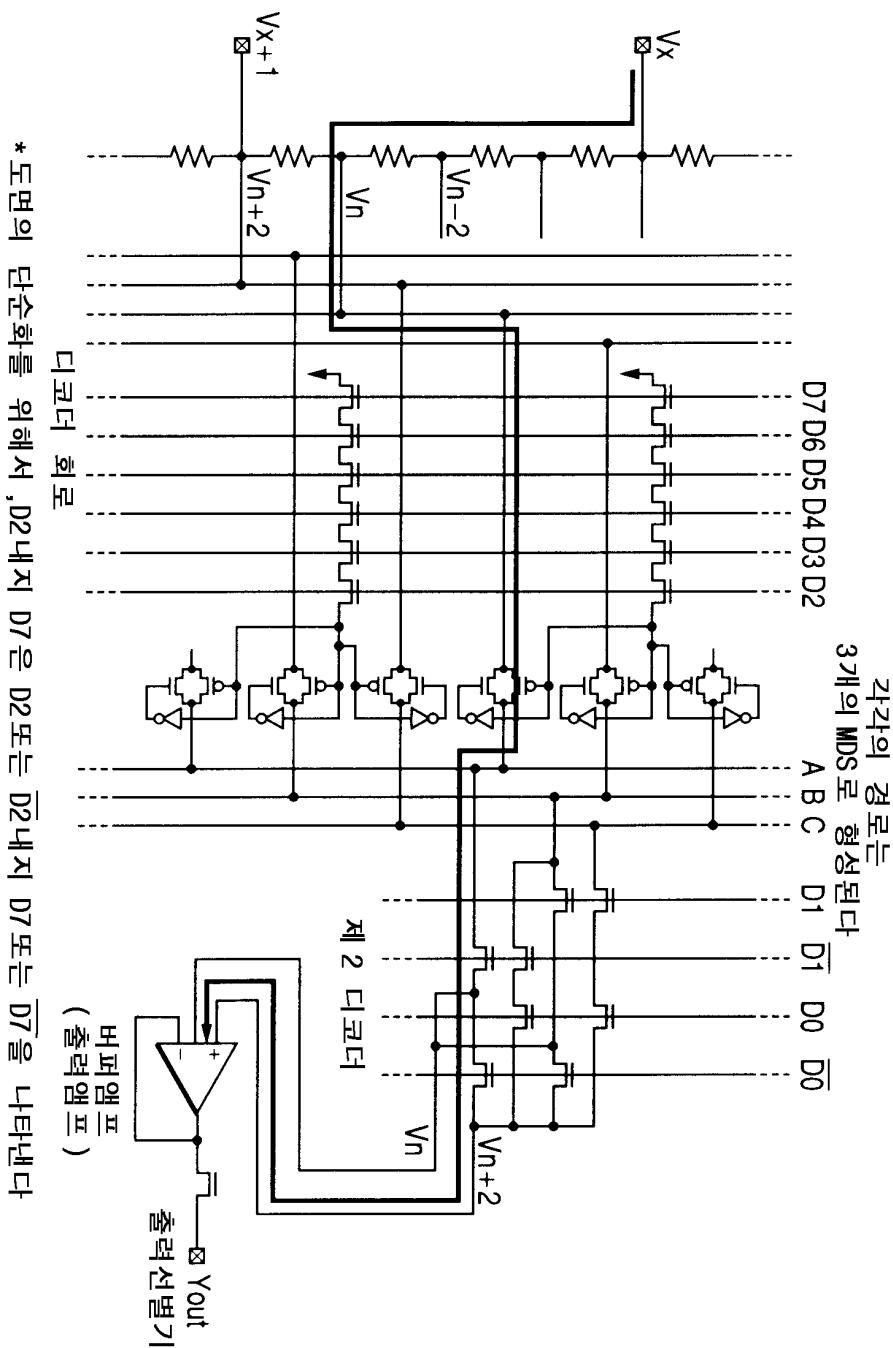

도 12는 도 11에 있어서의 제 1 디코더의 MOS 구성의 모식적 설명도이다. A디코더에 입력하는  $V(0+8n)$ 의 계조전압은, 6개의 MOS 트랜지스터를 통하여 표시데이터 D7, D6, D5, D4, D3, D2에서 선택되어 출력 A(VA)가 된다. 마찬가지로, B디코더에 입력하는  $V(2+4n)$ 의 계조전압은, 6개의 MOS 트랜지스터를 통하여 표시데이터 D7, D6, D5, D4, D3, D2에서 선택되어 출력 B(VB)로 된다. C디코더에 입력되는  $V(4+8n)$ 의 계조전압은 5개의 MOS 트랜지스터를 통하여 표시데이터 D7, D6, D5, D4, D3에서 선택되어 출력 C(VC)로 된다.

도 13은 도 10에 있어서의 제 2 디코더의 MOS 구성의 모식적 설명도이다. 도 10에서 설명한 바와 같이, 제 1 디코더로부터 입력하는 A(VA), B(VB), C(VC)는, 표시데이터 D2(DON), 반전 D2(DOF : 도에서는 D2의 상부에 획선을 그어 나타낸다. 이하, 동일)를 선택신호로서 선택받아, 표시데이터 D1, 반전 D1, D0, 반전 D0를 디코드하여 출력  $V_n(OUT1)$ ,  $V_{n+2}(OUT2)$ 를 출력한다.

도 14는 도 10에 있어서의 토너먼트 1의 구체적인 회로도이고, 도 15는 동 토너먼트 3의 구체적인 회로도이다. 도 14에 있어서, 토너먼트 1에서는, 계조전압  $V(0+8n)(V00, V08, V16, \dots, V248, V256)$ 을 입력하고, 표시데이터 DOP, DON, D1P, D1N, D2P, D2N, D3P, D3N, D4P, D4N, D5P, D5N을 디코드하여 출력 VA를 얻는다. 마찬가지로, 토너먼트 2에서는, 계조전압  $V(2+4n)(V02, V06, V10, V14, \dots, V250, V254)$ 을 입력하고, 표시데이터 DOP, DON, D1P, D1N, D2P, D2N, D3P, D3N, D4P, D4N, D5P, D5N을 디코드하여 출력 VB를 얻는다.

토너먼트(3)에서는, 계조전압  $V(4+8n)(V04, V12, V20, \dots, V244, V252)$ 를 입력하고, 표시데이터 DOP, DON, D1P, D1N, D2P, D2N, D3P, D3N, D4P, D4N, D5P, D5N을 디코드하여 출력 VC를 얻는다.

본 실시예에 의하여, 종래의 8MOS 디코더 256개로부터 제 1 디코더의 6MOS 디코더 64개 + 6MOS 디코더 33개 + 5MOS 디코더 32개 + 제 2 디코더로 줄일 수 있다. 또한, 제 1 디코더의 입력수, 즉 계조전압 배선수는 128개로 구성할 수 있다.

따라서, 256계조화 등으로 다계조화한 경우의 드레인 드라이버의 칩 크기의 증가를 억제하고, 액정패널의 고화질화, 액정표시장치의 프레임 협소화를 달성할 수 있다. 또한, 디코더회로의 모든 온저항을 낮출 수 있게 되어, 계조전압출력의 지연시간의 증대를 억제하고, 액정패널의 고해상도화, 고속화를 달성할 수 있다.

도 16은 본 발명의 제 3 실시예에 관한 TFT방식 액티브 매트릭스형 액정표시장치(TFT 액정표시장치)의 드레인 드라이버의 구성을 나타내는 블럭도이다. 본 실시예에서는, 표시데이터를 a비트의 D0~D(a-1), 계조전압을 V0, V2, V4, ..., V(M-4), V(M-2), V(M-1)로서 설명하기로 한다.

상기 드레인 드라이버는, 래치어드레스 셀렉터(2), 래치회로(45), 디코더(7), ..., 출력앰프회로(8), ...로 구성된다. 상기한 바와 같이, 입력계조는,

총 계조수 M이 짹수일 때, V0, V2, V4, ..., V(M-3), V(M-1)의  $(M+1)/2$ 개 ;

총 계조수 M이 짹수일 때, V0, V2, V4, ..., V(M-4), V(M-2), V(M-1)의  $M/2+1$ 개가 된다.

도 17은 도 16에 있어서의 디코더의 상세한 사항을 설명하는 블럭도이다. 상기 도에서는, 도 16에 나타난 계조를  $(4n+1)$ 번째( $n=0, 1, 2, 3, \dots$ )의 계조가 입력되는 디코더(B)의 출력을  $Vin_2$ ,  $(4n+3)$ 번째 ( $n=0, 1, 2, 3, \dots$ )의 계조가 입력되는 디코더(A)의 출력을  $Vin_1$ 로 한다.

또한, 도 18은 도 17의 동작의 설명도이다. 이하, 도 17의 회로를 도 18과 함께 설명하기로 한다.

$Vin_1$ 과  $Vin_2$ 와 함께 동일한 계조전압(예를들어 V2)을 출력하고자 하는 경우에는, 디코더(A)로 계조전압(V2)을 선택하고, 디코더(B)는 오프(고임피던스상태)로 하여, LSB(도 17에서는 D0)에 의하여 제어하는 스위치(SW)에 의해  $Vin_1$ 과  $Vin_2$ 를 단락시킨다. 이로 인해, 출력  $Vin_1$ 과  $Vin_2$ 는 모두 V2로 된다.

$Vin_1$ 과  $Vin_2$ 에 인접한 계조전압(예를들어, V0와 V2)을 출력하고자 하는 경우에는, 디코더(A)로 V2를 선택하고, 디코더(B)로 V0을 선택한다. 이로 인해, 출력  $Vin_1$ 에는 V2를,  $Vin_2$ 에는 V0을 출력시킬 수 있다.

표 2는, 최하위의 계조를 나타내는 표시데이터의 모든 비트를 '0'이라고 하였을 때의, 표시데이터, 디코더 선택전압, 및 출력앰프회로의 출력전압(표 2에서는 앰프출력)의 관계를 예로서 나타내고 있다. 물론, '0'과 '1'을 바꾸어도 표시데이터와의 관계가 성립한다. 또한, 여기서는, 256계조를 예로서 설명하고 있다.

TFT형 액정패널의 드레인 드라이버로는, 상기 표시데이터에 대응한 계조전압을 출력할 필요가 있다. 따라서, 출력앰프회로에서 합성하는 계조를 출력하는 경우에는, 드레인 드라이버에 입력되는 표시데이터와 다른 계조를 드라이버 내에서 선택할(2값) 필요가 있다.

예를들어, 표시데이터 V7을 표시하고자 하는 경우,

입력되는 표시데이터 V7 : 00000111

선택할 계조전압 V6 : 00000110

V8 : 00001000

으로 된다.

다음으로, 디코더(A, B)의 동작을 설명하기로 한다.

우선,  $(4n+3)$  번째의 계조전압 V $(4n+2)$ 를 출력하는 디코더(A)에 있어서, 예를 들어 계조전압 V6을 선택할 필요가 있는 것은, 표시데이터가 계조전압 V5, V6 또는 V7에 대한 것일 때이며, 이들 표시데이터는 하기와 같이 된다.

V6 : 00000110

V5 : 00000101

V7 : 00000111

상기 V6, V5 및 V7에 있어서와 같이, 표시데이터의 하위 2비트가 '00'이 되었을 때에는, 상기 입력된 표시데이터의 상위 6비트만을 사용하여 디코더(A)에 있어서 V6을 선택할 수 있다.

아울러, 상기의 경우와는 달리, 입력된 표시데이터의 하위 2비트가 '00'일 때에는,  $(4n+1)$  번째의 계조전압 VC를 출력하는 다른 디코더(B) 쪽에서부터 계조전압이 출력되기 때문에 디코더(A) 쪽은 OFF로 된다.

즉, 디코더(A)는 하위 2비트가 '00'일 때 외에 상위 6비트만으로 정해지는 출력을 수행하는 회로구성이라고 할 수 있다.

한편,  $(4n+1)$  번째의 계조전압 V $(4n)$ 를 출력하는 디코더(B)에 있어서, 예를 들어 계조전압 V8을 선택할 필요가 있는 것은, 표시데이터가 계조전압 V7, V8 또는 V9에 대한 것일 때이며, 이들 표시데이터는 하기와 같이 된다.

V7 : 00000111

V8 : 00001000

V9 : 00001001

$(4n+1)$  번째의 계조전압 V $(4n)$ 에 대응하는 표시데이터는 자리올림된 비트구성에 해당하기 때문에, 하위 측 비트구성이 하나 앞의 계조에 대한 비트구성과 크게 다르다(예를 들어, V7, V8의 표시데이터의 하위 4비트).

따라서, 표시데이터의 상위 6비트를 사용하여 V8만을 선택할 수는 없다.

예를 들어, V7의 상위 6비트와,  $(4n+1)$  번째의 계조군에 속하고, 계조전압 V7의 직전의 계조인 V4의 상위 6비트는, 모두 '000001'로 되고, 계조전압 V4까지도 선택해 버려 V4와 V8(V7을 표시하고자 하여 V8을 선택하고 있는 상태에 있어서)이 단락되어 표시불량이 된다.

따라서, 표시데이터의 상위 7비트를 사용할 필요가 있다. 상위 7비트를 사용함으로써, 표시데이터가 계조전압 V7, V8 또는 V9에 대한 것일 때,  $(4n+1)$  번째의 계조군 중에서 계조전압 V8만을 선택할 수 있다.

그 때, 하위 2비트가 '10'일 때에는 디코더(B)를 오프로 한다. 하위 2비트가 '10'일 때에는  $(4n+3)$  번째의 계조전압이 디코더(A)로부터 출력되기 때문에,  $(4n+1)$  번째의 계조전압을 출력하는 디코더(B)는 오프로 할 필요가 있다.

즉, 디코더(B)는 하위 2비트가 '10'일 때 외에 하위 7비트만으로 정해지는 출력을 수행하는 회로구성이라고 할 수 있다.

또한, 표 2의 Vin1, Vin2는 조합이기 때문에 순서가 다르다(도면과 표 2에서의 Vin1, Vin2의 대응이 역으로 되어 있는 부분이 있다).

도 19는 도 18을 구체화한 실제의 회로구성을 설명하는 회로도이고, 저전압측(음극성측) 디코더를 나타낸다. 또한, 고전압측(양극성측) 디코더는, 입력하는 표시데이터의 T와 B를 바꾸어, NMOS 트랜지스터를 모두 PMOS 트랜지스터로 함으로써 구성된다. 또한, 도 19는 부분만을 나타내고 있다.

도 20A~20C는, 드레인 드라이버의 동작특성의 설명도이다. 도 20A는 액정인가전압과 휘도와의 관계(액정의 특성), 도 20B는 드레인 드라이버의 출력전압특성, 도 20C는 계조단계와 휘도의 관계를 나타낸다. 도 20B에 나타난 바와 같이, 드레인 드라이버의 출력은 계조단계에 대하여 비선형이다.

도 20B에 나타난 바와 같이, 후술하는 차동앰프를 이용한 출력앰프회로에 2개의 입력을 인가하여 이들 간의 중간전압을 출력하는 경우, 2개의 입력값의 전압차가 크면 중간의 전압으로 되지 않고, 한쪽의 전압값으로 치우치는 특성을 가지고 있다.

V0입력시의 출력앰프회로의 차동부 전류 :  $(1/2) \cdot \beta (V0 - V_{th})^2$ , V2입력시의 출력앰프회로의 차동부 전류 :  $(1/2) \cdot \beta (V2 - V_{th})^2$ 이며,  $V_{th}$ 를 거의 동일하게 하면, V0과 V2의 차가 커지면 2제곱의 차도 커지게 되므로, 예를 들어  $V2 > V0$ 로 하면 2개의 입력 쌍방에 V2를 입력하였을 때의 전류값에 가까워지기 때문에, 출력되는 합성전압은 V2에 가까워지지만, 차가 작은 경우에는 거의 중간값이 된다.

도 20A에 나타난 액정인가전압에 대한 휘도특성(B-V커브)은 비선형이고, 휘도가 큰 부분과 작은 부분에서는 휘도부근의 액정인가전압 변화가 큰 것이 보통이라고 생각되기 때문에, 이 부분에서 출력앰프회로에서의 합성을 수행하면, 선형휘도변화의 계조표시를 수행하고자 하여도 선형휘도변화로 되지 않는다.

따라서, 이 부분에 대응하는 계조에서는, 출력앰프회로의 합성을 수행되지 않고, 그대로 계조전원을 출력하는 회로구성으로 할 필요가 있다.

상기한 사실에 입각하여, 본 발명의 제 4 실시예에서는 도 20A의 액정의 특성과 도 20B의 드레인 드라이버의 특성을 조합시킴으로써 도 20C에 나타난 바와 같이 백표시측과 흑표시측 모두 일그러짐이 없는 표시를 얻도록 한 것으로, 하기의 표 3에 나타난 처리 1~5와 같은 처리를 수행함으로써, 표시품질의 열화를

피할 수 있는 것이다.

본 실시예에 의하여, 다계조화한 경우의 전 계조영역에서 고해상화를 달성할 수 있으며, 고품질의 표시를 얻을 수 있다.

도 21은 본 발명의 제 4 실시예에 관한 TFT방식 액티브 매트릭스형 액정표시장치(TFT 액정표시장치)의 드레인 드라이버의 구성을 나타내는 블럭도이다. 본 실시예는, 도 16에 있어서의 입력계조전압( $V_0 \sim V_n \sim V_{(M-1)}$ ) 중의 하측 K계조와 상측의 n계조분을 모두 직접 입력(표시데이터와 입력계조 및 출력계조가 1대 1로 대응하는 통상의 디코더)으로 한 것이다. 본 실시예에서는, 표 3의 처리 1, 4, 5에 대응한 처리를 수행하는 것이다. 그 밖의 구성과 동작은 도 16에서 설명한 실시예와 마찬가지이다.

본 실시예에 의해서도 마찬가지로, 다계조화한 경우의 전 계조영역에서 고품질의 표시를 얻을 수 있다.

도 22는 도 21에 있어서의 디코더의 상세한 사항을 설명하는 블럭도로서, 상기 도 17에 나타낸 디코더에 입력계조전압의 하측 K계조분과 상측 ( $M-n$ )계조분을 모두 직접 입력하고, 입력표시데이터와 입력계조 및 디코더의 출력계조가 1대 1로 대응하는 디코더(C)를 추가한 것이다.

디코더(C)의 2개의 출력( $V_{in1}, V_{in2}$ )에는 표시데이터에 1대 1로 대응한 동일한 계조전압이 출력되도록 하고 있다. 디코더(A)와 디코더(B)는 도 19와 동일하기 때문에 설명은 생략하기로 한다.

본 실시예의 표시데이터출력(출력앰프회로의 출력)을 입력계조전압 ( $V_0 \sim V_{255}$ )을 예로서 정리한 것을 표 4에 나타내었다.

여기서는, 입력계조( $V_0 \sim V_{31}, V_{224} \sim V_{225}$ )가 디코더(C)에 대응하고,  $V_{32} \sim V_{233}$ 이 디코더(A)와 디코더(B)에 대응한다. 또한,  $V_{32} \sim V_{223}$ 은 표 1과 동일하다.

도 23은 도 22에서 설명한 본 발명의 제 4 실시예를 구체화한 실제의 회로구성을 설명하는 회로도로서, 저전압측(음극성측) 디코더를 나타낸다. 또한, 고전압측(양극성측) 디코더는, 입력하는 표시데이터의 T와 B를 바꾸어 NMOS 트랜지스터를 모두 PMOS 트랜지스터로 함으로써 구성된다. 또한, 본 회로도는 규모가 크기 때문에 도 23에는 부분만을 나타내고 있다.

본 실시예에 의해서도 마찬가지로 다계조화한 경우의 전 계조영역에서 고해상화를 달성할 수 있으며, 고품질의 표시를 얻을 수 있다.

[표 1]

| 그레이-<br>스케일<br>전압 | 디코더입력     |          | 디지털<br>입력비트 |      |    |    |    |    | 다중화기<br>입력전압 |      |      | 디지털<br>입력비트<br>(하위2비트) |      | 다중화기<br>선별전압 |      | 앰프출력     |      |

|-------------------|-----------|----------|-------------|------|----|----|----|----|--------------|------|------|------------------------|------|--------------|------|----------|------|

|                   | 디코더<br>개수 | 입력<br>전압 | D7          | D6   | D5 | D4 | D3 | D2 | A            | B    | C    | D1                     | D0   | Vin1         | Vin2 |          |      |

|                   |           |          | 0           | V000 | 0  | 0  | 0  | 0  | 0            | 0    | V000 | V002                   | V004 | 0            | 0    | A        | A    |

| V000              | 0         | V000     | 0           | 0    | 0  | 0  | 0  | 0  | V000         | V002 | V004 | 0                      | 0    | A            | A    | V000     |      |

| V001              | -         | -        | 0           | 0    | 0  | 0  | 0  | 0  |              |      |      | 0                      | 1    | A            | B    | V001(합성) |      |

| V002              | V002      | 0        | 0           | 0    | 0  | 0  | 0  | 0  |              |      |      | 1                      | 0    | B            | B    | V002     |      |

| V003              | -         | 0        | 0           | 0    | 0  | 0  | 0  | 0  |              |      |      | 1                      | 1    | B            | C    | V003(합성) |      |

| V004              | 1         | V004     | 0           | 0    | 0  | 0  | 0  | 1  | V004         | V006 | V008 | 0                      | 0    | A            | A    | V004     |      |

| V005              | -         | -        | 0           | 0    | 0  | 0  | 0  | 1  |              |      |      | 0                      | 1    | A            | B    | V005(합성) |      |

| V006              | V006      | 0        | 0           | 0    | 0  | 0  | 0  | 1  |              |      |      | 1                      | 0    | B            | B    | V006     |      |

| V007              | -         | 0        | 0           | 0    | 0  | 0  | 0  | 1  |              |      |      | 1                      | 1    | B            | C    | V007(합성) |      |

| V008              | 2         | V008     | 0           | 0    | 0  | 0  | 1  | 0  | V008         | V010 | V012 | 0                      | 0    | A            | A    | V008     |      |

| V009              | -         | -        | 0           | 0    | 0  | 0  | 1  | 0  |              |      |      | 0                      | 1    | A            | B    | V019(합성) |      |

| V010              | V010      | 0        | 0           | 0    | 0  | 0  | 1  | 0  |              |      |      | 1                      | 0    | B            | B    | V010     |      |

| V011              | -         | 0        | 0           | 0    | 0  | 0  | 1  | 0  |              |      |      | 1                      | 1    | B            | C    | V011(합성) |      |

| V012              | 3         | V012     | 0           | 0    | 0  | 0  | 1  | 1  | V012         | V014 | V016 | 0                      | 0    | A            | A    | V012     |      |

| V013              | -         | -        | 0           | 0    | 0  | 0  | 1  | 1  |              |      |      | 0                      | 1    | A            | B    | V013(합성) |      |

| V014              | V014      | 0        | 0           | 0    | 0  | 0  | 1  | 1  |              |      |      | 1                      | 0    | B            | B    | V014     |      |

| V015              | -         | 0        | 0           | 0    | 0  | 0  | 1  | 1  |              |      |      | 1                      | 1    | B            | C    | V015(합성) |      |

| V016              | 4         | V016     | 0           | 0    | 0  | 1  | 0  | 0  | V016         | V018 | V020 | 0                      | 0    | A            | A    | V016     |      |

| V017              | -         | -        | 0           | 0    | 0  | 1  | 0  | 0  |              |      |      | 0                      | 1    | A            | B    | V017(합성) |      |

| V018              | V018      | 0        | 0           | 0    | 1  | 0  | 0  | 0  |              |      |      | 1                      | 0    | B            | B    | V018     |      |

| V019              | -         | 0        | 0           | 0    | 1  | 0  | 0  | 0  |              |      |      | 1                      | 1    | B            | C    | V019(합성) |      |

| V020              | 5         | V020     | 0           | 0    | 0  | 1  | 0  | 1  | V020         | V022 | V024 | 0                      | 0    | A            | A    | V020     |      |

| V021              | -         | -        | 0           | 0    | 0  | 1  | 0  | 1  |              |      |      | 0                      | 1    | A            | B    | V021(합성) |      |

| V022              | V022      | 0        | 0           | 0    | 1  | 0  | 1  | 1  |              |      |      | 1                      | 0    | B            | B    | V022     |      |

| V023              | -         | 0        | 0           | 0    | 1  | 0  | 1  | 1  |              |      |      | 1                      | 1    | B            | C    | V023(합성) |      |

| V024              | 6         | V024     | 0           | 0    | 0  | 1  | 1  | 0  | V024         | V026 | V028 | 0                      | 0    | A            | A    | V024     |      |

| V025              | -         | -        | 0           | 0    | 0  | 1  | 1  | 0  |              |      |      | 0                      | 1    | A            | B    | V025(합성) |      |

| V026              | V026      | 0        | 0           | 0    | 1  | 1  | 0  | 0  |              |      |      | 1                      | 0    | B            | B    | V026     |      |

| V027              | -         | 0        | 0           | 0    | 1  | 1  | 0  | 0  |              |      |      | 1                      | 1    | B            | C    | V027(합성) |      |

| V028              | 7         | V028     | 0           | 0    | 0  | 1  | 1  | 1  | V028         | V030 | V032 | 0                      | 0    | A            | A    | V028     |      |

| V029              | -         | -        | 0           | 0    | 0  | 1  | 1  | 1  |              |      |      | 0                      | 1    | A            | B    | V029(합성) |      |

| V030              | V030      | 0        | 0           | 0    | 1  | 1  | 1  | 1  |              |      |      | 1                      | 0    | B            | B    | V030     |      |

| V031              | -         | 0        | 0           | 0    | 1  | 1  | 1  | 1  |              |      |      | 1                      | 1    | B            | C    | V031(합성) |      |

| V032              | 8         | V032     | 0           | 0    | 1  | 0  | 0  | 0  | V032         | V034 | V036 | 0                      | 0    | A            | A    | V032     |      |

| V033              | -         | -        | 0           | 0    | 1  | 0  | 0  | 0  |              |      |      | 0                      | 1    | A            | B    | V033(합성) |      |

| V034              | V034      | 0        | 0           | 1    | 0  | 0  | 0  | 0  |              |      |      | 1                      | 0    | B            | B    | V034     |      |

| V035              | -         | 0        | 0           | 1    | 0  | 0  | 0  | 0  |              |      |      | 1                      | 1    | B            | C    | V035(합성) |      |

| V036              | 9         | V036     | 0           | 0    | 1  | 0  | 0  | 0  | 1            | V036 | V038 | V040                   | 0    | 0            | A    | A        | V036 |

| V037              | -         | -        | 0           | 0    | 1  | 0  | 0  | 0  | 1            |      |      | 0                      | 1    | A            | B    | V037(합성) |      |

| V038              | V038      | 0        | 0           | 1    | 0  | 0  | 0  | 1  |              |      |      | 1                      | 0    | B            | B    | V038     |      |

| V039              | -         | 0        | 0           | 1    | 0  | 0  | 0  | 1  |              |      |      | 1                      | 1    | B            | C    | V039(합성) |      |

| V216              | 54        | V216     | 1           | 1    | 0  | 1  | 1  | 0  | V216         | V218 | V220 | 0                      | 0    | A            | A    | V216     |      |

| V217              | -         | -        | 1           | 1    | 0  | 1  | 1  | 0  |              |      |      | 0                      | 1    | A            | B    | V217(합성) |      |

| V218              | V218      | 1        | 1           | 0    | 1  | 1  | 0  | 0  |              |      |      | 1                      | 0    | B            | B    | V218     |      |

| V219              | -         | 1        | 1           | 0    | 1  | 1  | 0  | 0  |              |      |      | 1                      | 1    | B            | C    | V219(합성) |      |

표 1 계속

| 그레이-<br>스케일<br>전압 | 디코더<br>입력 |          | 디지털 입력비트 |    |    |    |    |    | 다중화기<br>입력전압 |      |      | 디지털<br>입력비트<br>(하위2<br>비트) |    | 다중화기<br>선별전압 |          | 앰프출력     |

|-------------------|-----------|----------|----------|----|----|----|----|----|--------------|------|------|----------------------------|----|--------------|----------|----------|

|                   | 디코더<br>개수 | 입력<br>전압 | D7       | D6 | D5 | D4 | D3 | D2 | A            | B    | C    | D1                         | D0 | Vin<br>1     | Vin<br>2 |          |

| V220              | 55        | V220     | 1        | 1  | 0  | 1  | 1  | 1  | V220         | V222 | V224 | 0                          | 0  | A            | A        | V220     |

| V221              |           | -        | 1        | 1  | 0  | 1  | 1  | 1  |              |      |      | 0                          | 1  | A            | B        | V221(합성) |

| V222              |           | V222     | 1        | 1  | 0  | 1  | 1  | 1  |              |      |      | 1                          | 0  | B            | B        | V222     |

| V223              |           | -        | 1        | 1  | 0  | 1  | 1  | 1  |              |      |      | 1                          | 1  | B            | C        | V223(합성) |

| V224              | 56        | V224     | 1        | 1  | 1  | 0  | 0  | 0  | V224         | V226 | V228 | 0                          | 0  | A            | A        | V224     |

| V225              |           | -        | 1        | 1  | 1  | 0  | 0  | 0  |              |      |      | 0                          | 1  | A            | B        | V225(합성) |

| V226              |           | V226     | 1        | 1  | 1  | 0  | 0  | 0  |              |      |      | 1                          | 0  | B            | B        | V226     |

| V227              |           | -        | 1        | 1  | 1  | 0  | 0  | 0  |              |      |      | 1                          | 1  | B            | C        | V227(합성) |

| V228              | 57        | V228     | 1        | 1  | 1  | 0  | 0  | 1  | V228         | V230 | V232 | 0                          | 0  | A            | A        | V228     |

| V229              |           | -        | 1        | 1  | 1  | 0  | 0  | 1  |              |      |      | 0                          | 1  | A            | B        | V229(합성) |

| V230              |           | V230     | 1        | 1  | 1  | 0  | 0  | 1  |              |      |      | 1                          | 0  | B            | B        | V230     |

| V231              |           | -        | 1        | 1  | 1  | 0  | 0  | 1  |              |      |      | 1                          | 1  | B            | C        | V231(합성) |

| V232              | 58        | V232     | 1        | 1  | 1  | 0  | 1  | 0  | V232         | V234 | V236 | 0                          | 0  | A            | A        | V232     |

| V233              |           | -        | 1        | 1  | 1  | 0  | 1  | 0  |              |      |      | 0                          | 1  | A            | B        | V233(합성) |

| V234              |           | V234     | 1        | 1  | 1  | 0  | 1  | 0  |              |      |      | 1                          | 0  | B            | B        | V234     |

| V235              |           | -        | 1        | 1  | 1  | 0  | 1  | 0  |              |      |      | 1                          | 1  | B            | C        | V235(합성) |

| V236              | 59        | V236     | 1        | 1  | 1  | 0  | 1  | 1  | V236         | V238 | V240 | 0                          | 0  | A            | A        | V236     |

| V237              |           | -        | 1        | 1  | 1  | 0  | 1  | 1  |              |      |      | 0                          | 1  | A            | B        | V237(합성) |

| V238              |           | V238     | 1        | 1  | 1  | 0  | 1  | 1  |              |      |      | 1                          | 0  | B            | B        | V238     |

| V239              |           | -        | 1        | 1  | 1  | 0  | 1  | 1  |              |      |      | 1                          | 1  | B            | C        | V239(합성) |

| V240              | 60        | V240     | 1        | 1  | 1  | 1  | 0  | 0  | V240         | V242 | V244 | 0                          | 0  | A            | A        | V240     |

| V241              |           | -        | 1        | 1  | 1  | 1  | 0  | 0  |              |      |      | 0                          | 1  | A            | B        | V241(합성) |

| V242              |           | V242     | 1        | 1  | 1  | 1  | 0  | 0  |              |      |      | 1                          | 0  | B            | B        | V242     |

| V243              |           | -        | 1        | 1  | 1  | 1  | 0  | 0  |              |      |      | 1                          | 1  | B            | C        | V243(합성) |

| V244              | 61        | V244     | 1        | 1  | 1  | 1  | 0  | 1  | V244         | V246 | V248 | 0                          | 0  | A            | A        | V244     |

| V245              |           | -        | 1        | 1  | 1  | 1  | 0  | 1  |              |      |      | 0                          | 1  | A            | B        | V245(합성) |

| V246              |           | V246     | 1        | 1  | 1  | 1  | 0  | 1  |              |      |      | 1                          | 0  | B            | B        | V246     |

| V247              |           | -        | 1        | 1  | 1  | 1  | 0  | 1  |              |      |      | 1                          | 1  | B            | C        | V247(합성) |

| V248              | 62        | V248     | 1        | 1  | 1  | 1  | 1  | 0  | V248         | V250 | V252 | 0                          | 0  | A            | A        | V248     |

| V249              |           | -        | 1        | 1  | 1  | 1  | 1  | 0  |              |      |      | 0                          | 1  | A            | B        | V249(합성) |

| V250              |           | V250     | 1        | 1  | 1  | 1  | 1  | 0  |              |      |      | 1                          | 0  | B            | B        | V250     |

| V251              |           | -        | 1        | 1  | 1  | 1  | 1  | 0  |              |      |      | 1                          | 1  | B            | C        | V251(합성) |

| V252              | 63        | V252     | 1        | 1  | 1  | 1  | 1  | 1  | V252         | V254 | V256 | 0                          | 0  | A            | A        | V252     |

| V253              |           | -        | 1        | 1  | 1  | 1  | 1  | 1  |              |      |      | 0                          | 1  | A            | B        | V253(합성) |

| V254              |           | V254     | 1        | 1  | 1  | 1  | 1  | 1  |              |      |      | 1                          | 0  | B            | B        | V254     |

| V255              |           | -        | 1        | 1  | 1  | 1  | 1  | 1  |              |      |      | 1                          | 1  | B            | C        | V255(합성) |

|                   |           | V256     |          |    |    |    |    |    |              |      |      |                            |    |              |          |          |

## [표 2]

| 그레이<br>-<br>스케일<br>전압 | 디코더입력 |                       | 디지털입력비트 |    |    |    |    |    |    |    | 디코더선택전압 |      | 앰프출력     |

|-----------------------|-------|-----------------------|---------|----|----|----|----|----|----|----|---------|------|----------|

|                       | 입력전압  | 일련번호<br>(n=0, 1, ...) | D7      | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Vin1    | Vin2 |          |

| V0                    | V0    | 4n+1                  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V0      | V0   | V0       |

| V1                    | -     | -                     | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 1  | V0      | V2   | V1(합성)   |

| V2                    | V2    | 4n+3                  | 0       | 0  | 0  | 0  | 0  | 0  | 1  | 0  | V2      | V2   | V2       |

| V3                    | -     | -                     | 0       | 0  | 0  | 0  | 0  | 0  | 1  | 1  | V2      | V4   | V3(합성)   |

| V4                    | V4    | 4n+1                  | 0       | 0  | 0  | 0  | 0  | 1  | 0  | 0  | V4      | V4   | V4       |

| V5                    | -     | -                     | 0       | 0  | 0  | 0  | 0  | 1  | 0  | 1  | V4      | V6   | V5(합성)   |

| V6                    | V6    | 4n+3                  | 0       | 0  | 0  | 0  | 0  | 1  | 1  | 0  | V6      | V6   | V6       |

| V7                    | -     | -                     | 0       | 0  | 0  | 0  | 0  | 1  | 1  | 1  | V6      | V8   | V7(합성)   |

| V8                    | V8    | 4n+1                  | 0       | 0  | 0  | 0  | 1  | 0  | 0  | 0  | V8      | V8   | V8       |

| V9                    | -     | -                     | 0       | 0  | 0  | 0  | 1  | 0  | 0  | 1  | V8      | V10  | V9(합성)   |

| V10                   | V10   | 4n+3                  | 0       | 0  | 0  | 0  | 1  | 0  | 1  | 0  | V10     | V10  | V10      |

| V11                   | -     | -                     | 0       | 0  | 0  | 0  | 1  | 0  | 1  | 1  | V10     | V12  | V11(합성)  |

| V12                   | V12   | 4n+1                  | 0       | 0  | 0  | 0  | 1  | 1  | 0  | 0  | V12     | V12  | V12      |

| V13                   | -     | -                     | 0       | 0  | 0  | 0  | 1  | 1  | 0  | 1  | V12     | V14  | V13(합성)  |

| V14                   | V14   | 4n+3                  | 0       | 0  | 0  | 0  | 1  | 1  | 1  | 0  | V14     | V14  | V14      |

| V15                   | -     | -                     | 0       | 0  | 0  | 0  | 1  | 1  | 1  | 1  | V14     | V16  | V15(합성)  |

| V16                   | V16   | 4n+1                  | 0       | 0  | 0  | 1  | 0  | 0  | 0  | 0  | V16     | V16  | V16      |

| V17                   | -     | -                     | 0       | 0  | 0  | 1  | 0  | 0  | 0  | 1  | V16     | V18  | V17(합성)  |

| V18                   | V18   | 4n+3                  | 0       | 0  | 0  | 1  | 0  | 0  | 1  | 0  | V18     | V18  | V18      |

| V19                   | -     | -                     | 0       | 0  | 0  | 1  | 0  | 0  | 1  | 1  | V18     | V20  | V19(합성)  |

| .                     | .     | .                     | .       | .  | .  | .  | .  | .  | .  | .  | .       | .    | .        |

| V252                  | V252  | 4n+1                  | 1       | 1  | 1  | 1  | 1  | 1  | 0  | 0  | V252    | V252 | V252     |

| V253                  | -     | -                     | 1       | 1  | 1  | 1  | 1  | 1  | 0  | 1  | V252    | V254 | V253(합성) |

| V254                  | V254  | 4n+3                  | 1       | 1  | 1  | 1  | 1  | 1  | 1  | 0  | V254    | V254 | V254     |

| V255                  | -     | -                     | 1       | 1  | 1  | 1  | 1  | 1  | 1  | 1  | V254    | V255 | V255     |

**[표 3]****공정 1**

그레이-스케일 전압공급회로(그레이-스케일 발전기 회로)로부터 공급된 그레이-스케일 전압은 백색 및 흑색의 압축을 피하기 위해서, 출력증폭기 내에 있는 그레이-스케일 전압공급회로로부터 공급된 그레이-스케일 전압들 사이의 중간 그레이-스케일 전압을 합성하지 않으면서 백색측에 R 그레이-스케일 단계를 적용하고 흑색측에 S 그레이-스케일 단계를 적용하는데 사용된다.

**공정 2**

그레이-스케일 전압공급회로(그레이-스케일 발전기 회로)로부터 공급된 그레이-스케일 전압은 백색의 압축을 피하기 위해서, 출력증폭기 내에 있는 그레이-스케일 전압공급회로로부터 공급된 그레이-스케일 전압들 사이의 중간 그레이-스케일 전압을 합성하지 않으면서 백색측에 R 그레이-스케일 단계를 적용하는데 사용된다.

**공정 3**

그레이-스케일 전압공급회로(그레이-스케일 발전기 회로)로부터 공급된 그레이-스케일 전압은 흑색의 압축을 피하기 위해서, 출력증폭기 내에 있는 그레이-스케일 전압공급회로로부터 공급된 그레이-스케일 전압들 사이의 중간 그레이-스케일 전압을 합성하지 않으면서 흑색측에 S 그레이-스케일 단계를 적용하는데 사용된다.

**공정 4**

그레이-스케일 전압공급회로(그레이-스케일 발전기 회로)로부터 공급된 그레이-스케일 전압은 해당 영역 내의 밝기의 압축을 피하기 위해서, 출력증폭기 내에 있는 그레이-스케일 전압공급회로로부터 공급된 그레이-스케일 전압들 사이의 중간 그레이-스케일 전압을 합성하지 않으면서 액정총을 가로지른 전압 및 밝기 사이의 관계가 선형적이지 않은 영역에 그레이-스케일 단계를 적용하는데 사용된다.

**공정 5**

그레이-스케일 전압공급회로로부터 공급된 그레이-스케일 전압은 출력증폭기에서 해당 영역 내에 있는 원하는 중간 그레이-스케일 전압에 대한 합성의 어려움을 피하기 위해서, 출력증폭기 내에 있는 그레이-스케일 전압공급회로부터 공급된 그레이-스케일 전압들 사이의 중간 그레이-스케일 전압을 합성하지 않으면서 두 개의 연속적인 그레이-스케일 단계 사이의 전압차가 상대적으로 큰 영역에 그레이-스케일 단계를 적용하는데 사용된다.

## [표 4]

| 그레이<br>-<br>스케일<br>전압 | 디코더입력    |                     | 디지털<br>입력비트 |    |    |    |    |    |    |    | 디코더<br>서별전압 |         | 앰프<br>출력 |

|-----------------------|----------|---------------------|-------------|----|----|----|----|----|----|----|-------------|---------|----------|

|                       | 입력<br>전압 | 일련번호<br>(n=0,1... ) | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Vin1        | Vin2    |          |

|                       |          |                     |             |    |    |    |    |    |    |    |             |         |          |

| V0                    | V0       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V0          | V0      | V0       |

|                       | V1       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 1  | V1          | V1      | V1       |

|                       | V2       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 0  | V2          | V2      | V2       |

|                       | V3       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 1  | V3          | V3      | V3       |

|                       | V4       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 0  | V4          | V4      | V4       |

|                       | V5       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 0  | V5          | V5      | V5       |

|                       | V6       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 1  | V6          | V6      | V6       |

|                       | V7       | -                   | 0           | 0  | 0  | 0  | 0  | 0  | 1  | 1  | V7          | V7      | V7       |

|                       | V8       | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 0  | 0  | V8          | V8      | V8       |

|                       | V9       | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 0  | 0  | V9          | V9      | V9       |

|                       | V10      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 0  | 1  | V10         | V10     | V10      |

|                       | V11      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 0  | 1  | V11         | V11     | V11      |

|                       | V12      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 1  | 0  | V12         | V12     | V12      |

|                       | V13      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 1  | 0  | V13         | V13     | V13      |

|                       | V14      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 1  | 1  | V14         | V14     | V14      |

|                       | V15      | -                   | 0           | 0  | 0  | 0  | 0  | 1  | 1  | 1  | V15         | V15     | V15      |

|                       | V16      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 0  | 0  | V16         | V16     | V16      |

|                       | V17      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 0  | 0  | V17         | V17     | V17      |

|                       | V18      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 0  | 1  | V18         | V18     | V18      |

|                       | V19      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 0  | 1  | V19         | V19     | V19      |

|                       | V20      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 1  | 0  | V20         | V20     | V20      |

|                       | V21      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 1  | 0  | V21         | V21     | V21      |

|                       | V22      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 1  | 1  | V22         | V22     | V22      |

|                       | V23      | -                   | 0           | 0  | 0  | 0  | 1  | 0  | 1  | 1  | V23         | V23     | V23      |

|                       | V24      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 0  | 0  | V24         | V24     | V24      |

|                       | V25      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 0  | 0  | V25         | V25     | V25      |

|                       | V26      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 0  | 1  | V26         | V26     | V26      |

|                       | V27      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 0  | 1  | V27         | V27     | V27      |

|                       | V28      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 0  | V28         | V28     | V28      |

|                       | V29      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 0  | V29         | V29     | V29      |

|                       | V30      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 1  | V30         | V30     | V30      |

|                       | V31      | -                   | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 1  | V31         | V31     | V31      |

| V32                   | V32      | 4n+1                | 0           | 0  | 1  | 0  | 0  | 0  | 0  | 0  | V32         | V32     | V32      |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 0  | 0  | 0  | 1  | V32         | V34     | V33(합성)  |

|                       | V34      | 4n+3                | 0           | 0  | 1  | 0  | 0  | 0  | 1  | 0  | V34         | V34     |          |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 0  | 0  | 1  | 1  | V34         | V36     |          |

|                       | V35      | -                   | 0           | 0  | 1  | 0  | 0  | 0  | 1  | 1  | V34         | V35(합성) |          |

| V36                   | V36      | 4n+1                | 0           | 0  | 1  | 0  | 0  | 1  | 0  | 0  | V36         | V36     | V36      |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 0  | 1  | 0  | 1  | V36         | V38     | V37(합성)  |

|                       | V38      | 4n+3                | 0           | 0  | 1  | 0  | 0  | 1  | 1  | 0  | V38         | V38     |          |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 0  | 1  | 1  | 1  | V38         | V40     | V39(합성)  |

| V40                   | V40      | 4n+1                | 0           | 0  | 1  | 0  | 1  | 0  | 0  | 0  | V40         | V40     | V40      |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 1  | 0  | 0  | 1  | V40         | V42     | V41(합성)  |

|                       | V42      | 4n+3                | 0           | 0  | 1  | 0  | 1  | 0  | 1  | 0  | V42         | V42     |          |

|                       | -        | -                   | 0           | 0  | 1  | 0  | 1  | 0  | 1  | 1  | V42         | V44     | V43(합성)  |

표 4계속

| 그레이-<br>스케일<br>전압 | 디코더입력                    |      | 디지털<br>입력비트 |    |    |    |    |    |    | 디코더<br>선별전압 |      | 앰프출력 |          |                                                      |

|-------------------|--------------------------|------|-------------|----|----|----|----|----|----|-------------|------|------|----------|------------------------------------------------------|

|                   | 입력<br>전압<br>(n=0, 1... ) | 일련번호 | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0          | Vin1 | Vin2 |          |                                                      |

| V44               | V44                      | 4n+1 | 0           | 0  | 1  | 0  | 1  | 1  | 0  | 0           | V44  | V44  | V44      | 합성<br>↓                                              |

| V45               | -                        | -    | 0           | 0  | 1  | 0  | 1  | 1  | 0  | 1           | V44  | V46  | V45(합성)  |                                                      |

| V46               | V46                      | 4n+3 | 0           | 0  | 1  | 0  | 1  | 1  | 1  | 0           | V46  | V46  | V46      |                                                      |

| V47               | -                        | -    | 0           | 0  | 1  | 0  | 1  | 1  | 1  | 1           | V46  | V48  | V47(합성)  |                                                      |

| V48               | V48                      | 4n+1 | 0           | 0  | 1  | 1  | 0  | 0  | 0  | 0           | V48  | V48  | V48      |                                                      |

| V49               | -                        | -    | 0           | 0  | 1  | 1  | 0  | 0  | 0  | 1           | V48  | V50  | V49(합성)  |                                                      |

| V50               | V50                      | 4n+3 | 0           | 0  | 1  | 1  | 0  | 0  | 1  | 0           | V50  | V50  | V50      |                                                      |

| V51               | -                        | -    | 0           | 0  | 1  | 1  | 0  | 0  | 1  | 1           | V50  | V52  | V51(합성)  |                                                      |

| .                 | .                        | .    | .           | .  | .  | .  | .  | .  | .  | .           | .    | .    | .        |                                                      |

| V220              | V220                     | 4n+1 | 1           | 1  | 0  | 1  | 1  | 1  | 0  | 0           | V220 | V220 | V220     |                                                      |

| V221              | -                        | -    | 1           | 1  | 0  | 1  | 1  | 1  | 0  | 1           | V220 | V222 | V221(합성) |                                                      |

| V222              | V222                     | 4n+3 | 1           | 1  | 0  | 1  | 1  | 1  | 1  | 0           | V222 | V222 | V222     |                                                      |

| V223              | -                        | -    | 1           | 1  | 0  | 1  | 1  | 1  | 1  | 1           | V222 | V224 | V223(합성) |                                                      |

| V224              | V224                     | -    | 1           | 1  | 1  | 0  | 0  | 0  | 0  | 0           | V224 | V224 | V224     | 그레이-<br>스케일<br>전압<br>로부터<br>공급회로로<br>공급된<br>것과<br>같음 |

| V225              | V225                     | -    | 1           | 1  | 1  | 0  | 0  | 0  | 0  | 1           | V225 | V225 | V225     |                                                      |

| V226              | V226                     | -    | 1           | 1  | 1  | 0  | 0  | 0  | 0  | 1           | V226 | V226 | V226     |                                                      |

| V227              | V227                     | -    | 1           | 1  | 1  | 0  | 0  | 0  | 0  | 1           | V227 | V227 | V227     |                                                      |

| V228              | V228                     | -    | 1           | 1  | 1  | 0  | 0  | 1  | 0  | 0           | V228 | V228 | V228     |                                                      |

| V229              | V229                     | -    | 1           | 1  | 1  | 0  | 0  | 1  | 0  | 1           | V229 | V229 | V229     |                                                      |

| V230              | V230                     | -    | 1           | 1  | 1  | 0  | 0  | 1  | 1  | 0           | V230 | V230 | V230     |                                                      |

| V231              | V231                     | -    | 1           | 1  | 1  | 0  | 0  | 1  | 1  | 1           | V231 | V231 | V231     |                                                      |

| V232              | V232                     | -    | 1           | 1  | 1  | 0  | 1  | 0  | 0  | 0           | V232 | V232 | V232     |                                                      |

| V233              | V233                     | -    | 1           | 1  | 1  | 0  | 1  | 0  | 0  | 0           | V233 | V233 | V233     |                                                      |

| V234              | V234                     | -    | 1           | 1  | 1  | 0  | 1  | 0  | 1  | 0           | V234 | V234 | V234     |                                                      |

| V235              | V235                     | -    | 1           | 1  | 1  | 0  | 1  | 0  | 1  | 1           | V235 | V235 | V235     |                                                      |

| V236              | V236                     | -    | 1           | 1  | 1  | 0  | 1  | 1  | 0  | 0           | V236 | V236 | V236     |                                                      |

| V237              | V237                     | -    | 1           | 1  | 1  | 0  | 1  | 1  | 0  | 1           | V237 | V237 | V237     |                                                      |

| V238              | V238                     | -    | 1           | 1  | 1  | 0  | 1  | 1  | 1  | 0           | V238 | V238 | V238     |                                                      |

| V239              | V239                     | -    | 1           | 1  | 1  | 0  | 1  | 1  | 1  | 1           | V239 | V239 | V239     |                                                      |

| V240              | V240                     | -    | 1           | 1  | 1  | 1  | 0  | 0  | 0  | 0           | V240 | V240 | V240     |                                                      |

| V241              | V241                     | -    | 1           | 1  | 1  | 1  | 0  | 0  | 0  | 1           | V241 | V241 | V241     |                                                      |

| V242              | V242                     | -    | 1           | 1  | 1  | 1  | 0  | 0  | 1  | 0           | V242 | V242 | V242     |                                                      |

| V243              | V243                     | -    | 1           | 1  | 1  | 1  | 0  | 0  | 1  | 1           | V243 | V243 | V243     |                                                      |

| V244              | V244                     | -    | 1           | 1  | 1  | 1  | 0  | 1  | 0  | 0           | V244 | V244 | V244     |                                                      |

| V245              | V245                     | -    | 1           | 1  | 1  | 1  | 0  | 1  | 0  | 1           | V245 | V245 | V245     |                                                      |

| V246              | V246                     | -    | 1           | 1  | 1  | 1  | 0  | 1  | 1  | 0           | V246 | V246 | V246     |                                                      |

| V247              | V247                     | -    | 1           | 1  | 1  | 1  | 0  | 1  | 1  | 1           | V247 | V247 | V247     |                                                      |

| V248              | V248                     | -    | 1           | 1  | 1  | 1  | 1  | 0  | 0  | 0           | V248 | V248 | V248     |                                                      |

| V249              | V249                     | -    | 1           | 1  | 1  | 1  | 1  | 0  | 0  | 0           | 1    | V249 | V249     | V249                                                 |

| V250              | V250                     | -    | 1           | 1  | 1  | 1  | 1  | 0  | 1  | 0           | V250 | V250 | V250     |                                                      |

| V251              | V251                     | -    | 1           | 1  | 1  | 1  | 1  | 0  | 1  | 1           | V251 | V251 | V251     |                                                      |

표 4계속

| 그레이<br>-<br>스케일<br>전압 | 디코더입력    |                    | 디지털입력비트 |    |    |    |    |    |    | 디코더선택전압 |      | 앰프출력 |      |                                |

|-----------------------|----------|--------------------|---------|----|----|----|----|----|----|---------|------|------|------|--------------------------------|

|                       | 입력<br>전압 | 일련번호<br>(n=0, 1~ ) | D7      | D6 | D5 | D4 | D3 | D2 | D1 | D0      | Vin1 | Vin2 |      |                                |

| V252                  | V252     | -                  | 1       | 1  | 1  | 1  | 1  | 1  | 0  | 0       | V252 | V252 | V252 | 그레이-<br>스케일<br>전압              |

| V253                  | V253     | -                  | 1       | 1  | 1  | 1  | 1  | 1  | 0  | 1       | V253 | V253 | V253 |                                |

| V254                  | V254     | -                  | 1       | 1  | 1  | 1  | 1  | 1  | 1  | 0       | V254 | V254 | V254 | 공급회로<br>로부터<br>공급된<br>것과<br>같음 |

| V255                  | V255     | -                  | 1       | 1  | 1  | 1  | 1  | 1  | 1  | 1       | V255 | V255 | V255 |                                |

### 발명의 효과

이상 설명한 바와 같이, 본 발명에 의하면, 칩크기가 증가하지 않으면서 다계조화를 실현할 수 있으며, 액정패널의 고화질화, 액정표시장치의 프레임 협소화를 달성할 수 있고, 또한, 디코더회로의 온저항의 증대를 억제할 수 있으며, 다계조화한 액정패널의 부하를 줄여 고화질화를 얻을 수 있다.

즉,  $(M+1)/2$ (총 계조수 M이 홀수인 경우) 또는  $M/2+1$ (총 계조수 M이 짝수인 경우)의 입력전압으로부터 M 계조의 출력전압을 생성할 수 있기 때문에, 드레인 드라이버의 회로구조를 줄일 수 있으며, 칩 면적의 축소가 가능하게 되고, 액정의 γ 특성에 맞는 출력전압을 얻을 수 있기 때문에, TFT 액정패널의 저비용화, 액정표시장치의 프레임 협소화를 실현할 수 있다.

### (57) 청구의 범위

#### 청구항 1

복수의 화소를 가지는 액정패널과,

P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고,

상기 영상신호선 구동회로는,

Q개의 서로 다른 계조전압을 공급하는 전원회로와,

상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 선택된 하나의 계조전압값을 가지는 2개의 계조전압, 또는 상기 Q개의 서로 다른 계조전압 중에서 선택된 서로 다른 값의 2개의 계조전압을 선택하여 출력하는, 상기 영상신호선의 각각에 대응하여 설치된 복수의 선택회로와,

상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압 중 어느 하나, 또는 상기 서로 다른 값의 2개의 계조전압으로부터 생성된 상기 서로 다른 값의 2개의 계조전압의 중간값의 계조전압을 바탕으로, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압을 출력하는 복수의 앰프회로로 이루어지는 것을 특징으로 하는 액정표시장치.

#### 청구항 2

청구항 1에 있어서,

상기 복수의 앰프회로의 각각은, 동일한 값의 2개의 전압(V1, V2)이 입력되었을 때, 전압(V1)을 출력하고, 서로 다른 값의 전압(V1, V3)이 입력되었을 때,  $V1 < V2 < V3$ 를 만족하는 전압(V2)을 출력하는 것을 특징으로 하는 액정표시장치.

#### 청구항 3

청구항 1에 있어서,

상기 복수의 선택회로의 각각은, P비트의 표시데이터에 대응한 P개의 스위칭소자를 가지고,

상기 P비트의 표시데이터의 각각을, 비트기준으로 복수의 그룹으로 분할하여 사용함으로써 상기 Q개의 계조전압 중에서,

동일한 값의 2개의 계조전압 또는 서로 다른 값의 2개의 계조전압을 선택하여 출력하는 것을 특징으로 하는 액정표시장치.

#### 청구항 4

복수의 화소를 가지는 액정패널과,

P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고,

상기 영상신호선 구동회로는,

Q개의 서로 다른 계조전압을 공급하는 전원회로와,

상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 복수의 계조전압을 선택하여 출력하는, 각 영상신호선에 대응하여 설치된 복수의 선택회로와,

상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 복수의 계조전압 중 하나의 계조전압, 또는 상기 공급된 복수의 계조전압으로부터 생성된 상기 복수의 계조전압과는 서로 다른 값의 계조전압을 바탕으로, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압을 출력하는 복수의 앰프회로로 이루어지는 것을 특징으로 하는 액정표시장치.

## 청구항 5

청구항 4에 있어서,

상기 복수의 선택회로는 P비트의 표시데이터에 대응한 P개의 스위칭소자를 가지고,

상기 P비트의 표시데이터의 각각을, 비트기준으로 복수의 그룹으로 분할하여 사용함으로써 상기 Q개의 계조전압 중에서 복수의 계조전압을 선택할 수 있게 한 것을 특징으로 하는 액정표시장치.

## 청구항 6

청구항 4에 있어서,

상기 복수의 선택회로의 각각은, 상기 Q개의 계조전압을 복수의 그룹으로 나누어, 상기 P비트로 이루어지는 표시데이터를 바탕으로, 상기 복수의 그룹 중에서 미리 정해진 수의 그룹을 선택하고, 동시에 상기 선택된 그룹의 각각으로부터 하나의 계조전압을 선택하도록 구성된 것을 특징으로 하는 액정표시장치.

## 청구항 7

복수의 화소를 가지는 액정패널과,

P비트로 이루어지는 표시데이터에 대응하는 영상신호전압을, 각 영상신호선을 사이에 두고 상기 복수의 화소의 각각에 공급하는 영상신호선 구동회로를 구비하고,

상기 영상신호선 구동회로는,

Q개의 서로 다른 계조전압을 공급하는 전원회로와,

상기 표시데이터를 바탕으로, 상기 Q개의 서로 다른 계조전압 중에서 선택된 하나의 계조전압값을 가지는 2개의 계조전압, 또는 상기 Q개의 서로 다른 계조전압 중에서 선택된 서로 다른 값의 2개의 계조전압을 선택하여 출력하는, 상기 영상신호선의 각각에 대응하여 설치된 복수의 선택회로와,

상기 표시데이터를 바탕으로, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압이 동일한 값을 때에는 그 계조전압을 전류증폭하고, 상기 복수의 선택회로 중의 대응하는 것으로부터 공급된 상기 2개의 계조전압이 서로 다른 값의 2개의 계조전압일 때는 상기 서로 다른 값의 2개의 계조전압으로부터 생성된 상기 서로 다른 값의 2개의 계조전압의 중간값 계조전압을 전류증폭하여, 상기 영상신호선 중의 대응하는 것으로 상기 영상신호전압으로서 출력하는 복수의 앰프회로로 이루어지는 것을 특징으로 하는 액정표시장치.

## 청구항 8

청구항 7에 있어서,

상기 Q개의 서로 다른 계조전압이, '연속하는 2개의 계조전압의 차'의 대소에 기초하여 복수의 그룹으로 분류되어 있으며,

상기 '연속하는 2개의 계조전압의 차'가 비교적 크게 설정되어 있는 그룹에 대해서는, 상기 복수의 선택회로의 각각이 동일한 값을 가지는 2개의 계조전압을 출력하도록 구성되어 있는 것을 특징으로 하는 액정표시장치.

## 청구항 9

청구항 7에 있어서,

상기 Q개의 서로 다른 계조전압 중, 계조전압이 계조단계와 함께 선형으로 증감되지 않는 범위에 있어서의 계조전압에 대해서는, 상기 복수의 선택회로의 각각이 동일한 값을 가지는 2개의 계조전압을 출력하도록 구성되어 있는 것을 특징으로 하는 액정표시장치.

## 청구항 10

청구항 7에 있어서,

상기 Q개의 서로 다른 계조전압을 대소의 순서대로 나열한 경우의, 미리 정해진 R개의 최대측 계조전압 및 미리 정해진 S개의 최소측 계조전압에 대해서는, 상기 복수의 선택회로의 각각이 동일한 값을 가지는 2개의 계조전압을 출력하도록 구성되어 있는 것을 특징으로 하는 액정표시장치.

## 청구항 11

청구항 7에 있어서,

상기 Q개의 서로 다른 계조전압을 백표시에서부터 흑표시의 순서대로 대응하도록 나열한 경우의, 미리 정해진 T개의 백표시측의 계조전압에 대해서는, 상기 복수의 선택회로의 각각이 동일한 값을 가지는 2개의

계조전압을 출력하도록 구성되어 있는 것을 특징으로 하는 액정표시장치.

### 청구항 12

청구항 7에 있어서,

상기 Q개의 서로 다른 계조전압을 백표시에서부터 흑표시의 순서대로 대응하도록 나열한 경우의, 미리 정해진 2개의 흑표시측 계조전압에 대해서는, 상기 복수의 선택회로의 각각이 동일한 값을 가지는 2개의 계조전압을 출력하도록 구성되어 있는 것을 특징으로 하는 액정표시장치.

### 청구항 13

청구항 7에 있어서,

상기 복수의 선택회로의 각각은, 상기 Q개의 서로 다른 계조전압 중의, 계조전압( $V$ )( $4n$ )( $n=0, 1, 2, 3, \dots$ )이 입력되는 제 1 디코더와, 계조전압( $V$ )( $4n+2$ )( $n=0, 1, 2, 3, \dots$ )이 입력되는 제 2 디코더와,

상기 표시데이터의 최하위 비트를 바탕으로, 상기 제 1 디코더의 출력단자와 상기 제 2 디코더의 출력단자를 접속 혹은 비접속시키는 스위치소자를 갖춘 것을 특징으로 하는 액정표시장치.

## 도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

\* 도면의 단순화를 위해서, D2 내지 D7은 D2 또는  $\bar{D}2$  내지 D7 또는  $\bar{D}7$ 을 나타낸다

도면10

도면11

도면12

도면13

제 2 디코더

도면14

도면15

## 도면 16

도면17

도면18

도면 19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

|                |                                                                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">KR1020010015402A</a>                                                                                                                                     | 公开(公告)日 | 2001-02-26 |

| 申请号            | KR1020000042011                                                                                                                                                      | 申请日     | 2000-07-21 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA<br>日立器件工程株式会社<br>日立超大规模集成电路系统株式会社                                                                                                            |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>히타치디바이스엔지니어링가부시키가이사<br>可否时期这一地都超密度的系统化.                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>히타치디바이스엔지니어링가부시키가이사<br>可否时期这一地都超密度的系统化.                                                                                                                 |         |            |

| [标]发明人         | AKIYAMA KENICHI<br>아키야마켄이치<br>YAMASHITA YUJI<br>야마시타유지<br>ISAMI HIRONOBU<br>이사미히로노부<br>GOTO MITSURU<br>고토미츠루<br>YASUKAWA SHINJI<br>야스카와신지<br>KOTERA KOICHI<br>코테라코이치 |         |            |

| 发明人            | 아키야마켄이치<br>야마시타유지<br>이사미히로노부<br>고토미츠루<br>야스카와신지<br>코테라코이치                                                                                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G G09G3/20 G02F                                                                                                                                |         |            |

| CPC分类号         | G09G3/3688 G09G3/2011 G09G2310/0297                                                                                                                                  |         |            |

| 代理人(译)         | 李钟IL                                                                                                                                                                 |         |            |

| 优先权            | 1999206468 1999-07-21 JP                                                                                                                                             |         |            |

| 其他公开文献         | <a href="#">KR100336683B1</a>                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                            |         |            |

## 摘要(译)

本发明涉及液晶显示器。并且，多个像素对应于由具有液晶面板的显示数据的视频信号电压和每个图像信号线的P位被置于该间隔中，并且包括分别提供多个像素的视频信号线的驱动电路。通过提供由电源电路，多个选择电路和多个AMP电路组成的液晶显示器，可以实现芯片尺寸的增加，并且可以实现多级。并且能够实现高清晰度的液晶面板负载随多级变化的技术降低，它可以控制液晶面板的高清晰度，而且还增加了解码器电路的导通电阻可以实现所呈现的液晶显示器的框架变窄。至于电源电路，视频信号线的驱动电路提供Q的不同灰度电压。多个选择电路分别对应于它输出它选择在具有一个灰度电压的灰度电压的不同灰度电压之间选择

的2个不同值的灰度电压。作为在Q或2的Q的不同灰度电压之间选择并且安装在图像信号线上的自然配置的显示数据的值。多个AMP电路，其对应于基于2个灰度电压的中间值的灰度电压输出图像信号线中的视频信号电压，所述2个灰度电压的中间值是从任意一个的2个灰度电压产生的自然配置的显示数据的不同值对应于在多个选择电路中提供2个或不同的灰度电压值。