**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

G02F 1/133

(45) 공고일자 2005년08월11일

(11) 등록번호 10-0506434

(24) 등록일자 2005년07월28일

(21) 출원번호

(22) 출원일자

10-2002-0031962

2002년06월07일

(65) 공개번호

(43) 공개일자

10-2002-0093625

2002년12월16일

(30) 우선권주장

JP-P-2001-00173410 2001년06월08일

일본(JP)

(73) 특허권자

가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

히타치디바이스 엔지니어링가부시키가이샤

일본국 지바켄 모바라시 하야노 3681

(72) 발명자

마루오까요시오

일본지바켄모바라시미나미요시다2811-9

미소노우도시끼

일본지바켄이찌하라시이끼와다790

마에다도시오

일본지바켄지바시미도리구오유미노2-36-5

와따나베아끼히로

일본지바켄모바라시마찌보13-2

나까가와히데끼

일본지바켄지바시미노리꾸아스미가오까4-39

(74) 대리인

장수길

구영창

심사관 : 임현석

(54) 액정 표시 장치

**요약**

아날로그 영상 신호를 상(相)전개하여 입력하는 액정 표시 장치에서, 회로 변동에 의한 표시 품질의 저하를 저감한다. 복수의 아날로그 회로에 의한 변동을 보정하기 위해서, 디지털의 신호 처리 회로 내에 복수의 아날로그 회로분의 대조표를 가짐으로써, 대조표에 설정하는 데이터로써 아날로그 회로의 변동의 보정을 행한다.

**대표도**

도 11

### 색인어

액정 패널, 영상 신호선, 증폭 회로, 액정 조성물

### 명세서

#### 도면의 간단한 설명

도 1은 본 발명의 실시 형태인 액정 표시 장치의 개략 구성을 도시하는 블록도.

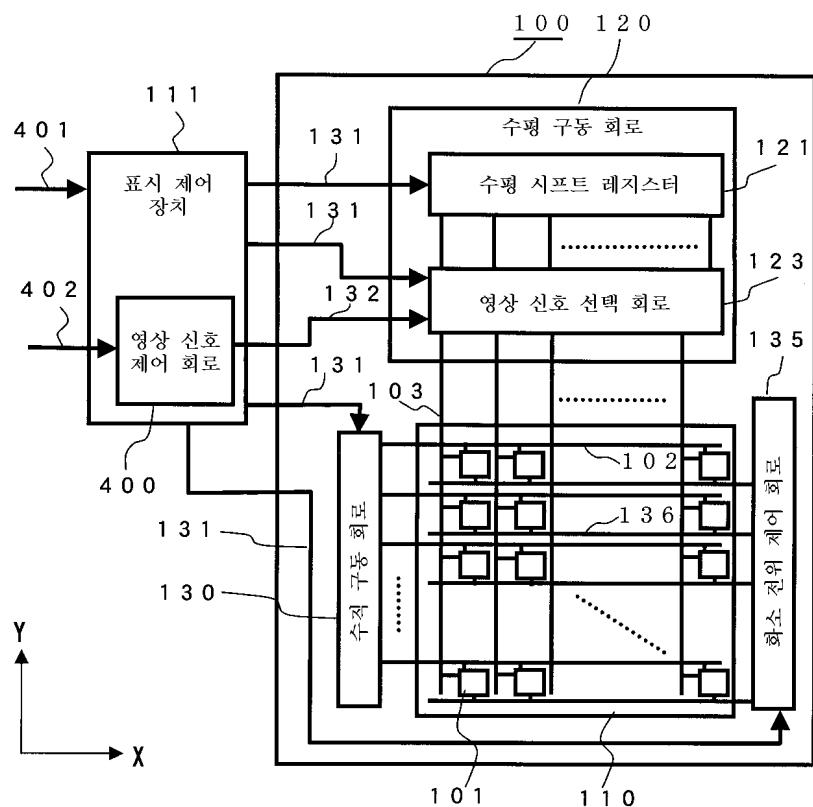

도 2는 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

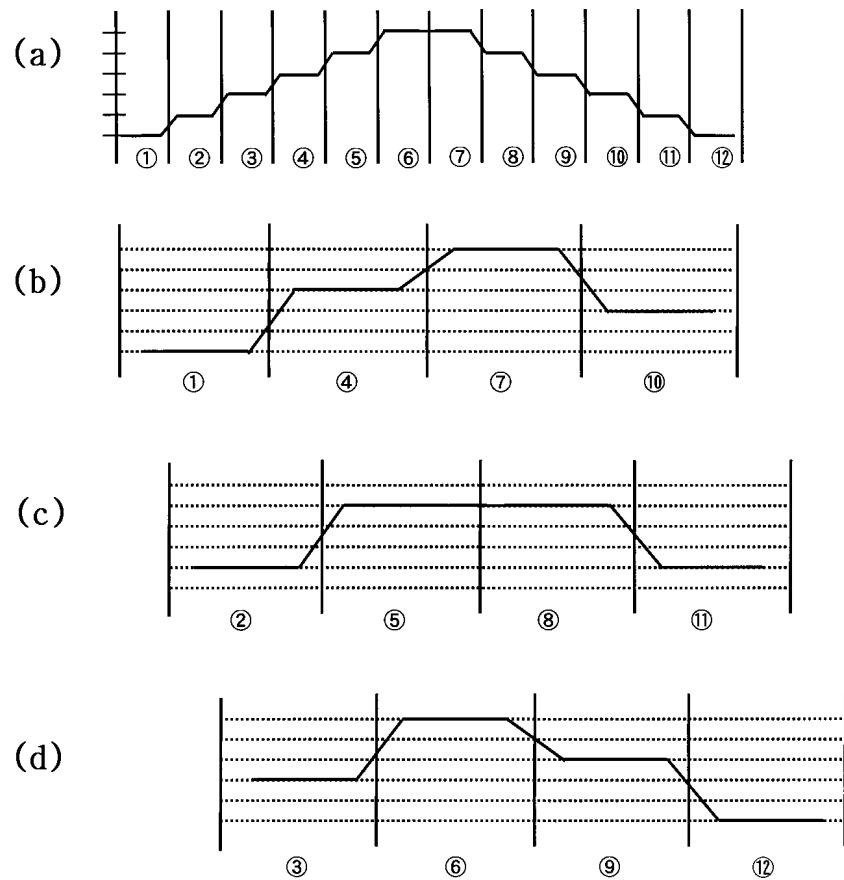

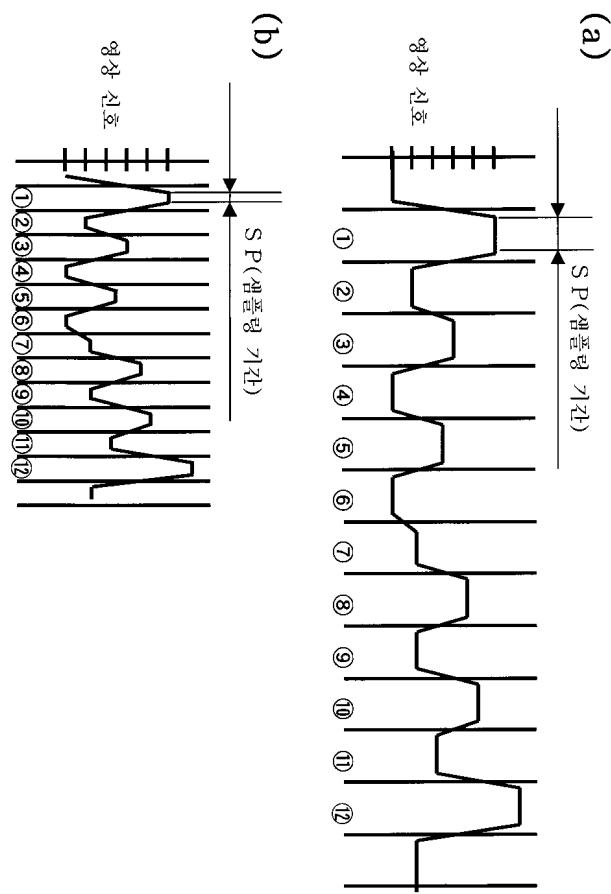

도 3은 상전개를 설명하는 타이밍도.

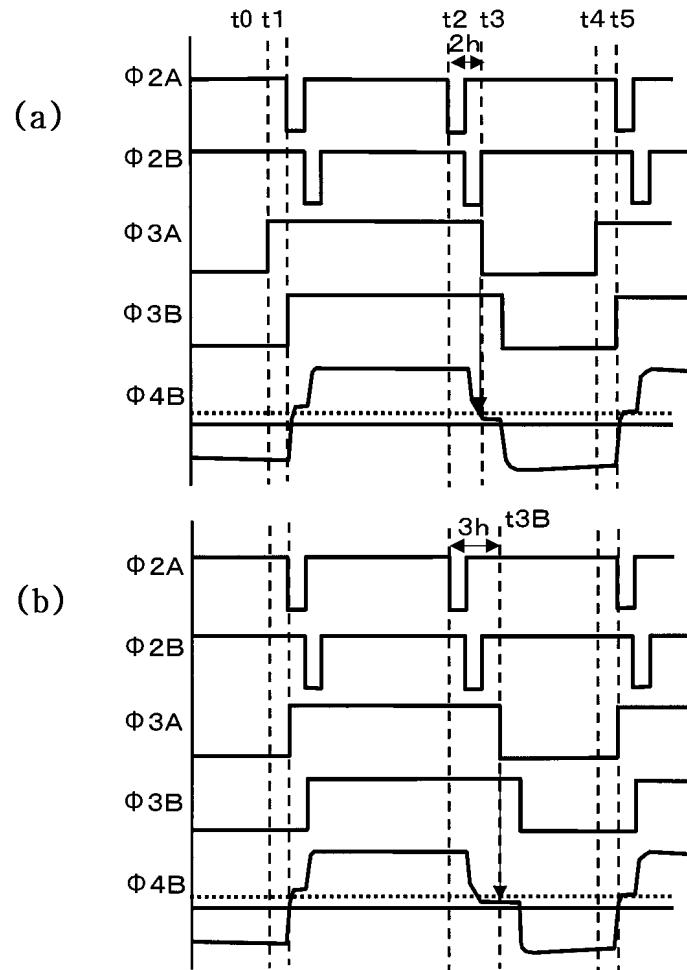

도 4는 샘플 홀드 회로를 설명하는 타이밍도.

도 5는 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

도 6은 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

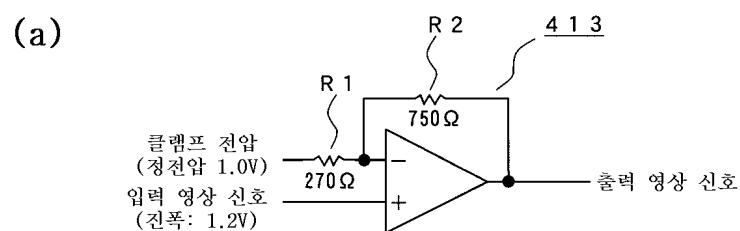

도 7은 증폭 회로의 변동을 설명하는 개략 회로도.

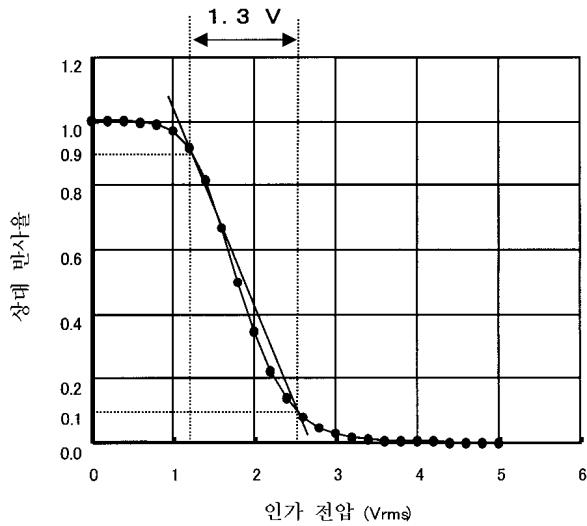

도 8은 본 발명의 실시 형태인 액정 표시 장치의 인가 전압-반사율 특성도.

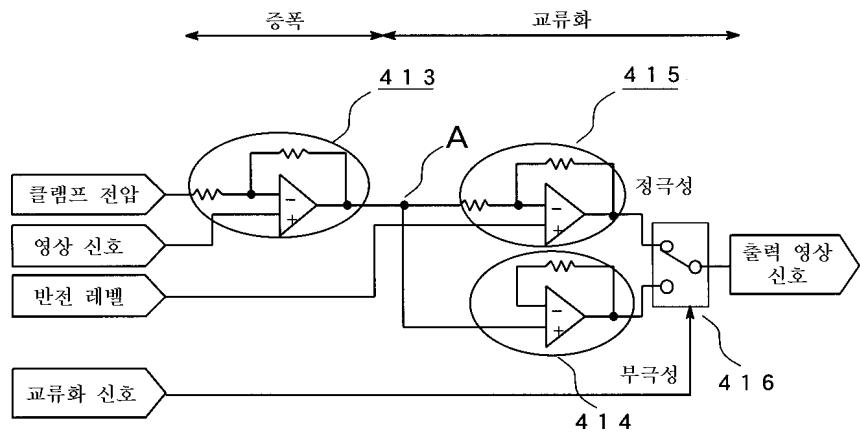

도 9는 교류화 회로의 변동을 설명하는 개략 회로도.

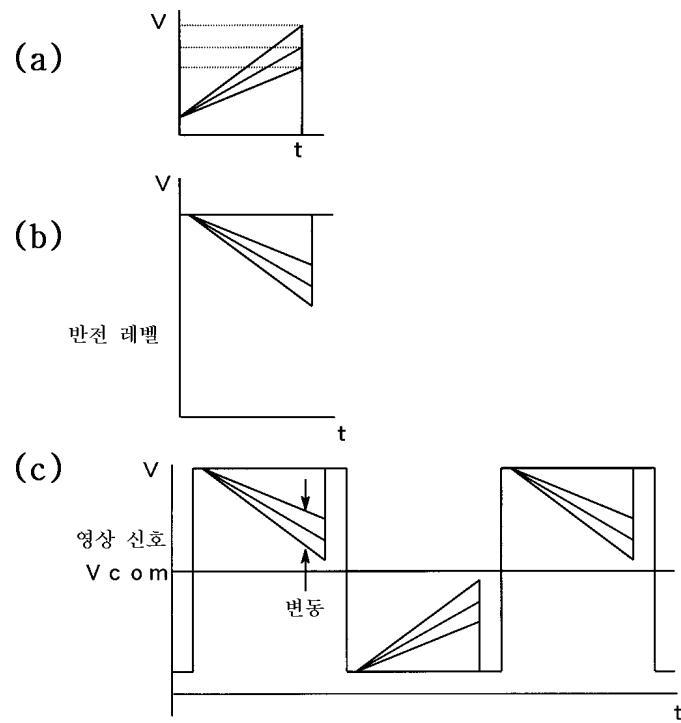

도 10은 교류화 회로의 변동을 설명하는 과정도.

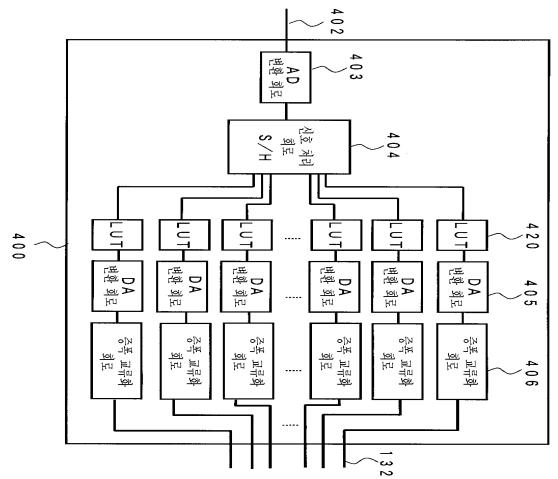

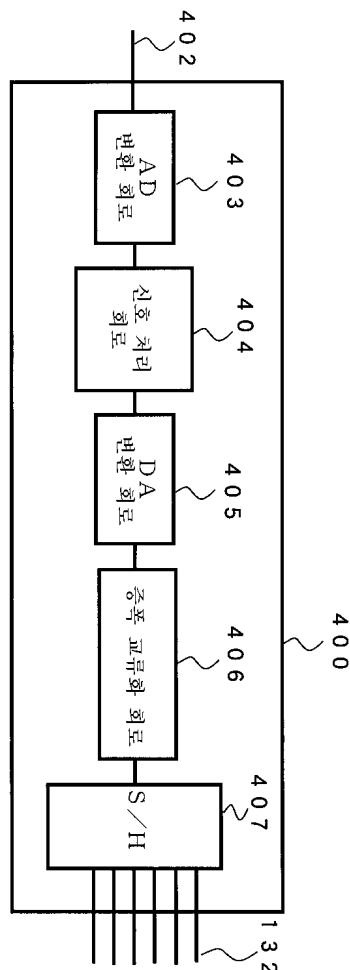

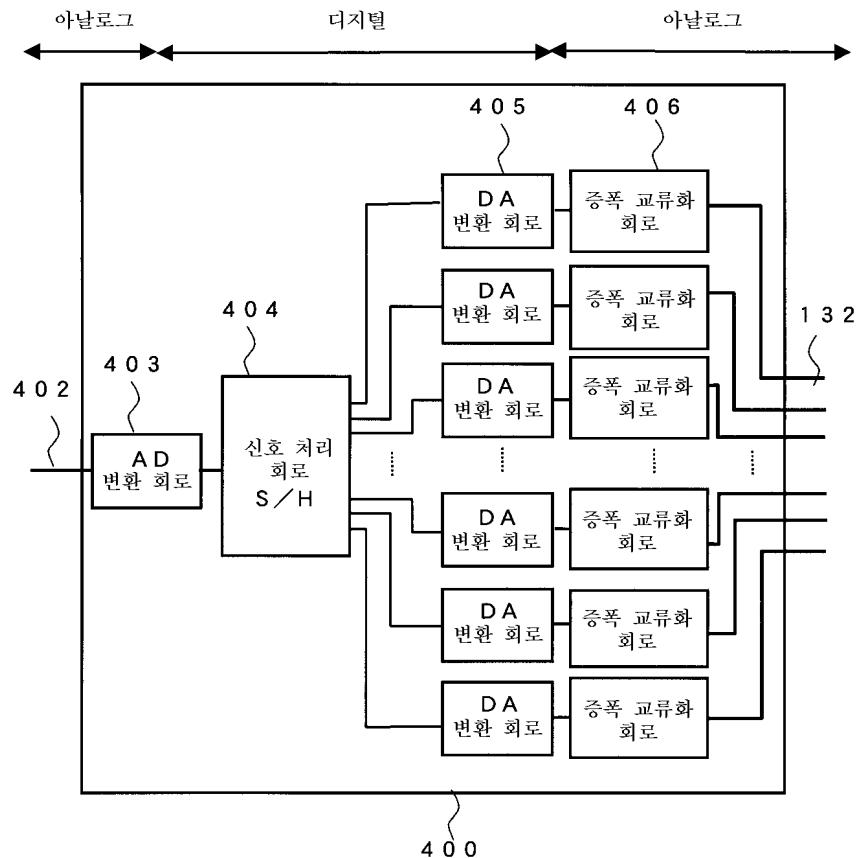

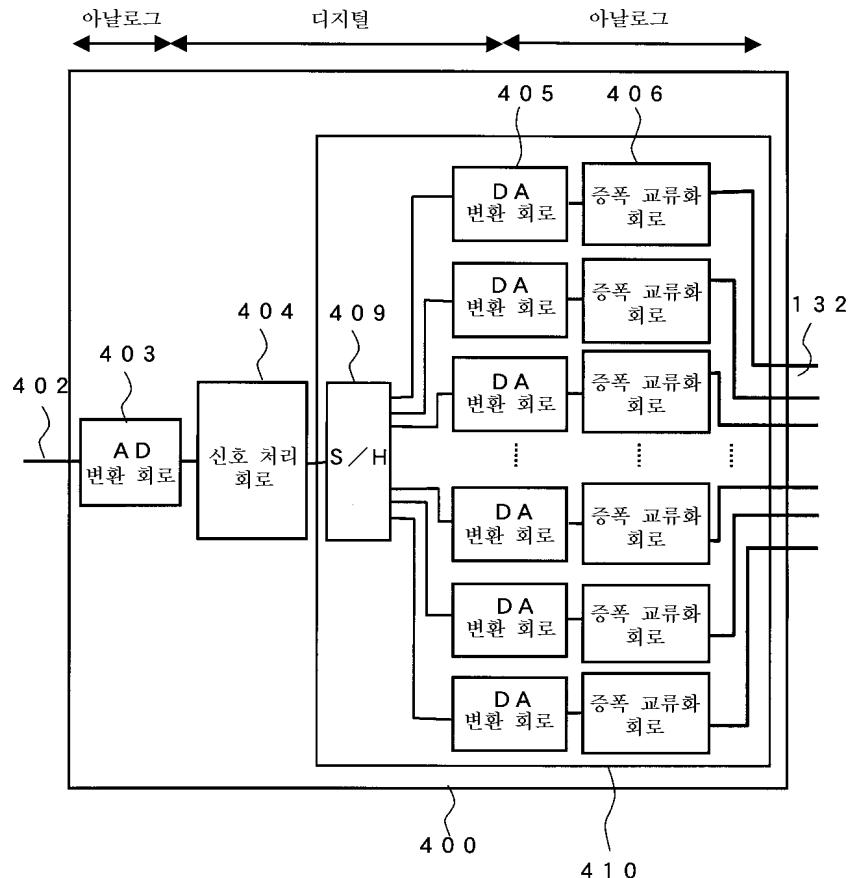

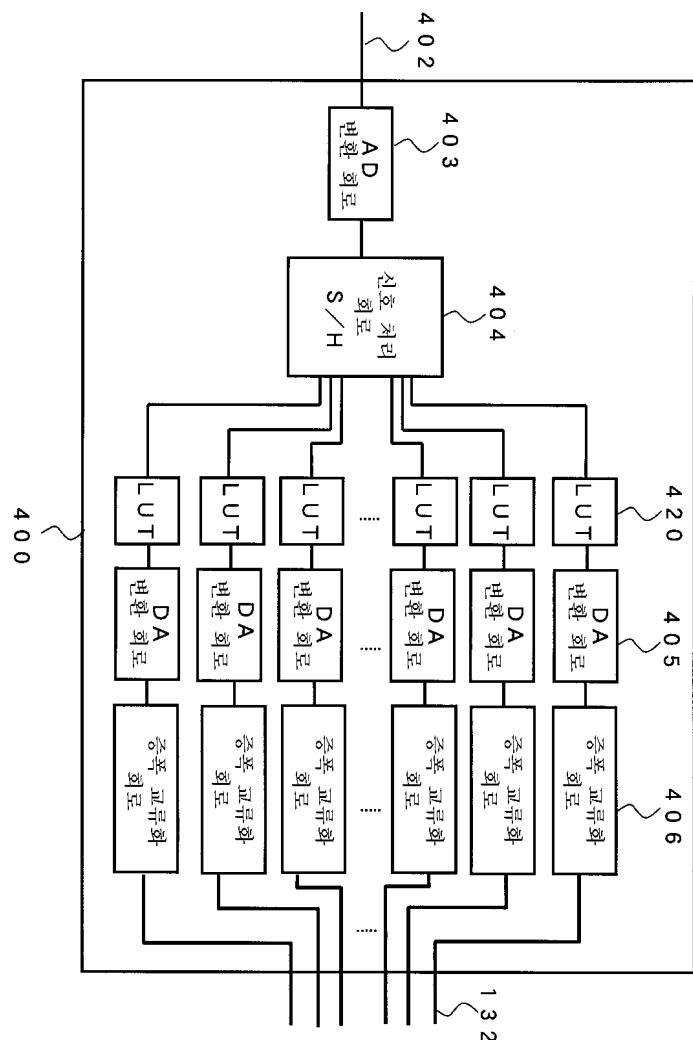

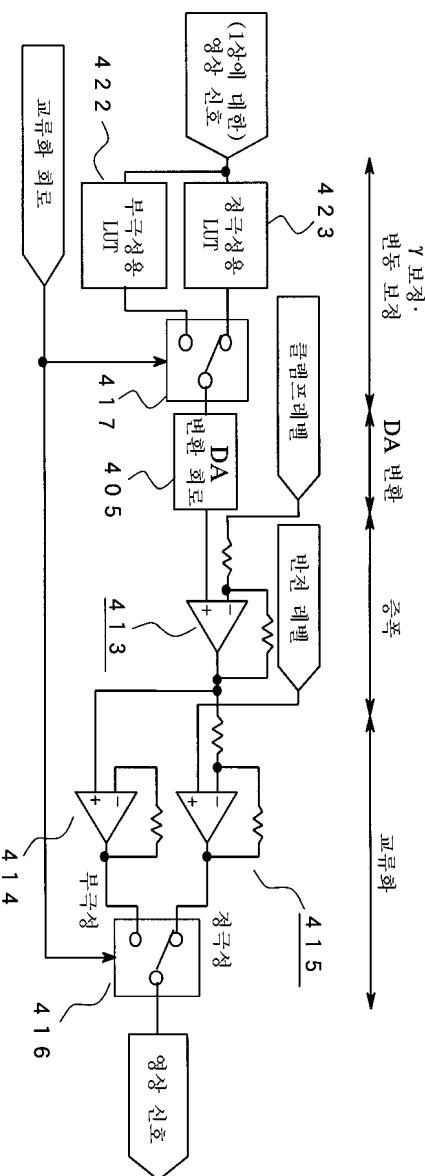

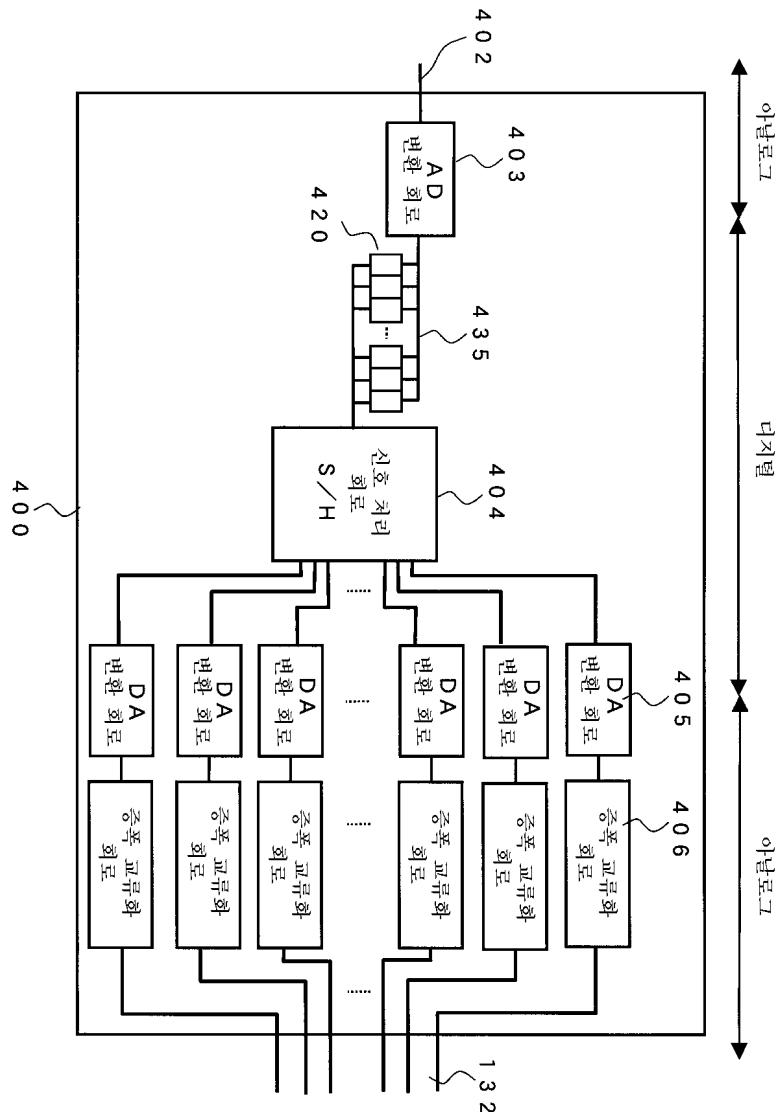

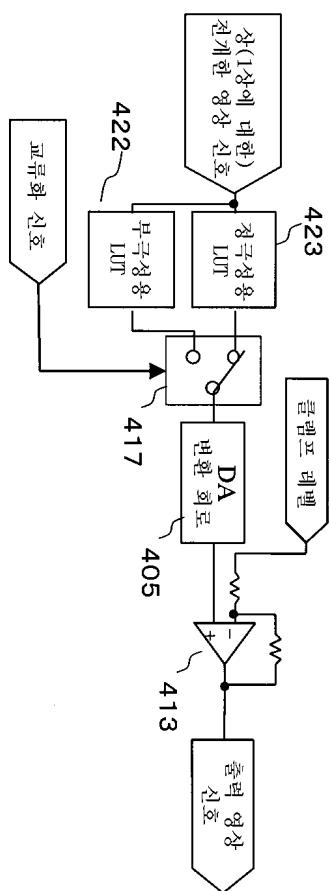

도 11은 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

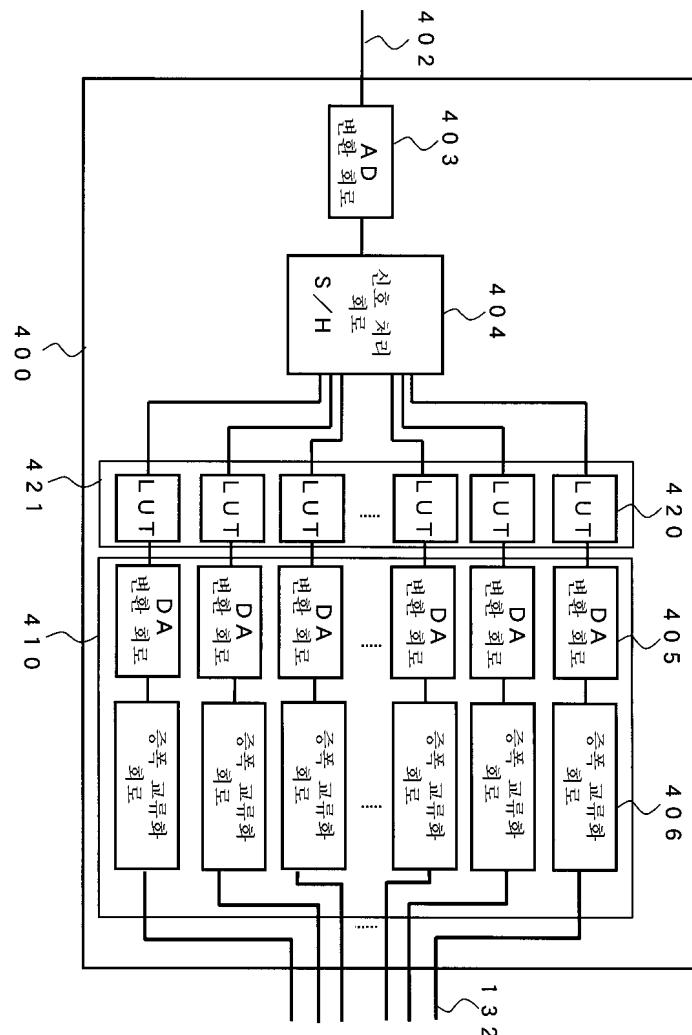

도 12는 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

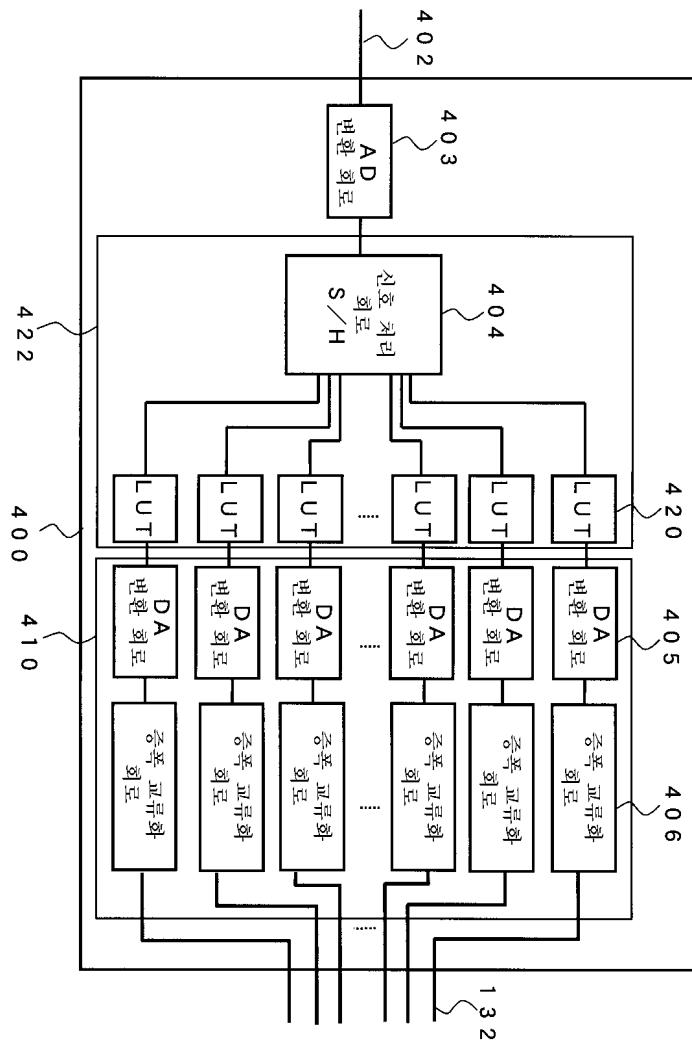

도 13은 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

도 14는 본 발명의 실시 형태인 액정 표시 장치의 참조표를 나타내는 데이터 구성도.

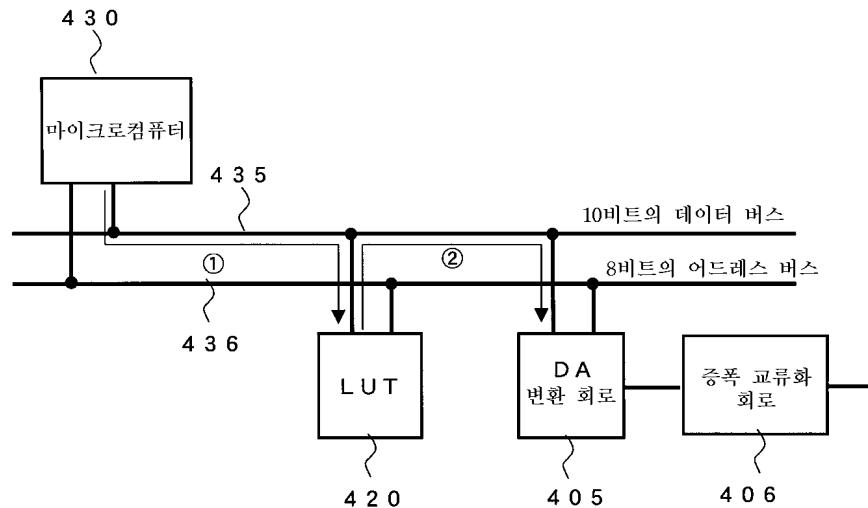

도 15는 본 발명의 실시 형태인 액정 표시 장치의 참조표에 데이터를 전송하는 경로를 도시하는 개략 회로도.

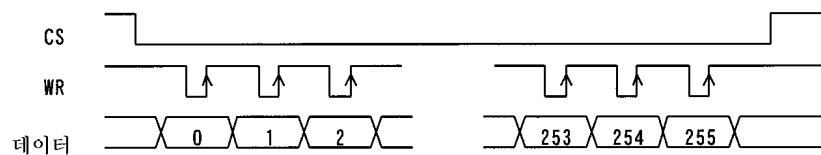

도 16은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 데이터를 전송하는 방법을 도시하는 타이밍도.

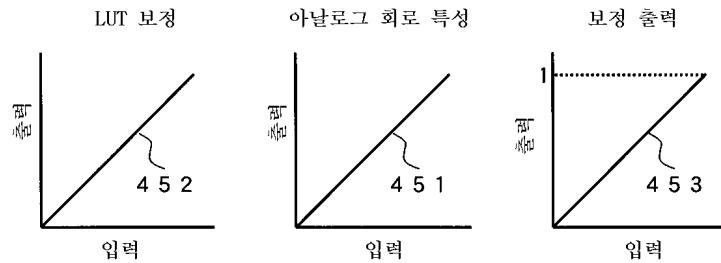

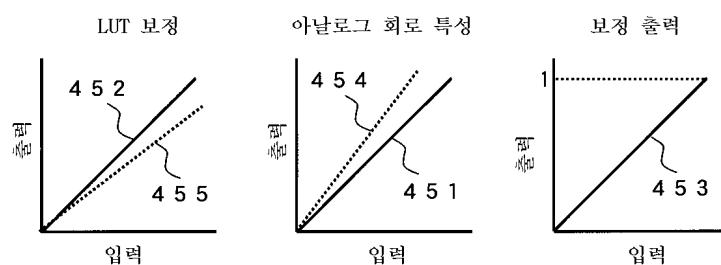

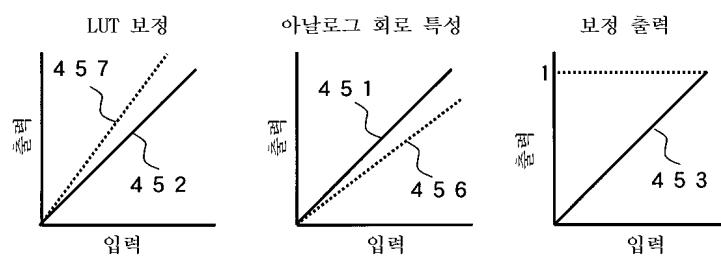

도 17은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의한 보정 방법을 도시하는 입력-출력 대조도.

도 18은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 교류화 변동을 보정하는 개략 회로도.

도 19는 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 영상 소스 간의 차이를 보정하는 개략 블록도.

도 20은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 의사적으로 계조를 증가시키는 방법을 설명하는 도면.

도 21은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 의사적으로 계조를 증가시키는 방법을 설명하는 도면.

도 22는 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 콘트라스트를 조정하는 방법을 설명하는 도면.

도 23은 본 발명의 실시 형태인 액정 표시 장치의 참조표에 의해 휘도를 조정하는 방법을 설명하는 도면.

도 24는 본 발명의 실시 형태인 액정 표시 장치의 참조표의 핀 수를 감소시키는 방법을 설명하는 개략 회로도.

도 25는 본 발명의 실시 형태인 액정 표시 장치의 영상 신호 제어 회로를 도시하는 블록도.

도 26은 본 발명의 실시 형태인 액정 표시 장치의 참조표의 데이터 전송 방법을 설명하는 개략 회로도.

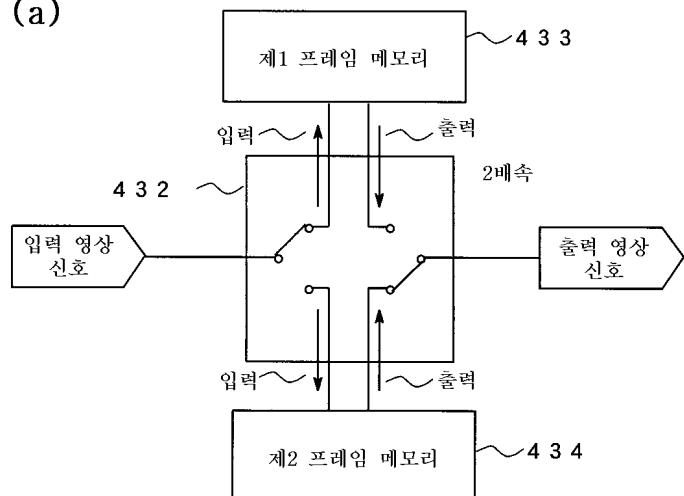

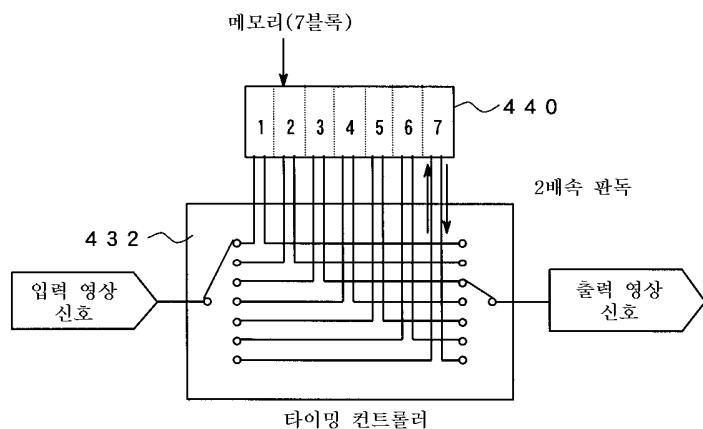

도 27은 본 발명의 실시 형태인 액정 표시 장치의 프레임 주파수를 체배화하는 방법을 설명하는 개략 회로도와 타이밍도.

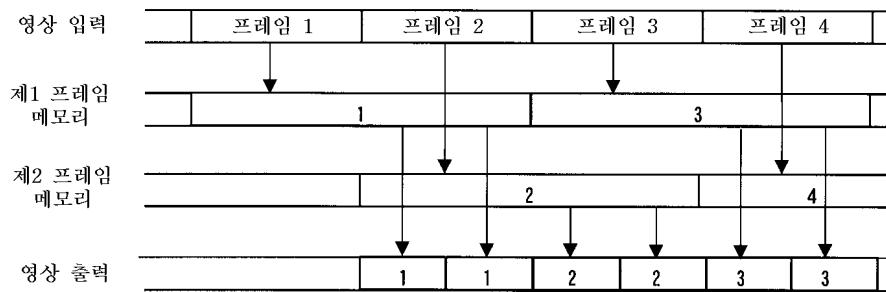

도 28은 본 발명의 실시 형태인 액정 표시 장치의 프레임 주파수를 체배화하는 방법을 설명하는 개략 회로도.

도 29는 본 발명의 실시 형태인 액정 표시 장치의 프레임 주파수를 체배화하는 방법을 설명하는 타이밍도.

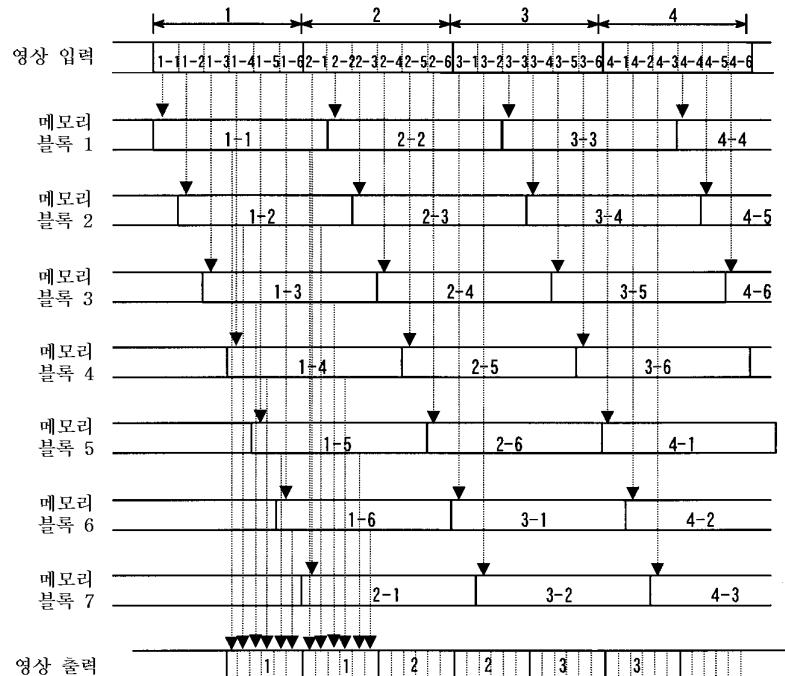

도 30은 본 발명의 실시 형태인 액정 표시 장치의 프레임 메모리를 이용하여 테스트 패턴을 표시하는 방법을 설명하는 개략 회로도.

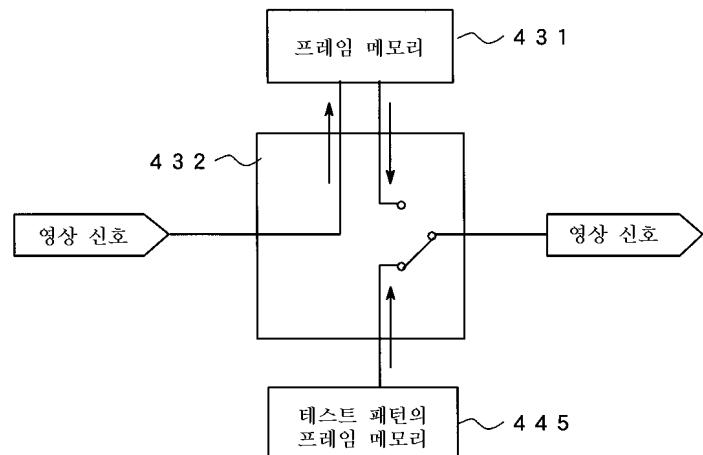

도 31은 본 발명의 실시 형태인 액정 표시 장치의 프레임 메모리를 이용하여 정지 화상을 표시하는 방법을 설명하는 개략 회로도.

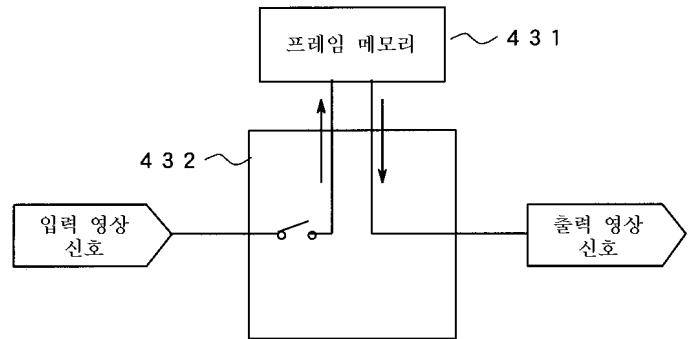

도 32는 본 발명의 실시 형태인 액정 표시 장치의 프레임 메모리를 이용하여 컨버전스를 조정하는 방법을 설명하는 개략 회로도.

도 33은 본 발명의 실시 형태인 액정 표시 장치의 화소부에 대하여 설명하는 블록도.

도 34는 본 발명의 실시 형태인 액정 표시 장치의 화소 전위를 제어하는 방법을 설명하는 개략 회로도.

도 35는 본 발명의 실시 형태인 액정 표시 장치의 화소 전위를 제어하는 방법을 설명하는 타이밍도.

도 36은 본 발명의 실시 형태인 액정 표시 장치의 화소 전위 제어 회로의 구성을 도시하는 개략 회로도.

도 37은 본 발명의 실시 형태인 액정 표시 장치의 클럭드 인버터의 구성을 도시하는 개략 회로도.

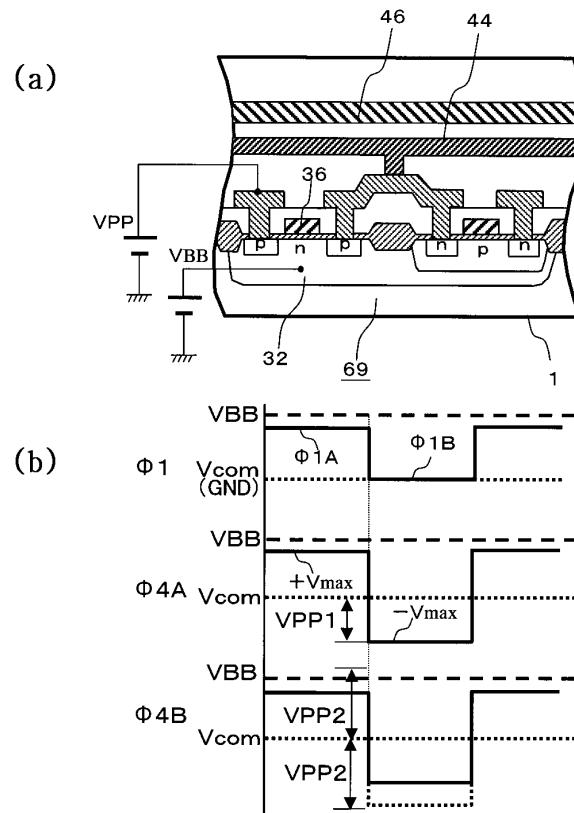

도 38은 본 발명의 실시 형태인 액정 표시 장치의 화소부를 도시하는 개략 단면도.

도 39는 본 발명의 실시 형태인 액정 표시 장치의 차광막을 이용하여 화소 전위 제어선을 형성하는 구성을 도시하는 개략 평면도.

도 40은 본 발명의 실시 형태인 액정 표시 장치의 구동 방법을 도시하는 타이밍도.

도 41은 본 발명의 실시 형태인 액정 표시 장치의 동작을 도시하는 개략도.

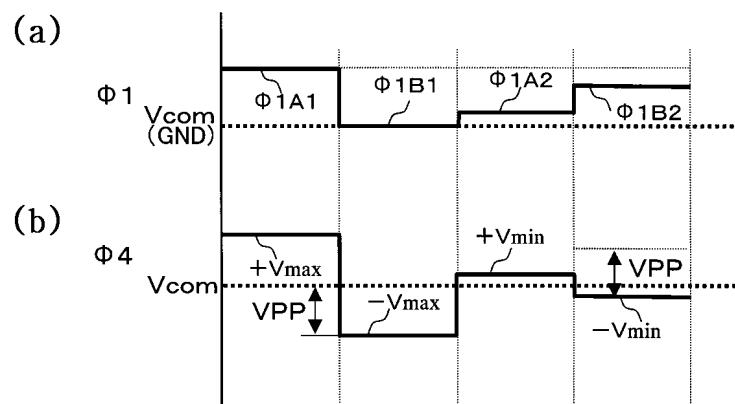

도 42는 본 발명의 실시 형태인 액정 표시 장치의 정극성, 부극성 과형을 설명하는 과형도.

도 43은 본 발명의 실시 형태인 액정 표시 장치의 정극성, 부극성 신호를 참조표를 이용하여 작성하는 개략 회로도.

도 44는 본 발명의 실시 형태인 액정 표시 장치의 동작을 설명하는 개략도.

도 45는 본 발명의 실시 형태인 액정 표시 장치의 액정 패널을 도시하는 개략 평면도.

도 46은 본 발명의 실시 형태인 액정 표시 장치의 더미 화소의 구동 방법을 도시하는 개략 회로도.

도 47은 본 발명의 실시 형태인 액정 표시 장치의 능동 소자 주변의 개략 단면도.

도 48은 본 발명의 실시 형태인 액정 표시 장치의 능동 소자 주변의 개략 평면도.

도 49는 본 발명의 실시 형태인 액정 표시 장치의 액정 패널을 도시하는 개략도.

도 50은 본 발명의 실시 형태인 액정 표시 장치의 액정 패널에 플렉시블 프린트 기판을 접속한 상태를 도시하는 개략도.

도 51은 본 발명의 실시 형태인 액정 표시 장치를 도시하는 개략 조립도.

도 52는 본 발명의 실시 형태인 액정 표시 장치를 도시하는 개략도.

<도면의 주요 부분에 대한 부호의 설명>

11 : 주변 프레임

12 : 시일재

14 : 외부 접속 단자

25 : 주사 리세트 신호 입력 단자

26 : 주사 스타트 신호 입력 단자

27 : 주사 종료 신호 출력 단자

28 : 리세트용 트랜지스터

30 : 능동 소자

34 : 소스 영역

35 : 드레인 영역

36 : 게이트 영역

38 : 절연막

39 : 필드 산화막

41 : 제1 층간막

42 : 제1 도전막

43 : 제2 층간막

44 : 제1 차광막

45 : 제3 층간막

46 : 제2 차광막

47 : 제4 층간막

48 : 제2 도전막

61~62 : 클럭드 인버터

65~66 : 클럭드 인버터

71 : 쿠션재

72 : 방열판

73 : 몰드

74 : 보호용 접착재

75 : 차광판

76 : 차광 프레임

80 : 플렉시블 배선판

100 : 액정 패널

101 : 화소부

102 : 주사 신호선

103 : 영상 신호선

104 : 스위칭 소자

107 : 대향 전극

108 : 액정 용량

109 : 화소 전극

110 : 표시부

111 : 표시 제어 장치

120 : 수평 구동 회로

121 : 수평 시프트 레지스터

122 : 표시 데이터 유지 회로

123 : 영상 신호 선택 회로

130 : 수직 구동 회로

131 : 제어 신호선

132 : 표시 데이터선

400 : 영상 신호 제어 회로

401 : 외부 제어 신호선

402 : 표시 신호선

403 : AD 변환 회로

404 : 신호 처리 회로

405 : DA 변환 회로

406 : 증폭 교류화 회로

407 : 샘플 홀드 회로

409 : 샘플 홀드 회로(디지털용)

410 : 아날로그 드라이버

413 : 연산 증폭기(증폭용)

414 : 연산 증폭기(부극성용)

415 : 연산 증폭기(정극성용)

416 : 아날로그 스위치(연산 증폭기 전환용)

417 : 아날로그 스위치(참조표 전환용)

418 : 아날로그 스위치(영상 소스 전환용)

420 : 참조표(LUT)

421 : 참조표(1 패키지)

422 : 정극성용 참조표

423 : 부극성용 참조표

424 : 제1 영상 소스용 참조표

425 : 제2 영상 소스용 참조표

426 : 제3 영상 소스용 참조표

427 : 제1 계조용 참조표

428 : 제2 계조용 참조표

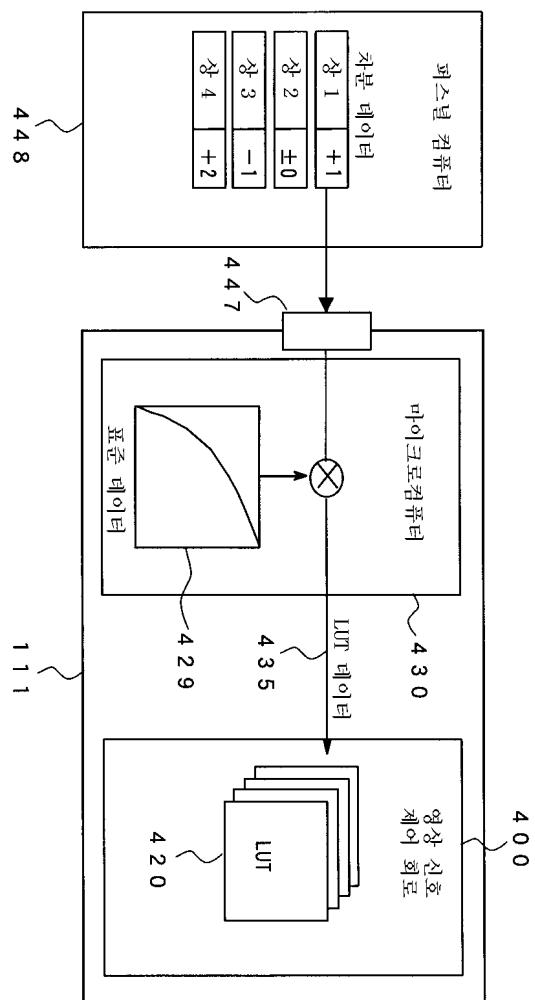

429 : 표준 참조표

430 : 마이크로 컴퓨터

431 : 프레임 메모리

432 : 타이밍 컨트롤러

433 : 제1 프레임 메모리

434 : 제2 프레임 메모리

435 : 데이터 버스

436 : 어드레스 버스

437 : 내부 스위치

438 : 외부 부착 스위치

440 : 블록 메모리

445 : 테스트 패턴 메모리

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 프로젝터용 표시 장치에 관한 것으로, 특히 증폭된 아날로그 영상 신호를 상(相)전개하여 입력하는 액정 표시 장치에서의 입력 화상 데이터의 화상 처리에 적용하기에 유효한 기술에 관한 것이다.

최근, 액정 표시 장치는 소형 표시 장치로부터 소위 OA 기기 등의 표시 단말용으로 널리 보급되고 있다. 이 액정 표시 장치는, 기본적으로는 적어도 한쪽이 투명한 유리판이나 플라스틱 기판 등으로 이루어지는 한쌍의 절연 기판 사이에 액정 조성물의 층(액정층)을 삽입하여 소위 액정 패널(액정 표시 소자 또는 액정 셀이라고도 함)을 구성한다.

이 액정 패널은 절연 기판에 형성한 화소 형성용 각종 전극에 선택적으로 전압을 인가하여 소정 화소 부분의 액정 조성물을 구성하는 액정 분자의 배향 방향을 변화시켜서 화소 형성을 행하는 형식(단순 매트릭스)과, 상기 각종 전극과 화소 선택용 능동 소자를 형성하여 이 능동 소자를 선택함으로써, 해당 능동 소자에 접속한 화소 전극과 상기 화소 전극에 대향하는 기준 전극 사이에 있는 화소의 액정 분자의 배향 방향을 변화시켜서 화소 형성을 행하는 형식(액티브 매트릭스)으로 크게 분류된다.

화소별로 능동 소자(예를 들면, 박막 트랜지스터)를 구비하고, 이 능동 소자를 스위칭 구동하는 액티브 매트릭스형 액정 표시 장치는 노트북 컴퓨터 등의 표시 장치로서 널리 사용되고 있다. 일반적으로, 액티브 매트릭스형 액정 표시 장치는 한쪽 기판에 형성한 전극과 다른 쪽 기판에 형성한 전극 사이에 액정층의 배향 방향을 변화시키기 위한 전계를 인가하는, 소위 종전계 방식을 채용하고 있다. 또, 액정층에 인가하는 전계의 방향을 기판면과 거의 평행한 방향으로 하는, 소위 횡전계 방식(IPS(In-Plane Switching) 방식이라고도 한다)의 액정 표시 장치가 실용화되어 있다.

한편, 액정 표시 장치를 이용하는 표시 장치로서, 액정 프로젝터가 실용화되어 있다. 액정 프로젝터는 광원으로부터의 조명광을 액정 패널에 조사하고, 액정 패널의 화상을 스크린에 투사하는 것이다. 액정 프로젝터에 이용되는 액정 패널에는 반사형과 투과형이 있는데, 액정 패널을 반사형으로 한 경우에는 화소의 거의 전역을 유효한 반사면으로 할 수 있어서, 액정 패널의 소형화, 고정밀화, 고휘도화에 있어서 투과형에 비해 유리하다. 또한, 액티브 매트릭스형 액정 표시 장치 내에 화소 전극을 형성한 기판 상에 화소 전극을 구동하는 구동 회로도 형성하는 소위 구동 회로로 일체형 액정 표시 장치가 알려져 있다.

또한, 구동 회로 일체형 액정 표시 장치에서 화소 전극 및 구동 회로를 절연 기판이 아니라, 반도체 기판 상에 형성한 반사형 액정 표시 장치(Liquid Crystal on Silicon, 이하 LCOS라고도 함)가 알려져 있다.

또한, 구동 회로 일체형 액정 표시 장치의 구동 방법에 있어서, 외부로부터 영상 신호를 액정 표시 장치에 아날로그 신호로 입력하고, 구동 회로에 의해 영상 신호를 샘플링하여 액정 패널로 출력하는 구동 방법이 알려져 있다.

### 발명이 이루고자 하는 기술적 과제

영상 신호를 샘플링하는 구동 방법으로는, 구동 회로가 영상 신호를 취득하는 시간을 확보하기 위해서, 영상 신호를 복수상으로 분할하는 방법(상전개)을 이용한다. 즉, 1개의 신호선에 의해 전송된 영상 신호를 복수개의 신호선으로 분배하여 전송한다. 영상 신호를 복수의 신호선으로 분배하여 출력함으로써, 동시에 복수의 회로에서 영상 신호를 취득할 수 있어, 그 때문에 영상 신호를 취득하기 위한 시간을 길게 하는 것이 가능하다. 그런데, 상전개함으로써 영상 신호를 취득하는 시간을 확보하는 것이 가능하지만, 회로의 변동에 의한 문제점이 생기는 것을 발견하였다. 즉, 복수의 신호선에는 영상 신호를 출력하기 위해 신호선마다 출력 회로를 형성되어 있다. 이 출력 회로의 특성에 변동이 있으면, 표시 화상에도 동일하게 변동이 생겨서 표시 품질이 저하한다는 문제가 발생한다.

### 발명의 구성 및 작용

복수의 아날로그 회로에 의한 변동을 보정하기 위하여, 디지털의 신호 처리 회로 내에 복수의 아날로그 회로만큼의 보정 수단을 가짐으로써, 보정 수단으로써 아날로그 회로의 변동의 보정을 행한다.

복수의 아날로그 회로마다 생기는 변동을 수정하는 데이터를 참조표로서 갖고 있으며, 디지털 신호를 참조표에 의해 보정함으로써, 아날로그 회로에 의해 생기는 변동을 보정한다.

### <발명의 실시 형태>

이하, 도면을 참조하여 본 발명의 실시 형태를 상세히 설명한다. 또, 발명의 실시 형태를 설명하기 위한 모든 도면에 있어서, 동일 기능을 갖는 것은 동일 부호를 붙여서 그 반복된 설명은 생략한다.

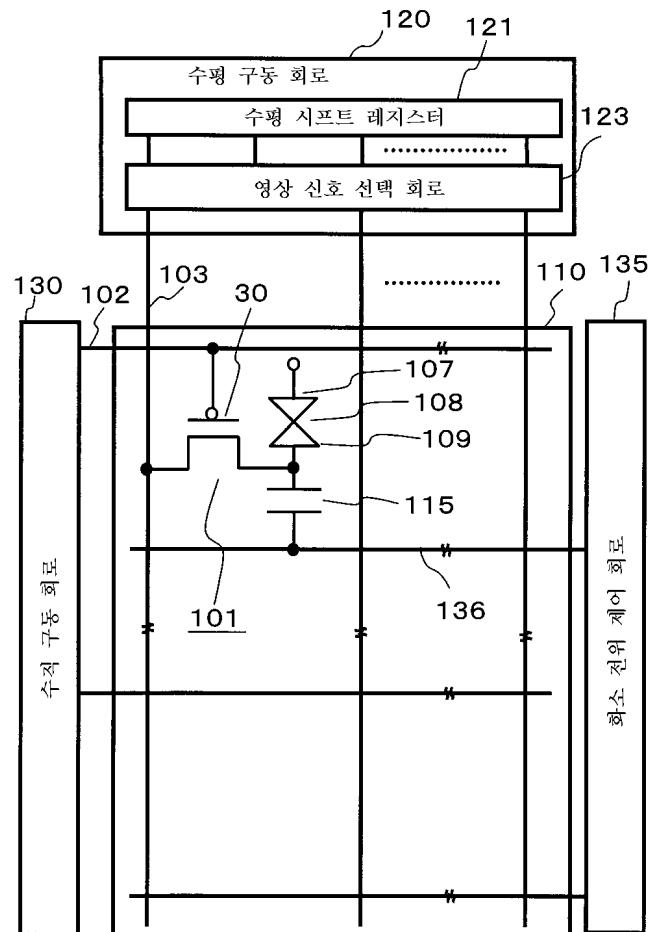

도 1은 본 발명의 실시 형태인 액정 표시 장치의 개략 구성을 도시하는 블록도이다.

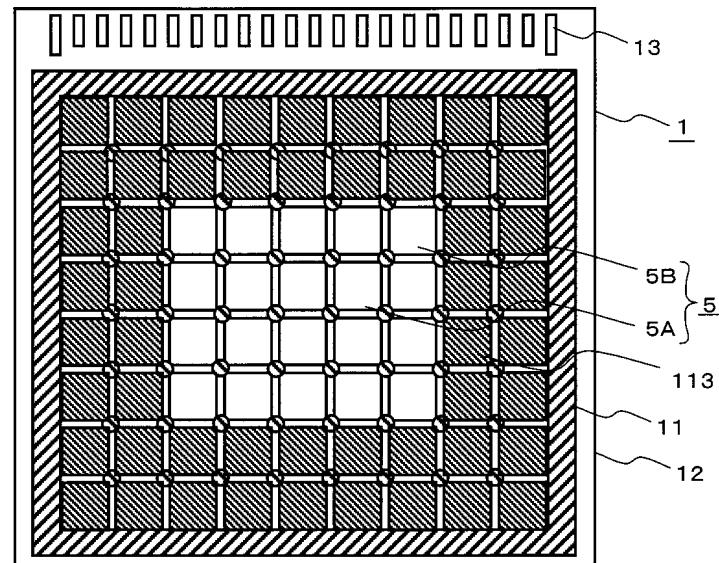

본 실시 형태의 액정 표시 장치는 액정 패널(액정 표시 소자: 100)과, 표시 제어 장치(111)로 구성된다. 액정 패널(100)은 매트릭스 형상으로 화소부(101)가 형성된 표시부(110)와, 수평 구동 회로(영상 신호선 구동 회로: 120)와, 수직 구동 회로(주사 신호선 구동 회로: 130)와, 화소 전위 제어 회로(135)로 구성된다. 또한, 표시부(110)와 수평 구동 회로(120)와 수직 구동 회로(130)와 화소 전위 제어 회로(135)는 동일 기판 상에 형성된다. 화소부(101)에는 화소 전극과 대향 전극과 양 전극에 샌드위치된 액정층이 형성된다(도시하지 않음). 화소 전극과 대향 전극 간에 전압을 인가함으로써, 액정 분자의 배향 방향 등이 변화하고, 그에 따라 액정층의 광에 대한 성질이 변화하는 것을 이용하여 표시가 행해진다. 또, 본 발명은 화소 전위 제어 회로(135)를 갖는 액정 표시 장치에 적용하기에 유효하지만, 화소 전위 제어 회로(135)를 갖는 액정 표시 장치에 한정되지는 않는다.

표시 제어 장치(111)에는 외부 장치(예를 들면, 퍼스널 컴퓨터 등)로부터 외부 제어 신호선(401)이 접속되어 있다. 표시 제어 장치(111)는 외부로부터 외부 제어 신호선(401)을 거쳐서 송신되는 클럭 신호, 디스플레이 타이밍 신호, 수평 동기 신호, 수직 동기 신호 등의 제어 신호를 이용하여, 수평 구동 회로(120) 및 수직 구동 회로(130), 화소 전위 제어 회로(135)를 제어하는 신호를 출력한다.

또한, 표시 제어 장치(111)는 영상 신호 제어 회로(400)를 갖고 있다. 영상 신호 제어 회로(400)에는 표시 신호선(402)이 접속되어 있어, 외부 장치로부터 표시 신호가 입력된다. 표시 신호는 액정 패널(100)에 표시하는 영상을 구성하도록 일정한 순서로 보내진다. 예를 들면, 액정 패널(100)의 좌측 위에 위치하는 화소를 선두로, 1 행분의 화소 데이터가 순서대로 보내지며 위에서 아래를 향하여 각 행의 데이터가 외부 장치로부터 순차 보내진다. 영상 신호 제어 회로(400)는 표시 신호를 기초로 영상 신호를 형성하고, 액정 패널(100)이 영상을 표시하는 타이밍에 맞추어서 영상 신호를 수평 구동 회로(120)에 공급한다.

참조 부호 131은 표시 제어 장치(111)로부터 출력하는 제어 신호선이고, 참조 부호 132는 영상 신호 전송선이다. 또, 도 1에서는 영상 신호 전송선(132)을 1개로 나타내고 있지만, 복수상으로 상전개하고 있어 복수개의 영상 신호 전송선(132)이 형성된다. 또, 상전개에 대해서는 후술한다.

영상 신호 전송선(132)은 표시 제어 장치(111)로부터 출력하여, 표시부(110)의 주변에 형성된 수평 구동 회로(120)에 접속한다. 수평 구동 회로(120)로부터는 수직 방향(도면 중 Y 방향)으로, 복수개의 영상 신호선(드레인 신호선 또는 수직 신호선이라고 함: 103)이 연장되어 있다. 또한 복수개의 영상 신호선(103)은 수평 방향(X 방향)으로 배열되어 형성된다. 영상 신호선(103)에 의해 영상 신호가 화소부(101)에 전해진다.

또한, 표시부(110)의 주변에는 수직 구동 회로(130)도 형성된다. 수직 구동 회로(130)로부터는 수평 방향(X 방향)으로 복수개의 주사 신호선(게이트 신호선 또는 수평 신호선이라고도 함: 102)이 연장된다. 또한 복수개의 주사 신호선(102)은 수직 방향(Y 방향)으로 배열되어 형성된다. 주사 신호선(102)에 의해 화소부(101)에 형성된 스위칭 소자를 온/오프하는 주사 신호가 전해진다.

또한, 표시부(110)의 주변에는 화소 전위 제어 회로(135)가 형성된다. 화소 전위 제어 회로(135)로부터는 수평 방향(X 방향)으로 복수개의 화소 전위 제어선(136)이 연장된다. 또한 복수개의 화소 전위 제어선(136)은 수직 방향(Y 방향)으로 배열되어 형성된다. 화소 전위 제어선(136)에 의해 화소 전극의 전위를 제어하는 신호가 전해진다.

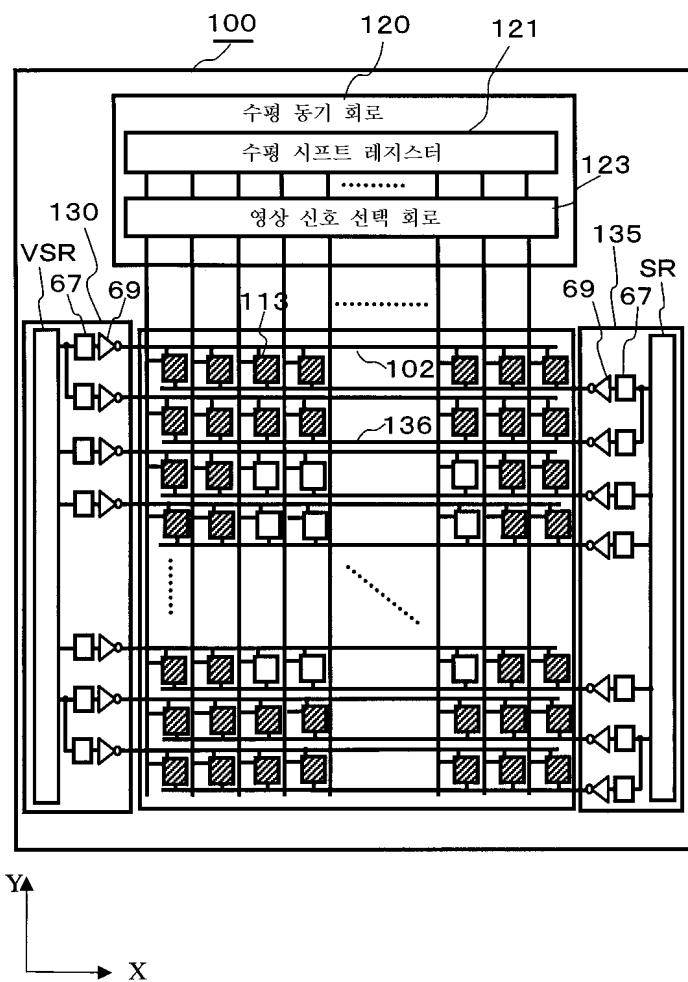

수평 구동 회로(120)는 수평 시프트 레지스터(121)와, 영상 신호 선택 회로(123)를 포함한다. 표시 제어 장치(111)로부터 제어 신호선(131)이나 영상 신호 전송선(132)이 수평 시프트 레지스터(121)와 영상 신호 선택 회로(123)에 접속되어, 제어 신호나 영상 신호가 송신된다. 또, 각 회로의 전원 전압선에 대해서는 표시를 생략하였지만, 필요한 전압이 공급되는 것으로 한다.

표시 제어 장치(111)는 외부로부터 수직 동기 신호 입력 후에, 제1번째의 디스플레이 타이밍 신호가 입력되면, 제어 신호선(131)을 통해 수직 구동 회로(130)에 스타트 펄스를 출력한다. 다음에, 표시 제어 장치(111)는 수평 동기 신호에 기초하여, 1수평 주사 시간(이하, 1h로 나타낸다)마다 주사 신호선(102)을 순차 선택하도록 시프트 클럭을 수직 구동 회로(130)에 출력한다. 수직 구동 회로(130)는 시프트 클럭에 따라 주사 신호선(102)을 선택하고, 주사 신호선(102)에 주사 신호를 출력한다. 즉, 수직 구동 회로(130)는 도 1 내에서 순서대로 1수평 주사 시간 1h 동안에, 주사 신호선(102)을 선택하는 신호를 출력한다.

또한, 표시 제어 장치(111)는 디스플레이 타이밍 신호가 입력되면, 이것을 표시 개시라고 판단하고, 영상 신호를 수평 구동 회로(120)에 출력한다. 표시 제어 장치(111)로부터 영상 신호는 순차 출력되지만, 수평 시프트 레지스터(121)는 표시 제어 장치(111)로부터 보내지는 시프트 클럭에 따라 타이밍 신호를 출력한다. 타이밍 신호는 영상 신호 선택 회로(123)가 각 영상 신호선(102)에 출력해야 할 영상 신호를 취득하는 타이밍을 나타낸다.

즉, 영상 신호 선택 회로(123)는 각 영상 신호선(103)마다 영상 신호를 취득하고, 유지하는 회로(샘플 홀드 회로)를 갖고 있고, 이 샘플 홀드 회로는 타이밍 신호가 입력되면 영상 신호를 취득한다. 표시 제어 장치(111)는 특정한 샘플 홀드 회로에 타이밍 신호가 입력되는 타이밍에 맞추어서, 해당하는 샘플 홀드 회로가 취득해야 할 영상 신호를 출력한다. 영상 신호는 아날로그 신호로, 영상 신호 선택 회로(123)는 타이밍 신호에 따라 아날로그 신호 중에서 일정한 전압을 영상 신호(계조 전압)로서 취득하고, 그 취득한 영상 신호를 영상 신호선(103)에 출력한다. 영상 신호선(103)에 출력된 영상 신호는 수직 구동 회로(130)로부터의 주사 신호가 출력되는 타이밍에 따라 화소부(101)의 화소 전극에 기입된다.

화소 전위 제어 회로(135)는 표시 제어 장치(111)로부터의 제어 신호에 기초하여, 화소 전극에 기입된 영상 신호의 전압을 제어한다. 영상 신호선(103)으로부터 화소 전극에 기입된 계조 전압은 대향 전극의 기준 전압에 대하여 임의의 전위차를 갖고 있다. 화소 전위 제어 회로(135)는 화소부(101)에 제어 신호를 공급하여 화소 전극과 대향 전극 간의 전위차를 변화시킨다. 또, 화소 전위 제어 회로(135)에 대해서는 후술한다.

다음에 도 2를 이용하여 영상 신호 제어 회로(400)에 대하여 설명한다. 도 2는 본 발명의 1 실시 형태인 액정 표시 장치의 영상 신호 제어 회로(400)의 회로 구성을 도시하는 개략 블록도이다. 상술한 바와 같이, 외부로부터 표시 신호선(402)을 통해 표시 신호가 영상 신호 제어 회로(400)에 입력된다. 참조 부호 403은 AD 변환 회로이다. 표시 신호가 아날로그 신호인 경우에, AD 변환 회로(403)로써 표시 신호를 디지털 신호로 변환한다. 참조 부호 404는 신호 처리 회로로서,  $\gamma$  보정, 해상도 변환 등의 신호 처리가 행해진다. 또, 표시 신호가 디지털 신호인 경우에는 직접 또는 각종 인터페이스 회로를 거쳐서 신호 처리 회로(404)에 표시 신호가 입력된다.

또한, 신호 처리 회로(404)에서는 프레임 주파수의 체배화가 행해진다. 외부로부터 표시에 필요한 신호는 영상 신호 제어 회로(400)에 1 화면마다 보내진다. 이 1 화면분의 표시에 필요한 신호가 보내지는 기간을 1 프레임 주기로 하고, 프레임 주기의 역수를 프레임 주파수로 한다. 특히 외부로부터 액정 표시 장치에 신호가 보내지는 경우를 외부 프레임 주기, 표시

제어 장치(111)가 액정 패널(100)에 신호를 보내는 경우를 액정 구동 프레임 주기라고 한다. 신호 처리 회로(404)에서는 외부 프레임 주파수에 대하여 액정 구동 프레임 주파수를 몇배로 올린다. 프레임 주파수의 체배화는 플리커를 방지할 목적으로 행해진다. 또, 프레임 주파수의 체배화에 대해서도 후술한다.

참조 부호 405는 DA 변환 회로이다. DA 변환 회로(405)에서는 신호 처리 회로(404)에서 신호 처리한 디지털 신호를 아날로그 신호로 변환한다. 참조 부호 406은 증폭 교류화 회로이다. 증폭 교류화 회로(406)는 DA 변환 회로(405)로부터 출력한 아날로그 신호를 증폭하고 교류화한다.

일반적으로 액정 표시 장치에서는 액정층에 인가하는 전압의 극성을 주기적으로 반전시키는 교류화 구동이 행해진다. 교류화 구동을 행하는 목적은 직류 전압이 액정에 인가되는 것에 의한 열화를 방지하기 위해서이다. 화소부(101)에는 상술한 바와 같이 화소 전극과 대향 전극이 형성되어 있지만, 교류화 구동을 행하는 하나의 방법으로서, 대향 전극에 정전압을 인가하고, 화소 전극에 대향 전극에 대하여 정극성, 부극성의 계조 전압을 인가한다. 또, 본 명세서에서는 정극성과 부극성의 전압은 대향 전극의 전위를 기준으로 한 화소 전극의 전압을 나타내고 있다. 반사형 액정 표시 장치 LCOS에서는, 이 교류화 구동을 프레임 주기로 행한다(프레임 반전). 라인 반전, 도트 반전이 이용되지 않은 이유는 반사형 액정 표시 장치 LCOS에서는 블랙 매트릭스를 형성하지 않기 때문에, 라인 반전, 도트 반전으로 생기는 불필요한 횡전계에 의한 광 누설을 숨길 수 없기 때문이다. 단, 프레임 반전을 행하면, 프레임 주기로 표시면에 플리커가 생긴다(면(面) 플리커). 상술한 바와 같이, 프레임 주기를 사람의 눈의 응답 시간보다 짧게 함으로써, 면 플리커를 저감한다.

참조 부호 407은 샘플 홀드 회로이다. 샘플 홀드 회로(407)에서는, 증폭 교류화 회로(406)로부터 출력한 영상 신호를 일정한 기간마다 취득하여, 영상 신호 전송선(132)에 출력한다. 상술한 바와 같이 영상 신호 전송선(132)은 복수개 형성되며, 샘플 홀드 회로(407)는 취득한 전압을 영상 신호 전송선(132)에 순서대로 출력한다. 그를 위해서, 영상 신호는 복수상으로 상전개되어 영상 신호 전송선(132)에 출력한다.

도 3을 이용하여 상전개에 대하여 설명한다. 또, 도 3에서는 설명을 간략화하기 위해서, 영상 신호 전송선(132)이 3개인 경우, 즉 3상으로 상전개하는 경우에 대해 도시한다. 도 3의 (a)는 샘플 홀드 회로(407)에 입력하는 영상 신호를 도시한다. 샘플 홀드 회로(407)는 원문자 숫자로 나타내는 기간에 영상 신호를 취득한다. 도 3의 (b)는 1번째의 영상 신호 전송선(132)에 출력되는 영상 신호를 도시한다. 샘플 홀드 회로(407)로부터 1번째의 영상 신호 전송선에는 기간 ①과, ④와, ⑦과 같이 3 기간 취득한 영상 신호가 출력되어 있다. 또한, 3개의 영상 신호 전송선(132)으로 나누어서 영상 신호를 전송함으로써, 영상 신호가 출력되는 기간을 3배로 하는 것이 가능하게 되어 있다. 도 3의 (c)는 2번째의 영상 신호 전송선(132)에 출력되는 영상 신호를 도시하며, 도 3의 (d)는 3번째의 영상 신호 전송선(132)에 출력되는 영상 신호를 도시한다.

영상 신호를 상전개함으로써, 액정 패널(100)에 형성된 영상 신호 선택 회로(123)에 있어서, 영상 신호를 취득하는 기간을 길게 하는 것이 가능해진다. 단, 샘플 홀드 회로(407)는 고속의 신호를 샘플 홀드하는 것이 가능한 고성능의 회로가 이용된다. 또, 이미 1단 샘플 홀드함으로써, 상전개 후의 영상 신호의 위상을 갖출 수 있다. 영상 신호의 위상을 갖춤으로써, 액정 패널(100) 내의 영상 신호 선택 회로(123)에서 동일한 샘플링 클럭을 이용하여 영상 신호를 샘플링하는 것이 가능해진다.

다음에 도 4를 이용하여 도 2에 도시하는 샘플 홀드 회로(407)의 문제점에 대하여 설명한다. 도 2에 도시하는 회로 방식으로는, 도 4의 (a)에 도시한 바와 같이 신호가 저속인 경우에는 샘플링 기간 SP가 충분히 길기 때문에, 샘플 홀드 회로(407)에 있어서 올바른 신호 레벨을 샘플링하는 마진은 충분하며, 샘플 홀드 회로(407)에 의한 변동은 작다. 그러나, 해상도가 높아짐에 따라, 또는 프레임 주파수의 체배화에 의해 신호가 고속으로 된 경우, 도 4의 (b)에 도시한 바와 같이 영상 신호 파형이 삼각파에 근접하게 되며, 샘플링 클럭의 위상 어긋남이나 노이즈 등에 의해 올바른 신호 레벨을 샘플링하는 기간이 적어져서, 쉽게 오샘플링되며, 샘플링 타이밍의 어긋남에 의한 레벨 변동이 커진다. 이것은, 표시 계조가 잘못 표시된 것으로, 표시 품질을 저하시키게 된다.

그래서 고해상도, 고프레임 주파수에서의 오샘플링에 대한 대책으로서, 도 5에 도시한 바와 같은 구성의 회로를 개발하였다. 본 회로는 도 2의 구성에 대하여, 샘플 홀드 처리를 디지털 신호로써 행하는 것이다. 외부로부터의 영상 신호는 AD 변환 회로(403)에 의해 디지털 신호로 변환된다. 디지털화한 신호는 신호 처리 회로(404)에서  $\gamma$  보정, 해상도 변환, 프레임레이트 변환 등의 신호 처리를 행한 후, 디지털 신호 채로 샘플 홀드되어 상전개한다. 디지털 신호 채로 상전개하기 때문에 샘플 홀드 변동은 현저히 개선되며, 아날로그 신호를 상전개했을 때의 샘플 홀드 변동은 발생하지 않는다. 또, 전개한 각 상의 신호는 후단의 DA 변환 회로(405)로써 아날로그 신호로 변환되고 증폭/교류화된다.

도 6에 도 5의 회로의 후단 처리를 IC화한 구성을 도시한다. 참조 부호 410은 IC화된 아날로그 드라이버이다. 신호 처리 회로(404)로써  $\gamma$  보정, 해상도 변환, 프레임레이트 변환 등의 신호 처리를 한 디지털 신호가 아날로그 드라이버(410)에 입

력된다. 아날로그 드라이버(410) 내에서는 샘플 홀드 회로(409)에서 입력한 디지털 신호를 디지털인 채로 상전개하고, 각각의 상(相)의 디지털 신호를 DA 변환 회로(405)에서 DA 변환하고, 증폭 교류화 회로(406)로 증폭/교류화한다. 본 구성에서는 후단을 1 칩화할 수 있어, 회로가 간단하게 된다.

상술한 바와 같이 도 5, 도 6과 같은 구성에서는, 샘플 홀드를 디지털 신호에서 행하기 때문에, 샘플 홀드 변동은 발생하지 않는다. 그 때문에, 신호가 고속화한 경우에 특히 유효하다. 디지털 신호를 샘플 홀드하여 상전개하는 방법으로는 영상 신호는 "1"이나 "0"의 디지털 신호이며, 신호선 상에 출력된 전압이 변동되었다고 해도, 신호로서는 "1"이나 "0"의 값으로서 취득되기 때문에, 아날로그 신호에서 문제가 되는 변동은 발생하지 않는다.

또, 복수의 신호선으로 영상 신호를 분할하는 방법에 대해서도, 디지털 신호이기 때문에 아날로그 신호에 비하여 데이터의 유지가 용이하다. 영상 신호는 표시하는 화상의 해상도에 따른 주기의 신호가 화면을 구성하는 순서대로, 외부 장치(예를 들면, 퍼스널 컴퓨터)로부터 입력하고 있고, AD 변환 회로(403)로부터 출력되는 디지털 신호도 외부 장치로부터 입력되는 영상 신호의 주기와 순서에 따른다. 그 때문에, 취득한 디지털 신호를 순서대로 복수의 신호선으로 출력함으로써, 디지털 신호에서 상전개가 가능하다. 그러나, 발명자는 상전개한 후의 회로의 특성에 의해 각 상 간에 변동이 발생하는 문제를 발견하였다. 다음에, 이 상전개 후의 회로에 의해 발생하는 변동에 대하여 설명한다.

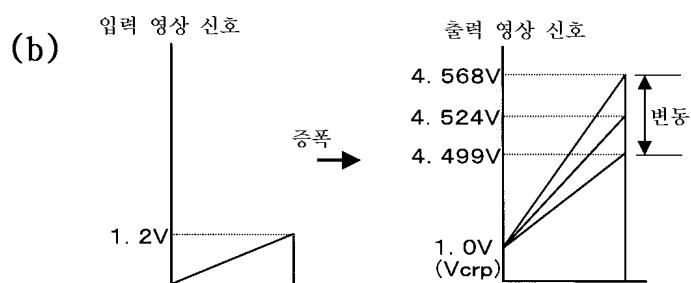

회로를 구성하는 부품에는 원래 특성의 변동이 있다. 도 44의 (b)에 연산 증폭기(413)에서 증폭 회로를 구성한 경우의 예를 도시한다. 이하 도 7의 (a)에 도시하는 예를 이용하여, 부품의 특성 변동에 의한 신호의 변동을 시산(試算)한다. 도 7의 (a)의 회로에서, 저항 R1의 저항치를  $270\Omega$ 으로 하고, 저항 R2의 저항치를  $750\Omega$ 로 하고, 이들 저항의 변동을  $\pm 0.5\%$ 로 하고, 연산 증폭기(413)의 개인 변동을  $\pm 0.025\%$ 로 하고, 영상 신호의 진폭을 1.2V로 하면, 연산 증폭기(413)의 증폭율은 R2/R1의 비로 결정되기 때문에, 특성 변동에 의해 증폭율이 최대가 되는 경우와 최소가 되는 경우의 출력 전압의 진폭을 구하면,

최대인 경우에는  $1.2V \times ((750 \times 1.005) \div (270 \times 0.995) + 1) \times 1.00025 = 4.568V$ 가 되며, 최소인 경우에는  $1.2V \times ((750 \times 0.995) \div (270 \times 1.005) + 1) \times 0.99975 = 4.499V$ 가 된다.

따라서, 최대인 경우와 최소인 경우의 차는  $4.568V - 4.499V = 0.069V$ 에 따라, 최대로  $69mV$ 의 변동이 생긴다. 이 증폭율의 변동은 도 7의 (b)에 도시한 바와 같은 과정이 되어 나타난다. 또, 클램프 전압 Vcrp는 일정전압이 공급되는데, 도 7의 (b)에서는 1.0V로 하였다.

또한, 도 8에 반사형 액정 표시 장치(LCOS)의 인가 전압-반사율 특성을 나타낸다. 상대 반사율 90%에서 인가 전압은 1.1V, 상대 반사율 10%에서 인가 전압은 2.4V가 되기 때문에, 1.3V의 전압차로 256 계조를 표시하게 되고, 도 8의 기울기는  $1.3V \div 256 = 5.1mV$  계조가 된다. 따라서 1 계조당 전압은 약  $5mV$ 가 된다. 따라서 변동이  $69mV$ 인 경우,  $69mV \div 5mV$  계조 = 13.8 계조가 된다. 따라서 이 경우,  $69mV$ 의 변동은 약 14 계조의 휘도차를 발생시킨다.

이 증폭 회로의 변동은 영상 신호 전송선(132) 사이에서의 변동이 된다. 영상 신호 전송선(132) 사이에서의 변동은 액정 패널 상의 표시 화상으로서는 주기성의 종선의 휘도차가 되어 나타나기 때문에, 현저하게 표시 품질을 저하시켜서 문제가 된다.

도 9에 도시한 바와 같이 증폭 교류화 회로는 증폭 회로가 갖는 연산 증폭기 외에, 교류화 회로도 연산 증폭기를 갖고 있고, 교류화 회로에서의 반전 변동도 생각된다. 또한, 액정 패널(100) 내에서의 트랜지스터의 특성 변동 등도 종선의 발생 요인으로서 들 수 있다.

도 10에 도 9에 도시하는 회로의 변동을 나타낸다. 도 10의 (a)는 도 7b에 도시하는 입력 과정이 연산 증폭기(413)에 입력되는 경우의 도 9의 절점 A에 출력하는 신호 과정을 도시한다. 도 10의 (b)는 정극성용 연산 증폭기(415)의 출력을 도시한다. 정극성용 연산 증폭기(415)는 증폭율이 1인 반전 증폭 회로에서 출력은 도 10의 (b)에 도시한 바와 같이 정전압으로 주어지는 반전 레벨 전압으로부터 입력 전압을 뺀 값이 된다. 부극성용 연산 증폭기(414)는 증폭율 1의 버퍼 증폭기로 입력 과정을 그대로 출력한다.

도 10의 (c)는 아날로그 스위치(416)를 이용하여, 부극성용 연산 증폭기(414)와 정극성용 연산 증폭기(415)와의 출력이 교대로 출력되는 모습을 도시한다. 또, 도 10의 (c)에 도시하는 영상 신호는 노멀 화이트인 경우를 도시한다. 그 때문에, 대향 전극의 기준 전극 Vcom에 대하여, 전위차가 적은 쪽이 고휘도(백표시)가 된다. 도 10의 (c)에 도시한 바와 같이, 각 회

로의 변동은 영상 신호 전송선(132) 사이에서의 변동이 된다. 예를 들면, 영상 신호 전송선(132)이 n개인 경우에, 1번 째가 최소이고 n번 째가 최대가 되도록 변동된 경우에, n개마다 액정 패널 상의 표시 화상에 종선이 나타나기 때문에, 현저히 표시 품질을 저하시키게 된다.

각 아날로그 회로를 조정함으로써, 변동을 보정하는 것은 가능하지만, 조정하는 부품수가 많아 양산성을 현저히 손상시킬 수 있다. 그래서, 아날로그 회로의 변동을 각 아날로그 회로에 입력하기 전의 디지털 신호에서 보정함으로써 저감시키도록 하였다.

도 11에 참조표를 이용하여 회로의 변동을 보정하는 회로 구성에 대하여 도시한다.

신호 처리 회로에서 디지털 신호를 샘플 홀드하여 상전개한 각 신호 라인은 각각 참조표(LUT: Look Up Table 이하 LUT라고 함)(420)를 가지며, 각 상 독립적으로 보정을 행한다. 각 상마다 변동이 다르기 때문에, 참조표(420)에는 사전에 최적의 데이터가 요구된다. 또한, 보정 데이터는 다른 메모리 등에 저장되어 있으며, 필요에 따라서 참조표(420)로 변동을 보정하는 데이터가 전송된다.

도 11에서, 신호 처리 회로(404)로써  $\gamma$  보정, 해상도 변환, 프레임레이트 변환 등의 신호 처리가 행해지며, 또한 상전개된 디지털 신호가 참조표(420)에 입력된다. 참조표(420)는 입력한 디지털 신호에 대응하는 디지털 데이터를 DA 변환 회로(405)로 출력한다. DA 변환 회로(405)는 디지털 데이터를 아날로그 신호로 변환하고 증폭 교류화 회로(406)로 출력한다.

참조표(420)에는 각 상마다 변동을 보정하는 데이터가 저장된다. 참조표(420)에 저장되는 보정 데이터의 설정은 표시 화면을 관찰, 평가하면서 행한다. 우선, 보정하지 않은 데이터(표준 데이터)를 참조표(420)에 저장하여 표시를 행하고, 각 상마다의 변동을 관찰한다. 그 후, 휙도가 저하하는 상은 휙도가 증가하는 계수가 표준 데이터에 걸려 보정 데이터가 되고, 휙도가 증가하는 상은 휙도가 감소하는 계수가 선택된다. 각 상마다의 휙도가 균일화되면, 그 경우의 계수가 최적의 계수로서 영상 신호 제어 회로(400)에 기록된다.

도 12에 도 11의 회로의 참조표(420)를 1 패키지화하고, 후단 처리를 IC화한 구성을 도시한다. 참조 부호 410은 IC화된 아날로그 드라이버이고, 참조 부호 421은 게이트 어레이 등으로 1 패키지화된 참조표(420)이다. 신호 처리 회로(404)로써  $\gamma$  보정, 해상도 변환, 프레임레이트 변환, 상전개 등의 신호 처리를 한 디지털 신호가 각 상마다 참조표(421)에 입력된다. 참조표(421)에서는 데이터를 보정하여 아날로그 드라이버(410)로 출력한다. 아날로그 드라이버(410)에서는 DA 변환, 증폭/교류화가 행해진다. 본 구성에서는 각 단을 1 패키지화할 수 있어 회로가 간단하게 된다.

또, 신호 처리 회로와 샘플 홀드 회로를 분리하여, 샘플 홀드 회로와 참조표를 1 패키지화하는 것도 가능하다. 또한, 1 패키지는 1 칩의 게이트 어레이로 구성하는 것도, 복수의 칩으로 분할하여 구성하는 것도 가능하다.

도 13에 신호 처리 회로(404)와 참조표(420)를 1 패키지로 구성하는 실시예를 도시한다. 참조 부호 422는 플랫 패키지로, 내부에 신호 처리 회로(404)와 참조표(420)를 갖는다. 신호 처리 회로(404)와 참조표(420)는 1 칩의 게이트 어레이로 구성하거나, 복수의 칩으로 구성하는 것도 가능하다.

도 14에 1색당 256 계조 데이터를 보정하는 참조표(420)의 데이터 구성의 실시예를 도시한다. 입력 데이터는 8 비트로 보정 데이터는 10 비트로 하였다. 보정 데이터는 충분히 계조 표현이 가능한 계조수만큼의 비트수를 사용한다. 참조표(420)는 기입 및 판독 가능한 메모리(RAM)로 구성되며, 입력된 256 계조의 영상 신호를 어드레스로 하여, 어드레스에 저장된 10 비트의 데이터를 보정 데이터로서 출력한다.

또, 보정 데이터를 출력하는 구성으로서는, 입력 데이터에 대하여 보정 데이터를 출력하는 기능을 갖는 것이면 이용 가능하다. 예를 들면, 입력 데이터에 대하여 보정 계수를 연산하여 보정 데이터를 출력하는 신호 처리 회로를 이용하는 것도 가능하다. 또한, 참조표는 어드레스와 그 각 어드레스에 데이터를 저장할 수 있는 것을 이용할 수 있는데, RAM 또는 ROM 등의 메모리로 구성하거나, 논리 회로로 구성하는 것도 가능하다.

도 14에 도시한 참조표(420)에 대한 보정 데이터 설정 방법의 예를 도 15에 도시한다. 영상 신호 제어 회로(400) 내부의 신호선의 구성은, 데이터 버스(435)는 10 비트, 어드레스 버스(436)는 8 비트로 구성된다. 또한, 데이터 처리용으로 마이크로 컴퓨터(430)가 형성된다. 또, 마이크로 컴퓨터(430)는 필요에 따라서 데이터 처리를 행할 수 있는 회로를 이용하는 것도 가능하다. 보정 데이터 설정 시에는 마이크로 컴퓨터(430)로부터 10비트×256의 보정용 데이터를 송신하여 참조표(420)용 RAM에 설정한다(경로 ①).

또, 병렬 통신에 의한 256 데이터의 설정 타이밍 예를 도 16에 도시한다. 마이크로 컴퓨터(430)는 RAM을 구성하는 칩의 칩 셀렉트 신호 CS를 로우 레벨로 한 후, 어드레스 버스(436)에 0~255의 값을 순서대로 출력한다. 또한, 어드레스의 출력과 동시에 각 어드레스별 보정 데이터를 데이터 버스(435) 상에 10 비트로 출력한다. 또한, 데이터 버스(435)에 보정 데이터를 출력한 상태에서 판독 기입 신호 WR을 출력한다. RAM은 판독 기입 신호 WR의 상승으로 데이터를 래치하고 저장한다. 어드레스는 판독 기입 신호 WR의 상승으로 인크리먼트되고, 데이터를 어드레스 0에서 순서대로 255까지 설정한다.

참조표(420)로부터 보정 데이터를 판독하는 경우에는 상전개된 디지털 신호가 어드레스 버스(436)에 설정되고, RAM은 어드레스 버스(436)가 지시하는 어드레스의 보정 데이터를 데이터 버스(435) 상에 출력한다(도 15 중 경로 ②). DA 변환 회로(405)는 데이터 버스(435)에 의해 입력되는 디지털 데이터를 아날로그 신호로 변환하여 증폭 교류화 회로에 출력한다.

참조표(420)에 의한 데이터의 보정을 도 17에 도시한다. 아날로그 회로에서 발생하는 특성 변동을 참조표(420)로써 역 방향으로 보정하고, 보정 후의 출력으로 변동을 최소로 한다. 도 17의 (a)는 아날로그 회로 특성이 이상적인 경우에, 입력에 대하여 정상적인 출력이 얻어진다. 선(451)은 입력에 대하여 정상적인 출력의 특성을 나타낸다. 선(451)으로 나타내는 특성은 정상적이기 때문에, 참조표(420)의 값은 보정을 하지 않은 값이 선택된다. 선(452)은 보정을 하지 않은 경우의 참조표(420)의 입력과 출력의 특성을 나타낸다.

다음에, 도 17의 (b)는 아날로그 회로 특성이 정상치에 대하여, 높은 값을 출력하는 경우를 도시한다. 선(454)은 입력에 대하여 출력이 높은 값이 되는 특성을 나타내는 선이다. 선(454)으로 나타내는 입력과 출력의 특성은 출력이 높은 값을 나타내기 때문에, 참조표(420)에서는 출력이 낮게 되는 보정 데이터가 선택된다. 참조표(420)의 특성은 선(455)으로 나타낸 바와 같이, 보정을 하지 않은 경우의 선(452)에 대하여 출력이 낮아지는 값으로 된다.

도 17의 (b)에서 도시하는 경우의 변동을 보정하는 방법으로서는, 액정 패널의 화상을 관찰하고, 고휘도의 상에 형성된 참조표의 특성이 도 17의 (b)의 선(455)이 되는 계수를 외부로부터 도 15에 도시하는 마이크로 컴퓨터(430)에 입력한다. 마이크로 컴퓨터(430)는 입력한 계수와 기준 데이터로부터 보정 데이터를 작성하고 참조표의 데이터를 작성한다. 액정 패널에는 보정한 화상이 출력된다. 또한, 보정이 필요한 경우에는 마찬가지의 조작을 반복하고, 화면에 휘도 불균일이 관찰되지 않게 되도록 조정한다. 또, 외부로부터 계수를 입력하기 위한 인터페이스부가 형성되어 마이크로 컴퓨터(430)에 접속된다.

한번 설정된 계수는 영상 신호 제어 회로(400)에 기록된다. 액정 표시 장치의 구동 동작 시에 마이크로 컴퓨터(430)에 의해, 표준 데이터와 계수로부터 보정 데이터가 작성되며, 참조표(420)에 저장된다.

다음에 도 17의 (c)에 아날로그 회로 특성이 정상치에 대하여, 낮은 값을 출력하는 경우를 도시한다. 선(456)은 입력에 대하여 출력이 낮은 값이 되는 특성을 나타내는 선이다. 선(456)으로 나타내는 입력과 출력의 특성은, 출력이 낮은 값을 나타내기 때문에, 참조표(420)에서는 출력이 높아지는 보정 데이터가 선택된다. 참조표(420)의 특성은 선(457)에 도시한 바와 같이, 선(452)에 대하여 출력이 높아지는 값으로 되어 있다.

또, 보정의 방법으로서는 액정 패널의 화상을 활상 장치에 의해 입력하고, 입력한 화상 데이터로부터 휘도 불균일이 있는 상을 검출하며, 자동적으로 계수를 산출하여, 산출한 계수를 기초로 참조표(420)에 보정 데이터를 작성하는 것도 가능하다.

도 17에 도시한 바와 같이, 아날로그 회로의 변동이 증폭율의 변동과 같은 경우에는 입력에 대하여 출력의 변동이 선형으로 변화하기 때문에, 변동을 보정하는 데이터도 입력에 대하여 선형으로 변화하는 값이 된다. 그 때문에, 표준 데이터에 계수를 걸어 보정 데이터를 구하는 것이 가능하다.

도 18에 교류화 회로에서 발생한 변동을 보정하는 경우의 구성을 도시한다. 참조표는 1상에 대하여 정극성용(423)과 부극성용(422)의 2개의 테이블을 갖고, 교류화 신호에 동기하여 아날로그 스위치(417)로 선택한다. 부극성용 연산 증폭기(414)로부터 영상 신호가 출력하는 경우에는 부극성용 참조표(422)에서 보정하고, 정극성용 연산 증폭기(415)로부터 영상 신호가 출력하는 경우에는 정극성용 참조표(423)에서 보정한다. 정극성용, 부극성용 각각의 참조표에 보정 데이터를 설정해 둠으로써, 양극과 음극 사이에서의 변동을 보정할 수 있다.

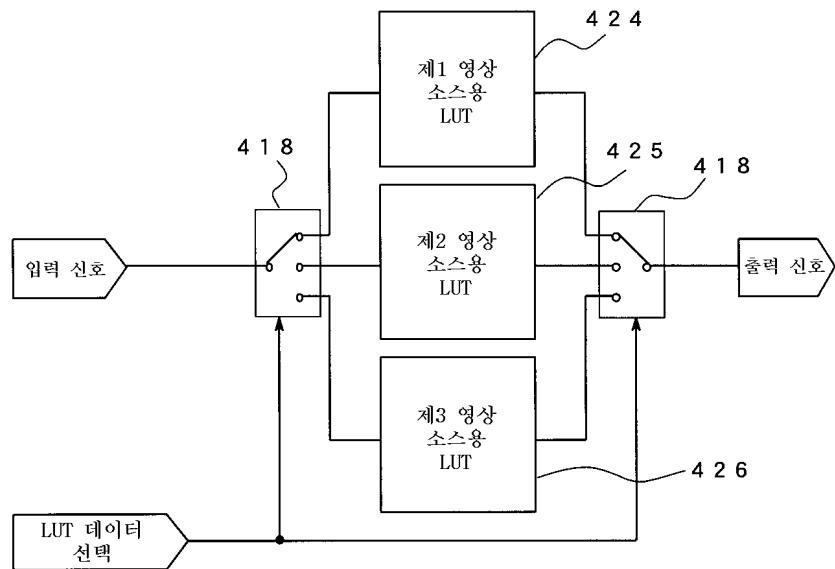

도 19에 영상 소스에 의해 복수의 참조표로부터 하나의 참조표를 선택하는 방법을 나타낸다. 통상, 신호의 소스로서는 퍼스널 컴퓨터의 원도우와 같은 그래픽 화상, 또는 영화, 자연 화상 등이 있다. 사전에 이들의 복수의 영상 소스에 적합한

보정 데이터 등의 참조표를 작성해 두고, 영상 소스에 의해 스위치를 전환하여 사용한다. 도 19에서는 3 종류의 영상 소스 용으로 참조표를 준비하는 경우를 도시한다. 또, 당연히 영상 소스의 수에 대응하여 복수의 참조표를 준비하는 것이 가능하다. 참조 부호 424는 제1 영상 소스용 참조표이고, 참조 부호 425는 제2 영상 소스용 참조표, 참조 부호 426은 제3 영상 소스용 참조표이다. 스위치(418)에 의해 어떤 참조표를 이용할지를 선택한다.

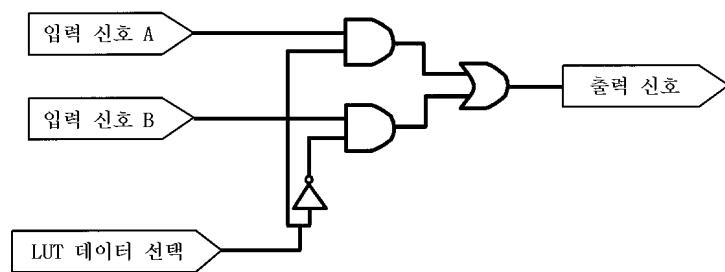

또, 스위치(418)는 디지털 신호의 전달 경로를 전환하는 스위치이면 이용 가능하다. 도 19의 (b)에 스위치(418)를 논리 회로로 구성하는 경우를 도시한다.

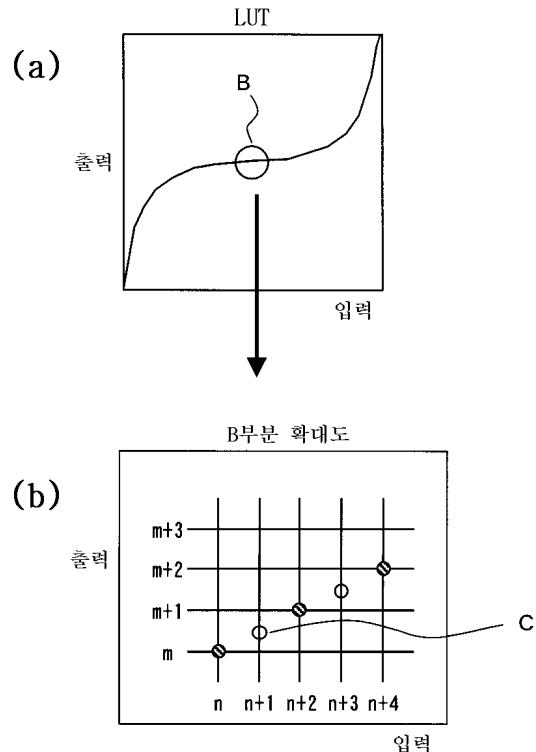

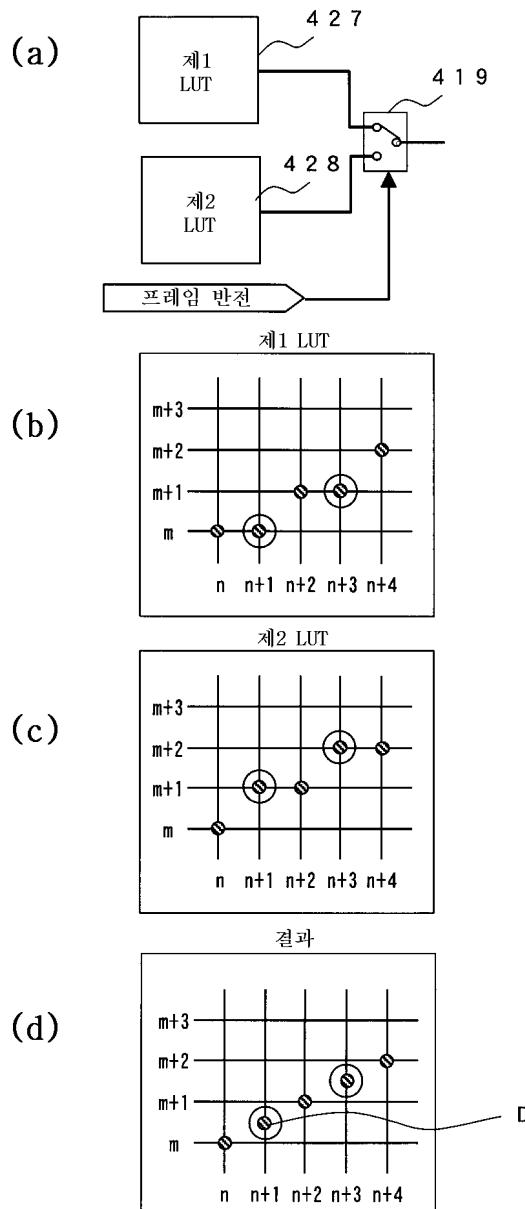

도 20, 도 21을 이용하여 참조표를 복수 사용하여, 의사적으로 계조를 높이는 방법을 설명한다. 8 보정용 참조표 등의 경우에는 도 20의 (a)와 같이, 입력에 대한 출력의 변화가 적으며, 출력하는 계조가 감소하여 화질이 열화한다. 도 20의 (b)에 출력의 변화가 적은 부분 B의 확대도를 나타낸다. 도 20의 (b)의 예에서는 부호 C로 나타내는 점과 같이,  $n+1$ 의 입력에 대하여,  $m$ 과  $m+1$  사이의 계조를 출력하고자 하지만, 비트수의 관계 때문에,  $m$  또는  $m+1$  중 어느 한쪽으로 밖에 표현할 수 없는 경우가 있다. 그래서, 2개의 참조표를 프레임마다 전환하여 중간 계조를 출력한다.

도 21의 (a)에 있어서, 참조 부호 427은 제1 참조표이고, 참조 부호 428은 제2 참조표이고, 참조 부호 419는 전환용 아날로그 스위치이다. 도 21의 (b)에 도시한 바와 같이, 제1 참조표(427)는  $n+1$ 이 입력되었을 때에  $m$ 을 출력한다. 도 21의 (c)에 도시한 바와 같이, 제2 참조표(428)는  $n+1$ 이 입력했을 때에,  $m+1$ 을 출력한다. 제1 참조표(427)와 제2 참조표(428)의 출력을 아날로그 스위치(419)를 이용하여, 프레임 주기로 교대로 전환하여 출력한다. 그에 따라 도 21의 (d)에 도시한 바와 같이, 의사적으로  $m$ 과  $m+1$ 의 중간의 계조(도면 중 D)를 시각적으로 표시하는 것이 가능해진다.

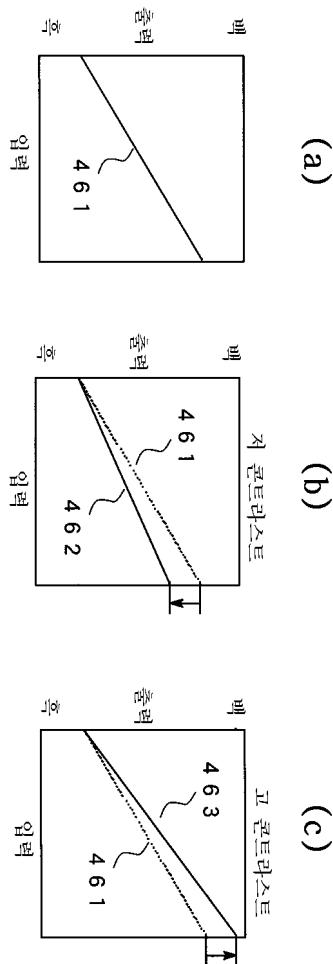

다음에 도 22, 도 23을 이용하여 참조표를 사용하여 콘트라스트, 및 휘도를 조정하는 방법을 설명한다. 또, 도 22, 도 23에서는 설명을 간단히 하기 위해서, 노멀 블랙인 경우로 설명한다. 즉, 전압이 높고 고휘도(백 표시)가 된다. 도 22는 콘트라스트를 조정하는 방법을 설명하는 도면이다. 도 22의 (a)의 입력에 대한 출력의 특성을 나타내는 선(461)에 나타내는 데이터의 콘트라스트를 낮추는 경우에는 도 22의 (b)에 도시한 바와 같이, 특성을 나타내는 선(462)의 기울기를 작게 한다. 콘트라스트를 높이는 경우에는 도 22의 (c)에 도시한 바와 같이, 특성을 나타내는 선(463)의 기울기를 크게 한다.

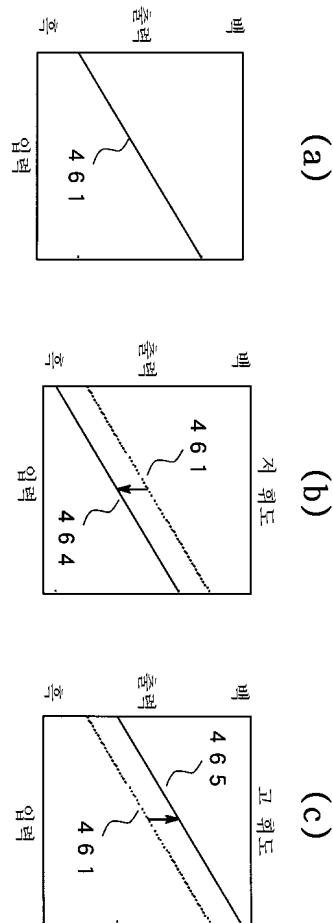

도 23은 휘도를 조정하는 방법을 설명하는 도면이다. 도 23의 (a)의 입력에 대한 출력의 특성을 나타내는 선(461)으로 나타내는 데이터의 휘도를 낮추는 경우에는, 도 23의 (b)에 도시한 바와 같이, 특성을 나타내는 선(464)을 흑 방향으로 평행 이동시키고, 도 23의 (c)에 도시한 바와 같이, 휘도를 높이는 경우에는 특성을 나타내는 선(465)을 백 방향으로 평행 이동시킨다.

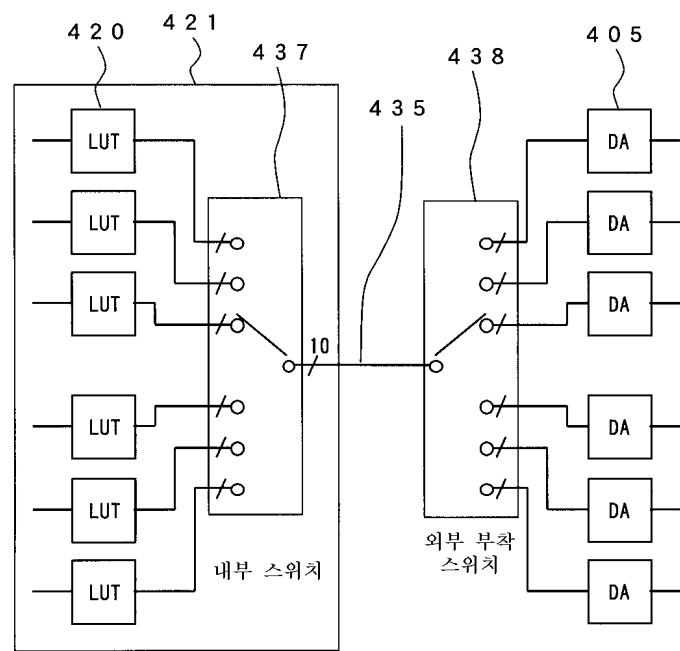

도 24에 아날로그 스위치를 형성하고, 1 패키지화한 참조표(421)의 핀 수를 줄이는 회로 구성은 도시한다. 또, 마찬가지로 구성으로 내외의 인터페이스의 배선 및 핀 수를 줄이는 것이 가능하다. 복수의 참조표(420)를 1 패키지에 수납한 경우, 회로 구성은 간단하게 되지만, 패키지의 핀 수가 증가한다는 문제가 생긴다. 참조표(420)와 DA 변환 회로(405) 사이의 데이터 버스(435)는 10 비트이기 때문에, 각 상마다 데이터 버스를 형성하면, 데이터 버스에 접속하기 위한 1 패키지화한 참조표(421)의 핀 수는 현저히 증가한다. 예를 들면 12상 10 비트의 경우, 120 핀이 된다. 그 때문에, 각 참조표의 출력을 내부 스위치(437)로 선택하고, 동일한 타이밍에서 외부 부착 스위치(438)로 출력처를 선택한다. 본 회로 구성에 의해, 예를 들면 12상 10 비트인 경우, 120 핀에서 10 핀으로 감소하기 때문에, 사용하는 패키지의 최소화가 가능해진다.

다음에 도 25를 이용하여, 배선수를 생략할 수 있는 구성에 대하여 설명한다. 도 25에서는 참조표(420)의 위치가 상전개용 샘플 홀드 회로(404)의 앞에 형성된다. 도 25에 도시하는 구성에서는 참조표(420)와 샘플 홀드 회로(404) 사이의 배선 수가 대폭 생략 가능하다. 예를 들면 도 11에 도시하는 구성에서는, 샘플 홀드 회로(404)와 참조표(420) 사이에서는 데이터를 전하는 신호선이 상전개한 수만큼 필요하다. 12상 10 비트인 경우에는, 배선수는 120개가 된다. 이에 대하여 도 25에 도시하는 경우에는 10 비트분의 10개로 해결된다.

도 25에 도시하는 참조표(420)에서는, 표시 신호선(402)에 의해 외부 장치로부터 표시 신호가 일정한 순서로, 영상 신호 제어 회로로 보내진다. 그 때문에, 표시 신호의 순서대로 맞추어서, 상전개되는 순서를 정하면, 상전개하는 구성과 보정하는 구성의 위치를 재배열해도 문제는 없다. 즉,  $n$  번째 상의 데이터인 것을 알면,  $n$  번째 상의 변동에 필요한 보정을 상전개 전에 행하는 것이 가능하다.

AD 변환 회로(403)로부터는, 예를 들면 10 비트의 데이터 버스(435)가 출력된다. 참조표(420)는 상전개하는 수만큼 준비되며, 각 참조표(420)에는 데이터 버스(435)가 접속된다. 영상 신호 제어 회로(400)는 AD 변환 회로(403)로부터 출력하는 데이터의 순서에 따라, 어떤 상의 데이터인지를 알고, 보정하는 참조표(420)를 선택한다.

다음에 도 26을 이용하여 참조표 데이터의 통신에 대하여 설명한다. 참조표로 설정하는 데이터량으로서는 1색당 12상, 10비트(2바이트) 데이터, 256계조로 한 경우,

$$12\text{상} \times 2\text{바이트} \times 256\text{계조} = 6144\text{바이트}$$

가 되며, 3색으로는,

$$6144\text{바이트} \times 3\text{색} = 18432\text{바이트}$$

가 된다. 예를 들면, 외부의 퍼스널 컴퓨터(448)에 참조표 데이터를 기록해 두고, 표시 제어 장치(111) 내의 마이크로 컴퓨터(430)로 데이터 통신을 행하고, 참조표(420)에 데이터를 취득하는 방법을 이용하면, 퍼스널 컴퓨터-마이크로 컴퓨터 간 통신을 RS-232C로 9600bps의 속도로 통신한 경우, 최단으로 15초 걸린다. 또, 참조 부호 447은 데이터 통신용 인터페이스부이다. 또한, 퍼스널 컴퓨터-마이크로 컴퓨터 간 데이터 통신은 RS-232C뿐만 아니라, 다른 방법(예를 들면 USB, IEEE1394, SCSI, 블루투스(Bluetooth) 등)을 이용하는 것이 가능하다.

다음에, 영상 신호 제어 회로(400) 내에 형성한 마이크로 컴퓨터 내장의 RAM에 기억해 두는 경우를 고찰하면, 18432바이트의 영역을 크게 소비하는 문제가 발생한다.

통신 시간의 단축 및 마이크로 컴퓨터 내장 RAM을 절약하기 위해서, 데이터를  $\gamma$  보정용 표준 데이터(429)와 차분 데이터로 나눈다. 차분 데이터는 외부 장치(퍼스널 컴퓨터)에 의해 표시 화상을 관찰하면서 최적의 값이 설정된다. 참조표 데이터를 작성하는 경우에는 마이크로 컴퓨터 내에서 표준 데이터(429)에 차분 데이터에 걸어 연산함으로써 참조표 데이터를 작성한다. 이에 따라 퍼스널 컴퓨터-마이크로 컴퓨터 간의 통신 데이터량의 증대도, 마이크로 컴퓨터 내장 RAM 영역을 크게 사용하지 않고 참조표에 데이터를 취득하는 것이 가능해진다.

다음에 도 27을 이용하여 프레임 주파수를 체배화하는 방법에 대하여 설명한다. 도 27의 (a)에 2프레임분의 프레임 메모리를 이용하여, 프레임 주파수를 변환하는 회로 구성과, 도 27의 (b)에 2배속으로 하는 경우의 타이밍차트를 도시한다.

프레임 주파수를 변환하는 회로는 타이밍 컨트롤러(432)와 1프레임분의 용량이 있는 제1프레임 메모리(433)와 제2프레임 메모리(434)에 의해 구성된다. 영상 신호는 타이밍 컨트롤러(432)에 입력하고, 타이밍 컨트롤러(432) 내의 스위치 조작에 의해, 제1프레임 메모리(433)와 제2프레임 메모리(434)에 입력한다. 제1프레임 메모리(433)와 제2프레임 메모리(434)로부터는, 예를 들면 주파수를 2배로 하는 경우에는 2배의 클럭으로 판독하여, 타이밍 컨트롤러(432)로부터 출력한다.

다음에 타이밍에 대하여 설명한다. 영상 신호의 입력이 프레임 1의 타이밍에서는 제1프레임 메모리(433)에 화상 데이터를 그대로 기입한다. 영상 입력이 프레임 2의 타이밍에서 제2프레임 메모리(434)에 프레임의 화상 데이터를 기입한다. 그와 동시에 제1프레임 메모리(433)로부터는 2배속의 스피드로 2회 프레임 1의 데이터를 판독한다. 프레임 3의 타이밍에서는 제1프레임 메모리(433)에 프레임 3의 화상 데이터를 기입하는 것과 동시에, 제2프레임 메모리(434)의 데이터를 2배의 스피드로 2회 판독한다. 이것을 반복함으로써 프레임 주파수가 2배의 신호를 출력하는 것이 가능해진다.

도 28에 메모리를 1프레임+1블록분 사용하여 프레임 주파수를 변환하는 경우의 회로 구성과, 도 29에 타이밍차트를 도시한다. 도 28에서 메모리 용량은 6블록으로 1프레임분의 경우를 예로 든다. 회로는 7블록으로 나누어지는 블록 메모리(440)와, 타이밍 컨트롤러(432)로 구성된다. 7개의 각 메모리 블록의 입출력은 타이밍 컨트롤러(432)에 의해 제어된다.

다음에 도 29에 도시하는 타이밍차트에 의해 동작을 설명한다. 1프레임분의 영상 신호를 6개의 타이밍으로 분할하고, 1-1~1-6로 한다. 1-1의 신호는 블록 1에, 1-2의 신호는 블록 2에 기입하고, 이후 순서대로 신호를 메모리의 각 블록에 기입한다. 그리고 기입 타이밍과는 비동기로 메모리로부터 2배의 스피드로 판독을 행하고, 도 29와 같이 2배속의 영상 신호를 출력한다. 다음에 2-1의 신호는 블록 7에, 2-2의 신호는 블록 1에 기입하도록 이후 로테이션을 반복하면서 기입 및 판독을 행한다. 이 회로 방식은 동작이 복잡하게 되지만 메모리 용량을 적게 할 수 있다는 이점이 있다. 메모리 용량은 분할 블록수를 늘릴수록 적어지지만, 그 만큼 동작이 복잡해지기 때문에, 양자의 밸런스를 고려할 필요가 있다.

도 30에 메모리를 사용하여 테스트 패턴을 출력하는 회로 구성을 도시한다. 통상 영상 신호에 의해 회로의 조정을 그 때마다 행하지만, 그 경우에는 도트 체크 무늬, 컬러 바 차트, 그레이 스케일 등의 테스트 패턴을 사용한다. 이들의 패턴을 출력하는 퍼스널 컴퓨터 등을 신호원으로서 준비할 필요가 있지만, 본 회로를 이용하면 영상 신호 제어 회로(400) 내에서 패

턴을 발생하기 위해 이들의 신호원이 불필요하게 된다. 회로는 통상의 주파수 변환 등에 사용하는 프레임 메모리(431)와, 테스트 패턴을 사전에 기입한 프레임 메모리(445), 타이밍 컨트롤러(432)로 구성된다. 통상 동작 시에는 프레임 메모리(431)로부터 영상 신호를 출력한다. 테스트 패턴 표시 시에는 스위치를 전환하여 테스트 패턴의 프레임 메모리(445)로부터 영상 신호를 출력한다.

도 31에 프레임 메모리(431)를 사용하여 정지 화상을 출력하는 회로 구성을 도시한다. 정지 화상 출력은 표시하고 싶지 않은 영상 신호를 입력하지 않을 수 없는 때 등에 유효한 기능이 된다. 통상 동작 시에는 프레임 메모리(431) 내의 영상 신호를 항상 갱신하기 위해 실시간으로 영상이 표시된다. 영상 신호의 메모리 기입을 차단하면, 영상이 갱신되지 않기 위해 차단하기 직전의 신호를 반복하여 메모리로부터 판독한다. 이와 같이 하여 정지 화상 출력은 메모리의 기입 스위치를 제어 한다.

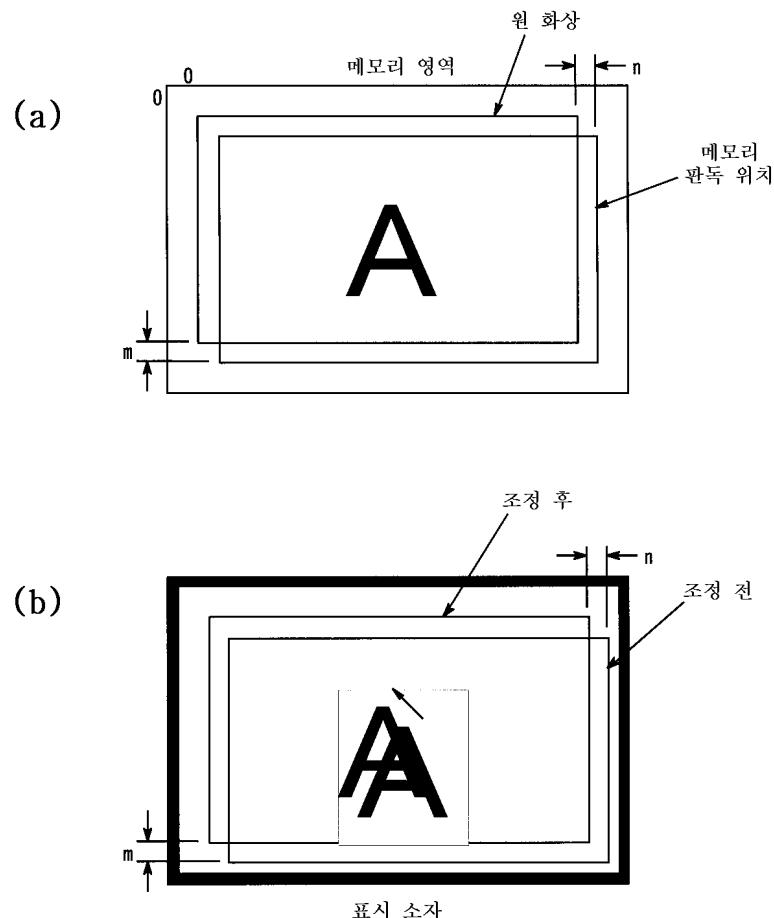

도 32에 프레임 메모리(431)를 이용한 회로의 컨버터스의 조정에 대하여 도시한다. 제품에 표시 소자를 복수 이용한 경우(예를 들면, 2판 혹은 3판), 이들의 서로의 위치를 화소 단위로 맞출 필요가 있다. 통상은 표시 소자의 위치를 미세하게 조정하여 맞추지만, 본 방식에 따르면 표시 소자의 위치를 바꾸지 않고서 조정이 가능해진다. 이하 방법에 대하여 설명한다. 프레임 메모리(431)에 기입한 영상 신호를 판독할 때에 어드레스를 조정하여 표시 위치를 조정한다. 프레임 메모리(431)의 어드레스와 표시 소자의 화소가 일치하는 경우, 예를 들면 도 32의 (a)와 같이 메모리 내의 영상 신호의 위치에 대하여, 판독 위치의 어드레스를 우측 방향으로 n, 하측 방향으로 m 변이시킨다. 그러면, 표시 소자에서의 표시 위치가 좌측 방향으로 n 화소, 상 방향으로 m 화소 이동한다. 이렇게 하여 표시 소자의 표시 위치를 조정한다.

다음에 도 33을 이용하여, 화소부(101)에 대하여 설명하고, 또한 화소 전위 제어 회로를 이용하여, 화소 전극의 전위를 변화시키는 구동 방법에 대하여 설명한다. 도 33은 화소부(101)의 등가 회로를 도시하는 회로도이다. 화소부(101)는 표시부(110)의 인접하는 2개의 주사 신호선(102)과, 인접하는 2개의 영상 신호선(103)과의 교차 영역(4개의 신호선으로 둘러싸인 영역)에 매트릭스 형상으로 배치된다. 단, 도 33에서는 도면을 간략화하기 위해서 하나의 화소부만을 도시한다. 각 화소부(101)는 능동 소자(30)와 화소 전극(109)을 갖고 있다. 또한, 화소 전극(109)에는 화소 용량(115)이 접속되어 있다. 화소 용량(115)의 한쪽 전극은 화소 전극(109)에 접속되며, 다른 쪽 전극은 화소 전위 제어선(136)에 접속된다. 또한 화소 전위 제어선(136)은 화소 전위 제어 회로(135)에 접속된다. 또, 도 33에서는 능동 소자(30)는 p형 트랜지스터로 도시한다.

상술한 바와 같이, 주사 신호선(102)에는 수직 구동 회로(130)로부터 주사 신호가 출력된다. 이 주사 신호에 의해 능동 소자(30)의 온·오프가 제어된다. 영상 신호선(103)에는 영상 신호로서 계조 전압이 공급되며, 능동 소자(30)가 온이 되면, 영상 신호선(103)으로부터 화소 전극(109)에 계조 전압이 공급된다. 화소 전극(109)에 대향하도록 대향 전극(107)(공통 전극)이 배치되어 있으며, 화소 전극(109)과 대향 전극(107) 사이에는 액정층(도시하지 않음)이 형성된다. 또, 도 33에 도시하는 회로도 상에는 화소 전극(109)과 대향 전극(107) 사이에는 등가적으로 액정 용량(108)이 접속되도록 표시하였다. 화소 전극(109)과 대향 전극(107) 사이에 전압을 인가함으로써, 액정 분자의 배향 방향 등이 변화하고, 그에 따라 액정층의 광에 대한 성질이 변화하는 것을 이용하여 표시가 행해진다.

액정 표시 장치의 구동 방법으로서는, 상술한 바와 같이 액정층에 직류 전류가 인가되지 않도록 교류화 구동이 행해진다. 교류화 구동을 행하기 위해서는, 대향 전극(107)의 전위를 기준 전위로 한 경우에, 영상 신호 선택 회로(123)로부터는 기준 전위에 대하여 정극성과 부극성의 전압이 계조 전압으로서 출력된다. 그러나, 영상 신호 선택 회로(123)를 정극성과 부극성의 전위차에 견디는 고내압인 회로로 하면, 능동 소자(30)를 비롯하여 회로 규모가 커진다는 문제나 동작 속도가 늦어진다는 문제가 생기게 된다. 또한, 도 10에 도시한 바와 같이, 영상 신호 제어 회로(400)에서는 정극성측과 부극성측의 연산 증폭기가 필요하다.

그래서, 영상 신호 선택 회로(123)로부터 화소 전극(109)에 공급하는 영상 신호는 기준 전위에 대하여 동극성의 신호를 이용하면서도 교류화 구동을 행하는 것을 검토하였다. 예를 들면, 영상 신호 선택 회로(123)로부터 출력하는 계조 전압은 기준 전위에 대하여 정극성의 전압을 이용하여, 기준 전위에 대하여 정극성의 전압을 화소 전극에 기입한 후에, 화소 전위 제어 회로(135)로부터 화소 용량(115)의 전극에 인가되고 있는 화소 전위 제어 신호의 전압을 강하시킴으로써, 화소 전극(109)의 전압도 강하시켜, 기준 전위에 대하여 부극성의 전압을 발생시킬 수 있다. 이러한 구동 방법을 이용하면, 영상 신호 선택 회로(123)가 출력하는 최대치와 최소치와의 차가 작기 때문에, 영상 신호 선택 회로(123)는 저내압의 회로로 하는 것이 가능해진다. 또 일례로서, 화소 전극(109)에 정극성의 전압을 기입하여 화소 전위 제어 회로(135)에 의해 부극성의 전압을 발생시키는 경우에 대해 설명하였지만, 부극성의 전압을 기입하여 정극성의 전압을 발생시키려면 화소 전위 제어 신호의 전압을 강하함으로써 가능하다.

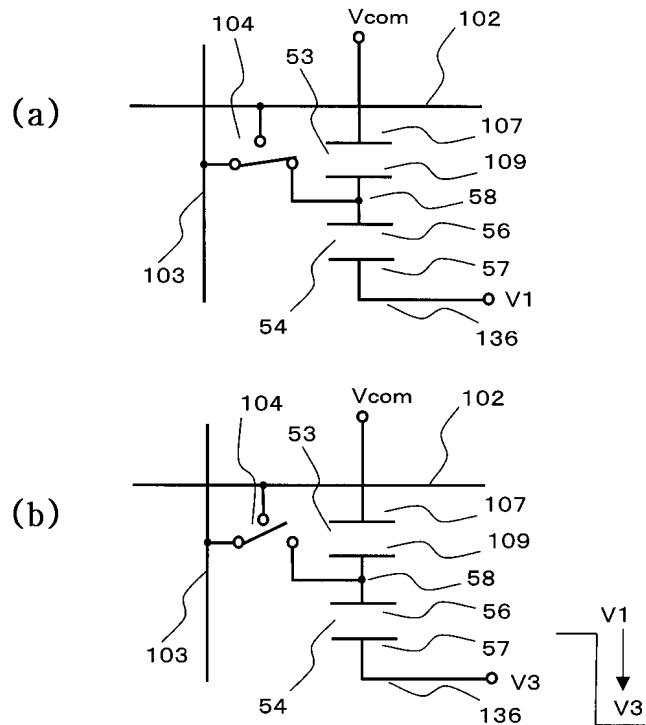

다음에 도 34를 이용하여, 화소 전극(109)의 전압을 변동시키는 방법에 대하여 설명한다. 도 34는 설명을 위해 액정 용량(108)을 제1 컨덴서(53)로 도시하고, 화소 용량(115)을 제2 컨덴서(54)로 도시하고, 능동 소자(30)를 스위치(104)로 도시

한 것이다. 화소 용량(115)의 화소 전극(109)에 접속되는 전극을 전극(56)으로 하고, 화소 용량(115)의 화소 전위 제어선(136)에 접속되는 전극을 전극(57)으로 한다. 또한, 화소 전극(109)과 전극(56)이 접속된 점을 절점(58)으로 도시한다. 여기서는 설명을 위해, 다른 기생 용량은 무시할 수 있는 것으로 하고, 제1 컨텐서(53)의 용량은 CL, 제2 컨텐서(54)의 용량은 CC으로 한다.

우선 도 34의 (a)에 도시한 바와 같이, 제2 컨텐서(54)의 전극(57)에는 외부로부터 전압 V1을 인가한다. 다음에, 주사 신호에 의해 스위치(104)가 온이 되면, 영상 신호선(103)으로부터 전압이 화소 전극(109) 및 전극(56)에 공급된다. 여기서, 절점(58)에 공급된 전압을 V2로 한다.

다음에, 도 34의 (b)에 도시한 바와 같이, 스위치(104)가 오프가 된 시점에서, 전극(57)에 공급하고 있는 전압(화소 전위 제어 신호)을 V1에서 V3으로 강하시킨다. 이 때, 제1 컨텐서(53)와 제2 컨텐서(54)에 충전된 전하의 총량은 변화하지 않기 때문에, 절점(58)의 전압이 변화하여 절점(58)의 전압은  $V2 - \{CC/(CL+CC)\} \times (V1 - V3)$ 이 된다.

여기서, 제1 컨텐서(53)의 용량 CL이 제2 컨텐서(54)의 용량 CC에 비하여 충분히 작은 경우( $CL < CC$ )에는  $CC/(CL+CC) \approx 1$ 이 되고 절점(58)의 전압은  $V2 - V1 + V3$ 이 된다. 여기서  $V2=0$ ,  $V3=0$ 으로 하면, 절점(58)의 전압은  $-V1$ 이 된다.

상술한 방법에 따르면, 화소 전극(109)에 영상 신호선(103)으로부터 공급하는 전압은 대향 전극(107)의 기준 전위에 대하여 정극성으로 하고, 부극성의 신호는 전극(57)에 인가하는 전압(화소 전위 제어 신호)을 제어함으로써 발생될 수 있다. 이러한 방법으로 부극성의 신호를 발생시키면, 영상 신호 선택 회로(123)로부터는 부극성의 신호를 공급할 필요가 없어지고, 주변 회로를 저내압의 소자로 형성하는 것이 가능해진다.

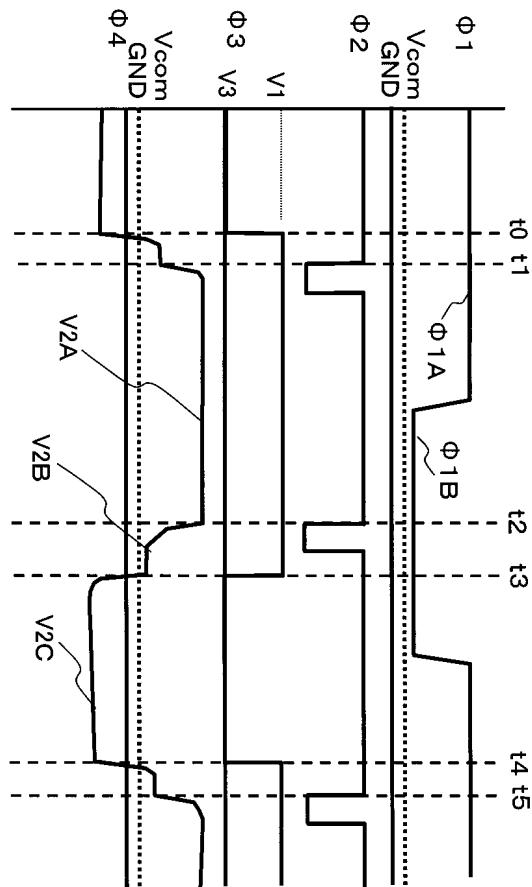

다음에 도 35를 이용하여, 도 33에 도시하는 회로의 동작 타이밍에 대해 설명한다.  $\phi 1$ 은 영상 신호선(103)에 공급되는 계조 전압을 나타낸다.  $\phi 2$ 는 주사 신호선(102)에 공급되는 주사 신호이다.  $\phi 3$ 은 화소 전위 제어 신호선(136)에 공급되는 화소 전위 제어 신호(강압 신호)이다.  $\phi 4$ 는 화소 전극(109)의 전위를 나타낸다. 또, 화소 전위 제어 신호  $\phi 3$ 은 도 32에 도시한 전압 V3과 V1에서 변동하는 신호이다.

도 35를 설명함에 있어서,  $\phi 1$ 은 정극성용 입력 신호  $\phi 1A$ 와, 부극성용 입력 신호  $\phi 1B$ 를 나타낸다. 여기서, 부극성용이란 화소 전극에 인가된 전압이 화소 전위 제어 신호에 의해 변동하여, 기준 전위 Vcom에 대하여 부극성이 되는 경우의 신호를 말한다. 본 실시예에서는 영상 신호  $\phi 1$ 로서 정극성용 입력 신호  $\phi 1A$ 와 부극성용 입력 신호  $\phi 1B$  모두, 대향 전극(107)에 인가된 기준 전위 Vcom에 대하여 전위가 정극성이 된 전압이 공급되는 경우를 설명한다.

도 35에서, 기간  $t_0$  내지  $t_2$  사이에는, 계조 전압  $\phi 1$ 이 정극성용 입력 신호  $\phi 1A$ 인 경우를 도시한다. 우선,  $t_0$ 에서 화소 제어 신호  $\phi 3$ 으로서 전압 VI를 출력한다. 다음에 시각  $t_1$ 에 있어서 주사 신호  $\phi 2$ 가 선택되어 로우 레벨이 되면, 도 33에 도시하는 p형 트랜지스터(30)가 온 상태가 되어, 영상 신호선(103)에 공급되는 정극성용 입력 신호  $\phi 1A$ 가 화소 전극(109)에 기입된다. 화소 전극(109)에 기입되는 신호는 도 35에서는  $\phi 4$ 로 나타낸다. 또한, 도 35에서  $t_2$ 로 화소 전극(109)에 기입된 전압은 V2A로 나타낸다. 다음에, 주사 신호  $\phi 2$ 가 비선택 상태가 되며, 하이 레벨이 되면 트랜지스터(30)는 오프 상태가 되고, 화소 전극(109)은 전압을 공급하는 영상 신호선(103)으로부터 분리된 상태가 된다. 액정 표시 장치는 화소 전극(109)에 기입된 전압 V2A에 따른 계조를 표시한다.

다음에, 기간  $t_2$  내지  $t_4$  사이에서 계조 전압  $\phi 1$ 이 부극성용 입력 신호  $\phi 1B$ 인 경우를 설명한다. 부극성용 입력 신호  $\phi 1B$ 인 경우, 시각  $t_2$ 에서 주사 신호  $\phi 2$ 가 선택되고, 화소 전극(109)에는  $\phi 4$ 에 도시한 바와 같은 전압 V2B가 기입된다. 그 후, 트랜지스터(30)를 오프 상태로 하여, 시각  $t_2$ 로부터 2h(2 수평 주사 시간) 후의 시각  $t_3$ 에서 화소 용량(115)에 공급되는 전압을 화소 전위 제어 신호  $\phi 3$ 에 도시한 바와 같이 V1에서 V3으로 강압한다. 화소 전위 제어 신호  $\phi 3$ 을 V1에서 V3으로 변동시키면 화소 용량(115)이 결합 용량의 역할을 완수하여, 화소 전위 제어 신호  $\phi 3$ 의 진폭에 따라, 화소 전극의 전위를 강하시킬 수 있다. 이에 따라, 기준 전위 Vcom에 대하여 부극성의 전압 V2C를 화소 내에 발생시킬 수 있다.

상술한 방법으로, 부극성의 신호를 발생하면, 주변 회로를 저내압의 소자로 형성하는 것이 가능해진다. 즉, 영상 신호 선택 회로(123)로부터 출력되는 신호는 정극성측이 진폭이 좁은 신호이기 때문에, 영상 신호 선택 회로(123)는 저내압의 회로로 하는 것이 가능해진다. 또, 부극성측의 연산 증폭기를 이용할 필요가 없고, 또한 영상 신호 선택 회로(123)가 저전압으로 구동 가능하면, 다른 주변 회로인 수평 시프트 레지스터(120), 표시 제어 장치(111) 등은 저내압의 회로이기 때문에, 액정 표시 장치 전체적으로 저내압의 회로에 의한 구성이 가능해진다.

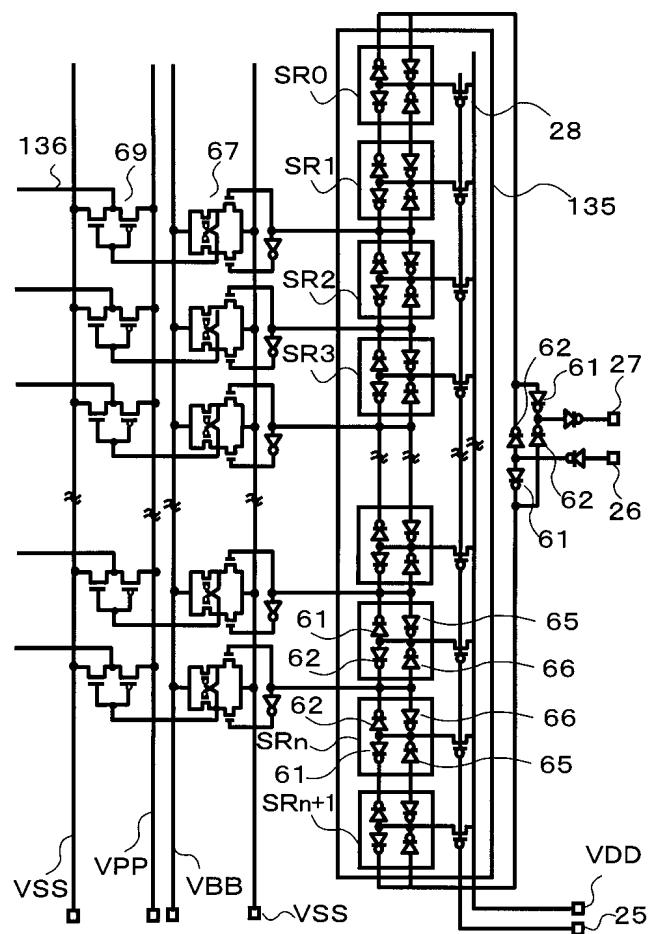

다음에 도 36을 이용하여, 화소 전위 제어 회로(135)의 회로 구성을 도시한다. SR은 쌍방향 시프트 레지스터로서, 상하 쌍방향으로 신호를 시프트하는 것이 가능하다. 쌍방향 시프트 레지스터 SR은 클럭드 인버터(61, 62, 65, 66)로 구성된다. 참조 부호 67은 레벨 시프터이고, 참조 부호 69는 출력 회로이다. 쌍방향 시프트 레지스터 SR 등은 전원 전압 VDD로 동작하고 있다. 레벨 시프터(67)은 쌍방향 시프트 레지스터 SR에서 출력하는 신호의 전압 레벨을 변환한다. 레벨 시프터(67)로부터는 전원 전압 VDD보다 고전위인 전원 전압 VBB와 전원 전압 VSS(GND 전위) 사이의 진폭을 갖는 신호가 출력된다. 출력 회로(69)는 전원 전압 VPP와 VSS가 공급되며, 레벨 시프터(67)로부터의 신호에 따라 전압 VPP와 VSS를 화소 전위 제어선(136)에 출력한다. 도 35에서 설명한 화소 전위 제어 신호  $\phi$ 3의 전압 V1이 전원 전압 VPP, 전압 V3가 전원 전압 VSS가 된다. 또, 도 36에서는 출력 회로(69)를 p형 트랜지스터와 n형 트랜지스터로 이루어지는 인버터로 도시한다. p형 트랜지스터에 공급하는 전원 전압 VPP와 n형 트랜지스터에 공급하는 전원 전압 VSS의 값을 선택함으로써, 전압 VPP와 VSS를 화소 전위 제어 신호  $\phi$ 3으로서 출력하는 것이 가능하다.

단, 후술하는 바와 같이 p형 트랜지스터를 형성하는 기판에는 기판 전압이 공급되어 있기 때문에, 전원 전압 VPP의 값을 기판 전압에 대하여 적절한 값이 설정된다.

참조 부호 26은 스타트 신호 입력 단자로서, 제어 신호의 하나인 스타트 신호를 화소 전위 제어 회로(135)에 공급한다. 도 36에 도시하는 쌍방향 시프트 레지스터 SR1로부터 SRn은 스타트 신호가 입력되면 외부로부터 공급되는 클럭 신호의 타이밍에 따라, 순서대로 타이밍 신호를 출력한다. 레벨 시프터(67)는 타이밍 신호에 따라 전압 VSS와 전압 VBB를 출력한다. 출력 회로(69)는 레벨 시프터(67)의 출력에 따라 전압 VPP과 전압 VSS를 화소 전위 제어선(136)에 출력한다. 도 35의 화소 전위 제어 신호  $\phi$ 3으로 나타내는 타이밍이 되도록, 스타트 신호 및 클럭 신호를 쌍방향 시프트 레지스터 SR에 공급함으로써, 화소 전위 제어 회로(135)로부터 희망하는 타이밍에서 화소 전위 제어 신호  $\phi$ 3을 출력하는 것이 가능하다. 또 참조 부호 25는 리세트 신호 입력 단자이다.

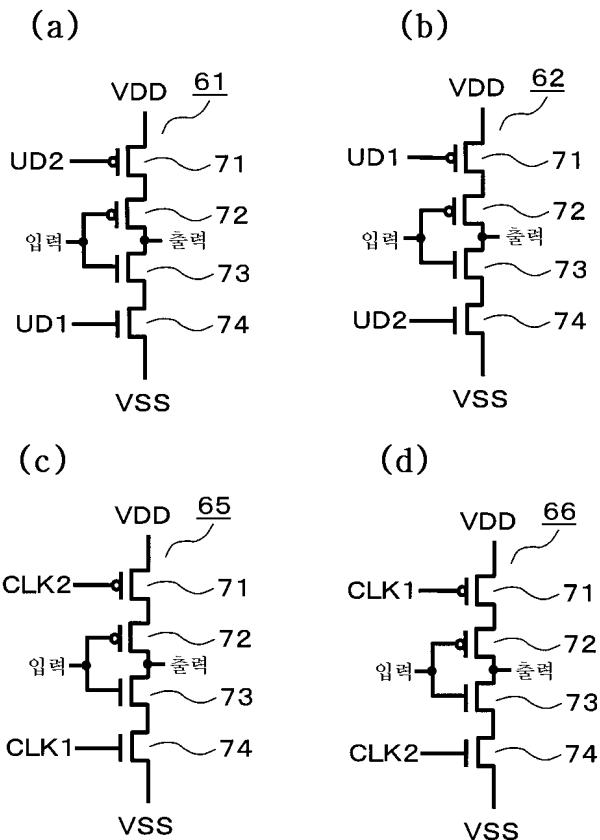

다음에, 도 37의 (a), 도 37의 (b)를 이용하여, 쌍방향 시프트 레지스터 SR에 이용되는 클럭드 인버터(61, 62)를 설명한다. UD1은 제1 방향 설정선, UD2는 제2 방향 설정선이다.

제1 방향 설정선 UD1은 도 36에서는 아래에서 위로 주사하는 경우 H 레벨이고, 제2 방향 설정선 UD2는 도 36에서는 위에서 아래로 주사하는 경우 H 레벨이다. 도 36에서는 도면을 보기 쉽게 하기 위해서 결선을 생략하지만, 제1 방향 설정선 UD1, 제2 방향 설정선 UD2는 모두 쌍방향 시프트 레지스터 SR을 구성하는 클럭드 인버터(61, 62)에 접속되어 있다.

클럭드 인버터(61)는 도 37의 (a)에 도시한 바와 같이, p형 트랜지스터(71, 72)와 N형 트랜지스터(73, 74)로 이루어진다. p형 트랜지스터(71)는 제2 방향 설정선 UD2에 접속되어 있고, n형 트랜지스터(74)는 제1 방향 설정선 UD1에 접속되어 있다. 그 때문에 제1 방향 설정선 UD1이 H 레벨이고 제2 방향 설정선 UD2가 L 레벨인 경우, 클럭드 인버터(61)는 인버터로서 기능하고, 제2 방향 설정선 UD2가 H 레벨이고 제1 방향 설정선 UD1이 L 레벨인 경우 하이 임피던스가 된다.

반대로 클럭드 인버터(62)는 도 37의 (b)에 도시한 바와 같이, p형 트랜지스터(71)는 제1 방향 설정선 UD1에 접속되어 있고, n형 트랜지스터(74)는 제2 방향 설정선 UD2에 접속되어 있다. 그 때문에 제2 방향 설정선 UD2가 H 레벨인 경우 인버터로서 기능하며, 제1 방향 설정선 UD1이 H 레벨인 경우 하이 임피던스가 된다.

다음에 클럭드 인버터(65)는 도 37의 (c)에 도시하는 회로 구성으로서, CLK1이 H 레벨이며, CLK2가 L 레벨인 경우에 입력을 반전 출력하고, CLK1이 L 레벨이고, CLK2가 H 레벨인 경우에, 하이 임피던스가 된다.

또한, 클럭드 인버터(66)는 도 37의 (d)에 도시하는 회로 구성으로서, CLK2가 H 레벨이고, CLK1이 L 레벨인 경우에, 입력을 반전 출력하고, CLK2가 L 레벨이고, CLK1가 H 레벨인 경우에, 하이 임피던스가 된다. 도 36에서는, 클럭 신호선의 결선을 생략하고 있지만 도 37의 클럭드 인버터(65, 66)에는 클럭 신호선 CLK1, CLK2가 접속되어 있다.

이상 설명한 바와 같이, 쌍방향 시프트 레지스터 SR을 클럭드 인버터(61, 62, 65, 66)로 구성함으로써, 타이밍 신호를 순서대로 출력하는 것이 가능하다. 또한 화소 전위 제어 회로(135)를 쌍방향 시프트 레지스터 SR로 구성함으로써, 화소 전위 제어 신호  $\phi$ 3을 쌍방향으로 주사하는 것이 가능하다. 즉, 수직 구동 회로(130)도 마찬가지의 쌍방향 시프트 레지스터로 구성되어 있고, 본 발명에 의한 액정 표시 장치는 상하 쌍방향의 주사가 가능하다. 그 때문에, 표시하는 상을 상하 역전하는 경우 등에 주사 방향을 반전하여 도면의 아래에서 위로 주사한다. 그래서 수직 구동 회로(130)가 아래에서 위로 주사하는 경우에는, 화소 전위 제어 회로(135)도 제1 방향 설정선 UD1과 제2 방향 설정선 UD2의 설정을 변경함으로써, 아래에서 위로 주사하도록 대응한다. 또, 수평 시프트 레지스터(121)도 마찬가지의 쌍방향 시프트 레지스터에 의해 구성되어 있다.

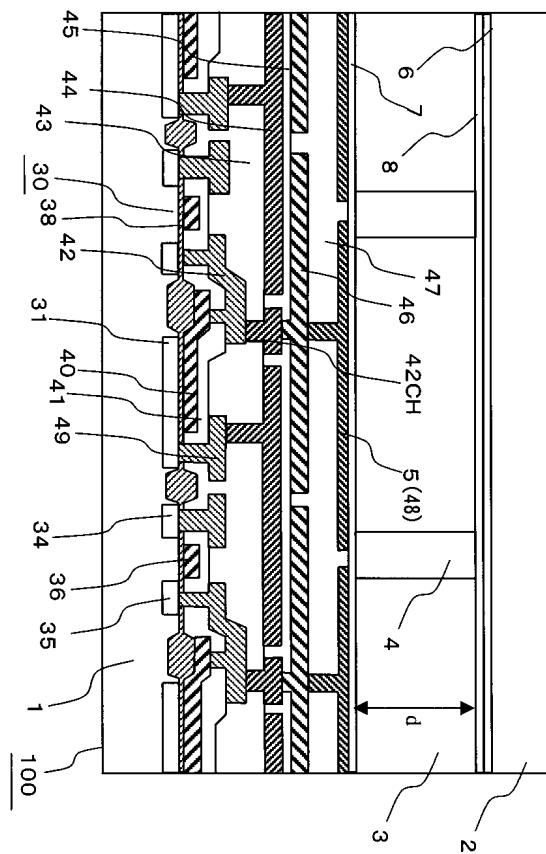

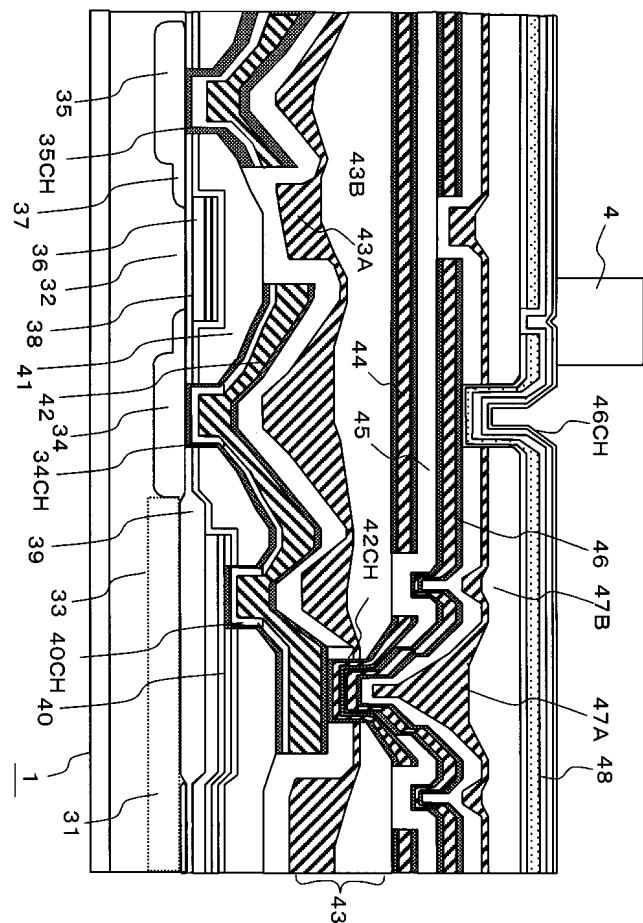

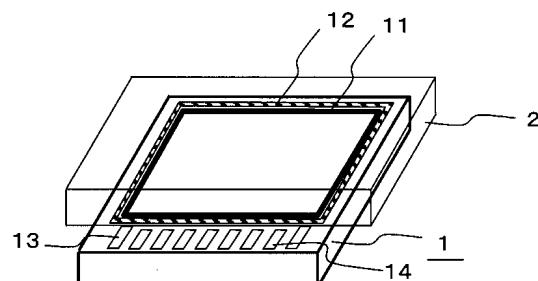

다음에 도 38을 이용하여, 본 발명에 의한 반사형 액정 표시 장치 LCOS의 화소부를 설명한다. 도 38은 본 발명의 일 실시 예인 반사형 액정 표시 장치의 모식 단면도이다. 도 38에서, 참조 부호 100은 액정 패널, 참조 부호 1은 제1 기판인 구동 회로 기판, 참조 부호 2는 제2 기판인 투명 기판, 참조 부호 3은 액정 조성물, 참조 부호 4는 스페이서이다. 스페이서(4)는 구동 회로 기판(1)과 투명 기판(2) 사이에 일정한 간격인 셀 갭(cell gap) d를 형성하고 있다. 이 셀 갭 d에 액정 조성물(3)이 삽입되어 있다. 참조 부호 5는 반사 전극(화소 전극)으로서 구동 회로 기판(1)에 형성되어 있다. 참조 부호 6은 대향 전극으로서 반사 전극(5) 사이에서 액정 조성물(3)에 전압을 인가한다. 참조 부호 7, 8은 배향막으로서 액정 분자를 일정 방향으로 배향시킨다. 참조 부호 30은 능동 소자로서 반사 전극(5)에 계조 전압을 공급한다.

참조 부호 34는 능동 소자(30)의 소스 영역, 참조 부호 35는 드레인 영역, 참조 부호 36은 게이트 전극이다. 참조 부호 38은 절연막, 참조 부호 31은 화소 용량을 형성하는 제1 전극이고, 참조 부호 40은 화소 용량을 형성하는 제2 전극이다. 절연막(38)을 통하여 제1 전극(31)과 제2 전극(40)은 용량을 형성한다. 도 38에서는, 제1 전극(31)과 제2 전극(40)을 화소 용량을 형성하는 대표적인 전극으로서 도시하고 있고, 그 외에도 화소 전극과 전기적으로 접속된 도체층과 화소 전위 제어 신호선과 전기적으로 접속된 도체층이 유전체층을 사이에 두고 대향하면 화소 용량을 형성하는 것이 가능하다.

참조 부호 41은 제1 층간막, 참조 부호 42는 제1 도전막이다. 제1 도전막(42)은 드레인 영역(35)으로부터 제2 전극(40)을 전기적으로 접속하고 있다. 참조 부호 43은 제2 층간막, 참조 부호 44는 제1 차광막, 참조 부호 45는 제3 층간막, 참조 부호 46은 제2 차광막이다. 제2 층간막(43)과 제3 층간막(45)에는 관통 홀(42CH)이 형성되고, 제1 도전막(42)과 제2 차광막(46)이 전기적으로 접속되어 있다. 참조 부호 47은 제4 층간막, 참조 부호 48은 반사 전극(5)을 형성하는 제2 도전막이다. 능동 소자(30)의 드레인 영역(35)으로부터 제1 도전막(42), 관통 홀(42CH), 제2 차광막(46)을 통해 계조 전압은 반사 전극(5)에 전해진다.

본 실시예의 액정 표시 장치는 반사형으로서, 대량의 광이 액정 패널(100)에 조사된다. 차광막은 구동 회로 기판의 반도체층에 광이 입사하지 않도록 차광한다. 반사형 액정 표시 장치에서 액정 패널(100)에 조사된 광은 투명 기판(2)측(도 38의 상측)으로부터 입사하고, 액정 조성물(3)을 투과하고 반사하여 재차 액정 조성물(3), 투명 기판(2)을 투과하여 액정 패널(100)로부터 출사한다. 그러나, 액정 패널(100)에 조사되는 광의 일부는 반사 전극(5)의 간극으로부터 구동 회로 기판측으로 누설된다. 제1 차광막(44)과 제2 차광막(46)은 능동 소자(30)에 광이 입사하지 않도록 하기 위해 형성된다. 본 실시예에서는 이 차광막을 도전층으로 형성하고, 제2 차광막(46)을 반사 전극(5)에 전기적으로 접속하고, 제1 차광막(44)에 화소 전위 제어 신호를 공급함으로써, 차광막을 화소 용량의 일부로서도 기능하도록 하고 있다.

또, 제1 차광층(44)에 화소 전위 제어 신호를 공급하면, 계조 전압이 공급되는 제2 차광막(46)과 영상 신호선(103)을 형성하는 제1 도전층(42)이나 주사 신호선(102)을 형성하는 도전층(게이트 전극(36)과 동층의 도전층) 사이에 전기적 실드층으로서 제1 차광막(44)을 형성할 수 있다. 이 때문에, 제1 도전층(42)이나 게이트 전극(36) 등과 제2 차광막(46)이나 반사 전극(5) 간의 기생 용량 성분이 감소한다. 상술한 바와 같이 액정 용량 CL에 대하여 화소 용량 CC은 충분히 크게 할 필요가 있지만, 제1 차광막(44)을 전기적 실드층으로서 형성하면, 액정 용량 LC와 별별로 접속되는 기생 용량도 작아져서 더 효율적이다. 또한 신호선으로부터의 잡음의 유입을 감소시킬 수도 있다.

또한, 액정 표시 소자를 반사형으로 하고, 구동 회로 기판(1)의 액정 조성물(3)측의 면에 반사 전극(5)을 형성한 경우, 구동 회로 기판(1)으로서 불투명한 실리콘 기판 등을 이용하는 것이 가능하다. 또한, 능동 소자(30)나 배선을 반사 전극(5) 아래에 형성할 수 있으며, 화소가 되는 반사 전극(5)을 넓게 하여, 소위 높은 개구율을 실현할 수 있다는 이점이 있다. 또한, 액정 패널(100)에 조사되는 광에 의한 열을 구동 회로 기판(1)의 이면으로부터 방열할 수 있다는 이점도 있다.

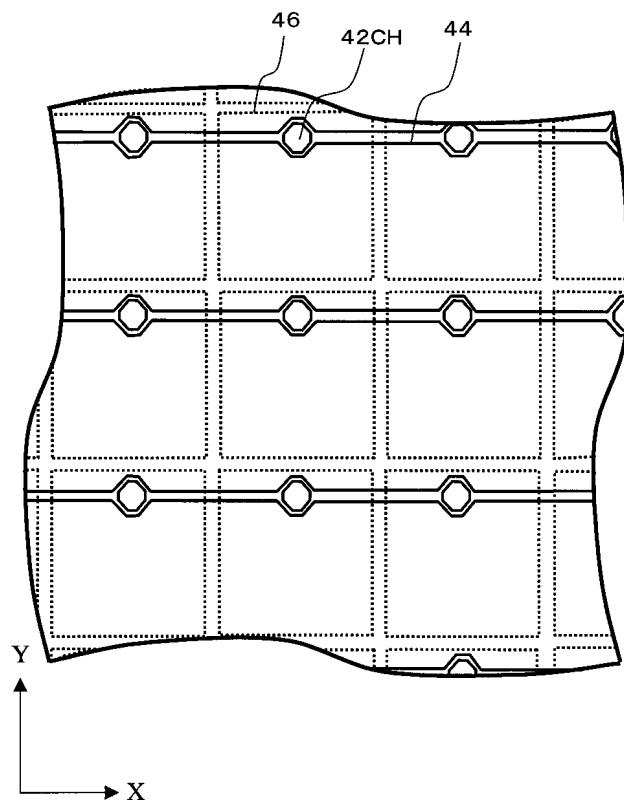

다음에 차광막을 화소 용량의 일부로서 이용하는 것에 대하여 설명한다. 제1 차광막(44)과 제2 차광막(46)은 제3 층간막(45)을 통해 대향하고 있고, 화소 용량의 일부를 형성한다. 참조 부호 49는 화소 전위 제어선(136)의 일부를 형성하는 도전층이다. 도전층(49)에 의해 제1 전극(31)과 제1 차광막(44)은 전기적으로 접속된다. 또한, 도전층(49)을 이용하여 화소 전위 제어 회로(135)로부터 화소 용량까지의 배선을 형성하는 것이 가능하다. 단, 본 실시예에서는 제1 차광막(44)을 배선으로 하여 이용하였다. 도 39에 제1 차광막(44)을 화소 전위 제어선(136)으로서 이용하는 구성에 대하여 도시한다.

도 39는 제1 차광막(44)의 배치를 도시하는 평면도이다. 참조 부호 46은 제2 차광막인데, 위치를 표시하기 위해서 점선으로 나타낸다. 참조 부호 42CH는 관통 홀로, 제1 도전막(42)과 제2 차광막(46)을 접속한다. 또, 도 39는 제1 차광막(44)을 알기 쉽게 나타내기 위해서, 다른 구성은 생략하고 있다. 제1 차광막(44)은 화소 전위 제어선(136)의 기능을 갖고 있고 도 39의 X 방향으로 연속하여 형성된다. 제1 차광막(44)은 차광막으로서 기능하기 위해서 표시 영역 전면을 덮도록 형성되어 있지만, 화소 전위 제어선(136)의 기능도 갖게 하기 위해서, X 방향으로 연장하고(주사 신호선(102)과 별별의 방향),

Y 방향으로 배열되어 라인 형상으로 형성되고, 화소 전위 제어 회로(135)에 접속된다. 또한, 화소 용량의 전극으로서도 기능하기 때문에, 제2 차광막(46)과 되도록 넓은 면적으로 중첩되도록 형성되어 있다. 또한, 차광막으로서 누설되는 광이 적어지도록, 인접하는 제1 차광막(44)의 간격은 되도록이면 좁아지도록 형성되어 있다.

단, 도 39에 도시한 바와 같이 인접하는 제1 차광막(44)의 간격을 좁게 형성하면, 차광막(44)의 일부가 인접하는 제2 차광막(46)과 중첩하게 된다. 상술한 바와 같이, 본 액정 표시 장치는 쌍방향으로 주사 가능하다. 그래서, 쌍방향으로 화소 전위 제어 신호를 주사한 경우에, 다음단의 제2 차광막(46)과 중첩하는 경우와 중첩하지 않은 경우가 생긴다. 도 39의 경우에는, 위에서 아래로 주사하는 경우에 제1 차광막(44)과 다음단의 제2 차광막(46)이 중첩한다.

도 40을 이용하여 차광막(44)의 일부가 다음단의 제2 차광막(46)과 중첩하는 것에 의한 문제점과 해결 방법을 설명한다. 도 40의 (a)는 문제점을 설명하는 타이밍도이다.  $\phi 2A$ 는 임의의 행의 주사 신호로서 A행째의 주사 신호로 한다.  $\phi 2B$ 는 다음단의 행의 주사 신호로서 B행째의 주사 신호로 한다. 또, 문제가 발생하는 기간  $t_2$  내지  $t_3$  사이에 대하여 설명하고, 그밖의 기간에 대해서는 생략한다.

도 40의 (a)에 있어서, A행째에 있어서 시각  $t_2$ 에서 2h(2수평 주사 시간) 후의 시각  $t_3$ 에 화소 전위 제어 신호  $\phi 3A$ 를 변화시킨다. 시각  $t_2$ 에서 1h 후에는 주사 신호  $\phi 2A$ 의 출력은 종료하며, 주사 신호  $\phi 2A$ 에서 구동되는 A행째의 능동 소자(30)는 오프 상태가 되고, A행째의 화소 전극(109)은 영상 신호선(103)으로부터 분리된다. 시각  $t_2$ 에서 2h 후의 시각  $t_3$ 이면, 신호가 전환에 의한 지연 등을 고려해도, A행째의 능동 소자(30)는 충분히 오프 상태로 된다. 그러나, 시각  $t_3$ 은 B행째의 주사 신호  $\phi 2B$ 가 전환하는 시간이다.

A행째의 제1 차광막(44)과 B행째의 제2 차광막(46)이 중첩하고 있기 때문에, B행째의 화소 전극과 A행째의 화소 전위 제어 신호선 간에 용량이 생기게 된다. 시각  $t_3$ 은 B행째의 능동 소자(30)가 오프 상태로 전환하는 때이기 때문에, B행째의 화소 전극(109)은 영상 신호선(103)으로부터 충분히 분리되어 있지 않다. 이 때에 B행째의 화소 전극(109)과 영상 신호선(103) 사이가 충분히 분리되어 있지 않기 때문에, 영상 신호선(103)과 화소 전극(109) 간에 전하가 이동한다. 즉, A행째의 화소 전자 제어 신호  $\phi 3A$ 의 전환이, B행째의 화소 전극(109)에 기입되는 전압  $\phi 4B$ 에 영향을 끼치게 된다.

이 화소 전자 제어 신호  $\phi 3A$ 에 의한 영향은 액정 표시 장치의 주사 방향이 일정하면 균일한 영향이 되어, 그다지 눈에 띄지는 않는다. 그러나, 적, 녹, 청 등의 색마다 액정 표시 장치를 구비하며, 각 액정 표시 장치의 출력을 거듭 컬러 표시하는 경우에, 액정 표시 장치의 광학적 배치에 의한 이유로, 예를 들면 하나의 액정 표시 장치만 아래에서 위로 주사하고, 다른 액정 표시 장치는 위에서 아래로 주사하는 경우가 있다. 이와 같이 복수의 액정 표시 장치 중에서 주사 방향이 다른 것이 있는 경우에는, 표시 품질이 불균일하게 되어 미관을 손상시키게 된다.

다음에, 도 40의 (b)를 이용하여 해결 방법을 설명한다. A행째의 화소 전위 제어 신호  $\phi 3A$ 를 A행째의 주사 신호  $\phi 2A$ 의 개시보다 3h 지연되어 출력하도록 한다. 이 경우, B행째의 주사 신호  $\phi 2B$ 도 전환한 후이고, B행째의 능동 소자(30)는 충분히 오프 상태이기 때문에 A행째의 화소 전위 제어 신호  $\phi 3A$ 에 의한 B행째의 화소 전극(109)에 기입되는 전압  $\phi 4B$ 에 미치는 영향이 감소한다.

또, 이 경우, 부극성용 입력 신호가 기입되는 시간이 정극성용 입력 신호에 대하여 3h 정도 짧아지는데, 예를 들면 주사 신호선(102)의 수가 100을 넘는 경우에는 3% 이하의 값이 된다. 그 때문에, 부극성용 입력 신호와 정극성용 입력 신호의 실효치의 차이는 기준 전위  $V_{com}$ 의 값 등에 의해 조정하는 것이 가능하다.

다음에 도 41을 이용하여 화소 용량에 공급되는 전압 VPP와 기판 전위 VBB와의 관계에 대하여 설명한다. 도 41의 (a)는 화소 전위 제어 회로(135)의 출력 회로(69)를 구성하는 인버터 회로를 도시한다.

도 41의 (a)에서 참조 부호 32는 p형 트랜지스터의 채널 영역이고 실리콘 기판(1)에 이온 주입 등의 방법에 의해 n형 웨이가 형성되어 있다. 실리콘 기판(1)에는 기판 전압 VBB가 공급되어 있고, n형 웨이(32)의 전위는 VBB로 되어 있다. 소스 영역(34)과 드레인 영역(35)은 p형 반도체층이고, 실리콘 기판(1)에 이온 주입 등의 방법에 의해 형성된다. p형 트랜지스터(30)의 게이트 전극(36)에 기판 전압 VBB보다 저전위의 전압이 인가되면 소스 영역(34)과 드레인 영역(35)이 도통 상태가 된다.

일반적으로 절연부를 형성하는 등의 필요가 없이 구조가 간단해지기 때문에, 동일한 실리콘 기판의 트랜지스터에는 공통의 기판 전위 VBB가 인가되어 있다. 본 발명의 액정 표시 장치는 동일한 실리콘 기판(1) 상에 구동 회로부의 트랜지스터와, 화소부의 트랜지스터가 형성되어 있다. 화소부의 트랜지스터도 마찬가지의 이유로, 동일한 전위의 기판 전위 VBB가 인가된다.

도 41의 (a)에 도시하는 인버터 회로에서는, 소스 영역(34)에는 화소 용량에 공급되는 전압 VPP가 인가된다. 소스 영역(34)은 p형 반도체층이고 n형 웨(32) 간에는 pn 접합으로 되어 있다. n형 웨(32)의 전위보다도 소스 영역(34)의 전위가 높아지면, 소스 영역(34)으로부터 n형 웨(32)에 전류가 흐른다는 문제점이 생긴다. 그 때문에, 기판 전압 VBB에 대하여 전압 VPP은 저전위가 되도록 설정된다.

상술한 바와 같이 화소 전극의 전압은 화소 전극에 기입된 전압을 V2, 액정 용량을 CL, 화소 용량을 CC, 화소 전극 제어 신호의 진폭을 VPP와 VSS로 하면, 전압 강하 후의 화소 전극의 전압은,  $V2 - \{CC/(CL+CC)\} \times (VPP-VSS)$ 로 나타낸다. 여기서, VSS에 GND 전위를 선택하면, 화소 전극의 전압 변동의 크기는 전압 VPP와 액정 용량 CL과 화소 용량 CC로 결정되게 된다.

도 41의 (b)를 이용하여  $CC/(CL+CC)$ 와 전압 VPP과의 관계를 나타낸다. 또 설명을 간단히 하기 위해서 기준 전압 Vcom을 GND 전위로 한다. 또한, 전압을 인가하지 않으면 백 표시(노멀 화이트)가 되는 방식인 경우에, 흑 표시(계조 최소)가 되도록 계조 전압이 화소 전극에 인가되는 경우를 설명한다. 도 41의 (b)의 φ1은 영상 신호 선택 회로(123)로부터 화소 전극에 기입되는 계조 전압을 나타낸다. φ1A는 정극성인 경우, φ2A는 부극성인 경우의 계조 전압이다. 흑 표시이기 때문에 기준 전압 Vcom과 화소 전극에 기입되는 계조 전압의 전위차가 최대가 되게 φ1A, φ1B가 설정된다. 도 41의 (b)에서, φ1A는 정극성용 신호이기 때문에, 종래대로 기준 전압 Vcom과의 전위차가 최대가 되도록  $+V_{max}$ 로 하고, φ1B는 Vcom(GND)으로 하여 화소 전극에 기입한 후에 화소 용량을 이용하여 강하한다.

φ4A, φ4B 모두 화소 전극의 전압을 나타내며, φ4A는  $CC/(CL+CC)$ 이 1인 이상적인 경우를 나타내고, φ4B는  $CC/(CL+CC)$ 이 1 이하가 되는 경우를 나타낸다. φ4A의 부극성인 경우, φ1B는 Vcom(GND)이 기입되기 때문에, 화소 전극 제어 신호의 진폭 VPP에 따라 강하된  $-V_{max}$ 는  $CC/(CL+CC)=1$ 로부터  $-V_{max}=-VPP$ 가 된다.

이에 대하여 φ4B는  $CC/(CL+CC)$ 이 1 이하이기 때문에,  $+V_{max} < VPP$ 가 되도록 화소 전극 제어 신호를 공급할 필요가 있다. 상술한 바와 같이  $VPP < VBB$ 일 필요가 있기 때문에,  $+V_{max} < VPP < VBB$ 와 같은 관계가 된다. 여기서, 저내압 회로로 하기 위해서, 화소 전압을 강하하는 방법을 이용하고 있지만, 화소 전극 제어 신호의 전압 VPP이 고전압으로 되게 되면, 기판 전압 VBB가 고전압이 되게 되어 결국 고내압 회로가 된다는 문제점이 생긴다. 그 때문에,  $CC/(CL+CC)$ 가 되도록 하면 1이 되도록, 즉  $CL < CC$ 가 되도록, CL과 CC의 값을 정할 필요가 있다.

또, 종래의 유리 기판에 박막 트랜지스터를 형성하는 액정 표시 장치에서는 화소 전극을 되도록이면 넓게(소위, 고개구울화) 할 필요가 있기 때문에, 기껏해야  $CL=CC$ 로 하는 것이 실현 가능할 정도이다. 또한, 본 발명의 액정 표시 장치는 구동 회로부와 화소부가 동일 실리콘 기판 상에 형성되는 것이기 때문에, 기판 전위 VBB를 고전압으로 해서는 저내압화할 수 없다는 문제점을 갖고 있다.

다음에 도 42를 이용하여 부극성용의 계조 전압에 대하여 설명하고, 또한 도 43에 의해 참조표를 이용하여 부극성용의 계조 전압을 형성하는 방법에 대하여 설명한다. 또, 도 42에서는 연이은 설명을 간단히 하기 위해서 기준 전압 Vcom을 GND 전위로 한다. 또한, 전압을 인가하지 않으면 백 표시(노멀 화이트)가 되는 방식의 경우에 설명한다.

도 42의 (a)의 φ1은 영상 신호 선택 회로(123)로부터 화소 전극에 기입되는 계조 전압을 나타내고, 도 42의 (b)의 φ4는 화소 전극의 전압을 나타낸다. 우선, 흑 표시(계조 최소)가 되도록 계조 전압이 화소 전극에 인가되는 경우에 대해 설명한다. φ1A1은 정극성인 경우에, φ1B1은 부극성의 경우를 도시한다. 흑 표시이기 때문에 기준 전압 Vcom과 화소 전극에 기입되는 전압의 전위차가 최대가 되도록 φ1A1, φ1B1 모두 설정된다.

도 42의 (b)에서, φ1A1은 정극성용 신호이기 때문에, 화소 전극의 전압은 종래대로 기준 전압 Vcom과의 전위차가 최대가 되도록  $+V_{max}$ 가 된다. 이에 대하여 부극성용 신호인 φ1B1은 화소 전극에 기입한 후에 화소 용량을 이용하여 강하되어  $-V_{max}$ 가 된다.

다음에, 백 표시(계조 최대)가 되도록 계조 전압이 화소 전극에 인가되는 경우에 대해 설명한다.  $\phi 1A2$ 는 정극성인 경우,  $\phi 1B2$ 는 부극성인 경우를 나타낸다. 백 표시이기 때문에 기준 전압  $V_{com}$ 과 화소 전극에 기입되는 전압의 전위차가 최소가 되게  $\phi 1A2$ ,  $\phi 1B2$  모두 설정된다.

도 42의 (b)에서  $\phi 1A2$ 는 정극성용 신호이기 때문에, 종래대로 기준 전압  $V_{com}$ 과의 전위차가 최소가 되도록  $+V_{min}$ 이 된다. 부극성용 신호  $\phi 1B2$ 는 화소 전극에 기입한 후에 화소 용량을 이용하여 강하된다. 강하되는 전압은 VPP이기 때문에, 강하된 후에  $-V_{min}$ 이 된 전압이  $\phi 1B2$ 로서 선택된다.

도 42에 도시한 바와 같이, 부극성용 신호  $\phi 1B1$ ,  $\phi 1B2$ 는 종래 이용된 방법과 같이, 단순하게 정극성용 신호  $\phi 1A1$ ,  $\phi 1A2$ 를 반전한 전압이 아니다. 그 때문에, 참조표를 이용하여 부극성용 신호를 작성하게 하였다. 도 43에 참조표를 이용하여 부극성용 신호를 작성하는 영상 신호 제어 회로(400)의 블록도를 도시한다. 참조 부호 422는 부극성용 참조표이고, 참조 부호 423은 정극성용 참조표이다. 부극성용 신호는 화소 용량을 이용하여 작성되기 때문에, 부극성, 정극성용 연산 증폭기는 사용되지 않는다.

정극성용 참조표(422)에는 변동 보정을 행하는 보정 데이터가 이용된다. 이에 대하여 부극성용 참조표(423)에는 변동 보정을 행하는 보정 데이터 외에 화소 용량에 의해 강하되고 부극성용 신호가 되는 보정도 가해진다. 교류화 신호에 의해 아날로그 스위치(417)를 전환함으로써, 정극성용 신호와 부극성용 신호가 DA 변환 회로(405)에 전해진다.

다음에 반사형 액정 표시 장치의 동작에 대하여 설명한다. 반사형 액정 표시 소자의 하나로서 전계 제어 복굴절 모드(ELECTRICALLY CONTROLLED BIREFRINGENCE MODE)가 알려진다. 전계 제어 복굴절 모드에서는 반사 전극과 대향 전극 간에 전압을 인가하여 액정 조성물의 문자 배열을 변화시켜, 그 결과로서 액정 패널의 복굴절율을 변화시킨다. 전계 제어 복굴절 모드는 이 복굴절율의 변화를 광 투과율의 변화로서 이용하여 상을 형성하는 것이다.

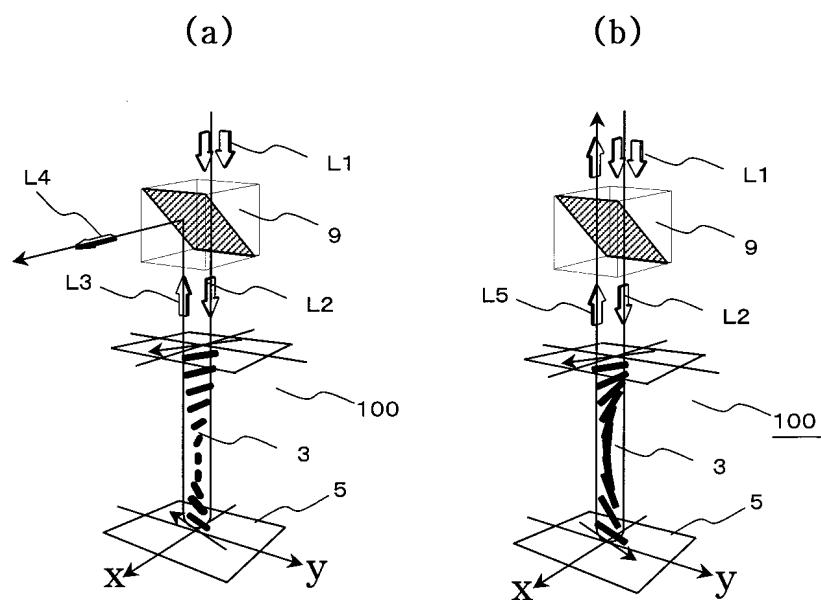

또한 도 44를 이용하여, 전계 제어 복굴절 모드의 하나인 단편광판 트위스티드 네마틱 모드(SPTN)에 대하여 설명한다. 참조 부호 9는 편광 빔분할기로 광원(도시하지 않음)으로부터의 입사광 L1을 2개의 편광으로 분할하고, 직선 편광이 된 광 L2를 출사한다. 도 44에서는 액정 패널(100)에 입사되는 광에 편광 빔분할기(9)를 투과한 광(P파)을 이용하는 경우를 도시하지만, 편광 빔 스플리터(9)에서 반사한 광(S파)을 이용하는 것도 가능하다. 액정 조성물(3)은 액정 문자 장축이 구동 회로 기판(1)과 투명 기판(2)에 대하여 평행하도록 배열되고, 유전 이방성이 플러스인 네마틱 액정을 이용한다. 또한, 액정 문자는 배향막(7, 8)에 의해 약 90도 어긋난 상태로 배향한다.

우선 도 44의 (a)에 전압이 인가되어 있지 않은 경우를 도시한다. 액정 패널(100)에 입사한 광은 액정 조성물(3)의 복굴절성에 의해 타원 편광이 되어 반사 전극(5)면에서는 원편광이 된다. 반사 전극(5)으로 반사한 광은 재차 액정 조성물(3) 중을 통과하여 다시 타원 편광이 되어 출사 시에는 직선 편광으로 되돌아가고, 입사광 L2에 대하여 90도 위상이 회전한 광 L3(S파)로서 출사한다. 출사 광 L3은 다시 편광 빔분할기(9)에 입사하지만, 편광면에서 반사되어 출사 광 L4가 된다. 이 출사 광 L4를 스크린 등에 조사하여 표시를 행한다. 이 경우, 전압을 인가하지 않은 경우에 광이 출사하는 소위 노멀 화이트(노멀 오픈)라고 불리는 표시 방식이 된다.

이에 대하여 도 44의 (b)에 액정 조성물(3)에 전압이 인가되어 있는 경우를 도시한다. 액정 조성물(3)에 전압이 인가되면, 액정 문자가 전계 방향으로 배열하기 때문에, 액정 내에서 복굴절이 발생하는 비율이 감소한다. 그 때문에, 직선 편광으로 액정 패널(100)에 입사한 광 L2는 그대로 반사 전극(5)에 의해 반사되어 입사광 L2와 동일한 편광 방향의 광 L5로서 출사한다. 출사 광 L5는 편광 빔분할기(9)를 투과하여 광원으로 되돌아간다. 그 때문에, 스크린 등에 광이 조사되지 않기 때문에, 흑 표시가 된다.

단편광판 트위스티드 네마틱 모드에서는 액정 문자의 배향 방향이 기판과 평행하기 때문에, 일반적인 배향 방향을 이용할 수 있어, 프로세스 안정성이 우수하다. 또한 노멀 화이트로 사용하기 위해서, 저전압측에서 발생하는 표시불량에 대하여 여유도를 갖게 할 수 있다. 즉, 노멀 화이트 방식으로는 암 레벨(흑 표시)이 고전압을 인가한 상태에서 얻어진다. 이 고전압의 경우에는 액정 문자의 대부분이 기판면에 수직인 전계 방향으로 정렬되어 있기 때문에, 암 레벨의 표시는 저전압 시의 초기 배향 상태에 별로 의존하지는 않는다. 또한, 인간의 눈은 휘도 불균일을 휘도의 상대적인 비율로서 인식하고, 또한 휘도에 대하여 대수 스케일에 가까운 반응을 갖는다. 그 때문에, 인간의 눈은 암 레벨의 변동에는 민감하다. 이러한 이유에서, 노멀 화이트 방식은 초기 배향 상태에 의한 휘도 불균일에 대하여 유리한 표시 방식이다.

그러나, 상술한 전계 제어 복굴절 모드로서는 높은 셀 캡의 정밀도가 요구된다. 즉, 전계 제어 복굴절 모드에서는, 광이 액정층 내를 통과하는 동안에 생기는 이상 광과 상광과의 위상차를 이용하기 때문에, 투과광 강도는 이상 광과 상광 간의 지연  $\Delta n \cdot d$ 에 의존한다. 여기서,  $\Delta n$ 은 굴절율 이방성이고,  $d$ 는 스페이서(4)에 의해 형성되는 투명 기판(2)과 구동 회로 기판(1) 사이의 셀 캡이다(도 38 참조).

이 때문에, 본 실시예의 경우, 표시 불균일을 고려하여 셀 캡 정밀도는  $\pm 0.05\mu\text{m}$  이하로 하였다. 또한, 반사형 액정 표시 소자에서는 액정에 입사한 광은 반사 전극으로 반사하여 재차 액정층을 통과하기 때문에, 동일한 굴절율 이방성  $\Delta n$ 의 액정을 이용하는 경우, 투과형 액정 표시 소자에 대하여 셀 캡  $d$ 는 반이 된다. 일반적인 투과형 액정 표시 소자의 경우 셀 캡  $d$ 는  $5 \sim 6\mu\text{m}$  정도인 데 대하여, 본 실시예에서는 약  $2\mu\text{m}$  이다.

본 실시예에서는 높은 셀 캡 정밀도와, 보다 좁은 셀 캡에 대응하기 위해서, 종래부터 있는 비즈 분산법 대신에 기동형의 스페이서를 구동 회로 기판(1) 상에 형성하는 방법을 이용하였다.

도 45에 구동 회로 기판(1) 상에 형성된 반사 전극(5)과 스페이서(4)와의 배치를 설명하는 모식 평면도를 도시한다. 일정한 간격을 유지하도록 다수의 스페이서(4)가 구동 회로 기판 전면에 매트릭스 형상으로 형성되어 있다. 반사 전극(5)은 액정 표시 소자가 형성하는 상의 최소의 화소이다. 도 45에서는 간략화를 위해서, 참조 부호 5A, 5B로 나타내는 세로 4 화소, 가로 5 화소로 나타내었다. 또, 최외측의 화소군을 참조 부호 5B로 나타내고, 이들보다 내측의 화소군을 참조 부호 5A로 나타낸다.

도 45에서는 세로 4 화소, 가로 5 화소의 화소가 표시 영역을 형성한다. 액정 표시 소자로 표시하는 상은 이 표시 영역에 형성된다. 표시 영역의 외측에는 더미 화소(113)가 형성된다. 이 더미 화소(113)의 주변에 스페이서(4)와 동일한 재료로 주변 프레임(11)이 형성된다. 또한, 주변 프레임(11)의 외측에는 시일재(12)가 도포된다. 참조 부호 13은 외부 접속 단자로서 액정 패널(100)에 외부로부터의 신호를 공급하는 데 이용된다.

스페이서(4)와 주변 프레임(11)의 재료로는 수지 재료를 이용하였다. 수지 재료로서, 예를 들면 주식회사 JSR제의 화학 증폭형 네가티브 타입 레지스트 「BPR-113」(상품명)을 이용할 수 있다. 반사 전극(5)이 형성된 구동 회로 기판(1) 상에 스펜코팅법 등으로 레지스트재를 도포하고, 마스크를 이용하여 레지스트를 스페이서(4)와 주변 프레임(11)의 패턴으로 노광한다. 그 후 제거제를 이용하여 레지스트를 현상하여 스페이서(4)와 주변 프레임(11)을 형성한다.

스페이서(4)와 주변 프레임(11)을 레지스트재 등을 원료로 하여 형성하면, 도포하는 재료의 막 두께로 스페이서(4)와 주변 프레임(11)의 높이를 제어할 수 있으며, 높은 정밀도로 스페이서(4)와 주변 프레임(11)을 형성하는 것이 가능하다. 또한, 스페이서(4)의 위치는 마스크 패턴으로 결정할 수 있어, 희망하는 위치에 정확하게 스페이서(4)를 형성하는 것이 가능하다. 액정 프로젝터에는 화소 위에 스페이서(4)가 존재하면, 확대 투영된 상에 스페이서에 의한 그림자가 보이게 되는 문제가 있다. 스페이서(4)를 마스크 패턴에 의한 노광, 현상에 의해 형성함으로써, 영상 표시했을 때에, 문제로 되지 않는 위치에 스페이서(4)를 형성할 수 있다.

또한, 스페이서(4)와 동시에 주변 프레임(11)을 형성하기 때문에, 액정 조성물(3)을 구동 회로 기판(1)과 투명 기판(2) 사이에 봉입하는 방법으로서, 액정 조성물(3)을 구동 회로 기판(1)에 적하하고 그 후 투명 기판(2)을 구동 회로 기판(1)에 접합하는 방법을 이용할 수 있다.

액정 조성물(3)을 구동 회로 기판(1)과 투명 기판(2) 사이에 배치하고, 액정 패널(100)을 조립한 후에는 주변 프레임(11)에 의해 둘러싸인 영역 내에 액정 조성물(3)이 유지된다. 또한, 주변 프레임(11)의 외측에는 시일재(12)가 도포되고, 액정 조성물(3)을 액정 패널(100) 내에 봉입한다. 상술한 바와 같이, 주변 프레임(11)은 마스크 패턴을 이용하여 형성되기 때문에, 높은 위치 정밀도로 구동 회로 기판(1) 상에 형성할 수 있다. 그 때문에, 액정 조성물(3)의 경계를 높은 정밀도로 정하는 것이 가능하다. 또한, 주변 프레임(11)은 시일재(12)의 형성 영역의 경계도 높은 정밀도로 정하는 것이 가능하다.

시일재(12)는 구동 회로 기판(1)과 투명 기판(2)을 고정하는 역할과, 액정 조성물(3)에 있어서 유해한 물질이 진입하는 것을 막는 역할이 있다. 유동성이 있는 시일재(12)를 도포한 경우에, 주변 프레임(11)은 시일재(12)의 스토퍼가 된다. 시일재(12)의 스토퍼로서 주변 프레임(11)을 형성함으로써, 액정 조성물(3)의 경계나 시일재(12)의 경계에서의 설계 여유도를 넓게 할 수 있고, 액정 패널(100)의 모서리에서 표시 영역까지의 사이를 좁게(협액연화) 하는 것이 가능하다.

표시 영역을 둘러싸도록 주변 프레임(11)이 형성되기 때문에, 구동 회로 기판(1)을 러빙 처리할 때에, 주변 프레임(11)에 의해 주변 프레임(11)의 근방이 잘 러빙될 수 없는 문제가 있다. 액정 조성물(3)을 일정한 방향으로 배향하기 위해서, 배향

막을 형성하여 러빙 처리가 행해진다. 본 실시예의 경우, 구동 회로 기판(1)에 스페이서(4), 주변 프레임(11)이 형성된 후에, 배향막(7)이 도포된다. 그 후, 액정 조성물(3)이 일정 방향으로 배향하도록, 배향막(7)을 천 등을 이용하여 문지름으로 써 러빙 처리가 행해진다.

러빙 처리에 있어서, 주변 프레임(11)이 구동 회로 기판(1)보다 돌출되어 있기 때문에, 주변 프레임(11)의 근방의 배향막(7)은 주변 프레임(11)에 의한 단차에 의해 충분히 문질러지지 않는다. 그 때문에, 주변 프레임(11)의 근방에는 액정 조성물(3)의 배향이 불균일한 부분이 생기기 쉽다. 액정 조성물(3)의 배향 불량에 의한 표시 불균일이 눈에 띠지 않게 하기 위해서, 주변 프레임(11)의 내측 화소를 더미 화소(113)로 함으로써, 표시에 기여하지 않는 화소로 하고 있다.

그런데, 더미 화소(113)를 형성하여 화소(5A, 5B)와 동일하게 신호를 공급하면, 더미 화소(113)와 투명 기판(2) 사이에는 액정 조성물(3)이 존재하기 때문에, 더미 화소(113)에 의한 표시도 관찰된다는 문제가 생긴다. 노멀 화이트로 사용하는 경우, 액정 조성물(3)에 전압을 인가하지 않으면, 더미 화소(113)가 희게 표시된다. 그 때문에, 표시 영역의 경계가 명확하지 않게 되어, 표시 품질을 손상시킨다. 더미 화소(113)를 차광하는 것도 생각되지만, 화소와 화소의 간격은 수  $\mu$ m이기 때문에, 표시 영역의 경계에 높은 정밀도로 차광 프레임을 형성하는 것은 곤란하다. 그래서, 더미 화소(113)에는 흑 표시가 된 전압을 공급하여 표시 영역을 둘러싸는 까만 테로서 관찰되도록 하였다.

도 46에 더미 화소(113)의 구동 방법에 대하여 설명한다. 더미 화소(113)에는 흑 표시가 되는 전압을 공급하기 때문에, 더미 화소가 형성된 영역은 일면 흑 표시가 된다. 일면 흑 표시가 되면, 표시 영역에 형성한 화소와 동일하게 개별로 형성할 필요가 없고, 복수의 더미 화소를 전기적으로 접속하여 형성할 수 있다. 또한, 구동에 필요한 시간을 생각하면, 더미 화소를 위해 기입 시간을 준비할 필요는 없다. 그래서, 복수의 더미 화소의 전극을 연속하여 형성하여 하나의 더미 화소 전극으로 하는 것이 가능하다. 그러나, 복수의 더미 화소를 접속하여 하나의 더미 화소로 하면 화소 전극의 면적이 증가하기 때문에, 액정 용량이 커지게 된다. 상술한 바와 같이 액정 용량이 커지면 화소 용량을 이용하여 화소 전압을 강화하는 효율이 저하한다.

그래서, 더미 화소도 표시 영역의 화소와 마찬가지로 개별로 형성하도록 하였다. 그러나, 유효 화소와 마찬가지로 1 라인 별로 기입을 행한 경우, 새롭게 형성한 복수 행의 더미 행을 구동하는 시간이 길어진다. 그리고, 그 만큼 유효 화소에 기입을 행할 시간이 짧아진다는 문제가 생긴다. 이에 대하여 고정밀 표시를 행하는 경우에는, 고속의 영상 신호(도트 클러리이 높은 신호)가 입력하기 때문에, 점점 더 화소의 기입 시간에 대한 제한이 생기게 된다. 그래서 1 화면의 기입 기간 중에 몇 라인분의 기입 시간을 절약하기 위해서, 도 43에 도시한 바와 같이 더미 화소에 대해서는 수직 구동 회로(130)의 수직 쌍방향 시프트 레지스터 VSR에서 복수 행분의 타이밍 신호를 출력시켜, 복수의 레벨 시프터(67)와 출력 회로(69)에 입력시켜 주사 신호를 출력하도록 하였다. 또한, 동일하게 화소 전극 제어 회로(135)에 대해서도 쌍방향 시프트 레지스터 SR에서 복수 행분의 타이밍 신호를 출력시켜, 복수의 레벨 시프터(67)와 출력 회로(69)에 입력시켜 화소 전극 제어 신호를 출력하도록 하였다.

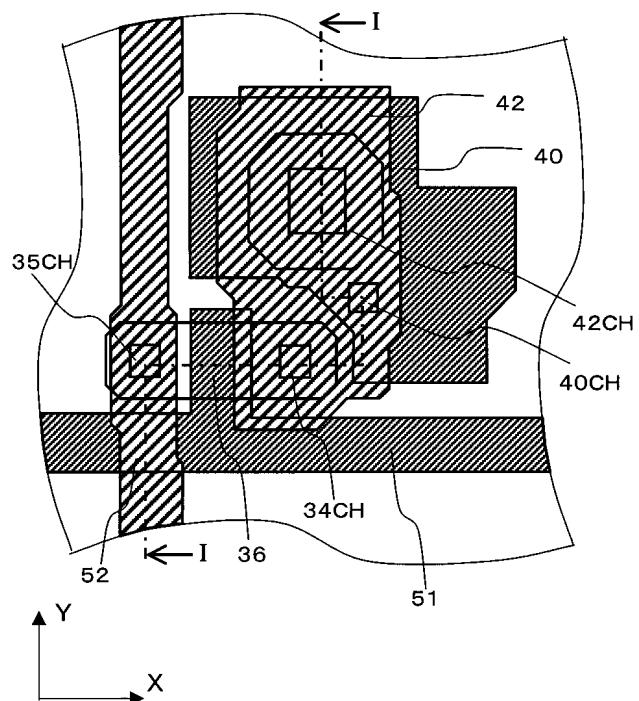

다음에, 도 47, 도 48을 이용하여 구동 회로 기판(1) 상에 형성되는 능동 소자(30)와 그 주변의 구성을 상세히 설명한다. 도 47, 도 48에 있어서, 도 38과 동일한 부호는 동일한 구성을 도시한다. 도 48은 능동 소자(30) 주변을 도시하는 개략 평면도이다. 도 47은 도 48의 I-I선에서의 단면도인데, 도 47과 도 48과의 각 구성 간의 거리는 일치하지 않는다. 또한 도 48은 주사 신호선(102)과 게이트 전극(36), 영상 신호선(103)과 소스 영역(35), 드레인 영역(34), 화소 용량을 형성하는 제2 전극(40)과 제1 도전층(42)과, 컨택트홀(35CH, 34CH, 40CH, 42CH)의 위치 관계를 나타내는 것으로, 그 밖의 구성은 생략하였다.

도 47에 있어서, 참조 부호 1은 구동 회로 기판인 실리콘 기판, 참조 부호 32는 실리콘 기판(1)에 이온 주입으로 형성한 반도체 영역(p형 웨), 참조 부호 33은 채널 스토퍼, 참조 부호 34는 p형 웨(32)에 이온 주입으로 도전화하여 형성한 드레인 영역, 참조 부호 35는 p형 웨(32)에 이온 주입으로 형성한 소스 영역, 참조 부호 31은 p형 웨(32)에 이온 주입으로 도전화하여 형성한 화소 용량의 제1 전극이다. 또, 본 실시예에서는 능동 소자(30)를 p형 트랜지스터로 나타내었지만, n형 트랜지스터로 하는 것도 가능하다.

참조 부호 36은 게이트 전극, 참조 부호 37은 게이트 전극 단부의 전계 강도를 완화하는 오프셋 영역, 참조 부호 38은 절연막, 참조 부호 39는 트랜지스터 사이를 전기적으로 분리하는 필드 산화막, 참조 부호 40은 화소 용량을 형성하는 제2 전극으로서 절연막(38)을 통하여 실리콘 기판(1)에 형성한 제1 전극(21)과의 사이에서 용량을 형성한다. 게이트 전극(36)과 제2 전극(40)은 절연막(38) 상에 능동 소자(30)의 임계치를 낮게 하기 위한 도전층과 저저항의 도전층을 적층한 2층막으로 이루어진다. 2층막으로서는, 예를 들면 폴리실리콘과 텅스텐 실리사이드의 막을 이용할 수 있다. 참조 부호 41은 제1

충간막, 참조 부호 42는 제1 도전막이다. 제1 도전막(42)은 접촉 불량을 방지하는 배리어 메탈과 저저항의 도전막의 다층 막으로 이루어지고 있다. 제1 도전막으로서, 예를 들면 티탄 텅스텐과 알루미늄의 다층 금속막을 스퍼터로 형성하여 이용할 수 있다.

도 48에서 참조 부호 102는 주사 신호선이다. 주사 신호선(102)은 도 48 중, X 방향으로 연장하고 Y 방향으로 병설되어 있고, 능동 소자(30)를 온 오프하는 주사 신호가 공급된다. 주사 신호선(102)은 게이트 전극과 동일한 2층막으로 이루어져 있어, 예를 들면 폴리실리콘과 텅스텐 실리사이드를 적층한 2층막을 이용할 수 있다. 영상 신호선(103)은 Y 방향으로 연장하고 X 방향으로 병설되어 있고, 반사 전극(5)에 기입되는 영상 신호가 공급된다. 영상 신호선(103)은 제1 도전막(42)과 동일한 다층 금속막으로 이루어져 있으며, 예를 들면 티탄 텅스텐과 알루미늄의 다층 금속막을 이용할 수 있다.

영상 신호는 절연막(38)과 제1 충간막(41)에 비워진 컨택트홀(35CH)을 통해 제1 도전막(42)에 의해 드레인 영역(35)에 전해진다. 주사 신호선(102)에 주사 신호가 공급되면, 능동 소자(30)는 은이 되어, 영상 신호가 반도체 영역(p형 웨이: 32)으로부터 소스 영역(34)에 전해지고, 컨택트홀(34CH)을 통해 제1 도전막(42)에 전해진다. 제1 도전막(42)에 전해진 영상 신호는 컨택트홀(40CH)을 통해 화소 용량의 제2 전극(40)에 전해진다.

또한, 도 47에 도시한 바와 같이 영상 신호는 컨택트홀(42CH)을 통해 반사 전극(5)에 전해진다. 컨택트홀(42CH)은 필드 산화막(39) 상에 형성되어 있다. 필드 산화막(39)은 막 두께가 두껍기 때문에, 필드 산화막의 윗 부분은 다른 구성에 비하여 높은 위치로 되어 있다. 컨택트홀(42CH)은 필드 산화막(39) 상에 형성됨으로써, 상층의 도전막에 보다 가까운 위치로 할 수 있어, 컨택트홀의 접속부의 길이를 짧게 하고 있다.

또한 도 47에 도시한 바와 같이, 제2 충간막(43)은 제1 도전막(42)과 제2 도전막(44)을 절연하고 있다. 제2 충간막(43)은 각 구성물에 의해 생기는 요철을 매립하는 평탄화막(43A)과 그 위를 덮는 절연막(43B)의 2층으로 형성되어 있다. 평탄화막(43A)은 SOG(spinongrass)을 도포하여 형성한다. 절연막(43B)은 TEOS 막이고, 반응 가스로서 TEOS(Tetraethylorthosilicate)를 이용하여  $\text{SiO}_2$  막을 CVD에 의해 형성한 것이다.

제2 충간막(43)의 형성 후, CMP(화학 기계적 연마)에 의해 제2 충간막(43)이 연마된다. 제2 충간막(43)은 CMP에 의해 연마함으로써 평탄화한다. 평탄화된 제2 충간막의 상에 제1 차광막(44)이 형성된다. 제1 차광막(44)은 제1 도전막(42)과 동일한 텅스텐과 알루미늄의 다층 금속막으로 형성되어 있다.

제1 차광막(44)은 구동 회로 기판(1)의 대략 전면을 피복하고 있고, 개구는 도 45에 도시하는 컨택트홀(42CH)의 부분만 있다. 제1 차광막(44)의 위에 제3 충간막(45)이 TEOS 막으로 형성되어 있다. 또한 제3 충간막(45) 위에 제2 차광막(46)이 형성되어 있다. 제2 차광막(46)은 제1 도전막(42)과 동일한 텅스텐과 알루미늄의 다층 금속막으로 형성한다. 제2 차광막(46)은 컨택트홀(42CH)에 의해 제1 도전막(42)과 접속되어 있다. 컨택트홀(42CH)에서는, 접속을 위해서 제1 차광막(44)을 형성하는 금속막과 제2 차광막(46)을 형성하는 금속막이 적층되어 있다.

제1 차광막(44)과 제2 차광막(46)을 도전막으로 형성하고, 사이에 제3 충간막(45)을 절연막(유전막)으로 형성하고, 제1 차광막(44)에 화소 전위 제어 신호를 공급하고, 제2 차광막(46)에 계조 전압을 공급하면, 제1 차광막(44)과 제2 차광막(46)으로 화소 용량을 형성할 수 있다. 또한, 계조 전압에 대한 제3 충간막(45)의 내압과, 막 두께를 얇게 하여 용량을 크게 하는 것을 고려하면, 제3 충간막(45)은 150nm 내지 450nm가 바람직하고, 보다 바람직한 것은 약 300nm이다.

다음에, 도 49에 구동 회로 기판(1)에 투명 기판(2)을 정합시킨 도면을 도시한다. 구동 회로 기판(1)의 주변부에는 주변 프레임(11)이 형성되어 있으며, 액정 조성물(3)은 주변 프레임(11)과 구동 회로 기판(1)과 투명 기판(2)에 둘러싸인 가운데에 유지된다. 중첩된 구동 회로 기판(1)과 투명 기판(2) 사이에서 주변 프레임(11)의 외측에는 시일재(12)가 도포된다. 시일재(12)에 의해 구동 회로 기판(1)과 투명 기판(2)이 접착 고정되어 액정 패널(100)이 형성된다. 참조 부호 13은 외부 접속 단자이다.

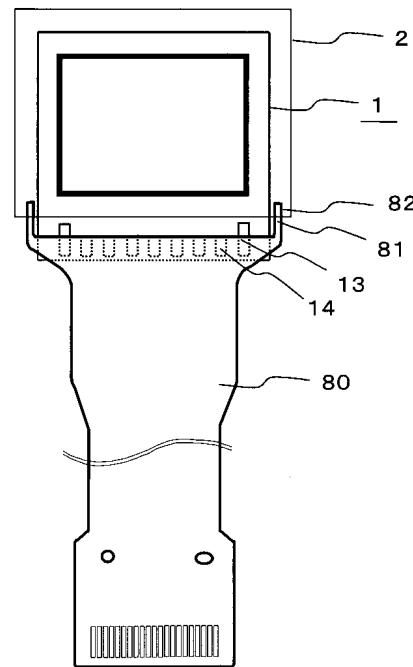

다음에 도 50에 도시한 바와 같이, 액정 패널(100)에 외부로부터의 신호를 공급하는 플렉시블 프린트 배선판(80)이 외부 접속 단자(13)에 접속된다. 플렉시블 프린트 배선판(80)의 양 외측의 단자는 다른 단자에 비하여 길게 형성되며, 투명 기판(2)에 형성된 대향 전극(5)에 접속되며, 대향 전극용 단자(81)를 형성한다. 즉, 플렉시블 프린트 배선판(80)은 구동 회로 기판(1)과 투명 기판(2)의 양방에 접속되어 있다.

종래의 대향 전극(5)에의 배선은 구동 회로 기판(1)에 형성된 외부 접속 단자에 플렉시블 프린트 배선판이 접속되며, 구동 회로 기판(1)을 경유하여 대향 전극(5)에 접속되는 것이었다. 본 실시예의 투명 기판(2)에는 플렉시블 프린트 배선판

(80)과의 접속부(82)가 형성되며, 플렉시블 프린트 배선판(80)과 대향 전극(5)이 직접 접속된다. 즉, 액정 패널(100)은 투명 기판(2)과 구동 회로 기판(1)이 중첩되어 형성되는데, 투명 기판(2)의 일부는 구동 회로 기판(1)보다 외측으로 돌출되어 접속부(82)를 형성하고 있으며, 이 투명 기판(2)의 외측으로 돌출된 부분에서 플렉시블 프린트 배선판(80)과 접속된다.

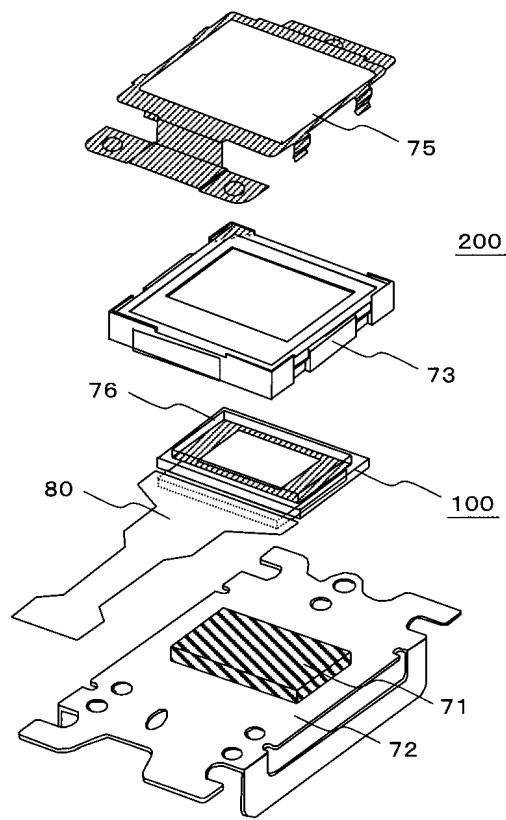

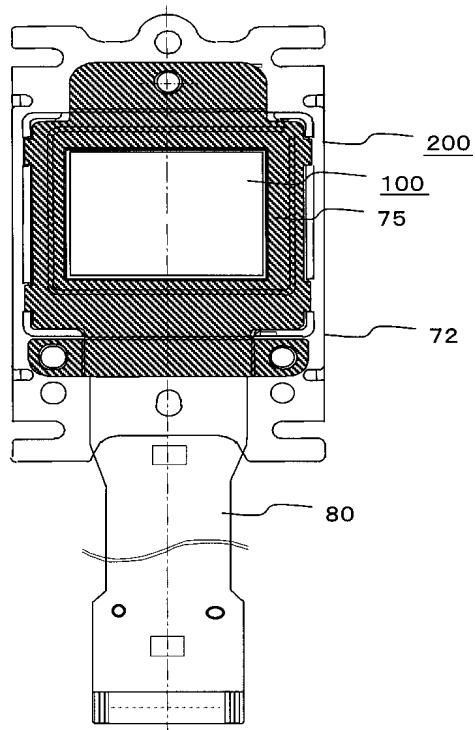

도 51, 도 52에 액정 표시 장치(200)의 구성을 도시한다. 도 51은 액정 표시 장치(200)를 구성하는 각 구성물의 분해 조립도이다. 또 도 52는 액정 표시 장치(200)의 평면도이다.

도 51에 도시한 바와 같이, 플렉시블 프린트 배선판(80)이 접속된 액정 패널(100)은 쿠션재(71)를 사이에 두고, 방열판(72)에 배치된다. 쿠션재(71)는 고열전도성이고, 방열판(72)과 액정 패널(100)과의 간극을 매립하여, 액정 패널(100)의 열이 방열판(72)에 전해지기 쉽게 하는 기능을 갖는다. 참조 부호 73은 몰드로, 방열판(72)에 접착 고정되어 있다.

또한 도 51에 도시한 바와 같이, 플렉시블 프린트 배선판(80)은 몰드(73)와 방열판(72) 사이를 지나 몰드(73)의 외측으로 돌출된다. 참조 부호 75는 차광판으로, 광원으로부터의 광이 액정 표시 장치(200)를 구성하는 다른 부재에 조사되는 것을 막고 있다. 참조 부호 76은 차광 프레임으로서 액정 표시 장치(200)의 표시 영역의 외부 프레임을 표시한다.

이상, 본 발명자에 의해 이루어진 발명을 상기 발명의 실시 형태에 기초하여 구체적으로 설명하였지만, 본 발명은 상기 발명의 실시 형태에 한정되지는 않고, 그 요지를 일탈하지 않는 범위에서 여러가지 변경 가능한 것은 물론이다.

### 발명의 효과

본원에 있어서 개시되는 발명 중 대표적인 것에 의해 얻어지는 효과를 간단히 설명하면 하기와 같다.

본 발명에 따르면 신호의 변동의 보정을 할 수 있기 때문에, 액정으로 화상을 표시할 때의 화질의 향상을 도모할 수 있다.

본 발명에 따르면, 변동 보정은 소프트웨어적으로 변경할 수 있기 때문에, 하드웨어적인 상수의 변경 등을 필요로 하지 않아 비용의 저감을 도모할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

액정 표시 장치에 있어서,

액정 패널과,

상기 액정 패널에 영상 신호를 공급하는 영상 신호 제어 회로와,

상기 액정 패널을 구동하는 구동 회로를 구비하고,

상기 영상 신호 제어 회로와 상기 구동 회로를 복수의 영상 신호선이 전기적으로 접속하여, 상기 구동 회로에 상기 영상 신호선을 통해 아날로그 신호를 입력하고,

상기 영상 신호 제어 회로에는, 1개의 디지털 신호를 복수의 디지털 신호로 분할하여 상기 영상 신호선마다 영상 신호를 출력하는 증폭 회로가 형성되고,

상기 영상 신호 제어 회로는, 디지털 신호로부터 아날로그 신호를 형성하고, 상기 아날로그 신호를 증폭하여 상기 증폭 회로로부터 상기 영상 신호로서 출력하고, 상기 증폭 회로간의 출력 변동을 상기 디지털 신호의 값을 변환함으로써 보정하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 2.

액정 표시 장치에 있어서,

액정 패널과,

상기 액정 패널을 형성하는 제1 기판 및 제2 기판과,

상기 제1 기판과 제2 기판 사이에 삽입된 액정 조성물과,

상기 제1 기판에 형성된 복수의 화소와,

상기 화소에 영상 신호를 공급하는 구동 회로와,

상기 액정 패널에 영상 신호를 공급하는 영상 신호 제어 회로를 구비하고,

상기 영상 신호 제어 회로로부터 상기 구동 회로에 복수의 영상 신호선이 전기적으로 접속되어, 상기 구동 회로에 상기 영상 신호선을 통해 아날로그 신호를 입력하고, 상기 영상 신호선마다 영상 신호를 출력하는 출력 회로가 형성되고,

상기 영상 신호 제어 회로는 1개의 디지털 신호를 복수의 디지털 신호로 분할하는 분할 회로와, 디지털 신호를 아날로그 신호로 변환하는 DA 변환 회로를 구비하고, 상기 DA 변환 회로로부터 출력되는 아날로그 신호를 상기 출력 회로로부터 출력하고, 상기 영상 신호선마다 형성된 참조표에 의해, 상기 출력 회로간의 출력 변동을 보정하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 3.

제2항에 있어서,

상기 제1 기판은 실리콘 기판인 것을 특징으로 하는 액정 표시 장치.

### 청구항 4.

제2항에 있어서,

표준 참조표를 구비하고, 상기 출력 회로의 변동 보정을 상기 표준 참조표의 값을 변경함으로써 상기 참조표를 작성하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 5.

제2항에 있어서,

상기 영상 신호선마다 형성된 복수의 참조표를 1칩으로 구성하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 6.

제2항에 있어서,

상기 참조표에 의해 콘트라스트 또는 휘도를 조정하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 7.

제2항에 있어서,

상기 참조표에 저장되는 데이터를 외부로부터 송신된 데이터를 이용하여, 마이크로 컴퓨터로 연산하여 참조표에 설정하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 8.

제2항에 있어서,

복수개의 참조표를 갖고, 영상 신호의 종류에 따라 참조표를 구분하여 사용하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 9.

제2항에 있어서,

복수개의 참조표를 갖고, 시분할적으로 사용할 참조표를 선택하여 의사적으로 계조수를 늘리는 것을 특징으로 하는 액정 표시 장치.

### 청구항 10.

액정 표시 장치에 있어서,

액정 패널과,

상기 액정 패널을 형성하는 제1 기판 및 제2 기판과,

상기 제1 기판과 제2 기판 사이에 삽입된 액정 조성물과,

상기 제1 기판에 형성된 복수의 화소와,

상기 화소에 대향하여 형성된 기준 전극과,

상기 화소에 영상 신호를 공급하는 구동 회로와,

상기 화소에 접속된 화소 용량과,

상기 화소 용량에 화소 전위 제어 신호를 공급하는 화소 전위 제어 신호선과,

상기 액정 패널에 영상 신호를 공급하는 영상 신호 제어 회로와,

상기 영상 신호선 제어 회로로부터 상기 구동 회로에 전기적으로 접속된 복수의 영상 신호선과, 상기 영상 신호선마다 형성된 영상 신호를 출력하는 출력 회로를 구비하고,

상기 영상 신호 제어 회로는 정극성(正極性)용 디지털 신호를 출력하는 제1 참조표와, 부극성(負極性)용 디지털 신호를 출력하는 제2 참조표와, 정극성용 디지털 신호를 입력하여 정극성용 아날로그 신호를 출력하고, 부극성용 디지털 신호를 입력하여 부극성용 아날로그 신호를 출력하는 변환 회로를 구비하고,

상기 출력 회로로부터 상기 영상 신호선에 출력하는 정극성용 아날로그 신호와 부극성용 아날로그 신호는 정극성의 전압이고,

상기 부극성용 아날로그 신호는 영상 신호로서 상기 화소에 입력된 후, 화소 전위 제어 신호에 의해 상기 기준 전극의 전압에 대하여 부극성의 전압이 되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 11.

삭제

### 청구항 12.

삭제

도면

도면1

## 도면2

## 도면3

도면4

## 도면5

도면6

도면7

도면8

도면9

## 도면10

도면11

## 도면12

### 도면13

### 도면14

| 아ドレス | 보정 데이터 |    |    |    |    |    |    |    |    |    |

|------|--------|----|----|----|----|----|----|----|----|----|

|      | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0    |        |    |    |    |    |    |    |    |    |    |

| 1    | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 2    | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 3    | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 4    | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 5    | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|      |        |    |    |    |    |    |    |    |    |    |

| 251  | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 252  | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 253  | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 254  | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 255  | D9     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

도면15

도면16

## 도면17

(a)

(b)

(c)

도면18

## 도면19

(a)

(b)

## 도면20

## 도면21

## 도면22

도면23

도면24

### 도면25

도면26

## 도면27

(a)

(b)

## 도면28

도면29

도면30

도면31

도면32

## 도면33

## 도면34

도면35

### 도면36

### 도면37

도면38

도면39

도면40

도면41

도면42

도면43

도면44

도면45

도면46

도면47

도면48

도면49

도면50

도면51

도면52

|                |                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR100506434B1</a>                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2005-08-11 |

| 申请号            | KR1020020031962                                                                                                                                                                                                                                                                                                                    | 申请日     | 2002-06-07 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA<br>日立器件工程株式会社                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>地伤装置工程可否让这个夏                                                                                                                                                                                                                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>地伤装置工程可否让这个夏                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | MARUOKA YOSHIO<br>마루오까요시오<br>MISONOU TOSHIKI<br>미소노우도시끼<br>MAEDA TOSHIO<br>마에다도시오<br>WATANABE AKIHIRO<br>와타나베아끼히로<br>NAKAGAWA HIDEKI<br>나카가와히데끼                                                                                                                                                                                    |         |            |

| 发明人            | 마루오까요시오<br>미소노우도시끼<br>마에다도시오<br>와타나베아끼히로<br>나카가와히데끼                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/36 H04N5/74 G09G3/20 G09G5/00 G09G3/00 G02F1/133                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G09G2320/0247 G09G3/2011 G09G2320/0285 G09G2320/0233 G09G2320/0673 G09G2340/0435<br>G09G2320/0693 G09G2320/0276 G09G2330/12 G09G2320/0613 G09G3/2092 G09G3/20 G09G2320<br>/0626 G09G3/3614 G09G2352/00 G09G2300/0876 G09G3/001 G09G2310/0232 G09G2320/066<br>G09G5/006 G09G5/005 G09G2320/0209 G09G2320/0606 G09G3/3655 G09G3/3648 |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                                                                                                                                                                                                                                                     |         |            |

| 优先权            | 2001173410 2001-06-08 JP                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | KR1020020093625A                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                          |         |            |

**摘要(译)**

在模拟视频信号被相位扩展和输入的液晶显示装置中，减少了由于电路变化引起的显示质量的劣化。为了校正由多个模拟电路的变型中，通过使片材的分钟的数字信号处理电路内的多个模拟电路执行的模拟电路为在片材上的数据集的变化的校正。11指教方面液晶面板，图像信号线，放大电路，液晶成分