(19)

(12)

(KR)

(A)

(51) 。 Int. Cl. 7

G09G 3/36

(11)

(43)

2002 - 0034836

2002 05 09

(21) 10 - 2001 - 0019825

(22) 2001 04 13

(30) 2000 - 333517 2000 10 31 (JP)

(71) 가 기

가 가 가 가 4 1-1

|      |   |   |   |   |           |   |   |

|------|---|---|---|---|-----------|---|---|

| (72) | 가 | 가 | 가 | 가 | 4 - 1 - 1 | 가 | 가 |

|      | 가 | 가 | 가 | 가 | 4 - 1 - 1 | 가 | 가 |

(74)

1

(54)

|    |     |   |     |

|----|-----|---|-----|

| 1  |     | 1 |     |

| 2  | (a) | 2 | (b) |

| 3  | 1   |   |     |

| 4  |     | 2 |     |

| 5  |     | 3 |     |

| 6  | 5   |   |     |

| 7  | 5   |   |     |

| 8  |     |   |     |

| 9  |     |   |     |

| 10 |     |   |     |

| 11 | 10  |   |     |

10, 10A, 10B, 10X, 10Y :

11 :

12 :

13 :

20 :

21 : PMOS

22 : NMOS

T11

C11

D1 D6 ·

G1 G4 :

VCOM :

B1 B9, B10 B12 :

S1 S9, S10 S12 :

R1 R6 :

PS1 PS3 :

NS1 NS3 :

PB1 PB3 :

NB1 NB3 :

P1 P6, N1 N6 :

T1 T6 :

LT :

VP31, VN31 :

A F, I T, U W :

가

가

8

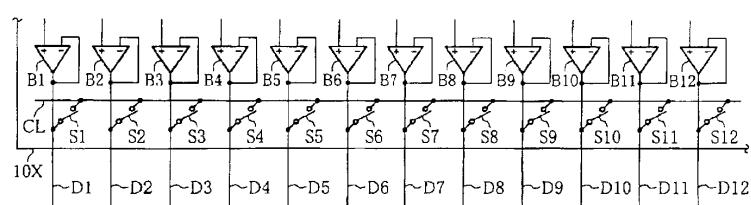

(10X)

(10X)

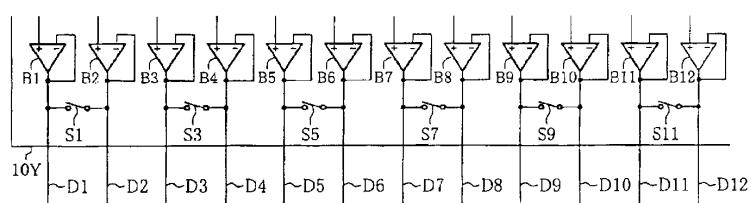

(D1 D12)

(B1 B12)

(follower)

(10X)

1

가 ,

(B1 B12)

가

가

(flicker) 가

,

(B1 B12)

가

,

D12)

(CL)

(S1 S12) 가

(blanking)

(D1

(B1 B12) 가 , (S1 S12)가

, (D1 D12) 가 .

(B1 B12)

, 가 , (10X)

가 .

9 10 - 282940 (10Y)

가 ,

가 ,

가

가 ,

가 ,

가

3 , 2 ,

가

[ 1 ]

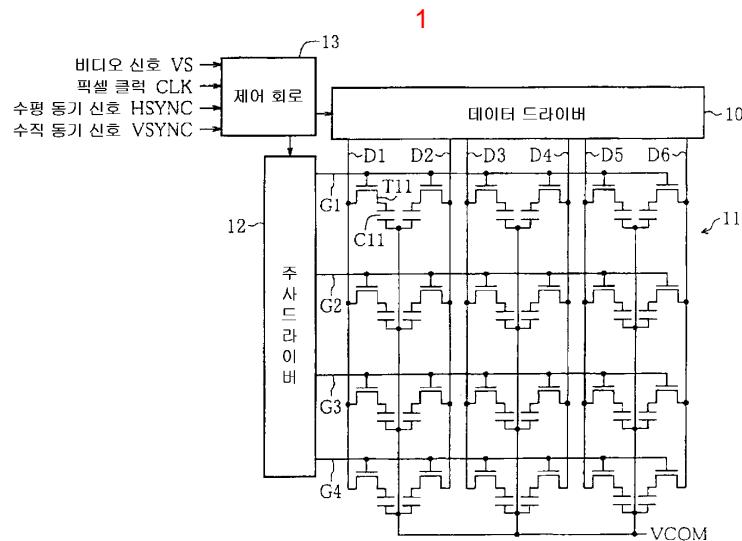

$$1 \quad \quad \quad 1 \\ (11) \quad \quad \quad 4 \quad 6$$

(11) , , , , , , , .

4 [G1 G4:] , , , 1

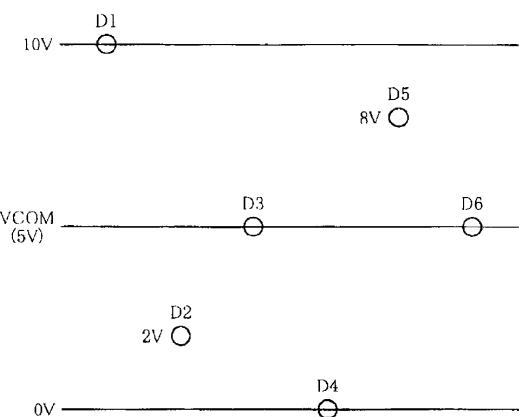

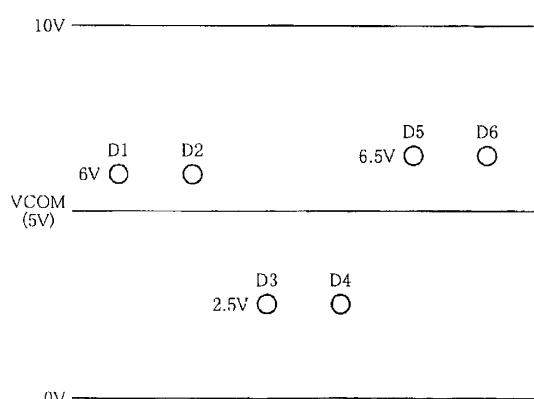

(D1 D6) , , , 6

(G1 G4)

(全)

(VCOM)가 가 . 1 1 (C11)

(D1) (T11)가 , (T11) 가 .

G1) , (C11) (VCOM)가 가 .

$$11) \quad (11) \quad (G1 \quad G4) \quad (D1 \quad D6) \quad (12) \quad (10) \quad . \quad , \quad ($$

(13) (VS), (CLK), (HSYNC) (VSYNC)

, , (10) (12)

가 (12) (10) (G1 G4) . (線順次) (10) , (D1 D6)

(10) 1 . ,

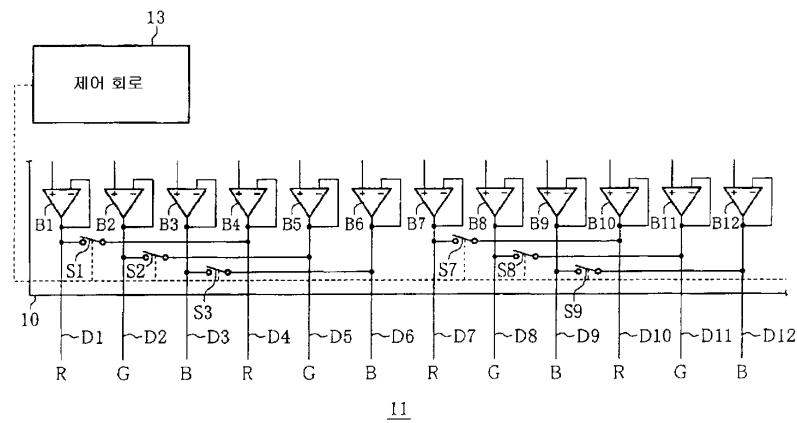

2 (a)      2 (b)      가

$$3 \quad (10) \quad 1024 \times \\ 3 = 3072 \quad , \quad 3 \quad (D1 \quad D12)$$

(11) (D1 D12) (10)

$(B1 \quad B12)$  . (R), (G) (b) 3

|      |       |       |       |   |   |

|------|-------|-------|-------|---|---|

| R    | (D1)  | (D4)  | (S1)가 | , |   |

| R    | (D4)  | (D7)  | 가     | , |   |

| R    | (D7)  | (D10) | (S7)가 | . | 가 |

| G    | (D2)  | (D5)  | (S2)가 | , | G |

|      | (D8)  | (D11) | (S8)가 | , | B |

|      | (D3)  | (D6)  | (S3)가 | , | B |

| (D9) | (D12) | (S9)가 | .     |   |   |

$$(13) \quad , \quad (B1 \quad B12) \\ (S1 \quad S3, S7 \quad S9) \quad .$$

[ 2 ]

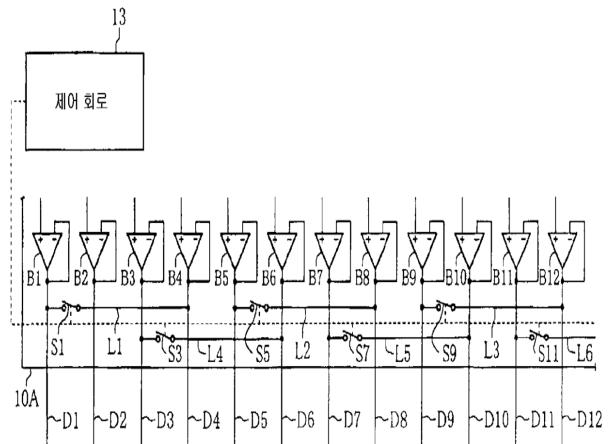

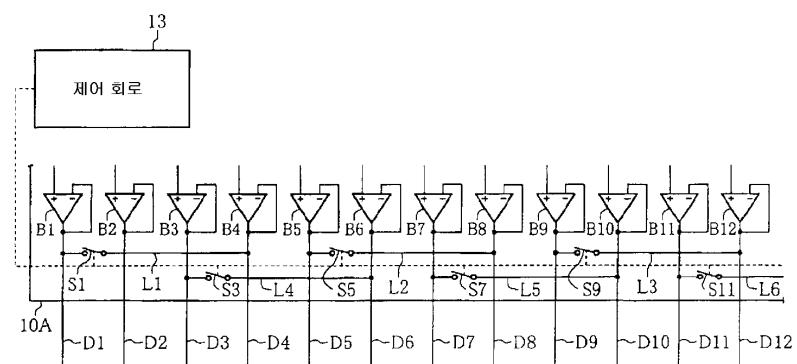

4                    2                    (10A) .

,                    1                    (L1 L3)            2                    (L4 L6)

, 1 2 (S1 S5) (D8 D9), (D4 D5) (S3 S7), (S5 S

, 9) (D6 D7), (S7 S11) (D10 D11)

(S1, S3, S5, S7, S9     S11)                  (13)                  1                  가

,                  1                  ,                  ,                  1

가                  가                  ,                  ,                  가

(10A)                  3                  ,                  (D1    D12)

[ 3 ]

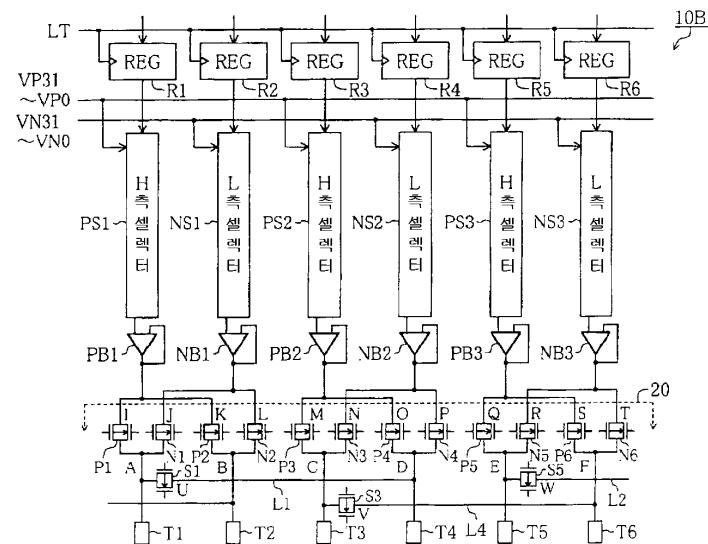

5                    3                    (10B)

(正極性) (PB1 PB3) [VCOM: , 5 V] (H )

, (負極性) (NB1 NB3) (VCOM) (L )

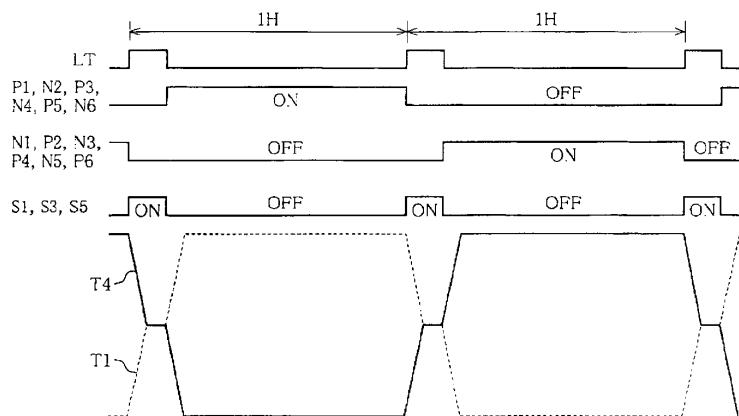

T1 T2 (PB1) (NB1) (1H) ( )

(P1 P2)가 , (PB1) (T1 T2)

(N1, N2)가 . (NB1) (T1 T2)

(P1, P2, N1 N2)가 1 . (T1 T6)

4 가 , (S1, S4 S5)가 .

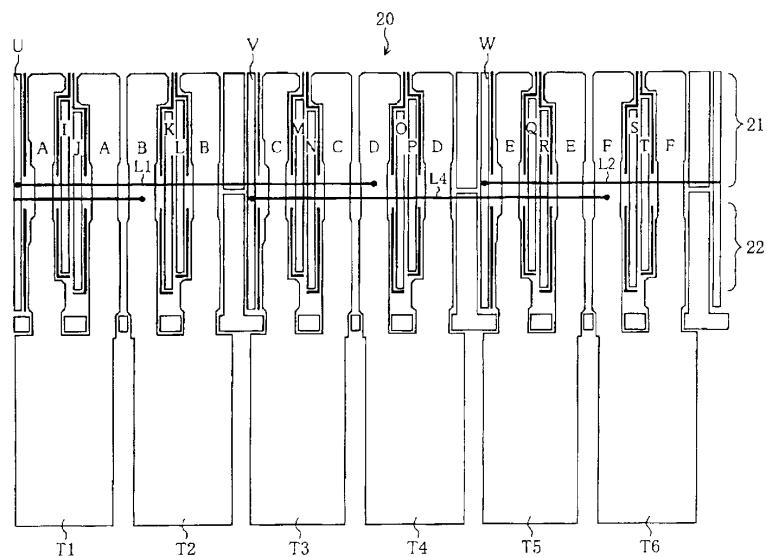

6 5 (20) . 6 (A F, I T U W)

5

5 PMOS NMOS 가 , PMOS

(21) , NMOS (22)

, (P1) PMOS (A) (I)

(N1) PMOS (A) (J)

(P1 N1) NMOS NMOS (22)

(S1) PMOS (A) (U)

(S3) PMOS (C) (V)

(S5) PMOS (E) (W)

(S1, S3 S5) NMOS NMOS (22)

(U) 1 (L1) (D) , (V) 2 (L4) (F)

(W) 1 (L5) .

L5) PMOS (21) NMOS (22) , 1 2 (L1, L4)

가 , (20) 1 (T1)

T6)

5 가 , (PS1 PS3) (R1, R3) (R5) ( )

(VP31 VP0) (R2 R4) (PB1 PB3) 가 ,

(NS1 NS3) (NB1 NB3) (R6) (VN31)

VN0) , (R1 R6)

(LT)가 .

7 5

(LT) 1H , (R1 R6) 가 .

(LT) , (P1 P6 N1 N6)가 , (S1, S3 S5)가 .

, 가 . ,

(57)

1.

, 가

,

; 가

2.

1 ,

3.

2 , 1 2

4.

3 , 1 2 1 2

5.

4 ,

6.

5 , 3 NMOS 4 PMOS

가

7.

6 , 1 2 3 4

8.

;

;

2

(a)

|   |   |   |   |   |   |

|---|---|---|---|---|---|

| + | - | + | - | + | - |

| - | + | - | + | - | + |

| + | - | + | - | + | - |

| - | + | - | + | - | + |

(b)

|   |   |   |   |   |   |

|---|---|---|---|---|---|

| - | + | - | + | - | + |

| + | - | + | - | + | - |

| - | + | - | + | - | + |

| + | - | + | - | + | - |

3

11

4

11

5

6

7

8

9

10

11

|                |                                                                           |         |            |

|----------------|---------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示器的数据驱动器                                                             |         |            |

| 公开(公告)号        | <a href="#">KR1020020034836A</a>                                          | 公开(公告)日 | 2002-05-09 |

| 申请号            | KR1020010019825                                                           | 申请日     | 2001-04-13 |

| [标]申请(专利权)人(译) | 富士通株式会社                                                                   |         |            |

| 申请(专利权)人(译)    | 富士sikki有限公司                                                               |         |            |

| 当前申请(专利权)人(译)  | 富士sikki有限公司                                                               |         |            |

| [标]发明人         | UDO SHINYA<br>우도신야<br>KOKUBUN MASATOSHI<br>고쿠분마사토시                        |         |            |

| 发明人            | 우도신야<br>고쿠분마사토시                                                           |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                               |         |            |

| CPC分类号         | G09G3/3607 G09G3/3685 G09G3/3614 G09G2310/0297 G09G2330/023 G09G2310/0248 |         |            |

| 代理人(译)         | 金泰HONG<br>SHIN JUNG KUN                                                   |         |            |

| 优先权            | 2000333517 2000-10-31 JP                                                  |         |            |

| 其他公开文献         | KR100734337B1                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                 |         |            |

## 摘要(译)

本发明旨在抑制电路面积的增加。电压缓冲放大器B1至B12的输出端分别连接到点反转驱动型数据驱动器10A中的液晶显示板的数据总线D1至D12，短路开关元件S1，S3，S5，S7，S9和S11在这些线之间一个接一个地连接，并且第一行的布线和第二行的布线交替地布置。这些短路开关元件形成在一条数据线的一侧。当电压缓冲放大器的输出处于高阻抗状态时，控制电路13接通短路开关元件。 4