(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년07월25일

(11) 등록번호 10-1423197

(24) 등록일자 2014년07월18일

(51) 국제특허분류(Int. Cl.)

G09G 3/36 (2006.01) G02F 1/133 (2006.01)

G09G 3/20 (2006.01)

(21) 출원번호 10-2006-0125336

(22) 출원일자 2006년12월11일

심사청구일자 2011년11월21일

(65) 공개번호 10-2008-0053600

(43) 공개일자 2008년06월16일

(56) 선행기술조사문헌

US20060001630 A1

KR1020060044817 A

KR1020050002428 A

KR1020040060708 A

전체 청구항 수 : 총 28 항

(73) 특허권자

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성2로 95 (농서동)

(72) 발명자

이재한

충청남도 태안군 소원면 대소산길 377-23

손선규

경기도 수원시 영통구 영통로 498, 황골마을1단지

아파트 135동 204호 (영통동)

(뒷면에 계속)

(74) 대리인

오세준, 권혁수, 송윤호

심사관 : 추장희

(54) 발명의 명칭 데이터 구동 장치 및 그것을 이용하는 액정 표시 장치

**(57) 요약**

본 발명은 차지 쉐어링 기능을 수행하는 액정 표시 장치에 관한 것이다.

본 발명의 데이터 구동 장치는 제1 및 제2 출력 단속 스위치, 전하 공유 라인 및 제1 및 제2 전하 공유 스위치를 포함한다. 제1 출력 단속 스위치는 정극성 계조 표시 전압을 제공하는 제1 앤프와 정극성 계조 표시 전압이 제공되는 제1 데이터 라인의 연결을 제어 신호에 응답하여 단속한다. 제2 출력 단속 스위치는 부극성 계조 표시 전압을 제공하는 제2 앤프와 부극성 계조 표시 전압이 제공되는 제2 데이터 라인의 연결을 제어 신호에 응답하여 단속한다. 제1 전하 공유 스위치는 제1 데이터 라인과 전하 공유 라인의 연결을 제어 신호에 응답하여 단속한다. 제2 전하 공유 스위치는 제2 데이터 라인과 전하 공유 라인의 연결을 제어 신호에 응답하여 단속한다.

**대표 도**

(72) 발명자

**임명빈**

서울특별시 서대문구 서소문로 27, 1714호 (

충정로3가, 충정리시온)

**황인용**

경기도 수원시 영통구 영통로102번길 19, 201호 (

망포동, 미림빌)

**김옥진**

충청남도 천안시 서북구 봉서산샛길 65, 주공9단지

409동 204호 (쌍용동)

## 특허청구의 범위

### 청구항 1

정극성 계조 표시 전압을 제공하는 제1 앰프와 상기 정극성 계조 표시 전압이 제공되는 제1 데이터 라인의 전기적 연결을 제어 신호에 응답하여 단속하는 제1 출력 단속 스위치;

부극성 계조 표시 전압을 제공하는 제2 앰프와 상기 부극성 계조 표시 전압이 제공되는 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 출력 단속 스위치;

상기 제1 데이터 라인과 제2 데이터 라인의 전하를 공유하기 위한 전하 공유 라인;

상기 제1 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제1 전하 공유 스위치; 및

상기 제2 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 전하 공유 스위치;

를 포함하는 데이터 구동 장치.

### 청구항 2

제 1 항에 있어서, 상기 제어 신호는,

상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 데이터 라인에 제공하고, 상기 제2 앰프가 정극성 계조 표시 전압을 제2 데이터 라인에 제공하도록 하는 로드 신호인

데이터 구동 장치.

### 청구항 3

제 2 항에 있어서,

상기 제1 및 제2 출력 단속 스위치는 상기 제어 신호의 인에이블 구간에서 개방되고,

상기 제1 및 제2 전하 공유 스위치는 상기 제어 신호의 인에이블 구간에서 단락되어, 상기 전하 공유 라인을 통하여 상기 제1 데이터 라인과 제2 데이터 라인의 전하가 공유되는

데이터 구동 장치.

### 청구항 4

제 3 항에 있어서, 상기 제1 및 제2 출력 단속 스위치는,

케이트에 상기 제어 신호가 제공되는 피모스 트랜지스터인

데이터 구동 장치.

### 청구항 5

제 4 항에 있어서, 상기 제1 및 제2 전하 공유 스위치는,

케이트에 상기 제어 신호가 제공되는 엔모스 트랜지스터인

데이터 구동 장치.

#### 청구항 6

제 3 항에 있어서, 상기 제1 및 제2 출력 단속 스위치는,

제1 게이트에 상기 제어 신호가 제공되고, 제2 게이트에 상기 제어 신호의 위상이 반전된 위상을 가지는 제어바 신호가 제공되는 트랜스퍼 게이트인

데이터 구동 장치.

#### 청구항 7

제 6 항에 있어서, 상기 제1 및 제2 전하 공유 스위치는,

제1 게이트에 상기 제어바 신호가 제공되고, 제2 게이트에 상기 제어 신호가 제공되는 트랜스퍼 게이트인

데이터 구동 장치.

#### 청구항 8

정극성 계조 표시 전압을 제공하는 제1 앰프와 상기 정극성 계조 표시 전압이 제공되는 제1 데이터 라인의 연결을 제어 신호에 응답하여 단속하는 제1 출력 단속 스위치;

부극성 계조 표시 전압을 제공하는 제2 앰프와 상기 부극성 계조 표시 전압이 제공되는 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 출력 단속 스위치; 및

상기 제1 데이터 라인과 상기 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 전하 공유 스위치;

를 포함하는 데이터 구동 장치.

#### 청구항 9

제 8 항에 있어서, 상기 제어 신호는,

상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 데이터 라인에 제공하고, 상기 제2 앰프가 정극성 계조 표시 전압을 제2 데이터 라인에 제공하도록 하는 로드 신호인

데이터 구동 장치.

#### 청구항 10

제 9 항에 있어서, 상기 제1 및 제2 출력 단속 스위치는,

상기 제어 신호의 인에이블 구간에서 개방되고, 상기 전하 공유 스위치는 상기 제어 신호의 인에이블 구간에서 단락되어, 상기 제1 데이터 라인과 제2 데이터 라인의 전하가 공유되는

데이터 구동 장치.

#### 청구항 11

제 10 항에 있어서, 상기 제1 및 제2 출력 단속 스위치는,

게이트에 상기 제어 신호가 제공되는 페모스 트랜지스터인

데이터 구동 장치.

### 청구항 12

제 11 항에 있어서, 상기 전하 공유 스위치는,

게이트에 상기 제어 신호가 제공되는 엔모스 트랜지스터인

데이터 구동 장치.

### 청구항 13

제 9 항에 있어서, 상기 제1 및 제2 출력 단속 스위치는,

제1 게이트에 상기 제어 신호가 제공되고, 제2 게이트에 상기 제어 신호의 위상이 반전된 위상을 가지는 제어바

신호가 제공되는 트랜스퍼 게이트인

데이터 구동 장치.

### 청구항 14

제 13 항에 있어서, 상기 전하 공유 스위치는,

제1 게이트에 상기 제어바 신호가 제공되고, 제2 게이트에 상기 제어 신호가 제공되는 트랜스퍼 게이트인

데이터 구동 장치.

### 청구항 15

계조 표시 전압을 제공하는 복수의 앰프와 상기 앰프에 대응하며 상기 계조 표시 전압이 제공되는 복수의 데이터 라인의 전기적 연결을 각각 단속하는 출력 단속 스위치;

상기 복수의 데이터 라인의 전하를 공유하기 위한 제1 전하 공유 라인;

복수의 앰프 중 첫 번째와 마지막 번째 앰프에 연결되는 데이터 라인 간의 전하 공유하기 위한 제2 전하 공유 라인; 및

상기 복수의 데이터 라인과 상기 제1 전하 공유 라인의 전기적 연결과, 복수의 앰프 중 첫 번째 앰프에 연결되는 데이터 라인 및 마지막 번째 앰프에 연결되는 데이터 라인과 상기 제2 전하 공유라인의 전기적 연결을 제어 신호에 응답하여 각각 단속하는 전하 공유 스위치;

를 포함하는 데이터 구동 장치.

### 청구항 16

제 15 항에 있어서,

상기 복수의 앰프는 정극성 계조 표시 전압을 제공하는 제1 앰프와 제1 앰프에 대응하며 부극성 계조 표시 전압을 제공하는 제2 앰프를 포함하며,

첫 번째 앰프와 마지막 번째 앰프 중 어느 하나의 앰프는 제1 앰프로 동작하고, 다른 하나의 앰프는 제2 앰프로 동작하는

데이터 구동 장치.

**청구항 17**

제 16 항에 있어서, 상기 제어 신호는,

상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 앰프에 대응하는 데이터 라인에 제공하고, 상기 제2 앰프가 정극성 계조 표시 전압을 상기 제2 앰프에 대응하는 데이터 라인에 제공하도록 하는 로드 신호인 데이터 구동 장치.

**청구항 18**

제 17 항에 있어서,

상기 출력 단속 스위치는 상기 제어 신호의 인에이블 구간에서 개방되고,

상기 전하 공유 스위치는 상기 제어 신호의 인에이블 구간에서 단락되어, 상기 전하 공유 라인을 통하여 상기 복수의 데이터 라인의 전하가 공유되는

데이터 구동 장치.

**청구항 19**

케이트 구동 신호에 응답하여 제공되는 계조 표시 전압에 의해 데이터를 표시하는 액정 패널; 감마 전압을 기준으로 상기 계조 표시 전압을 생성하고, 데이터 제어 신호에 응답하여 상기 계조 전압을 상기 액정 패널에 제공하는 데이터 구동부; 케이트 제어 신호에 응답하여 상기 케이트 구동 신호를 상기 액정 패널에 제공하는 케이트 구동부; 및 상기 데이터 제어 신호와 상기 케이트 제어 신호를 제공하는 타이밍 컨트롤러를 포함하며,

상기 데이터 구동부는 접적화된 복수의 데이터 구동 회로를 포함하며, 상기 데이터 구동 회로는 정극성 계조 표시 전압을 제공하는 제1 앰프, 제1 앰프에 대응하여 부극성 계조 표시 전압을 제공하는 제2 앰프, 및 상기 제1 앰프에 연결되는 제1 데이터 라인과 상기 제2 앰프에 연결되는 제2 데이터 라인을 상기 정극성 계조 표시 전압과 상기 부극성 계조 표시 전압이 제공되기 전에 전기적으로 연결하여 전하를 공유하시키는 스위치부를 포함하는

액정 표시 장치.

**청구항 20**

제 19 항에 있어서, 상기 데이터 제어 신호는,

상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 데이터 라인에 제공하고, 상기 제2 앰프가 정극성 계조 표시 전압을 제2 데이터 라인에 제공하도록 하는 로드 신호를 포함하는

액정 표시 장치.

**청구항 21**

제 20 항에 있어서, 상기 스위치부는,

상기 제1 앰프와 상기 제1 데이터 라인의 연결을 상기 로드 신호에 응답하여 단속하는 제1 출력 단속 스위치;

상기 제2 앰프와 상기 제2 데이터 라인의 전기적 연결을 상기 로드 신호에 응답하여 단속하는 제2 출력 단속 스위치;

상기 제1 데이터 라인과 제2 데이터 라인의 전하를 공유하기 위한 전하 공유 라인;

상기 제1 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 로드 신호에 응답하여 단속하는 제 1 전하

공유 스위치; 및

상기 제2 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 로드 신호에 응답하여 단속하는 제2 전하 공유 스위치;를 포함하는

액정 표시 장치.

## 청구항 22

제 21 항에 있어서,

상기 제1 및 제2 출력 단속 스위치는 상기 로드 신호의 인에이블 구간에서 개방되고,

상기 제1 및 제2 전하 공유 스위치는 상기 로드 신호의 인에이블 구간에서 단락되어, 상기 전하 공유 라인을 통하여 상기 제1 데이터 라인과 제2 데이터 라인의 전하가 공유되는

액정 표시 장치.

## 청구항 23

제 20 항에 있어서, 상기 스위치부는

상기 제1 앰프와 상기 제1 데이터 라인의 연결을 상기 로드 신호에 응답하여 단속하는 제1 출력 단속 스위치;

상기 제2 앰프와 상기 제2 데이터 라인의 전기적 연결을 상기 로드 신호에 응답하여 단속하는 제2 출력 단속 스위치; 및

상기 제1 데이터 라인과 상기 제2 데이터 라인의 전기적 연결을 상기 로드 신호에 응답하여 단속하는 전하 공유 스위치를 포함하는

액정 표시 장치.

## 청구항 24

제 23 항에 있어서,

상기 제1 및 제2 출력 단속 스위치는 상기 로드 신호의 인에이블 구간에서 개방되고,

상기 전하 공유 스위치는 상기 로드 신호의 인에이블 구간에서 단락되어, 상기 제1 데이터 라인과 제2 데이터 라인의 전하가 공유되는

액정 표시 장치.

## 청구항 25

게이트 구동 신호에 응답하여 제공되는 계조 표시 전압에 의해 데이터를 표시하는 액정 패널; 감마 전압을 기준으로 상기 계조 표시 전압을 생성하고, 데이터 제어 신호에 응답하여 상기 계조 전압을 상기 액정 패널에 제공하는 집적화된 복수의 데이터 구동 회로를 포함하는 데이터 구동부; 게이트 제어 신호에 응답하여 상기 게이트 구동 신호를 상기 액정 패널에 제공하는 게이트 구동부; 및 상기 데이터 제어 신호와 상기 게이트 제어 신호를 제공하는 타이밍 컨트롤러를 포함하며,

상기 데이터 구동 회로는 계조 표시 전압을 제공하는 복수의 앰프와 상기 앰프에 대응하여 상기 계조 표시 전압이 제공되는 복수의 데이터 라인의 전기적 연결을 각각 단속하는 출력 단속 스위치; 상기 복수의 데이터 라인의 전하를 공유하기 위한 제1 전하 공유 라인; 복수의 앰프 중 첫 번째와 마지막 번째 앰프에 연결되는 데이터 라인 간의 전하 공유하기 위한 제2 전하 공유 라인; 및 상기 복수의 데이터 라인과 상기 제1 전하 공유 라인의 전기적 연결과, 복수의 앰프 중 첫 번째 앰프에 연결되는 데이터 라인 및 마지막 번째 앰프에 연결되는 데이터 라

인과 상기 제2 전하 공유라인의 전기적 연결을 제어 신호에 응답하여 각각 단속하는 전하 공유 스위치;를 포함하는

액정 표시 장치.

### 청구항 26

제 25 항에 있어서,

상기 복수의 앰프는 정극성 계조 표시 전압을 제공하는 제1 앰프와 제1 앰프에 대응하며 부극성 계조 표시 전압을 제공하는 제2 앰프를 포함하며,

첫 번째 앰프와 마지막 번째 앰프 중 어느 하나의 앰프는 제1 앰프로 동작하고, 다른 하나의 앰프는 제2 앰프로 동작하는

액정 표시 장치.

### 청구항 27

제 26 항에 있어서, 상기 제어 신호는,

상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 앰프에 대응하는 데이터 라인에 제공하고, 상기 제2 앰프가 정극성 계조 표시 전압을 상기 제2 앰프에 대응하는 데이터 라인에 제공하도록 하는 로드 신호인

액정 표시 장치.

### 청구항 28

제 27 항에 있어서,

상기 출력 단속 스위치는 상기 제어 신호의 인에이블 구간에서 개방되고,

상기 전하 공유 스위치는 상기 제어 신호의 인에이블 구간에서 단락되어, 상기 전하 공유 라인을 통하여 상기 복수의 데이터 라인의 전하가 공유되는

액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- [0015] 본 발명은 액정 표시 장치에 관한 것으로서, 특히 차지 쉐어링 기능을 수행하는 액정 표시 장치에 관한 것이다.

- [0016] 일반적으로 액정 표시 장치는 전계 생성 전극이 각각 형성된 박막 트랜지스터 기판과 컬러 필터 기판을 전극이 형성된 면이 마주 대하도록 배치하고 두 기판 사이에 액정을 주입한 후, 전극에 전압을 인가하여 생성되는 전기장에 의해 액정을 움직이게 함으로써, 이에 따라 달라지는 빛의 투과율에 의해 화상을 표현하는 장치이다.

- [0017] 이러한 액정 표시 장치는, 데이터 라인과 게이트 라인의 교차 영역에 형성된 복수의 화소를 포함하는 액정 패널, 데이터 라인에 데이터 신호를 인가하는 데이터 구동부, 게이트 라인에 게이트 구동 신호를 인가하는 게이트 구동부, 데이터 구동부와 게이트 구동부를 제어하는 타이밍 컨트롤러 및 액정 패널의 구동 전압을 공급하는 전원 공급부를 포함한다.

- [0018] 액정 표시 장치는, 액정의 분극 현상을 방지하고 성능을 향상시키기 위하여 인접한 화소에 서로 다른 방향의 전계(Electric Field)를 인가하는 교류 신호 인가 방식으로 구동한다.

- [0019] 화소에 교류 신호를 인가하는 방식으로는 상호 인접하는 도트(Dot)마다 극성을 반전시켜 구동하는 도트 반전

(Dot Inversion) 방식, 이웃하는 게이트 라인씩 극성을 반전시켜 구동하는 라인 반전(Line Inversion) 방식, 이웃하는 데이터 라인씩 극성을 반전시켜 구동하는 컬럼 반전(Column Inversion) 방식 및 동일한 극성의 프레임(Frame) 전체를 프레임별로 반전시켜 구동하는 프레임(Frame Inversion) 방식 등이 있다.

- [0020] 한편 종래 액정 표시 장치는 데이터 라인에 인가되는 교류 전압 특성을 이용하여, 데이터에 상응하는 계조 표시 전압을 출력하기 전에 데이터 구동부에 연결된 데이터 라인을 단락시켜 각 데이터 라인의 전하를 공유하는 차지 쉐어링(Charge Sharing) 기능을 수행한다.

- [0021] 그런데 종래 액정 표시 장치는 차지 쉐어링을 위하여 데이터 구동부에 연결된 모든 데이터 라인을 단락(Short) 시켜 각 데이터 라인의 전하를 공유하는데, 처음과 마지막에 위치하는 데이터 라인은 가운데에 위치하는 데이터 라인에 비하여 차지 쉐어 레벨의 차이가 발생한다. 처음과 마지막에 위치하는 데이터 라인은 가운데 위치하는 데이터 라인과 달리 인접한 하나의 데이터 라인과 차지 쉐어링을 수행하기 때문이다.

- [0022] 차지 쉐어 레벨의 차이는 화소의 충전량의 차이를 발생시켜며, 데이터 구동부를 복수의 데이터 구동 접적 회로로 구현하여 액정 패널을 구동하는 경우, 세로줄 불량으로 시인되는 문제점을 발생시킨다.

- [0023]

### 발명이 이루고자 하는 기술적 과제

- [0024] 따라서, 본 발명은 종래의 문제점을 해결하기 위하여 안출된 것으로, 데이터 구동 접적 회로의 첫 번째 채널과 마지막 채널에 연결되는 데이터 라인을 균일하게 차지 쉐어하는 액정 표시 장치를 제공함에 그 목적이 있다.

### 발명의 구성 및 작용

- [0025] 상기 목적을 달성하기 위하여 본 발명의 데이터 구동 장치는, 정극성 계조 표시 전압을 제공하는 제1 앰프와 상기 정극성 계조 표시 전압이 제공되는 제1 데이터 라인의 전기적 연결을 제어 신호에 응답하여 단속하는 제1 출력 단속 스위치; 부극성 계조 표시 전압을 제공하는 제2 앰프와 상기 부극성 계조 표시 전압이 제공되는 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 출력 단속 스위치; 상기 제1 데이터 라인과 제2 데이터 라인의 전하를 공유하기 위한 전하 공유 라인; 상기 제1 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제1 전하 공유 스위치; 및 상기 제2 데이터 라인과 상기 전하 공유 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 전하 공유 스위치;를 포함한다.

- [0026] 여기서, 상기 제어 신호는 상기 제1 앰프가 상기 정극성 계조 표시 전압을 상기 제1 데이터 라인에 제공하고, 상기 제2 앰프가 부극성 계조 표시 전압을 제2 데이터 라인에 제공하도록 하는 것이 바람직하다.

- [0027] 또한 상기 제1 및 제2 출력 단속 스위치는 상기 제어 신호의 인에이블 구간에서 개방되고, 상기 제1 및 제2 전하 공유 스위치는 상기 제어 신호의 인에이블 구간에서 단락되어, 상기 전하 공유 라인을 통하여 상기 제1 데이터 라인과 제2 데이터 라인의 전하가 공유되는 것이 바람직하다.

- [0028] 또한 상기 제1 및 제2 출력 단속 스위치는 게이트에 상기 제어 신호가 제공되는 피모스 트랜지스터인 것이 바람직하다.

- [0029] 또한 상기 제1 및 제2 전하 공유 스위치는 게이트에 상기 제어 신호가 제공되는 엔모스 트랜지스터인 것이 바람직하다.

- [0030] 또한 상기 제1 및 제2 출력 단속 스위치는 제1 게이트에 상기 제어 신호가 제공되고, 제2 게이트에 상기 제어 신호의 위상이 반전된 위상을 가지는 제어바 신호가 제공되는 트랜스퍼 게이트인 것이 바람직하다.

- [0031] 또한 상기 제1 및 제2 전하 공유 스위치는 제1 게이트에 상기 제어바 신호가 제공되고, 제2 게이트에 상기 제어 신호가 제공되는 트랜스퍼 게이트인 것이 바람직하다.

- [0032] 본 발명의 데이터 구동 장치는 정극성 계조 표시 전압을 제공하는 제1 앰프와 상기 정극성 계조 표시 전압이 제공되는 제1 데이터 라인의 연결을 제어 신호에 응답하여 단속하는 제1 출력 단속 스위치; 부극성 계조 표시 전압을 제공하는 제2 앰프와 상기 부극성 계조 표시 전압이 제공되는 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 제2 출력 단속 스위치; 상기 제1 데이터 라인과 상기 제2 데이터 라인의 전기적 연결을 상기 제어 신호에 응답하여 단속하는 전하 공유 스위치를 포함한다.

- [0033] 본 발명의 데이터 구동 장치는 계조 표시 전압을 제공하는 복수의 앰프와 상기 앰프에 대응하여 상기 계조 표시 전압이 제공되는 복수의 데이터 라인의 전기적 연결을 각각 단속하는 출력 단속 스위치; 상기 복수의 데이터 라인의 전하를 공유하기 위한 제1 전하 공유 라인; 복수의 앰프 중 첫 번째와 마지막 번째 앰프에 연결되는 데이터 라인 간의 전하 공유하기 위한 제2 전하 공유 라인; 및 상기 복수의 데이터 라인과 상기 제1 전하 공유 라인의 전기적 연결과, 복수의 앰프 중 첫 번째 앰프에 연결되는 데이터 라인 및 마지막 번째 앰프에 연결되는 데이터 라인과 상기 제2 전하 공유라인의 전기적 연결을 상기 제어 신호에 응답하여 각각 단속하는 전하 공유 스위치;를 포함한다.

- [0034] 여기서 상기 복수의 앰프는 정극성 계조 표시 전압을 제공하는 제1 앰프와 제1 앰프에 대응하여 부극성 계조 표시 전압을 제공하는 제2 앰프를 포함하며, 첫 번째 앰프와 마지막 번째 앰프 중 어느 하나의 앰프는 제1 앰프로 동작하고, 다른 하나의 앰프는 제2 앰프로 동작하는 것이 바람직하다.

- [0035] 본 발명의 액정 표시 장치는 게이트 구동 신호에 응답하여 제공되는 계조 표시 전압에 의해 데이터를 표시하는 액정 패널; 감마 전압을 기준으로 상기 계조 표시 전압을 생성하고, 데이터 제어 신호에 응답하여 상기 계조 전압을 상기 액정 패널에 제공하는 데이터 구동부; 게이트 제어 신호에 응답하여 상기 게이트 구동 신호를 상기 액정 패널에 제공하는 게이트 구동부; 및 상기 데이터 제어 신호와 상기 게이트 제어 신호를 제공하는 타이밍 컨트롤러를 포함하며, 상기 데이터 구동부는 집적화된 복수의 데이터 구동 회로를 포함하며, 상기 데이터 구동 회로는 정극성 계조 표시 전압을 제공하는 제1 앰프, 제1 앰프에 대응하여 부극성 계조 표시 전압을 제공하는 제2 앰프, 및 상기 제1 앰프에 연결되는 제1 데이터 라인과 상기 제2 앰프에 연결되는 제2 데이터 라인을 상기 정극성 계조 표시 전압과 상기 부극성 계조 표시 전압이 제공되기 전에 전기적으로 연결하여 전하를 공유하시키는 스위치부를 포함한다.

- [0036] 본 발명의 액정 표시 장치는 게이트 구동 신호에 응답하여 제공되는 계조 표시 전압에 의해 데이터를 표시하는 액정 패널; 감마 전압을 기준으로 상기 계조 표시 전압을 생성하고, 데이터 제어 신호에 응답하여 상기 계조 전압을 상기 액정 패널에 제공하는 집적화된 복수의 데이터 구동 회로를 포함하는 데이터 구동부; 게이트 제어 신호에 응답하여 상기 게이트 구동 신호를 상기 액정 패널에 제공하는 게이트 구동부; 및 상기 데이터 제어 신호와 상기 게이트 제어 신호를 제공하는 타이밍 컨트롤러를 포함하며, 상기 데이터 구동 회로는 계조 표시 전압을 제공하는 복수의 앰프와 상기 앰프에 대응하여 상기 계조 표시 전압이 제공되는 복수의 데이터 라인의 전기적 연결을 각각 단속하는 출력 단속 스위치; 상기 복수의 데이터 라인의 전하를 공유하기 위한 제1 전하 공유 라인; 복수의 앰프 중 첫 번째와 마지막 번째 앰프에 연결되는 데이터 라인 간의 전하 공유하기 위한 제2 전하 공유 라인 상기 복수의 데이터 라인과 상기 제1 전하 공유 라인의 전기적 연결과, 복수의 앰프 중 첫 번째 앰프에 연결되는 데이터 라인 및 마지막 번째 앰프에 연결되는 데이터 라인과 상기 제2 전하 공유라인의 전기적 연결을 상기 제어 신호에 응답하여 각각 단속하는 전하 공유 스위치;를 포함한다.

- [0037] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 일 실시예에 대해 상세히 설명한다.

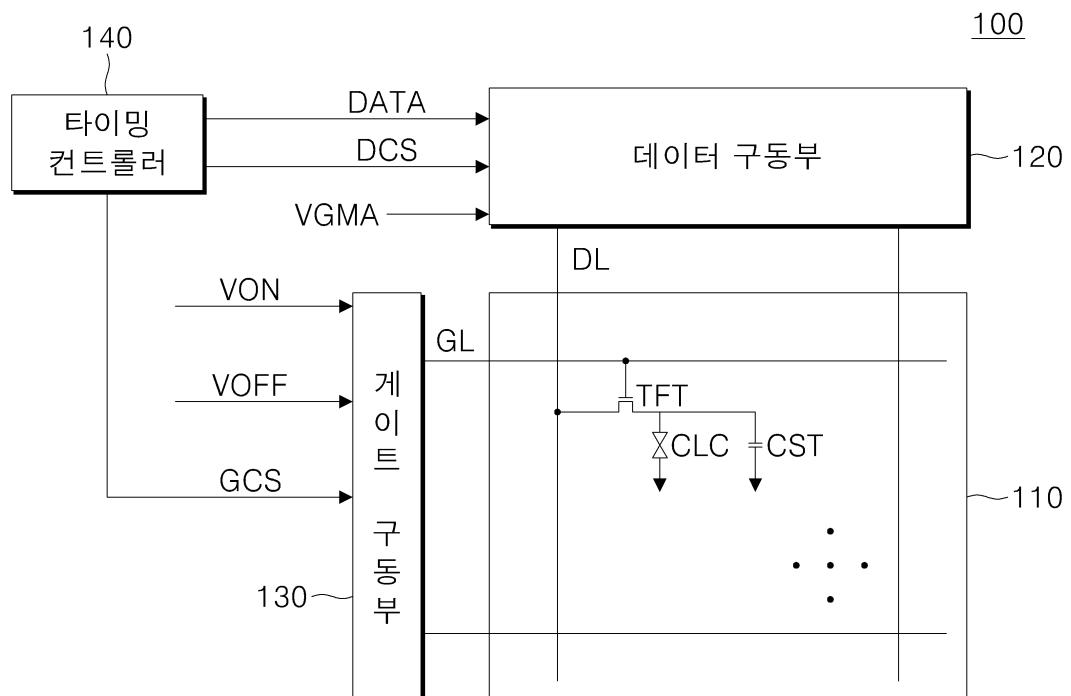

- [0038] 도 1은 본 발명의 일실시 예에 따른 액정 표시 장치의 구성 블록도이다. 도 1에 도시된 바와 같이, 본 발명의 일실시 예에 따른 액정 표시 장치(100)는 액정 패널(110), 데이터 구동부(120), 게이트 구동부(130), 및 타이밍 컨트롤러(140)를 포함한다.

- [0039] 상기 액정 패널(110)은 컬러 필터와 공통 전극이 형성된 컬러 필터 기판, 박막 트랜지스터와 화소 전극이 형성된 박막 트랜지스터 기판 및 컬러 필터 기판과 박막 트랜지스터 기판 사이에 충진되는 액정을 포함한다.

- [0040] 박막 트랜지스터 기판은 게이트 라인(GL)과 데이터 라인(DL)의 교차부에 데이터(DATA)를 표시하는 화소의 화소 용량(CLC)과 게이트 구동 신호에 응답하여 데이터(DATA)에 해당하는 전압을 화소 용량(CLC)에 인가하는 박막 트랜지스터(TFT) 및 화소 용량(CLC)에 인가된 데이터(DATA)에 해당하는 전압을 한 프레임 동안 유지하는 축적 용량(CST)을 포함한다.

- [0041] 박막 트랜지스터(TFT)는 게이트 라인(GL)에 연결되는 게이트, 데이터 라인(DL)에 연결되는 소스 및 화소 용량(CLC)의 화소 전극에 연결되는 드레인을 포함한다. 액정은 컬러 필터 기판에 형성된 공통 전극과 박막 트랜지스터 기판에 형성된 화소 전극 사이에 형성된 전계에 응답하여 회전함으로써 데이터(DATA)에 해당하는 계조를 표시한다.

- [0042] 상기 데이터 구동부(120)는 감마 전압(VGMA)을 이용하여 데이터(DATA)에 해당하는 아날로그 전압을 생성하고,

게이트 구동 신호에 의해 구동되는 박막 트랜지스터(TFT)에 데이터(DATA)에 해당하는 아날로그 전압을 인가하여 게이트 라인(GL) 단위로 데이터(DATA)를 표시한다.

[0043] 이를 위해 데이터 구동부(120)는 타이밍 컨트롤러(140)로부터 데이터 제어신호(DCS), 데이터(DATA)를 공급받고, 감마 전압 생성부(도시되지 않음)로부터 감마 전압(VGMA)을 인가받는다. 여기서 데이터 제어 신호(DCS)는 데이터 스타트 펄스(STH), 데이터 동기 클럭(CPH), 로드 신호(TP) 및 극성 반전 신호(POL)를 포함한다.

[0044] 데이터 구동부(120)는 복수 개의 데이터 구동 집적 회로(IC: Integrated Circuit)로 구현되어 TCP(Tape Carrier Package) 탑입으로 액정 패널(110)에 부착될 수 있으며, COG(Chip On Glass) 탑입으로 액정 패널(110)의 박막 트랜지스터 기판에 실장될 수 있다.

[0045] 상기 게이트 구동부(130)는 복수의 게이트 라인(GL)에 순차적으로 게이트 구동 신호를 인가하여 선택되는 게이트 라인(GL)에 각각 연결된 복수의 박막 트랜지스터(TFT)를 동시에 턴온시킨다. 이를 위해 게이트 구동부(120)는 타이밍 컨트롤러(140)로부터 게이트 제어신호(GCS)를 공급받고, 전원 공급부(도시되지 않음)로부터 게이트 구동 신호로 사용되는 게이트 온 전압(VON) 및 게이트 오프 전압(VOFF)을 공급받는다. 여기서 게이트 제어 신호(GCS)는 게이트 스타트 펄스(STV), 게이트 동기 클럭(CPV)을 포함한다.

[0046] 게이트 구동부(130)는 복수 개의 데이터 구동 집적 회로(IC: Integrated Circuit)로 구현되어 TCP(Tape Carrier Package) 탑입으로 액정 패널(110)의 박막 트랜지스터 기판에 부착될 수 있으며, 박막 트랜지스터 기판의 비표시 영역에 박막 트랜지스터(TFT)가 형성될 때 아몰포스 실리콘 게이트(ASG: Amorphous Silicon Gate) 형태로 집적되어 형성될 수 있다.

[0047] 상기 타이밍 컨트롤러(150)는 외부에서 입력되는 데이터(DATA)를 데이터 구동부(120)가 처리할 수 있는 데이터(DATA)로 변환하여 데이터 구동부(120)로 공급하고, 데이터 구동부(120)와 게이트 구동부(130)의 동작에 필요한 제어 신호(GCS, DCS)를 데이터 구동부(120)와 게이트 구동부(130) 각각에 공급한다.

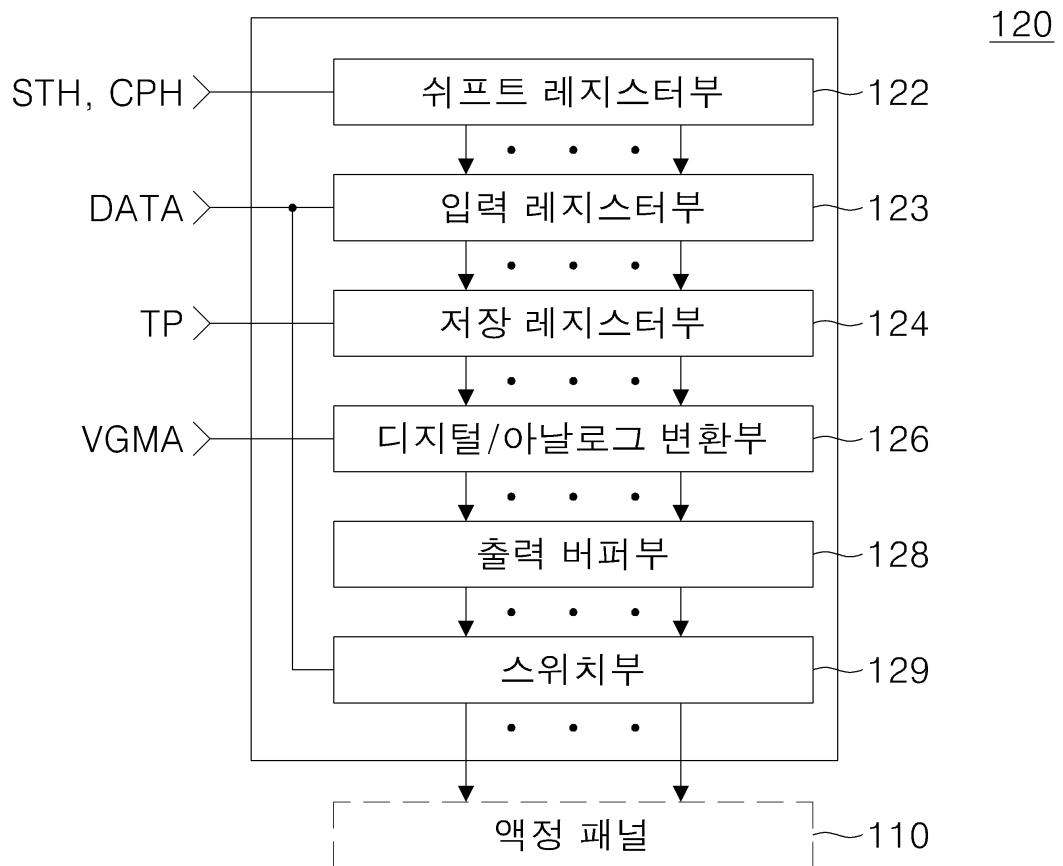

[0048] 도 2는 도 1의 액정 표시 장치의 데이터 구동부의 구성 블록도이다. 도2에 도시된 바와 같이, 본 발명의 일실시 예에 따른 데이터 구동부(120)는 쉬프트 레지스터부(122), 입력 레지스터부(123), 저장 레지스터부(124), 디지털/아날로그 변환부(126), 출력 버퍼부(128) 및 스위치부(129)를 포함한다.

[0049] 상기 쉬프트 레지스터부(122)는 데이터 스타트 신호(STH)와 데이터 동기 클럭(CPH)를 제공받아 샘플링 신호를 생성하여 입력 레지스터(124)로 제공한다. 구체적으로 쉬프트 레지스터(122)는 데이터 동기 클럭(CPH)의 한 주기마다 데이터 스타트 신호(STH)를 쉬프트 시키면서 n 개의 샘플링 신호를 생성한다. 이를 위해 쉬프트 레지스터(122)는 n 개의 쉬프트 레지스터를 포함한다. 여기서 n은 하나의 게이트 라인에 연결되는 화소 용량의 개수인 것이 바람직하다.

[0050] 상기 입력 레지스터부(123)는 쉬프트 레지스터부(122)로부터 순차적으로 입력되는 샘플링 신호에 응답하여 데이터(DATA)를 순차적으로 저장한다. 구체적으로 입력 레지스터부(123)는 샘플링 신호에 응답하여 1 라인 분에 해당하는 데이터(DATA)를 저장한다. 이를 위해 입력 레지스터부(123)는 n 개의 데이터(1 라인 분에 해당하는 데이터)를 래치시켜 저장하기 위한 데이터 입력용 래치를 포함한다.

[0051] 상기 저장 레지스터부(124)는 로드 신호(TP)가 입력되면, 입력 레지스터부(123)에 저장된 1 라인 분의 데이터(DATA)를 동시에 전달받아 저장한다. 이를 위해 저장 레지스터부(124)는 입력 레지스터부(123)의 데이터 입력용 래치와 동일한 개수의 데이터 저장용 래치를 포함한다. 여기서 로드 신호(TP)는 1 라인 분의 데이터(DATA)에 해당하는 아날로그 전압이 하나의 게이트 라인에 연결된 화소의 화소 용량에 동시에 인가되도록 하는 기능을 수행한다.

[0052] 상기 디지털/아날로그 변환부(126)는 감마 전압(VGMA)을 이용하여 데이터(DATA)에 대응하는 계조 표시 전압을 생성한 후 이를 출력 버퍼부(128)로 제공한다. 여기서 계조 표시 전압은 데이터의 계조에 대응하는 아날로그 전압이다.

[0053] 상기 출력 버퍼부(128)는 디지털/아날로그 변환부(126)으로부터 제공되는 아날로그 전압을 전류 증폭시켜 데이터 라인으로 제공하는 복수의 앰프(도시되지 않음)를 포함한다. 여기서 앰프는 Voltage Follower인 것이 바람직하다.

[0054] 상기 스위치부(129)는 액정 패널(110)과 출력 버퍼부(128) 사이에 위치하며, 로드 신호(TP)에 응답하여 출력 버

퍼부(128)의 출력을 스위칭하고, 데이터 라인을 차지 쉐어링(Charge Sharing)시켜 프리 차지(Pre-Charge)시킨다.

[0055] 본 실시 예에서 스위치부(129)는 데이터 구동부(129)에 포함되는 경우를 설명하였지만 이에 한정되지 아니하며, 스위치부(129)는 액정 패널의 박막 트랜지스터 기판에 접적되어 형성될 수도 있다.

[0056] 액정 패널(110)과 출력 버퍼부(128)에 연결되는 스위치부(129)를 좀 더 자세하게 설명한다.

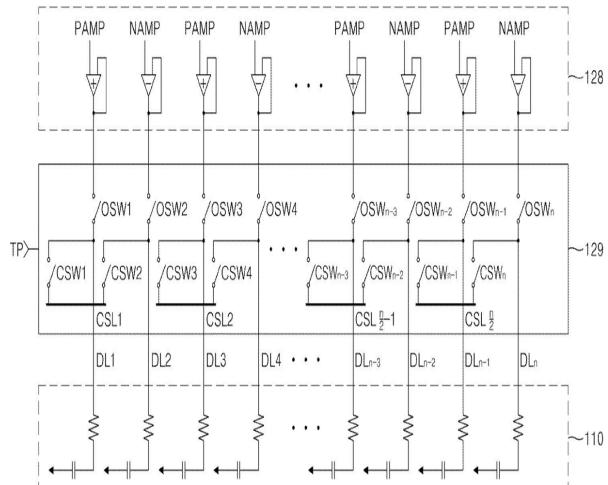

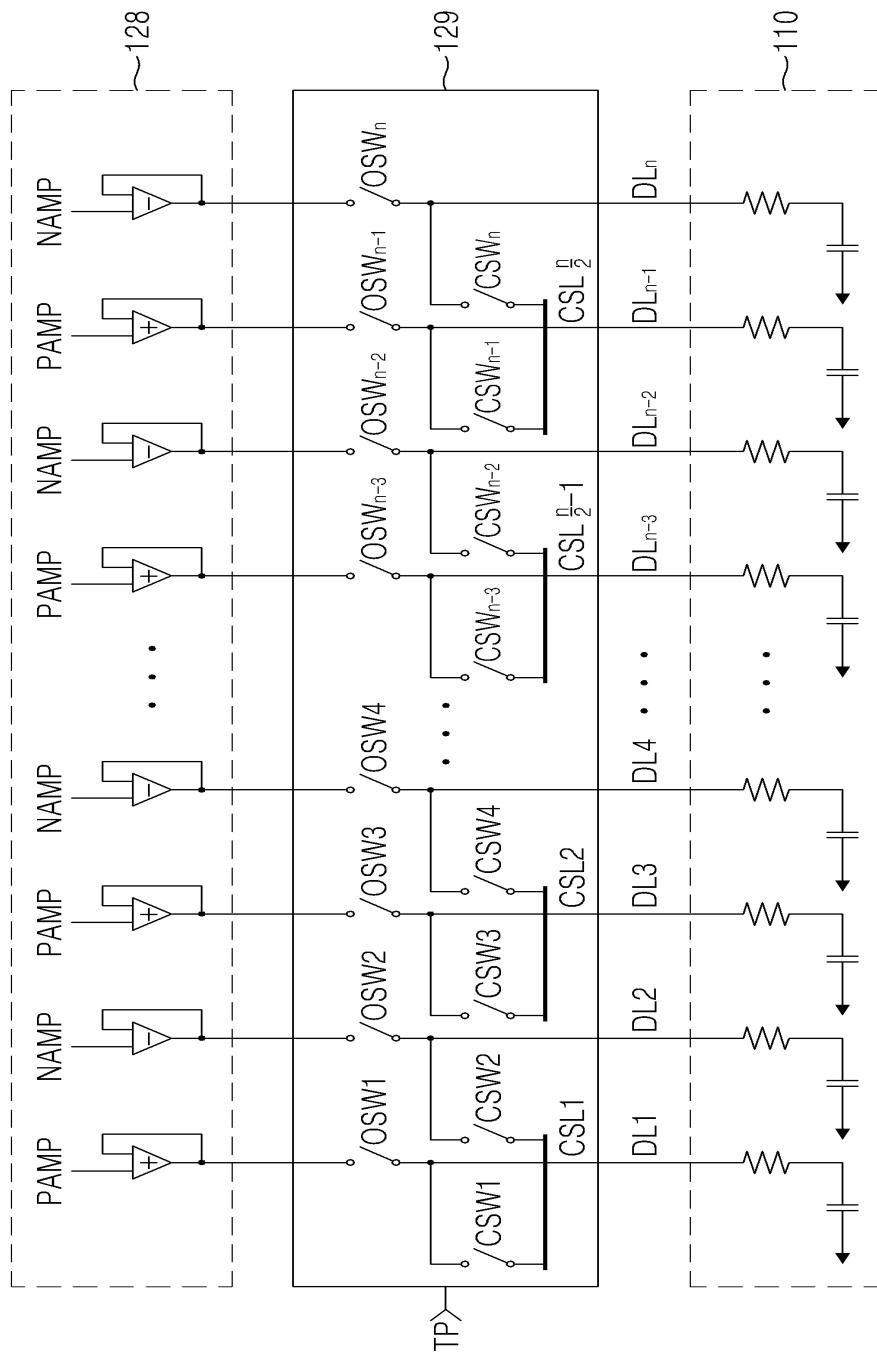

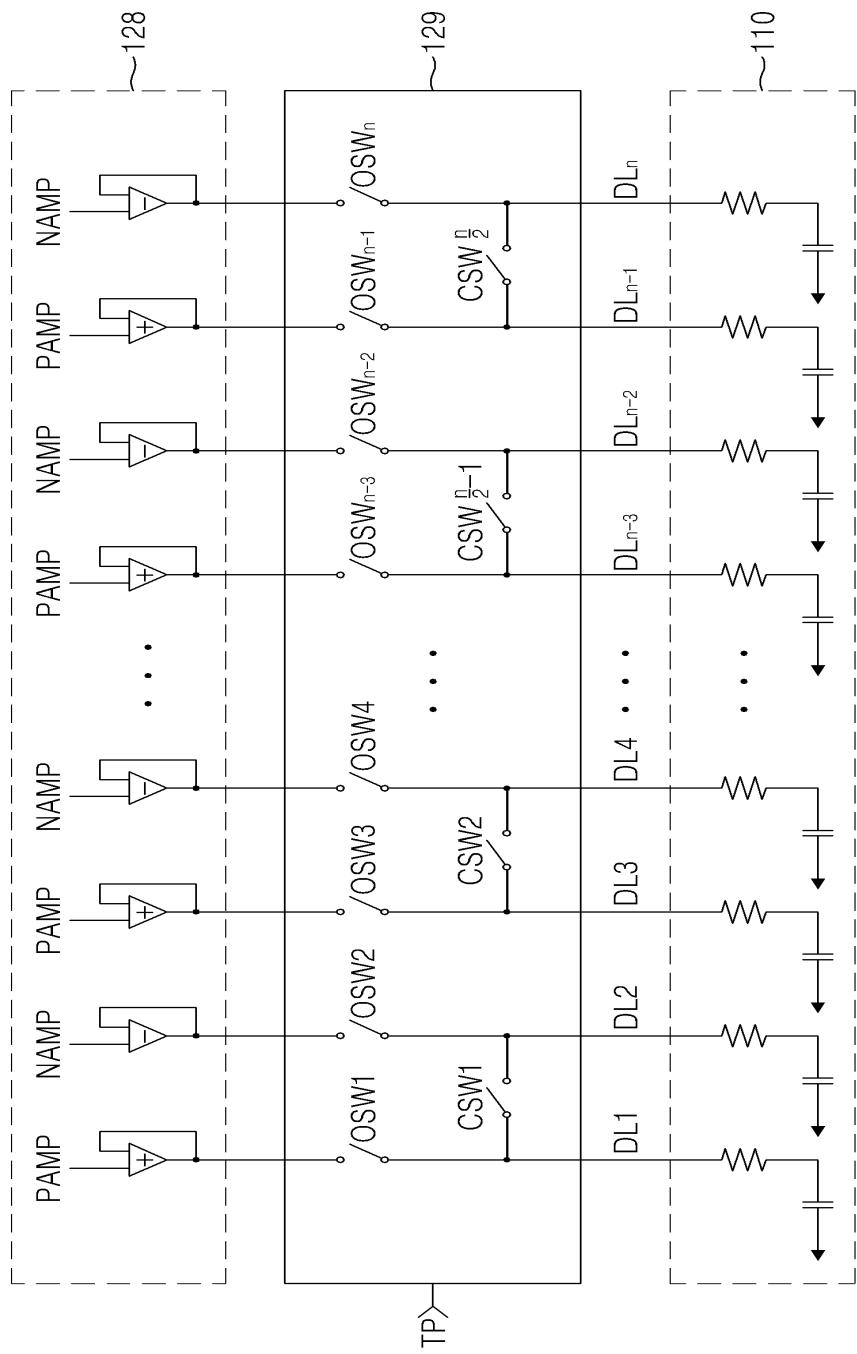

[0057] 도 3은 도 2에 도시된 스위치부의 구성 개념도이다. 도 3에 도시된 바와 같이, 출력 버퍼부(128)는 해당 데이터 라인에 극성 계조 표시 전압을 출력하는 복수의 앰프를 포함한다. 앰프는 극성 반전 신호(POL)에 응답하여 계조 표시 전압의 극성을 정극성 또는 부극성으로 출력한다.

[0058] 본 실시 예의 출력 버퍼부(129)는 도트 반전(Dot Inversion)을 수행하기 위한 것으로 복수의 앰프 중 홀수 번째 앰프는 정극성 계조 표시 전압을 출력하고 짝수 번째 앰프는 부극성 계조 표시 전압을 출력하는 경우를 예시한다. 이하 설명 및 이해의 편의를 도모하기 위하여 복수의 앰프 중 정극성 계조 표시 전압을 출력하는 앰프를 정극성 앰프(PAMP)라하고, 부극성 계조 표시 전압을 출력하는 앰프를 부극성 앰프(NAMP)라 한다.

[0059] 스위치부(129)는 복수의 출력 단속 스위치(OSW1 내지 OSWn), 복수의 전하 공유 스위치(CSW1 내지 CSWn) 및 복수의 전하 공유 라인(CSL1 내지 CSLn/2)을 포함한다. 출력 단속 스위치(OSW1 내지 OSWn)는 각 앰프와 각 앰프에 해당하는 데이터 라인(DL1 내지 DLn) 사이에 위치되며, 로드 신호(TP)에 응답하여 앰프 출력단과 데이터 라인 (DL1 내지 DLn)의 연결을 단속(斷續)한다. 전하 공유 스위치(CSW1 내지 CSWn)는 각 데이터 라인(DL1 내지 DLn)과 해당 전하 공유 라인 사이(CSL1 내지 CSLn/2)에 위치되며, 로드 신호(TP)에 응답하여 데이터 라인(DL1 내지 DLn)과 전하 공유 라인(CSL1 내지 CSLn/2)의 연결을 단속(斷續)한다.

[0060] 전하 공유 라인(CSL1 내지 CSLn/2)은 정극성 앰프(PAMP)에 연결된 데이터 라인(DL1, DL3, ..., DLn-1)과 부극성 앰프(NAMP)에 연결된 데이터 라인(DL2, DL4, ..., DLn)을 전기적으로 연결하여 데이터 라인 (DL1, DL2; DL3, DL4, ..., DLn-1, DLn)간에 전하가 공유되도록 한다. 다시 설명하면, 본 실시 예의 스위치부(129)는 한 쌍의 데이터 라인 단위(DL1, DL2; DL3, DL4; ..., DLn-1, DLn)로 하나의 전하 공유 라인(CSL1 내지 CSLn/2)을 구비한다. 여기서 한 쌍의 데이터 라인(DL1, DL2; DL3, DL4; ..., DLn-1, DLn)은 정극성 앰프(PAMP)에 연결되는 데이터 라인(DL1, DL3, ..., DLn-1)과 부극성 앰프(NAMP)에 연결되는 데이터 라인(DL2, DL4, ..., DLn)으로 구성된다.

[0061] 본 실시 예에서 전하 공유 스위치(CSW1 내지 CSLn)는 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DLn-1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DLn) 각각에 설치된다. 각 데이터 라인(DL1 내지 DLn)은 설치된 전하 공유 스위치(CSW1 내지 CSWn)를 통하여 각각 전하 공유 라인(CSL1 내지 CSLn/2)에 연결될 수 있다.

[0062] 로드 신호(TP)에 응답하여 출력 단속 스위치(OSW1 내지 OSWn)가 개방(Open)되고 전하 공유 스위치(CSW1 내지 CSWn)가 단락(Short)되면 각 전하 공유 라인(CSL1 내지 CSLn/2)을 통하여 한 쌍의 데이터 라인 (DL1, DL2; DL3, DL4, ..., DLn-1, DLn) 단위로 차지 쉐어링(Charge Sharing)이 일어나게 된다. 여기서 데이터 라인 쌍(DL1, DL2; DL3, DL4, ..., DLn-1, DLn)은 하나의 정극성 앰프(PAMP)에 연결되는 하나의 데이터 라인과 부극성 앰프(NAMP)에 연결되는 하나의 데이터 라인을 의미한다.

[0063] 그러므로 본 발명의 일실시 예에 따른 액정 표시 장치는 종래 데이터 구동 접적 회로의 첫 번째 데이터 라인과 마지막 데이터 라인에 발생되는 불균일한 차지 쉐어링 현상이 해소되며, 불균일한 차지 쉐어링 의해 나타나는 세로줄 시인 현상이 제거될 수 있다.

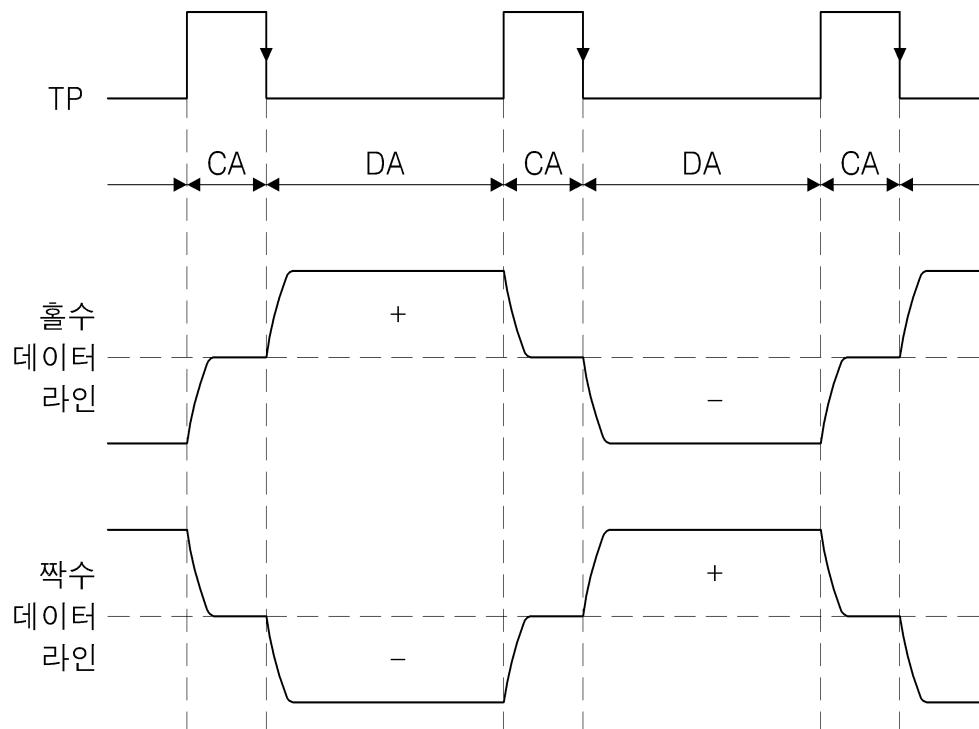

[0064] 도 4는 도 3에 도시된 스위치부의 동작을 설명하기 위한 타이밍도이다. 도 4에 도시된 바와 같이, 로드 신호 (TP)는 복수의 하이 레벨 구간과 복수의 로우 레벨 구간을 포함한다. 여기서 하이 레벨 구간은 차지 쉐어링이 일어나는 차지 쉐어링 구간(CA: Charge Sharing Area)이며, 로우 레벨 구간은 계조 표시 전압이 데이터 라인에 공급되는 드라이빙 구간(DA: Driving Area)이다.

[0065] 먼저 로드 신호(TP)가 하이 레벨 구간인 차지 쉐어링 구간(CA)에서 출력 단속 스위치(OSW1 내지 OSWn)는 개방(Open)되고 전하 공유 스위치(CSW1 내지 CSWn)는 단락(Short)된다. 따라서, 각 전하 공유 라인(CSL1 내지 CSLn/2)을 통하여 한 쌍의 데이터 라인 단위로 차지 쉐어링(Charge Sharing)이 일어나게 된다.

- [0066] 다음으로 로드 신호(TP)가 하이 레벨에서 로우 레벨로 떨어지는 폴링 시점에 출력 버퍼부(128)의 정극성 앰프(PAMP)는 정극성 계조 표시 전압을 홀수 데이터 라인(DL1, DL3, ..., DLn-1)으로 출력하고 부극성 앰프(NAMP)는 부극성 계조 표시 전압을 짝수 데이터 라인(DL2, DL4, ..., DLn)으로 출력하기 시작한다.

- [0067] 로드 신호(TP)가 로우 레벨 구간인 드라이빙 구간(DA)에서 출력 단속 스위치(OSW1 내지 OSWn)는 단락(Short)되고 전하 공유 스위치(CSW1 내지 CSWn)는 개방(Open)된다. 따라서, 데이터 라인(DL1 내지 DLn)에 정극성 또는 부극성을 가지는 계조 표시 전압이 제공된다.

- [0068] 한 라인 분의 계조 표시 전압이 데이터 라인(DL1 내지 DLn)에 공급된 후 다시 로드 신호(TP)가 하이 레벨 상태로 천이되어 차지 쉐어링이 일어나고, 로드 신호(TP)가 로우 레벨 상태로 천이되어 데이터 라인(DL1 내지 DLn)에 계조 표시 전압이 제공되는 과정을 반복한다.

- [0069] 한편 차지 쉐어링은 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DLn-1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DLn)이 쌍을 이루며 각 전하 공유 라인(CSL1 내지 CSLn/2)을 통하여 진행된다.

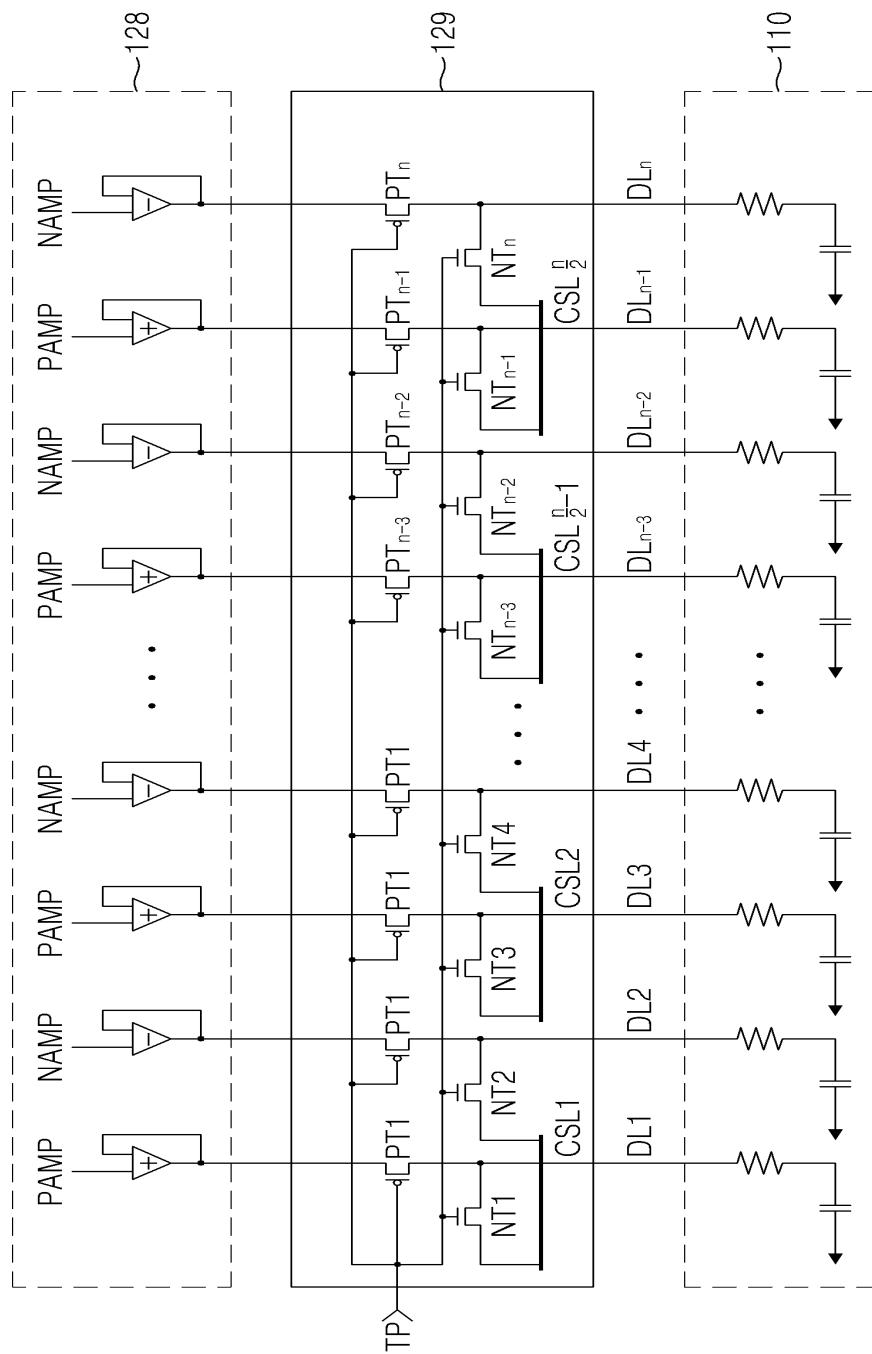

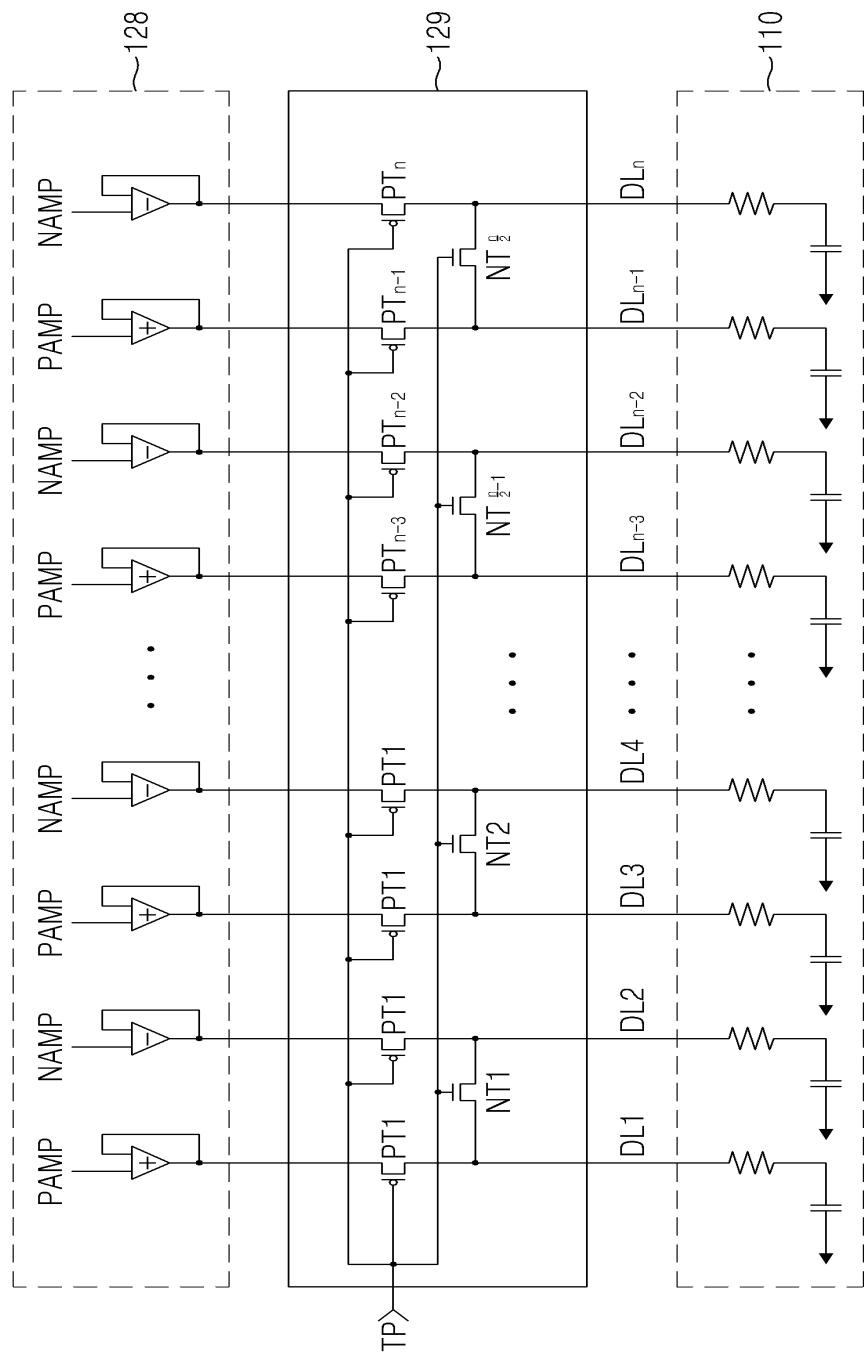

- [0070] 도 5는 도 3에 도시된 스위치부의 예시 회로도이다. 도 5에 도시된 바와 같이, 스위치부(129)는 PMOS 트랜지스터(PT1 내지 PTn)로 구성되는 출력 단속 스위치(OSW), NMOS 트랜지스터(NT1 내지 NTn)로 구성되는 전하 공유 스위치(CSW) 및 복수의 전하 공유 라인(CSL1 내지 CSLn/2)을 포함한다.

- [0071] 보다 구체적으로 출력 단속 스위치(OSW)를 구성하는 PMOS 트랜지스터(PT1 내지 PTn)는 앰프 출력단에 연결되는 소스, 데이터 라인에 연결되는 드레인 및 로드 신호(TP)가 인가되는 게이트를 포함한다. 따라서 출력 단속 스위치(OSW)는 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 개방(Open)되고 로드 신호(TP)가 로우 레벨이 드라이빙 구간에서 단락(Short)된다.

- [0072] 전하 공유 스위치(CSW)를 구성하는 NMOS 트랜지스터(NT1 내지 NTn)은 데이터 라인에 연결되는 드레인, 전하 공유 라인(CSL)에 연결되는 소스 및 로드 신호(TP)가 인가되는 게이트를 포함한다. 따라서 전하 공유 스위치(CSW)는 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 단락(Short)되고 로드 신호(TP)가 하이 레벨이 드라이빙 구간에서 개방(Open)된다.

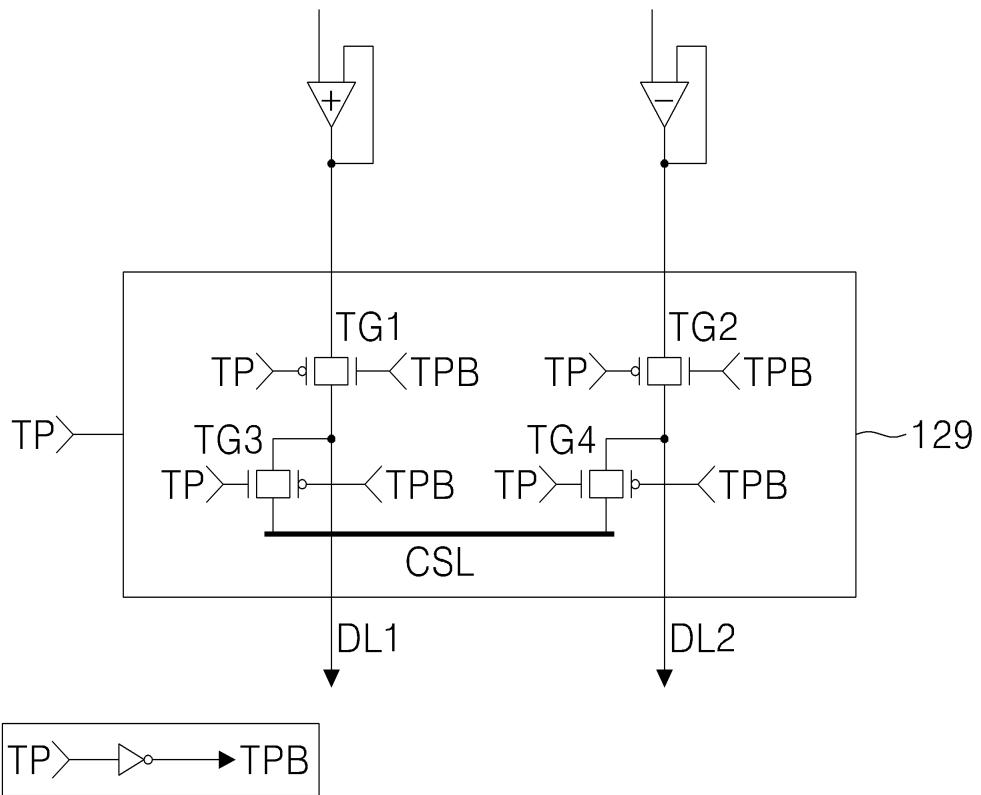

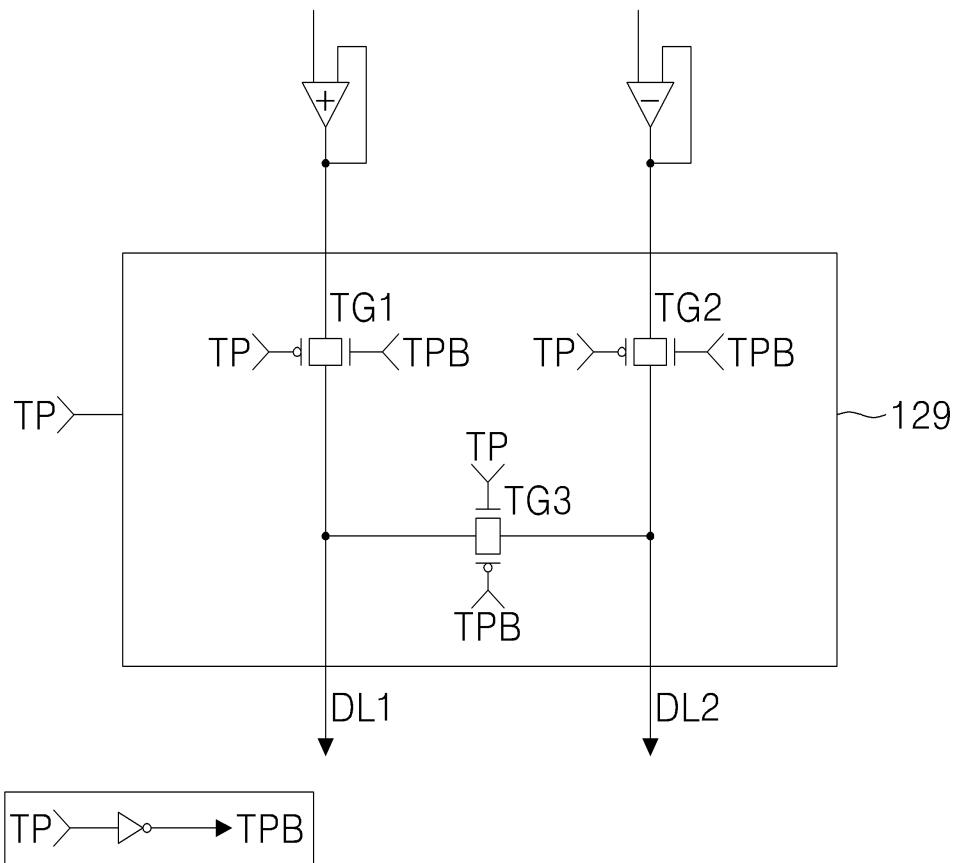

- [0073] 도 6은 도 3에 도시된 스위치부의 다른 예시 회로도로서, 정극성 계조 표시 전압이 제공되는 하나의 데이터 라인(DL1)과 부극성 계조 표시 전압이 제공되는 하나의 데이터 라인(DL2)에 해당하는 스위치부(129)를 도시한다. 도 6에 도시된 바와 같이, 스위치부(129)의 출력 단속 스위치(OSW)와 전하 공유 스위치(CSW)는 PMOS 트랜지스터와 NMOS 트랜지스터를 포함하는 트랜스퍼 게이트(TG1, TG2, TG3, YG4)로 구성된다.

- [0074] 보다 구체적으로 출력 단속 스위치(OSW)를 구성하는 트랜스퍼 게이트(TG1, TG2)는 PMOS 트랜지스터의 소스와 NMOS 트랜지스터의 드레인이 공통되어 앰프의 출력단에 연결되며, PMOS 트랜지스터의 드레인과 NMOS 트랜지스터의 소스가 공통되어 데이터 라인에 연결되고, PMOS 트랜지스터의 게이트에 로드 신호(TP)가 인가되고 NMOS 트랜지스터의 게이트에 로드바 신호(TPB)가 인가된다. 여기서 로드바 신호(TPB)는 로드 신호(TP)의 위상과 반전된 위상을 가지는 신호이다.

- [0075] 따라서 출력 단속 스위치(OSW)는 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 개방(Open)되고 로드 신호(TP)가 로우 레벨이 드라이빙 구간에서 단락(Short)된다.

- [0076] 전하 공유 스위치(CSW)를 구성하는 트랜스퍼 게이트(TG3, TG4)는 PMOS 트랜지스터의 소스와 NMOS 트랜지스터의 드레인이 공통되어 데이터 라인에 연결되며, PMOS 트랜지스터의 드레인과 NMOS 트랜지스터의 소스가 공통되어 전하 공유 라인(CSL)에 연결되고, PMOS 트랜지스터의 게이트에 로드바 신호(TPB)가 인가되고 NMOS 트랜지스터의 게이트에 로드 신호(TP)가 인가된다.

- [0077] 따라서 전하 공유 단속 스위치(CSW)는 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 단락(Short)되고 로드 신호(TP)가 로우 레벨이 드라이빙 구간에서 개방(Open)된다.

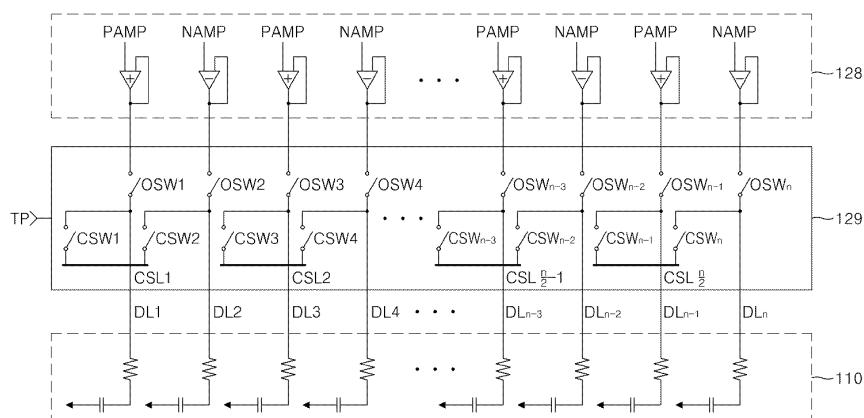

- [0078] 도 7은 도 2에 도시된 스위치부의 다른 구성 개념도이다. 도 7에 도시된 바와 같이, 스위치부의 전하 공유 스위

치(CSW1 내지 CSW<sub>n</sub>/2)는 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DL<sub>n</sub>-1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DL<sub>n</sub>) 사이에 설치된다. 각 데이터 라인 쌍(DL1, DL2; DL3, DL4, ..., DL<sub>n</sub>-1, DL<sub>n</sub>)은 각 데이터 라인 쌍(DL1, DL2; DL3, DL4, ..., DL<sub>n</sub>-1, DL<sub>n</sub>) 사이에 설치된 하나의 전하 공유 스위치(CSW1 내지 CSW<sub>n</sub>/2)를 공유하며 별도의 전하 공유 라인을 통하여 않고 전하 공유 스위치(CSW1 내지 CSW<sub>n</sub>/2)를 통하여 직접 연결될 수 있다.

[0079] 보다 구체적으로 전하 공유 스위치(CSW1 내지 CSW<sub>n</sub>/2)는 정극성 앰프(PAMP)에 연결된 데이터 라인(DL1, DL3, ..., DL<sub>n</sub>-1)과 부극성 앰프(NAMP)에 연결된 데이터 라인(DL2, DL4, ..., DL<sub>n</sub>) 사이에 형성되어 각 데이터 라인 쌍(DL1, DL2; DL3, DL4, ..., DL<sub>n</sub>-1, DL<sub>n</sub>)의 전기적 연결을 직접 단속한다.

[0080] 다시 설명하면, 본 실시 예의 스위치부(129)는 한 쌍의 데이터 라인(DL1, DL2; DL3, DL4, ..., DL<sub>n</sub>-1, DL<sub>n</sub>) 단위로 하나의 전하 공유 스위치(CSW1 내지 CSW<sub>n</sub>/2)를 구비한다. 여기서 한 쌍의 데이터 라인(DL1, DL2; DL3, DL4, ..., DL<sub>n</sub>-1, DL<sub>n</sub>)은 정극성 앰프(PAMP)에 연결되는 데이터 라인과 부극성 앰프(NAMP)에 연결되는 데이터 라인이다.

[0081] 스위치부(129)는 로드 신호(TP)에 응답하여 출력 단속 스위치(OSW1 내지 OSW<sub>n</sub>)를 개방(Open)하고 전하 공유 스위치(CSW1 내지 CSW<sub>n</sub>/2)를 단락(Short)시켜 한 쌍의 데이터 라인 단위(DL1, DL2; DL3, DL4; ...; DL<sub>n</sub>-1, DL<sub>n</sub>)로 차지 쉐어링(Charge Sharing)을 수행한다. 기타 다른 구성 요소 및 동작은 도 3에서 설명한 것으로부터 당업자가 용이하게 이해할 수 있는 것으로 상세한 설명은 생략한다.

[0082] 도 8은 도 7에 도시된 스위치부의 예시 회로도이다. 도 8에 도시된 바와 같이, 스위치부(129)는 PMOS 트랜지스터(PT1 내지 PT<sub>n</sub>)로 구성되는 출력 단속 스위치(OSW), NMOS 트랜지스터(NT1 내지 NT<sub>(n/2)</sub>)로 구성되는 전하 공유 스위치(CSW)를 포함한다.

[0083] 보다 구체적으로 전하 공유 스위치(CSW)를 구성하는 NMOS 트랜지스터(NT1 내지 NT<sub>(n/2)</sub>)는 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DL<sub>n</sub>-1)에 연결되는 드레인, 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DL<sub>n</sub>)에 연결되는 소스 및 로드 신호(TP)가 인가되는 게이트를 포함한다. 전하 공유 스위치(CSW)는 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 단락(Short)되고, 로드 신호(TP)가 하이 레벨인 드라이빙 구간에서 개방(Open)된다. 따라서 전하 공유 스위치(CSW)는 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DL<sub>n</sub>-1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DL<sub>n</sub>)을 전기적으로 서로 연결하여 차지 쉐어링을 수행한다.

[0084] 본 실시예에서 스위치부(129)는 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1, DL3, ..., DL<sub>n</sub>-1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2, DL4, ..., DL<sub>n</sub>)의 연결을 직접 스위칭하는 구조를 가지기 때문에 NMOS 트랜지스터의 개수를 줄일 수 있고 별도의 전하 공유 라인을 필요로 하지 않는 장점이 있다.

[0085] 도 9는 도 7에 도시된 스위치부의 다른 예시 회로도로서, 정극성 계조 표시 전압이 제공되는 하나의 데이터 라인과 부극성 계조 표시 전압이 제공되는 하나의 데이터 라인에 해당하는 스위치부를 도시한다. 도 9에 도시된 바와 같이, 스위치부(129)의 출력 단속 스위치(OSW)와 전하 공유 스위치(CSW)는 PMOS 트랜지스터와 NMOS 트랜지스터를 포함하는 트랜스퍼 게이트로 구성된다.

[0086] 보다 구체적으로 전하 공유 스위치(CSW)를 구성하는 트랜스퍼 게이트(TG1)는 PMOS 트랜지스터의 소스와 NMOS 트랜지스터의 드레인이 공통되어 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1)에 연결되며, PMOS 트랜지스터의 드레인과 NMOS 트랜지스터의 소스가 공통되어 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2)에 연결되고, PMOS 트랜지스터의 게이트에 로드바 신호(TPB)가 인가되고 NMOS 트랜지스터의 게이트에 로드 신호(TP)가 인가된다.

[0087] 전하 공유 단속 스위치(CSW)는 로드 신호(TP)가 로우 레벨이 드라이빙 구간에서 개방(Open)되고, 로드 신호(TP)가 하이 레벨인 차지 쉐어링 구간에서 단락(Short)된다. 따라서 전하 공유 단속 스위치(CSW)는 차지 쉐어링 구간에서 정극성 계조 표시 전압이 제공되는 데이터 라인(DL1)과 부극성 계조 표시 전압이 제공되는 데이터 라인(DL2)을 직접 전기적으로 연결하여 차지 쉐어링 동작을 수행한다.

- [0088] 출력 단속 스위치(OSW)는 도 6에서 설명한 것과 동일하므로 상세한 설명은 생략한다.

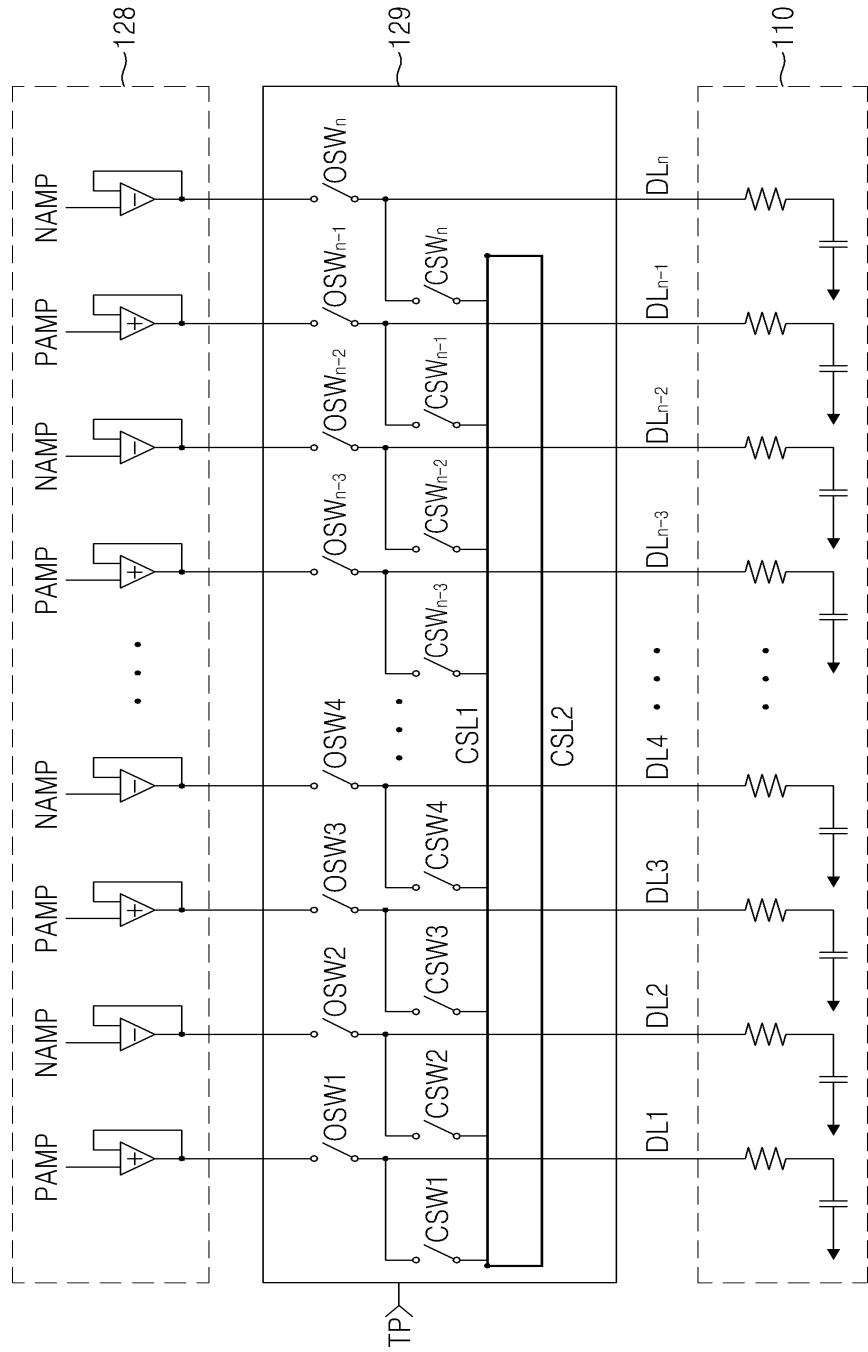

- [0089] 도 10은 본 발명의 다른 실시 예에 따른 액정 표시 장치의 스위치부의 구성 개념도이다. 도 10에 도시된 바와 같이, 스위치부(129)는 복수의 출력 단속 스위치(OSW1 내지 OSWn), 복수의 전하 공유 스위치(CSW1 내지 CSWn), 제1 전하 공유 라인(CSL1) 및 제2 전하 공유 라인(CSL2)을 포함한다.

- [0090] 전하 공유 스위치(CSWn)는 각 데이터 라인(DL1 내지 DLn)과 제1 전하 공유 라인(CSL1) 사이에 위치되며, 로드 신호(TP)에 응답하여 각 데이터 라인(DL1 내지 DLn)과 제1 전하 공유 라인(CSL1)의 연결을 단속(斷續)한다. 첫 번째 데이터 라인(DL1)과 마지막 번째 데이터 라인(DLn)에 설치된 전하 공유 스위치(CSW1, CSWn)는 제2 전하 공유 라인(CSL2)에 연결되어 첫 번째 데이터 라인(DL1)과 마지막 번째 데이터 라인(DLn)의 전기적 연결을 단속하는 기능을 동시에 수행한다.

- [0091] 제1 전하 공유 라인(CSL1)은 복수의 정극성 앰프(PAMP)에 각각 연결된 데이터 라인(DL1, DL3, DLn-1)과 복수의 부극성 앰프(NAMP)에 각각 연결된 데이터 라인(DL2, DL4, ..., DLn)을 전기적으로 연결하여 복수의 데이터 라인(DL1 내지 DLn)의 전하가 공유되도록 한다. 다시 설명하면, 본 실시 예의 스위치부(129)는 복수의 데이터 라인(DL1 내지 DLn)이 하나의 제1 전하 공유 라인(CSL1)을 공유하는 구성을 가진다.

- [0092] 제2 전하 공유 라인(CSL2)은 첫 번째 앰프에 연결되는 데이터 라인(DL1)과 마지막 번째 앰프에 연결되는 데이터 라인(DLn)간의 전하 공유를 위한 전하 공유 라인이다. 여기서 첫번째 앰프는 정극성 계조 표시 전압을 제공하고, 마지막 번째 앰프는 부극성 계조 표시 전압을 제공한다.

- [0093] 본 발명의 다른 실시 예에 따른 액정 표시 장치의 스위치부(129)는 제1 전하 공유 라인(CSL1)을 통하여 복수의 데이터 라인(DL1 내지 DLn)을 차지 쉐어링하고, 제2 전하 공유 라인을 통하여 첫 번째 데이터 라인(DL1)과 마지막 번째 데이터 라인(DLn)을 차지 쉐어링하는 구조를 가진다.

- [0094] 그러므로 본 발명의 다른 일실시 예에 따른 액정 표시 장치는 종래 데이터 구동 접적 회로의 첫 번째 데이터 라인과 마지막 데이터 라인에 발생되는 불균일한 차지 쉐어링 현상이 해소되며, 불균일한 차지 쉐어링 의해 나타나는 세로줄 시인 현상이 제거될 수 있다.

### 발명의 효과

- [0095] 본 발명의 데이터 구동 장치 및 액정 표시 장치는, 데이터 구동 접적 회로의 첫 번째 채널과 마지막 채널에 연결되는 데이터 라인을 균일하게 차지 쉐어하는 구조를 가지기 때문에 종래 전하 공유의 불균일로 발생하는 세로줄 시인 현상이 제거되는 효과가 있다.

- [0096] 이상에서 설명한 본 발명의 상세한 설명에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 숙련된 당업자 또는 해당 기술분야에 통상의 지식을 갖는 자라면 후술될 특허청구범위에 기재된 본 발명의 사상 및 기술 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

- [0097] 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허청구범위에 의해 정하여져야만 할 것이다.

### 도면의 간단한 설명

- [0001] 도 1은 본 발명의 일실시 예에 따른 액정 표시 장치의 구성 블록도,

- [0002] 도 2는 도 1에 도시된 액정 표시 장치의 데이터 구동부의 구성 블록도,

- [0003] 도 3은 도 2에 도시된 스위치부의 구성 개념도,

- [0004] 도 4는 도 3에 도시된 스위치부의 동작을 설명하기 위한 타이밍도,

- [0005] 도 5는 도 3에 도시된 스위치부의 예시 회로도,

- [0006] 도 6은 도 3에 도시된 스위치부의 다른 예시 회로도,

- [0007] 도 7은 도 2에 도시된 스위치부의 다른 구성 개념도,

- [0008] 도 8은 도 7에 도시된 스위치부의 예시 회로도,

- [0009] 도 9는 도 7에 도시된 스위치부의 다른 예시 회로도,

- [0010] 도 10은 본 발명의 다른 실시 예에 따른 액정 표시 장치의 스위치부의 구성 개념도이다.

- [0011] <도면의 주요부분에 대한 부호설명>

- [0012] 100: 액정 표시 장치                          110: 액정 패널

- [0013] 120: 데이터 구동부                          130: 게이트 구동부

- [0014] 140: 타이밍 컨트롤러

## 도면

### 도면1

## 도면2

도면3

도면4

도면5

도면6

$\text{TP} \nearrow \rightarrow \text{TPB}$

도면7

도면8

도면9

## 도면10

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 数据驱动装置和使用该装置的液晶显示器                                                                                        |         |            |

| 公开(公告)号        | <a href="#">KR101423197B1</a>                                                                                  | 公开(公告)日 | 2014-07-25 |

| 申请号            | KR1020060125336                                                                                                | 申请日     | 2006-12-11 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                                                                      |         |            |

| [标]发明人         | LEE JAE HAN<br>이재한<br>SON SUN KYU<br>손선규<br>LIM MYONG BIN<br>임명빈<br>HWANG IN YONG<br>황인용<br>KIM OCK JIN<br>김옥진 |         |            |

| 发明人            | 이재한<br>손선규<br>임명빈<br>황인용<br>김옥진                                                                                |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                    |         |            |

| CPC分类号         | G09G2330/023 G09G3/3614 G09G3/36 G09G3/3688 G09G2310/027 G09G2320/0233                                         |         |            |

| 代理人(译)         | KWON , HYUK SOO<br>SE JUN OH<br>宋 , 云何                                                                         |         |            |

| 其他公开文献         | KR1020080053600A                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                      |         |            |

### 摘要(译)

液晶显示装置技术领域本发明涉及一种执行电荷共享功能的液晶显示装置。本发明的数据驱动装置包括第一和第二输出中断开关，电荷共享线，以及第一和第二电荷共享开关。第一输出间歇开关响应于控制信号中断提供正极性灰度显示电压的第一放大器和提供有正极性灰度显示电压的第一数据线的连接。第二输出间歇开关中断提供负灰度显示电压的第二放大器的连接，并且第二数据线响应于控制信号提供负灰度显示电压。第一电荷共享开关响应于控制信号中断第一数据线和电荷共享线的连接。第二电荷共享开关响应于控制信号中断第二数据线和电荷共享线的连接。