(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년03월21일

(11) 등록번호 10-0815898

(24) 등록일자 2008년03월17일

(51) Int. Cl.

G09G 3/36 (2006.01)

(21) 출원번호 10-2001-0063208

(22) 출원일자 2001년10월13일

심사청구일자 2006년10월09일

(65) 공개번호 10-2003-0031282

(43) 공개일자 2003년04월21일

### (56) 선행기술조사문현

JP05204339 A

(뒷면에 계속)

### (73) 특허권자

엘지.필립스 엘시디 주식회사

서울 영등포구 여의도동 20번지

### (72) 발명자

이설우

경상북도국민신지평동642-3번지

최수경

경상북도국민신문집회동642-3번지

(74) 대체로

내나인

기욤이 밤여복

신사과 · 김세영

#### (54) 액정표시장치의 테이터 구동 장치 및 방법

(57) 8 약

본 발명은 디지털-아날로그 변환부와 출력버퍼부를 분리하여 집적화함으로써 테이프 캐리어 패키지의 불량에 따른 손실을 현저하게 줄일 수 있고, 디지털-아날로그 변환부를 시분할 구동함으로써 디지털-아날로그 변환기능을 하는 집적회로의 수를 줄일 수 있게 하는 액정표시장치의 데이터 구동 장치 및 방법에 관한 것이다.

본 발명은 입력된  $n$ 개씩의 화소데이터를 아날로그형태인 화소신호로 변환하고, 변환된  $n$ 개의 화소신호를  $k$ 개씩 시분할하여 출력하는 디지털-아날로그 변환 접적회로들과; 디지털-아날로그 변환 접적회로로부터  $k$ 개씩 공급되는 화소신호를 순차적으로 입력하여 훌딩한 다음, 동시에 신호완충시켜  $n$ 개씩의 데이터라인들로 출력하며, 디지털-아날로그 변환 접적회로들 각각에 적어도 2개가 공통으로 접속되어진 출력버퍼 접적회로들과; 디지털-아날로그 변환 접적회로들 및 출력버퍼 접적회로들 각각을 제어함과 아울러 디지털-아날로그 변환 접적회로들 각각에 공급 할 화소데이터를 상기  $n$ 개씩의 화소데이터로 구성되는 적어도 2개의 구간으로 시분할하여 공급하는 타이밍 제어 수단을 구비한다.

대표도 - 도3

(56) 선 행 기술조사 문현

JP09026765 A

JP2000137207 A

JP2003114650 A

KR1020010100792 A

---

## 특허청구의 범위

### 청구항 1

입력된 n개씩의 화소데이터를 아날로그 화소신호로 변환하고, 변환된 n개의 화소신호를 k개씩 시분할하는 디지털-아날로그 변환 집적회로들과;

상기 디지털-아날로그 변환 집적회로에 의해 상기 k개씩 시분할된 화소신호를 순차적으로 입력받아 홀딩한 다음 신호완충시켜 n개씩의 데이터라인들로 출력하는 출력버퍼 집적회로들과;

상기 디지털-아날로그 변환 집적회로들 각각에 공급할 화소데이터를 상기 n개씩의 화소데이터로 구성되는 적어도 2개의 구간으로 시분할하여 공급하는 타이밍 제어부을 구비하며,

상기 출력버퍼 집적회로들 중 적어도 2개가 공통으로 상기 디지털-아날로그 변환 집적회로들에 접속되는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 2

제 1 항에 있어서,

상기 디지털-아날로그 변환 집적회로는 상기 타이밍 제어부에 접속되는 인쇄회로기판 상에 실장되고,

상기 출력버퍼 집적회로는 상기 인쇄회로기판과 상기 데이터라인들이 배치된 액정패널 사이에 전기적으로 접속된 테이프 캐리어 패키지 상에 실장된 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 3

제 1 항에 있어서,

상기 디지털-아날로그 변환 집적회로들 각각은,

상기 타이밍제어부의 제어에 응답하여 샘플링신호를 순차적으로 출력하는 쉬프트 레지스터부와;

상기 타이밍제어부의 제어와 상기 샘플링신호에 응답하여 상기 타이밍제어부로부터 입력되는 n개의 화소데이터들을 순차적으로 래치하여 동시에 출력하는 래치부와;

입력된 감마전압을 이용하여 상기 n개의 화소데이터를 정극성 및 부극성 비디오 동시에 변환하고, 상기 타이밍제어부의 극성제어신호에 응답하는 n개의 화소신호를 선택함과 동시에 상기 타이밍제어부의 제1 선택제어신호에 응답하여 그 n개의 화소신호를 시분할하여 k개씩 출력하는 디지털-아날로그 변환부와;

상기 타이밍제어부의 제2 선택제어신호에 응답하여 상기 k개씩 순차적으로 출력되는 화소신호를 상기 적어도 2개의 출력버퍼 집적회로들에 선택적으로 출력하는 디멀티플렉서를 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 4

제 3 항에 있어서,

상기 디지털-아날로그 변환부는

상기 감마전압을 이용하여 상기 n개의 화소데이터를 정극성의 화소신호로 변환하는 정극성 디코딩부와;

상기 감마전압을 이용하여 상기 n개의 화소데이터를 부극성의 화소신호로 변환하는 부극성 디코딩부와;

상기 정극성 및 부극성 디코딩부에 공통 접속되어 상기 극성제어신호 및 제1 선택제어신호에 응답하는 상기 k개씩의 화소신호를 상기 디멀티플렉서로 순차적으로 출력하는 멀티플렉서를 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 5

제 3 항에 있어서,

상기 제1 및 제2 선택제어신호들은 상기 n개의 화소신호를 상기 k개씩의 화소신호로 시분할하는 횟수에 해당되

는 비트수를 가지는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

#### 청구항 6

제 1 항에 있어서,

상기 디지털-아날로그 변환 집적회로 각각은

상기 타이밍제어부의 제어에 응답하여 샘플링신호를 순차적으로 출력하는 소프트 레지스터부와;

상기 타이밍제어부의 제어와 상기 샘플링신호에 응답하여 상기 타이밍제어부로부터 입력되는 n개의 화소데이터들을 순차적으로 래치하여 동시에 출력하는 래치부와;

입력 감마전압을 이용하여 상기 n개의 화소데이터를 정극성 및 부극성 비디오 동시에 변환하고 상기 타이밍제어부의 극성제어신호에 응답하는 n개의 화소신호를 선택하여 출력하는 디지털-아날로그 변환부와;

상기 n개의 화소신호를 상기 타이밍제어부의 제1 선택제어신호에 응답하여 적어도 2개의 출력단에 선택적으로 출력하는 디멀티플렉서와;

상기 적어도 2개의 출력단 각각에 접속되어 상기 n개의 화소신호를 상기 타이밍제어부의 제2 선택제어신호에 응답하여 k개씩 시분할시켜 출력하는 적어도 2개의 멀티플렉서를 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

#### 청구항 7

제 3 항 또는 제 6 항에 있어서,

상기 디지털-아날로그 변환 집적회로 각각은

상기 디지털-아날로그 변환 집적회로의 구성요소들 각각에 상기 타이밍제어부로부터의 제어신호들과 화소데이터를 중계하여 공급하는 신호제어부와;

입력된 감마기준전압을 세분화하여 상기 감마전압을 발생하는 감마 전압부를 추가로 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

#### 청구항 8

제 3 항에 있어서,

상기 제1 선택제어신호는 상기 래치부의 출력을 제어하는 출력이네이블신호의 주기마다 상기 선택제어신호의 논리상태가 반전되고,

상기 제2 선택제어신호는 상기 n개의 화소신호를 상기 k개씩의 화소신호로 시분할하는 횟수에 해당되는 비트수를 갖는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

#### 청구항 9

제 1 항에 있어서,

상기 출력버퍼 집적회로들 각각은

상기 n개의 데이터라인들 중 k개씩의 데이터라인들에 접속되어 상기 화소신호 훌딩 및 신호완충 기능을 하는 다수개의 출력버퍼부와;

상기 디지털-아날로그 집적회로로부터 k개씩 공급되는 화소신호를 상기 타이밍제어부의 선택제어신호에 응답하여 상기 다수개의 출력버퍼부에 순차적으로 공급하는 디멀티플렉서를 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

#### 청구항 10

제 9 항에 있어서,

상기 다수개의 출력버퍼부 각각은

상기 k개의 데이터라인들에 각각 접속되는 k개의 출력버퍼들로 구성되고,

상기 출력버퍼들은 각각 입력된 상기 화소신호를 홀딩하는 홀딩수단과;

상기 타이밍제어부로부터의 제어신호에 응답하여 상기 홀딩된 화소신호를 출력하는 스위칭수단과;

상기 스위칭수단에 접속되어 상기 신호완충 기능을 하는 전압 추종기를 구비하는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 11

제 9 항에 있어서,

상기 선택제어신호는 상기 n개의 화소신호를 상기 k개씩의 화소신호로 시분할하는 횟수에 해당되는 비트수를 가지는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 12

제 1 항에 있어서,

상기 타이밍제어부로부터 상기 디지털-아날로그 변환 집적회로들에 공급되는 제어신호들과 화소데이터의 주파수가 적어도 2배 이상 증가된 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 13

제 2 항에 있어서,

상기 출력버퍼 집적회로를 실장한 테이프 캐리어 패키지는 상기 k개의 입력핀과 상기 n개의 출력핀을 갖는 것을 특징으로 하는 액정표시장치의 데이터 구동 장치.

### 청구항 14

n개씩의 데이터라인들에 접속되어진 출력버퍼 집적회로들과, 적어도 2개의 출력버퍼 집적회로 입력단에 공통 접속된 디지털-아날로그 변환 집적회로들로 구성되고, 액정패널에 배치된 데이터라인들을 구동하기 위한 데이터 구동 장치의 구동 방법에 있어서,

상기 디지털-아날로그 변환 집적회로들 각각에 공급될 화소데이터를 상기 n개씩의 화소데이터로 구성되는 적어도 2개의 구간으로 시분할하여 공급하는 단계와;

상기 디지털-아날로그 변환 집적회로가 상기 n개씩의 화소데이터를 아날로그 화소신호로 변환하고, 상기 변환된 화소신호를 k개씩 시분할하여 공급하는 단계와;

상기 적어도 2개의 출력버퍼 집적회로가 상기 k개씩의 화소신호들을 순차적으로 입력하여 홀딩한 다음 신호완충 시켜 상기 데이터라인들에 공급하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 데이터 구동 방법.

### 청구항 15

제 14 항에 있어서,

상기 디지털-아날로그 변환 집적회로가 상기 n개씩의 화소데이터를 아날로그 화소신호로 변환하고, 상기 변환된 화소신호를 k개씩 시분할하여 공급하는 단계는

상기 n개의 화소데이터를 감마전압을 이용하여 정극성 및 부극성 화소신호로 변환하고, 외부로부터 입력되는 극성제어신호와 제1 선택제어신호에 응답하는 k개씩의 화소신호를 순차적으로 공급하는 단계와;

상기 k개의 화소신호를 외부로부터의 제2 선택제어신호에 응답하여 상기 적어도 2개의 출력버퍼 집적회로 각각에 선택적으로 공급하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 데이터 구동 방법.

### 청구항 16

제 14 항에 있어서,

상기 디지털-아날로그 변환 집적회로가 상기 n개씩의 화소데이터를 아날로그 화소신호로 변환하고, 상기 변환된

화소신호를 k개씩 시분할하여 공급하는 단계는

상기 n개의 화소데이터를 감마전압을 이용하여 정극성 및 부극성 화소신호로 변환하고, 외부로부터 입력되는 극 성제어신호에 응답하는 n개의 화소신호를 공급하는 단계와;

상기 n개의 화소신호를 선택제어신호에 응답하여 상기 k개씩의 화소데이터로 시분할하여 공급하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 데이터 구동 방법.

## 청구항 17

삭제

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<20>

본 발명은 액정표시장치에 관한 것으로, 특히 디지털-아날로그 변환부와 출력버퍼부를 분리하여 집적화함으로써 테이프 캐리어 패키지의 불량에 따른 손실을 현저하게 줄일 수 있게 하는 액정표시장치의 데이터 구동 장치 및 방법에 관한 것이다. 또한, 본 발명은 디지털-아날로그 변환부를 시분할 구동함으로써 디지털-아날로그 변환기능을 하는 집적회로의 수를 줄일 수 있게 하는 액정표시장치의 데이터 구동 장치 및 방법에 관한 것이다.

<21>

통상의 액정표시장치는 전계를 이용하여 액정의 광투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여 액정표시장치는 액정셀들이 매트릭스 형태로 배열되어진 액정패널과 이 액정패널을 구동하기 위한 구동회로를 구비한다. 액정패널에는 게이트라인들과 데이터라인들이 교차하게 배열되고 그 게이트라인들과 데이터라인들의 교차로 마련되는 영역에 액정셀들이 위치하게 된다. 이 액정패널에는 액정셀들 각각에 전계를 인가하기 위한 화소전극들과 공통전극이 마련된다. 화소전극들 각각은 스위칭 소자인 박막트랜지스터(Thin Film Transistor)의 소스 및 드레인 단자들을 경유하여 데이터라인들 중 어느 하나에 접속된다. 박막트랜지스터의 게이트단자는 화소전압신호가 1라인분씩의 화소전극들에게 인가되게 하는 게이트라인들 중 어느 하나에 접속된다. 구동회로는 게이트라인들을 구동하기 위한 게이트 드라이버와, 데이터라인들을 구동하기 위한 데이터 드라이버와, 공통전극을 구동하기 위한 공통전압 발생부를 구비한다. 게이트 드라이버는 스캐닝신호를 게이트라인들에 순차적으로 공급하여 액정패널 상의 액정셀들을 1라인분씩 순차적으로 구동한다. 데이터 드라이버는 게이트라인들 중 어느 하나에 게이트신호가 공급될 때마다 데이터라인들 각각에 화소신호를 공급한다. 공통전압 발생부는 공통전극에 공통전압신호를 공급한다. 이에 따라, 액정표시장치는 액정셀별로 화소신호에 따라 화소전극과 공통전극 사이에 인가되는 전계에 의해 광투과율을 조절함으로써 화상을 표시한다. 데이터 드라이버와 게이트 드라이버는 집적회로(Integrated Circuit; 이하, IC라 함) 칩(Chip)으로 제작되어 테이프 캐리어 패키지(Tape Carrier Package; 이하, TCP라 함) 상에 실장되며 주로 템(TAB; Tape Automated Bonding) 방식으로 액정패널에 접속된다.

<22>

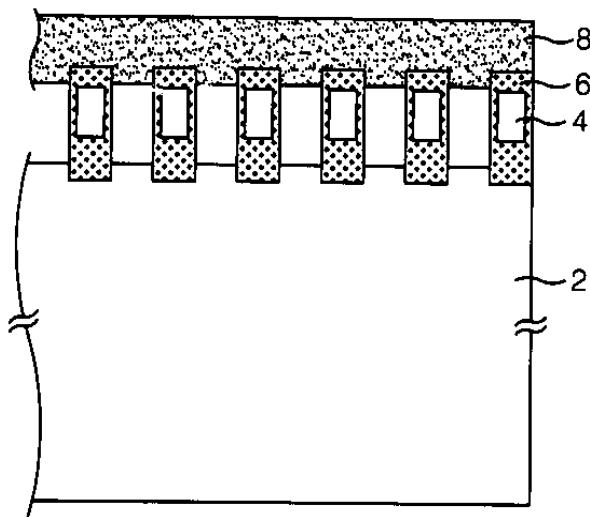

도 1은 종래 액정표시장치의 데이터 구동블록을 개략적으로 도시한 것으로, 데이터 구동블록은 TCP(6)를 통해 액정패널(2)과 접속되어진 데이터 드라이브 IC들(4)과; TCP(6)를 통해 데이터 드라이브 IC들(4)과 접속되어진 데이터 인쇄회로기판(Printed Circuit Board; 이하, PCB라 함)(8)을 구비한다.

<23>

데이터 PCB(8)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들 및 데이터 신호들과 파워부(도시하지 않음)로부터의 구동전압신호들을 입력하여 데이터 구동 IC들(4)로 중계하는 역할을 한다. TCP(6)는 액정패널(2)의 상단부에 마련된 데이터 패드들과 전기적으로 접속됨과 아울러 데이터 PCB(8)에 마련된 출력 패드들과 전기적으로 접속된다. 데이터 드라이브 IC들(4)은 디지털 신호인 화소데이터 신호를 아날로그 신호인 화소신호로 변환하여 액정패널(2) 상의 데이터라인들에 공급한다.

<24>

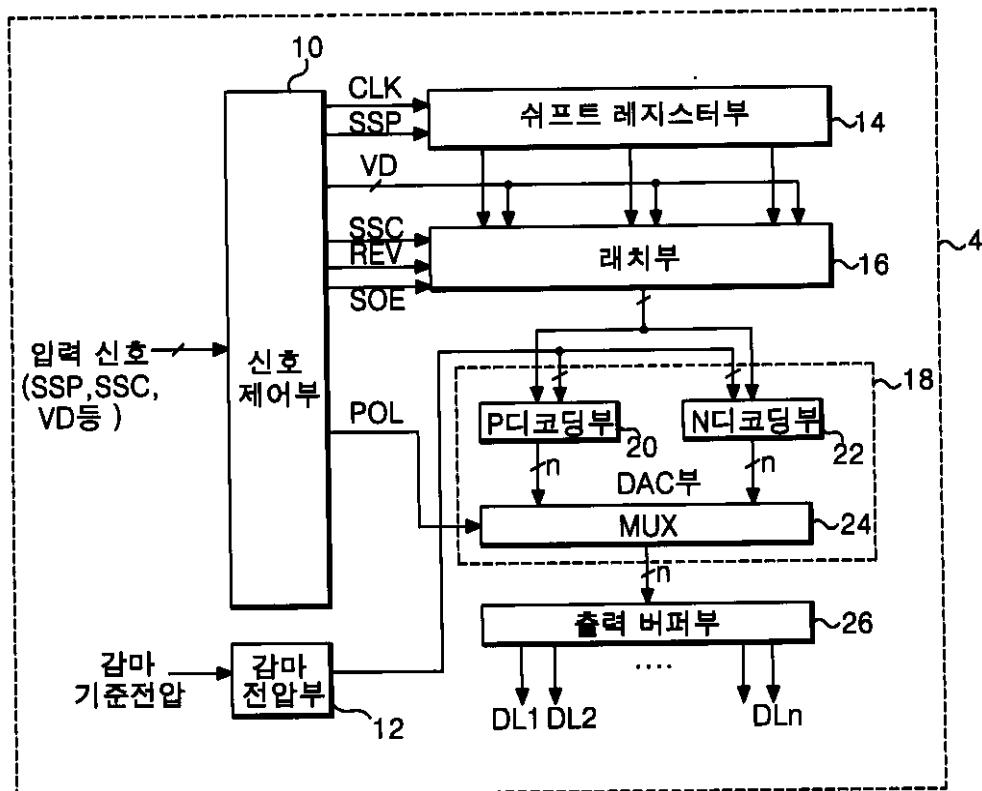

이를 위하여, 데이터 드라이브 IC들(4) 각각은 도 2에 도시된 바와 같이 순차적인 샘플링신호를 공급하는 쉬프트 레지스터부(14)와, 샘플링신호에 응답하여 화소데이터(VD)를 순차적으로 래치하여 동시에 출력하는 래치부(16)와, 래치부(16)로부터의 화소데이터(VD)를 화소신호로 변환하는 디지털-아날로그 변환부(이하, DAC부라 함)(18)와, DAC(18)로부터의 화소신호를 완충하여 출력하는 출력 버퍼부(26)를 구비한다. 또한, 데이터 드라이브 IC(4)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 화소데이터(VD)를 중계하는 신호

제어부(10)와, DAC부(18)에서 필요로 하는 정극성 및 부극성 감마전압들을 공급하는 감마 전압부(12)를 추가로 구비한다. 이러한 구성을 가지는 데이터 드라이브 IC들(4) 각각은 n개씩의 데이터라인들(D1 내지 Dn)을 구동하게 된다.

- <25> 신호제어부(10)는 타이밍 제어부로부터의 각종 제어신호들(CLK, SSP, SSC, SOE, REV, POL 등)과 화소데이터(VD)를 해당 구성요소들로 출력되게 제어한다.

- <26> 감마전압부(12)는 감마 기준전압 발생부(도시하지 않음)로부터 입력되는 다수개의 감마 기준전압을 그레이별로 세분화하여 출력한다.

- <27> 쉬프트 레지스터부(14)에 포함된 n개의 쉬프트 레지스터들은 신호제어부(10)로부터의 소스 스타트 펄스(SSP)를 클럭신호(CLK)에 따라 순차적으로 쉬프트시켜 샘플링신호로 출력한다.

- <28> 래치부(16)에 포함된 n개의 래치들은 쉬프트 레지스터부(14)의 샘플링신호에 응답하여 신호 제어부(10)로부터의 화소데이터(VD)를 순차적으로 샘플링하여 래치하게 된다. 이때, 래치들은 신호 제어부(10)로부터 공급되는 소스 샘플링 클럭신호(SSC)의 라이징 또는 폴링 에지에서 화소데이터(VD)를 샘플링하게 된다. 이어서, n개의 래치들은 신호 제어부(10)로부터의 소스 출력 이네이블신호(SOE)에 응답하여 래치된 화소데이터들(VD)을 동시에 출력한다. 이 경우, 래치부(16)는 데이터반전 선택신호(REV)에 응답하여 트랜지션 비트수가 줄어들게끔 변조된 화소데이터(VD)들은 복원시켜 출력하게 된다. 이는 타이밍 제어부에서 데이터전송시 전자기적 간섭(EMI)을 최소화하기 위하여 트랜지션되는 비트수가 기준치를 넘어서는 화소데이터(VD)들은 트랜지션 비트수가 줄어들게끔 변조하여 공급하기 때문이다.

- <29> DAC부(18)는 래치부(16)로부터의 화소데이터를 동시에 정극성 및 부극성 화소신호로 변환하여 출력하게 된다. 이를 위하여, DAC부(18)는 래치부(16)에 공통 접속된 P(Positive) 디코딩부(20) 및 N(Negative) 디코딩부(22) 와, P 디코딩부(20) 및 N 디코딩부(22)의 출력신호를 선택하기 위한 멀티플렉서(MUX; 24)를 구비한다.

- <30> P 디코딩부(20)에 포함되는 n개의 P 디코더들은 래치부(16)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(12)로부터의 정극성 감마전압들을 이용하여 정극성 화소신호로 변환하게 된다. N 디코딩부(22)에 포함되는 n개의 N 디코더들은 래치부(16)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(12)로부터의 부극성 감마전압들을 이용하여 부극성 화소신호로 변환하게 된다. 멀티플렉서(24)는 신호제어부(10)로부터의 극성 제어신호(POL)에 응답하여 P 디코더(20)로부터의 정극성 화소신호 또는 N 디코더(22)로부터의 부극성 화소신호를 선택하여 출력하게 된다.

- <31> 출력버퍼부(26)에 포함되는 n개의 출력버퍼들은 n개의 데이터라인들(D1 내지 Dn)들에 직렬로 각각 접속되어 전 전압추종기(Voltage follower) 등으로 구성된다. 이러한 출력버퍼들은 DAC부(18)로부터의 화소신호들을 신호완 충하여 데이터라인들(D1 내지 Dn)에 공급하게 된다.

- <32> 이와 같이, 종래의 데이터 드라이브 IC들(4) 각각은 n개의 데이터라인들(D1 내지 Dn)을 구동하기 위하여 n개씩의 쉬프트 레지스터들 및 래치들과 2n개의 디코더들을 구비해야만 한다. 이 결과, 종래의 데이터 드라이브 IC들(4)은 그 구성이 복잡하고 제조단가가 상대적으로 높은 단점을 가진다.

- <33> 또한, 종래의 데이터 드라이브 IC들(4) 각각은 도 1에 도시된 바와 같이 하나의 칩 형태로 TCP(6)에 부착되어 액정패널(2)과 데이터 PCB(8)와 접착된다. 여기서, TCP(6)는 단선, 단락 등과 같은 불량율이 상대적으로 높다. 이에 따라, TCP(6)에 불량이 발생하는 경우 그 TCP(6) 상에 실장된 고가의 데이터 드라이브 IC(4)도 같이 사용할 수 없게 되므로 경제적인 손실이 크다는 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

- <34> 따라서, 본 발명의 목적은 DAC부와 출력버퍼부를 분리하여 집적화함으로써 TCP 불량에 의한 손실을 최소화할 수 있는 액정표시장치의 데이터 구동 장치 및 방법을 제공하는 것이다.

- <35> 본 발명의 다른 목적은 DAC부를 시분할 구동함으로써 DAC IC의 수를 줄여 제조단가를 낮출 수 있는 액정표시장 치의 데이터 구동 장치 및 방법을 제공하는 것이다.

- <36> 본 발명의 또 다른 목적은 출력버퍼 IC의 입력핀 수를 줄여 인쇄회로기판 상에서 출력패드 피치를 충분히 확보 할 수 있게 하는 액정표시장치의 데이터 구동 장치 및 방법을 제공하는 것이다.

## 발명의 구성 및 작용

- <37> 상기 목적을 달성하기 위하여, 본 발명의 한 특징에 따른 액정표시장치의 데이터 구동 장치는 입력된 n개씩의 화소데이터를 아날로그형태인 화소신호로 변환하고, 변환된 n개의 화소신호를 k개씩 시분할하여 출력하는 디지털-아날로그 변환 집적회로들과; 디지털-아날로그 변환 집적회로로부터 k개씩 공급되는 화소신호를 순차적으로 입력하여 홀딩한 다음, 동시에 신호완충시켜 n개씩의 데이터라인들로 출력하며, 디지털-아날로그 변환 집적회로들 각각에 적어도 2개가 공통으로 접속되어진 출력버퍼 집적회로들과; 디지털-아날로그 변환 집적회로들 및 출력버퍼 집적회로들 각각을 제어함과 아울러 디지털-아날로그 변환 집적회로들 각각에 공급할 화소데이터를 상기 n개씩의 화소데이터로 구성되는 적어도 2개의 구간으로 시분할하여 공급하는 타이밍 제어수단을 구비한다.

- <38> 여기서, 상기 디지털-아날로그 변환 집적회로는 타이밍 제어부에 접속되는 인쇄회로기판 상에 실장되고, 출력버퍼 집적회로는 인쇄회로기판과 데이터라인들이 배치된 액정패널 사이에 전기적으로 접속되어진 테이프 캐리어 패키지 상에 실장된 것을 특징으로 한다.

- <39> 특히, 상기 디지털-아날로그 변환 집적회로 각각은 타이밍제어부의 제어에 응답하여 샘플링신호를 순차적으로 출력하는 쉬프트 레지스터부와; 타이밍제어부의 제어와 샘플링신호에 응답하여 타이밍제어부로부터 입력되는 n개의 화소데이터들을 순차적으로 래치하고 동시에 출력하는 래치부와; 입력 감마전압을 이용하여 n개의 화소데이터를 정극성 및 부극성 비디오 동시에 변환하고 타이밍제어부의 극성제어신호에 응답하는 n개의 화소신호를 선택함과 동시에 타이밍제어부의 제1 선택제어신호에 응답하여 그 n개의 화소신호를 시분할하여 k개씩 출력하는 디지털-아날로그 변환부와; 타이밍제어부의 제2 선택제어신호에 응답하여 k개씩 순차적으로 출력되는 화소신호를 적어도 2개의 출력버퍼 집적회로들에 선택적으로 출력하는 디멀티플렉서를 구비하는 것을 특징으로 한다.

- <40> 여기서, 상기 디지털-아날로그 변환부는 감마전압을 이용하여 n개의 화소데이터를 정극성의 화소신호로 변환하는 정극성 디코딩부와; 감마전압을 이용하여 상기 n개의 화소데이터를 부극성의 화소신호로 변환하는 부극성 디코딩부와; 정극성 및 부극성 디코딩부에 공통 접속되어 상기 극성제어신호 및 제1 선택제어신호에 응답하는 상기 k개씩의 화소신호를 상기 디멀티플렉서로 순차적으로 출력하는 멀티플렉서를 구비하는 것을 특징으로 한다.

- <41> 이와 달리, 다른 특징에 따른 상기 디지털-아날로그 변환 집적회로 각각은 타이밍제어부의 제어에 응답하여 샘플링신호를 순차적으로 출력하는 쉬프트 레지스터부와; 타이밍제어부의 제어와 샘플링신호에 응답하여 타이밍제어부로부터 입력되는 n개의 화소데이터들을 순차적으로 래치하고 동시에 출력하는 래치부와; 입력 감마전압을 이용하여 n개의 화소데이터를 정극성 및 부극성 비디오 동시에 변환하고 타이밍제어부의 극성제어신호에 응답하는 n개의 화소신호를 선택하여 출력하는 디지털-아날로그 변환부와; n개의 화소신호를 타이밍제어부의 제1 선택제어신호에 응답하여 적어도 2개의 출력단에 선택적으로 출력하는 디멀티플렉서와; 적어도 2개의 출력단 각각에 접속되어 n개의 화소신호를 타이밍제어부의 제2 선택제어신호에 응답하여 k개씩 시분할하여 출력하는 적어도 2개의 멀티플렉서를 구비하는 것을 특징으로 한다.

- <42> 그리고, 상기 디지털-아날로그 변환 집적회로 각각은 디지털-아날로그 변환 집적회로의 구성요소들 각각에 타이밍제어부로부터의 제어신호들과 화소데이터를 중계하여 공급하는 신호제어부와; 입력 감마 기준전압을 세분화하여 감마전압을 발생하는 감마 전압부를 추가로 구비하는 것을 특징으로 한다.

- <43> 상기 출력버퍼 집적회로들 각각은 n개의 데이터라인들 중 k개씩의 데이터라인들에 접속되어 상기 화소신호 홀딩 및 신호완충 기능을 하는 다수개의 출력버퍼부와; 디지털-아날로그 변환 집적회로로부터 k개씩 공급되는 화소신호를 상기 타이밍제어부의 선택제어신호에 응답하여 상기 다수개의 출력버퍼부에 순차적으로 공급하는 디멀티플렉서를 구비하는 것을 특징으로 한다.

- <44> 여기서, 상기 다수개의 출력버퍼부 각각은 k개의 데이터라인들에 각각 접속되는 k개의 출력버퍼들로 구성되고, 출력버퍼들 각각은 화소신호를 입력하여 홀딩하는 홀딩수단과; 타이밍제어부로부터의 제어신호에 응답하여 홀딩된 화소신호를 출력하는 스위칭수단과; 스위칭수단에 접속되어 신호완충 기능을 하는 전압 추종기를 구비하는 것을 특징으로 한다.

- <45> 상기 출력버퍼 집적회로를 실장한 테이프 캐리어 패키지는 상기 k개의 입력핀과 상기 n개의 출력핀 수를 갖는 것을 특징으로 한다.

- <46> 본 발명의 한 특징에 따른 액정표시장치의 데이터 구동 방법은 액정패널에 배치된 데이터라인들을 구동하기 위한 데이터 구동 장치의 구동 방법에 있어서, 데이터 구동 장치는 n개씩의 데이터라인들에 접속되어진 출력버퍼

집적회로들과, 적어도 2개의 출력버퍼 집적회로 입력단에 공통 접속된 디지털-아날로그 변환 집적회로들로 구성되고, 디지털-아날로그 변환 집적회로들 각각에 공급될 화소데이터를 n개씩의 화소데이터로 구성되는 적어도 2개의 구간으로 시분할하여 공급하는 단계와; 디지털-아날로그 변환 집적회로가 n개씩의 화소데이터를 아날로그 형태인 화소신호로 변환하고, 변환된 화소신호를 k개씩 시분할하여 공급하는 단계와; 적어도 2개의 출력버퍼 집적회로가 k개씩의 화소신호들을 순차적으로 입력하여 훌딩한 다음 동시에 신호완충시켜 데이터라인들에 공급하는 단계를 포함한다.

<47> 여기서, 상기 화소신호로 변환하는 단계는 n개의 화소데이터를 감마전압을 이용하여 정극성 및 부극성 화소신호로 변환하고, 외부로부터 입력되는 극성제어신호와 제1 선택제어신호에 응답하는 k개씩의 화소신호를 순차적으로 공급하는 단계와; k개의 화소신호를 외부로부터의 제2 선택제어신호에 응답하여 적어도 2개의 출력버퍼 집적회로 각각에 선택적으로 공급하는 단계를 포함하는 것을 특징으로 한다.

<48> 이와 달리, 상기 화소신호로 변환하는 단계는 n개의 화소데이터를 감마전압을 이용하여 정극성 및 부극성 화소신호로 변환하고, 외부로부터 입력되는 극성제어신호에 응답하는 n개의 화소신호를 공급하는 단계와; n개의 화소신호를 선택제어신호에 응답하여 k개씩의 화소데이터로 시분할하여 공급하는 단계를 포함하는 것을 특징으로 한다.

<49> 상기 목적 외에 본 발명의 다른 목적 및 이점들은 첨부한 도면들을 참조한 본 발명의 바람직한 실시예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

<50> 이하, 도 3 내지 도 8을 참조하여 본 발명의 바람직한 실시예에 대하여 설명하기로 한다.

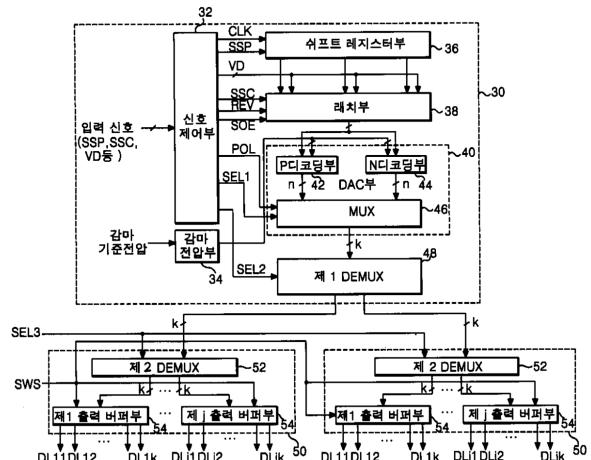

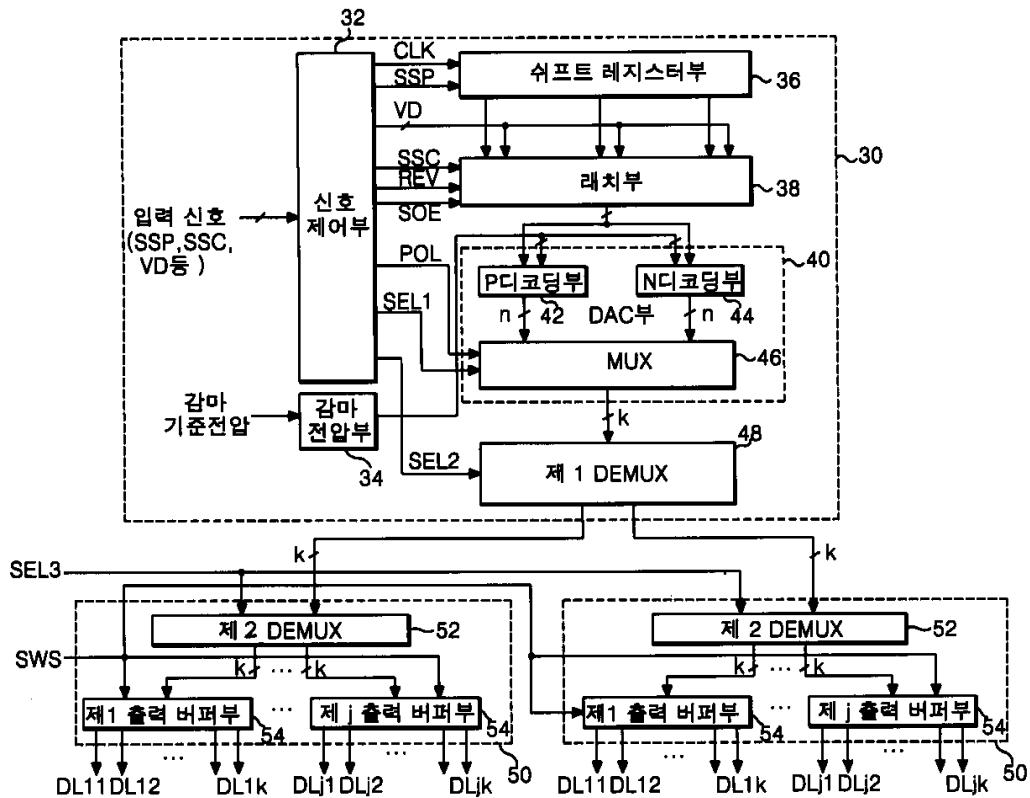

<51> 도 3은 본 발명의 실시 예에 따른 액정표시장치의 데이터 구동장치의 구성을 도시한 블록도이다. 도 3에 도시된 데이터 구동장치는 크게 DAC 기능을 하는 DAC 수단과 출력 버퍼링 기능을 하는 버퍼링 수단으로 분리되어 별도의 칩으로 집적화된다. 다시 말하여 데이터 구동장치는 DAC IC(30)와 출력버퍼 IC(50)로 분리되어 구성된다. 특히 하나의 DAC IC(30)에는 적어도 2개의 출력버퍼 IC(50)가 공통으로 접속된다. 그리고 DAC IC(30)는 적어도 2개의 구간으로 시분할되어 DAC 기능을 수행하게 된다. 여기서는 하나의 DAC IC(30)에 2개의 출력버퍼 IC(50)가 공통으로 접속된 경우를 예로 들어 설명하기로 한다.

<52> DAC IC(30)에는 2n개의 데이터라인들(DL11 내지 DL1n, DL21 내지 DL2n)에 공급되어질 2n개의 화소데이터가 n개씩 시분할되어 입력된다. DAC IC(30)는 입력되어진 n개의 화소데이터를 아날로그신호인 화소신호로 변환한다. 그리고 DAC IC(30)는 아날로그신호로 변환된 n개의 화소신호를 다시 k(<n>)개씩 분할하여 제1 및 제2 출력버퍼 IC(50)에 선택적으로 공급하게 된다. 이렇게 DAC IC(30)가 2n개의 화소데이터를 n개씩 분할하여 DAC 기능을 수행해야 하므로 그에 필요한 구동신호들은 종래 대비 2배의 주파수를 가지게 된다.

<53> 이를 위하여, DAC IC(30)는 순차적인 샘플링신호를 공급하는 쉬프트 레지스터부(36)와, 샘플링신호에 응답하여 화소데이터(VD)를 순차적으로 래치하여 동시에 출력하는 래치부(38), 래치부(38)로부터의 화소데이터(VD)를 화소신호로 변환하는 DAC부(40)와, DAC(40)로부터의 화소신호를 2개의 출력버퍼 IC(50)에 선택적으로 공급하는 제1 디멀티플렉서(DEMUX; 48)를 구비한다. 또한, DAC IC(30)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 화소데이터(VD)를 중계하는 신호 제어부(32)와, DAC부(40)에서 필요로 하는 정극성 및 부극성 감마전압들을 공급하는 감마 전압부(34)를 추가로 구비한다.

<54> 신호제어부(32)는 타이밍 제어부로부터의 각종 제어신호들(CLK, SSP, SSC, SOE, REV, POL 등)과 화소데이터(VD)를 해당 구성요소들로 출력되게 제어한다. 이 경우, 타이밍 제어부는 신호제어부(32)를 통해 공급되는 각종 제어신호들(CLK, SSP, SSC, SOE, REV, POL 등) 및 화소데이터(VD)가 종래 대비 2배의 주파수를 가지게 한다. 특히, 타이밍 제어부는 2n개의 데이터라인들(DL11 내지 DL1n, DL21 내지 DL2n)에 해당되는 2n개의 화소데이터(VD)를 2개의 구간으로 시분할하여 n개씩 순차적으로 공급되게 한다.

<55> 감마 전압부(34)는 감마 기준전압 발생부(도시하지 않음)로부터 입력되는 다수개의 감마 기준전압을 그레이별로 세분화하여 출력한다.

<56> 쉬프트 레지스터부(36)에 포함되는 n개의 쉬프트 레지스터들은 신호제어부(32)로부터의 소스 스타트 펄스(SSP)를 클럭신호(CLK)에 따라 순차적으로 쉬프트시켜 샘플링신호로 출력한다. 이 경우, 쉬프트 레지스터부(36)는 주파수가 2배로 증가된 소스 스타트 펄스(SSP)와 클럭신호(CLK)에 응답하여 종래의 2배 속도로 샘플링신호를 출력하게 된다.

<57> 래치부(38)에 포함되는 n개의 래치들은 쉬프트 레지스터부(36)의 샘플링신호에 응답하여 신호 제어부(32)로부터

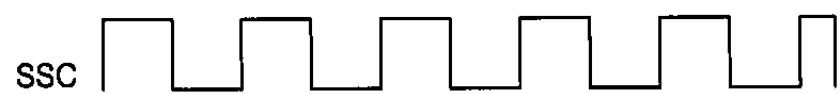

의 화소데이터(VD)를 순차적으로 샘플링하여 래치하게 된다. 이때 래치들은 신호 제어부(32)로부터 공급되는 소스 샘플링 클럭신호(SSC)의 라이징 또는 폴링 에지에서 화소데이터(VD)를 샘플링하게 된다. 이어서 래치들은 신호 제어부(32)로부터 공급되는 소스 출력 이네이블신호(SOE)에 응답하여 래치된 화소데이터들(VD)을 동시에 출력한다. 이 경우, 래치들은 데이터반전 선택신호(REV)에 응답하여 트랜지션 비트수가 줄어들게끔 변조된 화소데이터(VD)들은 복원시켜 출력하게 된다. 이는 타이밍 제어부에서 데이터전송시 전자기적 간섭(EMI)을 최소화하기 위하여 트랜지션되는 비트수가 기준치를 넘어서는 화소데이터(VD)들은 트랜지션 비트수가 줄어들게끔 변조하여 공급하기 때문이다. 이러한 래치부(38)에 공급되는 소스 샘플링 클럭신호(SSC)와 소스 출력 이네이블신호(SOE)는 도 4a 및 도 4b에 "NEW SSC"와 "NEW SOE"로 도시한 바와 같이 도 2에 도시된 종래의 래치부(16)에 공급되는 "SSC" 및 "SOE"와 대비하여 2배의 주파수를 가지고 공급된다.

<58> DAC부(40)는 래치부(38)로부터의 n개의 화소데이터를 동시에 정극성 및 부극성 화소신호로 변환하고 극성제어신호(POL) 및 제1 선택제어신호(SEL1)에 응답하여 k개씩 분리하여 출력하게 된다. 이를 위하여, DAC부(40)는 래치부(38)에 공통 접속된 P(Positive) 디코딩부(42) 및 N(Negative) 디코딩부(44)와, P 디코딩부(42) 및 N 디코딩부(44)의 출력신호를 선택하기 위한 멀티플렉서(MUX; 46)를 구비한다.

<59> P 디코딩부(42)에 포함되는 n개의 P 디코더들은 래치부(38)로부터 동시에 입력되는 n개의 화소데이터들을 감마전압부(34)로부터의 정극성 감마전압들을 이용하여 정극성 화소신호로 변환하게 된다. N 디코딩부(44)에 포함되는 n개의 N 디코더들은 래치부(38)로부터 동시에 입력되는 n개의 화소데이터들을 감마전압부(34)로부터의 부극성 감마전압들을 이용하여 부극성 화소신호로 변환하게 된다. 멀티플렉서(46)는 신호제어부(32)로부터의 극성제어신호(POL)에 응답하여 P 디코더(42)로부터의 정극성 화소신호 또는 N 디코더(44)로부터의 부극성 화소신호를 선택함과 동시에 제1 선택제어신호(SEL1)에 응답하여 n개의 화소신호를 k개씩 나누어 출력하게 된다. 이 경우, 제1 선택제어신호(SEL1)의 비트수는 n개의 화소신호를 분할하는 회수(j)에 따라 정해진다. 예를 들어, n개의 화소신호를 8(j=8)분할하여 출력하는 경우 제1 선택제어신호(SEL1)는 3비트로 구성되면 충분하다. 이와 같이, DAC부(40)는 2n개의 화소데이터를 처리하기 위하여 종래의 DAC부(18)와 대비하여 2배의 속도로 n개씩의 화소데이터를 화소신호로 변환하고 n개의 화소신호를 그보다 작은 k개씩 분리하여 출력하게 된다.

<60> 제1 디멀티플렉서(48)는 멀티플렉서(46)로부터 입력되는 k개씩의 화소신호를 신호 제어부(32)로부터 입력되는 제2 선택제어신호(SEL2)에 응답하여 제1 출력버퍼 IC(50) 또는 제2 출력버퍼 IC(50)로 출력하게 된다. 이 경우, 제2 선택제어신호(SEL2)도 n개의 화소신호가 분할된 회수(j)에 따라 정해지게 되므로 상기 제1 선택제어신호(SEL1)와 동일한 비트수를 갖게 된다.

<61> 제1 및 제2 출력버퍼 IC(50) 각각은 DAC IC(30)로부터 k개씩 입력되는 화소신호를 샘플링한 후 훌딩하여 n개의 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjk)에 동시에 출력하게 된다. 이를 위하여, 제1 및 제2 출력버퍼 IC(50) 각각은 제2 디멀티플렉서(52)와 제1 내지 제j 출력버퍼부(54)로 구성된다.

<62> 제2 디멀티플렉서(52)는 제1 디멀티플렉서(48)로부터 k개씩 입력되는 화소신호를 타이밍 제어부(도시하지 않음)로부터 공급되는 제3 선택제어신호(SEL3)에 응답하여 제1 내지 제j 출력버퍼부(54)에 순차적으로 공급되게 한다. 이 경우, 제3 선택제어신호(SEL3) 역시 상기 제1 및 제2 선택제어신호(SEL1, SEL2)와 동일하게 n개의 화소신호가 분할된 횟수(j)에 해당되는 비트수를 갖게 된다.

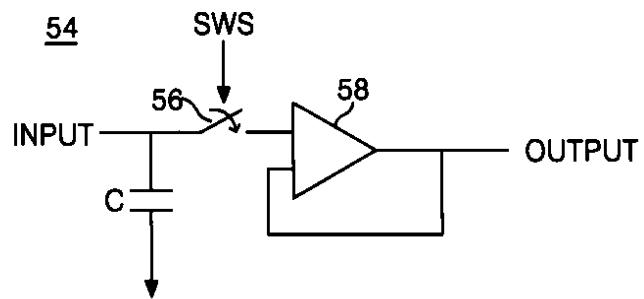

<63> 제1 내지 제j 출력버퍼부(54)는 제2 디멀티플렉서(52)로부터 공급되는 k개씩의 화소신호를 순차적으로 입력하여 훌딩시킨다. 이어서, 제1 내지 제j 출력버퍼부(54)는 타이밍 제어부로부터의 스위치제어신호(SWS)에 응답하여 훌딩된 k개씩의 화소신호를 동시에 해당 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 공급하게 된다. 이러한 제1 내지 제j 출력버퍼부(54) 각각은 해당 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 일대일로 접속되는 k개의 출력버퍼들로 구성된다. k개의 출력버퍼들 각각은 도 5에 도시된 바와 같이 입력 화소신호(INPUT)를 충전하여 훌딩하기 위한 캐패시터(C)와, 타이밍 제어부로부터의 스위치제어신호(SWS)에 응답하여 캐패시터(C)에 훌딩된 화소신호가 출력되게 하는 스위칭소자(56)와, 스위칭소자(56)에 접속되어 화소신호를 신호완충하여 출력 화소신호(OUTPUT)로 출력하기 위한 전압 추종기(58)로 구성된다.

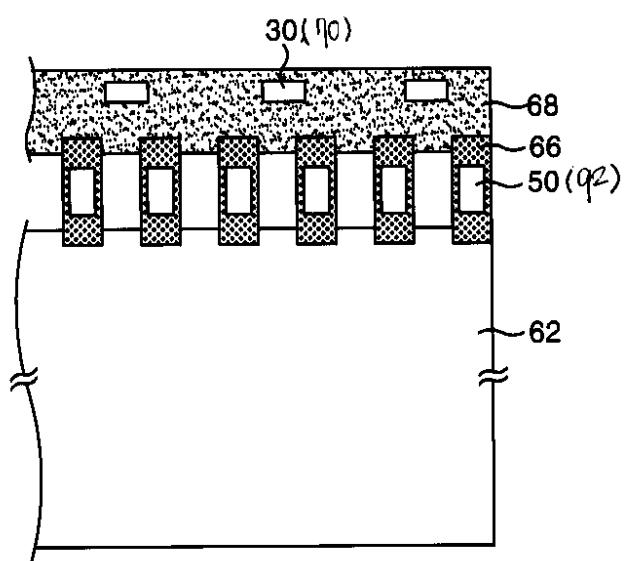

<64> 이러한 구성을 가지는 본 발명의 실시 예에 따른 DAC IC(30)는 도 6에 도시된 바와 같이 데이터 PCB(68) 상에, 출력버퍼 IC(50)들은 TCP(66) 상에 분리되어 실장되어진다. 데이터 PCB(68)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 데이터 신호들을 DAC IC들(30)로 전송함과 아울러, DAC IC(30)로부터의 화소신호들을 TCP(66)를 경유하여 출력버퍼 IC들(50)로 전송하는 역할을 한다. TCP(66)는 액정패널(62)의 상단부에 마련된 데이터 패드들과 전기적으로 접속됨과 아울러 데이터 PCB(68)에 마련된 출력 패드들과 전기적으로 접속된다.

- <65> 이와 같이 TCP(66) 상에는 버퍼링 기능만을 하는 단순구성의 출력버퍼 IC(50)만이 실장됨으로써 TCP(66) 불량이 발생하는 경우 출력버퍼 IC(50)만 손실을 입게 된다. 이 결과 종래의 TCP(66) 불량으로 고가의 데이터 드라이브 IC를 사용할 수 없게 되어 초래되었던 경제적인 손실을 현저하게 줄일 수 있게 된다. 또한, DAC IC(30)는 시분할 구동되어 적어도 2개의 출력버퍼 IC(50)에 화소신호를 공급하게 된다. 이에 따라 DAC IC(30)의 수를 종래보다 적어도 1/2로 줄일 수 있게 되므로 제조단가를 낮출 수 있게 된다.

- <66> 특히, DAC IC(30)의 DAC부(40)에서 n개의 화소신호를 j개로 시분할하여 k개씩 공급함에 따라 출력버퍼 IC(50) 각각의 입력핀 수를 n개의 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 접속되는 출력핀 수(n) 보다 작은 k개로 줄일 수 있게 된다. 이에 따라, 출력버퍼 IC(50)가 실장되는 TCP(66)의 입력핀 수도 줄어들게 되므로 TCP(66)의 입력핀과 접속되는 데이터 PCB(68)의 출력패드의 피치를 확보하는 것이 용이해지게 된다. 다시 말하여, 본 발명에서는 DAC IC(30)에서 출력된 화소신호를 데이터 PCB(68) 및 TCP(66)를 경유하여 출력버퍼 IC(50)로 전송함에 따라 데이터 PCB(68)에는 디지털형태의 화소데이터를 전송하는 종래의 데이터 PCB보다 상대적으로 많은 신호전송라인들과 출력패드들이 필요하게 된다. 이 결과, 일반적으로 데이터 PCB(68) 상에 출력패드의 피치를 확보하기가 어려웠으나 본 발명에서는 화소신호를 시분할 구동하여 출력패드를 줄임으로써 출력패드 피치 확보가 용이해지게 된다.

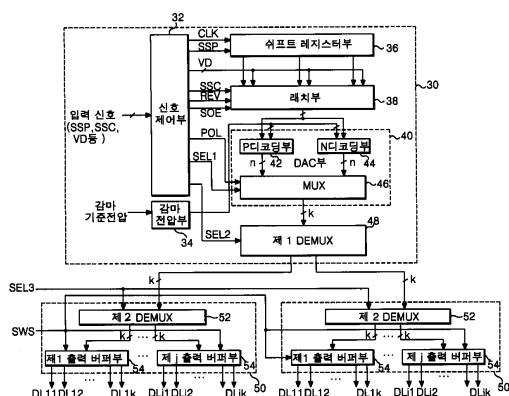

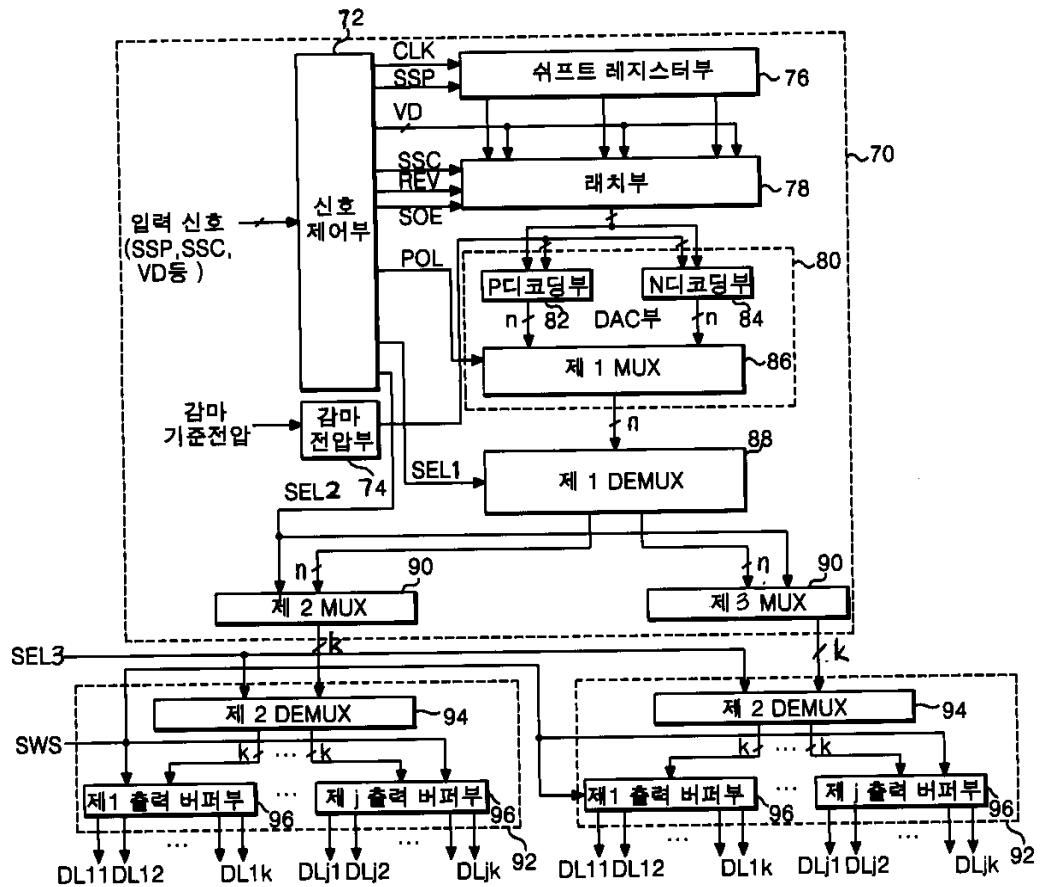

- <67> 도 7은 본 발명의 다른 실시 예에 따른 액정표시장치의 데이터 구동장치의 구성을 도시한 블록도이다. 도 7에 도시된 데이터 구동장치는 도 3에 도시된 데이터 구동장치와 대비하여 도 3의 멀티플렉서(46)가 가지는 n개 화소신호의 분할기능을 수행하기 위한 2개의 제2 멀티플렉서(90)가 추가된 것을 제외하고는 동일한 구성요소들을 구비한다. 하나의 DAC IC(70)에는 적어도 2개의 출력버퍼 IC(92)가 공통으로 접속된다.

- <68> DAC IC(70)에는 2n개의 데이터라인들(DL11 내지 DL1n, DL21 내지 DL2n)에 공급되어질 2n개의 화소데이터가 n개씩 시분할되어 입력된다. DAC IC(70)는 입력되어진 n개의 화소데이터를 아날로그신호인 화소신호로 변환한다. 그리고 DAC IC(70)는 아날로그신호로 변환된 n개의 화소신호를 다시 k(<n)개씩 분할하여 제1 및 제2 출력버퍼 IC(92)에 선택적으로 공급하게 된다. 이렇게 DAC IC(70)가 2n개의 화소데이터를 n개씩 분할하여 DAC 기능을 수행해야 하므로 그에 필요한 구동신호들은 종래 대비 2배의 주파수를 가지게 된다.

- <69> 이를 위하여, DAC IC(70)는 순차적인 샘플링신호를 공급하는 쉬프트 레지스터부(76)와, 샘플링신호에 응답하여 화소데이터(VD)를 순차적으로 래치하여 동시에 출력하는 래치부(78)와, 래치부(78)로부터의 화소데이터(VD)를 화소신호로 변환하는 DAC부(80)와, DAC부(80)로부터의 화소신호를 2개의 멀티플렉서(90)에 선택적으로 공급하는 제1 디멀티플렉서(DEMUX; 88)와, 제1 디멀티플렉서(88)로부터의 화소신호를 시분할하여 제1 및 제2 출력버퍼 IC(92) 각각에 공급하는 2개의 제2 멀티플렉서(90)를 구비한다. 또한, DAC IC(70)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 화소데이터(VD)를 중계하는 신호 제어부(72)와, DAC부(80)에서 필요로 하는 정극성 및 부극성 감마전압들을 공급하는 감마 전압부(74)를 추가로 구비한다.

- <70> 신호제어부(72)는 타이밍 제어부로부터의 각종 제어신호들(CLK, SSP, SSC, SOE, REV, POL 등)과 화소데이터(VD)를 해당 구성요소들로 출력되게 제어한다. 이 경우, 타이밍 제어부는 신호제어부(72)를 통해 공급되는 각종 제어신호들(CLK, SSP, SSC, SOE, REV, POL 등) 및 화소데이터(VD)가 종래 대비 2배의 주파수를 가지게 한다. 특히, 타이밍 제어부는 2n개의 데이터라인들(DL11 내지 DL1n, DL21 내지 DL2n)에 해당되는 2n개의 화소데이터(VD)를 2개의 구간으로 시분할하여 n개씩 순차적으로 공급되게 한다.

- <71> 감마 전압부(74)는 감마 기준전압 발생부(도시하지 않음)로부터 입력되는 다수개의 감마 기준전압을 그레이별로 세분화하여 출력한다.

- <72> 쉬프트 레지스터부(76)에 포함되는 n개의 쉬프트 레지스터들은 신호제어부(72)로부터의 소스 스타트 펄스(SSP)를 클럭신호(CLK)에 따라 순차적으로 쉬프트시켜 샘플링신호로 출력한다. 이 경우, 쉬프트 레지스터부(76)는 주파수가 2배로 증가된 소스 스타트 펄스(SSP)와 클럭신호(CLK)에 응답하여 종래 보다 2배 속도로 샘플링신호를 출력하게 된다.

- <73> 래치부(78)에 포함되는 n개의 래치들은 쉬프트 레지스터부(76)의 샘플링신호에 응답하여 신호 제어부(72)로부터의 화소데이터(VD)를 순차적으로 샘플링하여 래치하게 된다. 이때 래치들은 신호 제어부(72)로부터 공급되는 소스 샘플링 클럭신호(SSC)의 라이징 또는 폴링 에지에서 화소데이터(VD)를 샘플링하게 된다. 이어서 래치들은 신호 제어부(72)로부터 공급되는 소스 출력 이네이블신호(SOE)에 응답하여 래치된 화소데이터들(VD)을 동시에 출력한다. 이 경우, 래치들은 데이터반전 선택신호(REV)에 응답하여 트랜지션 비트수가 줄어들게끔 변조된 화소데이터(VD)들은 복원시켜 출력하게 된다. 이는 타이밍 제어부에서 데이터전송시 전자기적 간섭(EMI)을 최소

화하기 위하여 트랜지션되는 비트수가 기준치를 넘어서는 화소데이터(VD)들은 트랜지션 비트수가 줄어들게끔 변조하여 공급하기 때문이다. 이러한 래치부(78)에 공급되는 소스 샘플링 클럭신호(SSC)와 소스 출력 이네이블신호(SOE)는 도 4a 및 도 4b에 "NEW SSC"와 "NEW SOE"로 도시한 바와 같이 도 2에 도시된 종래의 래치부(16)에 공급되는 "SSC" 및 "SOE"와 대비하여 2배의 주파수를 가지고 공급된다.

<74> DAC부(80)는 래치부(78)로부터의 n개의 화소데이터를 동시에 정극성 및 부극성 화소신호로 변환하여 출력하게 된다. 이를 위하여, DAC부(80)는 래치부(78)에 공통 접속된 P(Positive) 디코딩부(82) 및 N(Negative) 디코딩부(84)와, P 디코딩부(82) 및 N 디코딩부(84)의 출력신호를 선택하기 위한 제1 멀티플렉서(86)를 구비한다.

<75> P 디코딩부(82)에 포함되는 n개의 P 디코더들은 래치부(78)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(74)로부터의 정극성 감마전압들을 이용하여 정극성 화소신호로 변환하게 된다. N 디코딩부(84)에 포함되는 n개의 N 디코더들은 래치부(78)로부터 동시에 입력되는 n개의 화소데이터들을 감마 전압부(74)로부터의 부극성 감마전압들을 이용하여 부극성 화소신호로 변환하게 된다. 제1 멀티플렉서(86)는 신호제어부(72)로부터의 극성제어신호(POL)에 응답하여 P 디코더(42)로부터의 정극성 화소신호 또는 N 디코더(44)로부터의 부극성 화소신호를 선택하여 n개씩 출력하게 된다. 이와 같이, DAC부(80)는 2n개의 화소데이터를 처리하기 위하여 종래의 DAC부(18)와 대비하여 2배의 속도로 n개씩의 화소데이터를 화소신호로 변환하여 출력하게 된다.

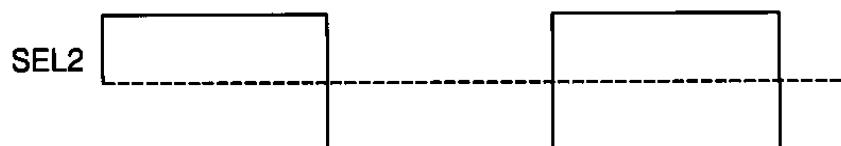

<76> 제1 디멀티플렉서(88)는 제1 멀티플렉서(46)로부터 입력되는 n개의 화소신호를 도 8에 도시된 바와 같이 신호 제어부(72)로부터 입력되는 제1 선택제어신호(SEL1)에 응답하여 제2 및 제3 멀티플렉서(90)에 선택적으로 출력하게 된다. 제1 선택제어신호(SEL1)는 래치부(78)에 공급되는 소스 출력 이네이블신호(SOE)의 한주기마다 논리 값이 반전됨으로서 n개씩의 화소신호가 2개의 제2 멀티플렉서(90)에 선택적으로 출력되게 한다.

<77> 제2 및 제3 멀티플렉서(90) 각각은 제1 디멀티플렉서(88)로부터 n개씩 공급되는 화소신호를 신호 제어부(72)로부터의 제2 선택제어신호(SEL2)에 응답하여 k개씩 나누어 출력하게 된다. 이 경우, 제2 선택제어신호(SEL2)의 비트수는 n개의 화소신호를 분할하는 회수(j)에 따라 정해진다. 예를 들어, n개의 화소신호를 8(j=8)분할하여 출력하는 경우 제2 선택제어신호(SEL2)는 3비트로 구성되면 충분하다.

<78> 제1 및 제2 출력버퍼 IC(92) 각각은 DAC IC(70)의 제2 및 제3 멀티플렉서(90) 각각으로부터 k개씩 입력되는 화소신호를 샘플링한 후 훌딩하여 n개의 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjk)에 동시에 출력하게 된다. 이를 위하여, 제1 및 제2 출력버퍼 IC(92) 각각은 제2 디멀티플렉서(94)와 제1 내지 제j 출력버퍼부(96)로 구성된다.

<79> 제2 디멀티플렉서(94)는 제2 및 제3 멀티플렉서(90) 각각으로부터 k개씩 입력되는 화소신호를 타이밍제어부(도시하지 않음)로부터 공급되는 제3 선택제어신호(SEL3)에 응답하여 제1 내지 제j 출력버퍼부(96)에 순차적으로 공급되게 한다. 이 경우, 제3 선택제어신호(SEL3)는 상기 제1 선택제어신호(SEL1)와 동일하게 n개의 화소신호가 분할된 횟수(j)에 해당되는 비트수를 갖게 된다.

<80> 제1 내지 제j 출력버퍼부(96)는 제2 디멀티플렉서(94)로부터 공급되는 k개씩의 화소신호를 순차적으로 입력하여 훌딩시킨다. 이어서, 제1 내지 제j 출력버퍼부(96)는 타이밍 제어부로부터의 스위치제어신호(SWS)에 응답하여 훌딩된 k개씩의 화소데이터를 동시에 해당 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 공급하게 된다. 이러한 제1 내지 제j 출력버퍼부(96) 각각은 해당 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 일대일로 접속되는 k개의 출력버퍼들로 구성된다. k개의 출력버퍼들 각각은 도 5에 도시된 바와 같이 입력 화소신호(INPUT)를 충전하여 훌딩하기 위한 캐페시터(C)와, 타이밍 제어부로부터의 스위치제어신호(SWS)에 응답하여 캐페시터(C)에 훌딩된 화소신호가 출력되게 하는 스위칭소자(56)와, 스위칭소자(56)에 접속되어 화소신호를 신호완충하여 출력 화소신호(OUTPUT)로 출력하기 위한 전압 추종기(58)로 구성된다.

<81> 이러한 구성을 가지는 본 발명의 실시 예에 따른 DAC IC(70)는 도 6에 도시된 바와 같이 데이터 PCB(68) 상에, 출력버퍼 IC(92)들은 TCP(66) 상에 분리되어 실장되어진다. 데이터 PCB(68)는 타이밍 제어부(도시하지 않음)로부터 공급되는 각종 제어신호들과 데이터 신호들을 DAC IC들(70)로 전송함과 아울러, DAC IC(70)로부터의 화소신호들을 TCP(66)를 경유하여 출력버퍼 IC들(92)로 전송하는 역할을 한다. TCP(66)는 액정패널(62)의 상단부에 마련된 데이터 패드들과 전기적으로 접속됨과 아울러 데이터 PCB(68)에 마련된 출력 패드들과 전기적으로 접속된다.

<82> 이와 같이 TCP(66) 상에는 버퍼링 기능만을 하는 단순구성의 출력버퍼 IC(92)만이 실장됨으로써 TCP(66) 불량이 발생하는 경우 출력버퍼 IC(92)만 손실을 입게 된다. 이 결과 종래의 TCP(66) 불량으로 고가의 데이터 드라이브 IC를 사용할 수 없게 되어 초래되었던 경제적인 손실을 현저하게 줄일 수 있게 된다. 또한, DAC IC(70)는

시분할 구동되어 적어도 2개의 출력버퍼 IC(92)에 화소신호를 공급하게 된다. 이에 따라 DAC IC(70)의 수를 종래보다 적어도 1/2로 줄일 수 있게 되므로 제조단가를 낮출 수 있게 된다.

<83> 특히, DAC IC(70)에서 n개의 화소신호를 j개로 시분할하여 k개씩 공급함에 따라 출력버퍼 IC(92) 각각의 입력핀 수를 n개의 데이터라인들(DL11 내지 DL1k, ..., DLj1 내지 DLjn)에 접속되는 출력핀 수(n) 보다 작은 k개로 줄일 수 있게 된다. 이에 따라, 출력버퍼 IC(92)가 실장되는 TCP(66)의 입력핀 수도 줄어들게 되므로 TCP(66)의 입력핀과 접속되는 데이터 PCB(68)의 출력패드들의 피치를 확보하는 것이 용이해지게 된다. 다시 말하여, 본 발명에서는 DAC IC(70)에서 출력된 화소신호를 데이터 PCB(68) 및 TCP(66)를 경유하여 출력버퍼 IC(92)로 전송함에 따라 데이터 PCB(68)에는 디지털형태의 화소데이터를 전송하는 종래의 데이터 PCB보다 상대적으로 많은 신호 전송라인들과 출력패드들이 필요하게 된다. 이 결과, 일반적인 데이터 PCB(68) 상에 출력패드의 피치를 확보하기가 어려웠으나 본 발명에서는 화소신호를 시분할 구동하여 출력패드를 줄임으로써 출력패드 피치 확보가 용이해지게 된다.

### 발명의 효과

<84> 상술한 바와 같이, 본 발명에 따른 액정표시장치의 데이터 구동 장치 및 방법에서는 DAC 기능을 하는 DAC 수단과 출력버퍼링 기능을 하는 출력 버퍼링 수단을 분리하여 별도의 침으로 접적화함으로써 불량율이 높은 TCP 상에는 단순구성의 출력버퍼 IC만을 실장할 수 있게 된다. 이에 따라, 종래의 TCP 불량으로 인해 고가의 데이터 드라이브 IC도 사용할 수 없게 되어 초래되었던 손실을 크게 줄일 수 있게 된다.

<85> 또한, 본 발명에 따른 액정표시장치의 데이터 구동 장치 및 방법에서는 DAC IC를 보다 높은 주파수를 가지는 구동신호들을 이용하여 시분할 구동하여 하나의 DAC IC에 적어도 2개의 출력버퍼 IC가 공통으로 접속되게 함으로써 DAC IC의 수를 줄일 수 있게 되므로 제조단가를 줄일 수 있게 된다.

<86> 나아가, 본 발명에 따른 액정표시장치의 데이터 구동 장치 및 방법에서는 DAC IC에서 아날로그신호로 변환되어진 화소신호도 다수개로 시분할하여 공급함에 따라 출력버퍼 IC 각각의 입력핀 수를 줄일 수 있게 된다. 이에 따라, 출력버퍼 IC가 실장되는 TCP의 입력핀 수를 줄일 수 있게 되므로 TCP의 입력핀과 접속되는 데이터 PCB의 출력패드 피치 확보가 용이해지게 된다.

<87> 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 도면의 간단한 설명

- <1> 도 1은 종래 액정표시장치의 데이터 구동블록을 개략적으로 도시한 도면.

- <2> 도 2는 도 1에 도시된 데이터 드라이브 접적회로의 상세 구성을 도시한 블록도.

- <3> 도 3은 본 발명의 실시 예에 따른 액정표시장치의 데이터 드라이버의 구성을 도시한 블록도.

- <4> 도 4a 내지 도 4b는 도 2에 도시된 래치부와 도 3에 도시된 래치부의 구동파형을 비교하여 도시한 도면

- <5> 도 5는 도 3에 도시된 출력버퍼부에 포함되는 출력버퍼의 구성을 도시한 도면.

- <6> 도 6은 도 3에 도시된 데이터 드라이버를 포함하는 액정표시장치의 데이터 구동블록을 개략적으로 도시한 도면.

- <7> 도 7은 본 발명의 다른 실시 예에 따른 액정표시장치의 데이터 구동장치를 도시한 블록도.

- <8> 도 8은 도 7에 도시된 제1 디멀티플렉서의 구동파형을 도시한 도면.

- <9> <도면의 주요부분에 대한 설명>

- <10> 2, 62 : 액정패널 4 : 데이터 드라이브 접적회로(IC)

- <11> 6, 66 : 테이프 캐리어 패키지(TCP) 8, 68 : 데이터 인쇄회로기판(PCB)

- <12> 10, 32, 72 : 신호 제어부 12, 34, 74 : 감마 전압부

- <13> 14, 36, 76 : 쉬프터 레지스터부 16, 38, 78 : 래치부

- <14> 18, 40, 80 : 디지털-아날로그 변환(DAC)부

<15> 20, 42, 82 : P 디코딩부 22, 44, 84 : N 디코딩부

<16> 24, 46, 86, 90 : 멀티플렉서(MUX) 26, 54, 96 : 출력 버퍼부

<17> 30, 70 : 디지털-아날로그 집적회로

<18> 48, 52, 88, 94 : 디멀티플렉서(DEMUX) 50, 92 : 출력버퍼 집적회로

<19> 56 : 스위치 58 : 전압추종기

## 도면

도면1

## 도면2

도면3

도면4a

도면4b

도면5

도면6

## 도면7

도면8

|                |                                                  |         |            |

|----------------|--------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于驱动液晶显示装置的装置和方法                                 |         |            |

| 公开(公告)号        | KR100815898B1                                    | 公开(公告)日 | 2008-03-21 |

| 申请号            | KR1020010063208                                  | 申请日     | 2001-10-13 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                        |         |            |

| [标]发明人         | LEE SEOKWOO<br>이석우<br>CHOI SUKYUNG<br>최수경        |         |            |

| 发明人            | 이석우<br>최수경                                       |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 H03M1/66             |         |            |

| CPC分类号         | G09G3/3688 G09G2310/027 G09G3/2011 G09G2310/0297 |         |            |

| 代理人(译)         | 金勇<br>年轻的小公园                                     |         |            |

| 其他公开文献         | KR1020030031282A                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                        |         |            |

### 摘要(译)

用于液晶显示器的数据驱动设备包括数模转换器部分，用于将输入像素数据转换为多个像素信号并将转换后的像素数据信号时分为时分像素信号，其中转换后的像素信号大于时分像素信号，至少两个输出缓冲器部分，用于依次从数模转换器部分接收像素信号，缓冲时分像素信号，并输出缓冲时间划分的像素信号到多条数据线，多个输出缓冲器部分中的至少两个共同连接到数模转换器部分，以及定时控制器，用于控制数模转换器部分和输出缓冲器部分，并将提供给数模转换器部分的像素数据时分到至少两个区域中，以将时分像素数据顺序地提供给数据线。