(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년11월21일

(11) 등록번호 10-0870005

(24) 등록일자 2008년11월17일

(51) Int. Cl.

G02F 1/1343 (2006.01)

(21) 출원번호 10-2002-0012121

(22) 출원일자 2002년03월07일

심사청구일자 2007년03월07일

(65) 공개번호 10-2003-0072859

(43) 공개일자 2003년09월19일

(56) 선행기술조사문현

KR1020000059783 A\*

(뒷면에 계속)

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

이백운

경기도 성남시 분당구 야탑동 331번지 동부아파트 110

동 802호

김희섭

경기도 화성군 태안읍 반월리 865-1번지 신영통 현대아

파트 110동 304호

(뒷면에 계속)

(74) 대리인

팬코리아 특허법인

전체 청구항 수 : 총 6 항

심사관 : 윤성주

(54) 액정 표시 장치

**(57) 요약**

절연 기판 위에 게이트선이 형성되어 있고, 게이트선과 교차하도록 데이터선이 형성되어 있다. 게이트선과 데이터선은 서로 절연되어 있으며 이들이 교차하여 이루는 화소 영역에는 게이트 전극, 소스 전극 및 드레인 전극의 3단자를 가지는 박막 트랜지스터가 2개 형성되어 있고, 방향 제어 전극과 화소 전극이 각각 형성되어 있다. 이 때, 두 개의 박막 트랜지스터 중 제1 박막 트랜지스터는 화소 전극을 스위칭하기 위한 것이고, 제2 박막 트랜지스터는 방향 제어 전극을 스위칭하기 위한 것이다. 제1 박막 트랜지스터의 게이트 전극, 소스 전극 및 드레인 전극은 각각 해당 화소단의 게이트선, 데이터선 및 화소 전극에 연결되어 있고, 제2 박막 트랜지스터의 게이트 전극, 소스 전극 및 드레인 전극은 각각 전단의 게이트선 및 데이터선에 연결되어 있다. 방향 제어 전극은 액정 분자의 선경사(pre-tilt)를 제어하기 위한 방향 제어 전압을 인가받아 대향 전극과의 사이에 방향 제어 전계를 형성한다.

**대 표 도 - 도1**

(72) 발명자

**홍성규**

경기도수원시팔달구영통동955-1황골주공아파트136

동1806호

**신경주**

경기도용인시기흥읍보라리289-12삼정선비마을102

동504호

**양영철**

경기도군포시금정동주공아파트2단지220동1201호

(56) 선행기술조사문현

KR1020020000662 A\*

KR1020010007523 A

KR1020000061368 A

KR1020020013759 A

US 6335771 B1

US 6078367 A

US 6335776 A

US 2001-00242441 A1

\*는 심사관에 의하여 인용된 문현

---

### 특허청구의 범위

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

제1 절연 기판,

상기 제1 절연 기판 위에 형성되어 있는 제1 배선,

상기 제1 절연 기판 위에 형성되어 있으며 상기 제1 배선과 절연되어 교차하고 있는 제2 배선,

상기 제1 배선과 상기 제2 배선이 교차하여 정의하는 화소 영역마다 형성되어 있으며 개구부를 가지는 화소 전극,

상기 제1 배선, 상기 제2 배선 및 상기 화소 전극과 연결되어 있는 제1 스위칭 소자,

상기 화소 전극의 개구부와 중첩하는 방향 제어 전극,

상기 방향 제어 전극에 신호 전압을 스위칭하는 제2 스위칭 소자,

상기 방향 제어 전극과 상기 화소 전극 사이를 절연시키는 절연막,

상기 제1 절연 기판과 대향하고 있는 제2 절연 기판,

상기 제2 절연 기판 위에 형성되어 있는 대향 전극,

상기 제1 절연 기판과 상기 제2 절연 기판 사이에 주입되어 있는 액정층

을 포함하고, 상기 대향 전극에 대한 상기 화소 전극의 전압을  $V_p$ , 상기 대향 전극에 대한 상기 방향 제어 전극의 전압을  $V_{DCE}$ , 상기 액정층의 유전율과 두께를 각각  $\epsilon$ ,  $d$ , 상기 절연막의 유전율과 두께를 각각  $\epsilon'$ ,  $d'$ 이라 할 때,  $V_{DCE} \geq V_p \times (1 + \frac{\epsilon d'}{\epsilon' d})$  를 만족하는 액정 표시 장치.

### 청구항 13

제12항에서,

상기 제2 스위칭 소자는 상기 제1 스위칭 소자보다 먼저 턴온되었다가 상기 제1 스위칭 소자가 턴온되기 이전에 턴오프되는 액정 표시 장치.

### 청구항 14

제12항 또는 제13항에서,

상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 3단자 소자인 박막 트랜지스터이고, 상기 제2 스위칭 소자의 3단자는 각각 상기 제1 배선, 상기 제2 배선 및 상기 방향 제어 전극에 연결되어 있으며, 상기 제2 스위칭 소자가 연결되는 제1 배선은 상기 제1 스위칭 소자가 연결되는 제1 배선의 전단 배선인 액정 표시 장치.

### 청구항 15

제14항에서,

상기 대향 전극과 상기 화소 전극 사이의 정전 용량을  $C_{LC}$ , 상기 방향 제어 전극과 상기 화소 전극 사이의 정전 용량을  $C_{DCE}$ , 전단의 화소 전극에 인가되는 전압을  $V_{n-1}$ 이라 하면,  $\frac{C_{LC}}{2C_{DCE}+C_{LC}} |V_p + V_{n-1}| > \frac{\epsilon d'}{\epsilon' d} |V_p|$  를 만족하는 액정 표시 장치.

### 청구항 16

제14항에서,

하나의 상기 화소 영역 내에 포함되어 있는 상기 제1 및 제2 스위칭 소자는 동일한 상기 제2 배선에 연결되어 있는 액정 표시 장치.

### 청구항 17

제14항에서,

하나의 상기 화소 영역 내에 포함되어 있는 상기 제1 및 제2 스위칭 소자는 상기 화소 영역을 정의하는 두 개의 상기 제2 배선에 각각 연결되어 있는 액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<11> 본 발명은 액정 표시 장치에 관한 것으로서, 특히 광시야각을 얻기 위하여 화소 영역을 다수의 소 도메인으로 분할하는 수직 배향 액정 표시 장치에 관한 것이다.

- <12> 액정 표시 장치는 일반적으로 대향 전극과 컬러 필터(color filter) 등이 형성되어 있는 상부 기판과 박막 트랜지스터와 화소 전극 등이 형성되어 있는 하부 기판 사이에 액정 물질을 주입해 놓고 화소 전극과 대향 전극에 서로 다른 전위를 인가함으로써 전계를 형성하여 액정 분자들의 배열을 변경시키고, 이를 통해 빛의 투과율을 조절함으로써 화상을 표현하는 장치이다.

- <13> 그런데 액정 표시 장치는 시야각이 좁은 것이 중요한 단점이다. 이러한 단점을 극복하고자 시야각을 넓히기 위한 다양한 방안이 개발되고 있는데, 그 중에서도 액정 분자를 상하 기판에 대하여 수직으로 배향하고 화소 전극과 그 대향 전극인 대향 전극에 일정한 개구 패턴을 형성하거나 돌기를 형성하는 방법이 유력시되고 있다.

- <14> 개구 패턴을 형성하는 방법으로는 화소 전극과 대향 전극에 각각 개구 패턴을 형성하여 이들 개구 패턴으로 인하여 형성되는 프린지 필드(fringe field)를 이용하여 액정 분자들이 눕는 방향을 조절함으로써 시야각을 넓히는 방법이 있다.

- <15> 돌기를 형성하는 방법은 상하 기판 위에 형성되어 있는 화소 전극과 대향 전극 위에 각각 돌기를 형성해 둠으로써 돌기에 의하여 왜곡되는 전기장을 이용하여 액정 분자의 눕는 방향을 조절하는 방식이다.

- <16> 또 다른 방법으로는, 하부 기판 위에 형성되어 있는 화소 전극에는 개구 패턴을 형성하고 상부 기판에 형성되어 있는 대향 전극 위에는 돌기를 형성하여 개구 패턴과 돌기에 의하여 형성되는 프린지 필드를 이용하여 액정의 눕는 방향을 조절함으로써 도메인을 형성하는 방식이 있다.

- <17> 이러한 시야각을 넓히기 위한 다양한 방안 가운데 대향 전극에 개구 패턴을 형성하는 방법은, 대향 전극을 패터닝하기 위하여 별도의 마스크가 필요하고, 색 필터 위에 오버코트막이 없는 구조에서는 색 필터의 안료가 액정 물질에 영향을 주게 되므로 색 필터 위에 오버코트막을 형성하여야 하며, 패터닝된 전극의 가장자리에서 전경이 심하게 발생하는 등의 문제점이 존재한다. 또, 돌기를 형성하는 방법 역시 돌기를 형성하기 위한 별도의 공정을 필요로 하거나 기존의 공정을 변형시켜야 하므로 액정 표시 장치의 제조 방법을 복잡하게 만드는 문제점이 있다. 또한 돌기나 개구부로 인하여 개구율이 감소한다.

### 발명이 이루고자 하는 기술적 과제

- <18> 본 발명이 이루고자 하는 기술적 과제는 제조 공정이 복잡하지 않으면서 안정한 다중 도메인을 형성하는 액정 표시 장치를 제공하는 것이다.

### 발명의 구성 및 작용

- <19> 이러한 과제를 해결하기 위하여 본 발명에서는 방향 제어 전극을 형성한다.

- <20> 구체적으로는, 절연 기판, 상기 절연 기판 위에 형성되어 있는 제1 배선, 상기 절연 기판 위에 형성되어 있으며 상기 제1 배선과 절연되어 교차하고 있는 제2 배선, 상기 제1 배선과 상기 제2 배선이 교차하여 정의하는 화소 영역마다 형성되어 있으며 개구부를 가지는 화소 전극, 상기 제1 배선, 상기 제2 배선 및 상기 화소 전극과 연결되어 있는 제1 스위칭 소자, 상기 화소 전극의 개구부와 중첩하는 방향 제어 전극, 상기 방향 제어 전극에 인가되는 신호 전압을 스위칭하는 제2 스위칭 소자를 포함하는 액정 표시 장치용 박막 트랜지스터 기판을 마련한다.

- <21> 이 때, 상기 제2 스위칭 소자는 상기 제1 스위칭 소자보다 먼저 턴온되었다가 상기 제1 스위칭 소자가 턴온되기 이전에 턴오프되는 것이 바람직하다. 또, 상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 3단자 소자인 박막 트랜지스터이고, 상기 제2 스위칭 소자의 3단자는 각각 상기 제1 배선, 상기 제2 배선 및 상기 방향 제어 전극에 연결되어 있으며, 상기 제2 스위칭 소자가 연결되는 제1 배선은 상기 제1 스위칭 소자가 연결되는 제1 배선의 전단 배선이다.

- <22> 하나의 상기 화소 영역 내에 포함되어 있는 상기 제1 및 제2 스위칭 소자는 동일한 상기 제2 배선에 연결되어 있거나, 상기 화소 영역을 정의하는 두 개의 상기 제2 배선에 각각 연결되어 있을 수 있다.

- <23> 또, 상기 방향 제어 전극은 상기 제1 배선과 동일한 층에 형성되거나 상기 제2 배선과 동일한 층에 형성될 수 있다.

- <24> 또, 상기 방향 제어 전극과 상기 화소 전극을 절연시키는 절연막을 더 포함하고, 상기 절연막은 상기 화소 전극 개구부와 중첩하는 위치에 형성되어 있는 트렌치를 가질 수 있다.

- <25> 또는, 제1 절연 기판, 상기 제1 절연 기판 위에 형성되어 있는 제1 배선, 상기 제1 절연 기판 위에 형성되어 있

으며 상기 제1 배선과 절연되어 교차하고 있는 제2 배선, 상기 제1 배선과 상기 제2 배선이 교차하여 정의하는 화소 영역마다 형성되어 있으며 개구부를 가지는 화소 전극, 상기 제1 배선, 상기 제2 배선 및 상기 화소 전극과 연결되어 있는 제1 스위칭 소자, 상기 화소 전극의 개구부와 중첩하는 방향 제어 전극, 상기 방향 제어 전극과 상기 화소 전극 사이를 절연시키는 절연막, 상기 제1 절연 기판과 대향하고 있는 제2 절연 기판, 상기 제2 절연 기판 위에 형성되어 있는 대향 전극, 상기 제1 절연 기판과 상기 제2 절연 기판 사이에 주입되어 있는 액정층을 포함하고, 상기 대향 전극에 대한 상기 화소 전극의 전압을  $V_p$ , 상기 대향 전극에 대한 상기 방향 제어 전극의 전압을  $V_{DCE}$ , 상기 액정층의 유전율과 두께를 각각  $\epsilon$ ,  $d$ , 상기 절연막의 유전율과 두께를 각각

$$\epsilon', d' \text{이라 할 때, } V_{DCE} \geq V_p \times \left(1 + \frac{\epsilon d'}{\epsilon' d}\right) \text{ 를 만족하는 액정 표시 장치를 마련한다.}$$

<26> 이 때, 상기 액정층에 포함되어 있는 액정은 음의 유전율을 이방성을 가지며 상기 액정은 그 장축이 상기 제1 및 제2 기판에 대하여 수직 배향되어 있거나, 상기 액정층에 포함되어 있는 액정은 양의 유전율 이방성을 가지며 상기 액정은 그 장축이 상기 제1 및 제2 기판에 대하여 수평 배향되어 있을 수 있다.

<27> 또, 상기 방향 제어 전극에 신호 전압을 스위칭하는 제2 스위칭 소자를 더 포함하고, 상기 제2 스위칭 소자는 상기 제1 스위칭 소자보다 먼저 턴온되었다가 상기 제1 스위칭 소자가 턴온되기 이전에 턴오프되도록 구동하는 것이 바람직하다. 여기서, 상기 제1 스위칭 소자 및 상기 제2 스위칭 소자는 3단자 소자인 박막 트랜지스터이고, 상기 제2 스위칭 소자의 3단자는 각각 상기 제1 배선, 상기 제2 배선 및 상기 방향 제어 전극에 연결되어 있으며, 상기 제2 스위칭 소자가 연결되는 제1 배선은 상기 제1 스위칭 소자가 연결되는 제1 배선의 전단 배선인 것이 바람직하다.

<28> 또, 상기 대향 전극과 상기 화소 전극 사이의 정전 용량을  $C_{LC}$ , 상기 방향 제어 전극과 상기 화소 전극 사이의

$$\frac{C_{LC}}{2C_{DCE} + C_{LC}} |V_p + V_{n-1}| > \frac{\epsilon d'}{\epsilon' d} |V_p| \text{ 정전 용량을 } C_{DCE}, \text{ 전단의 화소 전극에 인가되는 전압을 } V_{n-1} \text{이라 하면, } \frac{C_{LC}}{2C_{DCE} + C_{LC}} |V_p + V_{n-1}| > \frac{\epsilon d'}{\epsilon' d} |V_p| \text{ 를 만족하는 것이 바람직하다.}$$

<29> 그러면 도면을 참고로 하여 본 발명의 실시예에 따른 다중 도메인 액정 표시 장치에 대하여 설명한다.

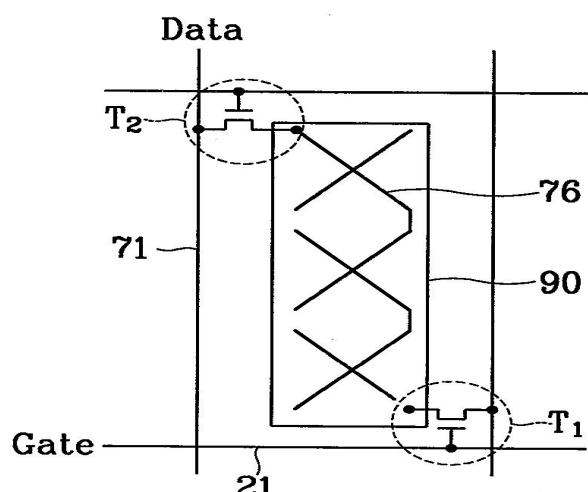

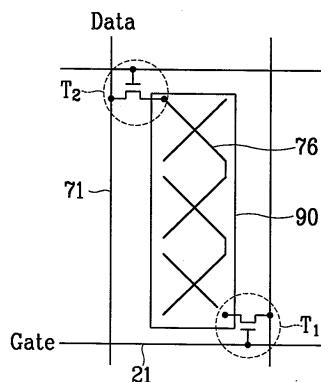

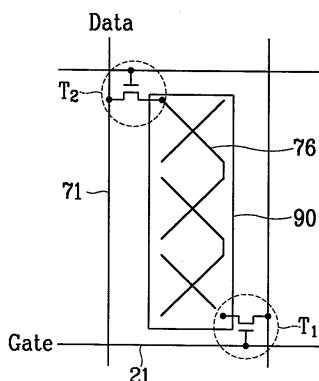

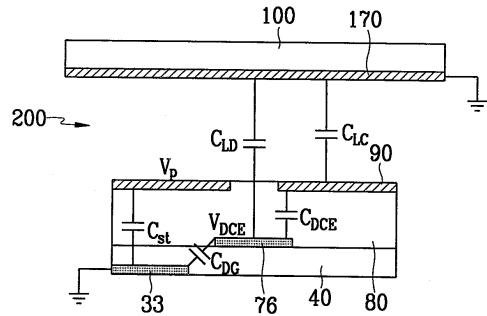

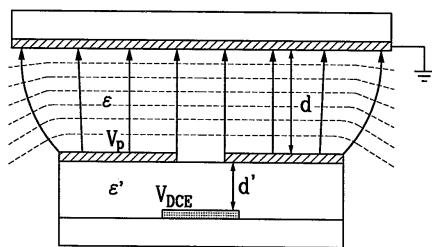

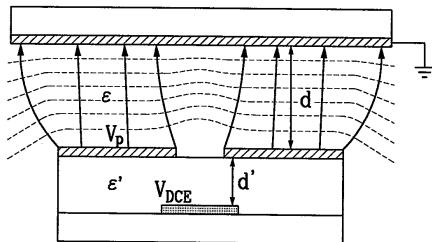

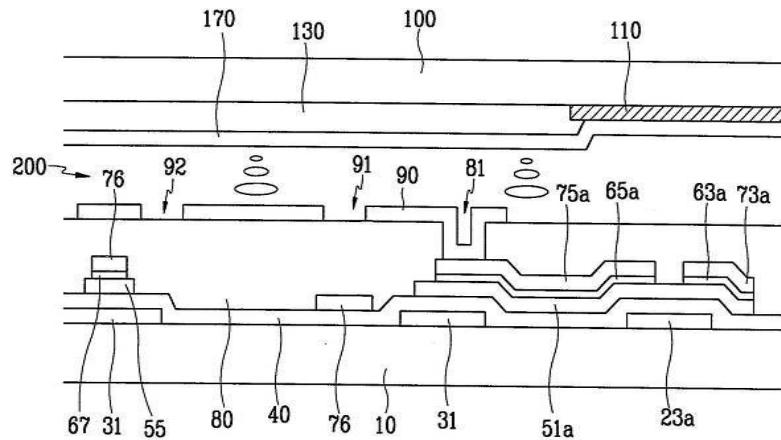

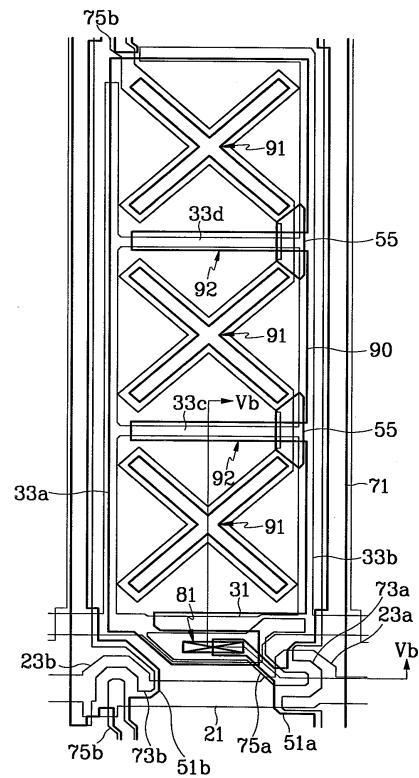

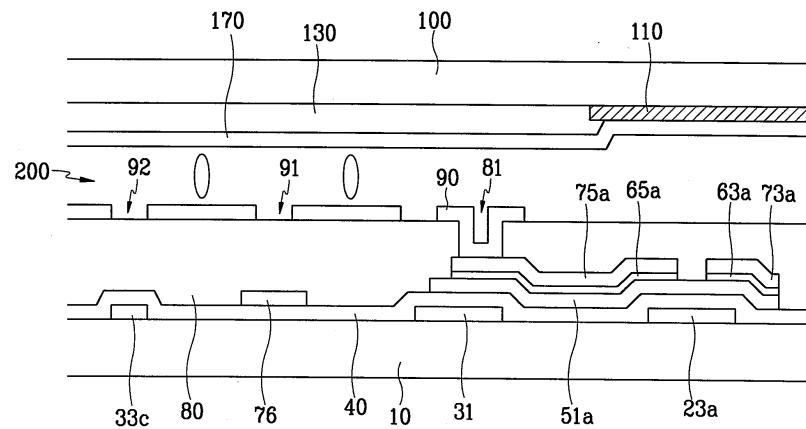

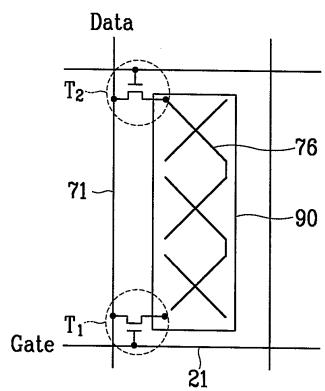

<30> 도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 개략적 구성도이고, 도 2는 본 발명의 제1 실시예에 따른 액정 표시 장치의 단면 구성도이다.

<31> 본 발명의 실시예에 따른 액정 표시 장치는 하부 기판(10)과 이와 마주보고 있는 상부 기판(100) 및 하부 기판(10)과 상부 기판(100) 사이에 주입되어 기판(10, 100)에 수직으로 배향되어 있는 액정 물질(200)로 이루어진다.

<32> 그러면, 하부 기판(10)에 대하여 좀 더 상세히 설명한다.

<33> 절연 기판(10) 위에 게이트선(21)이 형성되어 있고, 게이트선(21)과 교차하도록 데이터선(71)이 형성되어 있다. 게이트선(21)과 데이터선(71)은 서로 절연되어 있으며 이들이 교차하여 이루는 화소 영역에는 게이트 전극, 소스 전극 및 드레인 전극의 3단자를 가지는 박막 트랜지스터가 2개 형성되어 있고, 방향 제어 전극(76)과 화소 전극(90)이 각각 형성되어 있다. 이 때, 두 개의 박막 트랜지스터 중 제1 박막 트랜지스터( $T_1$ )는 화소 전극(90)을 스위칭하기 위한 것이고, 제2 박막 트랜지스터( $T_2$ )는 방향 제어 전극(76)을 스위칭하기 위한 것이다. 제1 박막 트랜지스터( $T_1$ )의 게이트 전극, 소스 전극 및 드레인 전극은 각각 해당 화소단의 게이트선(21), 데이터선(71) 및 화소 전극(90)에 연결되어 있고, 제2 박막 트랜지스터 ( $T_2$ )의 게이트 전극, 소스 전극 및 드레인 전극은 각각 전단의 게이트선(21) 및 데이터선(71)에 연결되어 있다. 방향 제어 전극(76)은 액정 분자의 선경사(pre-tilt)를 제어하기 위한 방향 제어 전압을 인가받아 대향 전극(170)과의 사이에 방향 제어 전계를 형성한다. 여기서 방향 제어 전극(76)은 게이트선(21) 또는 데이터선(71)을 형성하는 단계에서 함께 패터닝하여 형성한다.

<34> 그러면 방향 제어 전극(76)을 이용한 도메인 분할의 원리에 대하여 설명한다.

<35> 도 4에 나타낸 바와 같이, 대향 전극에 대한 상기 화소 전극의 전압을  $V_p$ , 상기 대향 전극에 대한 상기 방향 제어 전극의 전압을  $V_{DCE}$ , 상기 액정층의 유전율과 두께를 각각  $\epsilon$ ,  $d$ , 상기 절연막의 유전율과 두께를 각각  $\epsilon'$ ,

$d'$ 이라 할 때,  $V_{DCE} > V_p \times (1 + \frac{\epsilon d'}{\epsilon' d})$  를 만족하면 액정층에 형성되는 전계는 도 4b에 나타낸 바와 같이 화소 전극의 개구부가 형성되어 있는 부분에서 방향 제어 전극 전압의 영향을 받아 왜곡된다. 이러한 왜곡된 액정층 전계는 액정 분자를 소정의 방향으로 미리 기울도록 하여 선경사각을 가지도록 액정 분자를 제어한다. 그러나  $V_{DCE} = V_p \times (1 + \frac{\epsilon d'}{\epsilon' d})$  이면 액정층 전계는, 도 4a에 나타낸 바와 같이, 방향 제어 전극 전압에 크게 영향받지 않고 원래의 형태를 유지한다. 따라서, 이 경우에는 방향 제어 전극에 의한 액정 분자의 선경사각 제어 효과는 기대하기 어렵다. 또한  $V_{DCE} < V_p \times (1 + \frac{\epsilon d'}{\epsilon' d})$  인 경우에는 방향 제어 전극 전압에 의한 액정층 전계 왜곡의 긍정적인 효과는 기대할 수 없다.

<36> 그러면,  $V_{DCE} = V_p \times (1 + \frac{\epsilon d'}{\epsilon' d})$  이 유도되는 과정을 설명한다.

<37> 대향 전극에 분포하는 표면 전하 밀도를  $\sigma_0$ , 액정층 전계를  $E_{LC}$ , 방향 제어 전극과 화소 전극 사이의 절연층 전계를  $E_P$ 라 하면,

$$<38> V_p = E_{LC} \times d = \frac{\sigma_0 A}{\epsilon} \times d \quad (1)$$

$$<39> V_{DCE} = V_p + E_p \times d' \quad (2)$$

<40> 이다. 그런데 액정층 전계가 왜곡되지 않기 위해서는 화소 전극층에는 순표면 전하가 축적되지 않아야 한다. 따라서

$$<41> V_{DCE} = V_p + \frac{\sigma_0 A}{\epsilon'} d' \quad (3)$$

<42> (1)식을 이용하여 (3)식을 정리하면

$$<43> V_{DCE} = V_p \times V_p \frac{\epsilon d'}{\epsilon' d} = V_p \times (1 + \frac{\epsilon d'}{\epsilon' d}) \quad (4)$$

<44> 가 된다.

<45> 위에서 살펴본 바와 같이, 방향 제어 전극의 전압이 화소 전극 전압보다 소정의 값만큼 높아야 한다. 이를 위하여는 도 1과 같은 구조의 경우 다음과 같은 조건하에 방향 제어 전극에 전압을 인가하여야 한다.

<46> 첫째, 방향 제어 전극용 박막 트랜지스터는 화소 전극용 박막 트랜지스터보다 먼저 턴온(turn-on)되어서 화소 전극용 박막 트랜지스터가 턴온되기 이전에 턴오프되어야 한다.

<47> 둘째, 방향 제어 전극 전압과 화소 전극 전압의 극성은 동일하여야 한다.

<48> 이러한 두 가지 조건을 만족하도록 액정 표시 장치를 구동하면 방향 제어 전극을 이용하여 액정의 선경사각을 제어할 수 있다.

<49> 그러면 도 1 및 도 2와 도 3을 참고로 하여 위의 두 가지 조건을 만족하면 방향 제어 전극 전압이 화소 전극 전압보다 높게 되는 이유를 설명한다.

<50> 주어진 화소 전극이 양의 전압으로 리프레시(refresh)되는 순간을 생각해 보자. 리프레시 전에는 화소가 음의 전압으로 충전되어 있을 것이고, 전단의 게이트에 온(on) 신호가 인가되면 방향 제어 전극용 박막 트랜지스터 ( $T_2$ )가 턴온되어 방향 제어 전극이 양의 전하로 충전된다. 이 때, 화소 전극도 방향 제어 전극과 용량성 결합을 이루고 있으므로 따라서 충전된다. 방향 제어 전극과 화소 전극 사이의 정전 용량을  $C_{DCE}$ , 화소 전극과 공통 전극 사이의 정전 용량을  $C_{LC}$ 라고 하면, 도 2에서 알 수 있는 바와 같이,  $C_{DCE}$ 와  $C_{LC}$ 는 직렬로 연결되어 있다. 화소 전극은 음의 전압을 가지고 있었으므로 방향 제어 전극용 박막 트랜지스터를 통한 직렬 충전시 방향 제어 전극보다 낮은 전압을 가지게 된다. 즉,  $V_{DCE} > V_p$ 이다. 충전 후 방향 제어 전극용 박막 트랜지스터가 턴오프

되면 방향 제어 전극은 부유(floating) 상태가 된다. 따라서 화소 전극 전압이 어떻게 변화하더라도 항상 방향 제어 전극 전압이 화소 전극 전압보다 높은 상태를 유지하게 된다. 즉, 화소 전극용 박막 트랜지스터가 턴온되어서 화소 전극이 양의 전하로 충전되어 전압이 올라가면 방향 제어 전극의 전압도 화소 전극 전압과 일정한 전압차를 유지하며 동반 상승하게 된다.

<51> 이러한 액정 표시 장치에서 안정적인 도메인 분할이 이루어질 수 있는 액정 표시 장치의 설계 조건은 다음 수식을 만족하는 것이다. 여기서  $V_{n-1}$ 은 전단 화소에 인가되는 전압이다.

$$<52> \frac{C_{LC}}{2C_{DCE}+C_{LC}} |V_p + V_{n-1}| > \frac{\varepsilon d'}{\varepsilon' d} |V_p| \quad (5)$$

<53> 이러한 조건의 유도 과정을 설명한다.

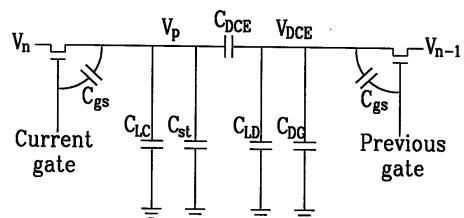

<54> 도 2의 액정 표시 장치를 회로 기호만으로 표시하면 도 3이 된다. 여기서,  $C_{st}$ 는 유지 용량 전극과 화소 전극 사이의 정전 용량이고,  $C_{gs}$ 는 게이트 전극과 소스 전극 사이의 기생 용량이며,  $C_{LD}$ 는 방향 제어 전극과 화소 전극 사이의 정전 용량이다. 아래의 계산에서는 계산상의 편의를 위하여 도 3에 표시된 정전 용량 중  $C_{st}$ 를  $C_{LC}$ 에 흡수시키고,  $C_{LD}$ 를  $C_{DG}$ 로 흡수시킨다.

<55> 전단의 화소 전극에 가해지는 전압을  $V_{n-1}$ , 현재의 화소 전극에 가해지는 전압을  $V_n$ , 박막 트랜지스터 턴온시의 게이트 전압을  $V_{on}$ , 박막 트랜지스터 턴오프시의 게이트 전압을  $V_{off}$ 라고 하면,

$$<56> V_p = V_{n-1} - \frac{C_{gs}}{C_{LC} + C_{LD} + 2C_{gs} - \frac{(C_{LD} + C_{gs})^2}{C_{DCE} + C_{LD} + C_{gs}}} (V_{on} - V_{off}) \approx V_n \quad (6)$$

$$<57> V_{DCE} \approx V_p + \frac{C_{LC}}{2C_{DCE} + C_{LC}} (V_p + V_{n-1}) \quad (7)$$

<58> 이 성립한다. 위의 수식 유도 과정에서  $C_{DCE}$ ,  $C_{LC} \gg C_{LD}$ ,  $C_{gs}$ 라고 가정하였다.

<59> 도메인 분할이 안정적으로 이루어지기 위해서는  $V_{DCE} > V_p \times (1 + \frac{\varepsilon d'}{\varepsilon' d})$  를 만족하여야 하므로 여기에 (7)식을 대입하면,

$$<60> V_p + \frac{C_{LC}}{2C_{DCE} + C_{LC}} (V_p + V_{n-1}) > V_p + \frac{\varepsilon d'}{\varepsilon' d} V_p \quad (8)$$

<61>이고, 이를 정리하면 (5)식을 얻을 수 있다. 이상의 유도 과정에서는 양의 전압으로 리프레시되는 과정을 고려한 것이므로 음의 전압으로 리프레시되는 경우까지 반영하면 (5)식과 같이 절대값으로 표시하여야 한다.

<62> (5)식을 만족하도록 패널을 설계하면 도메인이 안정적으로 분할된다. 여기서  $C_{DCE}$ 는 화소 전극과 방향 제어 전극과의 거리  $d'$  및 이들의 중첩 면적에 따라 결정되고,  $C_{LC}$ 는 셀캡  $d$ 와 액정의 유전율, 화소 전극의 면적 등에 따라 결정되며,  $C_{st}$ 는 화소 전극과 유지 용량 전극과의 거리 및 중첩된 면적에 따라 결정된다.

<63> 그러면, 본 발명의 실시예에 따른 액정 표시 장치의 구체적인 구조를 살펴본다.

<64> 도 5a는 본 발명의 제2 실시예에 따른 액정 표시 장치의 배치도이고, 도 5b는 도 5a의  $V_b - V_{b'}$  선에 대한 단면도이다.

<65> 본 발명에 따른 액정 표시 장치는 박막 트랜지스터 기판인 하부 기판(10)과 색 필터 기판인 상부 기판(100) 및 그 사이에 주입되어 있는 액정층(200)으로 이루어진다.

<66> 먼저 하부 기판(10)에 대하여 상세히 설명한다.

<67> 절연 기판(10) 위에 가로 방향으로 게이트선(21)과 제1 및 제2 게이트 전극(23a, 23b)이 형성되어 있다. 제1 및 제2 게이트 전극(23a, 23b)은 게이트선(21)에 돌기의 형태로 연결되어 있다. 또 절연 기판(10) 위에는 유지

용량선(31)과 유지 용량 전극(33a, 33b, 33c, 33d)이 형성되어 있다. 유지 용량선(31)은 가로 방향으로 뻗어 있고 제1 및 제2 유지 용량 전극(33a, 33b)은 유지 용량선(31)으로부터 세로 방향으로 뻗어 있다. 제3 및 제4 유지 용량 전극(33c, 33d)은 가로 방향으로 형성되어 있고 제1 유지 용량 전극(33a)과 제2 유지 용량 전극(33b)을 연결하고 있다. 게이트 배선(21, 23a, 23b) 및 유지 용량 배선(31, 33a, 33b, 33c, 33d)은 알루미늄 또는 그 합금, 크롬 또는 그 합금, 몰리브덴 또는 그 합금 등으로 이루어져 있으며, 필요에 따라서는 물리 화학적 특성이 우수한 Cr 또는 Mo 합금 등으로 이루어지는 제1층과, 저항이 작은 Al 또는 Ag 합금 등으로 이루어지는 제2층의 이중층으로 형성할 수도 있다.

<68> 게이트 배선(21, 23a, 23b) 및 유지 용량 배선(31, 33a, 33b, 33c, 33d)의 위에는 게이트 절연막(40)이 형성되어 있다.

<69> 제1 및 제2 게이트 전극(23a, 23b) 상부의 게이트 절연막(40) 위에는 비정질 규소 등의 반도체로 이루어진 제1 및 제2 반도체층(51a, 51b)이 형성되어 있으며, 제1 및 제2 반도체층(51a, 51b)의 상부에는 실리사이드 또는 n형 불순물이 고농도로 도핑되어 있는 n<sup>+</sup> 수소화 비정질 규소 따위의 물질로 만들어진 저항성 접촉층(63a, 65a, 63b, 65b)이 각각 형성되어 있다.

<70> 저항성 접촉층(63a, 65a, 63b, 65b) 및 게이트 절연막(40) 위에는 데이터 배선(71, 73a, 75a, 73b, 75b)이 형성되어 있다. 데이터 배선(71, 73a, 75a, 73b, 75b)은 세로 방향으로 형성되어 있으며 게이트선(21)과 교차하여 화소를 정의하는 데이터선(71), 데이터선(71)의 분지이며 저항 접촉층(63a, 63b)의 상부까지 연장되어 있는 제1 및 제2 소스 전극(73a, 73b), 데이터선(71)의 한쪽 끝에 연결되어 있으며 외부로부터의 화상 신호를 인가받는 데이터 패드(도시하지 않음), 제1 및 제2 소스 전극(73a, 73b)과 분리되어 있으며 각각 제1 및 제2 게이트 전극(23a, 23b)에 대하여 제1 및 제2 소스 전극(73a, 73b)의 반대쪽 저항성 접촉층(65a, 65b) 상부에 형성되어 있는 제1 및 제2 드레인 전극(75a, 75b)을 포함한다. 또 게이트선(21)과 데이터선(71)이 교차하여 이루는 화소 영역내에는 다수개의 X자 모양 금속편이 연결되어 이루어진 방향 제어 전극(76)이 형성되어 있다. 이 때, 방향 제어 전극(76)은 제2 드레인 전극(75b)과 연결되어 있다. 데이터 배선(71, 73a, 75a, 73b, 75b) 및 방향 제어 전극(76)은 알루미늄 또는 그 합금, 크롬 또는 그 합금, 몰리브덴 또는 그 합금 등으로 이루어져 있으며, 필요에 따라서는 물리 화학적 특성이 우수한 Cr 또는 Mo 합금 등으로 이루어지는 제1층과, 저항이 작은 Al 또는 Ag 합금 등으로 이루어지는 제2층의 이중층으로 형성할 수도 있다.

<71> 한편, 방향 제어 전극(76)과 유지 용량 전극(33c, 33d)이 교차하는 부분에는 이들 금속 배선 사이의 절연을 보장하기 위한 교차부 반도체층(55)이 형성되어 있다.

<72> 데이터 배선(71, 73a, 75a, 73b, 75b) 위에는 질화 규소 또는 유기 절연막으로 이루어진 보호막(80)이 형성되어 있다.

<73> 보호막(80)에는 제1 드레인 전극(75a)을 드러내는 접촉구(81)와 데이터 패드를 드러내는 접촉구(도시하지 않음)가 형성되어 있으며, 게이트 절연막(40)과 함께 게이트 패드를 드러내는 접촉 구멍(도시하지 않음)이 형성되어 있다. 이때, 패드를 드러내는 접촉 구멍은 각을 가지거나 원형의 다양한 모양으로 형성될 수 있으며, 면적은 2mm×60μm를 넘지 않으며, 0.5mm×15μm 이상인 것이 바람직하다.

<74> 보호막(80) 위에는 접촉구(81)를 통하여 제1 드레인 전극(75a)과 전기적으로 연결되어 있으며 다수개의 X자 모양 개구부(91)와 직선형 개구부(92)를 가지는 화소 전극(90)이 형성되어 있다. 이 때, 다수개의 개구부(91)는 방향 제어 전극(76)의 X자 모양 금속편과 중첩하고, 직선형 개구부(92)는 제3 및 제4 유지 용량 전극(33c, 33d)과 중첩한다. 또한, 보호막(80) 위에는 접촉구를 통하여 각각 게이트 패드 및 데이터 패드와 연결되어 있는 보조 게이트 패드(도시하지 않음) 및 보조 데이터 패드(도시하지 않음)가 형성되어 있다. 여기서, 화소 전극(90)과 보조 게이트 및 데이터 패드는 IZO(indium zinc oxide)로 이루어져 있다. 화소 전극(90) 및 보조 패드는 ITO로 형성할 수도 있다.

<75> 이상에서, 화소 전극(90)은 화소 영역을 다수의 소도메인으로 분할하기 위한 개구부 패턴(91, 92)을 가지며, 이 중 제1 개구부(91)는 방향 제어 전극(76)과 중첩되어 있고, 제2 개구부(92)는 유지 용량 전극(33c, 33d)과 중첩되어 있다. 즉, 액정 표시 장치를 위에서 바라볼 때 방향 제어 전극(76)이 제1 개구부(91)를 통하여 노출되어 보이도록 방향 제어 전극(76)과 제1 개구부(91)를 배열한다. 또, 두 개의 박막 트랜지스터를 형성하여 하나는 화소 전극(90)에 연결하고, 다른 하나는 후단의 방향 제어 전극(76)에 연결하여 이들 화소 전극(90)과 방향 제어 전극(76)에 별도로 신호를 인가할 수 있도록 한다.

<76> 한편, 유지 용량 배선(31, 33a, 33b, 33c, 33d)을 형성하는 대신 화소 전극(90)을 게이트선과 중첩시켜 유지 축

전기를 형성할 수도 있다.

<77> 방향 제어 전극(76)은 게이트 배선(21, 23a, 23b)과 같은 층에 형성할 수도 있다. 또, 방향 제어 전극(76) 상부의 보호막(80)을 제거하여 트렌치를 형성할 수도 있다.

<78> 상부 기판(100)에 대하여 좀 더 상세히 설명한다.

<79> 유리 등의 투명한 절연 물질로 이루어진 상부 기판(100)의 아래 면에 빛샘을 방지하기 위한 블랙 매트릭스(110)와 적, 녹, 청의 색필터(130) 및 ITO 또는 IZO 등의 투명한 도전 물질로 이루어져 있는 대향 전극(170)이 형성되어 있다.

<80> 액정층(200)에 포함되어 있는 액정 분자는 화소 전극(90)과 대향 전극(170) 사이에 전계가 인가되지 않은 상태에서 그 방향자가 하부 기판(10)과 상부 기판(100)에 대하여 수직을 이루도록 배향되어 있고, 음의 유전율이 방성을 가진다. 하부 기판(10)과 상부 기판(100)은 화소 전극(90)이 색필터(130)와 대응하여 정확하게 중첩되도록 정렬된다. 이렇게 하면, 화소 영역은 제1 및 제2 개구부(91, 92)에 의하여 다수의 소도메인으로 분할된다. 또, 방향 제어 전극(76)에 의하여 분할된 도메인 내에서 액정의 배향이 더욱 안정해진다.

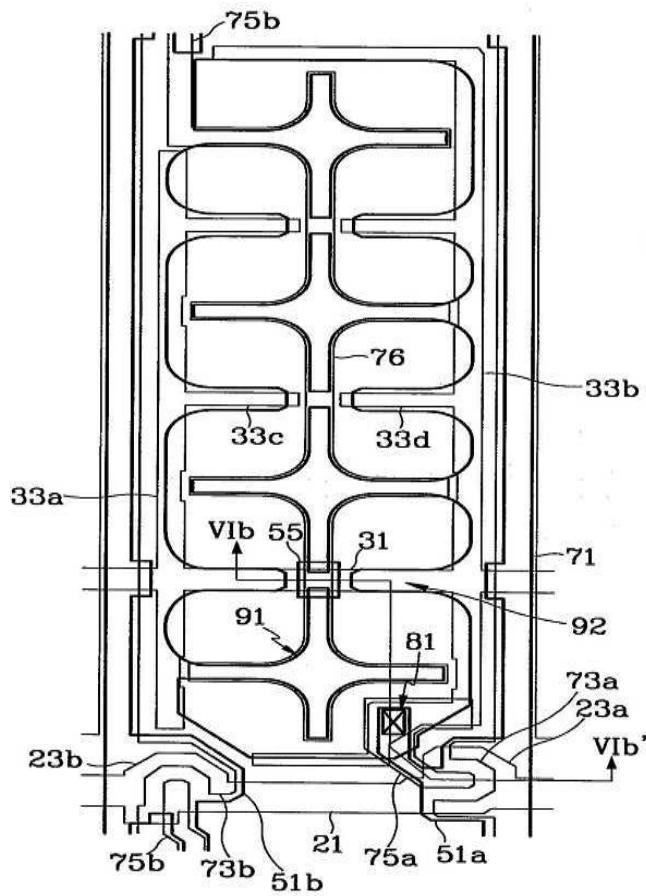

<81> 도 6a는 본 발명의 제3 실시예에 따른 액정 표시 장치의 배치도이고, 도 6b는 도 6a의 VIb-VIb'선에 대한 단면도이다.

<82> 본 발명의 제3 실시예에 따른 액정 표시 장치도 제2 실시예와 마찬가지로 박막 트랜지스터 기판인 하부 기판(10)과 색필터 기판인 상부 기판(100) 및 그 사이에 주입되어 있는 액정층(200)으로 이루어진다.

<83> 먼저 하부 기판(10)에 대하여 상세히 설명한다.

<84> 절연 기판(10) 위에 가로 방향으로 게이트선(21)과 제1 및 제2 게이트 전극(23a, 23b)이 형성되어 있다. 제1 및 제2 게이트 전극(23a, 23b)은 게이트선(21)에 돌기의 형태로 연결되어 있다. 또 절연 기판(10) 위에는 유지 용량선(31)과 유지 용량 전극(33a, 33b, 33c, 33d)이 형성되어 있다. 유지 용량선(31)은 가로 방향으로 뻗어 있고 제1 및 제2 유지 용량 전극(33a, 33b)은 유지 용량선(31)으로부터 세로 방향으로 뻗어 있다. 제3 및 제4 유지 용량 전극(33c, 33d)은 각각 제1 유지 용량 전극(33a)과 제2 유지 용량 전극(33b)으로부터 가로 방향으로 뻗어 나와 있다. 게이트 배선(21, 23a, 23b) 및 유지 용량 배선(31, 33a, 33b, 33c, 33d)은 알루미늄 또는 그 합금, 크롬 또는 그 합금, 몰리브덴 또는 그 합금 등으로 이루어져 있으며, 필요에 따라서는 물리 화학적 특성이 우수한 Cr 또는 Mo 합금 등으로 이루어지는 제1층과, 저항이 작은 Al 또는 Ag 합금 등으로 이루어지는 제2층의 이중층으로 형성할 수도 있다.

<85> 게이트 배선(21, 23a, 23b) 및 유지 용량 배선(31, 33a, 33b, 33c, 33d)의 위에는 게이트 절연막(40)이 형성되어 있다.

<86> 제1 및 제2 게이트 전극(23a, 23b) 상부의 게이트 절연막(40) 위에는 비정질 규소 등의 반도체로 이루어진 제1 및 제2 반도체층(51a, 51b)이 형성되어 있으며, 제1 및 제2 반도체층(51a, 51b)의 상부에는 실리사이드 또는 n형 불순물이 고농도로 도핑되어 있는 n<sup>+</sup> 수소화 비정질 규소 따위의 물질로 만들어진 저항성 접촉층(63a, 65a, 63b, 65b)이 각각 형성되어 있다.

<87> 저항성 접촉층(63a, 65a, 63b, 65b) 및 게이트 절연막(40) 위에는 데이터 배선(71, 73a, 75a, 73b, 75b)이 형성되어 있다. 데이터 배선(71, 73a, 75a, 73b, 75b)은 세로 방향으로 형성되어 있으며 게이트선(21)과 교차하여 화소를 정의하는 데이터선(71), 데이터선(71)의 분지이며 저항 접촉층(63a, 63b)의 상부까지 연장되어 있는 제1 및 제2 소스 전극(73a, 73b), 데이터선(71)의 한쪽 끝에 연결되어 있으며 외부로부터의 화상 신호를 인가받는 데이터 패드(도시하지 않음), 제1 및 제2 소스 전극(73a, 73b)과 분리되어 있으며 각각 제1 및 제2 게이트 전극(23a, 23b)에 대하여 제1 및 제2 소스 전극(73a, 73b)의 반대쪽 저항성 접촉층(65a, 65b) 상부에 형성되어 있는 제1 및 제2 드레인 전극(75a, 75b)을 포함한다. 또 게이트선(21)과 데이터선(71)이 교차하여 이루는 화소 영역내에는 다수개의 십자(+) 모양의 금속편이 연결되어 이루어진 방향 제어 전극(76)이 형성되어 있다. 이 때, 방향 제어 전극(76)은 제2 드레인 전극(75b)과 연결되어 있다. 데이터 배선(71, 73a, 75a, 73b, 75b) 및 방향 제어 전극(76)은 알루미늄 또는 그 합금, 크롬 또는 그 합금, 몰리브덴 또는 그 합금 등으로 이루어져 있으며, 필요에 따라서는 물리 화학적 특성이 우수한 Cr 또는 Mo 합금 등으로 이루어지는 제1층과, 저항이 작은 Al 또는 Ag 합금 등으로 이루어지는 제2층의 이중층으로 형성할 수도 있다.

<88> 한편, 방향 제어 전극(76)과 유지 용량선(31)이 교차하는 부분에는 이를 금속 배선 사이의 절연을 보장하기 위

한 교차부 반도체층(55)이 형성되어 있다.

<89> 데이터 배선(71, 73a, 75a, 73b, 75b) 위에는 질화 규소 또는 유기 질연막으로 이루어진 보호막(80)이 형성되어 있다.

<90> 보호막(80)에는 제1 드레인 전극(75a)을 드러내는 접촉구(81)와 데이터 패드를 드러내는 접촉구(도시하지 않음)가 형성되어 있으며, 게이트 절연막(40)과 함께 게이트 패드를 드러내는 접촉 구멍(도시하지 않음)이 형성되어 있다. 이때, 패드를 드러내는 접촉 구멍은 각을 가지거나 원형의 다양한 모양으로 형성될 수 있으며, 면적은  $2\text{mm} \times 60\mu\text{m}$ 를 넘지 않으며,  $0.5\text{mm} \times 15\mu\text{m}$  이상인 것이 바람직하다. 또한 보호막(80)에는 방향 제어 전극(76)을 노출시키는 트렌치(82)가 형성되어 있다. 이와 같이 트렌치(82)를 형성해 두면 트렌치(82)에 의하여도 액정의 프리틸트가 형성되어 더욱 안정하게 액정이 배향되고 텍스쳐도 안정화된다.

<91> 보호막(80) 위에는 접촉구(81)를 통하여 제1 드레인 전극(75a)과 전기적으로 연결되어 있으며 다수개의 십자(+) 모양의 개구부(91)와 직선형 개구부(92)를 가지는 화소 전극(90)이 형성되어 있다. 이 때, 다수개의 개구부(91)는 방향 제어 전극(76)의 십자 모양 금속편과 중첩하고, 직선형 개구부(92)는 제3 및 제4 유지 용량 전극(33c, 33d) 및 유지 용량선(31)과 중첩한다. 따라서 개구부(91)는 보호막(80)이 가지는 트렌치(82)를 노출시킨다. 또한, 보호막(80) 위에는 접촉구를 통하여 각각 게이트 패드 및 데이터 패드와 연결되어 있는 보조 게이트 패드(도시하지 않음) 및 보조 데이터 패드(도시하지 않음)가 형성되어 있다. 여기서, 화소 전극(90)과 보조 게이트 및 데이터 패드는 IZO(indium zinc oxide)로 이루어져 있다. 화소 전극(90) 및 보조 패드는 ITO로 형성할 수도 있다.

<92> 이상에서, 화소 전극(90)은 화소 영역을 다수의 소도메인으로 분할하기 위한 개구부 패턴(91, 92)을 가지며, 이 중 제1 개구부(91)는 방향 제어 전극(76)과 중첩되어 있고, 제2 개구부(92)는 유지 용량 전극(33c, 33d) 및 유지 용량선(31)과 중첩되어 있다. 즉, 액정 표시 장치를 위에서 바라볼 때 방향 제어 전극(76)이 제1 개구부(91)를 통하여 노출되어 보이도록 방향 제어 전극(76)과 제1 개구부(91)를 배열한다. 또, 두 개의 박막 트랜지스터를 형성하여 하나는 화소 전극(90)에 연결하고, 다른 하나는 후단의 방향 제어 전극(76)에 연결하여 이를 화소 전극(90)과 방향 제어 전극(76)에 별도로 신호를 인가할 수 있도록 한다. 또한 트렌치(82)를 형성해 두면 트렌치(82)에 의하여도 액정의 프리틸트가 형성되어 더욱 안정하게 액정이 배향되고 텍스쳐도 안정화된다.

<93> 한편, 유지 용량 배선(31, 33a, 33b, 33c, 33d)을 형성하는 대신 화소 전극(90)을 게이트선과 중첩시켜 유지 축 전기를 형성할 수도 있다. 또, 방향 제어 전극(76)은 게이트 배선(21, 23a, 23b)과 같은 층에 형성할 수도 있다.

<94> 상부 기판(100)은 앞서 설명한 제2 실시예에서와 동일한 구조를 가진다.

<95> 액정층(200)의 액정 분자는 기판(10, 100)에 대하여 수평 배향되어 있고, 양의 유전율 이방성을 가진다. 액정 분자는 하부 기판(10)으로부터 상부 기판(100)으로 진행하면서 비틀림 배향되어 있다. 이러한 배치의 액정 분자는 화소 전극(90)과 대향 전극(131) 사이에 전계가 인가되면 기판(10, 100)에 대하여 수직을 이루려는 방향으로 배향 상태가 변화한다.

<96> 제1 내지 제3 실시예에서는 액정 분자가 기판(10, 100)에 대하여 수직 배향되어 있는 구조를 실시예로서 제시하고 있으나

<97> 본 발명의 제1 내지 제3 실시예에서는 화소 전극을 스위칭하는 제1 박막 트랜지스터를 해당 게이트선과 데이터 선에 연결하고, 방향 제어 전극을 스위칭하는 제2 박막 트랜지스터를 전단의 게이트선과 데이터선에 연결하여, 방향 제어 전극용 박막 트랜지스터가 화소 전극용 박막 트랜지스터보다 먼저 턴온(turn-on)되어서 화소 전극용 박막 트랜지스터가 턴온되기 이전에 턴오프될 수 있도록 배치하였다. 그러나 제1 및 제2 박막 트랜지스터의 배치는 다양한 변형이 가능하다. 그 한 예를 제4 실시예를 통하여 제시한다.

<98> 도 7은 본 발명의 제4 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 개략적 구성도이다.

<99> 제4 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판은 박막 트랜지스터의 배치를 제외한 나머지 구조는 제1 실시예에 따른 박막 트랜지스터 기판과 동일하다. 제4 실시예에서는 화소 전극(90)을 스위칭하기 위한 제1 박막 트랜지스터( $T_1$ )의 드레인 전극이 방향 제어 전극(76)을 스위칭하기 위한 제2 박막 트랜지스터( $T_2$ )의 드레인 전극과 동일한 데이터선(71)에 연결되어 있다. 이러한 구조의 박막 트랜지스터 기판을 사용하는 액정 표시 장치도 그 구동 방법은 다음의 조건을 만족하여야 한다.

<100> 먼저,  $V_{DCE} > V_p \times (1 + \frac{\varepsilon d'}{\varepsilon' d})$  를 만족하여야 하고, 방향 제어 전극용 박막 트랜지스터는 화소 전극용 박막 트랜지스터보다 먼저 턴온(turn-on)되어서 화소 전극용 박막 트랜지스터가 턴온되기 이전에 턴오프되어야 하며, 방향 제어 전극 전압과 화소 전극 전압의 극성은 동일하여야 한다. 또,  $\frac{C_{LC}}{2C_{DCE} + C_{LC}} |V_p + V_{n-1}| > \frac{\varepsilon d'}{\varepsilon' d} |V_p|$  를 만족하여야 한다.

<101> 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허청구범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 발명의 효과

<102> 이상과 같이, 다중 도메인 액정 표시 장치에 있어서, 방향 제어 전극을 형성하고 방향 제어 전극 신호를 스위칭하기 위한 박막 트랜지스터를 화소 전극을 스위칭하기 위한 박막 트랜지스터와는 별개로 형성하여 방향 제어 전압을 인가하면, 액정의 기울기 방향을 용이하게 제어할 수 있고, 이를 통하여 안정한 도메인을 형성할 수 있다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 개략적 구성도이고,

- <2> 도 2는 본 발명의 제1 실시예에 따른 액정 표시 장치의 단면 구성도이고,

- <3> 도 3은 본 발명의 제1 실시예에 따른 액정 표시 장치의 회로도이고,

- <4> 도 4a는 방향 제어 전극 전압에 의하여 액정층 전계가 변화되지 않은 상태를 나타내는 액정 표시 장치의 단면도이고,

- <5> 도 4b는 방향 제어 전극 전압에 의하여 액정층 전계가 변화된 상태를 나타내는 액정 표시 장치의 단면도이고,

- <6> 도 5a는 본 발명의 제2 실시예에 따른 액정 표시 장치의 배치도이고,

- <7> 도 5b는 도 5a의 V<sub>b</sub>-V<sub>b'</sub> 선에 대한 단면도이고,

- <8> 도 6a는 본 발명의 제3 실시예에 따른 액정 표시 장치의 배치도이고,

- <9> 도 6b는 도 6a의 V<sub>Ib</sub>-V<sub>Ib'</sub> 선에 대한 단면도이고,

- <10> 도 7은 본 발명의 제4 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 개략적 구성도이다.

### 도면

#### 도면1

도면2

도면3

도면4a

도면4b

도면6b

도면5a

도면5b

도면6a

도면7

|                |                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">KR100870005B1</a>                                                                                    | 公开(公告)日 | 2008-11-21 |

| 申请号            | KR1020020012121                                                                                                  | 申请日     | 2002-03-07 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                         |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                                         |         |            |

| [标]发明人         | LEE BAEKWOON<br>이백운<br>KIM HEESEOB<br>김희섭<br>HONG SUNGKYU<br>홍성규<br>SHIN KYONGJU<br>신경주<br>YANG YOUNGCHOL<br>양영철 |         |            |

| 发明人            | 이백운<br>김희섭<br>홍성규<br>신경주<br>양영철                                                                                  |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/133 G02F1/1333 G02F1/1362                                                            |         |            |

| CPC分类号         | G02F1/133707 G02F1/134336 G02F1/13624 G02F1/1343                                                                 |         |            |

| 其他公开文献         | KR1020030072859A                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                        |         |            |

## 摘要(译)

栅极线形成在绝缘基板上。形成数据线以便与栅极线相交。在栅极线和数据线被绝缘并构成的同时聚集在这些头脑上的像素区域被提供给方向控制电极和像素电极，具有栅电极的薄膜晶体管，以及漏电极和源电极的3端子分别为2。此时，薄膜晶体管用于在两个薄膜晶体管之间切换像素电极。第二薄膜晶体管用于切换方向控制电极。薄膜晶体管的栅电极和源电极和漏电极连接到相应的相应像素组的栅极线，以及数据线和像素电极。第二薄膜晶体管的栅电极和源电极和漏电极连接到相应剪切的栅极线和数据线。它是关于方向控制电压施加的，其中方向控制电极控制液晶分子的预倾斜(预倾斜)，并且在相对电极之间形成方向控制场。液晶显示器，域，开口部分，方向控制电极，薄膜晶体管。