(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0104636

(43) 공개일자 2008년12월03일

(51) Int. Cl.

(71) 출원인

G02F 1/133 (2006.01) G02F 1/136 (2006.01)

엘지디스플레이 주식회사

(21) 출원번호 10-2007-0051668

서울 영등포구 여의도동 20번지

(22) 출원일자 2007년05월28일

(72) 발명자

심사청구일자 없음

백상윤

경기 파주시 아동동 팜스프링아파트 111-1903

조명준

경기 파주시 야동동 109동 1503호

(74) 대리인

허용록

전체 청구항 수 : 총 6 항

(54) 액정표시장치의 박막트랜지스터 기판 및 이의 형성방법

### (57) 요약

본 발명은 액정표시장치의 박막트랜지스터 기판에 관한 것이다.

본 발명에 의한 박막트랜지스터 기판은 베이스 기판과, 베이스 기판에서 절연층을 사이에 두고 형성된 제1 금속층 및 제2 금속층과, 제1 금속층에 형성된 게이트 라인과, 제2 금속층에 형성된 데이터 라인과, 데이터 라인들을 구동하기 위한 데이터 구동회로과, 게이트 라인들을 구동하기 위한 게이트 구동회로과, 게이트 구동회로에서 생성된 구동신호를 게이트 라인들에 공급하기 위한 것으로 베이스 기판상에서 서로 다른 두 개 이상의 레이어에 복수로 형성되는 라인-온-글라스형 게이트 구동신호라인군을 구비한다.

**대 표 도** - 도3

## 특허청구의 범위

### 청구항 1

베이스 기판;

상기 베이스 기판에서 절연층을 사이에 두고 형성된 제1 금속층 및 제2 금속층;

상기 제1 금속층에 형성된 게이트 라인;

상기 제2 금속층에 형성된 데이터 라인;

상기 데이터 라인들을 구동하기 위한 데이터 구동회로;

상기 게이트 라인들을 구동하기 위한 게이트 구동회로;

상기 게이트 구동회로에서 생성된 구동신호를 상기 게이트 라인들에 공급하기 위한 것으로, 상기 베이스 기판상에서 서로 다른 두 개 이상의 레이어에 복수로 형성되는 라인-온-글라스형 게이트 구동신호라인군을 구비하는 것을 특징으로 하는 박막트랜지스터 기판.

### 청구항 2

제 1 항에 있어서,

상기 라인-온-글라스형 게이트 구동신호라인군은 제1 금속층에 형성된 제1 구동신호라인군과;

상기 제1 구동신호라인군과 동일한 신호라인으로 구성되고, 상기 제2 금속층에 형성된 제2 구동신호라인군을 포함하는 것을 특징으로 하는 박막트랜지스터 기판.

### 청구항 3

제 1 항에 있어서,

상기 라인-온-글라스형 게이트 구동신호라인군은 제1 금속층에 형성된 제1 구동신호라인군과;

상기 제1 구동신호라인군을 통해 인가되는 구동신호와 서로 다른 구동신호를 인가하기 위한 것으로, 상기 제2 금속층에 형성된 제2 구동신호라인군을 포함하는 것을 특징으로 하는 박막트랜지스터 기판.

### 청구항 4

제 3 항에 있어서,

상기 라인-온-글라스형 신호라인군 중 일부는 상부기판이 합착될 영역 내부에 형성되는 것을 특징으로 하는 박막트랜지스터 기판.

### 청구항 5

제 2 항 또는 제 3 항 중 어느 한 항에 있어서,

상기 제1 구동신호라인군과 상기 제2 구동신호라인군은 적어도 하나 이상의 콘택홀을 통해 접속되는 것을 특징으로 하는 박막트랜지스터 기판.

### 청구항 6

베이스 기판에 제1 금속층을 형성하는 단계;

상기 제1 금속층에 제1 라인-온-글래스형 신호라인군을 형성하는 단계;

상기 제1 라인-온-글래스형 신호라인군을 덮도록 상기 제1 금속층에 절연막을 형성하는 단계;

상기 절연막상에 상기 제1 라인-온-글래스형 신호라인군의 일부분이 노출되도록 콘택홀을 형성하는 단계;

상기 콘택홀을 채우도록 상기 절연막상에 제2 금속층을 형성하는 단계;

상기 콘택홀과 접촉하도록 상기 제2 금속층에 제2 라인-온-글래스형 신호라인군을 형성하는 단계;

상기 제2 라인-온-글래스형 신호라인군을 덮도록 절연막을 형성하는 단계;

상기 절연막상에 투명 도전막을 형성하는 단계를 포함하는 것을 특징으로 하는 박막트랜지스터 기판의 형성방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <7> 본 발명은 액정표시장치에 관한 것으로, 특히 라인-온-글래스형 게이트 구동신호군의 불량을 줄일 수 있는 액정 표시장치의 박막트랜지스터 기판 및 이의 형성방법에 관한 것이다.

- <8> 음극선관의 한계를 극복하기 위한 많은 평판표시장치들이 증가하고 있고, 이러한 평판표시장치 중 액정표시장치는 전계를 이용하여 유전 이방성을 갖는 액정의 광투과율을 조절함으로써 화상을 표시하는 것이다. 이를 위하여, 액정표시장치는 복수의 액정셀들이 배열된 액정패널과, 액정패널을 구동하기 위한 구동회로를 구비한다.

- <9> 액정패널에는 게이트라인들과 데이터라인들이 교차하게 배열되고 그 게이트라인들과 데이터라인들의 교차로 마련되는 영역에 액정셀들이 위치한다. 이 액정패널에는 액정셀들 각각에 전계를 인가하기 위한 화소전극들과 공통전극이 마련된다. 화소전극들 각각은 스위칭 소자인 박막트랜지스터(Thin Film Transistor)의 소스 및 드레인 단자들을 경유하여 데이터라인들 중 어느 하나에 접속된다.

- <10> 구동회로는 게이트라인들을 구동하기 위한 게이트 드라이버와, 데이터라인들을 구동하기 위한 데이터 드라이버와, 게이트 드라이버와 데이터 드라이버를 제어하기 위한 타이밍콘트롤러와, 액정표시장치에서 사용되는 여러가지의 구동전압들을 공급하는 전원공급부를 구비한다.

- <11> 이들 중 액정패널과 직접 접속되는 데이터 드라이버와 게이트 드라이버는 다수개의 IC(Integrated Circuit)들로 집적화된다. 집적화된 데이터 드라이브 IC와 게이트 드라이브 IC 각각은 TCP(Tape Carrier Package) 상에 실장되어 TAB(Tape Automated Bonding) 방식으로 액정패널에 접속되거나 COG(Chip On Glass) 방식으로 액정패널 상에 실장된다.

- <12> 특히, COG 방식으로 액정패널에 실장되는 드라이브 IC들은 신호라인들이 액정패널, 즉 하부 글래스 상에 실장되는 라인 온 글래스(Line On Glass; 이하 "LOG"라 함) 방식으로 상호 접속됨과 아울러 타이밍콘트롤러 및 전원공급부로부터의 제어신호들 및 구동전압들을 공급받는다.

- <13> 최근에는 드라이브 IC들이 TAB 방식으로 액정패널에 접속되는 경우에도 LOG방식을 채택하여 PCB를 제거함으로써 액정표시장치를 제조하는데 소요되는 비용을 줄이면서 액정표시장치를 박형화하고 있다. 특히 상대적으로 적은 신호라인들을 필요로 하는 게이트 드라이브 IC들에 접속되는 신호라인들을 LOG 방식으로 액정패널 상에 형성함으로써 게이트 PCB를 제거하고 있다.

- <14> 다시 말하여 게이트 드라이브 IC들은 액정패널의 하부 글래스 상에 실장되는 신호라인들을 통해 직렬로 접속됨과 아울러 제어신호들 및 구동전압신호들(이하, "게이트 구동신호들"이라 함)을 공통적으로 공급받는다.

- <15> 이처럼 게이트 드라이브 IC들에 게이트 구동신호들(GSP, GSC, GOE 신호 등)을 전송하기 위한 LOG형 신호라인군(26)은 도 1에서 보는 바와 같이, 하부기판(2)의 외곽영역에 형성된다. 이는 여러 신호 라인을 형성하는 과정에서 각각의 라인을 상부기판(4)이 형성되는 패널의 내부의 영역에 형성하기에는 공간 마진 부족하고 저항이 높아지는 문제가 있기 때문이다.

- <16> 이처럼 LOG형 신호라인군(26)은 하부기판(2)의 외곽 모서리 영역에 형성되기 때문에 기판에 물리적 충격에 매우 취약한 상태에 있다. 즉, 기판의 제조 공정 및 운송과정에서 기판 모서리의 손상이 발생하는 경우가 빈번하고 이에 따라 LOG형 신호라인군(26)이 단선되는 불량이 발생한다.

#### 발명이 이루고자 하는 기술적 과제

- <17> 따라서, 본 발명의 목적은 LOG형 신호라인군의 단선 불량을 방지할 수 있는 액정표시장치의 박막트랜지스터 기

판 및 이의 형성방법을 제공하는 것이다.

### 발명의 구성 및 작용

- <18> 상기 목적을 달성하기 위하여, 본 발명에 의한 박막트랜지스터 기판은 베이스 기판과, 베이스 기판에서 절연층을 사이에 두고 형성된 제1 금속층 및 제2 금속층과, 제1 금속층에 형성된 게이트 라인과, 제2 금속층에 형성된 데이터 라인과, 데이터 라인들을 구동하기 위한 데이터 구동회로과, 게이트 라인들을 구동하기 위한 게이트 구동회로과, 게이트 구동회로에서 생성된 구동신호를 게이트 라인들에 공급하기 위한 것으로 베이스 기판상에서 서로 다른 두 개 이상의 레이어에 복수로 형성되는 라인-온-글라스형 게이트 구동신호라인군을 구비한다.

- <19> 상기 목적 외에 본 발명의 다른 목적 및 특징들은 첨부도면을 참조한 실시 예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

- <20> 이하, 도 2 내지 도 6을 참조하여 본 발명의 실시 예에 대하여 설명하기로 한다.

- <21> 도 2는 본 발명의 실시예에 의한 박막트랜지스터 기판을 포함하는 액정표시장치를 나타내는 평면도이다.

- <22> 도 2를 참조하면, 본 발명에 의한 액정표시장치는 액정패널(106)과, 데이터라인들을 구동하기 위한 데이터 드라이브 IC(114)들을 포함하는 데이터 TCP(112)들과, 게이트라인들을 구동하기 위한 게이트 드라이브 IC(110)들을 포함하는 게이트 TCP(108)들을 구비한다.

- <23> 액정패널(106)은 각종 신호라인들과 함께 박막트랜지스터 어레이가 형성된 하부기판(102)과, 칼라필터 어레이가 형성된 상부기판(104)과, 하부기판(102)과 상부기판(104) 사이에 주입된 액정을 포함한다. 이러한 액정패널(106)에는 게이트라인들(GL)과 데이터라인들(DL)의 교차영역마다 마련되는 액정셀들로 구성되어 화상을 표시하는 화상표시영역이 마련된다. 화상표시영역의 외곽부에 위치하는 하부기판(102)의 외곽영역에는 데이터라인(DL)으로부터 신장되어진 데이터 패드들과, 게이트라인(GL)로부터 신장되어진 게이트 패드들이 위치한다. 또한 하부기판(102)의 외곽영역에는 게이트 드라이브 IC들(110)에 공급되는 게이트 구동신호들(GSP, GSC, GOE 신호 등)을 전송하기 위한 LOG형 신호라인군(126)이 위치한다.

- <24> 데이터 TCP들(112) 각각에는 데이터 드라이브 IC(114)가 실장되고, 그 데이터 드라이브 IC(114)와 전기적으로 접속된 입력패드들 및 출력패드들이 형성된다. 데이터 TCP들(112)의 입력패드들은 데이터 PCB(116)의 출력패드들과 전기적으로 접속되고, 출력패드들은 하부기판(102) 상의 데이터패드들과 전기적으로 접속된다.

- <25> 수 개의 데이터 TCP(112) 중 적어도 어느 하나, 예컨대 첫번째 데이터 TCP(112)는 하부기판(102) 상의 LOG형 신호라인군(26)에 전기적으로 접속되는 게이트 구동신호 전송군(124)을 추가적으로 포함한다. 이 게이트 구동신호 전송군(124)은 데이터 PCB(116)를 경유하여 타이밍 콘트롤러(120) 및 전원공급부(124)로부터 공급되는 게이트 구동신호들(GSP, GSC, GOE 신호 등)을 LOG형 신호라인군(126)에 공급한다.

- <26> 이러한 LOG형 신호라인군(126)은 게이트 TCP(108)에 형성된 입력 게이트 구동신호 전송라인군(126)과 연결되어, 타이밍 콘트롤러(120)로부터 공급되는 게이트 구동신호들(GSP, GSC, GOE 신호 등)을 게이트 드라이브 IC(110)에 공급한다. 다시 말해, LOG형 신호라인군(126)은 통상 게이트 하이 전압신호(VGH), 게이트 로우 전압신호(VGL), 공통전압 신호(VCOM), 그라운드 전압신호(GND), 전원 전압신호(VCC)와 같은 전원공급부(도시하지 않음)로부터 공급되는 구동전압신호들과 타이밍 콘트롤러(120)로부터 공급되는 게이트 스타트 펄스(GSP), 게이트 쉬프트 클럭신호(GSC), 게이트 이네이블 신호(GOE)와 같은 게이트 구동신호들(GSP, GSC, GOE 신호 등) 각각을 공급하는 신호라인들로 구성된다. 이러한 LOG형 신호라인군(126)에는 공통전압(VCOM)을 공급하는 공통라인이 포함된다.

- <27> 이러한 LOG형 신호라인군(126)은 둘 이상의 레이어를 이용하여 형성하는 것을 특징으로 한다. 이를 도 3 및 도 4를 참조하여 살펴보면 다음과 같다.

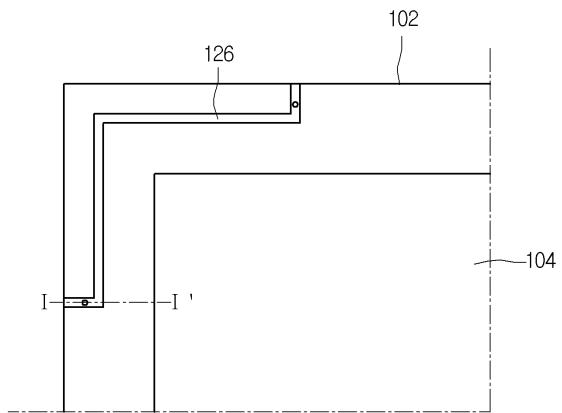

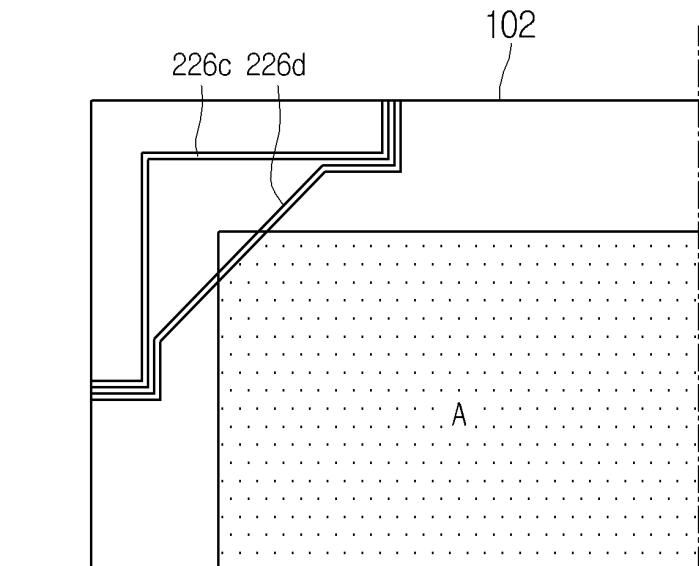

- <28> 도 3은 도 2에 표현된 'A' 영역에 대한 확대도이고, 도 4는 도 3의 I-I'에 대한 단면도이다.

- <29> 본 발명의 실시예에서 LOG형 신호 라인군(126)은 게이트 금속층과 데이터 금속층에 형성된 것을 도시하였다. 즉, 도 3 및 도 4에서 보는 바와 같이 LOG형 신호라인군(126)은 게이트 금속층에 형성된 제1 LOG형 신호라인군(126a)과 데이터 금속층에 형성된 제2 LOG형 신호라인군(126b)을 포함하고, 제1 및 제2 LOG형 신호라인군은 콘택홀(170)을 통하여 서로 접속된다.

- <30> 도 5a 내지 도 5f를 참조하여, 본 발명의 박막트랜지스터 기판을 형성하는 방법을 살펴보면 다음과 같다.

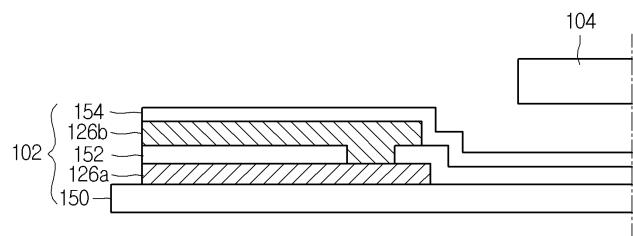

- <31> 먼저 도 5a와 같이 베이스 기판(150)에 크롬(Cr), 몰리브덴(Mo), 알루미늄계 금속 등을 이용하여 증착방법을 시

행함으로써 게이트 금속층(162)을 형성한다.

- <32> 이어서, 게이트 금속층(162)에 레지스트 물질을 도포하고, 도 3에 나타난 LOG형 신호라인군(126)과 동일한 형태의 패턴을 포함하는 마스크를 레지스트 물질상에 정렬한다. 이어서, 레지스트 물질을 선택적으로 패터닝하여 형성되는 레지스트 패턴을 마스크로 하여, 게이트 금속층(162)을 선택적으로 식각함으로써 제1 LOG형 신호라인 군(126a)을 형성한다. 이때, 표시영역에 해당하는 액티브 영역에는 게이트 전극과 게이트 라인 및 제1 스토리지 전극이 형성된다.

- <33> 이어서, 도 5b와 같이 게이트 금속층(162)에 형성된 제1 LOG형 신호라인군(126a) 및 각종 패턴들을 덮도록 게이트 금속층(162) 위에 게이트 절연막(152)을 형성한다. 게이트 절연막(152)은 플라즈마 화학기상 증착방법 (Plasma Enhanced Chemical Vapor Deposition ; PECVD) 등을 이용하여 형성할 수 있다.

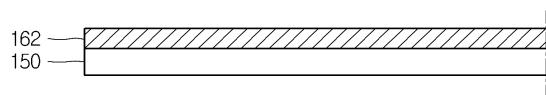

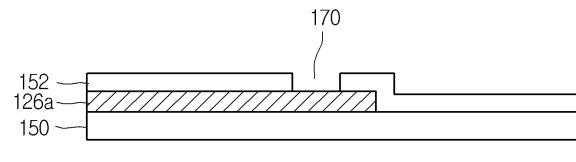

- <34> 그리고, 도 5c와 같이 제1 LOG형 신호라인군(126a)이 일부 노출되도록 콘택홀(170)을 형성한다. 콘택홀(170)은 마스크를 이용한 사진 식각 공정을 시행함으로써 형성할 수 있다.

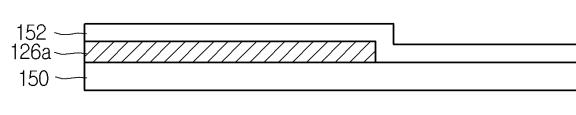

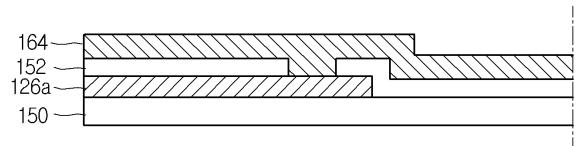

- <35> 콘택홀(170)을 형성한 다음에 도 5d와 같이 콘택홀(170)을 채우면서 데이터 금속층(164)을 형성한다. 데이터 금속층(164)으로 이용되는 금속은 구리(Cu), 크롬(Cr), 몰리브덴(Mo), 티타늄(Ti), 탄탈륨(Ta), 몰리브덴 합금 (Mo alloy) 또는 이를 중 두 개 이상의 혼합금속등이 있다.

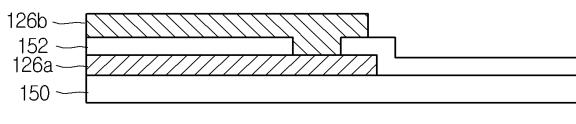

- <36> 이어서, 제1 LOG형 신호라인군(126a)을 형성하는 것과 마찬가지로 데이터 금속층(164)을 선택적으로 식각하여 도 5e에서와 같이 제2 LOG형 신호라인군(126b)을 형성한다. 이때, 액티브 영역에는 데이터 라인 및 소스/드레인 전극이 형성된다.

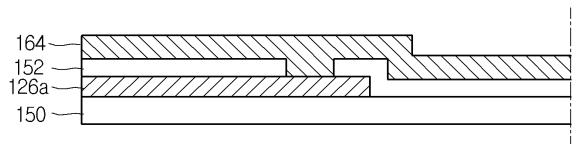

- <37> 그리고 도 5f와 같이 데이터 금속층(164)위에 절연막(154)을 형성한다.

- <38> 그리고 도시하지는 않았지만 화소전극을 형성하기 위하여 절연막(154)에 ITO, TO, IZO, ITZO 등의 금속을 스퍼터링 등의 방법으로 증착하여 투명도전막을 형성한다.

- <39> 이처럼 LOG형 신호라인군(126)을 복수로 형성할 경우 외부의 물리적 충격에 의해 일부가 단선되더라도 다른 LOG형 신호라인군을 통해 신호를 인가하는 것이 가능하다.

- <40> 전술한 실시예는 LOG형 신호라인군을 복수개로 형성하고 각각의 LOG형 신호라인군은 중복되는 실시예에 대해서 기술하였다.

- <41> 한편, 본 발명의 다른 실시예로서는 LOG형 신호라인군을 분리하여 형성할 수도 있다. 이처럼 LOG형 신호라인군을 분리하여 형성할 경우에는 도 6에서 보는 것처럼 일부의 LOG형 신호라인(126d)을 상부기판이 합착될 영역(A) 내에 형성할 수도 있다.

- <42> 하부기판의 외곽 모서리에 LOG형 신호라인군(126c)은 물리적 충격에 약하기 때문에 상부기판이 합착될 영역(A) 내에 LOG형 신호라인군(126d)을 형성하는 것이 유리하지만 공간 마진 부족 등의 이유로 전체적인 LOG형 신호라인군을 'A'영역 내부에 형성하기에는 난점이 있다. 하지만 LOG형 신호라인군을 분리할 경우에는 일부를 상부기판이 합착될 영역(A) 내에 형성할 수 있다.

- <43> 이처럼 LOG형 신호라인의 일부, 예컨대 절곡부위를 상부기판이 합착될 영역(A) 내에 형성함으로써 물리적 충격에 의해 LOG형 신호라인의 과손을 줄여서 불량 발생을 감소시킬 수 있다.

### 발명의 효과

- <44> 상술한 바와 같이, 본 발명에 의한 박막트랜지스터 기판 및 이의 형성방법에 의하면 LOG형 신호라인군의 단선으로 인한 불량 발생을 감소시킬 수 있다. 또한, 본 발명의 다른 실시예에 의한 박막트랜지스터 기판 및 이의 형성방법에 의하면 LOG형 신호라인군을 분리하여 형성함으로써 그 일부를 상부기판과 합착되는 영역내에 형성할 수 있다. 이에 따라, LOG형 신호라인의 일부가 패널 내부에 가깝게 형성됨으로써 라인 과손의 경우를 좀 더 줄일 수 있다.

- <45> 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여 쳐야만 할 것이다.

### 도면의 간단한 설명

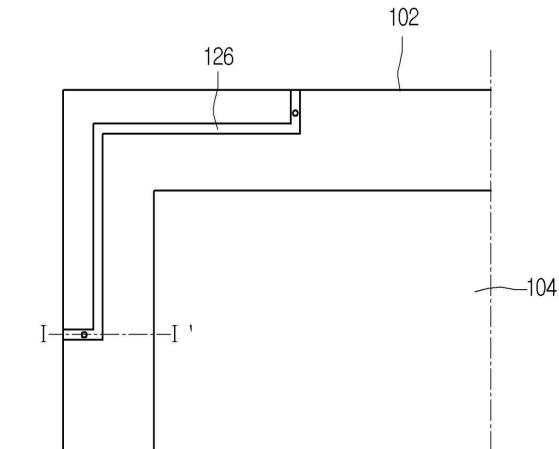

- <1> 도 1은 종래의 라인-온-글래스 방식의 박막트랜지스터 기판의 일부를 나타내는 도면.

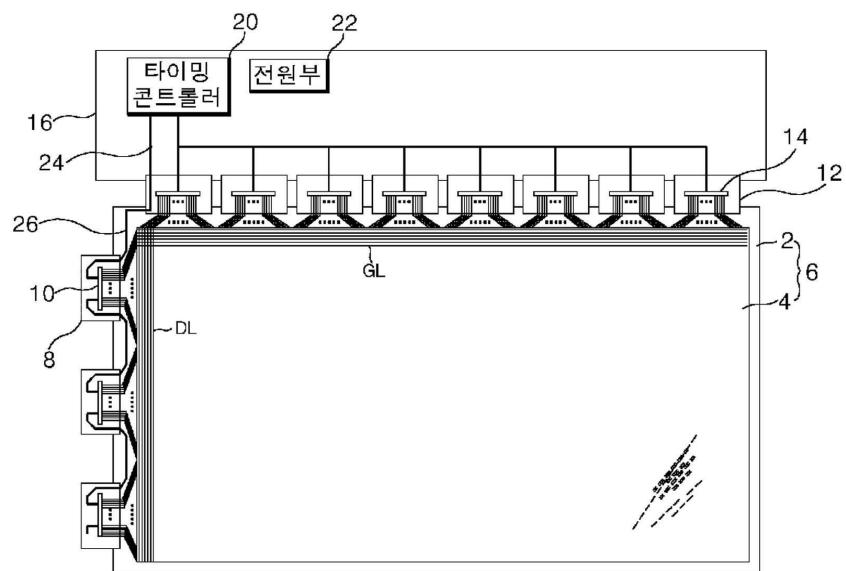

- <2> 도 2는 본 발명에 의한 액정표시장치를 나타내는 도면.

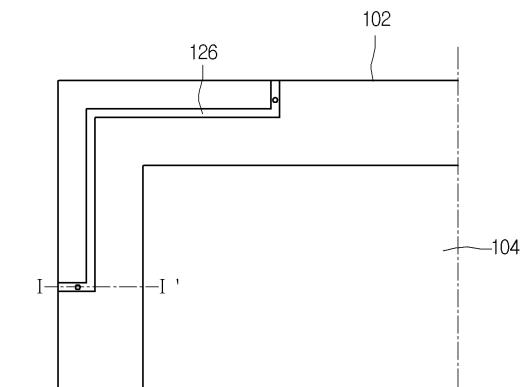

- <3> 도 3은 본 발명에 의한 액정표시장치의 박막트랜지스터 기판의 일부를 나타내는 도면.

- <4> 도 4는 본 발명에 의한 박막트랜지스터 기판의 단면을 나타내는 도면.

- <5> 도 5a 내지 도 5f는 본 발명에 의한 박막트랜지스터 기판의 형성방법을 나타내는 도면.

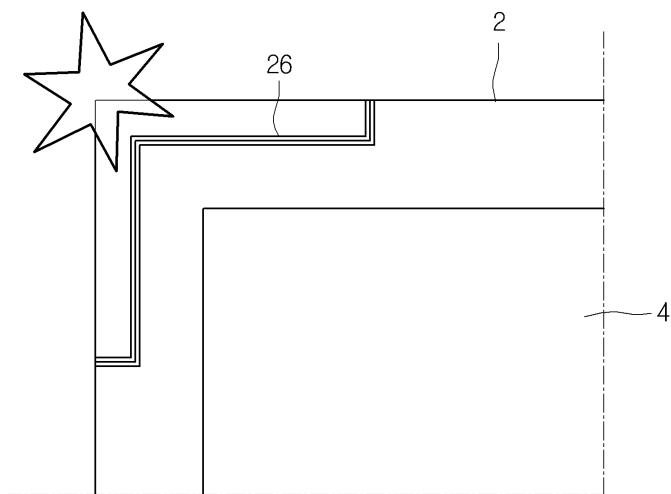

- <6> 도 6은 본 발명의 다른 실시예에 의한 박막트랜지스터 기판의 일부를 나타내는 도면.

## 도면

### 도면1

### 도면2

도면3

도면4

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면6

|                |                                                         |         |            |

|----------------|---------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的薄膜晶体管基板及其形成方法                                    |         |            |

| 公开(公告)号        | <a href="#">KR1020080104636A</a>                        | 公开(公告)日 | 2008-12-03 |

| 申请号            | KR1020070051668                                         | 申请日     | 2007-05-28 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                               |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                               |         |            |

| [标]发明人         | PAIK SANG YOON<br>백상윤<br>CHO MYUNG JUN<br>조명준           |         |            |

| 发明人            | 백상윤<br>조명준                                              |         |            |

| IPC分类号         | G02F1/133 G02F1/136                                     |         |            |

| CPC分类号         | G02F1/1362 G02F1/13458 G02F1/1368 G09G3/3614 G09G3/3648 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                               |         |            |

### 摘要(译)

液晶显示装置的薄膜晶体管基板本发明涉及液晶显示装置的薄膜晶体管基板。根据本发明的薄膜晶体管基板包括基础基板，形成在基础基板上的第一金属层和第二金属层，其间具有绝缘层，形成在第一金属层上的栅极线，形成在第二金属层上的数据线，用于驱动栅极线的栅极驱动电路，以及由栅极驱动电路产生的驱动信号，用于向栅极线提供在基础衬底上的两个或更多个不同层上形成的多条数据线和一组玻璃上线型栅极驱动信号线。