(19) (KR)

(12) (A)

(51)

(11)

(43)

2003 - 0020513

2003 03 10

(21) 10 - 2001 - 0052492

(22) 2001 08 29

3 416

(72)

70 4 210 40 4

(74)

(54)

가

가

■

1 2

1 2

1 2

1 2

가

1

가

가

,

가

2

, ,

1

2 1

3

4 2

가

, ,

가

, ,

가

가 ,

가

가

,

가

가

(ACF; anisotropic conducting film)

circuit)

가

(FPC:flexible printed

가

가

가

COG(Chip on Glass)

가

COG

2

가

가

가

가

가

가

가

가

가

1 2

가

,  $\frac{1}{n}$  ,  $\frac{1}{k}$  ,  $\frac{1}{k+1}$  ,  $\dots$  ,  $\frac{1}{n}$  ,  $\frac{1}{k}$  ,  $\frac{1}{k+1}$  ,  $\dots$

FPC

가 가

, 1 2 가 ;

가 .

, , , 가 ; ; ;

, ; ;

, 1 2 ;

가 ;

가 가 ;

1

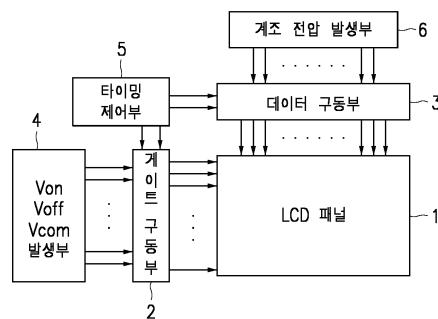

, 1 , LCD (1), (2),

(3), Von Voff Vcom (4), (5) (6) , LCD (1)

(3) (2) 가 가 .

LCD (1) ,

가

, (3) LCD (1)

, (3) (5)

가 LCD (1) (LOAD ) 가

(2) (3) 가

(1) TFT (Thin Film Transistor) . LCD

(Von, Voff) 가 , TFT ,

. Von Von Voff Vcom (4) Von, Voff Voff TFT Von Von Voff Vcom (4)

. Von Voff Vcom (5) (2) ,

(6) (2, 3) 가 (3) 가 , , , , ,

2 1 가

2 , 1 , LCD (1)

(200) (110) 가 ;

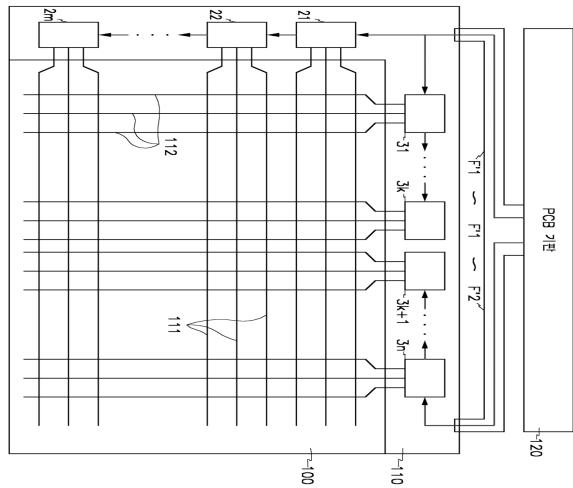

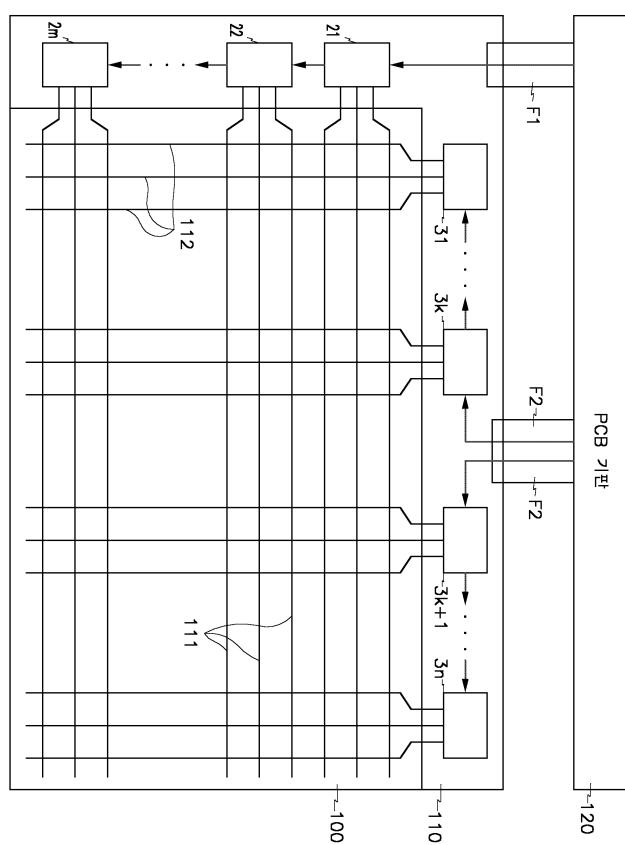

1 3n) (21 2m) 가 (31 3k, 3k+)

(112) 가 (110), (111),

(3) (2) (110) COG

(F) (120) . ,

(F) (120) (F1), (120) (F2), (F1, F2) (ACF; anisotropic c

1 2 . 1 2 (110) (110) .

$$1 \quad (F1) \quad , \quad (110)$$

$$(2) \quad (3)$$

$$1, \quad 1, \quad , \quad , \quad , \quad n$$

$$1 \quad (31) \quad , \quad ,$$

$$1 \quad (21) \quad .$$

$$\begin{array}{ccccccccc}

, & 1 & & (F1) & & & & 1 & \\

& (31) & & . & & & & (21) & \\

, & & & & 1 & & & & 2 \\

& & & & m & & & & \\

& & & & & (2m) & & & \\

& & & & & . & & & \\

\end{array}$$

가  $1, 1, (31, 3k, 3k+1, 3n), n$

$k, (3k), n, (3n)$

$k+1, (3k+1), K, 0 < k < n$

$k=n/2$

1 4 " A, B, C, D" 가 . , " E, F, G, H" 2

" E" 가 5 " F" 가

6 5 8 " E, F, G, H" 가 .

1 2 , 1 8

가 .

(31 3k, 3k+1 3n) 가 LCD (1) , (5) 가

LCD (1) , (2)

가

1 , 가

, 가 , 가

2

3 2

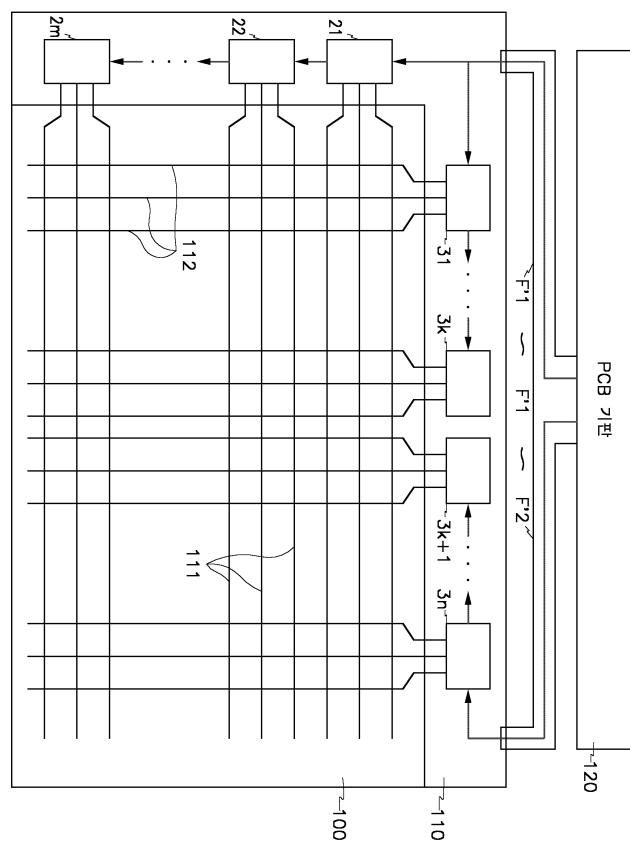

$$\begin{array}{ccccccccc} 2 & & 2 & & 1 & & & & \\ (200) & , & (110) & 가 & , & (112) & , & & (10) \\ \text{가} & (31 \ 3k, 3k+1 \ 3n) & (111) & & \text{가} \\ (21 \ 2m)\text{가} & . & & & \end{array}$$

$$2 \quad \begin{matrix} (F) & (120) \\ (F1) & (120) \\ (F2) & , \end{matrix} \quad , \quad (110)$$

$$\begin{matrix} 1 & & & & (110) \\ (2) & (F1) & & & \\ & & (110) & & \\ & & & 2 & (F2) \\ & & & (3) & \end{matrix}$$

$$\begin{array}{ccccccccc}

, & 2 & & (F2) & & 1 & & 1 & & 2 & & 2 \\

& , & 1 & & & & 1 & & n & & & (3) \\

k) & & & & , & 2 & & k+1 & & (3k+1) & & k

\end{array}$$

1 , 1 (F1) 가 1 (21) ,

1 , m (2m) .

2 2 (F2) 1 2 가 k (3k) k+1

(3k+1) , 1 2 1 .

1 (31) n (3n) .

1 , (31 3k, 3k+1 3n) 가 , 1

, 2 .

, 2 .

$$\begin{array}{ccccccccc}

, & 2 & & (F2) & & 1 & & k & (3k) & 1 \\

(31) & , & 2 & & (F2) & & 2 & & k+1 & (3k+1) \\

n & & (3n) & & . & & K & 1 < k < N (k, n) & ) & , \\

& & & & & & & & & n/2

\end{array}$$

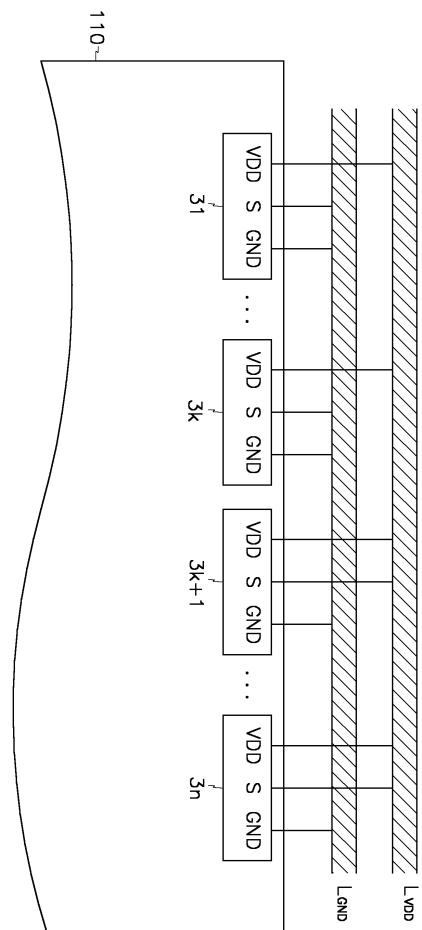

1 VDD GND 가

|                 |   |                 |      |                           |               |        |

|-----------------|---|-----------------|------|---------------------------|---------------|--------|

| 2               | , | 1               | (31) | n                         | (3n)          | 가      |

|                 | , | (5)             | 1    |                           | 2             |        |

| .               | , | 1               | ,    | " A, B, C, D, E, F, G, H" |               | , " A, |

| B, C, D"        | 1 | " A, B, C, D"   | ,    |                           | " A" 가        | 4      |

|                 | 1 |                 | ,    | " B" 가                    | 2             |        |

| 1               | 4 | " A, B, C, D" 가 | .    | ,                         | " E, F, G, H" | 2      |

|                 |   | " H" 가          | 5    |                           |               | 8      |

| ,               |   | " G" 가          | 7    |                           | 5             | 8      |

| " E, F, G, H" 가 | . |                 |      |                           |               |        |

1 2 가 ,

(2) 가 .

2 , 1 , 가

, , , 가

LVDS(low voltage differential signaling) RSDS(reduced sw

ing differential signaling) , 가

가 가

가

# 가 가

가

(57)

1.

가

;

가

;

,

,

1 2

가

2.

1

,

가 n

, 2

1

n

n

,

k

,

n

n

k+1

, k 0 &lt; k &lt; n

3.

1

,

1

,

2

4.

가

;

가

,

;

,

,

1

2

가

5.

4

,

$\frac{n}{k}$

$, \quad 2$

1

k+1

n

,

k

k

,

k+1

k+1

n

$, \quad k \quad 0 < k < n$

6.

4

,

1

2

,

7.

1

4

,

,

8.

1

4

,

9.

1

4

,

FPC

10.

1 4

LVDS (low voltage differential signaling)

11.

1 4

RSDS(reduced swing differential signaling)

12.

가

•

;

가

1 2

가

■

13.

12

가 n

k

1

k+1

n

$$, \quad k \quad 0 < k < n$$

n

14.

12

1

2

15.

가

;

,

1 2

가

;

가

.

16.

15

,

k

가 n

, k

,

k+1

k+1

n

, k 0 &lt; k &lt; n

17.

15

,

1

, 2

.

1

2

3

|                |                                        |         |            |

|----------------|----------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器及其驱动方法                            |         |            |

| 公开(公告)号        | <a href="#">KR1020030020513A</a>       | 公开(公告)日 | 2003-03-10 |

| 申请号            | KR1020010052492                        | 申请日     | 2001-08-29 |

| [标]申请(专利权)人(译) | 三星电子株式会社                               |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                               |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                               |         |            |

| [标]发明人         | MOON SEUNG HWAN<br>문승환                 |         |            |

| 发明人            | 문승환                                    |         |            |

| IPC分类号         | G09G3/36 G02F1/1345 G02F1/133 G09G3/20 |         |            |

| CPC分类号         | G09G3/3648 G09G3/3611 G09G2300/0426    |         |            |

| 其他公开文献         | KR100767365B1                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>              |         |            |

## 摘要(译)

本发明涉及液晶显示装置及其驱动方法。根据本发明的液晶显示器包括多条栅极线和相应数据线的栅极驱动集成电路，用于向数据驱动器提供栅极电压，数据驱动器包括提供对应于灰度电压的倍数的数据驱动集成电路。在相应的栅极线上，它对应于基板上的每条栅极线，它形成在基板上，其中数据线形成在每个行和列方向上。这里，在将分级数据输入到数据驱动器的第一和第二数据驱动集成电路之后，它被移位到第一和第二数据驱动集成电路的中间方向，或者它被移位到第一和第二数据驱动集成电路的中心相反方向。将分级数据输入到数据驱动器的第一和第二数据驱动集成电路之后。根据本发明，高速数据传输数据信号被提供给双重类型，并且在液晶显示器中移位，其中可以并行地布置多个数据驱动器。并且根据布线电阻的减小，可以在每个数据驱动器中发送相同电平的数据信号。液晶显示器，高速数据传输，和。